ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA

MAÎTRISE EN GÉNIE ÉLECTRIQUE

M. Ing.

PAR

Simon NOIROT

COMMANDÉ PAR FPGA :

DE LA MODÉLISATION À L'IMPLÉMENTATION

MONTRÉAL, LE 6 JUIN 2012

©Tous droits réservés, Simon Noirot, 2012

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE :

M. Christian Belleau, directeur de mémoire

Département de génie mécanique à l'École de technologie supérieure

M. Jean-François Boland, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Maarouf Saad, membre du jury

Département de génie électrique à l'École de technologie supérieure

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 14 MAI 2012

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

Je tiens à remercier M. Christian Belleau d'avoir accepté de me diriger dans le cadre mon mémoire. Ses conseils avisés et sa disponibilité m'ont permis d'apprendre énormément. Il a su me guider tout en me laissant libre dans mes choix et m'a fourni des ressources essentielles qui m'ont permis de m'épanouir dans mon projet.

Je tiens à saluer le département de génie électrique de l'INSA de Lyon qui a rendu possible mon cursus en double diplôme au sein de l'ETS. Je remercie également l'ÉTS pour la qualité de la formation que j'y ai reçue et pour m'avoir accordé une bourse interne.

Je remercie aussi tout ceux qui ont partagé ma vie au cours de ces derniers mois. D'abord, mon colocataire de toujours, Cyril, avec qui j'ai vécu cette aventure. Il reste, je m'en vais, ainsi va la vie. Une pensée également à Romain et Nicolas pour tous les bons moments passés ensemble. Ensuite, Rémi, avec qui nous avons fait des parties de foot endiablées et avons dévoré des tonnes de bagels !

Je remercie ma mère, que j'aime, et qui m'a toujours soutenu et encouragé au cours de mes études.

Enfin, je souhaite remercier Elise pour son soutien et son amour et, avec qui nous avons pris le pari un peu fou de vivre notre histoire malgré le temps et la distance.

# **COMMANDÉ PAR FPGA : DE LA MODÉLISATION À L'IMPLÉMENTATION**

Simon NOIROT

## **RÉSUMÉ**

Dans un monde où s'accroît la complexité des systèmes électromécaniques, des applications de plus en plus performantes sont exigées. La commande de tels systèmes doit donc pouvoir répondre à ces attentes. L'évolution des technologies numériques permet aujourd'hui de disposer de composants efficaces, reconfigurables. Le développement au cours de ces dernières années d'outils logiciels intégrés à haut niveau d'abstraction permet à un nombre croissant de concepteurs d'utiliser des circuits numériques de pointe. Les FPGA profitent de ces évolutions et sont des candidats de choix pour la réalisation de modules de commande performants.

Après avoir défini un système d'étude et en avoir donné sa modélisation mathématique, il est possible de passer à la phase de développement. En bénéficiant de l'outil HDL Coder intégré au sein de Matlab/Simulink, il est possible d'obtenir du code HDL à partir de schémas de modélisation de haut niveau. Dans un premier temps, un régulateur de type PID est proposé. Ensuite une commande plus élaborée est définie. La commande moderne, par ses calculs matriciels importants, permet de bénéficier de la puissance de calcul des FPGA. Enfin, une démarche de conception à base de modèles est proposée.

La méthodologie de conception à base de modèles couplées à la mise en place d'une bibliothèque de composants réutilisables permet de disposer de modèles à la fois simulable et synthétisable dans un FPGA. L'implémentation d'un PID, en utilisant l'arithmétique distribuée, permet d'obtenir des résultats intéressants. L'implantation d'un PID au sein d'un FPGA peut se réaliser rapidement et aisément comme peuvent le proposer d'autres méthodes, tel xPC Target. La mise en place de l'arithmétique distribuée au sein d'une commande dans l'espace d'état afin d'économiser les ressources du FPGA à disposition a montré ses limites. En effet, l'accumulation d'erreurs pourtant faibles ne permet pas de disposer d'un système stable. La raison est due, notamment, à un système d'étude peut propice au calcul numérique à point fixe. Il a également été montré que dans le cadre de la commande dans l'espace d'état, la résolution des convertisseurs jouait un rôle primordial. Une résolution trop faible produisant une erreur statique sur l'estimation des états provoquant la divergence de la boucle de commande. Enfin il a été possible de mettre en œuvre une bibliothèque de composants réutilisables et flexibles qui, utilisée dans une conception à base de modèles, permet de réduire le temps de mise sur le marché de façon significative.

**Mots-clés :** FPGA, Matlab/Simulink, HDL Coder, PID, commande moderne, conception à base de modèles, bibliothèque, commande

# **COMMANDÉ PAR FPGA : DE LA MODÉLISATION À L'IMPLÉMENTATION**

Simon NOIROT

## **ABSTRACT**

In a world where electro-mechanical systems are more and more complex has come an increasingly need of performances for this kind of applications. The evolution of digital technologies gives a set of components that can meet these requirements. Over the last years the development of electronic computer-aided design softwares has made FPGAs good candidates to enhanced the performances of controllers.

Once the model is described mathematically, the development process can start. It is possible to use an high level graphical model to generates HDL code by using the Matlab/Simulink Toolbox HDL Coder. First a classical PID controller is developped. Then a modern control technique is designed. FPGAs'computational ability is used to perform the required matrix multiplications. We also propose the model-based design as an other modeling approach.

The model-based design methodology as well as the development of a reusable and flexible components' library give models that can be both simulated and synthetized. A PID controller with distributed arithmetic gives great performances and presents a time to market equivalent to xPC Target for instance. The use of distributed arithmetic in the state space context has shown its limits. One reason for that result is that the system use is not « computational-friendly ». Also it has been shown that the resolution of converters has a great impact on the system stability and more particularly on the states estimation. Finally a library has been developped that enables the end-user to focus on the system level design. The massive use of flexible and reusable components associated with model-based design reduces significantly the time to market.

**Keywords :** FPGAs, Matlab/Simulink, HDL Coder, PID, modern control, model-based design, library, control

## TABLE DES MATIÈRES

|                                                                                     | Page      |

|-------------------------------------------------------------------------------------|-----------|

| INTRODUCTION .....                                                                  | 1         |

| <b>CHAPITRE 1 REVUE DE LITTÉRATURE .....</b>                                        | <b>9</b>  |

| 1.1 Field Programmable Gate Array (FPGA).....                                       | 9         |

| 1.2 Notions fondamentales .....                                                     | 10        |

| 1.2.1 Historique.....                                                               | 10        |

| 1.2.2 Concepts.....                                                                 | 12        |

| 1.2.3 Constitution interne.....                                                     | 14        |

| 1.2.4 Démarche de conception .....                                                  | 17        |

| 1.3 Conception de systèmes à base de FPGA.....                                      | 18        |

| 1.3.1 Comment utiliser les FPGA ? Quels sont les outils à notre disposition ? ..... | 19        |

| 1.3.2 Domaine d'utilisation.....                                                    | 21        |

| <b>CHAPITRE 2 CONCEPTION DES SYSTEMES DE COMMANDE .....</b>                         | <b>25</b> |

| 2.1 Notions fondamentales .....                                                     | 25        |

| 2.1.1 La transformée de Laplace.....                                                | 25        |

| 2.1.2 La transformée en Z .....                                                     | 27        |

| 2.1.3 Modélisation des systèmes physiques, fonction de transfert .....              | 28        |

| 2.1.4 Représentation des fonctions de transfert .....                               | 30        |

| 2.2 Dynamique et placement des pôles .....                                          | 32        |

| 2.3 Contrôleur Proportionnel-Integral-Dérivé (PID).....                             | 38        |

| 2.3.1 Descriptif du PID .....                                                       | 38        |

| 2.3.2 Discrétisation du contrôleur PID.....                                         | 39        |

| 2.4 Commande dans l'espace d'état .....                                             | 45        |

| 2.4.1 Représentation de systèmes dans l'espace d'état .....                         | 45        |

| 2.4.2 Commande dans l'espace d'état.....                                            | 50        |

| 2.4.2.1 Observateur d'état.....                                                     | 51        |

| 2.4.2.2 Régime établi .....                                                         | 54        |

| <b>CHAPITRE 3 TRAITEMENT NUMÉRIQUE .....</b>                                        | <b>57</b> |

| 3.1 La gestion numérique des nombres .....                                          | 57        |

| 3.2 Le traitement des opérations numériques .....                                   | 60        |

| 3.2.1 Opérations et fonctionnement .....                                            | 60        |

| 3.2.2 Introduction à l'arithmétique distribuée.....                                 | 63        |

| 3.2.3 Implémentation et taille mémoire .....                                        | 64        |

| 3.2.4 Quantification du gain de l'AD .....                                          | 65        |

| <b>CHAPITRE 4 DESCRIPTION DU SYSTEME.....</b>                                       | <b>67</b> |

| 4.1 Le processus à commander (Banc d'essai).....                                    | 68        |

| 4.2 Dynamique interne à la carte d'évaluation .....                                 | 70        |

| 4.2.1 Description du système de commande .....                                      | 73        |

|                                                                                     |                                                            |            |

|-------------------------------------------------------------------------------------|------------------------------------------------------------|------------|

| 4.2.2                                                                               | Convertisseurs A/N, N/A et conditionnement du signal ..... | 74         |

| 4.2.3                                                                               | Transfert total .....                                      | 77         |

| 4.2.4                                                                               | Contraintes et limitations dynamiques .....                | 78         |

| 4.3                                                                                 | Modélisation du système dans l'espace d'état.....          | 81         |

| <b>CHAPITRE 5      IMPLÉMENTATION DU MODULE PID.....</b>                            |                                                            | <b>85</b>  |

| 5.1                                                                                 | L'AD appliquée au régulateur PID filtré .....              | 85         |

| 5.2                                                                                 | Mise en place des blocs fonctionnels.....                  | 87         |

| 5.2.1                                                                               | L'interface Simulink .....                                 | 88         |

| 5.2.2                                                                               | Implémentation du système de commande type PID .....       | 91         |

| 5.2.2.1                                                                             | Action proportionnelle .....                               | 94         |

| 5.2.2.2                                                                             | Action intégrale.....                                      | 96         |

| 5.2.2.3                                                                             | Action dérivée.....                                        | 100        |

| 5.3                                                                                 | Simulation des actions du PID.....                         | 101        |

| 5.3.1                                                                               | Simulation de l'action proportionnelle.....                | 101        |

| 5.3.2                                                                               | Simulation de l'action intégrale .....                     | 102        |

| 5.3.3                                                                               | Simulation de l'action dérivée.....                        | 103        |

| 5.4                                                                                 | Simulation du système en boucle fermée .....               | 105        |

| 5.5                                                                                 | Résultats expérimentaux .....                              | 107        |

| <b>CHAPITRE 6      IMPLÉMENTATION DE LA COMMANDE DANS L'ESPACE<br/>D'ÉTAT .....</b> |                                                            | <b>113</b> |

| 6.1                                                                                 | Simulation du modèle simplifié.....                        | 113        |

| 6.2                                                                                 | Simulation du système à commande discrète .....            | 117        |

| 6.2.1                                                                               | Discrétisation du procédé .....                            | 117        |

| 6.2.2                                                                               | Système de commande discret .....                          | 118        |

| 6.2.3                                                                               | Système de commande synthétisable .....                    | 121        |

| 6.2.4                                                                               | Système de commande à AD .....                             | 126        |

| 6.2.4.1                                                                             | Construction de l'observateur par AD .....                 | 127        |

| 6.2.4.2                                                                             | Tests en boucle fermée.....                                | 132        |

| 6.3                                                                                 | Résumé .....                                               | 134        |

| <b>CHAPITRE 7      VERS UNE CONCEPTION À BASE DE MODÈLES.....</b>                   |                                                            | <b>135</b> |

| 7.1                                                                                 | Mise en œuvre du MBD .....                                 | 135        |

| 7.1.1                                                                               | MBD pour la commande par PID .....                         | 135        |

| 7.1.2                                                                               | MBD pour la commande dans l'espace d'état .....            | 137        |

| 7.2                                                                                 | Mise en place de la bibliothèque de composants.....        | 141        |

| 7.2.1                                                                               | Modules de gestion des interfaces.....                     | 142        |

| 7.2.2                                                                               | Les organes de commande .....                              | 142        |

| 7.3                                                                                 | Résumé .....                                               | 143        |

| <b>CHAPITRE 8      DISCUSSION .....</b>                                             |                                                            | <b>145</b> |

| 8.1                                                                                 | Commande PID par FPGA .....                                | 145        |

| 8.2                                                                                 | Commande dans l'espace d'état par FPGA .....               | 147        |

| <b>CONCLUSION .....</b>                                                             |                                                            | <b>151</b> |

|               |                                                 |     |

|---------------|-------------------------------------------------|-----|

| ANNEXE I      | UTILISATION DES OUTILS LOGICIELS .....          | 153 |

| ANNEXE II     | COMPLÉMENTS SUR L'ESPACE D'ÉTAT .....           | 159 |

| ANNEXE III    | CIRCUIT D'INSTRUMENTATION .....                 | 165 |

| ANNEXE IV     | GESTION DES TYPES NUMÉRIQUES (POINT FIXE) ..... | 171 |

| ANNEXE V      | PRÉSENTATION DE LA BIBLIOTHÈQUE .....           | 173 |

| BIBLIOGRAPHIE | .....                                           | 177 |

## LISTE DES TABLEAUX

|             | Page                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

| Tableau 3.1 | Addition avec retenue anticipée .....61                                                                                  |

| Tableau 5.1 | Description des étapes de l'AD .....95                                                                                   |

| Tableau 5.2 | Exemple de calcul décimal par AD .....99                                                                                 |

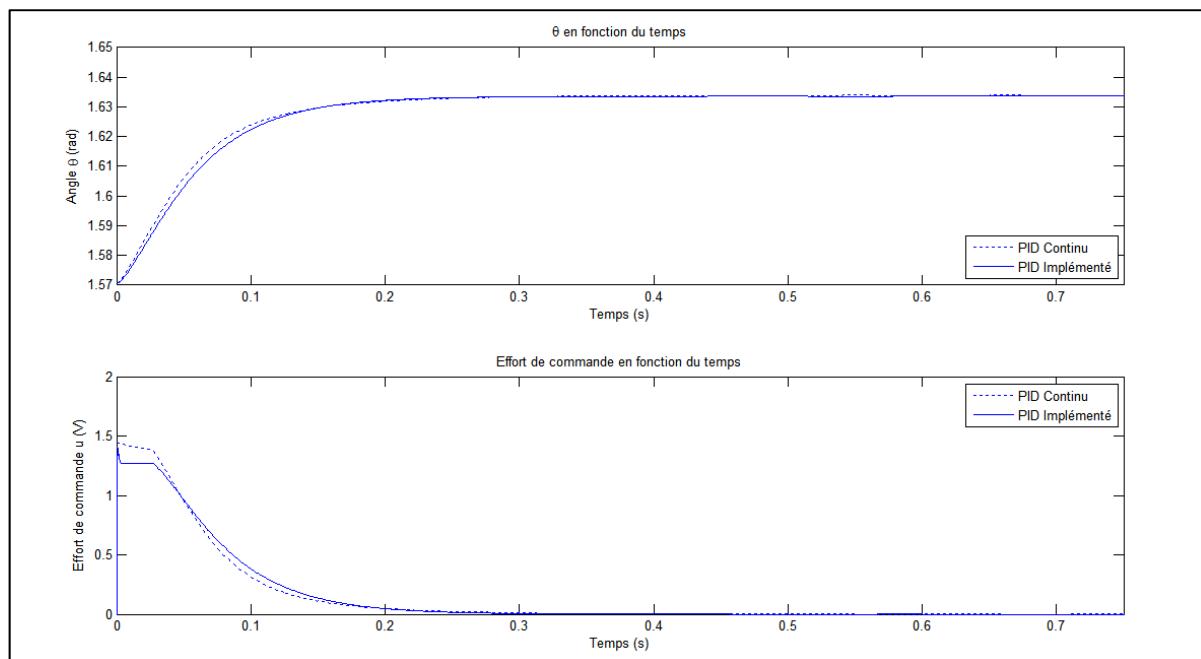

| Tableau 5.3 | Comparaison des grandeurs caractéristiques de la réponse entre PID<br>continu et à AD .....106                           |

| Tableau 5.4 | Résultats de la synthèse du PID implémenté avec AD issus du<br>logiciel ISE .....107                                     |

| Tableau 5.5 | Utilisation des ressources du FPGA pour l'implémentation des modules<br>d'entrées/sorties issus du logiciel ISE .....108 |

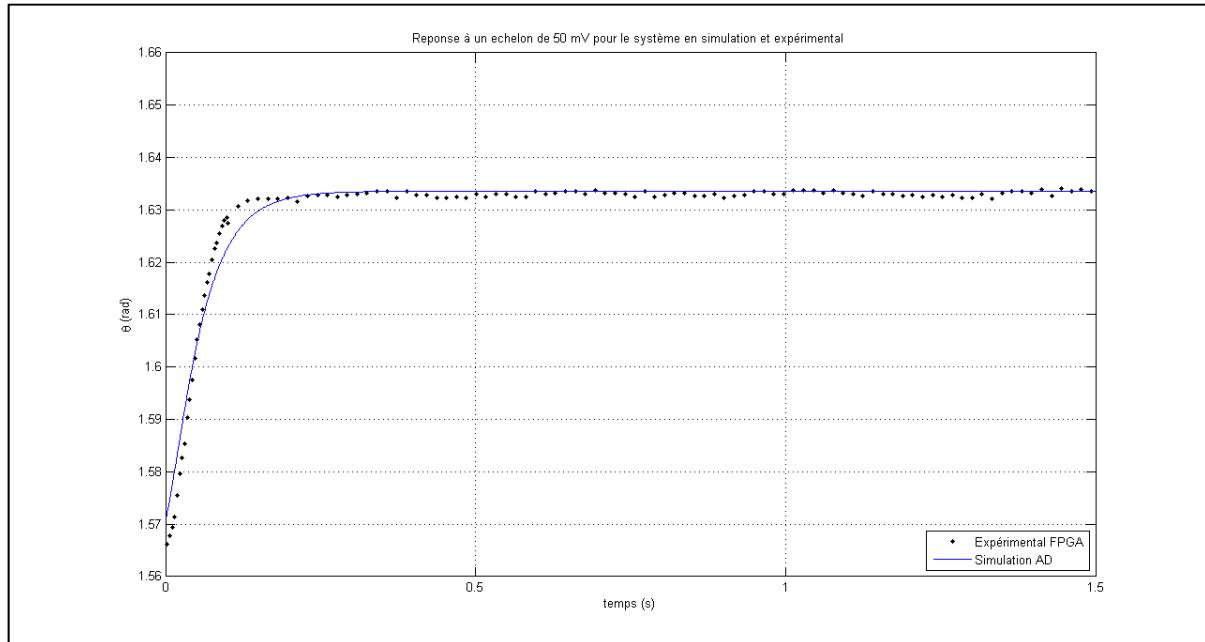

| Tableau 5.6 | Comparaison des grandeurs caractéristiques .....109                                                                      |

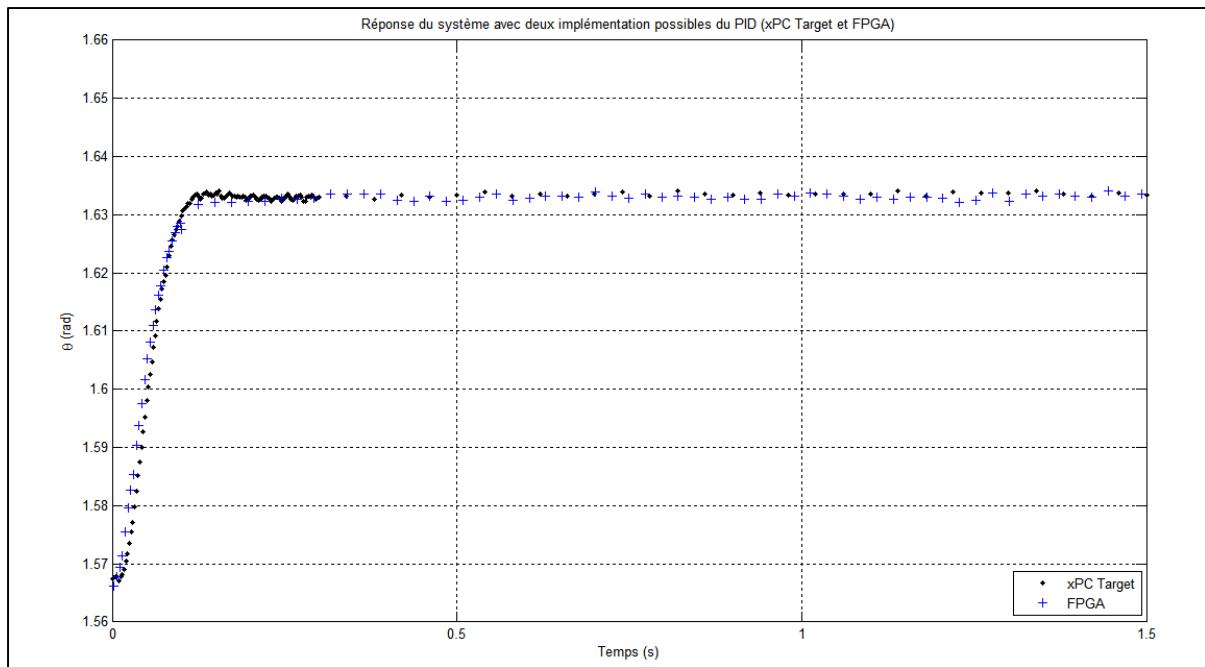

| Tableau 5.7 | Comparaison des caractéristiques entre implémentation via<br>xPC Target et FPGA .....110                                 |

| Tableau 6.1 | Temps caractéristiques de la commande continue .....116                                                                  |

| Tableau 6.2 | Temps caractéristiques du système à commande discrète .....121                                                           |

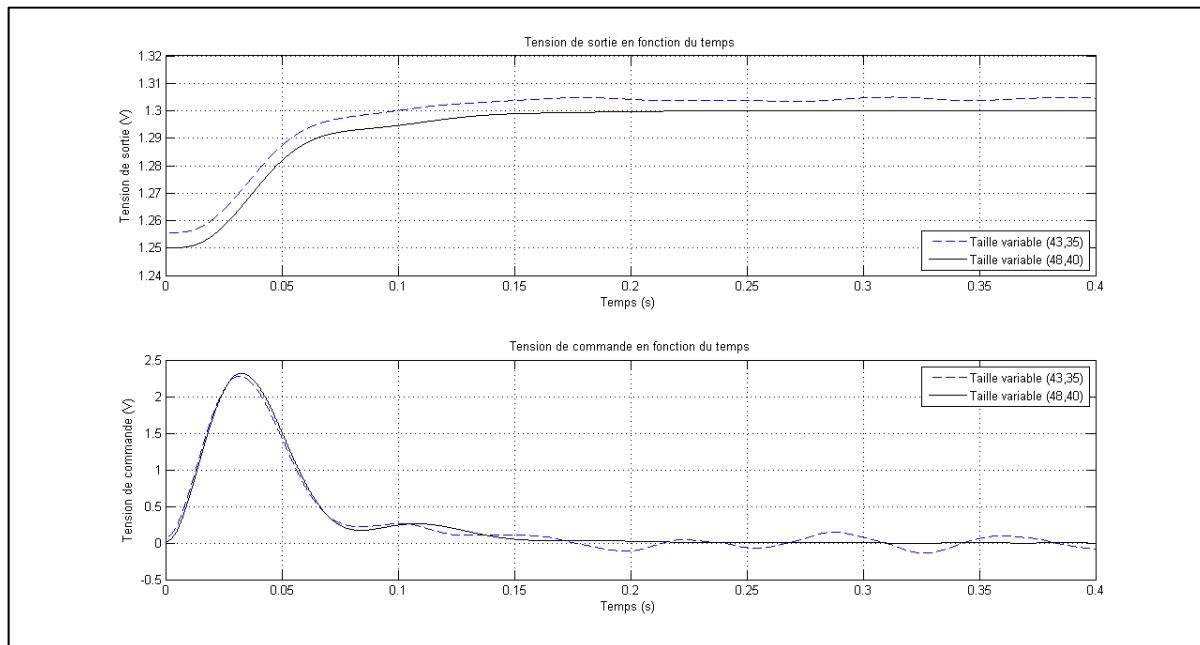

| Tableau 6.3 | Comparaison des temps caractéristiques entre deux précisions de<br>commande synthétisable .....125                       |

| Tableau 6.4 | Résultats de synthèse pour la commande synthétisable avec précision<br>(43,35) issus du logiciel ISE .....125            |

| Tableau 6.5 | Utilisation des ressources du FPGA pour différentes implantations .....132                                               |

## LISTE DES FIGURES

|            | Page                                                                            |    |

|------------|---------------------------------------------------------------------------------|----|

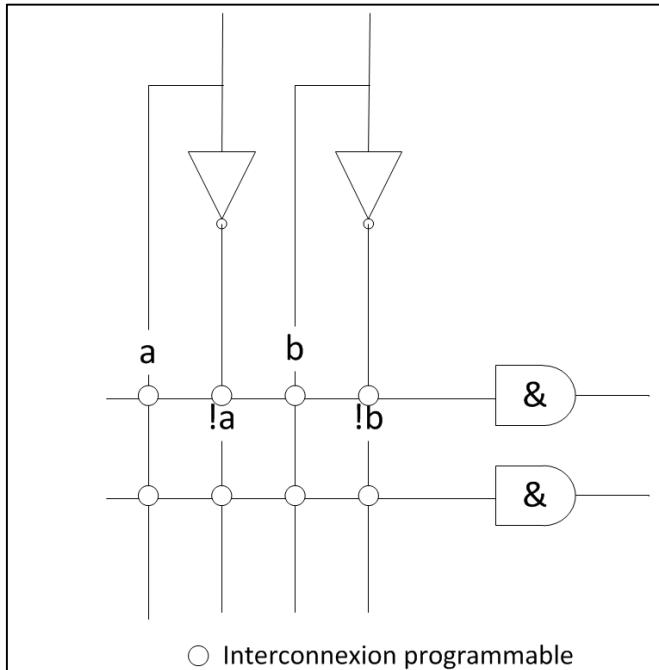

| Figure 1.1 | Principe d'un tableau logique (ou <i>Logic Array</i> ) .....                    | 12 |

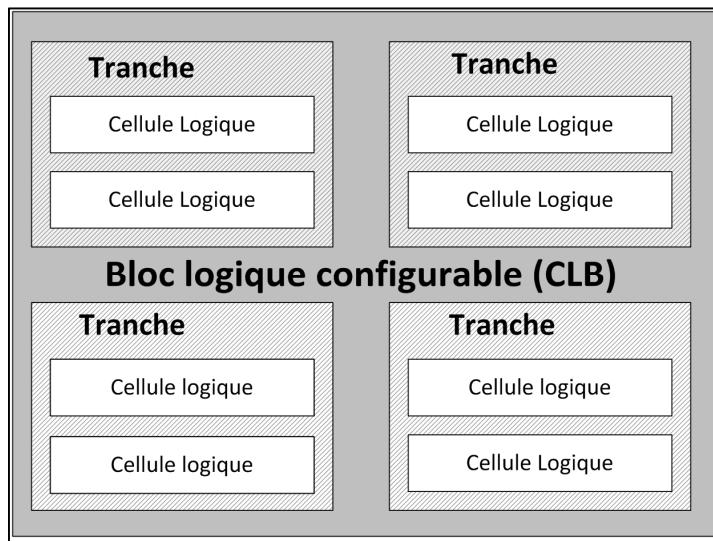

| Figure 1.2 | Structure d'un bloc logique configurable (CLB).....                             | 14 |

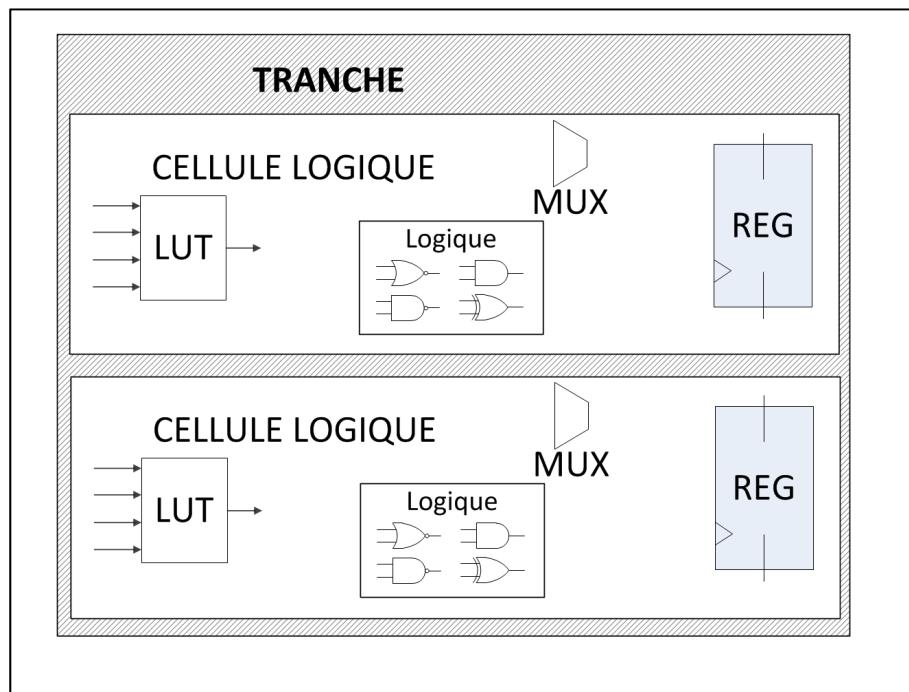

| Figure 1.3 | Détail d'une tranche .....                                                      | 15 |

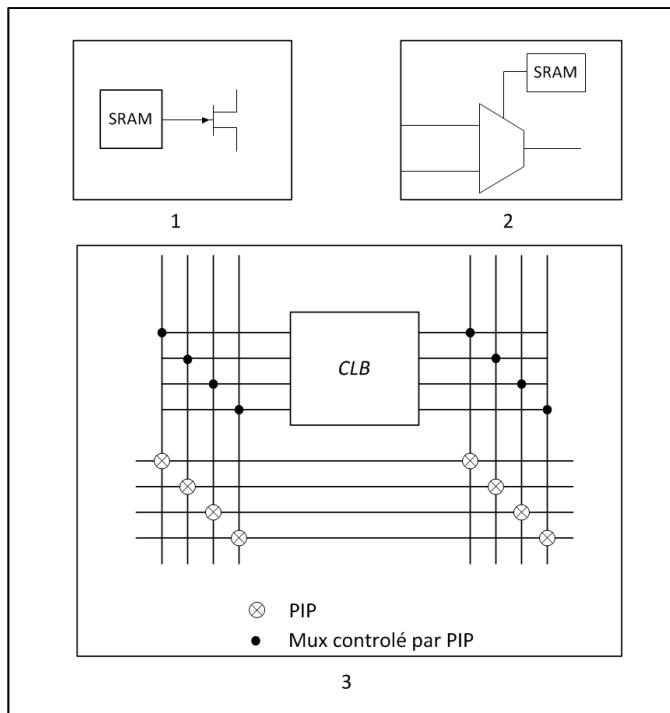

| Figure 1.4 | Points d'Interconnexions Programmables .....                                    | 17 |

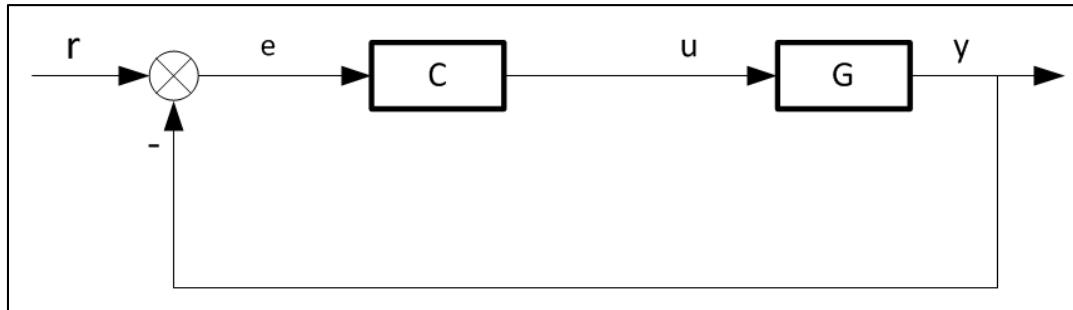

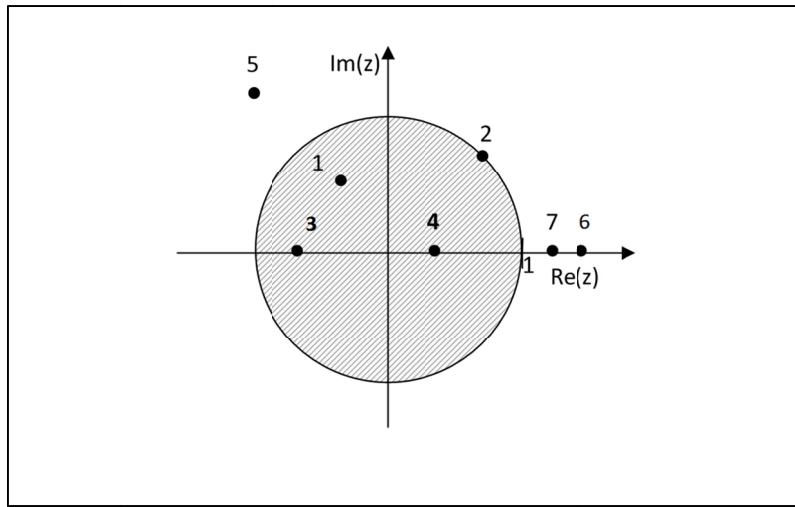

| Figure 2.1 | Schéma d'une boucle de commande à retour unitaire .....                         | 30 |

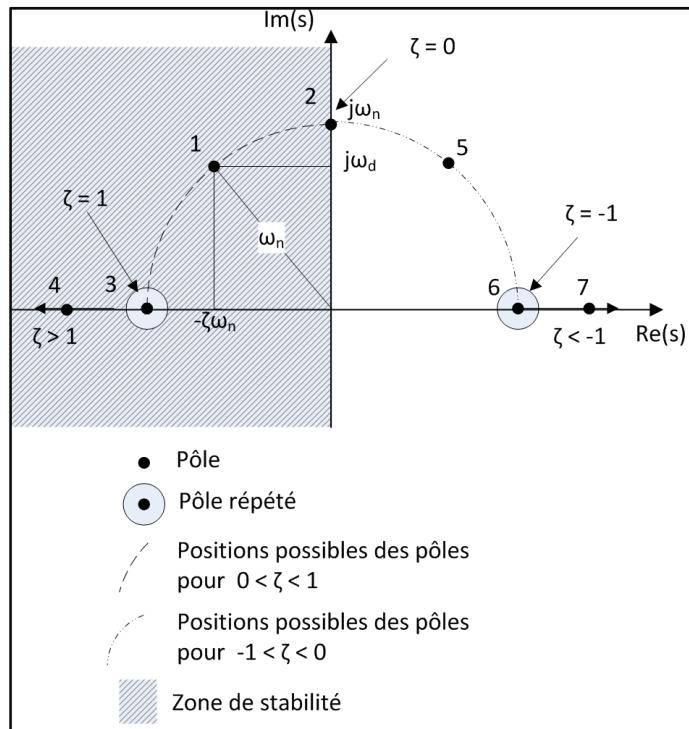

| Figure 2.2 | Position des pôles dans le plan de Laplace.....                                 | 34 |

| Figure 2.3 | Réponse impulsionnelle en fonction de la position des pôles .....               | 35 |

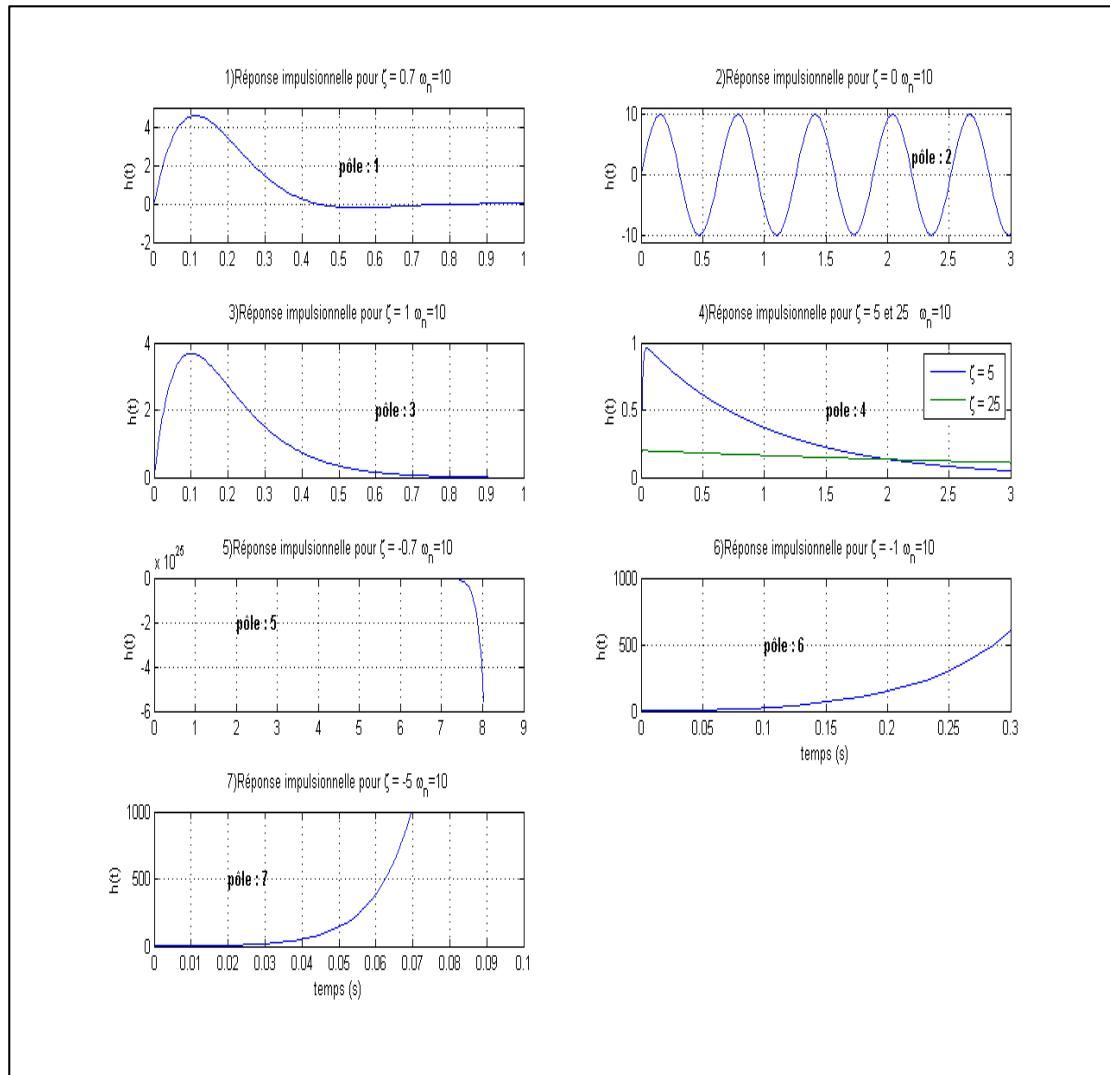

| Figure 2.4 | Positions des pôles dans le plan des Z.....                                     | 38 |

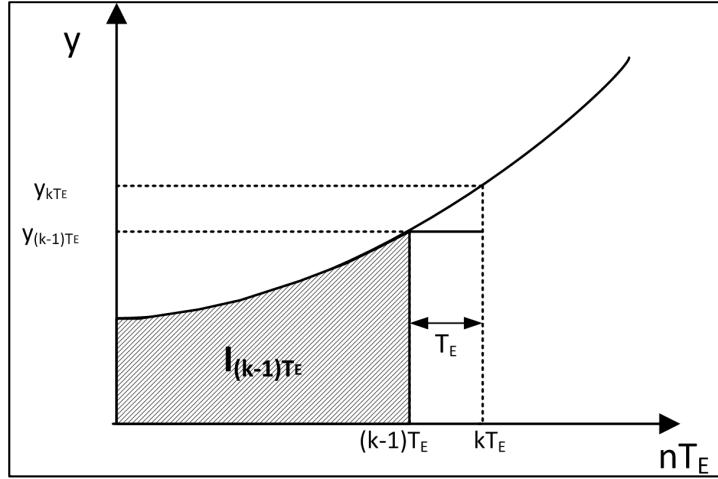

| Figure 2.5 | Principe d'intégration par les différences avant.....                           | 41 |

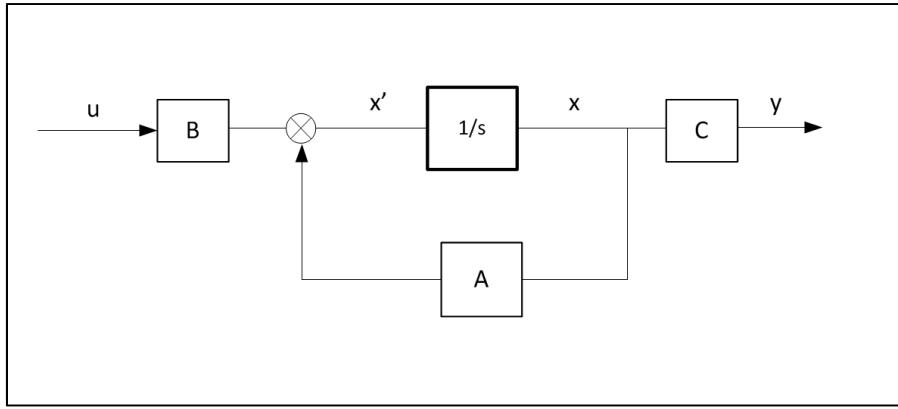

| Figure 2.6 | Représentation d'état d'un système (A,B,C) .....                                | 46 |

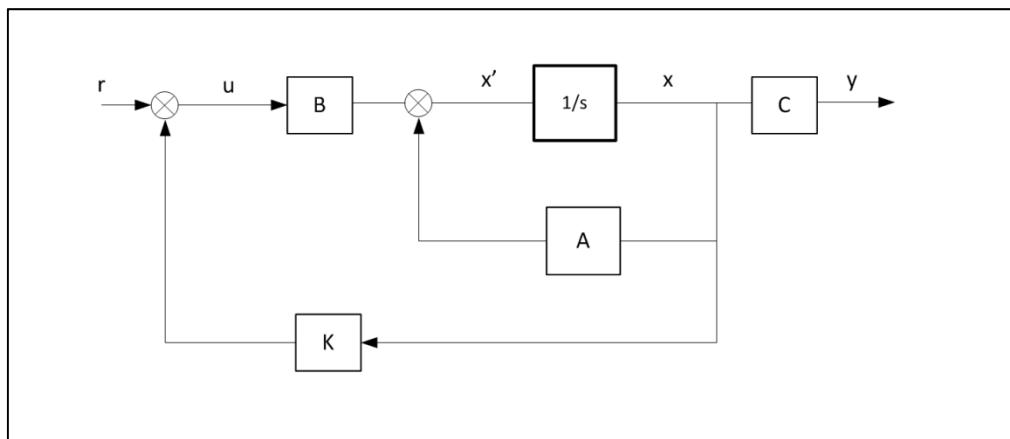

| Figure 2.7 | Représentation d'état avec retour d'état .....                                  | 50 |

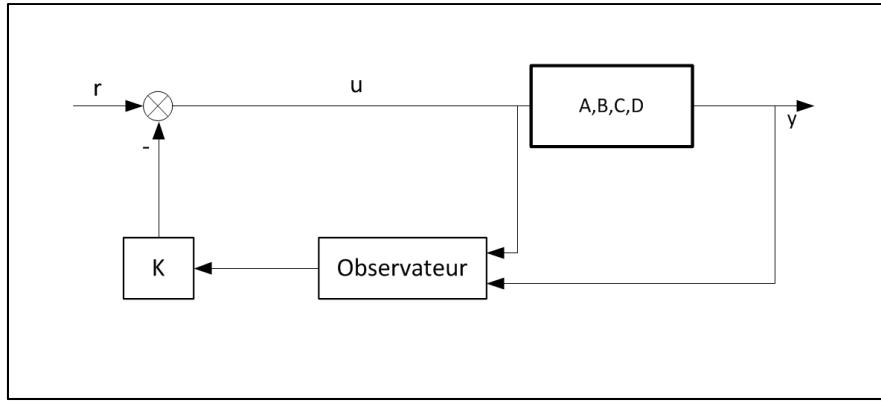

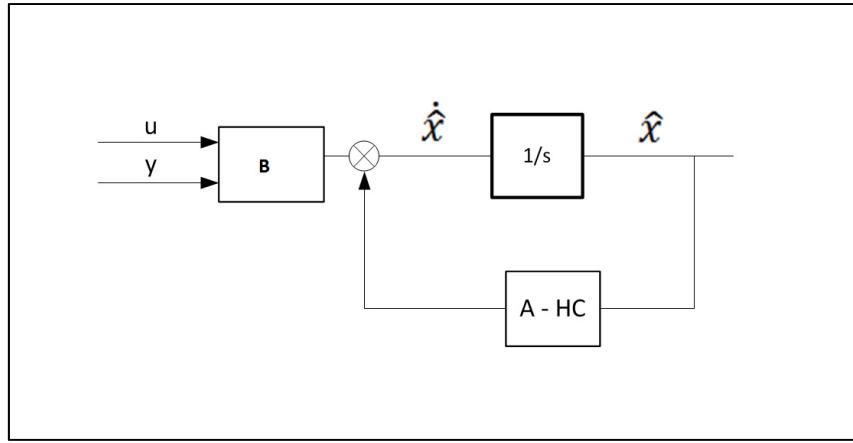

| Figure 2.8 | Système de commande dans l'espace d'état muni d'un observateur .....            | 52 |

| Figure 2.9 | Construction d'un observateur .....                                             | 54 |

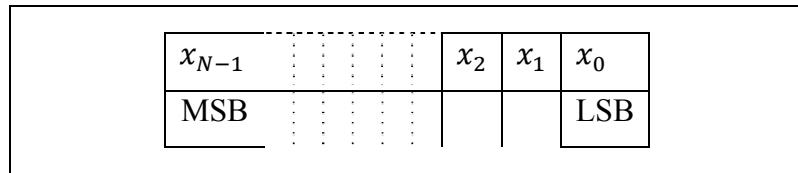

| Figure 3.1 | Représentation numérique à point fixe sur N bits .....                          | 57 |

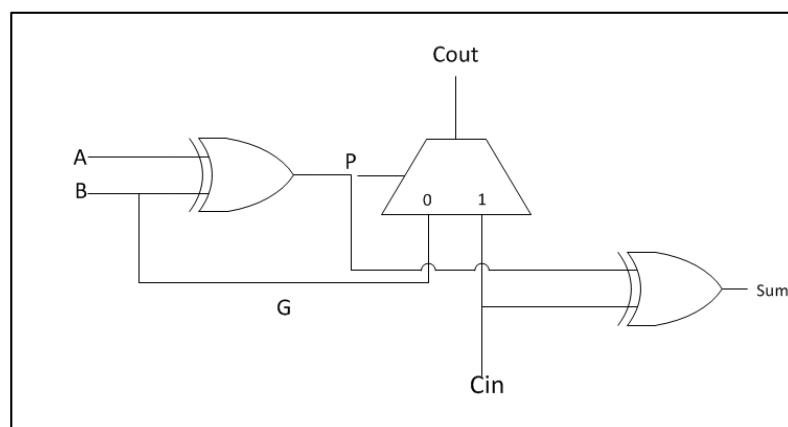

| Figure 3.2 | Implémentation d'une gestion CLA dans un FPGA de type Spartan-3.....            | 61 |

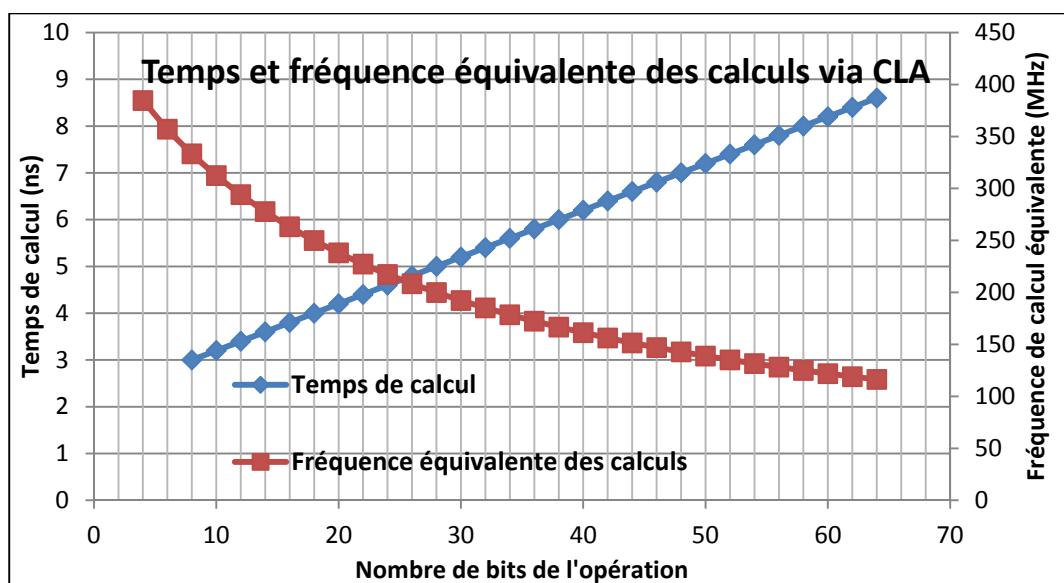

| Figure 3.3 | Temps et fréquence équivalente des calculs effectués<br>via la gestion CLA..... | 63 |

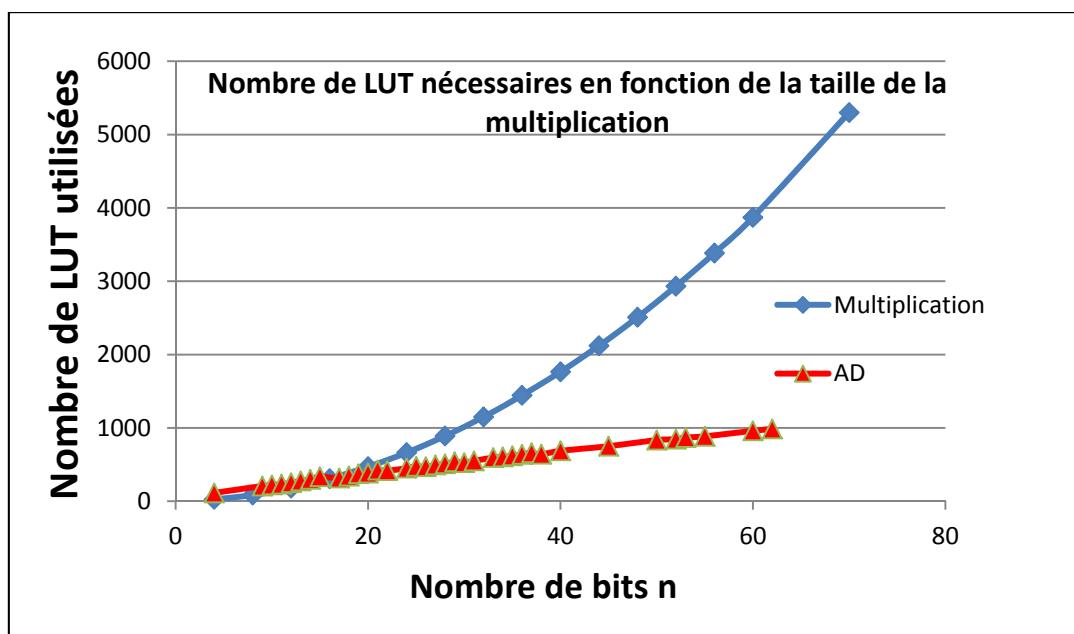

| Figure 3.4 | Utilisation des LUT en fonction de la taille de la multiplication .....         | 66 |

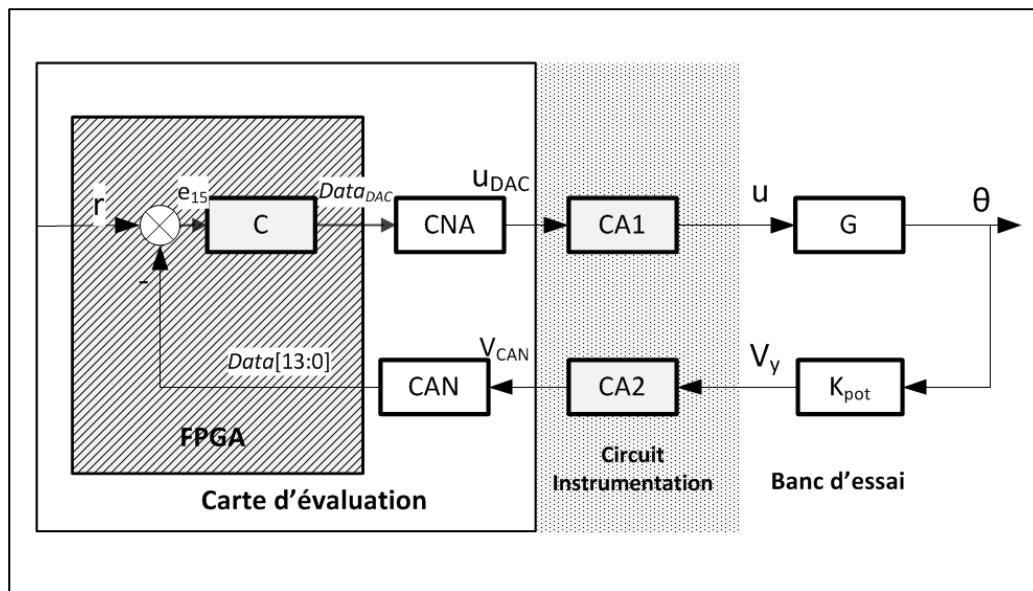

| Figure 4.1 | Boucle de commande globale.....                                                 | 67 |

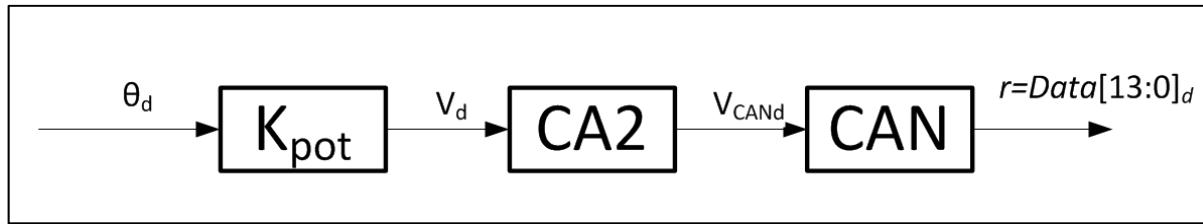

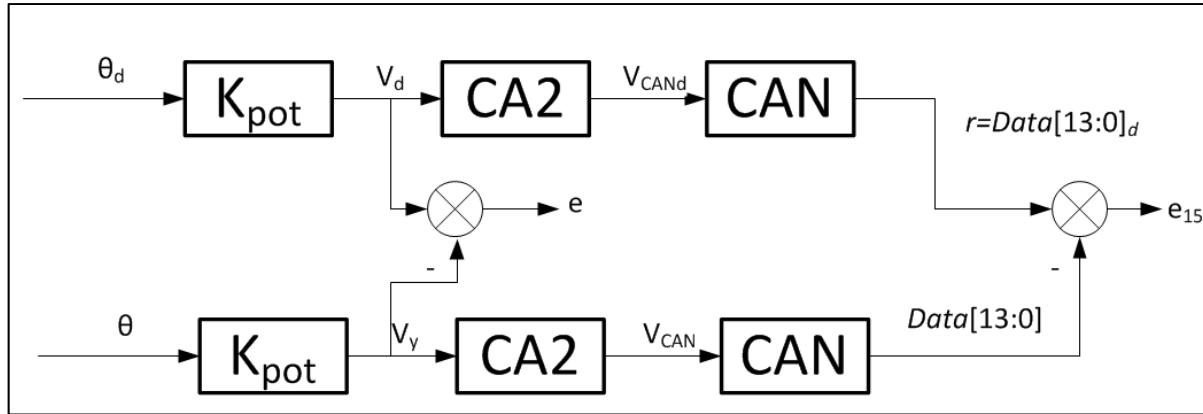

| Figure 4.2 | Traitement de la consigne.....                                                  | 68 |

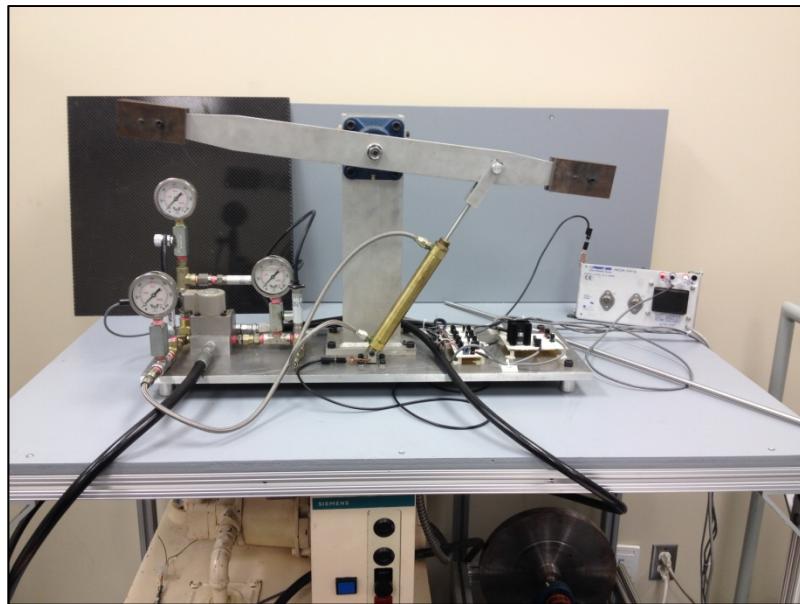

| Figure 4.3 | Banc d'essai .....                                                              | 69 |

|             |                                                                                  |     |

|-------------|----------------------------------------------------------------------------------|-----|

| Figure 4.4  | Représentation de la formation de l'erreur numérique et analogique .....         | 72  |

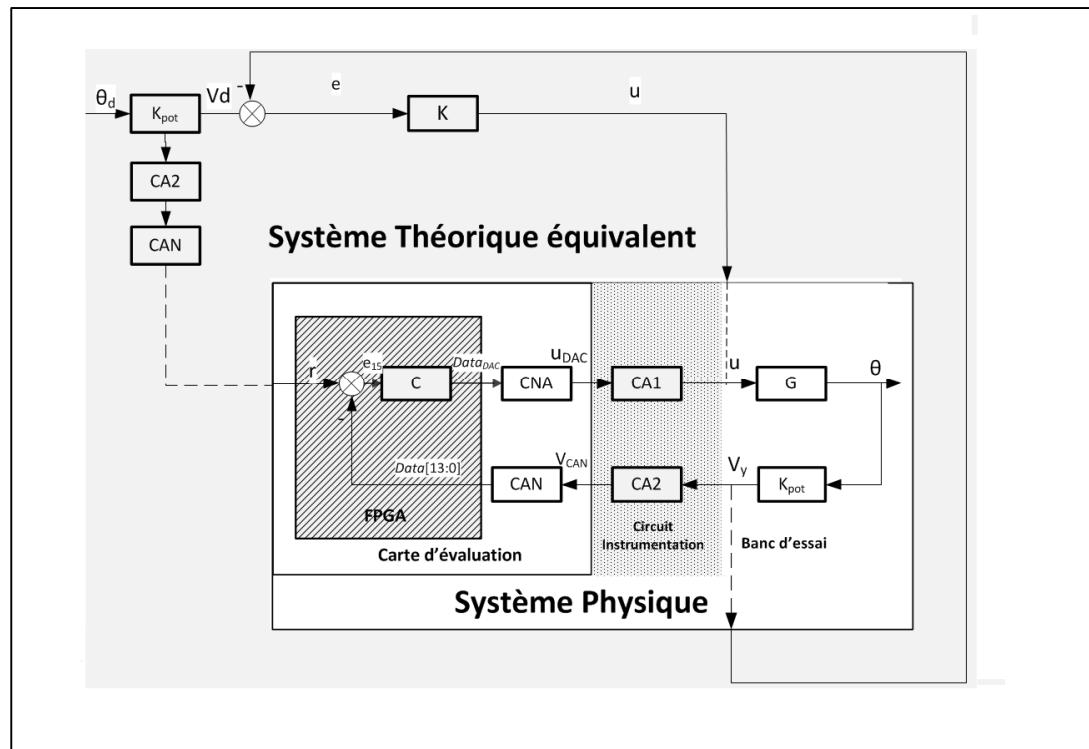

| Figure 4.5  | Représentation physique et abstraite du système .....                            | 73  |

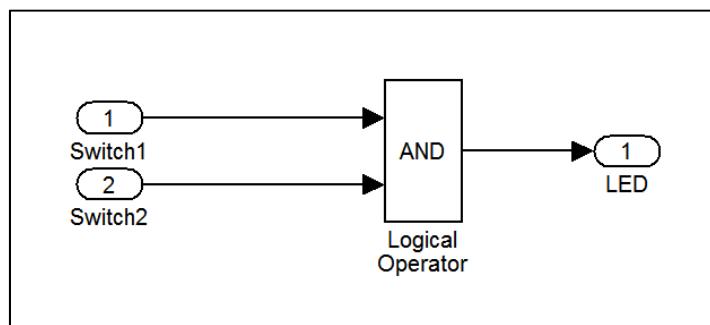

| Figure 5.1  | Implémentation d'une fonction basique sous Simulink .....                        | 88  |

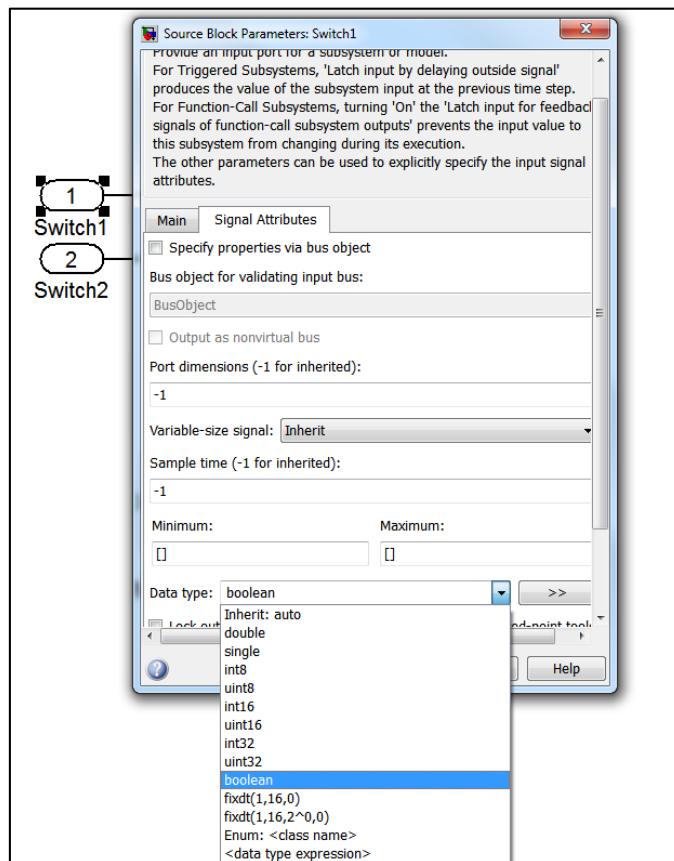

| Figure 5.2  | Choix du type d'un signal .....                                                  | 90  |

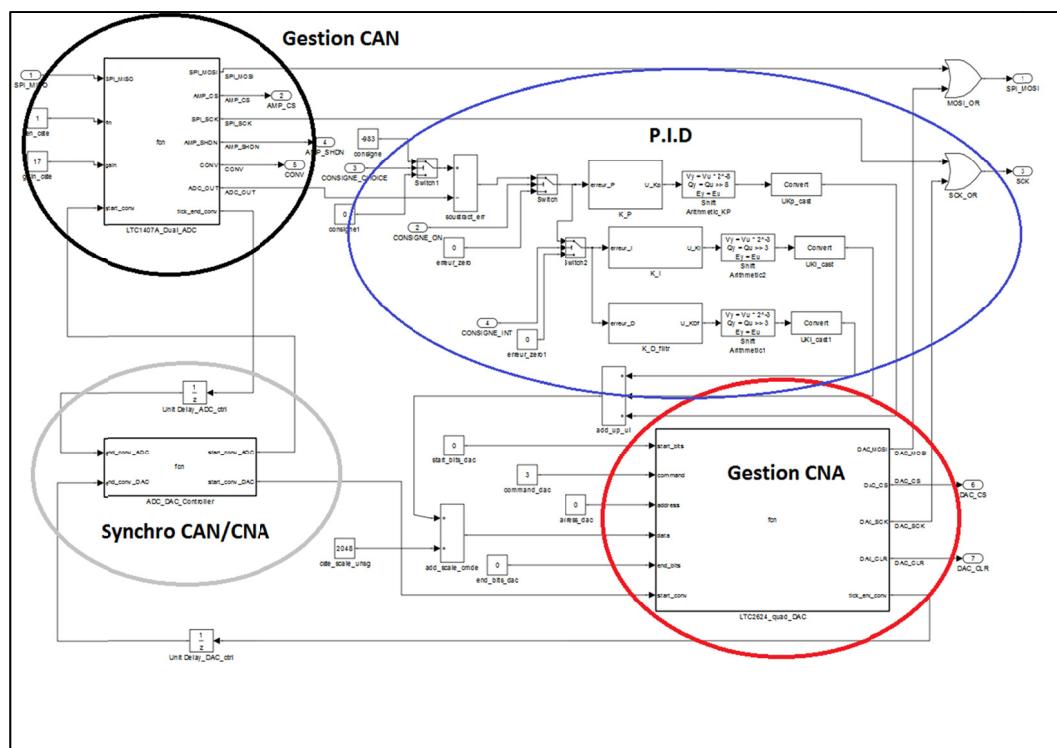

| Figure 5.3  | Schéma Simulink du régulateur PID complet destiné à être synthétisé ....         | 91  |

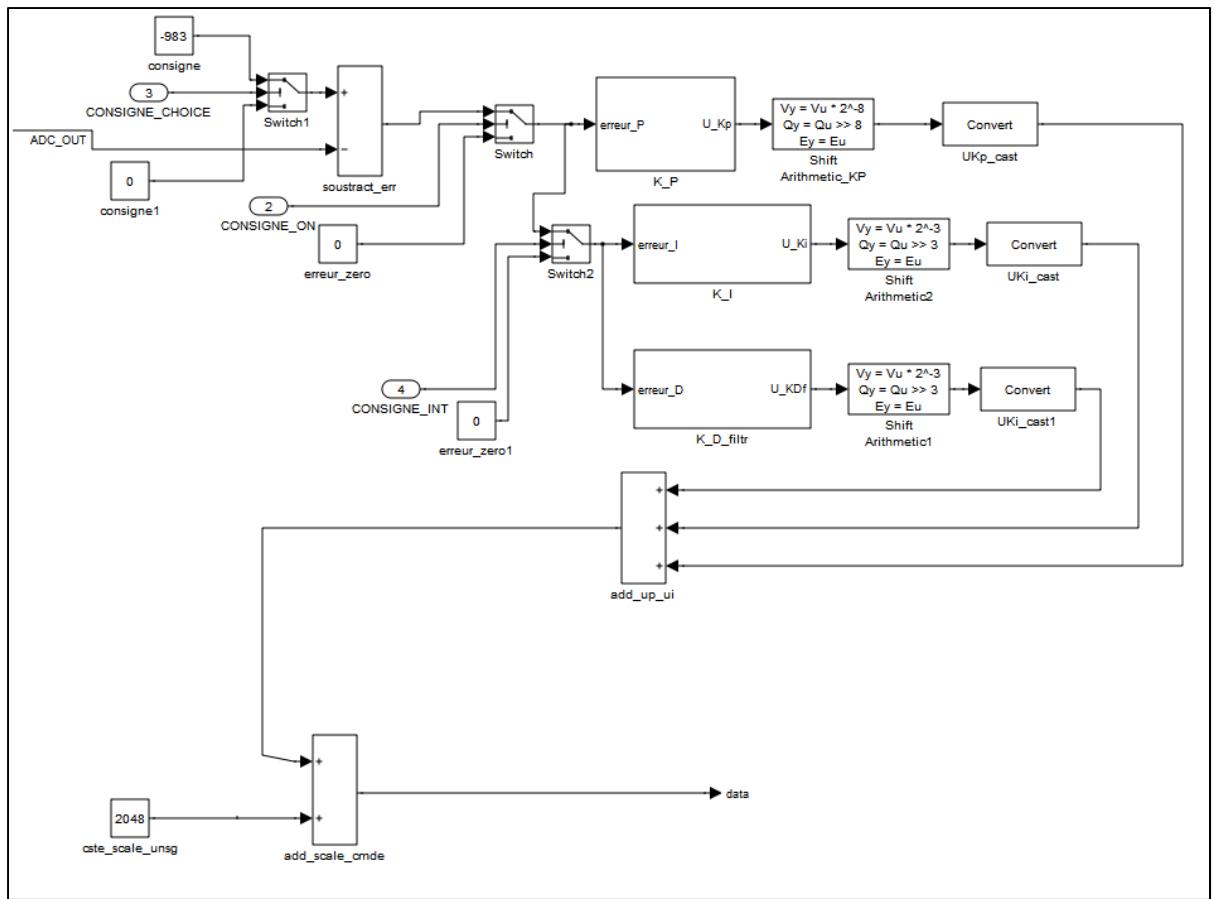

| Figure 5.4  | Schéma Simulink du cœur du régulateur PID .....                                  | 93  |

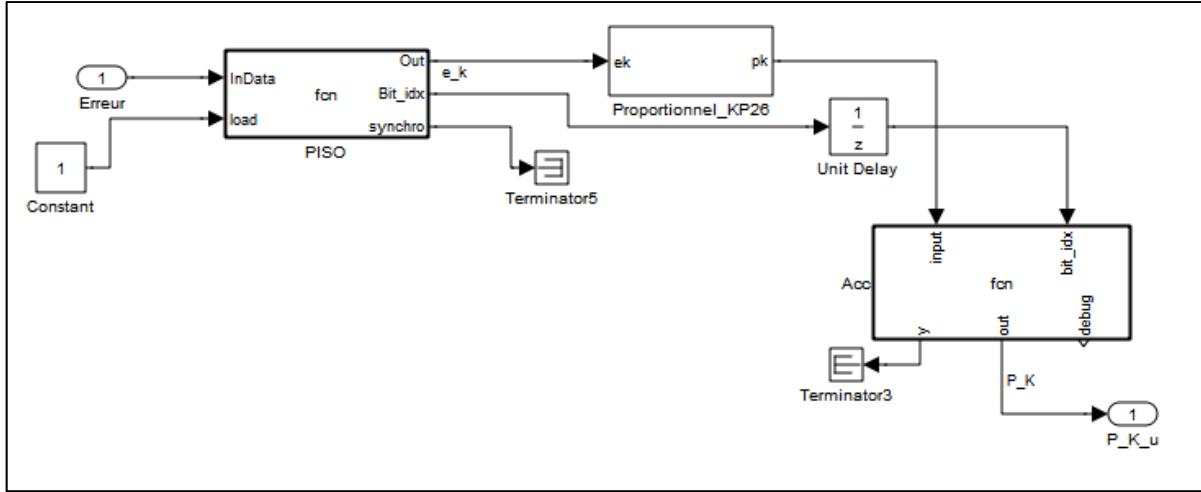

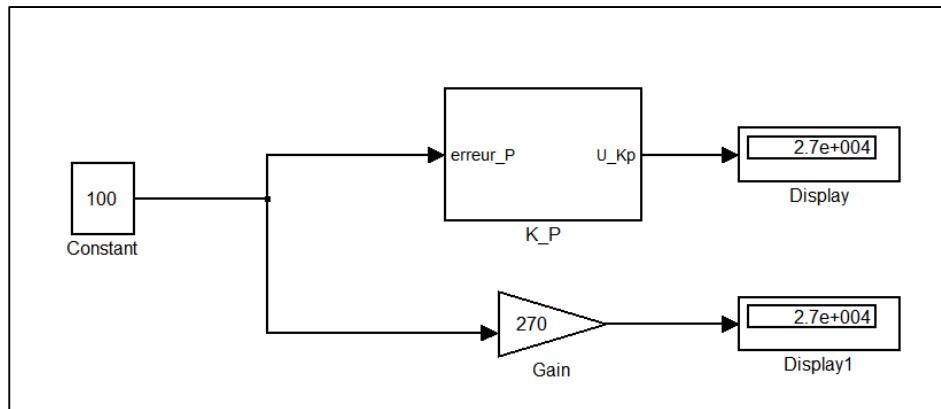

| Figure 5.5  | Schéma Simulink de l'Action proportionnelle avec AD (« K_P »).....               | 96  |

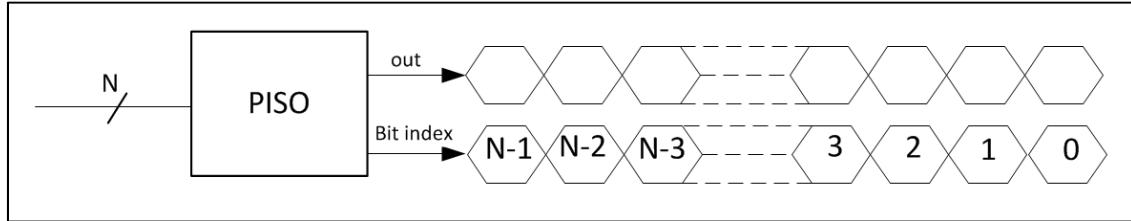

| Figure 5.6  | Principe du registre PISO .....                                                  | 96  |

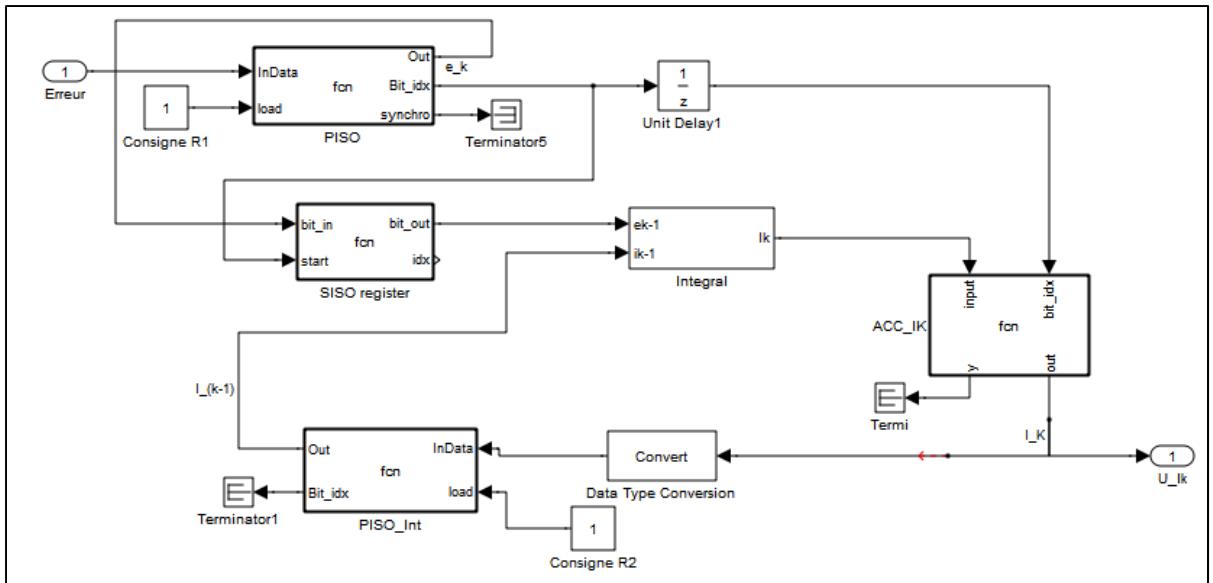

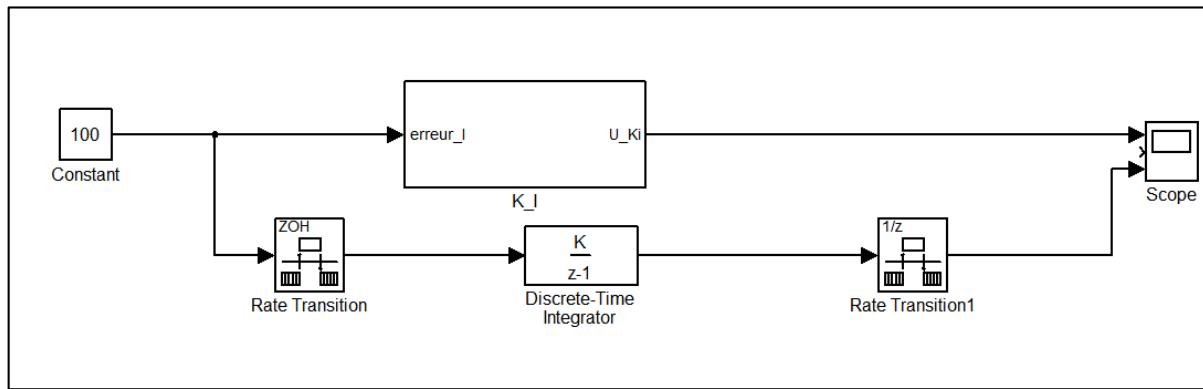

| Figure 5.7  | Schéma Simulink de l'action intégrale avec AD (« K_I ») .....                    | 97  |

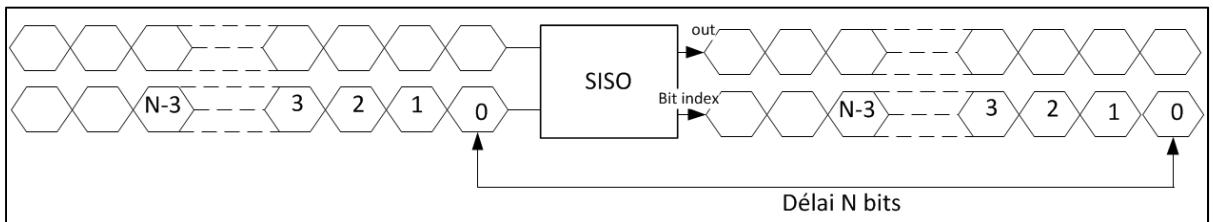

| Figure 5.8  | Principe du registre SISO .....                                                  | 97  |

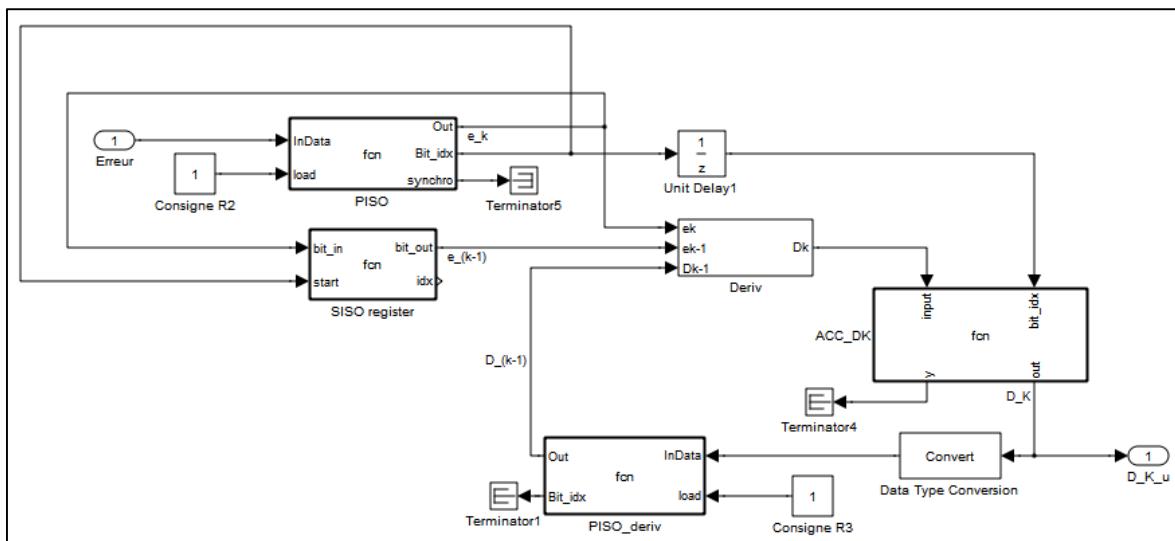

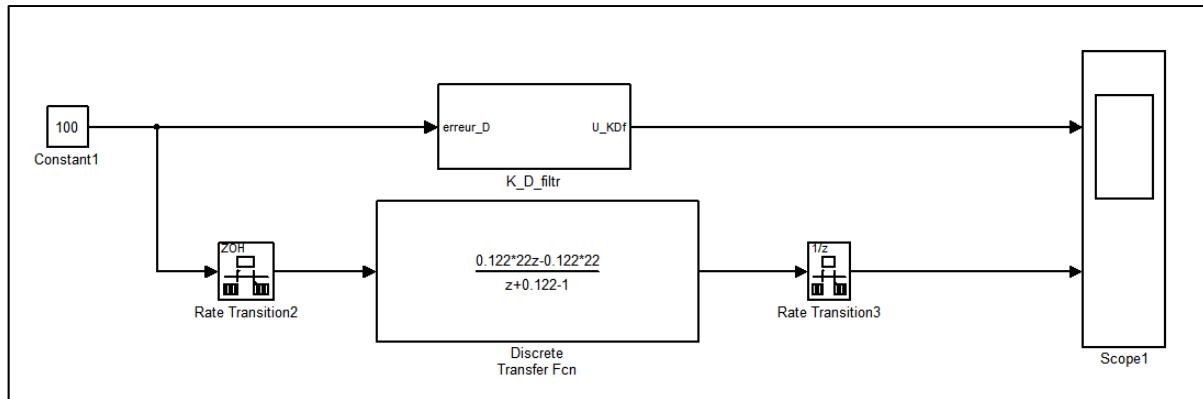

| Figure 5.9  | Schéma Simulink de l'action dérivée avec AD (« K_D_filtr ») .....                | 100 |

| Figure 5.10 | Schéma de simulation.....                                                        | 101 |

| Figure 5.11 | Schéma de simulation pour le bloc intégral.....                                  | 102 |

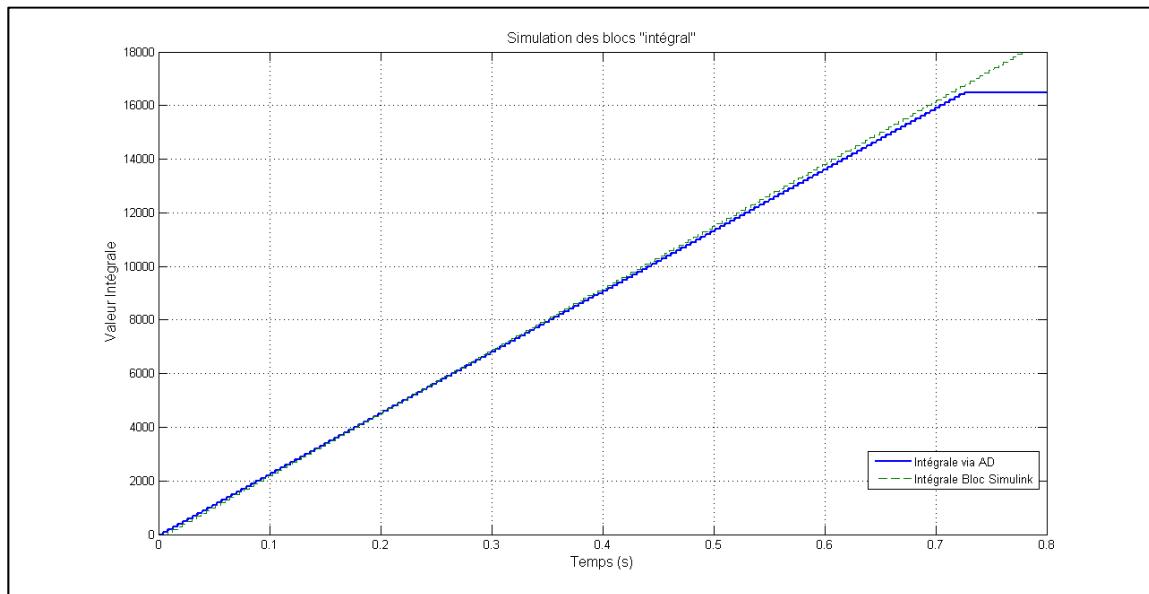

| Figure 5.12 | Courbes de simulation pour l'action intégrale .....                              | 103 |

| Figure 5.13 | Schéma de Simulation blocs "dérivé" .....                                        | 104 |

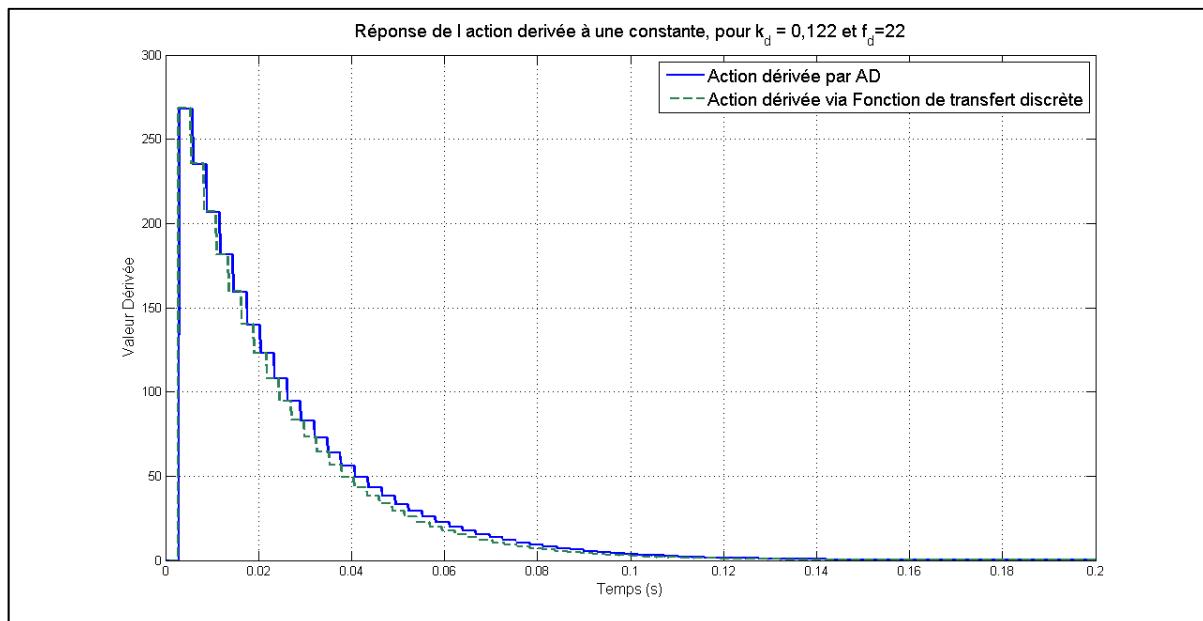

| Figure 5.14 | Résultats de simulation pour l'action dérivée.....                               | 104 |

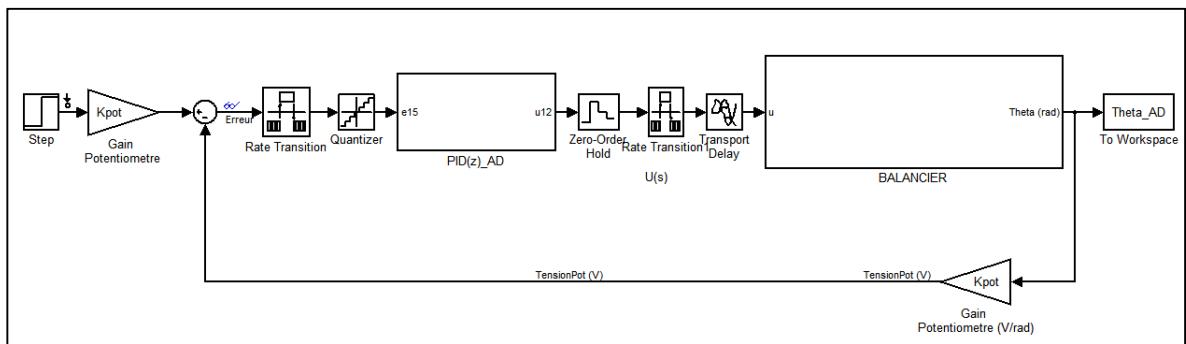

| Figure 5.15 | Schéma Simulink du système muni d'un PID à AD .....                              | 105 |

| Figure 5.16 | Résultats de simulation pour deux types PID modélisés<br>(continu et AD).....    | 106 |

| Figure 5.17 | Réponse simulée et expérimentale du système.....                                 | 108 |

| Figure 5.18 | Réponse du système pour deux types d'implémentation de PID (xPC et<br>FPGA)..... | 111 |

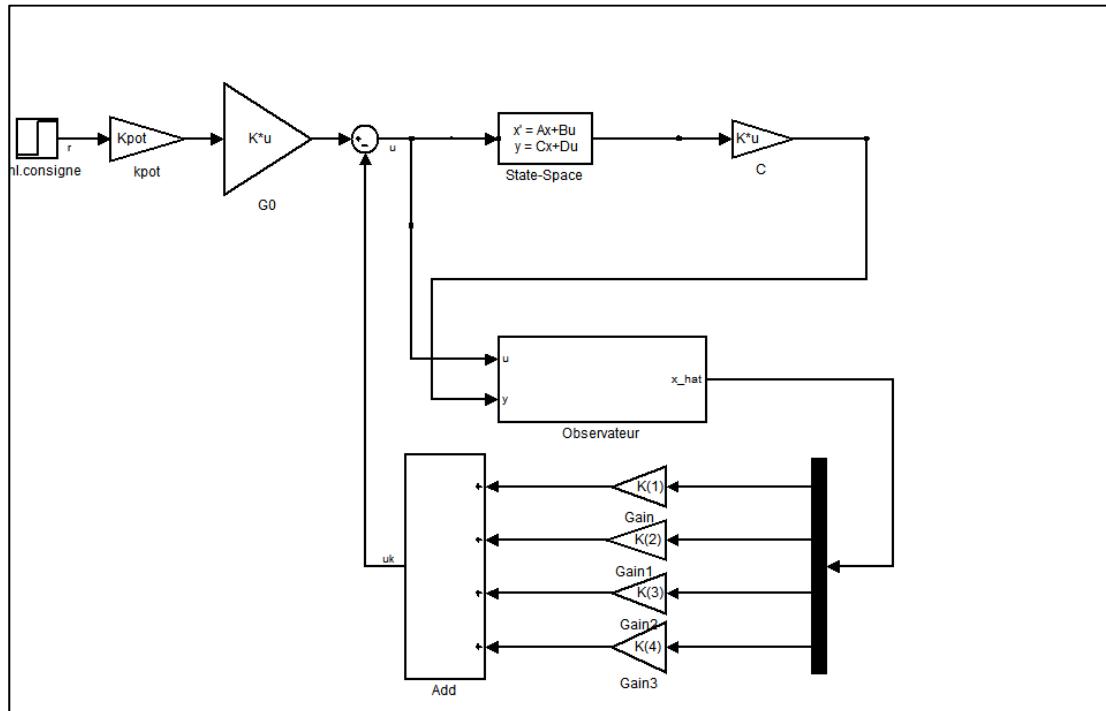

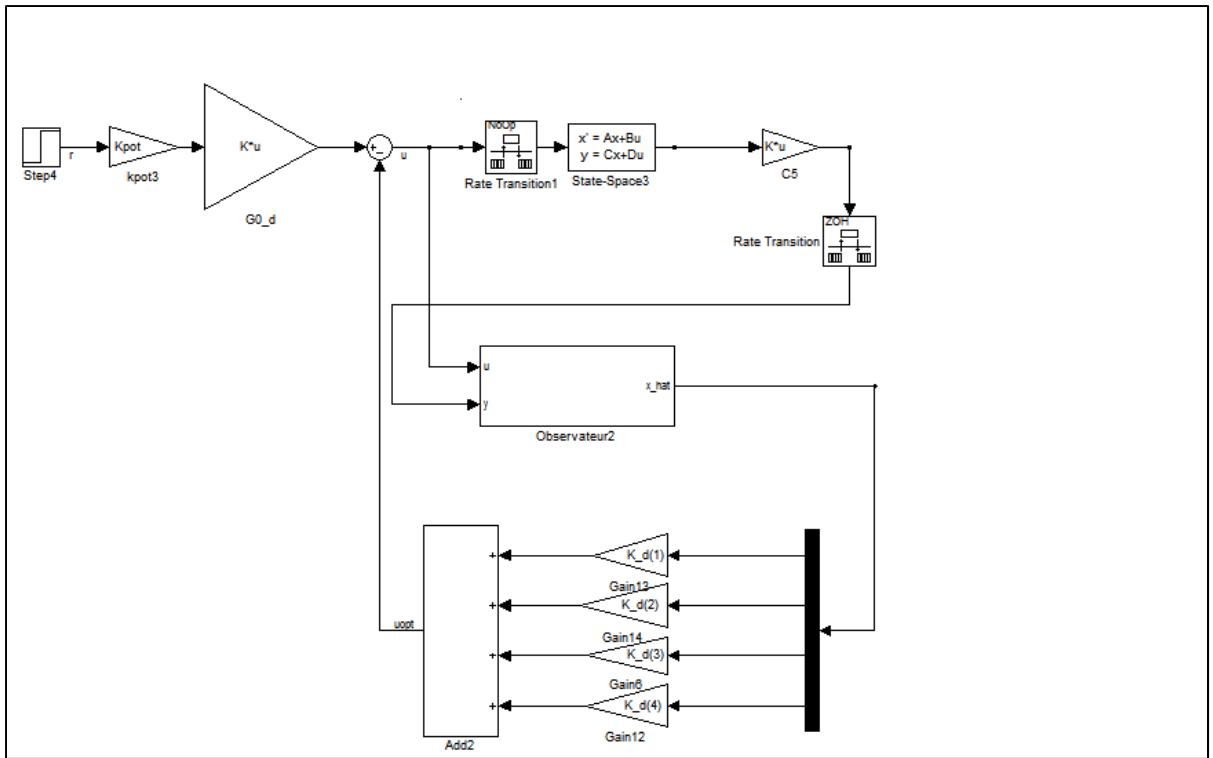

| Figure 6.1  | Schéma de simulation de la commande par retour et observateurs<br>d'état.....    | 113 |

|             |                                                                                                                      |     |

|-------------|----------------------------------------------------------------------------------------------------------------------|-----|

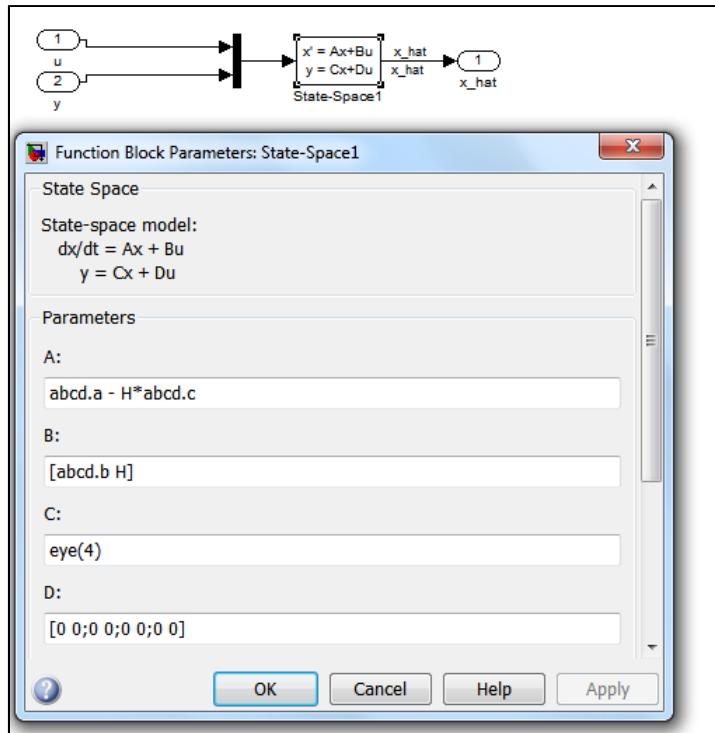

| Figure 6.2  | Description de l'observateur continu .....                                                                           | 114 |

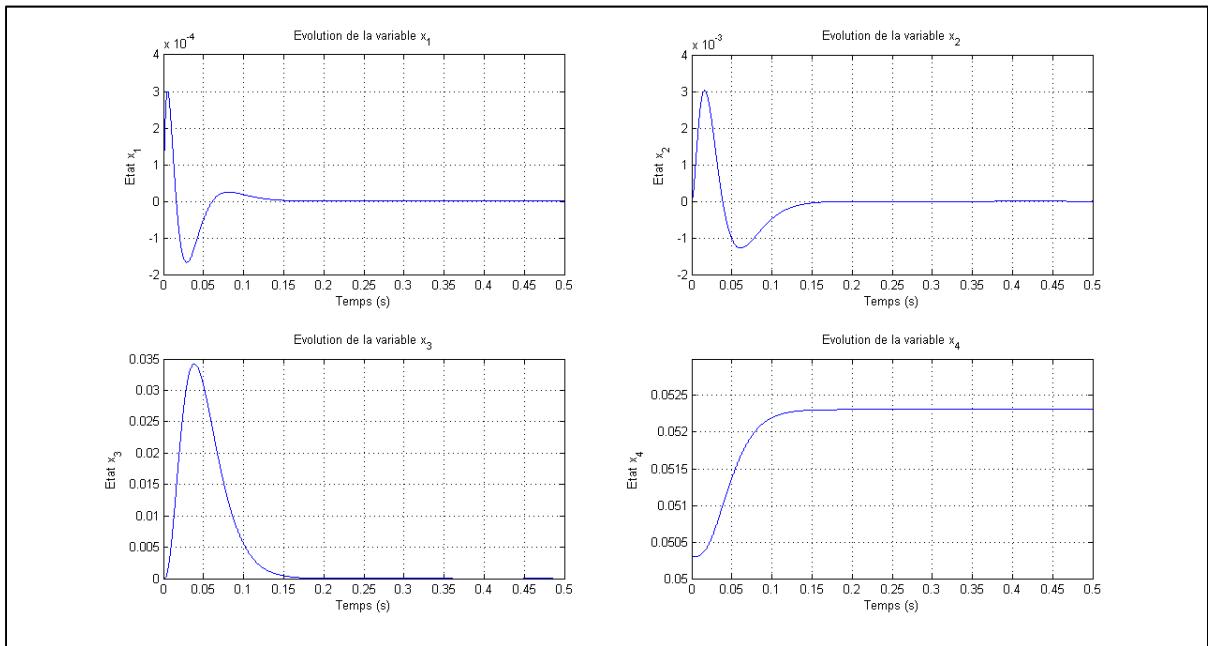

| Figure 6.3  | Estimation des états pour le modèle continu .....                                                                    | 115 |

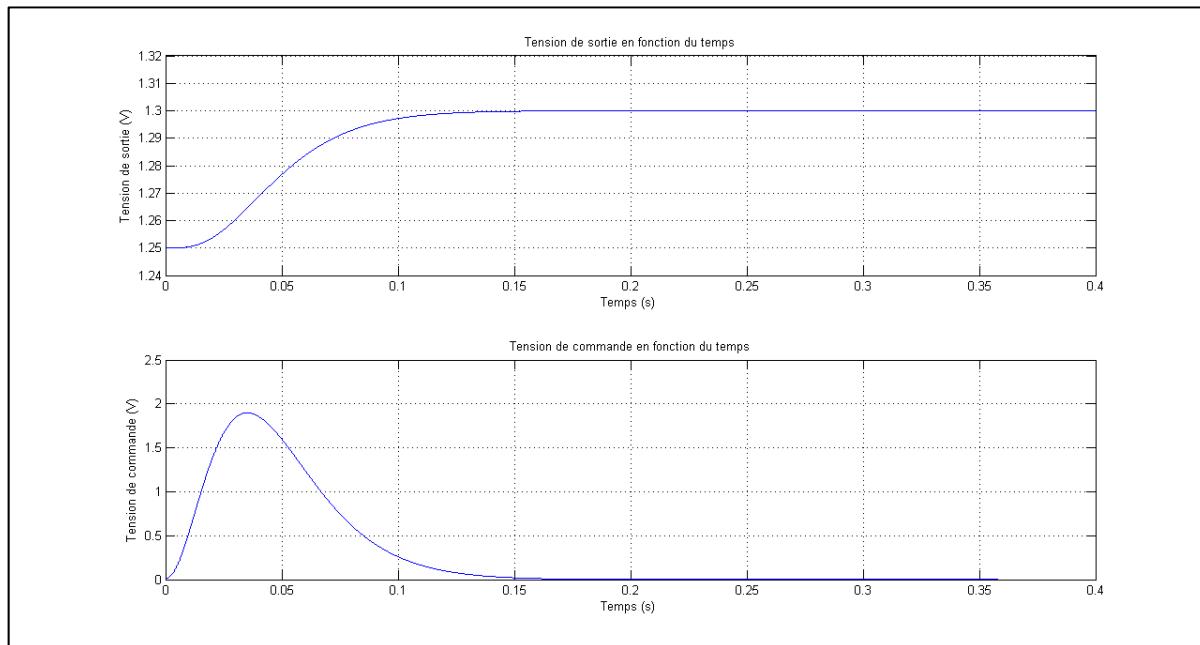

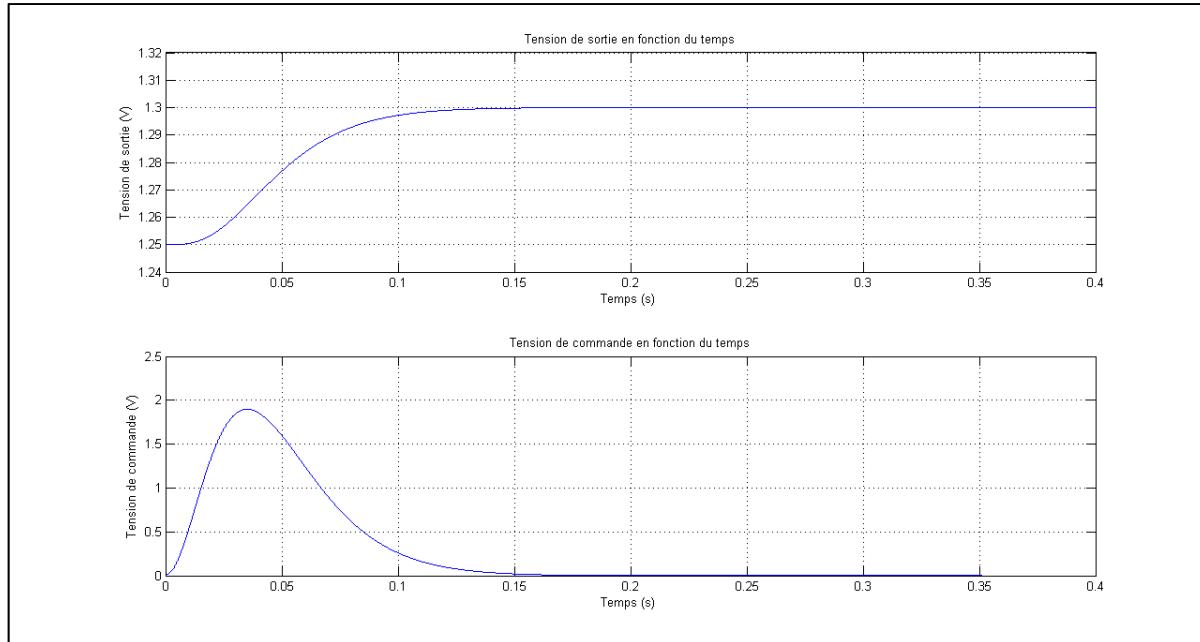

| Figure 6.4  | Tension de sortie et de commande du système modélisé en continu .....                                                | 116 |

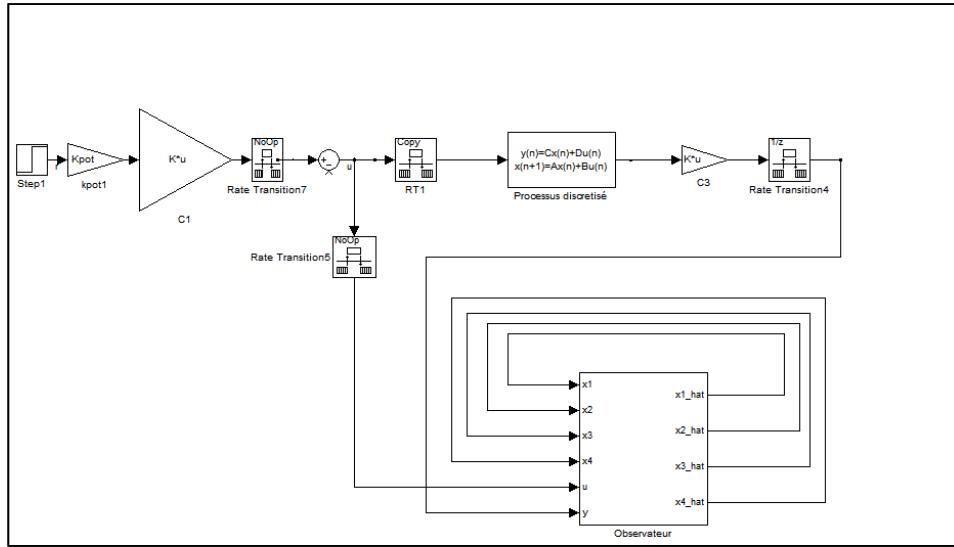

| Figure 6.5  | Schéma Simulink du système à commande discrète .....                                                                 | 119 |

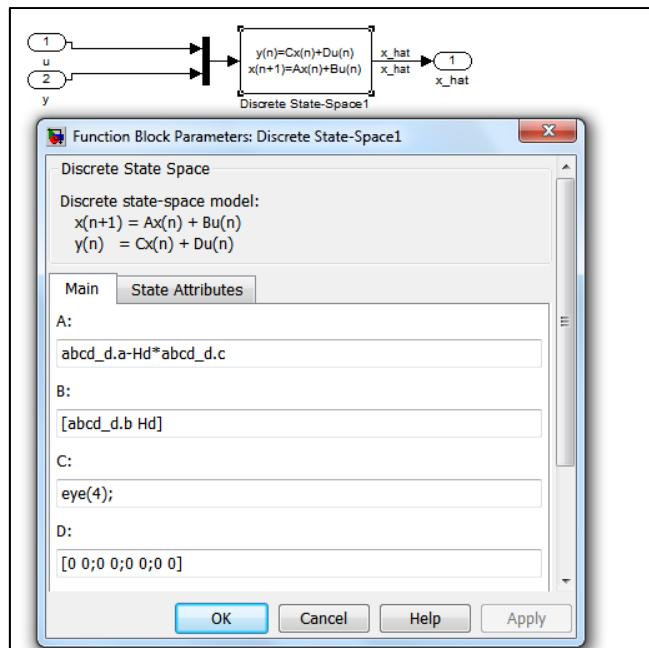

| Figure 6.6  | Implémentation de l'observateur discret .....                                                                        | 120 |

| Figure 6.7  | Tension de sortie et de commande du système à commande discrète.....                                                 | 120 |

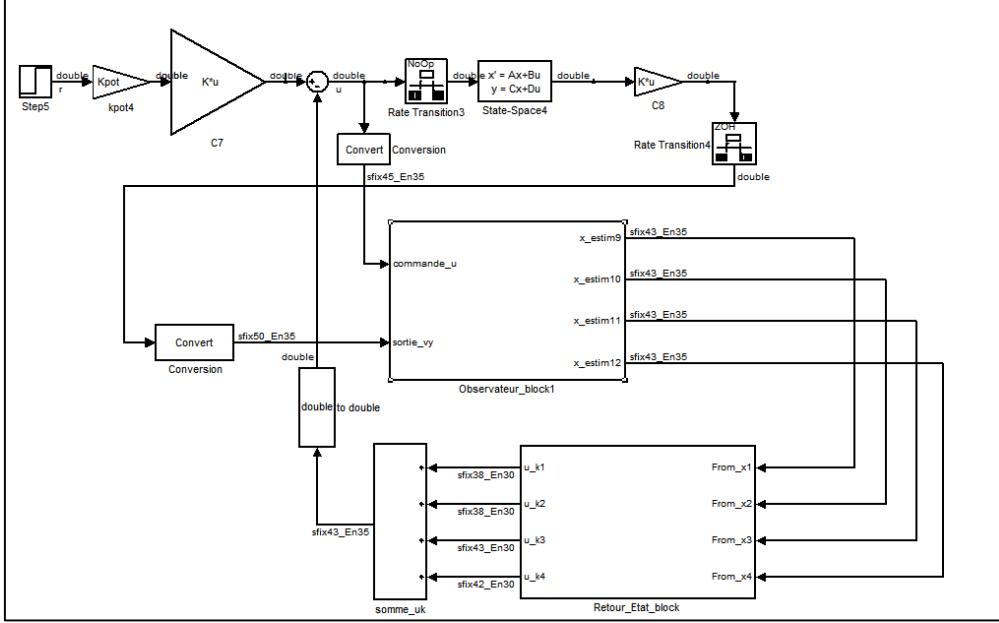

| Figure 6.8  | Schéma Simulink du système pour une commande synthétisable .....                                                     | 122 |

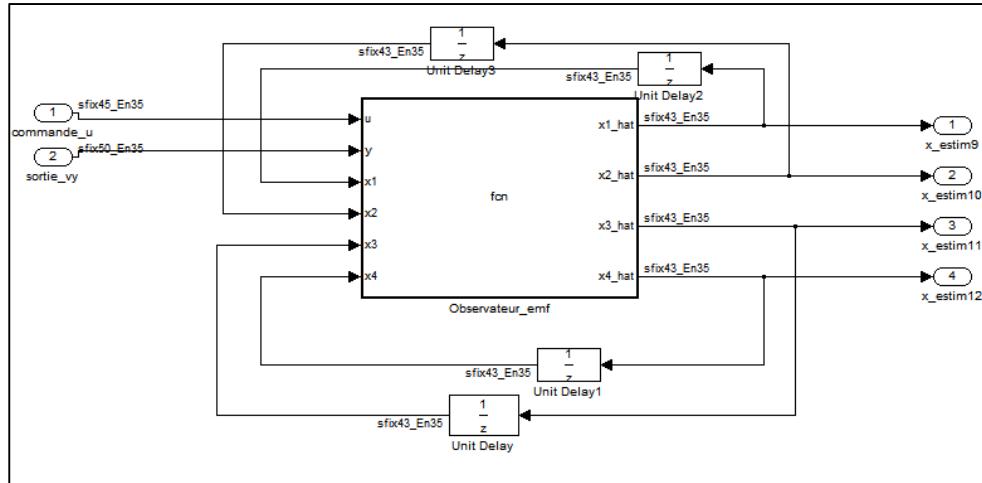

| Figure 6.9  | Schéma Simulink de l'observateur d'état synthétisable .....                                                          | 123 |

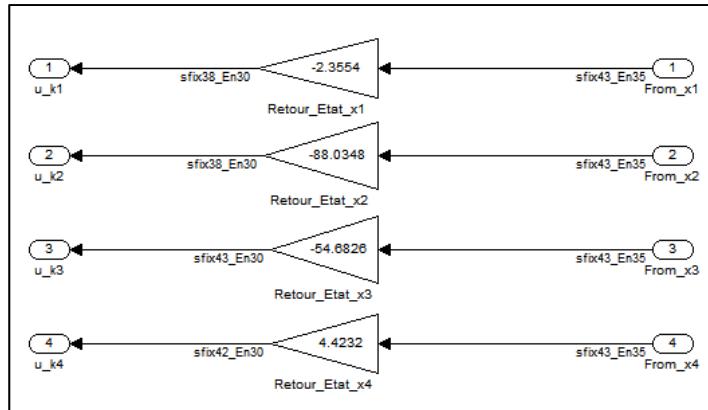

| Figure 6.10 | Retour d'état synthétisable .....                                                                                    | 123 |

| Figure 6.11 | Comparaisons des tensions de sortie et de commande du système à<br>commande synthétisable pour deux précisions ..... | 124 |

| Figure 6.12 | Schéma Simulink de l'observateur à AD .....                                                                          | 127 |

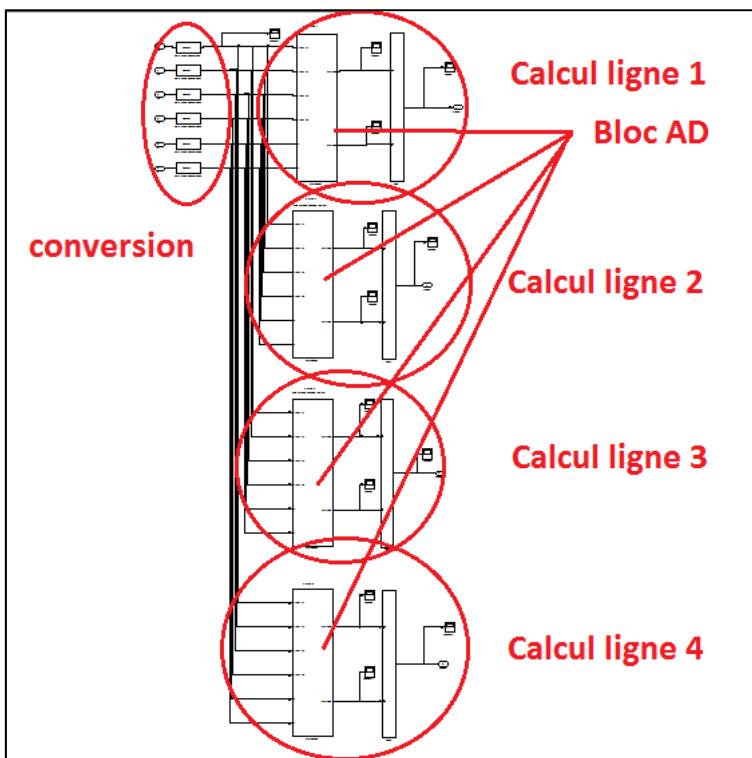

| Figure 6.13 | Structure de l'observateur à AD.....                                                                                 | 128 |

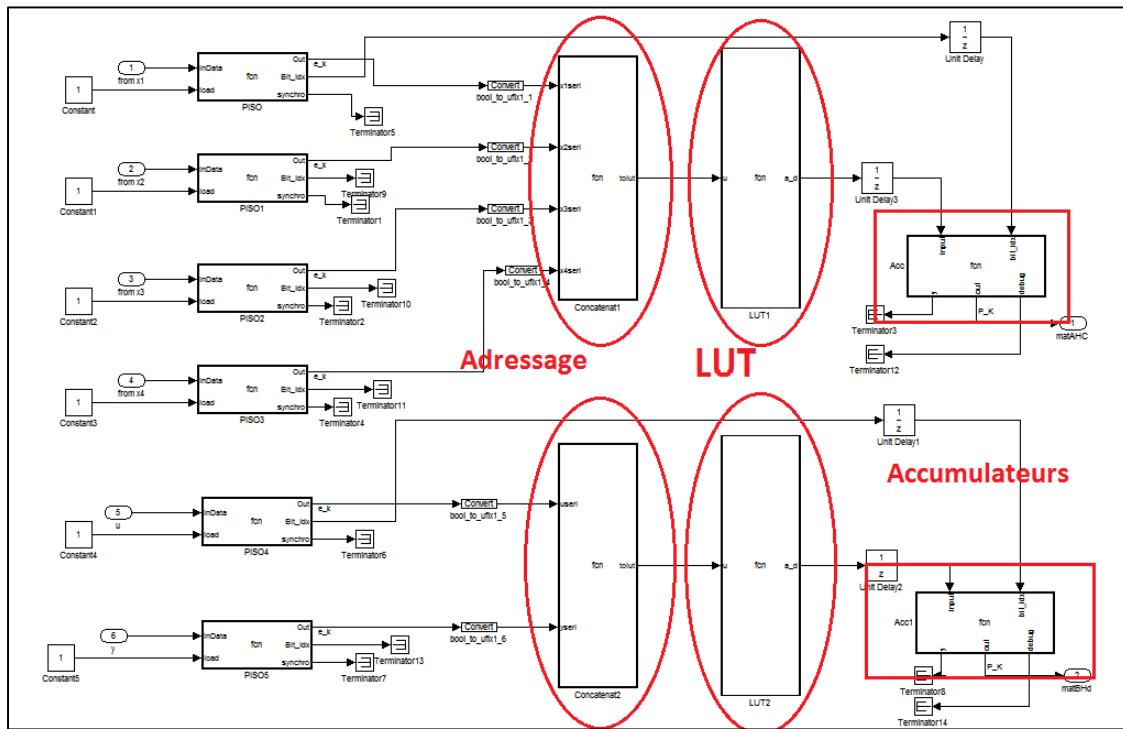

| Figure 6.14 | Détails de l'AD sur une ligne.....                                                                                   | 129 |

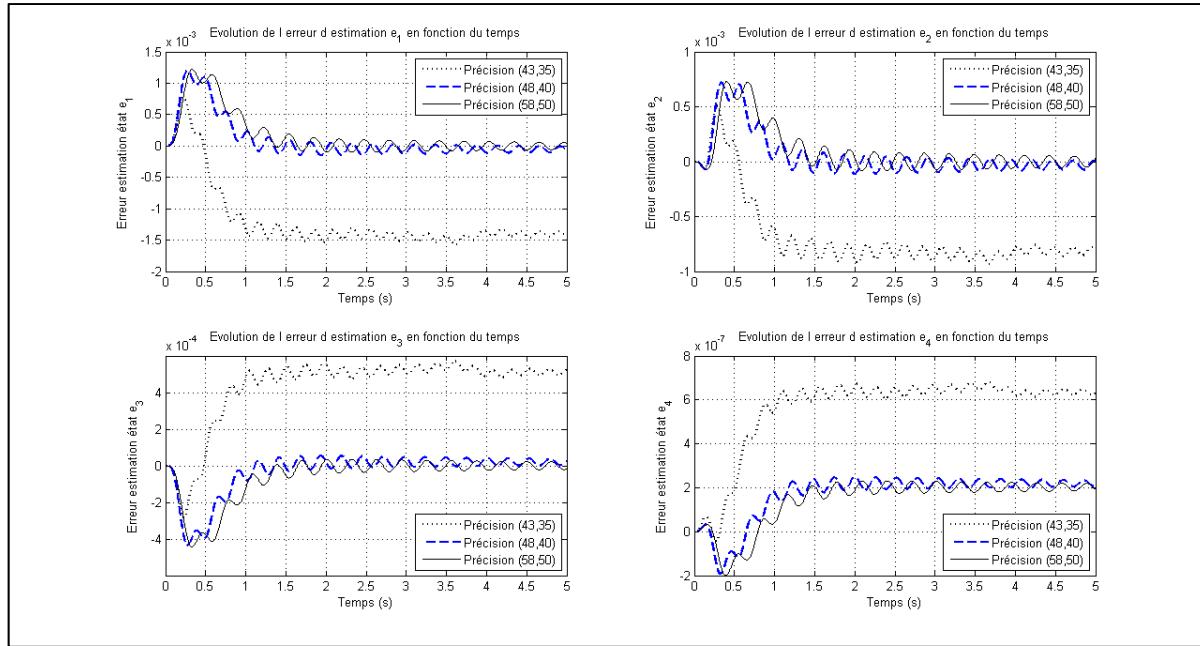

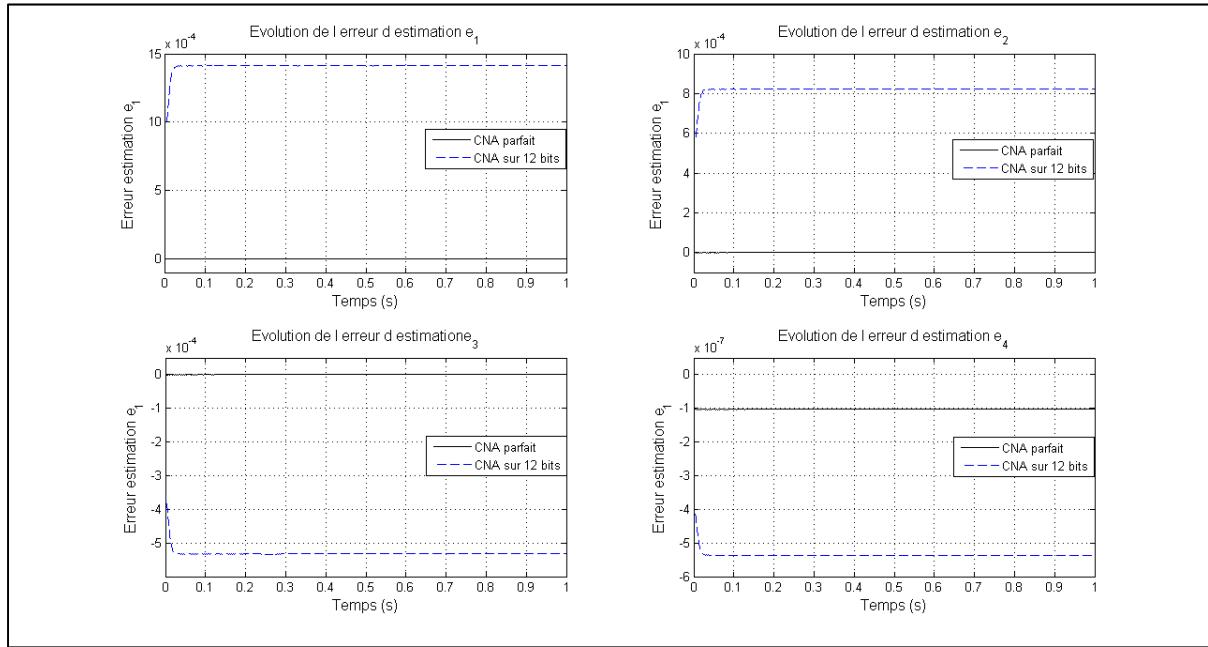

| Figure 6.15 | Erreurs d'estimation de l'observateur à AD.....                                                                      | 130 |

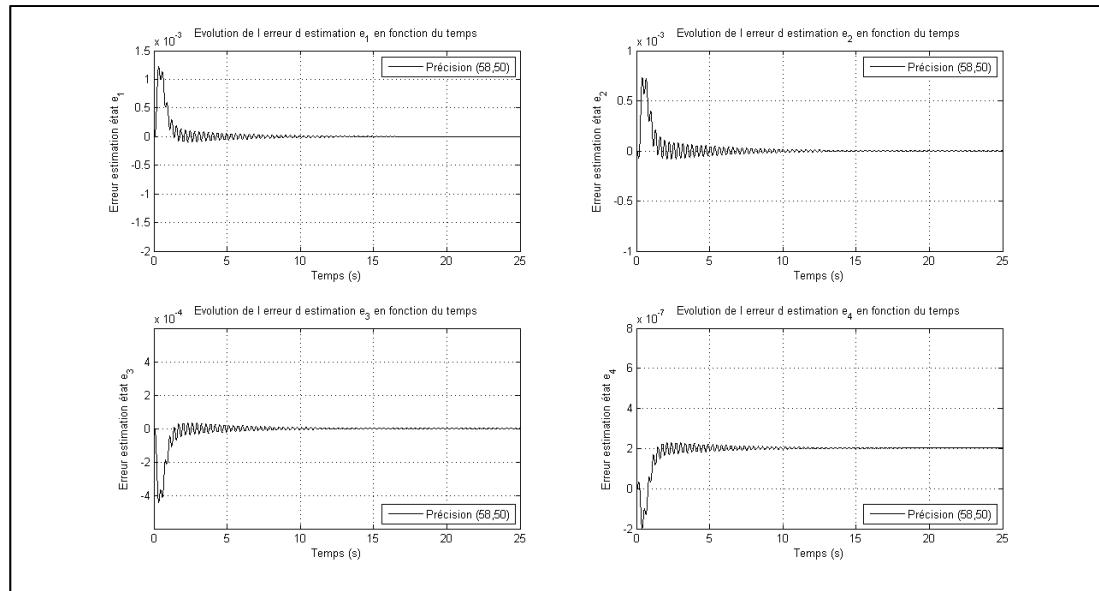

| Figure 6.16 | Erreurs d'estimation pour l'observateur (58,50) .....                                                                | 131 |

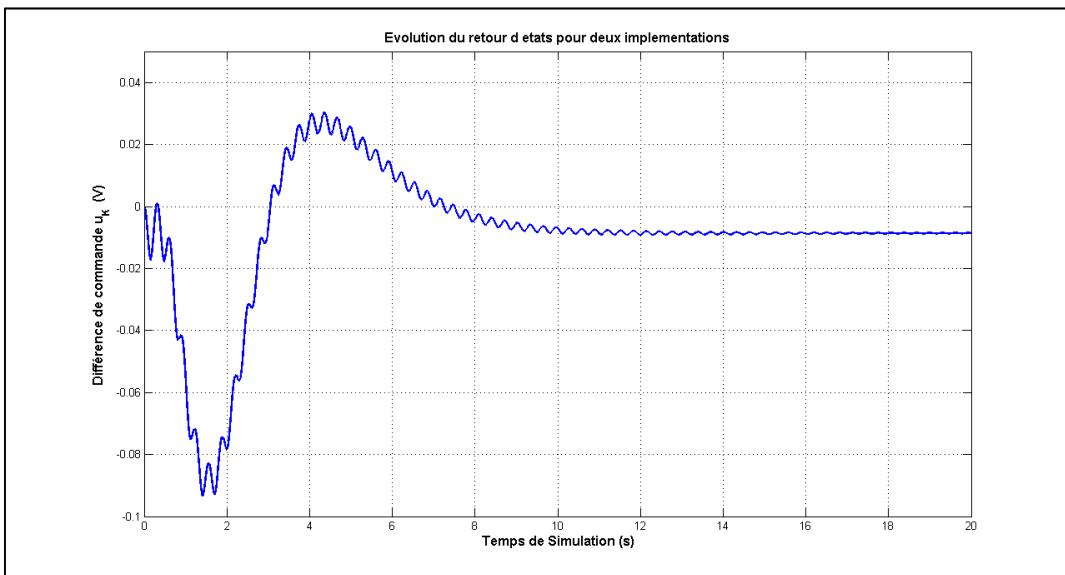

| Figure 6.17 | Evolution de la différence de la commande par retour état $u_k$ .....                                                | 132 |

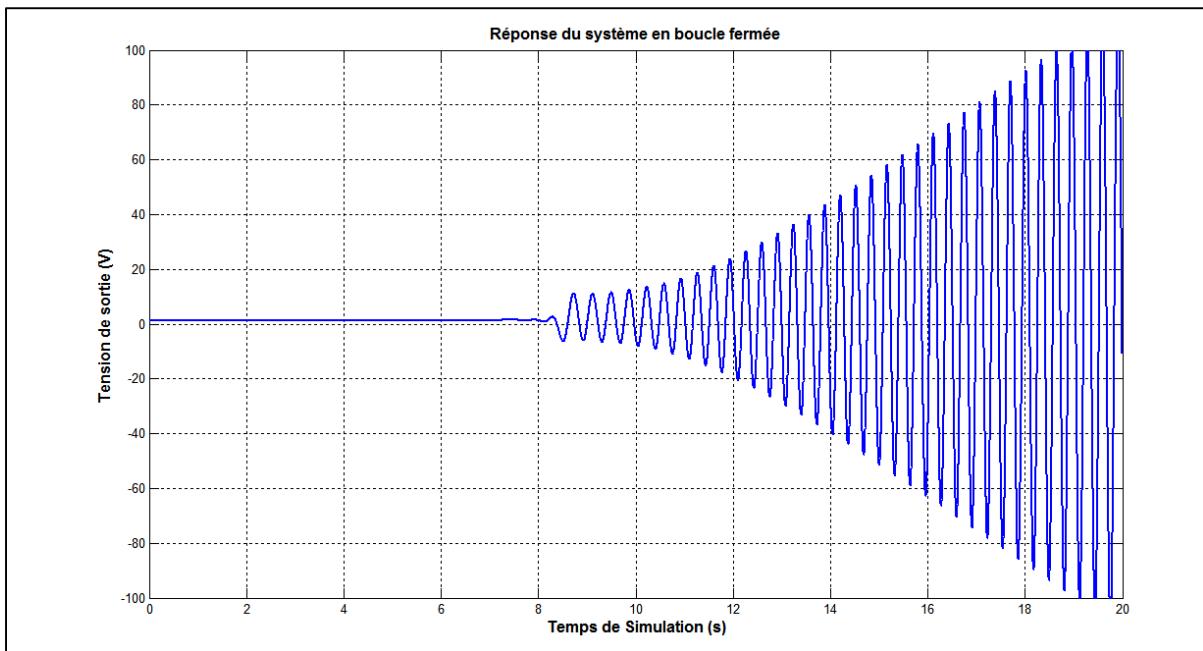

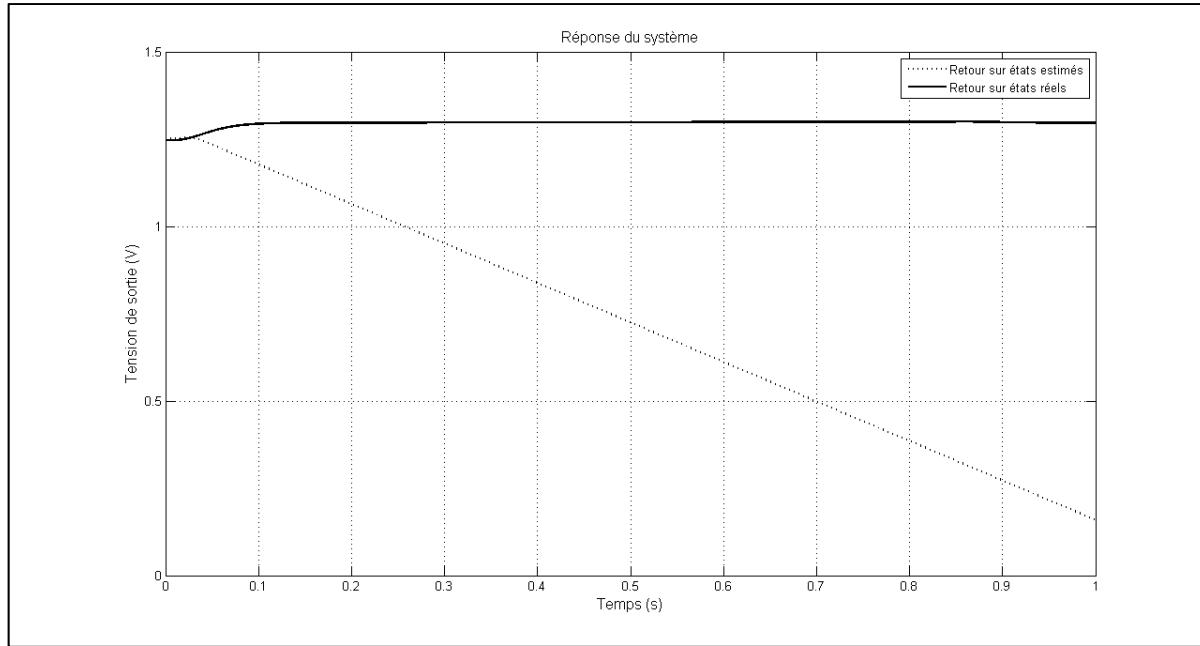

| Figure 6.18 | Réponse du système pour retour d'état et observateur de type (58,50) ....                                            | 133 |

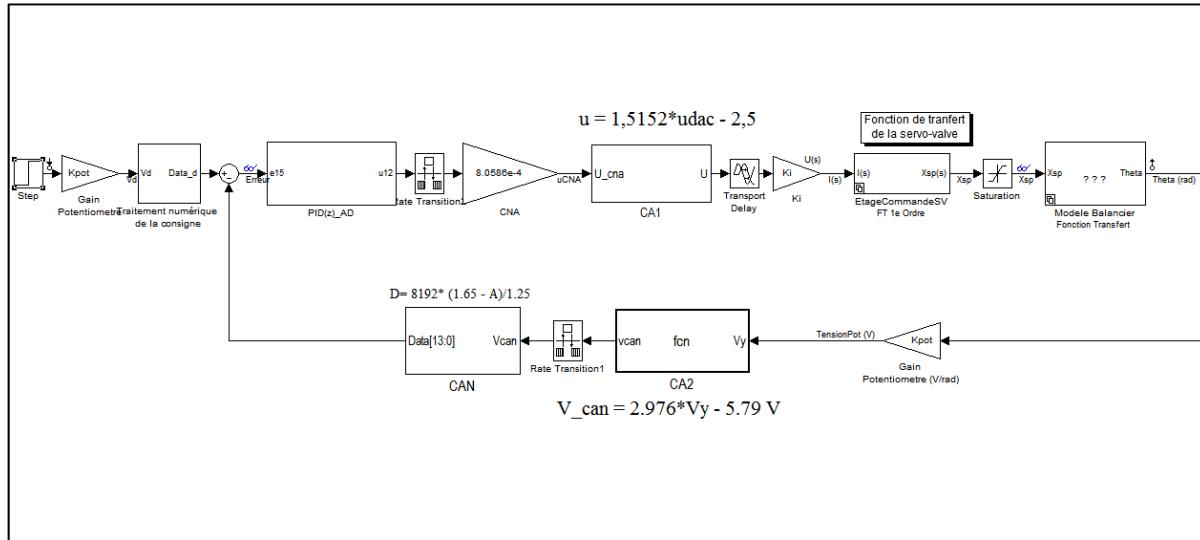

| Figure 7.1  | Schéma Simulink du système complet à commande PID .....                                                              | 136 |

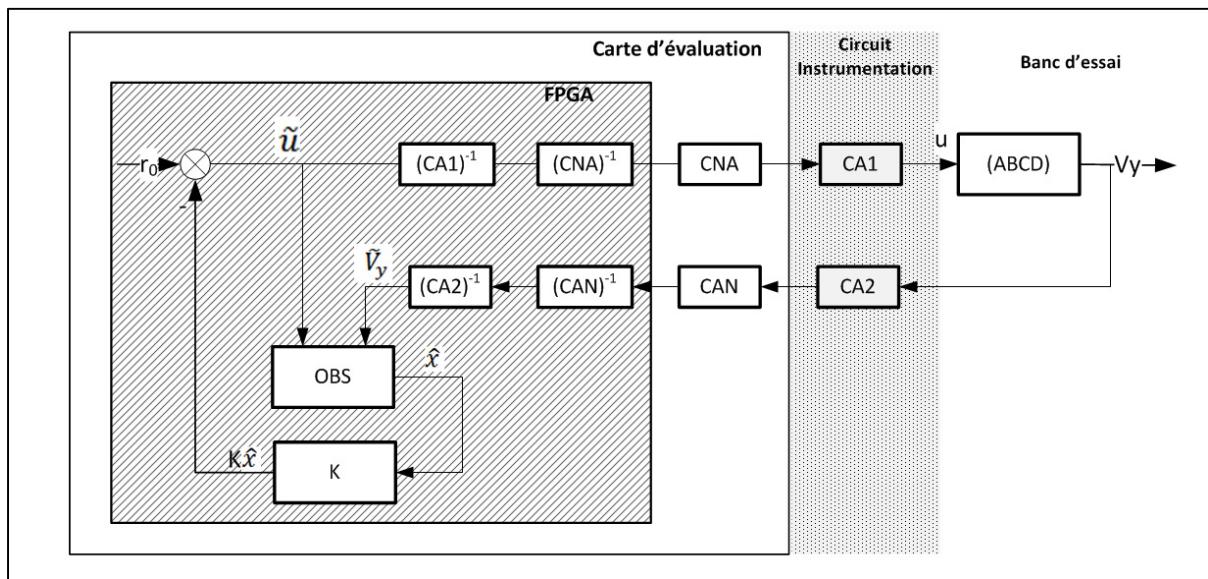

| Figure 7.2  | Schéma d'implémentation de la commande dans l'espace d'état .....                                                    | 137 |

| Figure 7.3  | Erreurs d'estimation de l'observateur en fonction du modèle du CNA .....                                             | 139 |

| Figure 7.4  | Réponse du système pour un retour d'état sur états réels et états estimés<br>avec CNA réel .....                     | 140 |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

### **Abréviations**

|         |                          |

|---------|--------------------------|

| SysGen  | System Generator for DSP |

| $\mu$ C | Microcontrôleur          |

| $\mu$ P | Micropuce                |

### **Acronymes**

|        |                                                     |

|--------|-----------------------------------------------------|

| ABEL   | Advanced Boolean Expression Language                |

| AD     | Arithmétique distribuée                             |

| ASIC   | Application-Specific Integrated Circuits            |

| BTCAM  | Bit-True Cycle-Accurate Models                      |

| CA     | Circuit d'adaptation                                |

| CAD    | Computer Aided Design                               |

| CAN    | Convertisseur Analogique/Numérique                  |

| CI     | Circuit intégré                                     |

| CLA    | Carry-Lookahead Adder                               |

| CLB    | Configurable Logic Blocks                           |

| CNA    | Convertisseur Numérique/Analogique                  |

| CPLD   | Complex Programmable Logic Devices                  |

| CPU    | Central Processing Unit                             |

| DSP    | Digital Signal Processors                           |

| ED     | Equation différentielle                             |

| EDA    | Electronic Design Automation                        |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

|        |                                                    |

|--------|----------------------------------------------------|

| EMF    | Embedded Matlab Function                           |

| EPROM  | Erasable Programmable Read-Only Memory             |

| FPGA   | Field Programmable Gate Array                      |

| HDL    | Hardware Description Languages                     |

| ISE    | Integrated Synthesis Environment                   |

| LC     | Logic Cell                                         |

| LUT    | Look-Up Table                                      |

| LTI    | Linear Time-Invariant                              |

| MBD    | Model-Based Design                                 |

| MOSFET | Metal-Oxyde Semiconductor Field Effect Transistors |

| OTP    | One Time Programmable                              |

| PAR    | Place And Route                                    |

| PID    | Proportionnel-Integral-Dérivé                      |

| PIP    | Points d'interconnexions programmables             |

| PISO   | Parallel-In Serial-Out                             |

| PLD    | Programmable Logic Devices                         |

| PROM   | Programmable Read Only Memory                      |

| RAM    | Random Access Memory                               |

| ROM    | Read-Only Memory                                   |

| RTL    | Register-Transfert Level                           |

| SISO   | Serial-In Serial-Out                               |

| SoC    | System-on-a-Chip                                   |

| SRAM   | Static Random Access Memory                        |

|       |                                                                    |

|-------|--------------------------------------------------------------------|

| TTM   | Time To Market                                                     |

| VHDL  | Very High Speed Integrated Circuits Hardware Description Languages |

| VHSIC | Very High Speed Integrated Circuits                                |

| VLSI  | Very Large Scale Integration                                       |

## INTRODUCTION

En 1947, les laboratoires Bell présentent un nouveau composant qui initie alors le développement de l'Électronique tout au long du XXème siècle, le transistor (Maxfield, 2004). Les années 1960 voient, quant à elles, l'émergence des semi-conducteurs et des circuits intégrés qui inaugurent une nouvelle discipline : l'électronique numérique<sup>1</sup> (Allard, 2009). Une dizaine d'années plus tard, le premier microprocesseur ( $\mu$ P) fait son apparition<sup>2</sup> (Intel, 2012). Puis, les techniques d'industrialisation se sont améliorées rendant possibles des gravures toujours plus fines, permettant de disposer d'une puissance de calcul toujours grandissante (Burghartz et al., 2006). A ce titre, la conjecture de Moore (1965), quant au doublement du nombre de transistors<sup>3</sup> sur une même puce tous les dix-huit mois s'est révélée exacte jusqu'au début du XXIème siècle. Ainsi le développement des moyens électroniques a permis de disposer de systèmes à très grande échelle d'intégration (Jullien et Bayoumi, 1991). On évoque alors la technologie *Very Large Scale Integration* (VLSI). Parallèlement, se sont développés des systèmes électromécaniques de plus en plus complexes dont leur commande a dû répondre à des attentes de plus en plus exigeantes (Monmasson, 2007). C'est ainsi qu'on a pu constater une explosion de la demande des systèmes embarqués toujours plus performants, et ce, dans tous les domaines comme le montrent Paiz et Porrmann (2007) ou Barlas et Moallem (2008).

Un des représentants de la technologie VLSI est le *Field Programmable Gate Array* (FPGA) qui est apparu dans les années 1980 mais dont l'utilisation n'a véritablement débuté qu'à partir des années 1990 (Maxfield, 2004). Un FPGA est un circuit intégré disposant d'un nombre important de blocs logiques configurables reliés entre eux par des interconnexions programmables. Ils permettent la réalisation de fonctions complexes (Xilinx, 2012a) en bénéficiant d'une architecture permettant la parallélisation des calculs, alliée à la flexibilité propre aux circuits numériques programmables (Rahul, Pramod et Vasantha, 2007),

---

<sup>1</sup> On parle aussi d'électronique digitale.

<sup>2</sup> Intel présente le 4004 en 1971.

<sup>3</sup> Moore parlait initialement de composants, ne précisant pas le terme transistor

(Mingyao, Wuhua et Xiangning, 2010). Ces composants sont venus occuper l'espace vacant entre d'un côté les circuits ultra-performants, les *Application-Specific Integrated Circuits* (ASIC), et de l'autre, les *Programmable Logic Devices* (PLD). Les ASIC sont capables de réaliser des fonctions extrêmement complexes mais la mise en place se révèle couteuse (dans le temps et économiquement). Les PLD qui, s'ils ont l'avantage de bénéficier d'un faible coût de mise en œuvre dû à leur simplicité, ne peuvent être utilisés pour des applications complexes (Maxfield, 2004). Toutefois, les FPGA n'auraient pas pu connaître leur essor actuel sans le développement d'outils d'aide à la conception directement emprunté aux ASIC (Monmasson, 2007). En effet, l'implémentation des FPGA se fait au moyen de langages de description matérielle, ou en anglais, *Hardware Description Languages* (HDL). Il y a deux principaux langages HDL : le Verilog et le *Very High Speed Integrated Circuits* (VHSIC) HDL, communément appelé VHDL. En outre, ces langages, comme leur nom l'indique, décrivent le fonctionnement au niveau électronique. Dès lors, ces langages apparaissent comme l'antonymie complémentaire à la réalisation de fonctions complexes, qui nécessitent, de fait, un certain niveau d'abstraction. On voit alors clairement apparaître un besoin croissant d'outils d'intégration efficaces gommant les différences entre niveaux de modélisation fonctionnelle et description matérielle (Barlas et Moallem, 2008; Monmasson, 2007). Ces outils permettant la description de haut niveau ont subi d'importantes recherches à partir de la fin des années 1990. Même si comme le montre Maxfield (2004), les recherches ont toujours poussé dans le sens d'une augmentation du niveau d'abstraction. Ce fut, d'ailleurs, un axe de recherche très tôt comme l'indique Brown (1996). Shanblatt (2005) regrettait toujours le manque d'un outil intégré complet permettant la conception, la simulation et l'implémentation d'un système au sein d'un FPGA.

La firme Xilinx propose dès le début des années 2000, (Ownby et Mahmoud, 2003), un module complémentaire à Matlab/Simulink, *System Generator for DSP* (SysGen), permettant de faire le lien entre le modèle du système et le système physique (Lazaro et al., 2006). SysGen permet de construire des modèles graphiques de systèmes à partir d'une bibliothèque de composants (mémoires, blocs logiques, additionneurs...) et de générer un code VHDL synthétisable (Lazaro et al., 2006). Toutefois, l'absence concrète de moyen d'implémentation

limitait cette pratique. En effet, le processus de conception était entrecoupé dans le sens où le *continuum* de conception était à certains moments rompu. Typiquement, la simulation nécessitait le concours d'une application tierce, un simulateur VHDL, fonctionnant en parallèle. On parle de cosimulation. Ainsi, l'environnement de conception initial ne se suffit pas à lui-même.

Depuis Mathworks (2007) *via* son logiciel Matlab/Simulink a proposé une solution plus intégrée permettant la démarche de conception, simulation, validation et implémentation<sup>4</sup> au sein d'un même environnement. En effet, la boîte à outils *HDL Coder* permet de générer du code HDL, Verilog ou VHDL, à partir de modèles Simulink. Avec la mise en place de la génération de code HDL *via* Matlab/Simulink, une étape a été franchie. En effet, HDL Coder permet de disposer de modèles vrais au bit et cycle près. On parle, en anglais, de *Bit-True Cycle-Accurate Models* (BTCAM) (Mathworks, 2007). Une telle génération permet de disposer de modèles de simulation reflétant le comportement du code VHDL, ce qui rend possible la création de bancs de test (ou en anglais *Testbenches*) plus efficaces toujours dans le même environnement.

Ce type d'outil permet d'utiliser une démarche de conception à base de modèles ou *Model-Based Design* (MBD) en anglais. Il s'agit alors de construire un modèle simulation permettant le réglage de la fonctionnalité et des performances du système (Zhixun et al., 2011).

Par ailleurs, l'utilisation combinée du logiciel de Mathworks et de SysGen dote le concepteur de moyens efficaces pour le design d'un système complexe requérant un fort niveau d'abstraction. En effet, les éléments disponibles au sein de SysGen sont dédiés aux FPGA de la même firme et sont donc optimisés pour ceux-ci. Cependant, le coût relativement élevé d'un tel module complémentaire (minimum de 1000\$CAN<sup>5</sup>) peut être un frein à son

<sup>4</sup> Il convient de nuancer. Nous le verrons plus tard, l'implémentation si elle est facilitée, n'est pas directement possible via Matlab/Simulink.

<sup>5</sup> [http://www.xilinx.com/onlinestore/design\\_resources.htm](http://www.xilinx.com/onlinestore/design_resources.htm)

utilisation dans le cas de petites compagnies s'étant déjà offertes une licence Mathworks. C'est pourquoi, dans le cadre de ce travail, nous nous focaliserons sur la boîte à outils HDL Coder, en laissant de côté SysGen mais en n'oubliant pas que ce module fut le pionnier dans le domaine.

La conception, ainsi de plus en plus intégrée, permet l'élaboration de systèmes toujours plus complexes. Si les FPGA sont longtemps restés dans le domaine des télécommunications et du traitement du signal comme le souligne Monmasson (2007) c'est parce que ces domaines requièrent des débits toujours plus importants. D'ailleurs, cela s'illustre lorsque l'on explore le contenu des modules précédemment cités dont les bibliothèques sont orientées vers ces domaines. On le comprend d'autant plus que le parallélisme des FPGA permet d'obtenir des vitesses de calcul jusqu'à cent fois supérieures à celle des *Digital Signal Processors* (DSP) (Zhengwei, Carletta et Veillette, 2005). Néanmoins, les télécommunications et le traitement du signal ne constituent pas des domaines réservés. En effet, peu à peu l'intérêt des concepteurs de régulateurs et de systèmes embarqués envers les FPGA n'a eu cesse de croître au cours des dernières années comme le démontre Monmasson (2007).

Ainsi, la plus grande intégration des outils au sein d'un même environnement (permettant d'effectuer toutes les tâches de la conception à l'implémentation) combinée à la prise en compte de hauts niveaux d'abstraction ont, aujourd'hui, rendu possible la conception de systèmes complexes et performants à base de FPGA tout en réduisant le temps de développement (Ownby et Mahmoud, 2003), (Paiz et Porrmann, 2007) et (Rahul, Pramod et Vasantha, 2007) . Cette dynamique s'applique aux développements de contrôleurs et des systèmes embarqués qui bénéficient de quatre facteurs :

- la réduction des coûts,

- la sécurité,

- la tolérance aux contraintes (temporelles, de consommation),

- une meilleure qualité du contrôle.

La réduction des coûts est liée à trois facteurs (Monmasson, 2007) : une architecture dédiée à une tâche spécifique, la réduction du temps de mise sur le marché (TTM pour *time to market*) et l'intégration, à terme, totale d'un système embarqué complet (entrées/sorties analogiques) sur un *System-On-a-Chip* (SoC). La sécurité des informations est aussi assurée via l'encryptage des données (Maxfield, 2004) dont le type diffère selon les distributeurs et le type de FPGA. La tolérance aux contraintes est, elle, assurée par la nature même d'un FPGA. En effet, ce dernier permet un parallélisme accru du calcul réduisant le temps de traitement, et permettant d'avoir de longue période de veille (peu de circuiterie active, donc peu de consommation). Enfin, ce type de contrôleur accroît ostensiblement la qualité du contrôle (par rapport à une autre solution numérique) puisque l'on se rapproche d'une dynamique analogique (par la rapidité du traitement) tout en conservant une grande flexibilité.

Il reste alors à développer des composants dédiés à la création de régulateurs au sein d'une librairie intégrée à Matlab/Simulink. Cela permettrait à des personnes non-initiées aux FPGA (et à l'électronique de façon générale) de pouvoir se doter d'organes de commande performants en utilisant un environnement largement répandu (Matlab/Simulink). Ce projet s'inscrit dans la continuité de disposer d'outils à haut niveau d'abstraction mais respectueux des contraintes matérielles. Ces dernières devront être prises en compte lors de la conception des éléments de la bibliothèque dédiée à la commande de systèmes.

Les avantages énoncés précédemment sont toutefois à nuancer un peu. Si l'efficacité d'un régulateur formé d'un FPGA est indéniable, sa mise en pratique comporte quelques zones plus complexes requérant, malgré un développement à haut niveau d'abstraction, des considérations matérielles. La façon dont sont gérés les nombres est un exemple. Ensuite, il faut savoir ce que les opérations que l'on souhaite effectuer impliquent au sein du FPGA. Si une addition ou une soustraction ne demande que peu de ressources, une multiplication est très gourmande en termes d'espace (Chan, Moallem et Wang, 2007) (Gupta, Khare et Singh, 2009) . Dès lors, il est nécessaire de comprendre ce qui se passe à bas niveau pour pouvoir être en mesure de développer des systèmes de haut niveau dont le fonctionnement demeure le même à haut comme à bas niveau.

La commande de systèmes repose sur trois principaux objectifs selon Nise (2011) : assurer la stabilité du système à commander, disposer d'une dynamique conforme au cahier des charges et avoir une réponse en régime établi conforme aux spécifications. Ainsi, le correcteur le plus simple à mettre en place serait un régulateur proportionnel. Dans les faits, cette simple implémentation implique une multiplication. Il est alors préférable de s'affranchir des contraintes matérielles en utilisant une méthode de calcul qui n'utilise pas de multiplication. Chan, Moallem et Wang (2004; 2007) et Gupta, Khare et Singh (2009), entre autres, ont travaillé sur des correcteurs, souvent de type Proportionnel-Intégral-Dérivé (PID), en utilisant des architectures sans moltiplicateurs. Ces structures de calculs ont été présentées pour la première fois par Peled et Bede (1973) avant que White (1989) n'établisse un article référence, sur ce que l'on appelle l'Arithmétique Distribuée (AD). Dans leur travaux Chan, Moallem et Wang (2004; 2007) ont montré que la mise en place de l'AD permet de réduire la consommation de 40% et de diminuer l'occupation mémoire. Toutefois, les compagnies de FPGA (Xilinx, Altera) ont fait évoluer leurs produits et aujourd'hui ceux-ci disposent de moltiplicateurs qui permettent un développement encore plus rapide si le système à commander est simple (Lazaro et al., 2006).

Nous allons donc chercher à savoir, si oui ou non, l'AD peut rester une bonne méthode de calcul dans certains cas. Nous poursuivrons, après avoir construit un compensateur de type simple, en développant un régulateur plus complexe qui permette de profiter des FPGA et de leurs performances (Scrofano, Seonil et Prasanna, 2002). Parallèlement à cela, nous insérerons les éléments de commande conçus afin de constituer une bibliothèque Matlab/Simulink de composants synthétisables et implantables sur un FPGA et facilement utilisables par des concepteurs n'ayant que des connaissances limitées sur le FPGA.

Afin de mener à bien ces objectifs, nous allons, dans un premier temps, nous intéresser aux FPGA et leur fonctionnement. Ce premier point nous permettra de toujours garder à l'esprit le lien à tisser entre haut et bas niveau d'abstraction (à l'échelle des bits, des registres).

Nous effectuerons ensuite un bref rappel sur les systèmes asservis qui nous permettra de disposer des bases nécessaires à l'étude critique de nos résultats car ne perdons pas de vue que l'on souhaite disposer d'un système de commande. Les systèmes de commande à l'épreuve seront :

- une commande type PID, la plus largement répandu dans l'industrie (Yu, 1999),

- une commande moderne munie d'un observateur d'état.

Le choix de ces deux commandes est simple. La première, la plus basique, la plus répandue, est également la plus usitée dans la littérature liée à la commande par FPGA. La seconde permet de disposer d'une commande plus complexe, tout en disposant d'un cadre théorique bien défini (Rugh, 1991), où le nombre d'opérations (et de multiplications) dépend de la dimension du système. Nous chercherons donc à savoir si ce qu'ont mis en évidence Scrofano, Seonil et Prasanna (2002), en termes d'efficacité de la multiplication matricielle, se révèle pertinent dans le domaine de la commande de systèmes.

Nous nous intéresserons ensuite à la façon dont sont traités les nombres dans un système numérique. Nous nous focaliserons plus particulièrement sur les nombres à virgules fixes puisqu'ils sont directement synthétisables en VHDL.

A la suite, nous tacherons de montrer que l'utilisation de logiciels à haut niveau d'abstraction se prête particulièrement bien à la conception de systèmes de commande embarquée. En effet, nous tenterons de mettre en évidence les avantages de tels outils afin de réduire le temps de mise sur le marché. Enfin, dans le but de poursuivre une démarche de conception à bases de modèles performantes nous verrons qu'il sera nécessaire de passer par la création d'une bibliothèque de composants dédiés à la commande.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

#### 1.1 Field Programmable Gate Array (FPGA)

Un FPGA est un circuit intégré (CI), qui est défini comme une matrice de blocs logiques configurables (*Configurable Logic Blocks*, CLB) reliés entre eux par des interconnexions entièrement reconfigurables (Monmasson, 2007). Ces blocs et interconnexions peuvent être programmés par l'utilisateur *via* des cellules mémoire statiques (Xilinx, 2011a).

Les FPGA sont des appareils programmables disposant de quelques centaines de millier à quelques millions de portes logiques configurables. Il est important de noter que dans le cas d'un FPGA, on parle de configuration plus que de programmation. En effet, les données que l'utilisateur charge dans le FPGA affectent directement l'architecture matérielle de ce dernier, il ne s'agit pas d'instructions purement logicielles.

Les FPGA sont des circuits logiques configurables *in situ (field-programmable)*. Ils sont venus remplir, à partir des années 1980, le vide que comportait le spectre des circuits logiques. Nous avions d'un côté les PLD qui, s'ils devenaient de plus en plus complexes (on parle de *Complex PLD (CPLD)*), ne permettaient pas de réaliser des fonctions de haut niveau, de l'autre les ASIC munis d'une architecture fixe. Ces derniers sont conçus pour des applications spécifiques et ne sont pas configurables.

Ainsi, étant reconfigurables à souhait, les FPGA peuvent servir à plusieurs applications ce qui représente un sérieux avantage.

Les FPGA sont donc des circuits logiques qui se configurent. La mise en œuvre de ceux-ci est radicalement différente de la programmation à laquelle nous pouvons d'ordinaire être habituée : celle des microprocesseurs ( $\mu$ P) ou microcontrôleurs ( $\mu$ C). En effet, ces derniers fonctionnent de façon séquentielle : tâche 1 puis tâche 2 (tâche 1 et tâche 2 indépendantes)

Cela vient du fait même de leur constitution : lecture du registre d'instruction, traitement de l'instruction etc.

Les FPGA, quant à eux, jouissent d'un parallélisme total si bien que dans l'exemple précédent la tâche 1 et la tâche 2 s'effectuent simultanément. Le parallélisme leur confère une grande rapidité en comparaison des µP et µC. Toutefois, cela a pour effet de considérablement modifier la façon dont on « programme » ces composants (le séquencement par exemple). Il existe deux principaux langages pour configurer les FPGA ce sont des langages dits de description matériel, *Hardware Description Language* (HDL) dont les deux largement répandus sont le Verilog et le VHDL.

Pour résumer, les FPGA sont des circuits numériques dotés d'une grande multitude de portes logiques programmables par l'utilisateur permettant la réalisation de fonctions de traitement dédiés à un besoin.

## 1.2 Notions fondamentales

Nous allons à présent revenir sur les aspects fondamentaux des FPGA à savoir leur place dans l'histoire de l'électronique ainsi que les phénomènes physiques liés à leur technologie. Enfin, nous verrons comment ces circuits peuvent servir à la conception de systèmes de haut niveau grâce à des outils qui n'ont eu cesse de se développer.

### 1.2.1 Historique

L'apparition des premiers FPGA, par la firme Xilinx, remonte à 1985 avec le XC2064 (Santo, 2009). Mais ce n'est qu'à partir des années 1990 qu'ils commencent à susciter un intérêt plus grand. Pour mieux comprendre le phénomène, il est nécessaire de revenir quelques années en arrière.

Les FPGA s'inscrivent, en plein, dans la grande Histoire de l'Electronique et ont pour point de départ l'apparition du premier transistor en 1947. Les transistors sont le fruit de recherches intenses, et en 1962 la technologie *Metal-Oxyde Semiconductor Field Effect Transistors* (MOSFET) émerge et permet la conception de circuits moins gourmands en énergie. Parallèlement, le concept de CI se développe et Jack Kilby, de Texas Instrument réussit en 1958 à créer le premier circuit intégré composé de cinq composants réunis sur le même morceau de semi-conducteur (Maxfield, 2004). Au cours des années 1960 se sont développées des gammes de CI, notamment chez Texas Instrument, proposant une petite dizaine de portes logiques.

Les premiers CI programmables arrivent sur le marché au début des années 1970 sous forme de *Programmable Read Only Memory* (PROM). En parallèle, se développent le premier microprocesseur ( $\mu$ P), et les mémoires de type *Static Random Access Memory* (SRAM). Le développement des mémoires (PROM, EPROM, E2PROM) permet la réalisation de CPLD toujours plus complexes. Ainsi, la société Altera mélange, en 1984, la technologie EPROM avec les MOSFET permettant de disposer d'un circuit numérique programmable ne consommant pas trop d'énergie (Maxfield, 2004). Le concept de tableau logique (*logic array*) fait son apparition. Le principe réside, comme le résume la Figure 1.1, en la programmation de liens logiques à l'aide d'opérations simples (AND, OR, XAND, XOR...). Typiquement, sont présents en entrée plusieurs signaux avec leur complémentaire, on dresse alors la matrice qui permet de connecter tous les signaux. Puis, lors de la programmation, on décide des nœuds que l'on souhaite activer afin de réaliser la fonction désirée. Ainsi les CPLD ont nécessité des moyens plus évolués de mise en œuvre à mesure que leur taille grandissait. On voit alors apparaître les premiers langages de description matérielle (HDL) qui serviront de base au VHDL et au Verilog, à ce titre on peut citer le langage *Advanced Boolean Expression Language* (ABEL) introduit par Data I/O en 1983.

Par ailleurs, le développement des ASIC s'effectue aussi en utilisant le principe de *logic array*. Si la conception des premiers circuits ASIC se faisait à la main, à l'aide de masques, la technologie, évoluant, et la finesse de gravure, permettant d'avoir plusieurs millions de

composants sur une même puce, rendent l'élaboration d'outils d'aide à la conception nécessaire. Ainsi l'émergence des langages HDL, VHDL et Verilog, avec la mise en place de standards IEEE (1988; 1994), a permis le développement d'outils d'aide à la conception électronique (*Computer Aided Design, CAD*) de hautes performances (Monmasson, 2007). On dénomme ce type de logiciel par *Electronic Design Automation* (EDA). Ils permettent la conception et l'implémentation des CI complexes.

Figure 1.1 Principe d'un tableau logique (ou *Logic Array*)

### 1.2.2 Concepts

Les concepts fondamentaux des FPGA sont très bien résumés par Maxfield (2004). L'élément clef de la compréhension réside dans la méthode de configuration des FPGA. En effet, les techniques de programmation ont considérablement évolué passant d'un système programmable une unique fois à un système capable de supporter un nombre infini de programmation.

Nous pouvons voir les interconnexions de la Figure 1.1 comme des interrupteurs. Au début de l'ère du numérique la technique des fusibles (*fuses*) était utilisée. La méthode consiste à choisir de façon définitive les connexions que l'on souhaite effectuées en « grillant » le fusible qui nous est inutile. Nous pouvons également envisager le principe inverse : l'anti-fusible (*anti-fuses*). On dispose d'anti-fusibles sur chacune de nos lignes, à l'état initial les anti-fusibles sont dotées d'une telle résistance que le circuit est vu comme ouvert. Lorsque l'utilisateur programme l'appareil configurable, il injecte une impulsion de courant sur l'un des anti-fusibles qui devient passant. Ce phénomène est rendu possible par la nature isolante que présente le silicium à l'état amorphe et son pouvoir conducteur lorsqu'il est sous forme cristalline. Dans les deux cas présentés, les appareils ne sont programmable qu'une seule fois, on parle de *One Time Programmable* (OTP).

Ces techniques ont été utilisées pour réaliser les premières mémoires de type *Read-Only Memory* (ROM). Toutefois, lors des phases de conception, il devenait fastidieux de sans cesse changer de ROM pour modifier les valeurs. Pour résoudre ce problème, Intel, en 1971, présente *l'Erasable Programmable Read-Only Memory* (EPROM) qui permet d'effacer la mémoire et d'y inscrire de nouvelles valeurs. Le principe de cette mémoire est quasi-similaire au MOSFET, y ajoutant seulement une seconde grille, appelée grille flottante, qui permet de maintenir le transistor à l'état passant lorsque le signal de commande a disparu. Pour effacer la valeur en mémoire, il suffit de « décharger » la grille flottante. Pour cela, une source de rayonnement ultraviolet est nécessaire. Toutefois, les mémoires EPROM ne permettent pas d'effacer les données stockées de façon précise, l'ensemble de la mémoire doit être effacé. C'est ensuite au tour de l'*Electrically Erasable Programmable Read-Only Memory* (EEPROM ou E2PROM) d'arriver sur le marché. L'E2PROM permet d'effacer précisément les données grâce à un signal électrique. La constitution physique de l'E2PROM est très proche de sa petite sœur, l'EPROM, c'est uniquement l'épaisseur, plus fine, de l'oxyde isolant qui permet à un transistor de fournir l'énergie nécessaire à la décharge de la grille flottante.

Cependant, la solution la plus répandue pour la configuration des FPGA ne réside pas dans des cellules mémoires mortes mais dans des mémoire vives, *Random Access Memory* (RAM) (Trimberger, 1993; Xilinx, 2011b). Il s'agit d'une cellule appelée *Static RAM* (SRAM). Cette cellule permet de changer sa valeur à tout moment, mais le principal problème réside dans le fait que les données sont perdues lorsque l'alimentation est coupée.

### 1.2.3 Constitution interne

Nous avons évoqué précédemment qu'un FPGA est constitué d'une matrice de CLB. Ces blocs sont eux-mêmes composés de quatre tranches (*Slices*) qui sont elles même formées par deux cellules logiques (*Logic Cell*, LC) (Xilinx, 2011b). La Figure 1.2 présente la structure d'un CLB.

Figure 1.2 Structure d'un bloc logique configurable (CLB)

La LC est la plus petite structure présente au sein d'un FPGA, elle est composée d'une table de conversion (*Look-Up Table*, LUT) à quatre entrées, d'un multiplexeur, d'un registre et d'une gestion de la retenue (Xilinx, 2011b) comme le rappelle la Figure 1.3. La gestion de la retenue (*carry* en anglais) est interne à chaque LC mais une chaîne de gestion est mise en place à travers tous les blocs quelque soit leur niveau hiérarchique (Xilinx, 2011b), de sorte

que les performances des fonctions logiques soient améliorées (Trimberger, 1993). Par ailleurs, la LUT à quatre entrées, présente dans chaque LC, est composée de seize cellules SRAM. L'utilisation de la SRAM pour construire les LUT permet, de fait, une grande flexibilité. En effet, lors de l'implémentation, le bloc formant la LUT peut être instancié sous différentes formes : une LUT standard à quatre entrées, un bloc  $16 \times 1$  bit RAM (on parle de RAM distribuée) ou un registre. Cela permet de disposer d'une architecture matérielle adaptée à la fonction souhaitée. Par ailleurs, les blocs d'interconnexions présents entre chaque CLB reposent sur des points d'interconnexions programmables (PIP). Ces PIP sont formés par un transistor contrôlé par une cellule mémoire de type SRAM. Ainsi, la sortie d'un CLB peut être routée vers un autre bloc de traitement *via* un PIP à l'état passant. La Figure 1.4 en rappelle le principe.

Figure 1.3 Détail d'une tranche

A la grande souplesse de configuration des FPGA, s'ajoute des éléments permettant la gestion de fonction plus complexes. Typiquement, des blocs de RAM embarqués sont insérés dans la matrice formée par les CLB et les PIP. Ces blocs se distinguent des modules de RAM

distribuée par une plus grande capacité. En outre, les FPGA peuvent embarquer des processeurs. On distingue deux types de processeurs pouvant être mis en place : les *soft core* et *hard core*. Les processeurs *hard core* sont des processeurs déjà câblés qui sont insérés (physiquement) dans la structure matricielle des FPGA. En revanche, les processeurs de type *soft core* sont construits à l'aide des blocs présents dans le FPGA. Le terme *soft* fait référence à la partie « logicielle ». En effet, un processeur *soft core* est créé à l'aide d'un langage de description. Ainsi la fonction de processeur *soft* est menée à bien par une partie du FPGA qui se comporte « comme » un processeur. La possibilité de disposer d'un processeur permet d'élargir encore un peu plus le spectre d'utilisation des FPGA leur permettant le traitement de fonctions complexes et séquentielles. Enfin, les nouvelles générations de FPGA<sup>6</sup> embarquent systématiquement des blocs multiplicateurs qui permettent la gestion d'opérations  $18 \times 18$  bits signés (Rahul, Pramod et Vasantha, 2007; Xilinx, 2009).

---

<sup>6</sup> Au moins depuis avril 2003 avec la sortie du Spartan 3 de Xilinx.

Figure 1.4 Points d'Interconnexions Programmables

- 1) Structure d'un PIP

- 2) Multiplexeur contrôlé par une cellule mémoire

- 3) Connexions des CLB

Adaptée de Trimberger (1993, p. 3)

#### 1.2.4 Démarche de conception

Riesgo (1999) présente une démarche de conception, ou parfois appelée *flow*<sup>7</sup> de conception comme le fait Derrien (2002), de haut en bas (*top-down*) qui consiste à partir du niveau d'abstraction le plus élevé pour finir à l'implémentation physique et électronique.

Les niveaux d'abstraction présentés par Derrien (2002), Maxfield (2004), Zerbe et Andelkovic (2004), Cong *et al.* (2011) sont, du plus haut au plus bas :

- le niveau « système » qui permet de définir les attentes du circuit à implémenter ;

- le niveau « comportemental » qui représente la description algorithmique ;

---

<sup>7</sup> Le terme *flow* fait directement sens puisqu'en anglais on utilise le mot *flow*

- le niveau « structurel » (*Register-Transfert Level*, RTL) qui décrit le système à l'aide de primitives logiques ;

- le niveau « physique » qui prend en compte l'appareil programmable choisi et rend compte de la fonction d'un point de vue électrique.

Quelque soit le niveau d'abstraction choisi pour implémenter la fonction désirée, le flot de conception se résume en quatre étapes comme le rappelle Derrien (2002) :

- la synthèse qui permet de passer d'une description abstraite à une architecture implantéable. Notons que la phase de synthèse est réalisée à l'aide d'un outil logiciel ;

- l'allocation des ressources qui permet faire correspondre le résultat de la synthèse aux ressources disponibles sur le FPGA ;

- le placement et routage (PAR) qui permet d'associer chaque ressource nécessaire à un bloc logique configurable tout en programmant les interconnexions ;

- la génération du fichier de configuration qui est le fichier chargé dans le FPGA afin d'obtenir la configuration requise.

### 1.3 Conception de systèmes à base de FPGA

A la lumière de ce que sont les FPGA, et de leurs routines d'implémentation, il convient désormais de s'attarder sur leur domaine d'application et de regarder en quoi ils peuvent présenter un avantage dans la commande des systèmes.

Nous venons de voir que les FPGA embarquent de plus en plus de fonctionnalités (processeurs, moltiplicateurs, mémoires...). Il reste à définir cependant leur domaine d'utilisation. Nous verrons d'abord les outils logiciels à la disposition du concepteur. Nous nous focaliserons ensuite sur l'utilisation des FPGA dans les boucles de commande.

### 1.3.1 Comment utiliser les FPGA ? Quels sont les outils à notre disposition ?

Dans leurs premières heures, les FPGA disposaient d'un champ d'application réduit. En effet, ils étaient utilisés dans une logique de glue permettant d'interfacer plusieurs PLD au moyen de décodeurs d'adresses ou de multiplexeurs (Derrien, 2002). Ce domaine d'utilisation réduit était directement induit par des outils logiciels d'implémentation limités (Maxfield, 2004; Monmasson, 2007). Les concepteurs devaient alors placer chaque transistor si bien que la mise en place de systèmes complexes était fastidieuse pour ne pas dire impossible. Ainsi, un effort conséquent a été fourni pour doter le concepteur de moyens efficaces. Très vite, les logiciels alors sur le marché proposent une implémentation graphique à l'aide de schématiques intégrant des portes logiques élémentaires (XOR, NAND, registres...). Toutefois, ce niveau d'abstraction reste limité. En effet, comme le souligne Derrien (2002), le concepteur doit à la fois faire la description structurelle (ou RTL) et comportementale. Cela revient à dire qu'à l'aide d'une seule couche d'abstraction, on doit pouvoir décrire la structure basse et électronique (les portes logiques) tout en assurant le bon comportement de la fonction implémentée. On comprend donc que ce genre d'outils limite considérablement l'évolution des fonctions implémentées, puisque le schéma est figé et la modification d'un paramètre du circuit doit se répercuter sur l'ensemble des paramètres associés<sup>8</sup> (Maxfield, 2004).

La mise en place, très tôt, de HDL standardisés IEEE (1988; 1996) a permis de s'affranchir du problème de la représentation de plusieurs couches d'abstraction au sein d'une même interface de description. En effet, les langages VHDL (IEEE, 1988; 1999; 2007) et Verilog (IEEE, 1996; 2005) se trouvent à un plus haut niveau d'abstraction et permettent la description comportementale de la fonction à implémenter sans le souci de la définition structurelle. Par ailleurs, Maxfield (2004) introduit une nuance entre les deux langages : le VHDL dispose d'un niveau d'abstraction légèrement supérieur à ce que propose le Verilog

---

<sup>8</sup> On peut par exemple citer la modification de la taille d'une variable de travail où les mémoires, registres et portes logiques par lesquels passe la variable modifiée doivent être également révisés.

(on peut citer les différences entre les types abstraits et fixes). Ainsi, les recherches sont toujours allées dans le sens d'une conception se faisant à plus haut niveau d'abstraction comme le soulignait très tôt Brown (1996).

A partir de la fin des années 1990, l'augmentation du niveau d'abstraction passait par la possibilité de concevoir un système, non pas à l'aide de HDL mais grâce au langage C (Cong et al., 2011). Toutefois, Shanblatt (2005) remarquait qu'un outil intégré à un logiciel de haut niveau comme Simulink permettant de passer de la description d'un système à une implémentation sur FPGA manquait. Les premières ébauches de travail dans ce sens ont pourtant démarré très tôt. Typiquement, Líčko (2003) présentait différentes façons d'effectuer un prototypage rapide à l'aide de Simulink. Mais d'où venait ce besoin d'environnements de conception de haut niveau ? Brettle (2009) et Cong et al. (2011) expliquent que l'utilisation d'environnements de conception de haut niveau largement usités dans le monde scientifique permet de toucher plus d'ingénieurs. En effet, les récent progrès ont permis de bâtir un pont entre deux mondes : les spécialistes des circuits numériques et les concepteurs de systèmes (quelque soit le domaine). Mais les environnements de développements largement utilisés dans le monde de l'ingénierie embarquant des fonctionnalités dédiés aux FPGA attendent la fin des années 2000 pour émerger comme le montrent Han (2007), Brettle (2009) ou le présente Auger (2008).

La compagnie The Mathworks (2007) présente une boîte à outils, HDL Coder, permettant la génération de code HDL synthétisable à partir de schéma Simulink. De la même façon Brettle (2009) présente l'utilisation du module FPGA du logiciel LabView de la société National Instruments. Ces avancées permettent en effet de s'affranchir des contraintes importantes liées aux langages HDL au profit d'environnement de développement largement répandu. Aujourd'hui les EDA embarquent donc des modules de génération automatique de codes HDL (VHDL ou Verilog) destinés à être synthétisé.

Devant la complexité grandissante des systèmes à concevoir, Zhixun et al.(2011) rappellent que l'approche directe au niveau « système » lors de la conception permet de se focaliser sur

la fonctionnalité. On parle alors de conception à base de modèles (MBD). Le MBD utilise les modèles du système comme des spécifications tout au long du processus de développement et répond aux contraintes imposées à la conception de systèmes complexes et hétérogènes (Rongqing et al., 2011).

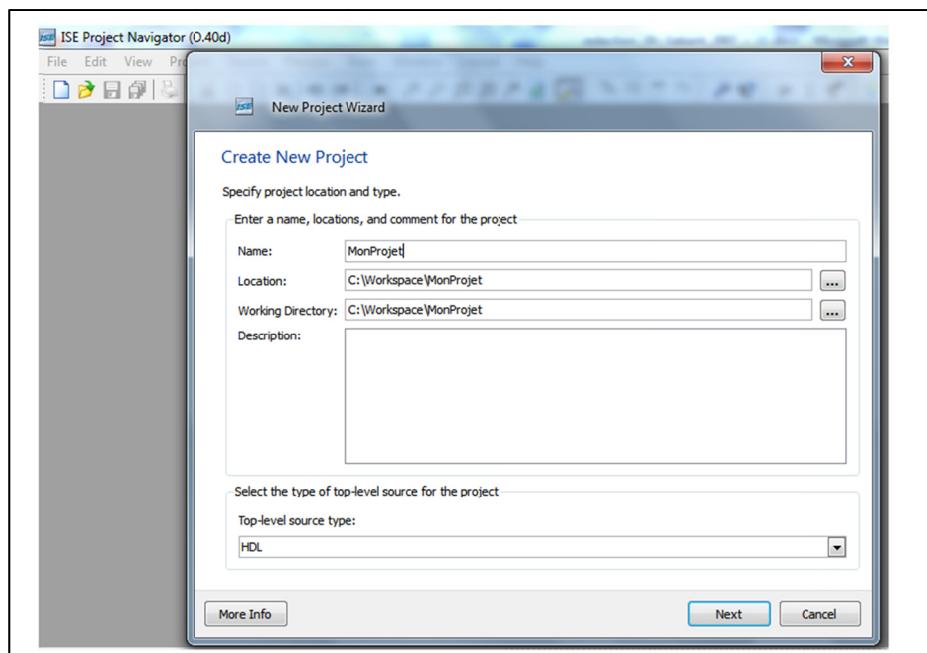

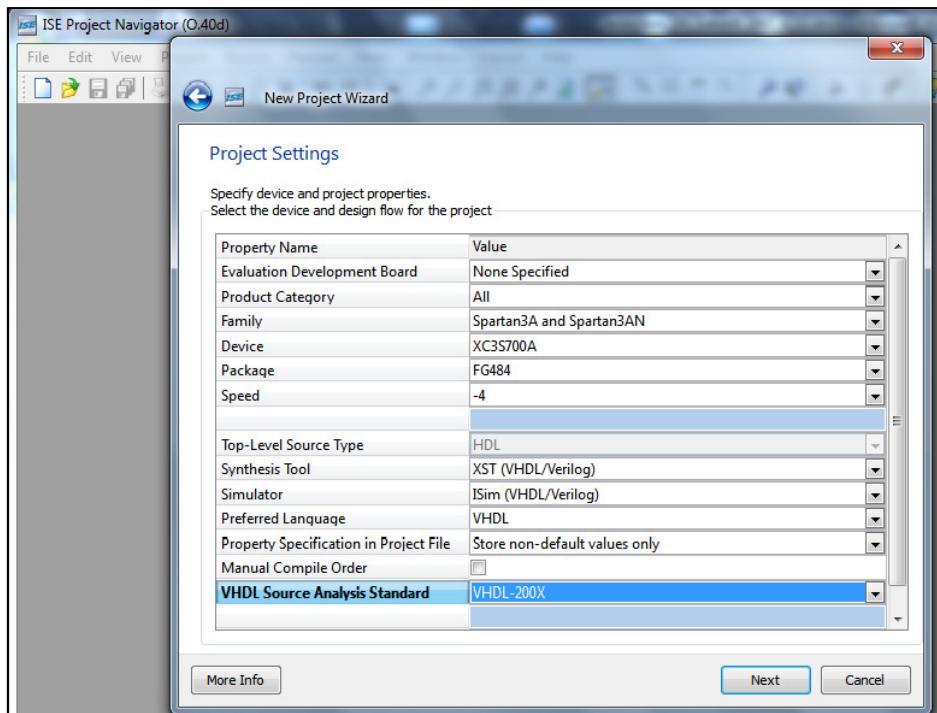

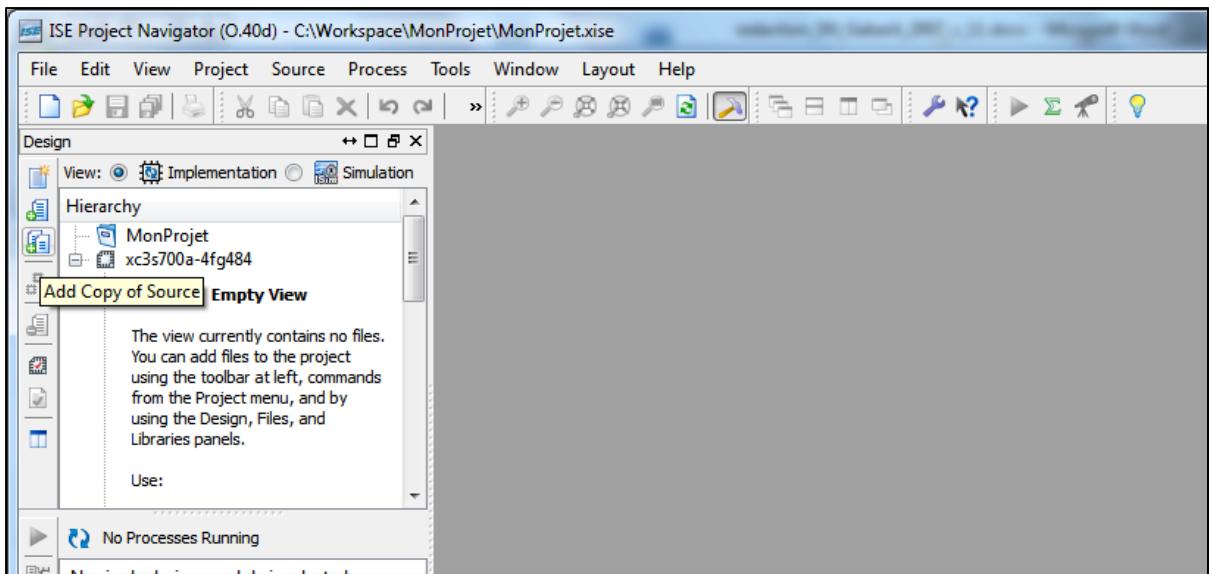

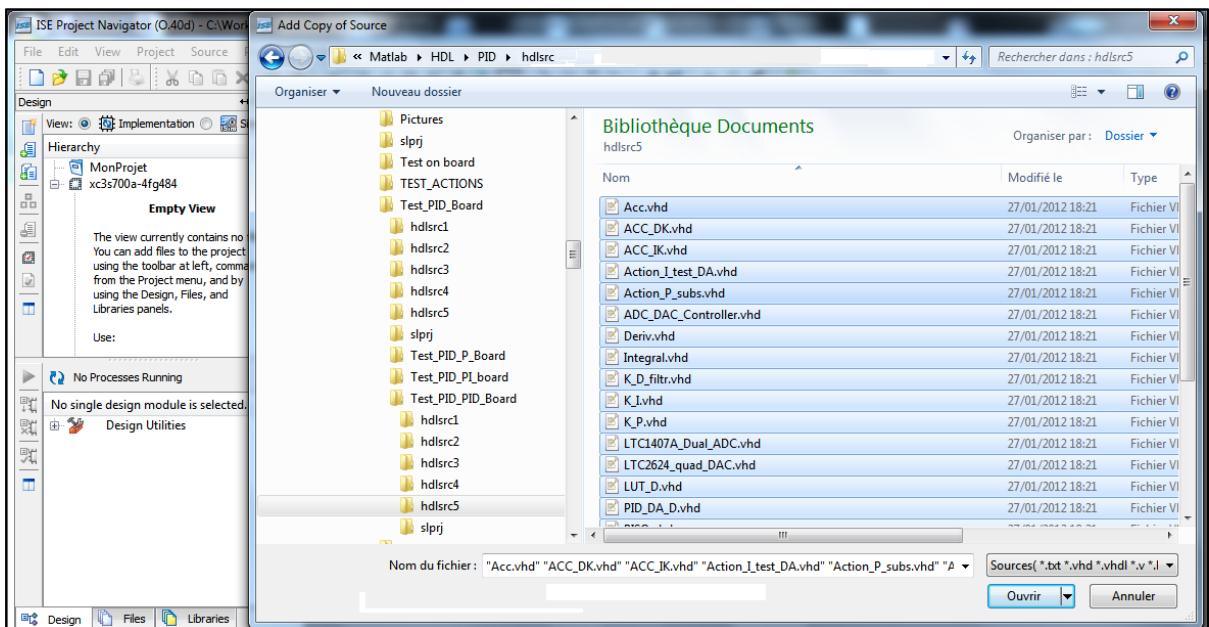

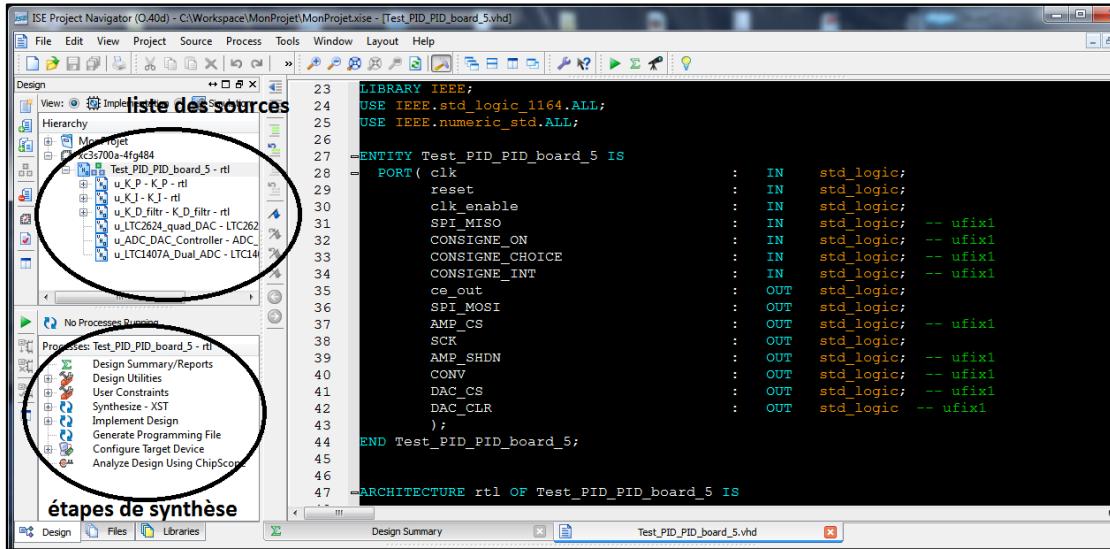

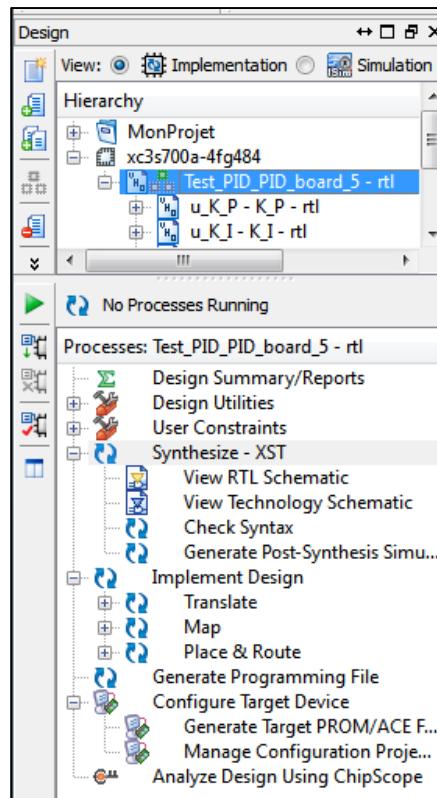

La méthodologie de conception descendante permet grâce aux développements des outils logiciels d'avoir des fonctionnements garantis. Toutefois, il subsiste une rupture dans le *continuum* des EDA. En effet, aujourd’hui nous avons toujours deux phases distinctes lors de la conception de systèmes numériques. D’abord, nous l’avons vu, une étape de conception se réalisant dans un environnement présentant un fort niveau d’abstraction, permet de disposer d’un code HDL synthétisable. Ce code doit ensuite être traité via un second environnement de travail. Ce deuxième ensemble permet un traitement successif correspondant aux étapes de synthèse, d’allocation des ressources, de Placement et routage (PAR pour *Place and Route*) et de génération de fichier de configuration décrite dans la partie 1.2.4. Dans notre travail, nous avons utilisé *Integrated Synthesis Environment* (ISE) proposé par Xilinx qui propose une suite de logiciels permettant la synthèse, le PAR et l’implémentation. Une présentation plus complète de cet environnement est proposée en ANNEXE I. Cet environnement de travail est lui aussi de haut niveau et les étapes du flot de conception sont presque transparentes pour l’utilisateur final. Celui-ci doit simplement s’assurer d’effectuer les tâches dans le bon ordre.

Au final, nous avons retracé l’historique de mise en place de systèmes de haut niveau de conception, en indiquant les raisons et montrant que cela répondait à un réel besoin d’abstraction. En connaissant à présent les bases des FPGA et les moyens de les utiliser, il nous reste à définir leurs domaines d’application.

### 1.3.2 Domaine d'utilisation

La migration technologique au profit des FPGA s’opère selon quatre facteurs selon Paiz (2007) :

- la performance algorithmique ;

- la flexibilité ;

- les coûts ;

- la consommation.

Il convient néanmoins de développer ces quatre points à la lumière de ce que nous avons établi précédemment. Tout d'abord, la performance algorithmique est garantie *via* le calcul parallèle qui réduit le temps de traitement. La flexibilité est assurée par la reconfigurabilité induite par les cellules SRAM et par l'utilisation d'EDA permettant de disposer de systèmes matériels et/ou logiciel. Typiquement, Patel et Moallem (2010) évoque la possibilité d'embarquer des systèmes multiprocesseurs disposant de systèmes d'exploitation temps réel capable de résERVER certaines tâches critiques à une exécution purement matérielle. La réduction des coûts est, quant à elle, rendue possible par plusieurs facteurs comme la réduction du temps de développement ou le rapport coût/performances. En effet, l'augmentation du niveau d'abstraction des EDA a permis la constitution de blocs réutilisables (bibliothèque) écourtant la phase de conception. Par ailleurs, l'émergence des aides à la conception permet de réduire le TTM permettant une plus grande viabilité économique des solutions à base de FPGA. Le rapport coût/performance est utilisé afin de choisir entre DSP et FPGA. En effet, ce rapport permet de savoir combien de DSP sont nécessaires afin de remplir la mission d'un seul FPGA. Les prix des DSP sont souvent moins dispendieux mais ce rapport permet de tirer une conclusion quant au choix qui doit être réalisé. Enfin, la question de la consommation a été traitée dans la littérature, notamment Scrofano, Seonil et Prasanna (2002) qui ont mis en évidence à la fois l'efficacité numérique et énergétique des FPGA par rapport aux DSP dans le cadre de multiplications matricielles.

Toutefois si tous les facteurs énoncés expliquent une tendance globale, il convient de présenter les éléments qui font des FPGA des solutions de choix dans le cas de systèmes de commande.

Les FPGA ont vu une croissance de leur utilisation au sein de systèmes embarqués de commande. Leur faible consommation et le temps de traitement très rapide en fait des candidats de choix. Monmasson (2007) explique que la vitesse d'opération des FPGA en fait des éléments « quasi analogiques » en présentant les avantages des éléments analogiques (délai réduit) tout en évitant les inconvénients (dérvies des paramètres). Leur qualité de système numérique leur permet de disposer d'une grande flexibilité. C'est d'ailleurs ce que souligne Han (2007) en précisant que les FPGA dans les systèmes de commande permettent des ajustements rapides *in situ*. Par ailleurs, l'auteur note également la fiabilité du processus de conception. C'est ainsi que l'utilisation des FPGA à des fins de commande de systèmes s'est répandu en électrotechnique (Li, 2008), équipement médical (Ruei-Xi, Liang-Gee et Lilin, 2000), robotique (Sanchez-Solano et al., 2007) ou électro-hydraulique (Stubkier et al., 2011).

Si les DSP et les FPGA occupent deux champs d'application différents, ceux-ci se recouvrent quant on traite la question des systèmes électriques. Si les solutions logicielles sont privilégiées (i.e. l'emploi de DSP), c'est, selon Monmasson (2007), en raison de la récente émergence des solutions matérielles qui continuent « d'effrayer » les concepteurs traditionnellement habitués aux solutions logicielles. Toutefois, les mœurs évoluent et, Zhang et al. (2010) proposent un enseignement basé sur les logiciels de haut niveau.

En outre, l'efficacité du calcul permet de disposer d'un temps d'inactivité conséquent entre le traitement de deux échantillons. Ce laps de temps peut être mis au service d'une autre activité comme la commande d'un second système. En effet, Garcia et al. (2004) ont mis en place un contrôleur multiple (commande d'un convertisseur DC-DC à 16 phases) au sein d'un même FPGA permettant une plus grande maîtrise de la consommation. Typiquement, ce type d'implémentation constitue un marché de niche pour les FPGA et est particulièrement adapté au domaine aéronautique où la fiabilité et l'énergie forment deux composantes essentielles.

Au final, tous ces éléments rendent les FPGA intéressants dans l'optique de systèmes de commande embarquée. Nous avons vu comment les FPGA étaient conçus et mis en œuvre. Nous avons également essayé de comprendre les efforts récents pour aider le concepteur à

l'aide d'EDA très évolués. Cela nous a permis de définir un domaine d'application cohérent. Nous avons, en outre, pu montrer que les caractéristiques des FPGA (matériels et logiciels) convergeaient vers l'idée d'en disposer comme de systèmes de commande.

## CHAPITRE 2

### CONCEPTION DES SYSTEMES DE COMMANDE

Nous allons, dans cette partie, nous focaliser sur la commande des systèmes. Dans un premier temps, nous rappellerons les notions et concepts qui nous permettront ensuite de poser les bases de la construction de régulateurs. Nous décrirons ensuite deux types de contrôleurs : le PID, largement répandu dans l'industrie, et la commande moderne.

#### 2.1 Notions fondamentales

Nous nous proposons de poser un certain nombre de bases théoriques liées à la commande. D'abord, un rappel mathématique succinct sur la transformée de Laplace nous permettra d'appliquer cette théorie aux systèmes dynamiques en introduisant la notion de *fonction de transfert*. Nous verrons ensuite comment nous les représentons schématiquement avant de présenter les enjeux sous-jacents à la dynamique des systèmes.

##### 2.1.1 La transformée de Laplace

Bensoussan (2008) rappelle la théorie de la transformation de Laplace. La transformée, notée  $F(s)$ , d'un signal continu  $f(t)$  est définie par :

$$F(s) = \int_0^{+\infty} f(t)e^{-st} dt \quad (2.1)$$

Avec  $s$  la variable complexe définie par :

$$s = \sigma + i \omega \quad (2.2)$$

Avec  $(\sigma, \omega) \in \mathbb{R}^2$

Comme le rappelle Astangul (2008) l'équation (2.1) converge pour  $\sigma > \sigma_0$ . La transformée de Laplace,  $F(s)$ , de la fonction  $f(t)$  peut également se noter par :

$$F(s) = \mathcal{L}[f(t)] \quad (2.3)$$

Il existe également une transformation inverse notée  $\mathcal{L}^{-1}$ , qui permet de passer d'un signal décrit dans l'espace de Laplace à un signal temporel. La transformée inverse de Laplace se réalise à l'aide d'une décomposition en éléments simples qui permet de représenter une fonction complexe en une somme de fonctions beaucoup simples permettant d'obtenir un signal dans le temps de façon plus commode (notamment à l'aide de tables).

La transformée de Laplace présente des propriétés tout à fait intéressantes qui nous sont utiles dans le domaine de la commande. Typiquement on peut présenter la propriété de dérivation qui nous servira dans la suite de notre travail. Cherchons la transformée de Laplace de la dérivée de la fonction  $f(t)$ , notée  $f'(t)$ .

Soit  $Re(s) > \sigma_0$

$$\mathcal{L}[f'(t)] = \int_0^{+\infty} f'(t)e^{-st} dt \quad (2.4)$$

$$\mathcal{L}[f'(t)] = sF(s) - f(0) \quad (2.5)$$

De façon plus générale, la dérivée n-ième d'une fonction  $f(t)$ , notée  $f^{(n)}(t)$ , s'exprimera dans l'espace de Laplace par :

$$\mathcal{L}[f^{(n)}(t)] = s^n F(s) - \sum_{i=0}^{n-1} s^{n-1-i} f^{(i)}(0) \quad (2.6)$$

### 2.1.2 La transformée en Z

Dans le cas de signaux discrets on utilise une autre transformation dite en Z. La définition de la transformée en Z monolatérale, notée  $F(z)$ , d'un signal discret  $f(n)$  est :

$$F(z) = \sum_{n=0}^{+\infty} f(n)z^{-n} \quad (2.7)$$

On peut également noter cela par :

$$Z[f(n)] = F(z) \quad (2.8)$$

Une fonction continue, notée  $f(t)$ , soumise à échantillonnage, de période  $T_e$  s'écrit alors  $f_e(t)$  tel que :

$$f_e(t) = \sum_{n=0}^{+\infty} f(nT_e)\delta(t - nT_e) \quad (2.9)$$

On peut alors effectuer la transformée de Laplace de l'expression précédente (Nise, 2011) :

$$F_e(s) = \mathcal{L}[f_e(t)] = \sum_{n=0}^{+\infty} f(nT_e)e^{-nT_e s} \quad (2.10)$$

En posant :

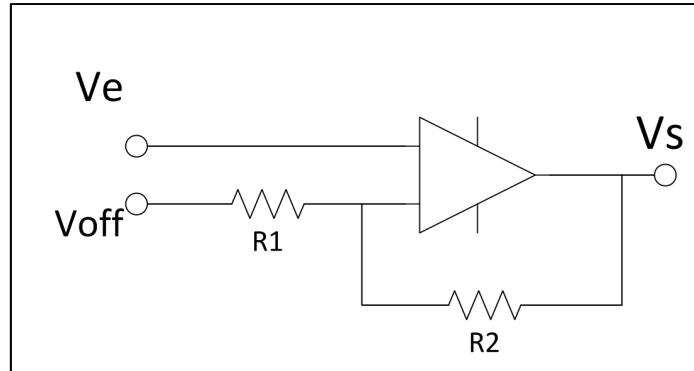

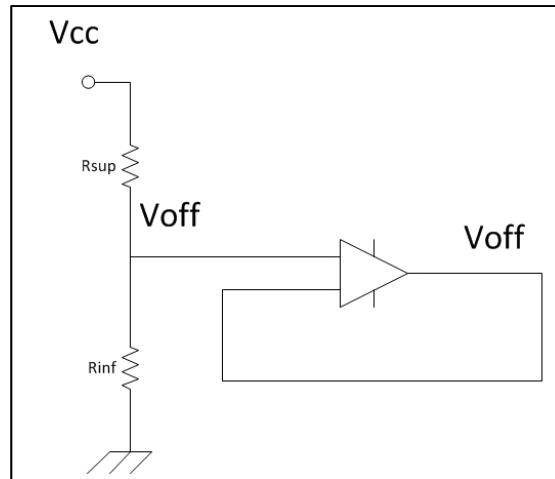

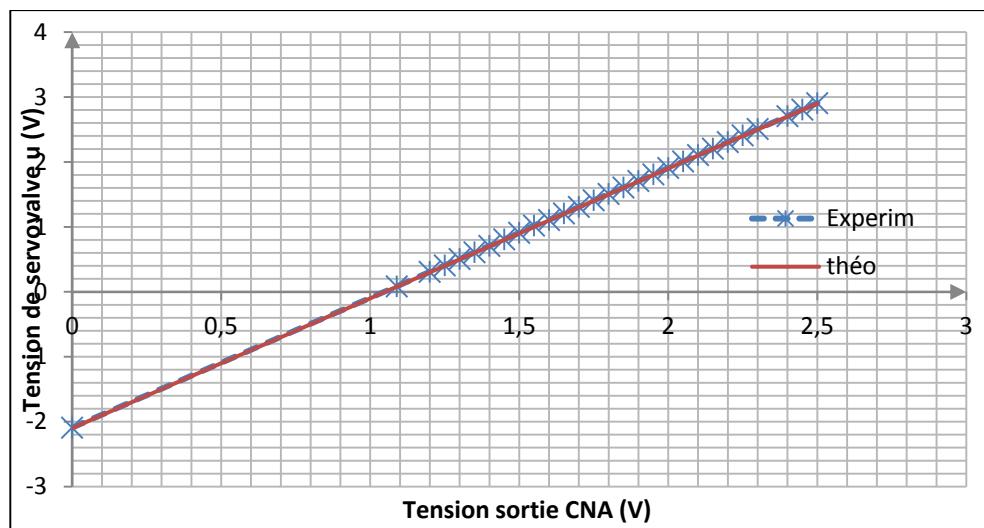

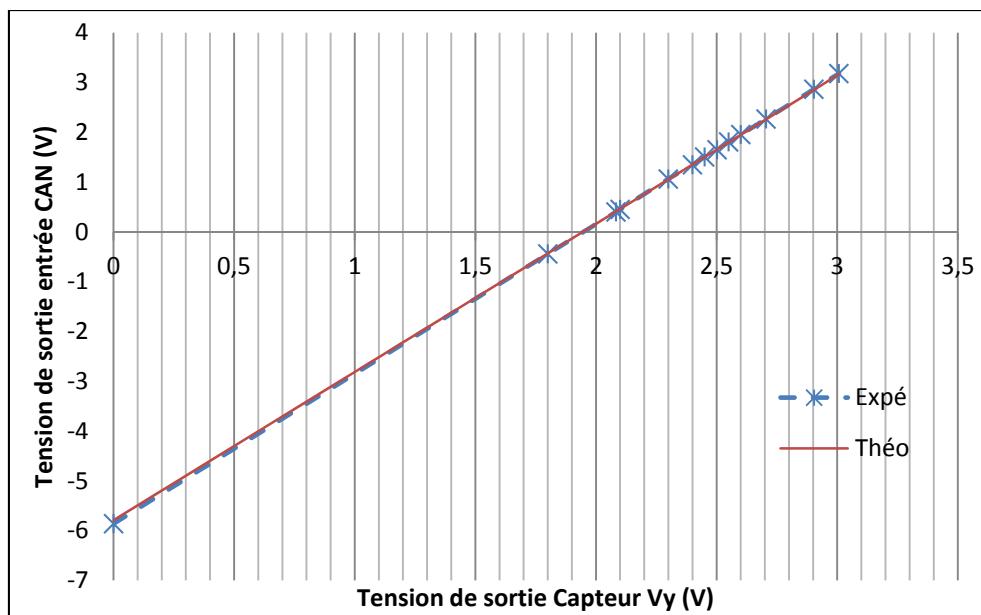

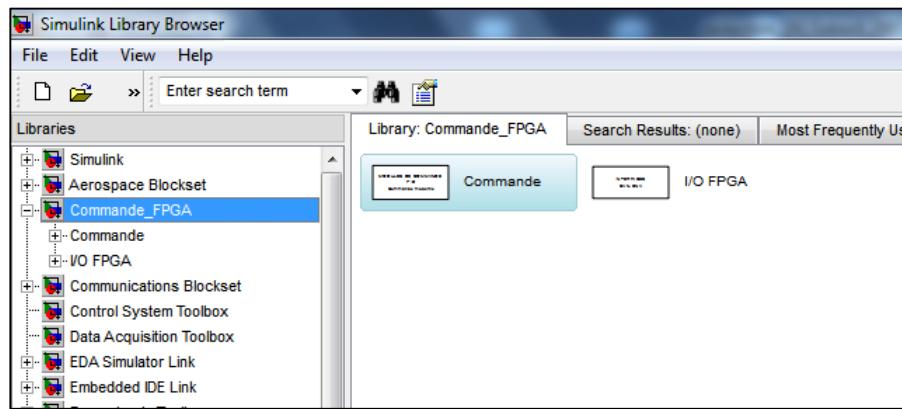

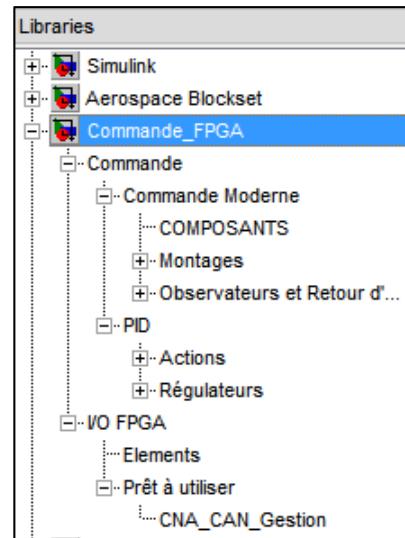

$$z = e^{T_e s} \quad (2.11)$$