# Development, Modulation, and Voltage Balancing of Multi-Level Converters and Modular multilevel Converters (MMCs)

by

# Saeed ARAZM

# MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT OF THE DEGREE OF DOCTOR OF PHILOSOPHY Ph. D.

MONTREAL, DECEMBER 13, 2021

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

This <u>Creative Commons</u> licence allows readers to download this work and share it with others as long as the author is credited. The content of this work can't be modified in any way or used commercially.

## **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Kamal Al-Haddad, Thesis Supervisor Department of Electrical Engineering, École de technologie supérieure

Mr. Gabriel J. Assaf, Chair, Board of Examiners Department of Electrical Engineering, École de technologie supérieure

Mr. Handy Fortin Blanchette, Examiner Department of Electrical Engineering, École de technologie supérieure

Mr. Sheldon Williamson, Independent External Examiner Department of Electrical Engineering, University of Ontario Institute of Technology

THIS THESIS WAS PRENSENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND PUBLIC

ON DECEMBER 10, 2021

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **ACKNOWLEDGMENTS**

I would like to convey my heartfelt gratitude to Professor Kamal Al-Haddad, my thesis director, for allowing me to work under his supervision. My research would not have been accomplished without his focus, good technical direction, patience, support, and encouragement. Certainly, he was the most leading person during my Ph.D. studies, and I hope that the bond we formed during the course of this research endeavor will last for many years to come.

I would also like to express my gratitude to Professor Gabriel J. Assaf, Professor Ambrish Chandra, Professor Handy Fortin Blanchette, Professor Sheldon Williamson, and Professor Kamal-Al-Haddad the members of my Ph.D. committee who eagerly agreed to review my dissertation.

I am appreciative for all of my colleagues' helpful feedback and a particular thanks to my greatest teammate Dr. Vahedi, for his constructive commentary and for his productive feedbacks.

My deep and sincere gratitude to my parents for their endless efforts for my success, for their help, support, and encouragement.

It is a great pleasure to thank my beloved wife without whom I would not have been able to accomplish this project. Thank you for your enduring support, backing, and advice.

Finally, I thank my lovely daughter, without whom I didn't have the strength and determination to overcome the obstacles. Thank you very much Arshida for giving me hope and encouragement to be able to complete this project successfully.

# Développement, modulation et équilibrage de la tension des convertisseurs multiniveaux et des convertisseurs modulaires multiniveaux (CMM)

#### Saeed ARAZM

## RÉSUMÉ

Les topologies de convertisseurs multiniveaux (CMN) permettant de réduire le nombre de composants tout en améliorant la qualité de puissance restent une préoccupation majeure pour les applications industrielles. Bien qu'au cours des dernières années, de nombreux CMN aient été proposés dans le domaine de la recherche pour augmenter les niveaux de tension, les sources de courant continu (CC) isolées et le nombre de dispositifs de commutation sont les facteurs limitatifs de leurs applications dans les industries. Les sources de CC isolées augmentent non seulement le poids, le volume et le coût des onduleurs en raison du transformateur déphaseur, mais aussi les pertes de puissance en raison des redresseurs. Les convertisseurs multiniveaux modulaires (CMM) sont la solution pour remplacer la source CC isolée par une seule source CC; cependant, des multitudes de dispositifs à semi-conducteurs doivent être utilisés dans les demi-pont convertisseurs multiniveaux modulaires (DM-CMM) classiques et populaires pour générer un niveau de tension donné. La gestion du courant de défaut CC, l'équilibrage de la tension dans les condensateurs volants et les courants de circulation sont des questions controversées pour les applications des CMM. Dans la première partie de cette thèse, une topologie à nombre réduit de composants du convertisseur multiniveau est proposée avec une seule source de CC pour les systèmes monophasés et triphasés. Cette topologie unipolaire appelée Z-Packed U-Cell (ZPUC) est utilisée comme sous-module de CMM (ZPUC-CMM) pour augmenter les niveaux de tension par rapport à ses homologues. L'équilibrage de tension intégré à la modulation de largeur d'impulsion de déphasage (MLI-DP) est mis en œuvre sur ce convertisseur pour réguler les tensions des condensateurs. La génération de niveaux de tension plus élevés avec une distorsion harmonique totale (DHT) plus faible fait de ce convertisseur une alternative appropriée pour les applications de haute et moyenne tension telles que les entraînements de moteur. Dans la deuxième partie de cette thèse, un équilibrage de tension basé sur l'apprentissage profond et intégré à la modulation par largeur d'impulsion à décalage de niveau (MLI-DN) et à la MLI-DP hybrides avec une tension de référence unique est mis en œuvre sur le ZPUC-CMM pour augmenter les niveaux de tension. Les résultats de simulation en état d'équilibre sont utilisés pour former l'équilibreur de tension d'apprentissage profond et il est mis en œuvre sur ZPUC-CMM dans le laboratoire sur les états stables et transitoires. Dans la dernière partie de cette thèse, la topologie PUC est développée comme un convertisseur Y-PUC triphasé à source unique en CC. Le convertisseur PUC nécessite trois sources CC isolées pour un système triphasé, ce qui limite son application. La topologie Y-PUC qui est un convertisseur modulaire multiniveau (PUC-CMM) avec sous-module PUC est proposé pour résoudre ce problème. Le Y-PUC modulaire peut être utilisé dans l'application HVDC en raison du fait que PUC est un convertisseur bipolaire, et il est capable de bloquer le courant de défaut CC. L'équilibrage de tension intégré avec la technique de modulation est mis en œuvre dans Y-PUC pour illustrer les performances du convertisseur proposé dans des états stables et transitoires.

**Mots-clés:** équilibrage de tension, convertisseur multiniveau, convertisseur multiniveau modulaire, ZPUC-CMM, Y-PUC, modulation, apprentissage profond, MLI-DP, MLI-DN

# Development, modulation, and voltage balancing of multilevel converters and modular multilevel converters (MMC)

#### Saeed ARAZM

#### **ABSTRACT**

Multilevel converter (MLC) topologies with lower components counts along with higher power quality are still a major concern for industrial applications. Although in recent years, many MLCs have been proposed in the research area to increase the voltage levels, isolated DC sources and number of switching devices are the limiting factors for their applications in industries. Isolated DC sources not only, increase the weight, volume, and cost of the inverters due to the phase-shift transformer, but also, increase the power losses because of the rectifiers. Modular multilevel converters (MMCs) are the solution to replace the isolated DC source with a single DC source; however, multitudes of semiconductor devices must be utilized in the conventional and popular HB-MMCs to generate a given voltage level. DC fault current handling, voltage balancing in flying capacitors, and circulating currents are controversial issues for MMCs applications. In the first part of this thesis, a single DC source reduced components counts topology of the multilevel converter is proposed for single-phase and threephase systems. This unipolar topology called Z-Packed U-Cell (ZPUC) is used as a submodule of MMC (ZPUC-MMC) to increase the voltage levels over its counterparts. Voltage balancing integrated with phase-shift pulse width modulation (PS-PWM) is implemented on this converter to regulate the voltages of the capacitors. Higher voltage levels waveform generation with a lower total harmonic distortion (THD) makes this converter an appropriate alternative for high power and medium voltage applications such as motor drives. In the second part of this thesis, a deep-learning-based voltage balancing integrated with hybrid level-shift pulse width modulation (LS-PWM) and PS-PWM with a single reference voltage is implemented on ZPUC-MMC to increase the voltage levels. Simulation results in steady states are employed to train the deep-learning voltage balancer and it is implemented on ZPUC-MMC in the lab on both steady and transient states. In the final part of this thesis, PUC topology is developed as a single DC source three-phase Y-PUC converter. PUC converter requires three isolated DC sources for a three-phase system which limits its application. Y-PUC topology that is a modular multilevel converter (PUC-MMC) with PUC submodule is proposed to address this problem. Modular Y-PUC can be used in HVDC applications due that PUC is a bipolar converter, and it is capable to block DC fault current. Voltage balancing integrated with modulation technique is implemented in Y-PUC to illustrates the performance of the proposed converter in steady and transient states.

**Keywords:** voltage balancing, multilevel converter, modular multilevel converter, ZPUC-MMC, Y-PUC, modulation, deep-learning, PS-PWM, LS-PWM

# **TABLE OF CONTENTS**

|      |          |                                                       | Page |

|------|----------|-------------------------------------------------------|------|

| INTI | RODUCTIO | ON                                                    | 1    |

| СНА  | PTER 1   | LITERATURE RIVIEW ON MULTILEVEL AND                   |      |

|      |          | MODULAR MULTILEVEL CONVERTERS                         | 11   |

| 1.1  | Introduc | tion                                                  | 11   |

| 1.2  |          | ional 2-Level converters                              |      |

| 1.3  | Multilev | el converters topologies                              | 13   |

|      | 1.3.1    | Cascaded H-Bridge                                     | 13   |

|      | 1.3.2    | Neutral Point Clamped (NPC) and its family topologies | 17   |

|      | 1.3.3    | Hybrid T-type NPC and FC H-bridge:                    |      |

|      | 1.3.4    | Topologies T-Type based structure:                    |      |

|      | 1.3.5    | Packed U-Cell (PUC) topology and switching states     |      |

|      | 1.3.6    | Topologies with PUC structures                        |      |

| 1.4  |          | multilevel converters (MMCs)                          |      |

| 1.5  |          | ion strategies                                        |      |

|      | 1.5.1    | Level-shift Modulation (LS-PWM)                       |      |

|      | 1.5.2    | Phase shift modulation (PS-PWM)                       |      |

|      | 1.5.3    | Space Vector Modulation Method (SVM)                  |      |

| 1.6  |          | ıl application                                        |      |

| 1.7  | Conclusi | ion                                                   | 45   |

| СНА  | PTER 2   | ZPUC: A NEW CONFIGURATION OF SINGLE DC                |      |

| CHA  | II ILK 2 | SOURCE FOR MODULAR MULTILEVEL CONVERTER               |      |

|      |          | (MMC) APPLICATIONS                                    | 47   |

| 2.1  | Abstract | (MMC) THE DETITION                                    |      |

| 2.2  |          | tion                                                  |      |

| 2.3  |          | opology and switching states                          |      |

|      | 2.3.1    | Switching States of ZPUC5                             |      |

|      | 2.3.2    | Voltage Balancing Method on Single Module of ZPUC5    | 57   |

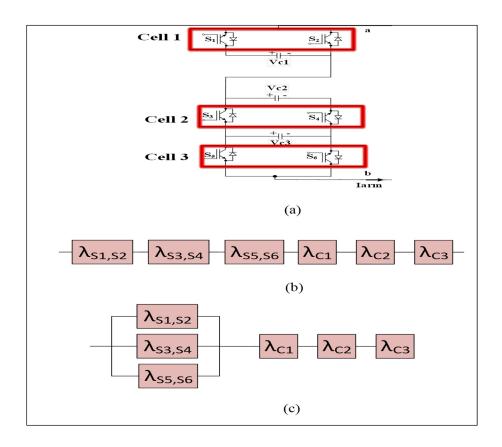

|      | 2.3.3    | Reliability of One Module of ZPUC Topology            |      |

|      | 2.3.4    | Voltage Balancing Method On Three-Phase               |      |

|      |          | ZPUC Multilevel Converter                             | 63   |

| 2.4  | Applicat | ion of ZPUC5 on Modular Multilevel Converters (MMCs)  | 65   |

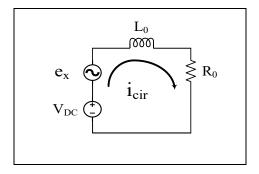

|      | 2.4.1    | Circulating Current in ZPUC-MMC                       | 69   |

|      | 2.4.2    | Power losses in ZPUC-MMC                              |      |

|      | 2.4.3    | Flying Capacitor design                               | 73   |

|      | 2.4.4    | Grid Connected Mode of ZPUC-MMC                       |      |

| 2.5  |          | on Results                                            |      |

|      | 2.5.1    | Standalone mode                                       |      |

| _    | 2.5.2    | Grid-connected mode                                   |      |

| 2.6  | Experim  | ental Results                                         | 85   |

| 2.7  | Conclusio       | on                                                                 | 91  |

|------|-----------------|--------------------------------------------------------------------|-----|

| CHA  | PTER 3          | DEEP LEARNING-BASED VOLTAGE BALANCING                              |     |

| CIII | TLICS           | INTEGRATED WITH HYBRID SPWM TO INCREASE                            |     |

|      |                 | VOLTAGE LEVELS IN ZPUC-MMC                                         | 93  |

| 3.1  | Abstract        |                                                                    |     |

| 3.2  |                 | on                                                                 |     |

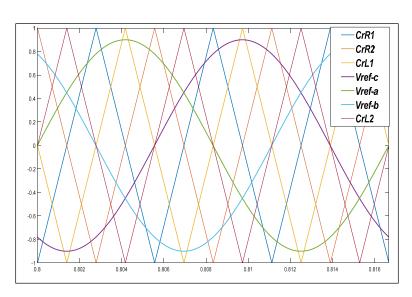

| 3.3  |                 | arrier-Based PWM                                                   |     |

|      | 3.3.1           | 8N+1 Increased Voltage Level Algorithm                             |     |

| 3.4  | Deep Lea        | rning-Based Voltage Balancer                                       |     |

|      | 3.4.1           | Data Preparation and Normalization                                 | 103 |

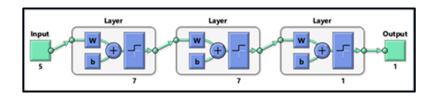

|      | 3.4.2           | 3-Layer Neural Network                                             |     |

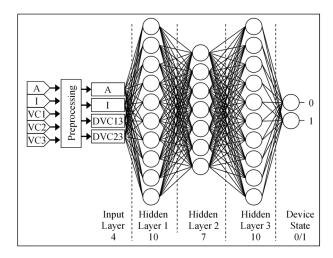

|      | 3.4.3           | Fully Connected Neural Network                                     | 107 |

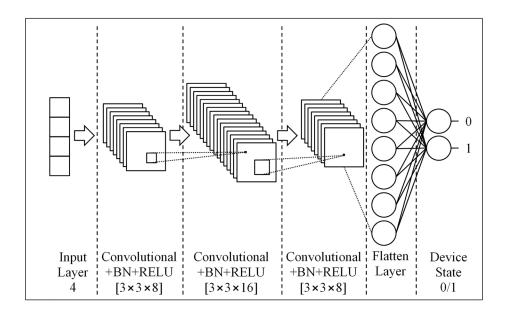

|      | 3.4.4           | Convolutional Neural Network                                       | 108 |

| 3.5  | Results         |                                                                    | 109 |

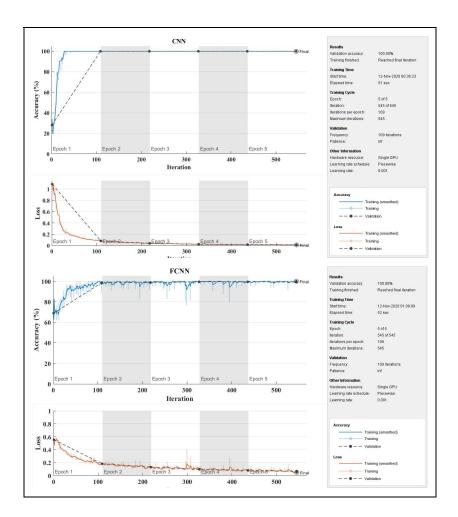

|      | 3.5.1           | Comparison of Deep Learning Methods                                | 110 |

|      | 3.5.2           | Experimental results                                               |     |

|      | 3.5.3           | Conclusion                                                         | 121 |

| CHA  | PTER 4          | A NOVEL SINGLE DC SOURCE THREE-PHASE                               |     |

|      |                 | WYE PACKED U-CELL (Y-PUC) CONVERTER                                | 123 |

| 4.1  | Abstract        |                                                                    | 123 |

| 4.2  | Introducti      | on                                                                 | 124 |

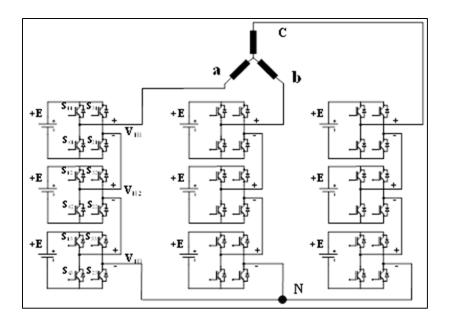

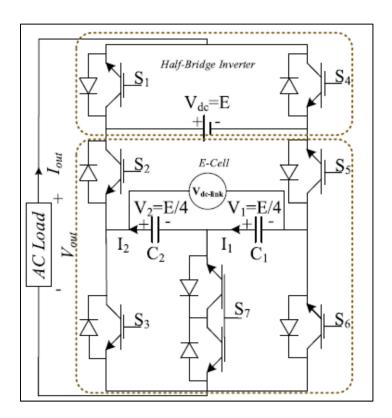

| 4.3  | Topology        | Description and Analysis                                           | 127 |

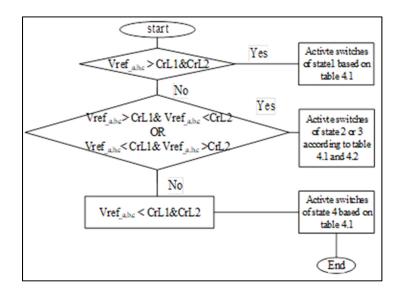

|      | 4.3.1           | Switching States and Voltage Balancing in Single Module of PUC5    | 128 |

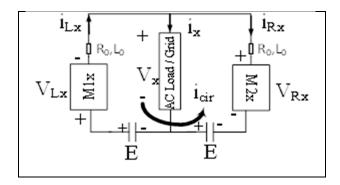

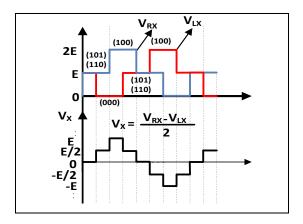

|      | 4.3.2           | Switching States and Circulating Currents of Y-PUC                 | 131 |

|      | 4.3.3           | Voltage balancing integrated with phase-shift modulation on Y-PUC. | 136 |

|      | 4.3.4           | DC fault blocking on modular Y-PUC converter                       |     |

|      | 4.3.5           | Full comparison between Y-PUC and HB-MMC                           | 145 |

| 4.4  | Simulation      | n Results                                                          | 145 |

| 4.5  | -               | ntal Results                                                       |     |

| 4.6  | Conclusio       | on                                                                 | 154 |

| CON  | CLUSION         |                                                                    | 157 |

| RECO | OMMEND <i>A</i> | ATIONS                                                             | 161 |

| APPE | ENDIX I         | GENERALIZED PS-PWM WITH CASE STUDY ON PUC5                         | 163 |

| LIST | OF REFER        | ENCES                                                              | 173 |

# LIST OF TABLES

|           |                                                                                                         | Page |

|-----------|---------------------------------------------------------------------------------------------------------|------|

| Table 1.1 | Switching States of 5L CHB With Equal DC Source                                                         | 15   |

| Table 1.2 | Component Counts of Single-Phase MLCs to Generate 5L Waveform                                           | 23   |

| Table 1.3 | Switching States of PUC Converter to Generate 5 and 7 Level Waveform                                    | 24   |

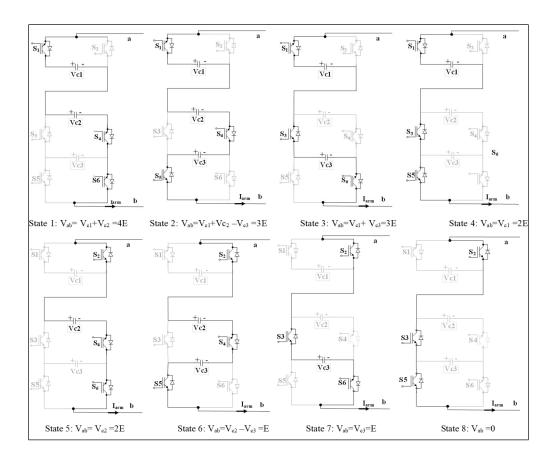

| Table 2.1 | Switching States of ZPUC Converter to Generate Five and Seven Level Waveforms                           | 54   |

| Table 2.2 | Components Counts Of Three-Phase Inverters to Generate 9-L Phase Voltage Wave                           | 57   |

| Table 2.3 | Situations of Charging and Discharging of Flying Capacitors at Corresponding States                     | 58   |

| Table 2.4 | Voltage balancing Algorithm for ZPUC of figure 2.2                                                      | 59   |

| Table 2.5 | V <sub>diff</sub> in Corresponding Lower and Upper Arms Voltages                                        | 70   |

| Table 2.6 | Power Losses Comparison Between HB-MMC and ZPUC-MMC with 9-L Output Waveform                            | 73   |

| Table 2.7 | Simulation and Experimental Parameters of Stand-alone Mode                                              | 76   |

| Table 2.8 | Simulation Parameters of Grid-Connected Mode                                                            | 82   |

| Table 3.1 | Switching States of ZPUC Submodule                                                                      | 100  |

| Table 3.2 | Training Data Fields                                                                                    | 106  |

| Table 3.3 | Confusion Matrix of 3-NN                                                                                | 111  |

| Table 3.4 | Confusion Matrix of FCNN                                                                                | 112  |

| Table 3.5 | Confusion matrix of CNN                                                                                 | 113  |

| Table 3.6 | Simulation and Experimental Parameters of Stand-alone Mode                                              | 115  |

| Table 3.7 | Comparison Among the MMCs for Single-phase 9L Waveform Generation with N Submodules per Arms (Vdc=100V) | 120  |

| Table 4.1 | Switching States of PUC5 Converter                                                                      | 129  |

| Table 4.2 | Selection of States on PUC5                                                                                                               | 130 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.3 | Switching States of Y-PUC to Generate 5-Level Waveform                                                                                    | 134 |

| Table 4.4 | Charge and Discharge Situation on Flying Capacitors of One Phase of Double Star Y-PUC5 Inverter                                           | 138 |

| Table 4.5 | Selection of Suitable States on Y-PUC                                                                                                     | 139 |

| Table 4.6 | Comparison of Modular Multilevel Converters and Y-PUC to Generate Single-phase 21 Voltage Levels at the Output when DC Link Voltage is 2E | 143 |

| Table 4.7 | Comparison the Technical Specifications Among Three Types of MMCs                                                                         | 144 |

| Table 4.8 | System Parameters for Proposed Y-PUC5 Configuration                                                                                       | 145 |

# LIST OF FIGURES

|             | I                                                                                                                | Page |

|-------------|------------------------------------------------------------------------------------------------------------------|------|

| Figure 0.1  | Share of renewables and coal in global power generation                                                          | 1    |

| Figure 0.2  | Annual change of wind capacity                                                                                   | 2    |

| Figure 0.3  | Annual change of solar capacity                                                                                  | 2    |

| Figure 0.4  | Semiconductor technologies in terms of frequency and voltage blocking                                            | 4    |

| Figure 0.5  | Two-Level Conventional converter                                                                                 | 4    |

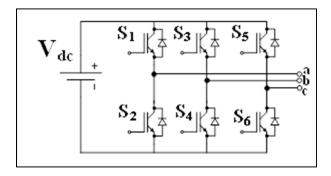

| Figure 1.1  | Conventional 2-L converter with series switches                                                                  | 14   |

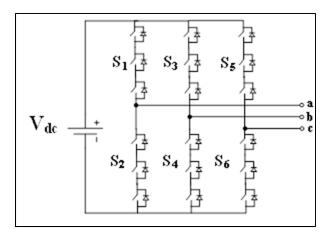

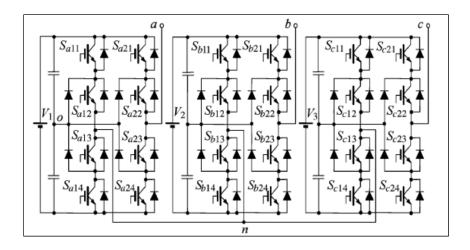

| Figure 1.2  | Three-phase cascaded H-Bridge with 7-L phase-voltage                                                             | 16   |

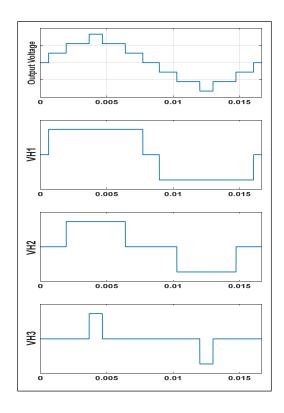

| Figure 1.3  | 7L waveforms in CHB with three cells                                                                             | 16   |

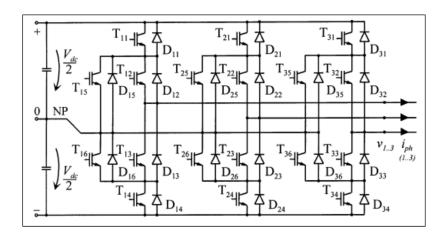

| Figure 1.4  | Three-phase three-level NPC                                                                                      | 17   |

| Figure 1.5  | Load current and phase voltage across the output terminals in 3L NPC                                             | 18   |

| Figure 1.6  | Single-phase 5L NPC                                                                                              | 18   |

| Figure 1.7  | Load current and voltage at the output of 5L NPC                                                                 | 18   |

| Figure 1.8  | Three-phase HNPC to generate 5-level waveform                                                                    | 19   |

| Figure 1.9  | Three level ANPC topology                                                                                        | 19   |

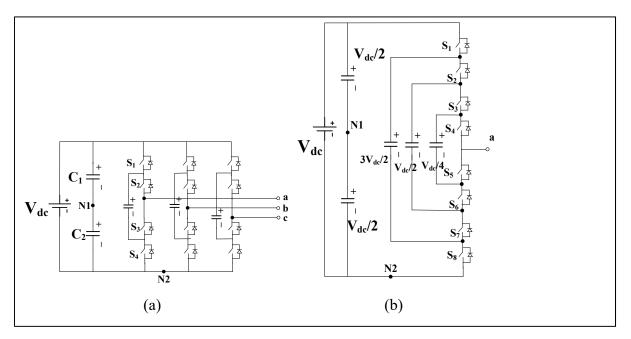

| Figure 1.10 | Flying capacitor multilevel topology a) three-level three-phase FC b) 5L single-phase FC                         | 20   |

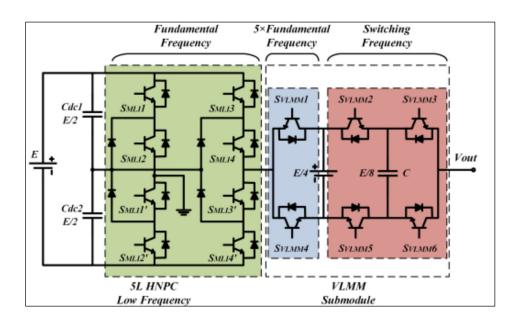

| Figure 1.11 | Hybrid multilevel converter to generate 9L waveform                                                              | 21   |

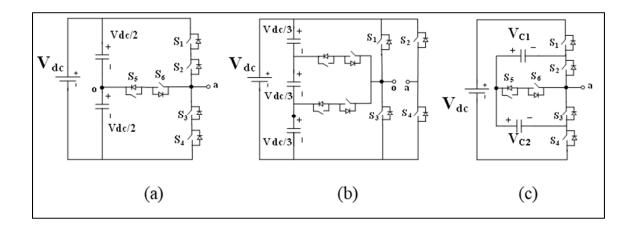

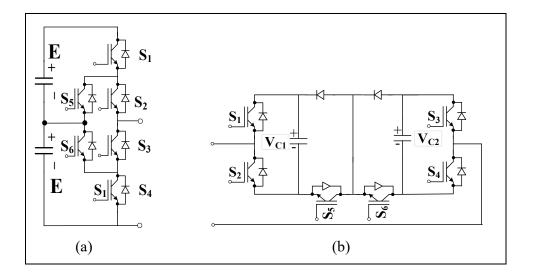

| Figure 1.12 | T-type based multilevel converter topologies a) T-type 3L Converter b) H-Bridge T-type 5L c) T-NNPC 5L converter | 22   |

| Figure 1.13 | PUC topology                                                                                                     | 23   |

| Figure 1.14 | PUC9 converter topology                                                                                          | 25   |

| Figure 1.15 | H-PUC 23Level multilevel converter.                                                                                                                                                  | 25 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.16 | 21 Level Qn-Hybrid HNPC                                                                                                                                                              | 26 |

| Figure 1.17 | Packed E-cell (PEC) multilevel converter topology                                                                                                                                    | 27 |

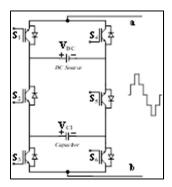

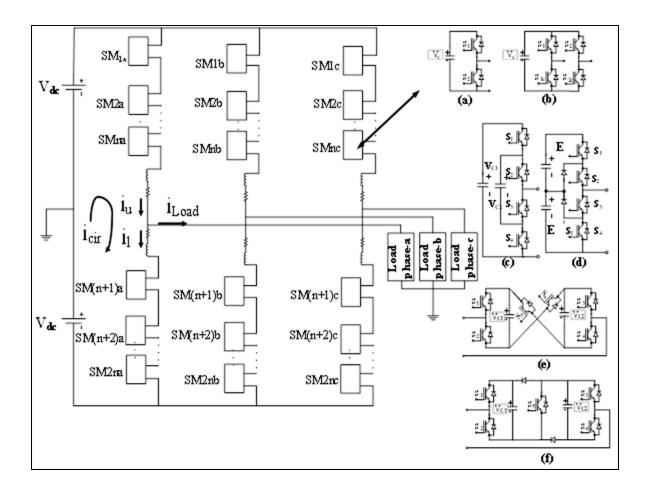

| Figure 1.18 | Double star MMC configuration a) HB-MMC b) FB-MMC c)FC-MMC d) NPC-MMC e) cross connected-MMC f) Double clamped-MMC                                                                   | 30 |

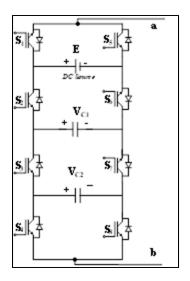

| Figure 1.19 | MMC submodules a) Modified ANPC submodule for MMC b) S-FBDSM.                                                                                                                        | 31 |

| Figure 1.20 | STATCOM with the MMC structure                                                                                                                                                       | 32 |

| Figure 1.21 | Carriers and modulating signals in LS-PWM                                                                                                                                            | 35 |

| Figure 1.22 | Phase shift PWM carrier wave forms                                                                                                                                                   | 36 |

| Figure 1.23 | Implementation of proposed PS-PWM on PUC5 inverter                                                                                                                                   | 37 |

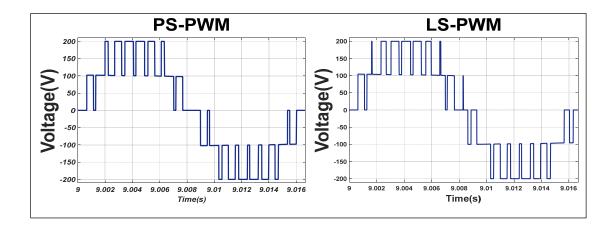

| Figure 1.24 | Waveforms of PS-PWM with 300Hz and LS-PWM with 1200Hz carrier frequency.                                                                                                             | 37 |

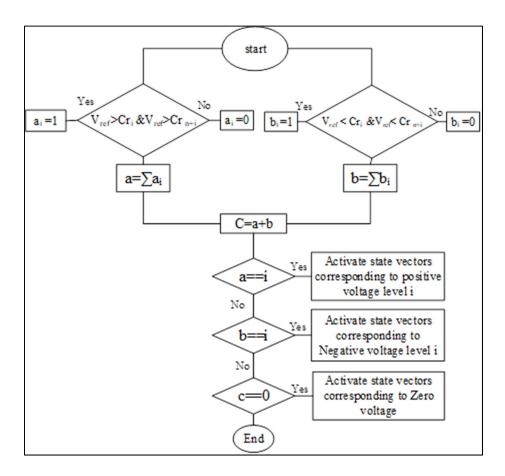

| Figure 1.25 | Generalized PS-PWM flowchart                                                                                                                                                         | 38 |

| Figure 1.26 | Vectors to produce switching states                                                                                                                                                  | 39 |

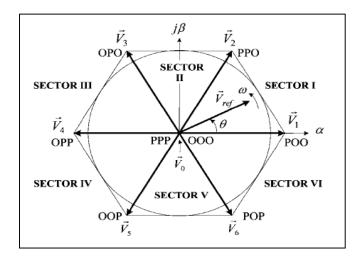

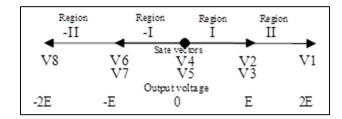

| Figure 1.27 | State vector diagram for five voltage levels at the output of PUC5                                                                                                                   | 41 |

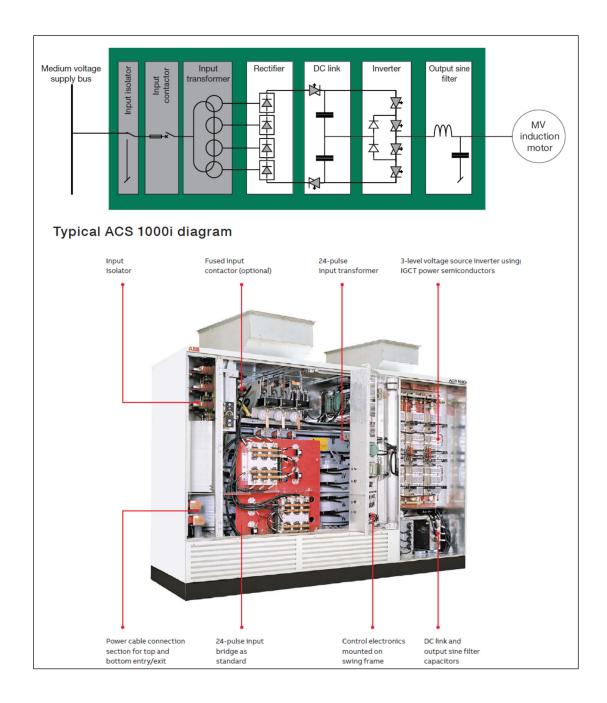

| Figure 1.28 | 3L NPC employed in motor drive 4.16 kV, 5MW                                                                                                                                          | 42 |

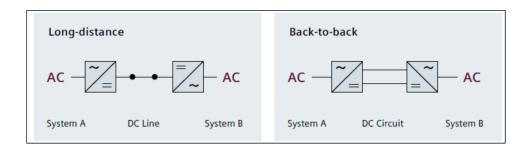

| Figure 1.29 | Diagram of HVDC applications. (Siemens, 2016)                                                                                                                                        | 43 |

| Figure 1.30 | Half-Bridge MMC project for linking between two grids                                                                                                                                | 43 |

| Figure 1.31 | One HB cutting edge submodule with 2 kA current and 6.5 kV rated voltage                                                                                                             | 44 |

| Figure 1.32 | Layout and section of PUC5                                                                                                                                                           | 45 |

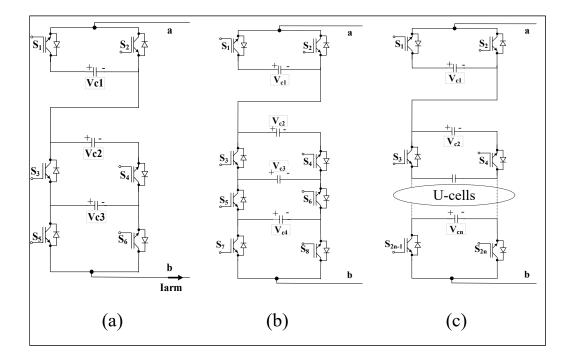

| Figure 2.1  | ZPUC topology (a) Simplest ZPUC converter topology with three capacitors and 6 switches that can generate 5-L or 7-L waveform (b) ZPUC9 or ZPUC15 topology (c) General model of ZPUC | 52 |

| Figure 2.2  | Switching states of ZPUC inverter in standalone mode                                                                                                                                 | 54 |

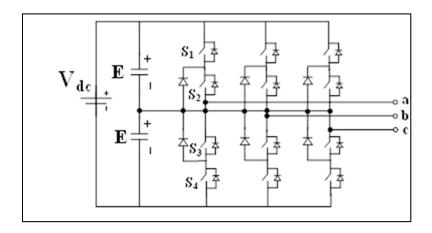

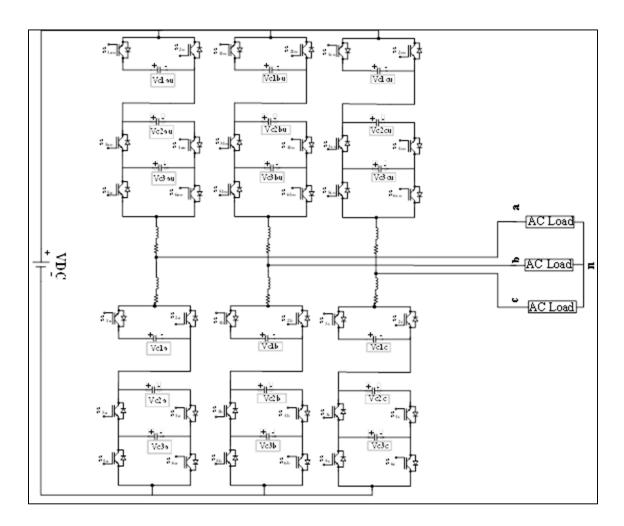

| Figure 2.3  | Three phase ZPUC converter topology which generates 9-L single phase waveform and 17-L line-voltage waveform                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

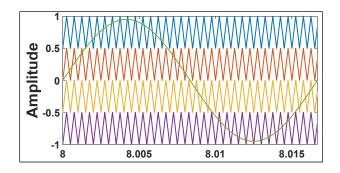

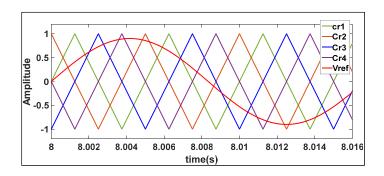

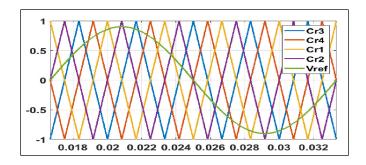

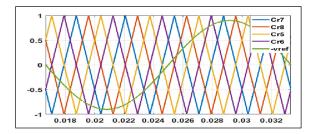

| Figure 2.4  | Carriers and voltage reference for modulation of one module of ZPUC                                                                                                                   |

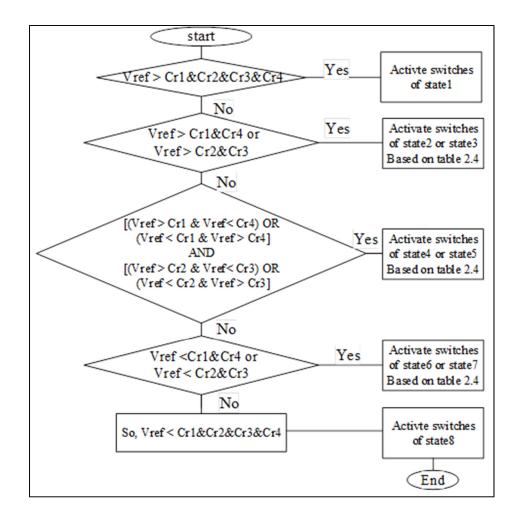

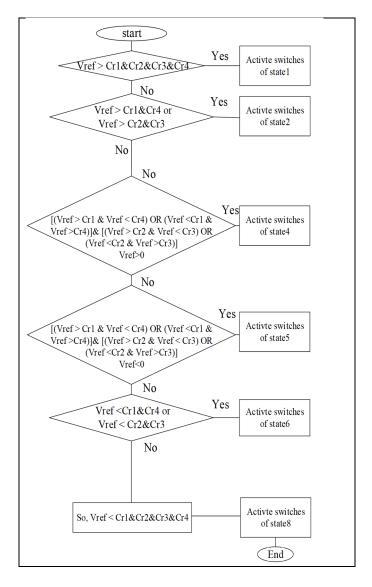

| Figure 2.5  | Flowchart of voltage balancing integrated with phase-shift modulation strategy                                                                                                        |

| Figure 2.6  | Reliability analysis a) Structure of one module of ZPUC topology based on separated Cells, b) reliability block diagram of one module of ZPUC without redundancy c) with redundancy63 |

| Figure 2.7  | Carriers and voltage reference for modulation ZPUC module of the lower arm shown in Figure 2.3                                                                                        |

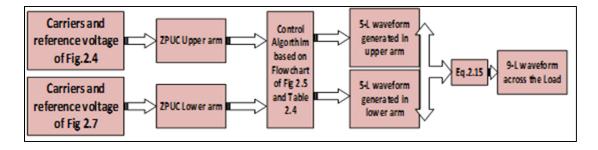

| Figure 2.8  | Control diagram of two ZPUC module in 9-L multilevel converter                                                                                                                        |

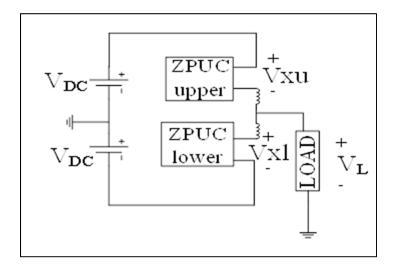

| Figure 2.9  | Single line diagram of 9-L ZPUC converter65                                                                                                                                           |

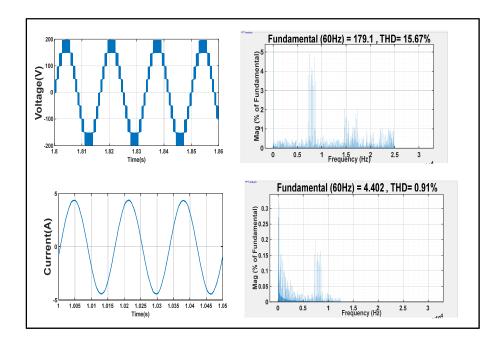

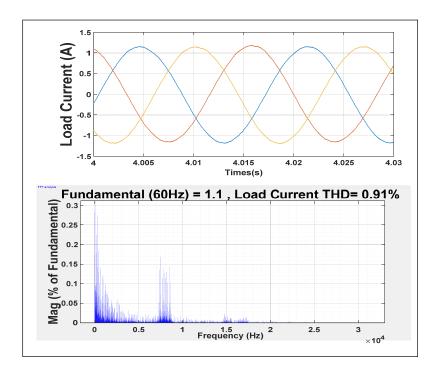

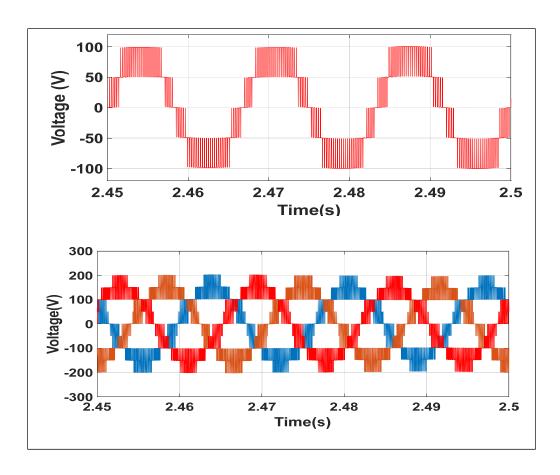

| Figure 2.10 | Voltage and Current waveform, voltage and current THD of single-phase ZPUC of Figure.2.366                                                                                            |

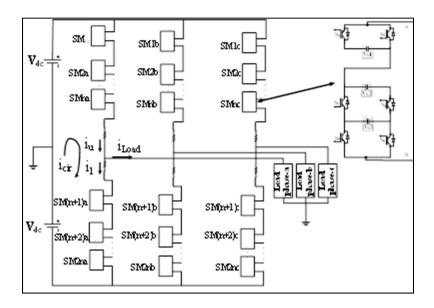

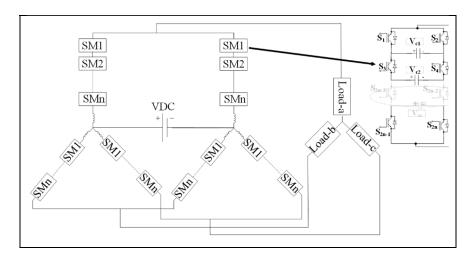

| Figure 2.11 | MMC configuration with ZPUC submodule                                                                                                                                                 |

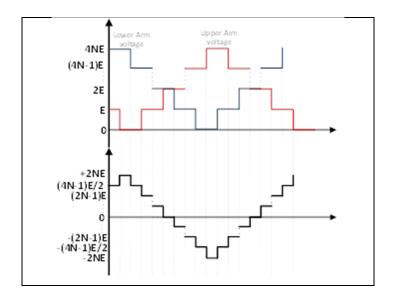

| Figure 2.12 | General voltage waveforms of upper and lower arms and across the load on ZPUC-MMC67                                                                                                   |

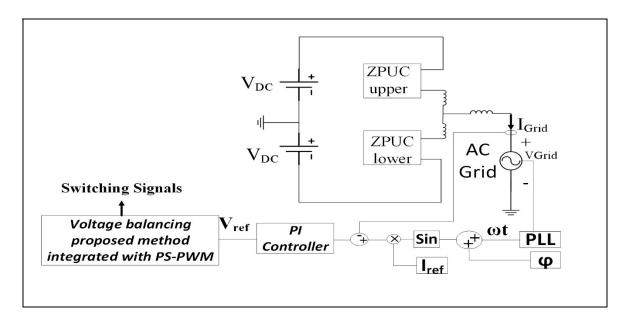

| Figure 2.13 | Single-line diagram of controller for ZPUC converter in grid connected mode                                                                                                           |

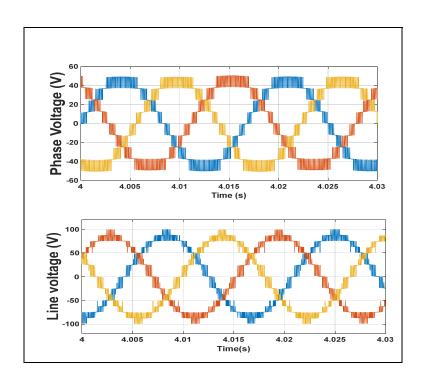

| Figure 2.14 | 9L phase voltages and 17L line voltages in three-phase single DC source ZPUC inverter                                                                                                 |

| Figure 2.15 | Three-phase current and current THD of ZPUC converter77                                                                                                                               |

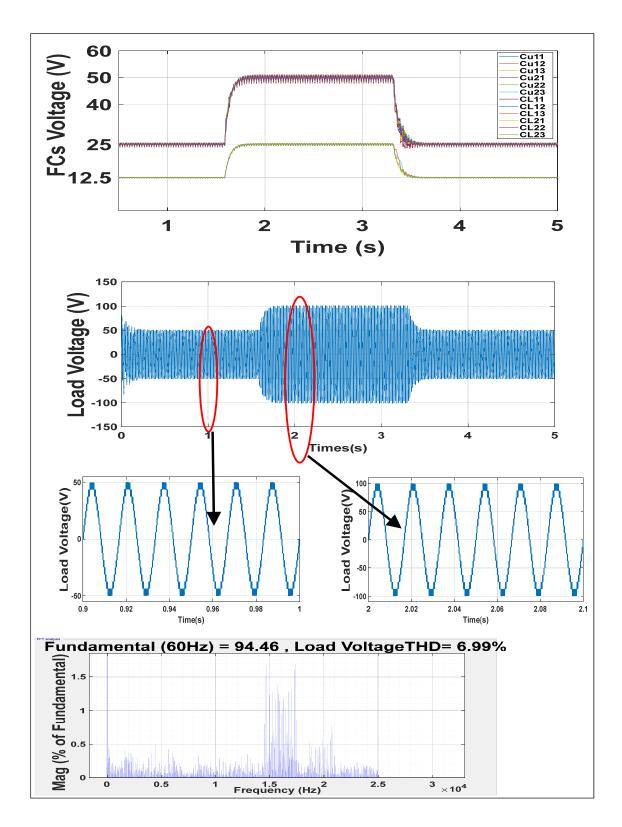

| Figure 2.16 | FCs voltage waveforms and load voltage during the DC link Variation from 100V to 200V and back to 100V, Load voltage THD when the DC link has been increased                          |

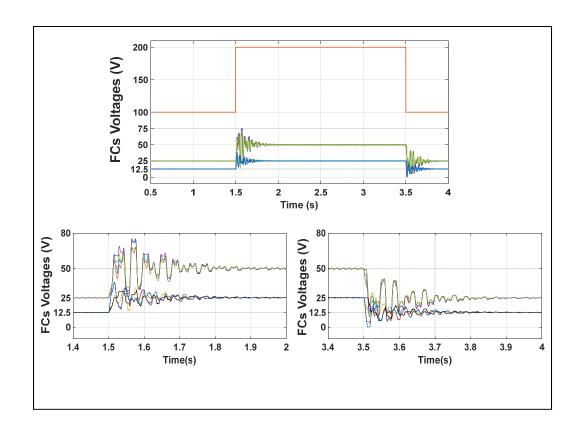

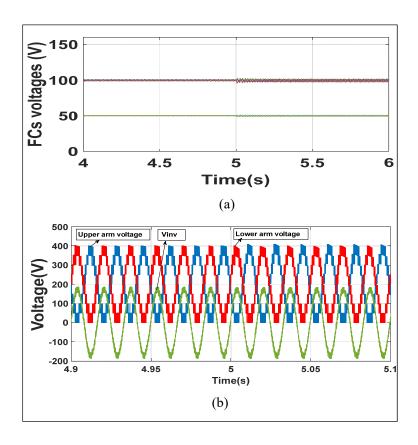

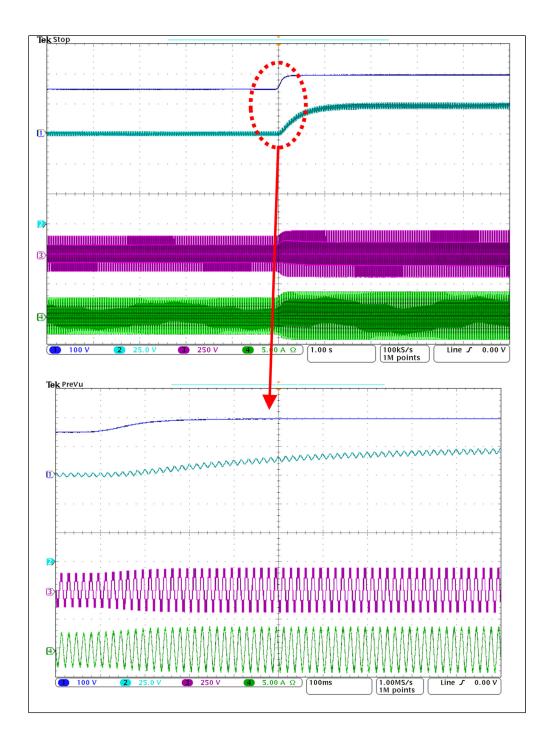

| Figure 2.17 | Dynamic response of ZPUC-MMC converter for a 100% step of dc voltage changing from 100 V to 200 V and then back to 100 V80                                                            |

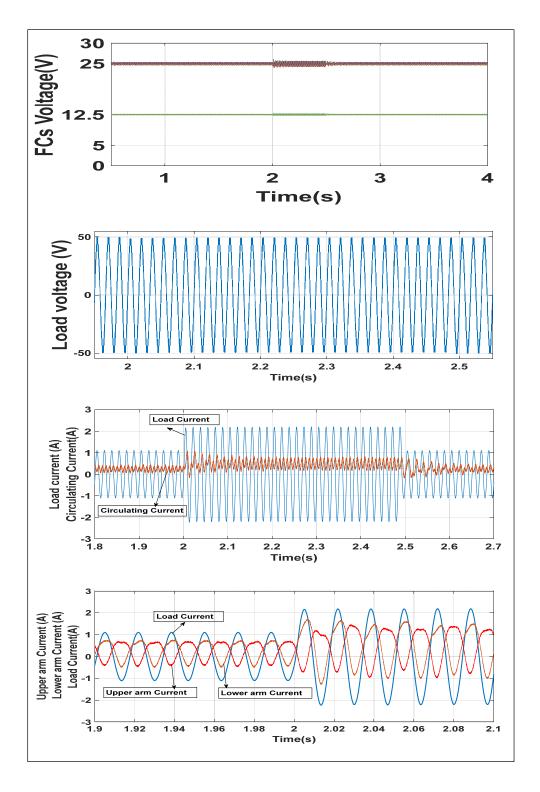

| Figure 2.18 | Wave forms of FCs voltage, load voltage, load current, upper arm current and circulating current during the load variation from $40\Omega-20\Omega-40\Omega$                          |

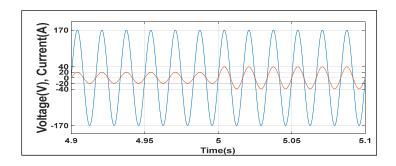

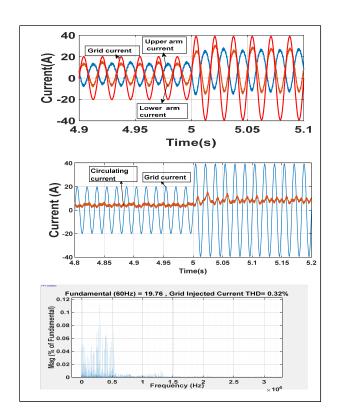

| Figure 2.19 | reference current from 20A to 40A and reference PF=083                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.20 | a) FCs voltages b) upper arm voltage, lower arm voltage and inverter voltage during reference current changes from 20A to 40A and reference PF=0                                                                                    |

| Figure 2.21 | Current waveforms in upper arm, lower arm, load current, circulating current, and current THD during reference current variation from 20A to 40A and reference PF=084                                                               |

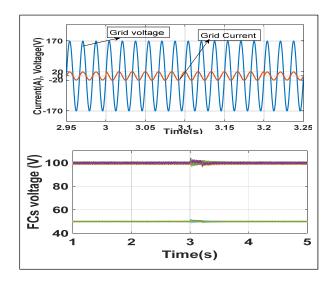

| Figure 2.22 | Grid connected waveforms, grid voltage and current during PF variations from 1 to 0 and again back to 1; and FCs voltage84                                                                                                          |

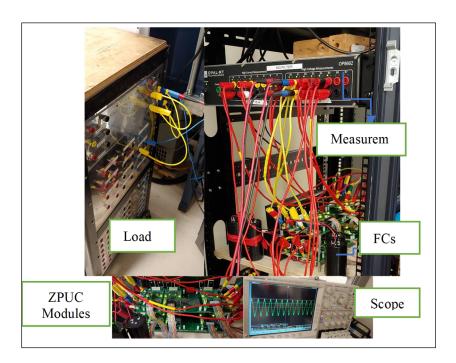

| Figure 2.23 | Experimental setup of the ZPUC multilevel converter85                                                                                                                                                                               |

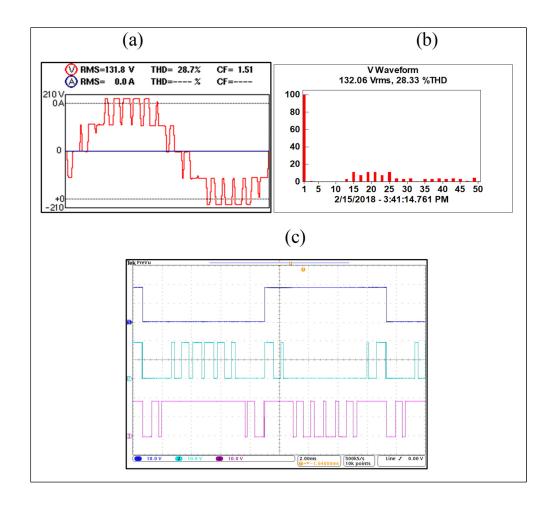

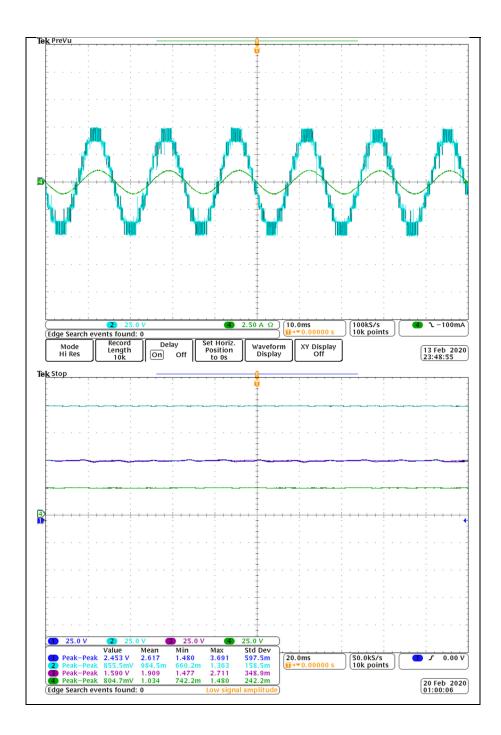

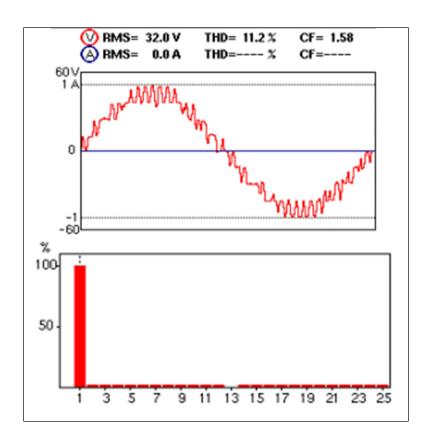

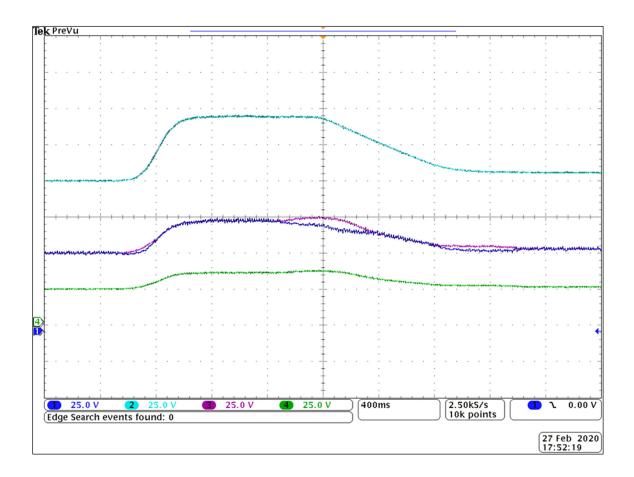

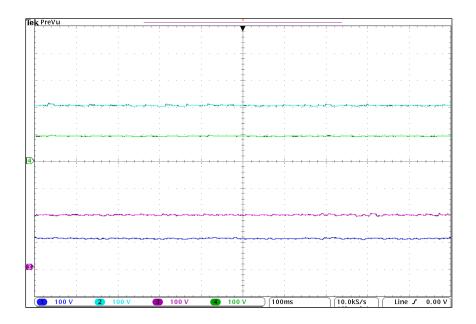

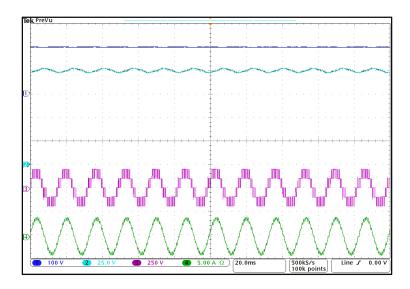

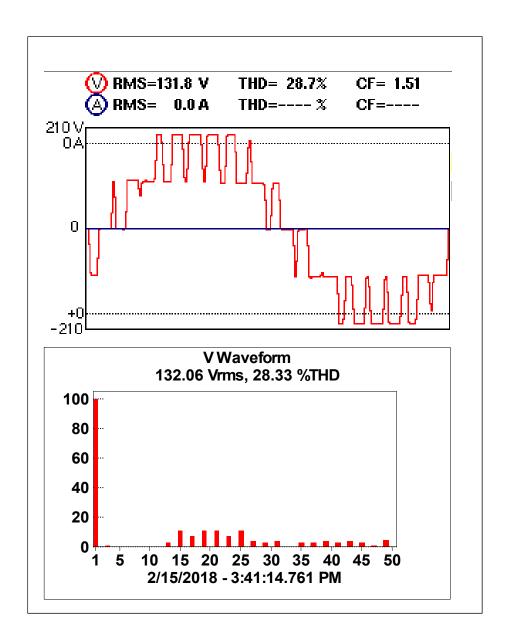

| Figure 2.24 | Load voltage, load current and capacitor voltage balancing86                                                                                                                                                                        |

| Figure 2.25 | Total harmonic distortion of load voltage of ZPUC converter87                                                                                                                                                                       |

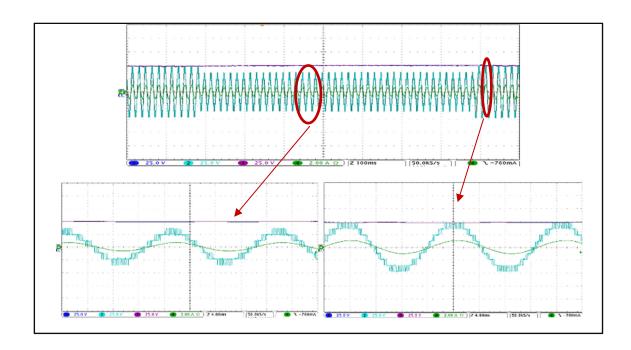

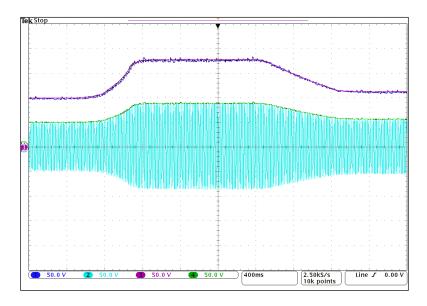

| Figure 2.26 | a) FCs voltages and load current b) Load voltage and load current during the load variation from 40 $\Omega$ -20 $\Omega$ -40 $\Omega$ 88                                                                                           |

| Figure 2.27 | FCs voltage variation during the DC link voltage change Channel 2 (light blue wave is the DC link voltage), Channels 1 and 3 are the voltage of C1 and C2 in upper arm module, Channel 4 is the voltage of C3 at upper arm module89 |

| Figure 2.28 | Load voltage and current during the DC source variation90                                                                                                                                                                           |

| Figure 2.29 | Load voltage, load current, voltage in capacitors C1 and C2 during the modulation index variation from 0.6 to 0.990                                                                                                                 |

| Figure 3.1  | Three-phase ZPUC-MMC configuration                                                                                                                                                                                                  |

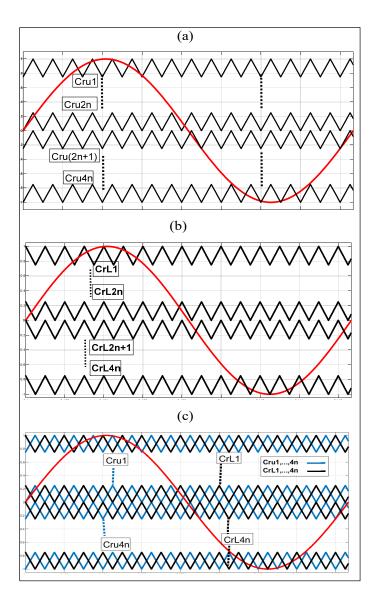

| Figure 3.2  | Carriers and reference signals attributed for upper and lower arms98                                                                                                                                                                |

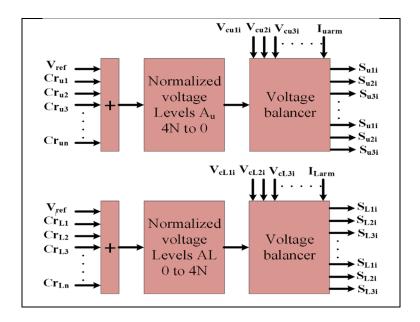

| Figure 3.3  | General control block diagram for upper and lower arms of ZPUC-MMC                                                                                                                                                                  |

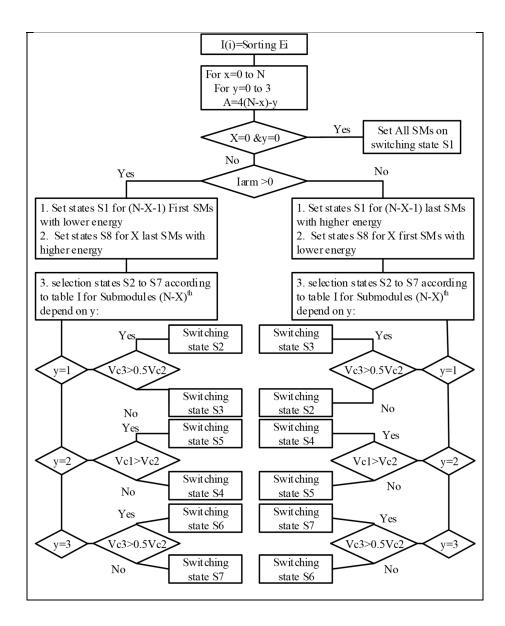

| Figure 3.4  | Voltage balancing algorithm for one arm of ZPUC-MMC102                                                                                                                                                                              |

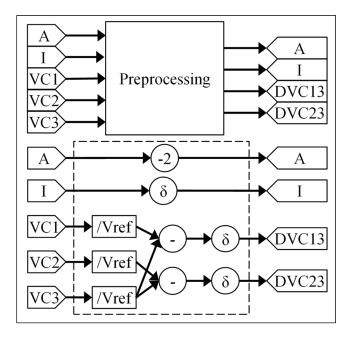

| Figure 3.5  | Preprocessing Module - $\delta(x > 0) = +1$ and $\delta(x < 0) = -1$ 106                                                                                                                                                            |

| Figure 3.6  | The architecture of the designed 3-Layer NN                                                                                                                                                                                         |

| Figure 3.7  | Fully Connected Network Balancer                                                                                                                                                                                                    |

| Figure 3.8  | Fully Connected Network Balancer                                                                                              | 109 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.9  | Simulink results for FCNN                                                                                                     | 114 |

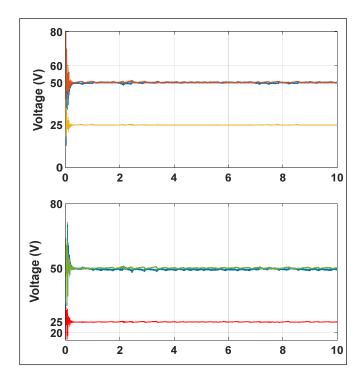

| Figure 3.10 | Simulink results for CNN                                                                                                      | 114 |

| Figure 3.11 | Training process CNN vs FCNN according to accuracy and loss function                                                          | 115 |

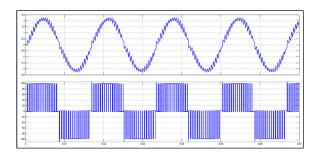

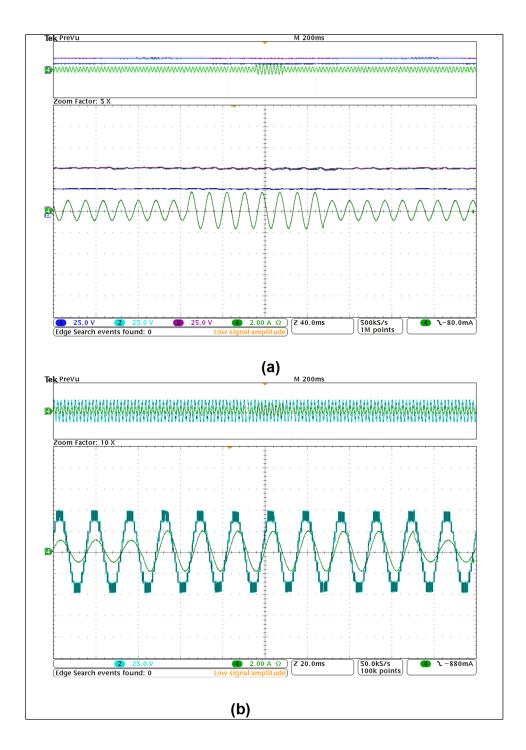

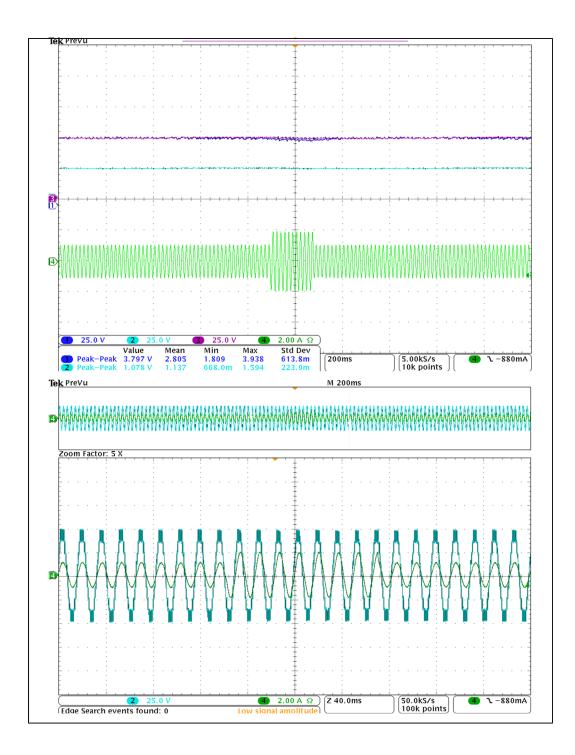

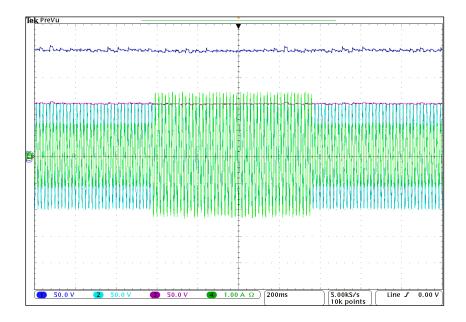

| Figure 3.12 | 9L (8N+1) voltage level waveform (V) and load current (A)                                                                     | 116 |

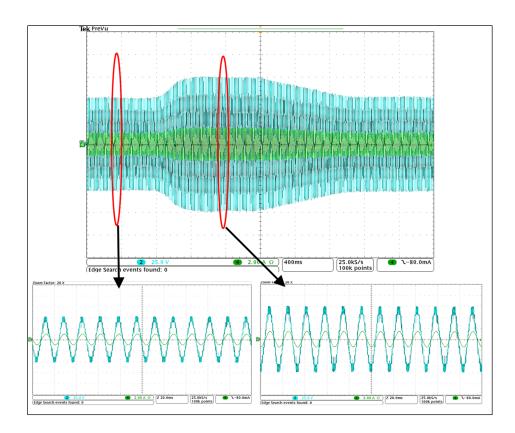

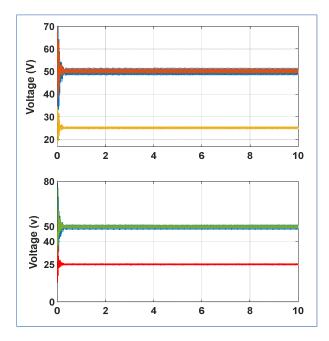

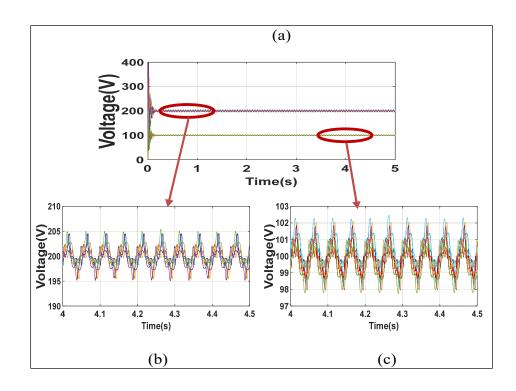

| Figure 3.13 | Flying capacitor voltage balancing on upper and lower arms                                                                    | 117 |

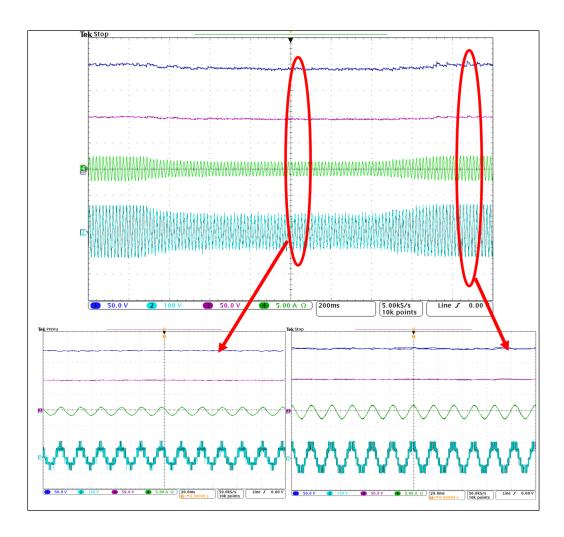

| Figure 3.14 | Load Voltage, load current, and voltage balancing during load variation in the range 40 $\Omega$ -20 $\Omega$ -40 $\Omega$ .  | 118 |

| Figure 3.15 | FCs voltages on upper and lower arms during the DC variation in range 100V-150V-100V.                                         | 119 |

| Figure 3.16 | Output voltage and load current during the DC variation                                                                       | 119 |

| Figure 3.17 | Voltages of FCs, output voltage and load current during modulation index change (0.95-0.6-0.95)                               | 120 |

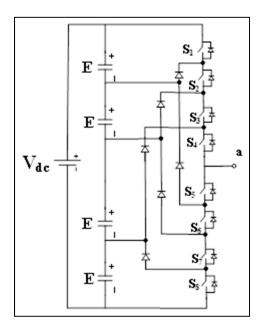

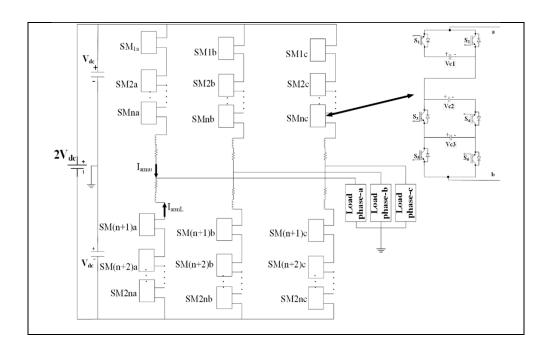

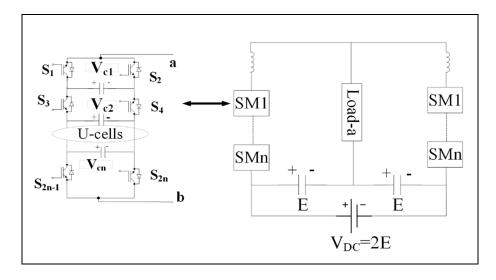

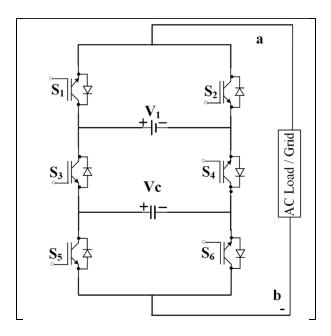

| Figure 4.1  | Single DC source three-phase Modular Wye Packed U-Cell (Y-PUC) Converter                                                      | 127 |

| Figure 4.2  | Single Phase of Proposed Configuration of PUC Converter                                                                       | 128 |

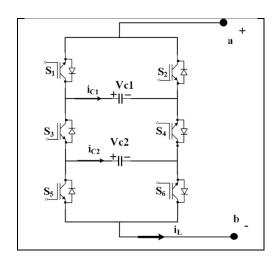

| Figure 4.3  | PUC topology with two flying capacitors as a SM in Y-PUC                                                                      | 129 |

| Figure 4.4  | Single line diagram of proposed PUC converter                                                                                 | 132 |

| Figure 4.5  | Voltage waveform across M1X, M2X and load on phase-x in Y-PUC converter that has been defined by VLX, VRX and VX respectively | 134 |

| Figure 4.6  | Equivalent circuit of circulating current                                                                                     | 136 |

| Figure 4.7  | Carrier signals and reference voltage for modulation of proposed configuration with PUC5                                      | 137 |

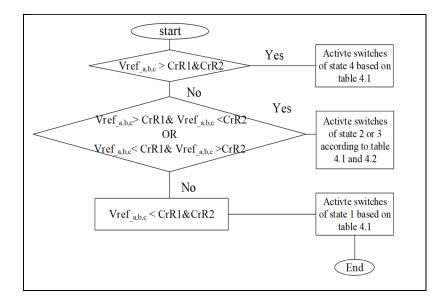

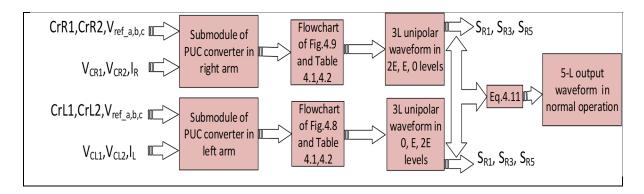

| Figure 4.8  | Voltage balancing integrated with PS-PWM flowchart for left arm of Y-PUC                                                      | 140 |

| Figure 4.9  | Voltage balancing integrated with PS-PWM flowchart for right arm of Y-PUC                                                     | 140 |

| Figure 4.10 | Voltage balancing block diagram control of Y-PUC converter141                                                                                                                                                                                                                                                                                                                                                                      |     |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

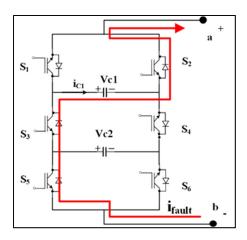

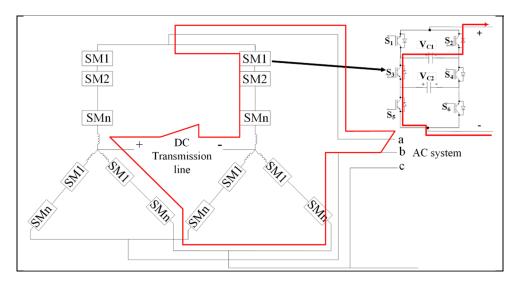

| Figure 4.11 | DC fault current path during the short circuit event                                                                                                                                                                                                                                                                                                                                                                               |     |  |  |  |

| Figure 4.12 | Pole to pole DC short circuit and fault current path during in HVDC system with Y-PUC configuration142                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

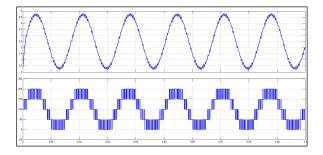

| Figure 4.13 | 5-L single phase voltage and 9-L Line voltage waveform of three-phase single DC source Y-PUC converter                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

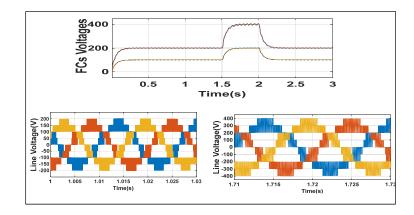

| Figure 4.14 | a) Voltage balancing on flying capacitors b) Voltage balancing across the FCs of upper arm c) Voltage balancing across the FCs of lower arm.                                                                                                                                                                                                                                                                                       |     |  |  |  |

| Figure 4.15 | Flying capacitors voltages during the DC link variation from 200 V to 400 V and returning to 200 V                                                                                                                                                                                                                                                                                                                                 |     |  |  |  |

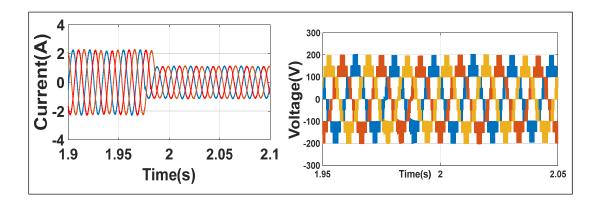

| Figure 4.16 | Current and Voltage waveform at the output of single DC source three-phase PUC due to load variation                                                                                                                                                                                                                                                                                                                               |     |  |  |  |

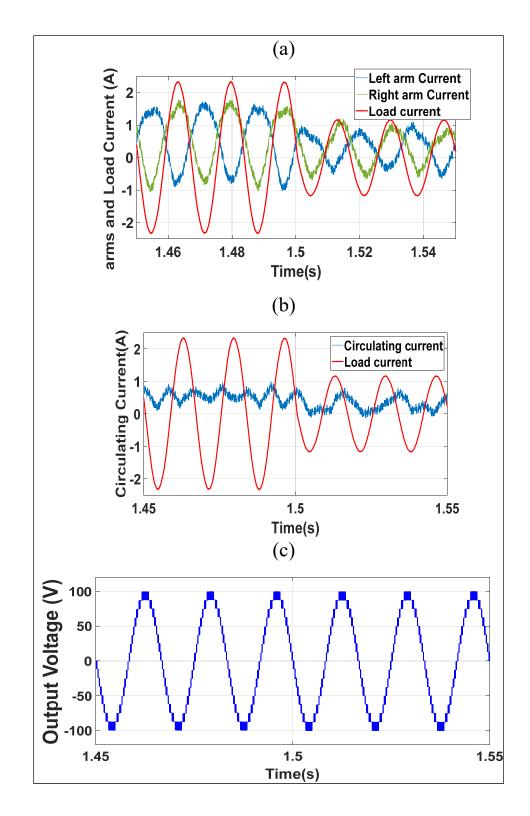

| Figure 4.17 | Dynamic response of Modular Y-PUC converter with 4 modules per arm during the load variation from 40 ohm to 80 ohm a)Arms current and load current b) circulating current c) load voltage                                                                                                                                                                                                                                          |     |  |  |  |

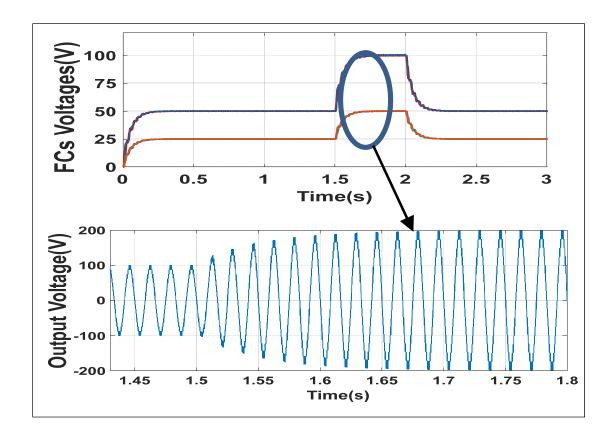

| Figure 4.18 | Dynamic response of Modular Y-PUC converter with 4 modules per arm during the DC voltage variation from 200 V to 400 V and returning to 200 V                                                                                                                                                                                                                                                                                      | 150 |  |  |  |

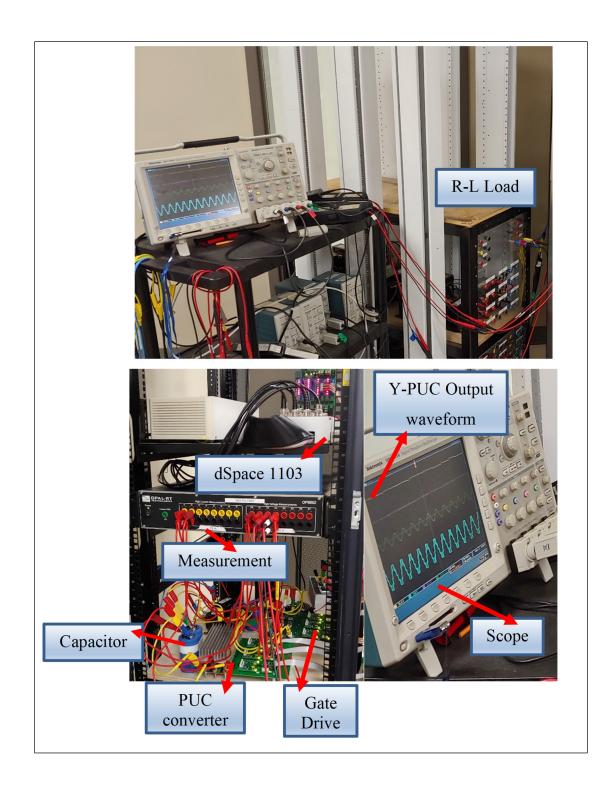

| Figure 4.19 | Laboratory setup of proposed configuration of Y-PUC                                                                                                                                                                                                                                                                                                                                                                                | 151 |  |  |  |

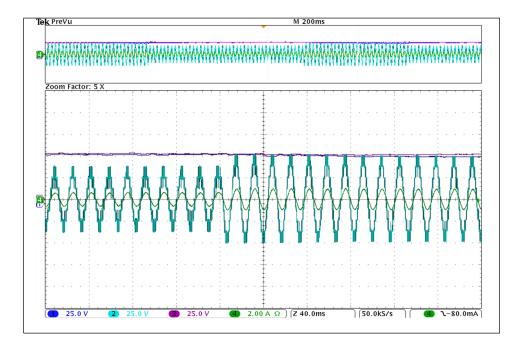

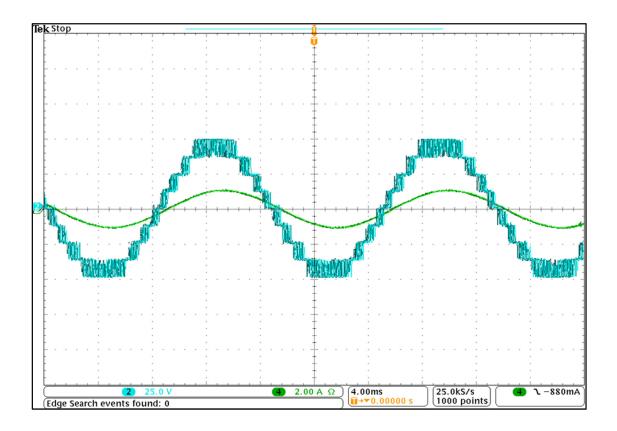

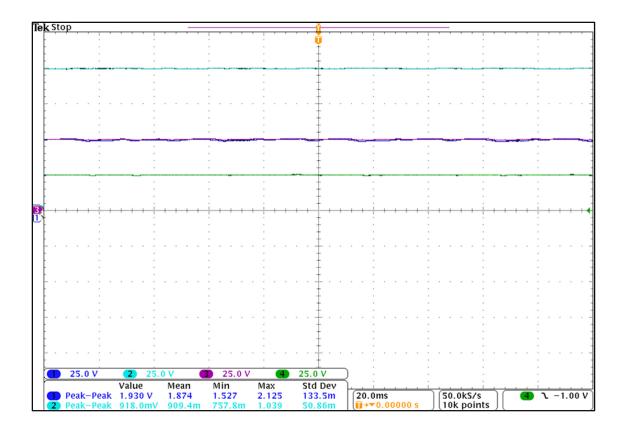

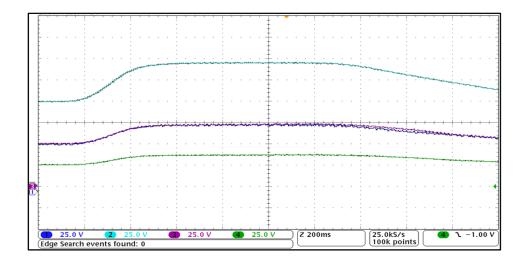

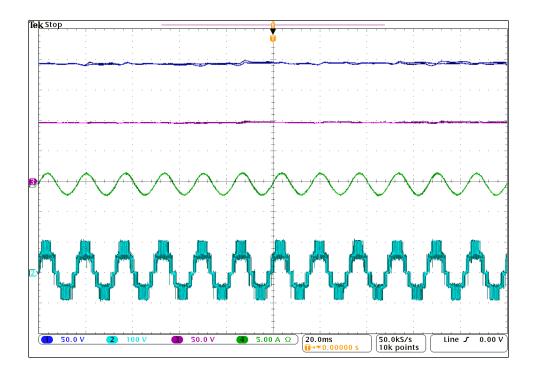

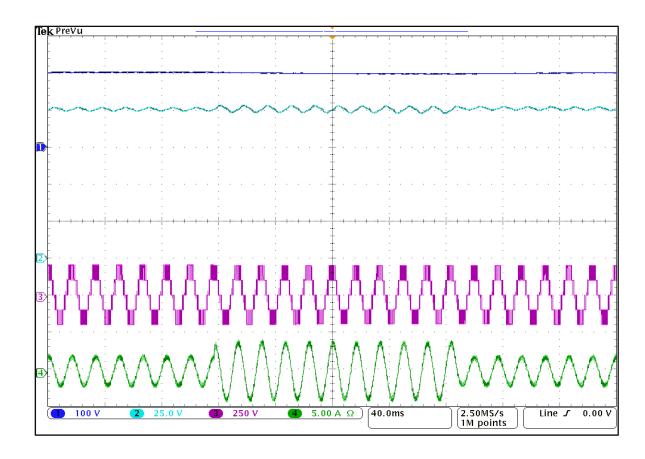

| Figure 4.20 | 5-L voltage (light blue wave, Channel.2), current (Channel.4, green wave), capacitor voltage V <sub>CL1</sub> and V <sub>CR1</sub> (dark blue, Channel.1) and capacitor voltage V <sub>CL2</sub> and V <sub>CR2</sub> (violet DC wave, Channel.3)                                                                                                                                                                                  | 152 |  |  |  |

| Figure 4.21 | Voltage balancing on four 1000µF flying capacitors. Channel 1, dark blue wave,100 V/div is VCL2, Channel 3,violet wave 100V/div is VCL1, Channel 4, dark green wave, 100 V/div is VCR2, Channel 3,blue wave 100V/div is VCR1                                                                                                                                                                                                       | 153 |  |  |  |

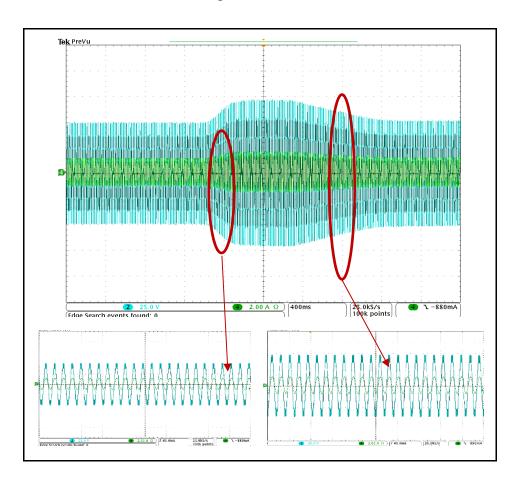

| Figure 4.22 | Voltage balancing on FCs and load voltage adjustment during the DC source variation. Channel 1,dark blue wave, 50 V/div is the V <sub>CL1</sub> voltage in upper capacitor, Channel. 2, blue wave, 50 V/div is the V <sub>X</sub> , voltage across the load in Y-PUC converter, Channel. 3, violet wave, 50 V/div is the DC source voltage, Channel 4, green wave, 50 V/div is the V <sub>CL2</sub> voltage in the upper capacitor | 153 |  |  |  |

| Figure 4.23 | Voltage (light blue wave) and current (green wave) across the load and FCs voltages during the load variation (dark blue wave is the V <sub>CR1</sub> , violet wave is the V <sub>CR2</sub> )154 |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Figure 4.24 | Load voltage, current and capacitor voltages during the modulation index variation from 0.6 to 0.95                                                                                              |  |  |  |

## LIST OF ABBREVIATION

TWh Tera watt-hour

GDP Gross Domestic Product

GW Giga watt

AC Alternative Current

DC Direct Current

PCC Point of Common Coupling

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

IGBT Insulated-Gate Bipolar Transistor

IGCT Integrated Gate Controlled Thyristor

GaN Gallium Nitride

HV High Voltage

MV medium Voltage

THD Total Harmonic Distortion

MLC Multilevel Converter

MMC Modular Multilevel Converter

CHB Cascaded H-Bridge

NPC Neutral Point Clamped

FC Flying Capacitor

PUC5 5 Level Packed U-cell

ZPUC Z-Packed U-cell

ZPUC5 5 Level Z-Packed U-cell

ZPUC-MMC Z-Packed U-cell- Modular Multilevel Converter

# XXIV

Y-PUC Double Star Packed U-Cell

PS-PWM Phase Shift Pulse Width Modulation

LS-PWM Level Shift Pulse Width Modulation

SVM Space vector Modulation

HVDC High Voltage Direct Current

STATCOM Static VAR Compensator

AI Artificial Intelligence

NN Neural Network

### **INTRODUCTION**

Nowadays, by augmenting the number of renewable energy sources, utilizing the power electronic converters is considerably increasing (Carrasco et al., 2006). Based on British Petroleum's statistical review of world energy 2021, the COVID-19 pandemic causes reduce energy consumption at the fastest rate since 1945. Nevertheless, renewable energy sources, especially solar power plants and wind farms, are growing faster than ever. In fact, the power demands declined to 4.4%, 405 TWh in 2020, while the renewable energy generation demonstrate its largest-ever including 173 TWh for wind and 148 TWh for solar energy. This augmentation in renewable energy is the largest ever which has been recorded (British-Petroleum, 2021).

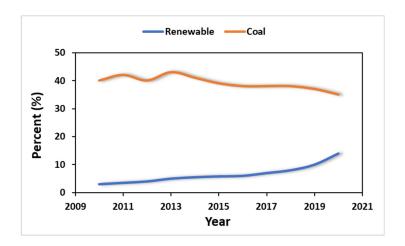

Figure 0.1 demonstrates the share of coal and renewable in global power generation from 2010 to 2020. To illustrate, increased rate of wind and solar energy are depicted separately in figures 0.2 and 0.3.

Figure 0.1 Share of renewables and coal in global power generation

Adapted from British-Petroleum (2021, p. 5)

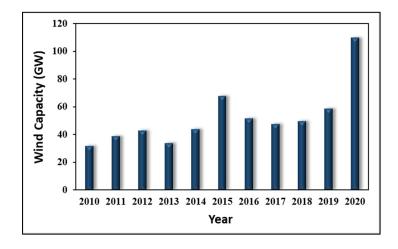

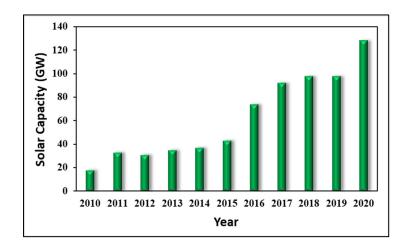

Augmentation of renewable energy generation was 238 GW in 2020 despite the collapse in GDP due to the pandemic that is 50% more than ever before. Between 2015 to 2020, the

capacity of solar and wind have doubled, and the increased capacity was around 800 GW. Thus, through such growth on the renewable energy and distributed generations, providing the

Figure 0.2 Annual change of wind capacity Adapted from British-Petroleum (2021, p. 5)

Figure 0.3 Annual change of solar capacity Adapted from British-Petroleum (2021, p. 5)

suitable technology to integrate them into the electrical grid is inevitable. Power electronic converters are the interface apparatus toward green energy and the world without carbon emission. In past years, switching devices have developed at the fastest rate by progressing in the semiconductor industries. The application of nanotechnology in this industry leads to

produce the new generation of switches in which the frequency, voltage rating and power rating have considerably augmented. Consequently, one of the biggest obstacles to apply the power electronic on high voltage and power was removed. Moreover, emerging of the robust digital controller paved the way of power electronic converters applications to integrate renewable sources into the grid.

In solar plants, two types of converters are utilized including chopper (DC/DC) and inverter (DC/AC) to connect to the principal electrical grid. In wind power plants rectifier (AC/DC) and inverter (DC/AC) are used to regulate the frequency, phase, and voltage amplitude for grid connection at the point of common coupling (PCC). Furthermore, in the high voltage transmission system, power electronic converters are responsible to exchange the frequency between two systems with different power frequencies, or transferring the DC voltage instead of AC to reduce the power losses. High power application of power converters is to drive the motors of compressors, pumps, fans, grinding and rolling mills, conveyors, crushers, and so forth (Kouro et al., 2010).

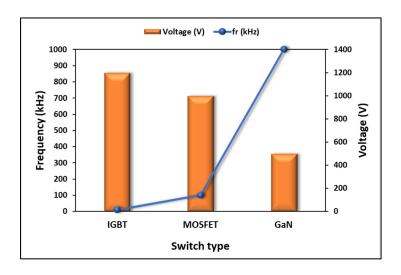

Today, the new generation of semiconductor switches that are almost used to construct the power electronic converters are insulated-gate bipolar transistor (IGBT), metal–oxide–semiconductor field-effect transistor (MOSFET), and Gallium Nitride (GaN). The main drawbacks of thyristor and gate turn-off thyristor (GTO) are the lower switching frequency and efficiency which limits their application on high power applications (K. J. Chen et al., 2017). In contrast, GaNs are the newest switches with the highest proficiency and switching frequency rather than their counterparts. Figure 0.4 illustrates the diagram of voltage in terms of frequency for three types of switches. For high switching frequency, the MOSFETs are not suitable due to their lower efficiency. In other words, when the frequency is increased the rise and fall time of the switches play the roles which are lower in GaN compared to MOSFET and IGBT. On the other hand, voltage blocking in the GaNs is lower than IGBT and MOSFET (Lidow & Reusch, 2015). Thus, appropriate selection of the switches and proper designing of the power converters are the vital process that must be considered.

Figure 0.5 shows the two-level power converter in which the total voltage of the system must be tolerated by each switch (Fang Zheng, Jih-Sheng, McKeever, & VanCoevering, 1996; Flourentzou, Agelidis, & Demetriades, 2009). However, as mentioned above, there are some limitations to choose suitable switching devices. To illustrate, figure 0.4 shows that the maximum voltage blocking for accessible IGBT in the market is around 1200V. Series switches, among which the total voltage could be divided, can be a solution to address this problem; however, the higher dv/dt and THD in the waveform is still trouble that causes to enlarge the printed circuit board (PCB) due to large size of the filters.

Figure 0.4 Semiconductor technologies in terms of frequency and voltage blocking

Figure 0.5 Two-Level Conventional converter

# **Description of the problem**

Application of power converters in medium voltage and high voltage is challenging due to the maximum allowable rating power and blocking voltage of the switching devices. Multilevel converters are the best solution to address this complication. This concept not only divides the voltage among several switches, but also reduces the THD and dV/dt that is not addressed on series switches in conventional two-level converters (Jose Rodriguez, Lai, & Peng, 2002).

The main drawbacks of Multilevel converters (MLCs) are the higher number of DC sources, switches, flying capacitors (FCs) and complications in modulation and control systems compared to the conventional ones. DC sources can be replaced by the FCs in some types of MLCs in which capacitors must be balanced properly with a minimum ripple. Due to that, the FCs occupy a large portion of the PCBs compared to the semiconductor parts, obtaining the lower size of FCs through appropriate and simple voltage balancing methods to achieve the minimum ripple is one of the controversial issues on MLCs.

A large number of isolated DC sources problem on MLCs was resolved by introducing the modular multilevel converters (MMC) which was invented firstly by Prof. R. Marquardt (Lesnicar & Marquardt, 2003). It includes submodules that can be conventional two-level converters (HB-MMC) or Multilevel converters such as 3-L flying capacitors (FC-MMC). HB-MMCs are the most common type of MMCs which require N cells per arm to generate N+1 voltage levels at the output. Besides, to achieve the higher quality of output waveform, the number of submodules in standard type must be increased that causes a higher power loss, lower reliability, higher complexity in voltage balancing, and higher number of components. To devise an optimized topology of MMCs, their application, as well as the standard requirements, must be considered to trade-off between the complexity and power losses (Debnath, Qin, Bahrani, Saeedifard, & Barbosa, 2015).

It should be noted that the unipolar topologies on MMCs cannot disconnect the DC short circuit fault current through the switches and they require the external DC circuit breaker (Callavik, Blomberg, Häfner, & Jacobson, 2012).

On the other hand, modulation strategy on MLCs is another challenging issue due to a large number of switches and different types of switching patterns and redundancy. Phase shift pulse width modulation (PS-PWM), level shift pulse width modulation (LS-PWM), and space vector modulation (SVM) are three well-known modulation strategies that are often used to generate the signals for switching of semiconductors (Saeed Arazm, Hani Vahedi, & Kamal Al-Haddad, 2018). The main advantage of PS-PWM in comparison with LS-PWM and SVM is shifting the harmonic contents to farther than the fundamental frequency. Accordingly, the size and cost of output filters could be reduced while the power quality is improved. PS-PWM is also interesting to apply on MMCs for improving the voltage balancing due to their high switching frequency with the same carrier frequency compared to LS-PWM and SVM (Y. Li, Wang, & Li, 2015). However, the normal type of PS-PWM through the logic gate can not be applied to all types of MLCs. (Bin Wu & Narimani, 2017a)

## **Research Objective**

As mentioned in the problem description, PS-PWM is an advantageous modulation strategy on MLCs. Thus, in this thesis, a generalized algorithm is proposed for designing the PS-PWM based on its analytical model in order to be implemented on all multilevel converters regardless of structure and number of levels.

Moreover, to overcome the problem of isolated DC sources on MLCs, one topology is invented to achieve the higher voltage levels, lower THD and consequently lower filter size through a single DC source for single-phase and three-phase. This topology is the proper alternative for MMC to reach the higher quality waveform with the lower devices. In addition, a deep learning-based voltage balancer integrated with hybrid phase shift and level shift modulation is proposed in this research work to increase the voltage levels in multilevel converters.

Furthermore, A bipolar configuration MMC is proposed in this thesis to be capable to disconnect the DC fault current through the semiconductor switches instead of the DC circuit breaker.

The summary of research objective is as follows:

- Proposing a Multilevel topology for single-phase, three-phase and MMCs applications.

- Developing the voltage balancing technique integrated with the modulation technique to control the FCs on MMCs without requiring the external controller.

- Developing a deep learning voltage balancer integrated with the hybrid modulation technique to increase the voltage levels on MMCs.

- Developing a (Packed U-Cells) PUC converter as a single DC source three-phase multilevel converter and for MMC applications to remove the DC fault circuit breaker.

## Methodology

This research methodology is based on three following steps:

- 1- Theoretical and mathematical analysis.

- 2- Simulation in Sim power system toolbox in Matlab.

- 3- Implementation in an experimental setup in GREPCI LAB.

First, a literature review has been carried out to scrutinize the several types of MLCs and MMCs. Modulation and control techniques are investigated to find their pros and cons. Secondly, mathematical, and theoretical analysis to resolve the problems is carried out. For this research work, the theoretical analysis is performed in three sections including modulation, voltage balancing, and suitable topology for MLCs. Thirdly, simulation and modeling of the novel ideas of topology and modulation are performed by the MATLAB Simulink. Finally, the single-phase pilot experimental set-up of MMCs with the newly proposed topology is constructed in the GREPCI Lab. The control algorithm of voltage balancing integrated with

modulation technique has been implemented on dSpace 1103 as a real-time controller and switching pulses are sent to the switches through the dSpace 1103 interface board.

#### **Thesis Contributions**

The main novelties and contributions of this thesis are as follows:

# 1. Proposing a single DC source topology for single-phase, three-phase and MMC application

In this section that is the main part of this research work, ZPUC topology is proposed as a multilevel electric power converter which has been filed in US patent (Saeed Arazm & Al-Haddad, 2019). This topology is originated from the Flying Capacitor similar to the PUC topology. However, in contrast with the PUC, it requires a single DC source in a three-phase system. Moreover, in MMC application, this is a powerful topology that can be a serious alternative to HB-MMC. HB-MMC is the most popular submodule of MMC which is produced by famous manufacturers such as Siemens, ABB, Alstom, and so forth. However, it requires a large number of semiconductor switches and FCs to generate the same voltage levels compared to ZPUC. Comparison between ZPUC and the other well-known topologies demonstrates its superiority for high power and medium voltage applications. In fact, more voltage level generation with the lower components counts makes ZPUC a converter with more power quality and lower cost.

# 2. Voltage balancing control method integrated with a modulation technique

In fact, to eliminate the external control system for voltage balancing of the FCs which reduces the system reliability and increases the total cost of the converter, the voltage balancing integrated with PS and LS-PWM is proposed in this research. Although some topologies like the PUC5 could be operated in sensor-less mode, these converters are not economically feasible due that it causes to the increase in the size of the FCs. Thus, voltage balancing

integrated with the modulation technique is one solution to reduce the size of the FCs without using external control systems.

# 3. development of voltage balancing on ZPUC-MMC by Deep learning integrated with hybrid modulation to increase the voltage levels

HB-MMCs with N submodules per arm which are largely used in the industries, generate N+1 voltage levels across the load in their output terminals. Although the voltage levels on high voltage applications such as HVDC is as much as high so that its THD is sufficiently low, in medium voltage application, where N is low, generating more voltage levels is advantageous to have a lower THD and consequently to reduce the filter size. In fact, in the usual method of modulation and voltage balancing for HB-MMC, FC-MMC, and ZPUC-MMC, the output voltage is N+1, 2N+1, and 4N+1. To increase the voltage levels on ZPUC-MMC, one method based on the artificial network is presented in this research. A deep learning-based voltage balancer integrated with hybrid LS and PS-PWM is proposed to generate 8N+1 voltage levels with the counts of the same component.

# 4. Development of PUC as a single DC source modular three-phase PUC

PUC is a Multilevel converter topology that is well-known for its lower components counts. The 5-level waveform is generated by only 6 switches and one FC supplied by a single DC source. However, for the three-phase system, three isolated DC source is required which is not feasible. Thus, to cope with this challenge, one configuration of PUC is proposed in this research work which not only requires a single DC source for three-phase PUC but also, it is a modular multilevel converter which is called Y-PUC (Saeed Arazm & Kamal Al-Haddad, 2020). This configuration can also be called PUC-MMC. Since PUC is a bipolar converter, the output voltage levels of this configuration are less than ZPUC-MMC. Nevertheless, the semiconductor in this configuration can be used to disconnect the DC fault current without using the external DC circuit breaker. The bipolar full-bridge MMC can be replaced by this topology due to the lower size and cost, and power losses. It is also shown in this section that the components count of PUC-MMC is lower than HB-MMC.

### **Thesis Outline**

The structure of this thesis is organized as follows:

Chapter 1 reviews the state of the arts of the multilevel converters and MMCs as well as the modulation methods. The topologies and waveforms of the famous and new converters are reviewed, and their challenges are explained. In Chapter 2, ZPUC multilevel converter topology is proposed and generalized ZPUC topology is developed. Moreover, modeling, control, and voltage balancing, switching states, circulating current, reliability, and power losses are completely explained on ZPUC-MMC. Increased voltage levels ZPUC-MMC through deep learning-based voltage balancing integrated with hybrid PS-PWM and LS-PWM modulation is described in chapter 3. Chapter 4 introduces a complete approach to a single DC source modular three-phase PUC converter. Moreover, challenges of PUC-MMCs including circulating current are discussed in this chapter. Finally, the conclusion of this thesis is discussed and some related ideas according to the author's opinion for future studies are listed.

### **CHAPTER 1**

# LITERATURE RIVIEW ON MULTILEVEL AND MODULAR MULTILEVEL CONVERTERS

#### 1.1 Introduction

Multilevel converter (MLC) is firstly introduced in 1975 by Baker in which multilevel waveform is generated at the output of the converter instead of the two-level waveform (R. H. Baker & Bannister, 1975). This topology that is called cascaded H-bridge (CHB), requires a large number of isolated DC sources to generate more voltage levels. The same authors introduce a topology to generate 3-Level and 5-Level with a single DC sources due to the fact that isolated DC sources are very bulky, heavy, and costly (R. Baker, 1980). This topology which is called Neutral point diode clamped was later developed by Nabae (Nabae, Takahashi, & Akagi, 1981). Then in 1992, the multilevel technology based on flying capacitor was invented which is the basic concept of a large number of novel MLCs topologies which are recently designed (Lavieville, Carrere, & Meynard, 1997),(T. Meynard & H. Foch, 1992),(Bin Wu & Narimani, 2017a).

MLCs have become more popular due to the following reasons: lower stress on power switches because of lower dv/dt, lower total harmonic distortion which leads to the lower filter size and better electromagnetic interference, the lower common-mode voltage which is better for motor drive application, switching redundancy that facilitates the voltage balancing and fault tolerance, output current with smaller THD compared to the two-level converter, lower switching frequency and lower switching losses, and combination of MLCs with the renewable energies such as wind and solar plants.(Gupta, Ranjan, Bhatnagar, Sahu, & Jain, 2016)

Since the MLCs require a great number of semiconductor devices, designing the reduced device counts MLC is always unavoidable. Hybrid topologies which are often comprised of two or more classical multilevel converters are one of the common ways to reduce the

components counts (Abarzadeh & Al-Haddad, 2019). In fact, the most important criteria to evaluate the MLCs are as following: 1. The number of semiconductor devices, 2. The total blocking voltage of the converter, 3. Controllability and simplicity of the converter to balance the voltages or sensor-less balancing. However, the application of the converters is the most important factor to define the competency of the MLC topology.

Modular multilevel converter (MMC) was firstly proposed by Prof. Marquardt that was implemented on half-bridge (HB-MMC) converter aiming to employ the multilevel converters in high voltage DC (HVDC) system. Voltage levels, modularity and scalability, simplicity in repair and maintenance, high efficiency, low switching frequency, small switching losses, THD reduction, and small size of the filters are the main advantages of this type of multilevel converters (Abarzadeh & Al-Haddad, 2019; Amarir & Al-Haddad, 2008; Javadi & Al-Haddad, 2015; Lesnicar & Marquardt, 2003). PI controllers have been used in HB-MMC to balance the FC voltages and to suppress the circulating current (Hagiwara & Akagi, 2009).

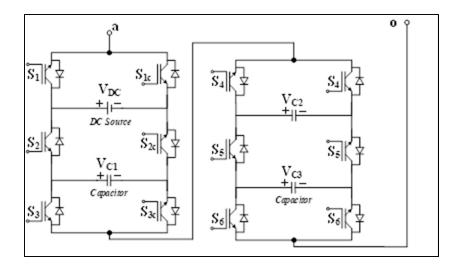

Although a large number of MLCs have been introduced in research work, a few of them can be employed as a submodule on MMCs. A three-level flying capacitor multilevel converter (FC-MLC) is a multilevel topology that is placed as a submodule of MMC with the purpose of increasing the voltage levels and improving the performance of MMCs (A. Dekka, Wu, Zargari, & Fuentes, 2016). In (Solas et al., 2013a, 2013b) authors replaced two-level half-bridge (HB), 3-level NPC, and FC as the submodules in MMC configuration. This research shows that the NPC is not a proper topology for MMC submodules due to unbalance in flying capacitors voltages. Moreover, although the capacitors are acceptably balanced in three-level FC-MMC, it does not have a considerable advantage rather than the HB-MMC due that the number of switching devices and capacitors are identical to generate the given voltage levels. However, the rated voltage blocking and the size of half of the flying capacitors and switches of 3L FC-MMC are twice those for HB and the rests have the same size. 3L FC-MMCs and their all issues have been discussed in (Du, Wu, & Zargari, 2017; Du, Wu, Zargari, & Cheng, 2017). Despite the mentioned disadvantages of 3L FC-MMC compared to HB-MMC, the authors (Du, Wu, & Zargari, 2018) verifies that this configuration of MMC is advantageous

for motor drives application due to deal with the issues of low-speed operation evaluated against the HB-MMC.

The Cross-connected submodule is introduced by authors in (Nami, Wang, Dijkhuizen, & Shukla, 2013) that uses two cells of half-bridge which have been connected in crossway for dc fault breaking current. This topology can be used as a submodule of MMCs individually or in a hybrid with half-bridge cells. Thus, proposing a suitable topology of MLCs to be replaced by the submodules of MMCs in order to reduce the components counts, power losses, and increasing the reliability for given voltage levels would be a great contribution. In the next sections, several well-known topologies as well as the recently introduced topologies, are discussed to draw out the highlights and challenges.

#### 1.2 Conventional 2-Level converters

The basic topology of conventional converters is shown in Figure 1.1. This configuration is called a full bridge or H-bridge, because of the apparent arrangement. Switches of each arm operate in a complementary manner. Thus, the voltage across the load varies between  $-V_{dc}$  and  $+V_{dc}$ . Two voltage levels generate the high content of THD at the output of the inverter so that the large size of the filters must be utilized to reduce the filter size. In addition, voltage and power permissible rates of switches are another issue for high voltage and high-power applications. This is a reason why the series switches are utilized in this figure to divide the voltage among the switches. However, higher THD, the number of elements and, power losses are the problems that lead the researcher and manufacturer to use the multilevel converters.

### 1.3 Multilevel converters topologies

#### 1.3.1 Cascaded H-Bridge

Cascaded H-Bridge (CHB) is obtained by cascading the conventional 2-L voltage source

Figure 1.1 Conventional 2-L converter with series switches

converters. Consequently, a multilevel waveform can be achieved to alleviate the voltage stress on devices. A three-phase CHB with three cascaded H-bridge is depicted in Figure 1.2 in which a 7-L single-phase waveform is generated at the output. The output voltage is equal to the sum of the voltages of each cell. For example, in this figure,  $V_{aN}=V_{H1}+V_{H2}+V_{H3}$ . Figure 1.3 shows the 7-level waveforms of the inverter to clarify the pulse technique in CHB. It should be noted that the DC source voltage at CHB could be either equal or unequal. The number of single-phase voltage levels for equal type is given by:

$$L_{Phase} = 2N + 1 \tag{1.1}$$

Where, L implies the number of voltage levels for N cells of H-Bridge for a single-phase system. Generally, the voltage level in line voltage is obtained by the following equation:

$$L_{Line} = 2L_{Phase} - 1 \tag{1.2}$$

Where, L<sub>Phase</sub> and L<sub>Line</sub> are the level number of phase and line voltage waveform, respectively. Moreover, the switching states and their corresponding redundancy are listed in Table 1.1 for CHB with two cells. It can be seen from this table that 16 switching states generate five voltage levels for single-phase including +2E, +E, 0, -E, -2E when the DC source voltage is equal to E. Although the equal DC source is worthwhile due that all the devices require the same rated

voltage, the plenty of the redundant states cause to use more devices for given voltage levels. In unequal DC source CHB, if  $V_{DC1}=2V_{DC2}$ , then 7-L and when  $V_{DC1}=3V_{DC2}$ , then 9-L is generated across the load. It is evident that, the redundancy in 9-L may not be sufficient for some purposes such as fault tolerant and voltage balancing modes.

Table 1.1 Switching States of 5L CHB With Equal DC Source

| State | S11 | S31 | S12 | S32 | Output Voltage |

|-------|-----|-----|-----|-----|----------------|

| 1     | 1   | 0   | 1   | 0   | 2E             |

| 2     | 1   | 0   | 1   | 1   | E              |

| 3     | 1   | 0   | 0   | 0   | Е              |

| 4     | 1   | 1   | 1   | 0   | Е              |

| 5     | 0   | 0   | 1   | 0   | Е              |

| 6     | 0   | 0   | 1   | 1   | 0              |

| 7     | 0   | 0   | 0   | 0   | 0              |

| 8     | 1   | 1   | 1   | 1   | 0              |

| 9     | 1   | 1   | 0   | 0   | 0              |

| 10    | 1   | 0   | 0   | 1   | 0              |

| 11    | 0   | 1   | 1   | 0   | 0              |

| 12    | 0   | 1   | 0   | 0   | -E             |

| 13    | 0   | 1   | 1   | 1   | -E             |

| 14    | 0   | 0   | 0   | 1   | -E             |

| 15    | 1   | 1   | 0   | 1   | -E             |

| 16    | 0   | 1   | 1   | 1   | -2E            |

Figure 1.2 Three-phase cascaded H-Bridge with 7-L phase-voltage

Figure 1.3 7L waveforms in CHB with three cells

# 1.3.2 Neutral Point Clamped (NPC) and its family topologies

NPC topology is a multilevel converter that produces even and odd voltage levels in contrast to the CHB that is only capable to produce the odd levels. Four and five-level NPCs are not usually used by the industry due to the high number of components and voltage balancing issues. In other words, NPCs are most popular as a three-level multilevel inverter.

Figure 1.4 shows a three-phase, three-level NPC inverter that could be used instead of conventional two-level VSI. Figure 1.5 illustrates a 3-level single-phase voltage waveform as well as the current wave at the output of NPC.

Figure 1.6 depicts a 5-Level NPC with 8 switches and 6 unequal rated voltage diodes or 12 equal rated voltage diodes which it is not interested in the industry. 5-L NPC output 5-Level voltage waveform as well as the output current is depicted in Figure 1.7.

In addition, 5L HNPC multi-level inverter has been also proposed based on equation 1.2 to generate more voltage levels with lower components counts compared to 5L NPC. Figure 1.8 shows a three-phase 5L HNPC in which the letter H is chosen due to its similarity by the full-bridge converters (Cheng & Wu, 2007).

Figure 1.4 Three-phase three-level NPC

Figure 1.5 Load current and phase voltage across the output terminals in 3L NPC

Figure 1.6 Single-phase 5L NPC

Figure 1.7 Load current and voltage at the output of 5L NPC

Figure 1.8 Three-phase HNPC to generate 5-level waveform Taken from Cheng & Wu (2007)

Another configuration which is extracted from HNPC is called Active NPC or ANPC which is a patent of ABB Company. Since the voltage stresses of switches are not equal in NPC, the power losses are distributed unevenly which causes the design of the special consideration for a cooling system. ANPC is invented to address this problem so that the IGBTs are substituted by diodes at NPC. Accordingly, it leads to the distribution of uniform losses among switches. This topology is shown in figure 1.9 (Bruckner, Bernet, & Guldner, 2005).

Figure 1.9 Three level ANPC topology Taken from Bruckner, Bernet, & Guldner (2005)

In flying capacitor multilevel topology, the clamped diode in NPC is replaced by the flying capacitors. It is derived from a two-level inverter that every two switches are supplied by a capacitor. Since a large number of flying capacitors are used in FC, it accordingly requires plenty of isolators for DC capacitors and a complex voltage balancing control which complicates its industrial applications. Figure 1.10.a. shows a three-phase three-level FC topology in which a bipolar waveform including the voltages +Vdc, 0, and -Vdc are produced in V<sub>aN1</sub>. However, through replacing the null point N1 with point N2, unipolar waveforms with the levels 0, Vdc, 2Vdc are generated at V<sub>aN2</sub>. In addition, a 5L single-phase FC topology is depicted in Figure 1.10.b in which the flying capacitors must tolerate the voltages 3Vdc/2, Vdc/2, and Vdc/4 and consequently, all the switches have to suffer Vdc/4. The capacitors with different rated voltages can also be replaced by the series capacitors with identical nominal voltages. Apart from these well-known topologies, considerable amounts of MLCs are introduced in recent years so as to achieve higher performance and quality with lower cost.

Figure 1.10 Flying capacitor multilevel topology a) three-level three-phase FC b) 5L single-phase FC

In (Gupta et al., 2016) the authors review the MLCs with reduced component counts. Authors in (Poorfakhraei, Narimani, & Emadi, 2021) review the topologies which are used in electrical

vehicles. In (Salem, Khang, Robbersmyr, Norambuena, & Rodriguez, 2021), the authors investigate some topologies of hybrid MLCs to reduce the counts of the component. Some of the interesting topologies which lead to reducing the counts of the devices are investigated in the following subsections.

# 1.3.3 Hybrid T-type NPC and FC H-bridge:

In this topology, one T-type NPC is connected to FCHB in which a 9L waveform is generated through the connection of two low-frequency switches to the DC source. In this topology, the FC voltages are balanced naturally through the PWM strategy.

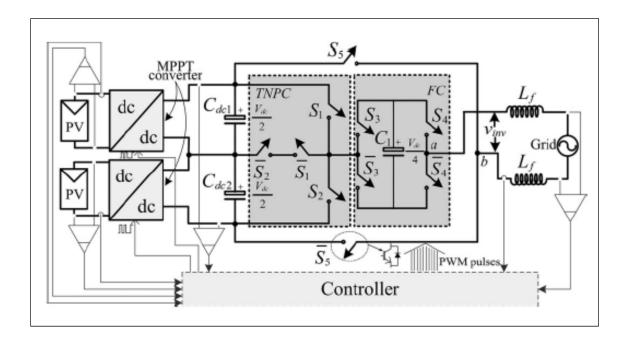

Figure 1.11 shows this topology and its application in PV connection to the grid (Sandeep & Yaragatti, 2017).

Figure 1.11 Hybrid multilevel converter to generate 9L waveform Taken from Sandeep & Yaragatti (2017)

# **1.3.4** Topologies T-Type based structure:

The T-type structure is depicted in Figure 1.12.a in which two switching devices are replaced by two diodes in NPC topology; however, there is a slight difference in their structures. It is firstly invented by authors (Guennegues, Gollentz, Meibody-Tabar, Rael, & Leclere, 2009) which represent a valuable 3L converter compared to NPC due that the blocking voltage of the semiconductor devices is half of the NPC. Moreover, in Figure 1.12.b an H-bridge T-type is illustrated in which not only the voltage levels are increased to 5L, but also the power losses are reduced due that the middle switches operate in system frequency. In (Bahrami & Narimani, 2019) authors present one 5L T-Type Nested Neutral Point Clamped (T-NNPC) Converter. T-NNPC is illustrated in figure 1.12.c in which V<sub>C1</sub> and V<sub>C2</sub> must be one-quarter of the DC source to generate five voltage levels.

Figure 1.12 T-type based multilevel converter topologies a) T-type 3L Converter b) H-Bridge T-type 5L c) T-NNPC 5L Converter

## 1.3.5 Packed U-Cell (PUC) topology and switching states