# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# THÈSE PRÉSENTÉE À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DU DOCTORAT EN GÉNIE ÉLECTRIQUE Ph. D.

> PAR René GAGNÉ

JADIS SYNCHRONES, DÉSORMAIS GALS, LES ARCHITECTURES DE FPGA

MONTRÉAL, LE 14 DÉCEMBRE 2009

© René Gagné, 2009

#### PRÉSENTATION DU JURY

# CETTE THÈSE A ÉTÉ ÉVALUÉE PAR UN JURY COMPOSÉ DE

M. Jean P. Belzile, directeur de thèse Département de génie électrique à l'École de technologie supérieure

M. Claude Thibeault, codirecteur de thèse Département de génie électrique à l'École de technologie supérieure

M. Stéphane Coulombe, président du jury Département de génie logiciel et des TI à l'École de technologie supérieure

M. Ghyslain Gagnon, membre du jury Département de génie électrique à l'École de technologie supérieure

M. Pierre Langlois, examinateur externe Département de génie informatique et génie logiciel à l'École Polytechnique de Montréal

# ELLE A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC 8 DÉCEMBRE 2009

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### REMERCIEMENTS

Avant de commencer, je tiens à remercier mon directeur de recherche, Dr Jean P. Belzile, pour son audace à aborder le thème de l'asynchronisme, ses judicieux conseils et sa facilité à transmettre son savoir. C'est sa passion, transmise au fil des années, qui m'a amené à présenter mes résultats de recherche lors de différents événements internationaux. Des activités, pour lesquelles, j'ai également pu bénéficier des talents de rédaction et du support de mon codirecteur de recherche, Dr Claude Thibeault.

Un travail d'une telle ampleur n'aurait jamais vu le jour sans un support financier et matériel adéquat. À cet effet, je tiens à exprimer ma gratitude, en ordre d'importance de contribution, au Conseil de recherches en sciences naturelles et en génie du Canada (CRSNG), au Fonds québécois de la recherche sur la nature et les technologies (FQNRT), à l'École de technologie supérieure (ETS) et à Bell Canada pour leurs contributions financières. Du point de vue matériel, toute ma reconnaissance va à la Société Canadienne de Microsystèmes (CMC Microsystems) pour les différents outils de simulation et de conception mis à ma disposition et au LACIME pour m'avoir fourni un environnement de travail.

Malgré la présence du mentorat et des ressources, ce travail n'aurait jamais été effectué sans le support et l'amour de ma famille ainsi qu'à l'appui indéfectible, aux perpétuels encouragements, à la patience et à la confiance, de ma muse, Eugénie chérie, tout au long de cette aventure, pour le moins, tortueuse.

Merci!

# JADIS SYNCHRONES, DÉSORMAIS GALS, LES ARCHITECTURES DE FPGA

## René GAGNÉ

## RÉSUMÉ

Il est de plus en plus difficile de répondre à la demande conflictuelle de circuits plus grands et plus rapides par les avancées seules des technologies des semi-conducteurs. À un certain point, on s'attend à ce que les concepteurs et les fabricants doivent abandonner la méthodologie de conception synchrone traditionnelle pour une méthodologie localement synchrone globalement asynchrone (GALS). De tels changements engendrent plus de contraintes de synchronisation, mais également plus de flexibilité.

En conséquence, une méthodologie pour l'implémentation de composants GALS sur FPGA synchrones traditionnels est d'abord présentée. Les objectifs sont de définir un ensemble minimal de composants asynchrones de base, de permettre leur implémentation et d'établir les contraintes et les limitations de tels circuits. Les résultats de simulation confirment que des conceptions GALS implémentées à l'aide de ressources du FPGA (tableau de correspondance et bascules) et des outils courants de placement et routage permettent l'implémentation de composants asynchrones tels que la ligne à retard, l'élément C de Muller et l'arbitre. Ces composants peuvent être implémentés dans des FPGA synchrones traditionnels tant que ces conceptions sont soumises à des contraintes appropriées et qu'elles sont utilisées en fonction des limitations du circuit.

Pour atteindre de meilleures performances, une nouvelle architecture de FPGA compatible avec les dispositifs synchrones existants et qui soutient intrinsèquement les conceptions GALS est présentée. L'objectif principal est simple : l'architecture proposée doit apparaître inchangée pour les conceptions synchrones, mais doit inclure un ensemble minimal de composants de base pour empêcher la métastabilité lors de communications asynchrones. Les résultats de simulation, d'un générateur d'horloge qui peut être arrêté, sont présentés. Tous ces résultats démontrent qu'avec très peu de circuits adaptés, une cellule standard de FPGA peut devenir appropriée pour les méthodologies GALS.

Un circuit de masquage des aléas temporels est finalement présenté pour masquer la métastabilité et les problèmes de synchronisation. Le but est de définir un circuit capable de mettre, physiquement, en application les contraintes qui masquent les sources de métastabilité de façon à ce que la synchronisation paraisse transparente. Les résultats de simulation confirment qu'un tel circuit peut masquer totalement toutes les sources de métastabilité sans dégradation des performances, mais avec une latence apparentée au temps nécessaire à la stabilisation d'une bascule de mémoire.

Mots clés: FPGA GALS, composants, architecture, masquage d'aléas temporels.

## FROM SYNCHRONOUS TO GALS, THE ARCHITECTURE OF FPGA

## René GAGNÉ

#### **ABSTRACT**

The conflictual demand of faster and larger designs is increasingly difficult to answer by the advances of solid state technology alone. At some point, it is expected that designers and manufacturers will have to give up the traditional synchronous design methodology for a Globally Asynchronous Locally Synchronous (GALS) one. Such changes imply more synchronization constraints, but also more flexibility.

Consequently, a methodology for implementing GALS design in conventional FPGAs using existing tools is first presented. The goals are to define the minimal set of basic asynchronous components, to permit the methodology of their implementation and to establish the design constraints and limitations of such circuits. Simulation results confirm that GALS designs implemented using the Look-Up Table or the Flip-Flop with Place & Route tools and asynchronous components such as the delay element, the Muller-C element or the arbiter are supported by conventional synchronous FPGAs as long as these designs are implemented within suitable constraints and operated within well defined circuit limitations.

To achieve better performances, a novel FPGA architecture that is compatible with existing devices and that can support GALS designs natively is presented. The main objective is simple: the proposed architecture must appear unchanged for synchronous design, but also includes a minimal amount of basic components to prevent metastability for efficient asynchronous communications. A pausible clock generator application and simulation results for the proposed architecture is presented. All results demonstrate that with a few additional customized circuits, a standard FPGA cell can become appropriate for GALS methodologies.

A glitch masking circuitry is finally presented to mask completely metastability and avoid synchronisation problems. The aim is to define a circuit able to implement physically the constraints that mask metastability sources and that appear transparent during synchronization. Simulation results confirm that such a circuit can totally mask metastability sources with no performances degradations, introducing only a latency equivalent to the setup time of a typical flip flop.

Keywords: GALS FPGA, components, architecture, glitch masking.

# TABLE DES MATIÈRES

|               |                                      |                                                                  | Page |  |  |

|---------------|--------------------------------------|------------------------------------------------------------------|------|--|--|

| INTRODUCTION1 |                                      |                                                                  |      |  |  |

| OII I I       | NED E 4                              |                                                                  |      |  |  |

|               | CHAPITRE 1 Revue de la littérature10 |                                                                  |      |  |  |

| 1.1           | <b>-</b> .                           | synchrone                                                        |      |  |  |

|               | 1.1.1                                | Synchronisation                                                  |      |  |  |

|               | 1.1.2                                | Approche traditionnelle de conception                            |      |  |  |

|               | 1.1.3                                | Approche moderne de conception                                   |      |  |  |

| 1.2           |                                      | asynchrone                                                       |      |  |  |

|               | 1.2.1                                | Forces de la logique asynchrone                                  |      |  |  |

|               | 1.2.2                                | Faiblesses de la logique asynchrone                              |      |  |  |

|               | 1.2.3                                | Protocole de communication                                       |      |  |  |

|               | 1.2.4                                | Encodage des données                                             | 21   |  |  |

|               | 1.2.5                                | Modèle de circuits asynchrones                                   |      |  |  |

|               | 1.2.6                                | Étude de cas                                                     | 26   |  |  |

| 1.3           | GALS                                 |                                                                  | 28   |  |  |

|               | 1.3.1                                | File de mémoire FIFO                                             | 29   |  |  |

|               | 1.3.2                                | Micro-pipeline                                                   | 30   |  |  |

|               | 1.3.3                                | Générateur d'horloge                                             | 30   |  |  |

| 1.4           | Discussi                             | on                                                               | 34   |  |  |

| CHAI          | PITRE 2                              | Máthadalacia d'implémentation de composante CALS sur EDCA        | 25   |  |  |

| 2.1           |                                      | Méthodologie d'implémentation de composants GALS sur FPGA        |      |  |  |

|               |                                      | GALS pour FPGA synchrone                                         |      |  |  |

| 2.2           |                                      |                                                                  |      |  |  |

|               | 2.2.1                                | Lacunes de synchronisation                                       |      |  |  |

|               | 2.2.2                                | Particularité des conceptions GALSArchitecture du FPGA Virtex-II |      |  |  |

|               | 2.2.3                                |                                                                  |      |  |  |

|               | 2.2.4                                | Indexation des ressources                                        |      |  |  |

|               | 2.2.5                                | Routage des composantes                                          |      |  |  |

|               | 2.2.6                                | Consignes pour les FPGA                                          |      |  |  |

| 2.3           | _                                    | ants de base                                                     | 48   |  |  |

|               | 2.3.1                                | Implémentation d'une ligne à retard                              |      |  |  |

|               | 2.3.2                                | Implémentation d'un élément C de Muller                          |      |  |  |

|               | 2.3.3                                | Implémentation d'un arbitre                                      |      |  |  |

| 2.4           |                                      | eur d'horloge d'un port de communication GALS unidirectionnel    |      |  |  |

| 2.5           | Conclusi                             | on et direction du prochain chapitre                             | 63   |  |  |

| СНАР          | PITRE 3                              | Architecture nativement GALS pour FPGA                           | 64   |  |  |

| 3.1           |                                      | tion                                                             |      |  |  |

| 3.2           |                                      | État de l'art                                                    |      |  |  |

| 3.3           |                                      | Requis pour une architecture GALS                                |      |  |  |

| 3.4           | Architecture proposée                |                                                                  |      |  |  |

| J. T          | Attended to propose                  |                                                                  |      |  |  |

| 3.5        | Analyse o   | des contraintes de synchronisation                             | 73    |

|------------|-------------|----------------------------------------------------------------|-------|

|            | 3 5 1       | Analyse de l'élément C de Muller                               | 75    |

|            | 3.5.2       | Analyse de l'élément mutuellement exclusif                     | 76    |

| 3.6        | Méthodo     | logie de simulation                                            | 81    |

| 2.0        | 3.6.1       | Extraction des retards                                         | 82    |

|            | 3.6.2       | Simulation logique après placement et routage                  | 83    |

|            | 3.6.3       | Simulation généraliste de circuits électroniques analogiques   | 87    |

| 3.7        | Générate    | ur d'horloge d'un port de communication GALS bidirectionnel    | 89    |

|            | 3.7.1       | Fonctionnement du générateur d'horloge                         | 90    |

|            | 3.7.2       | Modèle de simulation du générateur d'horloge                   | 91    |

| 3.8        |             | on                                                             | 93    |

|            | 3.8.1       | Performances                                                   |       |

|            | 3.8.2       | Impacts de variation des paramètres de fabrication             | 94    |

|            | 3.8.3       | Limitations                                                    | 95    |

|            | 3.8.4       | Évaluation de la surface et du nombre de transistors           | 95    |

| 3.9        |             | ons et travaux futurs                                          |       |

| 0.5        |             |                                                                |       |

| CHAP       | ITRE 4      | Masquage des aléas temporels                                   | 97    |

| 4.1        | Introduct   | tion                                                           | 97    |

| 4.2        | Revue de    | e littérature                                                  | 100   |

| 4.3        | Analyse     | des requis                                                     | 106   |

| 4.4        | Solution    | proposée                                                       | 107   |

|            | 4.4.1       | Éléments de conception                                         | . 108 |

|            | 4.4.2       | Circuit proposé                                                | . 114 |

| 4.5        | Discussion1 |                                                                | 119   |

|            | 4.5.1       | Impacts des variations de fabrication                          | . 120 |

|            | 4.5.2       | Estimation de la surface et du nombre de transistors           | . 121 |

|            | 4.5.3       | Limitations                                                    | . 122 |

| 4.6        | Conclusi    | on                                                             | 123   |

|            |             |                                                                |       |

| CONC       | CLUSION     |                                                                | 125   |

|            |             |                                                                | 120   |

| ANNE       | EXE I       | Conditions de simulation SPICE                                 | 128   |

|            | 37E II      | M/d - data is de simulation CDICE                              | 120   |

| ANNE       | EXEII       | Méthodologie de simulation SPICE                               | 129   |

| ANNEXE III |             | Résultat de l'extraction SPICE des retards                     | 130   |

| ANINIT     | EVE IV      | Modèle SPICE du circuit proposé de masquage d'aléas temporels  | 132   |

| ANNE       | EXE IV      | Modele St 1013 du chedit propose de masquage d'aleas temporeis | 192   |

| ANNEXE V   |             | Outil automatisé de segmentation asynchrone sur FPGA synchrone | 136   |

| LISTE      | E DE RÉF    | ÉRENCES BIBLIOGRAPHIQUES                                       | 143   |

# LISTE DES TABLEAUX

|             | Page                                                                                 |

|-------------|--------------------------------------------------------------------------------------|

| Tableau 2.1 | Contraintes du Virtex-II                                                             |

| Tableau 2.2 | Résumé des paramètres d'implémentation63                                             |

| Tableau 3.1 | Résumé des paramètres de vérification d'EME77                                        |

| Tableau 3.2 | Ordonnancement des cas selon l'axe $t_B \uparrow -t_A \uparrow$                      |

| Tableau 3.3 | Contraintes de conceptions pour le cas C1379                                         |

| Tableau 3.4 | Contraintes de conceptions pour les cas C5-C6-C2, C4 et C379                         |

| Tableau 3.5 | Résumé des PP&RS87                                                                   |

| Tableau 4.1 | Caractéristiques nécessaires pour le masquage d'aléas temporels106                   |

| Tableau 4.2 | Résumé des circuits de l'état de l'art                                               |

| Tableau 4.3 | Temps d'opération du circuit proposé pour une fabrication TT117                      |

| Tableau 4.4 | Temps d'opération du circuit proposé pour les limites de fabrication120              |

| Tableau 4.5 | Temps d'opération en fonction de la température du circuit proposé de fabrication TT |

## LISTE DES FIGURES

|             |                                                                     | Page |

|-------------|---------------------------------------------------------------------|------|

| Figure 1.1  | Pipeline synchrone                                                  | 11   |

| Figure 1.2  | Circuit combinatoire.                                               | 11   |

| Figure 1.3  | Exemple de communication du type poignée de main                    | 15   |

| Figure 1.4  | Protocole de communication à 2 phases.                              | 19   |

| Figure 1.5  | Protocole de communication à 4 phases.                              | 20   |

| Figure 1.6  | Classification des circuits.                                        | 23   |

| Figure 1.7  | Équivalence des modèles temporels SI et QDI.                        | 24   |

| Figure 1.8  | Micro-pipeline.                                                     | 25   |

| Figure 2.1  | Zone critique pour la synchronisation.                              | 37   |

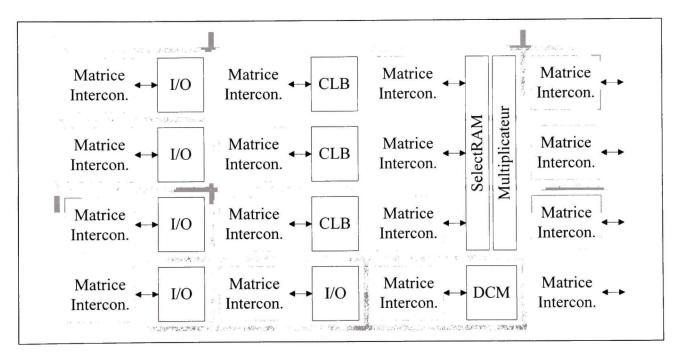

| Figure 2.2  | Vue simplifiée d'une tranche du Virtex-II XC2V4.                    | 39   |

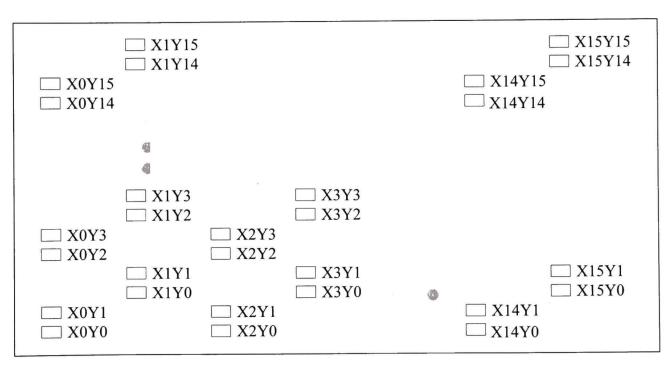

| Figure 2.3  | Disposition générale des tranches du Virtex-II XC2V4                | 41   |

| Figure 2.4  | Coin inférieur gauche de la matrice de routage du Virtex-II XC2V4   | 42   |

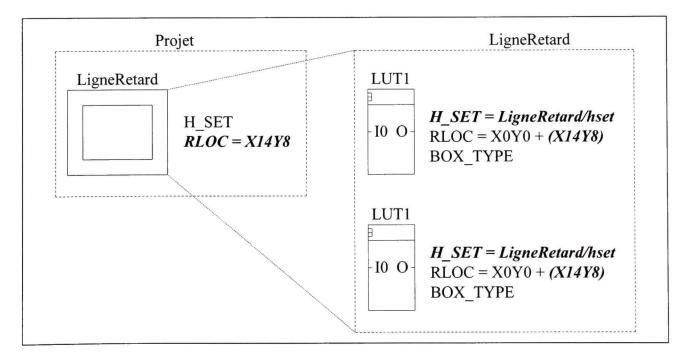

| Figure 2.5  | Contraintes d'une ligne à retard                                    | 50   |

| Figure 2.6  | Code VHDL d'une ligne à retard incluant les contraintes (attributs) | 51   |

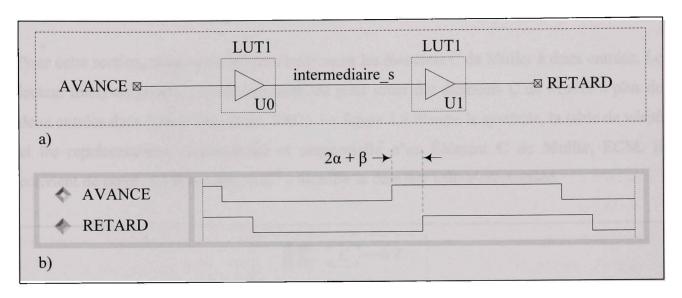

| Figure 2.7  | Ligne à retard                                                      | 52   |

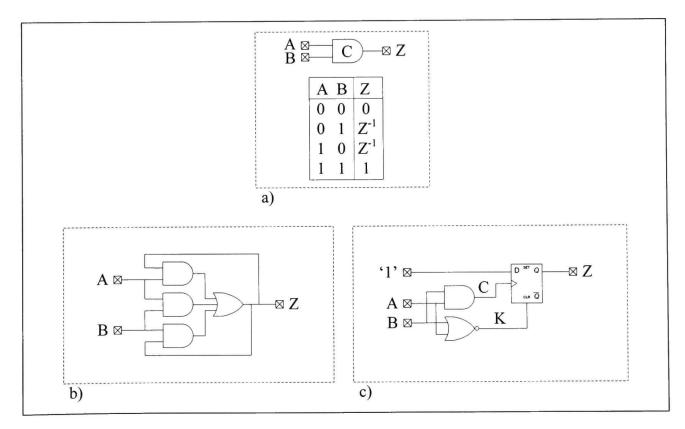

| Figure 2.8  | Élément C de Muller                                                 | 53   |

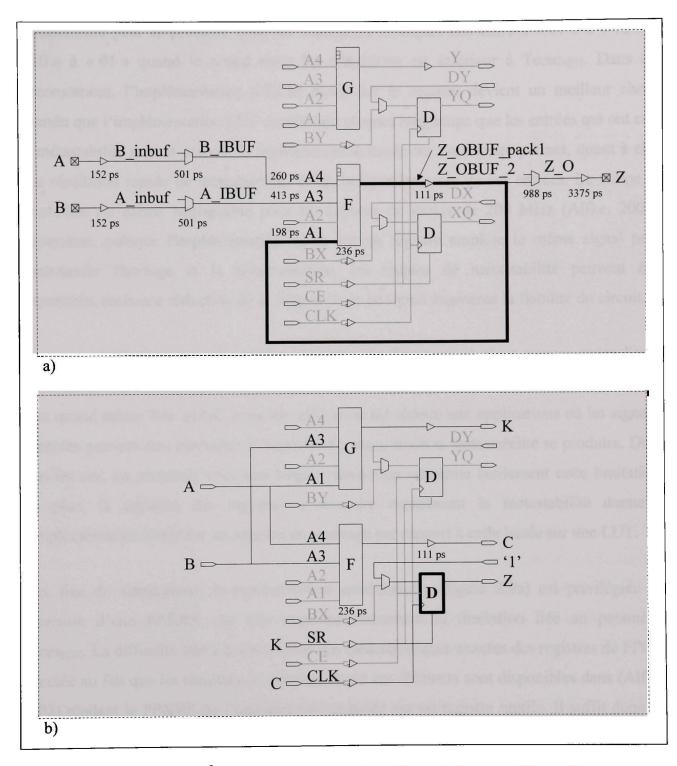

| Figure 2.9  | Élément C de Muller implémenté dans un Virtex-II.                   | 55   |

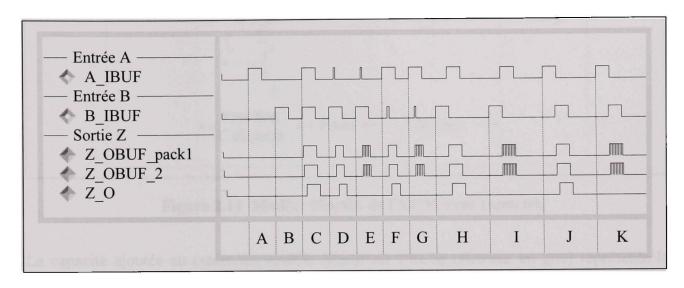

| Figure 2.10 | PP&RS de l'ECM dans un Virtex-II.                                   | 57   |

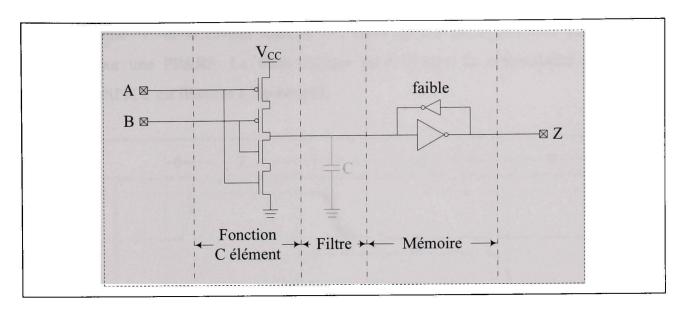

| Figure 2.11 | Modèle Martin de l'ECM avec capacité                                | 58   |

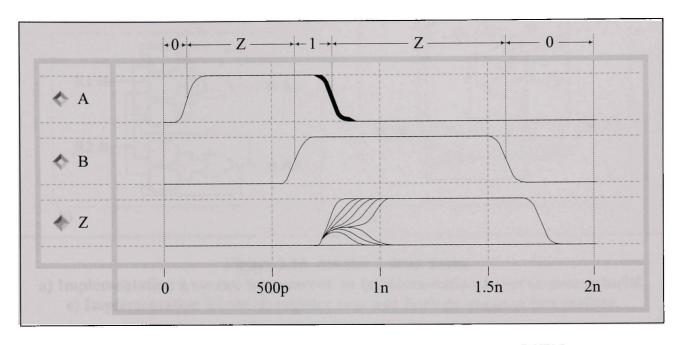

| Figure 2.12 | Simulation SPICE du modèle Martin de l'ECM.                         | 59   |

| Figure 2.13 | Arbitre à deux ports.                                               | 60   |

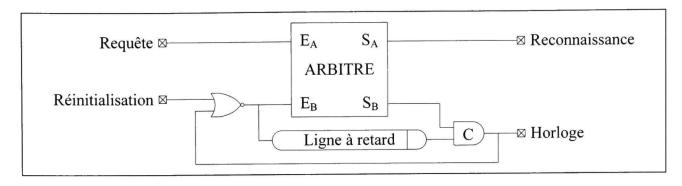

| Figure 2.14 | Générateur d'horloge pour communication GALS unidirectionnel        | 62   |

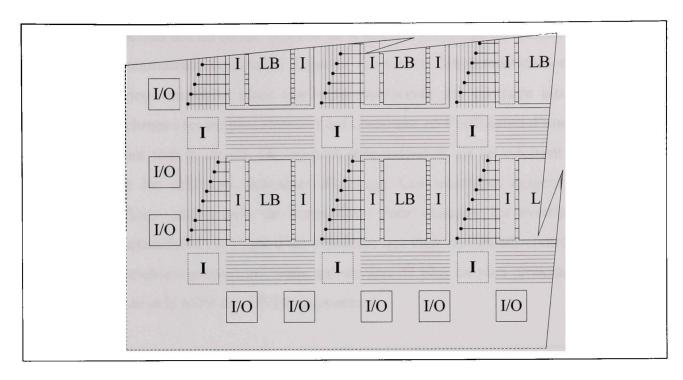

| Figure 3.1  | Coin inférieur gauche d'un FPGA du type île70                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------|

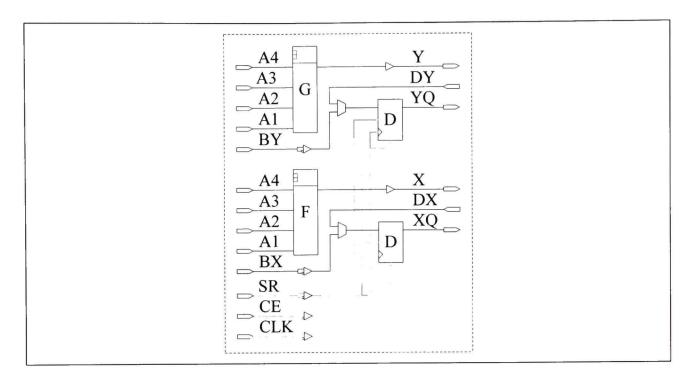

| Figure 3.2  | LB configurable typique de FPGA71                                                                            |

| Figure 3.3  | LB configurable typique de FPGA avec ECM73                                                                   |

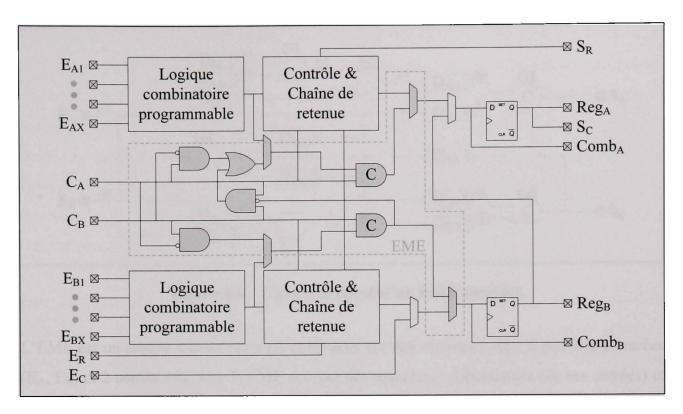

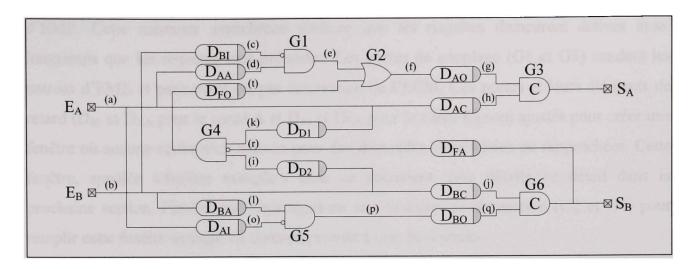

| Figure 3.4  | Circuit complet d'EME74                                                                                      |

| Figure 3.5  | Topologie non optimisée d'EME, mais qui respecte les contraintes82                                           |

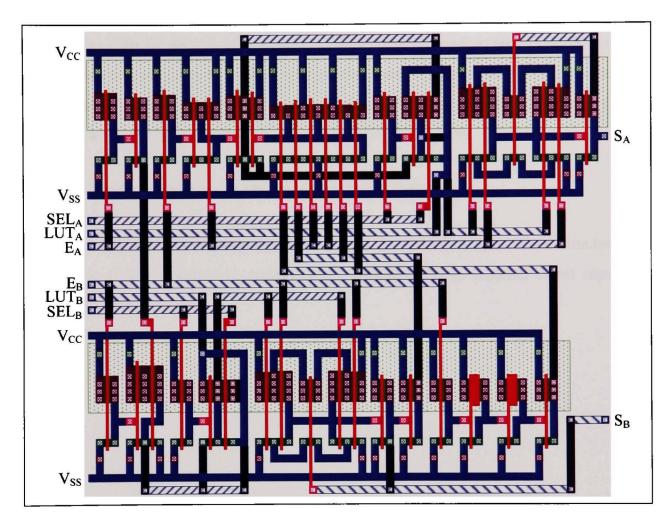

| Figure 3.6  | PP&RS de l'architecture proposée84                                                                           |

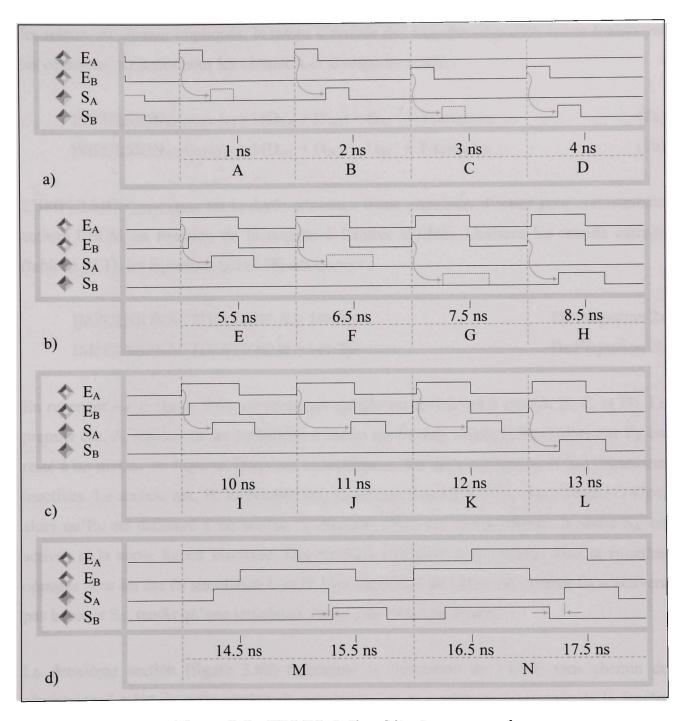

| Figure 3.7  | Simulation SPICE d'EME complet88                                                                             |

| Figure 3.8  | Port de communication GALS bidirectionnel89                                                                  |

| Figure 3.9  | Modèle de cosimulation VHDL-SDF/SPICE d'un générateur d'horloge92                                            |

| Figure 3.10 | Résultats de simulation du modèle combiné du générateur d'horloge93                                          |

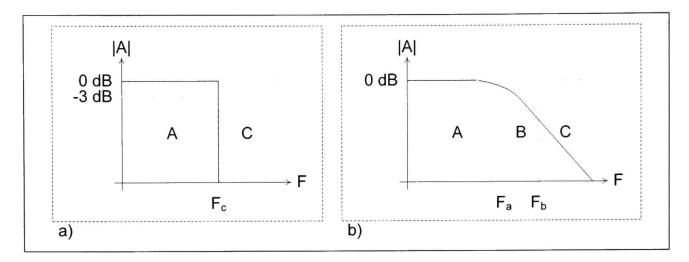

| Figure 4.1  | Réponse en fréquence98                                                                                       |

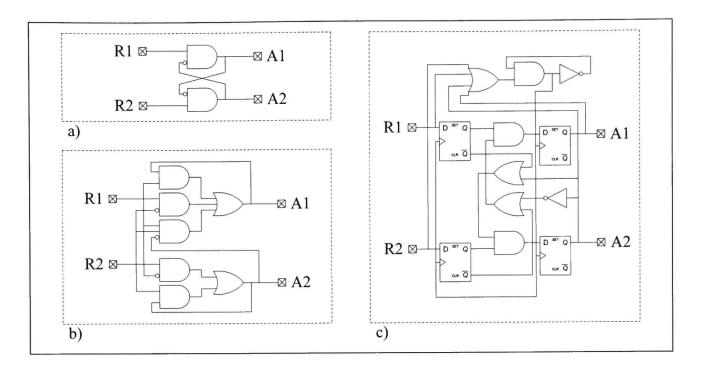

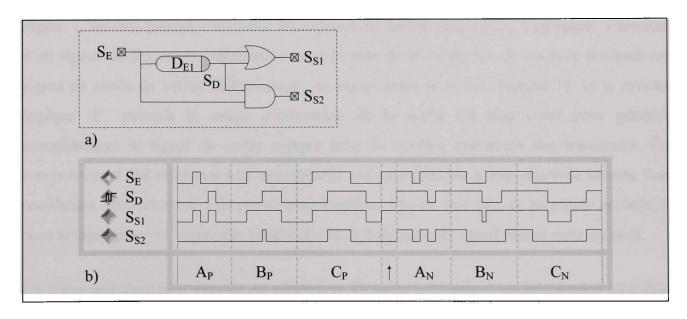

| Figure 4.2  | Deux types de circuit utilisés pour le filtrage logique101                                                   |

| Figure 4.3  | Problème d'activation de la sortie                                                                           |

| Figure 4.4  | Porte de Schmitt                                                                                             |

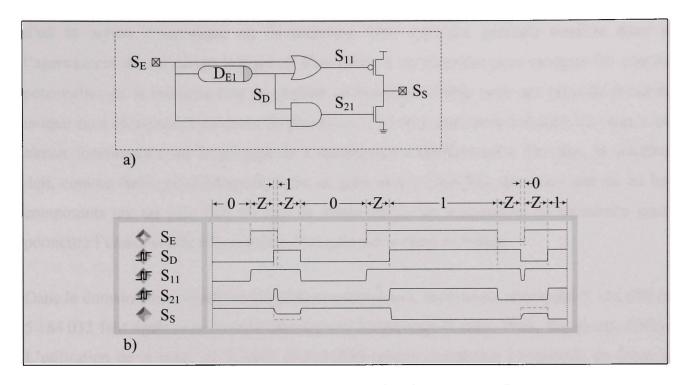

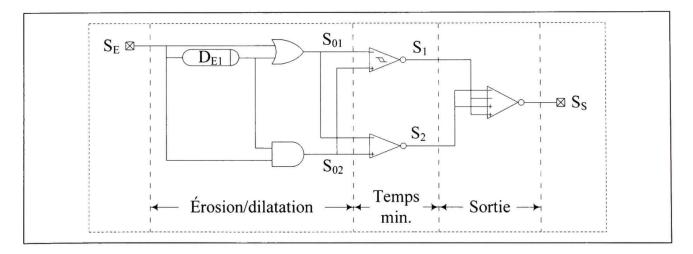

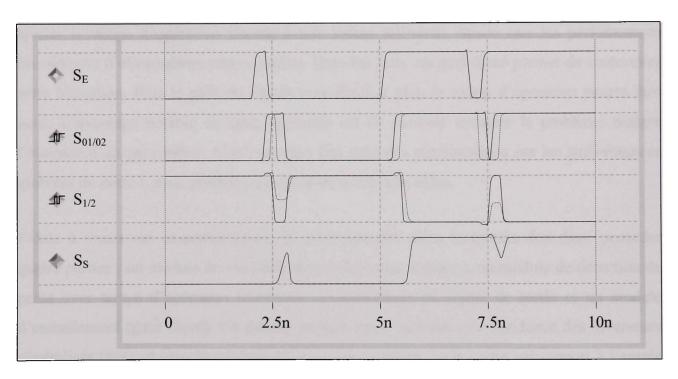

| Figure 4.5  | Masquage des aléas temporels à temps d'opération minimum                                                     |

| Figure 4.6  | Simulation SPICE du masquage des aléas temporels à temps d'opération minimum.                                |

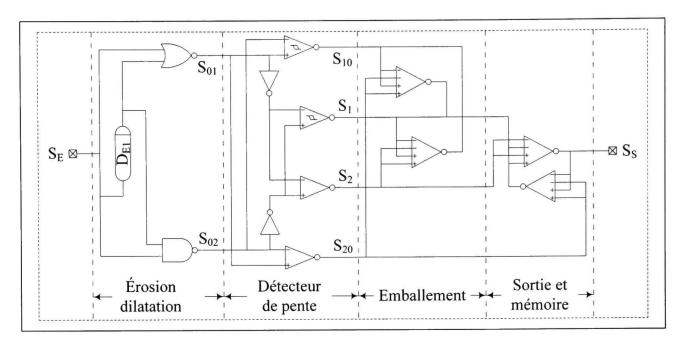

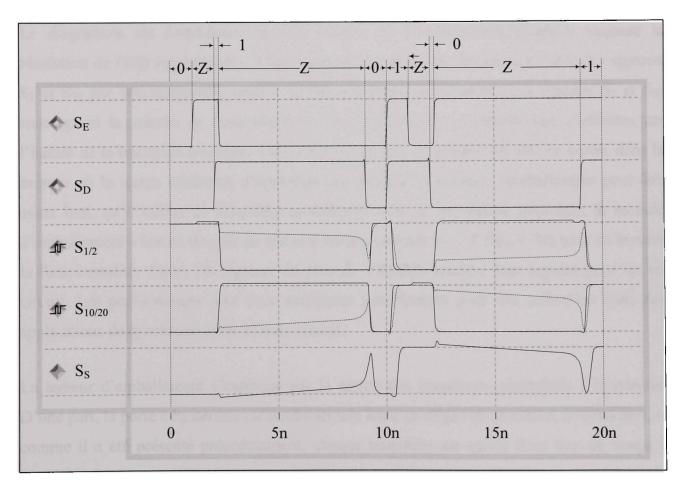

| Figure 4.7  | Diagramme de masquage des aléas temporels                                                                    |

| Figure 4.8  | Simulation SPICE du diagramme de masquage des aléas temporels112                                             |

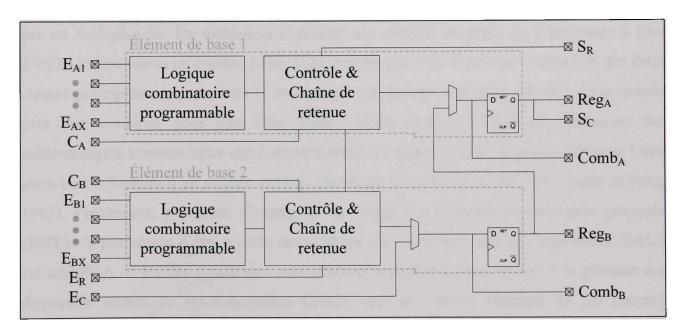

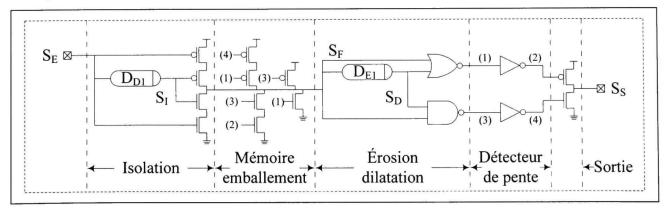

| Figure 4.9  | Circuit proposé de masquage des aléas temporels114                                                           |

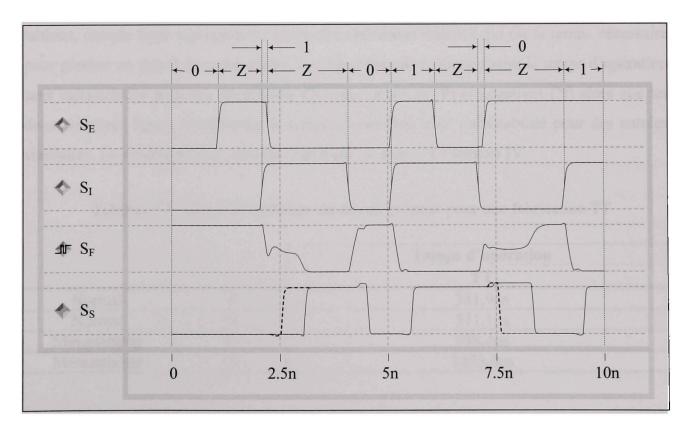

| Figure 4.10 | Simulation SPICE du circuit proposé de masquage des aléas temporels avec signal SD contrôlé de façon externe |

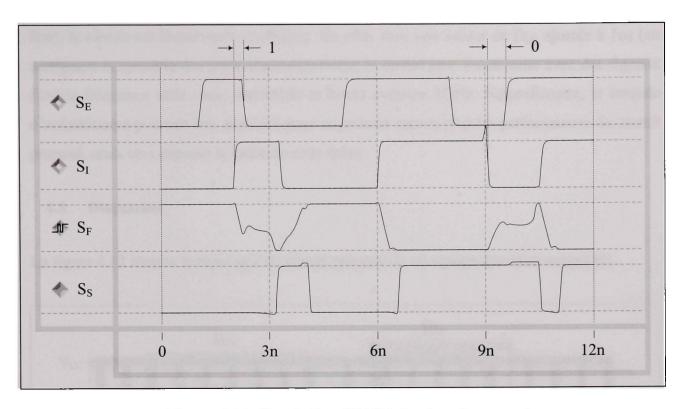

| Figure 4.11 | Simulation SPICE du circuit proposé de masquage des aléas temporels118                                       |

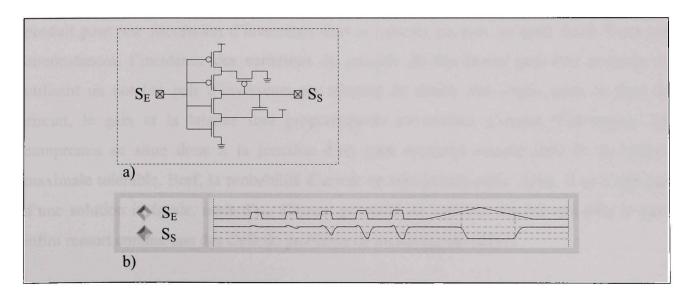

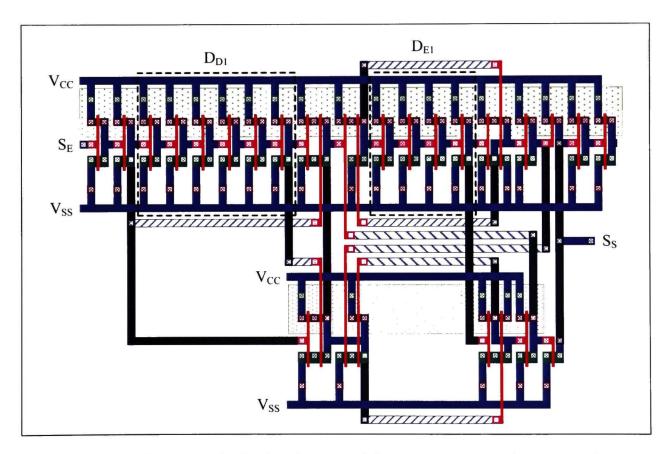

| Figure 4.12 | Topologie du circuit proposé de masquage des aléas temporels119                                              |

## LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

ASIC Application Specific Integrated Circuits

CAD Computer Aided Design

CASC Coalition for Academic Scientific Computing

CLB Configurable Logic Bloc

CMOS Complementary Metal-Oxide Semi-conductor

CPU Central Processing Unit

DI Delay Insensitive

DSP Digital Signal Processing

ECM Élément C de Muller

EDA Electronic Design Automation

EME Élément Mutuellement Exclusif

EMI ElectroMagnetic Interference

FIFO First In, First Out

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

HDL Hardware Description Language

I Interconnection

IC Integrated Circuit

IP Intellectual Property

I/O Input/Output

ITRS International Technology Roadmap for Semiconductors

LB Logic Bloc

LUT Look-Up Table

MUX MUltipleXer

MUTEX MUTual Exclusion

NCL Null Convention Logic

PCC Pausing Clock Circuit

PLL Phase-Locked Loop

P&R Place & Route

PP&RS Post Place & Route Simulation

QDI Quasi-Delay Insensitive

RAM Random Access Memory

SDF Standard Delay Format

SI Speed Independent

SoC System on Chip

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

VLSI Very Large Scale of Integration

VPCS Variable Period Clock Synthesis

# LISTE DES SYMBOLES ET UNITÉS DE MESURE

# UNITÉS DE BASE

m mètre (unité de longueur)

s seconde (unité de temps)

## UNITÉS DE TEMPS

s seconde

ms milliseconde

µs microseconde

ns nanoseconde

ps picoseconde

Fréquence

GHz gigahertz

MHz mégahertz

kHz kilohertz

Hz hertz

## UNITÉS GÉOMÉTRIQUES

Longueur

m mètre

mm millimètre

μm micromètre

nm nanomètre

Différence de potentiel (ou tension)

Force électromotrice V volt mV millivolt

Résistance et conductance électriques

$\begin{array}{ll} \Omega & \text{ohm} \\ m\Omega & \text{milliohm} \\ \mu\Omega & \text{microhm} \end{array}$

# Capacité électrique

F farad

μF microfarad

nF nanofarad

pF picofarad

fF femtofarad

#### INTRODUCTION

#### Contexte de réalisation

Entre 1971 et 2001, la densité des circuits intégrés a doublé tous les deux ans. Cette croissance, mue par la miniaturisation des circuits intégrés, a permis une intégration massive favorisant la production de circuits plus rapides à moindres coûts. Une évolution qui explique aussi l'escalade des performances des circuits intégrés.

Malgré les efforts concertés des concepteurs de circuits intégrés pour perpétuer la tendance, nous assistons, depuis quelques années, à un ralentissement. Bien qu'involontaire, ce dernier n'a pas pour objectif d'augmenter l'espérance de vie des circuits intégrés, mais plutôt de régler des difficultés, comme celui de la synchronisation liée à la miniaturisation. Pour comprendre le problème et construire les outils pour le contourner, une incursion dans l'univers des circuits intégrés s'impose.

## Une horloge pour tous

Durant les belles années de l'intégration, la synchronisation globale régissait essentiellement la conception de circuits électroniques. Un principe selon lequel un signal périodique, communément appelé « horloge », est responsable d'indiquer le début et la fin de toutes les opérations. À la manière du maître de bord qui ordonne les mouvements de rames dans une embarcation, chaque opération se voit octroyer une quantité de temps pour son exécution. Dans la mesure où chacune d'elle est effectuée dans le temps prévu, le système fonctionne correctement. Il est donc aisé de comprendre la popularité de la synchronisation globale.

Cette simplicité apparente cache néanmoins des limites. À titre d'exemple, notons la fréquence d'opération limitée par la tâche requérant le plus grand temps de traitement dans le système. À l'instar d'une chaîne dont la force est limitée par son maillon le plus faible, la vitesse maximale d'un tel système dit synchrone est limitée à son élément le plus lent. De surcroit, l'intégration complexifie la synchronisation globale. En regroupant plusieurs sous-

circuits qui ne partagent pas forcément la même horloge, les circuits ainsi créés n'ont plus leur référence unique et les principes de synchronisation deviennent difficiles, voire impossibles à appliquer.

Pendant des années, les méthodes de conceptions synchrones offraient rapidité et simplicité. Cependant, l'ampleur des inconvénients actuels liés à cette méthodologie de conception suggère qu'il serait plus efficace d'avoir une alternative à la synchronisation globale.

#### La ponctualité malgré l'absence d'horloge

Les systèmes sans horloge, dits asynchrones, présentent nombre d'avantages. L'élimination complète du réseau de distribution du signal d'horloge permet de supprimer les problèmes de distribution du signal d'horloge et de récupérer les 30 à 50 % de la puissance nécessaire à son fonctionnement. Ces systèmes asynchrones compensent l'absence d'horloge par l'utilisation de protocoles de communications. Parmi les différents protocoles, certains maximisent la vitesse d'opération, d'autres minimisent les ressources. Dans tous les cas, ils améliorent les performances des systèmes asynchrones par rapport aux systèmes synchrones. Chaque module travaille à capacité maximale sans être limité par l'élément le plus lent du système. En conséquence, les communications sont plus rapides tout en réduisant le taux d'émission d'ondes électromagnétiques, EMI, (ElectroMagnetic Interference). Une telle réduction est imputable à la nature aléatoire des communications qui ne sont pas dictées par le rythme régulier d'une horloge.

Malheureusement, l'absence d'horloge de synchronisation n'a pas que des avantages. Le manque de connaissances, d'outils et de techniques est le principal problème à l'émergence d'une méthodologie mature de conception asynchrone. Ces manques s'expliquent, en partie, par les besoins de l'industrie qui stimulent à leur tour la formation offerte. Les universités se concentrent sur les conceptions synchrones à cause de leur simplicité et de leur dominance. De fait, les concepteurs sont des experts de la conception synchrone et la disponibilité des outils reflète cette réalité. Dans ces circonstances, peu de concepteurs s'aventurent sur la voie de l'asynchronisme.

Malgré tout, quelques groupes ont travaillé sur la logique asynchrone au cours des dernières décennies. Ces travaux ont permis de mettre au point quelques outils relativement primitifs pour les conceptions asynchrones. Cependant, beaucoup de travail devra encore être fait pour créer des outils répondant aux besoins actuels en matière de conception numérique. Bien que plusieurs réalisations prouvent la viabilité de la logique asynchrone, elle demeure marginale.

Une solution à ce problème passe par une approche hybride. Une méthodologie exploitant les avantages des conceptions synchrones et asynchrones en minimisant leurs inconvénients.

## Plusieurs horloges locales sans synchronisation globale

La logique Globalement Asynchrone, mais Localement Synchrone, GALS, (Globally Asynchronous Locally Synchronous) est spécialisée pour les circuits contenant différents domaines d'horloge. Proposée il y a plus de 20 ans par D. M. Chapiro, cette méthode refait surface. Ce retour est motivé par l'évolution des techniques asynchrones et l'exacerbation des problèmes associés à la synchronisation globale. Une forme populaire de réalisation GALS consiste à créer des circuits synchrones de taille restreinte et de les relier entre eux par des protocoles asynchrones. Dans cette optique, il est possible de construire des circuits de très grande taille sans avoir les difficultés de la synchronisation globale.

Alors, pourquoi est-ce que tous les systèmes synchrones n'ont pas encore été remplacés? En fait, il ne s'agit pas d'éliminer la synchronisation globale. Certains circuits se réalisent et continueront de se réaliser très bien de façon synchrone. Pour ces derniers, un changement de méthodologie exigerait des efforts et des coûts supplémentaires inutiles.

Seuls les circuits très rapides, de tailles démesurées ou qui ont naturellement plusieurs domaines d'horloge posent problème. Pour ces circuits, une alternative à la synchronisation globale est nécessaire. En ce sens, la logique GALS représente, actuellement, une alternative prometteuse. Malheureusement, cette migration vers des méthodes de conception GALS est ralentie par le nombre restreint d'outils soutenant l'asynchronisme dans les circuits intégrés. Bref, c'est encore une fois le problème de l'œuf et de la poule. La rareté d'outils freine les

concepteurs et le nombre restreint de concepteurs gêne le développement d'outils performants. Cependant, pour ces circuits, les jours de la synchronisation globale semblent bel et bien comptés.

#### Support de réalisation

Le support de réalisation choisi pour l'implémentation de systèmes GALS est un composant de logique programmable, FPGA, (Field Programmable Gate Array). Ce support est privilégié pour plusieurs raisons telles que les coûts et la disponibilité. Cependant, il présente également l'avantage intrinsèque d'être programmable et donc de servir d'outil de vérification pour des réalisations à base de semi-conducteurs, ASIC, (Application Specific Integrated Circuits). Étant donné que les coûts liés aux ASIC sont très élevés, une telle plateforme de vérification permet de diminuer les risques avant la fabrication, mais également de développer, et ce, rapidement, des preuves de concept.

## **Objectifs**

Cette thèse regroupe trois objectifs complémentaires portant sur un même thème : les FPGA GALS. Pris séparément, chaque objectif pourrait déboucher sur une thèse complète. Cependant, une approche exploratoire a été privilégiée : aborder plusieurs thèmes connexes de façon à contribuer à l'avancement des connaissances, sur un large spectre, dans le domaine de la logique GALS. Malgré cette approche exploratoire, la recherche exhaustive sur ces trois objectifs nous a permis de cibler plusieurs aspects fondamentaux.

Le premier objectif est une méthodologie d'implémentation de composants GALS dans un FPGA synchrone. Il s'agit d'une méthode permettant d'utiliser les ressources disponibles des FPGA synchrones pour implémenter des composants asynchrones. Les composants ciblés sont ceux qui permettent d'établir des communications efficaces entre deux domaines d'horloge (de fréquence différente et de phase différente). Pour des systèmes de très grandes tailles ou de fréquences très élevées, les communications synchrones deviennent l'élément le plus contraignant pour la fréquence maximale du système. Dans ces circonstances, des

communications asynchrones, fonctionnant au maximum de performances des modules impliquées dans la communication, offrent un potentiel de performances supérieures à celles de la logique synchrone où le système est construit en fonction du pire cas.

De plus, cette méthodologie fournit un support viable de vérification pour les circuits asynchrones. Étant donné que la méthodologie proposée est basée sur un circuit programmable de type FPGA, il est possible d'exploiter un support connu peu coûteux et offert en masse pour faire des preuves de concept de circuits asynchrones avant de les réaliser sur des ASIC, beaucoup plus onéreux.

Malgré le potentiel de la méthodologie d'implémentation, le support synchrone limite les performances et l'étendue des applications réalisables. Ainsi, le second objectif consiste à proposer une nouvelle architecture GALS de FPGA. Cette architecture doit paraître fondamentalement synchrone tout en permettant les transferts asynchrones. Loin d'une architecture complètement asynchrone, cette architecture GALS cible les conceptions synchrones de très grandes tailles ou de fréquences très élevées pour lesquelles le remplacement des longs liens de communication synchrones par des liens asynchrones présente des avantages sur le plan des performances générales du système. Cet objectif n'invalide pas le précédent, en fait, il le complète en abordant une catégorie étendue de système GALS. Par contre, cet objectif ne couvre pas en détail la méthode utilisée pour déterminer la nature de ces liens et les remplacer au besoin. Cependant, certains éléments seront présentés, à cet égard, sous forme de travaux futurs.

Forts d'une méthodologie d'implémentation de composants GALS et d'une nouvelle architecture de FPGA GALS, nous constatons qu'un frein important à l'émergence des systèmes GALS et des systèmes asynchrones est la possibilité d'états métastables. C'est pourquoi le troisième objectif est de présenter un circuit qui masque complètement la métastabilité. L'approche exploitée ici est un circuit à une entrée et une sortie pour lequel seuls les signaux ne pouvant pas générer d'états métastables en sortie peuvent être portés de l'entrée à la sortie. L'aspect intéressant de ce circuit est l'absence d'hypothèse ou de restriction sur le signal d'entrée, le circuit se charge d'analyser la forme d'onde et de

masquer les aspects problématiques d'un signal. Le circuit produit un signal de sortie qui ne créera pas de métastabilité. Le problème est donc réglé avant qu'il ne se produise.

Malgré ce dernier objectif très ambitieux, le circuit doit être, en plus, suffisamment général pour être utilisable dans une pléiade d'applications. La plus importante est certainement celle de la synchronisation transparente de signaux haute fréquence et haut débit à travers différents domaines d'horloge.

#### **Contributions**

Cette thèse présente des contributions à différents niveaux :

- méthodologie de conception,

- architecture de circuit programmable,

- différents éléments de circuits.

Malgré son apparence simpliste, la contribution en méthodologie est très importante, puisqu'il n'est pas commun de synthétiser des composants asynchrones sur un FPGA synchrone à l'aide d'outils synchrones. Étant donné que la principale faiblesse des circuits asynchrones est le manque d'outils, une telle méthode s'avère un avantage de taille dans le but de réaliser un prototype programmable à faible coût avant de le réaliser sous forme d'ASIC. Dans ces circonstances, la contribution est un guide de synthèse pour implémenter les structures asynchrones souhaitées sans craindre les éventuelles optimisations synchrones de l'outil. De plus, la méthode permet d'identifier les éléments de synchronisation critiques étant donné l'utilisation d'outils synchrones. Ces résultats furent publiés à l'occasion de FETCH-2009 (Gagné, Belzile et Thibeault, 2009d), de NEWCAS-TAISA-2009 (Gagné, Belzile et Thibeault, 2009c).

La contribution, en architecture, s'articule autour de la réutilisation de l'architecture des FPGA de Xilinx et de l'ajout de la quincaillerie nécessaire pour effectuer les mêmes

opérations que celles présentées pour la contribution méthodologique. Cependant, le tout est fait nativement afin d'augmenter les performances des systèmes implémentés. De plus, dans le but de rendre cet ajout transparent aux concepteurs (pour les conceptions synchrones) et de modifier au minimum l'architecture de référence, cette contribution a donné lieu à une plus petite contribution en circuit : un circuit d'arbitrage constitué à l'aide de composants asynchrones. Le circuit proposé exhibe une très faible probabilité de métastabilité par le masquage, a priori, mais également a posteriori, de sources de métastabilité. Ces résultats furent publiés à l'occasion de NEWCAS-2007 (Gagné, Belzile et Thibeault, 2007), de FETCH-2008 où j'ai reçu *le prix du meilleur doctorant* (Gagné, Belzile et Thibeault, 2008) et du 77<sup>e</sup> congrès de l'ACFAS (Gagné, Belzile et Thibeault, 2009a). L'article de NEWCAS-2007 a, par la suite, été présélectionné pour être bonifié et publié dans la revue scientifique « microelectronics journal » (Gagné, Belzile et Thibeault, 2009e). Cet article est actuellement sous presse.

C'est ce circuit d'arbitrage qui est à la base du circuit de masquage complet des sources de métastabilité, la contribution majeure de cette thèse. Le circuit proposé implémente physiquement les contraintes de masquage de la métastabilité de façon à régler les problèmes de synchronisation en aval, et ce, de façon transparente pour le concepteur. Ce dernier n'a qu'à ajouter ce circuit sur les signaux de synchronisation et à oublier le concept même de la métastabilité. Le circuit masque les sources de métastabilité sans dégradation des performances, mais avec une latence de l'ordre du temps de stabilisation des éléments subséquents (peu importe leur nature). Ces résultats font l'objet d'une demande de brevet (numéro de dossier Valéo : VAL-077). Deux articles de revue sont en cours de rédaction.

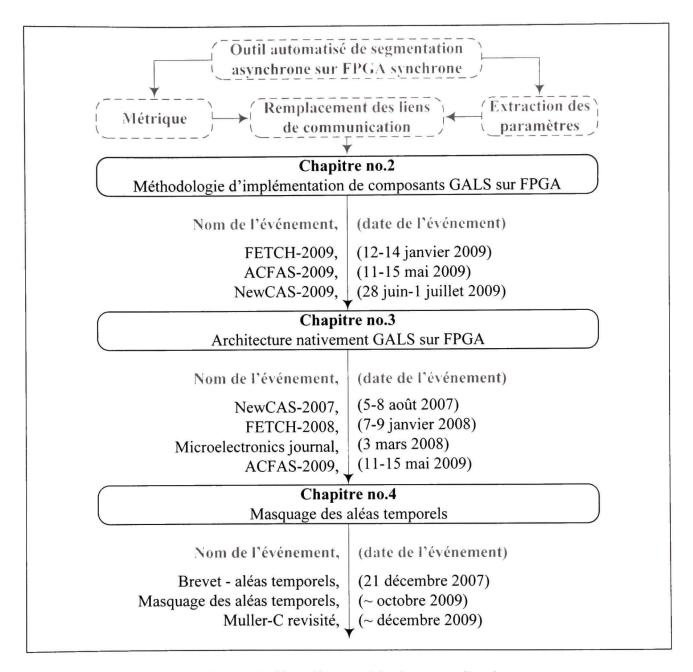

Les retombées de cette thèse en matière de publications sont illustrées à la figure 1. Cette figure illustre, également, la progression de la thèse en fonction de chaque objectif. Les éléments du haut, allant jusqu'au remplacement des liens de communication, représentent les objectifs tels que vus initialement. Pendant ce temps, d'autres objectifs, plus intéressants, ont captivé notre attention. Il est toutefois à noter que l'outil de segmentation sera présenté, en détail, dans la section des futurs travaux de la conclusion de cette thèse. Naturellement, étant donné l'ampleur des travaux effectués, cette section sera tout de même bien étoffée.

Figure 1 Vue d'ensemble des contributions.

#### **Organisation**

Cette thèse est divisée en quatre chapitres. Un premier chapitre de revue de la littérature chapeaute trois autres chapitres, à raison d'un chapitre par objectif.

Le chapitre 1 présente la revue de la littérature générale sur la logique synchrone et la logique asynchrone. Ce survol permet d'identifier les forces et faiblesses de façon à bien doser la

répartition synchrone/asynchrone pour les conceptions GALS. Il est à noter que chaque chapitre succédant possède également une brève revue de la littérature propre à chaque objectif de façon à cibler les aspects particuliers de chaque objectif.

Le chapitre 2 présente l'architecture générale des FPGA synchrones, la liste de contraintes pertinentes supportées par l'outil de synthèse pour FPGA ainsi que la méthode de conception proposée qui permet d'implémenter des circuits GALS sur un FPGA synchrone. De plus, les circuits implémentés sont comparés à d'autres implémentations équivalentes et sont caractérisés en fonction de leurs performances en thèmes de ressources utilisées.

Le chapitre 3 fait un bref retour sur les architectures de FPGA synchrones de façon à cibler l'endroit où implanter les ressources asynchrones et ainsi créer une architecture nativement GALS. Les éléments proposés sont présentés, analysés et simulés avant d'être incorporés à un exemple complexe de communication asynchrone.

Le chapitre 4 présente l'innovation majeure de cette thèse. Étant donné sa nature innovatrice, ce chapitre est construit de façon itérative, à la manière par laquelle le circuit a été conçu. Chaque étape de conception est basée sur une revue de la littérature exhaustive et les résultats de simulation aiguillent chaque prise de décision. Le chapitre converge rapidement sur la solution tout en restant suffisamment pédagogique pour être compris par un novice dans le domaine.

#### CHAPITRE 1

#### Revue de la littérature

Le chapitre de la revue de la littérature a pour objectif de couvrir de façon générale les éléments clefs permettant un passage de la logique synchrone à la logique asynchrone. Chacun des chapitres succédant présentera une brève revue de la littérature pour cibler les intérêts de recherche propres à chacun d'eux.

#### 1.1 Logique synchrone

La logique synchrone est, depuis les années 1960, la méthodologie de conception la plus utilisée pour les circuits intégrés. Pourtant, il ne s'agit pas d'une approche naturelle dans la mesure où toutes les interactions physiques se font de façon asynchrone. Un bon exemple est celui d'une centrale téléphonique. Tous les appels entrent à des instants indépendants. Malgré tout, ces appels sont numérisés, synchronisés et traités de façon synchrone. La synchronisation, inutile à première vue, sert paradoxalement à simplifier le traitement.

#### 1.1.1 Synchronisation

La synchronisation globale, faut-il le rappeler, exploite le principe selon lequel un signal périodique, communément appelé « horloge », est responsable d'indiquer le début des opérations. Cette synchronisation simplifie la vérification des circuits pour autant que le traitement soit terminé avant le début de la prochaine opération. On parle alors d'une synchronisation implicite. Cette contrainte, relative à la période de l'horloge utilisée pour cadencer les événements, force l'utilisation d'une horloge de période assez longue accommodant l'élément le plus lent du circuit considérant les pires conditions d'utilisation (valeur des entrées, température, tension d'alimentation, etc.). La méthode, couramment adoptée pour exploiter la synchronisation globale en réduisant les pertes de performances qu'elle peut engendrer, consiste à fractionner la logique combinatoire et à intercaler des

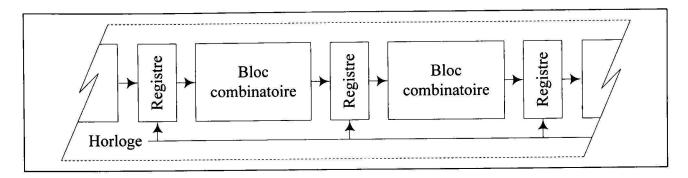

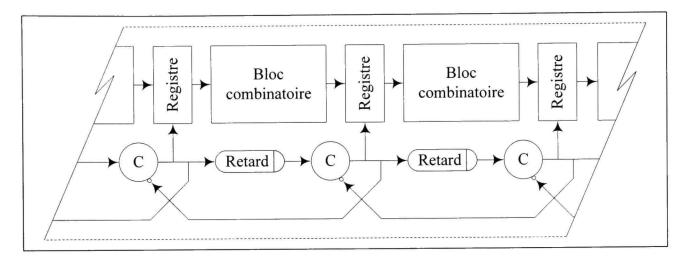

éléments de mémoire entre chaque sous-module créé. La figure 1.1 illustre une telle architecture communément désignée sous le nom « pipeline synchrone ».

Figure 1.1 Pipeline synchrone.

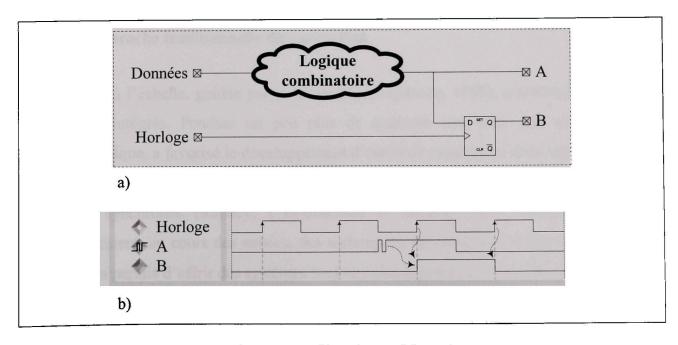

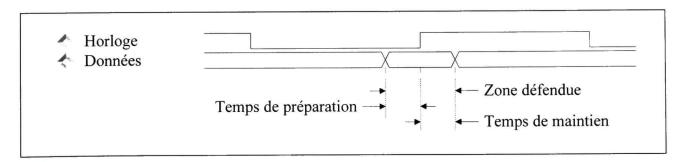

Cette mémoire supplémentaire sert à synchroniser les données entre les éléments tout en minimisant la période d'horloge, ceci aux dépens de la latence et de la quantité de ressources qu'une telle organisation ajoute. Ces ajouts constituent des inconvénients mineurs étant donné que la mémoire sert également à masquer les aléas temporels (statique ou dynamique) engendrés par la logique combinatoire. La figure 1.2 illustre le masquage des aléas temporels pour la logique synchrone.

Figure 1.2 Circuit combinatoire. a) Avec registre. b) Chronogramme associé.

Le circuit de la figure précédente reçoit une série particulière de données et produit un signal (signal A, figure 1.2) en fonction de l'agencement de la logique combinatoire. Cette sortie peut produire un aléa temporel qui se traduit par une donnée erronée. Un travail d'optimisation au niveau de l'équation booléenne de la logique combinatoire permet de prévenir la formation de cet aléa. Cependant, si on ajoute une bascule de synchronisation, ce travail supplémentaire s'avère inutile (signal B, figure 1.2). Cette bascule filtre les transitions indésirables lorsque les paramètres de la bascule sont respectés. Les spécificités de ces paramètres seront abordées dans les prochains chapitres. Malgré tout, il convient de noter qu'il ressort de ceci un désavantage clair pour la logique combinatoire, ou de façon plus générale, la logique asynchrone à générer des signaux sans aléas temporels (Cortadella, 2002). De plus, l'ajout de termes à l'équation booléenne crée des redondances qui rendent le test plus complexe et le circuit plus difficile à observer et à commander (Hazewindus, 1992).

Les éléments simplificateurs de la logique synchrone, dont le masquage des aléas temporels fait partie, font en sorte qu'elle est plus simple et plus facile à utiliser que la logique asynchrone. Ce sont ces éléments simplificateurs qui ont favorisé l'expansion et la dominance des méthodologies de conception synchrone.

# 1.1.2 Approche traditionnelle de conception

La réduction à l'échelle, guidée par la loi de Moore (Moore, 1965), a favorisé l'intégration des circuits intégrés. Pendant un peu plus de quarante ans, cette loi, au cœur de la microélectronique, a favorisé le développement d'outils de conception et de vérification pour les circuits à base de semi-conducteurs, CMOS, (Complementary Metal-Oxide Semi-conductor) synchrones (Rabaey, Chandrakasan et Nikolic, 2003; Savaria, 1988). Le perfectionnement, au cours des années, des techniques, des méthodes et des outils relatifs à ces circuits a permis d'offrir des systèmes toujours plus rapides, avec plus de fonctionnalités.

Cette évolution a cependant mis en évidence certaines limitations qui, selon l'ITRS, ITRS, (International Technology Roadmap for Semiconductors) ont tôt fait d'assombrir les perspectives de la logique synchrone (ITRS, 2007). Parmi les enjeux identifiés par l'ITRS,

notons la fréquence d'opération, la surface des circuits et la puissance consommée, des enjeux qui atteignent des envergures problématiques. Ainsi, malgré une évolution relativement constante des technologies CMOS, la disparité des différentes parties des systèmes exacerbe l'impact de ces enjeux sur les performances générales (Stallings, 1999). En ce sens, la vitesse d'accès mémoire, la capacité des mémoires, la vitesse des éléments de calcul et le taux de transfert entre ces éléments évoluent de façon disparate. À titre d'exemple, la capacité des éléments de calcul suit la loi de Moore et double tous les 18 mois alors que les performances des communications réseau doublent tous les 48 mois (Educause et CASC, 2009). Cette hétérogénéité complique considérablement la conception de systèmes de très grande taille et ceux de très grand débit (Johnson et Graham, 1993). Elle nuit également aux systèmes dits à contraintes temporelles dures comme les systèmes en temps réel (Laplante, 1997).

Traditionnellement, la logique synchrone bénéficiait d'un avantage de taille. La vitesse des portes logiques relativement lente par rapport à la vitesse de propagation des signaux dans les fils simplifiait l'analyse temporelle. Elle permettait même de la négliger dans certains cas. Il va sans dire que cet avantage a favorisé, par sa simplicité, l'utilisation des méthodologies de conception synchrones. Les percées technologiques des dernières années rendent cette réalité de moins en moins vraie. L'inertie favorise toujours les conceptions synchrones, mais il est de plus en plus évident qu'une place existe pour les logiques GALS et asynchrone dans le coffre à outils des concepteurs en microélectronique.

## 1.1.3 Approche moderne de conception

Malgré toutes les simplifications qu'apportent les méthodologies de conception synchrone lors de la conception de circuits intégrés, ces méthodologies s'avèrent de plus en plus difficiles à appliquer aux systèmes de très grandes envergures, VLSI, (Very Large Scale of Integration). En raison de leur maturité et leur lot impressionnant d'outils, il est plus attrayant de contourner le problème que de tenter de l'enrayer en changeant radicalement de méthodologie de conception. Le problème le plus complexe est celui de la distribution du signal d'horloge pour un budget de puissance donné (Rabaey, Chandrakasan et Nikolic,

2003). À titre d'exemple, il est courant d'utiliser des amplificateurs, qui consomment une puissance importante, pour minimiser les erreurs de phases sur le signal d'horloge. Un problème critique qui, malheureusement, prend de l'ampleur avec la taille des systèmes pour une fréquence donnée. Le même problème se pose pour des circuits de taille modeste, mais de fréquences très élevées.

L'augmentation des fonctionnalités, de la puissance de calcul et d'autres caractéristiques dont les usagers sont friands nécessite l'utilisation de composantes contenant de plus en plus de transistors. En ce sens, la vidéo sur appareil sans fil est un exemple pertinent dans le domaine des télécommunications. Malgré une réduction à l'échelle efficace, ces composantes atteignent des tailles inégalées et des fréquences d'opération toujours plus élevées. De plus, une telle tendance fait naturellement surgir l'idée de faible consommation de puissance pour assurer la durée de vie des piles.

Les longs liens de communication forcent la prise en compte des retards de communication provoqués. Les circuits sont de plus en plus grands et la réduction à l'échelle favorise des composants intégrés plus petits et plus rapides. Dans ces circonstances, le retard dans les portes logiques diminue, alors que celui des liens de communication demeure relativement constant. Ainsi, le retard dans les fils prend de l'importance par rapport à celui dans les portes logiques. Le résultat est que l'analyse temporelle devient plus complexe et l'énergie requise par l'horloge augmente relativement aux autres parties du circuit.

Bref, les circuits synchrones ont été privilégiés au cours des années à cause de leur simplicité de conception. Cependant, il devient de plus en plus évident que de tels systèmes ont des limites importantes.

## 1.2 Logique asynchrone

Parmi les possibilités de méthodologies de conception, l'ITRS mentionne le retour de la logique asynchrone : une logique qui n'exploite pas la synchronisation globale, mais une synchronisation locale (à l'aide d'un contrôle distribué) entre les modules pour lesquels cette

dernière a une signification fonctionnelle. C'est notamment le cas pour les modules impliqués dans une communication. Dans ces circonstances, les modules possèdent des signaux explicites de synchronisation permettant d'implémenter un protocole de communication de type « poignée de main » (« handshake ») entre modules associés aux transferts d'informations. La figure 1.3 illustre un exemple de communication avec transferts d'informations du type poignée de main.

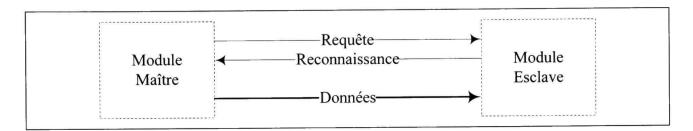

Figure 1.3 Exemple de communication du type poignée de main.

Le module maître signifie au module esclave, par l'entremise du signal de requête, qu'il veut mettre en œuvre un transfert et émettre des données. L'esclave répond à cette demande en activant le signal de reconnaissance lorsqu'il a récupéré les données, ce qui informe le maître de la possibilité d'enlever ou de changer les données. Ce dialogue simple illustre un protocole de communication de type poignée de main. Avant d'entrer dans les détails des protocoles de communication, voyons les forces et les faiblesses de la logique asynchrone.

## 1.2.1 Forces de la logique asynchrone

Les forces de la logique asynchrone sont bien connues (Furber, 1996; Hassoun, Kim et Lombardi, 2003). Elles correspondent exactement aux difficultés de la logique synchrone. Les enjeux qui favorisent l'utilisation de la logique asynchrone dans les conceptions numériques sont les suivants :

- élimination de l'obliquité d'horloge (« skew »);

- réduction du bruit;

- performance générale moyenne au lieu du pire cas;

- adaptation à l'environnement et aux variations du procédé de fabrication;

- modularité accrue;

- réduction de la consommation de puissance globale.

Le signal de synchronisation fourni sous forme d'horloge globale agit comme un chef d'orchestre. Cette horloge consomme une portion importante de puissance pouvant atteindre 50 % du budget de puissance du circuit, même si elle n'effectue aucun traitement. De plus, chaque transition synchronisée augmente le niveau de bruit et d'EMI dans le circuit à cause de la densité de transitions produites. Avec la réduction à l'échelle des circuits intégrés, ces problèmes de bruit, d'obliquité et de demande en puissance constituent des difficultés supplémentaires de conception. Dans cette optique, la suppression d'un signal global de synchronisation apaise les difficultés de conception des circuits intégrés.

Les performances des systèmes synchrones réfèrent au pire cas possible. Le signal d'horloge doit accommoder l'élément le plus lent du système. Les autres fonctionnent donc en deçà de leurs capacités. En ce sens, la logique asynchrone réfère à des performances moyennes, car seuls les modules impliqués dans un transfert peuvent influer sur les performances. Par exemple, si le module le plus lent d'un circuit est sollicité seulement 10 % du temps, le circuit fonctionnera 90 % du temps à une fréquence plus élevé que celle du module le plus lent. Ainsi, les circuits asynchrones ont un potentiel d'opération supérieur, en moyenne, par rapport aux circuits synchrones.

La logique asynchrone s'adapte mieux aux variations d'environnement et de fabrication, car elle peut être construite pour être insensible aux retards, DI, (Delay Insensitive). Dans ces circonstances, toute variation de l'environnement peut nuire aux performances du circuit, mais sans influencer la fonctionnalité. Pour la même raison, la logique asynchrone bénéficie d'une modularité accrue. Plusieurs modules de propriété intellectuelle, IP, (Intellectual Property) conçus séparément peuvent être assemblés sans vérification a posteriori, car la synchronisation locale des données s'opère automatiquement à fréquence maximale pour une technologie donnée. Finalement, seuls les modules sollicités dans un traitement précis ont besoin d'être actifs. Autrement, les modules sont inactifs et exploitent au maximum les

notions d'économie d'énergie des modes dormants. Ces derniers pourraient également être déconnectés des rails d'alimentation pour accroître le potentiel d'économie d'énergie.

Ces quelques avantages sont les plus importants et les plus cités. Pour l'ITRS, les problèmes reliés à la logique synchrone sont suffisamment importants pour changer de méthodologie de conception. Cependant, la logique totalement asynchrone ne semble pas, à ce jour, être une alternative viable à la logique synchrone. La section suivante met cet aspect en relief, en présentant les difficultés reliées à la logique asynchrone.

#### 1.2.2 Faiblesses de la logique asynchrone

La logique asynchrone est souvent comparée à la logique dynamique, car les problèmes rencontrés sont de même nature. Les principales difficultés sont les suivantes (Furber, 1993; Hassoun, Kim et Lombardi, 2003):

- les habitudes de conception;

- les outils de conception assistée par ordinateur, CAD, (Computer Aided Design);

- les outils de validation, vérification et de test;

- la sensibilité aux phénomènes de courses et aux aléas temporels;

Aujourd'hui, un concepteur n'a pas le choix des armes. Les méthodes les plus simples pour la réalisation de circuits intégrés de quelques millions de transistors sont celles concernant la logique synchrone. La raison est simple. La formation est concentrée sur les conceptions synchrones à cause de leur simplicité et de leur dominance dans l'industrie des semiconducteurs. Les cours sont principalement fondés sur les conceptions synchrones en insistant sur le fait que les réalisations asynchrones apportent des tracas supplémentaires lors de la conception et de la réalisation. Ce comportement favorise le quasi-monopole de la logique synchrone, et ce, sans considérer les avantages potentiels d'autres formes de réalisation. Les habitudes de conception forment un cercle vicieux où les concepteurs synchrones favorisent les méthodologies de conception synchrones. De fait, les concepteurs sont des experts de la conception synchrone et la disponibilité des outils reflète cette réalité.

Les outils de CAD, de validation, de vérification et de test se sont, de ce fait, multipliés en peu de temps pour la logique synchrone alors qu'en parallèle, les outils de la logique asynchrone ont bénéficié d'un support minimum. En considérant que les outils développés ne peuvent pas facilement s'adapter d'une méthodologie à l'autre, les outils pour la logique asynchrone sont donc très rares. Quelques outils ont quand même été développés au fil des années, mais leur nombre demeure insignifiant.

Finalement, la sensibilité des technologies asynchrones aux phénomènes de course et d'aléas n'a pas aidé l'émergence de cette dernière. La logique synchrone simplifie ce problème dans la mesure où ces effets négatifs peuvent être masqués. Peu importe la valeur ou la variation du signal à l'entrée, les éléments de mémoire (bascules) gardent les sorties stables. De cette façon, lorsque la contrainte temporelle du signal d'entrée est satisfaite, le signal de sortie peut de nouveau produire une valeur correcte et stable en sortie (voir figure 1.2). Un stratagème similaire peut être utilisé pour la logique asynchrone, mais il exige un déploiement d'importance qui se quantifie par une utilisation plus importante de transistors. L'étude du cas de la logique à phase nulle, NCL, (Null Convention Logic) est particulièrement intéressante et significative pour les circuits asynchrones (Martin, Nystrom et Wong, 2003). La technologie asynchrone NCL est dite correcte par construction sans aucun effet de course et d'aléas pour autant que la différence entre des retards concurrents, menant à une même porte logique, soit similaire. Cette caractéristique nommée « isochronic folk » propre au modèle temporel presque insensible aux retards, QDI, (Quasi Delay Insensitive) est utilisée pour la logique NCL. L'étude de cas sera présentée après avoir illustré les concepts sousjacents aux circuits asynchrones. Commençons par les protocoles de communication.

#### 1.2.3 Protocole de communication

Il existe deux méthodes particulièrement répandues pour implémenter un protocole de communication à poignée de main : un protocole à deux phases et un protocole à quatre phases. Étant donnée la nature binaire des signaux, les fronts montants (passage d'un niveau '0' logique à un niveau '1' logique) et les fronts descendants (passage d'un niveau '1' logique à un niveau '0' logique) sont les seuls événements qui peuvent avoir lieu sur les

signaux de requête et de reconnaissance. Naturellement, ces événements se succèdent dans le temps, c'est-à-dire qu'un front montant succédera toujours à un front descendant.

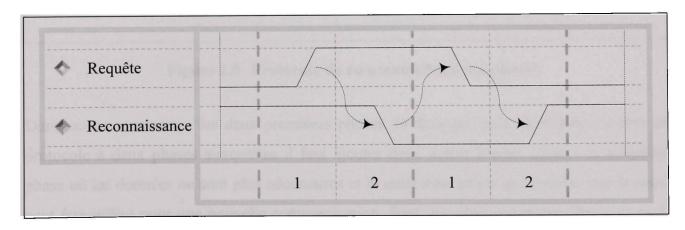

## Protocole à deux phases

Le protocole à deux phases est implémenté en considérant que toutes les transitions sont porteuses d'informations (Sparsø et Furber, 2001). Dans ce cas, une transition sur le signal de requête correspond à une donnée valide sur le canal de communication, alors qu'une transition sur le signal de reconnaissance correspond à une opération complétée. Un tel protocole est illustré à la figure 1.4. Il est à noter que la transition de reconnaissance est de polarité opposée (une requête sur front montant est reconnue par un front descendant sur le signal reconnaissance) au signal de requête pour une question d'optimisation du circuit en vue d'une réalisation.

Figure 1.4 Protocole de communication à 2 phases.

Ce protocole possède l'avantage de réduire au minimum les transitions sur les signaux. Cependant, il est très peu utilisé en pratique étant donné la complexité du circuit nécessaire à un protocole qui réagit de la même manière, peu importe la nature du front (front montant et front descendant).

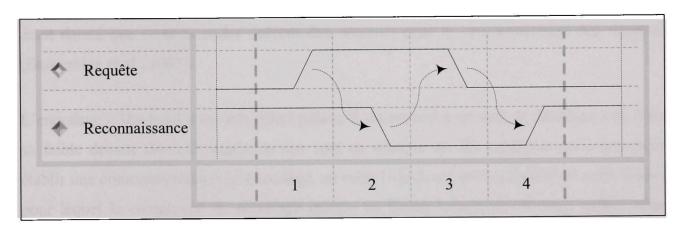

#### Protocole à quatre phases

Le protocole à quatre phases est une solution au problème du protocole à 2 phases : un seul type de transition est considéré pour chaque événement (fronts montants ou fronts descendants) (Sparsø et Furber, 2001). Cette approche diminue la bande passante du canal, mais assure la symétrie du circuit ce qui simplifie au maximum le circuit de détection des transitions. La figure 1.5 illustre un protocole à 4 phases.

Figure 1.5 Protocole de communication à 4 phases.

Dans ces circonstances, les deux premières phases du dialogue sont identiques à celles du protocole à deux phases auxquelles il faut ajouter deux autres phases soient : la troisième phase où les données ne sont plus nécessaires et la quatrième phase qui signifie que le canal peut être utilisé pour une nouvelle communication. Bref, les deux premières phases (1 et 2, figure 1.5) servent à l'opération et les deux dernières phases (3 et 4, figure 1.5) servent à la remise à zéro des signaux.

Pour la suite de cette thèse, seul le protocole à quatre phases sera utilisé, puisqu'il est le plus exploité et que sa symétrie entre les itérations successives simplifie grandement la réalisation du circuit de détection. Une fois le protocole choisit, il reste plus qu'à déterminer l'encodage des données.

#### 1.2.4 Encodage des données

L'encodage des données est essentiel pour les circuits asynchrones sur lesquels aucune hypothèse temporelle n'est faite. Dans ces circonstances, l'encodage fait référence, dans la totalité des cas, à un encodage incomplet avec un code m-de-n où m représente le nombre de codes utilisés sur une possibilité de n codes. Pour un encodage complet, où m = n, le taux d'efficacité est alors maximum (R=(m/n)=1). Cependant, cet encodage implique un décodage très complexe et il ne s'applique pas à la logique asynchrone sans hypothèses temporelles, étant donné que certains codes doivent être réservés pour la synchronisation des signaux. (Bainbridge et al., 2003).

L'encodage « Dual-rail » est très utilisé puisqu'il est associé à un coût de décodage nul, mais sa faible densité (R=0.5) augmente son coût en nombre de fils parallèles qu'il faut pour établir une communication. Cet encodage, un code 1-de-2, est un cas spécial du code 1-de-n pour lequel la complexité de décodage grimpe en flèche lorsque n > 4. Pour pallier cette difficulté, la solution est l'utilisation du code incomplet m-de-n par le jumelage de plusieurs codes simples (1-de-n) pour augmenter la densité du code. De cette façon, il est possible d'augmenter la densité du code sans trop influer sur la complexité de décodage. La solution optimale, performance par rapport au coût des ressources de communications, est atteinte par le jumelage de codes simples 1-de-n. Pour le reste de la thèse, seuls les codes simples 1-de-n seront considérés par souci d'efficacité.

Ce mécanisme de communication permet de rendre le système indépendant aux retards dans les circuits et dans les interconnexions. Cependant, cette synchronisation peut être simplifiée par certaines hypothèses temporelles qui définissent implicitement le mode de fonctionnement et qui permettent de classifier les circuits asynchrones.

Afin d'exposer les concepts sous-jacents aux circuits asynchrones, nous établirons, dans un premier temps, la classification de ces circuits asynchrones par leur mode de fonctionnement. Par la suite, nous résumerons le tout à l'aide d'une étude de cas.

#### 1.2.5 Modèle de circuits asynchrones

Avant d'aborder la classification des circuits, il convient de caractériser le mode de fonction et le type d'interaction du circuit avec l'environnement.

#### Mode de fonctionnement

Trois modes principaux se distinguent pour les circuits asynchrones :

- le mode fondamental,

- le mode rafale,

- le mode entrée/sortie.

Dans le mode fondamental, le circuit doit être initialement stable (signaux internes et externes). Dans cet état, l'environnement peut modifier un maximum d'une seule entrée et doit attendre que le circuit se stabilise avant de pouvoir enlever cette donnée ou la changer à nouveau. La faiblesse des travaux de Huffman (Huffman, 1964) et Unger (Unger, 1969) sur le mode fondamental est l'impossibilité pour le circuit d'informer l'environnement de la stabilité du système. L'approche utilisée pour contourner le problème est une hypothèse temporelle basée sur le retard le plus grand du circuit. En utilisant une approche de retards bornés, les circuits ainsi réalisés ressemblent fortement à des circuits synchrones.

Le mode rafale constitue une extension au mode fondamental au sens où plusieurs entrées et donc plusieurs sorties peuvent changer d'état entre deux retours à l'état stable. Le modèle de retard demeure toutefois borné.

Le mode entrée/sortie fonctionne sans hypothèse sur les signaux internes. Les signaux de sorties doivent refléter les changements des entrées. Malgré ceci, si la causalité entre les transitions d'entrées et les transitions de sorties sont assurées, les entrées peuvent changer avant que les signaux de sortie n'aient le temps de se stabiliser. Dans un tel paradigme, les circuits DI ainsi créés doivent être composés uniquement d'inverseurs et d'éléments C de

Muller (mémoire asynchrone) (Muller et Bartky, 1959). Bien que limités en fonctionnalité, de tels circuits, dits « insensibles aux retards », existent où l'élément C de Muller supporte les retards non bornés et au cœur de cette recherche. Cet élément sera analysé en profondeur dans les prochains chapitres.

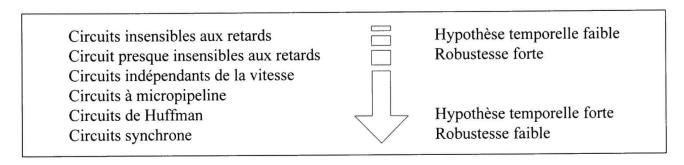

#### Classes de circuits asynchrones

La classification des circuits asynchrones, illustrée à la figure 1.6, qualifie le compromis robustesse/complexité propre à leur mode de fonctionnement (Vivet, 2001).

Figure 1.6 Classification des circuits.

Les circuits DI ne font aucune hypothèse temporelle. Ces circuits sont insensibles aux retards non bornés, et ce, aussi bien dans les portes logiques que ceux attribuables aux interconnexions (fils de communication). Ce comportement oblige d'informer explicitement le circuit récepteur que les données sont prêtes pour un traitement subséquent. Étant donné que la majorité des librairies modernes de porte logiques possèdent une seule sortie, ces portes s'avèrent inutilisables dans un tel paradigme où aucune hypothèse temporelle n'est faite. Naturellement, cette approche est très limitative en thème d'opérations réalisables puisque chaque élément devient très complexe.

Pour contourner ce problème, les circuits QDI acceptent une hypothèse temporelle où le retard d'un signal à plusieurs cibles (fourche) doit être égal. C'est-à-dire qu'une transition arrive aux différents points de destination en même temps. Cette hypothèse de fourches isochrones (« Isochronic fork ») permet l'utilisation de portes logiques à une seule sortie, puisqu'en supposant que les signaux se propagent de façon équivalente dans la fourche, il est

possible de reconnaître la fin du traitement à l'aide d'un seul signal. A.J. Martin a démontré que cette hypothèse est la plus faible qu'il est possible d'inclure pour permettre l'utilisation de porte logique à une seule sortie (Martin, 1993). Malgré tout, cette hypothèse demeure faible, car lorsque le temps de retard dans une fourche demeure inférieur au temps de traitement, cette contrainte est satisfaite (Martin, 1990).

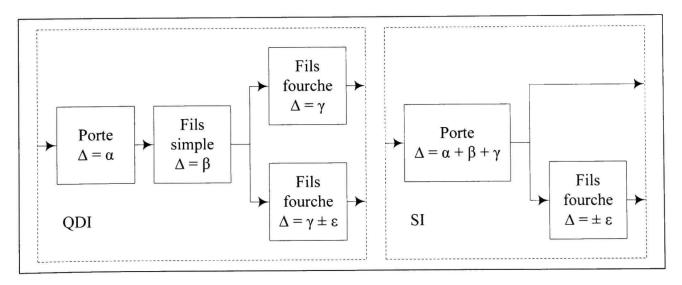

Les circuits indépendants de la vitesse, SI, (Speed Independent) utilisent l'hypothèse que les retards dans les fils sont négligeables pour des retards non bornés dans les portes logiques. En considérant l'intégration et la réduction à l'échelle, ce concept est de plus en plus difficile à vérifier intuitivement. Cependant, en étudiant les caractéristiques propres aux circuits QDI et SI, un consensus existe consistant à considérer ces modèles comme équivalents. La figure 1.7 illustre l'équivalence des modèles temporels SI et QDI (Hauck, 1995) où  $\alpha$ ,  $\beta$ ,  $\gamma$  et  $\epsilon$  représentent respectivement les retards dans les portes logiques, dans les fils simples et dans les fourches.

Figure 1.7 Équivalence des modèles temporels SI et QDI.

Naturellement, le modèle QDI est plus populaire que le modèle SI étant donné que le modèle QDI représente mieux le processus de fabrication actuel et qu'il y a beaucoup plus d'information disponible sur ce modèle temporel.

Les micro-pipelines introduits par Ivan Sutherland (Sutherland, 1989) sont des circuits où un chemin de données utilisant un modèle de retard borné (à l'image des circuits synchrones) est commandé par un protocole DI. La figure 1.8 illustre un micro-pipeline.

Figure 1.8 Micro-pipeline.

Le micro-pipeline ressemble au pipeline synchrone (figure 1.1) duquel le signal d'horloge a été remplacé par un protocole de communication à poignée de main où les éléments C de Muller sont représentés par des cercles avec l'étiquette « C ». Le micro-pipeline combine les avantages des circuits synchrones pour le chemin de données (outils disponibles) avec certains avantages de la logique asynchrone (disparition du signal d'horloge). Cependant, la conception au pire cas concernant la réalisation des retards nécessite une analyse temporelle, ce qui est superflu pour les modèles SI, QDI et DI.

Les circuits Huffman fonctionnent sous le principe de machine à états finis asynchrone (Huffman, 1964). Malgré l'élimination de l'horloge et l'utilisation de signaux de contrôle locaux s'apparentant à des horloges locales, ils sont pratiquement identiques aux circuits synchrones. Ces circuits sont sujets à des suppositions temporelles qui sont du même ordre que celles des circuits synchrones. Ainsi, ils ont tous les désavantages de la logique asynchrones sans les avantages. De plus, une erreur de conception sur un élément de retard (retard trop court) rend le circuit totalement non fonctionnel.

### 1.2.6 Étude de cas

La cellule de base NCL s'apparente à l'élément C de Muller, elle est asynchrone, mais elle possède la contrainte supplémentaire d'avoir des retards similaires pour chacune de ses entrées (Isochronic folk) (Bandapati, Smith et Choi, 2003). Cette limitation caractérise les cellules NCL. Une fois regroupées, de telles cellules forment des circuits QDI. Cette hypothèse permet de faire la reconnaissance d'une seule sortie au lieu d'avoir à considérer toutes les sorties.

Un circuit purement DI est, par définition, semi-modulaire. La semi-modularité se définit comme l'impossibilité de changer un état interne avant que cet état se stabilise. L'approximation QDI peut provoquer des violations de la semi-modularité (Taubin, Fant et McCardle, 2002). Cette violation se matérialise par l'apparition d'aléas sur une ou des sorties. Évidemment, ce comportement n'est pas souhaité en logique asynchrone. Cette violation de la semi-modularité survient lorsqu'une sortie possède des liens orphelins (non observables) et qu'elle passe de l'état « activé » à l'état « stable ». Ces liens orphelins n'ont pas de signaux de reconnaissance en sortie (aucune observation) pour un ensemble de signaux d'entrées. Heureusement, la détection d'aléas pour des circuits basés sur des cellules NCL se résume à la détection des chemins orphelins.

La méthodologie NCL permet de formuler des expressions symboliquement complètes contrairement à ce qu'offre la logique booléenne synchrone pour les conceptions asynchrones (Fant et Brandt, 1996). L'horloge globale est remplacée par le contrôle NULL ajouté aux données ('0' et '1') de la table de vérité. Les trois états sont normalement représentés sur 2 fils (dual rail). Ce contrôle permet de créer des vagues successives de données et de contrôle (NULL). Les vagues créées servent à transmettre puis effacer les données pour éviter les collisions et informer la cible de l'arrivée d'une nouvelle donnée.

Les implémentations statiques, semi-statiques et dynamiques de ces cellules en portes CMOS avec seuil et hystérésis simple (Sobelman et Fant, 1998) sont réalisées par des portes du type n-de-m qui doivent avoir « n » entrées avec des données valides « DATA » (autre que

NULL) pour que la sortie actualise sa sortie et qu'elle passe à « DATA ». La valeur de la donnée (« DATA ») dépend naturellement des entrées et de la fonction logique à réaliser. L'hystérésis est, quant à elle, réalisée en permettant à la sortie de retourner à « NULL » uniquement lorsque toutes les entrées redeviennent également « NULL».

Fort d'une bibliothèque de portes logiques, il reste à concevoir des circuits. Malheureusement, la logique asynchrone souffre d'une carence en outil de conception. Les modèles de description matérielle, HDL, (Hardware Description Language) créés dans une optique de conception synchrone sont adaptables à la logique asynchrone, mais beaucoup d'efforts sont nécessaires pour effectuer la transition pour des résultats souvent décevants (Ligthart et al., 2000). Utiliser des outils synchrones existants favorise un apprentissage rapide pour des utilisateurs matures et performants.

L'utilisation du VHDL/Verilog permet d'utiliser le même code pour faire la vérification et la synthèse (Smith et Ligthart, 2001). L'ajout des bibliothèques, pour convertir le code VHDL standard en 3NCL (NULL (N), 1 (T), 0 (F)) jusqu'en 2NCL (dual rail), offre la possibilité d'effectuer la synthèse avec des outils standards.

Dans le but d'automatiser encore plus le processus de création asynchrone, un analyseur de cycle est nécessaire pour la logique NCL (Masteller et Sorenson, 2003). Le cycle est l'unité fondamentale pour la sauvegarde d'information. La méthode consiste à parcourir le fichier contenant la liste des connexions (« netlist ») du circuit pour en extraire les PSN (primary singular node). La méthode permet d'identifier :

- le nombre de portes NCL,

- le nombre de registres,

- le nombre de cycles,

- le nombre de registres de test et

- le temps pris pour les opérations.

Une décomposition adéquate permet l'automatisation du processus de création.

La solution proposée est intéressante en plus d'offrir un bon potentiel. Cependant, les outils et l'environnement de réalisation sont protégés par des droits de propriété intellectuelle, dont des brevets au Canada et aux États-Unis. L'achat de licence est possible. Cependant, rares sont les concepteurs qui vont payer les frais associés à la migration d'une méthodologie synchrone mature vers une méthodologie en émergence avec peu ou pas de façon de réutiliser tout ce qui a été fait. Une solution moins draconienne est celle de la logique GALS présentée à la section suivante.

#### 1.3 GALS

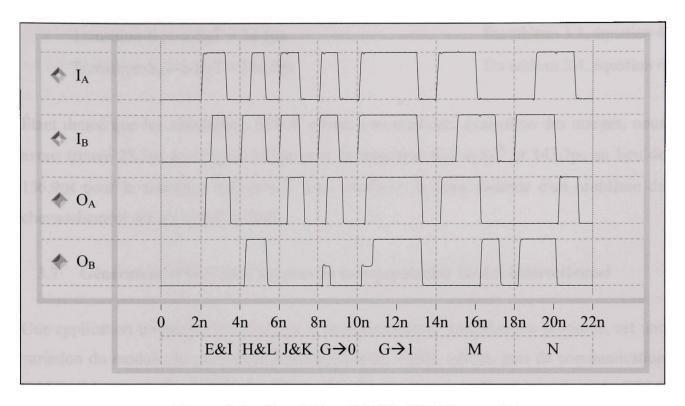

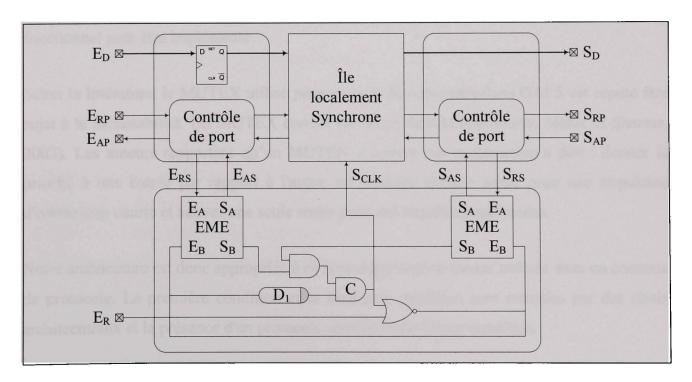

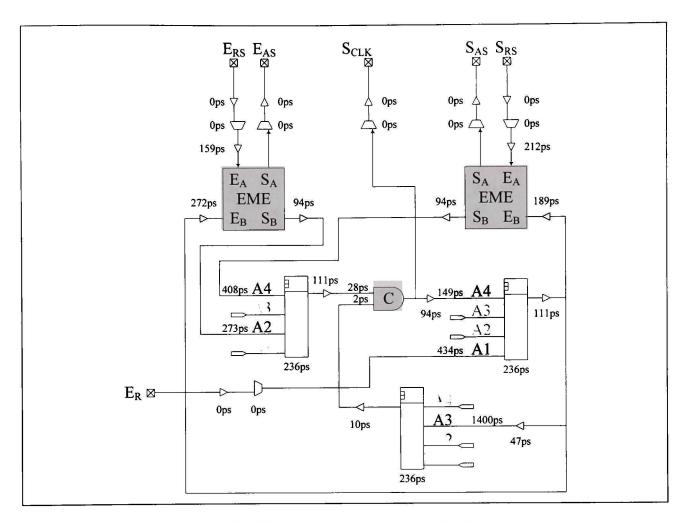

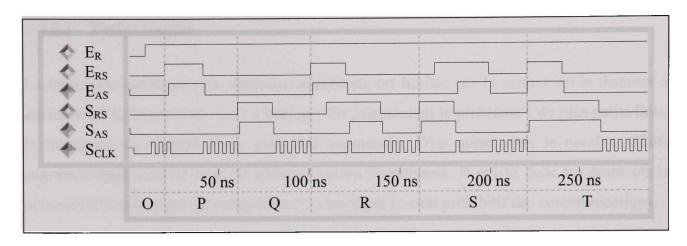

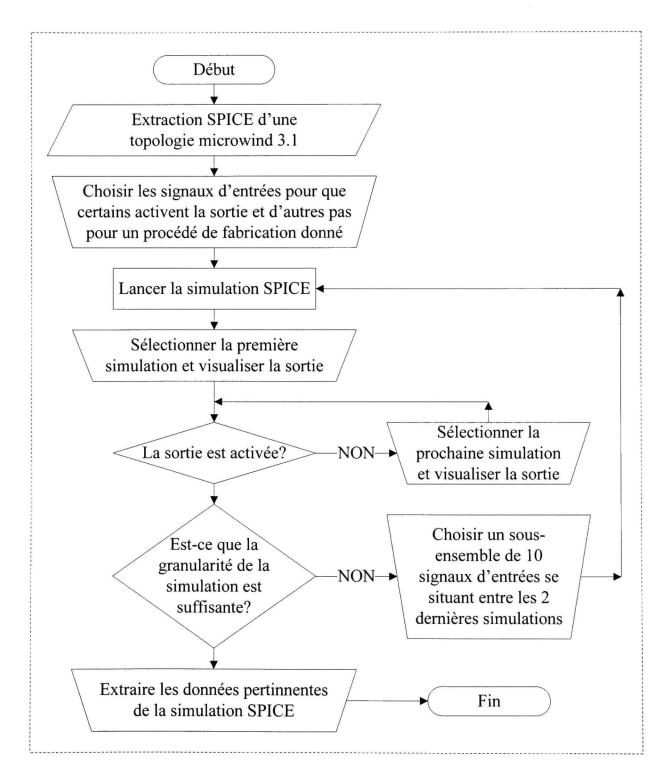

Dans la mesure où la synchronisation globale devient un coût trop élevé à payer pour les conceptions numériques de hautes fréquences ou de grandes surfaces pour les nouvelles technologies et que l'approche asynchrone souffre de graves carences en outils de développement, l'ITRS propose le retour de la logique asynchrone insérée dans le concept GALS. Un paradigme où les communications sont assurées par des liens asynchrones reliant des modules synchrones de tailles restreintes (petites à moyennes) cadencés à l'aide d'une horloge locale.