# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE M.Ing.

PAR

Tennessee CARMEL-VEILLEUX

ADAPTATION MULTICOEUR D'UN NOYAU DE PARTITIONNEMENT ROBUSTE VERS L'ARCHITECTURE POWERPC

MONTRÉAL, LE 7 SEPTEMBRE 2011

© Tous droits réservés, Tennessee Carmel-Veilleux, 2011

# PRÉSENTATION DU JURY

# CE MÉMOIRE A ÉTÉ ÉVALUÉ

### PAR UN JURY COMPOSÉ DE :

M Jean-François Boland, directeur de mémoire Département de génie électrique, ÉTS

M Guy Bois, codirecteur Département de génie informatique et logiciel, École Polytechnique

M Claude Thibeault, président du jury Département de génie électrique, ÉTS

M Bruno De Kelper, membre du jury Département de génie électrique, ÉTS

M Daniel Roy, examinateur externe CMC Électronique inc.

# IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 26 AOÛT 2011

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### REMERCIEMENTS

En premier lieu, j'aimerais remercier mon directeur Jean-François Boland et mon codirecteur Guy Bois, qui m'ont donné une grande latitude dans la réalisation de mon projet de maîtrise. J'ai aussi apprécié leur support tout au long de ma maîtrise et en particulier après la naissance de mon fils Léon, arrivé au milieu de mon cheminement.

J'aimerais aussi remercier l'École de technologie supérieure (ÉTS), le Fonds québécois de recherche sur la nature et les technologies (FQRNT) et le Regroupement stratégique en microélectronique du Québec (ReSMiQ) pour leur support financier qui m'a permis de réaliser mes travaux.

Enfin, je voudrais remercier tout particulièrement ma conjointe Melissa. Ses encouragements et son support ont été instrumentaux à la réussite de mes travaux.

### ADAPTATION MULTICOEUR D'UN NOYAU DE PARTITIONNEMENT ROBUSTE VERS L'ARCHITECTURE POWERPC

#### Tennessee CARMEL-VEILLEUX

# **RÉSUMÉ**

L'utilisation de plus en plus commune de l'architecture d'avionique modulaire intégrée (IMA) a permis de réduire le poids, la taille et l'encombrement des systèmes avioniques en consolidant l'exécution logicielle de plusieurs fonctions sur un même processeur. En même temps que l'adoption accélérée de l'architecture IMA, les microprocesseurs multicoeurs ont gagné en popularité en raison de la stagnation des fréquences d'horloge des processeurs monocoeurs. Les processeurs multicoeurs promettent d'augmenter l'intégration de fonctions logicielles, mais ces derniers ne sont toujours pas acceptés en avionique, pour des raisons de complexité qui affectent la sûreté.

La technologie principale permettant l'utilisation de l'architecture IMA est le noyau de partitionnement robuste. Un noyau de partitionnement robuste permet d'isoler les applications indépendantes d'un système IMA pour prévenir la propagation des fautes. Cette isolation est réalisée par partitionnement spatial et temporel robustes. Dans ce domaine, il n'existe actuellement aucun système d'exploitation supportant les recherches sur l'évaluation de sûreté des processeurs multicoeurs.

Nous proposons dans ce mémoire d'adapter un noyau de partitionnement robuste existant, afin qu'il supporte le déploiement de partitions en parallèle sur plusieurs coeurs d'un processeur multicoeur. Nous avons analysé l'architecture d'un noyau existant, nommé XtratuM, puis nous l'avons adapté à un modèle de partitionnement robuste multicoeur. Nous avons ensuite réalisé une implémentation de cette adaptation sur un processeur PowerPC multicoeur de la famille MPC8641 de Freescale. Le prototype résultant est nommé XtratuM-PPC. Nous présentons enfin une étude de cas de l'utilisation de XtratuM-PPC avec un plan d'exécution multicoeur.

Lors des phases d'adaptation et de réalisation, nous avons identifié un ensemble de problèmes techniques affectant la sûreté des noyaux de partitionnement robuste sur les processeurs multicoeurs. Ces problèmes mettent en relief la complexité d'implémentation de ce type de système logiciel.

Nos travaux nous permettent de conclure que l'adaptation d'un noyau de partitionnement robuste monocoeur existant à une architecture multicoeur est possible. Cependant, les problèmes de sûreté qui apparaissent avec les processeurs multicoeurs demeurent non résolus. Notre prototype de noyau de partitionnement robuste multicoeur est un point de départ pour la résolution de ces problèmes dans un environnement réel.

**Mots-clés :** Partitionnement, processeurs multicoeurs, systèmes d'exploitation, systèmes embarqués, avionique, IMA

### ADAPTATION MULTICOEUR D'UN NOYAU DE PARTITIONNEMENT ROBUSTE VERS L'ARCHITECTURE POWERPC

Tennessee CARMEL-VEILLEUX

#### **ABSTRACT**

Increasing use of the integrated modular avionics (IMA) architecture has helped reduce the size, weight and power consumption of avionics systems by consolidating multiple software functions on a same processor. At the same time as the accelerated adoption rate of IMA architectures, multi-core microprocessors have gained popularity due to stagnating performances of single-core offerings. Multi-core processors promise to increase software functions integration, but they are still not widely accepted in avionics, for reasons of complexity which affect safety.

The technological underpinning of the IMA architecture is the robust partitioning kernel. A robust partitioning kernel maintains an isolation between independant applications to prevent the propagation of faults within the system. This isolation is achieved by robust time and space partitioning. Unfortunately, there are no multicore-capable robust partitioning kernels currently available to support research in using multicore processors in IMA.

In this master's thesis, we propose to adaptat an existing robust partitioning kernel, so that it supports the deployment of partitions on several cores of a multi-core processor. To achieve this goal, we analyzed the existing XtratuM partitioning kernel and adapted it to support a multi-core robust partitioning model. We then implemented this adaptation on the Freescale MPC8641 multi-core PowerPC processor. The resulting prototype is named XtratuM-PPC. Finally, we present a case study using a multi-core execution plan on XtratuM-PPC.

During the adaptation and implementation phases, we identified a set of technical problems which affect the safety of robust partitioning kernels on multi-core processors. These problems highlight the implementation complexity of implementation of multi-core robust partitioning kernels.

Our work allows us to conclude that it is indeed possible to adapt a robust partitioning kernel from a single-core to a multi-core architecture. However, the safety-related problems that appeared due to the use of multi-core processors remain unresolved. Our multi-core robust partitioning kernel prototype is thus a starting point for the resolution of these problems in a real-world environment.

**Keywords:** Partitionning, multicore processors, operating systems, embedded systems, avionics, IMA

# TABLE DES MATIÈRES

|       |          | P                                                          | age |

|-------|----------|------------------------------------------------------------|-----|

| INTRO | DUCTIO   | ON                                                         | 1   |

| CHAPI | TDF 1    | PROBLÉMATIQUE                                              | 7   |

| 1.1   |          | me de recherche                                            |     |

| 1.1   |          | ifs                                                        |     |

| 1.3   | -        | outions                                                    |     |

| 1.4   |          | nèses et suppositions                                      |     |

| СПУДІ | TRE 2    | REVUE DE LA LITTÉRATURE ET FONDEMENTS                      | 11  |

| 2.1   |          | REVUE DE LA LITTERATURE ET PONDEMENTS                      |     |

| 2.1   |          | nes embarqués avioniques                                   |     |

| 2.2   | 2.2.1    | Fonctions avioniques                                       |     |

|       | 2.2.2    | Sûreté des systèmes avioniques                             |     |

|       | 2.2.2    | 2.2.2.1 Fiabilité des systèmes avioniques                  |     |

|       |          | 2.2.2.2 Lignes directrices de certification                |     |

|       |          | 2.2.2.3 Directive DO-178B visant le développement logiciel |     |

|       | 2.2.3    | Architecture des systèmes embarqués avioniques             |     |

|       |          | 2.2.3.1 L'avionique fédérée                                |     |

|       |          | 2.2.3.2 L'avionique modulaire intégrée                     |     |

| 2.3   | Partitio | onnement robuste                                           |     |

|       | 2.3.1    | Définition du partitionnement robuste                      | 19  |

|       | 2.3.2    | Partitionnement spatial                                    | 20  |

|       | 2.3.3    | Partitionnement temporel                                   |     |

|       | 2.3.4    | Le partitionnement robuste selon la norme ARINC-653        | 22  |

|       | 2.3.5    | Interdépendances entre partitionnement spatial et temporel |     |

| 2.4   |          | des de partitionnement spatial                             |     |

| 2.5   |          | des de partitionnement temporel                            |     |

| 2.6   |          | d'un noyau de partitionnement robuste à adapter            |     |

| 2.7   | Process  | seurs multicoeurs                                          | 33  |

| CHAPI | TRE 3    | ARCHITECTURE ET IMPLÉMENTATION DU NOYAU XTRATUM            |     |

|       |          | SUR PROCESSEURS LEON                                       |     |

| 3.1   |          |                                                            |     |

| 3.2   |          | que de XtratuM                                             |     |

| 3.3   |          | ecture de XtratuM                                          |     |

| 3.4   |          | e configuration du système                                 |     |

| 3.5   |          | ement du système partitionné                               |     |

|       | 3.5.1    | Configuration et construction du novau                     | 42  |

|      | 3.5.2    | Génération de la table de configuration binaire         | 44 |

|------|----------|---------------------------------------------------------|----|

|      | 3.5.3    | Construction des partitions                             |    |

|      | 3.5.4    | Construction de l'image de déploiement                  | 44 |

|      | 3.5.5    | Déploiement sur la carte matérielle                     | 45 |

| 3.6  | Service  | s de base du noyau                                      | 45 |

|      | 3.6.1    | Gestion de l'horloge                                    | 46 |

|      | 3.6.2    | Gestion des interruptions et exceptions                 | 48 |

|      | 3.6.3    | Virtualisation des opérations superviseur               |    |

| 3.7  | Mécani   | sme d'hyperappels                                       | 52 |

| 3.8  | Partitio | nnement temporel                                        | 58 |

| 3.9  | Partitio | nnement spatial                                         | 61 |

| 3.10 | Commu    | unication inter-partitions                              | 68 |

| 3.11 | Monite   | ur de santé du système                                  | 70 |

| 3.12 | Récapit  | ulation                                                 | 73 |

|      |          |                                                         |    |

|      |          | ANALYSE DE L'ADAPTATION MULTICOEUR DE XTRATUM           |    |

| 4.1  |          |                                                         |    |

| 4.2  |          | t existant pour traitement parallèle                    |    |

| 4.3  | Méthod   | lologie d'adaptation                                    |    |

|      | 4.3.1    | Hypothèses et suppositions                              |    |

|      | 4.3.2    | Identification des besoins                              |    |

| 4.4  |          | configuration du système                                |    |

| 4.5  | Déploie  | ement du système partitionné                            | 82 |

| 4.6  | Service  | s de base du noyau                                      | 82 |

|      | 4.6.1    | Duplication du fil d'exécution du noyau                 | 83 |

|      | 4.6.2    | Démarrage du noyau                                      | 84 |

|      | 4.6.3    | Gestion de l'horloge                                    | 87 |

|      | 4.6.4    | Gestion des interruptions et exceptions                 | 89 |

| 4.7  | Mécani   | sme d'hyperappels                                       | 90 |

| 4.8  | Partitio | nnement temporel                                        | 91 |

|      | 4.8.1    | Plans d'exécution multicoeur                            | 92 |

|      |          | 4.8.1.1 Modèle asymétrique (AMP)                        | 93 |

|      |          | 4.8.1.2 Modèle symétrique (SMP)                         | 94 |

|      |          | 4.8.1.3 Modèle hybride                                  | 95 |

|      | 4.8.2    | Ordonnancement multicoeur                               | 96 |

|      | 4.8.3    | Hyperappels de support multicoeur                       | 98 |

|      | 4.8.4    | Problèmes liés au partitionnement temporel multicoeur   |    |

|      |          | 4.8.4.1 Analyse du délai maximal d'exécution des tâches |    |

|      |          | 4.8.4.2 Synchronisation temporelle des ordonnanceurs    |    |

|      |          | 4.8.4.3 Gestion des fautes                              |    |

|      |          | 4.8.4.4 Modèles de programmation parallèle              |    |

| 4.9  | Partitio | nnement spatial                                         |    |

|      | 4.9.1    | Exploitation du MMU                                     |    |

|      |          |                                                         |    |

|       | 4.9.2   | Adaptation multicoeur du modèle de partitionnement spatial  | 108 |

|-------|---------|-------------------------------------------------------------|-----|

|       | 4.9.3   | Protection des données partagées                            | 113 |

|       | 4.9.4   | Problèmes liés au partitionnement spatial multicoeur        | 113 |

| 4.10  | Comm    | unication inter-partitions                                  | 116 |

| 4.11  | Monite  | eur de santé du système                                     | 116 |

| 4.12  | Récapi  | tulation                                                    | 116 |

| CIIAD | TTRE 5  | RÉALISATION DE XTRATUM-PPC SUR POWERPC                      | 100 |

| 5.1   |         |                                                             |     |

| 5.1   |         | orme cible                                                  |     |

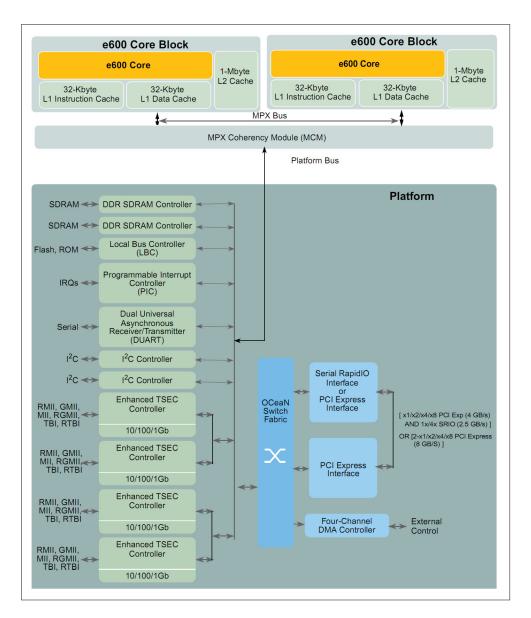

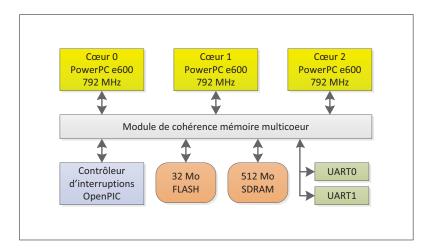

| 3.2   | 5.2.1   | Architecture du PowerPC MPC8641D.                           |     |

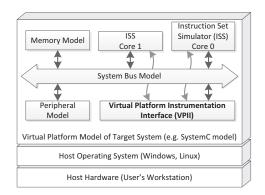

|       | 5.2.1   | Plateforme virtuelle                                        |     |

|       | 3.2.2   | 5.2.2.1 Motivations                                         |     |

|       |         | 5.2.2.2 Choix de la plateforme virtuelle                    |     |

|       | 5.2.3   | Configuration de la plateforme cible sous Simics            |     |

|       | 5.2.4   | Chaîne de compilation                                       |     |

| 5.3   |         | rage du système                                             |     |

| 5.5   | 5.3.1   | Vecteurs d'exceptions                                       |     |

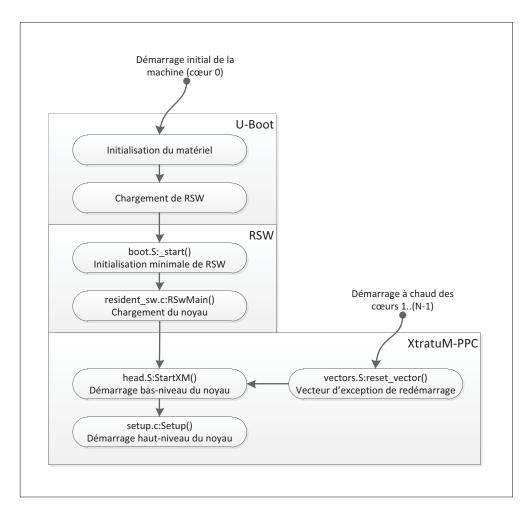

|       | 5.3.2   | Procédure de démarrage                                      |     |

|       | 5.3.3   | Identification des coeurs                                   |     |

|       | 5.3.4   | Problèmes potentiels                                        |     |

| 5.4   |         | n du temps                                                  |     |

|       | 5.4.1   | Horloges locales.                                           |     |

|       | 5.4.2   | Minuteries                                                  |     |

|       | 5.4.3   | Synchronisation des horloges locales                        |     |

|       | 5.4.4   | Problèmes potentiels                                        |     |

| 5.5   | Gestion | n des interruptions                                         |     |

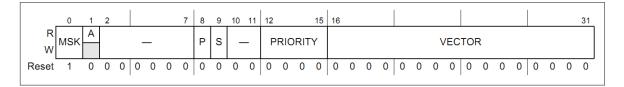

|       | 5.5.1   | Pilote du contrôleur d'interruptions OpenPIC                |     |

|       | 5.5.2   | Gestionnaires d'interruptions et d'exceptions               |     |

|       | 5.5.3   | Problèmes potentiels                                        | 148 |

| 5.6   | Synchr  | onisation multicoeur                                        | 150 |

|       | 5.6.1   | Opérations atomiques                                        | 150 |

|       | 5.6.2   | Verrous                                                     | 155 |

|       | 5.6.3   | Barrières                                                   | 155 |

|       | 5.6.4   | Problèmes                                                   | 157 |

| 5.7   | Mécan   | isme d'hyperappels                                          | 160 |

| 5.8   | Exploi  | tation du MMU                                               | 161 |

|       | 5.8.1   | Application du modèle de partitionnement spatial sur le MMU | 163 |

|       | 5.8.2   | Caches d'entrées des TLB                                    | 170 |

|       | 5.8.3   | Problèmes                                                   |     |

| 5.9   | _       | ement de contexte de partitions                             |     |

|       | 5.9.1   | Appel de l'ordonnanceur                                     |     |

|       | 5.9.2   | Composante générique du changement de contexte              | 177 |

|       | 5.9.3   | Implémentation du changement de contexte principal sur e600 | 179 |

|-------|---------|-------------------------------------------------------------|-----|

|       | 5.9.4   | Gestion des registres spécialisés                           | 181 |

| 5.10  | Mise à  | l'essai                                                     | 183 |

|       | 5.10.1  | Objectifs                                                   | 183 |

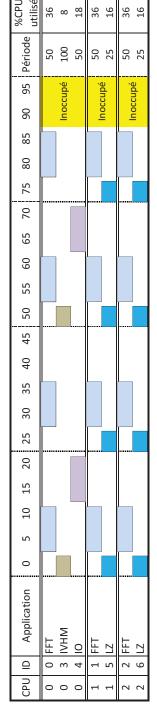

|       | 5.10.2  | Présentation de l'étude de cas                              | 184 |

|       | 5.10.3  | Méthodologie de mesure                                      | 187 |

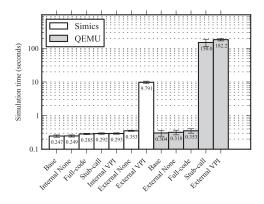

|       | 5.10.4  | Résultats                                                   | 189 |

|       |         | Conclusions                                                 |     |

| 5.11  | Récapit | tulation                                                    | 194 |

| CONC  | LUSION  |                                                             | 199 |

| ANNE  | XE I TA | ABLEAUX ET FIGURES SUPPLÉMENTAIRES                          | 203 |

| ANNE  | XE II A | ARTICLE DE CONFÉRENCE SUR LA MÉTHODE VPI                    | 209 |

| LISTE | DE RÉF  | ÉRENCES BIBLIOGRAPHIQUES                                    | 217 |

# LISTE DES TABLEAUX

|              | Page                                                                  |

|--------------|-----------------------------------------------------------------------|

| Tableau 2.1  | Paramètres de l'exemple d'un plan d'exécution à deux partitions 22    |

| Tableau 3.1  | Méthodes de virtualisation des fonctions privilégiées                 |

| Tableau 3.2  | Fonctions de base du mécanisme de pilote générique de XtratuM 57      |

| Tableau 3.3  | Liste des actions du moniteur de santé du système de XtratuM          |

| Tableau 4.1  | Types de zones de mémoire virtuelle dans XtratuM-PPC                  |

| Tableau 4.2  | Résumé des problèmes de l'adaptation architecturale de XtratuM 119    |

| Tableau 5.1  | Outils utilisés pour la réalisation XtratuM-PPC                       |

| Tableau 5.2  | Liste des huit premiers vecteurs d'exceptions du PowerPC              |

| Tableau 5.3  | Bits de configuration d'accès mémoire du MMU du coeur e600 168        |

| Tableau 5.4  | Configuration d'accès des zones de mémoire virtuelle                  |

| Tableau 5.5  | Registres sauvegardés lors du changement de contexte sur e600 180     |

| Tableau 5.6  | Sommaire des applications de l'étude de cas                           |

| Tableau 5.7  | Ressources de mémoire allouées aux applications                       |

| Tableau 5.8  | Ressources temporelles allouées aux applications                      |

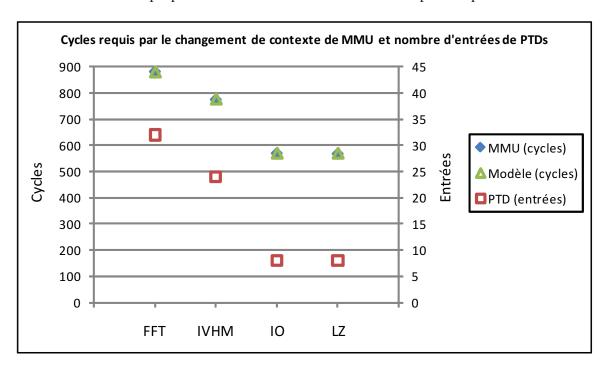

| Tableau 5.9  | Résultats des mesures de changement de contexte                       |

| Tableau 5.10 | Résultats des mesures de durée de fenêtres d'activation               |

| Tableau 5.11 | Résumé des problèmes trouvés lors de la réalisation de XtratuM-PPC196 |

# LISTE DES FIGURES

|             |                                                                  | Page |

|-------------|------------------------------------------------------------------|------|

| Figure 2.1  | Exemple schématique d'une architecture fédérée                   | 16   |

| Figure 2.2  | Exemple schématique d'une architecture IMA                       | 17   |

| Figure 2.3  | Exemple d'un plan d'exécution à deux partitions                  | 22   |

| Figure 2.4  | Modes de diffusion de messages inter-partitions                  | 29   |

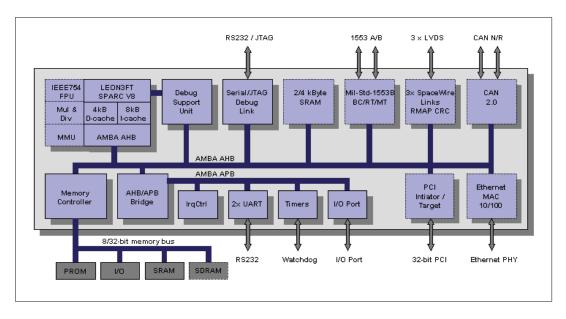

| Figure 3.1  | Schéma-bloc typique d'un processeur LEON3                        | 37   |

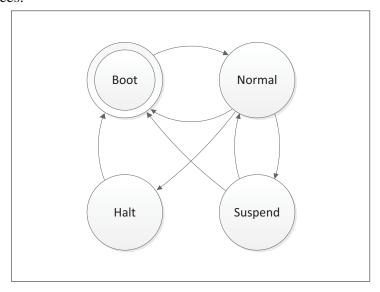

| Figure 3.2  | Diagramme des états possibles pour une partition dans XtratuM    | 39   |

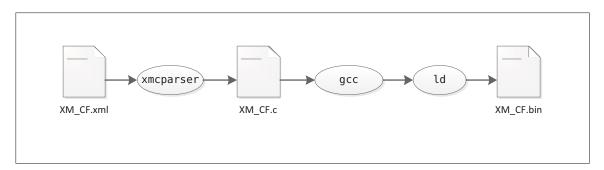

| Figure 3.3  | Flot de compilation de la table de configuration de XtratuM      | 41   |

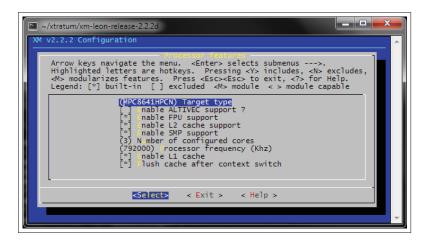

| Figure 3.4  | Fenêtre du script de configuration du noyau XtratuM              | 43   |

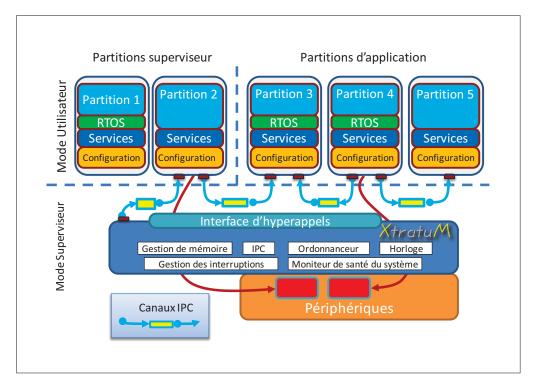

| Figure 3.5  | Schéma de l'architecture de XtratuM incluant les services        | 46   |

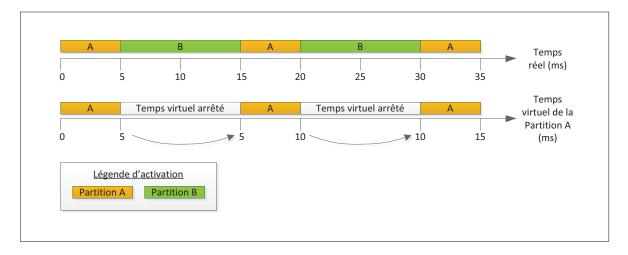

| Figure 3.6  | Illustration de la progression du temps réel et du temps virtuel | 47   |

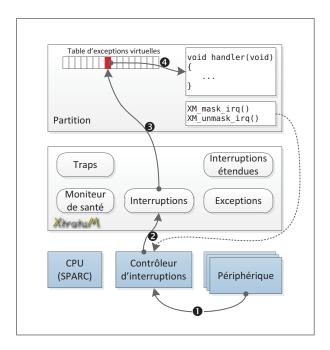

| Figure 3.7  | Cheminement de traitement d'une interruption de périphérique     | 50   |

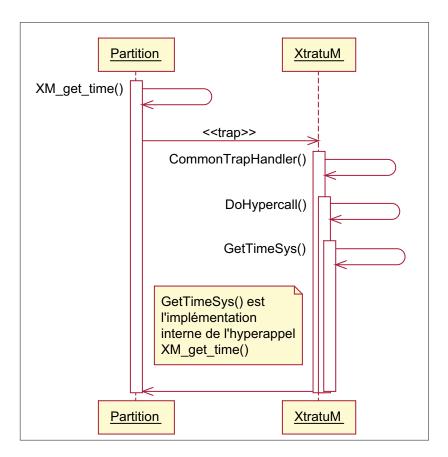

| Figure 3.8  | Diagramme de séquence pour l'hyperappel XM_get_time()            | 54   |

| Figure 3.9  | Code compilé de la routine d'hyperappel XM_get_time()            | 55   |

| Figure 3.10 | Compensation du WCET de l'hyperappel le plus coûteux             | 56   |

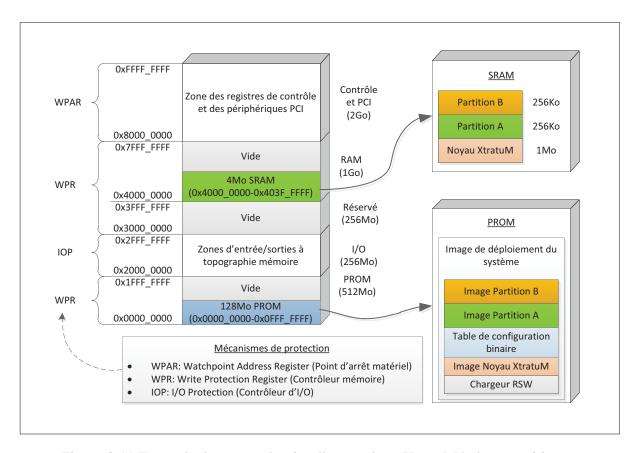

| Figure 3.11 | Exemple de carte mémoire d'un système XtratuM à deux partitions  | 64   |

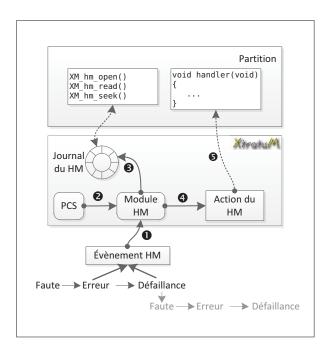

| Figure 3.12 | Cheminement d'une faute dans le moniteur de santé du système     | 72   |

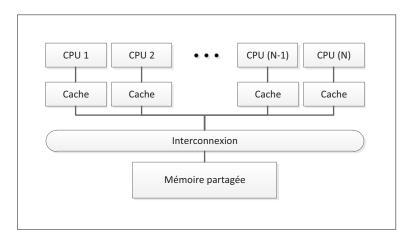

| Figure 4.1  | Digramme schématique d'un système parallèle SMP UMA              | 79   |

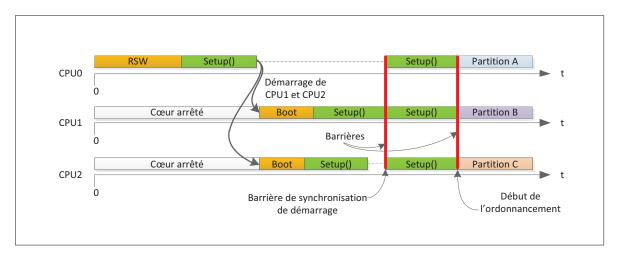

| Figure 4.2  | Chronogramme de la séquence de démarrage sur 3 coeurs            | 87   |

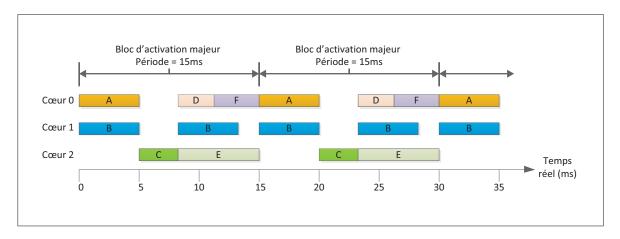

| Figure 4.3  | Plan d'exécution asymétrique (AMP) sur trois coeurs              | 93   |

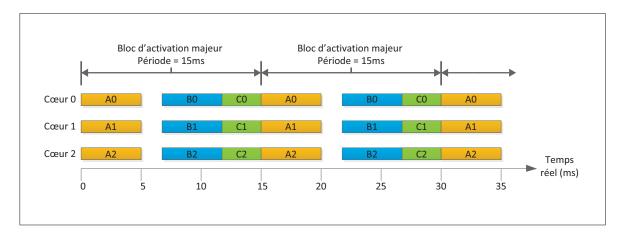

| Figure 4.4  | Plan d'exécution symétrique (SMP) sur trois coeurs               | 95   |

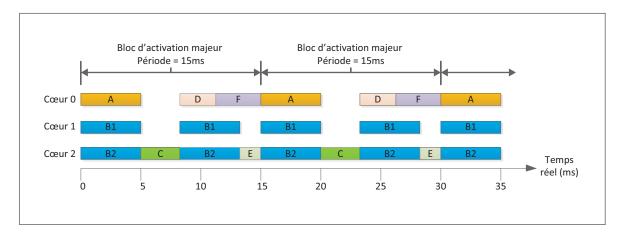

| Figure 4.5  | Plan d'exécution hybride sur trois coeurs                        | 96   |

| Figure 4.6  | Temps morts causé par le décalage temporel                            | 102 |

|-------------|-----------------------------------------------------------------------|-----|

| Figure 4.7  | Exemple de gestion d'une faute dans un groupe de partitions SMP       | 104 |

| Figure 4.8  | Exemple d'allocation de zones de mémoire virtuelle                    | 112 |

| Figure 5.1  | Diagramme-bloc du MPC8641D                                            | 125 |

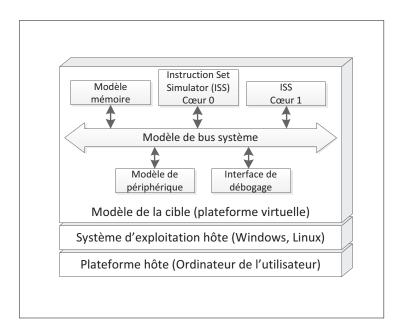

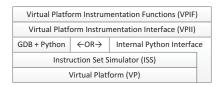

| Figure 5.2  | Couches conceptuelles d'une plateforme virtuelle                      | 127 |

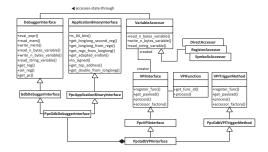

| Figure 5.3  | Diagramme-bloc du modèle de simulation utilisé                        | 130 |

| Figure 5.4  | Cheminement du démarrage du noyau XtratuM                             | 136 |

| Figure 5.5  | Registre de destination et de priorité d'une interruption             | 144 |

| Figure 5.6  | Cheminement de la translation d'une adresse dans le MMU               | 166 |

| Figure 5.7  | Illustration de la compression de la cache d'entrées des TLB de pages | 172 |

| Figure 5.8  | Illustration de l'utilisation du bloc de continuation                 | 182 |

| Figure 5.9  | Flux de données entre les partitions de l'étude de cas                | 187 |

| Figure 5.10 | Délai de changement de contexte du MMU                                | 191 |

# LISTE DES EXTRAITS DE CODE

|             |                                                                     | Page  |

|-------------|---------------------------------------------------------------------|-------|

| Extrait 3.1 | Code source de l'hyperappel XM_create_queuing_port()                | 57    |

| Extrait 3.2 | Exemple de définition du plan d'activation dans le PCS              | 58    |

| Extrait 5.1 | Exemple d'utilisation d'un verrou d'exclusion mutuelle              | . 151 |

| Extrait 5.2 | Implémentation de l'opération atomique XMAtomicIncReturn            | . 154 |

| Extrait 5.3 | Implémentation des verrous multicoeurs                              | . 156 |

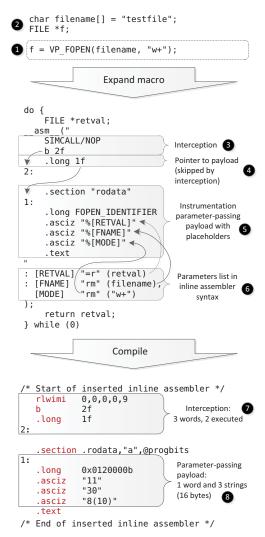

| Extrait 5.4 | Exemples de code employant l'appel système                          | . 163 |

| Extrait 5.5 | Structure de données d'une entrée dans les caches d'entrées des TLB | . 172 |

| Extrait 5.6 | Composante générique du changement de contexte                      | . 178 |

# LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

AECC Airlines Electronic Engineering Committee

AMP Asymetrical Multiprocessing

APEX ARINC-653 Application Executive

ARINC Aeronautical Radio Incorporated

DMA Direct Memory Access

ESA European Space Agency

FAA Federal Aviation Administration

FBW Fly-by-wire

FIFO First-In First-Out

FMS Flight management system

FPU Floating-point unit

GPL GNU Public License

IEEE Institute of Electrical and Electronics Engineers

IPC Inter-partition communication

ISS Instruction Set Simulator

IVHM Integrated Vehicle Health Management

JTAG IEEE Joint Test Action Group

MMU Memory Management Unit

MPU Memory protection unit

NASA National Aeronautics and Space Administration

NUMA Non-uniform Memory Access

OS Operating System

PCI Peripheral Component Interconnect

PCS Plan de configuration du système

RSW Resident Software

RTCA Radio Technical Commission for Aeronautics

SMP Symetrical Multiprocessing

TBC Timebase counter

TLB Translation Lookaside Buffer

VP Virtual Platform

VPI Virtual Platform Instrumentation

WCET Worst case execution time

#### INTRODUCTION

Depuis le début des années 2000, un nouveau modèle d'intégration avionique a pris son essor dans les derniers modèles des grands avionneurs. Le modèle d'avionique modulaire intégrée [68] (de l'anglais « Integrated Modular Avionics » ou IMA) propose de consolider et d'intégrer les fonctions avioniques des appareils dans un nombre réduit de boîtiers en exécutant plusieurs applications différentes sur un même microprocesseur.

Cette consolidation de plusieurs applications avioniques sur un microprocesseur va à l'encontre de la pratique traditionnelle. Avec le modèle d'avionique fédérée traditionnel, un ordinateur embarqué avec ses fonctions associées (alimentations, mémoires, interfaces) est dédié à chaque application avionique. Par exemple, le système de gestion de vol est réalisé avec un ordinateur complètement indépendant de celui du contrôle de climatisation de la cabine. Le modèle fédéré limite la complexité, ce qui simplifie la certification de sûreté. Cependant, l'augmentation du poids, de l'espace et de l'énergie consommée qui découle de la duplication des ordinateurs est trop élevée dans un contexte d'augmentation du nombre de fonctions et de diminution des coûts d'exploitation des avions. Le modèle IMA est de plus en plus employé dans les appareils développés récemment, dont le Boeing 787 Dreamliner et l'Airbus A380 [55].

La séparation des fonctions inhérente au modèle fédéré a cependant l'effet bénéfique de contenir les fautes. Par exemple, le plantage du logiciel dans un boîtier ne pourrait en aucun cas se propager à un autre boîtier. En contraste, dans le modèle IMA, on doit employer une isolation logicielle entre les différentes fonctions avioniques qui s'exécutent sur un même processeur afin d'empêcher la propagation des fautes entre les applications [57]. Cette isolation est réalisée à l'aide d'un mécanisme appelé « partitionnement robuste ». La norme ARINC-653 [12] spécifie un modèle de partitionnement robuste standardisé et des interfaces logicielles qui permettent de faire communiquer les applications d'un système IMA entre elles. Cette norme est déjà supportée par plusieurs systèmes d'exploitation du domaine commercial, dont VxWorks 653 de Wind River, Integrity-178B de Green Hills, PikeOS de SYSGO et LynxOS-178B de LynuxWorks.

Jusqu'à présent, les systèmes IMA déployés par les avionneurs emploient des ordinateurs monoprocesseurs classiques. Cela peut sembler surprenant puisque les ordinateurs à processeurs multicoeurs sont actuellement la norme. Les processeurs multicoeurs ont été largement adoptés en raison du plafonnement des fréquences d'horloge et de l'augmentation du nombre de transistors intégrables sur une même puce prévu par la loi de Moore [13]. Ils sont aussi de plus en plus employés dans les systèmes embarqués dans plusieurs domaines industriels [17, 24]. Malgré cela, l'utilisation des processeurs multicoeurs en avionique en général et en IMA en particulier relève encore du domaine de la recherche. Cela est dû au fait que la complexité additionnelle des systèmes parallèles introduit plusieurs nouveaux problèmes techniques qui affectent la certification de sûreté matérielle et logicielle [37]. D'ailleurs, la norme ARINC-653 ne spécifie que le comportement d'un système monoprocesseur (monocoeur) classique.

Certains systèmes d'exploitation commerciaux permettent déjà le partitionnement robuste sur plusieurs coeurs, dont QNX Neutrino [36] et SYSGO PikeOS [62]. Le système d'exploitation PikeOS est même certifié pour utilisation avionique. Cependant, l'adoption de ces systèmes d'exploitation est ralentie par les obstacles à la certification de sûreté rencontrés par les développeurs d'applications avioniques et les avionneurs. De plus, ces systèmes d'exploitation ne sont pas ouverts, empêchant ainsi une évaluation poussée par les chercheurs.

L'exploitation des nouveaux processeurs multicoeurs pour les applications IMA est un domaine de recherche encore très fertile. À notre connaissance, aucun système d'exploitation à partitionnement robuste supportant les processeurs multicoeurs n'est présentement disponible dans le domaine académique sans licence commerciale. Cette absence d'options dans le

domaine est un obstacle à l'avancement des recherches sur les sujets liés au partitionnement robuste avec les processeurs multicoeurs.

Dans ce contexte, nous identifions le problème de recherche suivant : « Comment serait-il possible d'adapter un noyau de partitionnement robuste monocoeur existant afin de le rendre compatible à un environnement multicoeur ? »

Le développement d'une solution à ce problème permettra de mettre en relief les obstacles qui empêchent actuellement l'exploitation en pratique des processeurs multicoeurs dans le domaine de l'IMA.

Nous visons aussi, à travers la réalisation du prototype de solution, l'évaluation d'une plateforme virtuelle pour le développement logiciel en avionique. Des projets de recherche récents,

mandatés par la FAA, suggèrent l'évaluation des plateformes virtuelles afin d'améliorer la

qualité de vérification des logiciels embarqués avioniques complexes [43]. Nous avons donc

choisi de suivre le sillage de ces chercheurs afin de valider, dans notre contexte, l'exploitation

de la même plateforme virtuelle, soit Wind River Simics, pour faciliter le développement de

notre prototype.

Ce mémoire présente l'adaptation logicielle du noyau de partitionnement robuste monocoeur académique « XtratuM » [19] qui vise l'architecture SparcV8 [60] afin de le rendre compatible avec un modèle de processeur multicoeur. L'adaptation ainsi réalisée, nommée « XtratuM-PPC », vise les processeurs multicoeurs de l'architecture PowerPC [34, 53]. Nous proposons une adaptation du modèle de partitionnement robuste de XtratuM applicable dans le cas des processeurs multicoeurs. De plus, nous identifions, à travers notre implémentation, des problèmes potentiels liés à l'exploitation des processeurs multicoeurs dans le contexte du partitionnement robuste. Enfin, nous présentons les résultats d'une étude de cas expérimentale de l'utilisation de notre noyau adapté, XtratuM-PPC, pour l'intégration d'un nombre d'applications plus élevé que ce qui est possible sur un processeur monocoeur.

Le corps de ce mémoire est structuré comme suit :

• le chapitre 1 présente la problématique de recherche ;

- le chapitre 2 présente une revue de la littérature pertinente au problème ;

- le chapitre 3 présente l'architecture du noyau XtratuM original;

- le chapitre 4 présente notre adaptation multicoeur de chacun des blocs du noyau;

- le chapitre 5 présente les détails techniques de l'implémentation de XtratuM-PPC sur les processeurs PowerPC et une étude de cas de son utilisation.

Nous concluons finalement avec une synthèse de nos travaux et des pistes de recherches ultérieures.

#### **CHAPITRE 1**

# **PROBLÉMATIQUE**

#### 1.1 Problème de recherche

Nous posons le problème de recherche avec la question suivante : « Dans le contexte des systèmes IMA, comment serait-il possible d'adapter un noyau de partitionnement robuste monocoeur existant afin de le rendre compatible à un environnement multicoeur ? »

Le problème est motivé par la stagnation des performances des processeurs monocoeurs depuis le milieu des années 2000 [13], ce qui force l'industrie avionique à considérer l'éventuelle adoption des processeurs multicoeurs [37]. Dans le cadre du projet CRIAQ AVIO-509, des partenaires industriels du domaine de l'avionique sont intéressés à l'utilisation éventuelle des processeurs multicoeurs pour augmenter le niveau d'intégration des plateformes avioniques afin d'en réduire les coûts. Le problème posé ci-haut a été identifié comme une première étape dans cette direction lors de réunions des chercheurs de notre équipe de projet.

### 1.2 Objectifs

Dans le cheminement vers la solution du problème de recherche, trois objectifs sont visés.

À notre connaissance, il n'existe actuellement aucun prototype librement disponible permettant l'évaluation du partitionnement robuste sur processeurs multicoeurs pour les applications avioniques.

1. Le premier objectif consiste à adapter un noyau de partitionnement robuste existant à une architecture multicoeur.

Le noyau adapté devra permettre :

- la consolidation d'un plus grand nombre d'applications avioniques sur une même machine en exploitant des processeurs multicoeurs existants;

- l'exploration des principaux modèles de partitionnement temporels parallèles (AMP, SMP et hybride);

- le prototypage d'applications IMA embarquées dans un environnement logiciel comparable aux solutions commerciales existantes.

L'implémentation d'un noyau de partitionnement robuste multicoeur vise à rendre possible l'intégration sécuritaire d'un nombre plus élevé de fonctions avioniques dans chaque boîtier physique. La mise en oeuvre d'une implémentation multicoeur du partitionnement robuste permettra de relever des problèmes d'intégration et de sûreté encore inconnus ou encore non validés expérimentalement.

2. Le second objectif consiste à identifier des problèmes d'intégration et de sûreté découlant du partitionnement robuste multicoeur.

Les noyaux de partitionnement robuste font partie de la classe logicielle des systèmes d'exploitation. Ils doivent prendre le contrôle total du matériel afin d'isoler adéquatement les applications. Les systèmes d'exploitation embarqués sont notoirement difficiles à développer, car les bogues surviennent le plus souvent à un niveau où l'utilisation de débogueurs est difficile, voire impossible et où les conséquences de bogues sont souvent le plantage dur de la machine. L'utilisation de plateformes virtuelles a été suggérée dans la littérature [43] pour simplifier le développement et la validation des logiciels embarqués.

3. Le troisième objectif consiste à implémenter la totalité du prototype sur une plateforme virtuelle afin d'évaluer les avantages et inconvénients de ce type d'outil pour le prototypage et le test de logiciels avioniques complexes.

#### 1.3 Contributions

Nous identifions ici les contributions découlant de la réalisation de nos travaux de recherche et de l'atteinte des objectifs du projet.

En premier lieu, nous réalisons un prototype de noyau de partitionnement robuste multicoeur adapté à partir d'un noyau existant. Le code source, la documentation et les exemples découlant de la réalisation de cette adaptation pourront servir de base à des travaux de recherche ultérieurs qui nécessitent un noyau de partitionnement robuste multicoeur fonctionnel.

En second lieu, nous présentons les problèmes d'adaptation que nous avons relevés, ainsi que la description du processus d'adaptation. Le contenu du présent mémoire sera utile à nos successeurs qui voudront réaliser le même genre d'exercice dans un environnement industriel.

En dernier lieu, nous présentons une étude de cas de l'utilisation de notre noyau adapté. Cette étude de cas est réalisée sur la plateforme virtuelle Simics. Par ailleurs, nous avons développé une méthode d'instrumentation nouvelle vouée aux plateformes virtuelles lors du débogage de notre implémentation du noyau XtratuM-PPC. Cette méthode, nommée VPI (« Virtual Platform Instrumentation »), a fait l'objet d'un article de conférence présenté à l'« IEEE International Symposium on Rapid System Prototyping » (RSP 2011). L'article est reproduit à l'annexe II. Notre couverture de l'utilisation de plateformes virtuelles sera donc réduite dans le présent mémoire, car ces résultats ne sont pas nécessaires à la compréhension de nos contributions principales liées à l'adaptation du noyau XtratuM.

### 1.4 Hypothèses et suppositions

Nous identifions dans cette section les hypothèses et suppositions générales qui ont servi à guider la méthodologie de recherche.

Notre hypothèse centrale est que l'adaptation multicoeur d'un noyau de partitionnement robuste existant est possible. De plus, nous émettons l'hypothèse que cette adaptation pourra supporter des plans d'exécution parallèles symétriques (SMP), asymétriques (AMP) et hybrides (SMP et AMP).

Ces hypothèses sont basées sur l'analyse préalable des architectures des systèmes d'exploitation Linux et RTEMS. Linux et RTEMS supportent déjà des modèles de programmation parallèles. De plus, le système d'exploitation temps réel RTEMS a déjà fait l'objet d'une adaptation afin de supporter le partitionnement robuste selon la norme ARINC-653 sur des processeurs monocoeurs. Cette adaptation avait été réalisée par l'équipe du projet AIR (« ARINC-653 in RTEMS ») [56], sans support de traitement parallèle. Enfin, le noyau de partitionnement robuste de PikeOS supporte maintenant les processeurs multicoeurs [30, 62]. Ce dernier est apparu vers la fin de nos travaux. Il est donc raisonnable de croire qu'il sera possible d'adapter un noyau de partitionnement robuste monocoeur à un modèle multicoeur dans nos travaux.

Afin de circonscrire plus précisément notre problématique, nous soulignons les suppositions suivantes :

- La cible des développements expérimentaux est l'architecture PowerPC. Plusieurs processeurs multicoeurs commerciaux emploient déjà cette architecture.

- La plateforme matérielle modélisée est considérée comme fiable et déterministe au sens de ses spécifications. Nous n'évaluerons pas la fiabilité intrinsèque de la plateforme matérielle cible.

- La plateforme virtuelle employée pour les travaux de prototypage est supposée fiable et déterministe.

- Aucune contrainte de certifiabilité n'est appliquée aux développements expérimentaux,

malgré la considération de ces mêmes contraintes dans la résolution du problème posé.

- Le modèle de partitionnement robuste défini par la norme ARINC-653 est prépondérant en industrie, mais nos travaux d'adaptations ne viseront que le respect de l'esprit de la norme et non pas son implémentation.

Ces suppositions générales s'appliquent en général à l'intégralité de nos travaux. Ces dernières s'ajoutent aux suppositions propres à chacune des tâches d'adaptation, qui seront présentées dans leur contexte particulier.

#### **CHAPITRE 2**

### REVUE DE LA LITTÉRATURE ET FONDEMENTS

#### 2.1 Survol

Dans ce chapitre, nous présentons les fondements nécessaires à la contextualisation du reste du mémoire. En premier lieu, nous décrivons le type de systèmes avioniques ciblés par nos travaux. En second lieu, nous jetons les bases du domaine du partitionnement robuste et présentons les méthodes employées pour implémenter les noyaux de partitionnement robuste modernes. Par la suite, nous justifions le choix du noyau de partitionnement robuste XtratuM comme base pour l'adaptation multicoeur décrite aux chapitres 4 et 5. Finalement, nous fournissons quelques références importantes à propos des processeurs multicoeurs.

### 2.2 Systèmes embarqués avioniques

Notre travail de recherche s'inscrit dans le domaine des systèmes embarqués avioniques.

Le domaine de l'avionique regroupe la conception, la réalisation et l'entretien des systèmes électriques, électroniques et informatiques des avions. Dans un avion de ligne moderne, l'avionique comprend entre autres une multitude de systèmes embarqués qui collabore pour assurer le bon fonctionnement de l'appareil.

Dans les sections suivantes, nous présentons un survol des caractéristiques principales des systèmes embarqués avioniques. En premier lieu, nous présentons des exemples de fonctions avioniques basées sur des systèmes embarqués. Ensuite, nous discutons de la sûreté des systèmes embarqués avioniques. Finalement, nous introduisons l'architecture des systèmes embarqués avioniques, incluant le modèle d'avionique modulaire intégrée et son rôle dans les systèmes avioniques contemporains.

## 2.2.1 Fonctions avioniques

Le cockpit moderne est occupé dans la majorité des cas par deux professionnels : un pilote et un copilote. Les postes de mécanicien de bord et de navigateur ont pour ainsi dire disparu depuis l'apparition de systèmes avioniques suffisamment performants pour les remplacer [61, p. 172]. Ainsi, le contrôle des paramètres mécaniques et du plan de vol est maintenant réalisé par des systèmes embarqués. Ces derniers mesurent et évaluent en temps réel une multitude de capteurs. Les conditions normales sont gérées automatiquement et l'attention du pilote n'est demandée que lorsqu'un évènement anormal survient. De cette façon, la surveillance continuelle d'un mur complet d'indicateurs n'est plus nécessaire. Les pilotes peuvent donc se concentrer uniquement à leurs tâches principales de pilotage et de gestion du vol, avec un nombre réduit de distractions.

Deux exemples de fonctions avioniques très communes sont les systèmes de commande de vol électriques (de l'anglais « fly-by-wire », abrégé FBW) et les systèmes de gestion de vol (de l'anglais « flight management system », abrégé FMS).

Les systèmes de commande électrique de vol contrôlent le déplacement de toutes les gouvernes (ailerons, déporteurs et volets) à l'aide d'actionneurs électriques en fonction des commandes du pilote et de lois de contrôle adaptées [16, pp. 24-2–24-3], au lieu d'employer des systèmes à câbles à lien direct. Les systèmes FBW améliorent la stabilité statique de l'appareil et garantissent la sûreté des paramètres de l'enveloppe de vol en prévenant par exemple une inclinaison latérale excessive [26, pp. 140–142].

Les systèmes de gestion de vol, quant à eux, remplacent la position du navigateur dans le cockpit par un ensemble d'ordinateurs et d'affichages. Le FMS fournit aux pilotes les données de trajectoire nécessaires au respect du plan de vol et leur permet de suivre en temps réel l'évolution de la position de l'appareil [67].

### 2.2.2 Sûreté des systèmes avioniques

Le droit de vol dans l'espace aérien public implique des appareils sûrs. La sûreté est certifiée par les autorités d'aviation civile, telles que la « Federal Aviation Administration » (FAA) aux États-Unis et Transport Canada. Ces certifications ont pour objectif d'assurer la sûreté du public, des passagers et des équipages [9, p. 145].

### 2.2.2.1 Fiabilité des systèmes avioniques

Selon McIntyre de la FAA [47, p. 327], la sûreté des avions passe par la fiabilité et c'est pourquoi la réglementation vise principalement cet aspect. Deux éléments sont nécessaires à l'obtention de la fiabilité : 1) la conception à sécurité intégrée (« fail-safe design ») et 2) la redondance des systèmes. Selon Allerton, ces deux concepts sont inextricablement reliés [9, p. 146]. Il est actuellement impossible de réaliser des systèmes électroniques ou mécaniques dont la probabilité de défaillance respecte le barème actuel d'une défaillance par 10<sup>9</sup> heures <sup>1</sup>. La redondance des systèmes est le seul moyen d'obtenir la fiabilité nécessaire.

Les moteurs, boîtiers avioniques, actionneurs et autres composants sont dits « certifiables » lorsqu'ils ont passé une évaluation de conception et passé leurs tests de certification. À partir de ce moment, ils peuvent être inclus dans un système intégré, qui sera certifié dans son ensemble.

### 2.2.2.2 Lignes directrices de certification

Des lignes directrices (« guidelines » en anglais) ont été développées par les organismes régulateurs, de concert avec l'industrie, afin d'assurer l'uniformité et la faisabilité commerciale

<sup>1.</sup> Une défaillance par 10<sup>9</sup> h équivaut à une défaillance par 1 000 ans pour une flotte de 100 avions ou une défaillance par 100 000 ans pour un seul avion [9, p. 145].

des critères d'évaluation lors de l'étape de certification. Ces documents couvrent tous les aspects du développement d'équipements pour les avions, incluant les systèmes mécaniques, électroniques, logiciels, ainsi que l'intégration de ces derniers.

Les lignes directrices sont des « normes » de facto dont la validité est généralement reconnue par les organismes régulateurs à travers le monde. En prouvant avoir suivi le cheminement d'une ligne directrice, on prouve que notre système atteint les objectifs de sa conception [33].

Il est important de noter que les lignes directrices sont très vagues et ne sont pas des normes en tant que telles. Chaque fournisseur doit développer ses propres processus de développement pour atteindre les objectifs de certification. Le respect de l'esprit des lignes directrices assure cependant une plus grande probabilité que les processus développés respectent les standards de certification. Ces standards de certification sont disponibles auprès des autorités aériennes [8].

Les lignes directrices les plus populaires en avionique sont développées par la « Radio Technical Commission for Aeronautics » (RTCA), un organisme sans but lucratif. Plusieurs normes avioniques sont développées par l'« Airlines Electronic Engineering Committee » (AECC) et publiées par Aeronautical Radio, inc. (ARINC). Ces normes sont respectées par l'industrie et reconnues par les organismes régulateurs.

### 2.2.2.3 Directive DO-178B visant le développement logiciel

La directive RTCA DO-178B [1] concerne le processus de développement logiciel en avionique. Son titre complet est « Software considerations in airborne systems and equipment certification ». Il s'agit de la plus importante directive dans le domaine du développement logiciel sur systèmes embarqués avioniques. Elle couvre tous les aspects importants pour la certification d'équipement comportant une composante logicielle :

- la planification du projet;

- le développement logiciel;

- la validation et vérification;

- la gestion de la configuration (autant au niveau externe qu'au niveau des livrables).

L'esprit de la directive est le déterminisme, c'est-à-dire que chaque effet réactif du système a une cause prédéfinie, identifiable et reproductible dans les mêmes conditions [33, p. 15]. De plus, chaque fonction ou groupe d'instructions doit être traçable vers une spécification fonctionnelle. Il ne doit donc y avoir rien qui puisse être laissé au hasard ou inséré inutilement dans le logiciel.

Avant qu'un système logiciel ne puisse être certifiable, on doit s'assurer qu'il est correct. Avec DO-178B, on doit s'assurer de la préservation sémantique entre le code source et le code binaire. Les résultats des compilateurs doivent être vérifiés. Une autre contrainte de DO-178B est que le code doit être robuste aux valeurs aberrantes. En effet, si une variable contient une mesure physique impossible pour le mode d'exécution courant, l'erreur doit être détectée. Cette contrainte réduit considérablement les risques de catastrophes dans les cas de fautes logiques ou de corruption de mémoire, mais augmente grandement le nombre de cas à vérifier.

Les étapes de vérification sont les plus coûteuses dans un processus DO-178B en raison des contraintes de vérification qui sont très sévères [9]. Malgré les contraintes sévères, DO-178B est une directive pragmatique, développée conjointement par l'industrie et les organismes régulateurs. Des justifications adéquates permettent souvent de simplifier les vérifications nécessaires, ce qui permet de réduire les coûts de développement.

### 2.2.3 Architecture des systèmes embarqués avioniques

### 2.2.3.1 L'avionique fédérée

Le modèle avionique classique est le modèle dit « fédéré » : l'ensemble avionique d'un appareil est constitué d'une pluralité de systèmes conçus indépendamment par différents fabricants

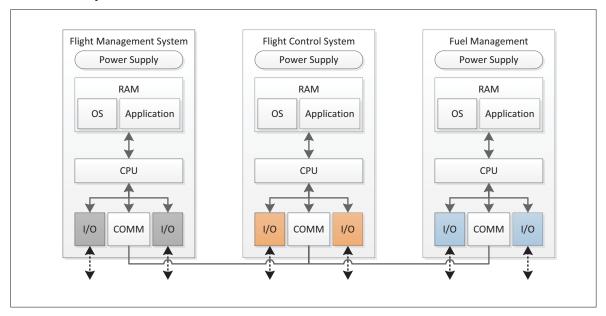

et intégrés par l'avionneur. L'architecture des systèmes fédérés fournit à chaque fonction avionique les ressources suivantes [69, p. 12-2] (voir aussi figure 2.1) :

- un système embarqué dédié;

- une infrastructure dédiée (alimentations, refroidissement, châssis);

- des interfaces d'entrées/sorties dédiées ;

- un bus système dédié.

Figure 2.1 Exemple schématique d'une architecture fédérée

Le modèle fédéré facilite la conception et la certification, car les interactions avec les autres systèmes sont bien circonscrites et la complexité des systèmes est maîtrisable avec des méthodologies éprouvées depuis plusieurs décennies. L'hétérogénéité des fonctions avioniques dans un environnement fédéré augmente cependant les frais d'exploitation des appareils, en raison notamment du nombre élevé de pièces de rechange à gérer, de l'encombrement et du poids « mort » dédié à une réplication de modules à fonction unique.

### 2.2.3.2 L'avionique modulaire intégrée (IMA, « Integrated Modular Avionics »)

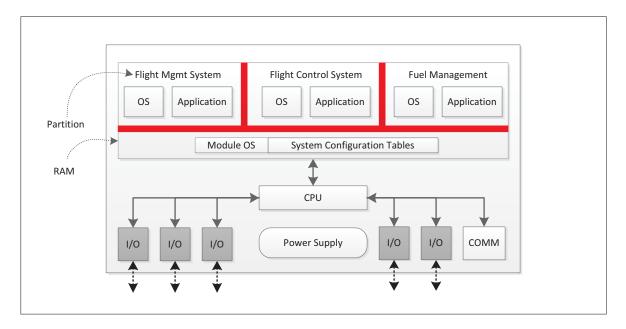

Par opposition au modèle fédéré, le modèle avionique modulaire intégré vise à faire converger sur une même plateforme matérielle plusieurs fonctions avioniques qui auraient été développées sur des systèmes indépendants dans le passé [10]. La figure 2.2 présente l'intégration des fonctions de la figure 2.1 avec le modèle IMA.

Figure 2.2 Exemple schématique d'une architecture IMA

L'objectif de cette convergence est très clair, selon ARINC651 :

« The [IMA] system design should make maximum use of shared resources to reduce resource duplication to a minimum. Such integration lowers the cost of ownership by reducing the acquisition cost, spares requirements, weight, and volume of the avionics equipment. » [10, p. 3]

Les systèmes IMA atteignent cet objectif en fournissant :

- un système embarqué partagé où les applications sont isolées avec un partitionnement robuste (voir section 2.3 page suivante);

- une infrastructure commune (alimentations, refroidissement, châssis);

- des interfaces distantes d'entrée/sortie partagées ;

- un bus système distribué, par exemple un bus Ethernet redondant à haut débit.

L'IMA permet aussi d'améliorer la standardisation des modules matériels. Cette standardisation vise à réduire le temps de développement d'un système complet, car la phase de développement matériel n'est pas à refaire. La même équipe peut ainsi entreprendre d'autres projets sans réapprendre les spécificités d'une architecture unique au projet [10, p. 47]. De plus, la réutilisation entre différents projets de fonctions avioniques déjà programmées est un objectif à long terme de l'IMA.

La plateforme Genesis [68] développée par Smiths Aerospace est un exemple de modèle idéalisé de plateforme IMA. Le « Common Core System » (CCS), une implémentation de la plateforme Genesis, est à la base de l'ensemble avionique du Boeing 787 Dreamliner [68]. Le CCS supporterait entre 80 et 100 applications (une fonction avionique est composée d'une ou plusieurs « applications ») [6]. L'Airbus A380, quant à lui, supporterait une vingtaine de fonctions avioniques sur sa plateforme IMA développées par une dizaine de fournisseurs [35, p. 25]. Dans ces deux cas, un réseau temps-réel ARINC-664 [11] réalise l'interconnexion entre les modules IMA.

L'intégration IMA ne respecte les critères de sûreté logicielle que si les développeurs ont l'illusion d'avoir un système complètement indépendant et isolé. Sans cette indépendance entre les logiciels, une défaillance logicielle peut se propager à l'intérieur du système.

Les nouveaux systèmes d'exploitation adaptés à l'IMA sont dotés de mécanismes de partitionnement robuste qui isolent les partitions avec un niveau de sûreté très élevé. Nous présentons un survol de ces mécanismes à la section suivante.

#### 2.3 Partitionnement robuste

La contribution principale de ce mémoire est l'adaptation d'un noyau de partitionnement robuste afin qu'il puisse supporter les processeurs multicoeurs. Dans cette section, nous définirons en premier lieu ce qui est entendu par « partitionnement robuste », puisqu'il s'agit d'un concept central à nos travaux. Par la suite, nous introduirons les considérations techniques liées au partitionnement robuste, incluant un survol de la norme ARINC-653. Finalement, nous présenterons une vue d'ensemble des différentes méthodes de partitionnement robuste.

# 2.3.1 Définition du partitionnement robuste

Le partitionnement robuste est défini comme suit dans la norme ARINC-653 :

« [Robust Partitioning :] A mechanism for assuring the intended isolation of independent aircraft operational functions residing in shared computing resources in all circumstances, including hardware and programming errors. The objective of Robust Partitioning is to provide the same level of functional isolation as a federated implementation (i.e., applications individually residing on separate computing elements). This means robust partitioning must support the cooperative coexistence of applications on a core processor, while assuring unauthorized, or unintended interference is prevented. » [12, p. 110]

Avant de continuer, mentionnons que cette description inclue la mention « on a core processor » (au singulier), ce qui implique qu'une définition formelle du cas à plusieurs coeurs n'est pas fournie dans cette norme.

Le partitionnement robuste, dans le contexte du modèle IMA, vise à émuler le modèle avionique fédéré dans un système avionique intégré. Ainsi, chaque fonction avionique s'exécutant sur un même processeur se verra isolée dans une « partition logicielle » <sup>2</sup> afin d'éviter que la défaillance d'une application n'en affecte une autre. Dans ce contexte, le mot « partition » est employé dans son sens informatique traditionnel : on sépare l'ensemble des ressources partagées d'un système en fragments isolés les uns des autres.

Rushby aborde de manière exhaustive le sujet du partitionnement dans les applications avioniques dans son rapport technique publié conjointement par la NASA et la FAA [57]. Il y présente intuitivement l'objectif-clé du partitionnement :

<sup>2.</sup> On réduira cette expression au seul mot « partition » pour simplifier le discours.

« The behavior and performance of software in one partition must be unaffected by the software in other partitions. » [57, p. 11]

Sans partitionnement robuste, il serait impossible de partager une machine entre plusieurs fonctions avioniques de façon sécuritaire. La nécessité du partitionnement est confirmée par l'inclusion du concept dans DO-178B [1] et son document de clarification DO-248B [3].

L'implémentation du partitionnement robuste est réalisée par le « noyau » de partitionnement robuste. Dans notre cas, nous employons le mot « noyau » dans le sens informatique moderne : il s'agit de la composante centrale du système d'exploitation d'un ordinateur qui agit comme interface entre le matériel et les applications. Le bloc « Module OS » de la figure 2.2 représente le noyau de partitionnement robuste dans le modèle d'un système IMA.

On peut décomposer le partitionnement robuste en deux mécanismes interreliés dont la combinaison assure l'isolation désirée : le partitionnement temporel et le partitionnement spatial. Nous traiterons séparément de ces deux mécanismes tout au long de notre exposé.

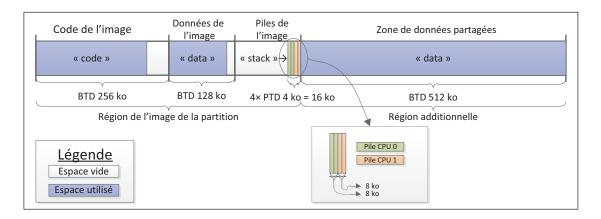

#### 2.3.2 Partitionnement spatial

Le partitionnement spatial vise à empêcher le partage de ressources physiques (mémoire, régions d'entrée/sortie) qui pourrait causer un couplage ou la transmission de défaillances entre les partitions. Chaque ressource partageable doit être assignée à une seule partition par une table de configuration. La table de configuration est statique, ce qui veut dire qu'elle est prédéfinie et qu'elle ne peut en aucun cas changer après le démarrage de la machine. On assigne aux partitions des zones de mémoire qui ne se chevauchent pas. Ensuite, la composante de partitionnement spatial du noyau de partitionnement robuste se charge de faire appliquer les restrictions de la configuration à l'aide de divers mécanismes matériels et logiciels. Nous discuterons plus en détail de ces mécanismes à la section 2.4. Grâce au partitionnement spatial, le dépassement de capacité d'un tampon mémoire dans une partition A ne pourrait en aucun

cas écraser de données dans une partition B. Pour le moment, on considérera le cas usuel d'une seule partition par application. Cette contrainte sera révisée au chapitre 4 lorsque nous présenterons notre modèle de partitionnement spatial multicoeur adapté.

# 2.3.3 Partitionnement temporel

Le partitionnement temporel sert quant à lui à garantir que chaque partition obtient l'usage exclusif du processeur pendant des périodes suffisantes pour respecter ses échéances critiques. On assigne des tranches de temps à chaque partition, en fonction de l'analyse du pire cas de temps d'exécution (« worst case execution time » en anglais, WCET) et des exigences de périodicité de chaque programme. Ces assignations sont combinées pour construire un plan d'exécution, défini sur la base d'un « bloc d'activation temporel majeur » périodique, dont la période est fixe. Le bloc d'activation temporel majeur est aussi connu sous le nom de « major time frame » en anglais. Les partitions obtiennent le contrôle du processeur durant des « fenêtres d'activation ». Ces fenêtres d'activations sont définies dans le bloc d'activation temporel majeur par leur durée et leur décalage temporel par rapport au début du bloc.

Un ordonnanceur applique ensuite le plan d'exécution préconfiguré. Encore ici, la configuration est fixe et ne peut pas changer après le démarrage du système. Contrairement à ce qui est fait dans les systèmes d'exploitation temps réel classiques, les ordonnanceurs employés pour le partitionnement temporel n'appliquent en aucun cas de préemption aux partitions. Ainsi, une partition qui aurait fini son traitement plus tôt que prévu n'accorderait pas le reste de sa tranche de temps à une autre partition. Tout au plus, le temps mort pourrait être réutilisé par le noyau pour des tâches administratives internes ou des fonctions ne pouvant pas mettre en péril la sûreté du système.

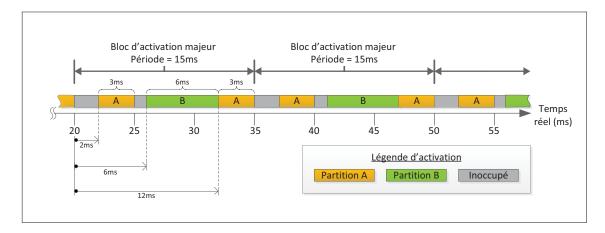

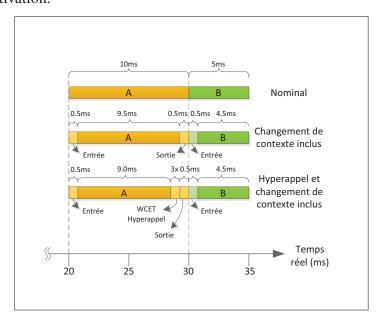

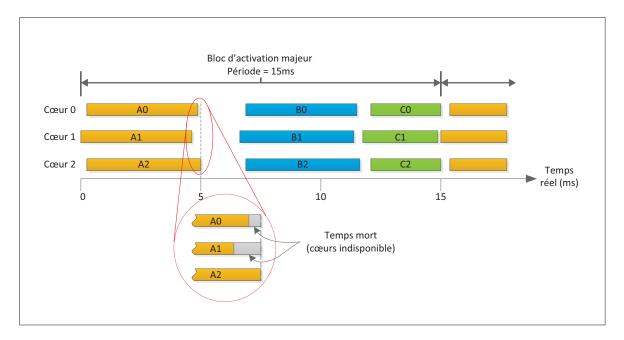

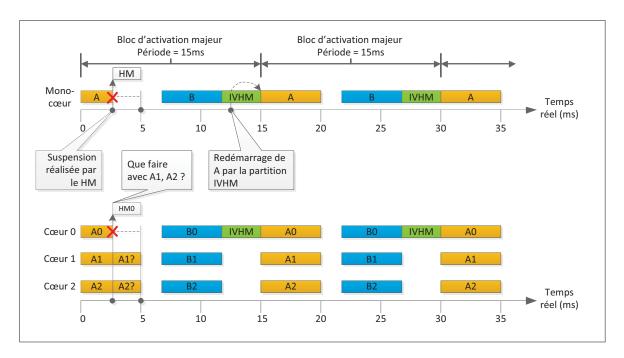

La figure 2.3 présente un exemple de plan d'exécution à deux partitions. Les paramètres de ce plan d'exécution sont résumés au tableau 2.1. Dans cet exemple, deux partitions se partagent le temps du bloc d'activation majeur. Les deux partitions obtiennent des fenêtres d'activation

totalisant la même durée totale, soit 12 ms. L'exécution de la partition A est séparée en deux fenêtres d'activations distinctes. On remarque que les fenêtres d'activation sont les mêmes dans chaque bloc d'activation majeur et qu'il est possible de laisser des fenêtres d'activation inoccupées (celles présentées en gris) pour permettre des extensions futures ou prendre en considération certains délais, tels que le changement de contexte.

Figure 2.3 Exemple d'un plan d'exécution à deux partitions

Tableau 2.1 Paramètres de l'exemple d'un plan d'exécution à deux partitions de la figure 2.3

| Fenêtre | Partition active | Décalage | Durée |

|---------|------------------|----------|-------|

| 1       | A                | 2 ms     | 3 ms  |

| 2       | В                | 6 ms     | 6 ms  |

| 3       | A                | 12 ms    | 3 ms  |

# 2.3.4 Le partitionnement robuste selon la norme ARINC-653

L'augmentation de la popularité du modèle IMA dans les projets d'aviation militaire des années 90 a encouragé un mouvement de standardisation dans l'industrie avionique [49]. Ces efforts se sont soldés par la publication de la norme ARINC-653 [12] en 1997. Dans cette section, nous décrirons les principales caractéristiques d'ARINC-653 puisque son modèle de partitionnement est très commun en IMA.

La norme ARINC-653 définit un système exécutif d'applications (« APlication EXecutive », APEX) qui réalise le partitionnement robuste d'un processeur et de sa mémoire. De plus, elle définit une interface logicielle permettant la gestion des partitions, la communication entre ces dernières, ainsi que la gestion des conditions d'erreurs dans un système IMA. La norme est séparée en trois parties, mais nous ne faisons référence qu'à la partie 1 (ARINC-653P1, « Required Services »), qui spécifie l'APEX, les services de partitionnement essentiels et les mécanismes de configuration d'un système IMA.

Le modèle du système APEX est un noyau de partitionnement robuste où chaque partition apparaît comme une machine entièrement dédiée à l'application qui y est exécutée.

Outre le fait que la norme spécifie les caractéristiques spatiales d'une partition, aucune restriction n'est donnée quant à l'implémentation du partitionnement spatial sous ARINC-653. Les développeurs de systèmes d'exploitation sont libres d'employer les mécanismes d'isolation spatiale les mieux adaptés à l'architecture matérielle choisie.

Un système conforme à APEX emploie un ordonnanceur à deux niveaux pour le partitionnement temporel. Le niveau primaire est un ordonnanceur statique qui fournit des tranches de temps prédéfinies à chaque partition. Le niveau secondaire doit être un ordonnanceur préemptif à priorité fixe, équivalent à un système d'exploitation temps réel classique propre à chaque partition. Ce système d'exploitation de partition implémente aussi les services habituels d'un système d'exploitation temps réel.

La configuration d'un système ARINC-653 (appelée « System Blueprint » en anglais) est chargée à partir d'une table au démarrage et ne varie pas : elle est complètement statique. Il en va de même pour l'allocation de la mémoire, qui n'est permise que lors de la phase d'initialisation des partitions et du système d'exploitation. Le déterminisme est ainsi garanti et les opportunités de débordement causées par l'allocation de mémoire dynamique sont éliminées.

Un moniteur de la santé du système veille à surveiller les partitions. Si l'une d'entre elles venait à planter, une action de contingence serait exécutée et l'erreur serait communiquée aux partitions qui en dépendent. Il est possible que la partition soit redémarrée. Dans ce cas, il est spécifié que le redémarrage doit être complètement transparent pour les autres applications.

Dans un système d'exploitation ARINC-653, les partitions communiquent à travers des ports virtuels. Ces ports sont eux aussi prédéfinis dans la configuration du système. L'utilisation des ports virtuels permet l'abstraction du moyen de communication (local ou distant, ARINC-664 [11] ou autre) et le respect de l'isolation spatiale entre les partitions.

Depuis sa publication, ARINC-653 a été implémentée dans la majorité des systèmes d'exploitation avioniques commerciaux : Integrity-178B de Green Hills, LynxOS-178B de Lynux-Works, VxWorks 653 de WindRiver et PikeOS de SYSGO.

### 2.3.5 Interdépendances entre partitionnement spatial et temporel

Le partitionnement spatial et temporel sont interreliés à plusieurs niveaux. En particulier, l'implémentation du partitionnement spatial a toujours un effet sur le partitionnement temporel en raison des délais non nuls d'accès aux différents niveaux de la hiérarchie de mémoire sur les processeurs modernes.

Par exemple, la réalisation de la protection mémoire à l'aide d'une unité matérielle de gestion de la mémoire (« Memory Management Unit » ou MMU en anglais) peut causer des exceptions de fautes de pages. Ces exceptions sont nécessaires au bon fonctionnement des algorithmes de protection de mémoire, mais elles consomment du temps de traitement à la partition en cours.

Un autre exemple est l'effet du contenu des caches lors du changement de contexte de partitions. L'implémentation du partitionnement spatial doit gérer les caches afin d'empêcher une incertitude temporelle au niveau de l'exécution de la prochaine partition causée par le contenu de la cache de la partition précédente dans le plan d'exécution. En raison de ces interdépendances fonctionnelles entre la composante spatiale et temporelle du partitionnement robuste, l'implémentation des noyaux de partitionnement est une combinaison d'une multitude de mécanismes dont la frontière est moins bien circonscrite qu'elle n'apparaît au premier coup d'oeil. Les noyaux de partitionnement robuste, malgré leur variété, font tous partie de la classe logicielle des systèmes d'exploitation. Ainsi, ils sont composés d'ordonnanceurs, de fonctionnalités de gestion de la mémoire, de pilotes de périphériques et d'autres services de base. Les différences se retrouvent dans les choix architecturaux effectués lors de la réalisation des composantes logicielles du noyau.

# 2.4 Méthodes de partitionnement spatial

Un scénario classique avant l'invention de la protection de mémoire était le plantage de toutes les applications d'un système en raison du débordement de mémoire d'une seule application. Sans mécanismes de protection de mémoire, un programme pouvait écrire partout en mémoire, incluant dans les zones déjà occupées par d'autres programmes ou par le système d'exploitation. Les premiers mécanismes de protection de la mémoire visaient donc à faire appliquer une politique de partitionnement spatial afin de permettre l'exécution sécuritaire de plusieurs programmes sur une même machine.

Au fil des développements dans le domaine des systèmes d'exploitation, l'apparition de nouveaux problèmes a motivé la conception de systèmes de protection de ressources partagées de plus en plus sophistiqués.

Le partitionnement spatial est réalisé avec une combinaison de méthodes logicielles et matérielles de protection des ressources partagées, couplées à un moniteur de santé du système qui applique des politiques de contingence lorsqu'une opération illégale survient.

Trois mécanismes matériels sont minimalement nécessaires pour permettre la protection des ressources partagées [52, p. 529] :

- 1. Le support d'au moins deux niveaux de privilèges matériels afin de pouvoir distinguer si le contexte d'exécution actuel est le noyau ou une application qui doit être restreinte. On parlera de mode « superviseur » et de « mode usager ». Dans certains cas, des « anneaux » concentriques représentent les niveaux de privilèges. Avec cette nomenclature les anneaux plus au centre sont plus privilégiés (plus près du coeur).

- La protection des registres de contrôle de la machine contre l'écriture par les applications en mode usager. Des instructions réservées au mode superviseur doivent être employées pour modifier ces registres.

- 3. Le support d'une instruction permettant d'entrer en mode superviseur de manière contrôlée et une autre pour revenir en mode usager à partir du mode superviseur. La plupart des processeurs possèdent une version de l'instruction « system call » (appel système) qui permet de demander une opération privilégiée au logiciel superviseur. Cette instruction est toujours accompagnée d'une instruction « return from exception » (retour d'exception) qui quitte atomiquement le mode superviseur après l'exécution de l'opération privilégiée par le noyau.

Les mécanismes de gestion des privilèges sont employés en conjonction avec des mécanismes matériels de protection de la mémoire afin d'appliquer une politique de protection de la mémoire. Il existe deux types de ces mécanismes matériels de protection de mémoire : les unités de protection de mémoire (« Memory Protection Unit », MPU) et les unités de gestion de mémoire virtuelle (MMU). Dans les deux cas, le système d'exploitation configure les politiques d'accès dans ces unités et un accès interdit se solde par une exception.

Les MPU s'occupent uniquement de protection de la mémoire et se retrouvent habituellement dans les processeurs embarqués très simples ou lorsque la performance maximale est un critère.

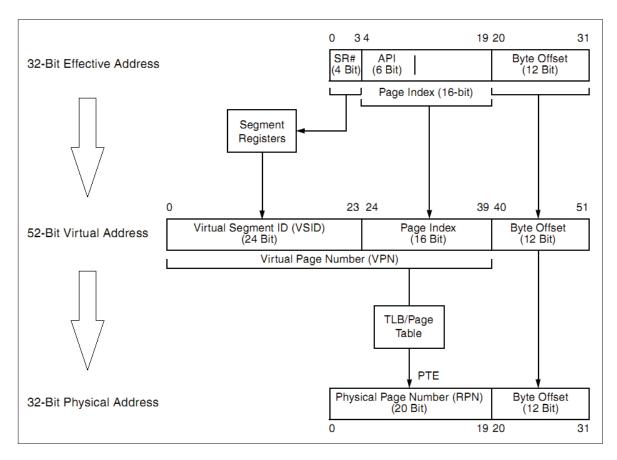

Les MMU, quant à eux, gèrent la protection de la mémoire physique et permettent aussi d'employer un adressage à mémoire virtuelle. Ce type d'adressage permet la traduction entre des

adresses dites virtuelles, visibles au programmeur, et les adresses physiques de la mémoire, visibles uniquement au système d'exploitation. Plusieurs des mécanismes logiciels de partitionnement spatial sont basés sur la disponibilité d'un espace d'adresses virtuelles indépendant de l'espace d'adresses physiques [52]. Les processeurs de la famille PowerPC utilisés dans nos travaux possèdent tous un MMU flexible et performant.

Un système d'exploitation implémente la protection de la mémoire en combinant les mécanismes matériels de protection à des algorithmes de partitionnement de la mémoire. L'objectif est de configurer les mécanismes matériels afin de maximiser les performances de l'application, tout en proscrivant les accès interdits d'après la configuration du système. Souvent, le code exécutable d'un programme, ses données et sa pile seront placés dans des zones différentes de la mémoire, avec des permissions adaptées. Par exemple, la zone de données sera accessible en lecture et en écriture, alors que la zone de code ne le sera qu'en lecture-seule.

La granularité de la protection de mémoire est proportionnelle au niveau de sûreté désirée. Plus le niveau de sûreté est élevé, plus la granularité de protection sera fine afin de pouvoir déterminer précisément la cause d'un accès interdit. En connaissant précisément cette cause, il devient possible de réduire l'ampleur de l'action de contingence. Par exemple, l'accès interdit à un périphérique pourrait se solder par un simple signal d'erreur au lieu de la suspension de l'application.

Notons qu'il est possible de réaliser entièrement par logiciel la protection de mémoire nécessaire au partitionnement spatial. Cela est possible en insérant du code de vérification des bornes à chaque accès mémoire potentiellement dangereux [66]. Le code de vérification est inséré par le compilateur ou par le chargeur de programme. Cette approche est cependant sujette à la compromission lorsque le code de protection n'est pas géré par le noyau de partitionnement. De plus, la vérification des bornes engendre un coût en performances non-négligeable. On ne peut donc pas se fier aux méthodes entièrement logicielles dans le contexte IMA, à

moins que toutes les applications soient programmées par des groupes coopératifs au sein de l'entreprise qui réalise l'intégration.

En plus des mécanismes de protection de la mémoire, l'implémentation du partitionnement spatial requiert des mécanismes de communication inter-partition (« inter-partition communication » en anglais, IPC). Ces mécanismes permettent aux applications d'interagir et de partager leurs résultats sans compromettre les barrières d'isolation. Le noyau de partitionnement robuste s'assure que toutes les communications sont autorisées selon des tables de privilèges préconfigurées. La plupart du temps, des restrictions s'appliquent quant à la taille et au nombre de messages permis entre chacune des partitions.

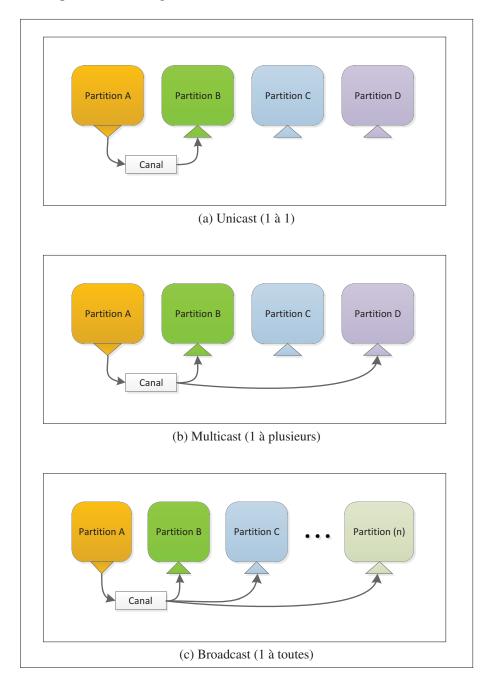

Considérons les mécanismes d'IPC définis dans la norme ARINC-653. Deux mécanismes y sont définis : les ports à échantillonnage (« sampling ports » en anglais) et les ports à file d'attente (« queuing ports » en anglais). On parle ici de « ports » de communication virtuels. Il ne s'agit pas de ports de communication physiques, mais plutôt d'abstractions, tels les ports d'entrée et de sortie d'une boîte noire. Comme leur nom l'indique, les ports à échantillonnage représentent l'abstraction d'un échantillonneur-bloqueur. À chaque fois qu'une nouvelle valeur y est inscrite par un producteur, elle demeure lisible sur le port par les consommateurs jusqu'à son expiration, le cas échéant. Inversement, les ports à file d'attente contiennent une file qui se vide au fur et à mesure que les données sont lues par les consommateurs.

L'interconnexion des ports de communication des différentes partitions est réalisée à travers des « canaux » virtuels. Dans ARINC-653, les canaux sont des liens logiques entre une source et une ou plusieurs destinations. Il est possible d'effectuer une assignation logique entre un port et une procédure ou un identifiant de pilote pour des réseaux de communication avionique, en plus d'une assignation vers des canaux inter-partition internes.

Dépendamment de l'implémentation, un même port de sortie peut être relié à plusieurs canaux permettant ainsi de réaliser une diffusion sélective. Les trois modes de diffusion définis dans ARINC-653 sont présentés à la figure 2.4.

Figure 2.4 Modes de diffusion de messages inter-partitions

### 2.5 Méthodes de partitionnement temporel

Alors que le partitionnement spatial vise à prévenir les partages de ressources indésirables, le partitionnement temporel vise à garantir des ressources de traitement suffisantes aux partitions.

L'implémentation du partitionnement temporel dans un noyau de partitionnement robuste se résume à la combinaison d'un ordonnanceur de partitions et d'un ensemble de règles qui enrayent la subtilisation de cycles d'une partition par une autre.

L'ordonnanceur statique cyclique est le plus populaire en partitionnement temporel robuste en raison de sa simplicité. Le seul critère de changement de contexte de ce type d'ordonnanceur est l'avancement du temps. Son implémentation doit être extrêmement robuste et sûre, car l'intégrité du partitionnement temporel en dépend directement. Comme nous l'avons déjà mentionné, la norme ARINC-653 mandate l'utilisation de ce type d'ordonnanceur comme premier niveau d'ordonnancement dans l'APEX.

En plus de l'ordonnanceur, la gestion des interruptions est un élément clé afin d'éviter les dépassements temporels des partitions. En particulier, la gestion des interruptions du système doit être centralisée dans le noyau. Les partitions ne peuvent avoir accès qu'à des interruptions virtuelles et les sources d'interruptions doivent être rigoureusement contrôlées afin d'éviter qu'une source imprévue n'interrompe la partition en cours, même pour un très court laps de temps.

Finalement, les autres fonctions avancées des processeurs, tels que l'accès direct à la mémoire (« Direct Memory Access » ou DMA, en anglais) et les bus partagés d'accès aux périphériques, doivent aussi être gérées par le noyau de partitionnement robuste. Par exemple, les modules DMA peuvent subtiliser des cycles d'accès au bus de mémoire si leur gestion est complètement indépendante des réalités du plan d'exécution. D'ailleurs, certains noyaux de partitionnement robuste simples, tels que POK [22] et XtratuM [19] n'offrent aucune fonctionnalité intégrée pour l'exploitation des modules DMA.

### 2.6 Choix d'un noyau de partitionnement robuste à adapter

Lors de la phase d'exploration de nos travaux, nous avons cherché des noyaux de partitionnement robuste académiques existants afin d'en trouver un qui pourrait servir de base à notre adaptation multicoeur. Nous pouvons classifier les noyaux identifiés au sein de trois catégories : 1) ceux qui supportent directement ARINC-653, 2) ceux qui supportent des modèles similaires à ARINC-653 et 3) ceux qui ne supportent pas des modèles similaires à ARINC-653.