## ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

## MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAITRISE EN GÉNIE ÉLECTRIQUE M. Ing.

> PAR PELLETIER, Sébastien

IMPLÉMENTATION EN VHDL/FPGA D'AFFICHEUR VIDÉO NUMÉRIQUE (AVN) POUR DES APPLICATIONS AÉROSPATIALES

MONTRÉAL, LE 16 OCTOBRE 2008

C Sébastien Pelletier, 2008

## PRÉSENTATION DU JURY

## CE MÉMOIRE A ÉTÉ ÉVALUÉ

## PAR UN JURY COMPOSÉ DE

M. Vahé Nerguizian, directeur de mémoire Génie électrique à l'École de technologie supérieure

M. Jean-François Boland, président du jury Département de Génie Électrique à l'École de technologie supérieure

M. Robert Sabourin, membre du jury Département de Génie de la production automatisée à l'École de technologie supérieure

M. Vartivar Aklian, examinateur externe CMC ÉLECTRONIQUE

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY

LE 2 OCTOBRE 2008

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## IMPLÉMENTATION EN VHDL/FPGA D'AFFICHEUR VIDÉO NUMÉRIQUE (AVN) POUR DES APPLICATIONS AÉROSPATIALES

#### PELLETIER, Sébastien

#### RÉSUMÉ

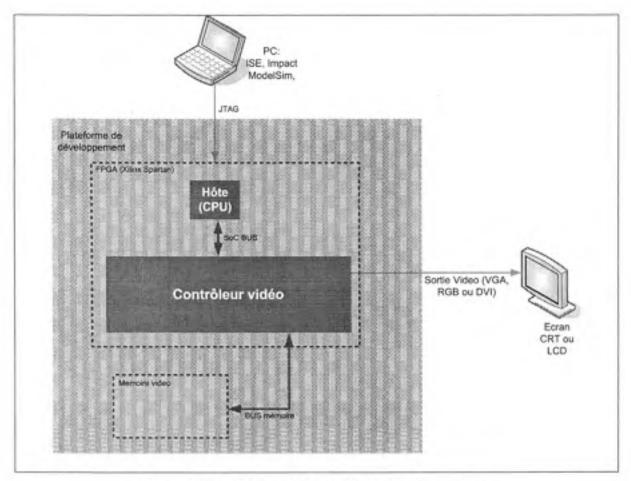

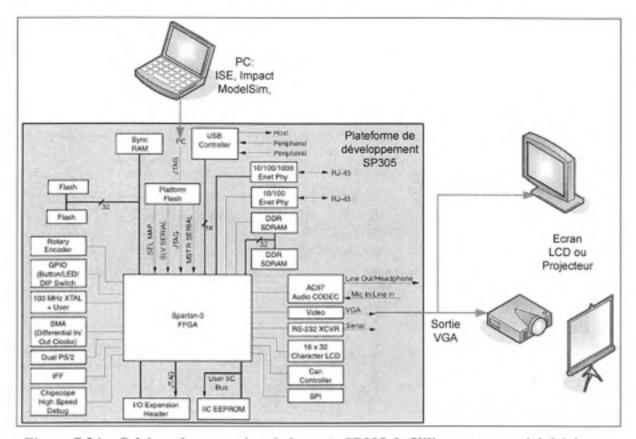

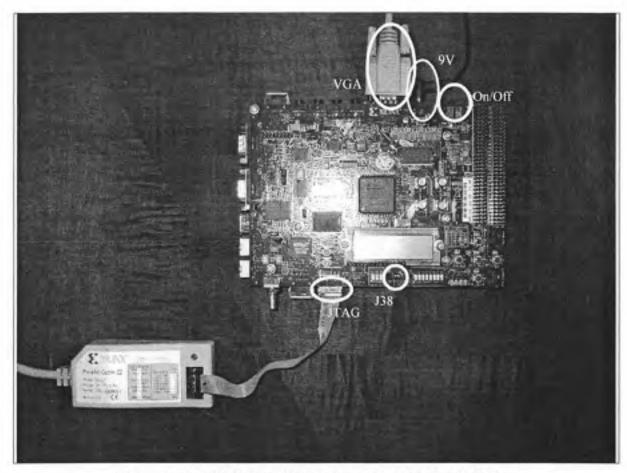

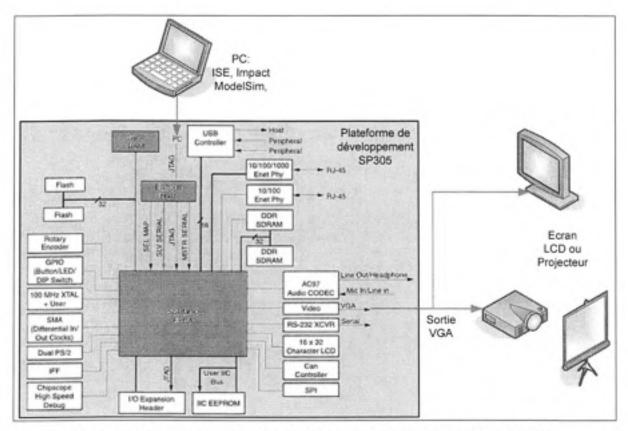

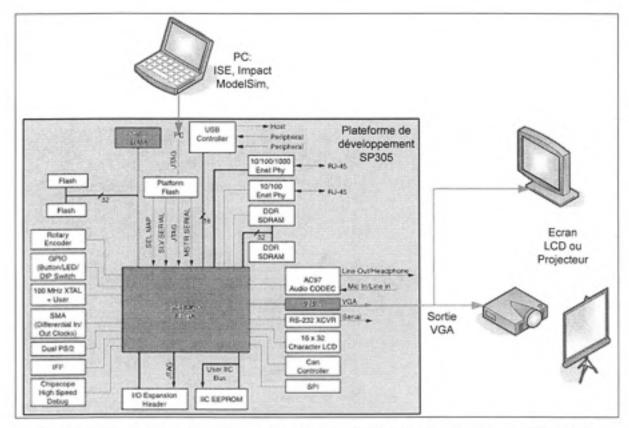

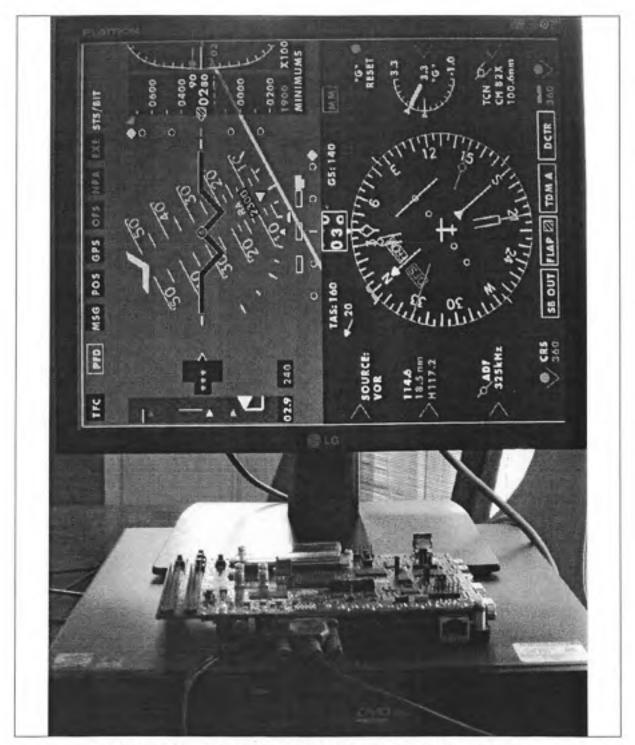

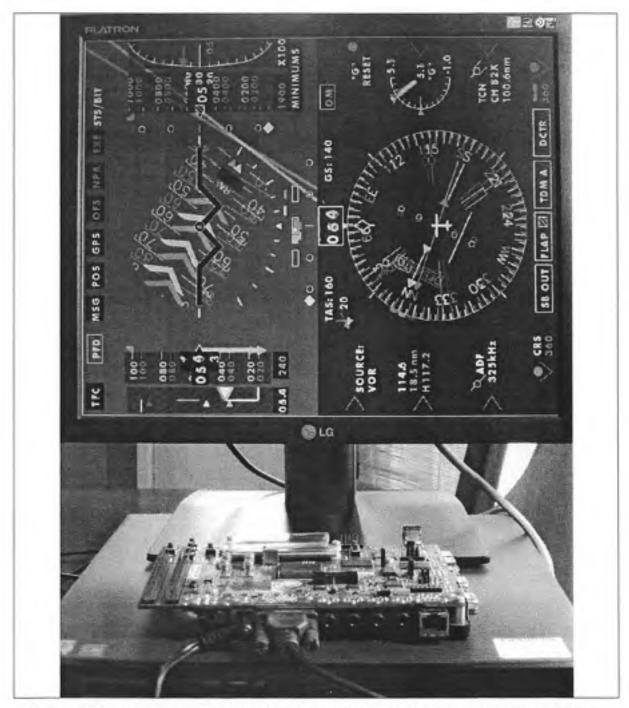

L'objectif de ce projet est de développer un contrôleur vidéo en langage VHDL afin de remplacer la composante spécialisée présentement utilisée chez CMC Électronique. Une recherche approfondie des tendances et de ce qui se fait actuellement dans le domaine des contrôleurs vidéo est effectuée afin de définir les spécifications du système. Les techniques d'entreposage et d'affichage des images sont expliquées afin de mener ce projet à terme. Le nouveau contrôleur est développé sur une plateforme électronique possédant un FPGA, un port VGA et de la mémoire pour emmagasiner les données. Il est programmable et prend peu d'espace dans un FPGA, ce qui lui permet de s'insérer dans n'importe quelle nouvelle technologie de masse à faible coût. Il s'adapte rapidement à toutes les résolutions d'affichage puisqu'il est modulaire et configurable. À court terme, ce projet permettra un contrôle amélioré des spécifications et des normes de qualité liées aux contraintes de l'avionique.

Mots clés: VGA, vidéo, VHDL, PROM, SP305, Wishbone

## IMPLÉMENTATION EN VHDL/FPGA D'AFFICHEUR VIDÉO NUMÉRIQUE (AVN) POUR DES APPLICATIONS AÉROSPATIALES

Pelletier, Sébastien

#### ABSTRACT

The Purpose of this project is to develop a digital display controller with the VHDL language to replace the specialized device presently used at CMC Electronics. To define the system specifications, an extensive research is performed on tendencies and on what is nowadays made in the field of the video display controllers. Pictures storage and display techniques are explained to lead this project to completion. The new controller is developed on an electronic platform having FPGA, VGA port and some RAM memory data storage. It is programmable and takes little space in FPGA, what allows it to be inserted in whatever new mass technology at low cost. Because it is modular and configurable, it can be quickly adapted to all possible display resolutions. In the short term, this project will allow a better control on avionic specifications and quality standards constraints.

Keywords: VGA, video, VHDL, PROM, SP305, Wishbone

#### REMERCIEMENTS

Premièrement, je voudrais souligner le soutient, les encouragements ainsi que la patience dont a fait preuve Sophie Bouchard, ma conjointe, durant toute la durée du projet.

Je tiens à remercier Vartivar Aklian pour toute l'aide et le support qu'il a apporté et aussi pour la patience dont il a fait preuve.

Je voudrais remercier Vahé Nerguizian pour son encadrement et aussi pour la confiance qu'il a témoignée pendant ces années de recherche.

Un merci spécial à Rigoberto Avelar pour avoir pu rapidement faire les modifications nécessaires sur la plateforme de développement afin que le projet puisse continuer sans délais.

Merci aussi à CMC Électronique et à l'École de technologie supérieure qui ont fourni le budget et l'infrastructure sans quoi ce projet n'aurait jamais été possible.

Merci à Frédéric Arteau pour son ouverture et sa patience.

# TABLE DES MATIÈRES

|       | Page                                                                         |

|-------|------------------------------------------------------------------------------|

| INTRO | DUCTION1                                                                     |

|       |                                                                              |

| CHAP  | TRE 1 PROBLÉMATIQUE ET PRÉPARATION DU PLAN DE                                |

| Ciini | DÉVELOPPEMENT3                                                               |

| 1.1   | Problématique rencontrée                                                     |

| 1.1.1 |                                                                              |

| 1.1.2 | Aspect sécurité et fiabilité                                                 |

| 1.1.3 | Aspect évolutif                                                              |

| 1.1.4 | Aspect énergétique                                                           |

| 1.1.5 | Aspect économique                                                            |

| 1.1.6 | Synthèse de la problématique                                                 |

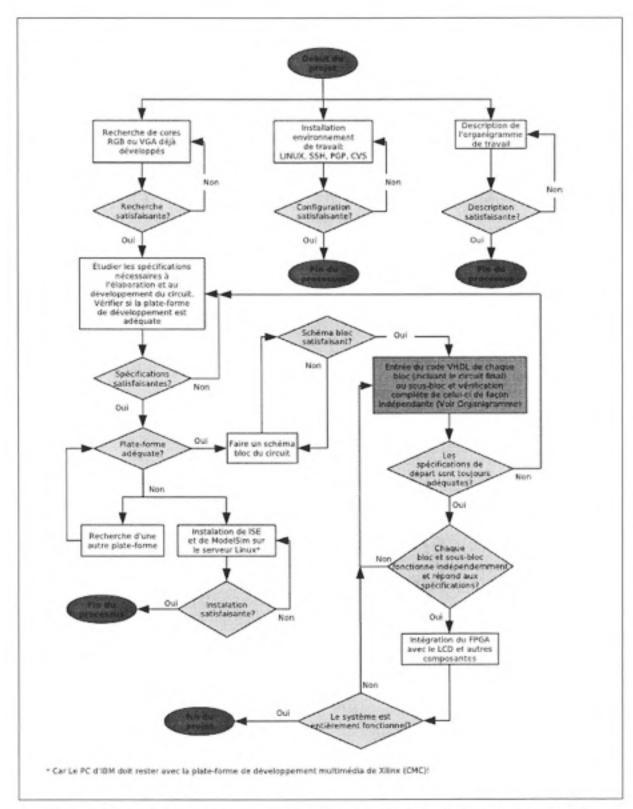

| 1.2   | Explication du plan de développement utilisé                                 |

| 1.2.1 | Recherche de cores RGB ou VGA déjà développés                                |

| 1.2.2 | Installation de l'environnement de travail et liste des logiciels utilisés10 |

| 1.2.3 | Étude des spécifications nécessaires à l'élaboration et au développement du  |

| 1.20  | circuit et choix de la plateforme de développement11                         |

| 1.2.4 | Faire un schéma bloc du circuit                                              |

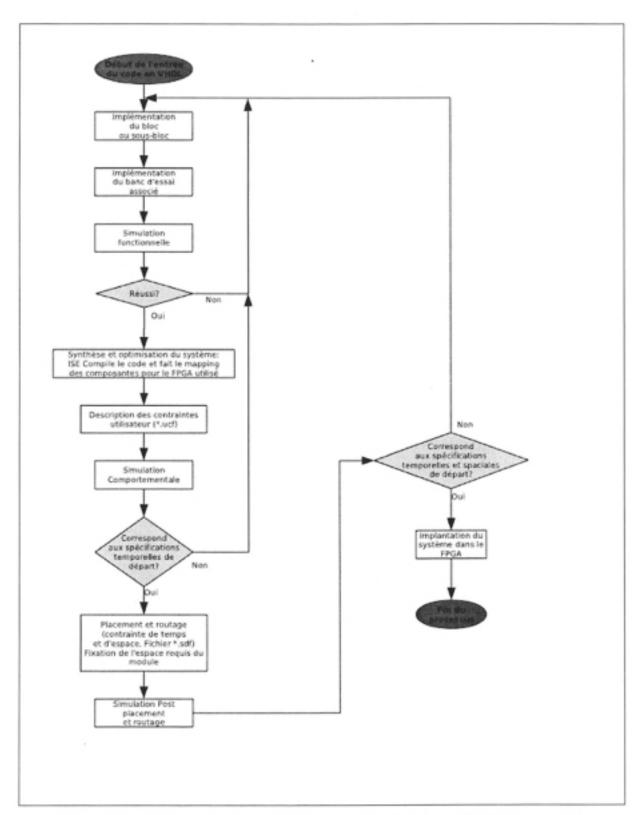

| 1.2.5 | Entrée du code VHDL en fonction du schéma bloc                               |

| 1.2.6 | Synthèse et optimisation du système                                          |

| 1.2.7 | Placement et routage                                                         |

| 1,2,, | Tracement of Tourage                                                         |

| CHAPI | TRE 2 RECHERCHE BIBLIOGRAPHIQUE DE CŒUR EXISTANT ET                          |

|       | SPÉCIFICATIONS FONCTIONNELLES PRÉLIMINAIRES DU PROJET                        |

|       | SUR LES AVN14                                                                |

| 2.1   | Spécifications de départ minimales recherchées pour le projet14              |

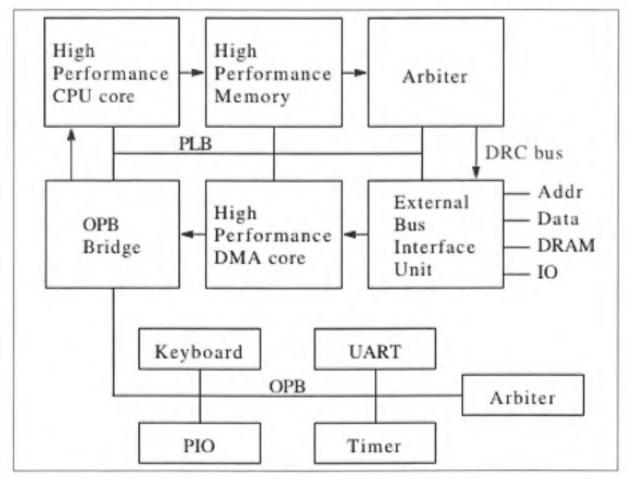

| 2.2   | Recherche sur les bus SoC                                                    |

| 2.2.1 | Bus Sériel SERDES :                                                          |

| 2.2.2 | Bus parallèle CoreConnect (IBM)16                                            |

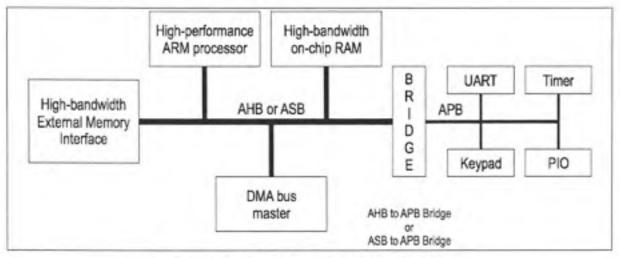

| 2.2.3 | Bus parallèle AMBA (ARM):                                                    |

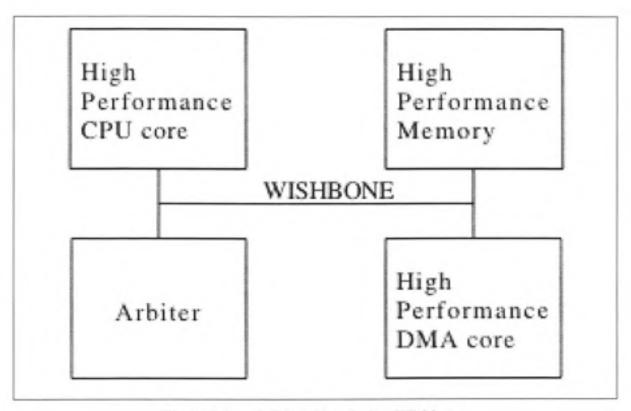

| 2.2.4 | Bus parallèle Wishbone :                                                     |

| 2.2.5 | Notre choix de BUS                                                           |

| 2.3   | Recherche sur les protocoles et signaux de sortie vidéo :                    |

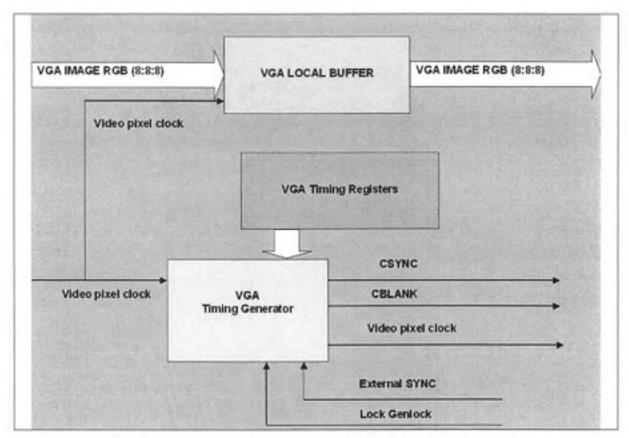

| 2.3.1 | Port RGB (ou VGA):20                                                         |

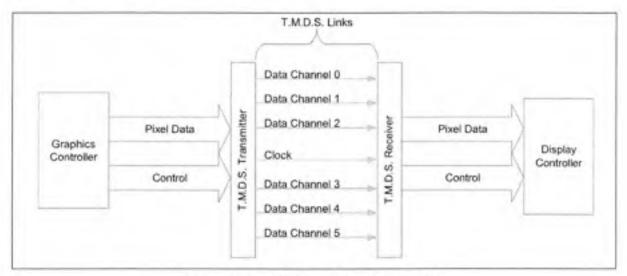

| 2.3.2 | Port de DVI (Digital Visual Interface) développé par le DDWG (Digital        |

|       | Display Working Group)20                                                     |

| 2.4   | Cores (cœurs) VGA, RGB ou DVI disponibles:                                   |

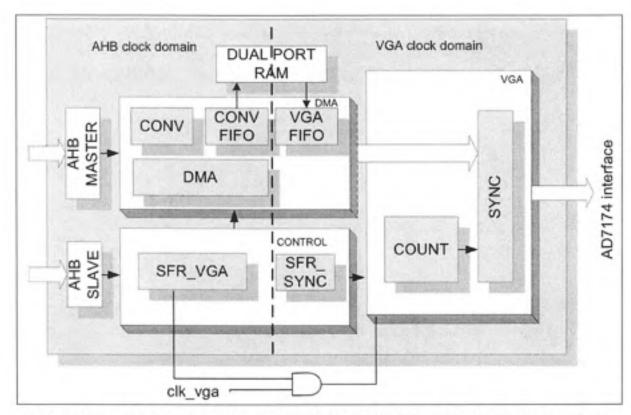

| 2.4.1 | GRLIB (Gaisler research):                                                    |

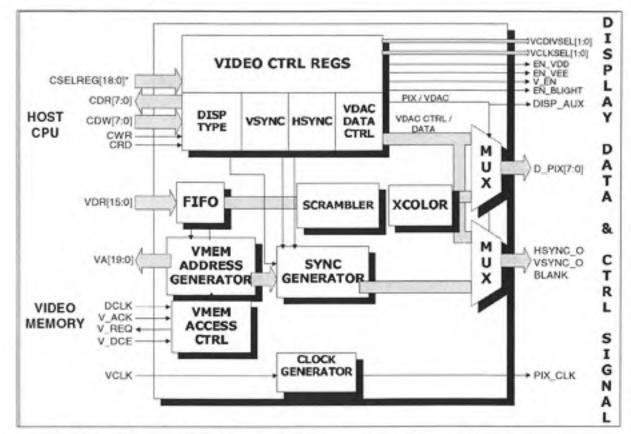

| 2.4.2 | Mistral Software: 23                                                         |

| 2.4.3  | TVOUT_CTRL (Cast inc.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.4.4  | LogiCVC Compact Video Controler (Xylon logicbricks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 2.4.5  | INT416-SXGA (Intrinsix)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

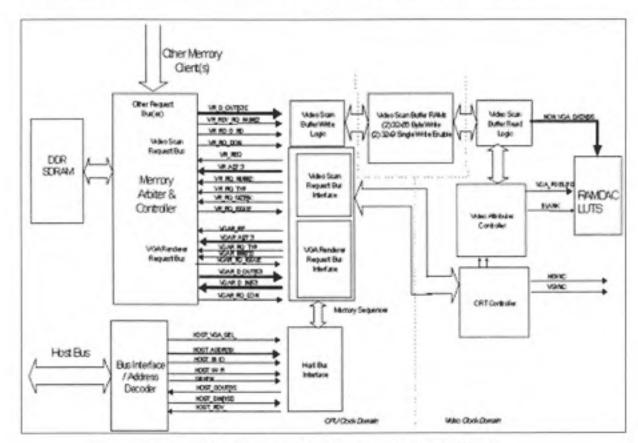

| 2.4.6  | Xilinx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 2.4.7  | Altera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 2.4.8  | Sources du laboratoire pour le cours ELE-748 de l'École de Technologie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|        | Supérieure :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31  |

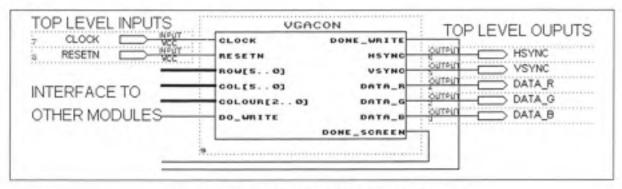

| 2.4.9  | VGACON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32  |

| 2.4.10 | XESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

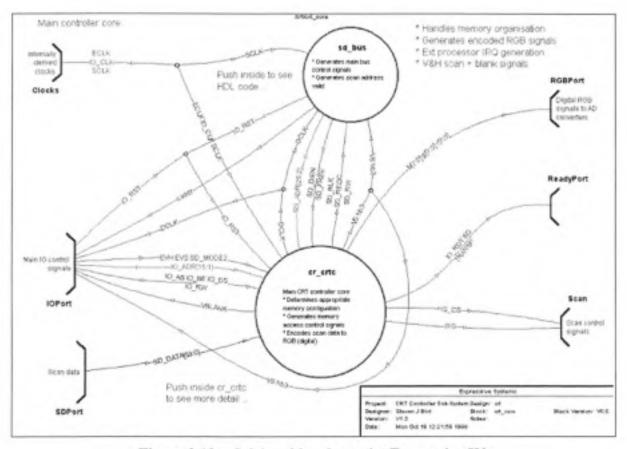

| 2.4.11 | Expressive IV (Parallel Systems co.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 2.4.12 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 2.5    | Conclusion sur le choix des spécifications fonctionnelles de départ du projet:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| CHAPE  | TRE 3 ÉTUDE DES POSSIBILITÉS DE PLATEFORMES DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| CHAIL  | DÉVELOPPEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41  |

| 3.1    | Introduction, ce qui guide notre recherche :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41  |

| 3.2    | Les solutions étudiées                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 3.2.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

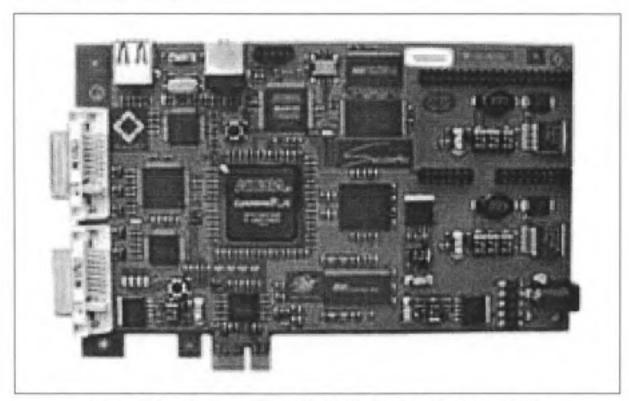

|        | 1.1 La carte Sendero développée par Microtronix :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|        | 1.1.1.1 Caractéristiques de la carte d'évaluation « Sendero »:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|        | 1.2 La Carte de développement vidéo haute performance VIODC développée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42  |

| 3.4.   | par Xilinx :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44  |

| 3.7    | 2.1.2.1 Caractéristiques de la solution vidéo haute performance de Xilinx:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46  |

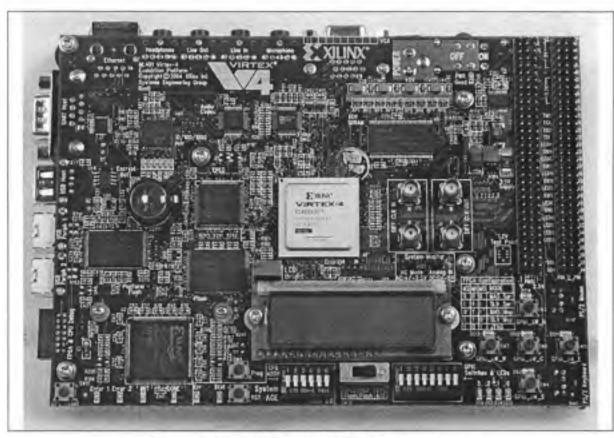

|        | 1.3 La carte ML402 :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|        | 1.3.1 Caractéristiques de la carte ML402 :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

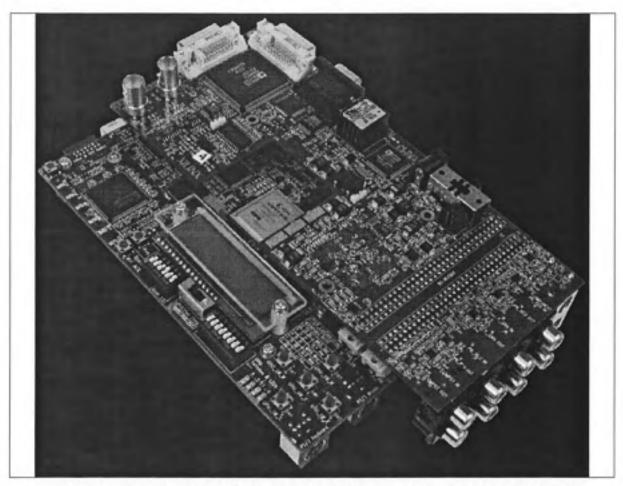

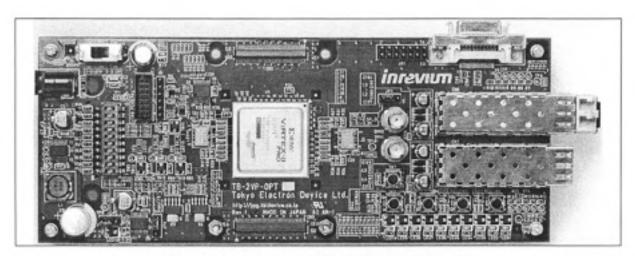

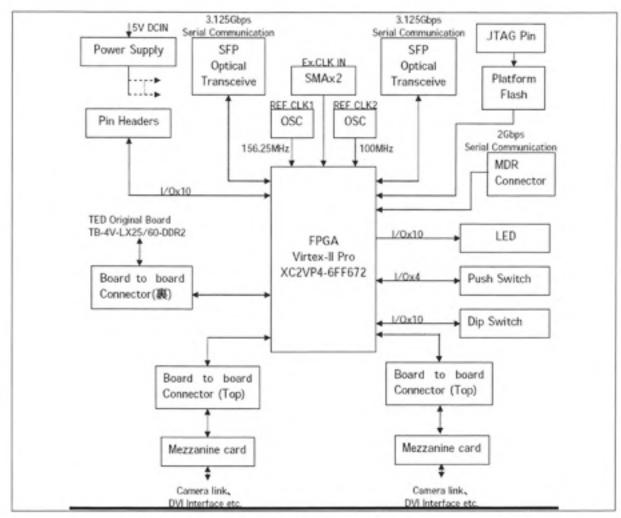

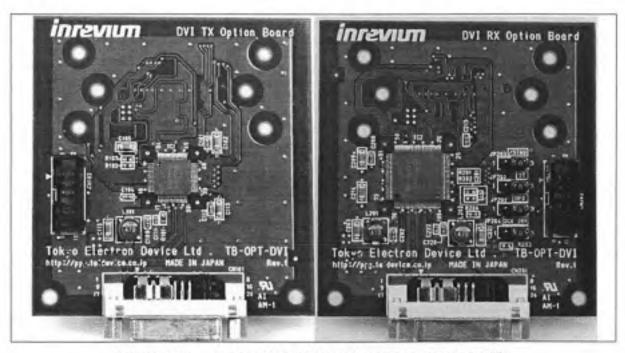

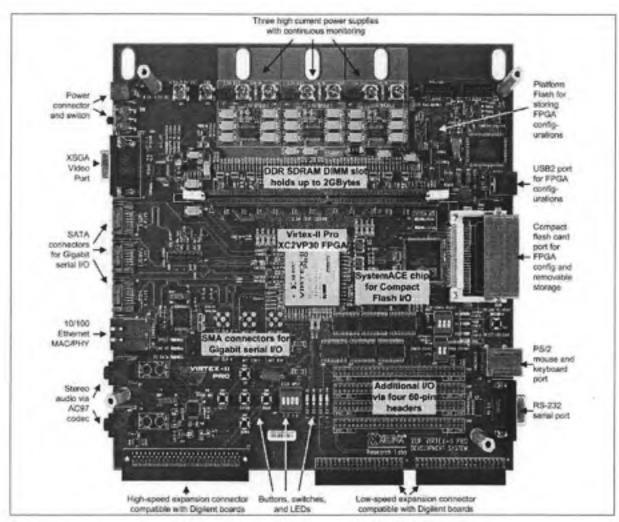

|        | 1.4 La carte TB-V2P-OPT -2G fabriquée par la compagnie Inrevium :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|        | 1.1.4.1 Les caractéristiques de la solution avec la carte TB-V2P-OPT -2G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40  |

| 3.2    | d'Inrivium:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51  |

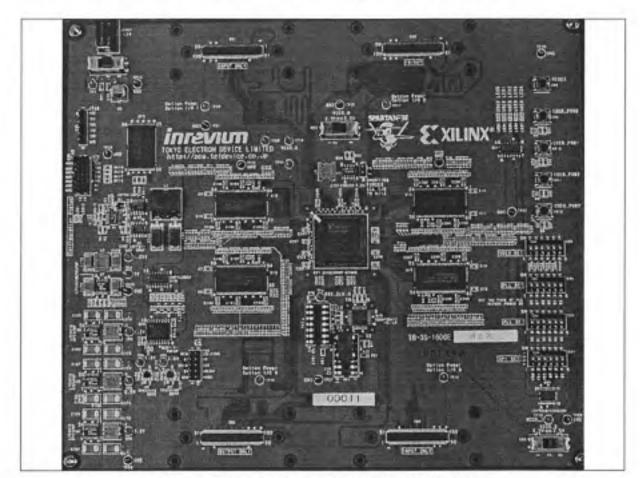

| 32     | 1.5 La carte TB-3S-1600E-IMG de la compagnie Inrevium :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .52 |

|        | .1.5.1 Les caractéristiques de la carte TB-3S-1600E-IMG:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|        | 1.6 La carte TB-3S-1500-IMG de Xilinx :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|        | 1.1.6.1 Les caractéristiques de la plateforme de développement TB-3S-1500-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 27.4   | IMG:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 3.2.2  | Les solutions composées de plusieurs pièces provenant de manufacturiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |