### ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# MODEL-BASED TECHNIQUES FOR THE FUTURE INTEGRATION FOR FORMAL VERIFICATION OF CRITICAL REAL-TIME SOFTWARE SYSTEMS

BY Tiyam Robati

### THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph. D.

MONTREAL, 19 OCTOBER 2016

##

This Creative Commons license allows readers to download this work and share it with others as long as the author is credited. The content of this work cannot be modified in any way or used commercially.

### **BOARD OF EXAMINERS**

### THIS THESIS HAS BEEN EVALUATED

### BY THE FOLLOWING BOARD OF EXAMINERS:

M. Abdelouahed Gherbi, Thesis Supervisor Département de génie logiciel et des TI, École de technologie supérieure

M. Michel Kadoch, President of the Board of Examiners Département de génie électrique, École de technologie supérieure

M. Alain April, Member of the jury Département de génie logiciel et des TI, École de technologie supérieure

Mme. Yosr Jarraya, External Examiner Researcher, Ericsson Canada

### THIS THESIS WAS PRESENTED AND DEFENDED

### IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

### ACKNOWLEDGEMENTS

Family is one of nature's masterpieces (George Santayana). I would like to dedicate this thesis to my father, Mohammad Jafar Robati, for supporting me spiritually throughout my life. I am sure he would be very happy and proud of me. I would like to thank my mother and my brother for spending by me through the good and challenging times. Finally, to my lovely son, Diyako, who is the light of my life.

I would like to express my deepest gratitude to my advisor, Dr. Abdelouahed Gherbi, for his guidance, motivation, patience, and for providing me with an excellent atmosphere for my research.

I would like to acknowledge the contribution of Bombardier Aerospace, CMC Electronics and CRIAQ for providing the finance of this study.

### TECHNIQUES BASÉES SUR UN MODÈLE POUR L'INTÉGRATION ET LA VÉRIFICATION FORMELLE DE SYSTÈMES LOGICIELS CRITIQUES EN TEMPS RÉEL

#### Tiyam Robati

### RÉSUMÉ

Les architectures avioniques modulaires intégrées combinées avec la norme SAE TTEthernet constituent une infrastructure solide pour le déploiement des applications avioniques a criticités mixtes ayant des exigences strictes en termes de sécurité, fiabilité et de performance. L'intégration de tels systèmes est une tâche d'ingénierie complexe et difficile. Par conséquent, l'approche basée sur les modèles qui offre aux ingénieurs systèmes une méthodologie et les outils de support pour maitriser cette complexité, est d'une grande importance. Dans cette thèse, nous présentons une extension pour le langage de modélisation AADL pour supporter la modélisation des applications avioniques à criticités mixtes déployées sur des architectures IMA basées sur TTEthernet. En particulier, nous présentons un méta-modèle qui étend le métamodèle de base de AADL avec les concepts et les contraintes de ce domaine. Nous définissons une syntaxe textuelle concrète pour cette extension ainsi que l'implémentation de cette extension en utilisant l'outil OSATE. Par la suite, on construit par-dessus notre extension du langage AADL et nous utilisons les transformations de modèles pour supporter la vérification des modèles de systèmes produits avec cette méthodologie. En particulier, nous proposons une transformation des modèles de systèmes en modèles convenables à la simulation avec DEVs. Finalement, nous illustrons l'approche proposée via une étude de cas fournies par Bombardier, notre partenaire industriel dans le projet. Nous utilisons cette étude de cas pour démontrer notre extension et procéder à la vérification de la contrainte contention-freedom d'un ordonnancement TTEthernet.

**Mots clés:** Système Critique, IMA, TTEthernet, ARINC 653, AFDX, AADL, La Vérification, DEVS

### MODEL-BASED TECHNIQUES FOR THE FUTURE INTEGRATION FOR FORMAL VERIFICATION OF CRITICAL REAL-TIME SOFTWARE SYSTEMS

Tiyam Robati

### ABSTRACT

Integrated modular avionics architectures combined with the emerging SAE TTEthernet standard provides a strong infrastructure for the deployment of mixed-critical avionic applications that meet stringent safety, reliability and performance requirements. Integrating these systems is a complex and challenging engineering task. Of paramount importance is the development of a model-based approach that can endow system engineers with a methodology and supporting tools to cope with this complexity. In this thesis, we present an extension of AADL, the standard language used for architecture and analysis modeling, in order to enable the modeling of integrated multi-critical avionic applications deployed on TTEthernet-based IMA architectures. To do this, we first present a metamodel for the TTEthernet domain followed by an extension of the core AADL metamodel with concepts and constraints relevant for this domain. In doing so, we define the concrete textual syntax for this extension, and we outline the implementation of this extension using the Open Source AADL Tool Environment (OSATE). To verify the AADL model for TTEthernet, we build on our extension of AADL and leverage model transformations to assess the system models produced with this methodology. In this process, we transform the system models to a target model that is compatible with DEVS formalism in its dedicated simulation environment.

We illustrate the proposed approach using a case study provided by Bombardier, our industrial partner in this project, and we show the benefits of our AADL extension and verification approach to the *contention-freedom* property of the TTEthernet schedule.

**Keywords:** Critical system, IMA, TTEthernet, ARINC 653, AFDX, AADL, Verification, DEVS

### TABLE OF CONTENTS

| INTRO | ODUCTI                 | ON                                          | . 1  |  |

|-------|------------------------|---------------------------------------------|------|--|

| 0.1   | Problem Statement      |                                             |      |  |

| 0.2   | Research Objective     |                                             |      |  |

| 0.3   | Research Contributions |                                             |      |  |

| 0.4   |                        | ion                                         |      |  |

| 0.5   |                        | Drganization                                |      |  |

| 010   | 1110010                |                                             |      |  |

| CHAP  | TER 1                  | BACKGROUND                                  | 7    |  |

| 1.1   | Time-Tr                | iggered Architecture (TTA)                  | 7    |  |

| 1.2   |                        | iggered Protocol (TTP)                      |      |  |

|       | 1.2.1                  | Time-Triggered Transmission                 |      |  |

|       | 1.2.2                  | Rate-Constrained Transmission               |      |  |

|       | 1.2.3                  | Data Flow integration                       |      |  |

| 1.3   | Time-Tr                | iggered Ethernet (TTEthernet)               |      |  |

| 1.4   |                        | ed Modular Avionic Architecture (IMA)       |      |  |

|       | 1.4.1                  | ARINC 653                                   |      |  |

|       | 1.4.2                  | ARINC664 part7, AFDX                        |      |  |

| 1.5   | Model-I                | Driven Engineering Approach                 |      |  |

| 1.6   |                        | hitecture Analysis Design Language (AADL)   |      |  |

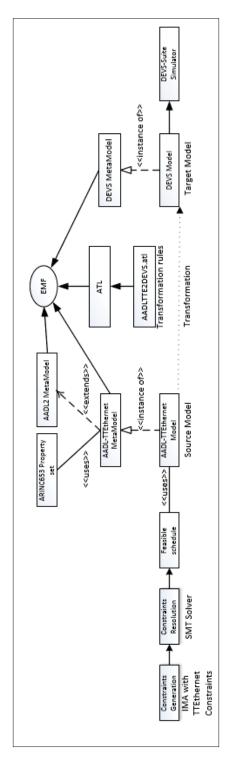

| 110   | 1.6.1                  | AADL Annexes                                |      |  |

|       | 1.0.1                  | 1.6.1.1 Behavioral Annex                    |      |  |

|       |                        | 1.6.1.2 ARINC 653 Annex                     |      |  |

| 1.7   | Verificat              | tion and Simulation Techniques              |      |  |

| 1.7   | 1.7.1                  | Discrete Event System Specification (DEVS)  |      |  |

|       | 1./.1                  | Discrete Livent System Specification (DLVS) | . 50 |  |

| CHAP  | TER 2                  | RELATED WORK                                | . 33 |  |

| 2.1   | TTEther                | rnet-based platform                         |      |  |

| 2.2   |                        | chitecture                                  |      |  |

| 2.3   |                        |                                             |      |  |

| 2.4   |                        |                                             |      |  |

|       |                        |                                             |      |  |

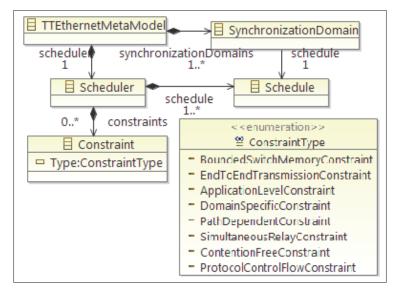

| CHAP  | TER 3                  | TIME-TRIGGERED ETHERNET METAMODEL           | . 37 |  |

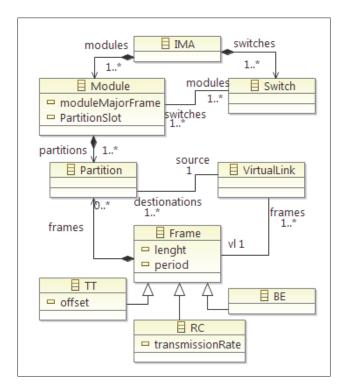

| 3.1   | TTEther                | rnet Model                                  | . 37 |  |

| 3.2   | A Metai                | nodel for TTEthernet Domain                 | . 39 |  |

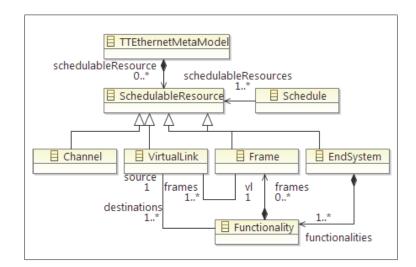

|       | 3.2.1                  | Schedulable Resources                       | . 42 |  |

|       | 3.2.2                  | Channel                                     |      |  |

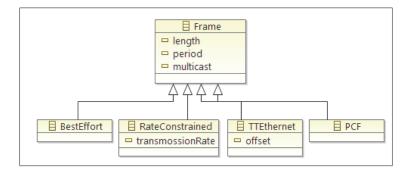

|       | 3.2.3                  | Frames                                      |      |  |

|       | 3.2.4                  | Scheduler                                   |      |  |

|       | 3.2.5                  | The Metamodel of IMA                        |      |  |

| 3.3   |                        | ion                                         |      |  |

|       |                        |                                             | -    |  |

### Page

| CHAPTER 4 |                                                | AN EXTENSION FOR AADL TO MODEL MIXED-CRITICAL                |    |

|-----------|------------------------------------------------|--------------------------------------------------------------|----|

|           | AVIONIC SYSTEMS DEPLOYED ON IMA ARCHITECTURES  |                                                              |    |

|           |                                                | WITH TTETHERNET                                              | 47 |

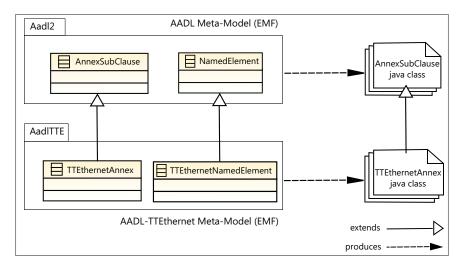

| 4.1       | Metamo                                         | del Extending AADL capability to model TTEthernet            | 47 |

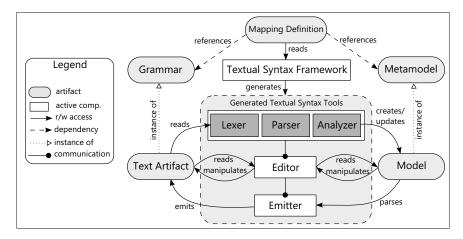

| 4.2       | Textual S                                      | Syntax for the TTEthernet Extension for AADL                 | 48 |

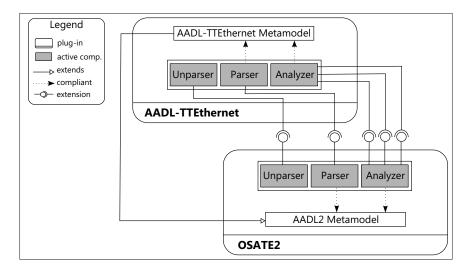

|           | 4.2.1                                          | Integration of the AADL-TTEthernet Compiler to OSATE2        | 49 |

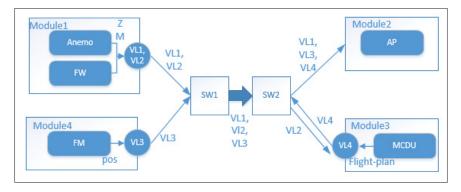

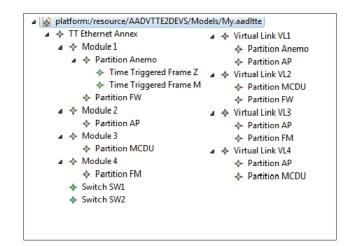

| 4.3       | An Exan                                        | nple: A Model of a Subsystem of the Flight Management System | 50 |

| 4.4       | Conclusi                                       | ion                                                          | 53 |

|           |                                                |                                                              |    |

| CHAPTER 5 |                                                | VERIFICATION APPROACH TO THE DESIGN OF DISTRIBUTED           |    |

|           |                                                | IMA ARCHITECTURES USING TTETHERNET                           | 55 |

| 5.1       | Verificat                                      | ion Approach                                                 | 55 |

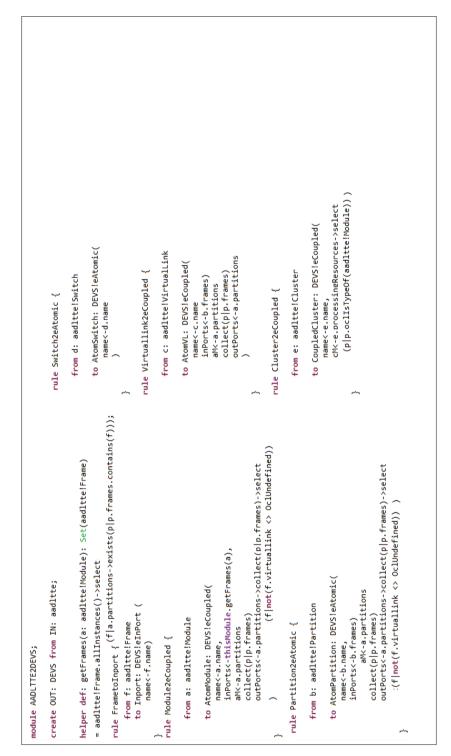

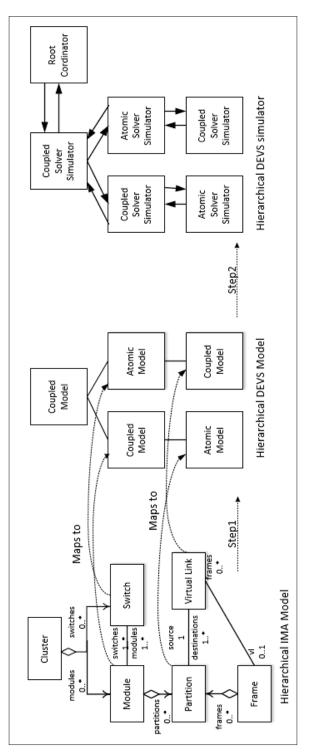

| 5.2       | Simulation of the Navigation & Guidance System |                                                              | 61 |

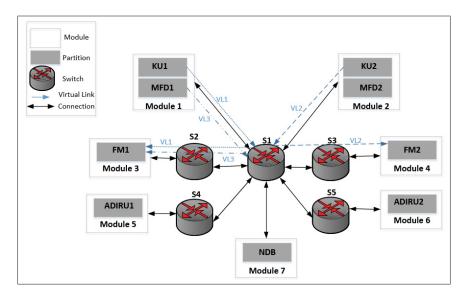

|           | 5.2.1                                          | System Description                                           | 61 |

|           | 5.2.2                                          | Model Transformation                                         | 62 |

|           | 5.2.3                                          | Property verification: Contention-Freedom                    | 62 |

| 5.3       | Conclusi                                       | ion                                                          |    |

| CHAP'     | TER 6                                          | CASE STUDY                                                   | 67 |

| 6.1       | System I                                       | Description                                                  | 67 |

| 6.2       | Property                                       | verification: Contention-Freedom                             | 69 |

| CONC      | LUSION                                         | AND RECOMMENDATIONS                                          | 75 |

| BIBLI     | OGRAPH                                         | IY                                                           | 78 |

### LIST OF TABLES

|           |                                                       | Page |

|-----------|-------------------------------------------------------|------|

| Table 3.1 | TTEthernet levels                                     | 38   |

| Table 3.2 | IMA metamodel in accordance with TTEthernet metamodel | 46   |

| Table 4.1 | Virtual Links details                                 | 52   |

| Table 5.1 | Mapping source model into target model                | 58   |

| Table 6.1 | Virtual Links detail                                  | 69   |

### LIST OF FIGURES

Page

| Figure 1.1  | TTP example                                         |

|-------------|-----------------------------------------------------|

| Figure 1.2  | TTP example                                         |

| Figure 1.3  | Integration Method                                  |

| Figure 1.4  | Federated Architecture V.S. IMA Architecture        |

| Figure 1.5  | An Example of ARINC 653 RTOS 17                     |

| Figure 1.6  | ARINC 653 module with two partitions                |

| Figure 1.7  | ARINC 653 hierarchical scheduling example           |

| Figure 1.8  | Virtual Link                                        |

| Figure 1.9  | Virtual Link Flow Regulation                        |

| Figure 1.10 | The Scheduler Flow of Virtual Link                  |

| Figure 1.11 | The Jitter Effect for a Maximum Bandwidth Data Flow |

| Figure 1.12 | Model transformation pattern                        |

| Figure 1.13 | ATL overview                                        |

| Figure 1.14 | Integration Method                                  |

| Figure 1.15 | DEVS a common formalism                             |

| Figure 3.1  | TTEthernet network                                  |

| Figure 3.2  | TTEthernet Multi Cluster                            |

| Figure 3.3  | TTEthernet Cluster                                  |

| Figure 3.4  | TTEthernet Metamodel                                |

| Figure 3.5  | TTEthernet Metamodel Overview                       |

| Figure 3.6  | Schedulable Resources                               |

| Figure 3.7  | Frame Categories                                    |

| Figure 3.8 | TTEthernet Scheduler                                                 |

|------------|----------------------------------------------------------------------|

| Figure 3.9 | The metamodel of IMA 45                                              |

| Figure 4.1 | AADL-TTEthernet metamodel dependencies                               |

| Figure 4.2 | General structure of a textual syntax framework                      |

| Figure 4.3 | xText grammar overview for AADL-TTEthernet                           |

| Figure 4.4 | AADL-TTEthernet plug-in integrated to OSATE251                       |

| Figure 4.5 | A subsystem of the Flight Management System51                        |

| Figure 4.6 | Flight Management Subsystem Model using AADL TTEthernet<br>Extension |

| Figure 5.1 | Overall Architecture                                                 |

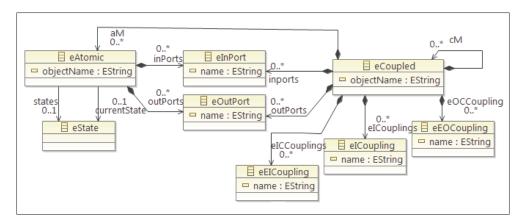

| Figure 5.2 | DEVS metamodel                                                       |

| Figure 5.3 | ATL transformation rules                                             |

| Figure 5.4 | Mapping a hierarchical model onto a hierarchical simulator           |

| Figure 5.5 | The Navigation & Guidance system62                                   |

| Figure 5.6 | Textual Syntax                                                       |

| Figure 5.7 | TTEthernet Model                                                     |

| Figure 5.8 | The corresponding DEVS model                                         |

| Figure 5.9 | Simulation graph for the navigation & guidance system                |

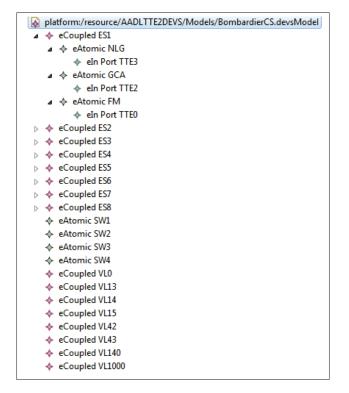

| Figure 6.1 | Case study                                                           |

| Figure 6.2 | Textual Syntax                                                       |

| Figure 6.3 | The AADL TTEthernet model71                                          |

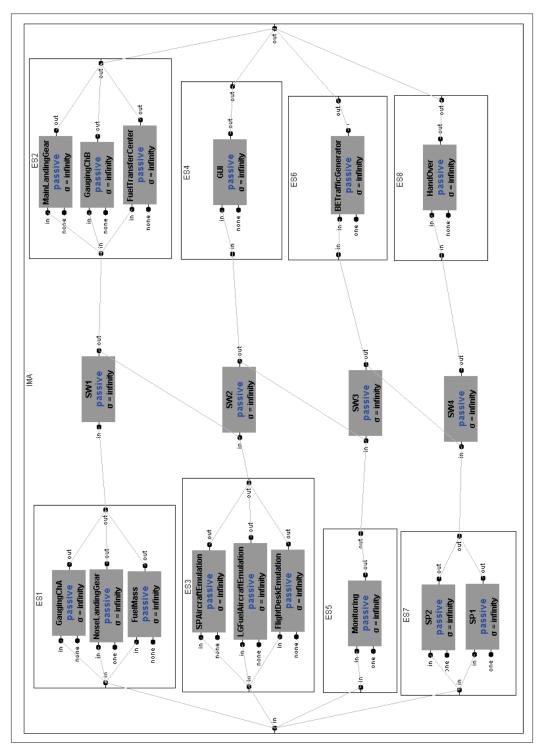

| Figure 6.4 | The DEVS model                                                       |

| Figure 6.5 | Simulation graph for Case study73                                    |

### LIST OF ABREVIATIONS

| Ν | MDE               | Model-Driven Engineering                |

|---|-------------------|-----------------------------------------|

| Ι | MA                | Integrated Modular Avionics             |

| ] | <b>ITEthernet</b> | Time Triggered Ethernet                 |

| I | ARINC             | Aeronautical Radio, Incorporated        |

| I | AFDX              | Avionics Full-Duplex Switched Ethernet  |

| I | AADL              | Architecture Analysis & Design Language |

| Ι | DEVS              | Discrete Event System Specification     |

| S | SAE               | Society of Automotive Engineers         |

| ] | ГТЕ               | Time-Triggered Ethernet                 |

| ł | RC                | Rate-constrained                        |

| I | BE                | Best Effort                             |

| ] | ГТА               | Time-Triggered Architecture             |

| ] | ГТР               | Time-Triggered Protocol                 |

| S | SC                | Synchronization Client                  |

| S | SM                | Synchronization Master                  |

| ( | CM                | Compression Master                      |

| V | VL                | Virtual Link                            |

| ł | FMS               | Flight Management System                |

#### **INTRODUCTION**

Avionic systems belong to the class of safety-critical systems that must meet strict safety, reliability and real-time requirements. These systems were designed to used as federated architectures, where each software function is designed and deployed to use exclusive resources. This approach, however, is costly in terms of equipment and wiring. Today, most avionic systems are based on Integrated Modular Avionics (IMA) architectures, where several system functions, each having different levels of safety and performance, might be deployed in the same computing module (e.g. control functions and comfort functions). In fact, IMA architectures are based on an isolation of resources Watkins and Walter (2007), which is achieved through resource sharing between functionalities. IMA-based avionic systems, therefore, demonstrate mixedcriticality and require solid isolation and partitioning. These features are supported in IMA with operating systems and executives compliant with the ARINC 653 standard Aerospace (2011b). IMA architectures are distributed using a communication infrastructure, which can meet the same level of safety and performance requirements.

Ethernet is a widely used standard network (IEEE 802.3) that is not only used as infrastructure for classic office systems but is increasingly used to support industrial and embedded systems due to the high bandwidths it provides. However, Ethernet does not meet strict time constraints for safety critical applications. Several extensions to enhance the predictability of Ethernet have been developed. One of these extensions is the Avionic Full Duplex AFDX standard, ARINC 664 part 7 Incorporated (2009). AFDX is a deterministic real-time extension of Ethernet based on static bandwidth scheduling and control using the concept of virtual links. The Society of Automotive Engineers' (SAE) standard TTEthernet Aerospace (2011d), which was designed to achieve bounded latency and low jitter, is the most recent Ethernet extension based on the time-triggered communication paradigm Kopetz and Bauer (2003) and Obermaisser (2004). A TTEthernet network implements a global time using clock synchronization and offers fault isolation mechanisms to manage channel and node failures. TTEthernet integrates

three types of data flow: Time-Triggered (TT) data flow, which is the highest priority flow; Rate Constrained (RC) data flow, also known as AFDX traffic; and Best Effort (BE) data flow. This makes TTEthernet suitable for mixed-criticality applications, such as avionic and automotive applications, where highly critical control functions (e.g. flight management systems) cohabit with less critical functions (e.g. entertainment systems).

IMA architectures with TTEthernet provide a platform to integrate avionic systems and applications with particular features suitable to particular needs. This platform provides error isolation both at the module level, through time and space partitioning, and at the network level, by integrating differentiated data flows. The focus of this research is on avionic applications deployed on IMA architectures interconnected using TTEthernet. The advantages of this infrastructure are numerous (resource sharing, error isolation, integration of data flows). However, these systems are also complex, and the integration of diverse applications with mixed-criticality levels capable of meeting strict real-time constraints is very challenging. In order to control the complexity of such systems, a model-based approach is required which provides system engineers with a methodology and supporting tools to accomplish this integration correctly and efficiently.

A key element of this approach is a modeling language that can allow engineers to express the system at a convenient level of abstraction and to interface with sophisticated formal analysis techniques to verify the safety and performance properties of the system. Architecture Analysis and Design Language (AADL) is a well-established standard modeling language used in the domain of real-time critical systems. AADL has been extended to support the modeling of IMA with an Annex ARINC 653 Aerospace (2011b). However, there is as yet no support for AADL to model the networking of IMA modules through TTEthernet.

### 0.1 Problem Statement

Mixed-critical applications deployed on distributed architectures are an important issue in many engineering domains. TTEthernet can enrich these architectures and provide an infrastructure with numerous advantages. These advantages are obtained from the combination of distributed architecture (e.g. resource sharing) and TTEthernet (e.g. fault-tolerant). However, the integration of these systems is complex and challenging. To cope with the complex integration of such an infrastructure, we advocate for a model-driven engineering approach (MDE). MDE allows us to produce a methodology that can develop supporting tools that hide the complexity of runtime phenomena from system engineers. Furthermore, using verification techniques, system engineers can ensure that the integration has been accomplished correctly and efficiently. The key element of such an approach is a modeling language that can allow the engineers to express the system at a convenient level of abstraction. The engineers then can set up an interface between the model and tools for sophisticated formal analysis techniques to verify the safety and performance properties of the system. Briefly, the main observations of our research project are summarized as follows:

- There is as yet no modeling framework for IMA architecture interconnected with TTEthernet.

- AADL is a convenient modeling language that has also been used to develop ARINC 653 annex; however, AADL does not support network modeling.

- There is a need for automatic verification of TTEthernet requirements and constraints deployed on distributed systems such as IMA.

### 0.2 Research Objective

The main objectives of our research are as follows:

- a. *Objective 1*: Define and implement an extension for the standard architecture and analysis modeling language AADL to enable the modeling of integrated multi-critical avionic applications deployed on TTEthernet-based IMA architectures.

- b. *Objective 2*: Develop a verification approach for the system models produced by our extension of the AADL modeling language.

- c. *Objective 3*: Validate our proposed approach using a real-world case study provided by our industrial partner.

### 0.3 Research Contributions

The main contributions of this thesis consist in the definition of an MDE approach to support system engineers in using TTEthernet. More specifically our contributions involve:

- A metamodel of the TTEthernet standard; we developed a metamodel to support the SAE TTEthernet standard, AS6802 Aerospace (2011d) for distributed architectures on which safety-critical applications are deployed.

- b. An extension for AADL to model mixed-criticality avionic systems deployed on IMA architectures with TTEthernet. This AADL-TTEthernet metamodel describes the structural aspects of a distributed IMA system interconnected using TTEthernet and makes explicit all concepts specified by this standard.

- c. A model-based approach to automate the verification of AADL models for extension.

We used model transformation techniques to map the AADL-TTEthernet metamodel to the DEVS metamodel in order to simulate the output model using the DEVS simulation environment.

- d. Collaboration with SAE AADL committee in developing the AADL networking annex.

#### **0.4 Publication**

The main outcome of this thesis in terms of scientific publications are four accepted conference and journal papers and one submitted journal paper. These publications are reported in following:

- An Extension for AADL to Model Mixed-Criticality Avionic Systems Deployed on IMA architectures with TTEthernet. 1st Workshop on Architecture Centric Virtual Integration@ the 17th International Conference on Model Driven Engineering Languages and Systems (MoDELS 2014)

- b. Simulation-Based Verification of Avionic Systems Deployed on IMA Architectures. ACM/IEEE

18th International Conference on Model Driven Engineering Languages and Systems (MoDELS'15).

- c. A Modeling and Verification Approach to the Design of Distributed IMA Architectures using TTEthernet. The 7th International Conference on Ambient Systems, Networks and Technologies (ANT 2016). Procedia Computer Science 83, 229-236.

- d. Time-Triggered Ethernet Metamodel: Design and Application. Journal of software (JSW Vol. 11, No. 10, October 2016)

- e. Design and Simulation of Distributed IMA Architectures using TTEthernet: A Model-Driven Approach. Journal of Ambient Intelligence and Humanized Computing (SI-JAIHC-2016)

### 0.5 Thesis Organization

This thesis is organized in six chapters. In Chapter 1, we introduce the main concepts and terms that are used in this thesis. In Chapter 2, we succinctly review the most closely related

research to our own. Chapter 3 outlines the metamodel of TTEthernet, and this is followed in Chapter 4 by a definition of the AADL extension to support the TTEthernet metamodel. Chapter 5 describes the automatic verification and validation methodology. In Chapter 6, we demonstrates the application of the proposed extension with an illustrative case study. Finally, Conclusion presents our conclusion of the thesis.

#### **CHAPTER 1**

#### BACKGROUND

In order to make this thesis as self-contained as possible, we introduce in this chapter the main concepts of Model-Driven Engineering, TTEthernet, IMA architecture, AADL modeling language and the DEVS simulation environment. These are the main concepts that we are using them in following chapters.

#### **1.1 Time-Triggered Architecture (TTA)**

Time-Triggered Architecture (TTA) acts as the computing infrastructure for distributed safetycritical real-time systems. It distributes safety-critical applications into clusters and nodes, and it establishes a fault tolerant global time for the whole system. This global time specifies the communication protocol between clusters and nodes accordingly. It also guarantees time-lines for real-time applications and instant error detection. TTA is based on the Time-Triggered communication protocol (TTP).

#### **1.2 Time-Triggered Protocol (TTP)**

TTP has been implemented and used in different domains such as FlexRay in the automotive industry, SAFEbus for serial production and the avionics industry. It is also used for the Airbus A380 and Boeing 787 Kopetz (2003). TTP presents a deterministic, synchronized and congestion-free network based on the IEEE 802.3 Ethernet protocol and is compliant with AR-INC 664 part7. Figure 1.1 taken from Domitian Tamas-Selicean and Steiner (2012), provides an example of how this protocol functions.

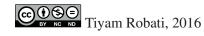

In this example, there are two *End-Systems*,  $ES_1$  and  $ES_2$ , and three network *Switches*,  $NS_1$  to  $NS_3$ . Task  $T_2$  on  $ES_1$  sends the TT message  $m_2$  to task  $T_4$ , which is mapped on  $ES_2$ , while task  $T_1$  on  $ES_1$  sends the RC message  $m_1$  to task  $T_3$  on  $ES_2$ . This is assuming that tasks  $T_1$  and  $T_3$  are part of application  $A_1$  and tasks  $T_2$  and  $T_4$  belong to application  $A_2$ . Furthermore,  $A_1$  and

Figure 1.1 TTP example

$A_2$  introduce different levels of safety-criticality. The isolation of the applications is achieved at the CPU-level through partitioning. Thus, tasks  $T_1$  and  $T_3$  are placed in partitions  $P_{1,1}$  and  $P_{2,2}$ , respectively, while tasks  $T_2$  and  $T_4$  are assigned to partitions  $P_{1,2}$  and  $P_{2,1}$ , respectively. Message  $m_1$  is sent by application  $A_1$  and packed in frame  $f_1$ , and  $m_2$  is sent by  $A_2$  and packed into frame  $f_2$ . There are two different virtual links,  $vl_1$  and  $vl_2$  (not depicted in the figure), in order to separate the different criticality frames. Frames  $f_1$  and  $f_2$  are transmitted by the switch  $NS_1$ , which also forwards frames  $f_3$  and  $f_4$  from  $NS_2$  and  $NS_3$ , respectively.

#### 1.2.1 Time-Triggered Transmission

In step (a), task  $T_2$  packs  $m_2$  into frame  $f_2$ . Then, in step (b),  $f_2$  is placed into buffer  $B_{1.Tx}$  to prepare it for transmission. There is one buffer for every TT message sent from  $ES_1$ . There are always static communication schedules that are stored in the form of tables, referred to as routing tables in *ESs* and *NSs*. These tables are produced off-line. In this example, the schedule is shown by *S*. In step (d),  $f_2$ , which is a TT task, is sent to  $NS_1$ . The duration of this transformation is determined by the schedule and is stored in the *S* of  $ES_1$  in step (c). Generally, TT tasks are scheduled to be sent before the next scheduled message for transmission. In step (e),  $f_2$  is sent to  $NS_1$  through a dataflow link. The Filtering Unit (FU) checks the integrity and validity of frame  $f_2$  in step (f) and forwards it to the TT receiver task,  $TT_R$ , in step (h), which then copies it into sending buffer  $B_{1,Tx}$  for later transmission. In the last step,  $f_2$  is sent by the TT sender task in  $NS_1$  to  $NS_2$ . Then, in step (k),  $f_2$  arrives at  $ES_2$ , and the FU stores the frame in buffer  $B_{2,Rx}$ . The task  $T_4$ , then, is activated to read  $f_2$  from buffer (m).

#### **1.2.2 Rate-Constrained Transmission**

The example of Figure 1.1 shows the Rate-Constrained (RC) transmission, where RC traffic presents event-triggered messages. Frame  $f_1$  is then sent from  $T_1$  on  $ES_1$  to  $T_3$  on  $ES_2$ .  $T_1$  packs message  $m_1$  into frame  $f_1$  in step (1) and inserts it into a queue  $Q_{1,Tx}$  in step (2). There is one queue per virtual link, where each  $vl_i$  carrying an RC frame  $f_i$  has a Bandwidth Allocation Gap (BAG). The BAG is calculated and enforced by the Traffic Regulator (TR) task.  $TR_1$  in  $ES_1$  ensures that each  $BAG_1$  interval contains one instance of  $f_1$  shown in step (3). Therefore, each frame leaves the TR task within a specified BAG. The maximum bandwidth used by a  $vl_i$  transmitting an RC frame  $f_i$  is calculated by the Equation 1.1:

$$BW(vl_i) = f_{i.size}/BAG_i \tag{1.1}$$

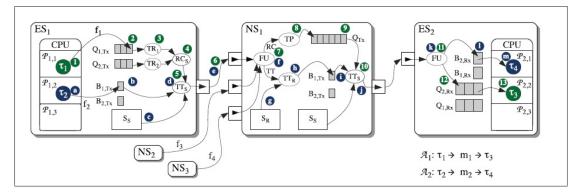

An *ES* can send several messages due to the multiplexing properties of RC messages. Figure 1.2 taken from Domitian Tamas-Selicean and Steiner (2012), demonstrates how the multiplexing of two RC flows coming from  $TR_i$  is done. Two RC flows,  $f_x$  and  $f_y$ , each with a specified size and BAG are illustrated in line (a) and (b). Line (c) shows how the multiplexed flow is performed on the outgoing dataflow link. As demonstrated in line (c),  $f_{y,1}$  was delayed with jitter ( $f_{y,1,jitter}$ ) in order to allow for the complete transmission of  $f_x$ .

#### **1.2.3** Data Flow integration

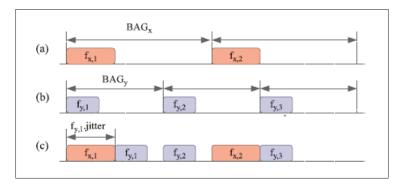

This section seeks to describe the mechanisms and consequences of the integration of TT and RC dataflow on the single physical platform. There are three different ways to accomplish this integration: Preemption, Timely Block and Shuffling. As shown in Figure 1.3 taken from Wilfried Steiner and Varadarajan (2009), the purpose of these three integration mechanisms is

Figure 1.2 TTP example

to clarify when a concurrency exists between two messages with different priorities and what decision should be taken in such a case. If these messages have the same priority, they will be served in FIFO, but in the case of unequal priority, the message with high-priority (H) is served and the message with low-priority (L) will be queued.

Figure 1.3 Integration Method

Preemption stops the process of relaying message L when message H arrives. The switch takes a minimum of silence time and relays the message H. This mechanism introduces the constant and a priori known latency for message H. But the truncated messages could appear incorrectly to the receiver, which is one of the issues with the preemption mechanism. Two possible solutions to this are first, to include the message length within the message second, to use a signal pattern that violates the line encoding rules when a message is truncated. If a fraction of a truncated message is lost, the whole message will be retransmitted; this causes a loss of bandwidth due to the truncation. Timely Block is a mechanism that ensures switches

will not forward messages at those times that TT messages are expected. This mechanism causes more delays while it keeps the scheduled ports free for messages H. The maximum possible number of Ethernet frames for messages L in Timely Block is only 19. To overcome this constraint, the *ES* and *SW* need to act more intelligently; thus when the length of message L is known and transported inside of a given message, the switch will determine if enough bandwidth is available to send message L completely before message H has to be relayed.

Shuffling is an optimal solution that delays message H until the message L process is finished. In the worst case, the delay is equal to the maximum length of message L. This delay also impacts the subsequent message H, because the bandwidth required for the message L is compensated by the sum of the inter-frame gaps between the two succeeding messages H. This mechanism does not truncate a message, nor block the outgoing port for message L, which makes it more efficient then the two previous mechanisms. If message H is a TT message, the real-time quality of the time-triggering is degraded. Latency cannot be mitigated; however, in a 100 Mbit/sec or 1 Gbit/sec network, shuffling still has sufficient real-time quality for applications such as avionics Wilfried Steiner and Varadarajan (2009).

### **1.3** Time-Triggered Ethernet (TTEthernet)

TTEthernet is a new SAE Standard Aerospace (2011d) that provides time-triggered services for Ethernet in order to allow synchronous communication with constant latency, tight jitter ( $\mu$  sec) and determinism properties. TTEthernet integrates three data flows: Time-Triggered (TT) data flow, which is the highest priority flow; Rate Constrained (RC) traffic, which is equivalent to AFDX traffic; and Best Effort (BE) traffic. This makes TTEthernet suitable for mixed-critical applications where highly critical functions work alongside less critical functions.

The origins of TTEthernet can be trace back to an collaborative academic project between Vienna University of Technology and TTTech Computertechnik AG TTT. The main objective of this project was to integrate time-triggered messages with event-triggered messages on a single physical Ethernet network.

TT frames are transmitted at specific time intervals established by an off-line time schedule. This schedule specifies the dispatch frame points in time and temporal characteristics for intervals used for asynchronous traffic such as RC and BE. The temporal properties of TT frame  $f_i$ are specified by Equation 1.2:

$$f_i[v_x, v_y] = f_i.period, f_i^{[v_x, v_y]}.offset, f_i.length$$

(1.2)

The period and length of the TT frame are determined by the off-line configured parameters of the system, and the offset is assigned by the scheduler. The assigned value of the offset for all frames F on all links L in the network is:  $F^L.offset$ . The dispatch point in time of a TT frame  $f_i$  on the communication link  $[v_x, v_y]$  is represented by  $f_i^{[v_x, v_y]}.dispatch_{pit}$ . This is identified by the period and offset of the frame where  $f_i^{[v_x, v_y]}$  represents frame  $f_i$  transferred as TT on the communication link  $[v_x, v_y]$ .

The RC traffic, which represents AFDX traffic, guarantees bounded latency in a complex network. AFDX, which is a shorthand for Avionics Full-Duplex Switched Ethernet, ARINC 664 part7 Incorporated (2009), is a predictable communication network that shares network bandwidth between functionalities of a system and maintains the predictability of the communication Brau *et al.* (2013). The characteristics of the RC frame are its maximum transmission rate and length, described by Equation 1.3:

$$f_i = f_i.rate, f_i.length \tag{1.3}$$

The RC frame should always respect its transmission rate limit. In the event that the RC frame exceeds its transmission rate, a traffic policing function implemented in the switch (e.g. leaky bucket) drops the frame. The traffic policing function measures the time between the reception of two frames to determine whether the transmission rate was violated or not.

Finally, BE traffic represents classic Ethernet traffic, where no guarantee exists for the transmission time, reception at the recipient location or delays. In fact, BE frames use the remaining bandwidth of the network due to its lower priority in comparison to TT and RC frames. A typical example of BE traffic is web services.

TT traffic must be free of any conflict. For this to be so, an off-line schedule of frame transmissions that respects the synchronized global time is required. The necessity for there not be any conflict introduces the fundamental constraint of TTEthernet network, known as *contention-freedom*. This definition is formally expressed by Equation 1.4 Steiner (2010), where LCM(F.period) represents the least common multiple of all frame periods known collectively as a *cluster cycle*. It ensures the mutual exclusion of the frames transmitted in the same data flow link, which means that within a given link, only one frame will be transmitted at a certain time.

$$\forall [v_{k}, v_{l}] \in L, \forall f_{i}, f_{j} \in F$$

$$\forall a \in [0..(\frac{LCMF.period}{F_{i}.period} - 1)], \forall b \in [0..(\frac{LCMF.period}{F_{j}.period} - 1)]:$$

$$((F_{i} \neq F_{j}) \land \exists F_{i}^{[v_{k}, v_{l}]} \land \exists F_{j}^{[v_{k}, v_{l}]}) \Rightarrow$$

$$((a \times f_{i}.period) + F_{i}^{[v_{k}, v_{l}]}.offset \ge (b \times f_{j}.period) + F_{j}^{[v_{k}, v_{l}]}.offset + f_{j}.length)$$

$$\lor ((b \times f_{j}.period) + F_{j}^{[v_{k}, v_{l}]}.offset \ge (a \times f_{i}.period) + F_{i}^{[v_{k}, v_{l}]}.offset + f_{i}.length))$$

$$(1.4)$$

An off-line schedule established at the time the system was designed is responsible for prohibiting runtime conflicts. Therefore, in the schedule, TT frames have a higher priority than RC and BE frames. When a TT frame and an RC frame arrive in the same outgoing port, the TT frame takes priority over the RC frame. In fact, RC traffic is dispatched if TT traffic is not pending. Therefore, when TT traffic arrives, it will be immediately transmitted. To ensure the immediate transmission, the switch must confirm that the network is free.

TTEthernet is a transparent synchronization protocol that allows different types of traffic to coexist on the same physical communication network. In fact, this synchronization protocol permits transparent integration of time-triggered services on top of standard Ethernet infrastructure.

TTEthernet introduces a fault-tolerant algorithm, which detects failures and disorders in the network. In particular, fault-tolerant algorithms set up the send order for the synchronization messages (i.e. *PCFs*) in order to ensure the synchronization of local clocks in a distributed system. *Protocol Control Frame (PCF)* is a dedicated Ethernet frame, which carries the TTEthernet protocol control frame to synchronize the local clock. *Protocol Control Frame* includes the transmission of overhead protocols from higher layer protocols such as IP and UDP. Therefore, a multitude of TTEthernet End-Systems generate *PCFs* and distribute them with TTEthernet switches. Fault-tolerant algorithms use multiple redundant paths established by the TTEthernet net network in order to tolerate the failure of a single path without affecting the entire system applications. It is vital for safety-critical systems to have fault-tolerant algorithms. Multiple redundant paths in the system ensure that even multiple faults can be tolerated.

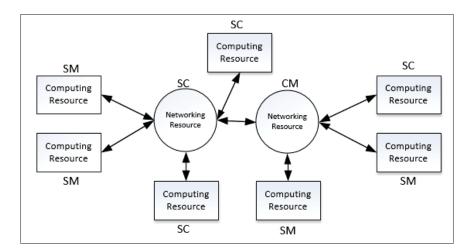

As previously mentioned, TTEthernet provides local clock synchronization in distributed systems. To do so, a synchronization approach must be established. The main elements of this synchronization approach include a *Synchronization Master (SM)*, a *Compression Master (CM)* and a *Synchronization Client (SC)*. Based on the requirements on the system architecture, either *SM* or *CM* should be selected. Once the system designer decides on the configuration approach of *SM* and *CM*, the remaining components are configured to be the *SC*. The synchronization approach of TTEthernet is organized in two steps. In the first step, *SM*s send *PCF*s to the *CM*s. Then, after a new calculation, a new *PCF* is sent out from the *CM*s to the *SM*s and, in the second step, to the *SC*s. The new *PCF* contains an average value of arrival times of dispatched *PCF*s in the first step.

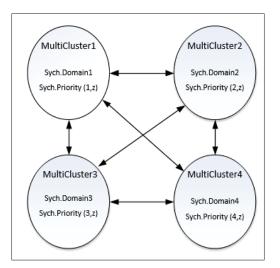

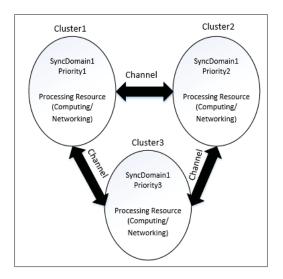

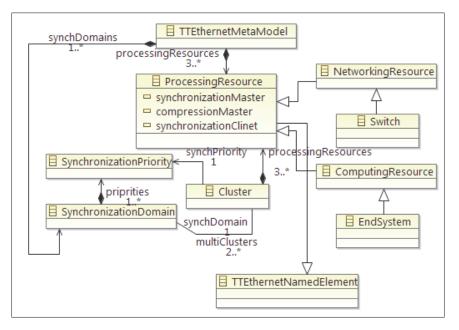

The synchronization topology is configured at different levels in the system architecture. The lowest level of this topology is composed of ESs and switches, which are configured as SM, CM and SC. The next level presents the concept of cluster, where a single synchronization domain and synchronization priority are considered. TTEthernet introduces different synchronization domains and synchronization priorities in order to support system-of-system communication. Synchronization domains refer to independent TTEthernet systems inside of a system-of system that respects their synchronization priorities. It is important to point out that two components belonging to different synchronization domains will never synchronize their local clocks. That means the communication between two components of different synchronization domains is only possible with non-time-triggered traffic classes. The concept of *cluster* is defined in TTEthernet to permit the running of different *clusters* in a large TTEthernet network in isolation. A cluster is organized as a set of ESs and switches that are connected using communication redundance channels. These communication channels contain at least one switch. Several clusters constitute a *multi cluster* in the synchronization topology where one synchronization domain and many synchronization priorities are introduced. A multi *cluster* system supports a master-slave paradigm, which tries to synchronize all devices in the system while respecting the highest synchronization priorities. Finally, the *network* level of the synchronization topology is composed of several *multi clusters* with different synchronization domains and synchronization priorities.

### 1.4 Integrated Modular Avionic Architecture (IMA)

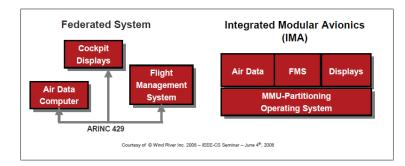

The main idea underlying the concept of IMA architecture is the sharing of resources between some functions while ensuring their isolation to prevent any interference Lauer (2010b, 2013); Michaël Lafaye and Pautet (2010); A. Al Sheikh (2010); Watkins and Walter (2007). This contrasts with the federated architectures, where each function is designed and deployed to use exclusive resources. Avionic systems are now based on IMA architectures, where several system functions with different safety and performance requirements might be deployed on the same computing module Watkins and Walter (2007). Figure 1.4 taken from Inc. (2008),

demonstrates the difference between federated and IMA architectures for cockpit display, Air data and Flight Management System (FMS) functionalities. In federated architectures, the functionalities are implemented on separate processing units, and these processing units are connected using ARINC 429 for a network. But in IMA architecture, all functionalities are deployed on the same processing unit and managed with an operating system. The resource sharing in IMA architecture reduces the cost of voluminous wiring and equipment, while the non interference guarantee is required for safety reasons.

The IMA architecture is defined by the ARINC 653 standard Incorporated (2013). Each functionality in the system is implemented by one or a set of functions distributed across different modules. A module represents a computing resource hosting many functions. Functions deployed on the same module may have different criticality levels. For safety reasons, the functions must be strictly isolated using partitions. IMA-based avionic systems, therefore, have a mixed-criticality that requires solid isolation and partitioning. These features are supported in IMA with operating systems and executives compliant with the ARINC 653 standard Incorporated (2013). The partitioning of functionalities is done in two dimensions: spatial partitioning and temporal partitioning. The spatial partitioning is implemented by statically assigning all of the resources to the partition executed in a module, where no other partition can have access to the same resources at the same time. The temporal partitioning is implemented by allocating a periodic time window dedicated to the execution of each partition.

Figure 1.4 Federated Architecture V.S. IMA Architecture

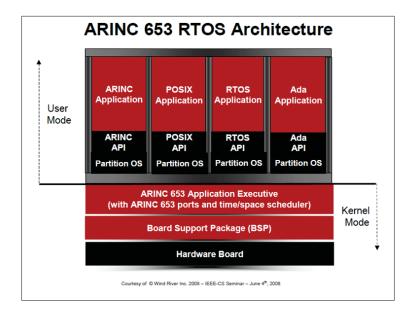

The segregation and partitioning in IMA are accomplished with the ARINC 653 Real Time Operating System (RTOS). ARINC 653 Incorporated (2013) manages the computational resources of IMA and performs temporal and spatial isolation between partitions. Figure 1.5 taken from Inc. (2008), presents an example of the ARINC 653 RTOS composed of one module hosting four partitions deployed on a hardware board using the ARINC 653 Application Executive.

Figure 1.5 An Example of ARINC 653 RTOS

Two ARINC standards define IMA systems, ARINC 653 Incorporated (2013) and ARINC 664 Incorporated (2009). In following sections, we briefly explain them.

### 1.4.1 ARINC 653

ARINC 653 is a real-time operating system produced by ARINC Corporation. Isolation between partitions, which ARINC 653 accomplishes is particularly important because failure in a partition should not affect the functionality of other partitions that run on the same processor (module). Furthermore, partitions demand strict access to processing resources and memory shared between them. Therefore, the need for temporal and spatial isolation between partitions on the same module is obvious. In temporal partitioning, each partition is executed in a dedicated time slot defined at system start-up. The spatial partitioning dedicates a predetermined amount of memory space, which is also determined at system start-up Brau *et al.* (2013).

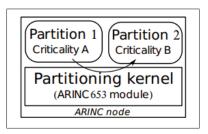

Figure 1.6 Julien Delange and Kordon (2009) presents an example of the conceptual model behind ARINC 653: a system composed of two partitions with different criticality levels, where partition 1 has a higher level of criticality. The communication between them is realized by the ARINC 653 kernel using one communication channel from partition 1 to partition 2, which allows unidirectional data transmission from partition 1 to partition 2. The ARINC 653 module is responsible for managing the address space in memory in order to isolate the partition code and data, and it also manages the time slot to execute partitions.

Figure 1.6 ARINC 653 module with two partitions

The concept of hierarchical scheduling is performed in ARINC 653 in two levels; kernel or module level, partition level, illustrated in Figure 1.7 taken fromJulien Delange and Kordon (2009). The kernel level is a static scheduling and executes each partition cyclically at a given rate. The scheduling policing which is defined by system designer is performed in the partition level. That enables defining different scheduling policy per partition.

ARINC 653 modules realize two types of communication, communication between ARINC 653 processes in the same partition (intra-partition communication) and communication between ARINC 653 processes across partitions (inter-partition communication). In the case of interface communication between ARINC 653 processes in the same partition, no kernel or module is used. Therefore, they are isolated because failure of an intra-partition communica-

| evel 1 | RMS<br>policy |                       | RMS<br>policy |                       |   |

|--------|---------------|-----------------------|---------------|-----------------------|---|

| Le     |               | Round-Robin<br>policy |               | Round-Robin<br>policy |   |

| 0      | Partition 1   | Partition 2           | Partition 1   | Partition 2           |   |

|        | )ms           |                       |               |                       | > |

Figure 1.7 ARINC 653 hierarchical scheduling example

tion does not cause failure in other partition functionalities. The intra-partition communication is established by four mechanisms, as listed below:

- The buffer stores multiple messages in the message queue (FIFO, Priority).

- The blackboard stores one instance of a message until it is cleared or overwritten by a new instance.

- The event notifies the completion of a job.

- The semaphore controls access to shared resources.

The inter-partition communication is supervised by the module. The ports' routing policy is statically defined by the system designer. The inter-partition communication proceeds as follows:

- The queuing ports store multiple messages in queues.

- The sampling ports are similar to blackboard services in intra-partition communication.

During the design and development process of an ARINC 653 system, several issues should be taken into account to address needs of reliability and robustness (e.g. partition scheduling, resources dimensioning). All scheduling policies must be validated in order to ensure there is enough time for their execution. All resource dimensions must be corrected in accordance with run time requirements. Therefore, no unexpected deadlock or crash should happen. For example, the buffer size should be checked to avoid buffer overflow at execution time. The validation of these requirements needs a lot of testing and implementation efforts. However, they can be validated at the design-level before any implementation has begun, which can reduce the need for testing efforts and error detection.

#### 1.4.2 ARINC664 part7, AFDX

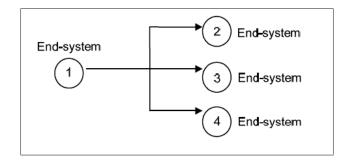

One established communications medium in IMA is Avionics Full DupleX Ethernet (AFDX) Incorporated (2009), which is a deterministic real-time network based on Ethernet. AFDX supports Rate Constrained (RC) traffic, which is event-triggered traffic, and uses the concept of Virtual Link (VL) in order to share bandwidth between partitions and modules of IMA architecture. VL is a unidirectional logical connection from one sender module to one or more receiver modules. This is shown in Figure 1.8 taken from Incorporated (2009).

Figure 1.8 Virtual Link

VL replaces point-to-point cabling used in federated architectures and uses traffic shaping to regulate the time between two consecutive frames that would be sent on the same VL. This leads to bandwidth controlling that provides traffic at a constant and deterministic rate Ahmad Al Sheikh and Hladik (2013). Figure 1.9 Incorporated (2009) shows this regulated flow for a single VL. VL has two main characteristics: Bandwidth Allocation Gap (BAG) and Maximum Frame Size (MFS). BAG is defined as the minimum time interval between two consecutive

frames on an AFDX network, and MFS is the maximum size of a transmitted frame on a VL. This is shown in Figure 1.9 Incorporated (2009).

Figure 1.9 Virtual Link Flow Regulation

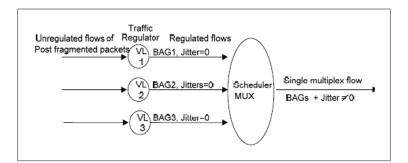

In the case of a transmission using multiple VLs, the scheduler multiplexer is used to manage the multiplexing of different flows coming from the regulator, as depicted in Figure 1.10 Incorporated (2009).

Figure 1.10 The Scheduler Flow of Virtual Link

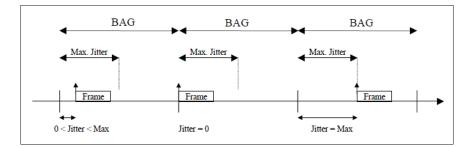

At the output of the scheduler multiplexer, frames appear in bounded time intervals, as in Figure 1.11 Incorporated (2009), where the maximum possible jitter is respected. This jitter is produced by the scheduler, not by the traffic flow in the AFDX network.

# **1.5 Model-Driven Engineering Approach**

In the domain of software engineering, there is often a wide conceptual gap between a problem and the implementation of an effective solution. The bridging of this gap is usually done by a systematic transformation of a real problem into an implementation domain, where the real

Figure 1.11 The Jitter Effect for a Maximum Bandwidth Data Flow

problem is represented by a model at multiple levels of abstraction, France and Rumpe (2007). This process is known as MDE.

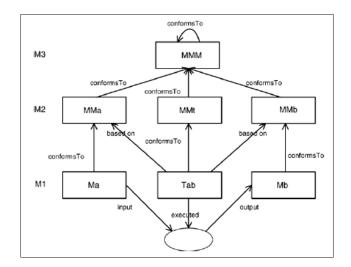

*Model, metamodel* and *metametamodel* are key elements of MDE. A *model* represents a system that refers to the real-world. This representation contains the characteristics of the system and any knowledge about it. A *metamodel* defines a languages that enables the expression of models. Moreover, it describes the elements of a model, the relation between these, as well as the constraints that should be respected by the model. A *metamodel* defines the abstract syntax of modeling languages F. Jouault and Kurtev (2008). The conceptual foundation of a *meta-model* is captured in a model called a *metametamodel*. Figure 1.12 shows the common pattern for model transformations in MDE. M1, M2 and M3 are three levels of abstraction of this architecture representing *model*, *metamodel* and *metametamodel*. Globally, a *model* is defined in conformance with a *metamodel*, and a *metamodel* in conformance with a *metamodel*. In Figure 1.12 taken from F. Jouault and Kurtev (2008), Tab represents a transformation language, such as ATL, which is responsible for the automatic generation of *Mb* by executing *Ma*, where *Ma*, *Mb* and Tab conform to *MMa*, *MMb* and *MMt*, respectively. All three metamodels conform to the *metamodel MMM*, which could be MOF or EMF. In our context, *MMM* is EMF.

Eclipse is an open universal tool platform for software development, particularly for the construction of IDEs (integrated development environments). The Eclipse Modeling Framework (EMF) is the most used environment for MDE. It provides an underlying modeling language

Figure 1.12 Model transformation pattern

called *Ecore* as well as a code generation framework. The adaptable extensibility of EMF provides a solid foundation for many model-based language development tools. In fact, EMF supports creating, modifying, storing and loading instances of models by describing class models and Java code generation. It incorporates JAVA, XML and UML. An EMF model is the common representation of these languages regardless of what technology the utilized technology to define a model Biermann *et al.* (2006).

The metamodel of EMF, which is also called EMF core model, contains elements such as *EClass*, *EDataType*, *EAttribute* and *EReference*. *EPackage* arranges *EClasses* in order to perform sub-packages, the elements of model as well as the relation between these. Also, the EMF metamodel contains some abstract classes, such as *ENamedElement*, *ETypedElement* and others, to help better structure the model.

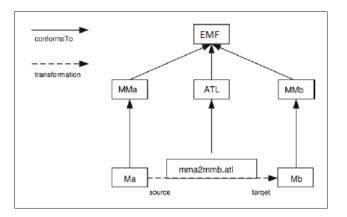

The ATLAS Transformation Language (ATL) F. Jouault and Kurtev (2008) is a domain-specific language for specifying model-to-model transformations. An ATL transformation program is composed of transformation rules that define how source model elements are mapped into the elements of target models. Figure 1.13 taken from F. Jouault and Kurtev (2008), presents the transformation pattern of the ATL model transformation language. In this Figure, *Ma* is the source model that is transformed into *Mb*, the target model, according to the ATL transformation.

tion rules written in *mma2mmb.atl*. The model representing the ATL transformation definition conform to the ATL *metamodel*. At a higher level, all metamodels conform to EMF. The Eclipse environment contains a set of tools and features that have been adapted and extended to best suit the needs of ATL development.

Figure 1.13 ATL overview

#### **1.6** The Architecture Analysis Design Language (AADL)

Many model-based languages exist, such as Architecture Analysis Design Language (AADL), Unified Modeling Language (UML), System Modeling Language (SysML), Analysis of Real Time and Embedded systems (MARTE), and others. Of these languages, AADL is the most appropriate for our project due to its extensibility properties and its already developed and published annexes, which include ARINC 653Incorporated (2013), behavioral annex Aerospace (2011c) and error modeling annex Aerospace (2011a). Moreover, AADL is an open source software built on the Eclipse Modeling Framework. Our proposed tooling set also builds on the Eclipse ecosystem, and our motivation for choosing AADL was mainly informed by its interoperability. The AADL SAE group (AS-2D) also helps us a lot in terms of presenting our progress every three months and conducting our project, which will be published as the next AADL annex called *Networking Annex*. The following section will present more details about these modeling languages.

AADL is a standard architecture description language developed by SAE AS5506 SAE (2012) for formal specifications of hardware and software architectures of embedded computer systems. It focuses on the distinct components and the interaction between components Pi (2009). It also describes the dynamic architecture of an embedded system, the constraints of a real-time system and the mapping of software to hardware components Frana (2007). AADL is used for the modeling of software system architectures and supports the analysis and verification of non-functional properties of modeled system (i.e. quality attributes). More specifically, AADL is used to model software system architectures and its deployment on the execution platform. A number of operating system characteristics, including communication and synchronization mechanisms and thread behavior, are directly supported by the language.

In the AADL execution model, both synchronous and asynchronous aspects are mixed Frana (2007). A synchronous execution model is defined by logically synchronized periodic threads communicating through data ports. The value transmission from output port to input port is done at the beginning of the period. Two threads in the same period can communicate together by means of the existing immediate transfer protocol, which implements a zero-time computation hypothesis. To validate the synchronous hypothesis, the real-time properties attached to model elements is used. AADL also introduces an asynchronous model, which allows it to declare buffered data, to raise events on events or an event of the data port, to specify sporadic and aperiodic threads with different periods, which can communicate together through shared variables and remote procedure calls. The execution model is based on automatic modeling stopwatches. For that, the execution time of threads is defined and compared with the requirements deadline.

AADL provides different types of components with precise semantics in order to express the entire system. AADL components that represent the elements of architecture are listed as follows:

• Software components such as *thread, thread group, subprogram, data and process.*

- Hardware components, which include *processor or virtual processor, memory, bus/virtual bus and device*.

- Hybrid components such as *system*, which is used to describe the hierarchical grouping of hardware and software components.

*Thread*, which is the only schedulable component of AADL, represents a sequential flow of execution. Different *threads* communicate together through *data flows*. *Subprogram* represents the piece of code that can be called on by a thread or another subprogram. The connection points are defined by the interface of the communication components such as *ports*, *data accessing*. A *Component* is defined by a *type* in order to define the component's external interface, and its *implementation* to define the internal structure of the component. The management of large and complex systems is performed in AADL by using *Packages*, which define name space and component libraries.

AADL is an extensible modeling language that uses two extensibility mechanisms. The first mechanism is a construct for property set definition. This construct enables the defining or modifying of AADL properties. The second extensibility mechanism is an annex extension mechanism, which enables it to specify sub-languages that will be processed within an AADL model. Some AADL annexes are now standardized, such as the Error Modeling Annex Aerospace (2011a), which allows the specification of error models to be associated with core components supporting safety and dependability modeling.

An open source tool set built on Eclipse plug-in technology is provided for AADL. Known as OSATE CMU/SEI (2014), it is implemented by the Society Automotive Engineers (SAE) standard AADL Liu and Gluch (2009).

# 1.6.1 AADL Annexes

As mentioned above, AADL is an extensible modeling language that uses two extensibility mechanisms, property set definition and the annex extension mechanism. Some AADL annexes

have already been standardized and published such as ARINC653 and Behavioral annexes. In this thesis, we do not describe these annexes in detail, but in the next section we briefly review them in order to explain the concept of developing a new annex in AADL.

## **1.6.1.1 Behavioral Annex**

The behavioral annex of AADL (AADL-BA) Aerospace (2011c) provides constructions to define the expected behaviors of system components described by AADL. It is an automatabased annex. This annex is used to describe the behaviors of port communication, subprogram call, timing, and others. Because it is an extension of the dispatch mechanism of the execution model, the role of the AADL execution model is to determine when a behavior annex is processed and what data it executes. The behavioral annex can be attached to the thread or subprogram, as shown in Figure 1.14 taken from Pi (2009). In this example, the system has two states (initial state and return state) and a transition state between them.

```

subprogram implementation example.i

annex behavior_specification {**

states

s0: initial state;

s1: return state;

transitions

s0 -[p?(x) ]-> s1 { p!(x+1); };

***};

end example.i;

```

Figure 1.14 Integration Method

#### 1.6.1.2 ARINC 653 Annex

In the previous section, we explained the functionalities of ARINC 653 in IMA architecture. In this section, we focus on modeling ARINC 653 using AADL. In order to provide safetycritical services in this model, space and time partitioning of ARINC 653 avionics standard is necessary. The first version of AADL was not amenable to the present model for ARINC 653, particularly in the matter of isolation requirements for the system. This was the main reason for developing a new annex in order to support the ARINC653 specification.

An ARINC653 module is modeled by a processor component Julien Delange and Kordon (2009). This processor models partitioning functionalities. Therefore, it contains partitions runtime as a sub-component, and it defines partitions scheduling policy as component properties. Virtual processor models partition runtime such as scheduling policy for partition tasks, partition resources and so on. The process component models the partition address space and contains thread and data, which are the partition content. The AADL property *Actual-Processor-Binding* combines the virtual processor and process together. Also *Actual-Memory-Binding* combines memory with a process component in order to facilitate the allocation of memory segments.

## **1.7** Verification and Simulation Techniques

Simulation is defined as providing the model of a real system or a real problem in order to undertake experiments toward describing the behavior of that system or problem. This process concludes by evaluating various scenarios for the system. In fact, the output result obtained from the simulation is used for making better decision during the implementation process of most engineering projects, which contributes to better efficiency, system performance, and error detection in early stages of design. Two different types of simulation are reported by Klingstam and Gullander (1999):

- Discrete event simulation (DES)

- Geometric simulation (GS)

DES simulates the behavior of a system at a discrete point in time, whereas GS simulates continuous time. In this project, we mostly focus on DES due to the nature of TTEthernet, which includes time-triggered and event-triggered messages.

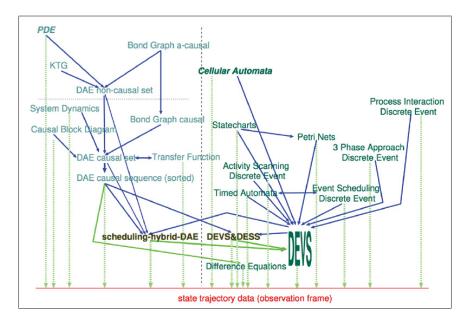

Figure 1.15 illustrates a Formalism Graph Transformation (FGT) Vangheluwe (2000). The different formalisms are the nodes of this graph, and the solid arrows represent mapping relations between formalisms. The dotted, vertical thick arrows indicate the existence of a simulator that can map an abstract model onto a state trajectory. The dashed line in the middle distinguishes the crude division between continuous and discrete formalisms. As we can see from Figure 1.15 taken from Vangheluwe (2000), DEVS is a common denominator for the representation of discrete-event and continuous-time models. This is because, firstly, DEVS is the most appropriate and most common formalism in targeting simulation. Secondly, the semantics of discrete-event formalisms, such as Event Scheduling, Activity Scanning and Process Interaction, can be declared using DEVS.

Figure 1.15 DEVS a common formalism

DEVS is a super-formalism that surrounds the expressiveness of the individual formalism. The super-formalism is an alternative to analyzing complex multi-formalism systems. Multi-formalism systems are a modeling approach for complex systems where no single analysis or modeling method can successfully tackle all aspect of the systems. Another benefit of DEVS is its high level syntactic elements, which enables learning about the semantics of the high-level formalism by transforming from high-level to low-level. In our context, the rich syntactic

elements in the AADL modeling language are modeled explicitly using DEVS. The property required to describe the AADL model with DEVS increases as a result of transformation.

#### **1.7.1** Discrete Event System Specification (DEVS)

DEVS formalism, Zeigler. (1984) provides a rigorous common basis for discrete-event and continuous-time modeling and simulation. It is presented as an extension to Finite State Automata that describes the behavior of systems in two levels, *atomic* DEVS and *coupled* DEVS. The behavior of a discrete-event system is described with the help of *atomic* DEVS, which takes advantage of Finite State Automata to produce output events from the reaction to input event. *atomic* DEVS is structured using Equation 1.5, Zeigler. (1984). T is the continuous time base, state set of S is the set of admissible sequential states. Concurrent parts of a system are defined by n. The time advance function, ta, is used to model the time in the system. The internal transition function,  $\delta_{int}$ , describes the behaviour of a Finite State Automaton. The output set, Y, denotes the set of admissible outputs, whereas  $\ell$  represents the output ports of systems. The output function,  $\lambda$ , is responsible for mapping the internal state onto the output set. Q denotes the total state of the system, whereas e refers to elapsed time.  $\sigma$  describes the time left in a state. In the case that the system receives an external set of inputs, X represents all admissible input values and m for input ports. The set  $\Omega$  contains all admissible input segments  $\omega$ . Finally, the reaction of systems into all external events is represented by  $\delta_{ext}$ .

$$atomicDEVS \equiv \langle S, ta, \delta_{int}, X, \delta_{ext}, Y, \lambda \rangle$$

(1.5)

Where,

$$T = R$$

$$S = \times_{i=1}^{\ell} Y_{i}$$

$$t_{a} : S \to R_{0,+\infty}^{+}$$

$$\delta_{int} : S \to S$$

$$Y = \times_{i=1}^{\ell} S_{i}$$

$$\lambda : S \to Y \bigcup \{\phi\}$$

$$Q = \{(s,e) | s \in S, 0 \le e \le ta(s)\}$$

$$\sigma = ta(s) - e$$

$$X = \times_{i=1}^{m} X_{i}$$

$$\omega : T \to X \bigcup \{\phi\}$$

$$\delta_{ext} : Q \times X \to S$$

A *coupled* DEVS represents the overall system as a network of coupled components. These components can be *atomic* DEVS or *coupled* DEVS in their own right Zeigler. (1984). *coupled* DEVS is structured using Equation 1.7, Zeigler. (1984):

$$coupledDEVS \equiv \langle X_{self}, Y_{self}, D, \{M_i\}, \{I_i\}, \{Z_{i,j}, select \rangle$$

(1.7)

(1.6)

Where,

$$\{M_{i}|i\varepsilon D\}$$

$$M_{i} = \langle S_{i}, ta_{i}, \sigma_{int,i}, X_{i}, \sigma_{ext,i}, Y_{i}, \lambda_{i} \rangle, \forall i\varepsilon D$$

$$\{I_{i}|i\varepsilon D \bigcup \{self\} \langle$$

$$\forall i\varepsilon D \bigcup \{self\} : I_{i}$$

$$\{Z_{i,j}|i\varepsilon D \bigcup \{self\} : I_{j}\}$$

$$select : 2^{D} \rightarrow D$$

$$select(E)\varepsilon E$$

(1.8)

Self represents the coupled model,  $X_{self}$  and  $Y_{self}$  denotes the set of allowed external inputs and outputs to the coupled model. The set of unique component references is represented by D.  $M_i$  is a set of components that are *atomic* DEVS. The coupling network is denoted by  $I_i$ .  $Z_{i,j}$ describes how the output of a component is mapped to the input of other components. In fact, Z is a translation functions, where different components such as atomics or coupled influence themselves. Finally, a *select* function is used for tie-breaking between simultaneous events in a *coupled* DEVS.

# **CHAPTER 2**

#### **RELATED WORK**

In this chapter, we present an overview of the most closely related research work to our own. The chapter is organized in two parts. In the first, we review research work that focuses on issues and techniques related to TTEthernet-based distributed architectures, such as IMA architectures. In the second part, we review research work in the domain of AADL. Finally, we discuss research work in the domain of the DEVS simulation environment.

#### 2.1 TTEthernet-based platform

Several research works Kopetz (2003), Abeni and Buttazzo (1998) have focused on real-time systems with mixed-criticality requirements. They describe how Time-Triggered (TT) tasks and Event-Triggered (ET) tasks can be integrated in the same physical platform in order to support mixed-critical applications. Izosimove et al. Izosimov *et al.* (2008) presented TT and ET tasks that share the same processor, and they also addressed the problem of mapping and partitioning. The order of tasks (TT and ET) decided by different scheduling approaches is reported by a number of researchers, but this is outside the scope of our work. Braun *et al.* (2001) included task mapping to heterogeneous architectures.

Steinhammer et al. Steinhammer (2007) described and implemented a prototypical TTEthernet controller in FPGA. Many approaches have attempted to adapt Ethernet technology for deployment in applications that require temporal guarantees.

Modeling TTEthernet has been mainly used for simulation purposes. Steinbach et al. Steinbach *et al.* (2011) developed an extension for the OMNeT++ INET framework to support the simulation of TTEthernet. Zhang et al. Zhang and Koutsoukos (2013) introduced and developed a TTEthernet model using SystemC/TLM in order to facilitate the design and integration of a Cyber Physical System (CPS). They integrated the TT task, and they proposed to integrate the TT and ET tasks together in future work, although the efficiency of the simulation in their work meets TTEthernet requirements. Abuteir et al. Abuteir and Obermaisser (2013) introduced a TTEthernet simulation environment based on OPNET for generic building blocks such as switches and systems.

#### 2.2 IMA Architecture

Michaël Lafaye and Pautet (2010) and Lafaye (2010) are two works of the same group that have proposed a modeling approach that describes different levels of detail the IMA execution platform. They propose a modeling approach that computes worst case traversal time (WCTT) for IMA architecture interconnected with AFDX. They produced a functional analysis using a model-checking verification approach. This work fits with the early phase of the development process. They used two standard languages: AADL, to model the high level abstraction of IMA platform; and SystemC, to refine the description of the architectural platform and to provide simulation results. The difference between our project and this work is that, when we target the TTEthernet, the communication network inside IMA remains AFDX. Moreover, they used SystemC languages to refine the AADL model and simulation. We only use the AADL modeling language.

Lauer (2010a) proposed a modeling approach for IMA platforms based on time-automation (as a formal modeling approach). Again, they computed the worst case traversal time (WCTT) for the AFDX network in IMA architecture and produced a functional analysis using a model-checking verification approach. The communication network of the IMA platform is always AFDX. In terms of verification, they used a model-checking approach, which is also interesting for us. In a similar vein, Lauer (2011b) and Lauer (2011a) continued to work on worst case temporal consistency and latency and freshness analysis for IMA platform with different evaluation methods, such as the tagged signal model and Integer Linear Programming (ILP).

A. Al Sheikh (2010) presented an integer linear programming formulation for resource scheduling in IMA architecture that takes resource and temporal constraints into account. This work is interesting to us because it recognizes the main requirements and constraints of the IMA platform that should be verified. Two next work of this group, Ahmad Al Sheikh and Prabhu (2012) and A. Al Sheikh (2009) focus on scheduling and task mapping in IMA architecture.

Lauer (2013) focused on IMA architecture for TTEthernet in order to present a cost effective strategy for integrating multi-critical functions in IMA architecture. This work also used a binary integer problem formalization with an off-the-self solver.

#### **2.3** AADL

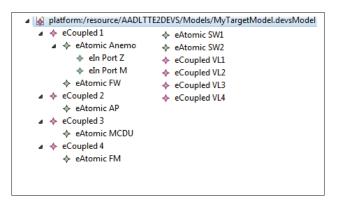

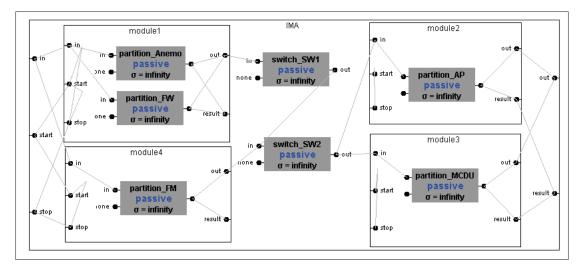

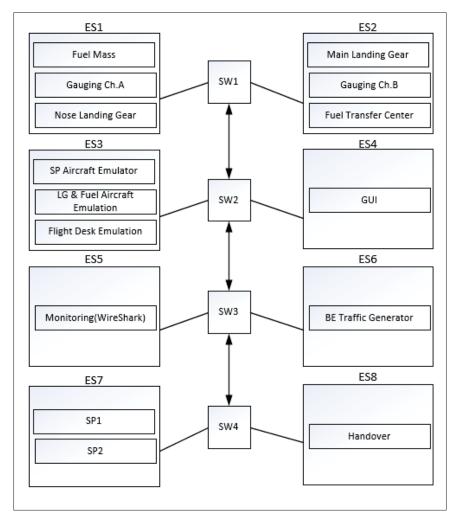

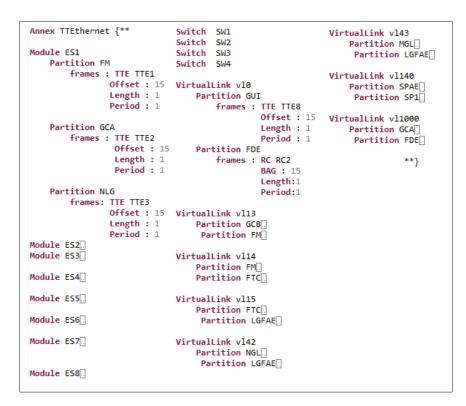

AADL presents two extension mechanisms, namely property sets and sub-languages (i.e. annex). Several AADL extensions based on these mechanisms are now standardized as official annexes. These include the Data modeling annex, ARINC653 annex, AADL Behavior Annex Aerospace (2011b), and Error Model Annex Aerospace (2011a). Some works have focused on extending the language using these extension mechanisms or in other ways.