# Noise Propagation in Power Converter - Modeling and Attenuation Approaches

by

Tung Ngoc NGUYEN

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

# MONTREAL, MARCH 20, 2018

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

CONSC NUT TUNG NGOC NGUYEN, 2018

#

This Creative Commons license allows readers to download this work and share it with others as long as the author is credited. The content of this work cannot be modified in any way or used commercially.

## **BOARD OF EXAMINERS**

## THIS THESIS HAS BEEN EVALUATED

## BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Handy Fortin Blanchette, Thesis Supervisor Department of Electrical Engineering, École de Technologie Supérieure

Mr. Vincent Duchaine, President of the Board of Examiners Department of Automated Manufacturing Engineering, École de Technologie Supérieure

Mr. Kamal Al-Haddad, Member of the jury Department of Electrical Engineering, École de Technologie Supérieure

Mr. Frédéric Sirois, External Independent Examiner Department of Electrical Engineering, École Polytechnique de Montréal

### THIS THESIS WAS PRESENTED AND DEFENDED

#### IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

### ON MARCH 13, 2018

## AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGEMENTS

It has been a long journey since the beginning of my graduate study to the finishing of this thesis. I couldn't have completed my study without great helps from such important persons.

Firstly, I would like to give my best appreciation to my supervisor, Professor Handy Fortin Blanchette for his guidance and uncountable supports. Not only my teacher in academic life, he is also the inspiration of my professional career and an adviser in my personal life.

In addition, I would like to thank my first mentor at work, Truong-Khoa Nguyen, who enlightens me with industrial design experience and growths me to be an engineer. I also would like to thank my friends: Tuyen Dinh Nguyen, My - Ha Le, Trung Duy Tran and Phi Luan Nguyen for standing with me in such difficult situations during my study period.

Since my research topic requires multiple experimental prototypes and measurement devices, I received lots of help from the great technology team in GREPCI: Christian Talbot, André Zalzal, and Youssef Bekbouti for their support. I also would like to thank Dr. Ruxi Wang for his excellent discussions during my PhD.

I am the luckiest man in the world to be the son of my parents. My mother, Thi Thu Hong Huynh, always encourages and cares about me despite of her difficult health situation. During my study period, my father, Dzung Ngoc Nguyen, spends his whole time to take care of all difficulties happened in addition to giving me important instructions in life. There is no word can spread my appreciation to them for what they have been done for me. I also thank my sister, Quyen Nguyen, for her love and care since the beginning of time. Everyday, I come back home, eager to see my daughters, Hannah and Emily, who illuminate my mind with their love. Finally, I would like to thank my wife, Kaori Yoshida. I couldn't have finished my study without her love, unconditional support, and unlimited efforts on taking care of the kids. Last but not least, I would like to give my greatest thank to my whole family including my grand-parents, uncles, aunts and my parents - in - law. Their love and encouragement have been my biggest motivation during several years.

## PROPAGATION DU BRUIT DANS LE CONVERTISSEUR DE PUISSANCE -MODÉLISATION ET MÉTHODE D'ATTÉNUATION

Tung Ngoc NGUYEN

# RÉSUMÉ

Dans cette thèse, une analyse de la propagation du bruit électromagnétique dans les circuits de faible puissance des convertisseurs de puissant ainsi que des règles de conception est présentée. Dans la littérature, la majeure partie des publications traitent de la propagation du bruit du circuit de forte puissance. Ces bruits entraînent des interférences électromagnétiques élevées qui peuvent excéder les normes EMI. Malheureusement, les normes EMI ne permettent pas de fixer des seuils de bruit acceptables pour les circuits de faible puissance. Les bruits dans le circuit de faible puissance peuvent créer des signaux de rétroaction perturbés, entraînant des fonctionnements erratiques du convertisseur. Pour résoudre ce problème, cette thèse vise tout d'abord à aider les concepteurs à comprendre l'origine de la propagation de ces bruits. Sur la base de ces connaissances, des techniques d'atténuation du bruit sont développées pour garantir la performance et la fiabilité du convertisseur de puissance. Les méthodes proposées peuvent être appliquées à un stade initial ou avancé de la conception d'un convertisseur.

Cette thèse débute par des observations sur la propagation du bruit dans les circuits de faible puissance d'un convertisseur typique. Sur la base des résultats expérimentaux, les chemins de propagation du bruit sont analysés en mode différentiel (DM) et en mode commun (CM). Pour mieux comprendre les effets de la conception du convertisseur sur le bruit, les parties fondamentales du circuit de faible puissance qui comprend les conducteurs, les dispositifs passifs et la distribution de faible puissance qui alimente tous les circuits fonctionnels sont étudiées. Ces recherches aboutissent aux modèles proposés de pilote de grille à haute fréquence, à la représentation générale d'impédance (GIR) des dispositifs passifs, et au modèle de calcul de la distribution de faible puissance, qui seront présentés dans les différents chapitres de cette thèse. Plus spécifiquement, les techniques d'atténuation du bruit sont développées pour réduire le bruit dans la distribution de faible puissance. Par exemple, le bruit est atténué localement par des condensateurs Y. De plus, la modélisation GIR ainsi que le modèle 2D passif des structures multicouches des PCB fournissent des outils puissants pour un design optimal, à bruit réduit. Enfin, il est proposé de minimiser le bruit dans le circuit basse puissance en tenant compte des interactions complexes entre les différentes parties du circuit. Dans toutes les parties de cette thèse, la revue de la littérature, les modèles / approches proposées, les résultats des différents calculs ainsi que des résultats expérimentaux seront présentés afin de valider l'efficacité des contributions.

**Mots-clés:** Découplage, EMI, filtre, propagation du bruit, modélisation du convertisseur de puissance, carte de circuit imprimé.

## NOISE PROPAGATION IN POWER CONVERTER - MODELING AND ATTENUATION APPROACHES

Tung Ngoc NGUYEN

### ABSTRACT

In this thesis, an analysis of noise propagation and complete design guidelines for low noise low power circuit of a power converter is presented. In literature, majority of publication deal with noise propagation in the high power circuit resulting in high EMI, which may not pass EMI standards. Unfortunately, EMI standards are not relevant to solve EMI issues in the board level. Consequently, this thesis focuses on noise propagation in the low power circuit, consisting of sensing and control circuits. Noise in the low power circuit can create noisy feedback signals, leading to bad performance and poor reliability converter. In order to resolve this issue, this thesis helps the designers to understand well noise in low power circuit in term of its existence, source and propagation paths. Based on this knowledge, noise mitigation techniques are developed to ensure the performance and reliability of the power converter. The proposed methods can be applied in the early design stage or improving noise profile of a complete converter.

This thesis begins with the experimental observations of noise in the low power circuit of a typical Buck converter in several operating points of the high power circuit and different components of low power circuit. Based on the experimental results, the noise propagation paths are analyzed without considering differential (DM) and common modes (CM) separately. To further understand the effects of converter design on noise profile, the fundamental parts of the low power circuit including Gate driver, passive devices and low power rails supplying all functional circuits, are studied. These researches result in the proposed models of Gate driver at high frequency, the General Impedance Representation (GIR) of passive devices, and the computational model of the low power rails, which will be presented in the contents of this thesis. Furthermore, the noise mitigation techniques are developed to reduce noise in the low power circuit based on knowledge of these aforementioned parts. Noise is attenuated locally at the Gate driver by using Y-capacitor. In addition, the GIR and 2D model of low power rails provide powerful tools for optimal design. In each part of this thesis, the literature review, proposed models/approaches, computational and experimental results will be presented to validate the effectiveness of the thesis contributions.

**Keywords:** Decoupling, EMI, filter, noise propagation, power converter modeling, printed circuit board.

# TABLE OF CONTENTS

|                                                          |           | P                                                                    | Page |

|----------------------------------------------------------|-----------|----------------------------------------------------------------------|------|

| INTRO                                                    | DUCTIO    | DN                                                                   | 1    |

| CHAPTER 1                                                |           | LITERATURE REVIEW OF NOISE ISSUES IN POWER                           |      |

|                                                          |           | CONVERTER                                                            | . 13 |

| 1.1                                                      | Practical | design guidelines                                                    | . 14 |

| 1.2                                                      | Research  | n of EMI in high power circuit                                       | . 16 |

| 1.3                                                      | Microwa   | ave researches                                                       | . 17 |

| 1.4                                                      | Comput    | ational softwares                                                    | . 18 |

| 1.5                                                      | Conclus   | ion                                                                  | . 18 |

| CHAPTER 2 EXPERIMENTAL INVESTIGATION OF NOISE PROPAGATIO |           | EXPERIMENTAL INVESTIGATION OF NOISE PROPAGATION                      |      |

|                                                          |           | IN LOW POWER CIRCUIT OF POWER CONVERTER                              | . 21 |

| 2.1                                                      | Introduc  | tion                                                                 | . 21 |

| 2.2                                                      | Experim   | ental setup                                                          | . 25 |

|                                                          | 2.2.1     | Overall experimental setup                                           | . 25 |

|                                                          | 2.2.2     | Buck converter designed for noise measurement                        | . 27 |

|                                                          | 2.2.3     | Common mode noise rejection                                          | . 28 |

|                                                          | 2.2.4     | Isolation capacitance measurement                                    | . 32 |

| 2.3                                                      | Experim   | ental results                                                        | . 33 |

|                                                          | 2.3.1     | Effect of power transistor switching operating on noise spectrum     |      |

|                                                          |           | in Low power circuit                                                 | . 34 |

|                                                          | 2.3.2     | Effect of Gate driver DC/DC converter isolation capacitance on       |      |

|                                                          |           | noise spectrum in low power circuit                                  | . 37 |

|                                                          | 2.3.3     | Effect of duty cycle of power transistors on noise spectrum in Low   | 20   |

|                                                          | 0.2.4     | power circuit                                                        | . 39 |

|                                                          | 2.3.4     | Effect of switching frequency on noise spectrum in low power circuit | 40   |

| 2.4                                                      | Conclus   | ion                                                                  |      |

| 2.4                                                      | Conclus   | 1011                                                                 | . 42 |

| CHAP                                                     | TER 3     | GENERAL IMPEDANCE REPRESENTATION OF PASSIVE                          |      |

|                                                          |           | DEVICES BASED ON MEASUREMENT                                         | . 45 |

| 3.1                                                      |           | tion                                                                 |      |

| 3.2                                                      | Passive   | components modeling and impedance extraction                         |      |

|                                                          | 3.2.1     | Impedance Extraction                                                 |      |

| 3.3                                                      |           | proach                                                               |      |

| 3.4                                                      |           | o impedance shorting paths analysis                                  |      |

| 3.5                                                      |           | d Newton - Raphson method                                            |      |

|                                                          | 3.5.1     | Step 1: Variables definition                                         |      |

|                                                          | 3.5.2     | Step 2: Write NR Functions                                           |      |

|                                                          |           | 3.5.2.1 Open admittance                                              | . 58 |

|               |                      | 3.5.2.2 VTGs between pin pairs                               |

|---------------|----------------------|--------------------------------------------------------------|

|               |                      | 3.5.2.3 Combined equations                                   |

|               | 3.5.3                | Step 3: Jacobian matrix computing                            |

|               | 3.5.4                | Step 4: Error computing                                      |

|               | 3.5.5                | Step 5: Connecting admittance update       63                |

|               | 3.5.6                |                                                              |

| 3.6           |                      | Over-relaxation factor computing strategy                    |

| 5.0           | -                    | mental results                                               |

|               | 3.6.1                | Experimental results at conducted EMI frequencies            |

|               | 3.6.2                | Experimental results at radiated EMI frequencies             |

| 3.7           | Conclu               | sion                                                         |

| CHAPTER 4     |                      | AN ACCURATE MODELING APPROACH TO COMPUTE                     |

|               |                      | NOISE TRANSFER GAIN IN COMPLEX LOW POWER                     |

|               |                      | RAILS GEOMETRIES OF POWER CONVERTERS                         |

| 4.1           | Motiva               | tion and Summary71                                           |

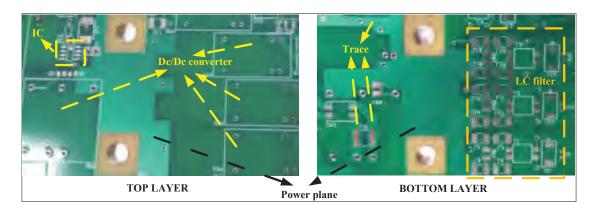

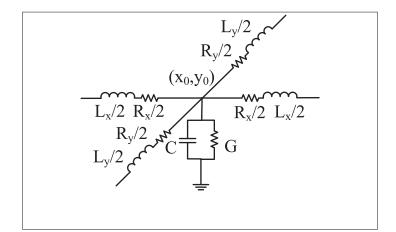

| 4.2           |                      | ground plane modeling                                        |

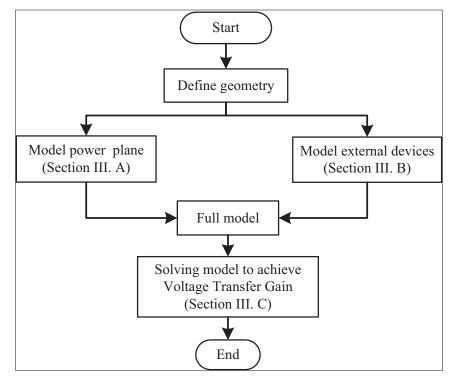

| 4.3           |                      | ng approach                                                  |

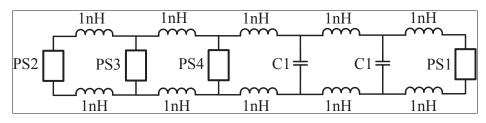

|               | 4.3.1                | 2D Lumped model for complex low power rails geometry         |

|               | 4.3.2                | External device modeling                                     |

|               | 4.3.3                | Solving approach                                             |

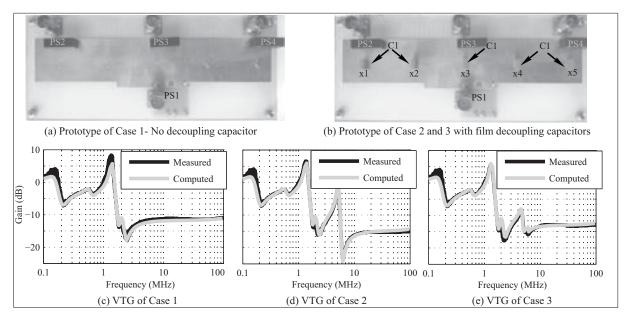

| 4.4           |                      | nental results                                               |

| 4.4           | 4.4.1                |                                                              |

|               |                      | Experimental setup                                           |

|               | 4.4.2                | 2D lumped model parameters identification                    |

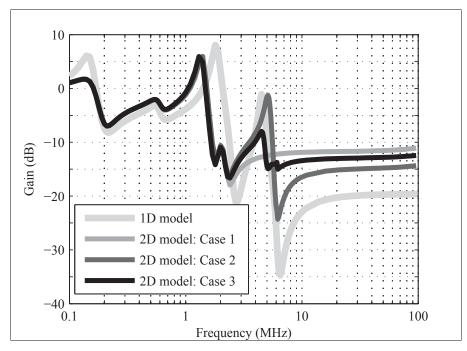

|               | 4.4.3                | VTG with decoupling capacitors                               |

|               | 4.4.4                | VTG with ferrite beads                                       |

| 4.5           | Conclu               | sion                                                         |

| CHA           | PTER 5               | APPLICATION OF Y-CAP ON NOISE ATTENUATION IN                 |

|               |                      | LOW POWER PARTS OF POWER CONVERTER                           |

| 5.1           | Introdu              | ction                                                        |

| 5.2           | Voltage              | e oscillation on gate driver DC/DC converter analysis        |

|               | 5.2.1                | Current through Miller capacitor, <i>i</i> <sub>GD</sub>     |

|               | 5.2.2                | Discharging current of Gate - Source Capacitor, $i_{GS}$     |

|               | 5.2.3                | Voltage oscillation on DC/DC converter inputs                |

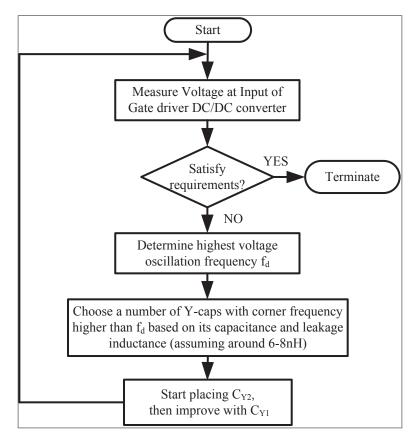

| 5.3           |                      | ed Y-cap application on noise attenuation in power converter |

| 5.4           | Experimental Results |                                                              |

| 5.5           |                      | sion                                                         |

| <b>CITA</b> 7 |                      | DESIGN CHIDELINES FOR A LOW NOISE PROFILE - LOW              |

| CHAI          | PTER 6               | DESIGN GUIDELINES FOR A LOW NOISE PROFILE - LOW              |

| <i>с</i> 1    | <b>•</b>             | POWER CIRCUIT                                                |

| 6.1           |                      | power converter design procedure                             |

| 6.2           |                      | nitigation design procedure for low power circuit113         |

|               | 6.2.1                | Step 1 - Gate driver circuit design113                       |

|               | 6.2.2                | Step 2 - Y-cap and Ferrite bead design115                    |

|      | 6.2.3    | Step 3 - Filter design6.2.3.1Filter design for Gate driver circuit |     |

|------|----------|--------------------------------------------------------------------|-----|

|      |          | 6.2.3.2 Filter design for sensing circuit                          |     |

|      | 6.2.4    | Step 4- Low power rail design                                      | 117 |

| 6.3  | Conclus  | sion                                                               | 117 |

| CON  | ICLUSION | AND RECOMMENDATIONS                                                |     |

| APP  | ENDIX I  | LOW POWER RAILS EQUIVALENT CIRCUIT                                 |     |

| APP  | ENDIX II | S-PORT CALIBRATION PROCEDURE                                       |     |

| BIBI | LIOGRAPI | НҮ                                                                 | 126 |

# LIST OF TABLES

Page

| Table 2.1 | List of commercial DC/DC converters used as Gate driver supply | . 32 |

|-----------|----------------------------------------------------------------|------|

| Table 2.2 | List of experimental characteristics                           | . 34 |

| Table 4.1 | List of external devices                                       | . 87 |

| Table 4.2 | Computing time of the proposed method                          | . 92 |

| Table 5.1 | Operational parameters of Buck converter                       | 105  |

## LIST OF FIGURES

|             | Page                                                                                 |

|-------------|--------------------------------------------------------------------------------------|

| Figure 0.1  | Current paths during ON state of power transistor 2                                  |

| Figure 0.2  | Noise current generated during turn - off intervals of power transistor              |

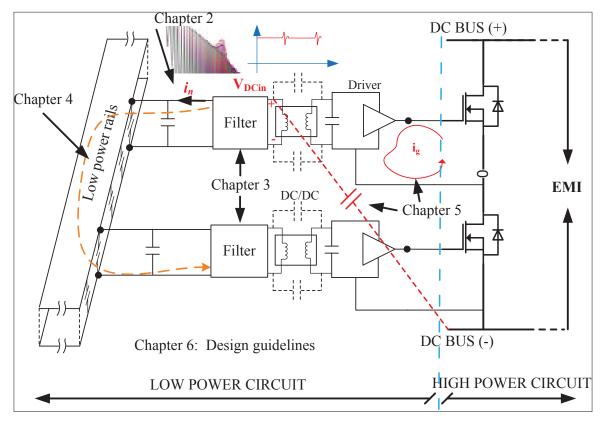

| Figure 0.3  | Power converter structure including high power and low power circuit                 |

| Figure 0.4  | Noise propagation in low power circuit of converter                                  |

| Figure 0.5  | Dead-time generator scheme for an H-bridge                                           |

| Figure 0.6  | Performance of gate signals with good ground integrity                               |

| Figure 0.7  | Performance of gate signals with bad ground integrity 8                              |

| Figure 1.1  | Research topic and state - of - the - art literature                                 |

| Figure 1.2  | Graphical thesis outline                                                             |

| Figure 2.1  | Turn - off switching waveform of SiC MOSFET module                                   |

| Figure 2.2  | Voltage ringing at low power rail of a laboratory Buck converter                     |

| Figure 2.3  | Power supply rejection ratio of typical op-amps                                      |

| Figure 2.4  | Schematic of the experimental setup for noise measurement                            |

| Figure 2.5  | Complete noise measurement setup with common mode current rejection by ferrite cores |

| Figure 2.6  | Prototype of a Buck converter used for noise measurement                             |

| Figure 2.7  | Equivalent impedance seen from power transistor to low power circuit supply          |

| Figure 2.8  | Ferrite cores to remove CM current                                                   |

| Figure 2.9  | CM impedance of the cable with different combinations                                |

| Figure 2.10 | CM current spectrum with and without ferrite cores on the cable                      |

| Figure 2.11 | DC/DC converter isolation capacitance measurement                                    |

# XVIII

| Figure 2.12 | DC/DC converter isolation capacitance                                                    | 33 |

|-------------|------------------------------------------------------------------------------------------|----|

| Figure 2.13 | Noise current of operation of difference devices                                         | 35 |

| Figure 2.14 | CM noise spectrum with TRACO DC/DC converter                                             | 36 |

| Figure 2.15 | DM noise spectrum with TRACO DC/DC converter                                             | 36 |

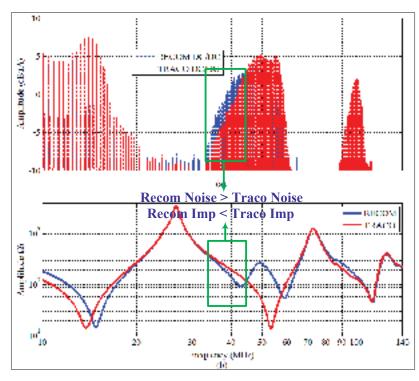

| Figure 2.16 | (a) DM current with different DC/DCs (b) Equivalent impedance (DC/DC + cables)           | 38 |

| Figure 2.17 | (a) DM current with different DC/DCs (b) Equivalent impedance of DC/DC + cables          | 39 |

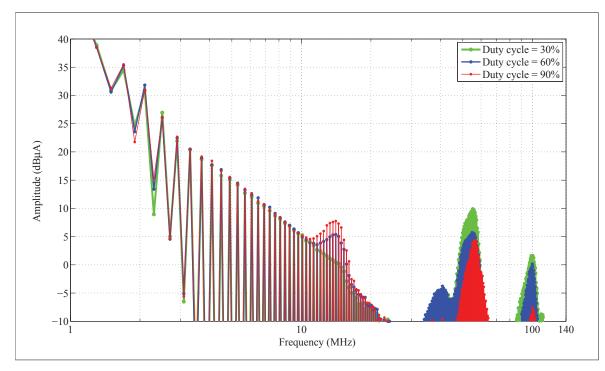

| Figure 2.18 | DM current spectra with CUI DC/DC converter, switching frequency of 120kHz               | 40 |

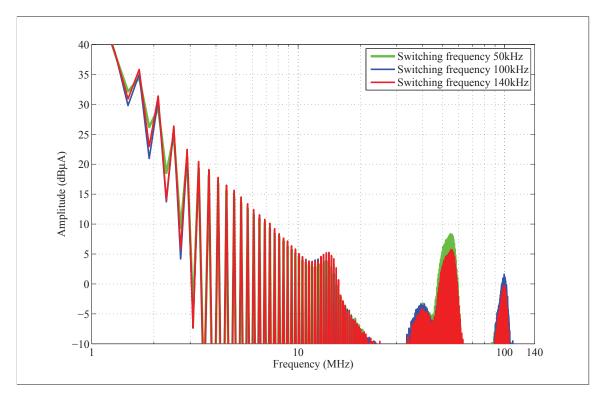

| Figure 2.19 | DM current spectra with CUI DC/DC at different switching frequencies                     | 41 |

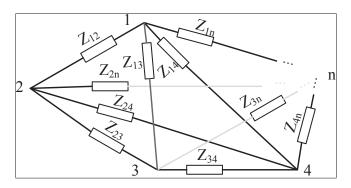

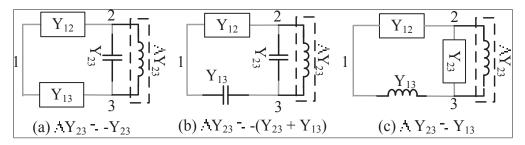

| Figure 3.1  | Basic noise paths in a power converter                                                   | 47 |

| Figure 3.2  | Equivalent circuit of a n-pin passive device                                             | 48 |

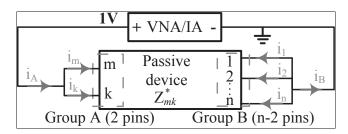

| Figure 3.3  | Group - impedance measurement by VNA                                                     | 52 |

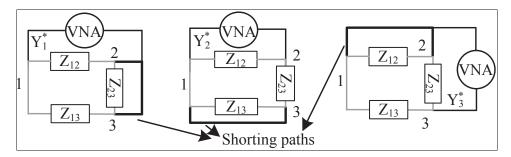

| Figure 3.4  | Impedance measurement procedure for 3-pin device with perfect shorting impedance paths   | 55 |

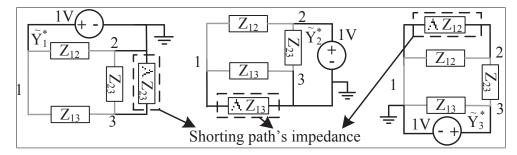

| Figure 3.5  | Impedance measurement procedure for 3-pin device with imperfect shorting impedance paths | 55 |

| Figure 3.6  | Specific cases in which significant errors are created                                   | 56 |

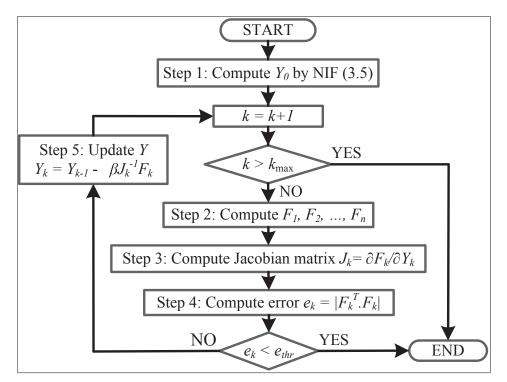

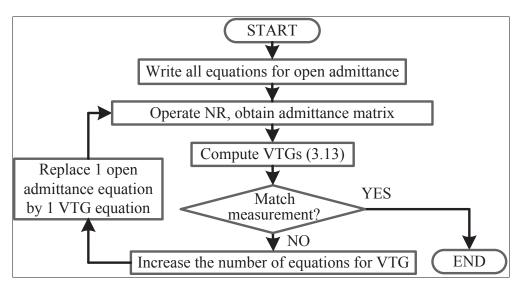

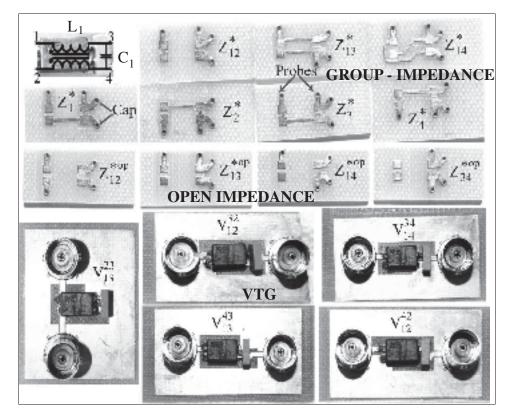

| Figure 3.7  | Newton-Raphson method for GIR at each frequency                                          | 56 |

| Figure 3.8  | Open admittance between pins 1 - 2                                                       | 59 |

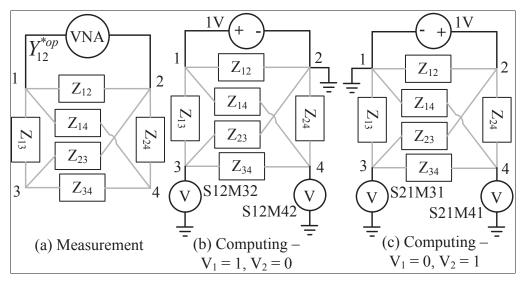

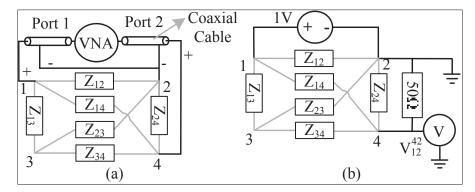

| Figure 3.9  | VTG (a) Measurement by S- ports (b) Computational model                                  | 60 |

| Figure 3.10 | Proposed NR with the combined set of equations                                           | 62 |

| Figure 3.11 | Over-relaxation factor computing algorithm                                               | 64 |

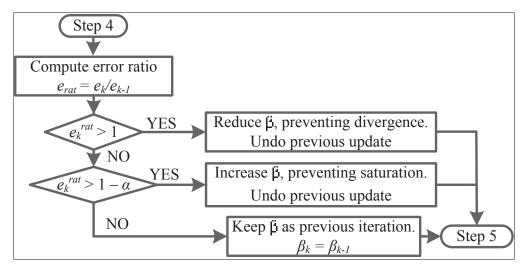

| Figure 3.12 | Impedance measurement procedure for 4-pin device                                         | 65 |

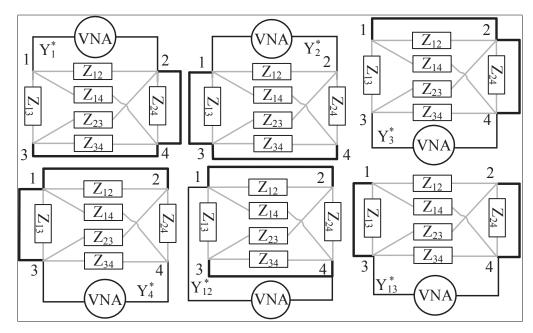

| Figure 3.13 | Measured prototypes of the LC filter                                                     | 66 |

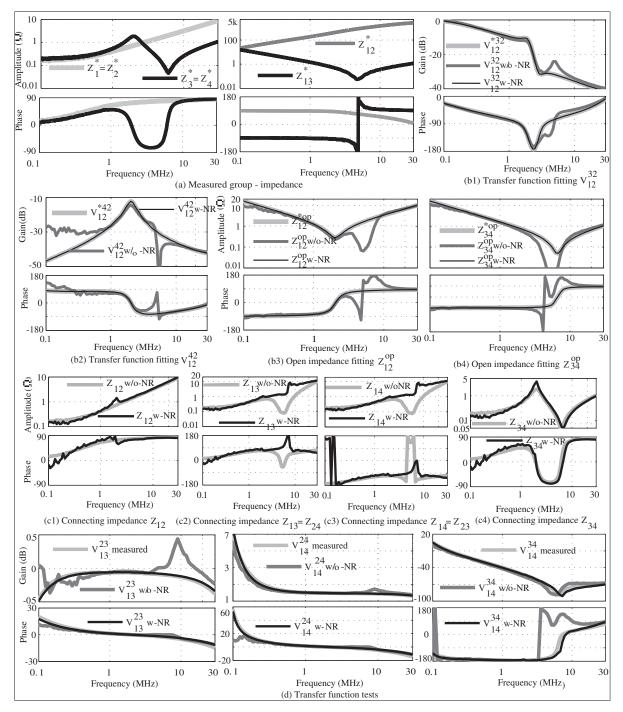

| Figure 3.14 | Experimental results for LC filter at low frequency                    |

|-------------|------------------------------------------------------------------------|

| Figure 3.15 | Experimental results for LC filter at high frequency                   |

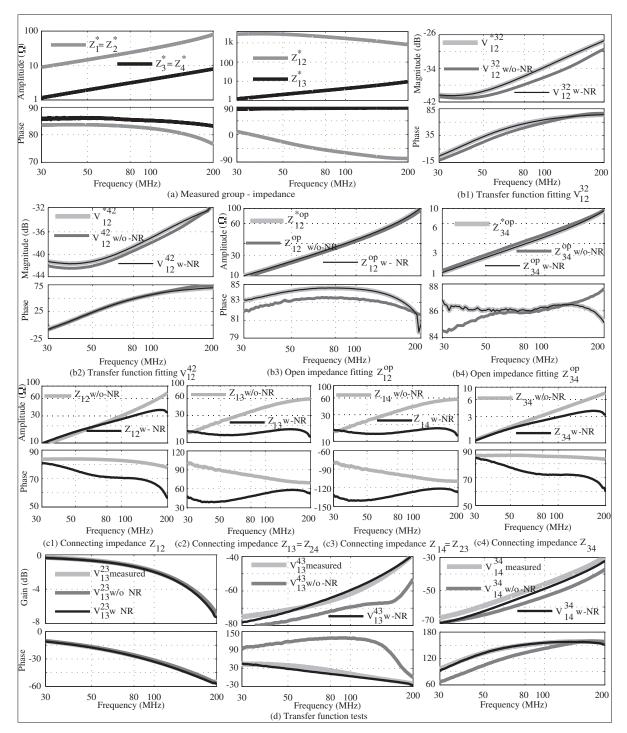

| Figure 3.16 | Newton Raphson characteristics                                         |

| Figure 4.1  | Noise propagation in low power circuit of converter                    |

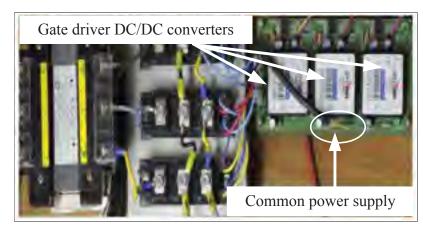

| Figure 4.2  | Supply for Gate driver of a laboratory prototype                       |

| Figure 4.3  | Low power rails of a power converter used in industrial application    |

| Figure 4.4  | Modeling approach                                                      |

| Figure 4.5  | Lumped model of one cell                                               |

| Figure 4.6  | Example for a 2D model of power rails                                  |

| Figure 4.7  | Voltage and current definition at cell 6                               |

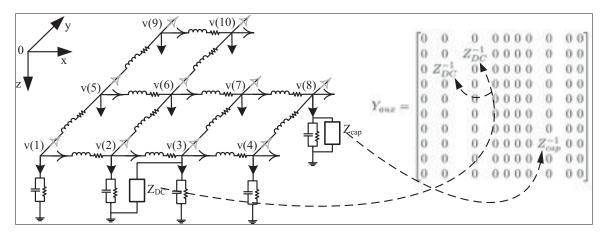

| Figure 4.8  | 2D lumped model with external devices                                  |

| Figure 4.9  | Prototype of low power rails                                           |

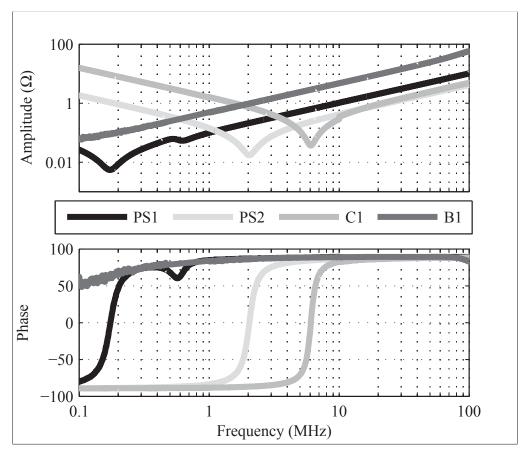

| Figure 4.10 | Measured impedance of external devices                                 |

| Figure 4.11 | 1D lumped model neglecting low power rails                             |

| Figure 4.12 | VTG of low power rails for different cases of decoupling capacitors 88 |

| Figure 4.13 | Computed VTGs from PS1 to PS2                                          |

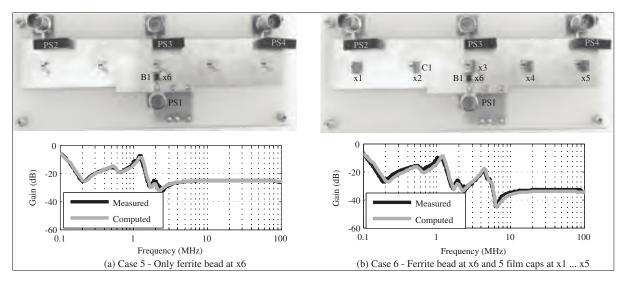

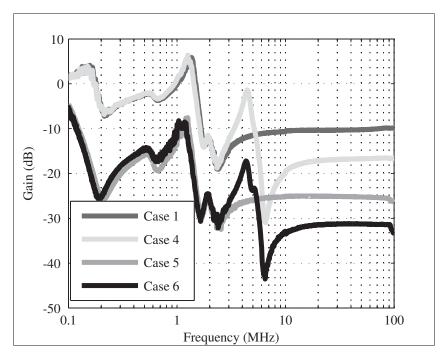

| Figure 4.14 | VTG of low power rails with different combinations of ferrite bead91   |

| Figure 4.15 | Experimental results with bead and film capacitor                      |

| Figure 5.1  | Noise propagation path                                                 |

| Figure 5.2  | Snubber configurations                                                 |

| Figure 5.3  | High frequency model of the triggering circuit                         |

| Figure 5.4  | Current path of $i_{GD}$                                               |

| Figure 5.5  | Current path of $i_{GS}$                                               |

| Figure 5.6  | Current sharing at Gate driver DC/DC converter                         |

| Figure 5.7  | Proposed Y-cap circuit to attenuate high frequency noise                             | 103 |

|-------------|--------------------------------------------------------------------------------------|-----|

| Figure 5.8  | Proposed method                                                                      | 105 |

| Figure 5.9  | Experimental prototype of Buck converter                                             | 106 |

| Figure 5.10 | Experimental results of input voltage of DC/DC converter with/without proposed Y-cap | 107 |

| Figure 5.11 | Branch impedance with proposed Y-caps                                                | 108 |

| Figure 6.1  | Complete design for low noise profile low power circuit                              | 112 |

| Figure 6.2  | Step 1 of design process - design Gate driver circuit                                | 113 |

| Figure 6.3  | Detailed guidelines for design Gate driver circuit                                   | 114 |

| Figure 6.4  | Step 2 - design Y-cap and ferrite bead                                               | 115 |

| Figure 6.5  | Step 3 - design filter for Gate driver                                               | 116 |

| Figure 6.6  | Step 4 - design low power plane                                                      | 118 |

# LIST OF ABREVIATIONS AND ACRONYMS

| ADC    | Analog to Digital Conversion         |

|--------|--------------------------------------|

| СМ     | Common Mode                          |

| DM     | Differential Mode                    |

| DSC    | Digital Signal Controller            |

| EMI    | Electromagnetic Interference         |

| ESR    | Equivalent Series Resistance         |

| FEM    | Finite Element Method                |

| GIR    | General Impedance Representation     |

| IA     | Impedance Analyzer                   |

| LISN   | Line Impedance Stabilization Network |

| LDO    | Low Dropout Linear Regulator         |

| РСВ    | Printed Circuit Board                |

| PEEC   | Partial Element Equivalent Circuit   |

| PSRR   | Power Supply Rejection Ratio         |

| PWM    | Pulse Width Modulation               |

| OP-AMP | Operational Amplifier                |

| NIF    | Node - to - node Impedance Function  |

| NR     | Newton - Raphson                     |

| THD    | Total Distortion Harmonic            |

| XXII |                         |

|------|-------------------------|

| VNA  | Vector Network Analyzer |

| VTG  | Voltage Transfer Gain   |

# LISTE OF SYMBOLS AND UNITS OF MEASUREMENTS

A Current unit Ampere FCapacitor unit Farad Η Inductor unit Henry Voltage unit Volt VΩ Resistor unit Ohm Frequency unit Hertz HzdBLogarithmic unit Decibel Active power unit Watt WMicro or  $10^{-6}$ μ Milli or  $10^{-3}$ т Kilo or  $10^3$ k Mega or  $10^6$ М

#### **INTRODUCTION**

Noise in power converter is an important topic which has been extensively researched. Typically, there are two types of noise mentioned in power converter researches:

- Electromagnetic Interference (EMI): noise generated by the converter, propagating to the grid, which impacts other circuits or device's operation. To limit these effects, EMI of each power converter must be controlled under certain levels given by standards such as FCC, CISPR11, CISPR22, IEC61000-4, MIL-STD-461, etc;

- Noise immunity: the noise picked up by the converter from the other circuits or devices in the grid, affecting the converter's performance. The converter must be designed to prevent this noise to degrade its performance.

Both types of related to the interactions between the power converter and other devices. On the other hand, there is another kind of noise inside the power converter, which can degrade the performance of control circuits. It is the noise in the low power circuit of the power converter. This noise results from the switching transients of power transistors. This noise type is not well addressed in literature, hence, it remains a difficult topic with multiple relating sub-topics for research. In order to fulfill this lack in literature, the problematic of this type noise will be introduced in the next sections of this chapter and the sub-research topics will be presented in the remaining chapters of this thesis.

#### **Origin of Noise in Low Power Circuit**

The first question arises is that "How is noise in low power circuit is generated by the switching transients of power transistor?". The answer of this question is the high frequency current created during turn - off intervals of the power transistor, it is explained below by the switching transient analysis.

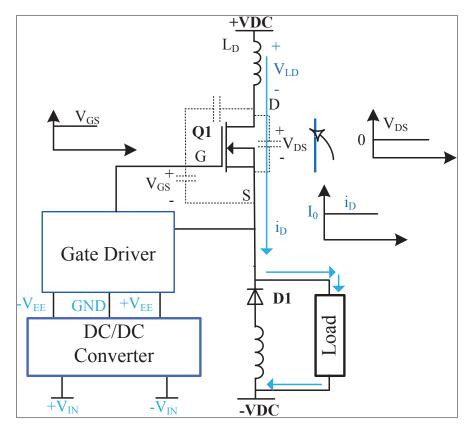

When voltage applied on the Gate of power transistor is higher than the its Gate threshold voltage ( $V_{GS} > V_{GS(th)}$ ), the transistor is at ON state with  $V_{DS} = 0$ . The current flows from +*VDC* to the load, as given in Fig. 0.1.

Figure 0.1 Current paths during ON state of power transistor

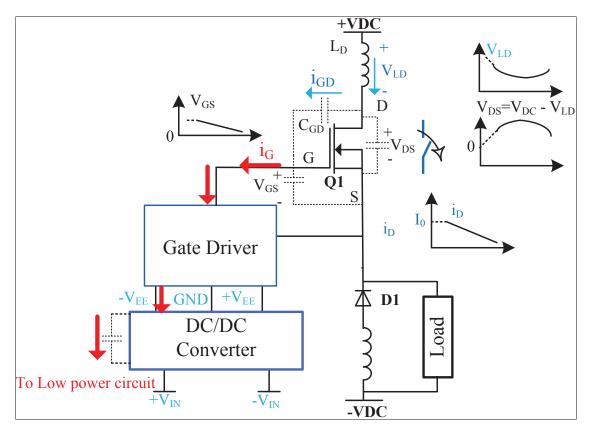

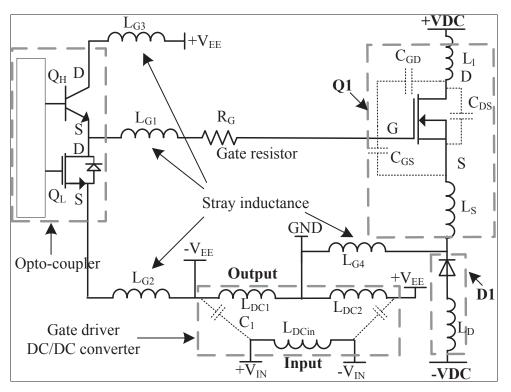

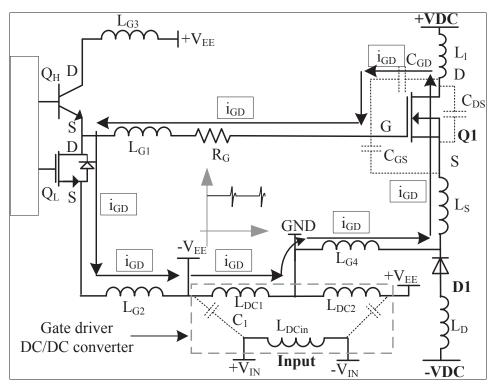

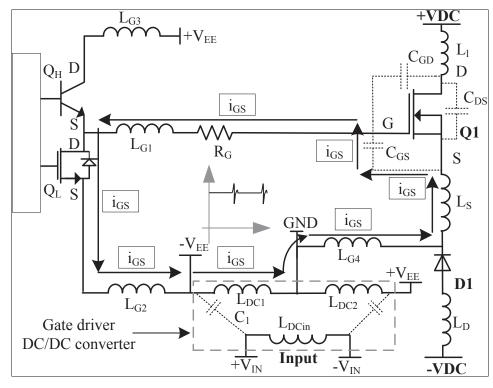

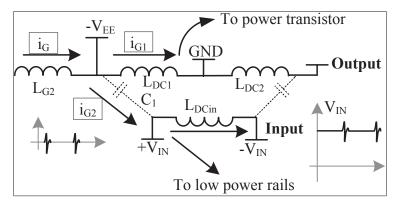

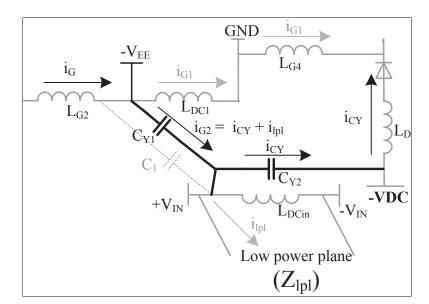

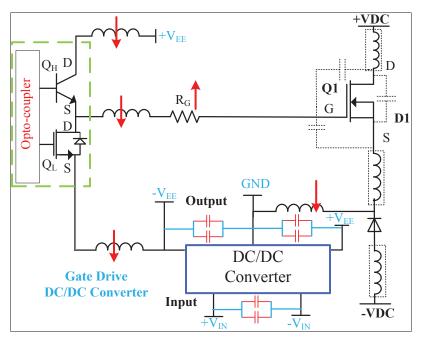

When voltage applied on the Gate of power transistor is lower than its Gate threshold voltage  $(V_{GS} < V_{GS(th)})$ , the transistor is turning to OFF state. At this moment, the voltage across DS junction,  $V_{DS}$ , increases. Consequently, voltage on stray inductance between Drain and +VDC,  $V_{LD}$ , changes creating current flowing to Miller capacitance,  $C_{GD}$ , of the power transistor. This current is a significant part of the noise current,  $i_G$ , in the Gate driver. This current propagates to the low power circuit via the isolation capacitance of the DC/DC converter supplying the gate driver. This process is shown in Fig. 0.2. The effect of  $i_{GD}$  on the noise spectrum in low power circuit will be presented by experimental results in Chapter 2.

Figure 0.2 Noise current generated during turn - off intervals of power transistor

### **Research Problematic**

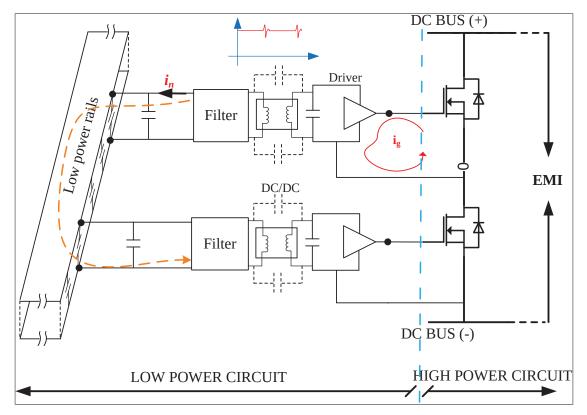

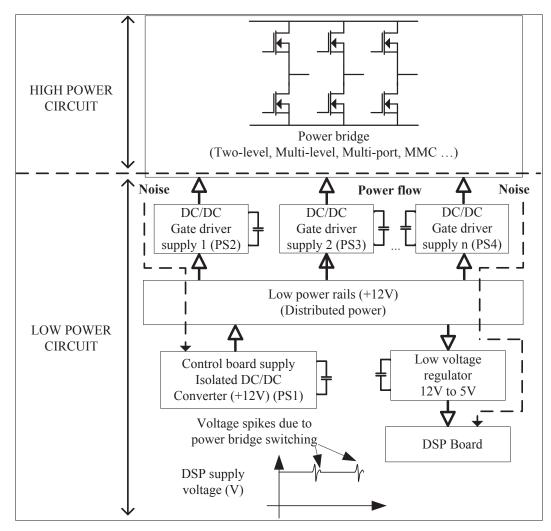

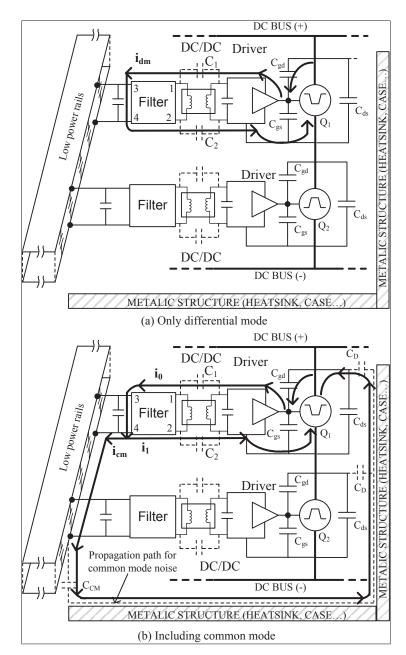

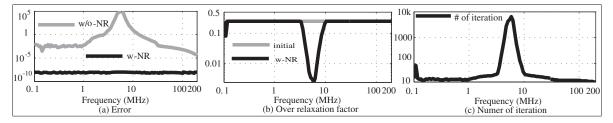

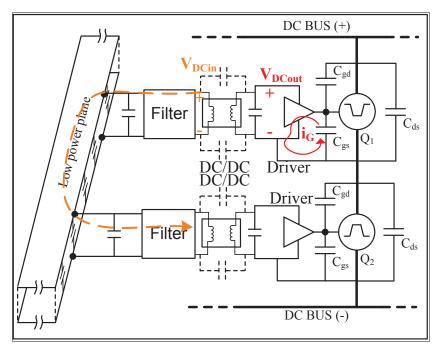

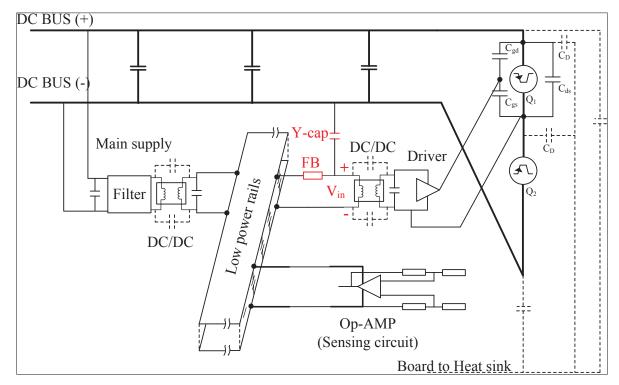

As pointed before, noise is generated by the switching transients of the power transistors of the high power circuit and propagates to the low power circuit through parasitic capacitive barriers. The definitions of high and low power circuits are presented in Fig. 0.3, which shows a typical power converter structure. The high power circuit includes the components operating on high voltage and current levels such as power transistors, DC bus filter, input filter, current and voltage sensors. The low power circuit contains the components operating on low voltage and current such as sensing circuit, i.e. outputs of voltage/current sensors with their amplifiers, DSP/micro-controller, gate driver to control the high power transistors, and power supplies of these functional circuits.

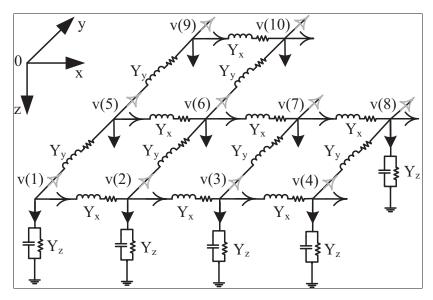

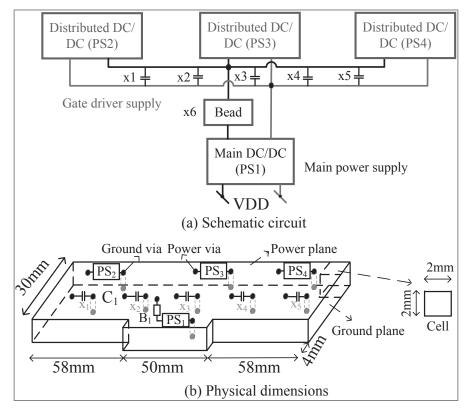

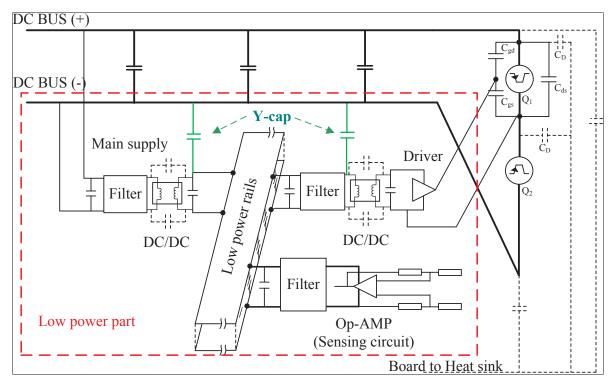

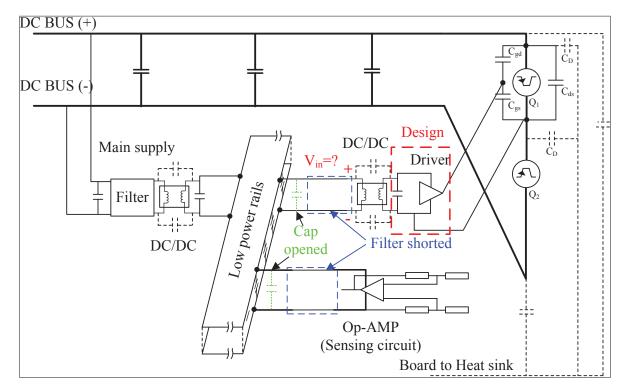

The detailed view of the low power circuit of a typical power converter is illustrated in Fig. 0.4. In this structure, an isolated DC/DC converter (PS1) regulates a +12V voltage from the power

Figure 0.3 Power converter structure including high power and low power circuit

source. The output of this DC/DC converter is connected to a low voltage power rails distributing power for the other DC/DC converters. These isolated DC/DC converters (PS2, PS3, PS4) provide positive and negative rails to supply gate drivers and micro-controllers. During the converter power operation, the switching process of them generates very high  $\partial V/\partial t$  across power transistors, propagating noise through the numerous stray capacitances in the converter structure. This noise travels along the connecting traces, passes through parasitic elements of gate drivers and distributed DC/DC converters before reaching the low power rails, where low power control circuits are located.

The parasitic capacitance between the input and output sides of the DC/DC converters (PS2, PS3, PS4), defined as isolated capacitance in manufacturer's documentations, is usually low, i.e. in the range of hundreds of pF. However, its combination with the surrounding impedance, i.e. the low power rails and impedances of functional circuits, can provide an easy way for noise to propagate in EMI frequency range. Once in the low power rails, the noise propa-

Figure 0.4 Noise propagation in low power circuit of converter

gates in a complex way to other DC/DC converters and other low-voltage devices, resulting in voltage spikes in their supply. These voltage spikes can cause inaccurate voltage and current measurements, malfunction of DSP and gate drivers, altering the overall reliability of the power converter. To avoid this issue and ensure the converter reliability, noise in the low power circuit must be handled carefully in the early design state.

#### **Example of Impact of Noise in Low Power Circuit**

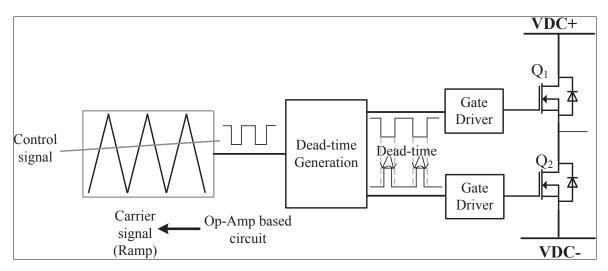

As mentioned previously, noise in low power circuit degrades the converter reliability, but how bad can its impact be? This section aims to provide an example of a typical gate signals controller of an H-bridge, as shown in Fig. 0.5. In order to prevent the current shoot-through where both transistors  $Q_1$  and  $Q_2$  are ON at the same moment, a dead-time is added between their triggering signals. This task is performed by the dead-time generator circuit. Input of the dead-time generator circuit is the comparison output of the control and carrier signals. In this scheme, the carrier signal (ramp) is generated by an Op-AMP based circuit. Due to very low power supply rejection ratio (PSRR) of the Op-AMP in EMI frequency range, it is expected that noise in its power supply will present on the output signal. An experiment is conducted to check the effect of noise on Op-AMP power supply to the performance of overall circuit.

Figure 0.5 Dead-time generator scheme for an H-bridge

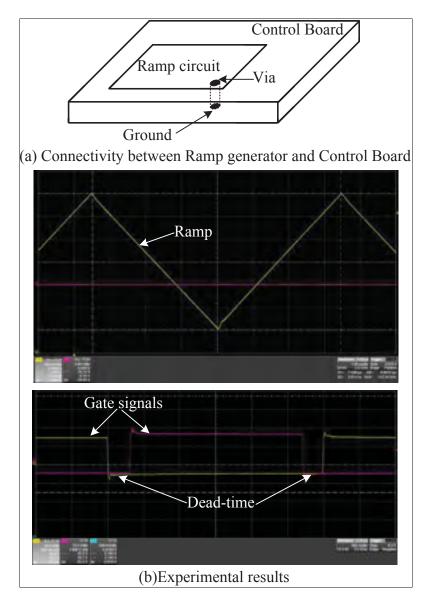

In good ground integrity condition, there is no noise on the Ramp signal while the gate signals are clean, and the dead-time is controlled at 200*ns*, as shown in Fig. 0.6.

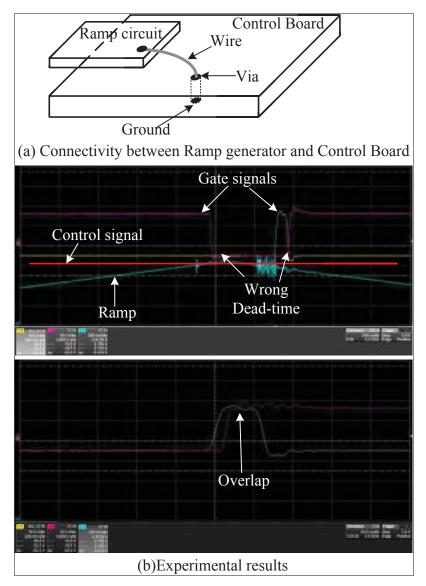

In case of bad ground integrity, where ground of the Ramp generator circuit is connected to that of the control board by small wire, high frequency noise appears on the Ramp signal, as illustrated in Fig. 0.7. Consequently, the dead-time generator circuit input has multiple commutations. Therefore, the dead-time is wrong. For instance, there are 350*ns* and 0*ns* dead-time periods instead of the designed period of 200*ns*. Once high frequency noise increases, the overlap period of 50*ns* between 2 gate signals appears creating current shoot-through in the DC bus, which can damage the power converter.

Figure 0.6 Performance of gate signals with good ground integrity

## **Motivation and Challenges**

Power converter reliability is always a critical concern for industrial applications. Amongst the factors degrading power converter reliability, noise in low power circuit is an important issue as pointed previously. Meanwhile, it is difficult for the designers to handle this issue due to following reasons:

Figure 0.7 Performance of gate signals with bad ground integrity

First, noise in low power circuit does not have direct impact on the power converter performance. Instead, noise can create errors at an input of a control circuit (feedback signals) or on the controller supply. Hence, the controller reacts to these errors providing wrong control signals. On the other hand, noise can be added directly to the control signals in its propagation paths. In both cases, errors on control signals easily lead to bad converter performance such as degraded total distortion harmonic (THD) and pulse width modulation (PWM) jittering. Second, noise may not be constant over time and may not be repeatable since it depends on transistor switching dynamic which changes with converter operating points. For example, duty cycle and switching frequency of power transistors change with different load demands and topologies (such as modern flyback). In addition, noise attenuation performance of filters changes with current/voltage bias conditions. These facts make noise difficult to observe.

Third, noise measurement in low power circuit during power converter operation is a tricky task. In fact, noise obtained in measurements is affected by the additional impedance of the measurement devices (such as voltage probe). Moreover, the common mode noise will increase with the additional paths provided by multiple measurement probes. These altered measured results mislead the debugging process. More dangerously, in case of improper measurement setup, the additional paths given by the measurement probes can create circulating current between the converter and the measurement devices, giving wrong converter operation or even damage both the converter and the measurement devices.

Due to the aforementioned reasons, noise mitigation in power converter is a difficult task. Specifically, this issue becomes more critical with such recent developments of power converters. First, SiC and GaN devices with short rising and falling times create noise in higher frequency than Si - devices (Kim *et al.*, 2017; Rondon-Pinilla *et al.*, 2014; Basu & Undeland, 2013; Han *et al.*, 2017a). In high frequency range (over 30MHz), noise mitigation is more difficult due to degraded filtering performance of the components. Second, control circuits become more complex in multi-level and multi-port converters with more devices and large dimensions of the common low power rails. In this case, noise is more difficult to manage due to complicated interactions between impedance of the low power rails and impedance of numerous components supplied by this rail.

Until now, there is no complete research for noise mitigation in low power circuit. Majority of power converter design guidelines for typical circuits were issued from know-how and practical experiences without computational models. On the other hand, the high frequency propagation problems, which can be applied for such case of noise, have been studied by the microwave

researches without direct application to power converters. Recently, the computational - based modeling techniques for noise prediction in power converter such as FEM and PEEC have been developed. However, taking into consideration the complete converter doesn't give the designers the ability to improve noise profile by changing design of typical components. Therefore, it is mandatory to develop a guideline for complete power converter design procedure based on computational models and insights of component effect on noise profile. It will help designers to understand well noise issue in converter resulting in improved design of each component to achieve low noise profile converter. The research presented in this thesis is performed to reach this goal.

In order to achieve the research targets, several challenges must be overcome in addition to the lack of references in literature and simulation tools.

First, it is necessary to observe noise and its influence on converter performance and reliability. Then, it is essential to divide the complex problem of noise propagation in a large low power circuit into smaller research objectives, and focus on small specific targets.

Second, since the research is performed based on measurement, the measurement setup must be selected correctly to avoid wrong measurement results. Taken into account the significant contribution of small inductive (in the range of nH) and capacitive elements (in the range of nF) on the total impedance in EMI frequency range, it is difficult to perform correct impedance measurements even with a modern device such Vector Network Analyzer (VNA). Every detail in the experimental setup must be taken care of to avoid errors in results.

Last but not least, the proposed modeling techniques must be validated in different components and different parameters to ensure its accuracy in general cases. The components and parameters for validation must be chosen properly and errors during measurement must be considered.

### **Research Objectives and Contributions**

As mentioned before, this thesis focuses on several small specific research objectives in order to understand and improve noise profile in the low power circuit. The research contributions are listed as below.

- 1. In chapter 2, introduce noise issue in low power circuit and propagation paths inside the power converter, which are not well addressed in literature;

- 2. In Chapters 3 and 4, propose new impedance models for the fundamental parts of the low power circuit such as passive devices and low power rails;

- 3. In Chapter 5, analyze and suggest an attenuation method for high frequency noise at the gate driver.

- 4. In Chapter 6, suggest a complete design process to achieve a low noise profile low power circuit.

#### Methodology

The research of all chapters in this thesis is performed by the following steps:

- Literature review: The literature relating to the research objects are reviewed from basic to state - of - the - art to understand the problem itself and figure out their limit on the application of the research topic to improve;

- Experimental observations: Since the topic of noise in low power circuit has not been welladdressed in literature, experimental observations are important to identify the research objectives. Variety of measurements have been performed with setups for each objective to define whether change in each part leads to change in noise profile;

- 3. Mathematical model development: Based on experimental observations and the literature review, mathematical models are developed;

4. Experimental verifications: The proposed mathematical models are validated with experimental measurements for different design to confirm its accuracy. If errors appear with the measurement results, the mathematical model will be further improved.

## Conclusion

In this chapter, we have introduced the problematic of the research presented in this thesis. The research on noise propagation in low power circuit is important to ensure power converter's high performance and reliability. Despite of its importance, it is still a big lack in literature for several reasons. The research presented in this thesis will contribute to to fulfill a part of this gap. In addition, we also presented the objectives, challenges and methodology to conduct the research.

## **CHAPTER 1**

## LITERATURE REVIEW OF NOISE ISSUES IN POWER CONVERTER

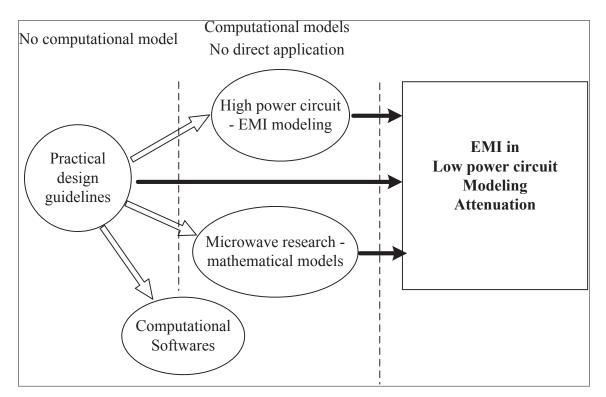

Noise propagation in the low power circuit is an important factor which impacts performance and reliability of power converters, as pointed in the previous chapter. A complete research on this area should consist of defining noise sources, analyzing propagation paths and developing noise mitigation techniques. Inspite of a deep litterature review, this topic has not been well covered in literature. However, separated parts of the project are studied in different relating research areas, as shown in Fig. 1.1.

Figure 1.1 Research topic and state - of - the - art literature

First, since converter design is indeed practical, we can start with the practical design guidelines summarized by the experience designers and component manufacturers. However, the *know - how* is not proven by mathematical models. This fact can lead to improper design in specific cases requiring more design iterations with high cost and time consuming. Thus, the computational model for each part of the circuit is mandatory to guarantee good design in term of noise minimization. This is the general motivation of the research presented in this thesis. We not only follow the fundamental design guidelines as practical designers, but we also research on the mathematical models of the circuit. It helps to understand for which cases guidelines are applicable or not and further improve them. As general speaking, we try to improve the practical guidelines by providing their bases of theories and computation. The computational models, as introduced previously as research objectives, can be researched by applying knowledge of relevant topics as below.

- Noise source analysis, filter design and mitigation techniques can be studied based on knowledge in the area of EMI modeling of high power circuit;

- PCB structure models can be referred to area of microwave researches which are conducted for high frequency applications;

- Some specific PCB structure models can be extracted by computational softwares.

Even though the outcomes of these studies are very useful, they are not directly applicable to our main research topic due to different objectives and applications. Since these topics are identical, it is more convenient to present their comprehensive reviews in the relevant chapters. In the next sections of this chapter, we will summarize the literature at high level to provide the overall view of related research areas, how they are useful to our research and what are the limits making them not directly employed to the main research topic.

## **1.1 Practical design guidelines**

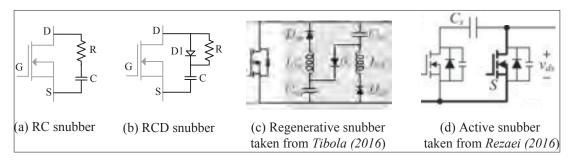

The know - how to design low noise power converter is represented by the practical design guidelines. These guidelines are introduced in design handbooks (Johnson *et al.*, 1993; Salman & Friedman, 2012; Horowitz & Hill, 1989) and manufacturer's documentations (TI, 2001, 2015). These guidelines provide excellent practice for high speed signal integrity such as: routing laws for gate driver, supply and ground planes in mixed - signal PCB, use of decoupling capacitors and ferrite beads, and so on. However, these suggestions are not based on mathematical model, so it is difficult to employ in specific cases. Below are some examples:

- Ferrite beads are suggested to prevent high frequency noise arriving at the *victim circuit* in high frequency. The ferrite bead impedance is the sum of its resistive and inductive parts. In case that the *victim circuit* has capacitive impedance, the total impedance of ferrite bead and *victim circuit* is represented by the resistive part at the resonant frequency created by the capacitive and inductive parts (serial LCR circuit). So, which ferrite bead impedance curve should be used to avoid noise amplification in a certain frequency range? Where will noise propagate if it is blocked from the *victim circuit*?;

- 2. In order to supply a circuit, a low power rails with power/ground plane structure is used to connect that circuit and the source. It is to minimize the impedance between these two circuits, preventing voltage spikes on the target circuit. EMI attenuators such as decoupling capacitors and filters are used to further attenuate noise. Usually, the decoupling capacitors are distributed along the low power rails and the filters are connected directly to the circuits. However, how to distribute decoupling capacitors on the low power rails? Which value of the capacitors should be used for a specific converter structure (different power transistors and layout of low power circuit lead to different noise frequencies, and hence, different values and locations of decoupling capacitors)? Which filters should be used? How impedance of the filter interact with that of the low power rails? Can it ensure noise attenuation or result in noise amplification in certain frequency ranges? These issues become more complex in case that numerous circuits are placed on the low power rails.

In such above cases, one must use a *trial - error* approach in several design iterations until an acceptable noise level is achieved. However, these above questions can be answered in early design phase by using computational tools to analyze the circuit and ensure a reliable design. There are mathematical models in research areas discussed in the following sections.

### 1.2 Research of EMI in high power circuit

EMI in high power circuit of power converter has been the essential research topic over the last ten years. Several efforts have been made to obtain EMI prediction for a whole power converter (Espina *et al.*, 2011; Rondon-Pinilla *et al.*, 2014; Ferber *et al.*, 2013; Zhai *et al.*, 2015; Ardon *et al.*, 2010; Musznicki *et al.*, 2013; Mrad *et al.*, 2013). In addition, in order to meet conducted EMI standards, passive and active EMI filters are used to attenuate noise. They have been improved in terms of frequency response (Raggl *et al.*, 2010; Akagi & Shimizu, 2008; McDowell & Hubing, 2015; Shin *et al.*, 2015) and density (Biela *et al.*, 2009; Maillet *et al.*, 2010).

These researches provide the insights of noise origin, EMI analysis, and EMI filter. These knowledge are the proper basics for conducting research on EMI in low power circuit. However, they are not always valid to employ directly in board level due to the following reasons.

- On board level, CM and DM are not well defined and separated as in high power circuit due to multiple propagation paths provided by PCB structures and components. Thus, CM and DM models of the filter developed for high power circuit are not valid in low power circuit;

- 2. In high power circuits, EMI model of a complete converter can be the summary of several parts whose impedance can be measured directly (Zhai *et al.*, 2015). This approach is valid since each part can be considered as a two port circuit. However, at board level, the low power rails is a multi-port circuit. Hence, which impedance can be used to compute noise propagation while there are plenty of the port to port impedance? Since impedance is not effective to evaluate noise propagation, what can be used?;

- 3. In high power circuit, EMI attenuation is mostly focused on EMI filter design to comply with standards. Therefore, EMI filter is designed with the only purpose of preventing noise to propagate to the input of the converter. However, in low power circuit, the situation is more complicated. Since noise always propagate on the low impedance paths, increasing

impedance at one port by the filter can result in noise increasing at the other ports of the circuit. Therefore, "where should we block noise and where should we let noise propagate to?". This is a challenge that designers must face. Such difficulties clearly show that care must not only be taken in the local design, but also the complete circuit.

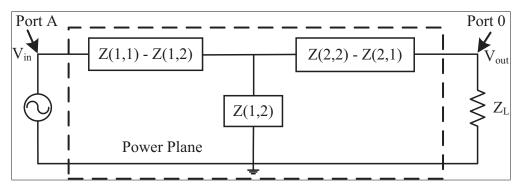

#### **1.3** Microwave researches

As pointed above, multi-port PCB structures are usually designed in low power circuit. In order to study noise propagation in low power circuit, analysis of these structure in high frequencies (up to hundreds of MHz) must be done. It is not focused in power electronics area, but has been a popular topic in microwave researchs (Pozar, 2009). Power/ground planes structure used for low power rails design is analyzed with either rectangular (Lei *et al.*, 1999; Hampe & Dickmann, 2005; Fan *et al.*, 2001) or arbitrary geometries (Štumpf & Leone, 2009; Štumpf, 2014; Smith *et al.*, 2001; Bednarz *et al.*, 2014; Lee *et al.*, 2015), including effects of decoupling capacitors (Kim *et al.*, 2004; Guo & Hubing, 2006; Hampe *et al.*, 2007; Kim & Swaminathan, 2001). The transmission line effect, skin effect and proximity effect are important to consider in these high frequencies (Haus & Melcher, 1989). In addition, the PCB structure without current returned path, which is popular in low power circuit, is developed by the powerful Partial Element Equivalent Circuit (PEEC) model.

However, these methods are not directly applicable to the low power circuit due to following reasons. First, since these models are developed for very high frequency applications (can be up to  $GH_z$ ), several effects are considered making the models complicated and not practical to employ for power electronic applications. Second, these models are not flexible to merge into a larger model with numerous other components used in the low power circuit. Therefore, more practical and flexible modeling approaches must be developed to predict noise in low power circuits.

## **1.4** Computational softwares

Beside mathematical approaches introduced previously, there are softwares that can be used to extract the parasitic elements of devices and PCB structures such as FastHenry, FastCap (free), Q3D Ansoft, StarRC, QRC (commercial). These softwares are developed based on mathematical methods such as Finite Element Method (FEM), PEEC and Method-of-Moment (MoM). Even though softwares provide many advantages, engineers must have knowledge of the problem's physics and valid conditions of the software for effective utilization. In addition, the available softwares are not able to compute the EMI model of a complete low power circuit including arbitrary PCB structures and numerous passive and active devices. Furthermore, since these softwares only provide the extracted result of completely built component or PCB structure, they do not provide information to improve the design for lower noise profile.

Due to these above limits, in our point of view, softwares can be used for PCB structures that require complex mathematical models such as thin power/ground plane or PCB trace without current return path underneath. However, they are not effective for modeling a complete circuit.

## 1.5 Conclusion

In this chapter, a general review of the topic of noise in low power circuit has been presented. As pointed before, due to the lack of literature on the main research topic, it is divided into small specific targets which are related to other research areas such as practical design guidelines, EMI in high power circuit and microwave research. This chapter also introduces the advantages and limits of these studies in term of application to EMI research in low power circuit. Based on these discussions, each specific objective will be developed using the basics of relevant research topics.

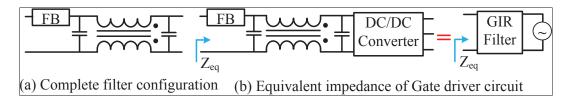

The research contributions will be presented in the next chapters of this thesis, as summarized in Fig. 1.2. Chapter 2 provides the experimental evidences of noise propagation inside power converter, which is the reason for conducting the research presented in this thesis. The proposed modeling approaches for passive devices (GIR) and low power rails are introduced in Chapters

3 and 4, respectively. Chapter 5 presents the Y-cap application method to attenuate noise at high frequency where EMI filter is not effective. The complete design process to minimize noise in low power circuit is suggested in Chapter 6. Finally, the conclusion and recommendations for future works are presented.

Figure 1.2 Graphical thesis outline

## **CHAPTER 2**

# EXPERIMENTAL INVESTIGATION OF NOISE PROPAGATION IN LOW POWER CIRCUIT OF POWER CONVERTER

### **Summary**

As pointed before, there is a lack of literature on noise propagation in low power circuit, meaning that this topic has not been mentioned in research. Therefore, the first topic is to prove the existence of the problem itself. It is done by measuring noise and observing its changes with different designs and operating points of the power converter. This content is presented in this chapter by experiment results on a typical Buck converter designed for noise measurement purpose. This chapter also introduces the voltage variation limits of fundamental components to emphasize the importance of noise control in the low power circuit.

#### 2.1 Introduction

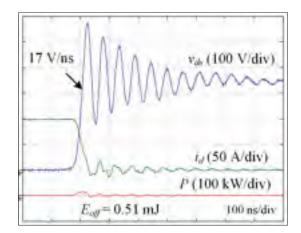

While Silicon MOSFET has been used in power converter applications for decades, Silicon Carbine MOSFET (SiCMOS) has been developed in the last 10 years. Due to the high switching frequency of SiCMOS, the sizes of key components in the converter such as magnetic devices (input inductors of the Buck/Boost/Rectifier, transformers of the Flyback) and output capacitors can be reduced while the current and voltage ripples are maintained in the acceptable ranges (Biela *et al.*, 2011). Therefore, SiCMOS is the key to achieve high power density converter design. However, the sharp voltage applied on the SiCMOS during very high switching operation with short rise and fall times result in voltage ringing across the switching devices at very high frequency, i.e. 50 - 100MHz, due to the effect of stray inductance and device's parasitic capacitances (Han & Sarlioglu, 2016) - (Li & Munk-Nielsen, 2014). An example of the voltage ringing across Drain - Source ( $V_{DS}$ ) of the SiCFET is shown in Fig. 2.1 which is captured from (Shi *et al.*, 2017). This voltage ring produces higher EMI than standard Si-based converters in the conducted EMI frequency range (10 - 30MHz) (Kim *et al.*, 2017; Rondon-Pinilla *et al.*, 2014; Basu & Undeland, 2013; Han *et al.*, 2017a). Moreover, the voltage and

current spectra through switching devices in SiC - based converters are  $20-30dB\mu V$  and  $20 - 30dB\mu A$  higher than those in the Si-based ones in frequency range from 20 to 100MHz, respectively (Oswald *et al.*, 2014). These augmented spectral contents at high frequency will be translated into significant increase of EMI at the converter input (Zare *et al.*, 2015).

Figure 2.1 Turn - off switching waveform of SiC MOSFET module Taken from Shi *et al.* (2017)

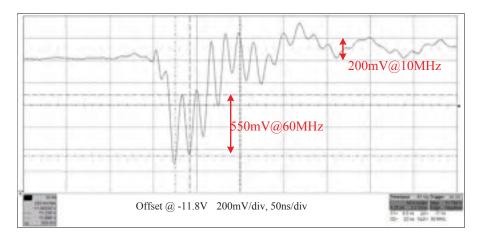

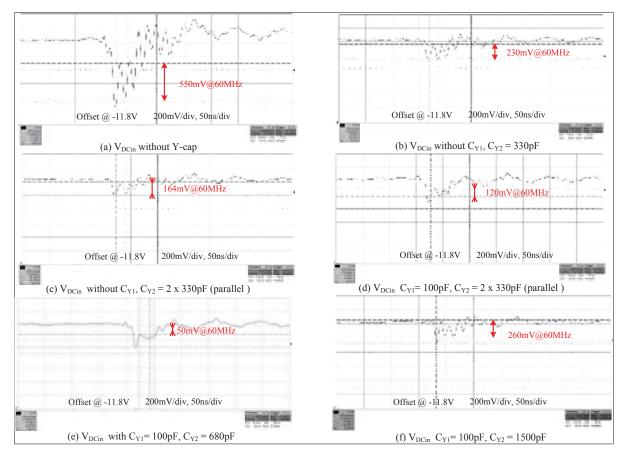

On the other hand, these voltage ringings can propagate to the Gate of power transistors, resulting in voltage oscillation on the Gate - Source ( $V_{GS}$ ) during transient time (Clemente *et al.*, 1987; Nguyen & Blanchette, 2017). Taking into account the fact that small gate resistor is required to minimize the delay time on rising/falling edges and minimize the power dissipation during high frequency switching operation of the SiCFET, the high frequency voltage ringing appearing on  $V_{GS}$  can be seen by all the components in the Gate driver circuit, including the output of Gate driver power supply. From there, these voltage ringings can propagate to the input of the DC/DC converter, i.e. low power rail, by passing through its *parasitic capacitance* (Nguyen *et al.*, 2017c). The low power rail voltage waveform of a reduced scale Buck converter, which will be introduced in Chapter 5, is shown in Fig. 2.2 with a quite high voltage variation at high frequency, i.e. 200mV at 10MHz and 550mV at 60MHz.

From the low power rails, this noise can result in voltage spikes on the components. Although no standard exists on an acceptable noise margin, each component has strong requirements

Figure 2.2 Voltage ringing at low power rail of a laboratory Buck converter

on their supply variation, which are usually described in the manufacturer's documentations. Below are the examples of characteristics related to noise on power supply of two important components in low power circuit such as the digital signal controller (DSC) and operational amplifier (Op-amp).

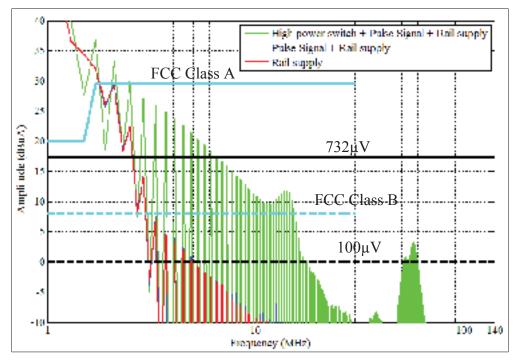

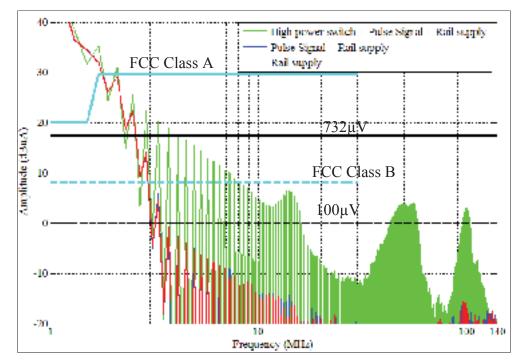

- In the DSC case, the limit of its power supply variation is  $\pm 5\%$  (TI, 2016), which is equivalent to the limit of 165mV variation in absolute value. However, the noise margin required for proper operation is much more critical. As suggested by the manufacturer (TI, 2015), the power supply noise must be quite low to not influence the ADC's step size of  $732\mu V$  for the input range of 0-3V. In addition, the reference voltage for ADC block must be less than  $100\mu V$ . Violating these limits will increase the on-chip PLL jittering which impacts the controller precision, which is mandatory to ensure low THD waveforms;

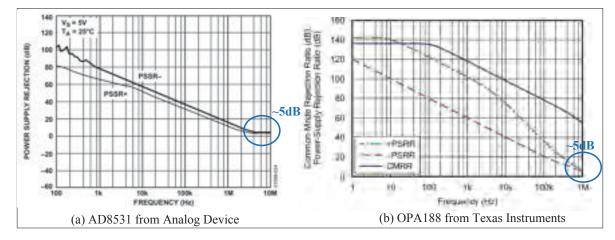

- The Op-amps are usually used in current and voltage sensing circuits. Their outputs are connected to the ADC inputs of the controller. Therefore, noise and errors on its outputs are critical to achieve accurate control. However, the Op-amp power supply rejection ratio (PSRR) is very low inside the EMI frequency range, meaning that noise appearing on its power supply can propagate into the outputs with few or no attenuation. For instance, as examples shown in Fig. 2.3a and b, the PSRR of the AD8531 and OPA188 is less than 5dB at frequency over 3MHz and 1MHz, respectively. Assuming that there is 200*mV* noise at

the power supply at 3MHz considering the single supply of 5VDC, the noise observed at the output is 150mV, which is equivalent to 3% error of the full sensing range. Depending on the sampling rate of the controller, this error can randomly appear on the controller computation. Once all the sensed signals content a few percentages of errors, the control becomes jerky and even unstable resulting in poor converter reliability.

Figure 2.3 Power supply rejection ratio of typical op-amps (a) AD8531 Taken from Analog Device (2008) (b) OPA188 Taken from TI (2016b)

The above examples show the fact that violating the voltage variation limits of the components can drive the power converter into an erratic control behavior resulting in poor reliability. Therefore, it is mandatory to control noise appearing in the low power circuit.

Due to the lack of literature about the research problematic, this chapter aims to answer the essential questions of noise in power converter: "a) **Does noise exist in low power circuit of power converter and b) where it comes from?**" This chapter provides the clearly observable evidences of noise in low power circuit and noise propagation from high power circuit to low power circuit by experimental results. In addition, this chapter also investigates the effects on noise spectra of different operating points of the high power circuit and impedance of components in the low power circuit by experiment. Based on the results shown in this chapter, the modeling approaches and noise attenuation methods will be introduced in the next chapters.

### 2.2 Experimental setup

## 2.2.1 Overall experimental setup

Noise measurement is a complex task. Consequently, it requires a well designed experimental setup to avoid incorrect results. In this section, a proposed experimental setup is explained in details. Since noise measurement is strongly related to the experimental setup, the converter is designed carefully to control the noise propagation paths and avoid unwanted noise sources. The standard Si-FET is used as the high power switch of the converter instead of SiCMOS to keep the gate driver circuit simple and convenient to analyze the noise propagation paths. Instead, the SiCMOS driver circuit contains the supported current amplifier circuit complicating the noise propagation paths to be determined (Cree, 2014) - (Avago, 2014). It is worth noticed that the commercial DC/DC converters are used in this experiment due to its compliance with industrial EMI standards. It is essential in the proposed experiment to avoid the unwanted noise created by a non-standard compliant DC/DC converter.

The purpose of the experiment is to measure noise in the low power circuit of the power converter during the switching transients of the power transistors. Since the low power circuit is linked to the power supply of the high power transistor's gate driver, the voltage probe's impedance may have significant influence on the results. Therefore, the current measurement method using current transformer is employed to avoid direct contact with the converter circuit. The results can be translated to the voltage spectrum by multiplying current spectrum with LISN impedance.

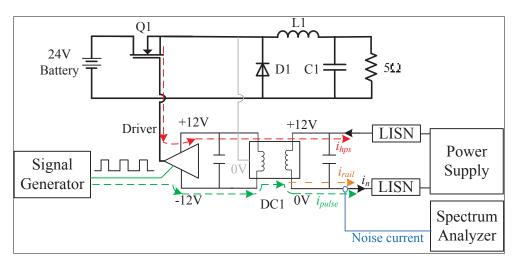

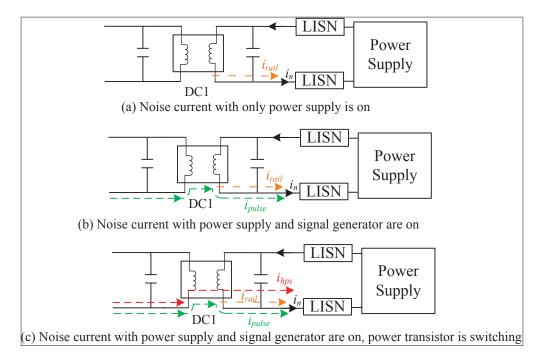

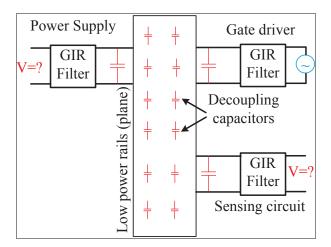

The experimental setup, shown schematically in Fig.2.4, is used to measure the current spectrum of  $i_n$  in the low power rail supplying the gate driver DC/DC converter DC1. The measurements are taken at several operating points of the high power circuit and low power circuit components.

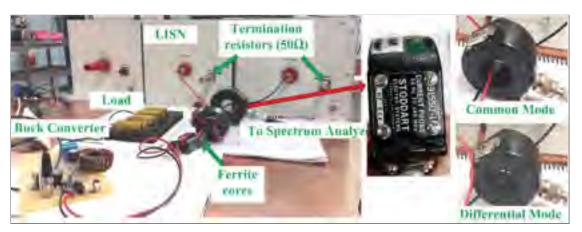

The experimental setup is shown in Fig. 2.5, including:

Figure 2.4 Schematic of the experimental setup for noise measurement

Figure 2.5 Complete noise measurement setup with common mode current rejection by ferrite cores

- An experimental buck converter, which will be presented in Section. 2.2.2;

- An Agilent Signal Analyzer CXA N9000A to measure the current spectrum using the Current probe (Lindgren, 2008);

- Several ferrite cores are used in the winding of the cables prior to enter in the LISN to attenuate the CM noise from measurements. It is to ensure that the measured results for DM current is not affected by CM current. This practical method will be introduced in Sec. 2.2.3.

Fig. 2.5 also shows the way of measuring CM and DM current noise. DM current is measured on 1 line (positive or negative rail) whereas the CM current is measured on both 2 lines.

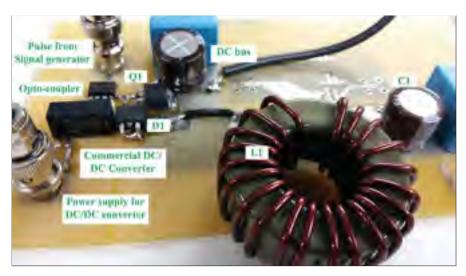

## 2.2.2 Buck converter designed for noise measurement

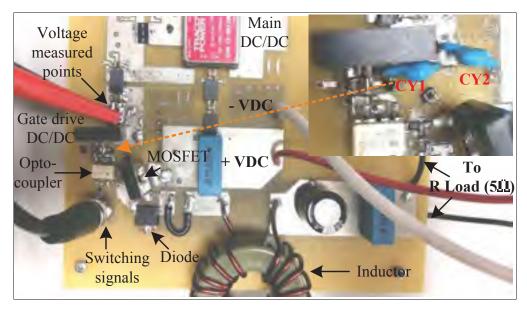

A basic Buck converter prototype is shown in Fig. 2.6. Its operating principle has been introduced in many documentations, so it is not presented here to keep the focus on noise measurement. The noise current is measured at the low power rail, typically 12V, which supplies the input of the Gate driver DC/DC converter (DC1), whose outputs are typically  $\pm 12V$ . To avoid multiple noise sources and multiple propagation paths for noise in the setup, resulting in unknown results, the power supply for each part is chosen as below:

- The DC bus is supplied by a 24V battery bank consisting of 2 serial 12V batteries. Since noise in the current from the battery is negligible, there is no noise coming from the supply of the DC bus. In addition, the batteries are isolated from other devices used in the measurement, so their is no unknown propagation path for noise to travel to the low power circuit through those devices;

- The pulse driving the power switch,  $Q_1$ , is provided by a commercial signal generator to avoid the noise to propagate to the remaining parts of the low power circuit. In practical applications, the pulse signal is generated by a comparator of an analog controller or a digital micro-controller. For both devices, the power supply is generated from the low power rails, where noise is measured. This loop is a possible propagation path for noise in low power circuit, which complicates the analysis of the results;

- A commercial DC power supply to provide 12VDC rail to the input of DC1 via a 2-phase LISN. Each phase of LISN is terminated by a standard 50Ω resistor, resulting in 100Ω constant impedance of the DC power source over large frequency range. This selection ensures that their is no noise coming from the source of the power rails and impedance of the power source is constant.

Figure 2.6 Prototype of a Buck converter used for noise measurement

Finally, there are 3 possible noise sources in the proposed setup, propagating to the power supply by the paths indicated in Fig.2.4:

- $i_{rail}$  resulted from the voltage ringing due to switching operation of DC1;

- $i_{hps}$  produced by the voltage ringing due to switching operation of Q1;

- $i_{pulse}$  created by the input pulse of the Opto-coupler.

The noise current measured by the signal generator is the sum of 3 aforementioned currents.

# 2.2.3 Common mode noise rejection

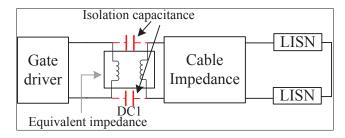

Noise measurement on a cable can consist of CM and DM noise with significant contribution of CM. It is difficult to analyze the noise propagation paths corresponding to each mode. Thus, removing CM while measuring DM current is necessary to properly analyze the obtained noise spectrum. Taken into account the cables used to connect the input of DC1 to the LISN, as illustrated in Fig. 2.5, the equivalent impedance seen from the power transistor to the power supply for the low power circuit is shown in Fig. 2.7. In this figure, the DC/DC converter is

represented by its isolation capacitance. In order to reduce CM current, a practical method is using common chokes to increase the CM impedance of the cables.

Figure 2.7 Equivalent impedance seen from power transistor to low power circuit supply

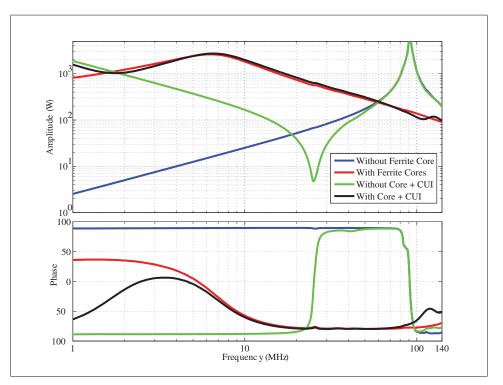

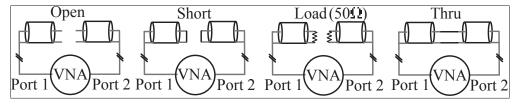

In this approach, the cable CM impedance is increased by winding positive and negative rails together on the ferrite cores. Considering the fact that each ferrite core is effective on a limited bandwidth, several cores are used in series to increase the CM impedance of the cables over the considered frequency range (100kHz - 140MHz), as shown in Fig. 2.8. This figure also shows the cable impedance measurement setup with the Vector Network Analyzer (VNA) Agilent E5061B using the method called port 1 reflection, which is accurate for high bandwidth (up to 3GHz) and mid-impedance level (Keysights, 2017). Prior to take the measurements, the device is calibrated using open, short and load (standard 50 $\Omega$ ) calibration procedure.

The CM impedances of the cable with and without the ferrite cores are shown in Fig. 2.9. One observes a significant increase of the CM impedance with the effect of ferrite cores compared to the case without ferrite core, especially in the frequency range of 100kHz - 60MHz. In the frequency range over 60MHz, the CM impedance of the cable without ferrite cores is higher due to the transmission line effect. The total of DC1 isolation capacitance and CM impedance of cable for both cases with and without ferrite cores are also plotted in Fig.2.9. It is the impedance seen from the high power transistor to the +12V rail power supply of the low power circuit while neglecting the stray inductance in the gate driver circuit. This assumption is valid since the stray inductance is very small compared to the CM impedance of long cables used

Figure 2.8 Ferrite cores to remove CM current

Figure 2.9 CM impedance of the cable with different combinations

in measurement, especially with ferrite cores. Thus, it is interesting to analyze the mentioned total impedance with the CM current spectrum obtained from measurement.

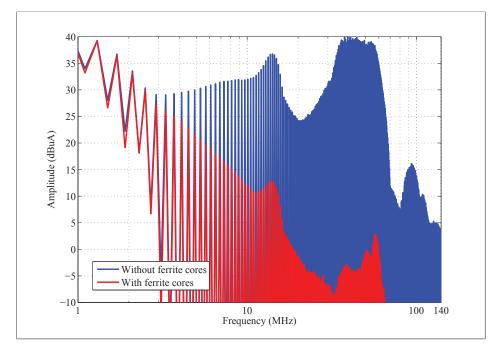

One observes the same impedance for both cases in the frequency range below 2MHz due to the high impedance of the isolated capacitance of DC1. The ratio between these two impedance increases logarithmically in the frequency range of 2MHz - 25MHz and reaches the highest difference of 40dB at 25MHz. This trend is reflected in the CM noise current spectra shown in Fig. 2.10, where the noise attenuation increases up to 30dB at 25MHz.

Figure 2.10 CM current spectrum with and without ferrite cores on the cable

In the frequency range over 25MHz, noise without ferrite cores is higher than that at lower frequency range since its impedance becomes inductive with positive phase, which provides an ideal path for noise to travel. Instead, the impedance with ferrite cores is capacitive with negative phase, providing barriers for noise to propagate As a result, the attenuation obtained with the ferrite cores is about 30 - 40dB in this frequency range. This significant attenuation confirms the effectiveness of the ferrite cores to attenuate CM noise in the cable.

# 2.2.4 Isolation capacitance measurement

As pointed in Sec. 2.2.3, the isolation capacitance, which is the capacitance between the input and output, of the DC/DC converter, including its amplitude and phase, has a significant contribution on the noise spectrum. The positive phase can increase noise propagation despite of its very high amplitude. Therefore, the actual impedance curve with parasitic inductance is more important than only the capacitance value, which is the only information being received from the manufacturer. The only way to accurately obtain the isolation capacitance is to extract it experimentally, as shown in Fig. 2.11. In this measurement, the pins at the input side are shorted together, as well as the pins at the output side. The impedance is measured between 2 sets of input and output pins.

Figure 2.11 DC/DC converter isolation capacitance measurement

| Manufacturer | Part Number       | Description        | Isolation Capacitance        |

|--------------|-------------------|--------------------|------------------------------|

| TRACO        | TMH 1212D         | 2W 12VIN +/-12VOUT | 80 <i>pF</i>                 |

| CUI          | VASD1-S12-D12-SIP | 1W 12VIN +/-12VOUT | Not mentioned                |

| RECOM        | RD-1212D          | 2W 12VIN +/-12VOUT | 40 <i>pF</i> - 115 <i>pF</i> |

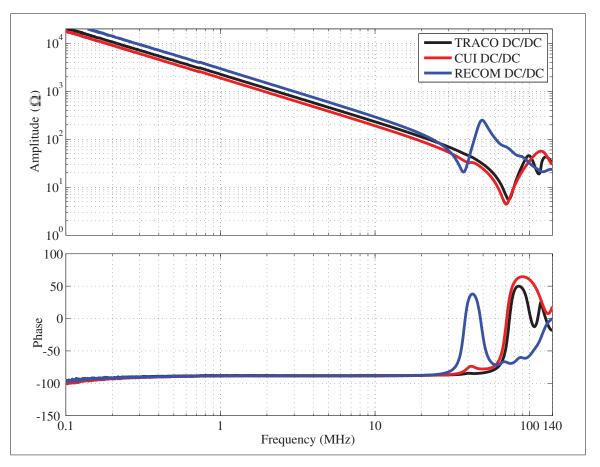

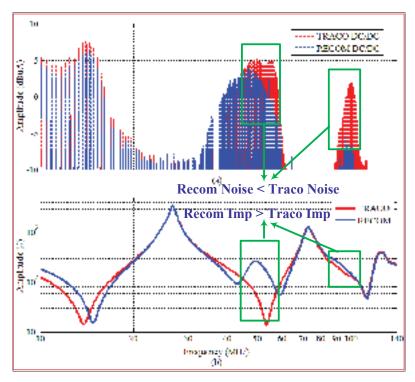

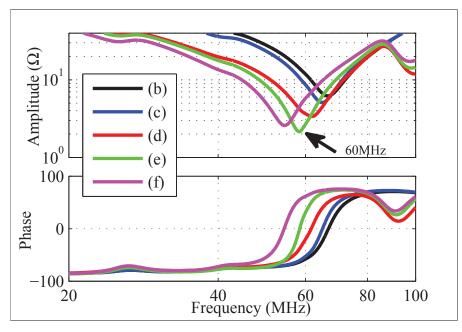

In the experiments, 3 commercial DC/DC converters are used. These devices are summarized in Table 2.1. Their isolation impedances are shown in Fig. 2.12. As can be seen, all isola-

Figure 2.12 DC/DC converter isolation capacitance

tion impedances are very high up to 30MHz. There are two corner frequencies of 35MHz and 50MHz in the RECOM DC/DC impedance with positive phase within this frequency range. The isolation impedance of the TRACO DC/DC and CUI DC/DC are similar with corner frequencies at 70MHz and 75MHz, respectively. From these impedances, one expects different noise spectra between a converter built with RECOM DC/DC and TRACO DC/DC or CUI DC/DC. An experiment to compare these two cases will be presented in Sec. 2.3.2.

## 2.3 Experimental results

In this section, experimental results of noise measurements on the converter introduced in the previous sections are presented. The measurements are taken under different operating conditions of the high power circuit and for different components of the low power circuit. Through the comparisons, one observes the influences of each factor in the noise spectrum. Based on these experimental observations, more details about sub-research topics will be presented in the next chapters of this thesis. Table 2.2 shows the common experimental characteristics used in the following sections. Some variables will be changed for specific measurements for comparison purpose.

Table 2.2 List of experimental characteristics

| DC Power Supply | Load | Switching frequency | Duty Cycle |

|-----------------|------|---------------------|------------|

| 24V             | 5Ω   | 100kHz              | 60%        |

# 2.3.1 Effect of power transistor switching operating on noise spectrum in Low power circuit

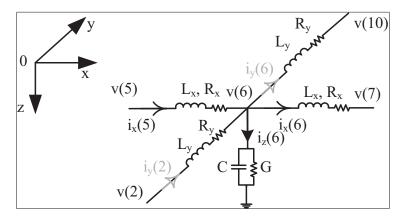

In order to investigate the effect of the high power transistor operation on the low power circuit, the DM and CM current at the input of the DC1 are compared for the following cases. The descriptions are given in Figs. 2.14 and 2.15, showing the spectra of CM and DM noise current at the input of Gate driver DC/DC converter, respectively.