# Diagnostic automatisé en environnement de production à faible volume et haute complexité

par

# Simon PICHETTE

# THÈSE PRÉSENTÉE À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE COMME EXIGENCE PARTIELLE À L'OBTENTION DU DOCTORAT EN GÉNIE Ph. D.

MONTRÉAL, LE 16 SEPTEMBRE 2022

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

©Tous droits réservés, Simon Pichette, 2022

|   | ©Tous droits réservés                                                                                              |

|---|--------------------------------------------------------------------------------------------------------------------|

| ( | Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le pré |

|   | document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante d                   |

| ' | document, doit obligatoirement en demander l'autorisation à l'auteur.                                              |

# PRÉSENTATION DU JURY

# CETTE THÈSE A ÉTÉ ÉVALUÉE PAR UN JURY COMPOSÉ DE :

M. Claude Thibeault, directeur de thèse Département de génie électrique à l'École de technologie supérieure

M. Stéphane Coulombe, président du jury Département de génie logiciel et des TI à l'École de technologie supérieure

M. Pascal Giard, membre du jury Département de génie électrique à l'École de technologie supérieure

Mme. Catherine Laporte, membre du jury Département de génie électrique à l'École de technologie supérieure

M. Pierre Langlois, examinateur externe Département de génie informatique et génie logiciel à Polytechnique Montréal

# ELLE A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC LE 31 AOÛT 2022

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### REMERCIEMENTS

J'aimerais d'abord remercier le professeur Claude Thibeault pour sa patience, sa générosité et sa sagesse. J'ai beaucoup appris à son contact, qui a contribué à faire de moi un meilleur ingénieur et une meilleure personne.

Je souhaite également exprimer ma gratitude envers mes collègues étudiants et chargés de cours, en particulier Vincent, Francis, Stéphane et Louis-Philippe, pour les discussions intéressantes et les encouragements. Merci aussi à ma collègue Christelle pour une importante leçon de persévérance appliquée.

Merci à mes parents, Suzanne et Serge, pour leur amour inconditionnel et pour m'avoir transmis le goût de la découverte et l'amour des sciences et du savoir.

Et finalement, mille mercis à mes filles Roxanne et Marianne, ainsi qu'à ma merveilleuse Manon. Vous êtes magnifiques, la meilleure famille dont un homme puisse rêver.

# Diagnostic automatisé en environnement de production à faible volume et haute complexité

#### Simon PICHETTE

#### RÉSUMÉ

Les impératifs commerciaux ayant déplacé la production de cartes électroniques à grand volume vers l'Asie, les fabricants nord-américains n'ont d'autre choix que de se positionner dans les créneaux plus difficiles de la production à bas volume, de systèmes plus complexes, dits « Low-Volume, High-Mix » (LVHM).

Ces produits souvent destinés aux secteurs industriel, médical ou militaire intègrent des dispositifs dispendieux et leur coût unitaire justifie le déploiement d'un effort de diagnostic et de réparation important lors de la détection d'une défectuosité pendant la production. Bien que l'automatisation du diagnostic soit souhaitable, le faible volume limite la quantité de données disponibles et rend impraticables les techniques d'apprentissage machine conventionnelles.

Cette thèse propose une nouvelle approche basée sur la modélisation des connaissances et le raisonnement par cas pour le diagnostic automatisé de cartes de circuits imprimés adapté à l'environnement de production LVHM. Notre approche hybride, dont l'efficacité a été démontrée à l'aide d'un prototype que nous avons développé, permet de surmonter le goulot d'étranglement de l'acquisition des connaissances (knowledge-acquisition bottleneck) malgré le fait qu'un environnement pauvre en données soit ciblé. L'approche proposée ne nécessite pas la contribution des concepteurs ou d'experts du produit et est conçue pour opérer uniquement avec l'information disponible lors de la fabrication.

Notre approche repose sur l'utilisation d'un système raisonnant accumulant de l'expérience jumelé à un dépôt de connaissances du produit et du domaine. Afin d'accélérer l'acquisition d'expérience sur un nouveau produit, nous procédons à la génération de cas synthétiques à l'aide d'un émulateur de carte au niveau *boundary-scan* branché à l'équipement de test utilisé en production. Les résultats de nos essais démontrent que ces cas synthétiques permettent au système diagnostic de détecter, localiser et classer toutes les pannes simples ainsi que les pannes multiples touchant jusqu'à trois nœuds voisins avec un meilleur taux de succès que l'outil commercial de référence.

De plus, les données de la base de cas, incluant les informations de disposition physique des cartes (board layout) ainsi que les rétroactions de l'utilisateur après chaque réparation sont utilisées pour alimenter un système recommandeur chargé de faire l'analyse des causes racines des défectuosités pour identifier le composant fautif et proposer une réparation. Un simulateur de données de production et de réparation est décrit et intégré au prototype pour faire la vérification du système recommandeur, dont la performance est évaluée. Les résultats obtenus sont prometteurs et permettent d'envisager l'utilisation du système proposé dans un environnement commercial.

**Mots clés** : diagnostique automatisé, émulation matérielle, dictionnaire de pannes, test au niveau carte, modélisation des connaissances, raisonnement par cas, test JTAG.

# Automated Diagnostic in a Low-Volume, High-Mix Production Environment

#### Simon PICHETTE

#### **ABSTRACT**

Commercial pressures having resulted in the transfer of most high-volume printed circuit board assembly operations to Asia, remaining North-American manufacturers have had little choice but to reposition themselves in the more difficult market segment of lower volume, higher complexity products, also called Low-Volume, High-Mix (LVHM).

These products, commonly targeted to the industrial, medical or military sectors, integrate expensive components and their high unit costs justify substantial diagnosis and repair efforts when defects are detected in production. Although automated diagnostics is desirable, the low production volumes impose severe limits on available data and make conventional machine learning techniques impractical.

In this thesis, we propose a novel approach based on knowledge modeling and case-based reasoning for automated diagnosis of printed circuit boards in an LVHM production environment. Our hybrid approach, whose effectiveness we have demonstrated using a prototype we developed, can overcome the knowledge-acquisition bottleneck even though it is targeting a data-poor environment. The proposed approach does not require a contribution from product designer or experts and is designed to operate using information available during manufacturing only.

Our approach is based on using a reasoning system to accumulate experience coupled with a repository of domain and product knowledge. In order to accelerate the acquisition of experience on a new product, we generate synthetic cases using a boundary-scan level board emulator connected to the same test equipment used on the real board in production. Our test results demonstrate that these synthetic cases allow our diagnostic system to detect, locate and classify all single faults and multiple faults affecting up to three neighboring nodes with a better success rate than the reference commercial tool.

Moreover, case base data, including board layout information and user feedback from previous repairs, are used to feed a recommender system tasked with performing root-cause analysis to identify faulty components and suggest repairs. A production and repair data simulator is described and integrated with our prototype system in order to verify functionality of the recommender system and evaluate its effectiveness. Results are promising and allow us to consider using the proposed system in a commercial environment.

**Keywords**: automated diagnostics, hardware emulation, fault dictionary, board-level testing, knowledge modeling, JTAG boundary scan testing.

# TABLE DES MATIÈRES

|      |            |                                                                      | Page |

|------|------------|----------------------------------------------------------------------|------|

| INTR | ODUCTIO    | N                                                                    | 1    |

| CHAI | PITRE 1    | REVUE DE LITTÉRATURE                                                 | C    |

| 1.1  |            | e défaillances des circuits électroniques                            |      |

| 1.2  |            | n du diagnostic                                                      |      |

| 1.3  |            | 'un système de diagnostic automatisé                                 |      |

| 1.4  |            | ticuliers de la production LVHM                                      |      |

| 1.5  |            | iie des principaux systèmes de diagnostic automatisé en électronique |      |

| 1.6  |            | es traditionnelles                                                   |      |

|      | 1.6.1      | Dictionnaire de pannes                                               |      |

|      | 1.6.2      | Arbre de décision                                                    |      |

|      | 1.6.3      | Système à base de règles                                             | 16   |

| 1.7  | Approche   | es basées sur des modèles                                            |      |

|      | 1.7.1      | Modèles de pannes                                                    | 16   |

|      | 1.7.2      | Modèles causals                                                      | 17   |

|      | 1.7.3      | Modèles structuraux et comportementaux                               | 18   |

| 1.8  | Approche   | es utilisant l'apprentissage machine                                 | 19   |

|      | 1.8.1      | Raisonnement par cas                                                 |      |

|      | 1.8.2      | Apprentissage machine par réseaux de neurones artificiels            | 21   |

| 1.9  | . •        | hybrides                                                             |      |

| 1.10 | État de l' | art                                                                  |      |

|      | 1.10.1     | Approches traditionnelles                                            |      |

|      | 1.10.2     | Approches basées sur des modèles                                     |      |

|      | 1.10.3     | Approches utilisant l'apprentissage machines                         |      |

| 1.11 |            | ilité des différentes approches à la production LVHM                 |      |

| 1.12 |            | ement et originalité de la recherche                                 |      |

| 1.13 | Conclusion | on                                                                   | 31   |

| CHAI | PITRE 2    | DIAGNOSTIQUE CENTRÉ SUR LES CONNAISSANCES, AVEC                      | ;    |

|      |            | RAISONNEMENT PAR CAS ET GÉNÉRATION DE CAS                            |      |

|      |            | SYNTHÉTIQUES                                                         | 33   |

| 2.1  | Introduct  | ion                                                                  | 33   |

| 2.2  |            | ation du système                                                     |      |

| 2.3  | Sélection  | des sources de connaissances à modéliser                             | 33   |

| 2.4  | Démarrag   | ge accéléré par la génération de cas synthétiques                    | 34   |

| 2.5  | Architect  | ure du système proposé                                               | 34   |

| 2.6  |            | e concept                                                            |      |

| 2.7  | Cartes d'  | essai                                                                |      |

|      | 2.7.1      | Carte A                                                              |      |

|      | 2.7.2      | Carte B                                                              |      |

| 2.8  | Conclusio  | on                                                                   | 41   |

| CHAPITRE 3 |          | ÉMULATION DE CIRCUIT AU NIVEAU JTAG POUR LA                 |     |

|------------|----------|-------------------------------------------------------------|-----|

|            |          | GÉNÉRATION AUTOMATIQUE D'UN DICTIONNAIRE                    |     |

|            |          | DE PANNES AVEC L'ÉQUIPEMENT DE TEST RÉEL                    | 43  |

| 3.1        | Introduc | tion                                                        | 43  |

| 3.2        | Chaîne d | le balayage et JTAG                                         | 43  |

| 3.3        | Système  | s commerciaux                                               | 45  |

|            | 3.3.1    | Génération d'une suite de test avec l'outil commercial      | 46  |

| 3.4        | Modélisa | ation de carte de circuit imprimé au niveau JTAG            | 46  |

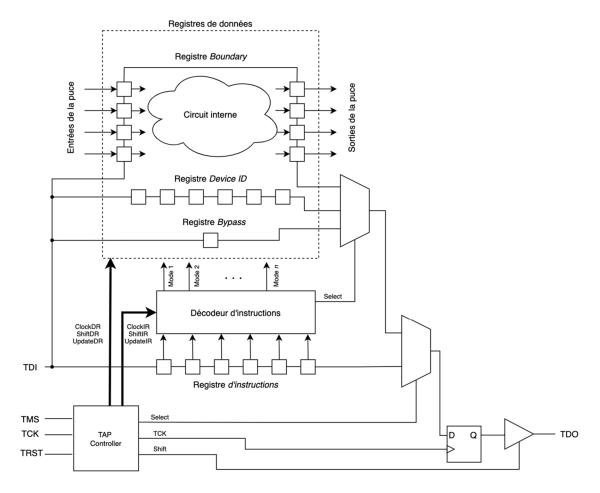

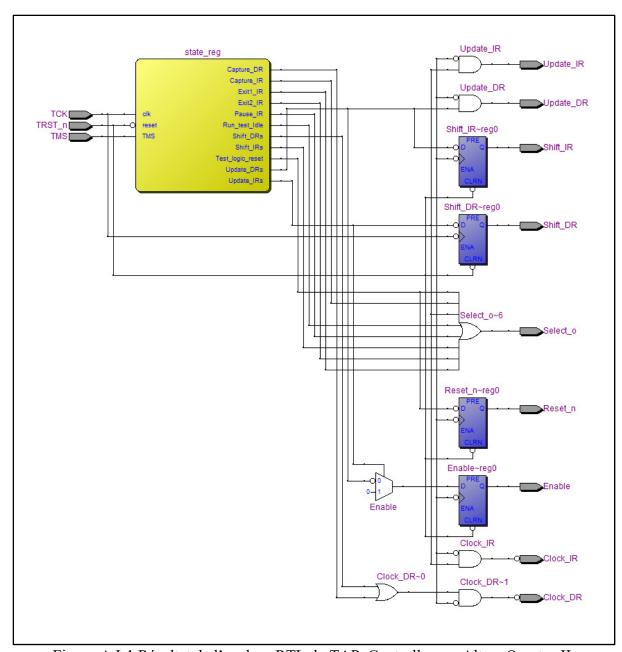

|            | 3.4.1    | TAP Controller et instructions JTAG                         | 47  |

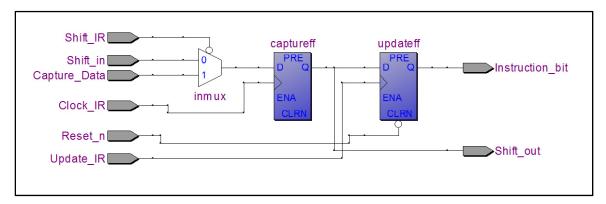

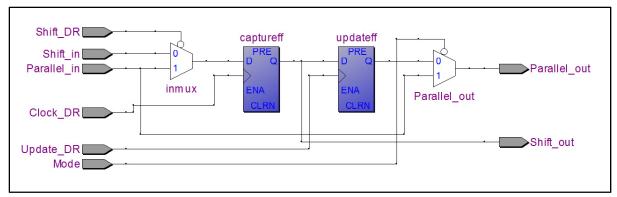

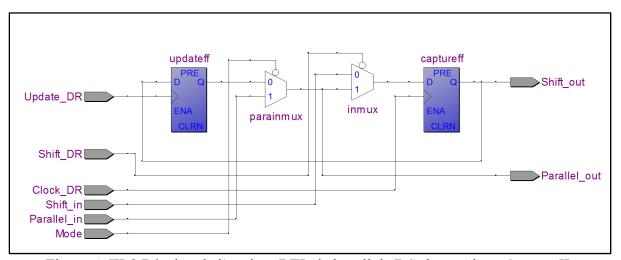

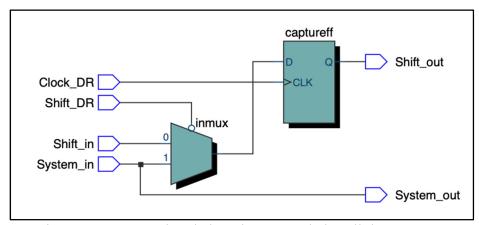

|            | 3.4.2    | Structure des cellules et registres JTAG                    | 49  |

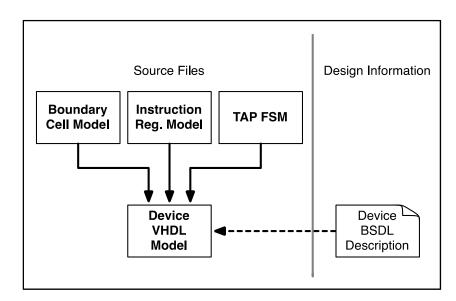

|            | 3.4.3    | Description BSDL des circuits intégrés                      | 50  |

|            | 3.4.4    | Génération de modèles VHDL à partir du BSDL                 | 51  |

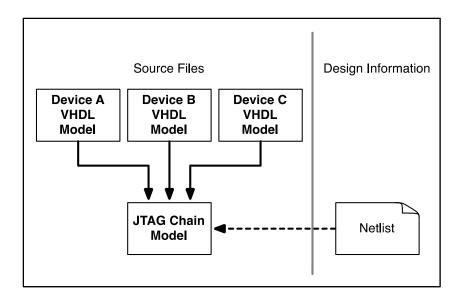

|            | 3.4.5    | Modélisation de la chaîne JTAG                              |     |

|            | 3.4.6    | Vérification du modèle de la chaîne JTAG                    | 54  |

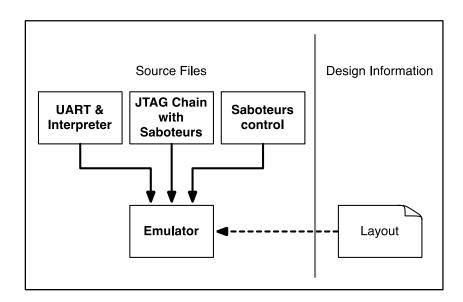

| 3.5        | Émulatio | on de pannes                                                | 55  |

|            | 3.5.1    | Scénarios de panne                                          | 58  |

|            | 3.5.2    | Saboteurs                                                   | 58  |

|            | 3.5.3    | Contrôle des saboteurs                                      | 61  |

| 3.6        | Générati | on automatique d'un dictionnaire de pannes                  | 63  |

|            | 3.6.1    | Automatisation de l'outil de test commercial                |     |

| 3.7        | Conclusi | ion                                                         | 65  |

|            |          |                                                             |     |

| CHAP       | PITRE 4  | REPRÉSENTATION DES CONNAISSANCES POUR LE                    |     |

|            |          | DOMAINE DU DIAGNOSTIC EN ÉLECTRONIQUE                       |     |

|            | _        | NUMÉRIQUE                                                   |     |

| 4.1        |          | tion                                                        |     |

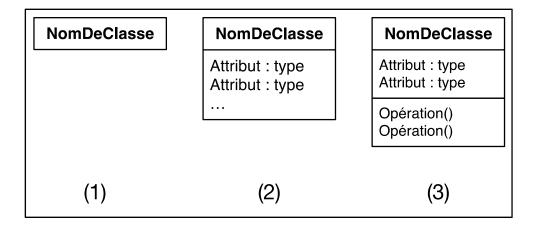

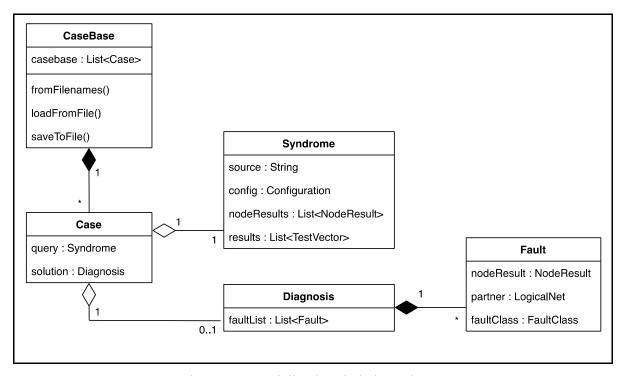

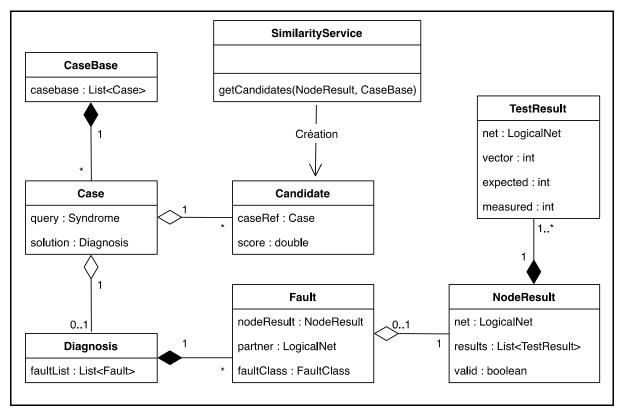

| 4.2        | _        | imes de classe UML                                          |     |

|            | 4.2.1    | Classes                                                     |     |

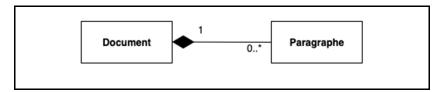

|            | 4.2.2    | Relations                                                   |     |

|            | 4.2.3    | Cardinalité                                                 |     |

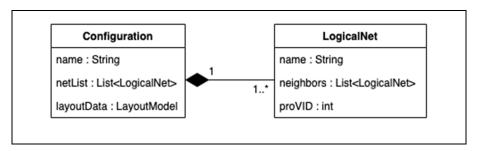

| 4.3        |          | ntation logique du réseau                                   |     |

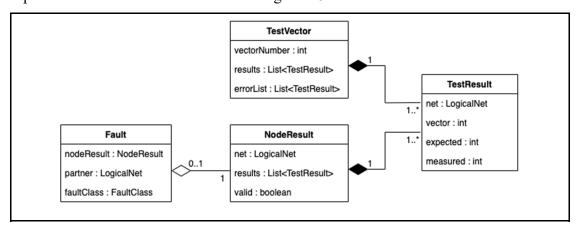

| 4.4        | -        | ntation des mesures et des défectuosités                    |     |

| 4.5        | _        | on des données de fabrication assistée par ordinateur (FAO) |     |

|            | 4.5.1    | Extended Gerber (Ucamco NV, 2021)                           |     |

|            | 4.5.2    | ODB++ (Siemens, 2021)                                       |     |

|            | 4.5.3    | Sélection d'un format et intégration                        |     |

|            | 4.5.4    | Reconstruction des chemins                                  |     |

|            | 4.5.5    | Visualisation et validation du LayoutModel                  |     |

| 4.6        | -        | le détection et localisation des pannes                     |     |

| 4.7        |          | ation des nœuds voisins et partenaires                      |     |

| 4.8        | Conclusi | ion                                                         | 86  |

| CILAR      | NTDE C   | DIA CNOCTIC A LITOMATICÉ DAD LA MÉTUODE DU                  |     |

| CHAP       | PITRE 5  | DIAGNOSTIC AUTOMATISÉ PAR LA MÉTHODE DU                     | 0.5 |

| <i>E</i> 1 | T 1      | RAISONNEMENT PAR CAS                                        |     |

| 5.1        | Introduc | tion                                                        | 87  |

| 5.2  | Raisonne    | ement par cas                                                                 | 88  |

|------|-------------|-------------------------------------------------------------------------------|-----|

|      | 5.2.1       | Modèle humain                                                                 |     |

|      | 5.2.2       | Modèle machine                                                                | 88  |

| 5.3  | Représen    | tation des cas                                                                | 89  |

| 5.4  | Classes d   | le défectuosités                                                              | 90  |

|      | 5.4.1       | Défectuosités multiples                                                       | 91  |

| 5.5  | Notion de   | e similarité                                                                  |     |

|      | 5.5.1       | Similarité et distance                                                        | 93  |

|      | 5.5.2       | Choix des critères d'évaluation                                               | 94  |

|      | 5.5.3       | Attribution des poids relatifs                                                | 98  |

| 5.6  | Rappel d    | e cas                                                                         |     |

|      | 5.6.1       | Rappel séquentiel et méthode des k plus proches voisins                       | 101 |

| 5.7  | Réutilisa   | tion, révision et rétention                                                   |     |

| 5.8  |             | entation                                                                      |     |

| 5.9  | Résultats   |                                                                               | 104 |

|      | 5.9.1       | Applicabilité de l'apprentissage obtenu sur un produit vers un autre          | 105 |

|      | 5.9.2       | Taux de succès avec $k > 1$                                                   |     |

| 5.10 | Utilisatio  | on de cas synthétiques pour l'accélération du démarrage                       | 109 |

| 5.11 |             | ison avec l'outil commercial                                                  |     |

| 5.12 | Conclusi    | on                                                                            | 116 |

| CHA  | PITRE 6     | SYSTÈME RECOMMANDEUR POUR L'ANTICIPATION DES CAUSES PHYSIQUES DE DÉFECTUOSITÉ |     |

| 6.1  |             | ion                                                                           |     |

| 6.2  | Rétroacti   | on et identification des causes physiques                                     |     |

|      | 6.2.1       | Causes physiques de défaillance                                               | 118 |

| 6.3  | Intégration | on des données de production et de réparation                                 | 120 |

| 6.4  | Anticipat   | tion des causes physiques lors du diagnostic                                  | 121 |

|      | 6.4.1       | Systèmes recommandeurs                                                        |     |

|      | 6.4.2       | Raisonnement par cas et fonction de similarité                                |     |

|      | 6.4.3       | Application 1 : Suggestion de causes physiques lors du diagnostic             |     |

|      | 6.4.4       | Application 2 : Détection de bris sur une ligne de production                 | 123 |

| 6.5  |             | ur de cas                                                                     | _   |

|      | 6.5.1       | Défectuosités aléatoires vs systématiques                                     |     |

|      | 6.5.2       | Modélisation des particularités d'un produit                                  |     |

|      | 6.5.3       | Modélisation des particularités d'une ligne de production                     |     |

|      | 6.5.4       | Phénomène d'apparition en grappe des défectuosités                            |     |

|      | 6.5.5       | Fonctionnement du simulateur                                                  |     |

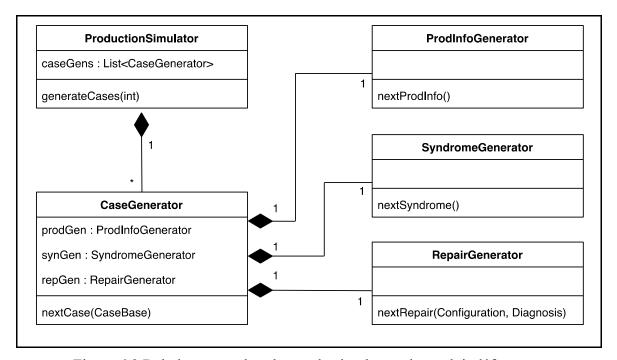

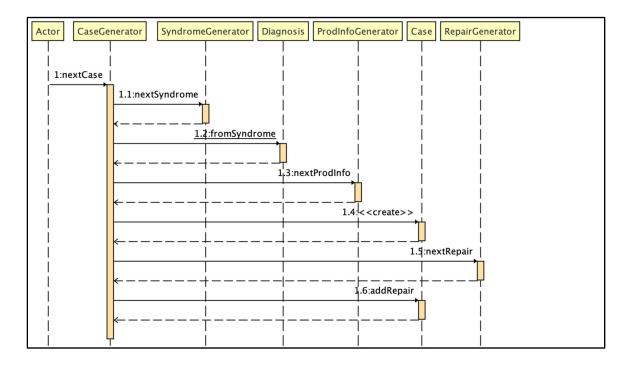

|      | 6.5.6       | Architecture logicielle                                                       |     |

|      | 6.5.7       | Fichiers de configuration                                                     |     |

| 6.6  | -           | entation                                                                      |     |

| 6.7  | Résultats   |                                                                               |     |

|      | 6.7.1       | Conditions de test                                                            |     |

|      | 6.7.2       | K = 1 et 0% de probabilité d'apparition en grappe                             |     |

|      | 6.7.3       | K = 1 et 20% de probabilité d'apparition en grappe                            | 136 |

|       | 6.7.4      | K = 1 et 20% de probabilité d'apparition en grappe suivie d'un bris | . 138 |

|-------|------------|---------------------------------------------------------------------|-------|

|       | 6.7.5      | K = 2 et 0% de probabilité d'apparition en grappe                   | . 140 |

|       | 6.7.6      | K = 2 et 20% de probabilité d'apparition en grappe                  |       |

|       | 6.7.7      | K = 2 et 20% de probabilité d'apparition en grappe suivie d'un bris | . 143 |

| 6.8   | Conclusion | 1                                                                   |       |

| CONC  | CLUSION    |                                                                     | 145   |

| RECC  | MMANDA     | TIONS                                                               | 149   |

| ANNI  | EXE I      | IMPLÉMENTATION DU TAP CONTROLLER                                    | 151   |

| ANNI  | EXE II     | REGISTRE D'INSTRUCTION JTAG                                         | 157   |

| ANNI  | EXE III    | BOUNDARY REGISTER JTAG                                              | 159   |

| ANNI  | EXE IV     | OUTILS POUR LA TRANSFORMATION BSDL-VHDL                             | 165   |

| ANNI  | EXE V      | TRANSFORMATION BSDL VERS VHDL                                       | 167   |

| ANNI  | EXE VI     | VÉRIFICATION DU SIMULATEUR                                          | 175   |

| LISTE | E DE RÉFÉI | RENCES BIBLIOGRAPHIQUES                                             | 183   |

# LISTE DES TABLEAUX

| P | a | g | $\epsilon$ |

|---|---|---|------------|

| 1 | а | ~ | L          |

| Tableau 1.1 | Couverture des sous-problèmes du diagnostic automatisé dans la littérature |

|-------------|----------------------------------------------------------------------------|

| Tableau 1.2 | Couverture des quatre tâches d'un système diagnostic dans la littérature   |

| Tableau 2.1 | Composants de la preuve de concept                                         |

| Tableau 2.2 | Principaux dispositifs présents sur la carte B                             |

| Tableau 3.1 | Registres JTAG45                                                           |

| Tableau 3.2 | Broches dédiées à la chaîne de balayage                                    |

| Tableau 3.3 | Scripts utilisés pour la génération de modèles VHDL53                      |

| Tableau 3.4 | Exemples de configuration des saboteurs60                                  |

| Tableau 4.1 | Sous-ensemble des relations du diagramme de classes UML69                  |

| Tableau 4.2 | Classes de défectuosités associées à un NodeResult72                       |

| Tableau 4.3 | Règles d'identification des nœuds partenaires86                            |

| Tableau 5.1 | Classes de défectuosités91                                                 |

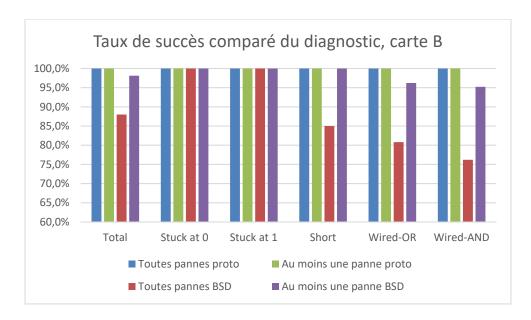

| Tableau 5.2 | Résultats pour des défectuosités touchant trois nœuds voisins, carte B     |

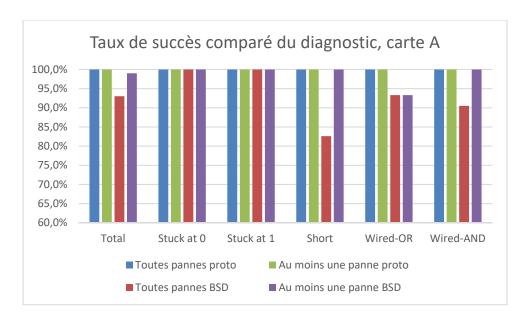

| Tableau 5.3 | Résultats comparatifs entre le prototype et BSD, carte A                   |

| Tableau 5.4 | Résultats comparatifs entre le prototype et BSD, carte B                   |

| Tableau 6.1 | Catégories de défectuosités les plus courantes et leur prévalence118       |

| Tableau 6.2 | Classes de causes physiques utilisées par le prototype119                  |

| Tableau 6.3 | Applicabilité des causes physiques aux classes de défectuosités120         |

| Tableau 6.4 | Distribution de base des causes physiques par classe de défectuosité       |

| Tableau 6.5 | Particularité des lignes de production et des produits pour la |     |

|-------------|----------------------------------------------------------------|-----|

|             | simulation                                                     | 133 |

# LISTE DES FIGURES

Page

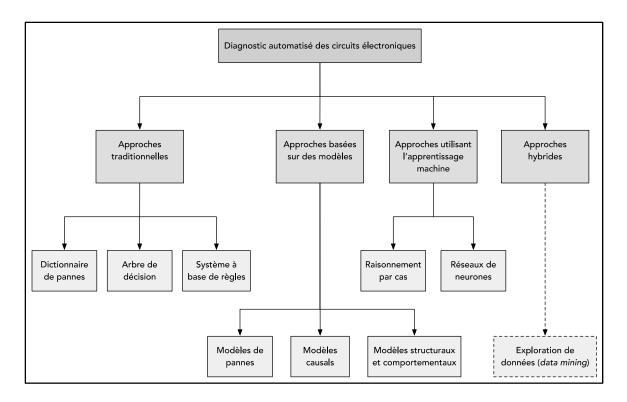

| Figure 1.1  | Taxonomie des méthodes de diagnostic automatisé                                                     | 4  |

|-------------|-----------------------------------------------------------------------------------------------------|----|

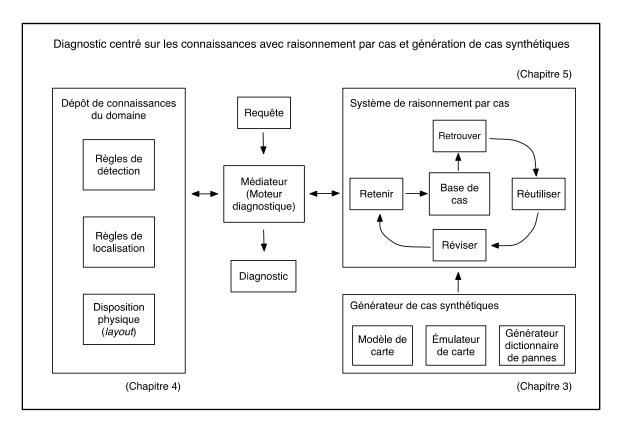

| Figure 2.1  | Schéma bloc du système de diagnostic automatisé                                                     | 5  |

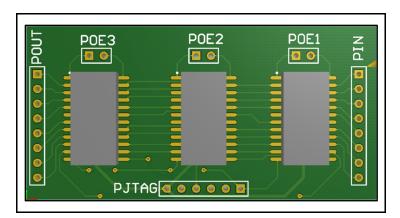

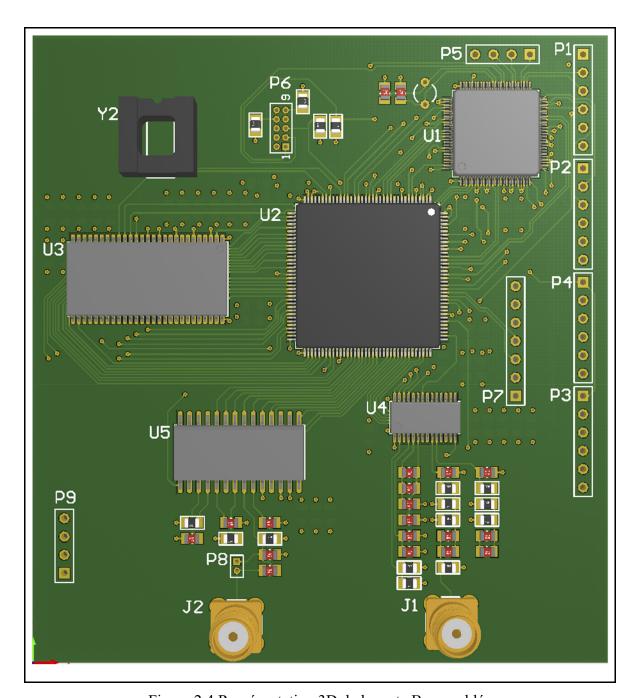

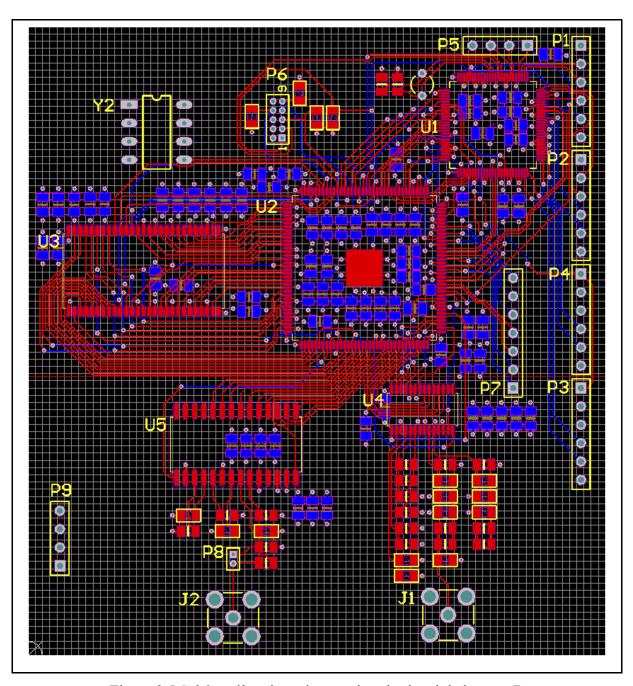

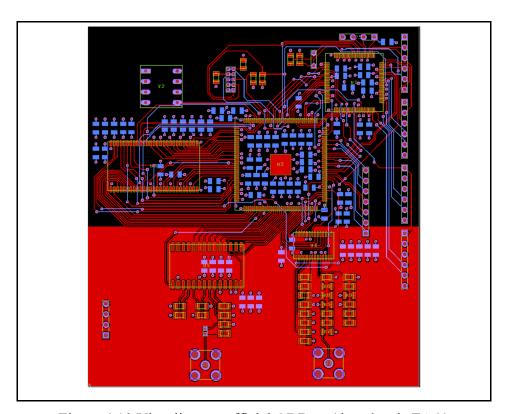

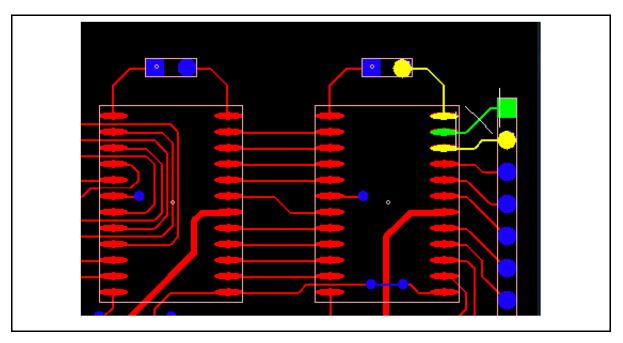

| Figure 2.2  | Représentation 3D de la carte A assemblée                                                           | 7  |

| Figure 2.3  | Schéma électrique des couches de signal de la carte A                                               | 7  |

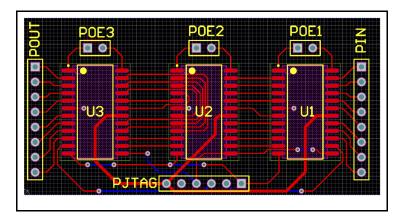

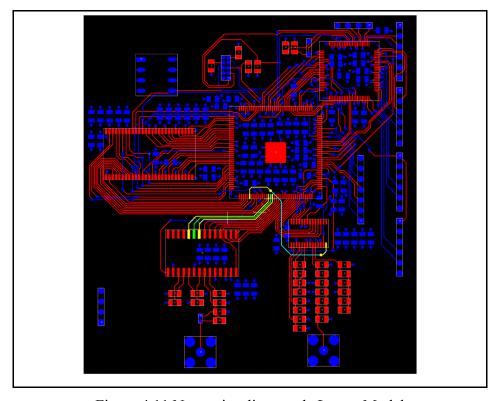

| Figure 2.4  | Représentation 3D de la carte B assemblée                                                           | 9  |

| Figure 2.5  | Schéma électrique des couches de signal de la carte B                                               | 0  |

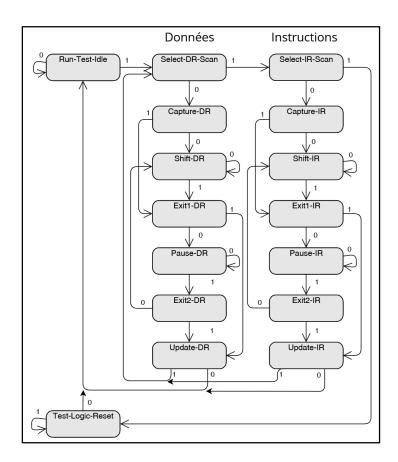

| Figure 3.1  | Transitions d'états de la MEF du <i>TAP Controller</i>                                              | 8  |

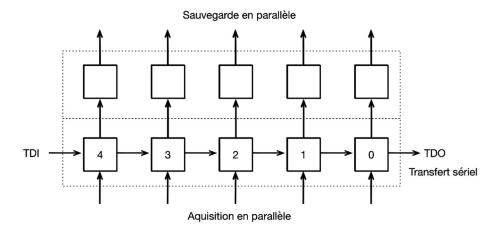

| Figure 3.2  | Structure générale des registres JTAG5                                                              | 0  |

| Figure 3.3  | Architecture générale d'une implémentation JTAG5                                                    | 52 |

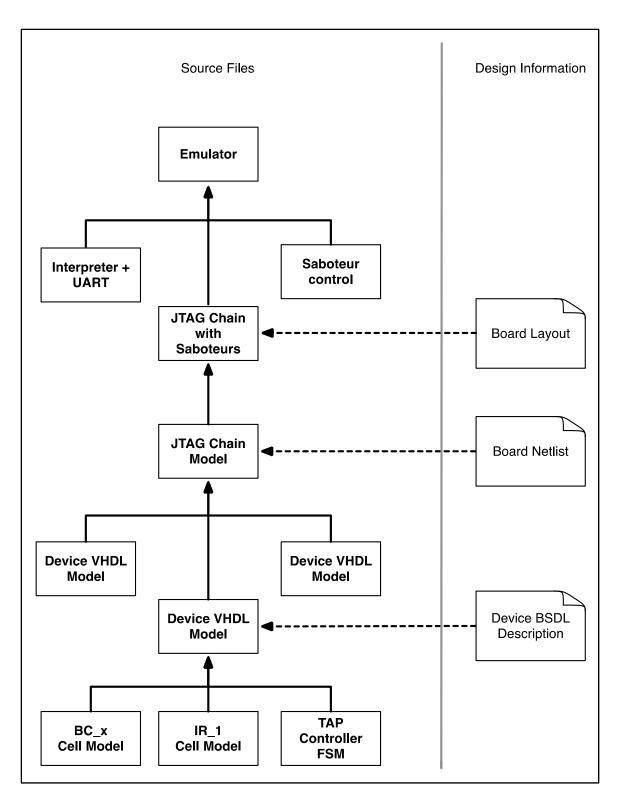

| Figure 3.4  | Entités VHDL et source d'information nécessaires à l'élaboration du modèle VHDL d'une puce          | ;3 |

| Figure 3.5  | Entités VHDL et source d'information nécessaires à l'élaboration du modèle VHDL d'une carte         | 54 |

| Figure 3.6  | Entités VHDL et source d'information nécessaires à l'élaboration de l'émulateur                     | 6  |

| Figure 3.7  | Entités VHDL et sources d'informations nécessaires à l'élaboration du système d'émulation de pannes | ;7 |

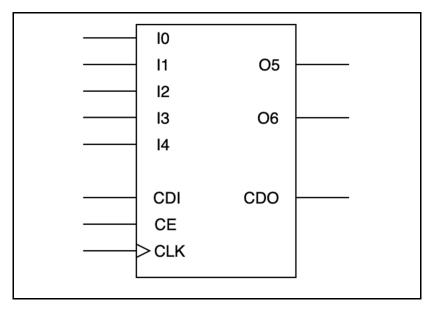

| Figure 3.8  | Interface de la cellule reprogrammable CFGLUT55                                                     | ;9 |

| Figure 3.9  | Patrons de configuration des CFGLUT56                                                               | 51 |

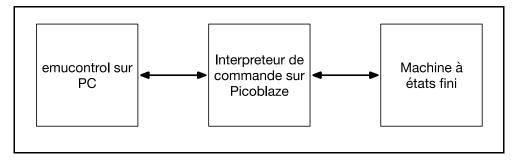

| Figure 3.10 | Architecture du système de contrôle des saboteurs6                                                  | 52 |

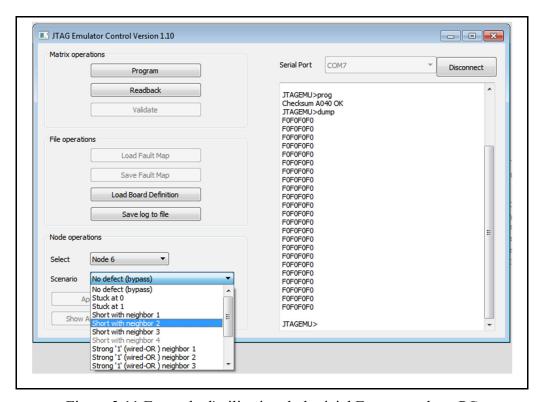

| Figure 3.11 | Exemple d'utilisation du logiciel Emucontrol sur PC6                                                | 52 |

| Figure 4.1  | Trois niveaux de représentation des classes6                                                        | 8  |

| Figure 4.2  | Exemple de relation avec cardinalité                                                                | 59 |

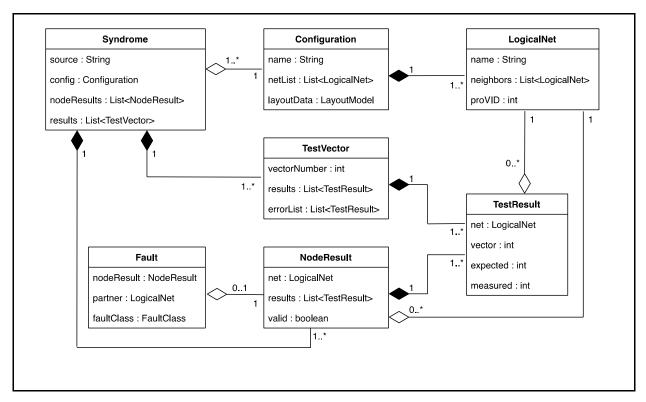

| Figure 4.3  | Représentation logique du réseau                                               | 70  |  |  |

|-------------|--------------------------------------------------------------------------------|-----|--|--|

| Figure 4.4  | Sortie de ProVision utilisée pour générer un Syndrome                          |     |  |  |

| Figure 4.5  | Représentation des résultats de test en deux collections                       |     |  |  |

| Figure 4.6  | Modélisation complète d'une séance d'essais sur une carte au niveau logique    |     |  |  |

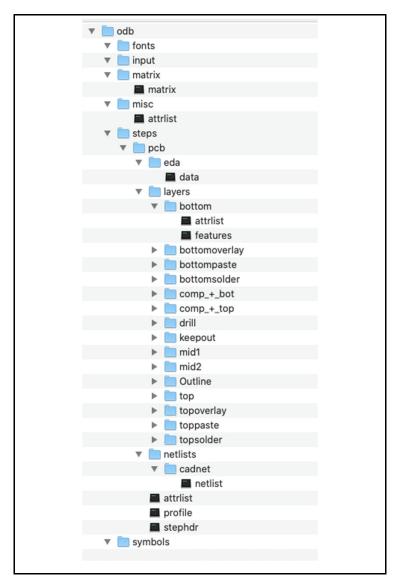

| Figure 4.7  | Hiérarchie ODB++ pour une carte 4 couches                                      | 76  |  |  |

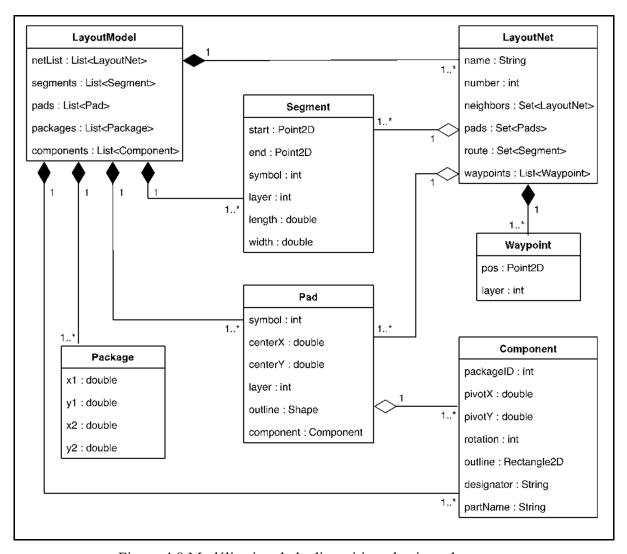

| Figure 4.8  | Modélisation de la disposition physique des cartes                             | 78  |  |  |

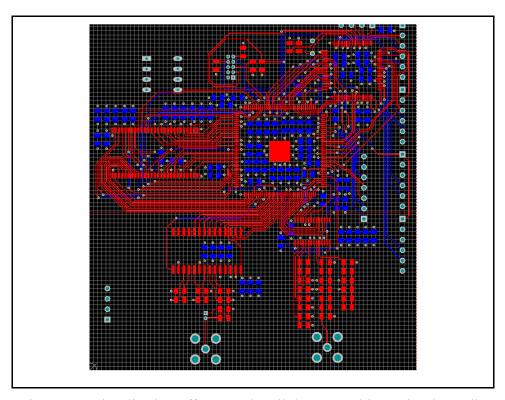

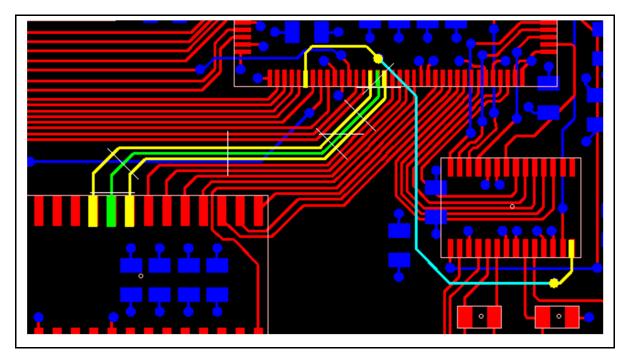

| Figure 4.9  | Visualisation offerte par l'outil de CAO Altium Circuit Studio                 | 80  |  |  |

| Figure 4.10 | Visualisateur officiel ODB++ (données de FAO)                                  | 81  |  |  |

| Figure 4.11 | Notre visualisateur de LayoutModel                                             | 81  |  |  |

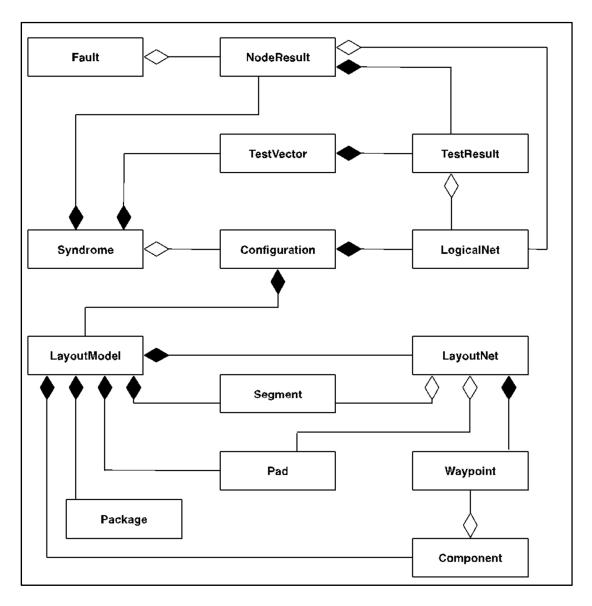

| Figure 4.12 | Modèle du domaine                                                              | 82  |  |  |

| Figure 4.13 | Visualisation de la détection des voisins                                      | 84  |  |  |

| Figure 4.14 | Nœuds voisins par adjacence des pastilles                                      | 84  |  |  |

| Figure 5.1  | Étapes du raisonnement par cas                                                 | 89  |  |  |

| Figure 5.2  | Modélisation de la base de cas                                                 | 90  |  |  |

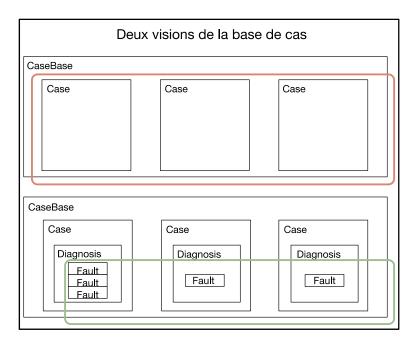

| Figure 5.3  | Visualisations de la base de cas                                               | 92  |  |  |

| Figure 5.4  | Exemple de sortie de ProVision utilisée pour générer un Syndrome               | 94  |  |  |

| Figure 5.5  | Exemple de Syndrome montrant un pont dominé par les zéros                      | 95  |  |  |

| Figure 5.6  | Représentation des cas d'une base selon leur distance                          | 97  |  |  |

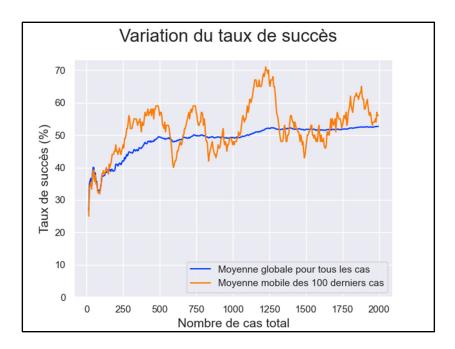

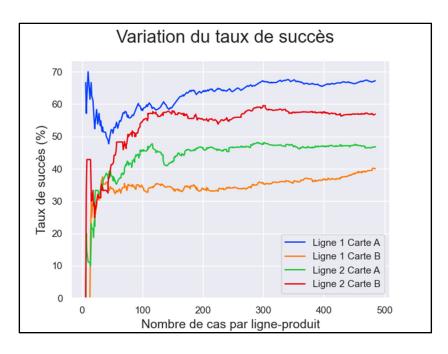

| Figure 5.7  | Variation du taux de succès en fonction du poids relatif des critères, carte A | 99  |  |  |

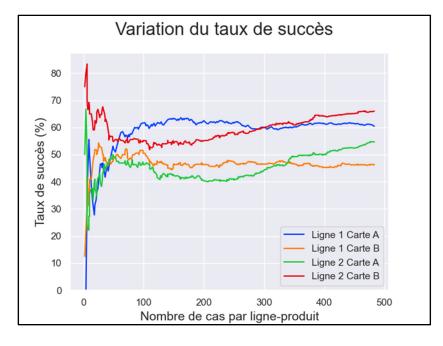

| Figure 5.8  | Variation du taux de succès en fonction du poids relatif des critères, carte B | 99  |  |  |

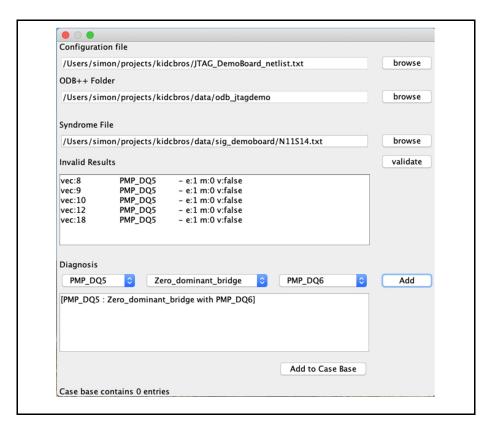

| Figure 5.9  | Classes impliqués dans le rappel de cas                                        | 100 |  |  |

| Figure 5.10 | Interface utilisateur du module de saisie manuelle des cas                     | 102 |  |  |

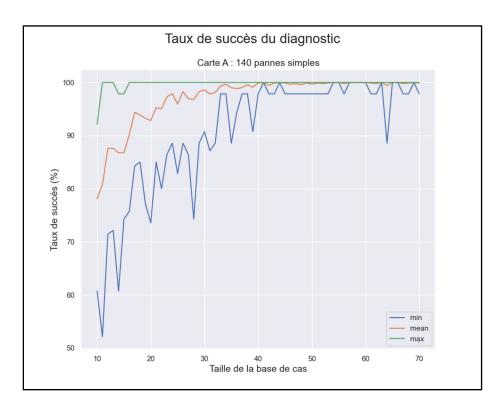

| Figure 5.11 | Taux de succès minimum, maximum et moyen du diagnostic selon la taille de la base de cas, carte A                                                                                  |     |  |

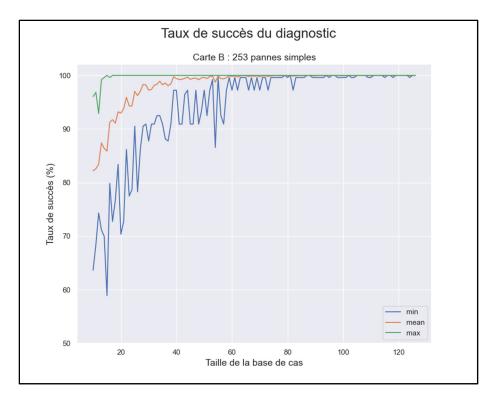

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

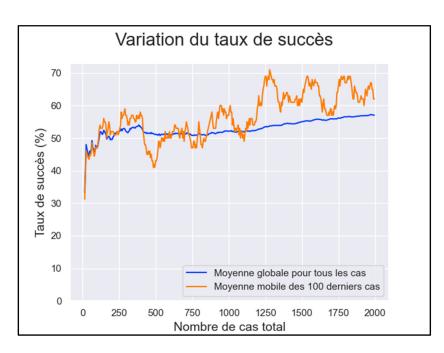

| Figure 5.12 | Taux de succès minimum, maximum et moyen du diagnostic selon la taille de la base de cas, carte B                                                                                  |     |  |

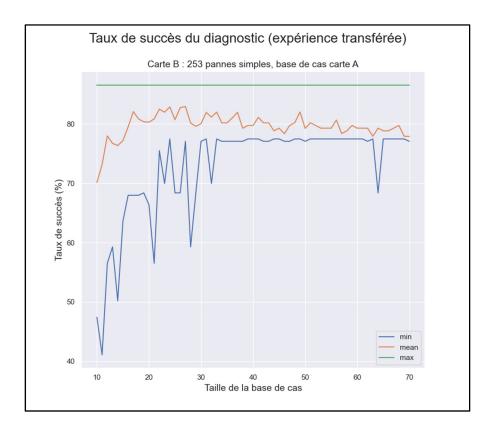

| Figure 5.13 | Taux de succès minimum, maximum et moyen du diagnostic selon la taille de la base de cas, carte B, avec expérience sur la carte A uniquement                                       | 106 |  |

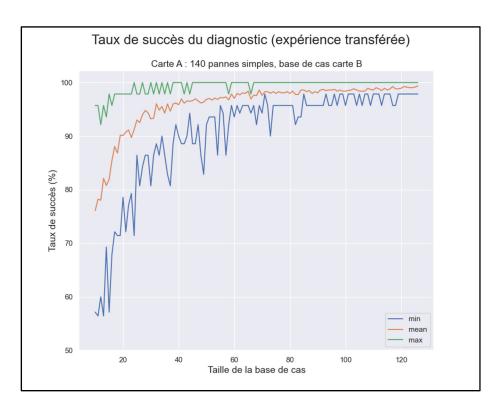

| Figure 5.14 | Taux de succès minimum, maximum et moyen du diagnostic selon la taille de la base de cas, carte A, avec expérience sur la carte B uniquement                                       | 107 |  |

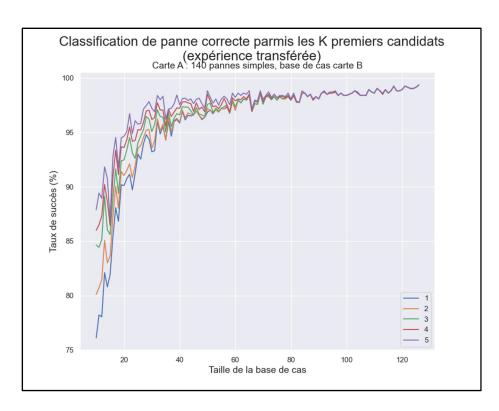

| Figure 5.15 | Présence du diagnostic correct parmi les $k$ plus proches voisins selon la taille de la base de cas, carte A, avec expérience sur la carte B uniquement, pour $k$ variant de 1 à 5 | 108 |  |

| Figure 5.16 | Taux de succès du diagnostic pour syndrome comportant une défectuosité touchant trois nœuds voisins, carte B                                                                       | 110 |  |

| Figure 5.17 | Taux de succès comparés du prototype et de BSD pour des défectuosités touchant 3 nœuds voisins, carte A                                                                            | 113 |  |

| Figure 5.18 | Taux de succès comparés du prototype et de BSD pour des défectuosités touchant 3 nœuds voisins, carte B                                                                            | 114 |  |

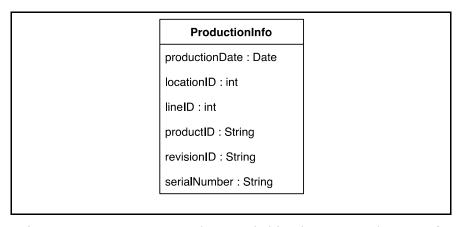

| Figure 6.1  | Données encapsulées par l'objet de type ProductionInfo                                                                                                                             | 120 |  |

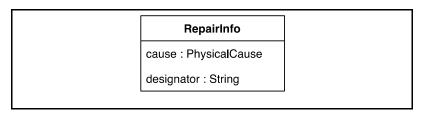

| Figure 6.2  | Données encapsulées par l'objet de type RepairInfo                                                                                                                                 | 121 |  |

| Figure 6.3  | Relations entre les classes du simulateur de produit défectueux                                                                                                                    | 128 |  |

| Figure 6.4  | Séquence d'appels nécessaires à la création d'un objet Case complet                                                                                                                | 130 |  |

| Figure 6.5  | Exemple de fichier de configuration pour une combinaison ligne-produit                                                                                                             | 131 |  |

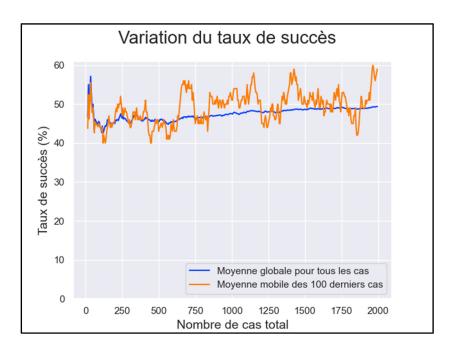

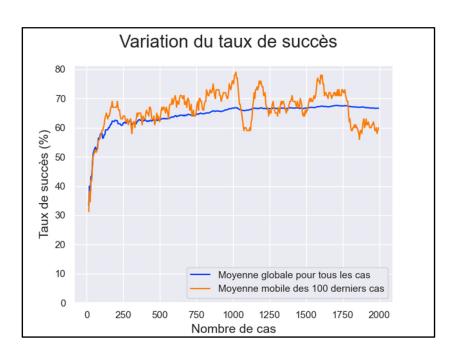

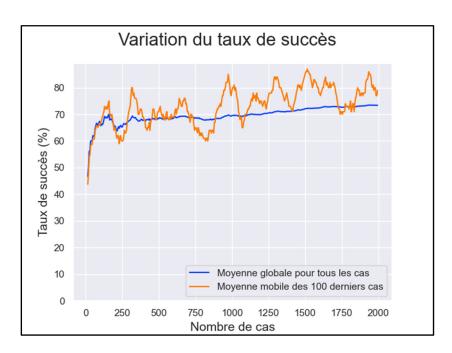

| Figure 6.6  | Taux de succès avec $K = 1$ sans apparition en grappe                                                                                                                              | 134 |  |

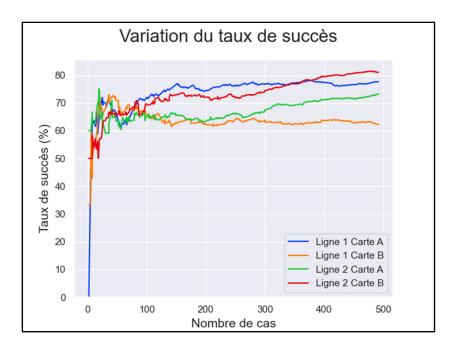

| Figure 6.7  | Taux de succès par ligne-produit avec $K = 1$ sans apparition en grappe                                                                                                            | 135 |  |

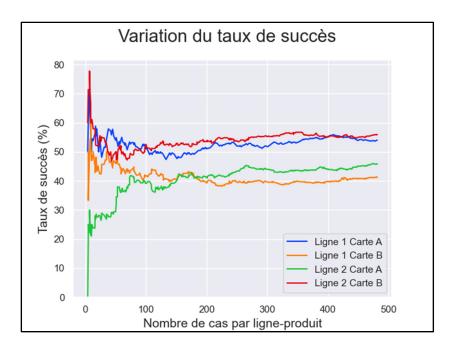

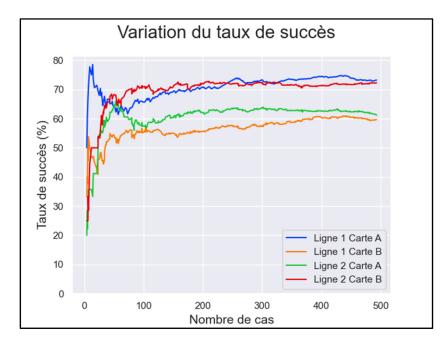

| Figure 6.8  | Taux de succès avec K = 1 et 20% de probabilité d'apparition en grappe                                                                                                             | 136 |  |

| Figure 6.9  | Taux de succès par ligne-produit avec K = 1 et 20% de probabilité d'apparition en grappe                          | 137 |

|-------------|-------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.10 | Taux de succès avec K = 1, 20% de probabilité d'apparition en grappe et apparition d'un bris                      | 138 |

| Figure 6.11 | Taux de succès par ligne-produit avec $K = 1$ , 20% de probabilité d'apparition en grappe et apparition d'un bris | 138 |

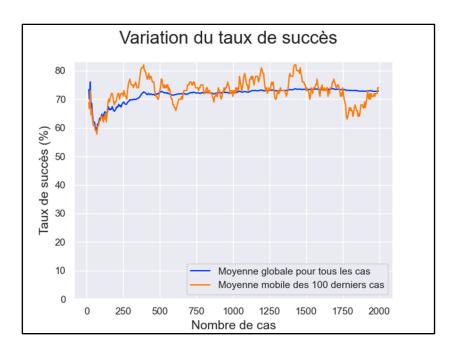

| Figure 6.12 | Taux de succès avec K = 2 sans apparition en grappe                                                               | 140 |

| Figure 6.13 | Taux de succès par ligne-produit avec K = 2 sans apparition en grappe                                             | 140 |

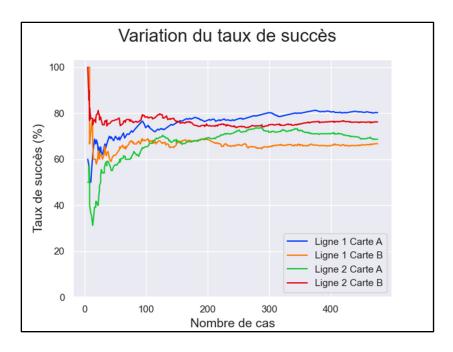

| Figure 6.14 | Taux de succès avec K = 2 et 20% de probabilité d'apparition en grappe                                            | 141 |

| Figure 6.15 | Taux de succès par ligne-produit avec K = 2 et 20% de probabilité d'apparition en grappe                          | 142 |

| Figure 6.16 | Taux de succès avec K = 2, 20% de probabilité d'apparition en grappe et apparition d'un bris                      | 143 |

| Figure 6.17 | Taux de succès par ligne-produit avec K = 2, 20% de probabilité d'apparition en grappe et apparition d'un bris    | 143 |

#### INTRODUCTION

Dans le contexte actuel de mondialisation, les équipementiers (« Original Equipment Manufacturer », OEM) confient de plus en plus la fabrication et le test de leurs produits à des sous-traitants appelés EMS (« Electronic Manufacturing Service »). Les EMS asiatiques, bénéficiant d'avantages majeurs au niveau des coûts de main-d'œuvre ainsi que de la réglementation environnementale et industrielle, sont spécialisés dans la production à haut volume et à bas prix. Les EMS nord-américains, qui détiennent toujours environ 17% du marché mondial, n'ont d'autre choix que de se positionner dans les créneaux plus difficiles de la production à bas volume, de systèmes plus complexes, dits «Low Volume, High Mix» (LVHM) (Sprovieri, 2004). En production LVHM, un grand nombre de produits différents est fabriqué sur les mêmes lignes de production, en quantités variant de quelque centaines à quelque milliers d'unités par produit par an. Une différence importante entre ce mode d'opération et la fabrication en grande série réside dans le fait qu'il soit nécessaire de reconfigurer rapidement et fréquemment l'équipement de production. La nécessité de fabriquer de nombreux produits en quantités restreintes sur de l'équipement partagé touche aussi le domaine des semiconducteurs. Les défis de prédiction du rendement et de la qualité (Okusa et al., 2020) ainsi que d'ordonnancement de la production (Boydon et al., 2021) s'appliquent également au domaine de l'assemblage des carte.

La différence de coût de la main-d'œuvre, même hautement qualifiée, dans les pays asiatiques par rapport à l'Amérique du Nord ou à l'Europe, peut atteindre un facteur de dix (Tourangeau, 2006). Cette grande disparité force les EMS nord-américains à utiliser de l'équipement de pointe, plus automatisé, afin de réduire leur besoin de main-d'œuvre au minimum. La taille réduite, le niveau technologique et l'expertise des EMS nord-américains leur confèrent également l'avantage en début et en fin de vie des produits à plus grands volumes. Pour exploiter ces avantages et renforcer leur modèle d'affaires, les EMS nord-américains doivent offrir des services à valeur ajoutée, afin de convaincre leurs clients de se départir d'une partie de leurs activités non stratégiques, par exemple au niveau de la validation et du développement des tests de nouveaux produits.

# Contexte et environnement du projet

Ce projet constitue une continuation d'un projet démarré originalement en partenariat avec la société Varitron Technologies, un EMS dont le siège social est situé à St-Hubert en Montérégie et qui se spécialise dans l'assemblage de produits électroniques à faible volume et haute complexité. Le projet hôte consistait à développer une infrastructure de test et de diagnostic définie par logiciel. Cette infrastructure était perçue comme un élément important de la stratégie de Varitron Technologies visant à offrir des services à valeur ajoutée permettant de mieux accompagner leurs clients, en particulier au début du cycle de vie des produits, incluant la phase de déverminage.

Minimiser la phase de déverminage d'un produit signifie, dans un premier temps, de concevoir un produit qui a de meilleures chances d'être manufacturé avec succès, et, dans un deuxième temps, d'identifier et de corriger rapidement les problèmes causant des pertes de rendement. Ces problèmes peuvent provenir des composants à assembler sur les plaquettes de circuits imprimés ou de l'assemblage lui-même. Lorsque ces problèmes sont liés au procédé d'assemblage, leur identification peut permettre une correction des règles de conception des circuits imprimés afin d'en améliorer ultérieurement la « manufacturabilité ».

Au centre de l'infrastructure envisagée, on retrouvait une station générique de test et de diagnostic qui permettrait d'offrir une interface unifiée pour l'opérateur, combinant toutes les fonctions de test et de diagnostic en un seul outil, et dont l'interface serait commune pour tous les produits fabriqués. Notre contribution au projet original devait être le développement d'un système de diagnostic automatisé adapté à l'environnement de production à faible volume et haute complexité.

Suite à des changements à la tête de l'entreprise, Varitron Technologies a pris la décision à l'été 2016 de ne pas participer à la suite du projet. Puisque nous avions déjà identifié quelques avenues prometteuses, nous avons décidé de continuer le développement sans partenaire industriel, avec la contrainte supplémentaire qu'il nous serait désormais impossible d'accéder aux données ou à l'environnement de production.

# **Problématique**

L'identification de la cause de la défaillance d'un produit est un exercice laborieux qui demande un grand niveau d'expertise et une connaissance approfondie du produit. Chez Varitron Technologies, comme c'est le cas pour la majorité des EMS, cet exercice demande l'implication de techniciens et d'ingénieurs, qui peuvent prendre plusieurs heures voire même parfois des jours avant de mettre le doigt sur la cause du problème. Dans le cas des EMS responsables de l'assemblage, la première impérative est de vérifier si la cause du mauvais fonctionnement n'est pas le procédé d'assemblage lui-même. Pour ce faire, le responsable du procédé d'assemblage (c.-à-d. le directeur de production) doit disposer d'informations très complètes sur son procédé de fabrication, des résultats de tests structuraux et fonctionnels ainsi que des résultats du diagnostic des produits défaillants, indiquant la cause probable des défectuosités. Idéalement, le directeur de production devrait pouvoir accéder à cette information en temps réel, afin de suivre l'évolution de son procédé et d'apporter les modifications nécessaires le plus rapidement possible, minimisant ainsi le nombre de produits défectueux fabriqués.

Malheureusement, les méthodes de diagnostic automatisé existantes nécessitent soit une très grande quantité de données de production et de défaillance, soit une contribution majeure de la part d'un expert du produit pour l'élaboration du système. Une telle contribution n'est pas envisageable pour la production en sous-traitance, à faible volume. Ce genre de production souffre également de la faible quantité de données et de produits défectueux. Ces deux contraintes, le manque de données et la nécessité de recourir au travail d'experts, ne sont pas uniques au domaine de la production à faible volume et haute complexité en électronique, mais constituent en fait l'un des problèmes universels du diagnostic automatisé connu sous le nom de goulot d'étranglement de l'acquisition des connaissances (GEAC), ou « knowledge acquisition bottleneck » en anglais (Buchanan et Wilkins, 1993).

# Objectifs de la recherche

Ce projet vise le développement et la mise en œuvre de stratégies permettant la diminution du temps de déverminage et l'amélioration du rendement dans un environnement de production LVHM par une identification plus rapide des causes de défaillances.

L'objectif principal repose sur la disponibilité d'un système de diagnostic automatisé qui soit adapté aux contraintes particulières de la production sur une même chaîne de montage de plusieurs produits différents à volume faible ou moyen. Puisqu'il ne pourra reposer ni sur un grand volume de données de production et de défaillance ni sur la contribution d'experts de chaque produit, le système devra nécessairement proposer une solution au problème plus général du GEAC. Le développement d'un tel système constitue l'un des objectifs secondaires de la recherche.

En l'absence d'accès aux données et à l'environnement de production commercial, la validation du système de diagnostic devra être effectuée par simulation. Un simulateur de données de production et de défaillances avancé, capable de modéliser les caractéristiques propres à un produit ou à une ligne de production devra être conçu et réalisé, ce qui constitue un autre objectif secondaire de ce projet.

#### Contributions de la thèse

Les principales contributions de cette thèse sont les suivantes :

- Une méthode de diagnostic automatisé destinée à un environnement pauvre en donnée et capable de surmonter le GEAC en combinant l'émulation matérielle, la modélisation des connaissances et le raisonnement par cas. Cette méthode comprend :

- La génération automatique d'un dictionnaire de pannes par émulation matérielle de circuits imprimés au niveau JTAG connecté à l'équipement de test utilisé en production.

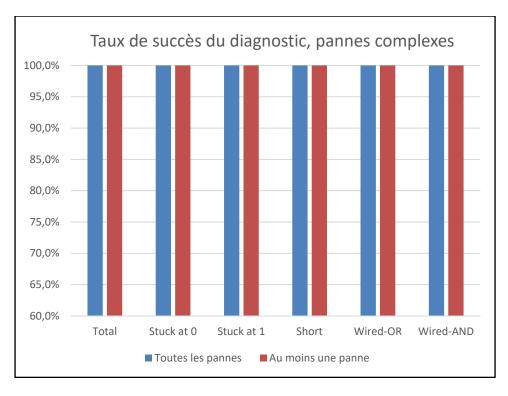

- O Un système de diagnostic automatisé capable de détecter, localiser et classifier 100% des pannes de types « stuck-at », court-circuit ou pont directionnel

- impliquant jusqu'à trois nœuds voisins observables avec l'équipement de test JTAG.

- Un système recommandeur permettant la suggestion de causes physiques probables lors du diagnostic et la détection de défaillance sur l'équipement de production.

- Un simulateur de données de production et de défaillances capable de modéliser les particularités d'un produit et d'une ligne de production.

Les contributions proposées dans cette thèse constituent de fait un système de diagnostic automatisé complet prenant en charge la détection, la localisation, la classification et la recherche des causes racines des défectuosités présentes sur les cartes de circuits imprimés. Le système décrit dans cette thèse a également fait l'objet d'un article de revue (Pichette & Thibeault, 2022).

# Organisation de la thèse

Le chapitre 1 présente les bases théoriques du problème du diagnostic ainsi qu'une revue des différentes méthodes de diagnostic automatisé ainsi que de leurs forces et leurs faiblesses respectives. Les résultats de recherche récents sont présentés et classés selon les méthodes auxquels ils se rattachent. L'applicabilité des différentes méthodes au contexte particulier de la production à faible volume et haute complexité est évaluée et les contributions de la thèse sont positionnées par rapport à l'état de l'art.

Le chapitre 2 montre une vue d'ensemble de la méthode que nous proposons, qui est basée sur une approche hybride. Il présente également l'architecture globale du système de diagnostic automatisé que nous avons réalisé pour démontrer la validité de la méthode. Les cartes de circuits imprimés de démonstration, conçues pour ce projet, sont également introduites. La description détaillée des différents sous-systèmes constitue l'objet des chapitres suivants.

Le chapitre 3 présente l'émulateur de cartes de circuit imprimé au niveau JTAG sur dispositif programmable FPGA utilisé pour la génération automatique de dictionnaires de pannes. Il

introduit les notions de base du test par balayage des frontières et de la norme IEEE 1149.1 avant de présenter notre implémentation des éléments de base requis par la norme. L'émulateur est ensuite présenté en suivant une approche ascendante. L'assemblage des composants de base pour la reproduction du fonctionnement de la chaîne JTAG des puces est montré en premier, suivi de l'assemblage de ces puces pour former un modèle de la carte entière. Les types de défectuosités pouvant être émulées, les saboteurs et leur dispositif de contrôle et de reprogrammation sont introduits puis nous amènent à une vue d'ensemble de l'émulateur complet et de son logiciel de contrôle. Finalement, l'utilisation de l'émulateur couplé à l'équipement de test commercial et à sa suite logicielle pour la génération automatique d'un dictionnaire de pannes est montrée.

Le chapitre 4 est consacré à la représentation des connaissances dans notre système hybride. Il introduit d'abord certains éléments du formalisme des diagrammes de classe UML utilisés dans ce chapitre et les suivants. Il montre ensuite les éléments de la représentation logique du modèle de carte, suivis d'une représentation des mesures et des défectuosités. La section suivante introduit la façon dont nous avons intégré les données de fabrication assistée par ordinateur (FAO) pour reconstruire les chemins électriques et élaborer un modèle de la disposition physique des composants sur les cartes, normalement invisible au niveau JTAG.

Le chapitre 5 présente d'abord la technique du raisonnement par cas puis son utilisation dans notre système de diagnostic automatisé. La représentation des cas et les classes de défectuosités sont introduites puis les notions de similarité et de distance entre les cas sont présentées, suivies du choix des critères de sélection et de l'attribution des poids relatifs. Une expérimentation visant à démontrer la capacité du système à détecter, localiser et classifier les défectuosités, en s'améliorant avec l'expérience par apprentissage machine, est présentée. Un autre volet expérimental montre la transférabilité de l'apprentissage effectué sur un produit vers un autre produit. Finalement, l'utilisation de cas synthétiques générés à partir du dictionnaire de panne élaboré au chapitre 3 pour accélérer de façon importante la phase d'apprentissage est présentée puis les performances du système sont comparées à celles d'un outil de diagnostic JTAG commercial.

Le chapitre 6 montre la conception et l'utilisation d'un second système de raisonnement par cas exploitant les mêmes données de façon cette fois à formuler des recommandations plutôt que comme classificateur. Ce sous-système est responsable de la recherche des causes racines des défectuosités. Ce chapitre présente d'abord les classes de causes physiques de défaillance, ainsi que les taux d'occurrence relatifs trouvés dans la littérature. Le tout est suivi par la présentation de deux applications envisagées pour ce système, soient la suggestion de causes physiques au technicien lors du diagnostic et la détection de bris sur une ligne de production par la surveillance des courbes de taux de succès de la recommandation. Afin de valider le fonctionnement du système en l'absence de données de production réelles, nous avons conçu un simulateur de cas capable de modéliser les particularités d'un produit et d'une ligne de production. Ce simulateur est présenté et décrit en détail avant d'être utilisé pour mesurer la performance du système recommandeur pour les deux applications.

Le dernier chapitre présente les conclusions de la thèse ainsi qu'une discussion des travaux futurs envisagés.

#### **CHAPITRE 1**

#### REVUE DE LITTÉRATURE

Le problème de la vérification, du test et du diagnostic des circuits électroniques assemblés est inhérent au domaine et existe depuis aussi longtemps que l'industrie. Chaque avancée technologique permettant une augmentation de la complexité des circuits doit être accompagnée d'avancées technologiques ou méthodologiques complémentaires au niveau de la vérification, du test et du diagnostic afin de maintenir le rendement élevé et le coût unitaire faible.

Dans ce chapitre, nous proposons un survol des notions de base du domaine ainsi qu'une taxonomie des différentes approches de diagnostic automatisé proposées et utilisées dans les quatre dernières décennies. Nous présenterons également les résultats de recherches récentes touchant à chacune des approches. Finalement, nous décrirons comment notre projet se positionne parmi ces recherches récentes.

#### 1.1 Causes de défaillances des circuits électroniques

Selon (Lirov, 1989), il est possible de regrouper les causes de défaillance en trois grandes catégories : (1) les dispositifs défectueux, (2) les défectuosités d'assemblage (ex. ponts de soudure, dispositif manquant, défaut d'alignement, etc.) et (3) les problèmes opérationnels, par exemple des dispositifs en apparence fonctionnels qui entraînent des problèmes de délais, lorsque combinés. En accord avec cette catégorisation, une stratégie de test en trois phases est généralement appliquée dans l'industrie. Les cartes assemblées sont donc inspectées (visuellement ou aux rayons X), testées électriquement puis au niveau fonctionnel.

L'augmentation de la complexité et de la densité des circuits provoque une augmentation parallèle de la difficulté du test. L'intégration de méthodologies de conception en vue du test (design for test) est devenue nécessaire et a entraîné à son tour l'émergence de technologies novatrices comme le test par chaîne de balayage et de standards industriels comme la norme

IEEE1149.1 JTAG. L'intégration de la chaîne de balayage dans les dispositifs (puces) et sur les cartes permet de réduire la surface occupée par les éléments nécessaires au test sur les cartes (Parker, 2016).

# 1.2 Définition du diagnostic

Toujours selon (Lirov, 1989), le diagnostic des circuits électroniques est un processus qui permet de déterminer les causes de comportement erroné (en sortie) du circuit pour une certaine combinaison (valide) de valeurs d'entrées.

Plus formellement, soit un circuit P=P(S,B), modélisé par sa structure S et son comportement B. La structure S=S(C,T) est définie par l'ensemble C des composants et la topologie T sur l'ensemble C. Le comportement B=B(IO,R) est défini par deux modèles mathématiques: (1) le modèle IO décrivant les relations entrée-sortie de chacun des composants  $c \in C$  et (2) le modèle R décrivant la fiabilité de chaque composant  $c \in C$ .

Un composant  $c \in C$  est dit **défaillant** si son comportement observé  $b_o$  est différent de  $b_e$ , le comportement attendu selon le modèle IO ( $b_e \in IO$ ).

#### Problème du diagnostic

Soit un circuit à composants multiples P et un syndrome indiquant une anomalie par rapport au comportement IO attendu. Le problème du diagnostic se résume à identifier le sous-ensemble  $C_f \in C$  des composants défaillants.

Puisque l'opération d'identification du problème ci-dessus est elle-même un problème complexe, (Lirov, 1989) identifie six sous-problèmes que doivent surmonter tous les systèmes de diagnostic automatisé :

# 1. Génération d'hypothèse

À partir d'un syndrome et des résultats des tests ou mesures déjà effectués, obtenir une estimation du sous-ensemble défaillant  $C_f$ .

#### 2. Planification

À partir d'une estimation de  $C_f$ , obtenir la séquence de mesures ou tests supplémentaires de coût minimal permettant d'affirmer ou d'infirmer l'hypothèse. Puisque le problème de la génération d'une séquence idéale est NP-complet (Ibarra et Sahni, 1976) (Hyafil et Rivest, 1976), de nombreuses approches par heuristique ou inférence ont été et continuent d'être proposées (Amati, 2009) (Bolchini, 2013, 2014).

#### 3. Raisonnement

Trouver une méthode efficace de raisonner à propos des circuits électroniques. Ce sousproblème implique la manipulation de structures de données qui représentent à la fois les informations structurelles et comportementales et le raisonnement sur ces deux axes.

#### 4. Représentation

Trouver une façon efficace de représenter le circuit P=P(S,B). L'efficacité est ici déterminée par la complétude, la régularité, la transparence et la calculabilité (Winston, 1984).

#### 5. Acquisition et modélisation des connaissances

Trouver une méthode efficace pour acquérir et emmagasiner les connaissances d'experts du domaine à propos du diagnostic des circuits électroniques. Aussi appelée ingénierie des connaissances (*knowledge engineering*).

#### 6. Interface utilisateur

Trouver une façon efficace de conduire un dialogue fructueux entre le système et l'opérateur.

La définition de Lirov décrit le problème du diagnostic de façon abstraite, du point de vue du chercheur. On retrouve aussi dans la littérature une description centrée sur les tâches à accomplir par un système de diagnostic automatisé, telles que perçues par l'utilisateur.

# 1.3 Tâches d'un système de diagnostic automatisé

Selon (Fenton et al, 2001), du point de vue de l'utilisateur, les systèmes de diagnostic automatisés utilisés en contexte industriel sont chargés de 3 tâches :

- 1. Détecter les défaillances,

- 2. Localiser les défaillances,

- 3. Faire la classification des défaillances.

Les systèmes de pointe, tels que décrits dans (Ye et al., 2015) doivent de plus faire l'analyse des causes racines pour :

4. Proposer des suggestions de réparation à l'utilisateur.

La réalisation de ces tâches étant un des objectifs de ce projet, il est important de considérer les facteurs propres à l'environnement de production visé avant l'évaluation des méthodes et approches proposées dans la littérature.

#### 1.4 Défis particuliers de la production LVHM

Les caractéristiques particulières de la production à faible volume et haute complexité entraînent les conséquences suivantes au niveau du diagnostic :

- La complexité des produits rend leur diagnostic plus difficile et coûteux.

- Le petit nombre d'unités défaillantes augmente la difficulté pour les techniciens et ingénieurs assignés au diagnostic, car ils ne peuvent accumuler beaucoup d'expérience avec un produit.

- Le faible volume réduit aussi considérablement la génération de données à propos des produits et du procédé de fabrication. De fait, c'est un environnement qui sera considéré comme pauvre en données (*data poor*).

- Le recours fréquent à la sous-traitance a comme conséquence que les données de CAO

ne sont pas toujours disponibles pour l'assembleur. Seul un ensemble plus restreint,

appelé données de « fabrication assistée par ordinateur » (FAO) est généralement

disponible.

# 1.5 Taxonomie des principaux systèmes de diagnostic automatisé en électronique

Il existe de nombreuses méthodes de diagnostic automatisé. Afin de pouvoir les comparer, nous présentons brièvement dans cette section les plus importantes d'entre elles et nous identifions leurs forces et leurs faiblesses, en tenant compte des particularités de notre environnement.

Il est possible de regrouper ces méthodes en trois catégories ou générations (Fenton et al. 2001, 2002). On retrouve d'abord les approches traditionnelles, qui n'utilisent ni modélisation ni apprentissage machine, ensuite les approches basées sur des modèles et finalement les approches utilisant l'apprentissage machine. La taxonomie proposée ici est également inspirée de celle proposée par (Binu et Kariyappa, 2017) pour le diagnostic des circuits analogiques. La figure 1.1 illustre la taxonomie retenue. Les trois prochaines sections décrivent plus en détail chacune de ces trois approches. Notons que ces différentes approches ne sont pas mutuellement exclusives et que par conséquent, des approches hybrides sont possibles. Cet aspect sera également abordé à la section 1.9.

Figure 1.1 Taxonomie des méthodes de diagnostic automatisé

#### 1.6 Approches traditionnelles

Ces approches incluent l'utilisation de dictionnaire de pannes, les arbres de décision informatisés et les systèmes à base de règles. Notons que ces approches sont apparues dès le début de la recherche sur l'intelligence artificielle dans les années 1960, et sont considérées comme des approches traditionnelles pour le diagnostic automatisé (Fenton et al. 2001).

#### 1.6.1 Dictionnaire de pannes

Le dictionnaire de pannes est un dépôt de connaissances où sont associés les comportements défaillants du système ainsi que les causes anticipées de ces derniers. Les comportements sont généralement représentés par des échantillons de sorties erronées. Lors de l'utilisation, il suffit théoriquement de retrouver le comportement correspondant dans le dictionnaire pour en obtenir la cause. Les dictionnaires de pannes sont traditionnellement générés par simulation des comportements fautifs les plus probables ou fréquents.

#### **Forces**

- Utilisation très simple et rapide.

- Génération relativement simple.

- Requiert peu d'expertise du produit pour la génération.

#### **Faiblesses**

- Croissance très rapide du dictionnaire pour les systèmes complexes.

- Généralement incomplets puisqu'il est difficile d'anticiper tous les comportements erronés possibles.

- Souvent ambigus, des comportements similaires pouvant avoir des causes différentes.

#### 1.6.2 Arbre de décision

L'arbre de décision est une méthode traditionnelle et très répandue de documentation des procédures de diagnostic, antérieure à l'informatique. Les symptômes en constituent la racine, et un embranchement d'actions, de résultats et de décisions guide l'utilisateur jusqu'à une recommandation.

#### **Forces**

- Utilisation intuitive.

- Modèle traditionnel utilisé dans les manuels de réparation.

- Permet à l'utilisateur non-spécialiste d'arriver à un diagnostic rapidement.

# **Faiblesses**

- Croissance très rapide de l'arbre dans le cas des systèmes complexes.

- Fortement lié au système et tout changement à ce dernier, même mineur, peut entraîner la nécessité de modifications importantes de l'arbre.

- Difficulté d'acquisition des connaissances nécessaires à la construction de l'arbre; c'est le GEAC, qui affecte à différents degrés toutes les méthodes de diagnostic automatisé.

# 1.6.3 Système à base de règles

Les systèmes à base de règles tentent de représenter les connaissances d'un diagnosticien expérimenté sous une forme propositionnelle : SI symptôme(s), ALORS défaillance(s).

Un grand nombre de règles, de quelques centaines à plusieurs milliers, sont nécessaires pour représenter adéquatement le domaine d'application. La plupart des systèmes de diagnostic automatisé développés dans les années 1970 et 1980 étaient de ce type (Rowland et Jain, 1993). Plusieurs sont toujours utilisés aujourd'hui, dans les réseaux téléphoniques, les disques durs, les ordinateurs et les systèmes de contrôle d'avionique. Les systèmes experts, très populaires dans les années 1980 et 1990, sont des systèmes à base de règles.

#### **Forces**

Simplicité.

#### **Faiblesses**

- Très fortement affecté par le GEAC.

- Incapacité à traiter une panne imprévue.

- Dépendant du système. Un nouvel ensemble de règles doit être généré pour tout nouveau type de système.

#### 1.7 Approches basées sur des modèles

À partir du milieu des années 1980, les approches reposant sur la modélisation sont venues remplacer graduellement les approches traditionnelles dans la littérature et dans l'industrie. Nous les avons regroupés selon la nature de la modélisation.

#### 1.7.1 Modèles de pannes

Très utilisée dans le domaine des circuits numériques, et très bien adaptée aux circuits de types combinatoires, la modélisation de panne consiste à effectuer un ensemble de simulations, dans

lesquelles chacun des types de pannes (par exemple, les courts-circuits, les bits « collés » ou les délais excessifs) est inséré tour à tour dans chacun des composants du système.

Chaque simulation produit une description de l'opération du système en présence d'une panne donnée. Les résultats de simulations sont analysés afin de fournir une liste de doublets pannes/symptômes qui serviront de base à la construction d'un dictionnaire de pannes. Le dictionnaire est à son tour utilisé lors du diagnostic pour identifier le composant fautif selon les symptômes rencontrés (Simpson, 1996). Ceci constitue un exemple d'approche hybride.

#### Forces

• Modélise avec précision les pannes rencontrées dans les circuits combinatoires.

#### **Faiblesses**

- Incapable de traiter une panne imprévue (non simulée).

- Plus difficiles à utiliser dans le cas des circuits séquentiels. La division du circuit en portions plus petites, appelée encapsulation, est une solution possible (Simpson, 1996).

- Une très grande quantité de vecteurs de test peut être nécessaire pour les circuits de grande taille, ce qui allonge de façon excessive la durée des tests. La compression de donnée peut être appliquée comme méthode de mitigation (Chess, 1999).

#### 1.7.2 Modèles causals

Le modèle causal est un graphe orienté où les nœuds représentent les variables du système modélisé et les arcs représentent les relations ou les associations entre les variables. Dans le cas d'un modèle utilisé pour le diagnostic, les nœuds correspondent aux symptômes et aux pannes et les arcs représentent les associations symptôme-panne. Le poids relatif ou une probabilité est associé par un expert du domaine à chacun des arcs.

#### **Forces**

- Représentation plus compacte des connaissances structurées que l'ensemble de règles menant à des avantages au niveau du temps de calcul.

- Basé sur la théorie mathématique des probabilités.

## **Faiblesses**

• Une grande expertise du domaine d'application est nécessaire pour construire le modèle, c'est à nouveau le GEAC.

## 1.7.3 Modèles structuraux et comportementaux

Pour ces modèles, une double représentation de la structure et du comportement du système à l'étude est utilisée. La représentation structurelle est une liste de tous les composants ainsi que de leurs interconnexions. Le modèle comportemental de son côté décrit le fonctionnement correct de chacun des composants.

### **Forces**

- Utilisation de modèles corrects permettant théoriquement le diagnostic de toutes les pannes possibles.

- Les données des outils de conception assistée par ordinateur (CAO) peuvent être utilisées pour la génération automatique des modèles.

#### **Faiblesses**

- Une grande puissance de calcul est nécessaire dans le cas des systèmes complexes.

L'utilisation conjuguée de modèles de pannes peut améliorer l'efficacité.

- La représentation comportementale de composants complexes comme les microprocesseurs avancés et les systèmes sur puces (*System-on-a-Chip*, SoC) est très difficile.

- Si l'autogénération à partir des données de CAO n'est pas possible, le développement des modèles peut s'avérer excessivement long.

Ne considère pas les défauts physiques. Par exemple un pont de soudure entre deux composants ne sera pas représenté par le modèle structurel.

## 1.8 Approches utilisant l'apprentissage machine

Les approches conventionnelles ont toutes en commun d'offrir un niveau de performance constant selon l'implémentation. Le succès ou l'échec du diagnostic n'influence pas l'utilisation future.

Les approches utilisant l'apprentissage machine profitent des expériences passées pour informer le système et améliorer ses performances futures. Nous présentons d'abord ici l'approche du raisonnement par cas, qui reproduit le processus naturel de résolution de problème utilisé (souvent inconsciemment) par l'humain, soit de faire appel à une expérience similaire sans être identique et de l'adapter au problème actuel (Richter et Weber, 2013).

Ensuite, nous présentons brièvement les techniques utilisant les réseaux de neurones artificiels comme celle de l'apprentissage profond (*deep learning*), qui sont en plein essor à l'heure actuelle. Très utilisés pour supporter le diagnostic en imagerie médicale (Buettner et al. 2020), de nombreuses applications au domaine du test des puces et des systèmes électroniques sont envisagées, avec une attention particulière au problème de l'explicabilité (*explainability*) des conclusions (Amrouch et al, 2021).

Il est également possible d'utiliser les techniques d'exploration de données (*data mining*) pour l'extraction automatique des connaissances, qui pourront être mises à profit par la suite dans la construction de systèmes utilisant toutes les approches présentées.

## 1.8.1 Raisonnement par cas

La technique du raisonnement par cas (*case-based reasoning*, CBR) consiste à conserver les données et les résultats des diagnostics précédents pour ensuite les adapter et les réutiliser lors

de diagnostics futurs. La boucle de rétroaction permet d'améliorer rapidement l'efficacité du système. Il s'agit d'une forme de raisonnement inductif.

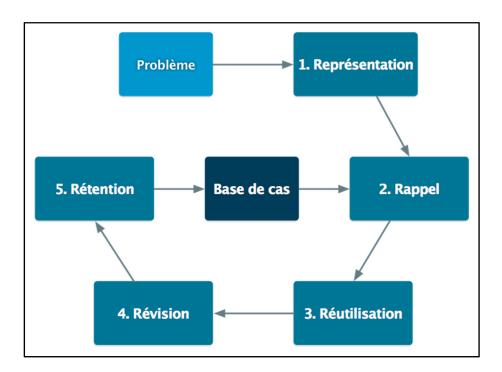

Une solution CBR est constituée en cinq phases distinctes (Richter et Weber, 2013):

- 1. Lors de la **représentation de cas**, les données pertinentes sont sélectionnées, des structures de données appropriées sont choisies ainsi qu'une méthode d'indexation qui favorisera un rappel efficace.

- 2. Le rappel de cas consiste à identifier les éléments qui résument le problème ou le cas actuel, puis à utiliser ces éléments afin de retrouver des cas similaires emmagasinés dans la mémoire. Dans le cas où plusieurs candidats sont disponibles, celui offrant la plus grande similarité doit être sélectionné.

- 3. Au cours de l'étape de **réutilisation de cas**, les différences entre le cas actuel et le cas passé sélectionné lors du rappel sont identifiées. Le cas passé est ensuite adapté pour qu'il corresponde au cas actuel. Les méthodes d'adaptation incluent la substitution de valeurs, et la transformation basée sur des heuristiques.

- 4. La **révision de cas** implique l'évaluation de la solution proposée sur le cas réel et sa correction en cas de besoin. La correction constitue un apport de connaissances spécifiques au domaine.

- 5. L'étape finale est celle de l'apprentissage ou rétention, où l'information utile produite pendant la résolution du problème vient bonifier l'ensemble de cas. La conservation des résultats négatifs comme positifs est importante afin d'éviter de reproduire des erreurs déjà corrigées.

### **Forces**

- Permet d'atteindre des taux de succès supérieurs à 90% lorsqu'une base de cas substantielle est constituée.

- La simulation et les données historiques peuvent être réutilisées pour informer la base de cas (Zhang et al., 2011).

• Le développement est plus facile que dans le cas d'un système traditionnel à base de règles puisque l'acquisition de connaissances est incrémentale et que la contribution d'experts du domaine nécessaire est limitée. (Jin et al, 2016).

#### **Faiblesses**

- Nécessite un volume de cas important pour atteindre un taux d'efficacité intéressant.

- Une nouvelle base de cas doit être générée pour chaque produit. (Sugimatsu, 1994) propose l'utilisation de deux bases, l'une, générique, partagée par tous les produits et la seconde, plus spécifique, propre à chacun des produits.

- L'efficacité peut être affectée par la qualité des algorithmes de rappel et d'indexation, surtout dans le cas d'une base de cas volumineuse.

# 1.8.2 Apprentissage machine par réseaux de neurones artificiels

Les réseaux de neurones artificiels sont des systèmes de traitement de l'information dont la structure est inspirée de la structure biologique du cerveau. Il s'agit de graphes dirigés et pondérés où les nœuds sont appelés des « neurones » et où les liens pondérés appelés « synapses » forment les connexions entre les neurones. Les neurones sont organisés en couches. Une fonction de propagation calcule l'entrée d'un neurone à partir des sorties de ses prédécesseurs. En règle générale, les neurones d'une couche sont uniquement connectés aux neurones des couches immédiatement précédente et suivante.

(Watt et al., 2020) présente le pipeline traditionnel de l'apprentissage machine par réseaux de neurones artificiels :

- 1. Collecte des données (*Data Collection*)

- 2. Ingénierie des caractéristiques d'intérêt (Feature Design)

- 3. Entraînement du réseau (*Model Training*)

- 4. Validation du modèle (*Model Validation*)

Bien qu'ils existent depuis des décennies, les applications et la performance des réseaux de neurones artificiels étaient limitées par des contraintes importantes d'espace mémoire et de puissance de calcul disponibles. L'augmentation rapide de la performance des ordinateurs depuis le début du siècle a permis la résurgence de ces techniques ainsi que l'exploitation de réseaux comportant un très grand nombre de couches internes. Ces réseaux, dits d'apprentissage profond (*deep learning*), ont permis une véritable révolution dans les domaines de l'analyse d'image, de la reconnaissance de la voix ou encore dans le traitement d'information en langage naturel.

#### **Forces**

- Permet le diagnostic des systèmes très complexes, pour lesquels la construction d'un modèle traditionnel est très coûteuse (Zhang et al., 2011).

- Nécessite peu de contribution d'experts du domaine par rapport aux méthodes traditionnelles ou basées sur des modèles (Totton et Limb, 1991).

- Les données historiques de réparation peuvent être utilisées pour l'entraînement.

#### **Faiblesses**

- Nécessite un grand volume de données pour l'entraînement.

- Très sensibles à la qualité des données fournies pour l'entraînement, les réseaux mal entraînés peuvent s'avérer fragiles ou peu performants (Chowdhury et al, 2022).

- Il peut être difficile pour l'opérateur humain de comprendre les causes qui ont mené aux conclusions d'un réseau de neurones multicouches, comme ceux utilisés en apprentissage profond. Ce manque d'explicabilité (ou d'interprétabilité) peut réduire le niveau de confiance envers le système diagnostic (Amrouch et al, 2021).

## 1.9 Systèmes hybrides

Puisque toutes les méthodes de diagnostic automatisé élaborées jusqu'à présent comportent des forces et des faiblesses, il est rare qu'elles soient utilisées de façon exclusive dans un système de production. La plupart des systèmes de diagnostic automatisé modernes sont donc

des hybrides, qui utilisent une combinaison de techniques pour accomplir les différentes tâches présentées à la section 1.4.

La combinaison du raisonnement par cas et de la modélisation est particulièrement fréquente, puisqu'elle permet de séparer l'algorithme de raisonnement de la représentation du domaine (Dendani et al, 2012).

À la figure 1.1, on peut remarquer la présence d'un bloc, lié par un lien pointillé à celui des approches hybrides : celui de l'exploration de données ou *data mining*. Le lien pointillé est utilisé en raison du fait que l'exploration de données n'est pas une approche complète pour la construction d'un système de diagnostic automatisé, mais plutôt un outil important utilisé dans la réalisation de systèmes hybrides.

Une façon de vaincre le *knowledge acquisition bottleneck* est l'extraction de connaissances ou d'informations de cas complets dans les bases de données existantes, parfois très imposantes. Il existe certains domaines où le volume de données historiques est très important, ce qui favorise ces techniques. Le diagnostic automobile est un bon exemple et de tels systèmes ont été développés chez certains grands constructeurs (Richter & Weber, 2013).

L'utilisation de l'exploration de données peut contribuer à diminuer l'impact du *knowledge* acquisition bottleneck sur un système utilisant l'une des autres méthodes présentées. Il faut alors comparer le coût d'implémentation de l'exploration de données aux coûts reliés à l'implication d'un expert du domaine.

## 1.10 État de l'art

Dans cette section, nous présentons les résultats de recherche récents concernant les méthodes de diagnostic automatisé, en particulier les méthodes utilisées pour le diagnostic des circuits électroniques au niveau carte.

Nous avons regroupé les publications selon les catégories présentées dans la taxonomie de la section 1.4. Les approches basées sur l'apprentissage machine et les systèmes hybrides, qui combinent plusieurs approches, sont dominantes dans la littérature récente. Nous avons classé les articles décrivant des systèmes hybrides selon l'approche destinée à la contribution principale de l'article.

## 1.10.1 Approches traditionnelles

(Nigh et al., 2021) propose l'utilisation d'un système expert intégré directement à l'équipement de test automatisé (*Automated Test Equipment*, ATE) des puces électroniques. Le système peut contrôler l'ATE afin de réaliser de façon autonome des tests permettant de valider ses hypothèses et procéder au diagnostic de façon incrémentale. Un prototype simple est construit et comparé au traitement manuel dans le cas de défectuosités touchant la chaîne de balayage des puces. Le système expert présente des avantages intrinsèques au niveau de l'explicabilité du diagnostic. Les auteurs mentionnent les difficultés reliées à l'acquisition des connaissances, mais ne proposent pas de solution.

## 1.10.2 Approches basées sur des modèles

L'approche incrémentale présentée dans (Amati et al., 2009) vise à réduire le temps de diagnostic en effectuant seulement un sous-ensemble des tests disponibles, en utilisant le syndrome partiel obtenu pour sélectionner le prochain test à effectuer jusqu'à l'identification du composant fautif. Elle repose sur l'utilisation d'un modèle probabiliste. L'approche a été testée sur 10 circuits d'essais et a permis une réduction de l'ordre de 30% du nombre de tests nécessaires pour arriver au diagnostic, par rapport au nombre de tests disponibles.

(X. Zhang et al., 2012) présente une base mathématique théorique pour un système de diagnostic à base de modèles qui soit à la fois sain (« sound ») et complet. La méthodologie permet de développer un moteur de diagnostic en sélectionnant des tests dérivés d'un modèle. Comme la méthodologie est cependant très lourde dans le cas d'un système complexe, il est nécessaire d'augmenter le niveau d'abstraction du modèle.

(Bolchini et al., 2013) présente une technique utilisant certains algorithmes de l'exploration de données afin de découvrir les relations entre les vecteurs de test et le composant fautif identifié. La technique d'exploration utilisée est celle de la recherche des règles d'association (association rule mining). Les modèles système utilisés sont très simples. Les résultats expérimentaux sont obtenus en testant 5 circuits d'essais synthétiques non décrits. Une réduction du nombre de tests variant de 32% à 88% est annoncée, ainsi qu'un taux de succès de 100%.

# 1.10.3 Approches utilisant l'apprentissage machine

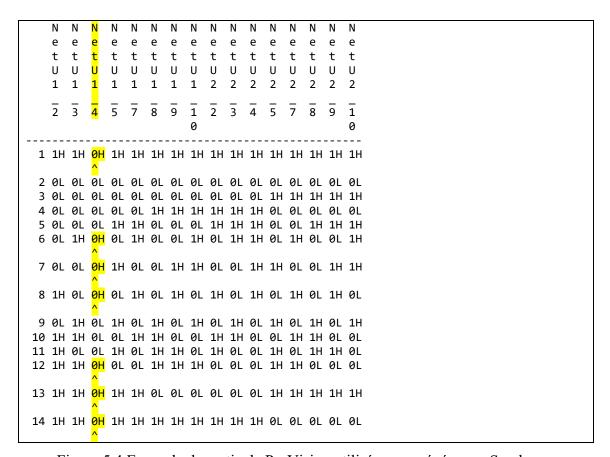

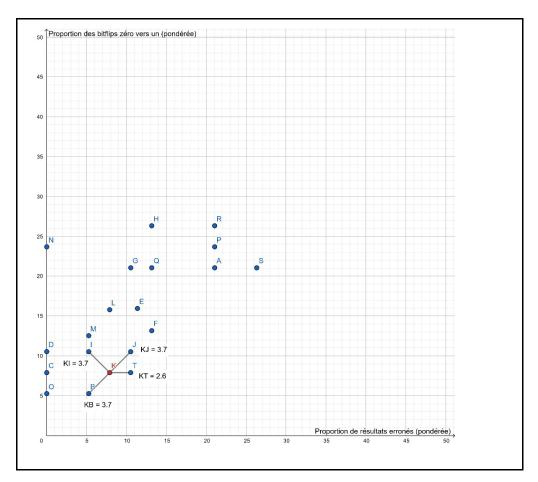

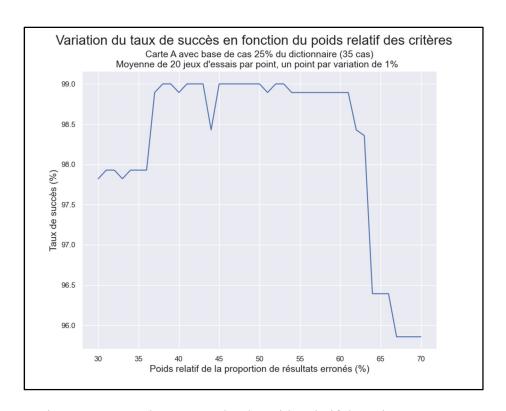

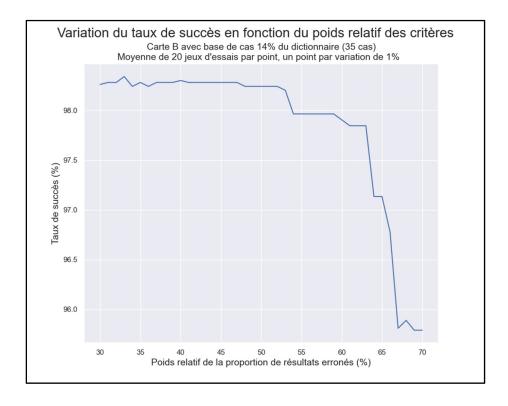

(Z. Zhang et al, 2011) propose une méthodologie de diagnostic basée sur les réseaux de neurones artificiels. Plutôt qu'un seul réseau multicouche, les auteurs utilisent un ensemble de réseaux à une seule couche, un par composant de la carte. Cette approche réduit l'occupation mémoire et le temps d'entraînement. L'entraînement est effectué à l'aide des données historiques de réparation. Le système est utilisé expérimentalement pour le diagnostic de commutateurs de réseau industriels et comparé à un réseau de neurones à trois couches conventionnel ainsi qu'à un système de raisonnement par cas utilisant un classificateur Bayesien simple et montre un taux de succès amélioré et un temps d'entraînement réduit.