Prédiction et analyse statistique des performances des circuits

asynchrones dans un contexte d'adaptation dynamique de la

tension d'alimentation

par

Maryem BENYOUSSEF

THÈSE PRÉSENTÉE À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE

DU DOCTORAT EN GÉNIE

Ph. D.

MONTRÉAL, LE 10 OCTOBRE 2024

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

## **PRÉSENTATION DU JURY**

CETTE THÈSE A ÉTÉ ÉVALUÉE

PAR UN JURY COMPOSÉ DE :

M. Claude Thibeault, directeur de thèse

Département de génie électrique à l'École de technologie supérieure

M. Yvon Savaria, codirecteur de thèse

Département de génie électrique à Polytechnique

M. Éric Granger, président du jury

Département de génie des systèmes à l'École de technologie supérieure

M. Pascal Giard, membre du jury

Département de génie électrique à l'École de technologie supérieure

Mme. Rachel Bouserhal, membre du jury

Département de génie électrique à l'École de technologie supérieure

M. Daniel Massicotte, examinateur externe

Département de génie électrique à l'Université du Québec à Trois-Rivières

ELLE A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 19 AOUT 2024

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEUR

## **REMERCIEMENTS**

Je tiens à exprimer ma profonde gratitude envers mes directeurs de recherche, Claude Thibeault et Yvon Savaria, pour leur guidance, leur expertise, et leur soutien inestimable tout au long de cette aventure de recherche. Leurs connaissances et leur engagement inébranlable ont été des sources d'inspiration pour moi. Leur capacité à susciter la curiosité intellectuelle et à inciter à l'excellence a été un véritable moteur pour la réussite de cette thèse. Leurs précieux conseils, leur patience et leur disponibilité ont été essentiels pour me guider à travers les défis de la recherche. Je leur suis profondément reconnaissante pour leur contribution à mon développement académique et professionnel, et je ne saurais les remercier suffisamment pour leur confiance en moi.

Je souhaite également remercier mes collègues, Mickael Fiorentino, Andrei Dulipovici, Marc-André Léonard, et bien d'autres collègues du laboratoire LACIME. Leur collaboration et leur expertise partagée ont enrichi ma vie professionnelle.

Je tiens à exprimer ma profonde gratitude envers ma famille, qui a joué un rôle exceptionnel dans ma réussite académique et professionnelle. Tout d'abord, mon père Abdellah, qui a attendu avec fierté ce moment de ma graduation au doctorat, a été un modèle de persévérance et de détermination. Ma mère Fatiha, grâce à ses prières et son amour inconditionnel, a été une source d'inspiration constante. Mon mari Rachid a été mon pilier, avec sa patience, son amour, ses encouragements, son aide précieuse et sa générosité. Enfin, mes enfants, Firdaws, Yassir et Sarah, avec leur amour inconditionnel et leur présence dans ma vie, ont été ma motivation ultime. Leur soutien a été inestimable tout au long de mon parcours.

# **Prédiction et analyse statistique des performances des circuits asynchrones dans un contexte d'adaptation dynamique de la tension d'alimentation**

Maryem BENYOUSSEF

## **RÉSUMÉ**

L'analyse des circuits asynchrones revêt une importance cruciale dans la conception et l'optimisation des systèmes électroniques, permettant de garantir des performances fiables et efficaces. Cette thèse se penche sur deux aspects cruciaux de l'analyse des circuits asynchrones.

Dans le premier volet, la thèse explore les contraintes de délai pour les circuits *SRBDHF* (*Single Rail Bundled Data Handshake Free*) utilisant la technique *DVS* (*Dynamic Voltage Scaling*) afin de gérer la consommation d'énergie. Un modèle novateur est proposé pour définir ces contraintes, couvrant divers aspects tels que la synchronisation, la dégradation du signal de synchronisation et la sensibilité des portes logiques à la variation de tension d'alimentation. Ces contraintes, jusque-là non explicitement formulées, sont cruciales pour garantir la conformité temporelle. Les résultats des simulations mettent en évidence la faisabilité de respecter ces contraintes avec la *DVS*, mais indiquent également que des ajustements peuvent être nécessaires pour optimiser la propagation des signaux et l'efficacité des opérations.

Le second volet de cette thèse introduit un modèle d'analyse statistique de performance spécialement adapté aux pipelines asynchrones. Ce modèle est applicable à deux styles de circuits asynchrones, les *SRBDHF* et les *CE* (*Click Element*), et il permet une évaluation efficace des performances face à des variations de procédé de fabrication, de tension et de température. Il inclut un modèle de variabilité de délai pour évaluer l'impact des variations de procédé de fabrication sur les performances, ainsi qu'un modèle d'analyse statistique de performance intégrant diverses vérifications de contraintes, logiques et temporelles. La prise en compte de la variation de tension d'alimentation dans l'analyse, de la région nominale à la région proche du seuil, ainsi que des variations de température, est essentielle pour vérifier les différentes contraintes statistiques. Les résultats démontrent que ce modèle offre une précision raisonnable, avec une erreur moyenne de seulement 2% par rapport aux analyses détaillées basées sur des simulations Monte Carlo de bas niveau. De plus, cette méthode permet une évaluation rapide des performances des circuits asynchrones, réduisant considérablement le temps nécessaire pour des analyses approfondies.

Ces deux aspects de la thèse apportent une contribution significative à l'analyse des circuits asynchrones, offrant des perspectives prometteuses pour l'avancement de la conception de ces circuits.

**Mots clés :** circuit asynchrones, adaptation dynamique de la tension d'alimentation, prédition des performances, analyse statistique, contraintes temporelles, contraintes logiques

# Prediction and Statistical Analysis of Asynchronous Circuit Performance in the Context of Dynamic Voltage Scaling

Maryem BENYOUSSEF

## ABSTRACT

The analysis of asynchronous circuits is of crucial importance in the design and optimization of electronic systems, ensuring reliable and efficient performance. This thesis delves into two crucial aspects of asynchronous circuit analysis.

In the first part, the thesis explores delay constraints for Single-Rail Bundled-Data Handshake-Free (*SRBDHF*) circuits using *Dynamic Voltage Scaling (DVS)* to manage power consumption. An innovative model is proposed to define these constraints, covering various aspects such as synchronization, degradation of the synchronization signal, and the sensitivity of logic gates to changes in supply voltage. These constraints, not explicitly formulated before, are crucial to ensure temporal compliance. Simulation results highlight the feasibility of meeting these constraints with *DVS*, but also suggest that adjustments may be necessary to optimize signal propagation and operation efficiency.

The second part of this thesis introduces a statistical performance analysis model specifically tailored to asynchronous pipelines. This model is applicable to two styles of asynchronous circuits, *SRBDHF* and Click Element (*CE*), and enables effective performance evaluation in the face of variations in manufacturing process, voltage, and temperature. It includes a delay variability model to assess the impact of manufacturing process variations on performance, as well as a statistical performance analysis model incorporating various logical and temporal constraint checks. Accounting for supply voltage variation in the analysis, from the nominal region to the near-threshold region, as well as temperature variations, is essential for verifying different statistical constraints. Results demonstrate that this model offers reasonable accuracy, with an average error of only 2% compared to detailed analyses based on low-level Monte Carlo simulations. Moreover, this method allows for a rapid assessment of asynchronous circuit performance, significantly reducing the time required for in-depth analyses.

These two aspects of the thesis make a significant contribution to asynchronous circuit analysis, providing promising insights for the advancement of the design of these circuits.

**Keywords:** asynchronous circuits, dynamic voltage scaling, performance prediction, statistical analysis, temporal constraints, logical constraints

## TABLE DES MATIÈRES

|                                                                                                                                                                | Page      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>INTRODUCTION .....</b>                                                                                                                                      | <b>1</b>  |

| <b>CHAPITRE 1 NOTIONS DE BASE .....</b>                                                                                                                        | <b>11</b> |

| 1.1 Introduction.....                                                                                                                                          | 11        |

| 1.2 Les circuits asynchrones .....                                                                                                                             | 11        |

| 1.2.1 Protocole de communications .....                                                                                                                        | 12        |

| 1.2.2 Type de codage .....                                                                                                                                     | 14        |

| 1.2.3 Classification des circuits asynchrones.....                                                                                                             | 14        |

| 1.3 Variabilité de procédés de fabrication .....                                                                                                               | 18        |

| 1.3.1 Sources de variation de procédés de fabrication.....                                                                                                     | 19        |

| 1.3.2 Types de variation de procédés de fabrication.....                                                                                                       | 21        |

| 1.3.3 Modélisation des variations de procédés de fabrication .....                                                                                             | 23        |

| 1.4 Délai de propagation d'une porte logique.....                                                                                                              | 24        |

| 1.5 Techniques de réduction de la consommation énergétique .....                                                                                               | 26        |

| 1.5.1 Dynamic Voltage Scaling .....                                                                                                                            | 26        |

| 1.6 Analyse temporelle de circuit .....                                                                                                                        | 27        |

| 1.6.1 Analyse statique .....                                                                                                                                   | 28        |

| 1.6.2 Analyse statistique .....                                                                                                                                | 29        |

| 1.6.3 Rendement temporel .....                                                                                                                                 | 30        |

| 1.7 Notions statistiques .....                                                                                                                                 | 31        |

| 1.7.1 Calcul de la moyenne et écart type d'une variable aléatoire .....                                                                                        | 31        |

| 1.7.2 Calcul de la moyenne et écart type de plusieurs variables aléatoires .....                                                                               | 32        |

| 1.7.3 La fonction de répartition cumulative ( <i>CDF</i> ) .....                                                                                               | 35        |

| <b>CHAPITRE 2 REVUE DE LITTÉRATURE.....</b>                                                                                                                    | <b>37</b> |

| 2.1 Introduction.....                                                                                                                                          | 37        |

| 2.2 <i>DVS</i> dans les circuits synchrones et asynchrones .....                                                                                               | 37        |

| 2.3 Analyse de performance dans les circuits asynchrones .....                                                                                                 | 42        |

| 2.4 Approche proposée .....                                                                                                                                    | 44        |

| <b>CHAPITRE 3 MODÈLE DE PRÉDICTION DES CONTRAINTES DE DÉLAIS<br/>ASSOCIÉES À LA TECHNIQUE <i>DVS</i> DANS LES CIRCUITS<br/>ASYNCHRONES DE TYPE SRBDHF.....</b> | <b>45</b> |

| 3.1 Introduction.....                                                                                                                                          | 45        |

| 3.2 Type de circuits ciblés .....                                                                                                                              | 45        |

| 3.3 Modèle de prédiction proposé.....                                                                                                                          | 47        |

| 3.3.1 Propagation de l'impulsion de synchronisation.....                                                                                                       | 48        |

| 3.3.2 Les marges de prépositionnement et de maintien .....                                                                                                     | 51        |

| 3.3.3 Sensibilité de la logique utilisée .....                                                                                                                 | 52        |

| 3.3.4 Application du modèle proposé .....                                                                                                                      | 54        |

| 3.4 Résultats et discussion .....                                                                                                                              | 56        |

|                                                                                                                                                       |                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|

| 3.5                                                                                                                                                   | Conclusion .....                                                                        | 64  |

| <b>CHAPITRE 4 MÉTHODE D'ANALYSE STATISTIQUE DE PERFORMANCES<br/>POUR LES CIRCUITS ASYNCHRONES EN CONSIDÉRANT LA<br/>TECHNIQUE <i>DVS</i> .....</b> 67 |                                                                                         |     |

| 4.1                                                                                                                                                   | Introduction.....                                                                       | 67  |

| 4.2                                                                                                                                                   | Approche d'analyse statistique .....                                                    | 67  |

| 4.2.1                                                                                                                                                 | Modèle de variabilité de délai.....                                                     | 68  |

| 4.2.2                                                                                                                                                 | Modèle d'analyse statistique de performance.....                                        | 73  |

| 4.3                                                                                                                                                   | Résultats et discussion .....                                                           | 80  |

| 4.3.1                                                                                                                                                 | Validation du modèle de variabilité de délai proposé.....                               | 82  |

| 4.3.2                                                                                                                                                 | Impact des variations de tension, de température et de procédés de<br>fabrication ..... | 89  |

| 4.3.3                                                                                                                                                 | Analyse statistique versus analyse statique.....                                        | 93  |

| 4.3.4                                                                                                                                                 | Comparaison avec les travaux de littérature .....                                       | 95  |

| 4.4                                                                                                                                                   | Conclusion .....                                                                        | 102 |

| <b>CONCLUSION.....</b>                                                                                                                                |                                                                                         | 103 |

| <b>RECOMMANDATIONS .....</b>                                                                                                                          |                                                                                         | 109 |

| ANNEXE I                                                                                                                                              | CODE HSPICE DU CIRCUIT <i>SRBDHF</i> .....                                              | 99  |

| ANNEXE II                                                                                                                                             | CODE HSPICE DU CIRCUIT <i>CE</i> .....                                                  | 105 |

| ANNEXE III                                                                                                                                            | ÉROSION / DILATATION.....                                                               | 111 |

| ANNEXE IV                                                                                                                                             | PERTE DE L'IMPULSION DANS LA LIGNE À DÉLAI .....                                        | 113 |

| ANNEXE V                                                                                                                                              | DÉLAI DE PROPAGATION EN FONCTION DE FANOUT .....                                        | 114 |

| <b>LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES .....</b>                                                                                                     |                                                                                         | 131 |

## LISTE DES TABLEAUX

|                                                                                                                                                                                                                                                             | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Tableau 3.1 Délais des transitions montantes et descendantes pour différentes valeurs de tension d'alimentation et portes logiques.....                                                                                                                     | 49   |

| Tableau 3.2 Facteurs de croissance des délais des différentes portes logiques lorsque Vdd passe de 1.1V à 0.9V ( <i>DGF1</i> ) et de 1.1V à 0.7V ( <i>DGF2</i> ).....                                                                                       | 53   |

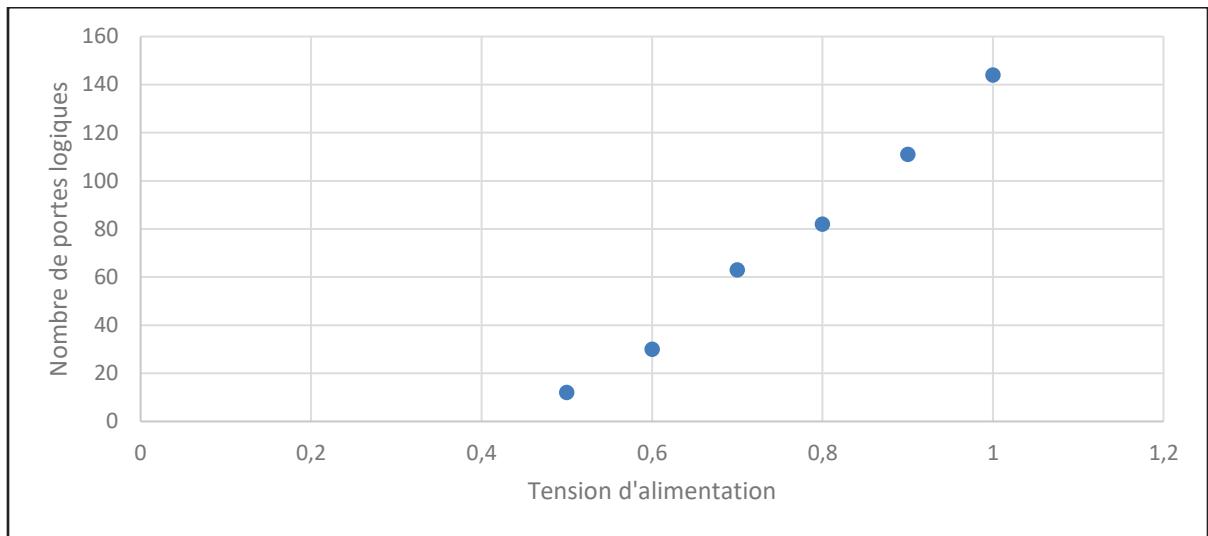

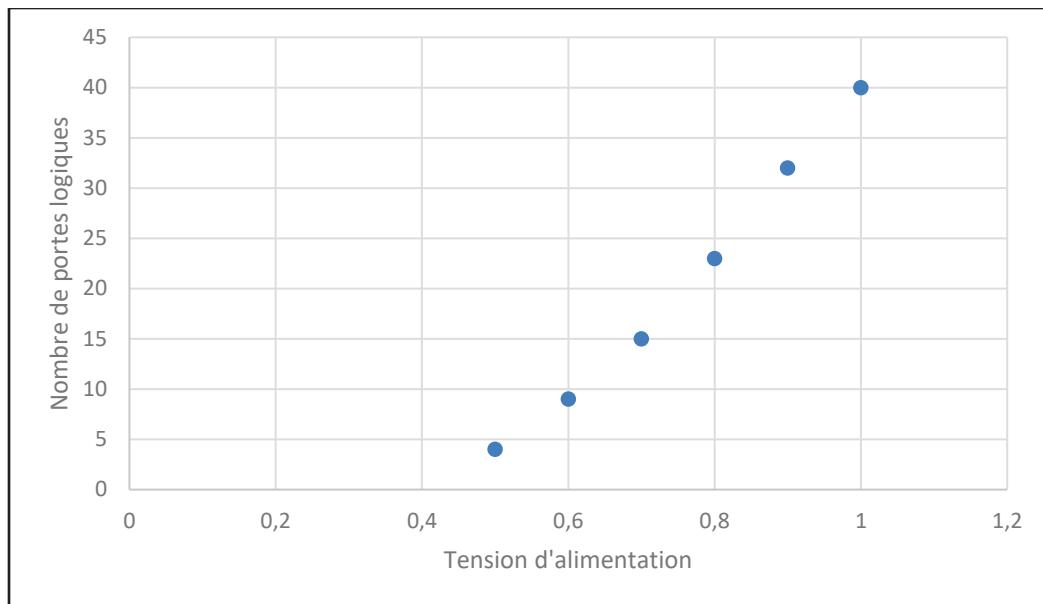

| Tableau 3.3 Largeur initiale de l'impulsion (PW1, PW2) en nanosecondes et le nombre de portes logiques (Nb1, Nb2) à partir desquelles l'impulsion est perdue à différentes tensions $V_{dd}$ et pour deux longueurs de chaîne d'inverseurs <i>PGB</i> ..... | 58   |

| Tableau 3.4 Délais et marge (en nanoseconde) pour différents cas.....                                                                                                                                                                                       | 61   |

| Tableau 3.5 Correction et optimisation de la marge de prépositionnement en nanosecondes pour différentes valeurs de tension et types d'ajustement .....                                                                                                     | 62   |

| Tableau 3.6 Configurations des éléments de délai pour différentes valeurs de tension, ajustement 2 .....                                                                                                                                                    | 64   |

| Tableau 4.1 Valeurs statistiques des paramètres L Vthn et Vthp .....                                                                                                                                                                                        | 81   |

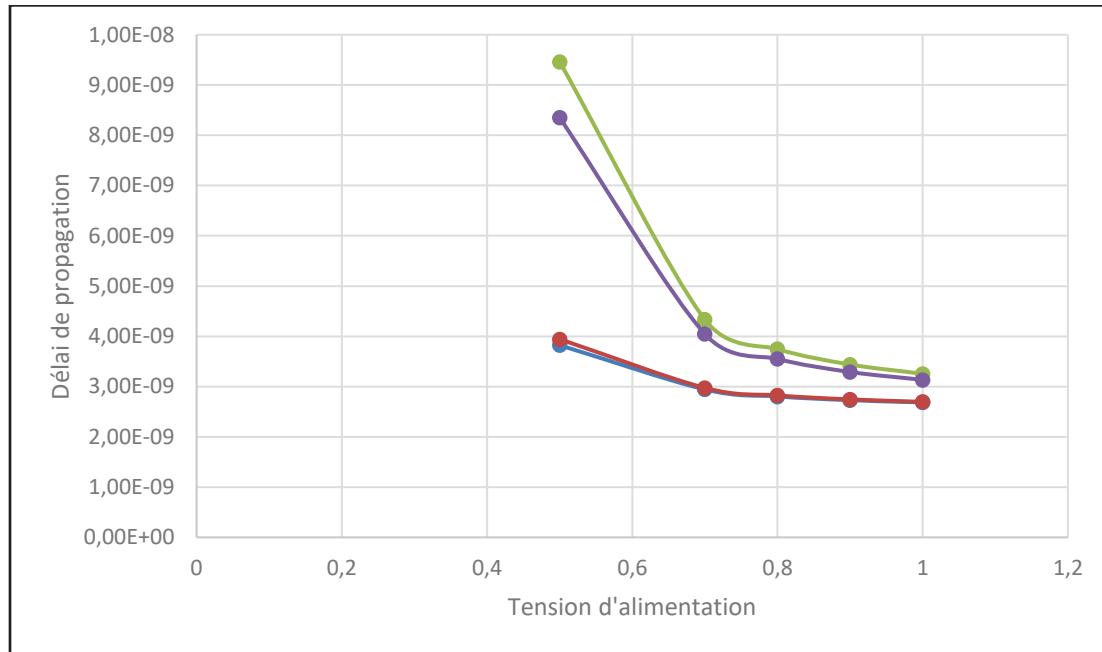

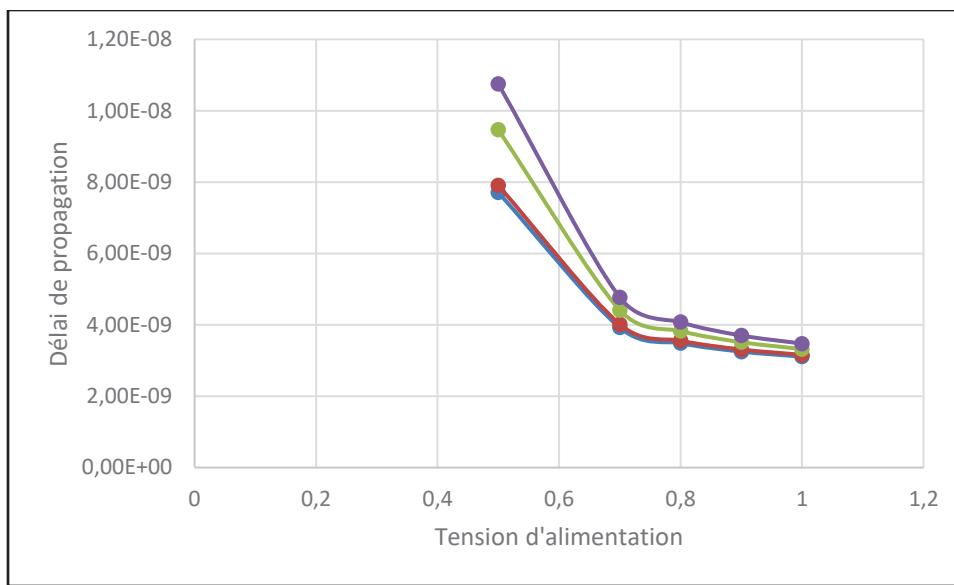

| Tableau 4.2 Erreurs relatives de la moyenne et de l'écart type des différents délais en (%) entre <i>MC</i> et le modèle proposé pour le circuit <i>CE</i> en fonction de la variation de tension d'alimentation.....                                       | 84   |

| Tableau 4.3 Erreurs relatives de la moyenne et de l'écart type des différents délais en (%) entre <i>MC</i> et le modèle proposé pour le circuit <i>SRBDHF</i> en fonction de la variation de tension d'alimentation .....                                  | 85   |

|              |                                                                                                                                                                                                                                            |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 4.4  | Comparaison du ratio $\mu/\sigma$ pour les marges de prépositionnement et de maintien estimé par les mesures <i>Hspice</i> et le modèle proposé pour les circuits <i>CE</i> et <i>SRBDHF</i> en fonction de la tension d'alimentation..... | 87  |

| Tableau 4.5  | Évolution des performances logiques statistiques pour le circuit <i>SRBDHF</i> sous variation de tension d'alimentation.....                                                                                                               | 89  |

| Tableau 4.6  | Évaluation de la contrainte logique statistique pour le circuit <i>SRBDHF</i> à différentes valeurs de température sous variation de tension, en utilisant des simulations <i>Hspice</i> .....                                             | 90  |

| Tableau 4.7  | Comparaison du rapport $\mu/\sigma$ estimé par les mesures <i>Hspice</i> pour les circuits <i>CE</i> et <i>SRBDHF</i> sous variation de température.....                                                                                   | 92  |

| Tableau 4.8  | Comparaison des marges de prépositionnement pire cas et statistique (s) des circuits <i>CE</i> et <i>SRBDHF</i> en fonction de la variation de tension d'alimentation.....                                                                 | 94  |

| Tableau 4.9  | Impact des variations de tension, de température et de procédés de fabrication sur les contraintes statistiques temporelles .....                                                                                                          | 96  |

| Tableau 4.10 | Impact des variations de tension, de température et de procédés après ajustement de configuration.....                                                                                                                                     | 98  |

| Tableau 4.11 | Comparaison entre le modèle proposé et les travaux de la littérature .....                                                                                                                                                                 | 101 |

## LISTE DES FIGURES

|             | Page                                                                                                                           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1  | Protocole deux phases Tirée de Yahya (2009, p. 6) .....12                                                                      |

| Figure 1.2  | Protocole quatre phases Tirée de Yahya (2009, p. 6) .....13                                                                    |

| Figure 1.3  | Schéma bloc du pipeline <i>CE</i> .....16                                                                                      |

| Figure 1.4  | Configuration détaillée d'architecture du pipeline CE .....17                                                                  |

| Figure 1.5  | Architecture de base d'une unité d'exécution ( <i>EU</i> )<br>des circuits <i>SRBDHF</i> .....18                               |

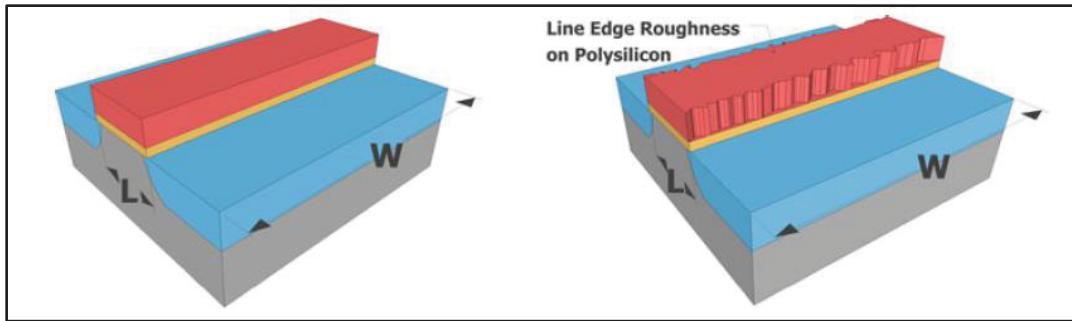

| Figure 1.6  | Rugosité des bords de ligne Tirée de Champac (2018, p 51) .....20                                                              |

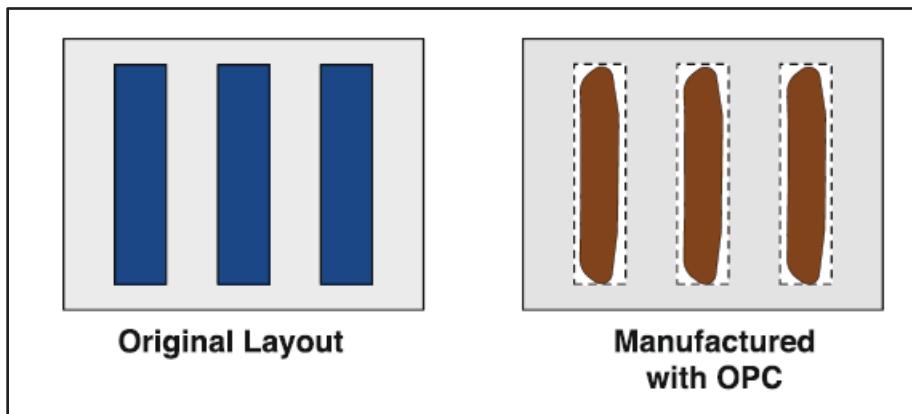

| Figure 1.7  | Effet de proximité optique Tirée de Champac (2018, p 52) .....20                                                               |

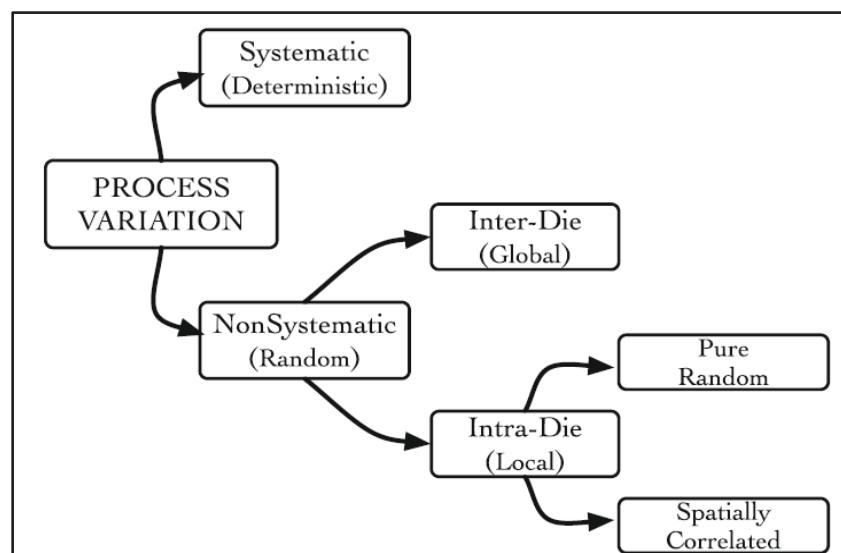

| Figure 1.8  | Classification des variations de procédé en fonction<br>de leur comportement Tirée de Champac (2018, p 56) .....21             |

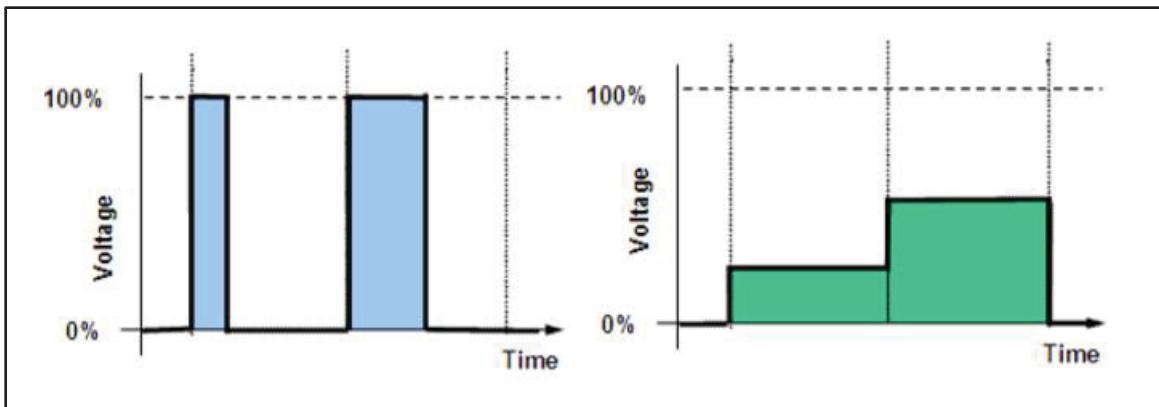

| Figure 1.9  | Vitesse de traitement d'une tache lors de l'application de la <i>DVS</i> .....27                                               |

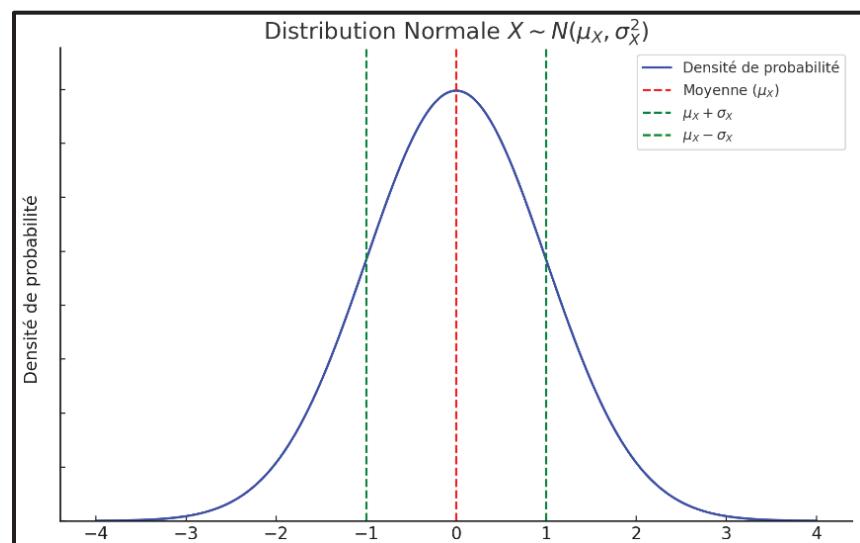

| Figure 1.10 | Distribution normale de X .....31                                                                                              |

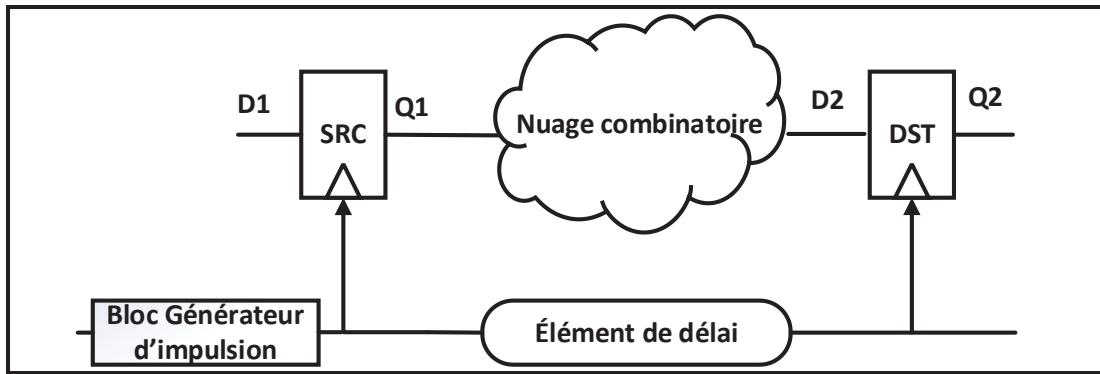

| Figure 3.1  | Architecture de base d'une unité d'exécution ( <i>EU</i> ) dans des circuits<br>asynchrones de type <i>SRBDHF</i> .....46      |

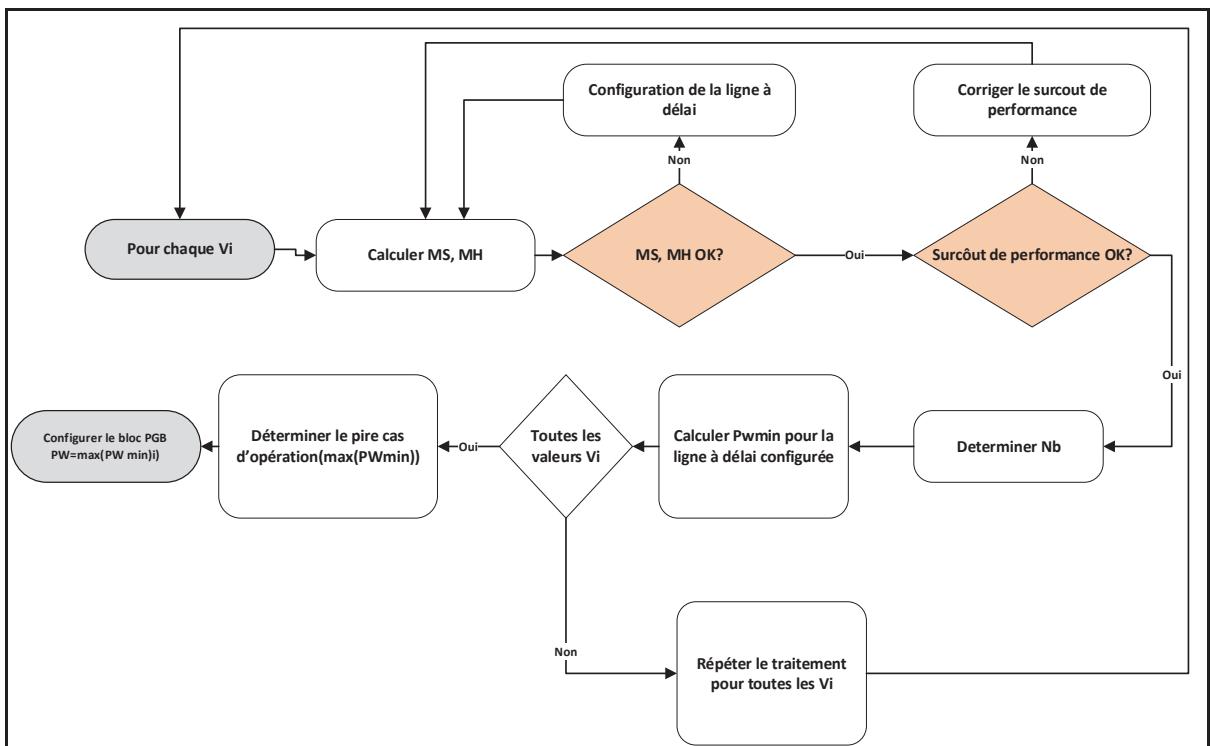

| Figure 3.2  | Diagramme de flux du processus de vérification dans un circuit<br>asynchrone <i>SRBDHF</i> utilisant le modèle proposé .....55 |

|            |                                             |    |

|------------|---------------------------------------------|----|

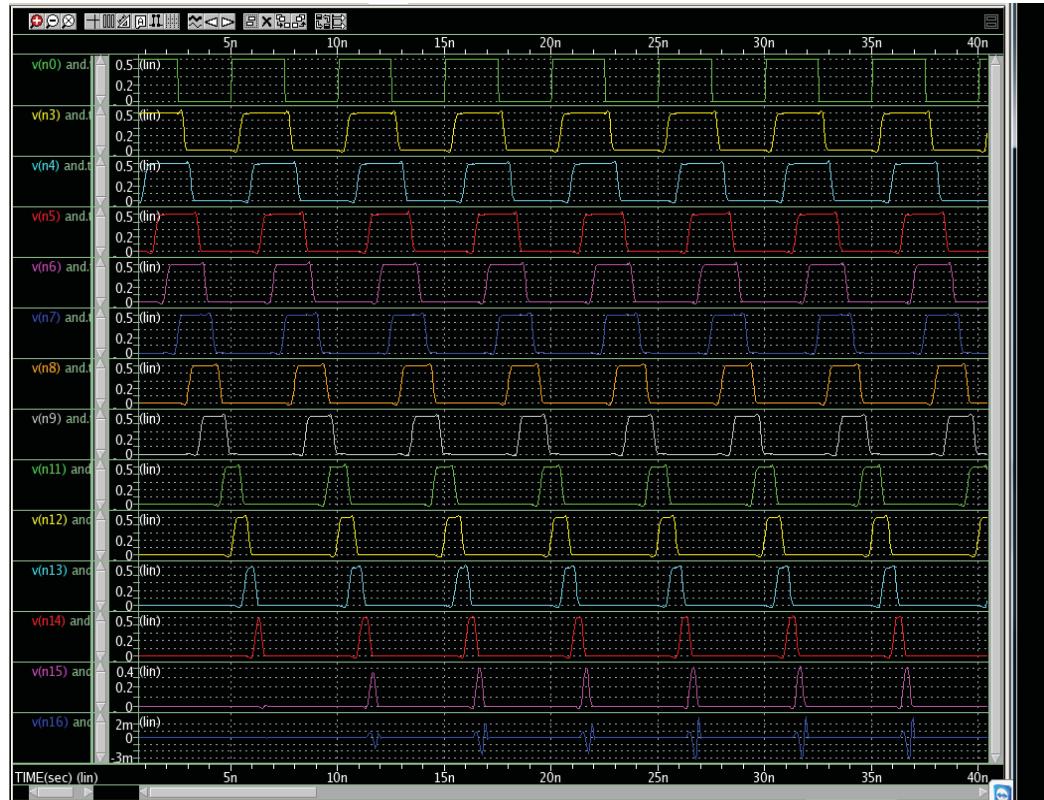

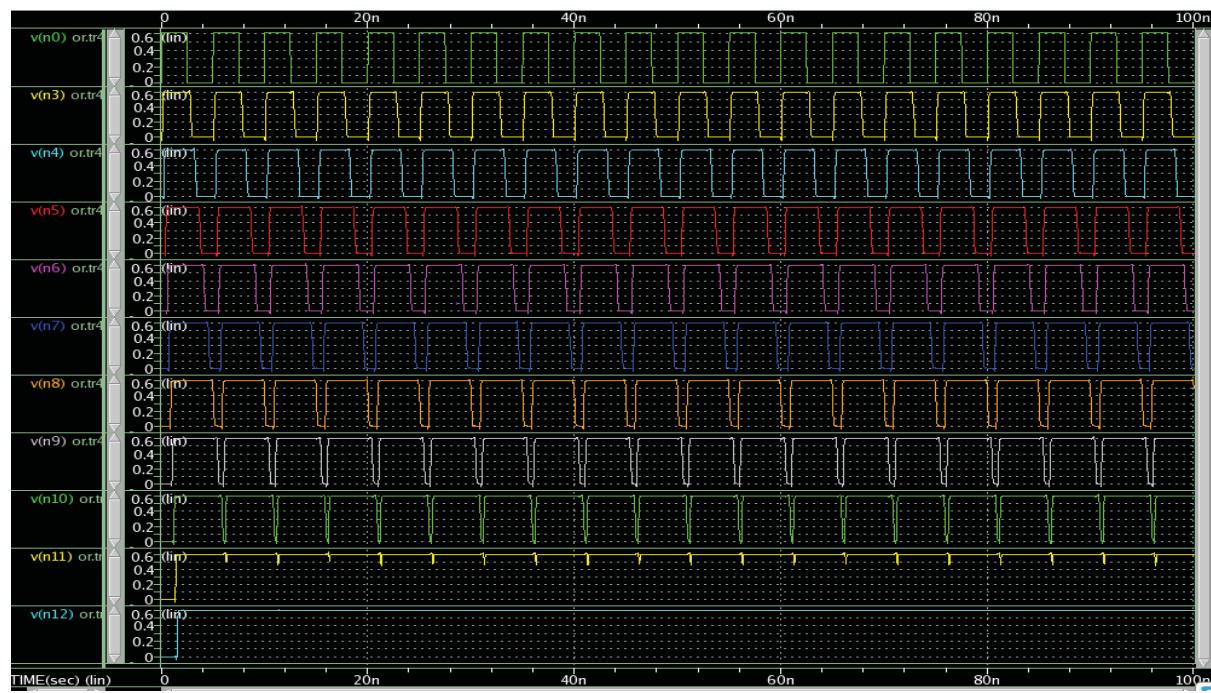

| Figure 3.3 | Circuit d'essai .....                       | 57 |

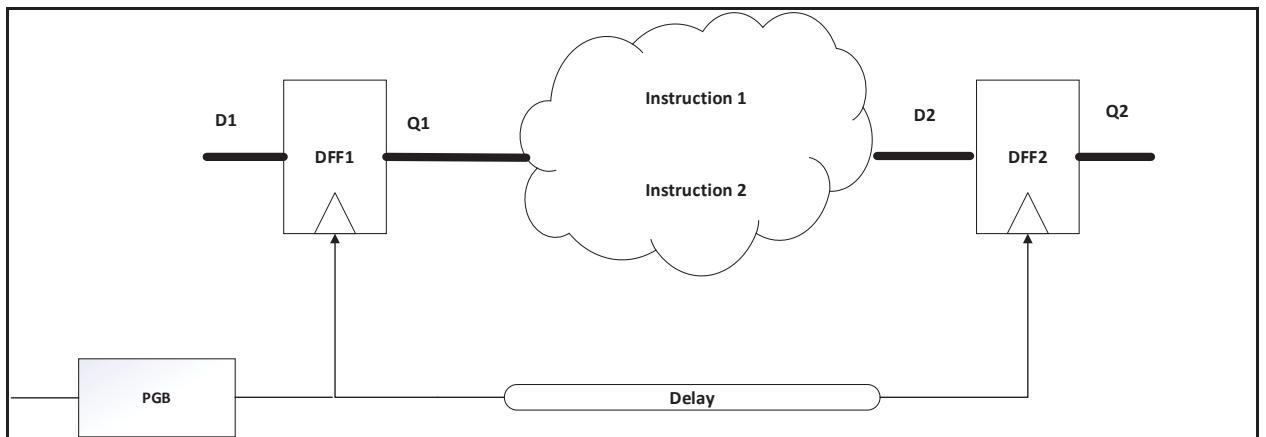

| Figure 4.1 | Circuit d'essai de type <i>SRBDHF</i> ..... | 82 |

| Figure 4.2 | Circuit d'essai de type <i>CE</i> .....     | 82 |

## INTRODUCTION

### Contexte et motivation

La conception des circuits numériques a connu une évolution constante au fil des années pour répondre aux demandes croissantes en termes de performance, de fiabilité et d'efficacité énergétique. Les circuits asynchrones sont perçus comme une option intéressante lorsqu'il s'agit de concevoir des systèmes électroniques qui consomment peu d'énergie. Plutôt que de suivre une horloge fixe, les circuits asynchrones fonctionnent de manière autonome, ce qui signifie qu'ils peuvent s'adapter dynamiquement aux besoins de traitement et ils peuvent contribuer à réduire la consommation d'énergie. Cette approche est particulièrement pertinente dans de nombreuses applications où l'efficacité énergétique est essentielle, comme dans les appareils mobiles, les capteurs sans fil et d'autres systèmes alimentés par batterie. Les circuits asynchrones offrent donc une solution prometteuse pour répondre à ces exigences de conception à faible consommation d'énergie (Beigne, Vivet, Thonnart, Christmann, & Clermidy, 2016). Les compromis de la conception des circuits asynchrones sont principalement liés à la complexité accrue de conception et de vérification par rapport aux circuits synchrones, l'absence de signal d'horloge global compliquant l'analyse du comportement et la détection des erreurs. Dans cette introduction, nous explorerons cette approche de conception asynchrone et mettrons en évidence les avantages qu'elle offre. Nous discuterons également de l'influence des variations paramétriques de procédés de fabrication, de température et de tension d'alimentation sur la conception des circuits asynchrones.

La conception des circuits numériques synchrones est la norme depuis de nombreuses années. Dans cette approche, un signal d'horloge global est utilisé pour synchroniser toutes les opérations à travers le circuit. Cette méthode présente des avantages évidents en termes de facilité de conception, de vérification et d'implémentation (Kaeslin, 2014), Le signal d'horloge global coordonne toutes les parties du circuit, simplifiant ainsi le flux de données et permettant aux concepteurs de se concentrer sur la logique à chaque front d'horloge, et comme l'état des registres change de manière synchrone, la vérification, la simulation, le débogage et les tests deviennent plus systématiques et efficaces. Ainsi l'architecture synchrone, largement utilisée

dans l'industrie, bénéficie d'outils de conception, de simulation et de vérification très efficaces. Cependant, à mesure que les exigences en matière de performance et de complexité des systèmes numériques ont augmenté, les limites de la conception synchrone ont commencé à se manifester (Khodosevych & Sakib, 2022).

Tout d'abord, les circuits asynchrones présentent un avantage en termes d'efficacité énergétique par rapport aux circuits synchrones. La principale raison en est l'absence d'une horloge globale constamment active. À la base, dans les systèmes synchrones, l'horloge fonctionne en permanence, même lorsque certaines parties du circuit sont inactives, entraînant une consommation d'énergie inutile. En revanche, les conceptions asynchrones activent uniquement les parties du circuit nécessaires, minimisant ainsi la dépense énergétique inutile. Notons cependant qu'il existe des techniques pour moduler le fonctionnement de l'horloge (*power gating* et *frequency scaling*) qui permettent aux circuits synchrones de minimiser la consommation d'énergie. De plus, la nature événementielle de la conception asynchrone génère des circuits en veille à faible consommation d'énergie, en comparaison avec la conception synchrone qui maintienne une consommation d'énergie en veille inefficace. De plus, certaines techniques de conception asynchrone qui utilisent des bascules sensibles aux niveaux permettent de réduire la consommation d'énergie en raison notamment d'une plus faible capacité d'entrée sur l'entrée d'horloge que les bascules sensibles aux fronts de l'horloge utilisés dans les systèmes synchrones. Ces avantages contribuent de manière significative à l'économie d'énergie globale des circuits asynchrones (Beerel, Ozdag, & Ferretti, 2010) .

En outre, contrairement à la conception synchrone, où la fréquence d'horloge est fixée en fonction du pire scénario de délai de propagation, les circuits asynchrones, en utilisant des signaux de commande dépendant des données, ont la flexibilité d'exploiter le délai de propagation moyen. Cela se traduit souvent par un délai moyen plus court par rapport au pire cas synchrone, car il n'est pas nécessaire d'ajuster la fréquence d'horloge en fonction du scénario le plus pessimiste (Beerel et al., 2010).

De plus, l'avantage des circuits asynchrones par rapport aux circuits synchrones en ce qui concerne la modularité réside dans la facilité avec laquelle les différents blocs d'un circuit asynchrone peuvent être interconnectés et validés. Cela est rendu possible grâce à l'utilisation de canaux de communication spécifiques dans la conception asynchrone. Ces canaux sont conçus pour permettre une communication efficace entre les blocs du circuit, en utilisant une discipline de synchronisation adaptée. En comparaison, dans les circuits synchrones, l'interconnexion des blocs peut être plus complexe en raison de la synchronisation stricte imposée par l'horloge globale. Les concepteurs de circuits synchrones doivent veiller à ce que chaque bloc du circuit soit synchronisé avec précision en fonction du signal d'horloge global. Cela peut entraîner des défis supplémentaires, en particulier lorsqu'il s'agit d'assurer une synchronisation précise dans un système complexe. L'utilisation de canaux de communication dans les circuits asynchrones facilite la connectivité entre les blocs, car les signaux sont transmis de manière asynchrone, c'est-à-dire sans dépendance d'une horloge globale. Cela permet aux blocs de communiquer de manière plus flexible, en se basant sur des événements spécifiques plutôt que sur une horloge commune. En conséquence, les interfaces entre les modules asynchrones sont mieux définies et plus cohérentes, ce qui simplifie leur validation. Cette approche modulaire offre une meilleure flexibilité et elle simplifie le processus de développement des circuits complexes.

Enfin, dans un circuit synchrone, comme toutes les opérations sont synchronisées avec une horloge globale, toutes les transitions de signaux à la sortie des bascules se produisent en même temps, générant des impulsions de courant et de tension très pointues à des fréquences spécifiques correspondant à la fréquence de l'horloge. Cette concentration d'énergie autour de la fréquence d'horloge crée des pics de bruit électromagnétique bien définis à ces fréquences. Ces pics de bruit peuvent potentiellement interférer avec d'autres circuits électroniques, en particulier les circuits analogiques, car ils peuvent introduire des signaux indésirables à des fréquences précises. En revanche, dans un circuit asynchrone, les opérations ne sont pas synchronisées par une horloge globale, et les transitions de signaux se produisent en fonction d'événements spécifiques. Par conséquent, le spectre de bruit généré est plus dispersé et moins concentré autour d'une fréquence précise. Cela signifie qu'il y a moins de pics de bruit à des

fréquences spécifiques, ce qui réduit le risque d'interférences avec d'autres circuits. Les niveaux de bruit électromagnétique global sont généralement plus faibles dans les circuits asynchrones.

Cependant, il convient de noter que la conception asynchrone présente également des défis spécifiques. Les tests et le débogage sont compliqués en raison de l'absence d'horloge, rendant le processus de débogage moins intuitif que dans les conceptions synchrones. Malgré la recherche en cours, la commercialisation de ces techniques progresse lentement. En outre, il y a un manque d'outils de CAO (conception assistée par ordinateur) adaptés à la conception asynchrone. La facilité de conception de circuits asynchrones de haute qualité dépendra de la disponibilité d'outils de CAO adaptés, de l'expertise dans ce domaine et de la demande industrielle.

## Problématique et objectifs

La conception des circuits asynchrones constitue un domaine de recherche en constante évolution, offrant de nombreuses perspectives prometteuses. Les circuits asynchrones présentent des avantages significatifs par rapport à leurs homologues synchrones, tels que des performances améliorées et une consommation d'énergie réduite. Cependant, la mise en œuvre de techniques avancées, telles que l'adaptation dynamique de tension d'alimentation (*DVS* : *Dynamic Voltage Scaling*), introduit de nouveaux défis dans la conception des circuits asynchrones.

L'implémentation de la *DVS* dans les circuits asynchrones vise à réduire davantage la consommation d'énergie en ajustant dynamiquement la tension d'alimentation du circuit en fonction de sa charge et de ses besoins en performance. Cette technique permet de réduire la consommation d'énergie en exploitant les niveaux de tension appropriés pour chaque partie du circuit. Cependant, dans un environnement asynchrone, caractérisé par l'absence d'horloge globale, l'application de la *DVS* peut s'avérer complexe. Les variations paramétriques

inhérentes aux procédés de fabrication peuvent compromettre les performances et la fiabilité du circuit lorsqu'il est soumis à une tension d'alimentation réduite. Par conséquent, il est essentiel de développer des approches de conception spécifiques pour garantir le bon fonctionnement des circuits asynchrones lors de l'application de la *DVS*.

Dans les circuits synchrones, la robustesse du fonctionnement repose souvent sur des marges de sécurité importantes pour éviter les erreurs, notamment en s'appuyant sur une horloge globale pour coordonner les opérations. Cependant, à faibles tensions, cette méthode montre ses limites, car elle peut ralentir davantage les systèmes, nécessitant des ajustements excessifs pour compenser les variations de tension.

Parallèlement à l'implémentation de la *DVS*, la prise en compte des variations paramétriques de procédés de fabrication est un autre défi majeur dans la conception des circuits asynchrones. Les variations de procédés de fabrication, telles que les variations de tension seuil, les variations de longueur du canal et les variations de la largeur d'oxyde, combinés aux variations de température peuvent entraîner des écarts significatifs par rapport aux valeurs nominales attendues des paramètres de conception. Ces variations peuvent affecter les performances du circuit, entraînant des délais de propagation non uniformes, des violations de synchronisation et des problèmes de fiabilité. Par conséquent, une analyse précise et robuste des performances des circuits asynchrones en présence de variations paramétriques est nécessaire pour garantir un fonctionnement fiable et efficace.

L'analyse statistique des délais de propagation (*SSTA - Statistical Static Timing Analysis*) est une approche puissante pour évaluer et prendre en compte les variations paramétriques de procédés de fabrication dans la conception des circuits asynchrones. Contrairement aux méthodes déterministes traditionnelles, la *SSTA* permet de modéliser les variations paramétriques comme des variables aléatoires, fournissant ainsi des estimations statistiques des performances du circuit. L'application de la *SSTA* permet de prendre en compte les incertitudes liées aux variations paramétriques dans la conception, la vérification et

l'optimisation des circuits asynchrones. Elle offre également une vision plus réaliste des performances du circuit dans des conditions réelles de fonctionnement.

Dans cette étude, nous explorons les défis spécifiques liés à la conception des circuits asynchrones dans le contexte de l'implémentation de la *DVS* et des variations paramétriques de procédés de fabrication et de température. Nous mettons en évidence l'importance d'appliquer l'analyse statistique, telle que la *SSTA*, pour évaluer et garantir les performances des circuits asynchrones dans des conditions réalistes. Nous discutons des avantages de l'application de la *SSTA*, tels que la prise en compte des variations paramétriques et la capacité d'améliorer la conception pour répondre aux contraintes de synchronisation et de performance.

### **Contributions de la thèse :**

Les travaux de thèse ont mené à 2 contributions majeures :

Contribution 1 : Un nouveau modèle de prédiction tenant en compte de nouvelles contraintes à satisfaire pour appliquer la *DVS* sur les circuits asynchrones.

Contribution 2 : Une approche d'analyse statistique des performances des circuits asynchrones tenant compte des variations paramétriques des procédés de fabrication, de la tension d'alimentation et de la température, en se basant sur un modèle de variabilité de délai pour estimer l'impact de ces variations sur les performances des circuits asynchrones.

### **Organisation de la thèse :**

La suite de cette thèse est organisée comme suit. Le chapitre 1 se concentre sur la présentation des notions de base essentielles pour comprendre le sujet abordé. Il explore tout d'abord les circuits asynchrones, en examinant leurs protocoles de communication et leurs classifications.

En deuxième partie de ce chapitre, on met l'accent sur la variabilité de procédé de fabrication et son impact sur les circuits asynchrones. Nous explorons les différentes sources de variations,

et examinons comment ces variations peuvent affecter les performances des circuits. Nous abordons également les techniques de modélisation des paramètres de variabilité de procédé pour une meilleure compréhension et une conception plus robuste des circuits asynchrones.

Nous étudions aussi l'analyse temporelle des circuits asynchrones. Nous examinons l'analyse temporelle statique, qui permet de déterminer les délais de propagation dans les pires cas d'opération, ainsi que l'analyse temporelle statistique, qui prend en compte les variations de délai pour une évaluation plus précise des performances des circuits.

Finalement, la dernière partie du chapitre 1 se concentre sur les techniques de réduction de la consommation de puissance dans les circuits asynchrones. Nous explorons en détail l'adaptation dynamique de la tension d'alimentation (*Dynamic Voltage Scaling*), qui permet d'ajuster la tension d'alimentation en fonction des besoins de performance, contribuant ainsi à une consommation d'énergie réduite.

Le chapitre 2 présente les travaux connexes et les recherches existantes dans le domaine des circuits asynchrones. Nous explorons les contributions précédentes, les résultats obtenus et les tendances actuelles de recherche. Cette analyse nous permet de situer notre recherche dans le contexte global et d'identifier les lacunes et les opportunités pour des avancées futures.

Le troisième chapitre de cette thèse se concentre sur le développement d'un modèle de prédiction des performances du type de circuit asynchrone *SRBDHF* (*Single-Rail Bundled-Data Handshake-Free*). Ce modèle, offre une approche novatrice pour évaluer les performances de ce type spécifique de circuit asynchrone.

Nous présentons en détail le modèle de prédiction proposé pour le circuit *SRBDHF*. Nous explorons les différents aspects du modèle, en commençant par la propagation de l'impulsion à travers les différents éléments du circuit. Nous examinons également les marges de pré-positionnement (*setup*) et de maintien (*hold*), qui sont des paramètres critiques pour assurer le

bon fonctionnement du circuit. De plus, nous analysons la sensibilité de la logique utilisée dans le circuit *SRBDHF* et son impact sur les performances globales.

Nous présentons aussi l'application du modèle de prédiction dans le processus de vérification des circuits *SRBDHF*. Nous décrivons la manière dont le modèle de prédiction est utilisé, nous expliquons comment les résultats du modèle sont utilisés pour guider les choix de conception, les optimisations et les ajustements nécessaires pour atteindre les performances souhaitées.

Les résultats obtenus à partir de l'application du modèle de prédiction dans les circuits *SRBDHF* seront analysés. Nous discutons des performances mesurées par rapport aux performances prédictes par le modèle. Enfin, nous tirons des conclusions sur l'efficacité et la pertinence du modèle de prédiction des performances du circuit *SRBDHF*, ainsi que sur les perspectives de recherche future dans ce domaine.

Le quatrième chapitre de cette thèse se concentre sur l'analyse statistique des performances des circuits asynchrones. Ce chapitre propose une approche statistique pour évaluer les performances de ces circuits. Nous détaillons le flot d'analyse statistique proposé. Nous commençons par présenter le modèle de variabilité, qui tient compte des variations inhérentes aux procédés de fabrication. Ensuite, nous abordons la contrainte statistique de la largeur de l'impulsion, qui joue un rôle crucial dans la synchronisation des signaux dans les circuits asynchrones de type *SRBDHF*. Enfin, nous explorons la contrainte statistique temporelle, qui permet de vérifier les limites de temps imposées par le fonctionnement du circuit.

Nous présentons ensuite les résultats obtenus à partir de l'analyse statistique des performances des circuits asynchrones. Nous discutons des mesures statistiques utilisées pour évaluer les performances, telles que les marges de variation et les probabilités de dépassement des contraintes. Nous analysons les résultats obtenus à partir de différentes simulations et nous en tirons des conclusions pertinentes sur l'efficacité de l'approche statistique proposée.

Le dernier chapitre est dédié à la conclusion et aux perspectives de recherche futures. Dans ce chapitre, nous procédons à une synthèse des résultats obtenus tout au long de cette thèse. Nous mettons en évidence les contributions et les avancées significatives réalisées dans le domaine des circuits asynchrones. Nous récapitulons les modèles, les méthodes et les techniques développés, ainsi que les résultats expérimentaux obtenus. Nous soulignons également les principales conclusions tirées de ces résultats et leur impact potentiel sur le domaine des circuits asynchrones.

Finalement, nous proposons des pistes de recherche prometteuses pour l'avenir. Nous identifions les domaines qui nécessitent davantage d'investigations et d'approfondissements. Cela peut inclure l'exploration de nouvelles modélisations pour prendre en compte des facteurs spécifiques, l'amélioration d'analyse, ainsi que l'élargissement de l'étude à d'autres types de circuits asynchrones.

# CHAPITRE 1

## NOTIONS DE BASE

### 1.1 Introduction

Dans cette section de notre thèse, nous nous plongeons au cœur de la revue de littérature, explorant un éventail de sujets cruciaux pour notre recherche sur les circuits asynchrones et la réduction de la consommation énergétique. Nous débutons en examinant les caractéristiques essentielles des circuits asynchrones, ainsi que leur classification. En parallèle, nous étudions les protocoles de communication et les types de codage associés, avant de nous pencher sur la variabilité des procédés de fabrication, comprenant les variations systématiques et non systématiques qui influencent la performance des circuits asynchrones. Ensuite, nous explorons les techniques de réduction de la consommation énergétique, en mettant l'accent sur la technique *DVS (Dynamic Voltage Scaling)*. Notre investigation se poursuit en explorant les méthodes d'analyse temporelle des circuits, notamment l'analyse statique, statistique et le rendement temporel. Enfin, nous concluons cette section en présentant quelques notions de base statistiques essentielles dans le développement de la suite de nos travaux proposés dans cette thèse.

### 1.2 Les circuits asynchrones

Un circuit asynchrone est un circuit électronique dans lequel les composants ne sont pas strictement synchronisés par une horloge centrale, ce qui signifie que leur fonctionnement peut être déclenché par des signaux ou des événements spécifiques. Contrairement aux circuits synchrones qui se basent sur un signal d'horloge pour coordonner les opérations, les circuits asynchrones réagissent aux changements des signaux locaux en temps réel. Ils sont conçus pour effectuer des opérations au fur et à mesure que les données sont disponibles, sans attendre un signal d'horloge global (Srivastava, 2022).

### 1.2.1 Protocole de communications

La communication entre deux blocs d'un circuit asynchrone se fait dans la majorité des cas à travers des protocoles de communication pour synchroniser l'émission et la réception des données. Ces protocoles sont de type poignée de main « *handshaking protocol* » (chaque activité de l'émetteur est validée par le récepteur et vice versa). Ce protocole permet aux différentes parties du circuit de s'envoyer des signaux de demande (*Req*) et d'accusé de réception (*Ack*) pour synchroniser leurs actions (Spars & Furber, 2002). Lorsqu'une partie du circuit souhaite communiquer avec une autre partie, elle envoie un signal de demande. Lorsque la partie cible est prête à recevoir les données, elle envoie un signal d'accusé de réception, permettant ainsi le transfert des données. Ce protocole de *Handshake* permet une coordination efficace entre les parties du circuit sans nécessiter une horloge globale.

Ces protocoles sont gérés dans chacun des blocs asynchrones par des contrôleurs. Deux principales classes de protocoles sont utilisées : les protocoles deux phases et les protocoles quatre phases.

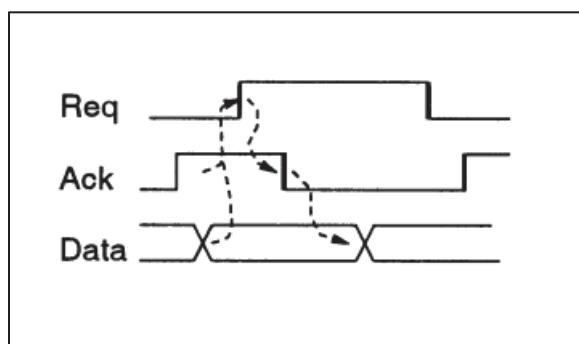

Pour les protocoles deux phases, les données s'enchaînent et le signal d'acquittement changent d'état pour autoriser le passage à la donnée suivante (Figure 1.1).

Figure 1.1 Protocole deux phases

Tirée de Yahya (2009, p. 6)

Le fonctionnement d'un protocole en deux phases, illustré à la figure 1.2, se divise en deux étapes distinctes, comme l'indique son nom :

Phase 1 : Dans cette phase, l'émetteur envoie une transition sur le fil de demande (Req) pour signaler qu'elle a de nouvelles données à transmettre. Cette transition indique au récepteur qu'il doit se préparer à recevoir ces données.

Phase 2 : Dans cette phase, une fois que le récepteur a lu les données, il envoie une transition sur le fil d'accusé de réception (Ack) pour confirmer qu'il a reçu les données correctement. Après cette confirmation, la source sait que la transmission a été réussie et peut envoyer d'autres données si nécessaire.

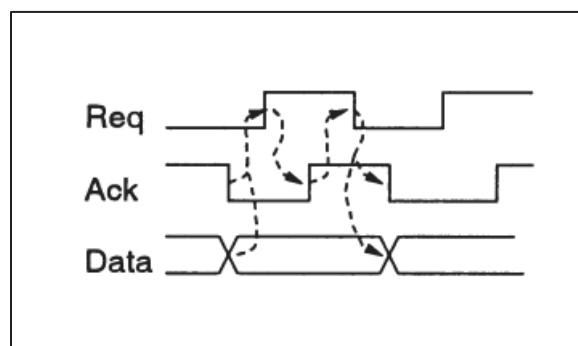

Pour les protocoles quatre phases, l'enchainement de données et l'acquittement sont séparés par un état de repos (Figure 1.2).

Figure 1.2 Protocole quatre phases

Tirée de Yahya (2009, p. 6)

Lors de la première phase, l'émetteur envoie la demande, activant le récepteur en mettant le signal Req à 1. À la deuxième phase, le récepteur lit les données et envoie l'accusé de réception en mettant le signal Ack à 1. À la troisième phase l'émetteur désactive la demande en mettant Req à 0. Et finalement, à la quatrième phase, le récepteur finalise l'échange et remet le signal Ack à 0.

### 1.2.2 Type de codage

Les circuits asynchrones utilisent différents types de codage pour représenter et transmettre les données. Deux de ces méthodes sont souvent employées : le codage *Dual-Rail* et le codage *Single-Rail* (Myers, 2001).

- Codage *Dual-Rail* (Double Fil) : Dans ce mode de codage, chaque bit de donnée est représenté par deux fils de signal. Les bits sont encodés en utilisant une combinaison de transitions sur les fils. Par exemple, un "0" pourrait être représenté par une transition sur un fil et l'absence de transition sur l'autre fil. Le "1" serait alors l'inverse : absence de transition sur le premier fil et transition sur le second fil.

- Codage *Single-Rail* (Simple Fil) : Contrairement au codage *Dual-Rail*, le codage *Single-Rail* utilise un seul fil de signal pour représenter chaque bit. Un "0" pourrait être représenté par une transition ou un niveau bas, tandis qu'un "1" pourrait être représenté par l'absence de transition ou un niveau élevé.

### 1.2.3 Classification des circuits asynchrones

Les circuits asynchrones sont généralement regroupés en fonction de l'hypothèse temporelle. Les circuits asynchrones peuvent être classés comme étant auto-rythmés (*self-timed*), indépendants de la vitesse (*SI* pour *Speed-Independent*) et insensibles aux délais (*DI* pour *Delay-Insensitive*) (Myers, 2001) (Hauck, 1995) (Fiorentino, 2020; Spars & Furber, 2002).

Un circuit *speed-independent* (*SI*) est conçu en tenant compte de l'idée que les délais à l'intérieur des portes logiques sont constants et positifs, et que les fils de connexion n'ont aucun délai. Toutefois, cette supposition se révèle non réaliste dans le contexte des technologies actuelles de semi-conducteurs.

Un circuit *delay-insensitive* (*DI*) assure son fonctionnement de manière correcte même lorsque les délais, bien que positifs et bornés, restent inconnus à la fois sur les fils de connexion et à

l'intérieur des portes logiques. Ces circuits se distinguent par leur grande robustesse, leur capacité à résister aux variations de délai sans compromettre leur bon fonctionnement. Malheureusement, très peu de circuits font partie de cette classe, seuls les circuits composés d'éléments C et d'inverseurs peuvent être insensibles aux délais (pipeline de *Muller*).

Pour pallier à cette limitation, une sous-classe de circuits *DI* a été proposée : les circuits *quasi-delay-insensitive (QDI)*. Cette sous-classe couvre les circuits qui sont *DI*, à l'exception de certaines déviations de fil où les transitions de signal se produisent simultanément à tous les points d'extrémité, qualifiées d'*isochroniques*.

En ce qui concerne les circuits « *self-timed* », les propriétés d'indépendance de la vitesse et d'insensibilité aux délais décrites ci-dessus sont bien définies d'un point de vue mathématique pour les portes logiques et les fils de connexion. Les circuits qui dépendent de considérations de délai plus complexes ou spécifiques à l'ingénierie sont simplement appelés « *self-timed* ». Dans le cadre d'un projet parrainé par la société Octasic, nous avons choisi de nous concentrer spécifiquement sur deux classes de circuits asynchrones qui font partie de la catégorie (*self-timed*) : les Circuits (*CE* : *Click-Element*) et les Circuits (*SRBDHF* : *Single-Rail Bundled-Data Handshake-Free*).

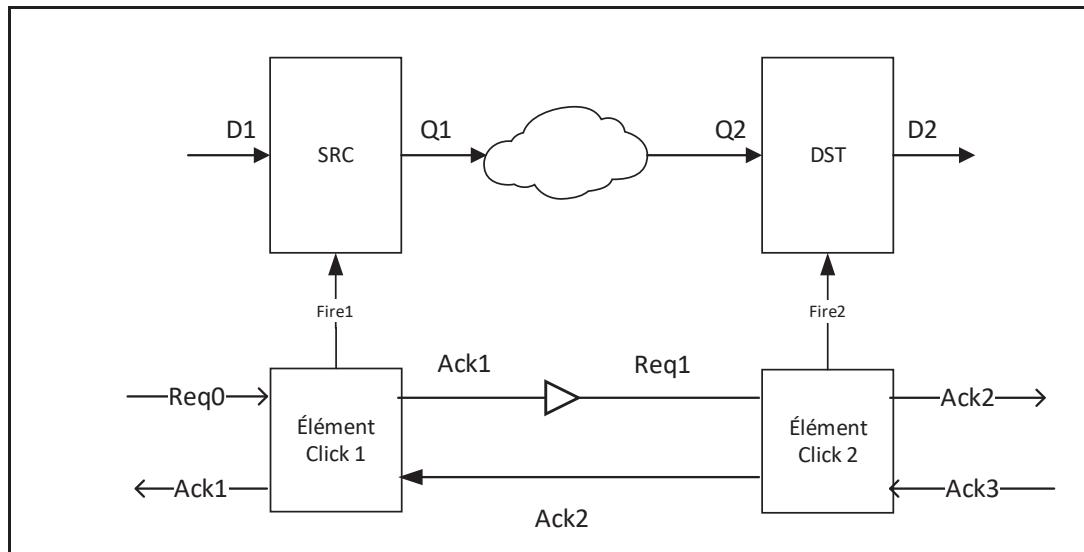

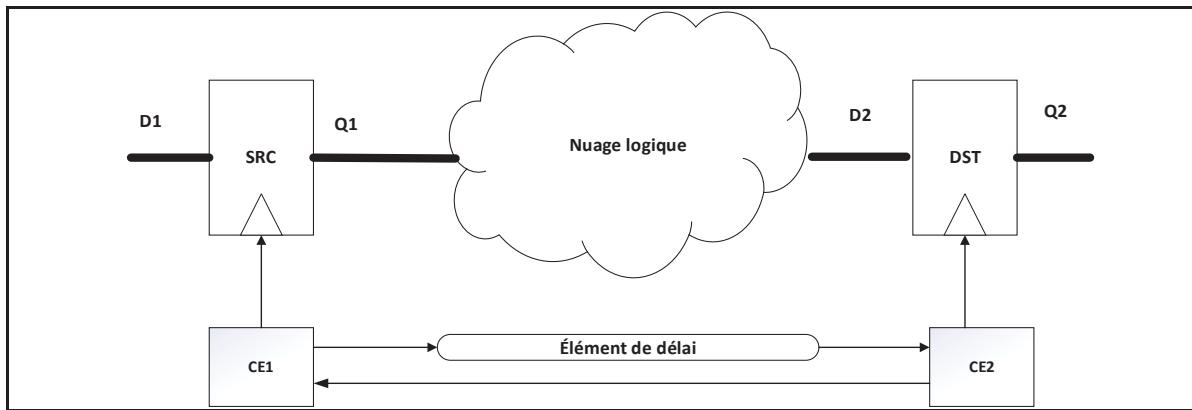

- **Circuit *CE***

Le concept du modèle asynchrone *CE* a été présenté en 2009 au sein d'une approche de conception asynchrone novatrice (A. Peeters, Te Beest, De Wit, & Mallon, 2010) (W. C. M. A. M. G. Peeters, 2009-05-28). Ce modèle utilise le protocole de communication en deux phases, utilisant uniquement des cellules standards. Le modèle *CE* utilise des bascules (*flip flop*) déclenchées par front montant pour le contrôle et les données. La Figure 1.3 montre une implémentation basique du circuit *CE* (Fiorentino, 2020). Il est composé d'un nuage logique combinatoire, de registres source et destination, ainsi que de deux blocs de signaux de protocole de communication appelés "éléments click". Chaque élément click, détaillé à la Figure 1.4, comprend une bascule de contrôle D et un circuit de conversion de phase. Le circuit

de conversion de phase est constitué de deux portes "ET" et une porte "OU". Entre les deux blocs d'éléments click, un élément de délai est intégré pour assurer une synchronisation adéquate entre les étages.

Lorsqu'une nouvelle donnée est prête, une transition du signal "Req0" dans "click\_element1" est utilisée pour générer une horloge locale "Fire1". La transition du signal "Ack1" peut être transmise à "Req1" dans "click\_element2", devenant ainsi le signal de requête d'entrée de l'étage suivante. Le signal "Fire1" est utilisé pour capturer les données et déclencher "click\_element2" afin de générer "Fire2". Ensuite, une transition du signal d'accusé de réception "Ack2" dans "click\_element2" indique la fin de cette action. Les transitions montantes et descendantes du signal de requête indiquent la validité des données, tandis que les transitions montantes et descendantes du signal d'acquittement indiquent que les données ont été capturées. Notons que la largeur d'impulsion des signaux Fire1 et Fire2 doit être supérieure à la largeur minimale définie dans la bibliothèque de la technologie utilisée pour garantir un fonctionnement correct (Kuentzer, Herrera, Schrape, Beerel, & Krstic, 2020).

Figure 1.3 Schéma bloc du pipeline *CE*

Figure 1.4 Configuration détaillée d'architecture du pipeline CE

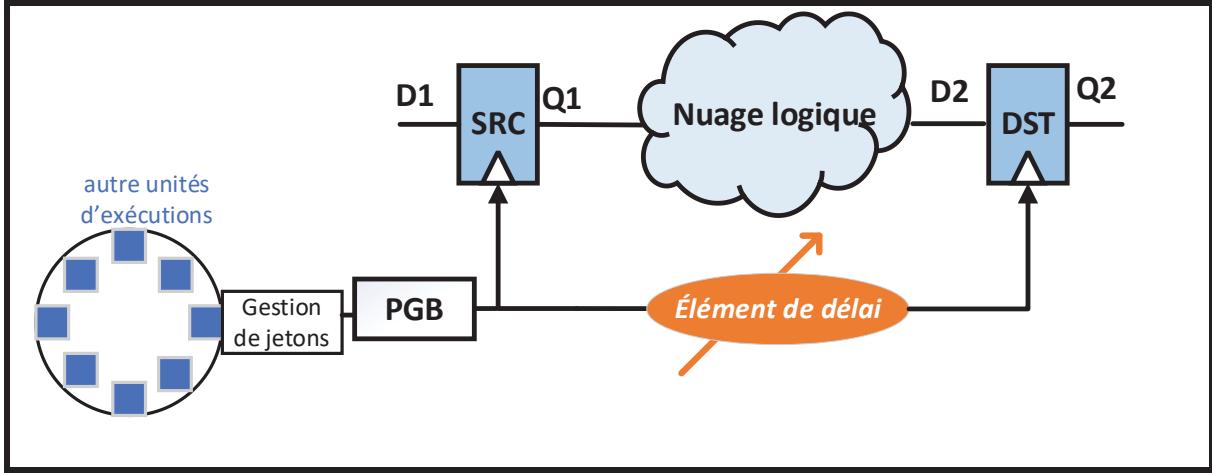

- **Circuit SRBDHF**

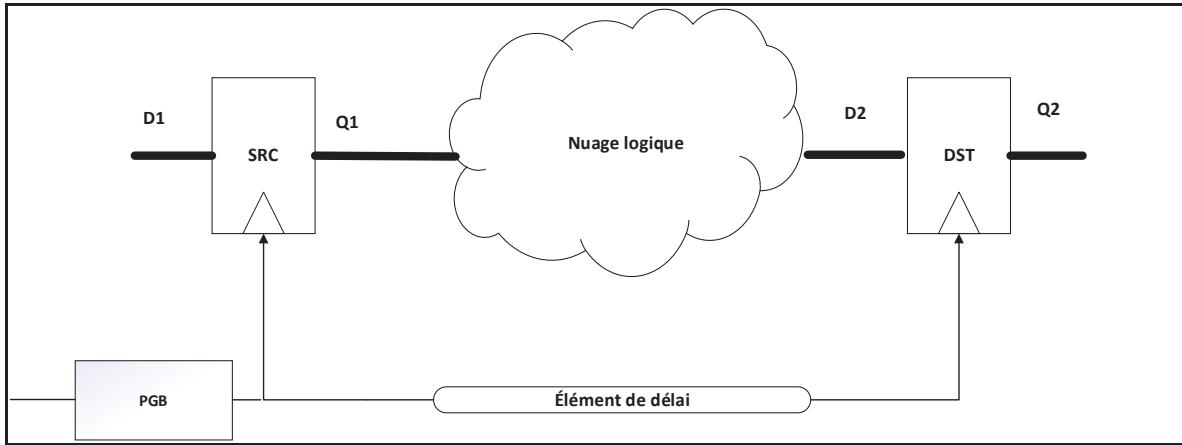

Le type de circuits ciblé appartient à la classe des circuits asynchrones à données groupées (*Bundled Data*) (Laurence, 2012) (Fiorentino, 2020), avec la particularité de ne pas utiliser de mécanisme de handshake. Ce style de conception particulier repose sur l'utilisation d'un certain nombre d'unités d'exécution (*EU*) qui communiquent dans un anneau séquentiel. Elle est composée d'un nuage de logique combinatoire, d'une ligne à délai variable (bloc configurable ajusté à l'opération effectuée lors d'un cycle donné), ainsi que de registres source (*SRC*) et destination (*DST*). Le registre *SRC* est activé par le front montant de l'impulsion émise par le bloc générateur d'impulsions, lançant les données vers le nuage combinatoire. Les données sortantes du nuage combinatoire sont capturées par le registre *DST*, qui est activé par le front montant d'une version retardée de l'impulsion.

Figure 1.5 : Architecture de base d'une unité d'exécution (*EU*) des circuits *SRBDHF*

### 1.3 Variabilité de procédés de fabrication

La variabilité de procédé de fabrication se réfère à la fluctuation naturelle des paramètres lors de la fabrication de composants électroniques tels que des puces de silicium. Lorsque des circuits électroniques sont fabriqués en masse, des variations involontaires peuvent survenir dans les propriétés physiques et électriques des composants individuels. Ces variations peuvent être causées par divers facteurs, notamment les fluctuations dans le procédé de fabrication, la qualité des matériaux utilisés et les conditions environnementales (Champac & Gervacio, 2018). Cette variabilité peut avoir un impact significatif sur les performances des circuits électroniques. Les variations de paramètres tels que les dimensions des transistors, les tensions de seuil, les capacités interconnectées et les vitesses de commutation peuvent entraîner des différences dans les performances des composants individuels, même s'ils sont censés être identiques.

Dans le contexte des circuits asynchrones et de la conception de systèmes électroniques, la variabilité de procédé de fabrication peut causer des problèmes tels que des délais inattendus dans les signaux et des défaillances de communication entre les composants (J. Liu, Nowick,

& Seok, 2013). Les concepteurs de circuits doivent prendre en compte cette variabilité pour garantir que les circuits fonctionnent correctement dans une plage de conditions différentes.

### 1.3.1 Sources de variation de procédés de fabrication

Les caractéristiques physiques et électriques des dispositifs définissent les caractéristiques de performance. La longueur du canal ( $L$ ), la largeur du canal ( $W$ ), l'épaisseur de l'oxyde ( $Tox$ ) et la tension de seuil ( $Vth$ ) sont les principaux paramètres qui définissent le comportement de performance des dispositifs MOSFET. Par conséquent, les variations des valeurs nominales de ces paramètres dues au procédé de fabrication modifient les avantages de performance attendus (Orshansky, Nassif, & Boning, 2007), (Wirnshofer, 2013), (Dietrich & Haase, 2011). La longueur ( $L$ ) et la largeur ( $W$ ) du canal sont des paramètres physiques qui déterminent les dimensions d'un transistor MOSFET et sont connus sous le nom de dimensions critiques ( $CD$ ). L'isolant qui sépare l'électrode de la grille du substrat a une épaisseur définie ( $Tox$ ); ce paramètre physique joue un rôle critique dans le comportement du dispositif. La tension de seuil ( $Vth$ ) est la tension minimale requise à la grille du transistor pour le mettre en marche. Les principales sources de variation de ces paramètres sont exposées ci-dessous.

- **La rugosité des bords de ligne :** (*LER : Line Edge Roughness*) est la variation aléatoire des bords en polysilicium le long de leur largeur. Étant donné que les systèmes de photolithographie utilisent des sources lumineuses avec des longueurs d'onde supérieures à la taille minimale des caractéristiques (dimension critique), le procédé lié à la lithographie entraîne une plus grande variation de la porte en raison du *LER* (C. A. Mack, 2006), (Bai et al., 2004), (C. Mack, 2007). Le *LER* est devenu une source importante de variation de la longueur de canal, et il devrait continuer à augmenter dans les technologies à venir (Asenov, Kaya, & Brown, 2003). La Figure 1.6 illustre le *LER* sur une porte en polysilicium d'un transistor. On peut observer que la longueur de canal effective fluctue le long de la largeur du canal.

Figure 1.6 Rugosité des bords de ligne

Tirée de Champac (2018, p 51)

- **L'effet de proximité optique :** (*OPE; Optical proximity effect*) est la variation de la taille et de la forme d'une caractéristique en fonction de la proximité d'autres caractéristiques voisines (C. A. Mack, 1993), (C. A. Mack, 1996), (C. Mack, 2007). L'*OPE* se produit pendant le procédé de photolithographie en raison de la diffraction de la lumière par les structures voisines (Figure 1.7). En raison de cela, la taille et la forme d'une ligne isolée seraient différentes de la taille et de la forme d'une ligne dans un réseau.

Figure 1.7 Effet de proximité optique

Tirée de Champac (2018, p 52)

- **La fluctuation aléatoire de dopant :** (*RDF : Random dopant fluctuations*) La région de canal du transistor est dopée avec des atomes d'un matériau différent du substrat pour contrôler et déterminer la tension de seuil. Ce procédé est réalisé par implantation. La

manière dont ce procédé se développe fait que la quantité et l'emplacement des atomes implantés dans le canal du transistor sont complètement aléatoires ; d'où le terme Fluctuation Aléatoire de Dopant (*RDF*) (Veendrick, 2017), (Takeuchi, Nishida, & Hiramoto, 2009).

### 1.3.2 Types de variation de procédés de fabrication

D'un point de vue global, les variations peuvent être générées en raison d'un comportement systématique ou non systématique. Les variations non systématiques peuvent être générées à l'échelle inter-puces et intra-puces. De plus, la variation intra-puce peut être produite en raison d'un comportement purement aléatoire ou corrélé.

Figure 1.8 Classification des variations de procédé en fonction de leur comportement

Tirée de Champac (2018, p 56)

La Figure 1.8 illustre la classification des variations de procédé en fonction de leur comportement.

**Variations systématiques :** Les variations systématiques (déterministes) sont celles qui sont produites de manière systématique par les mêmes étapes du procédé de fabrication (Kishore, Patnala, Tigadi, & Jamshed, 2020). Dans le développement des dispositifs et des interconnexions, plusieurs étapes du procédé peuvent causer des variations systématiques ; cependant, la plus importante est celle de la photolithographie. Les effets de proximité optique dans les motifs voisins sont la source principale de ces variations. En raison de la nature des variations systématiques, la quantité de variation introduite est approximativement la même. Pour cette raison, elle peut être prévisible et corrigible à l'aide de techniques d'amélioration de la résolution telles que l'*OPC* (Correction de la Proximité Optique). Il peut rester quelques variations après l'*OPC*.

**Variations non systématiques:** Les variations non systématiques (aléatoires) sont celles qui sont produites de manière aléatoire à partir d'un grand nombre d'étapes de procédé et d'équipements utilisés dans le flot de fabrication (Kishore et al., 2020). Dans le développement des dispositifs et des interconnexions, de nombreuses étapes peuvent causer des variations aléatoires. En raison de leur nature arbitraire, les variations aléatoires sont modélisées statistiquement et sont les plus importantes d'un point de vue du concepteur. Ce type de variations peut être divisé en fonction de leur comportement en variations inter-dé (globales) et intra-dé (locales). Les deux types de variations sont décrits ci-dessous.

- Variations Inter-Dé : Les variations inter-dé (*D2D :Die-to-Die*) (ou variations globales ou dé-à-dé) affectent tous les dispositifs fabriqués d'une puce de la même manière (Zuchowski, Habitz, Hayes, & Oppold, 2004). La valeur d'un paramètre dans tous les dispositifs d'une puce a la même valeur en raison des variations *D2D*. Les variations inter-die se produisent à différents niveaux du procédé de fabrication. Les variations dé-à-dé peuvent se produire pendant l'exposition d'un masque au suivant car le scanner doit être aligné sur le procédé précédemment réalisé. Les variations de gaufre à gaufre peuvent se produire lors du traitement d'une tranche à une autre en raison de la position inexacte des tranches dans l'équipement. Les variations de lot à lot peuvent se produire lors du traitement d'un lot de tranches à un autre en raison des changements dans le fonctionnement de

l'équipement. Les variations d'usine à usine peuvent se produire en raison des conditions de fabrication uniques de chaque usine.

- Variations Intra-Dé : Les variations intra-dé (*WID* : *Within Die*) (ou variations locales ou à l'intérieur de la puce) affectent chaque dispositif fabriqué dans la même puce de manière différente (Zuchowski et al., 2004). Les variations *WID* font que les tailles de caractéristiques de certains dispositifs dans une puce ont des dimensions plus petites que nominales, tandis que d'autres dispositifs de la même puce ont des dimensions plus grandes que nominales. En raison de cela, les dispositifs conçus avec une taille et une forme égale et fabriqués dans la même puce donnent lieu à des propriétés intrinsèques différentes les unes des autres et par conséquent avec des performances différentes. Aux technologies sub-nanométriques, la variation intra-die représente la plus grande partie de la variation totale.

- Les variations purement aléatoires, sont des variations des dispositifs sans corrélation spatiale ni dépendance entre elles. Elles sont principalement causées par les fluctuations aléatoires des dopants (*RDF*) et les irrégularités des bords de ligne (*LER*)

- La variation corrélée spatialement, ou variation dépendante de la position, signifie que la déviation d'un paramètre dans un dispositif est liée aux déviations des autres dispositifs proches sur la puce. Plus les dispositifs sont proches, plus leur variation est similaire. Les étapes des procédés de fabrication comme la photolithographie et le polissage influencent cette corrélation.

### 1.3.3 Modélisation des variations de procédés de fabrication

Des modèles statistiques de dispositifs décrivant l'effet des variations de procédé sont nécessaires pour analyser les performances des circuits. Ces modèles permettent de représenter le comportement des paramètres variant avec le procédé et peuvent être utilisés pour comprendre le comportement des circuits avec des outils de CAO. Une manière de quantifier la variation de procédé d'un paramètre consiste à utiliser la somme linéaire des différentes

composantes de variation. Par exemple, soit  $X$  une variable aléatoire normale représentant un paramètre de procédé. Le modèle tenant compte des variations inter-dé et intra-dé peut être écrit comme suit (Agarwal, Blaauw, & Zolotov, 2003; Agrawal, 2003):

$$X = X_0 + X_{D2D} + X_{WID} \quad (1.1)$$

Où  $X_0$  représente la valeur nominale du paramètre.  $X_{D2D}$  et  $X_{WID}$  sont des variables normales représentant les variations inter-dé et intra-dé, respectivement.

#### 1.4 Délai de propagation d'une porte logique

L'estimation du délai de propagation dans les portes *CMOS* (*Complementary Metal-Oxide-Semiconductor*) est un aspect crucial de la conception de circuits numériques. Le délai d'une porte *CMOS* dépend principalement de facteurs tels que la capacité d'entrée, l'effort logique, la capacité parasite et la technologie utilisée dans le processus de fabrication. Voici quelques considérations clés pour estimer le délai dans les portes *CMOS*:

- **Effort logique :** L'effort logique est une mesure utilisée pour estimer le délai relatif d'une porte. Il est calculé comme le rapport de la capacité d'entrée à la capacité équivalente d'un inverseur qui alimente la même charge. Cette mesure aide à comparer le délai relatif de différentes configurations de portes.

- **Capacité d'entrée :** La capacité d'entrée d'une porte *CMOS* est déterminée par le nombre et la taille des transistors et des interconnexions. Une capacité d'entrée plus importante entraîne un délai plus long.

- **Capacité parasite :** Outre la capacité intrinsèque, la capacité parasite des interconnexions et du routage peut s'ajouter à la capacité d'entrée de la porte, augmentant ainsi le délai.

- **Nœud technologique** : Le délai des portes *CMOS* est affecté par le nœud technologique de fabrication des semi-conducteurs. Les nœuds avancés offrent généralement des vitesses de porte plus élevées en raison de la réduction de la taille des composants.

- **Charge de porte** : La charge capacitive que la porte *CMOS* pilote joue également un rôle crucial dans l'estimation du délai. Des charges plus importantes entraînent des délais plus longs.

- **Dimensionnement des transistors** : Les tailles des transistors NMOS et PMOS dans une porte *CMOS* affectent ses performances. Un dimensionnement approprié des transistors peut minimiser le délai.

Par exemple dans (Cao & Clark, 2005), le délai de propagation d'une porte logique est donné par :

$$T_d = \frac{K V_{dd} \left\{ 1 + \ln \left[ \left( \frac{V_{dd} - V_{th}}{E_{sat} L} \right) \right] \right\}}{\left\{ \ln \left[ 1 + \exp \left( \frac{V_{dd} - V_{th}}{2S} \right) \right] \right\}} \quad (1.2)$$

Avec :

$V_{dd}$  : tension d'alimentation de la porte logique.

$V_{th}$  : tension de seuil.

$S$  : paramètre de la technologie (sub-threshold swing).

$L$  : longueur de canal.

$E_{sat}$  : vitesse de saturation des porteurs de charge.

$K$ : coefficient de proportionnalité qui peut être extrait des données de simulation sous différentes conditions de  $V_{DD}$ ,  $L$ , et capacité de charge.

Pour estimer le délai d'une porte *CMOS* spécifique, vous pouvez utiliser des modèles de délai fournis par les fonderies de semi-conducteurs ou des outils *EDA* (*Electronic Design Automation*) tels que *Cadence* ou *Synopsys*. Ces outils utilisent divers algorithmes et données pour fournir des estimations précises du délai en fonction des paramètres de la porte et des informations technologiques.

## 1.5 Techniques de réduction de la consommation énergétique

Dans le domaine de la conception électronique moderne, l'efficacité énergétique est devenue une préoccupation primordiale. Les circuits électroniques, qu'ils soient synchrones ou asynchrones, sont confrontés à la nécessité croissante de réduire leur consommation de puissance pour répondre aux exigences du marché (Engels, 2022). Dans ce contexte, les techniques de réduction de la consommation de puissance dans les circuits asynchrones ont gagné en importance, offrant des solutions pour relever ce défi majeur (Tan, Li, & Wang, 2014).

### 1.5.1 Dynamic Voltage Scaling

L'une des approches potentielles pour réduire la consommation d'énergie dans les circuits asynchrones est la technique d'ajustement dynamique de la tension d'alimentation également connue sous le nom de *Dynamic Voltage Scaling (DVS)*, (K.-H. Chen, 2016). La *DVS* repose sur le principe de varier la tension d'alimentation appliquée aux circuits en fonction des besoins de performances à un moment donné. Cette technique permet d'adapter la tension d'alimentation aux exigences de traitement, réduisant ainsi la puissance dissipée et améliorant l'efficacité énergétique.

Figure 1.9 Vitesse de traitement d'une tache lors de l'application de la *DVS*

Lorsque des performances élevées sont nécessaires, la tension d'alimentation est augmentée, ce qui permet d'atteindre des vitesses de fonctionnement plus élevées. En revanche, lorsque des performances plus modestes sont suffisantes, la tension d'alimentation est réduite, permettant de diminuer la consommation d'énergie tout en maintenant un fonctionnement stable.

Par exemple, dans la Figure 1.10, lorsque la tension d'alimentation est réduite à 50 % ou 70 % de sa valeur initiale, le gain en termes de consommation de puissance est significatif. Cependant, cette réduction de tension s'accompagne d'une augmentation considérable du temps nécessaire pour effectuer le traitement, comparé à une situation où la tension est maintenue à sa valeur nominale, ceci est acceptable si la charge de travail est inférieure à la capacité de traitement du processeur, ce qui se traduit par des temps morts.

## 1.6 Analyse temporelle de circuit

L'analyse temporelle des circuits est une méthode cruciale dans la conception et la vérification des circuits électroniques. Elle vise à évaluer comment les signaux se propagent à travers le circuit en termes de délais et de synchronisation. Cette analyse permet de s'assurer que les signaux arrivent aux bons moments, évitant ainsi les problèmes de synchronisation qui pourraient conduire à des erreurs de fonctionnement (Sapatnekar, 2004). L'analyse temporelle consiste à calculer les délais de propagation des signaux le long des différents chemins du

circuit. Ces délais dépendent des caractéristiques des composants tels que les transistors et les interconnexions, ainsi que des conditions environnementales comme la tension d'alimentation et la température. L'objectif est de garantir que les signaux respectent les contraintes de synchronisation nécessaires pour que le circuit fonctionne correctement. Deux principales approches d'analyse temporelle sont utilisées : l'analyse statique et l'analyse statistique.

### 1.6.1 Analyse statique

L'analyse temporelle statique des circuits repose sur la modélisation des délais de propagation des signaux à travers les différents composants d'un circuit électronique. Cette modélisation permet de prédire le temps nécessaire pour qu'un signal atteigne un point spécifique du circuit à partir d'un autre point (Bhasker & Chadha, 2009). Voici les principaux éléments sur lesquels repose cette analyse :

- **Modèles de délai :** Les modèles de délai décrivent comment les signaux se propagent à travers les portes logiques, les interconnexions et les autres composants du circuit. Ces modèles sont basés sur des caractéristiques physiques des composants, telles que les capacités de charge, les transistors et les résistances.

- **Chemin critique :** L'analyse temporelle statique identifie les chemins critiques dans le circuit, c'est-à-dire les chemins où les signaux prennent le plus de temps pour se propager. Ces chemins ont un impact majeur sur les performances globales du circuit et sont ceux qui limitent la vitesse de fonctionnement.

- **Contraintes temporelles :** Les concepteurs définissent des contraintes temporelles pour garantir que les signaux atteignent leurs destinations dans les délais spécifiés. Ces contraintes incluent les délais maximaux et minimaux pour les signaux d'entrée, de sortie et internes.

- **Calcul des délais :** À l'aide des modèles de délai et des chemins critiques, l'analyse temporelle statique calcule les temps de propagation des signaux le long de ces chemins. Ces calculs tiennent compte des caractéristiques des composants, des interconnexions et des conditions de fonctionnement.

- **Vérification des contraintes :** Une fois les délais calculés, l'analyse compare ces délais aux contraintes temporelles. Si un délai ne respecte pas les limites spécifiées, cela indique une violation de contrainte.

- **Optimisation :** Si des violations de contraintes sont détectées, les concepteurs peuvent corriger le circuit en apportant des ajustements tels que le redimensionnement des composants, ou l'ajout de tampons pour améliorer les performances temporelles.

### 1.6.2 Analyse statistique

Les variations inévitables des procédés de fabrication actuels ont entraîné d'importantes fluctuations de performances dans la conception des circuits à l'échelle nanométrique. À mesure que les technologies se miniaturisent, les écarts dans les dimensions des transistors et autres paramètres augmentent, affectant significativement les performances des circuits (Nassif, 2001). L'analyse statistique, également connue sous le nom de *SSTA* (Statistical Static Timing Analysis), permet non seulement d'évaluer les délais moyens, mais aussi de modéliser leur distribution statistique, ce qui améliore la précision et réduit les marges de sécurité excessives. Plusieurs recherches ont exploré cette approche ((H. Chang & Sapatnekar, 2003), (Devgan & Kashyap, 2003), (Agarwal et al., 2003), (Viswesvariah, Ravindran, Kalafala, Walker, & Narayan, 2004), (Zhan et al., 2005), (Feng, Li, & Zhan, 2007)).

La *SSTA* consiste en une modélisation statistique de la variabilité du délai et de ses effets sur les performances du circuit. Voici comment cela fonctionne :