Conception, fabrication et caractérisation d'une puce CMOS

pour l'alimentation et le diagnostic d'un réseau configurable de

commutateurs MEMS électrothermiques

par

Allan RIBOULLET

MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAÎTRISE

AVEC MÉMOIRE EN GÉNIE ÉLECTRIQUE

M. Sc. A.

MONTRÉAL, LE 22 JANVIER 2025

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

Allan Riboulet, 2025

Cette licence Creative Commons signifie qu'il est permis de diffuser, d'imprimer ou de sauvegarder sur un autre support une partie ou la totalité de cette oeuvre à condition de mentionner l'auteur, que ces utilisations soient faites à des fins non commerciales et que le contenu de l'oeuvre n'ait pas été modifié.

**PRÉSENTATION DU JURY**

**CE MÉMOIRE A ÉTÉ ÉVALUÉ**

**PAR UN JURY COMPOSÉ DE:**

M. Frédéric Nabki, directeur de mémoire

Département de génie électrique à l'École de technologie supérieure

M. Glenn Cowan, codirecteur

Electrical and Computer Engineering at Concordia University

M. Michaël Ménard, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Richard Al Hadi, membre du jury

Département de génie électrique à l'École de technologie supérieure

**IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC**

**LE 17 DÉCEMBRE 2024**

**À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE**

## AVANT-PROPOS

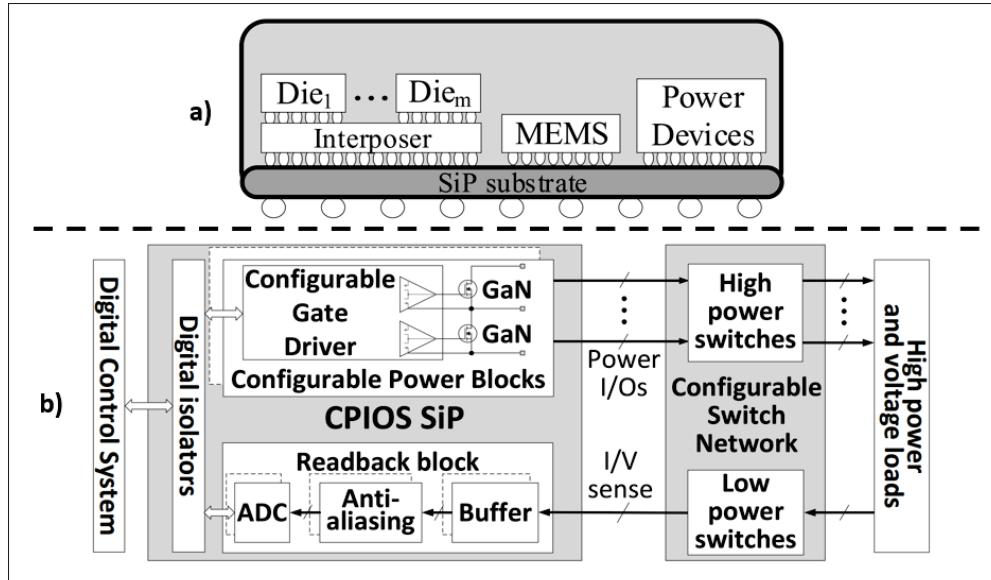

Ce travail de recherche fait partie intégrante d'un projet d'une plus grande envergure visant à concevoir des systèmes intégrés configurables d'entrée/sortie de puissance (CPIOS) pour des applications industrielles. Dirigé par le professeur Blaquièvre depuis plusieurs années maintenant, l'entreprise partenaire et les partenaires gouvernementaux offrent un soutien indéfectible voué à perdurer dans la décennie. Par ailleurs, les travaux accomplis sont le fruit d'une collaboration interuniversitaire permettant l'échange de savoir-faire dans différents domaines de compétence propre à chaque institut. En tant qu'étudiant (tous niveaux académiques) issu des domaines du génie électrique et physique, il est possible de s'orienter dans ce projet sur la conception de circuits intégrés analogiques et numériques, de microsystèmes électromécaniques (MEMS) ainsi que de système dans un boîtier (SiP) hétérogène.

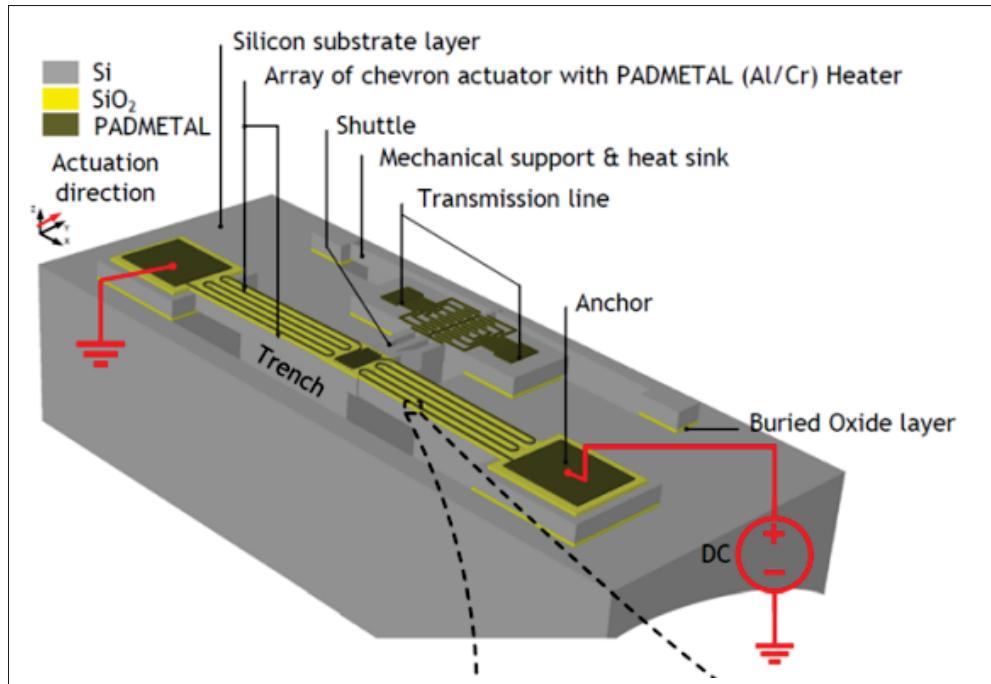

Dans le cadre de ce mémoire, nous explorerons la conception d'une puce CMOS destinée à alimenter un prototype de commutateur MEMS électrothermique, réalisé par un autre étudiant du projet. Grâce à mon parcours académique généraliste, ce sujet m'a permis d'améliorer mes compétences en conception de circuits intégrés CMOS tout en mettant à profit mes connaissances en mécanique et en physique des matériaux. La conception a conduit à la fabrication d'un prototype dont les tests en ont démontré le fonctionnement. Un article de conférence a été publié et présenté en lecture. Un article de journal va également être rédigé.

### Référence de l'article :

- A. Riboulet, F. Nabki, Y. Blaquièvre and G. Cowan, "Configurable and Intelligent Switched CMOS Current Driver Powering Arrays of Electrothermal Actuators for MEMS Switches," 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 2024, pp. 1-5, doi : 10.1109/ISCAS58744.2024.10558666.

## REMERCIEMENTS

Premièrement, je tiens à exprimer ma profonde gratitude envers l'INSA Centre Val de Loire et ses professeurs pour l'enseignement de qualité que j'ai reçu, ainsi que pour l'opportunité de poursuivre mes études en double diplôme à l'ÉTS que je remercie également pour l'expérience enrichissante que ces trois dernières années m'ont offerte.

Merci au Département de génie électrique et au LACIME pour l'invitation à des conférences, l'accès à des infrastructures et à des équipements de qualités. Merci aux étudiants avec qui j'ai pu dialoguer, au Professeur Al Hadi pour son écoute et son aide quand j'en ai eu le plus besoin, ainsi qu'à Mathieu pour son soutien indéfectible. Je remercie tous les membres du projet CPIOS pour les conseils reçus, les présentations fantastiques sur nos sujets respectifs, ainsi que la bonne humeur lors de nos réunions mensuelles. Mention spéciale au Professeur Blaquière, pour l'organisation du projet et sa confiance. Je remercie Monsieur Rigoberto pour son assistance lors du montage et les modifications des PCB. Merci à CMC Microsystems pour la sous-traitance de la fabrication de la puce, et spécialement à Jim pour l'aide apportée sur les vérifications DRC.

Je tiens à remercier chaleureusement mes colocataires qui ont illuminé mon quotidien au cours de cette dernière année et qui m'ont aidé à me sortir la tête du travail. Un immense merci à mes amis Adrien, Loïc et Timothé, avec qui j'ai commencé cette magnifique expérience à Montréal.

Je remercie chaleureusement mes directeurs de recherche, le Professeur Nabki et le Professeur Cowan, pour leurs conseils avisés, leur encouragement, leur patience et surtout leur confiance indéfectible. Leur expertise et leur rigueur m'ont été d'une aide précieuse. Ce sont des exemples de bienveillance et de dévouement au travail. Merci au Professeur Nabki qui m'a donné l'opportunité de travailler comme chargé de laboratoire, où j'ai eu la chance d'acquérir une expérience de pédagogie qui sera marquante pour ma carrière professionnelle future.

Enfin, je remercie ma famille pour leur soutien constant et surtout leur patience. C'est grâce à vous que je suis ici aujourd'hui pour écrire ces mots. C'est une magnifique occasion pour vous rappeler tout l'amour que je vous porte.

# **Conception, fabrication et caractérisation d'une puce CMOS pour l'alimentation et le diagnostic d'un réseau configurable de commutateurs MEMS électrothermiques**

Allan RIBOULLET

## **RÉSUMÉ**

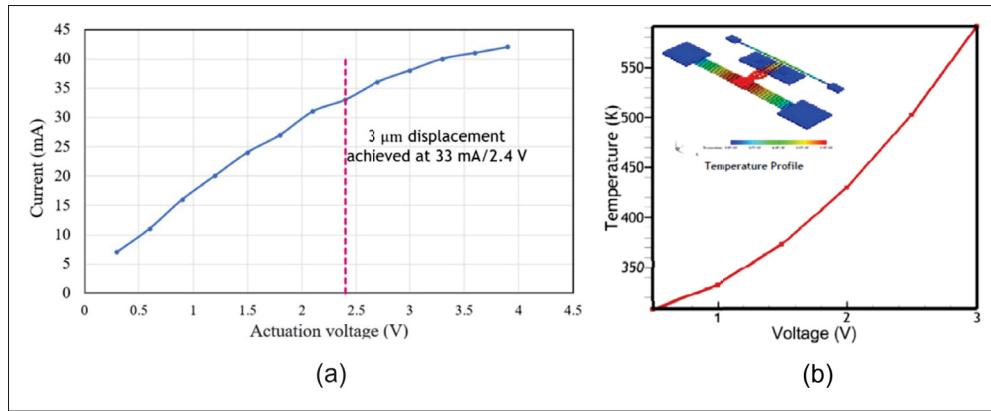

Ce mémoire présente la conception d'un circuit de commande pour alimenter un réseau de commutateurs configurables reposant sur l'utilisation de microsystèmes électromécaniques (MEMS) électrothermiques. Une nouvelle approche d'alimentation à courant constant est proposée pour obtenir un contrôle précis de la puissance sur un ensemble de dispositifs utilisant des  $\mu$ heaters comme actionneurs thermiques. Le système est compatible avec un courant à double impulsion et une modulation de largeur d'impulsion (PWM), permettant respectivement d'accélérer la fermeture et de réduire la consommation énergétique du commutateur. Le circuit d'actionnement est conçu de sorte à alimenter des commutateurs MEMS électrothermiques différents en série et en parallèle. Par ailleurs, des circuits de rétroaction basés sur une technique d'auto-détection de la température des  $\mu$ heaters et sur la propriété ohmique des contacts de l'actionneur sont proposés pour détecter et résoudre les problèmes liés à la durée de vie des commutateurs MEMS. Une revue de la littérature scientifique sur la structure électrothermique en V, incluant les modèles thermiques, les capteurs, les méthodes et les circuits d'alimentation ainsi que les problèmes liés à l'actionnement, constitue une contribution supplémentaire. Bien que plusieurs circuits électroniques standard soient présentés, la nouveauté de ce travail de recherche est axée sur l'application et la proposition d'un système complet sur puce en technologie CMOS, comprenant les circuits d'actionnement et de diagnostic. Finalement, les circuits sont réalisés avec la technologie 0,18  $\mu$ m BCD de TSMC, occupant une surface totale de 1,3 mm<sup>2</sup> pour une puce ayant des dimensions de 2 mm  $\times$  2 mm. Les essais expérimentaux, réalisés avec un PCB conçu spécifiquement, démontrent une puce fonctionnelle pouvant fournir un courant maximal de 125 mA avec une résolution de 2 mA. Avec une tension d'alimentation de 8 V en sortie et une tension de sortie minimale de 1,6 V, la puissance maximale correspondante est de 800 mW. Dans ces conditions, la résistance maximale du  $\mu$ heater est de 51  $\Omega$ .

**Mots-clés:** Commutateur MEMS électrothermique, réseau de commutateur, CMOS, actionnement, diagnostic

# **Design, fabrication, and characterization of a CMOS chip for the actuation and diagnosis of a configurable network of electrothermal MEMS switches**

Allan RIBOULET

## **ABSTRACT**

This master's thesis presents the design of a current driver for a configurable switch network based on electrothermal micro-electro-mechanical-systems (MEMS) components. A new constant current power supply approach is proposed to achieve precise power control over an array of devices using  $\mu$ heaters as thermal actuators. The system is compatible with a double pulse current and pulse-width modulation (PWM), to increase switching speed and reduce energy consumption. The actuation circuit is designed to supply different electrothermal MEMS switches in series and parallel. Furthermore, diagnostic circuits based on self-temperature sensing technique of the  $\mu$ heater and the ohmic contact property of the actuator are proposed for detecting and addressing MEMS lifetime concerns early. A review of the scientific literature on the V-shaped electrothermal structure, including thermal models, sensors, methods, and actuation circuits, as well as issues related to actuation, constitutes an additional contribution. Although several standard electronic circuits are presented, the novelty of this research work focuses on the application and proposal of a complete system in CMOS technology, including the driving and diagnostic circuits. Finally, the circuits are implemented with TSMC's 0.18  $\mu$ m BCD technology, occupying a total area of 1.3 mm<sup>2</sup> for a chip with dimensions of 2 mm  $\times$  2 mm. Experimental tests conducted with a specially designed PCB demonstrate a functional chip capable of providing a maximum current of 125 mA with a resolution of 2 mA. With an output power supply of 8 V and a minimum output voltage of 1.6 V, the corresponding maximum power is 800 mW. Under these conditions, the maximum resistance of the  $\mu$ heater is 51  $\Omega$ .

**Keywords:** Electrothermal MEMS switch, switch network, CMOS, driving circuit, diagnosis

## TABLE DES MATIÈRES

|                                                                                                                     | Page |

|---------------------------------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                                                  | 1    |

| 0.1    Environnement de recherche .....                                                                             | 2    |

| 0.1.1    Laboratoire de communication et d'intégration de la microélectronique - LACIME .....                       | 2    |

| 0.1.2    Présentation du projet CPIOS - Systèmes intégrés configurables d'entrée/sortie de puissance .....          | 3    |

| 0.2    Motivations de recherche .....                                                                               | 4    |

| 0.2.1    Comparaison des relais statiques et des commutateurs MEMS .....                                            | 4    |

| 0.2.2    Prototype d'un commutateur MEMS électrothermique en V (chevron) .....                                      | 5    |

| 0.2.3    Défis et motivations des récentes recherches sur les commutateurs MEMS et leurs circuits de commande ..... | 7    |

| 0.2.4    Problématiques et sous-problématiques de recherche .....                                                   | 9    |

| 0.3    Contributions scientifiques .....                                                                            | 11   |

| 0.3.1    Résumé et principales contributions de ce mémoire .....                                                    | 11   |

| 0.3.2    Communication et publication dans la cadre de la maîtrise .....                                            | 12   |

| 0.4    Plan du mémoire .....                                                                                        | 12   |

| <br>CHAPITRE 1 ÉTAT DE L'ART DES COMMUTATEURS MEMS ET LES SPÉCIFICITÉS DE L'ACTIONNEMENT ÉLECTROTHERMIQUE .....     | 13   |

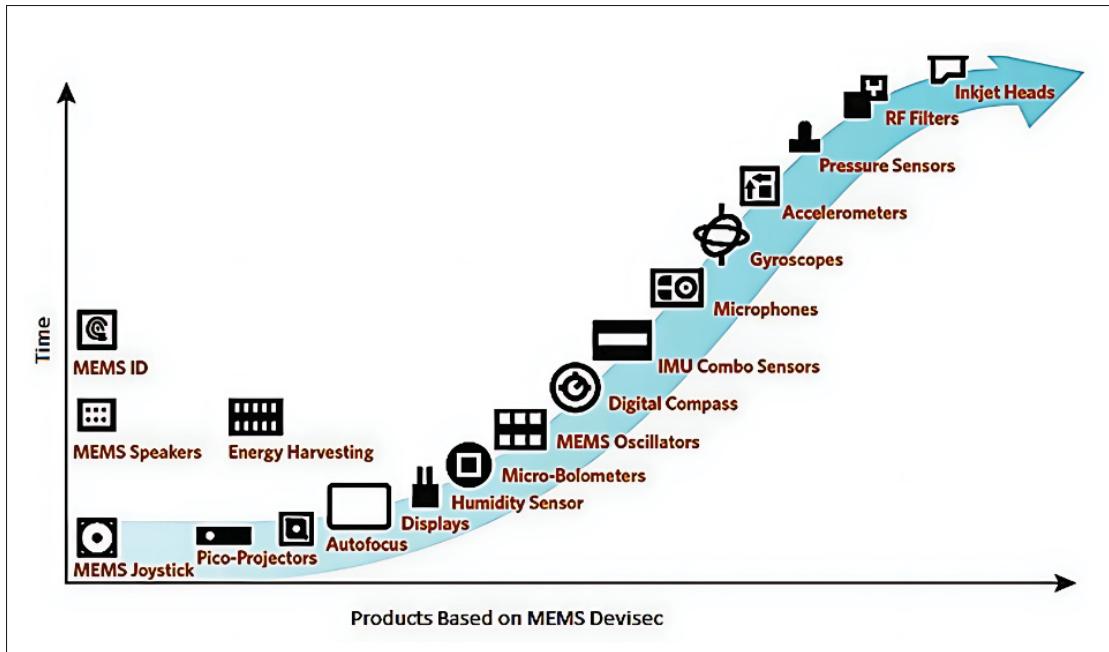

| 1.1    Vue d'ensemble du marché des MEMS depuis les années 2000 .....                                               | 13   |

| 1.2    Les MEMS et leurs spécificités en tant que dispositifs de commutation .....                                  | 14   |

| 1.2.1    4 physiques d'actionnement .....                                                                           | 16   |

| 1.2.2    Comparaison des performances .....                                                                         | 17   |

| 1.2.3    Problématiques majeures des commutateurs MEMS .....                                                        | 19   |

| 1.3    Vue d'ensemble d'un système de contrôle d'un commutateur MEMS électrothermique en V .....                    | 21   |

| 1.3.1    Les modèles statiques et dynamiques .....                                                                  | 21   |

| 1.3.1.1    Modélisation du comportement électrothermique .....                                                      | 22   |

| 1.3.1.2    Modélisation du comportement thermomécanique .....                                                       | 26   |

| 1.3.2    Revue des capteurs intégrés dans la structure en V .....                                                   | 27   |

| 1.3.2.1    Mesurer la température du $\mu$ heater .....                                                             | 28   |

| 1.3.2.2    Mesurer le déplacement de la poutre .....                                                                | 30   |

| 1.3.2.3    Mesurer la force de contact .....                                                                        | 32   |

| 1.3.3    Évaluer l'état du commutateur .....                                                                        | 32   |

| 1.3.3.1    Effet d'électromigration (EM) dans le $\mu$ heater .....                                                 | 33   |

| 1.3.3.2    Contact ohmique de la ligne de transmission .....                                                        | 36   |

| 1.3.4    Les circuits intégrés d'actionnement et d'interface .....                                                  | 36   |

| 1.3.4.1    Deux modes d'excitation .....                                                                            | 37   |

| 1.3.4.2    Les différents types de contrôleurs existants .....                                                      | 38   |

| 1.4    Conclusion .....                                                                                             | 40   |

|                                                                                           |           |

|-------------------------------------------------------------------------------------------|-----------|

| <b>CHAPITRE 2 ÉTAT DE L'ART DES CIRCUITS CMOS .....</b>                                   | <b>43</b> |

| 2.1 Revue des circuits de courant CMOS .....                                              | 43        |

| 2.1.1 Miroirs de courant .....                                                            | 44        |

| 2.1.1.1 Indicateurs de performance et <i>trade-off</i> .....                              | 45        |

| 2.1.1.2 Architectures offrant de meilleures performances .....                            | 48        |

| 2.1.2 Amplificateurs différentiels .....                                                  | 52        |

| 2.1.2.1 Indicateur de performance et <i>trade-off</i> .....                               | 52        |

| 2.1.2.2 Architectures offrant de meilleures performances .....                            | 55        |

| 2.1.3 Circuit de polarisation de courant .....                                            | 56        |

| 2.1.3.1 Références indépendantes de la tension d'alimentation .....                       | 57        |

| 2.1.3.2 Références indépendantes de la température .....                                  | 58        |

| 2.1.3.3 Référence auto-polarisée .....                                                    | 59        |

| 2.1.3.4 Référence à partir d'une tension de polarisation stable .....                     | 61        |

| 2.1.4 Convertisseur tension (V) - courant (I) .....                                       | 61        |

| 2.1.5 Convertisseur Numérique Analogique - CNA .....                                      | 62        |

| 2.1.5.1 Indicateurs de performance et <i>trade-off</i> .....                              | 62        |

| 2.1.5.2 Les différentes architectures de CNA .....                                        | 64        |

| 2.1.6 Cellule copieuse de courant .....                                                   | 66        |

| 2.1.6.1 Configuration standard et ses caractéristiques .....                              | 67        |

| 2.1.6.2 Variation entre le courant d'entrée et de sortie .....                            | 68        |

| 2.1.6.3 Configurations offrant de meilleures performances .....                           | 69        |

| 2.1.7 Pont en H .....                                                                     | 71        |

| 2.2 Revue des circuits d'interface CMOS .....                                             | 71        |

| 2.2.1 Circuits mesureur de tension .....                                                  | 72        |

| 2.2.1.1 Amplificateur différentiel .....                                                  | 72        |

| 2.2.1.2 Amplificateur d'instrumentation .....                                             | 75        |

| 2.2.1.3 Comparateur .....                                                                 | 76        |

| 2.2.2 Circuits mesureur de courant .....                                                  | 79        |

| 2.2.3 Traitement des données .....                                                        | 81        |

| 2.2.3.1 Convertisseur analogique numérique - CAN .....                                    | 81        |

| 2.2.3.2 Filtres analogiques et numériques .....                                           | 82        |

| 2.2.3.3 DéTECTEUR de crête .....                                                          | 83        |

| 2.3 Conclusion .....                                                                      | 84        |

| <b>CHAPITRE 3 CONCEPTION DE LA PUCE CMOS ET DE SES CIRCUITS DE RÉTROACTION .....</b>      | <b>87</b> |

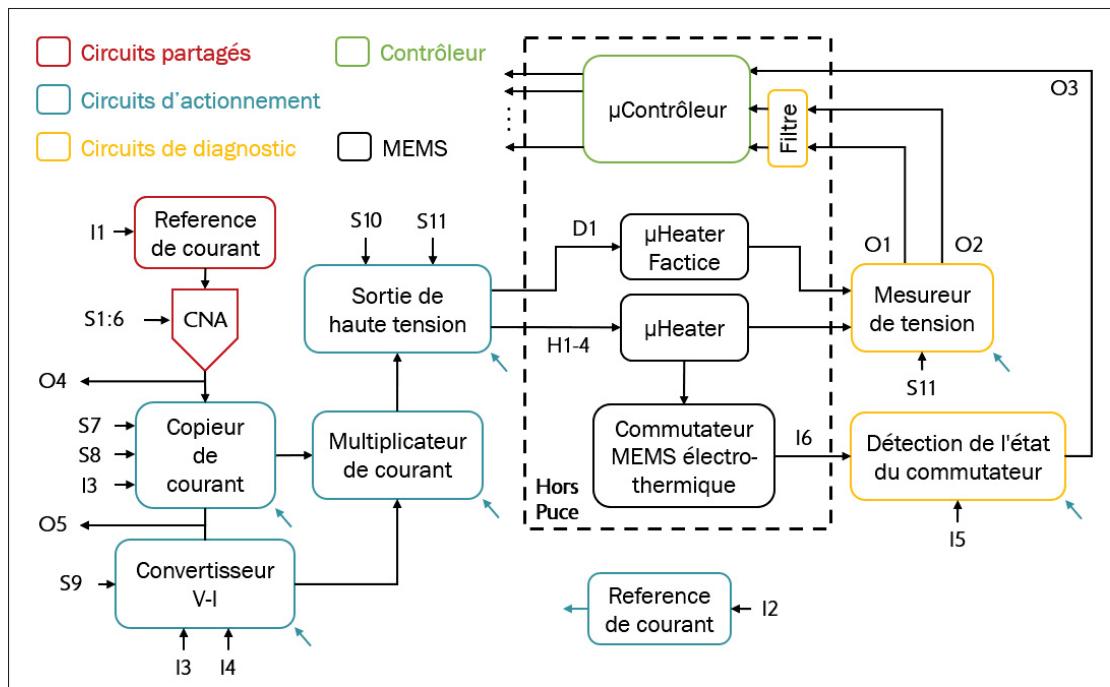

| 3.1 Vue d'ensemble du système .....                                                       | 87        |

| 3.1.1 Ajustements réalisés pour la fabrication d'un prototype fonctionnel et fiable ..... | 92        |

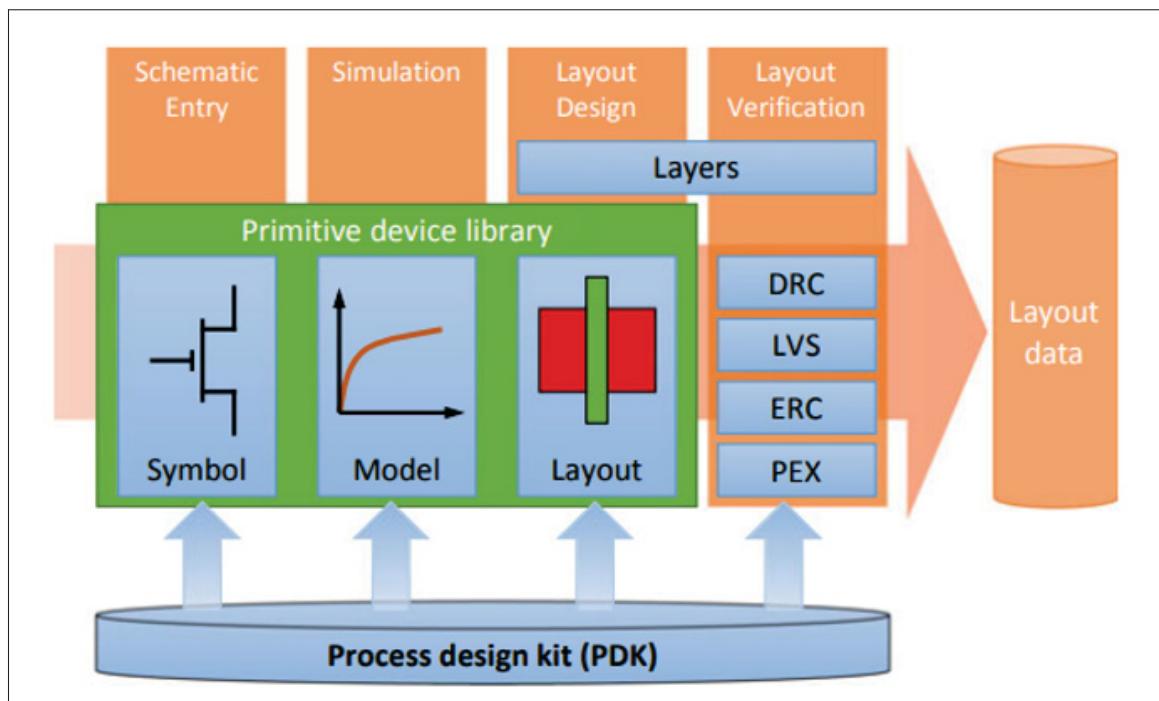

| 3.2 Technologie CMOS 0,18µm BCD de TSMC .....                                             | 94        |

| 3.2.1 Paramètre du kit d'installation .....                                               | 94        |

| 3.2.2 Utilisation du logiciel Cadence Virtuoso .....                                      | 95        |

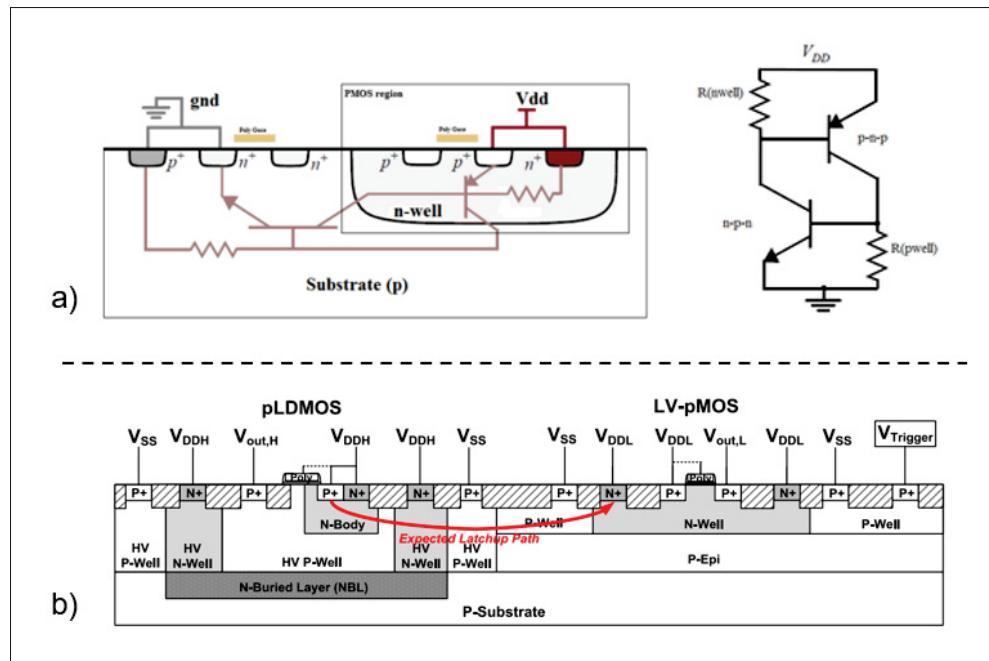

| 3.2.3 Méthodologie et étapes de conception .....                                          | 95        |

|                                                                 |                                                                                        |     |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|

| 3.3                                                             | Présentation des circuits d'actionnement et d'interface .....                          | 98  |

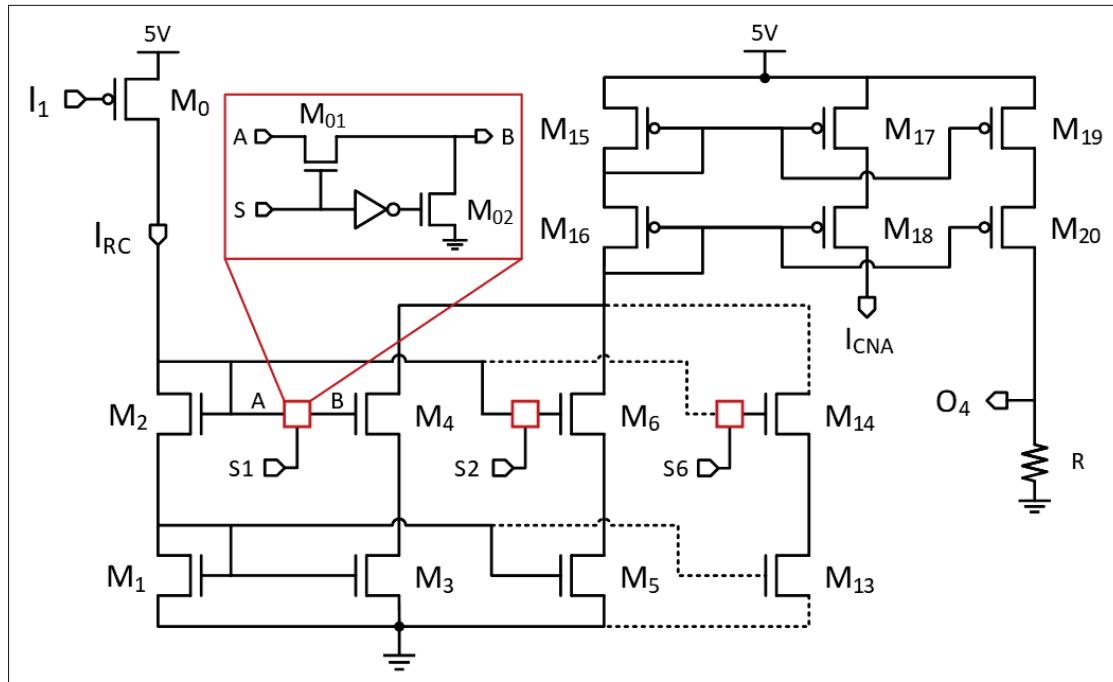

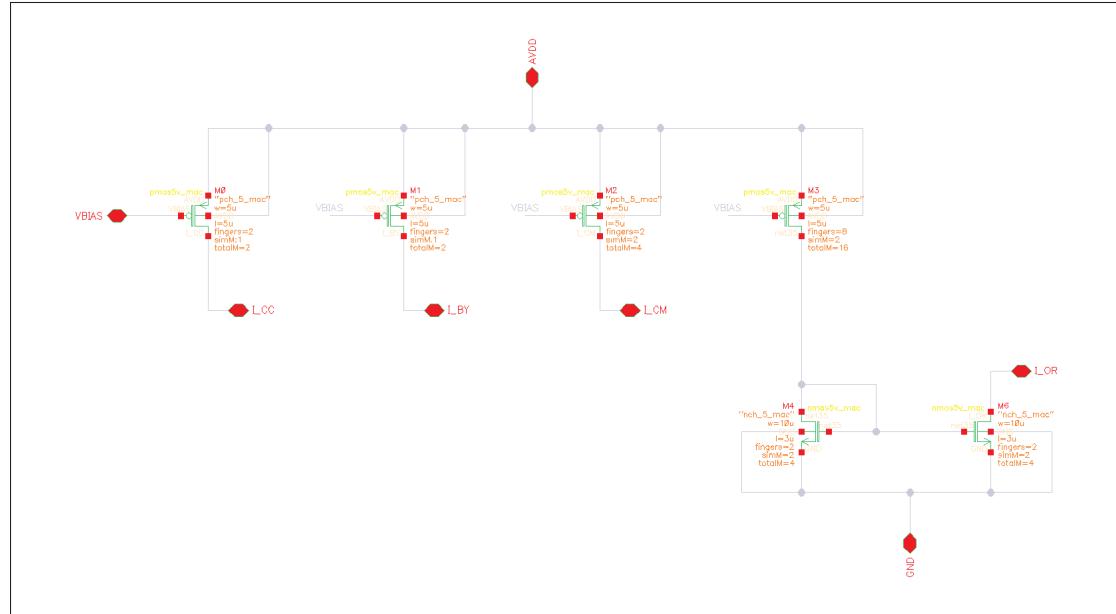

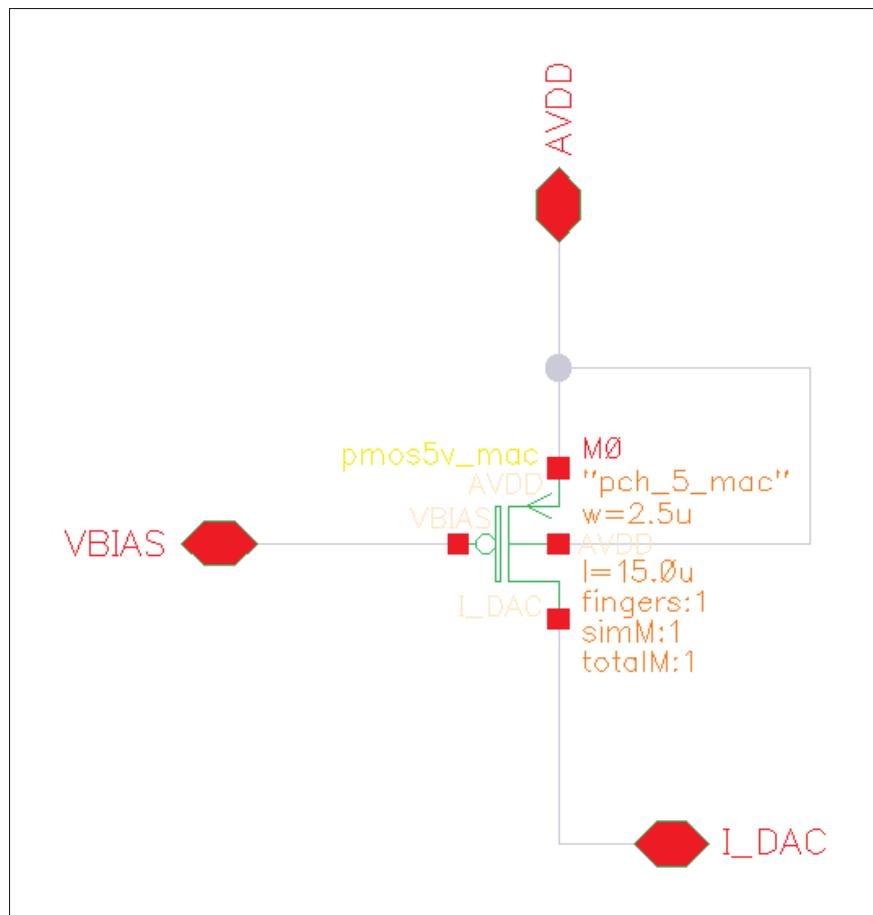

| 3.3.1                                                           | Référence de courant .....                                                             | 98  |

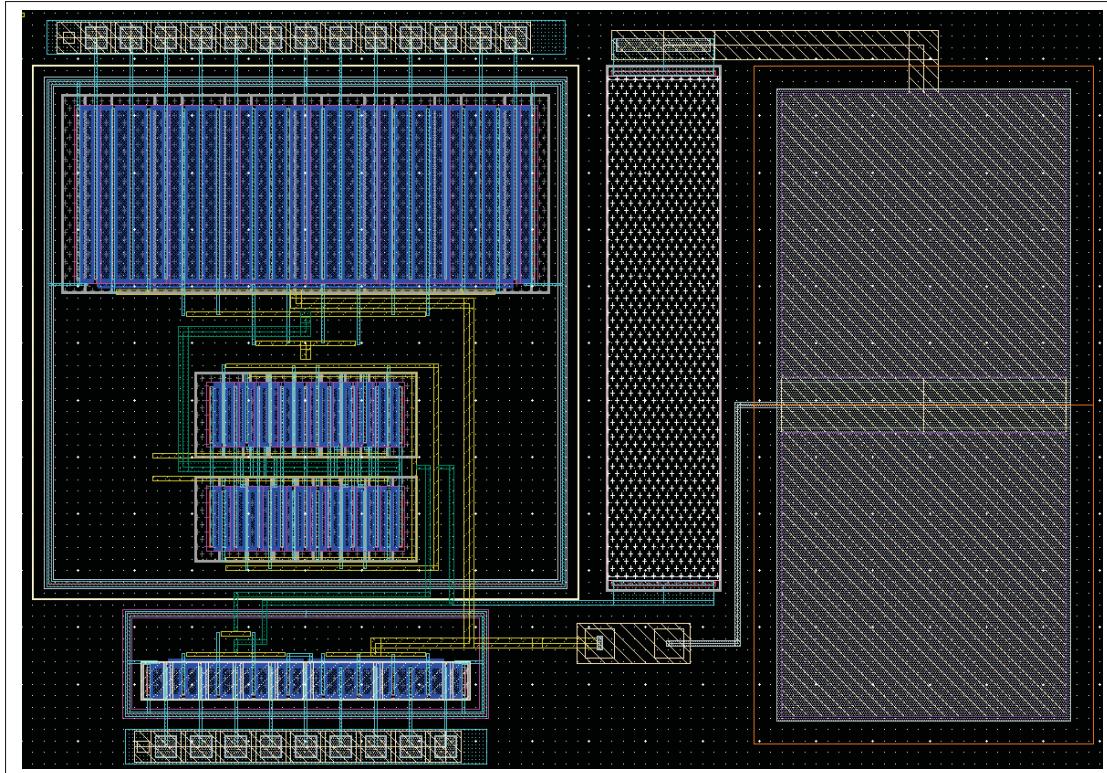

| 3.3.2                                                           | Convertisseur Numérique Analogique .....                                               | 100 |

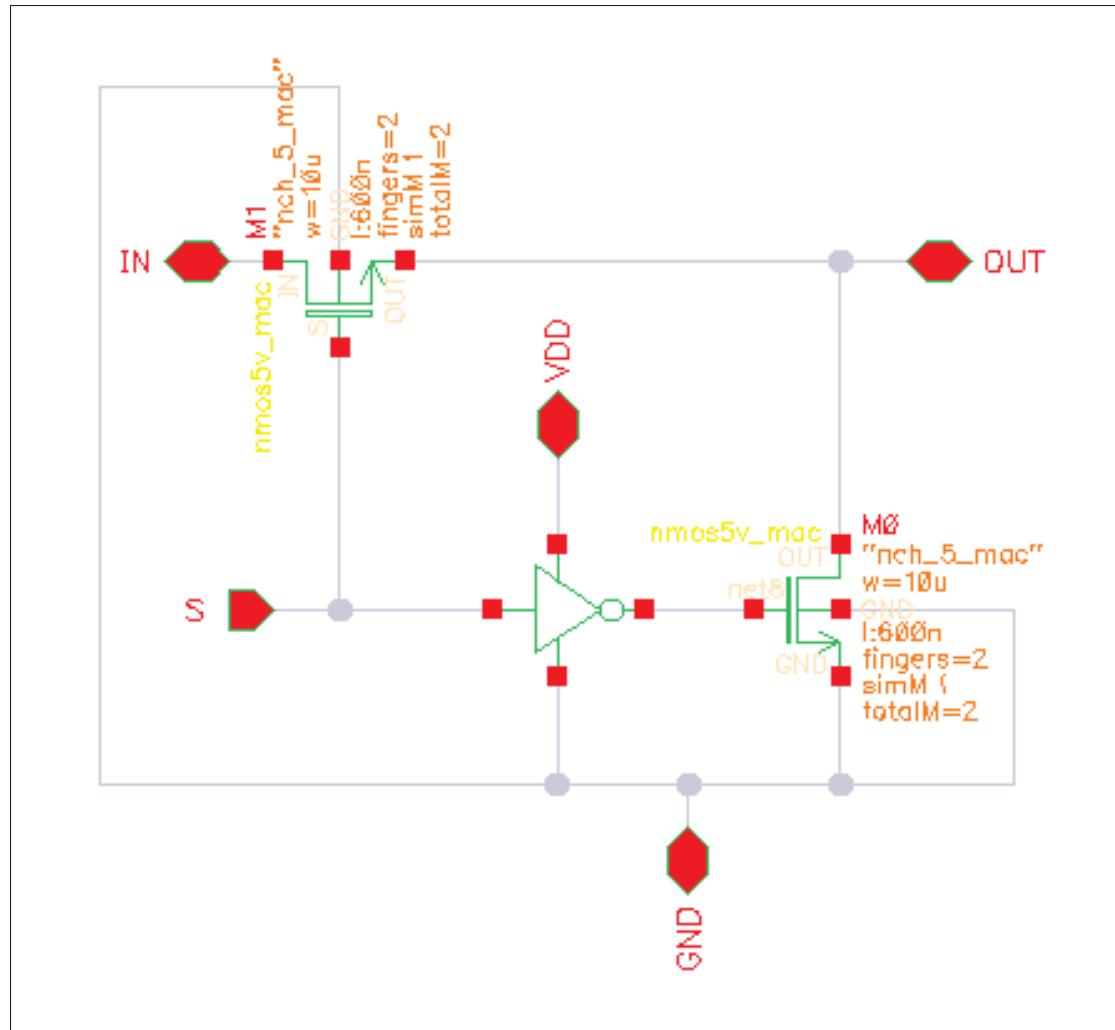

| 3.3.3                                                           | Cellule copieuse de courant .....                                                      | 100 |

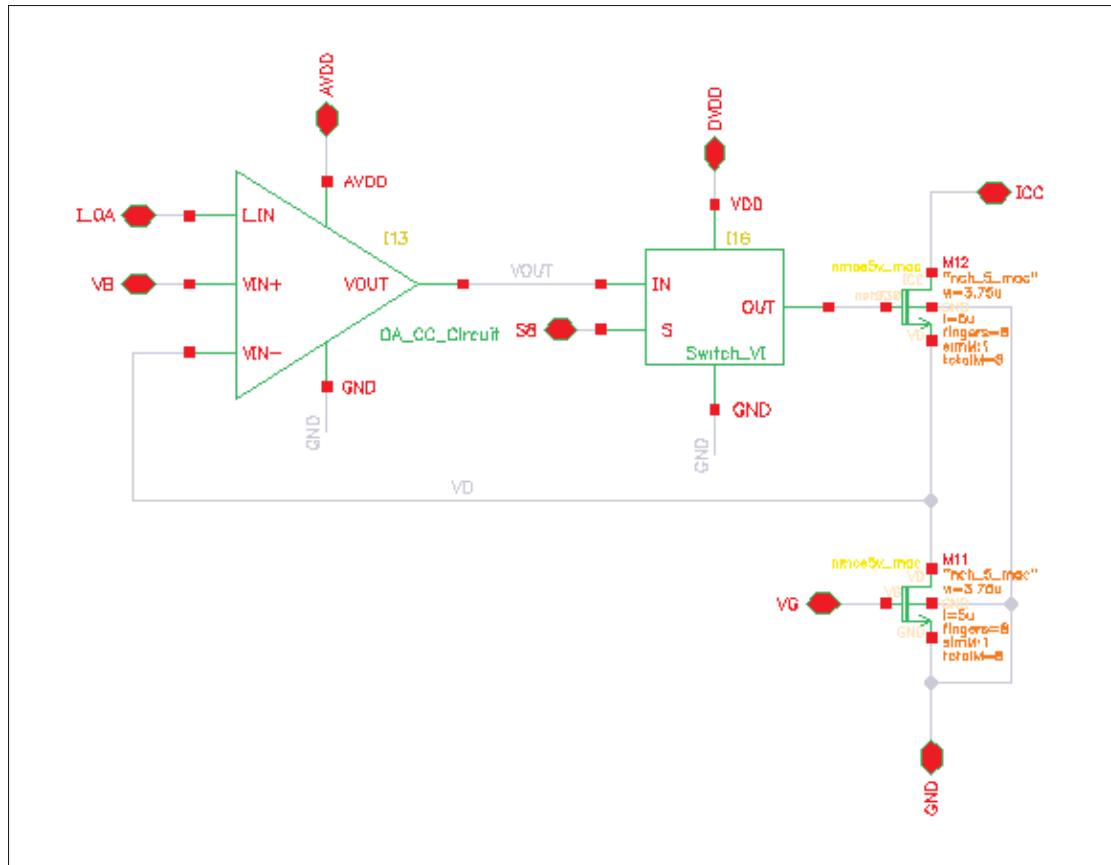

| 3.3.4                                                           | Convertisseur V-I .....                                                                | 103 |

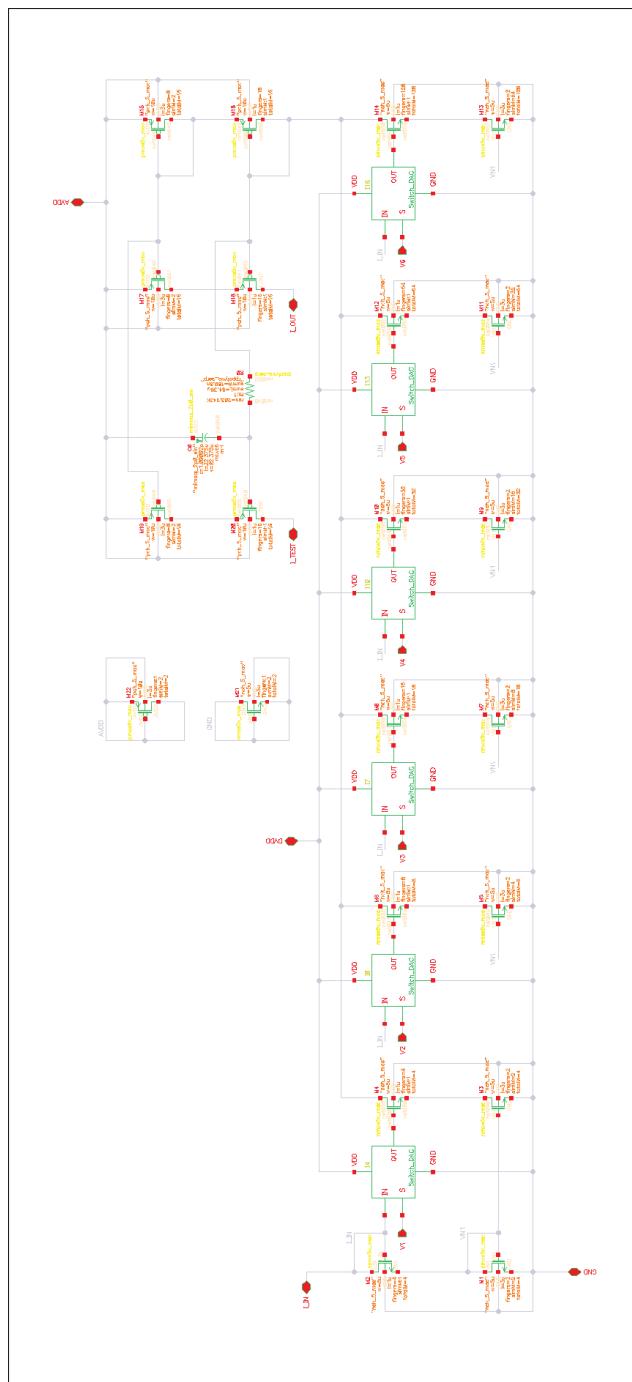

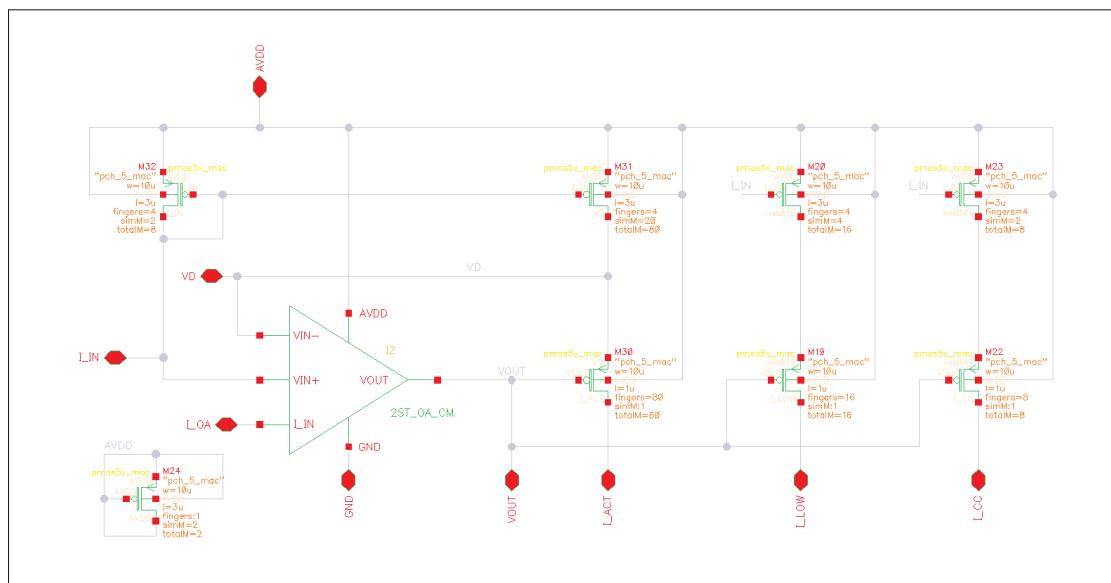

| 3.3.5                                                           | Multiplicateur de courant .....                                                        | 106 |

| 3.3.5.1                                                         | Courant de haute intensité pour l'actionnement du commutateur MEMS .....               | 106 |

| 3.3.5.2                                                         | Courant de faible intensité pour mesurer la température du $\mu$ heater .....          | 108 |

| 3.3.6                                                           | Sortie de courant compatible haute tension .....                                       | 109 |

| 3.3.7                                                           | Erreurs relatives cumulées des circuits .....                                          | 110 |

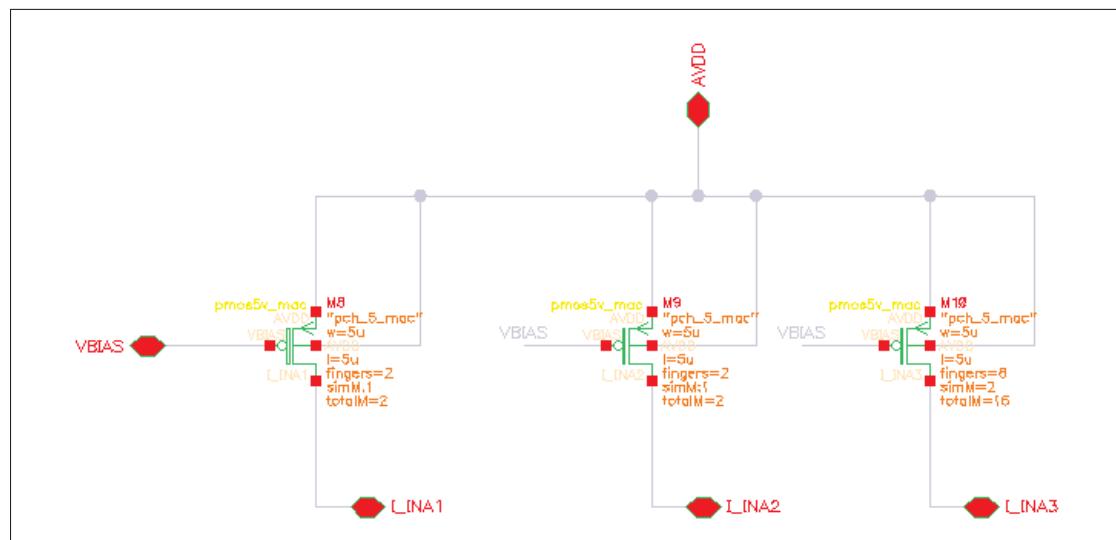

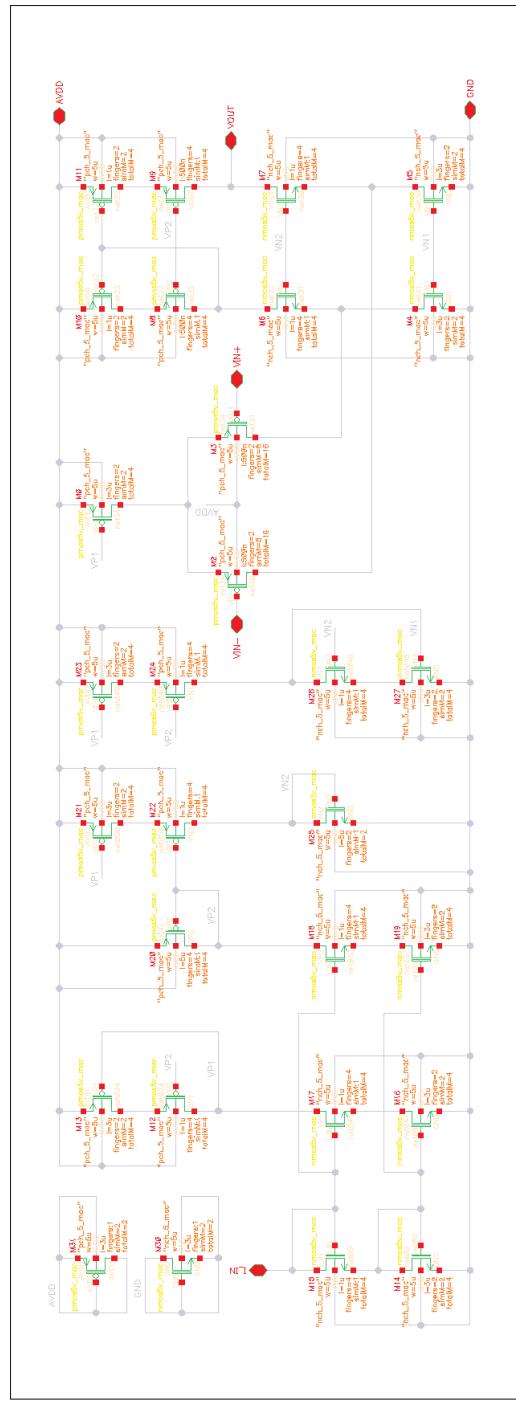

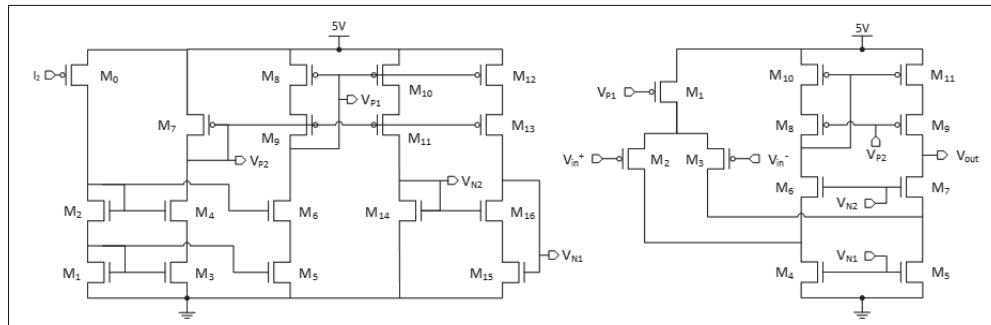

| 3.3.8                                                           | Amplificateur d'instrumentation .....                                                  | 111 |

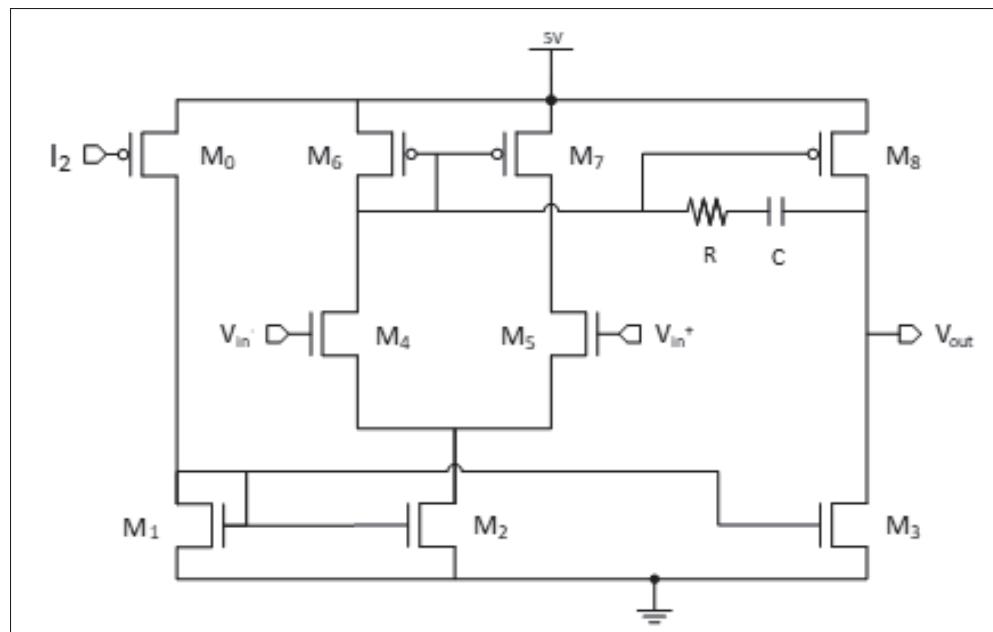

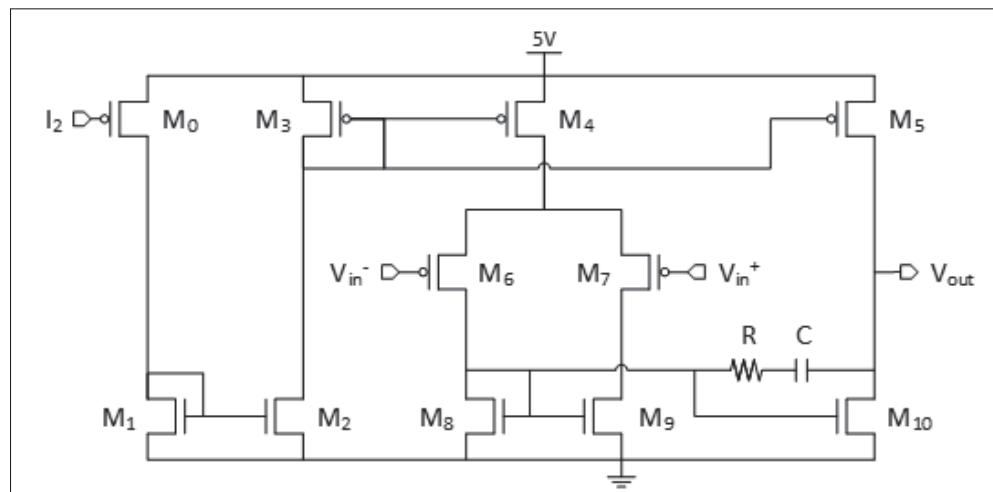

| 3.3.9                                                           | Comparateur .....                                                                      | 113 |

| 3.4                                                             | Simulations et analyse complète de la puce .....                                       | 115 |

| 3.4.1                                                           | Présentation du schéma de haut niveau .....                                            | 115 |

| 3.4.2                                                           | Simulations <i>post-layout</i> .....                                                   | 116 |

| 3.4.3                                                           | Résultats de simulation lorsque le heater est connecté .....                           | 117 |

| 3.4.4                                                           | Réponse thermique du $\mu$ heater avec un modèle du premier ordre .....                | 117 |

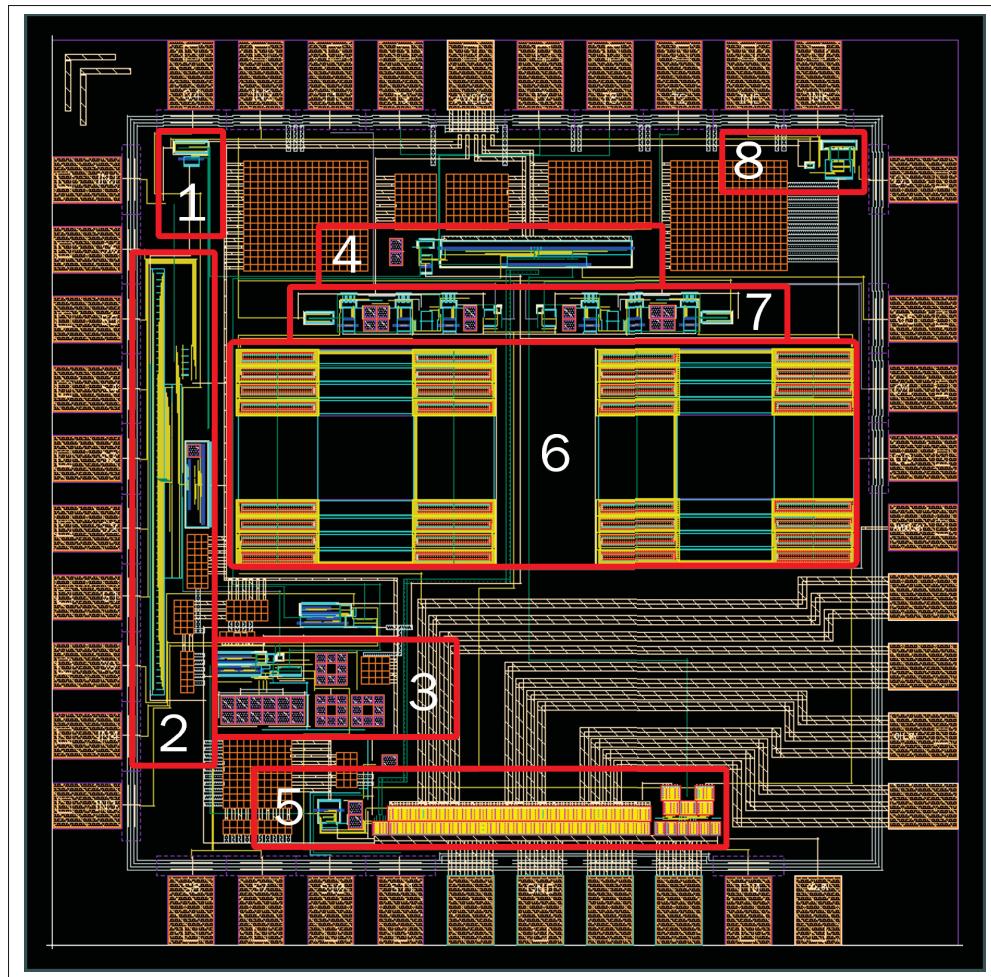

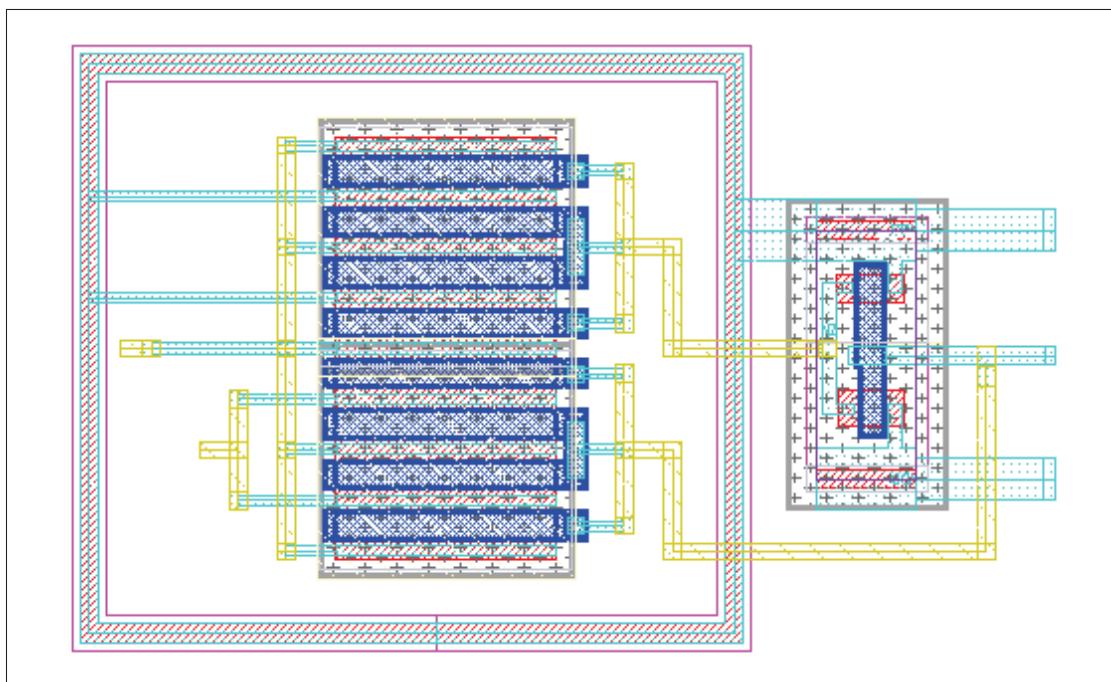

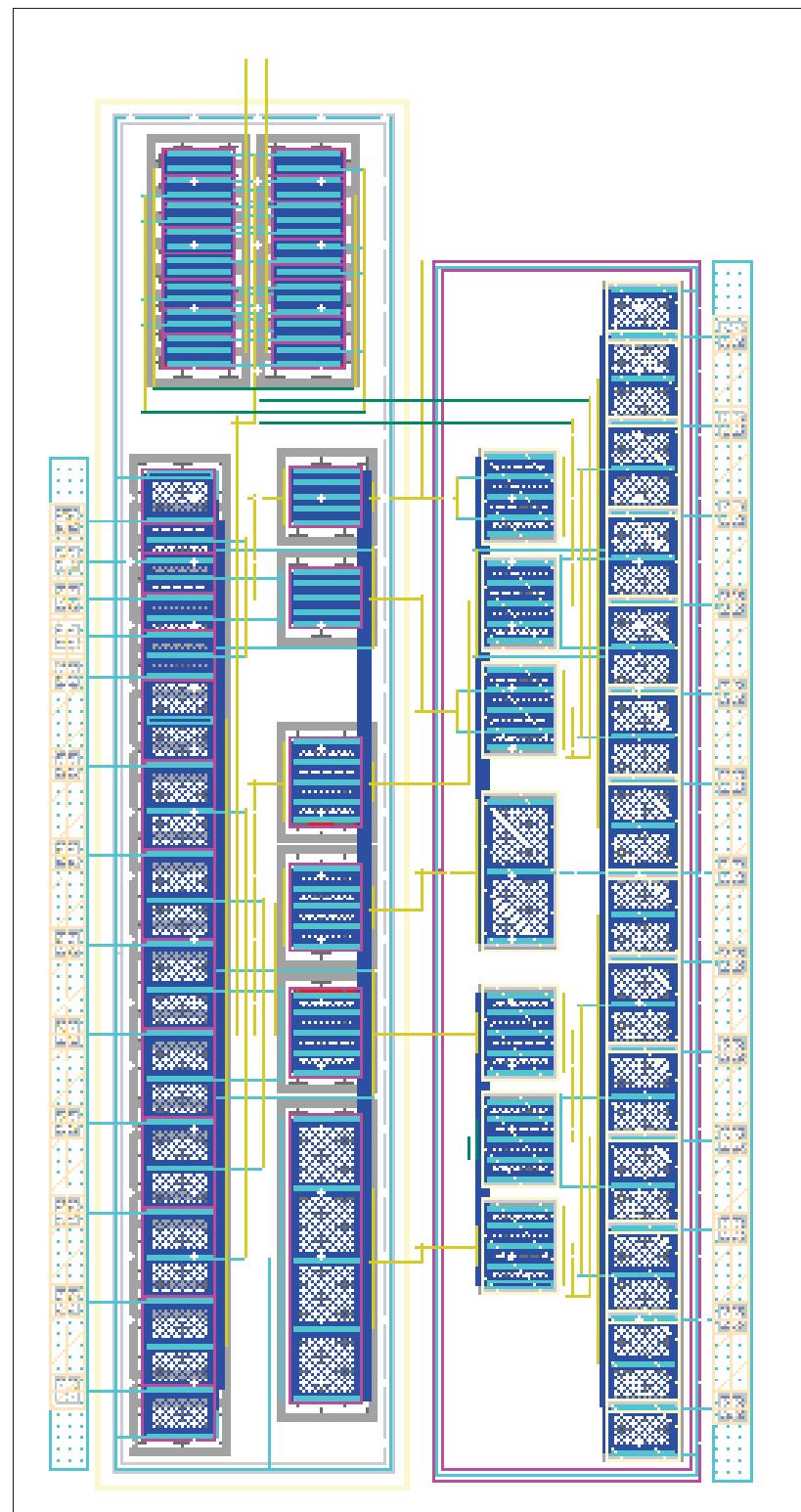

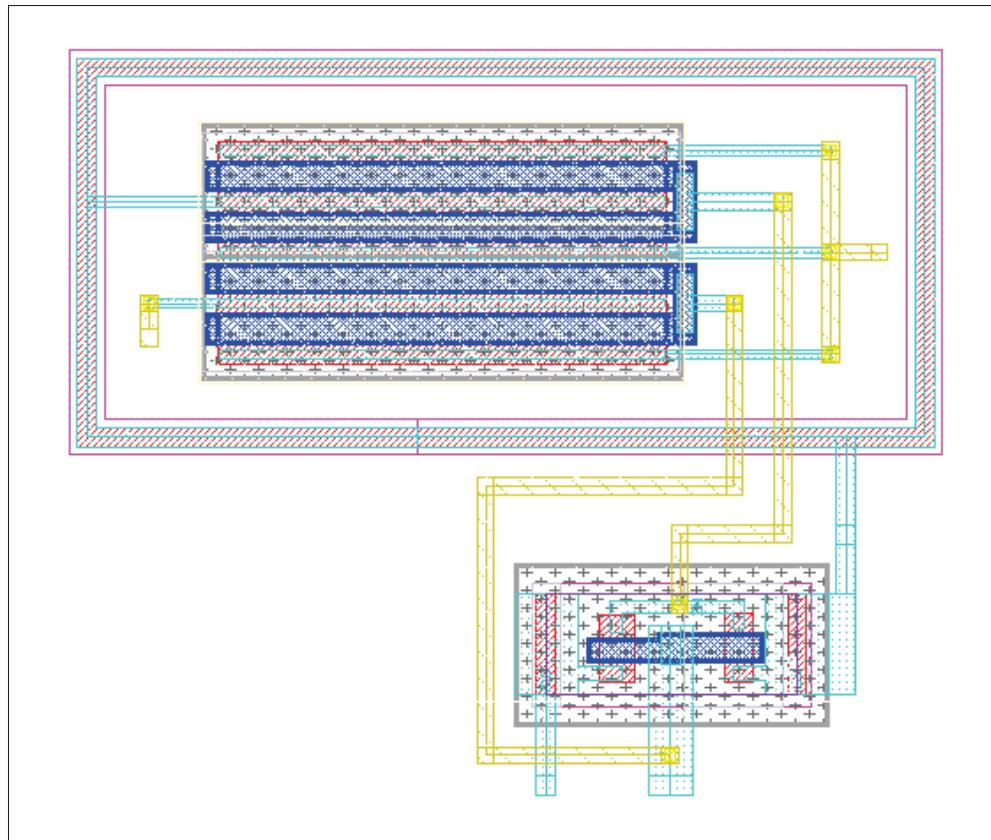

| 3.5                                                             | Présentation du <i>layout</i> de la puce .....                                         | 121 |

| 3.5.1                                                           | Anneau externe de la puce .....                                                        | 122 |

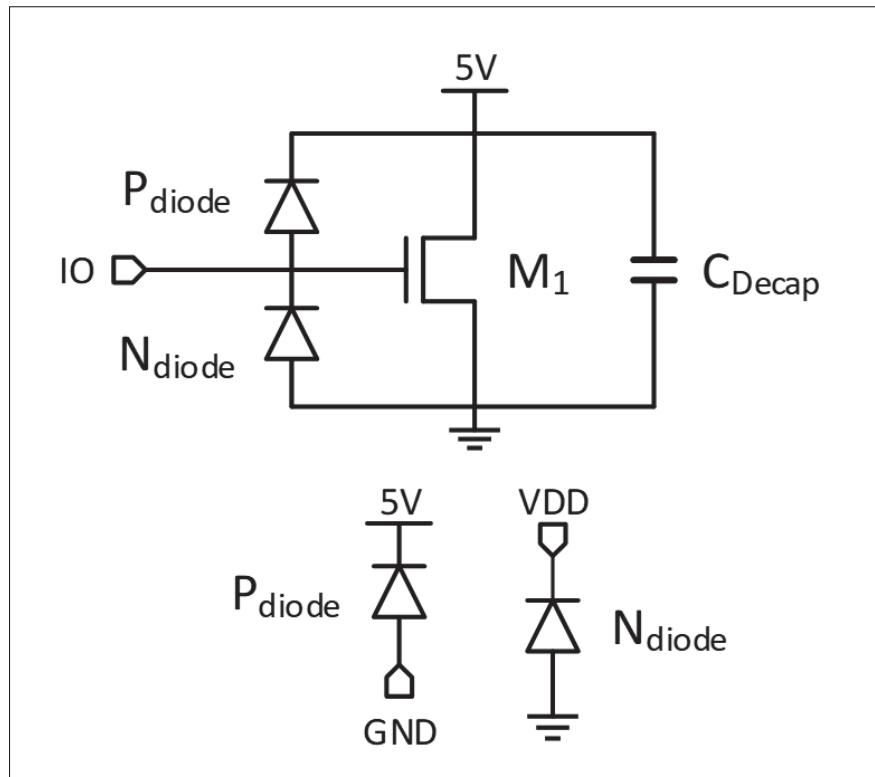

| 3.5.1.1                                                         | Protection contre les décharges électrostatiques .....                                 | 123 |

| 3.5.1.2                                                         | Nombre maximum d'entrées/sorties .....                                                 | 124 |

| 3.5.1.3                                                         | Nombre de plots requis par les circuits .....                                          | 125 |

| 3.5.2                                                           | <i>Layout</i> des circuits intégrés .....                                              | 125 |

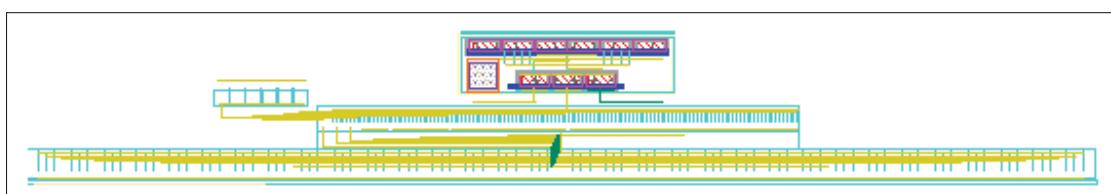

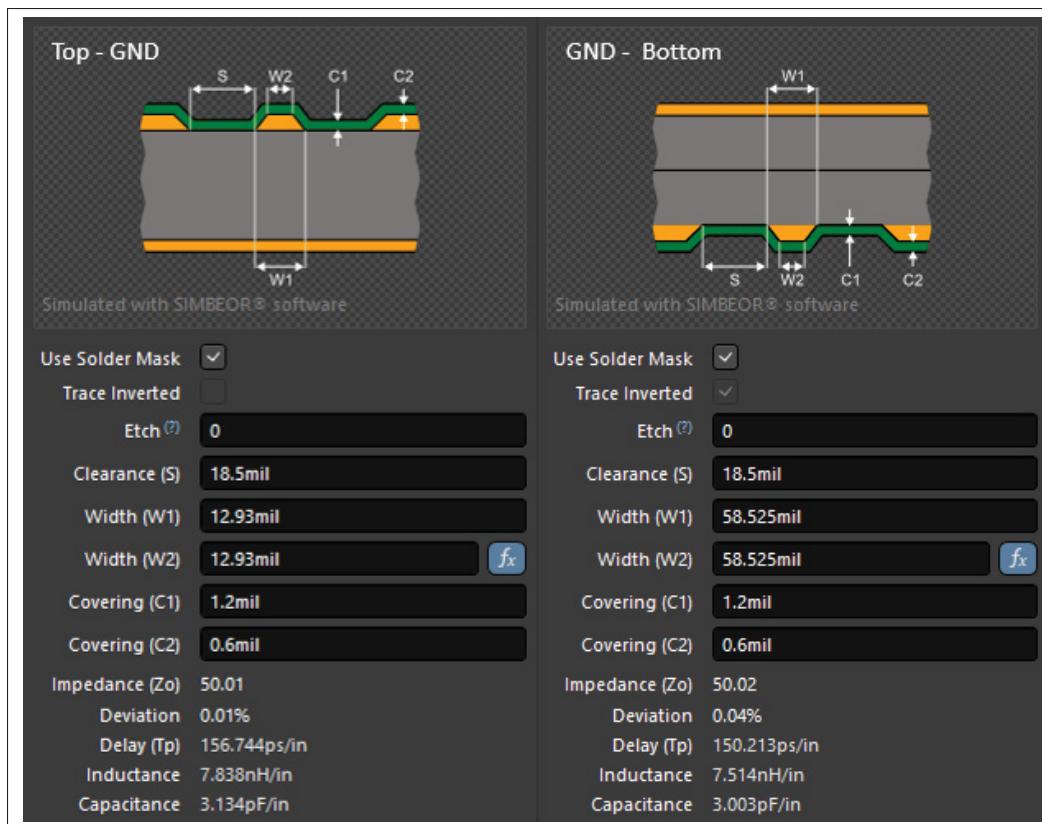

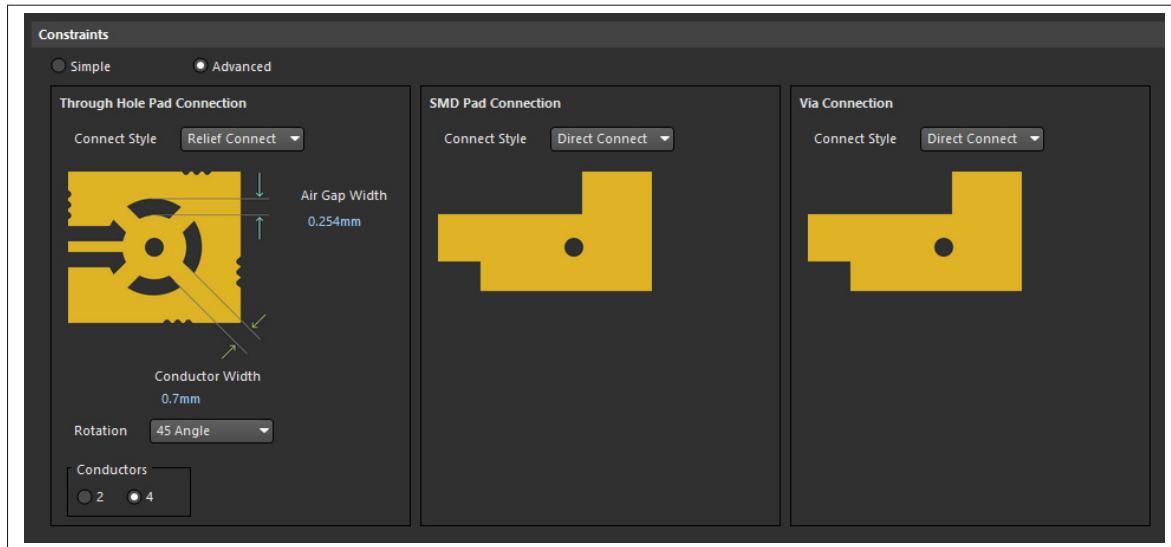

| 3.5.2.1                                                         | Allocation des différentes couches métalliques .....                                   | 125 |

| 3.5.2.2                                                         | Isolation entre les composants de basse et de haute tension .....                      | 127 |

| 3.5.2.3                                                         | Techniques de conception spécifiques pour les circuits intégrés analogiques .....      | 128 |

| 3.5.2.4                                                         | Vue d'ensemble des techniques utilisées .....                                          | 128 |

| 3.5.2.5                                                         | Placement et orientation des E/S et des circuits .....                                 | 130 |

| 3.5.2.6                                                         | Condensateur de découplage .....                                                       | 132 |

| 3.5.3                                                           | Vérifications DRC .....                                                                | 132 |

| 3.5.3.1                                                         | Règle de densité des couches de métal et remplissage automatique .....                 | 133 |

| 3.5.3.2                                                         | Récapitulatif des règles DRC ignorées .....                                            | 133 |

| 3.6                                                             | Conclusion .....                                                                       | 134 |

| <b>CHAPITRE 4 RÉSULTATS EXPÉRIMENTAUX DE LA PUCE CMOS .....</b> |                                                                                        | 137 |

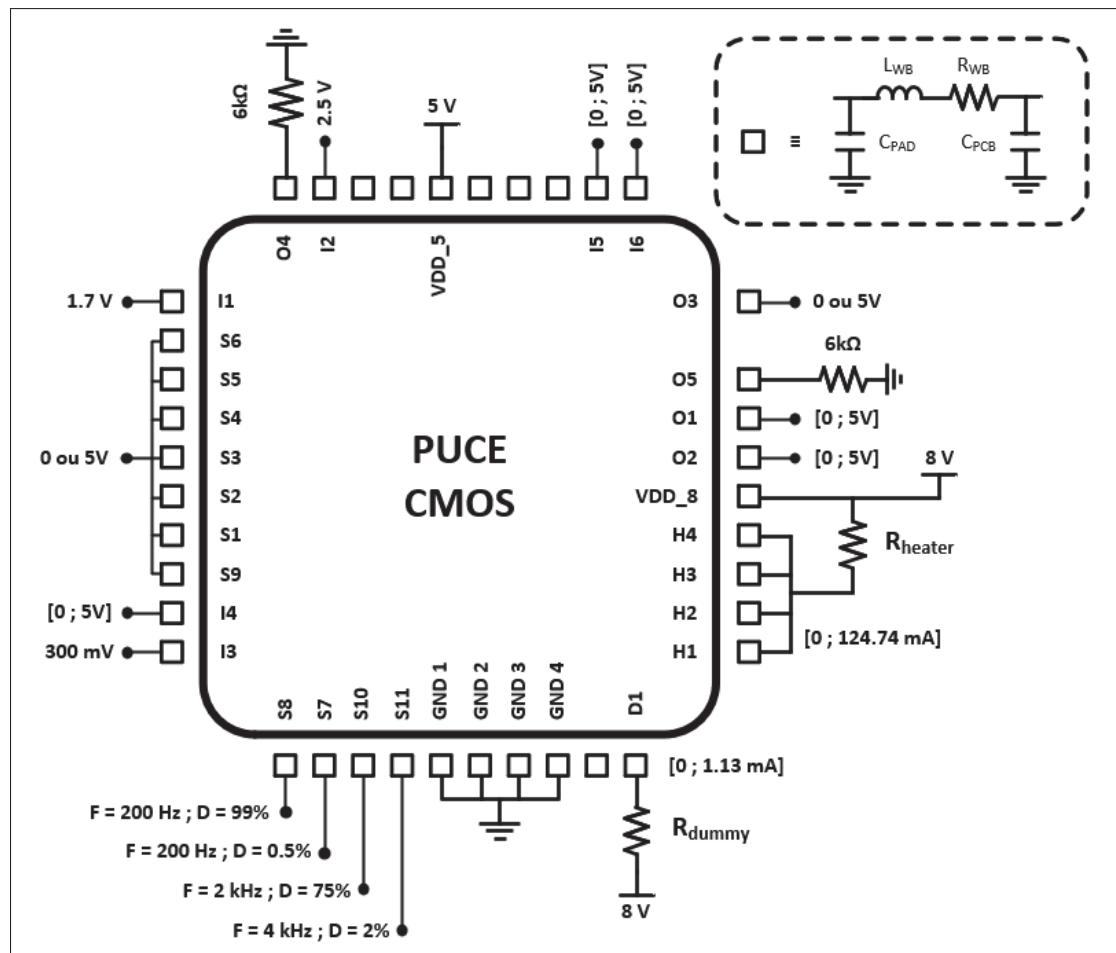

| 4.1                                                             | Banc de test .....                                                                     | 137 |

| 4.1.1                                                           | Générer des signaux PWM ou des signaux d'horloge à l'aide d'un Arduino MEGA 2560 ..... | 138 |

| 4.2                                                             | Comparaison entre les simulations et les résultats expérimentaux .....                 | 140 |

|             |                                                                                              |     |

|-------------|----------------------------------------------------------------------------------------------|-----|

| 4.2.1       | Référence de courant .....                                                                   | 141 |

| 4.2.2       | Convertisseur Numérique Analogique .....                                                     | 142 |

| 4.2.3       | Cellule copieuse de courant .....                                                            | 143 |

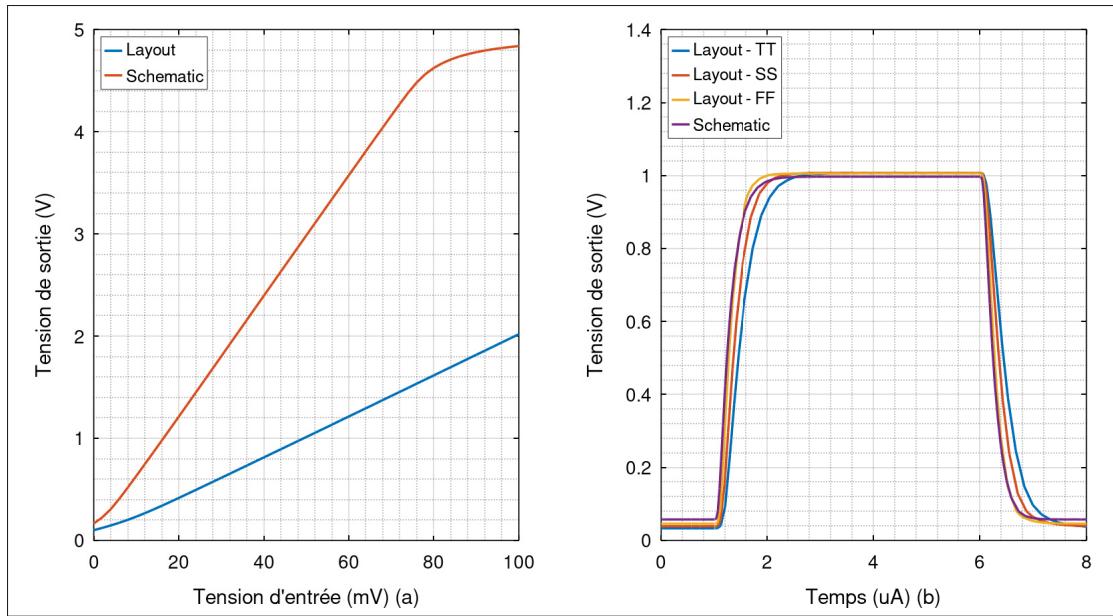

| 4.2.4       | Convertisseur V-I .....                                                                      | 143 |

| 4.2.5       | Courant de sortie .....                                                                      | 145 |

| 4.2.6       | Amplificateur d'instrumentation .....                                                        | 145 |

| 4.2.7       | Comparateur .....                                                                            | 147 |

| 4.3         | Comparaison de 4 puces sur 4 PCB différents .....                                            | 147 |

| 4.4         | Test avec le prototype de commutateur MEMS .....                                             | 148 |

|             | CONCLUSION .....                                                                             | 151 |

|             | RECOMMANDATIONS .....                                                                        | 155 |

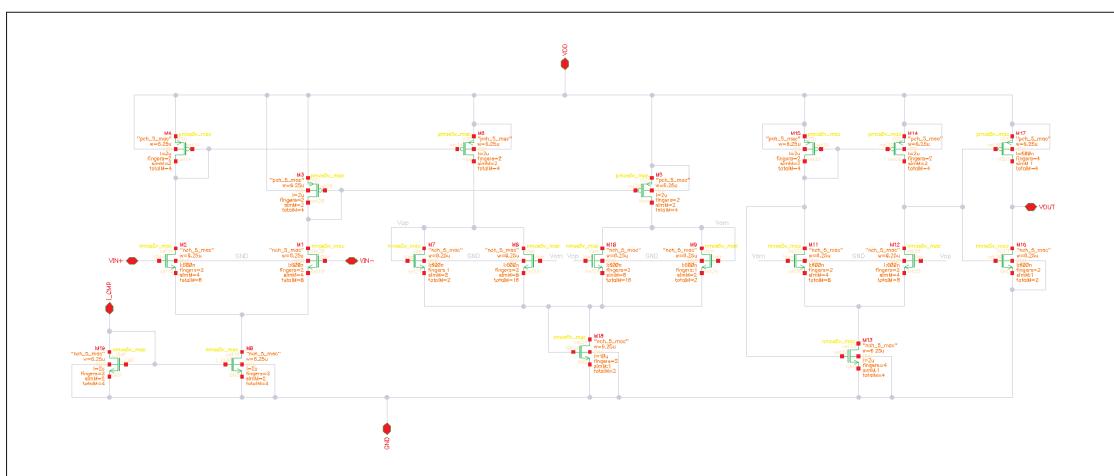

| ANNEXE I    | ARBRE HIÉRARCHIQUE DE CONCEPTION DANS LE LOGICIEL<br>CADENCE .....                           | 159 |

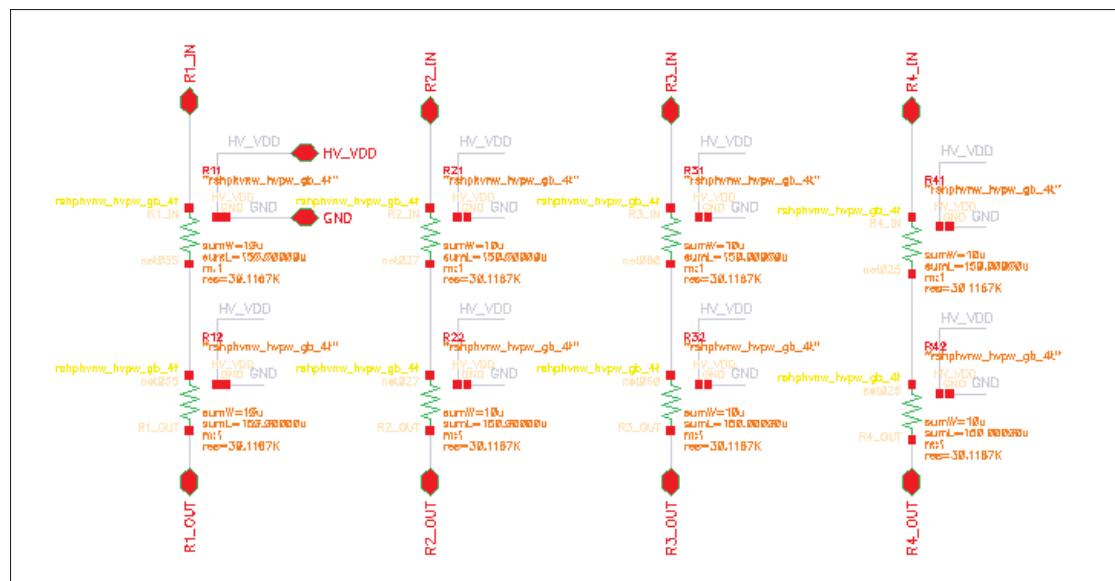

| ANNEXE II   | SCHÉMAS ÉLECTRIQUES DES DIFFÉRENTS CIRCUITS DE LA<br>PUCE CMOS .....                         | 165 |

| ANNEXE III  | RÉSUMÉ DES PERFORMANCES DES CIRCUITS DE LA PUCE<br>CMOS .....                                | 177 |

| ANNEXE IV   | DIMENSIONS DES COMPOSANTS ÉLECTRIQUES DES<br>CIRCUITS .....                                  | 181 |

| ANNEXE V    | CODE MATLAB DU MODÈLE DE PREMIER ORDRE DU<br>$\mu$ HEATER .....                              | 185 |

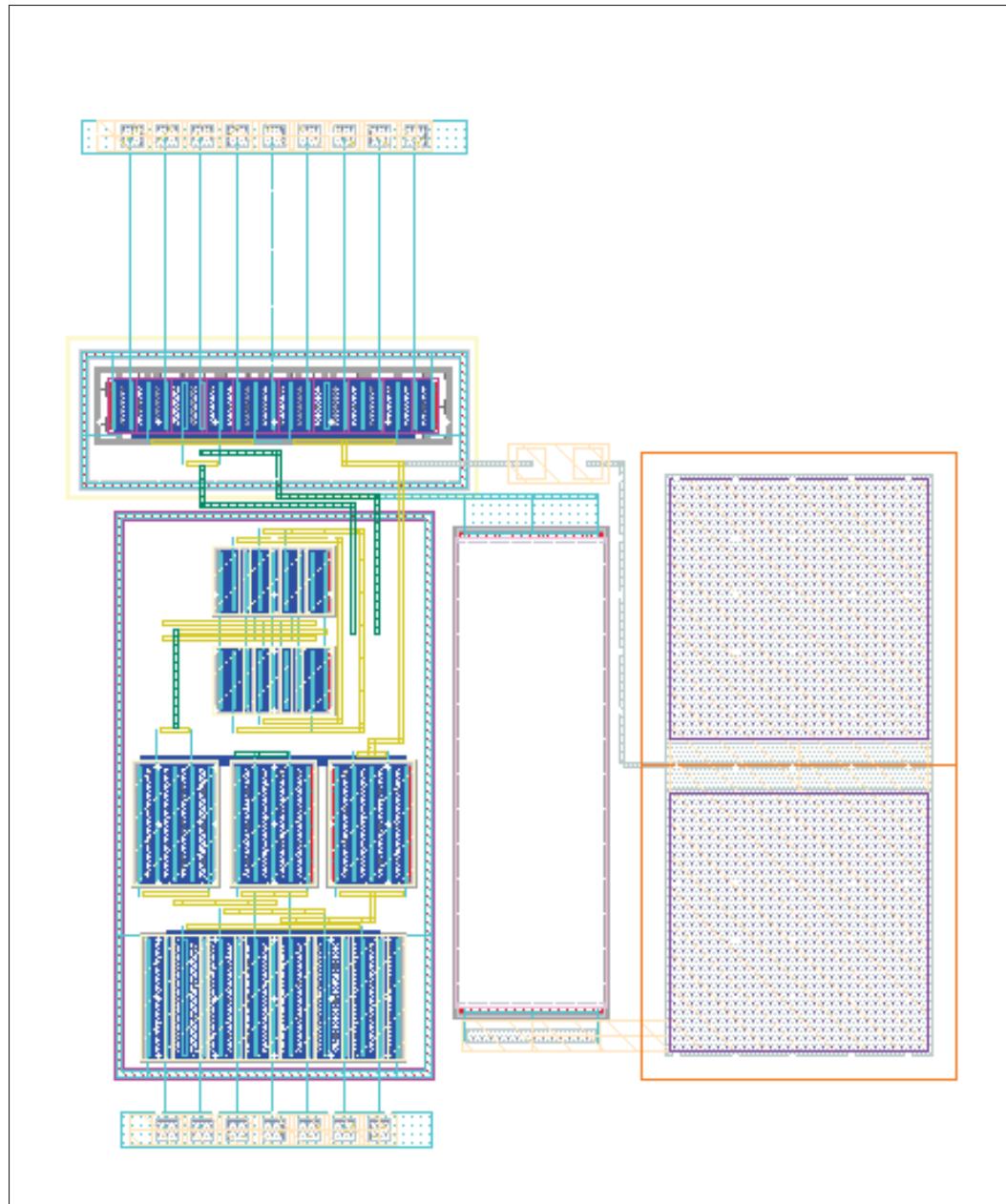

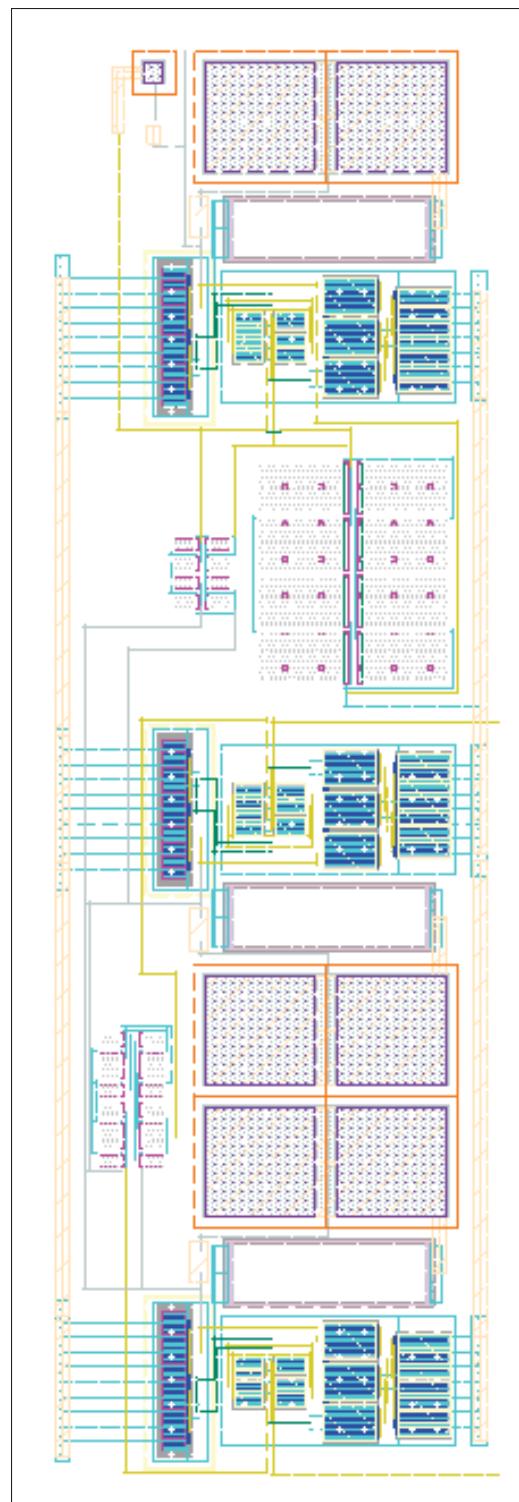

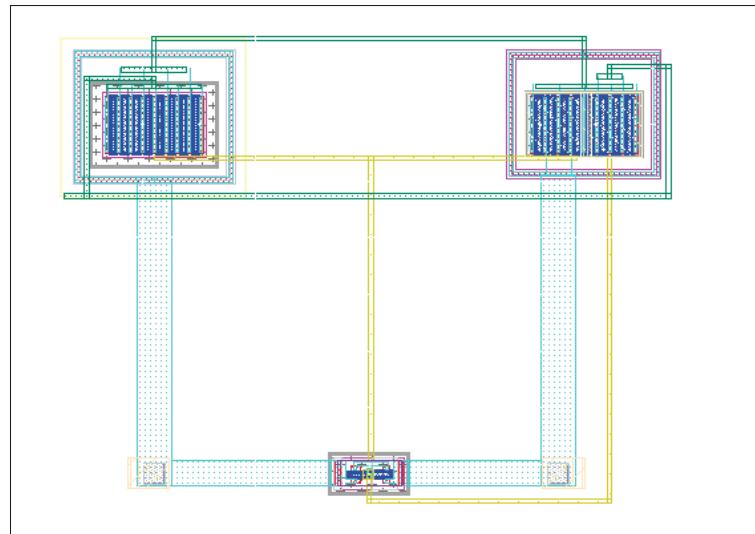

| ANNEXE VI   | DESSINS DE MASQUE DES DIFFÉRENTS CIRCUITS DE LA PUCE<br>CMOS .....                           | 193 |

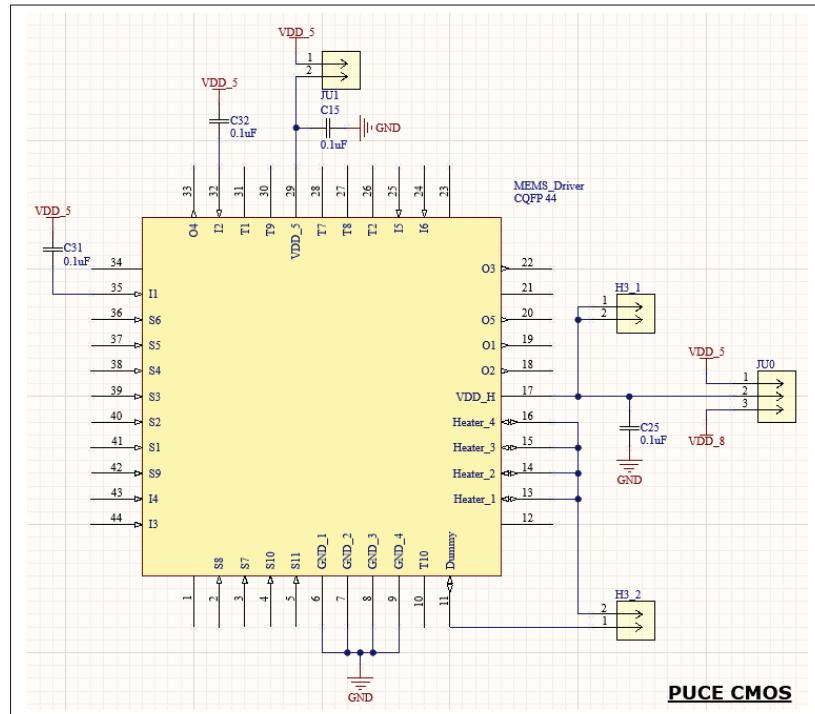

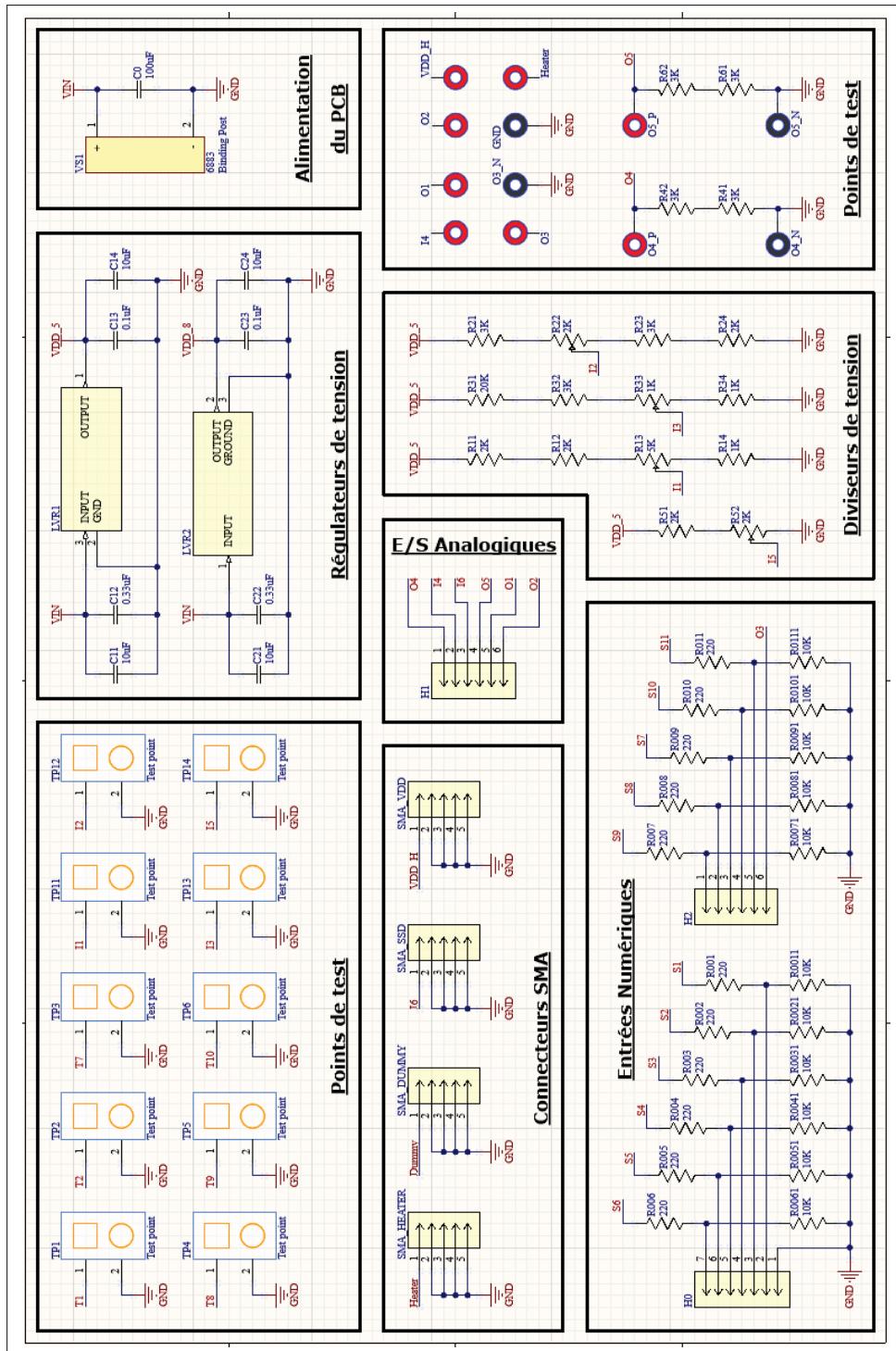

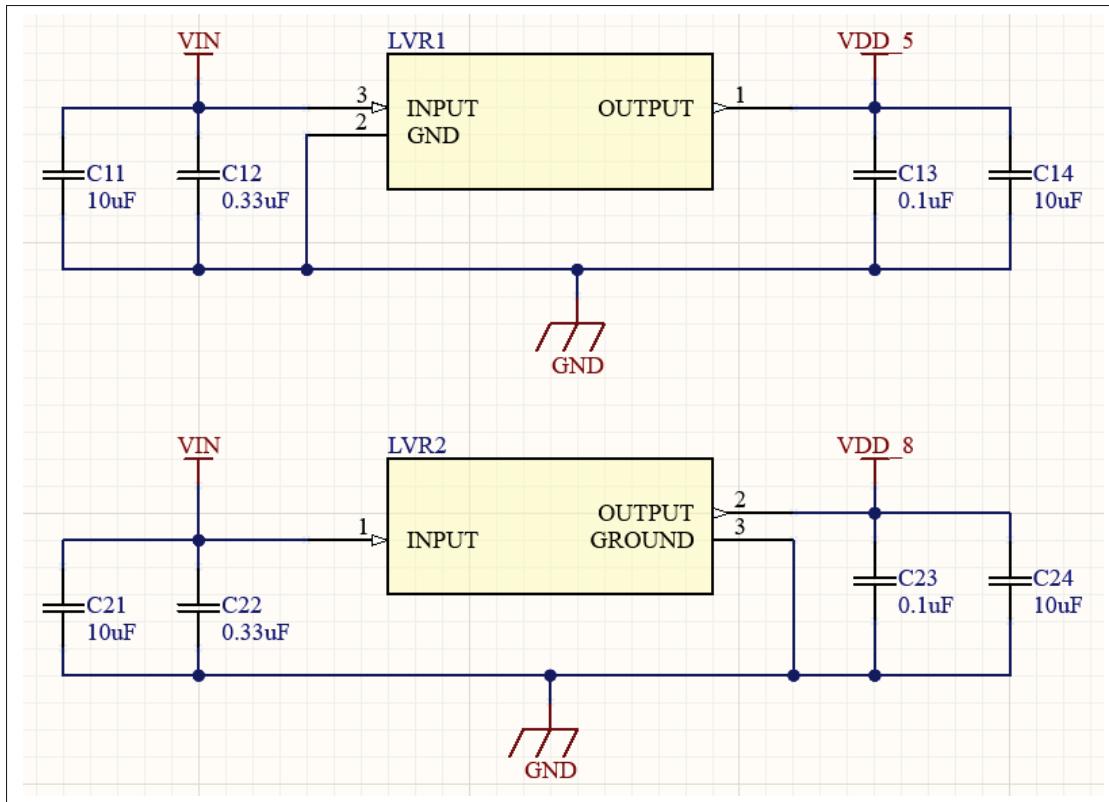

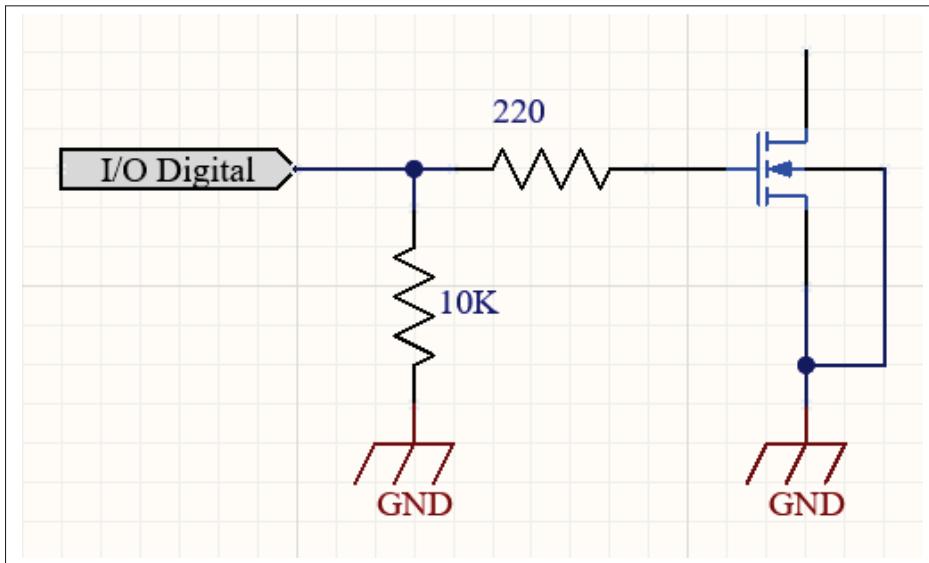

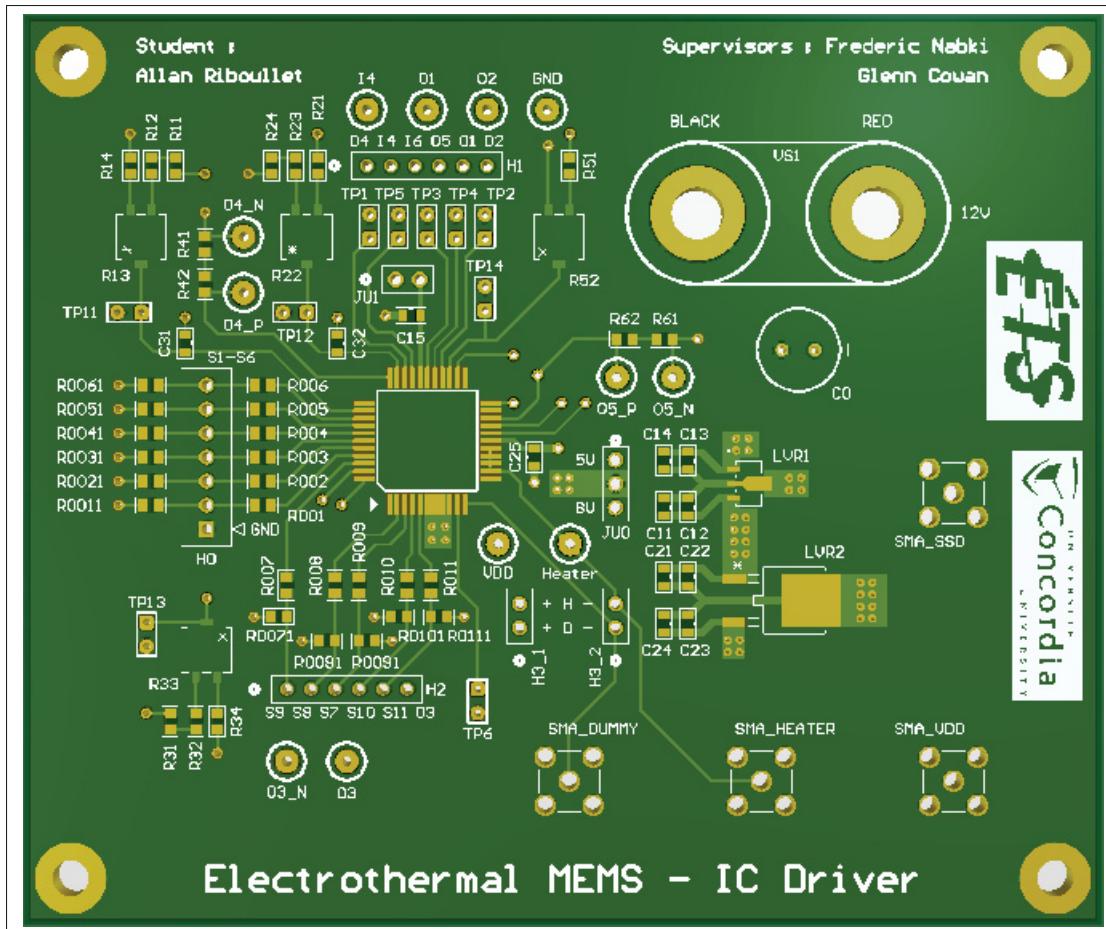

| ANNEXE VII  | CONCEPTION D'UN CIRCUIT IMPRIMÉ (PCB) POUR LES ESSAIS<br>EXPÉRIMENTAUX DE LA PUCE CMOS ..... | 205 |

| ANNEXE VIII | CODE ARDUINO POUR GÉNÉRER LES SIGNAUX PWM ET/OU<br>D'HORLOGE .....                           | 229 |

| ANNEXE IX   | ARTICLE DE CONFÉRENCE - ISCAS 2024 .....                                                     | 233 |

|             | BIBLIOGRAPHIE .....                                                                          | 237 |

## LISTE DES TABLEAUX

|             | Page                                                                                                                                                 |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 | Comparaison des performances des commutateurs MEMS pour chaque physique d'actionnement Adapté de (Cao, Hu & Zhao, 2020, p. 4) .....                  | 17  |

| Tableau 1.2 | Fiabilité des commutateurs MEMS : problèmes courants et solutions proposées Adapté de (Goggin, Fitzgerald, Wong, Hecht & Schirmer, 2011, p. 3) ..... | 20  |

| Tableau 1.3 | Équivalence entre un système électrique et thermique Tiré de (Wikipedia, 2024) .....                                                                 | 25  |

| Tableau 2.1 | Comparaison des performances de diverses architectures d'amplificateurs différentiels Tiré de (Razavi, 2017, p. 374) .....                           | 56  |

| Tableau 3.1 | Courant de référence - Analyse des <i>corners</i> et de Monte Carlo .....                                                                            | 99  |

| Tableau 3.2 | Analyse de Monte Carlo pour l'actionnement du commutateur .....                                                                                      | 117 |

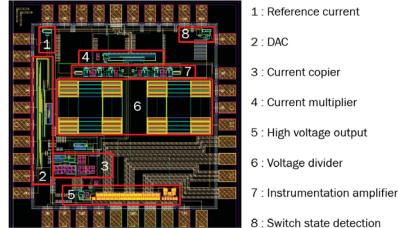

| Tableau 3.3 | Nomenclature des circuits sur le <i>layout</i> de la puce .....                                                                                      | 126 |

| Tableau 4.1 | Synthèse du fonctionnement des circuits pour chaque puce testée .....                                                                                | 147 |

## LISTE DES FIGURES

|            | Page                                                                                                                                                                                                                                                              |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 0.1 | Illustration CPIOS : (a) Vue en coupe du SiP, (b) Schéma bloc Tirée de (Nobert, Alameh, Ly, Constantin & Blaqui  re, 2021, p.2) .....                                                                                                                             | 4  |

| Figure 0.2 | Illustration en 3D du prototype d'un commutateur MEMS electrothermique en forme de V Tir  e de (Shuaibu, Nabki & Blaqui  re, 2022, p. 318) .....                                                                                                                  | 6  |

| Figure 0.3 | Donn  es exp  imentales du prototype de commutateur MEMS : (a) Relation I-V, (b) Profil de temp  rature Tir  es de (Shuaibu <i>et al.</i> , 2022, p. 3-4) .....                                                                                                   | 7  |

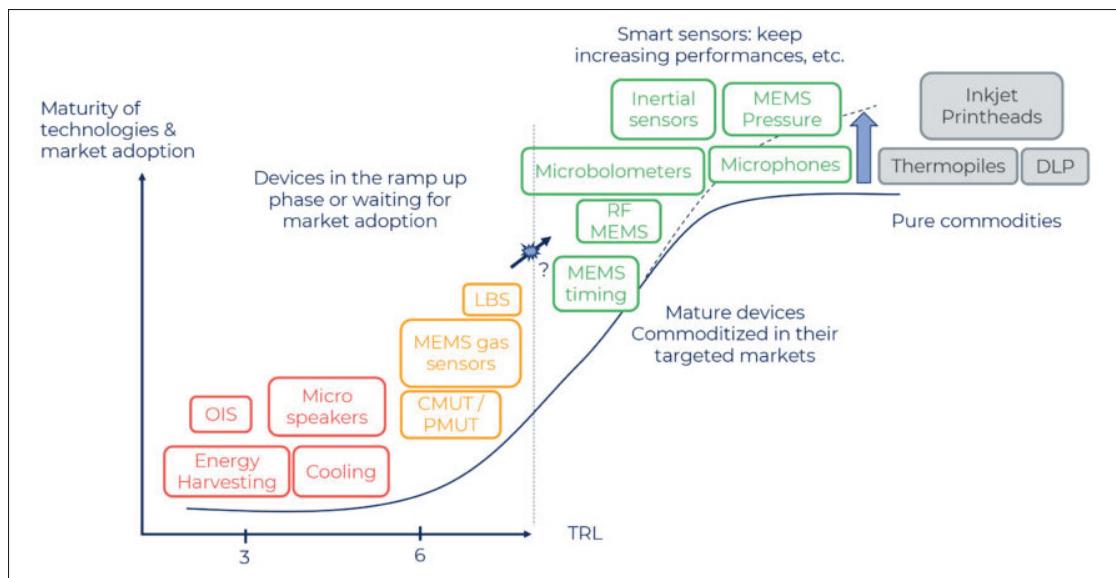

| Figure 1.1 | Croissance des produits MEMS sur le march   Tir  e de (Mishra, Dubey, Mishra & Khan, 2019, p. 10) .....                                                                                                                                                           | 14 |

| Figure 1.2 | Industrie des MEMS : qui sera le prochain  franchir le gouffre ? Tir  e de Spherical-Insights (2022) .....                                                                                                                                                       | 15 |

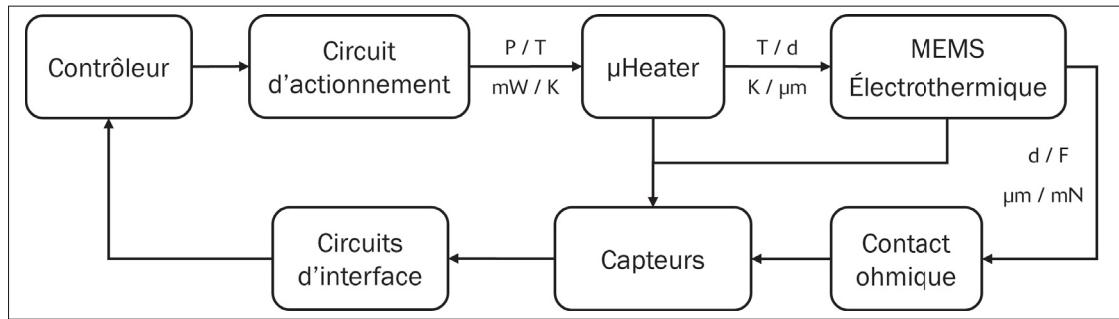

| Figure 1.3 | Sch  ma fonctionnel d'un syst  me de contr  le pour un commutateur MEMS electrothermique .....                                                                                                                                                                    | 21 |

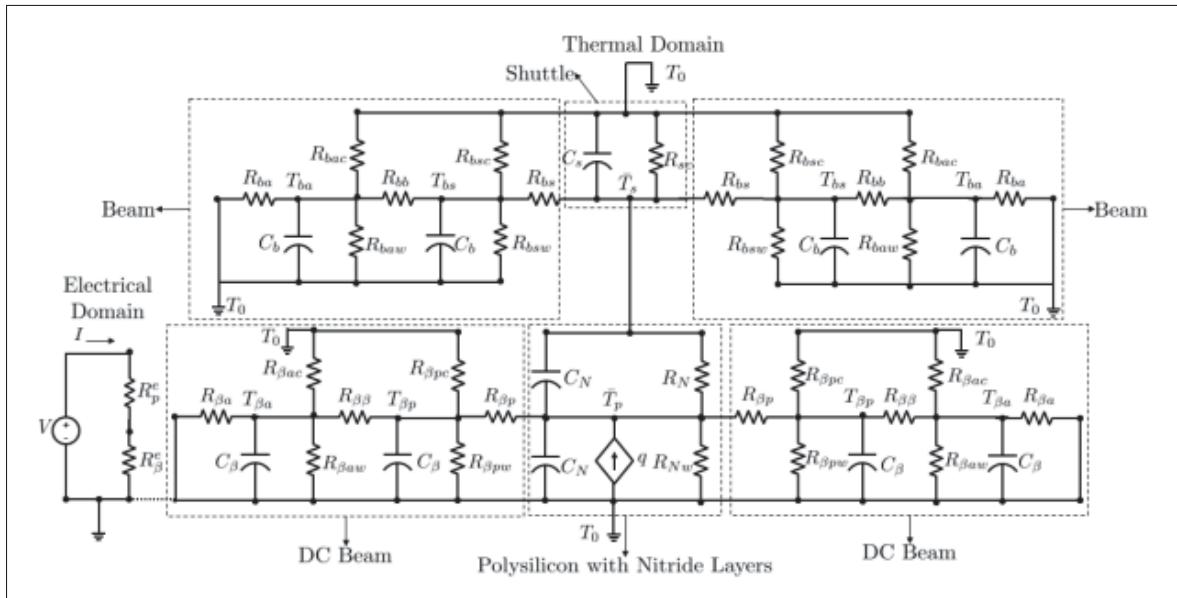

| Figure 1.4 | Mod  le LEM d'un commutateur MEMS electrothermique en V Tir  e de (Estahbanati, 2017, p. 35) .....                                                                                                                                                                | 25 |

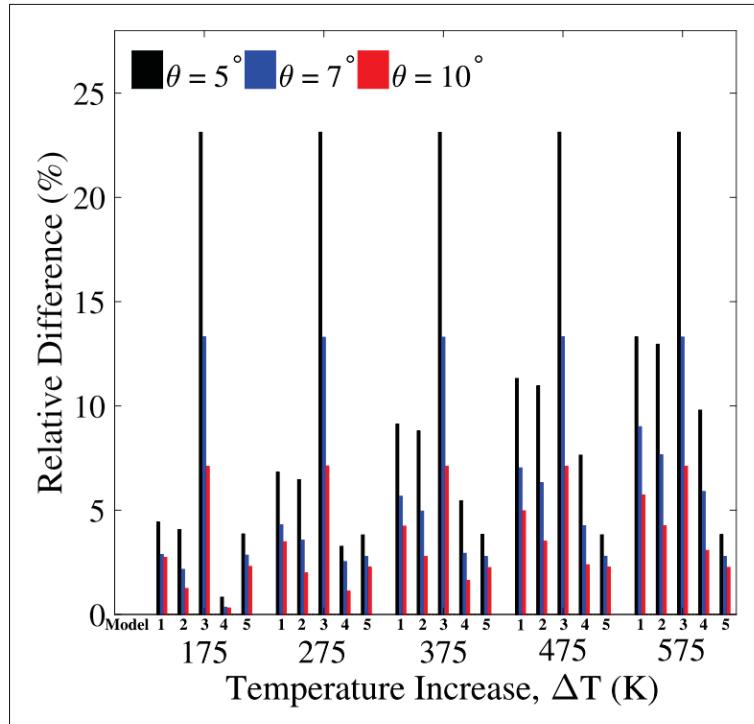

| Figure 1.5 | Erreur relative entre la d  formation de la poutre calcul  e  partir des mod  les 1  5 et celle calcul  e  l'aide de la m  thode des l  ments finis. Tir  e de (Cohen & Ya'akovitz, 2019, p. 3770) .....                                                      | 27 |

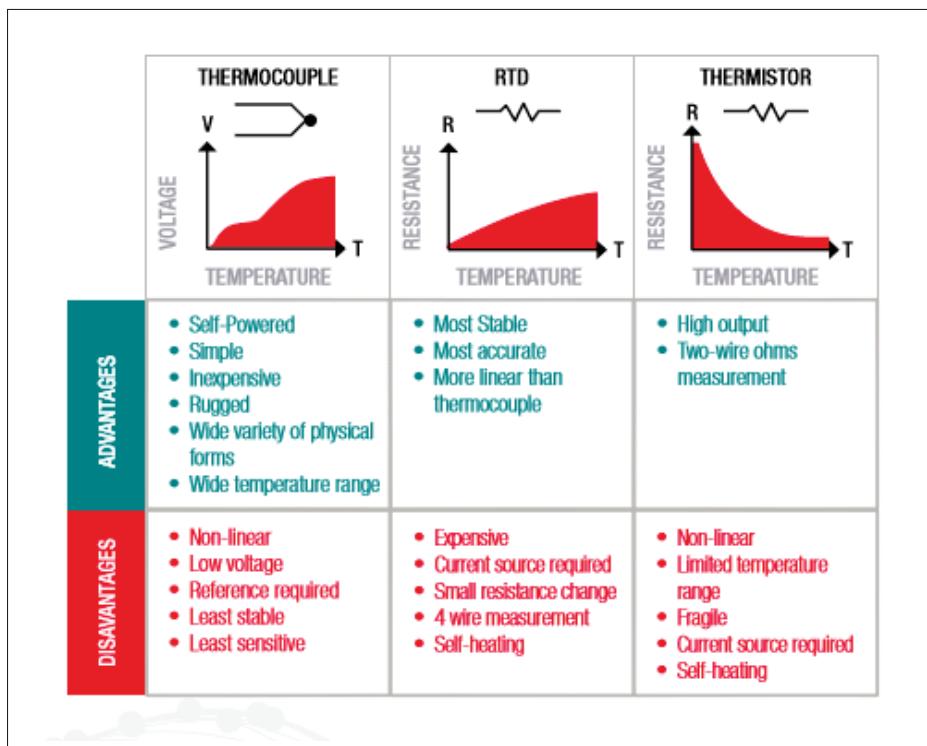

| Figure 1.6 | Comparaison des capteurs de temp  rature : avantages et inconv  nients Tir  e de (Keysight) .....                                                                                                                                                                 | 28 |

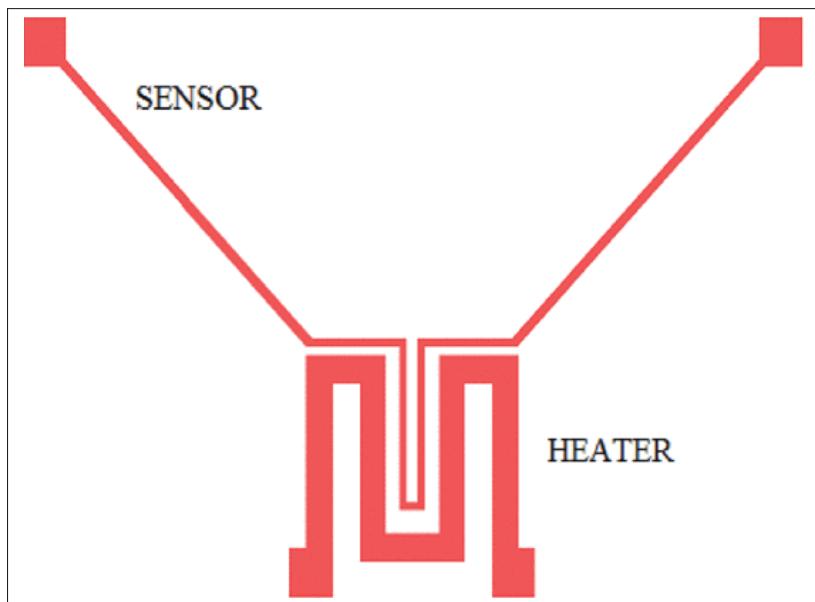

| Figure 1.7 | Thermistor int  gr   au plus proche d'un $\mu$ heater Tir  e de (Mendoza-Acevedo, Reyes-Barranca, Flores-Nava, vila Garc  a & Gonz  lez-Vidal, 2009, p. 2) .....                                                                                                 | 29 |

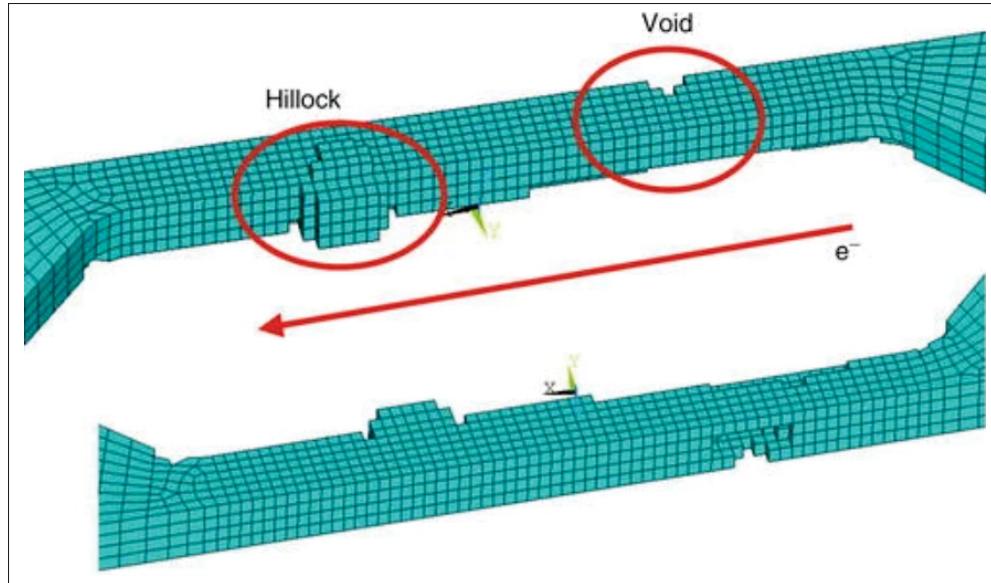

| Figure 1.8 | Illustration de l'effet d'electromigration Tir  e de (Liu, 2014, p. 5263) ...                                                                                                                                                                                     | 33 |

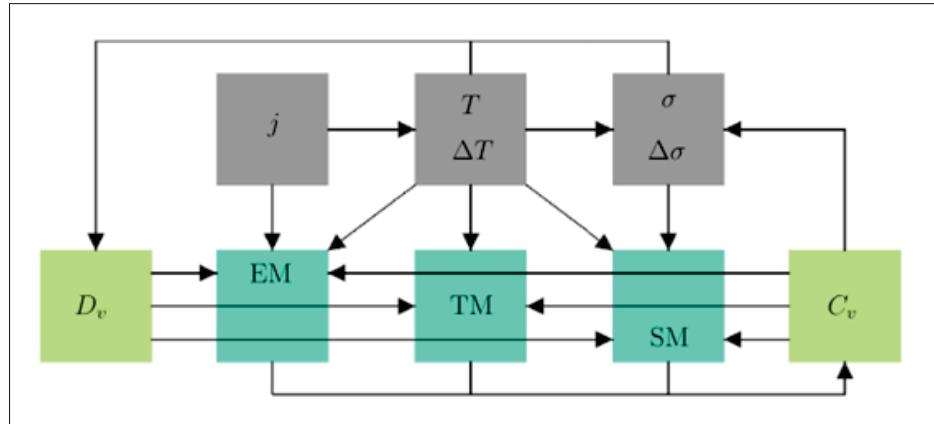

| Figure 1.9 | Repr  sentation des d  pendances entre EM, TM et SM, leurs forces motrices $j$ , $T$ , $\Delta T$ , $\sigma$ , $\Delta\sigma$ et les param  tres du mouvement des <i>void</i> : diffusivit   $D_v$ et concentration $C_v$ Tir  e de (Filipovic, 2021, p. 5) ..... | 35 |

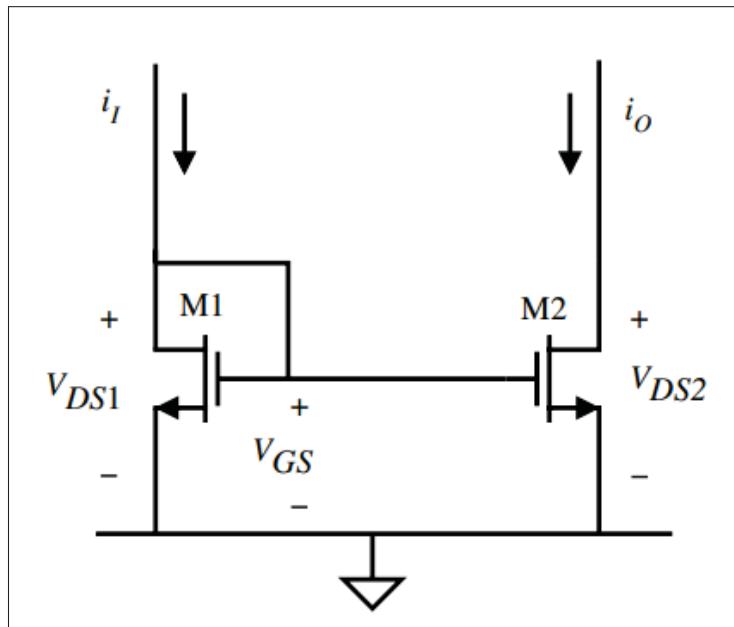

| Figure 2.1 | Miroir de courant NMOS Tir  e de (Allen & Holberg, 2012, p. 138) .....                                                                                                                                                                                            | 44 |

|             |                                                                                                                                                                         |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

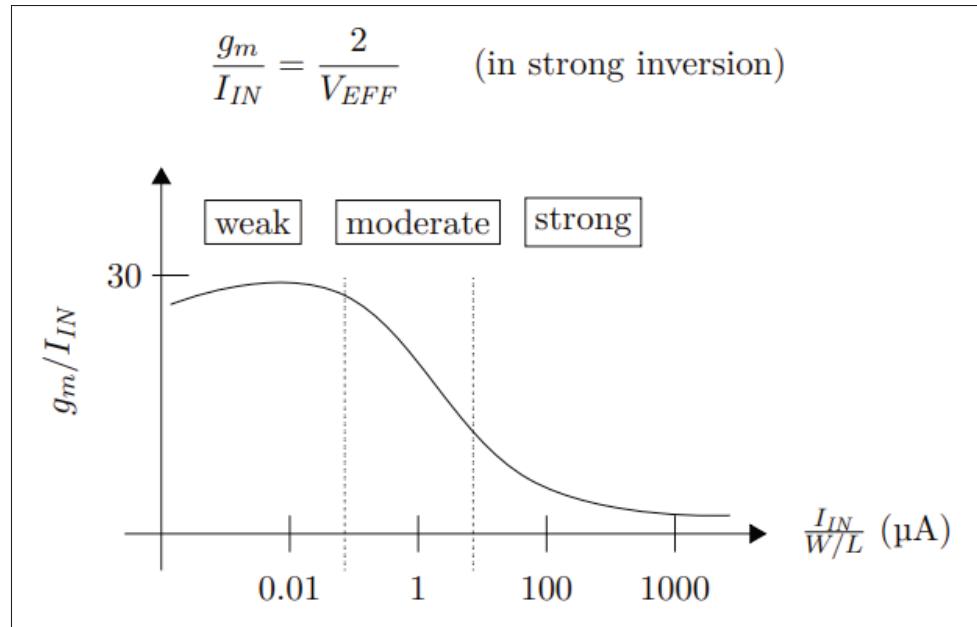

| Figure 2.2  | Courbe du ratio $\frac{g_m}{I_{IN}}$ en fonction du courant de drain normalisé Tirée de (Mohan, 2018, p. 40) .....                                                      | 47 |

| Figure 2.3  | Définition des figures de mérite pour la comparaison des miroirs de courant Tirée de (Mohan, 2018, p. 29) .....                                                         | 48 |

| Figure 2.4  | Miroir de courant NMOS cascode Tirée de (Razavi, 2017, p. 142) .....                                                                                                    | 49 |

| Figure 2.5  | Miroir de courant NMOS Wilson .....                                                                                                                                     | 49 |

| Figure 2.6  | Miroir de courant NMOS à large amplitude Tirée de (Gray, 2009, p. 267) .....                                                                                            | 50 |

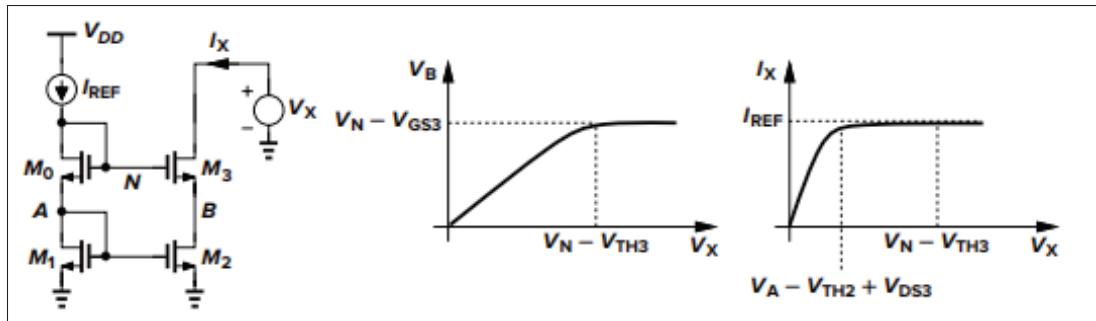

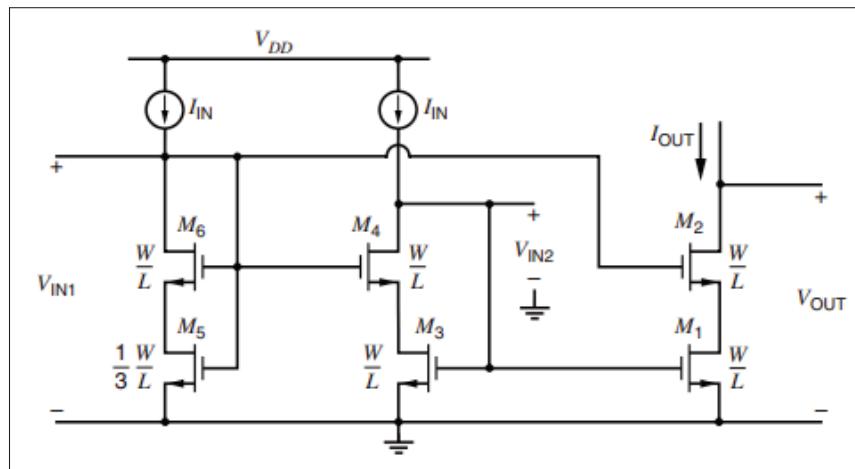

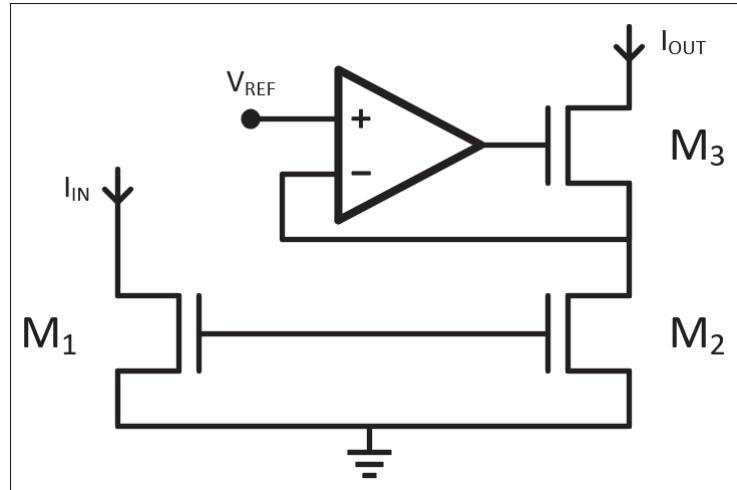

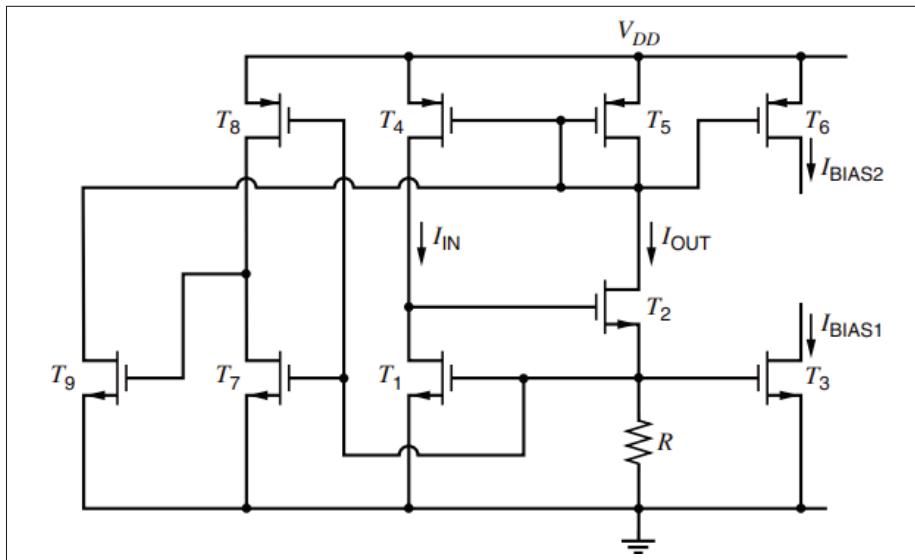

| Figure 2.7  | Miroir de courant NMOS cascode régulée en sortie .....                                                                                                                  | 51 |

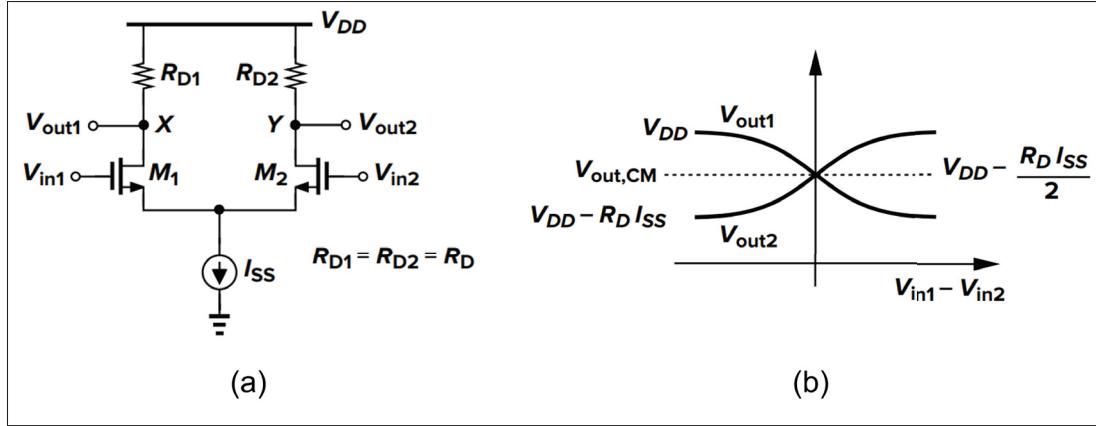

| Figure 2.8  | Amplificateur différentiel avec des charges résistives : (a) Circuit, (b) Relation entre les tensions d'entrée et de sorties Tirées de (Razavi, 2017, p. 102-103) ..... | 53 |

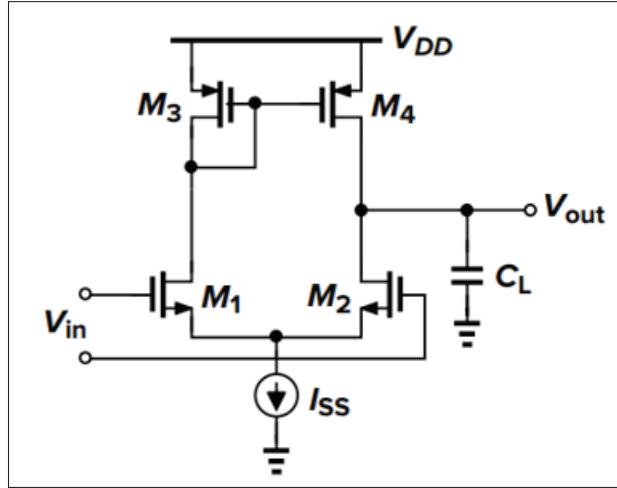

| Figure 2.9  | Amplificateur différentiel avec une charge active Tirée de (Razavi, 2017, p. 349) .....                                                                                 | 54 |

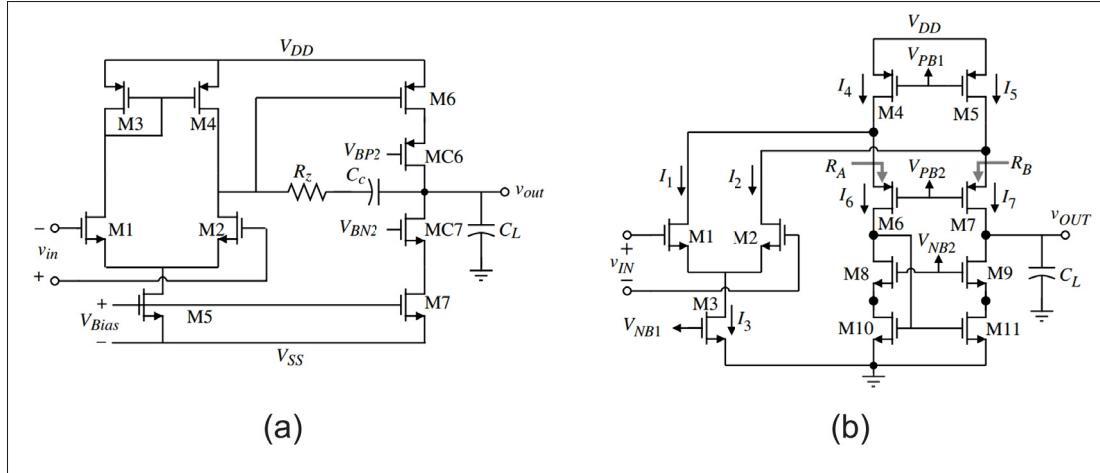

| Figure 2.10 | Amplificateurs opérationnels : (a) 2 étages, (b) Cascode repliée Tirées de (Allen & Holberg, 2012, p. 315-317) .....                                                    | 55 |

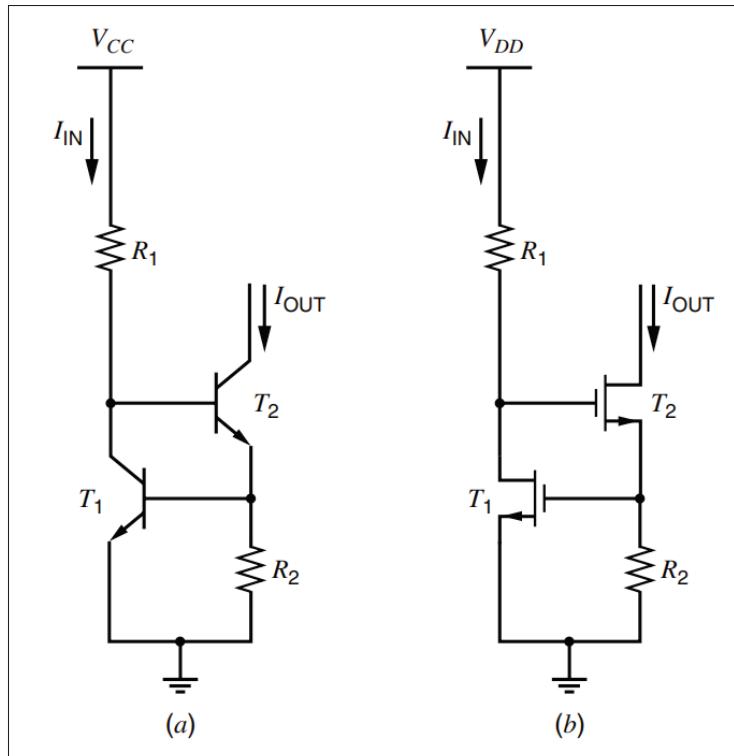

| Figure 2.11 | Sources de courant indépendantes de la tension d'alimentation : (a) Référence $V_{BE}$ , (b) Référence $V_{TH}$ Tirée de (Gray, 2009, p. 306) .....                     | 58 |

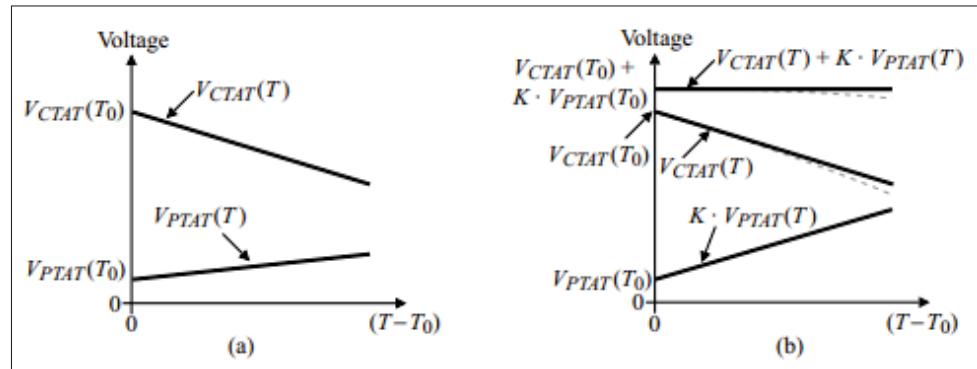

| Figure 2.12 | (a) Illustration des références PTAT et CTAT en fonction de la température, (b) Référence indépendante de la température Tirée de (Allen & Holberg, 2012, p. 157) ..... | 59 |

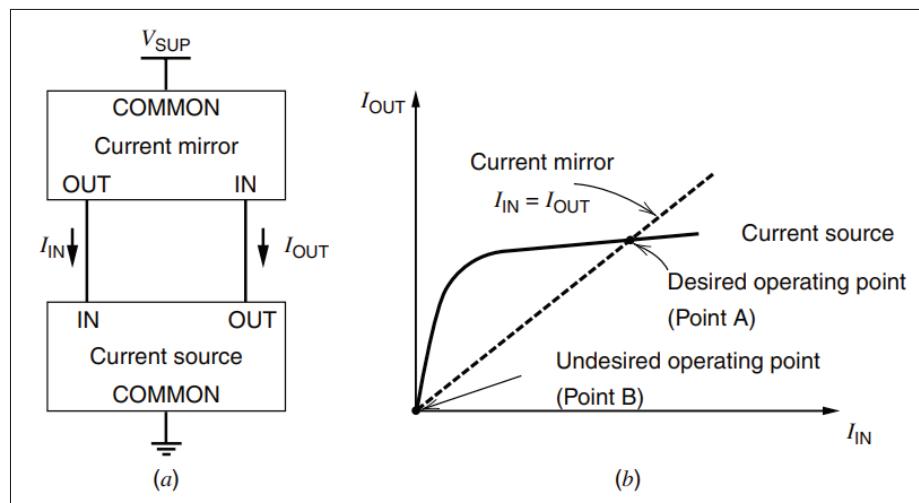

| Figure 2.13 | (a) Schéma fonctionnel d'une référence de courant auto-polarisée, (b) Différents points de fonctionnement Tirée de (Gray, 2009, p. 307) .....                           | 59 |

| Figure 2.14 | Circuit d'une référence de courant $V_{TH}$ auto-polarisée Tirée de (Gray, 2009, p. 310) .....                                                                          | 60 |

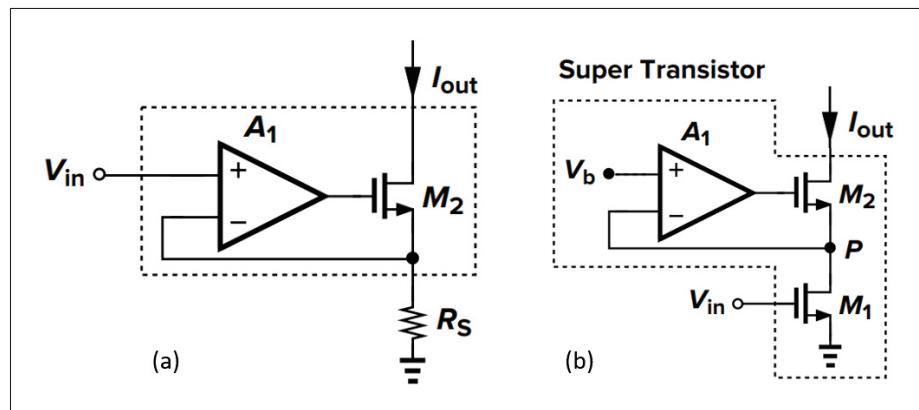

| Figure 2.15 | Convertisseur V-I : (a) Circuit conventionnel, (b) Résistance remplacée par un transistor CMOS Tirées de (Razavi, 2017, p. 364-366) .....                               | 61 |

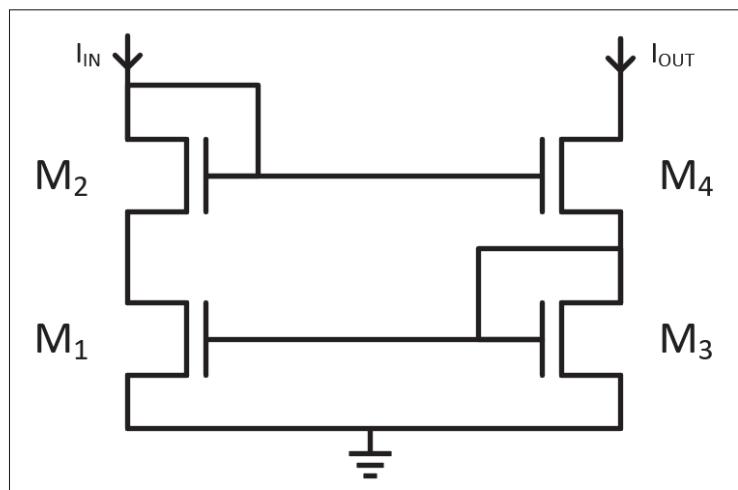

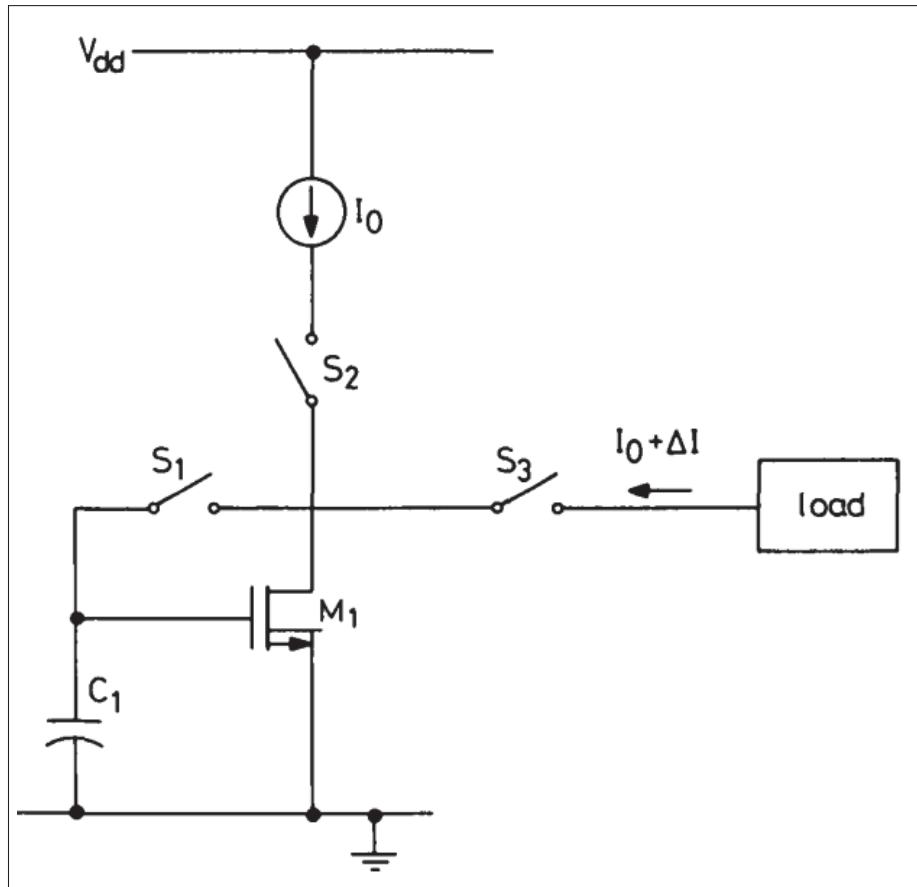

| Figure 2.16 | Circuit conventionnel d'une cellule copieuse de courant Tirée de (Daubert & Vallancourt, 1990, p. 109) .....                                                            | 67 |

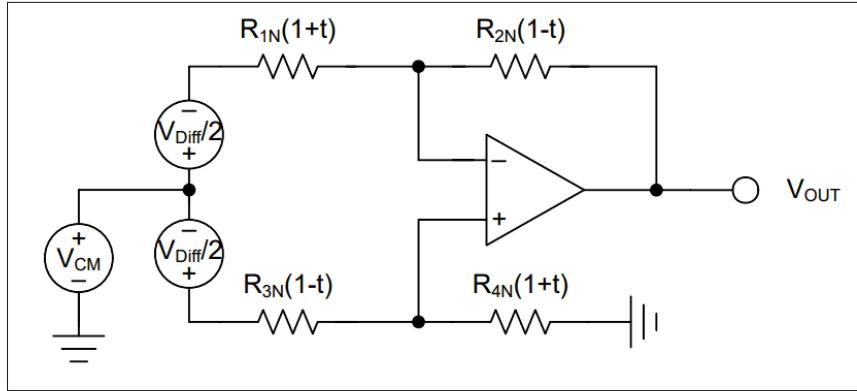

| Figure 2.17 | Amplificateur différentiel utilisant des résistances appariées Tirée de (Olson, 2023, p. 3) .....                                                                       | 73 |

|             |                                                                                                                                                                                                                                                                                                  |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.18 | Amplificateur différentiel utilisant des résistances non parfaitement appariées Tirée de (Olson, 2023, p. 9) .....                                                                                                                                                                               | 74  |

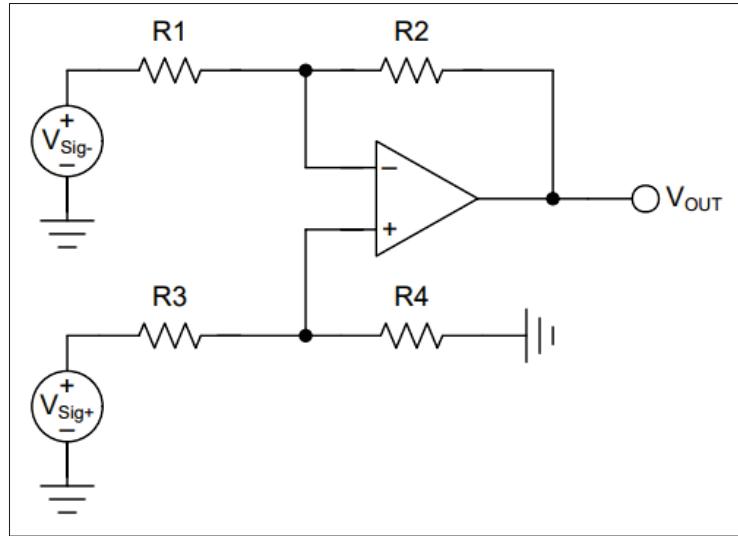

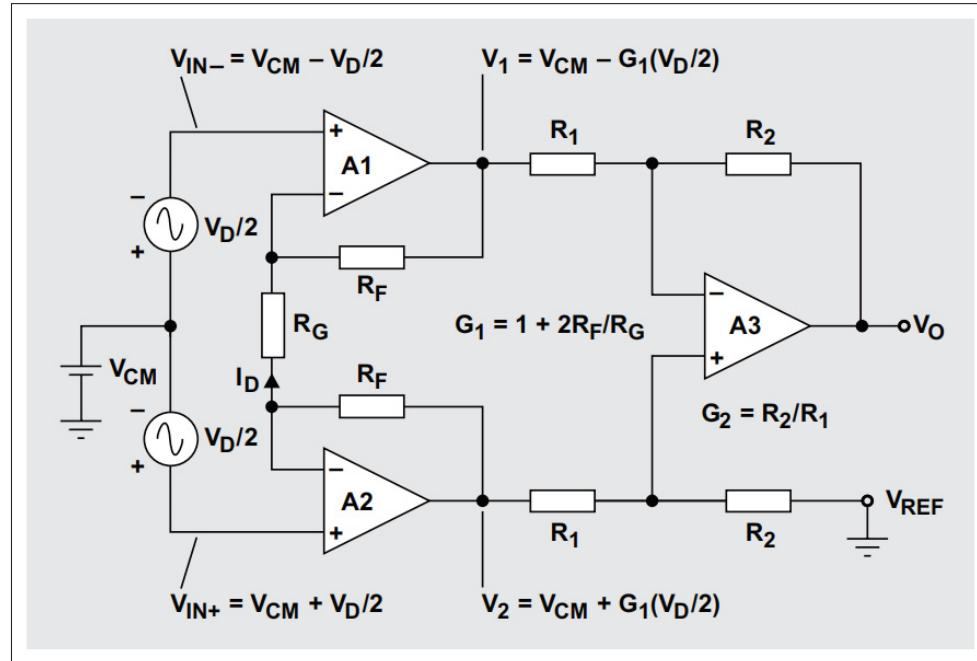

| Figure 2.19 | Circuit conventionnel d'un amplificateur d'instrumentation Tirée de (Kugelstadt, 2005, p. 25) .....                                                                                                                                                                                              | 75  |

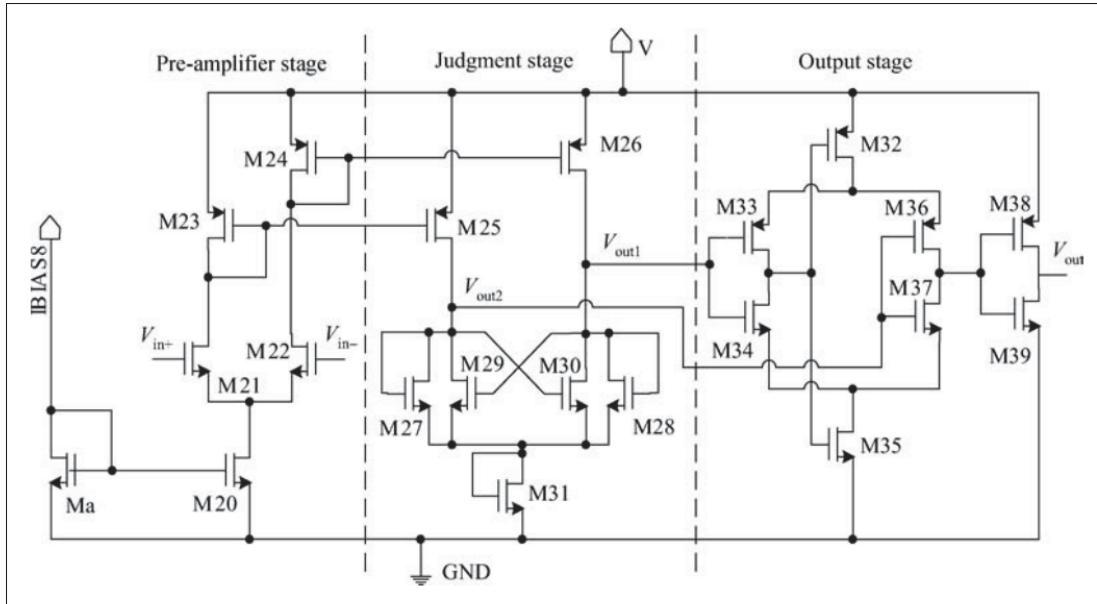

| Figure 2.20 | Comparateur à haute vitesse Tirée de (Liu, Zhu & Yang, 2012, p. 4) .....                                                                                                                                                                                                                         | 78  |

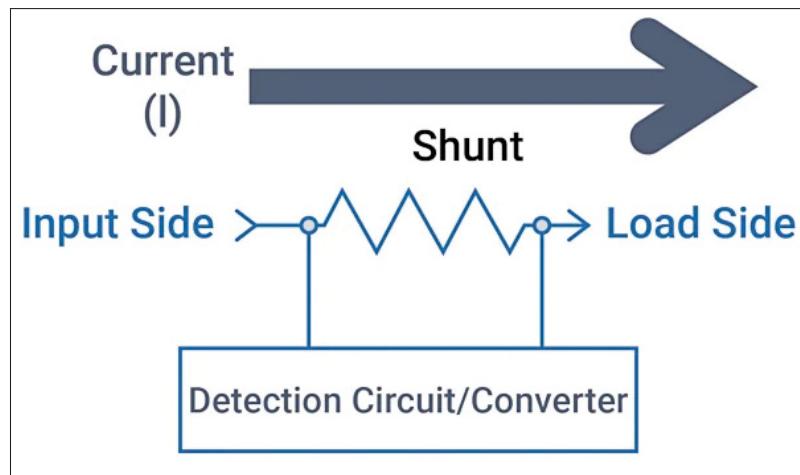

| Figure 2.21 | Illustration du principe d'une résistance shunt Tirée de (ROHM) .....                                                                                                                                                                                                                            | 79  |

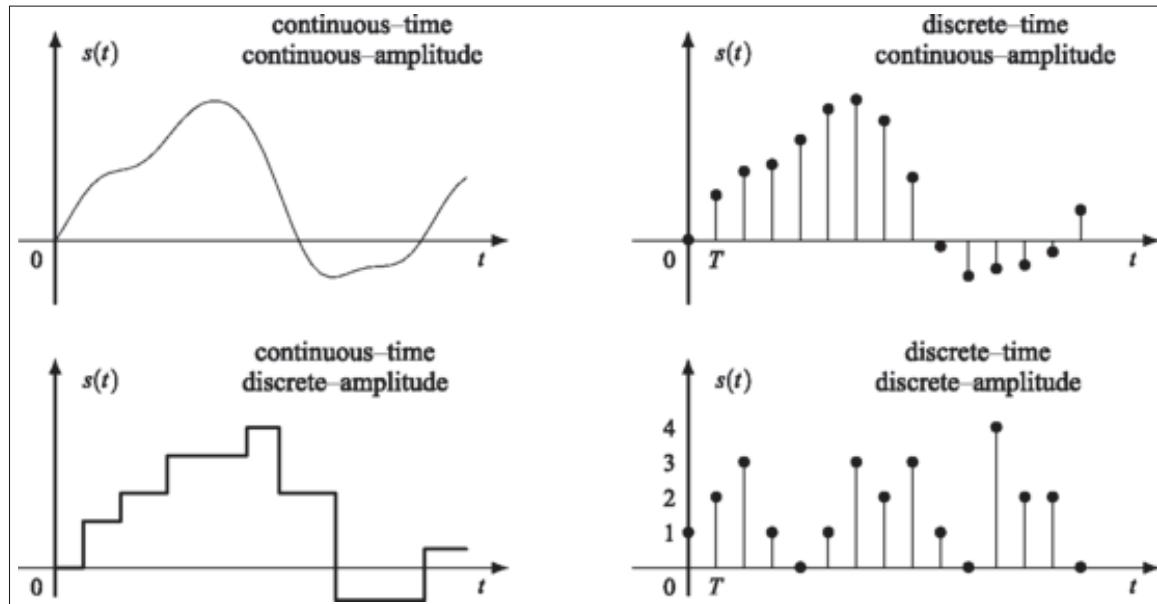

| Figure 2.22 | Illustration des signaux mixtes Tirée de (Cariolaro, 2011, p. 3) .....                                                                                                                                                                                                                           | 80  |

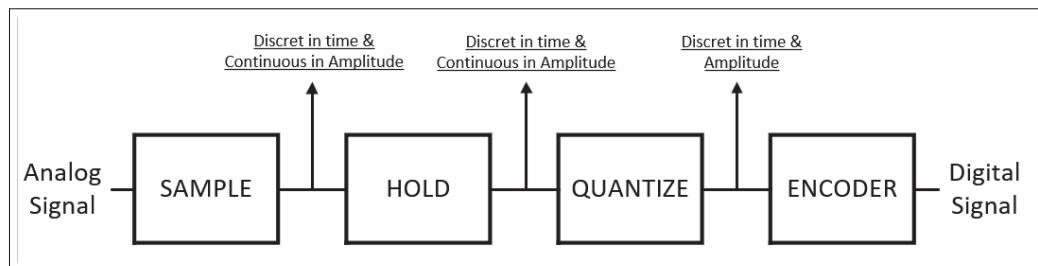

| Figure 2.23 | Schéma fonctionnel d'un ADC Tirée de (He, Tian, Wei, Tian & He, 2023, p. 2) .....                                                                                                                                                                                                                | 81  |

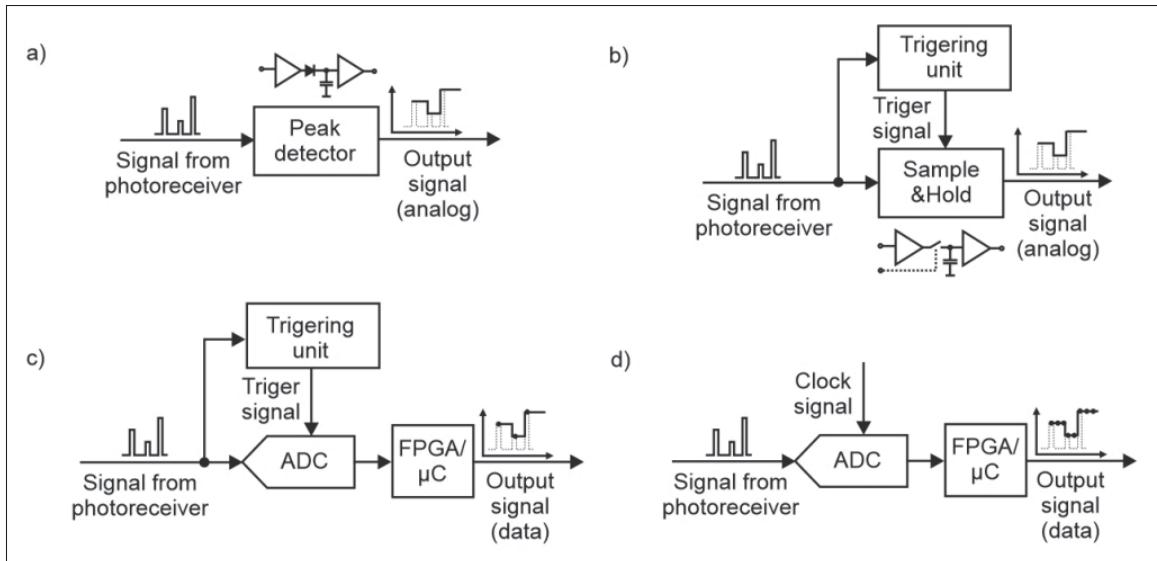

| Figure 2.24 | Différentes architectures de détecteur de crête : (a) Standard, (b) Avec une fonction d'échantillonnage et de maintien, (c) Un ADC avec signal de déclenchement, (d) Un ADC avec un signal d'horloge rapide Tirée de (Achtenberg, Mikołajczyk, Szabra, Prokopiuk & Bielecki, 2020, p. 204) ..... | 83  |

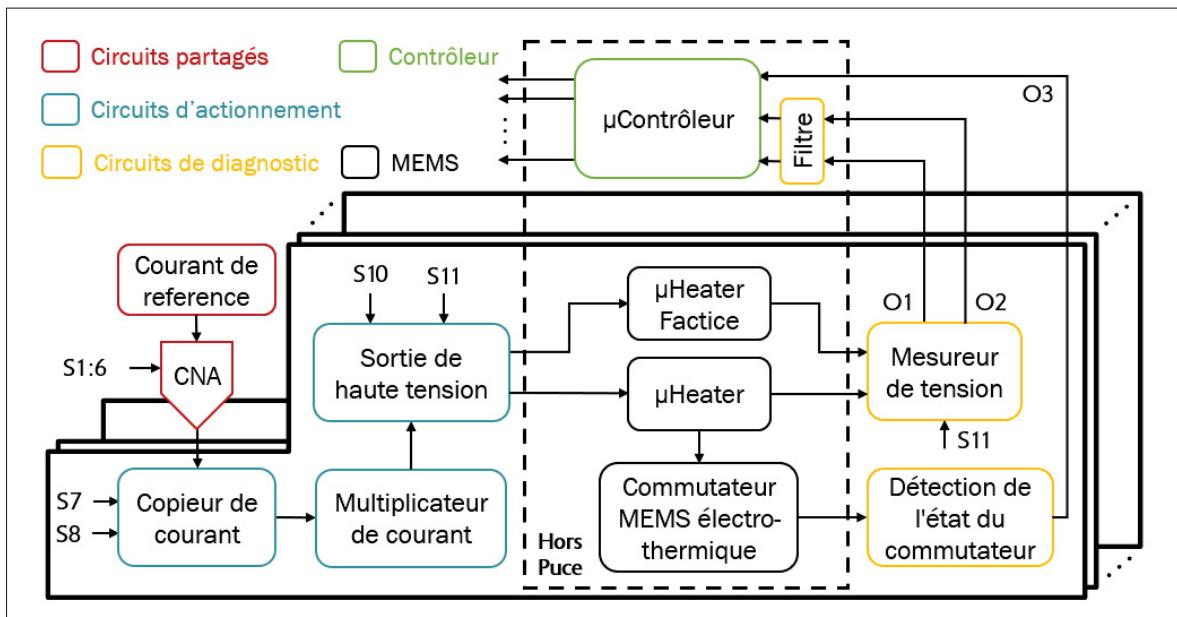

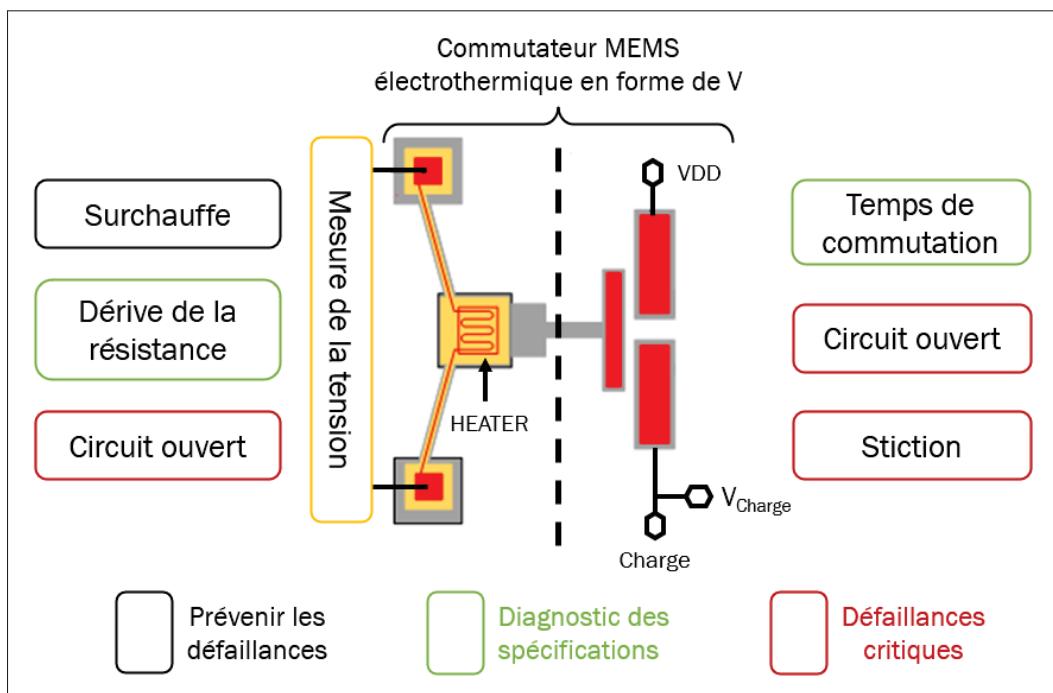

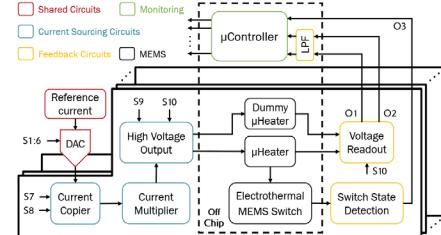

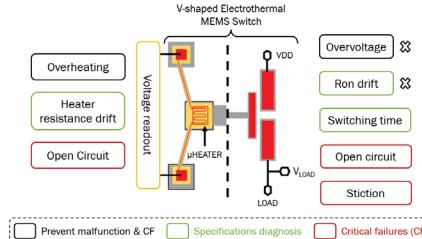

| Figure 3.1  | Schéma fonctionnel des circuits CMOS de la puce .....                                                                                                                                                                                                                                            | 87  |

| Figure 3.2  | Les défaillances d'un commutateur MEMS électrothermique et de son actionneur .....                                                                                                                                                                                                               | 90  |

| Figure 3.3  | Schéma fonctionnel des circuits de la puce CMOS fabriquée .....                                                                                                                                                                                                                                  | 92  |

| Figure 3.4  | Éléments d'un kit de conception et leur relation avec les différentes étapes de la conception Tirée de (Lienig & Scheible, 2021, p.120) .....                                                                                                                                                    | 97  |

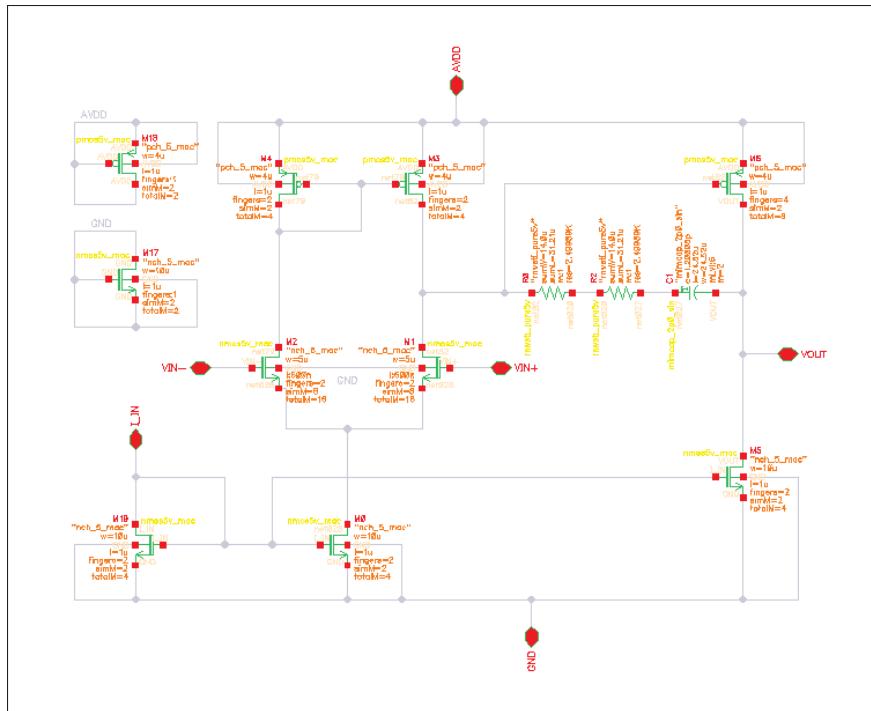

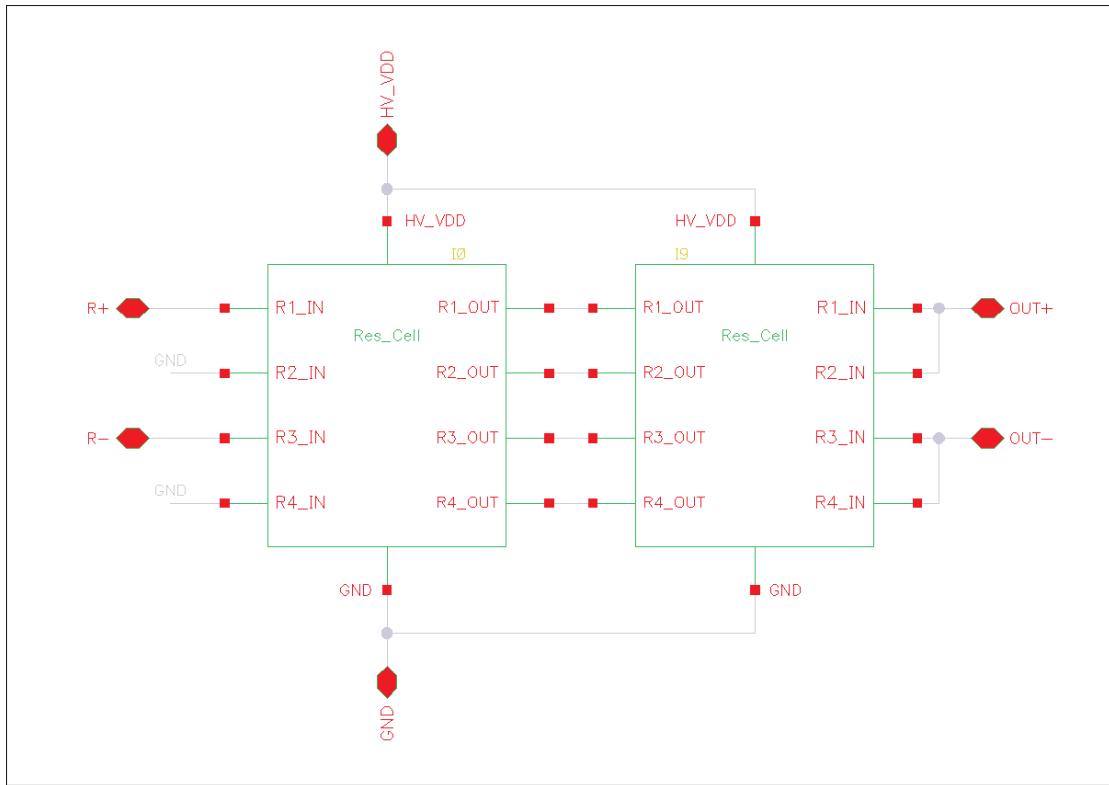

| Figure 3.5  | Circuits partagés comprenant la référence de courant et le convertisseur numérique analogique .....                                                                                                                                                                                              | 98  |

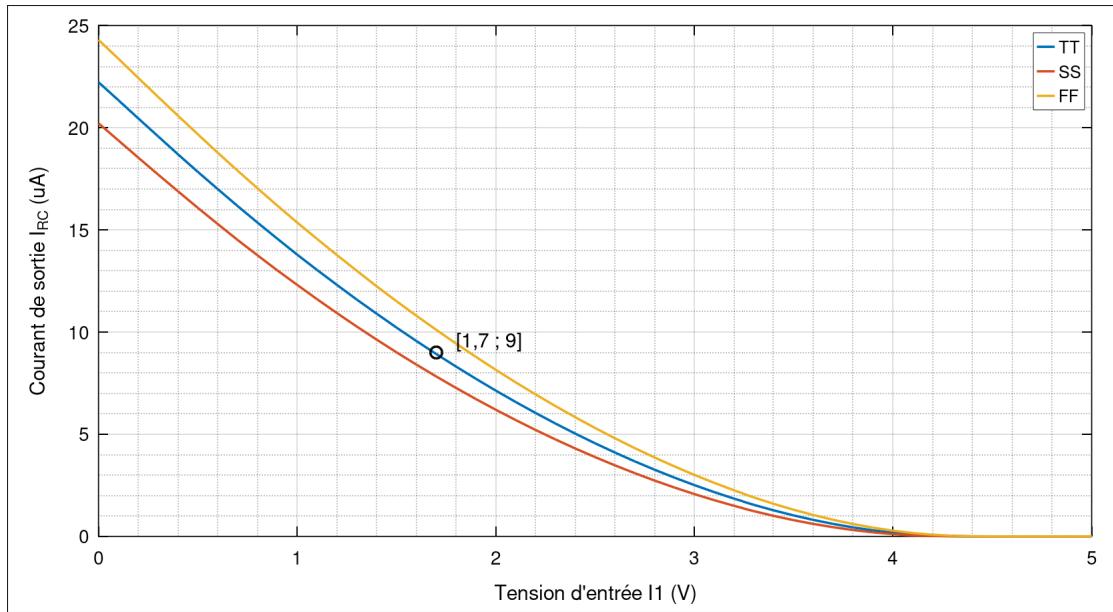

| Figure 3.6  | Variation du courant de référence $I_{RC}$ en fonction de la tension d'entrée I1 .....                                                                                                                                                                                                           | 99  |

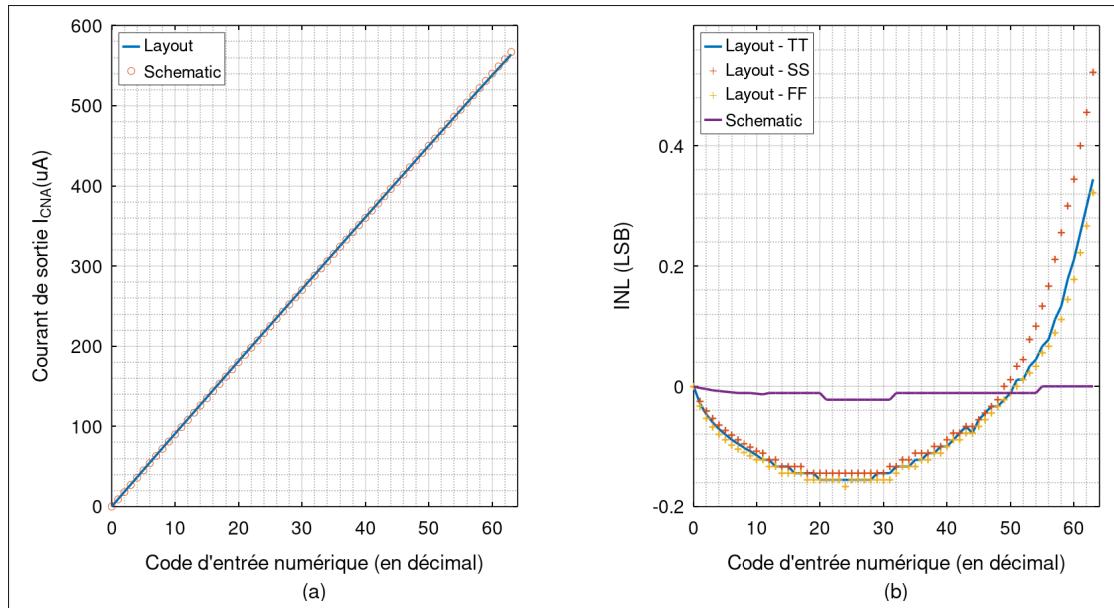

| Figure 3.7  | Simulations du CNA par rapport au code d'entrée numérique : (a) Variation du courant $I_{CNA}$ , (b) INL .....                                                                                                                                                                                   | 101 |

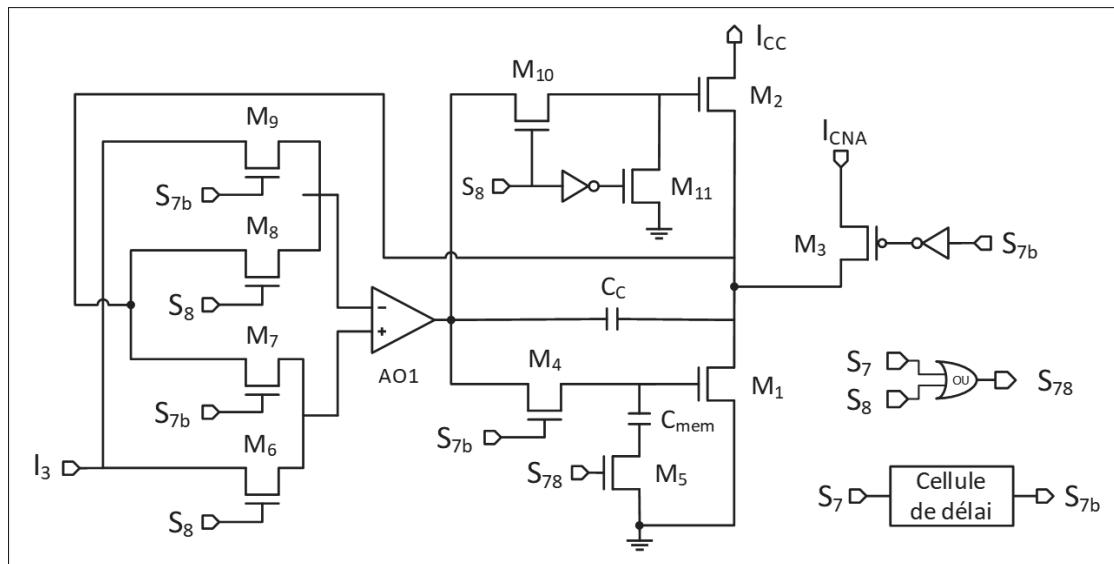

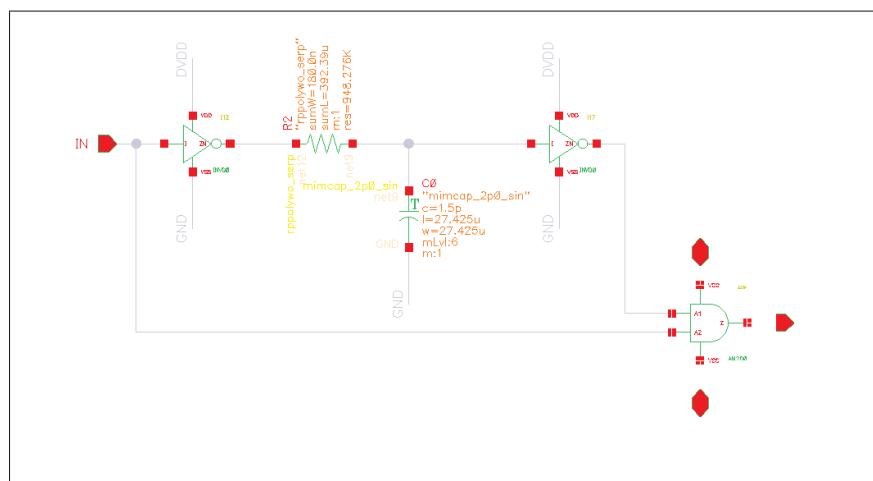

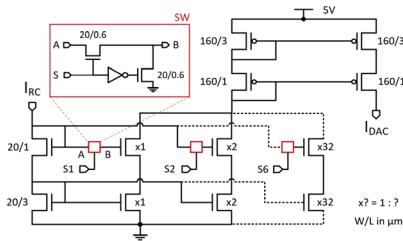

| Figure 3.8  | Circuit de la cellule copieuse de courant .....                                                                                                                                                                                                                                                  | 101 |

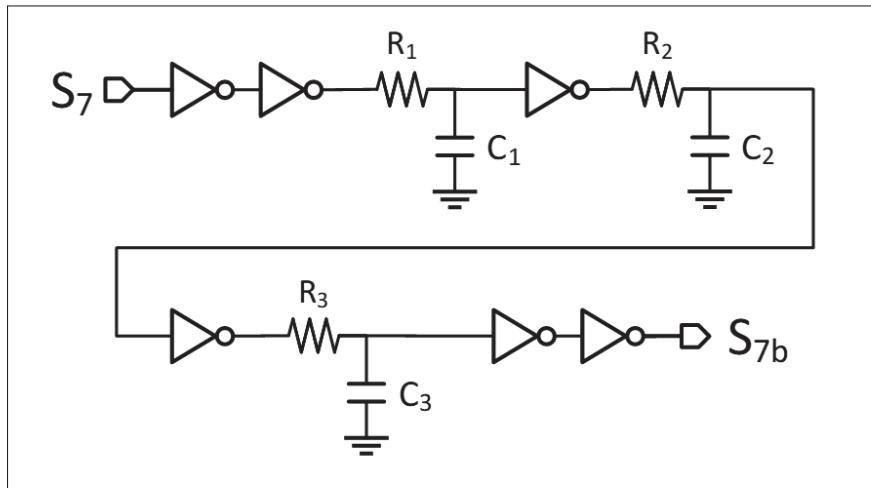

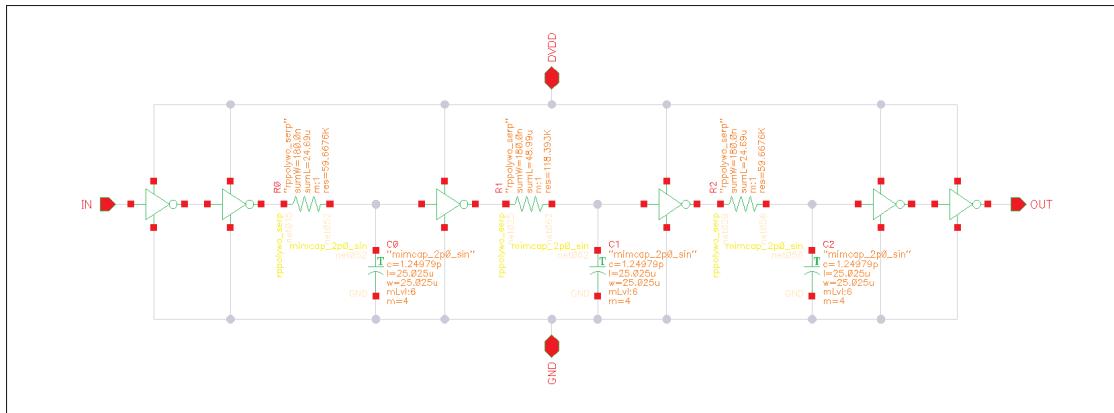

| Figure 3.9  | Circuit de la cellule de délai du signal S7 .....                                                                                                                                                                                                                                                | 102 |

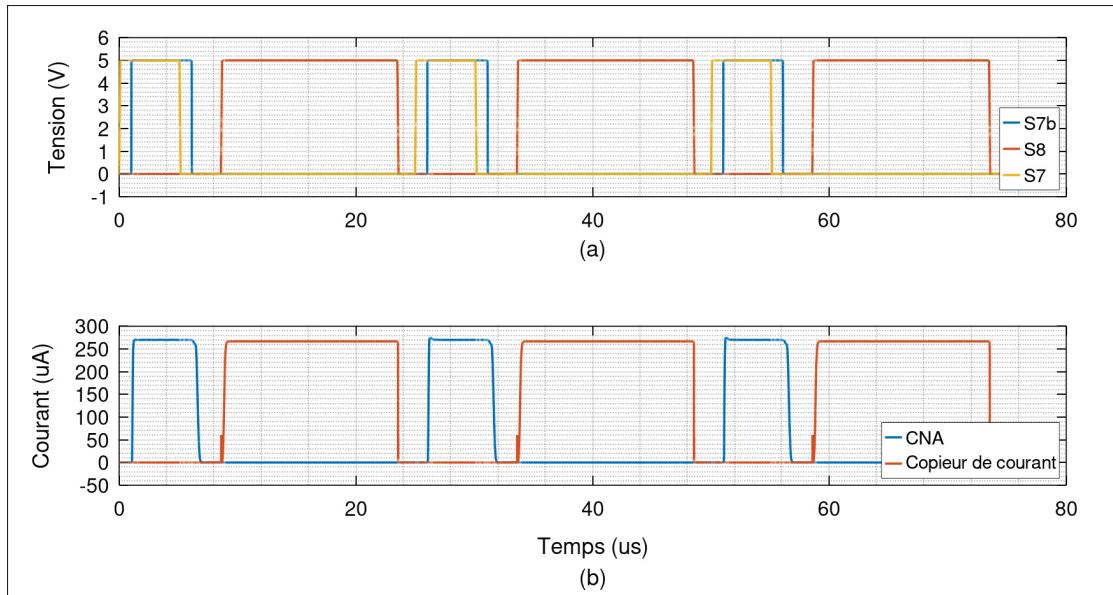

| Figure 3.10 | Simulations temporelles de la cellule copieuse de courant : (a) Signaux de commande, (b) Courant d'entrée ( $I_{CNA}$ ) et de sortie ( $I_{CC}$ ) .....                                                                                                                                          | 103 |

|             |                                                                                                                                                                                                                          |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

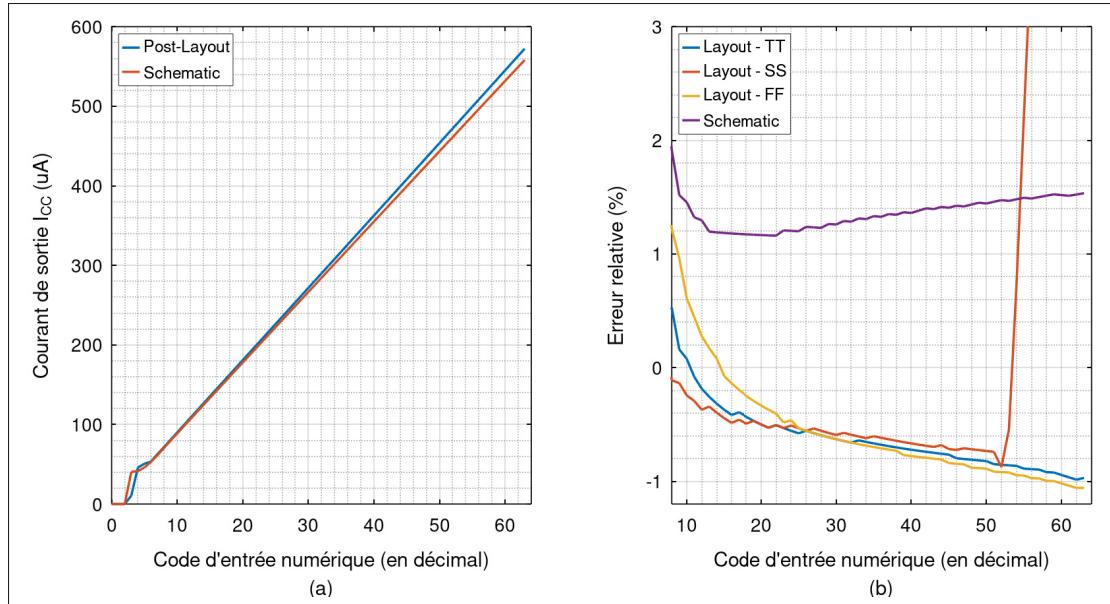

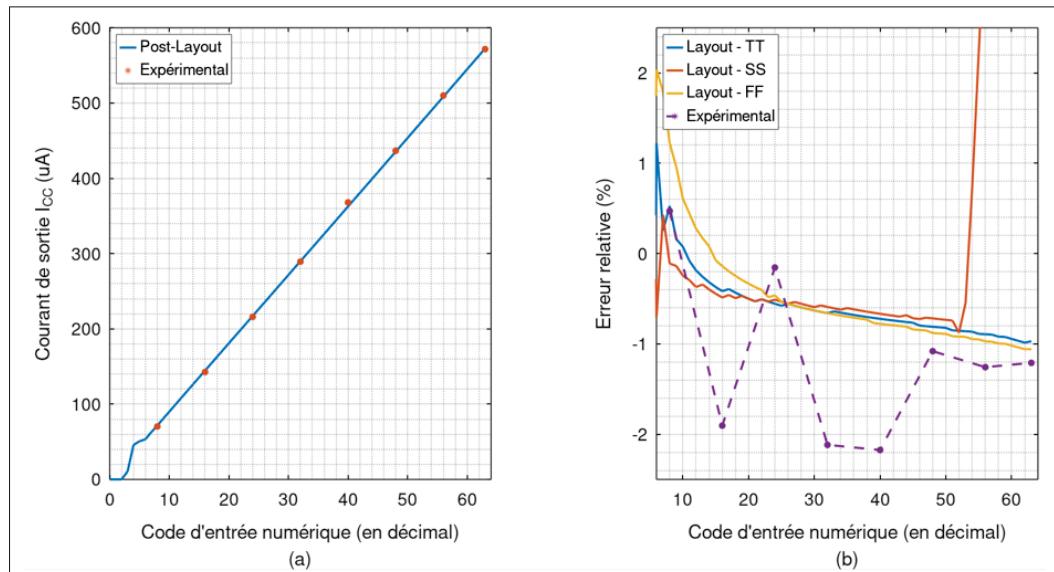

| Figure 3.11 | Précision de la recopie du courant par rapport au code d'entrée numérique : (a) Variation du courant $I_{CC}$ , (b) Erreur relative .....                                                                                | 104 |

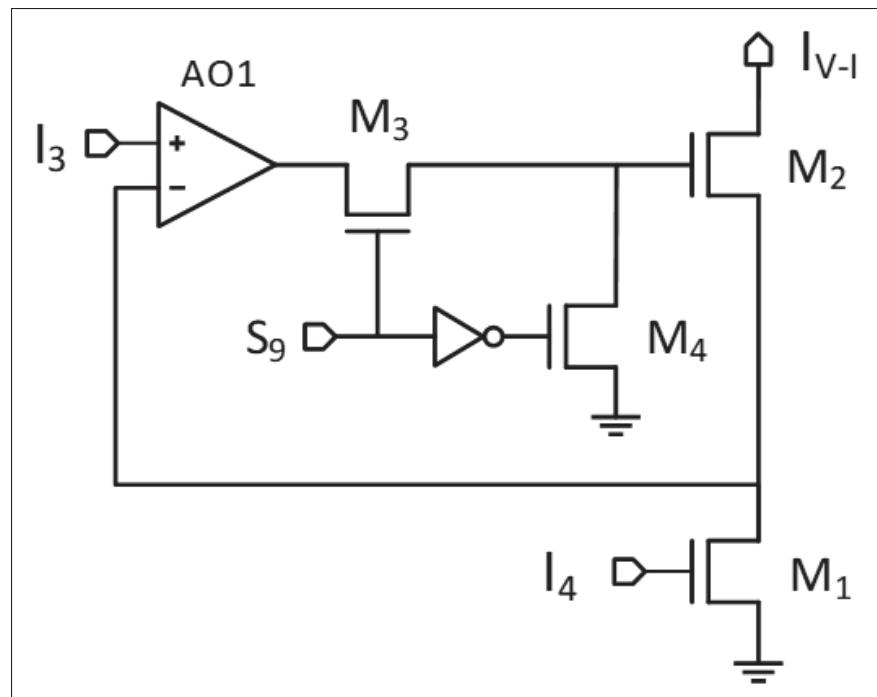

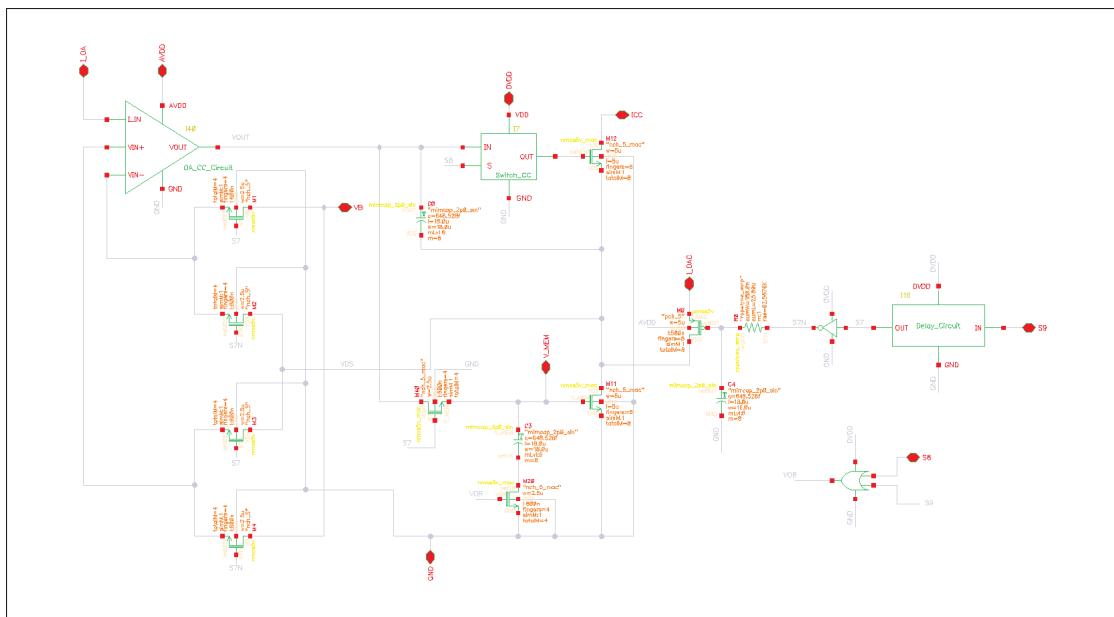

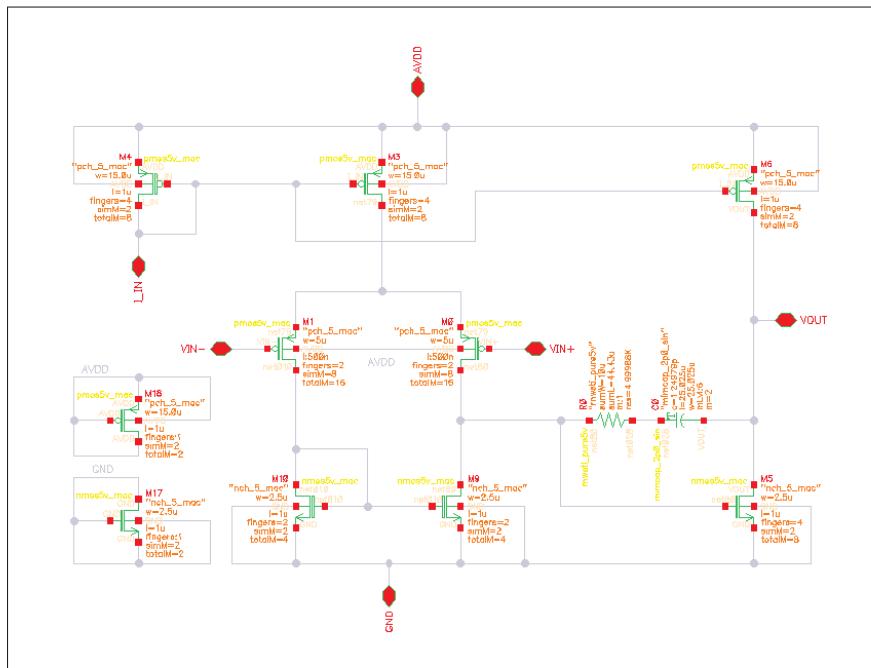

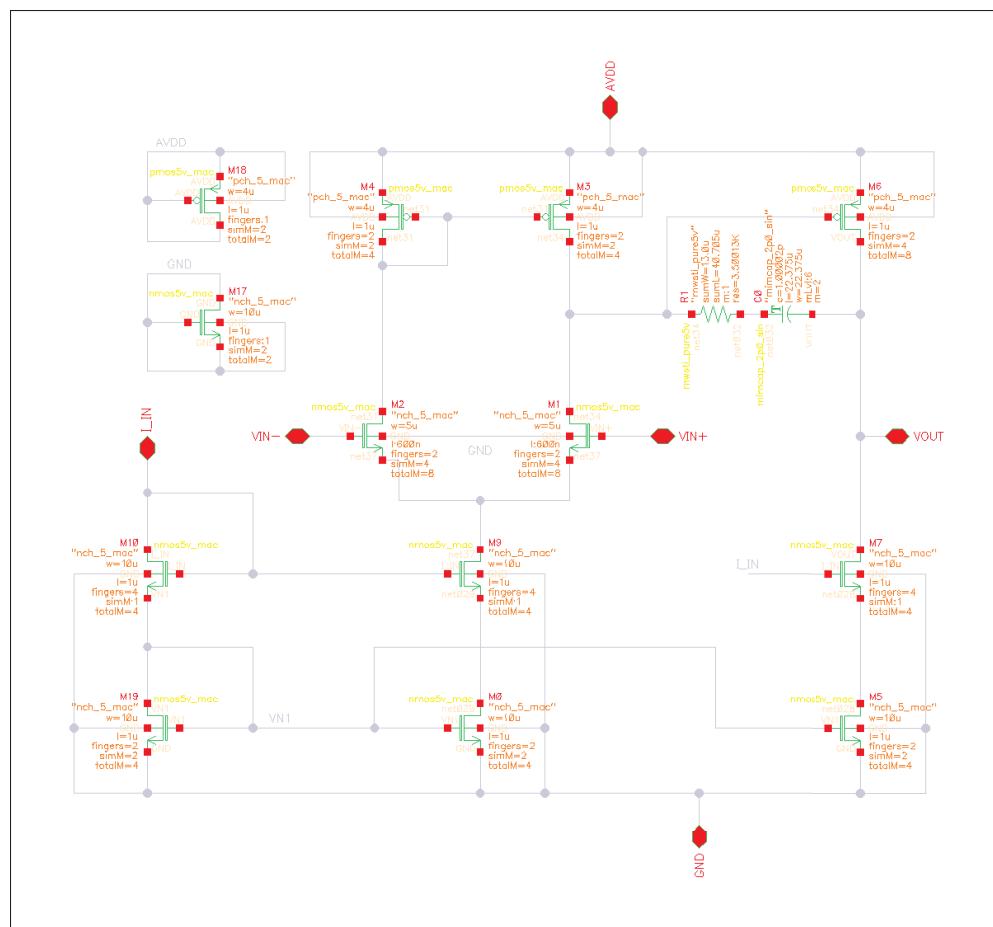

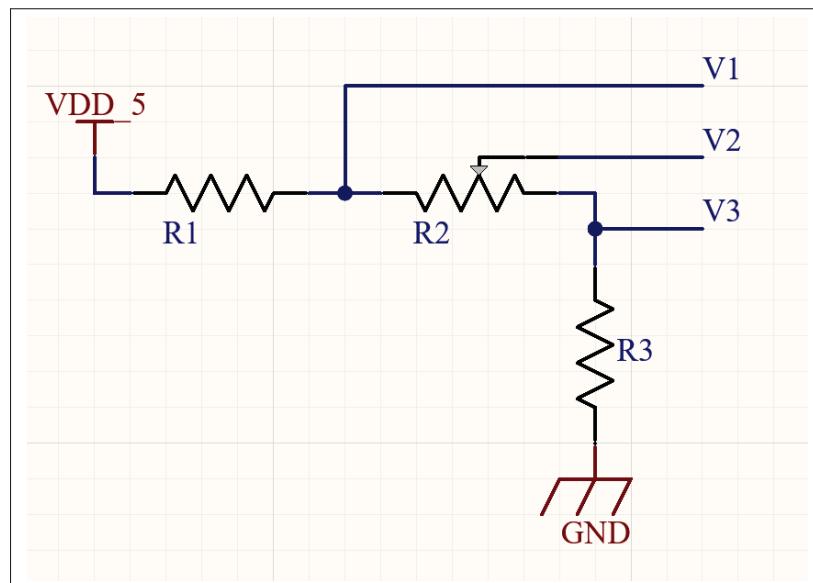

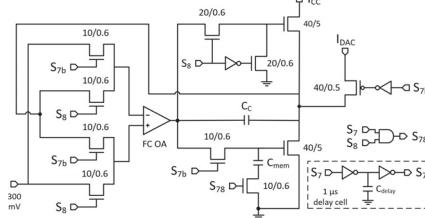

| Figure 3.12 | Circuit du convertisseur V-I .....                                                                                                                                                                                       | 105 |

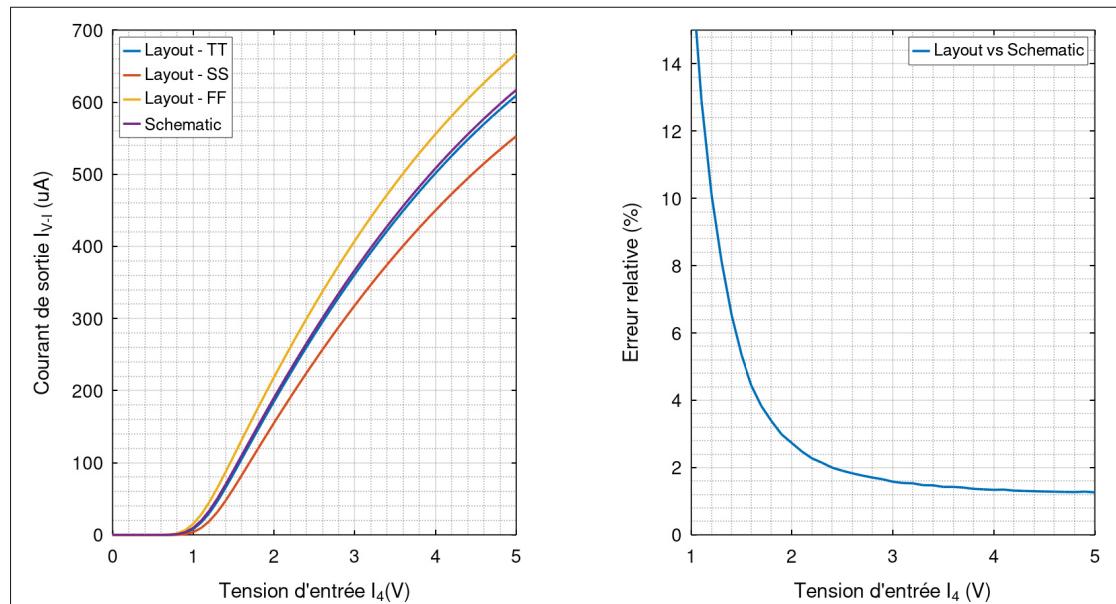

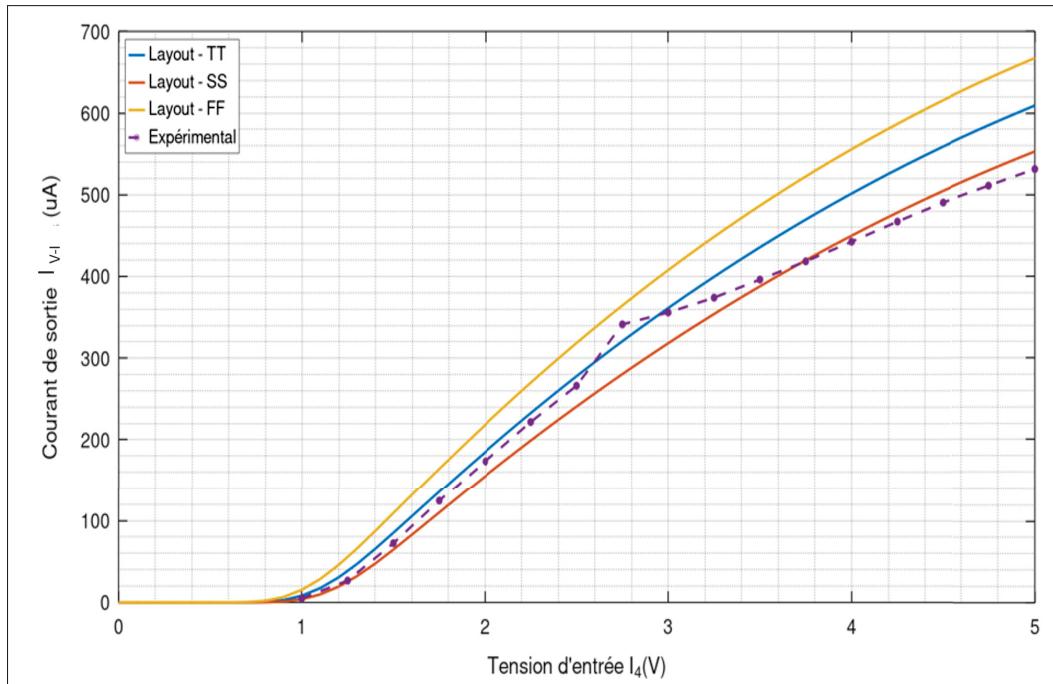

| Figure 3.13 | Simulations du convertisseur V-I : (a) Variation du courant $I_{VI}$ , (b) Erreur relative en fonction de la tension d'entrée I4 .....                                                                                   | 105 |

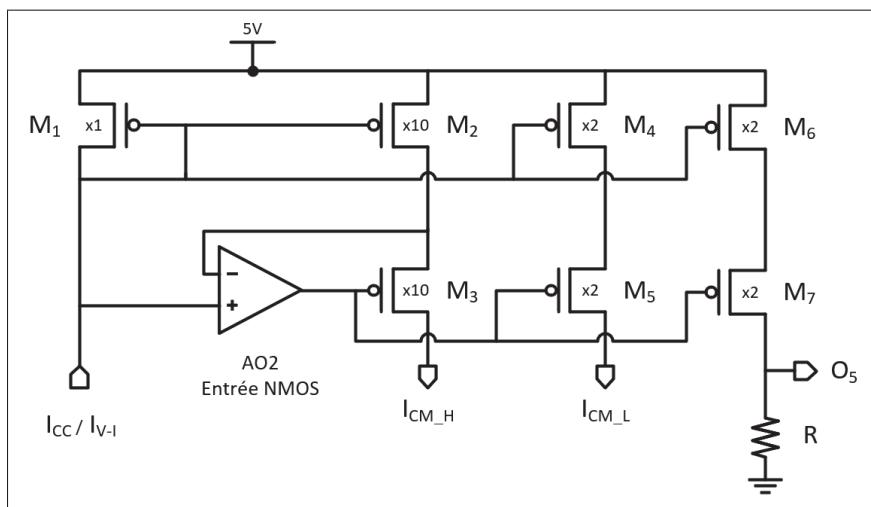

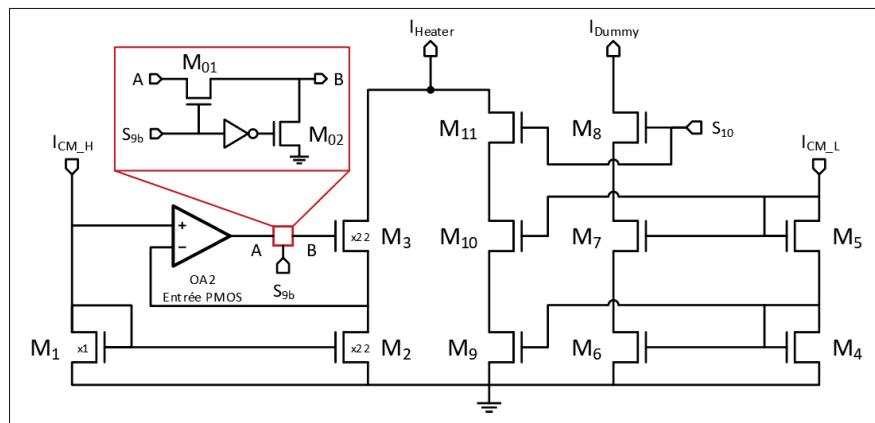

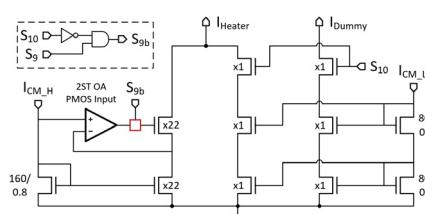

| Figure 3.14 | Circuit du 1er étage du multiplicateur de courant .....                                                                                                                                                                  | 106 |

| Figure 3.15 | Circuit du 2nd étage du multiplicateur de courant .....                                                                                                                                                                  | 107 |

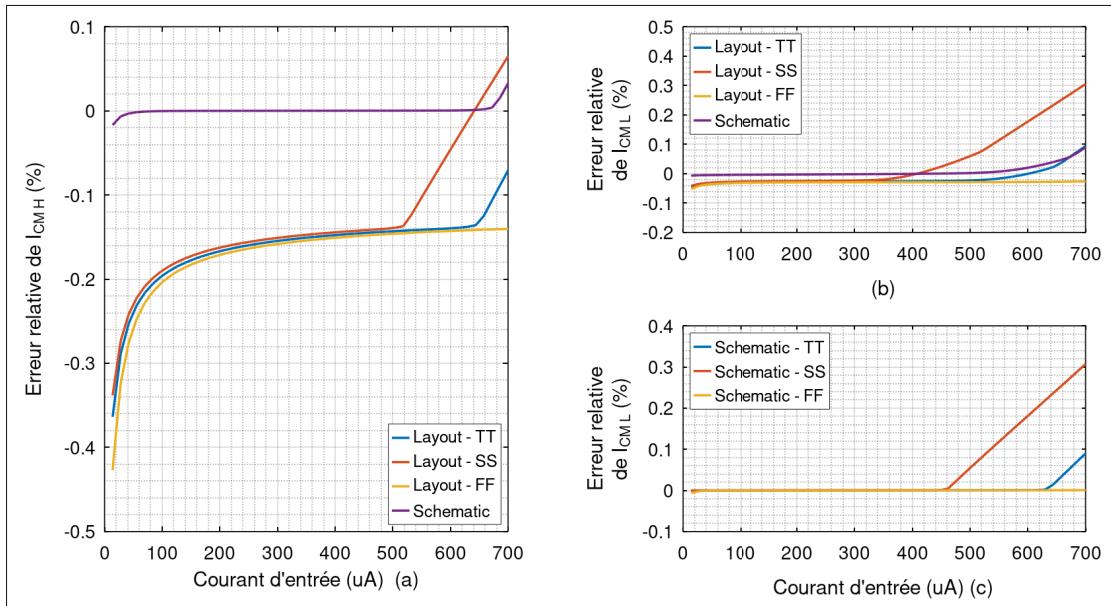

| Figure 3.16 | Erreur relative du 1er étage du multiplicateur de courant : (a) Courant $I_{CMH}$ , (b) Courant $I_{CML}$ avec réutilisation de l'amplificateur, (c) Courant $I_{CML}$ sans réutilisation de l'amplificateur .....       | 108 |

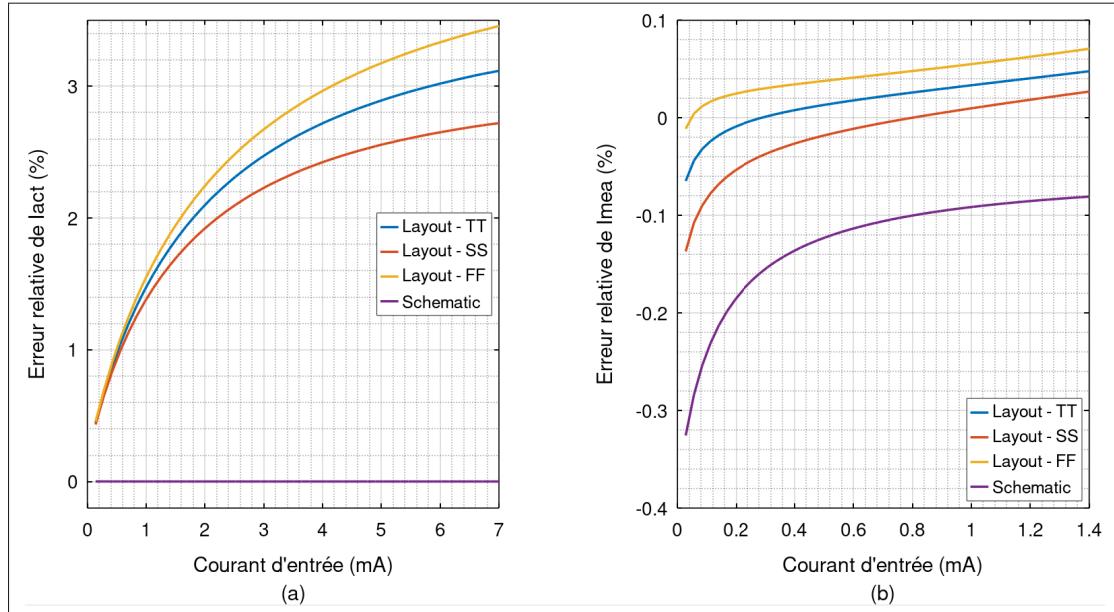

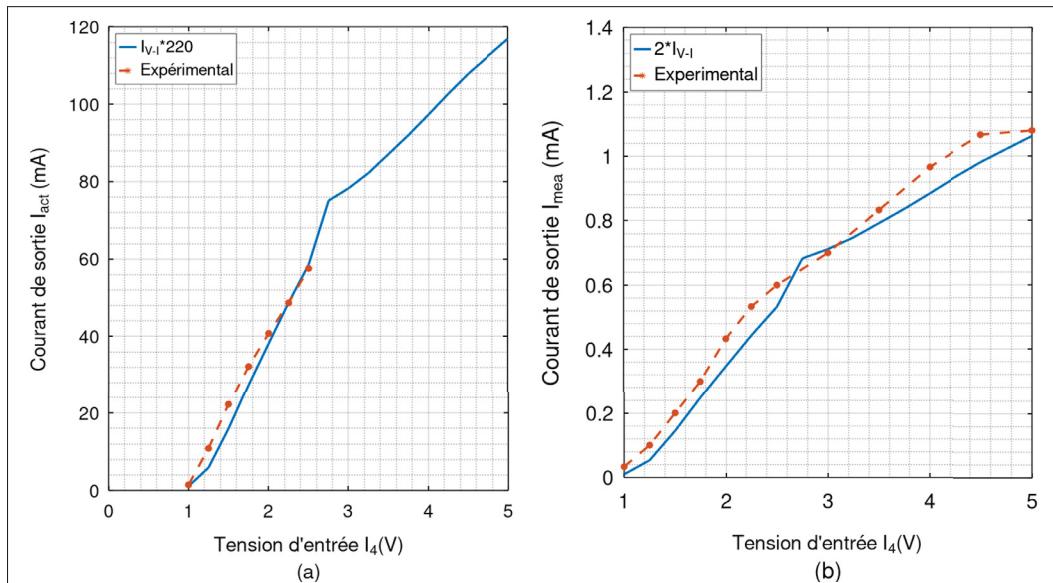

| Figure 3.17 | Erreur relative du 2nd étage du multiplicateur de courant : (a) Courant $I_{ACT}$ , (b) Courant $I_{MEA}$ .....                                                                                                          | 109 |

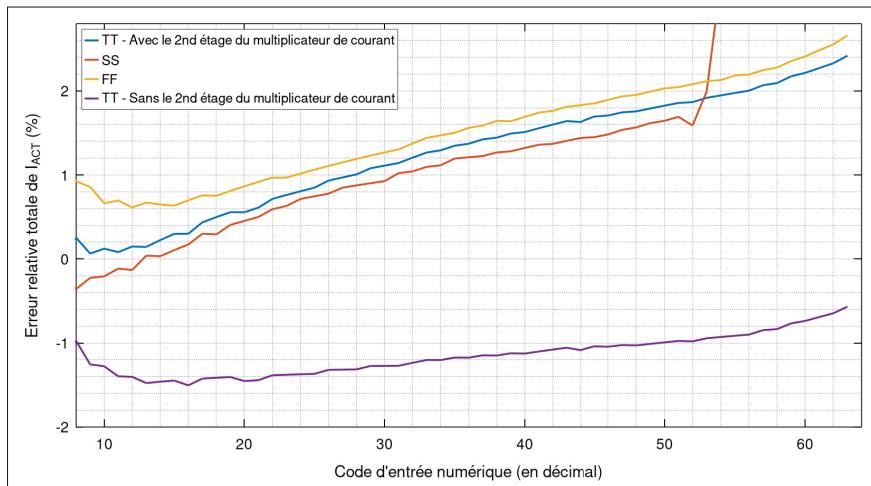

| Figure 3.18 | Erreurs relatives cumulées des circuits partagés et d'actionnement pour le courant de haute intensité $I_{ACT}$ .....                                                                                                    | 110 |

| Figure 3.19 | Erreurs relatives cumulées des circuits partagés et d'actionnement pour le courant de faible intensité $I_{MEA}$ .....                                                                                                   | 110 |

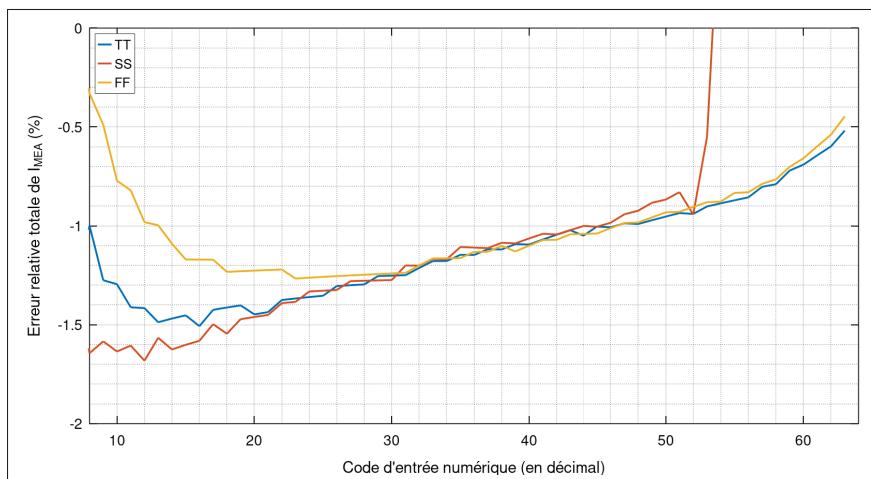

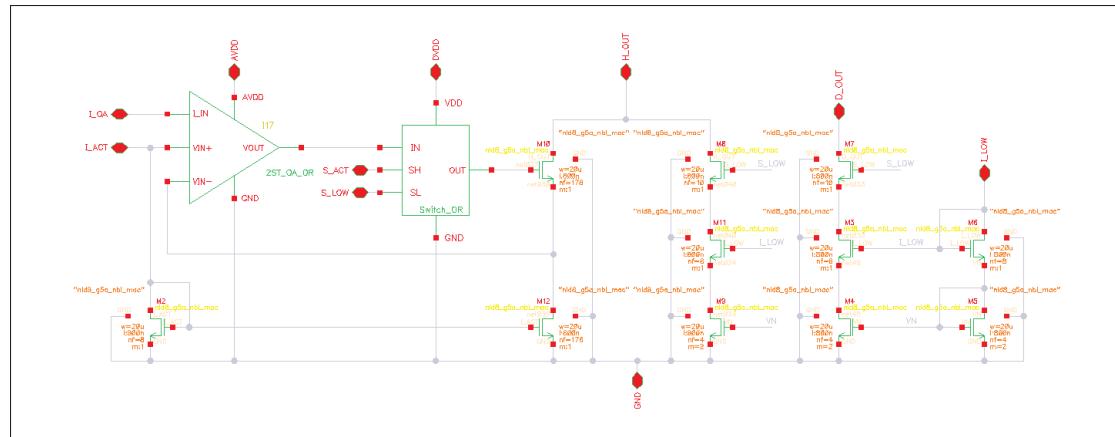

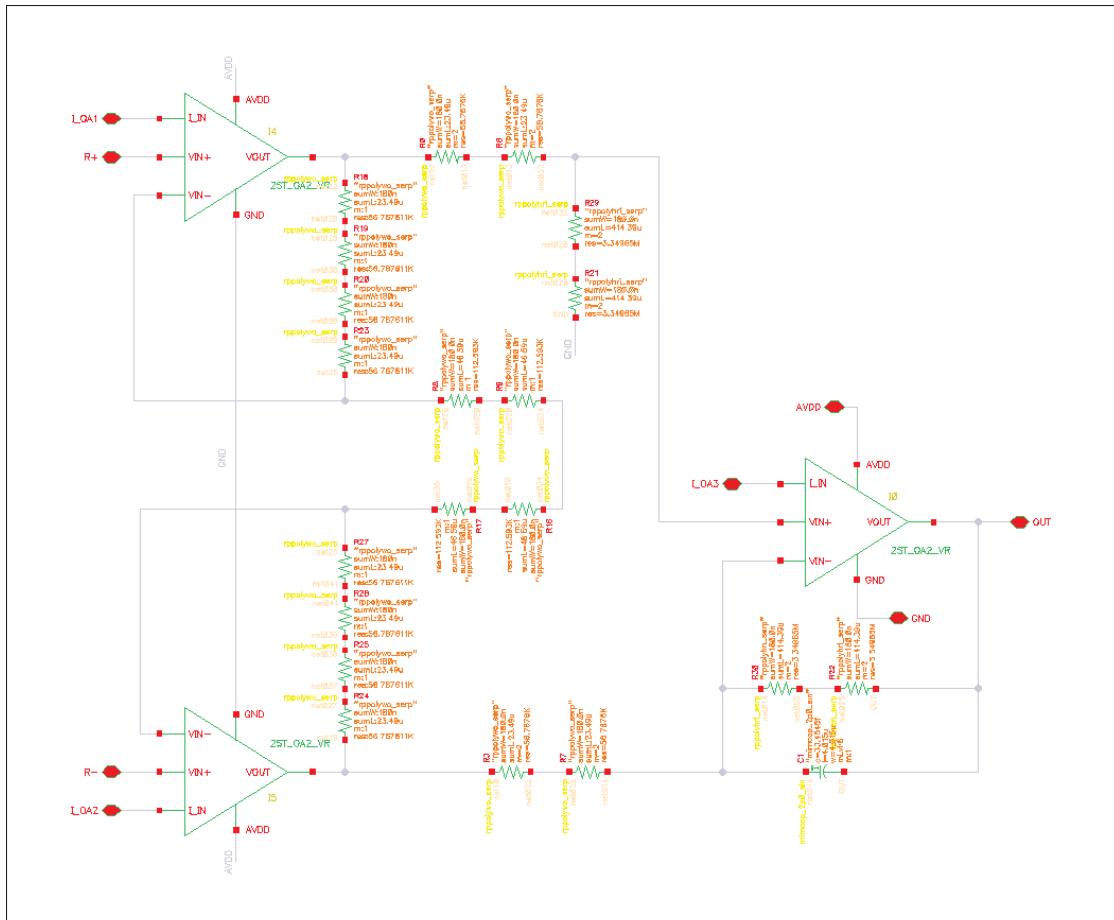

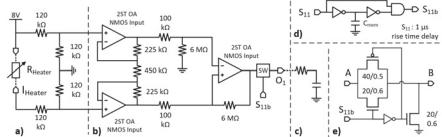

| Figure 3.20 | Circuit de mesure de la tension du $\mu$ heater et du $\mu$ heater factice : (a) Diviseur de tension, (b) Amplificateur d'instrumentation, (c) Porte de transmission, (d) Cellule de délai du front montant de S11 ..... | 111 |

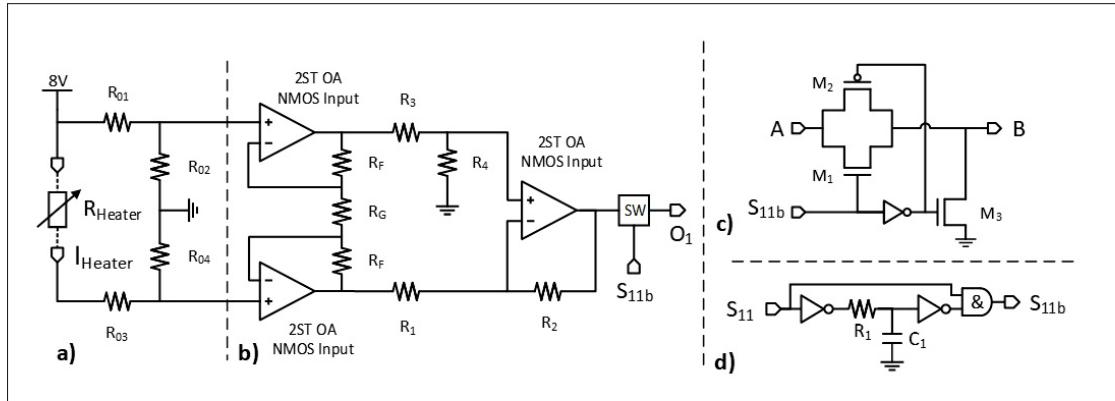

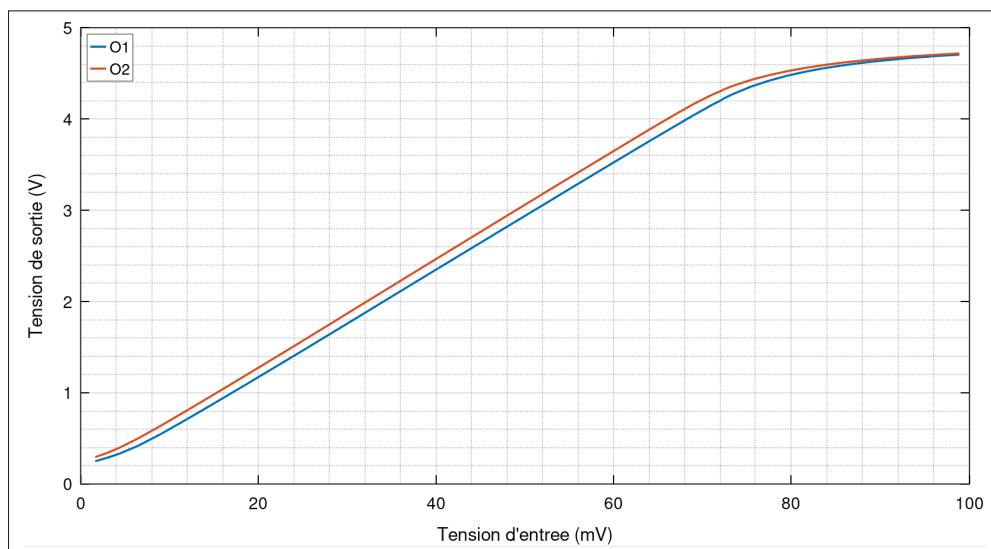

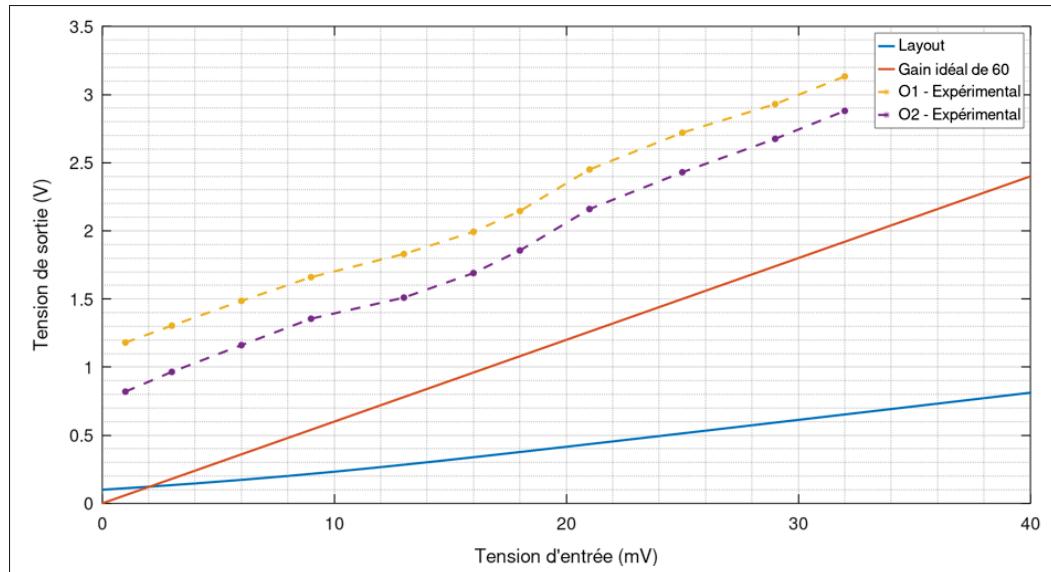

| Figure 3.21 | Simulations de l'amplificateur d'instrumentation : (a) Variation des tensions O1 et O2 en fonction de la tension du $\mu$ heater, (b) Analyse transitoire .....                                                          | 113 |

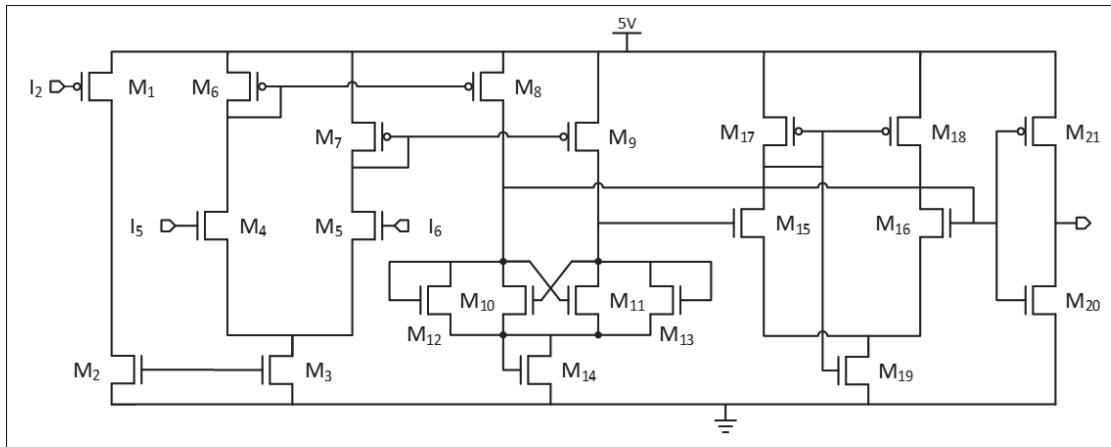

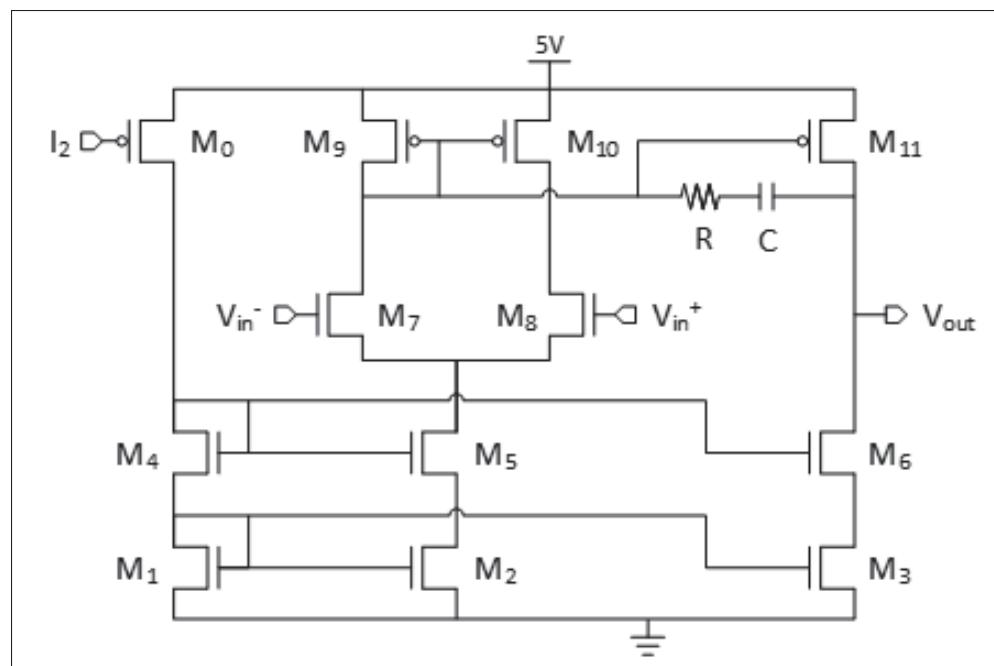

| Figure 3.22 | Circuit du comparateur haute vitesse pour la détection de l'état du commutateur .....                                                                                                                                    | 114 |

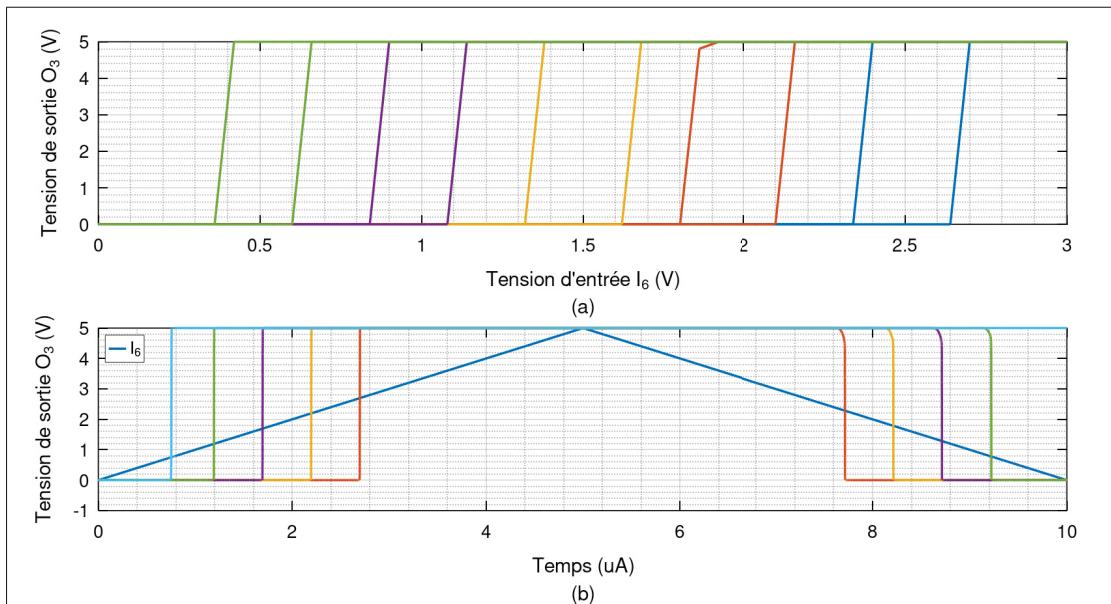

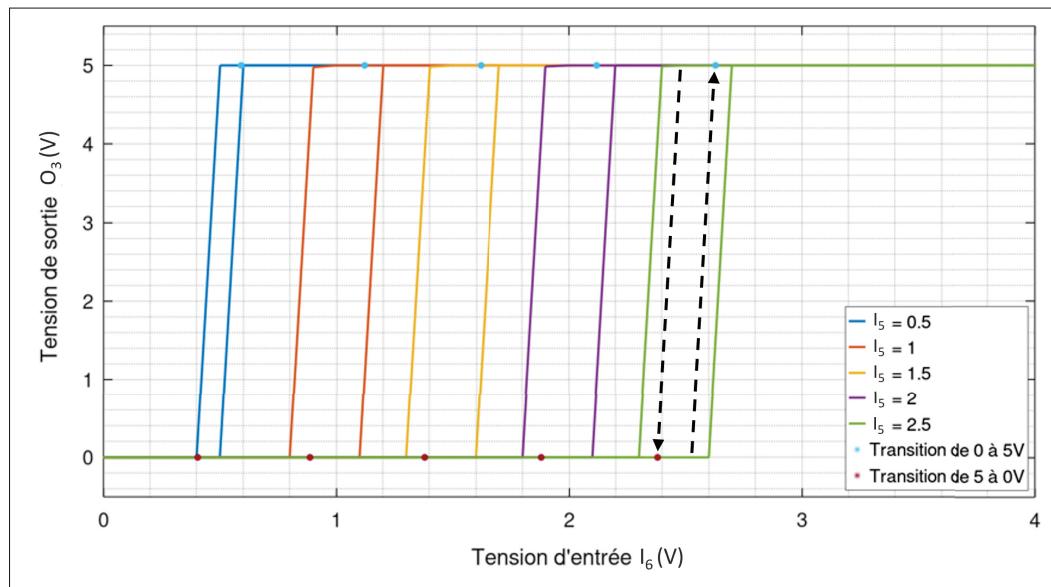

| Figure 3.23 | Variation de la tension de sortie O3 pour différentes valeurs de I5 : (a) Analyse DC des boucles d'hystérésis, (b) Analyse transitoire .....                                                                             | 114 |

| Figure 3.24 | Illustration du schéma électrique de plus haut niveau .....                                                                                                                                                              | 115 |

| Figure 3.25 | Décalage entre les sorties O1 et O2 .....                                                                                                                                                                                | 116 |

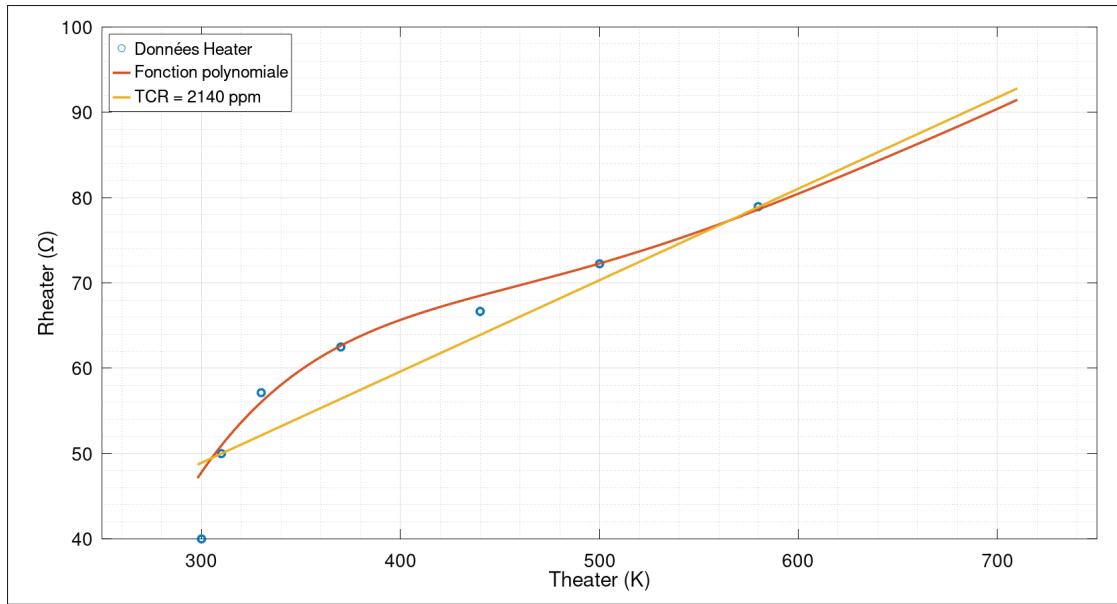

| Figure 3.26 | Modélisation de la variation de la résistance électrique du $\mu$ heater en fonction de la température à partir des données expérimentales .....                                                                         | 119 |

|             |                                                                                                                                                                                                                                                    |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

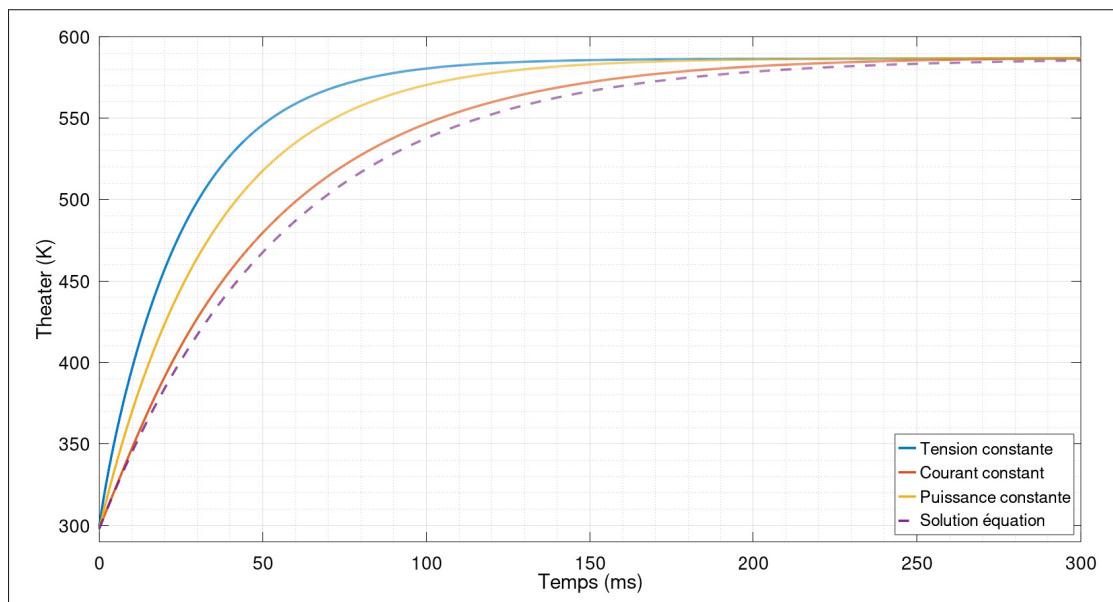

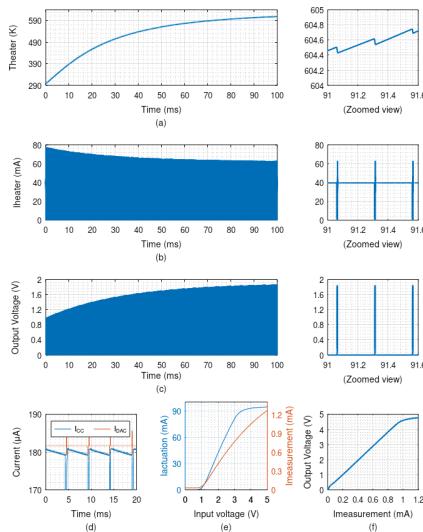

| Figure 3.27 | Réponse thermique du $\mu$ heater avec un modèle thermique du 1 <sup>er</sup> ordre par méthode itérative .....                                                                                                                                    | 120 |

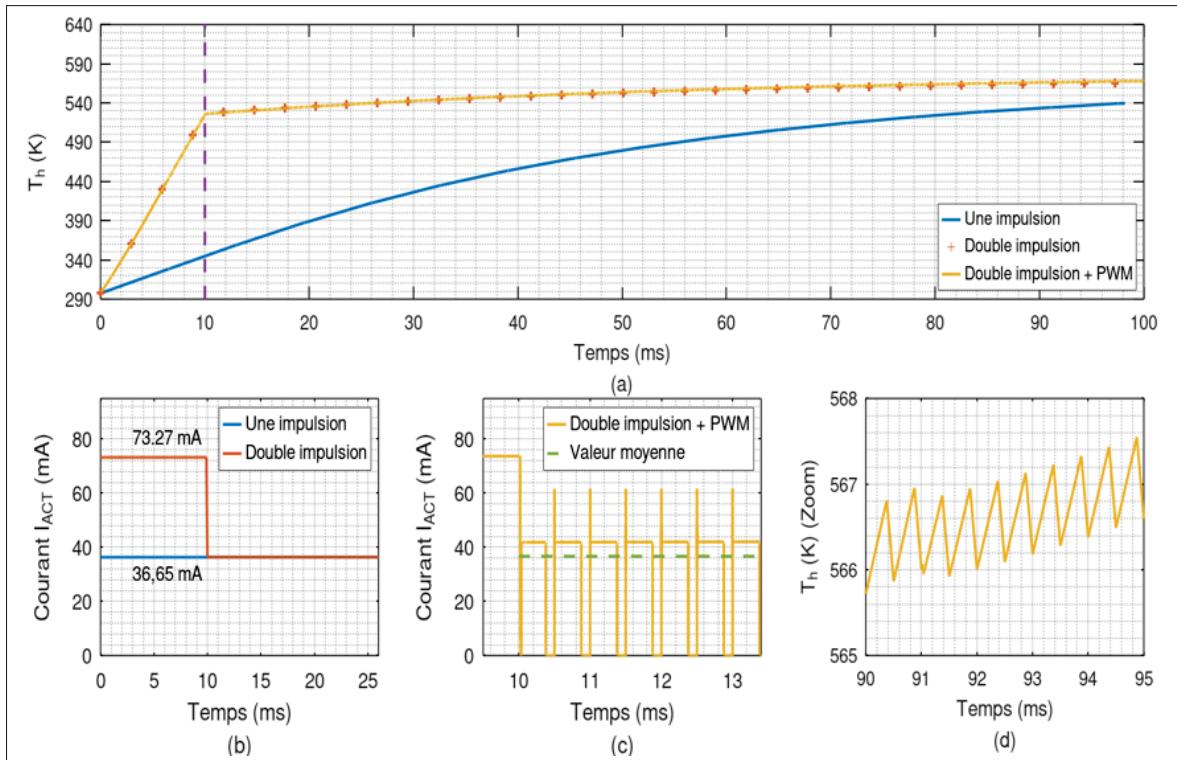

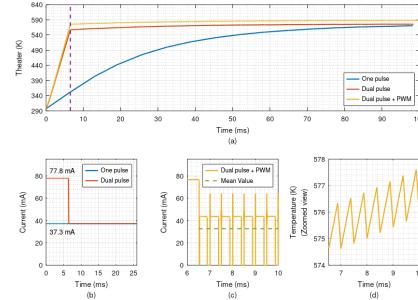

| Figure 3.28 | (a) Réponse thermique du $\mu$ heater avec différents courants d'actionnement, (b) Courant continu avec/sans double impulsion, (c) Courant PWM avec un rapport cyclique de 75 %, (d) Ondulation de la température du $\mu$ heater. .....           | 121 |

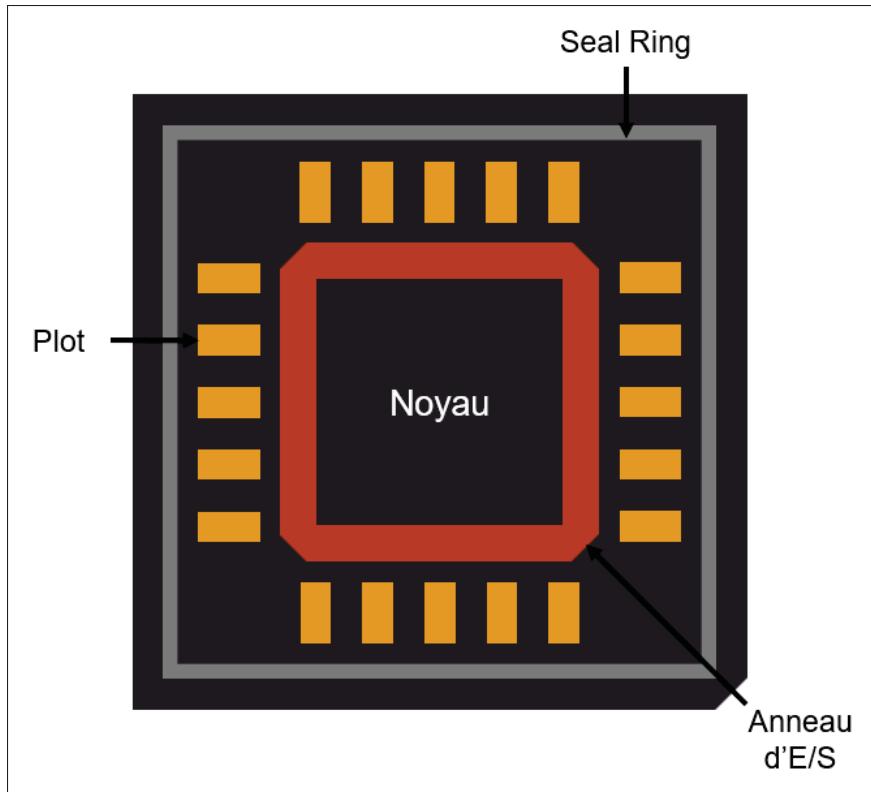

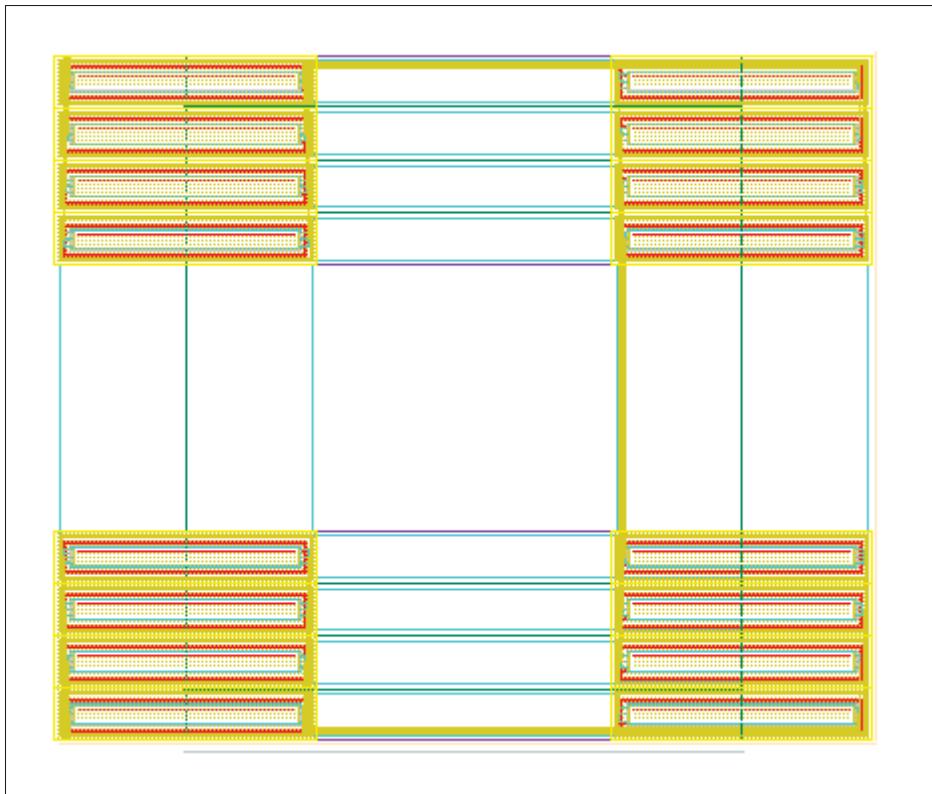

| Figure 3.29 | Anneau externe de la puce CMOS .....                                                                                                                                                                                                               | 122 |

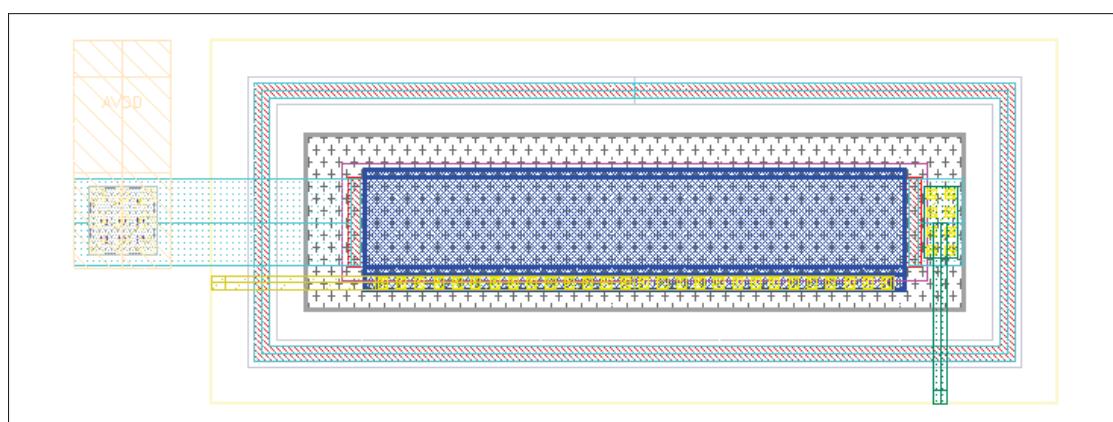

| Figure 3.30 | Circuit de protection contre les ESD .....                                                                                                                                                                                                         | 123 |

| Figure 3.31 | Taille et espacement des plots selon les spécifications de la machine de <i>wire bonding</i> M17S .....                                                                                                                                            | 124 |

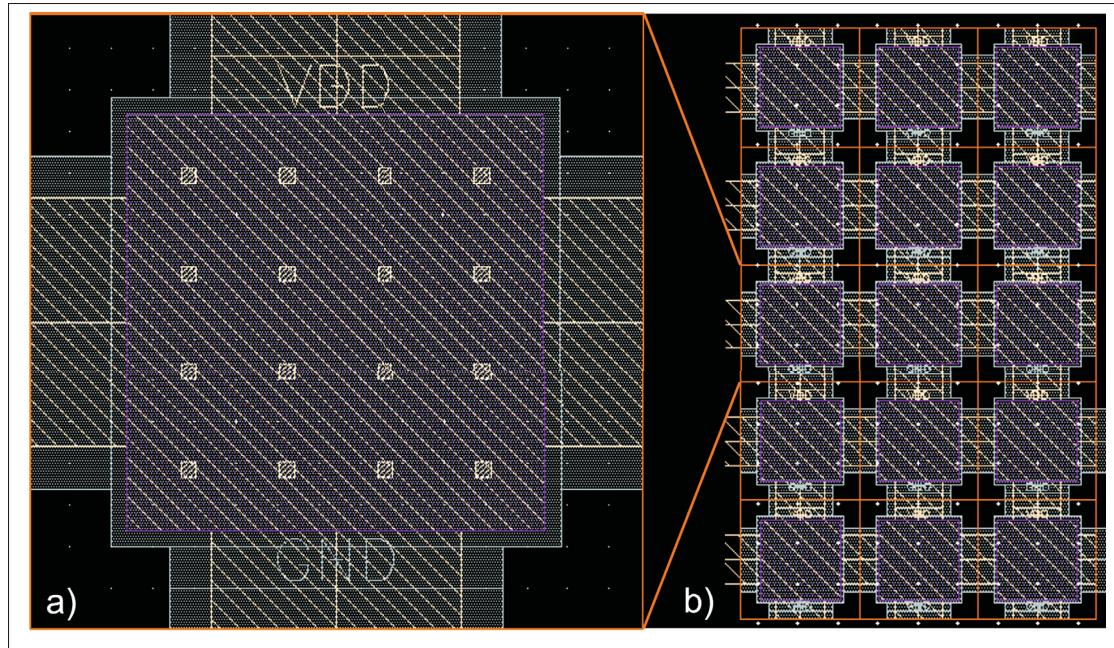

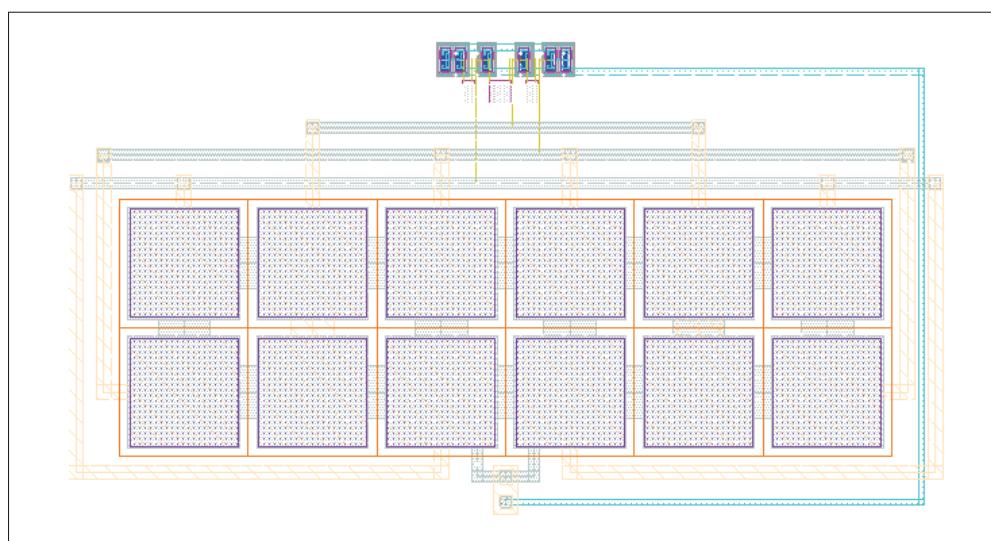

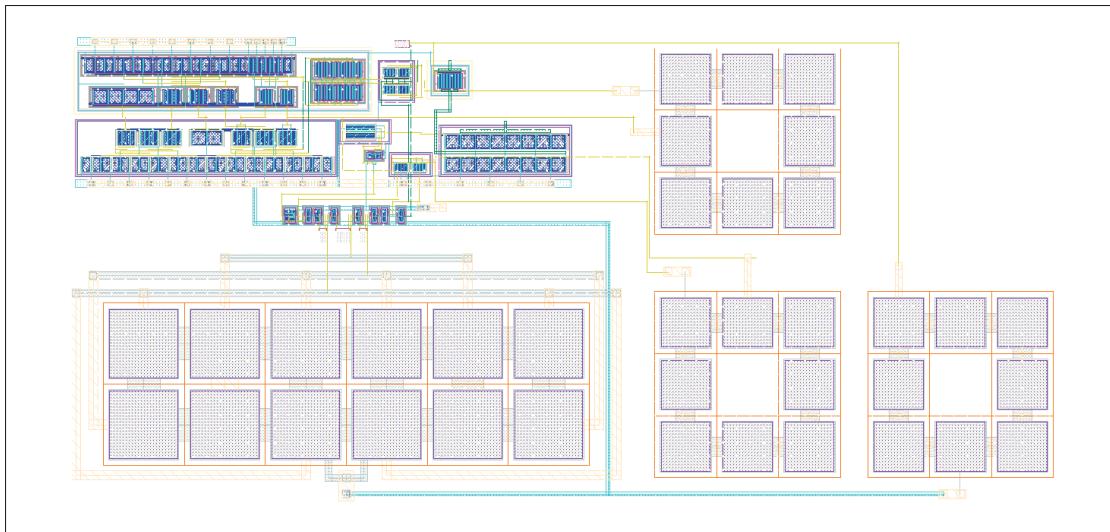

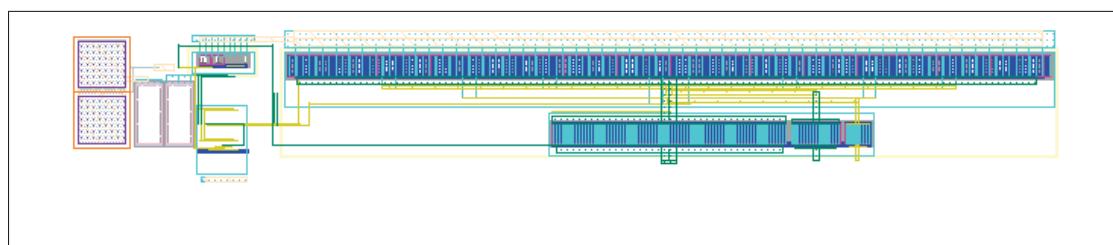

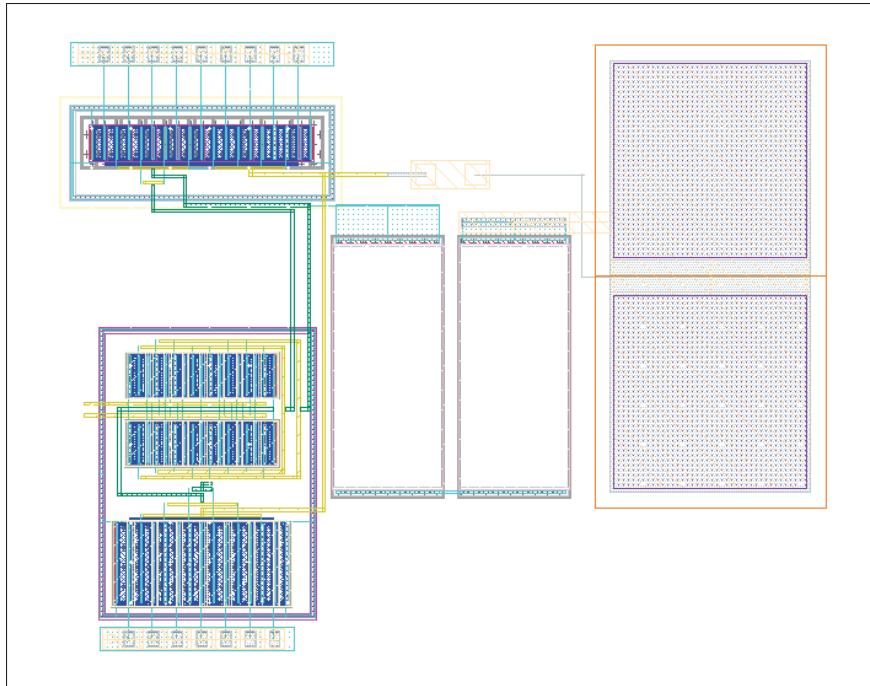

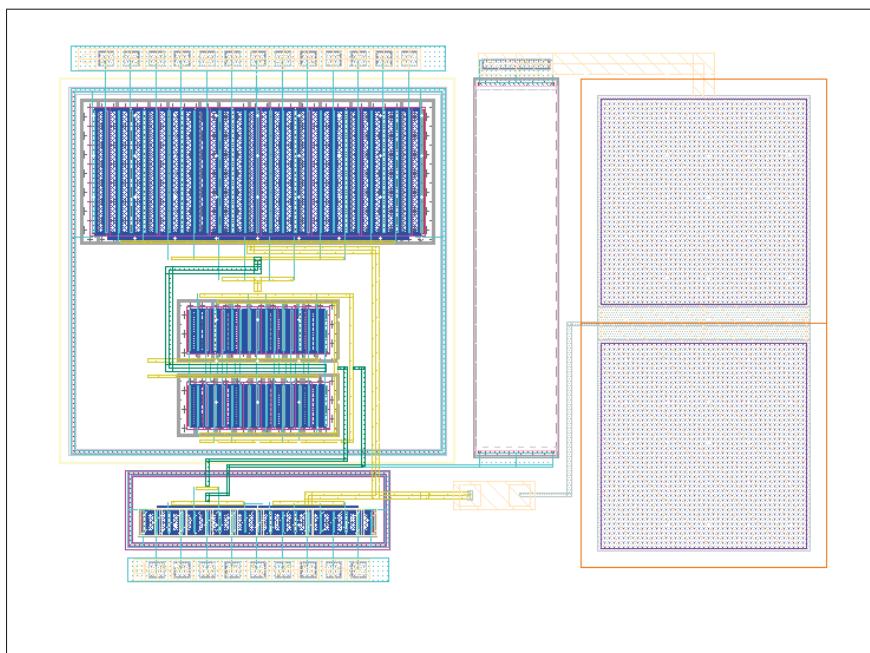

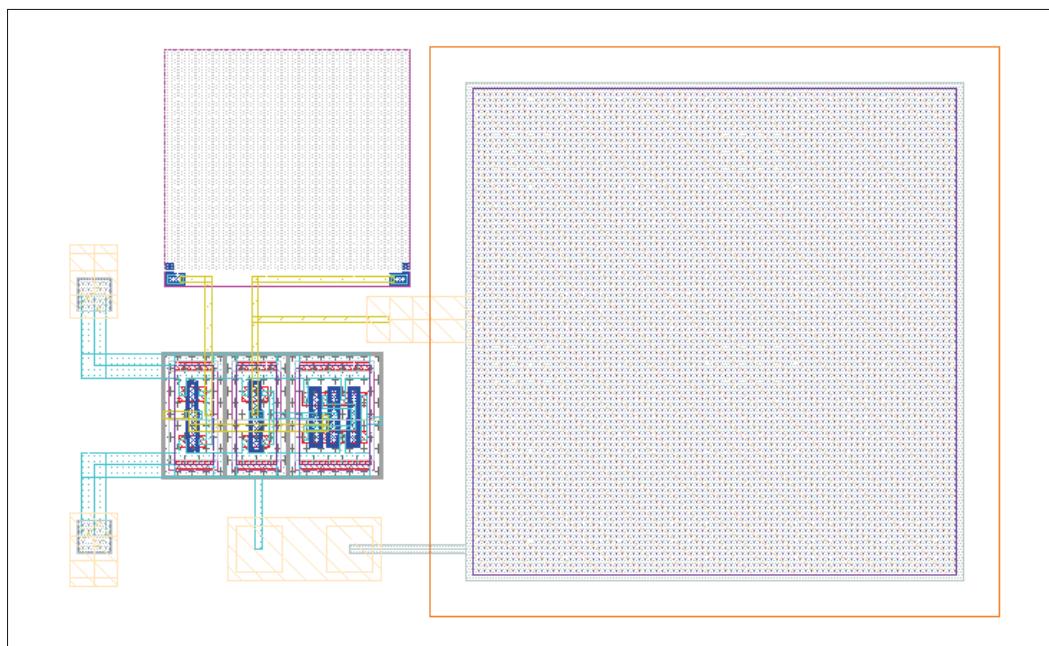

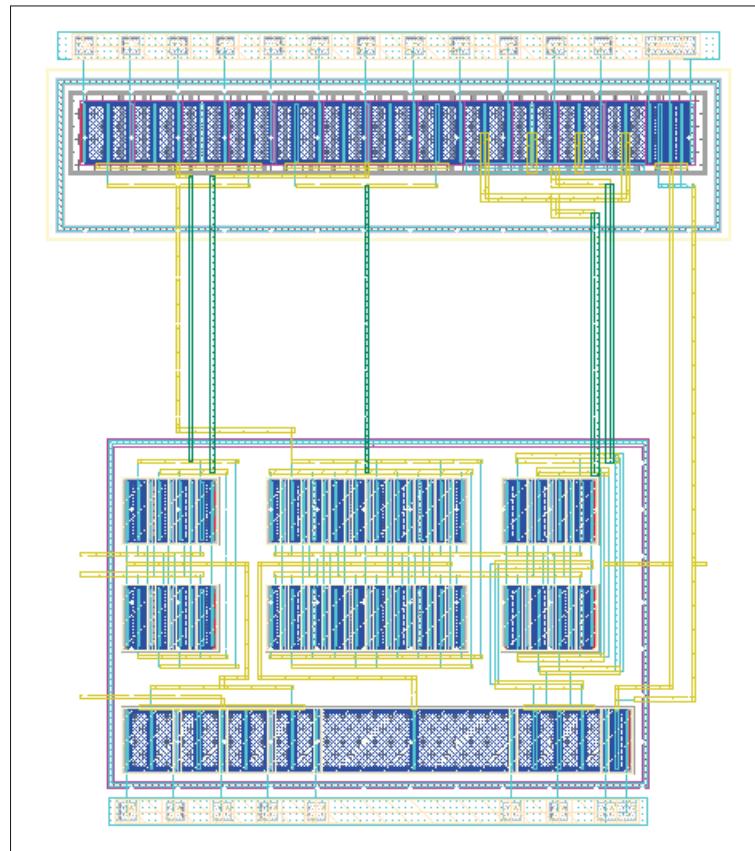

| Figure 3.32 | <i>Layout</i> de la puce CMOS .....                                                                                                                                                                                                                | 126 |

| Figure 3.33 | Vue en coupe de transistor : (a) Circuits parasites des transistors NMOS-PMOS, (b) Chemin <i>latch-up</i> susceptible dans une configuration entre des transistors HV et LV Tirées respectivement de Wikipédia et (Dai & Ker, 2017, p. 3520) ..... | 127 |

| Figure 3.34 | Résumé des concepts de <i>matching</i> selon le degré de précision requis Tirée de (Lienig & Scheible, 2021, p. 254) .....                                                                                                                         | 129 |

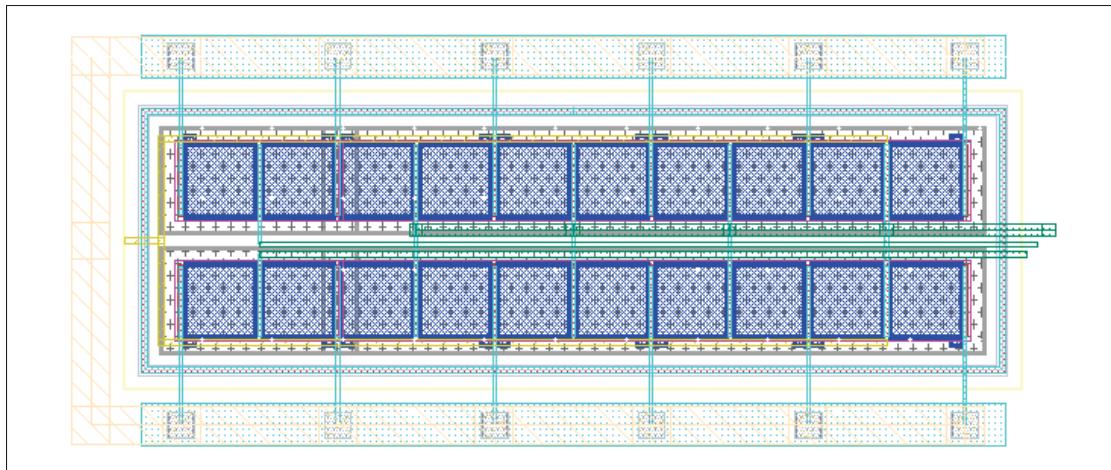

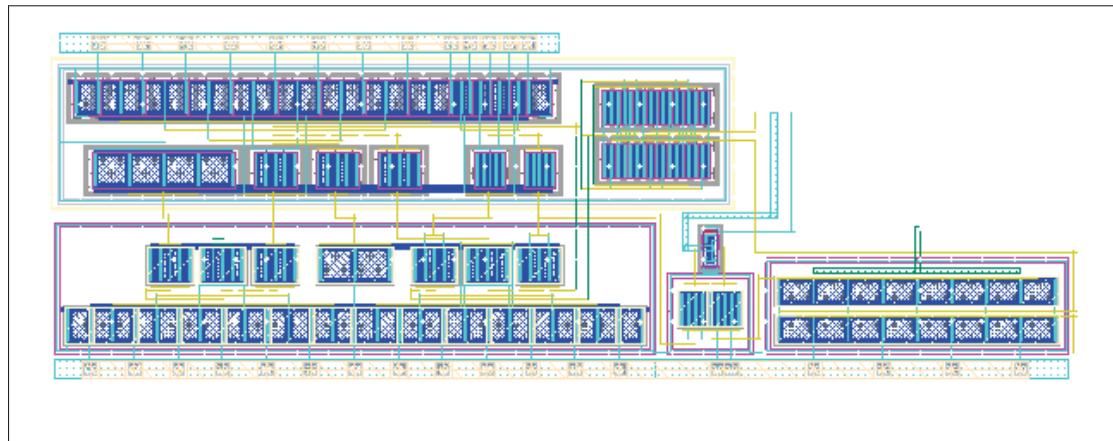

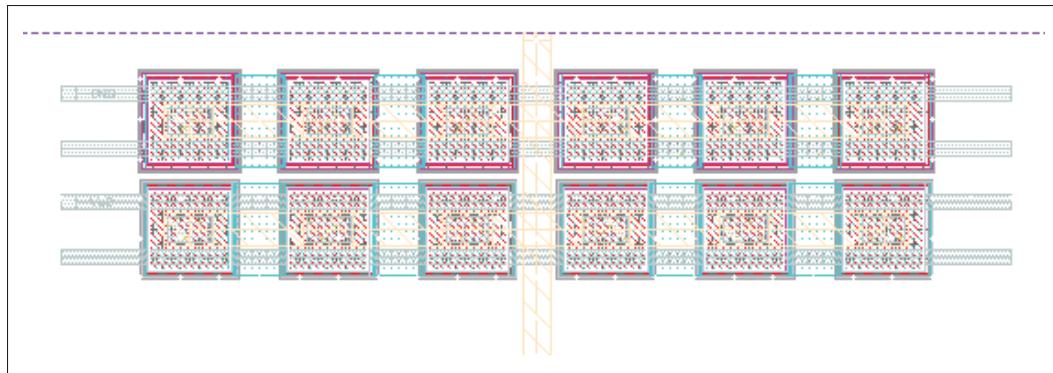

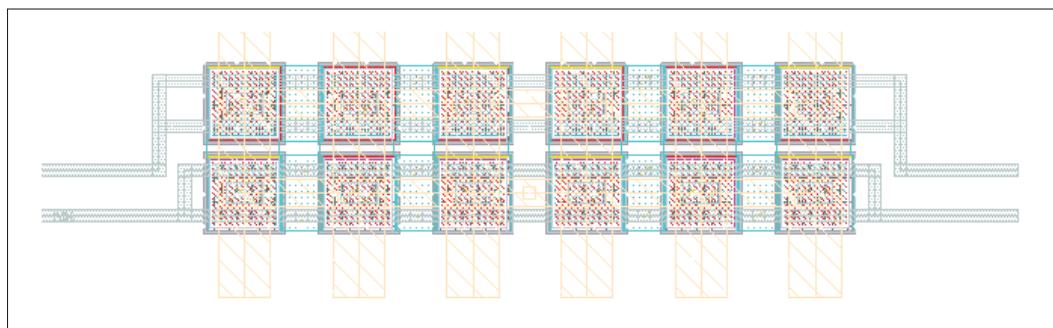

| Figure 3.35 | <i>Layout</i> d'un amplificateur opérationnel : Exemple de technique employée .....                                                                                                                                                                | 130 |

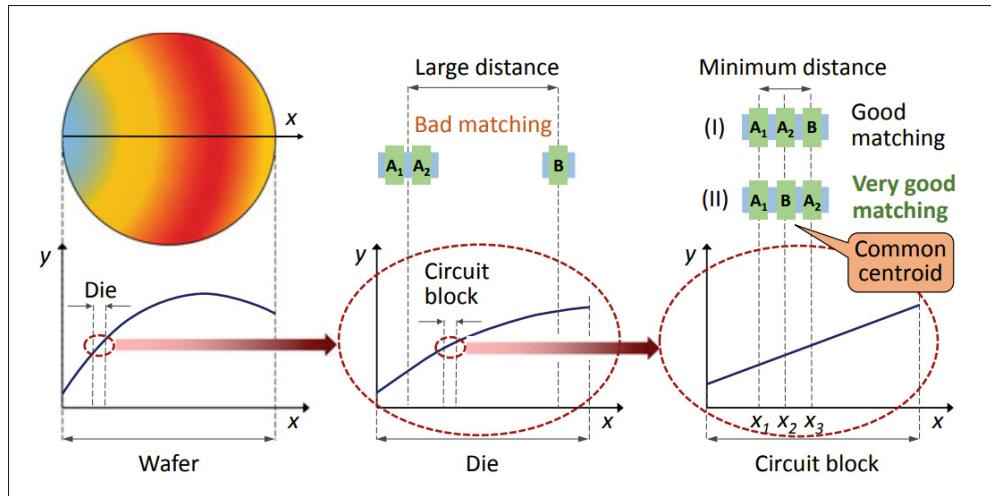

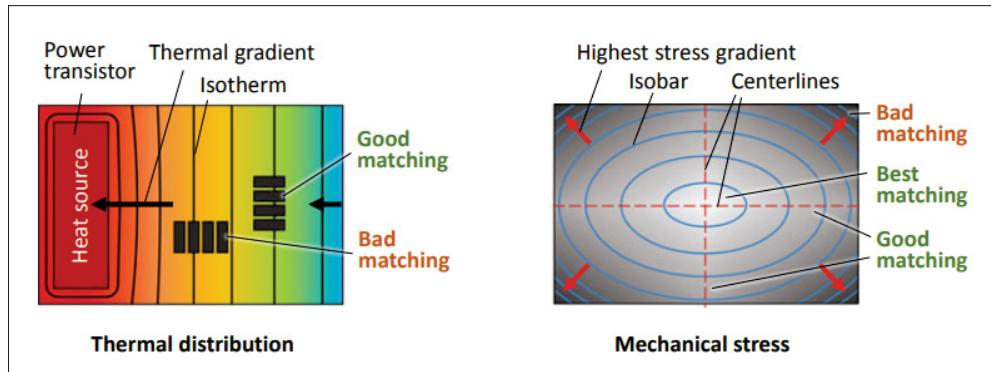

| Figure 3.36 | Gradients des paramètres des composants en fonction de la position, causés par les tolérances de fabrication Tirée de (Lienig & Scheible, 2021, p. 247) .....                                                                                      | 131 |

| Figure 3.37 | <i>Matching</i> des composants sur une puce selon les gradients thermiques et les contraintes mécaniques dues à l'emballage de la puce Tirée de (Lienig & Scheible, 2021, p. 251) .....                                                            | 131 |

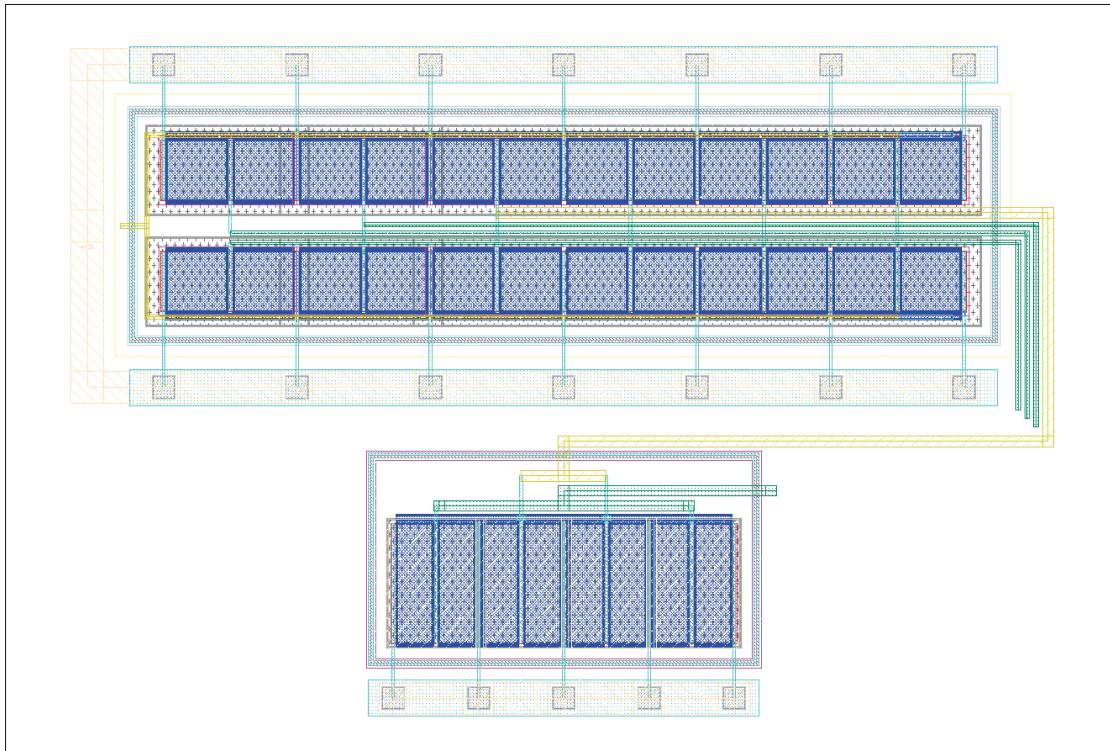

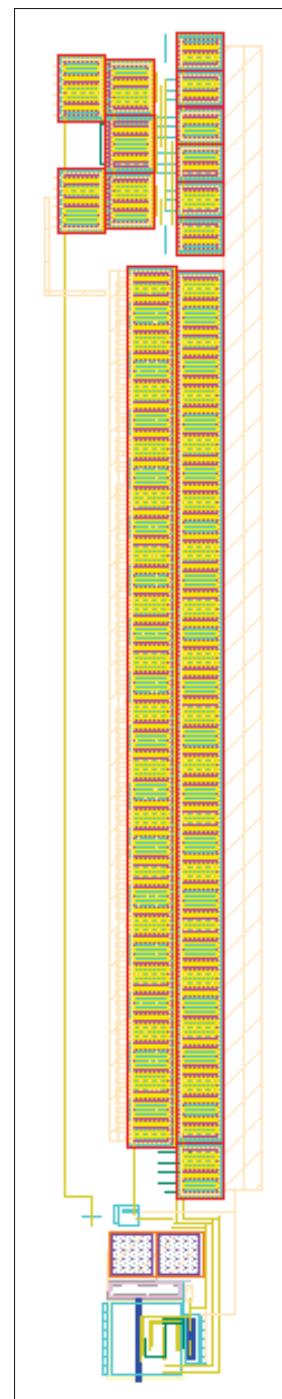

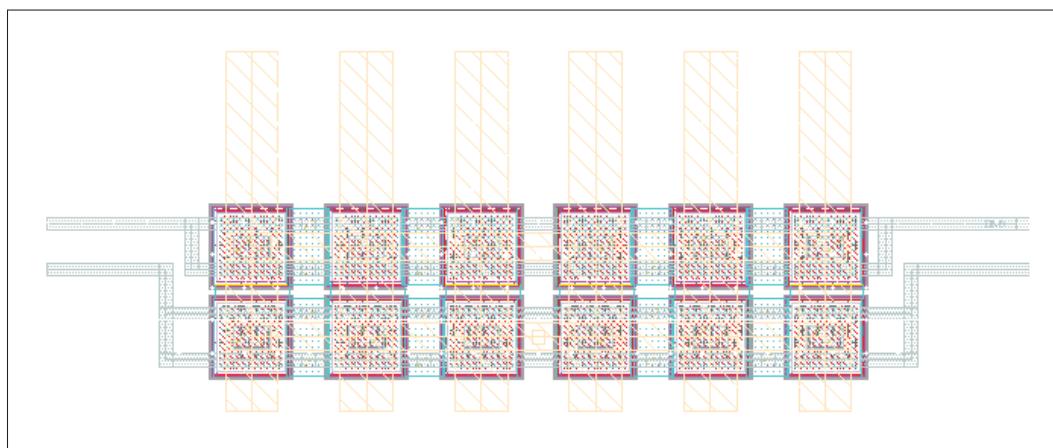

| Figure 3.38 | <i>Layout</i> des condensateurs de découplage : (a) Cellule, (b) Cellules dupliquées .....                                                                                                                                                         | 133 |

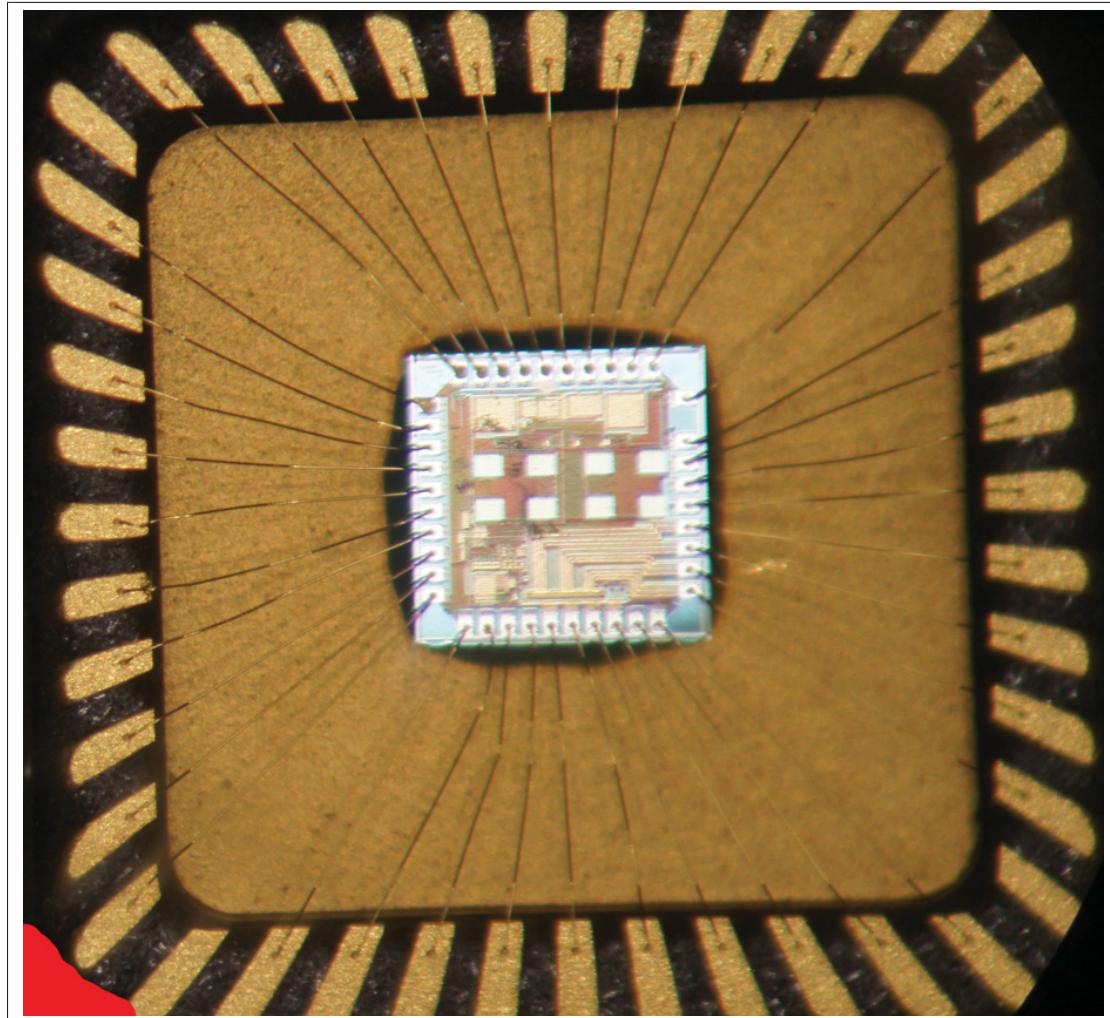

| Figure 3.39 | Photo de la puce CMOS fabriquée (le coin rouge correspond au repère de l'emballage) .....                                                                                                                                                          | 135 |

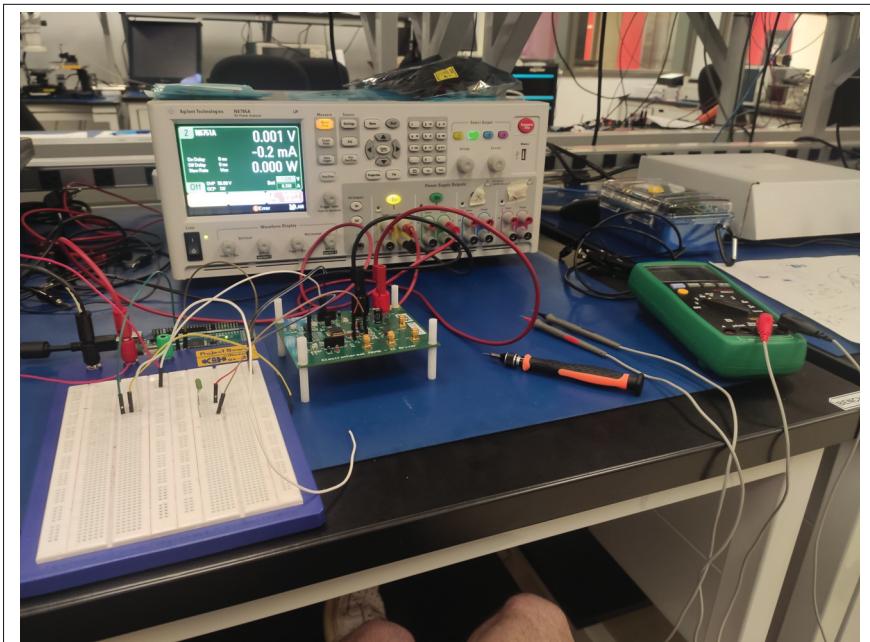

| Figure 4.1  | Banc de test dans le laboratoire du LACIME .....                                                                                                                                                                                                   | 137 |

|             |                                                                                                                                                                                                                                                                                |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

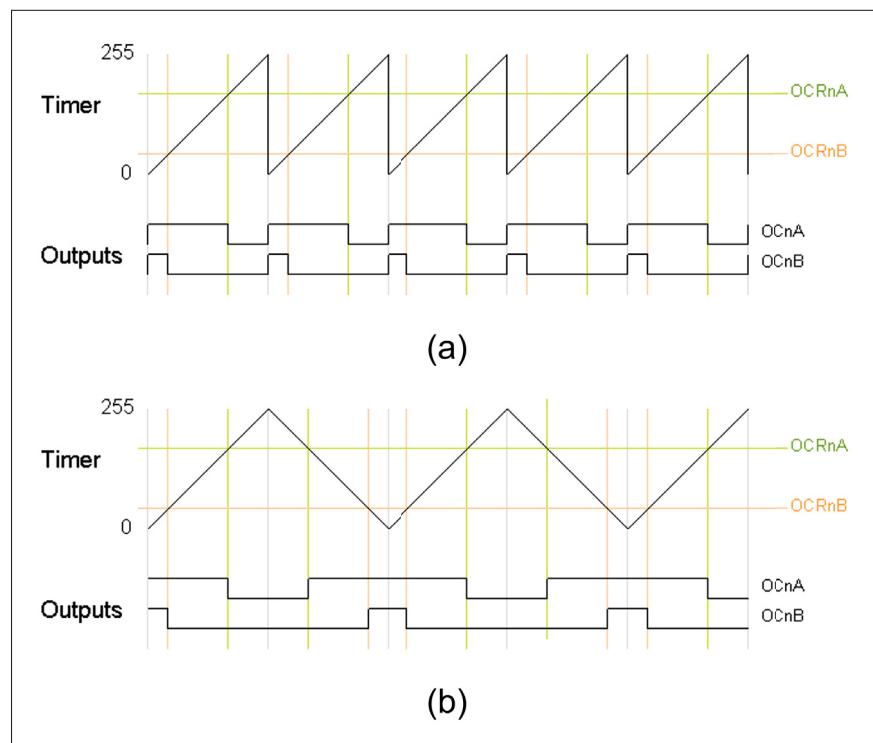

| Figure 4.2  | Génération des signaux PWM selon différents modes, (a) <i>Fast PWM</i> ,<br>(b) <i>PWM phase correct</i> Tirées de « <a href="https://docs.arduino.cc/tutorials/generic/secrets-of-arduino-pwm/">https://docs.arduino.cc/tutorials/generic/secrets-of-arduino-pwm/</a> » ..... | 139 |

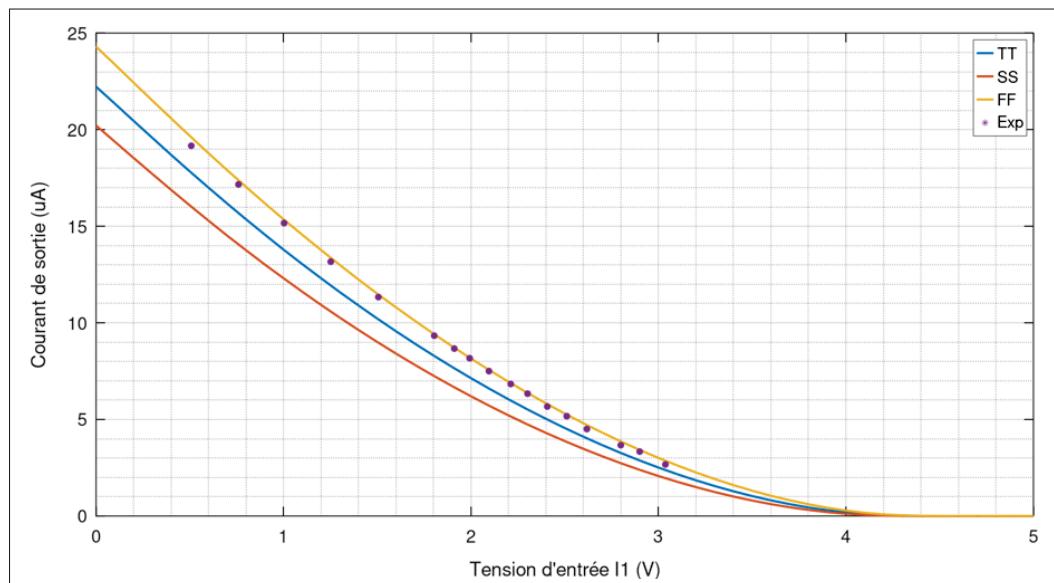

| Figure 4.3  | Variation du courant de référence $I_{RC}$ en fonction de la tension d'entrée<br>I1 - Résultats expérimentaux .....                                                                                                                                                            | 141 |

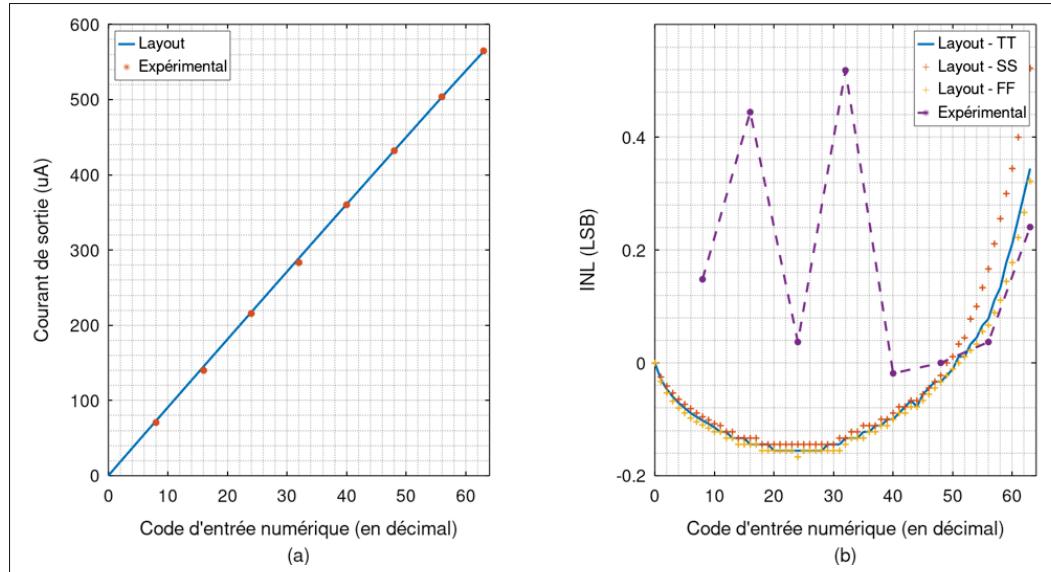

| Figure 4.4  | Simulations du CNA par rapport au code d'entrée numérique (a)<br>Variation du courant $I_{CNA}$ , (b) INL - Résultats expérimentaux .....                                                                                                                                      | 142 |

| Figure 4.5  | Précision de la recopie du courant : (a) Variation du courant $I_{CC}$ , (b)<br>Erreur relative par rapport au code d'entrée numérique - Résultats<br>expérimentaux .....                                                                                                      | 143 |

| Figure 4.6  | Variation du courant $I_{VI}$ par rapport à la tension d'entrée I4 - Résultats<br>expérimentaux .....                                                                                                                                                                          | 144 |

| Figure 4.7  | Variation du courant de sortie par rapport à la tension d'entrée I4 : (a)<br>$I_{ACT}$ , (b) $I_{MEA}$ - Résultats expérimentaux .....                                                                                                                                         | 144 |

| Figure 4.8  | Variation des tensions de sortie O1 et O2 des amplificateurs<br>d'instrumentation en fonction de la tension de la résistance de sortie<br>de la puce – Résultats expérimentaux .....                                                                                           | 146 |

| Figure 4.9  | Variation de la tension de sortie O3 du comparateur en fonction de la<br>tension d'entrée I6 – Résultats expérimentaux .....                                                                                                                                                   | 146 |

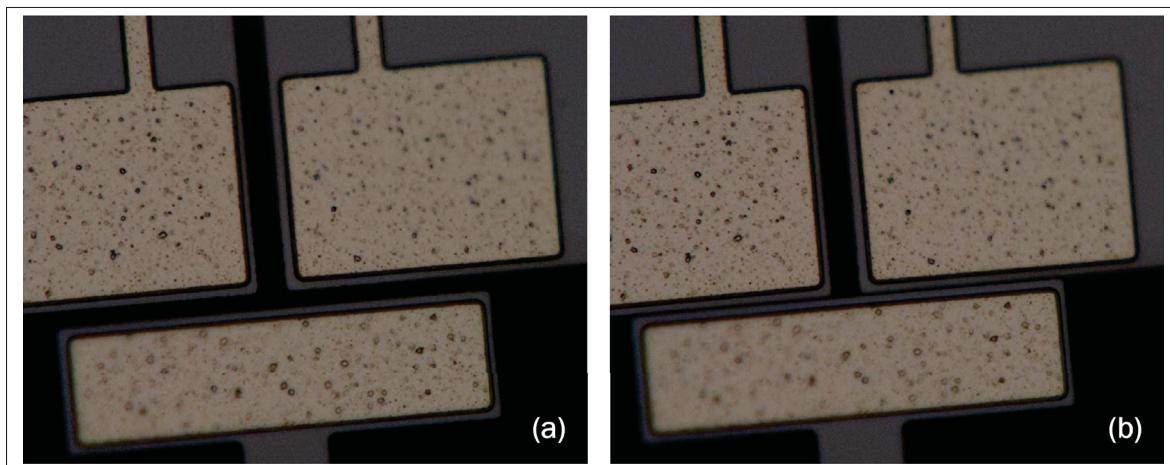

| Figure 4.10 | Observation d'un prototype de commutateur MEMS électrothermique<br>au microscope : (a) État ouvert, (b) État fermé .....                                                                                                                                                       | 148 |

## LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

|       |                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| AO    | Amplificateur opérationnel<br><i>Operational amplifier</i>                                                               |

| ASIC  | Circuit intégré spécifique à une application<br><i>Application-specific integrated circuit</i>                           |

| BCD   | Bipolar CMOS DMOS                                                                                                        |

| CAN   | Convertisseur analogique numérique<br><i>Analog to digital converter</i>                                                 |

| CAO   | Conception assistée par ordinateur                                                                                       |

| CC    | Cellule copieuse de courant<br><i>Current copier cell</i>                                                                |

| CM    | Multiplicateur de courant<br><i>Current multiplier</i>                                                                   |

| CMOS  | Complementary metal oxide semiconductor                                                                                  |

| CMRR  | Taux de réjection du mode commun<br><i>Common-mode rejection ratio</i>                                                   |

| CNA   | Convertisseur numérique analogique<br><i>Digital to analog converter</i>                                                 |

| CPIOS | Systèmes intégrés configurables d'entrée/sortie de puissance<br><i>Configurable integrated power input/output system</i> |

| CTAT  | Complémentaire à la température absolue<br><i>Complementary to absolute temperature</i>                                  |

| DC    | Courant continu<br><i>Direct current</i>                                                                                 |

| DMOS  | Double-diffused metal–oxide–semiconductor                                                                                |

| DNL   | Erreur de linéarité différentielle<br><i>Differential nonlinearity</i>                                                   |

|      |                                                                        |

|------|------------------------------------------------------------------------|

| DRC  | Vérification des règles de dessin<br><i>Design rule check</i>          |

| EAD  | <i>Electrically aware design</i>                                       |

| EM   | Électromigration                                                       |

| ERC  | <i>Electrical rule check</i>                                           |

| E/S  | Entrées / Sorties                                                      |

| ESD  | Décharge électrostatique<br><i>Electrostatic discharge</i>             |

| ÉTS  | École de Technologie Supérieure                                        |

| FC   | <i>Folded Cascode</i>                                                  |

| FEM  | Méthode des éléments finis<br><i>Finit element method</i>              |

| FF   | <i>Fast - Fast</i>                                                     |

| FOM  | Figure de mérite<br><i>Figure of merit</i>                             |

| FPGA | Réseau de portes programmables<br><i>Field-programmable gate array</i> |

| GND  | <i>Ground</i>                                                          |

| HV   | Haute tension<br><i>High voltage</i>                                   |

| IC   | Circuit imprimé<br><i>Integrated circuit</i>                           |

| IN   | Entrée<br><i>Input</i>                                                 |

| INA  | Amplificateur d'instrumentation<br><i>Instrumentation amplifier</i>    |

| INL  | Erreur de linéarité intégrale<br><i>Integral nonlinearity</i>          |

|        |                                                                                                |

|--------|------------------------------------------------------------------------------------------------|

| ISCAS  | <i>IEEE International Symposium on Circuits and Systems</i>                                    |

| LACIME | Laboratoire de communication et d'intégration de la microélectronique                          |

| LDO    | Régulateur de tension linéaire à faible chute<br><i>Low-dropout linear voltage regulator</i>   |

| LEM    | Modèle à éléments localisés<br><i>Lumped element modeling</i>                                  |

| LPF    | Filtre passe-bas<br><i>Low-pass filter</i>                                                     |

| LVS    | Dessin de masque vs schéma<br><i>Layout vs schematic</i>                                       |

| MEMS   | Microsystèmes électromécaniques<br><i>Micro-electromechanical systems</i>                      |

| MUMPs  | <i>Multi-User MEMS Process</i>                                                                 |

| MOSFET | Metal – oxyde – semiconductor field-Effect transistor                                          |

| MPC    | Commande prédictive<br><i>Model predictive control</i>                                         |

| NMOS   | N- channel Metal – Oxide – Semiconductor                                                       |

| NTC    | Coefficient de température négatif<br><i>Negative temperature coefficient</i>                  |

| OTA    | Amplificateur opérationnel à transconductance<br><i>Operational transconductance amplifier</i> |

| OUT    | Sortie<br><i>Output</i>                                                                        |

| PCB    | Carte de circuit imprimé<br><i>Printed circuit board</i>                                       |

| PDK    | <i>Process design kit</i>                                                                      |

| PEX    | <i>Parasitic extraction</i>                                                                    |

| PID    | Proportionnel-Intégral-Différentiel <i>Proportionnal-Integral-Differential</i>                 |

|      |                                                                                          |

|------|------------------------------------------------------------------------------------------|

| PMOS | P- channel Metal – Oxide – Semiconductor                                                 |

| PTAT | Proportionnelle à la température absolue<br><i>Proportional to absolute temperature</i>  |

| PTC  | Coefficient de température positif<br><i>Positive temperature coefficient</i>            |

| PVT  | Procédé-Tension-Température<br><i>Process-Voltage-Temperature</i>                        |

| PWM  | Modulation de largeur d'impulsion<br><i>Pulse with modulation</i>                        |

| RC   | Résistance - Capacitance                                                                 |

| RF   | Radio fréquence<br><i>Radio frequency</i>                                                |

| RTD  | Détecteur de température de résistance<br><i>Resistance temperature detector</i>         |

| S/H  | Échantillonage & Maintien <i>Sample &amp; Hold</i>                                       |

| SiP  | Système dans un boîtier<br><i>System in Package</i>                                      |

| SM   | Migration des électrons due aux contraintes volumétriques<br><i>Stress migration</i>     |

| SMA  | SubMiniature version A                                                                   |

| SS   | <i>Slow - Slow</i>                                                                       |

| TCR  | Coefficient de température de résistance<br><i>Temperature coefficient of resistance</i> |

| TM   | Migration des électrons due aux contraintes thermiques<br><i>Thermal migration</i>       |

| TSMC | Taiwan Semiconductor Manufacturing Company                                               |

| TT   | <i>Typical - Typical</i>                                                                 |

V/I Convertisseur tension courant

## *Voltage to current converter*

## LISTE DES SYMBOLES ET UNITÉS DE MESURE

| <b>UNITÉS DE LONGUEUR ET D'aire</b> |                  | <b>UNITÉS COMPOSANTS ÉLECTRIQUES</b> |               |

|-------------------------------------|------------------|--------------------------------------|---------------|

| m                                   | mètre            | $\text{M}\Omega$                     | megaohm       |

| mm                                  | millimètre       | $\text{k}\Omega$                     | kiloohm       |

| $\mu\text{m}$                       | micromètre       | $\Omega$                             | ohm           |

| nm                                  | nanomètre        | $\mu\text{F}$                        | microfarad    |

| $\text{m}^2$                        | mètre carré      | pF                                   | picofarad     |

| $\text{mm}^2$                       | millimètre carré | fF                                   | femtofarad    |

|                                     |                  | mH                                   | millihenry    |

| <b>UNITÉS ÉLECTRIQUES</b>           |                  | <b>UNITÉS DE FRÉQUENCE / TEMPS</b>   |               |

| A                                   | ampère           | GHz                                  | gigahertz     |

| mA                                  | milliampère      | MHz                                  | mégahertz     |

| $\mu\text{A}$                       | microampère      | kHz                                  | kilohertz     |

| nA                                  | nanoampère       | Hz                                   | kilohertz     |

| V                                   | volt             | s                                    | seconde       |

| mV                                  | millivolt        | ms                                   | milliseconde  |

| $\mu\text{V}$                       | microvolt        | $\mu\text{s}$                        | microseconde  |

| nV                                  | nanovolt         | ns                                   | nanoseconde   |

| W                                   | watt             | <b>UNITÉS DE TEMPÉRATURE</b>         |               |

| mW                                  | milliwatt        | $^{\circ}\text{C}$                   | degré celsius |

| <b>AUTRES UNITÉS</b>                |                  | K                                    | kelvin        |

| $^{\circ}$                          | degré            | <b>SYMBOLE D'ÉLÉMENT CHIMIQUE</b>    |               |

| dB                                  | décibel          | Pt                                   | platine       |

| J                                   | joule            | Ti                                   | titane        |

| C                                   | coulomb          |                                      |               |

| nN                                  | millinewton      |                                      |               |

---

**SYMBOLE DES COMPOSANTS ÉLECTRIQUES**

|                  |                                                                          |

|------------------|--------------------------------------------------------------------------|

| R                | Résistance électrique                                                    |

| L                | Inductance                                                               |

| C                | Condensateur                                                             |

| W                | Largeur du canal de conduction                                           |

| L                | Longueur du canal de conduction                                          |

| N                | Ratio ou multiplicateur                                                  |

| gm               | Transconductance                                                         |

| $\mu$            | Mobilité des porteurs de charge                                          |

| $C_{ox}$         | Capacité d'oxyde de grille                                               |

| $\beta$          | Constant représentant $\mu C_{ox}$                                       |

| $\lambda$        | Modulation de la longueur                                                |

| $V_{GS}$         | Tension grille-source                                                    |

| $V_{DS}$         | Tension drain-source                                                     |

| $V_{TH}$         | Tension de seuil                                                         |

| $V_{ov}/V_{EFF}$ | Tension de saturation                                                    |

| $V_A$            | Tension d'Early                                                          |

| $C_G$            | Condensateurs du transistor reportés à la grille                         |

| $A_{V_{TH}}$     | Constante pour la représentation de la variation statistique de $V_{TH}$ |

| $A_\beta$        | Constante pour la représentation de la variation statistique de $\beta$  |

| $\kappa$         | Constante dépendant de l'état du transistor                              |

| $V_{T,Diode}$    | Tension de seuil de la conduction d'une diode                            |

---

**SYMBOLE DES CIRCUITS DE LA PUCE CMOS**

|          |                        |

|----------|------------------------|

| VDD      | Tension d'alimentation |

| GND      | Masse                  |

| $I_{RC}$ | Courant de référence   |

|              |                                                                                  |

|--------------|----------------------------------------------------------------------------------|

| $I_{CNA}$    | Courant en sortie du CNA                                                         |

| $I_{CC}$     | Courant en sortie de la cellule copieuse de courant                              |

| $I_{VI}$     | Courant en sortie du convertisseur V-I                                           |

| $I_{CMH}$    | Courant de haute intensité en sortie du 1er étage du multiplicateur de courant   |

| $I_{CML}$    | Courant de faible intensité en sortie du 1er étage du multiplicateur de courant  |

| $I_{ACT}$    | Courant de haute intensité en sortie du 2ème étage du multiplicateur de courant  |

| $I_{MEA}$    | Courant de faible intensité en sortie du 2ème étage du multiplicateur de courant |

| $N_{diode}$  | Diode N                                                                          |

| $P_{diode}$  | Diode P                                                                          |

| $C_{DECAP}$  | Condensateur de découplage                                                       |

| $C_{mem}$    | Condensateur mémoire                                                             |

| $C_C$        | Condensateur de stabilisation                                                    |

| $I_{heater}$ | Courant du $\mu$ heater                                                          |

| $I_{dummy}$  | Courant du $\mu$ heater factice                                                  |

| $V_{in}^+$   | Tension d'entrée de la borne positive                                            |

| $V_{in}^-$   | Tension d'entrée de la borne négative                                            |

| $V_{CM}$     | Tension du mode commun                                                           |

| $A/G$        | Gain                                                                             |

| $A_d$        | Gain différentiel                                                                |

| $A_c$        | Gain mode commun                                                                 |

| $V_{OS}$     | Offset à l'entrée un amplificateur opérationnel                                  |

---

**SYMBOL DE LA PUCE CMOS ET DU COMMUTATEUR MEMS**

|           |                             |

|-----------|-----------------------------|

| S1 à S11  | Entrée numérique            |

| I1 à I6   | Entrée analogique           |

| O1 à O5   | Sortie numérique/analogique |

| AO1 à AO5 | Amplificateur opérationnel  |

|              |                                     |

|--------------|-------------------------------------|

| H1 à H4      | Sortie pour le $\mu$ heater         |

| D1           | Sortie pour le $\mu$ heater factice |

| VDD_8        | Tension d'alimentation de 8V        |

| VDD_5        | Tension d'alimentation de 5V        |

| GND1 à 4     | Masse de la puce                    |

| $R_{heater}$ | Résistance du $\mu$ heater          |

| $R_{dummy}$  | Résistance du $\mu$ heater factice  |

| $R_{on}$     | Résistance de ligne de transmission |

| $R_{WB}$     | Résistance du <i>wire bonding</i>   |

| $L_{WB}$     | Inductance du <i>wire bonding</i>   |

| $C_{PAD}$    | Condensateur du PAD/plots           |

| $C_{PCB}$    | Condensateur du PCB                 |

| $Nb_{plot}$  | Nombre de plots                     |

| $Y_{puce}$   | Longueur de la puce                 |

| $Y_{seal}$   | Longueur du <i>seal ring</i>        |

| $Y_{plot}$   | Longueur des plots                  |

| $Y_{anneau}$ | Longueur de l'anneau des E/S        |

| $pitch$      | Espacement entre les plots          |

---

### SYMBOLE DU MODÈLE ÉLECTROTHERMIQUE

|              |                                           |

|--------------|-------------------------------------------|

| $y_0/x_0$    | Conditions initiales d'une fonction       |

| $\alpha$     | Coefficient de température de résistance  |

| $R_{th}$     | Résistance thermique                      |

| $C_{th}$     | Capacité thermique                        |

| $T_h$        | Température du $\mu$ heater               |

| $\Delta T_h$ | Différence de température du $\mu$ heater |

| $R_h$        | Résistance du $\mu$ heater                |

|                    |                                                              |

|--------------------|--------------------------------------------------------------|

| $R_{h_{25}}$       | Résistance du $\mu$ heater à la température ambiante de 25°C |

| $I_h$              | Courant dans le $\mu$ heater                                 |

| $Q_h$              | Chaleur créée par le $\mu$ heater                            |

| $T_{amb} / T_{25}$ | Température ambiante / Température de 25°C                   |

| $\Delta t$         | Écart de temps                                               |

| $R_{shunt}$        | Résistance <i>shunt</i>                                      |

| $R_{shunt_{25}}$   | Résistance <i>shunt</i> à la température ambiante de 25°C    |

| $\alpha_s$         | Coefficient de température de la résistance <i>shunt</i>     |

| $R_{factice}$      | Résistance <i>shunt</i>                                      |

| $R_{factice_{25}}$ | Résistance <i>shunt</i> à la température ambiante de 25°C    |

| $\tau_{th}$        | Constante de temps                                           |

| $\varepsilon$      | Erreur relative                                              |

| $P_{elec}$         | Puissance électrique du $\mu$ heater                         |

| $P_{moy}$          | Puissance moyenne                                            |

| $P_{DC}$           | Puissance avec un courant continu                            |

| $P_{DC}$           | Puissance avec un courant avec une modulation PWM            |

| $P_{moy}^E$        | Puissance électrique moyenne                                 |

| $P_{moy}^T$        | Puissance thermique moyenne                                  |

| $i_{DC}$           | Courant continu                                              |

| $i_{PWM}$          | Courant avec une modulation PWM                              |

---

### SYMBOLE POUR LES RÉGULATEURS DE TENSION

|                 |                          |

|-----------------|--------------------------|

| $I_q$           | <i>Quiescent current</i> |

| $I_i / I_{IN}$  | Courant d'entrée         |

| $I_o / I_{OUT}$ | Courant de sortie        |

| $V_i / V_{IN}$  | Tension d'entrée         |

| $V_o / V_{OUT}$ | Tension de sortie        |

|                 |                                                                |

|-----------------|----------------------------------------------------------------|

| $\Delta V_{oT}$ | Variation de la tension de sortie par rapport à la température |

| $\Delta V_{oI}$ | Variation de la tension de sortie par rapport au courant       |

| $V_{TC}$        | Tension dépendant de la température                            |

| $V_{RLOAD}$     | Tension de la charge                                           |

| $\Delta T$      | Variation de la température                                    |

| $T_j$           | Température de jonction                                        |

| $R_{th-j}$      | Résistance thermique de la junction                            |

| $R_{amb}$       | Résistance à température ambiante                              |

---

### SYMBOLE POUR LA CARACTÉRISATION DE L'ÉLECTROMIGRATION

|                          |                                       |

|--------------------------|---------------------------------------|

| $\overleftarrow{F}_{EM}$ | Force induite par le flux d'électrons |

| e                        | Charge d'un électron                  |

| $Z^*$                    | Numéro atomique effectif              |