Assemblage et interconnexion de composant électro-optique

au-dessus de 100 GHz

par

Étienne THERRIAULT

MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAÎTRISE

AVEC MÉMOIRE EN GÉNIE ÉLECTRIQUE

M. Sc. A.

MONTRÉAL, LE “10 JUIN 2025”

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

Étienne Therriault, 2025

Cette licence Creative Commons signifie qu'il est permis de diffuser, d'imprimer ou de sauvegarder sur un autre support une partie ou la totalité de cette oeuvre à condition de mentionner l'auteur, que ces utilisations soient faites à des fins non commerciales et que le contenu de l'oeuvre n'ait pas été modifié.

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE:

M. Dominic Deslandes, directeur de mémoire

Département de génie électrique à l'École de technologie supérieure

M. Ricardo Izquierdo, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Frédéric Nabki, membre du jury

Département de génie électrique à l'École de technologie supérieure

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE "16 AVRIL 2025"

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## REMERCIEMENTS

Avant toute chose, je tiens à dédier les premières lignes de ce mémoire aux remerciements de tout ceux et celles qui, de par leur aide académique ou morale, m'ont permis de réaliser et compléter ce long projet de recherche.

Merci à mon directeur de recherche à l'ETS, Dr. Dominic Deslandes, pour son accompagnement tout au long de mon cheminement. Dominic, de par sa passion et son savoir inestimable, a tout d'abord su me transmettre bien des connaissances, mais a aussi permis de transformer celles-ci en compétences. En somme, je tenais à te remercier pour les nombreuses discussions captivantes et tout le temps que tu m'as gracieusement offert.

Merci à mon directeur de recherche chez Ciena, Jean-Frédéric Gagné, sans qui ce projet n'aurait jamais existé. Premièrement, c'est Jean-Frédéric qui m'a donné la piqûre pour le domaine qui le passionne lors de mon premier stage chez Ciena en 2018, soit celui des radio fréquences. Ensuite, c'est aussi ce dernier qui a mis sur pied ce projet de recherche MITACS. Je tenais à te remercier pour ta confiance, tes précieux enseignements, ton temps et ton accompagnement du début à la fin de ce projet de recherche.

Merci à mes collègues de chez Ciena qui ont su me consacré de leur temps pour répondre à mes nombreuses questions et interrogations. Je tenais à remercier spécialement Gregory Brookes pour sa patience et son temps qui n'a jamais cessé de répondre à mes questions, et ce, même lorsque celle-ci était posé pour la enième fois.

Je tenais aussi à remercier aussi les membres du laboratoire LACIME de l'ETS pour leurs efforts soutenus dans la fabrication des pièces LTCC malgré les difficultés rencontrées.

Merci à ma conjointe, Alexandra Bédard, pour son support émotionnelle inestimable pendant ces 3 années. Sans toi, les embûches auraient eu raison de ma santé mentale et ce projet n'aurait pas été complété. Je pense que le plus difficile n'est pas de réaliser un projet de recherche mais bien de vivre avec quelqu'un qui en réalise un, surtout en temps de télétravail ! Ensuite, merci à ma mère, Andrée St-Laurent, mon père, André Therriault. Vos mots d'encouragements m'ont

grandement aidés. Finalement, merci à ma famille et à mes amis proches pour les bons moments partagés dans ces dernières années.

# Assemblage et interconnexion de composant électro-optique au-dessus de 100 GHz

Étienne TERRIAULT

## RÉSUMÉ

La demande croissante en termes de débits de données dans les liaisons haut débit modernes force les ingénieurs et physiciens œuvrant dans le domaine des communications à concevoir de nouveaux systèmes opérant dans les THz, et ce, avec de très large bande passante. Au cours des dernières décennies, les composants sur semiconducteurs ont atteint de nouveaux sommets en termes de fréquence limite d'opération en franchissant la barre des 100 GHz. De plus, les modulateurs optiques atteignent désormais des bandes passantes de modulation à grand signal supérieure à 100 GHz sur silicium hybride photonique. Toutefois, le principal défi auquel ces systèmes sont actuellement confrontés est le manque d'interconnexions large bande efficaces.

La technique d'encapsulation conventionnelle qu'est la liaison par fils n'est vraisemblablement plus la solution d'interfaçage approprié aux ondes millimétriques en raison d'un fort comportement inductif forçant une utilisation en bande étroite ou causant une dégradation des performances large bande. Heureusement, d'autres technologies, comme celle de la puce retournée, semblent très prometteuses. En effet, de nombreuses transitions par puces retournées large bande de DC jusqu'au-delà de 100 GHz ont été démontrées dans la littérature via l'utilisation de différentes techniques et technologies de billes. Le problème est que plusieurs d'entre elles ne sont pas rentables ou utilisent des processus vraiment complexes qui ne conviennent pas à la production de masse. Toutefois, il existe une technologie de bille qui est très accessible, a une excellente répétabilité, un faible coût et permet une grande densité de connection. Cette technologie de liaison est la bille d'or empilable et elle est peut-être réalisée très simplement à l'aide d'une machine de liaison par fils conventionnelle. L'un des avantages principaux de cette technique est le fait que les billes d'or peuvent être empilées afin de réduire le comportement capacitif de la transition Flip-Chip et faciliter l'obtention d'une plus grande bande passante avec moins de compensation ou simplement être utilisées comme une option flexible pour satisfaire les besoins de conception. Dans la littérature, de bonnes performances large bande ont été démontrées pour les billes d'or empilées dans les interconnexions puce à puce sur ligne simple au-delà de 100 GHz, mais les transitions puce à boîtier et celles sur lignes différentielles restent à démontrer.

Ce travail a pour but d'étudier la technologie de billes d'or empilées comme type d'interconnexions puce à boîtier pour des lignes coplanaires simples et différentielles du DC jusqu'à plus de 100GHz. Afin de respecter l'aspect contextualisation, les choix, des substrats du boîtier et de la puce sont le LTCC et le silicium respectivement. Des simulations ondes pleines 3D utilisant HFSS ont été effectués pour l'optimisation et la compensation de manière à trouver les meilleurs candidats. Ensuite, les assemblages expérimentaux de puces retournées ont été caractérisés du DC à 110 GHz à l'aide de sondes RF. Finalement, des règles de conception ont été extraites pour guider les futurs concepteurs souhaitant utiliser cette technologie.

**Mots-clés:** onde millimétrique, micro-onde, interconnexion, puce retournée, fils d'or, compensation, transition à large bande, encapsulation, circuit intégré, large bande, photonique, céramique, LTCC, silicium, guide d'ondes coplanaire, ligne différentielle, ligne simple, RF

# MILLIMETER-WAVE COMPONENT PACKAGING AND INTERCONNECT USING STACKED GOLD STUD

Étienne THERRIAULT

## ABSTRACT

The increasing demand for data rates in modern high-speed links calls for new updated systems operating in high millimetre-wave frequency with a very large bandwidth. Over the past few decades, semiconductor devices have attained new heights in terms of frequency limits by reaching THz frequencies. Furthermore, optical modulators are now achieving a beyond-100-GHz large-signal modulation bandwidth in hybrid silicon photonics. The main challenge that such systems are currently facing is the lack of efficient broadband interconnections.

Conventional packaging techniques like the wirebond exhibit poor performance at THz frequencies because of high inductive behaviour. However, flip-chip technology seems to be the most promising option for broadband THz interconnects. Numerous broadband Flip-Chip transitions from DC to beyond 100 GHz have been demonstrated in the literature using different techniques and bump technologies. The problem is that many are not cost-effective or use really complex processes that are not suitable for mass production. However, there is one interesting type of bonding technique that is highly accessible, has excellent repeatability, low cost and allows small pitches for high signal density. This technology is called the gold stud bumping and it is made using a wire bonder. One of the advantages of this technique is the fact that the gold stud can be stacked in order to reduce the capacitive behaviour of the Flip-Chip transition and makes it easier to achieve greater bandwidth with less compensation or simply be used as a flexible option to satisfy the needs of a designer. In the literature, good broadband performance has been demonstrated for stacked gold studs in single-ended chip-to-chip interconnections above 100 GHz but chip-to-package and differential transitions are yet to be demonstrated.

This work aims to study the use of stacked gold stud bump chip-to-package interconnects from DC to above 100 GHz for single ended and differential coplanar waveguide transitions. In order to respect the contextualization aspect, the choices of the package and chip substrates are chosen to be LTCC and silicon, respectively. Full-wave simulations using HFSS have been used for optimization and compensation in order to find candidates exhibiting good broadband performance. The experimental Flip-Chip assembly has been characterized from DC to 110 GHz using RF probes. Finally, design rules have been extracted to help guide future designers wishing to use this technology.

**Keywords:** millimeter-wave, microwave, interconnect, flip-chip, gold stud, compensation, wideband transition, packaging, integrated circuit, broadband, photonic, LTCC, silicon, coplanar waveguide, differential, single-ended

## TABLE DES MATIÈRES

|                                                                                                     | Page |

|-----------------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                                  | 1    |

| CHAPITRE 1 REVUE DE LITTÉRATURE .....                                                               | 5    |

| 1.1    Liaison par fil .....                                                                        | 6    |

| 1.1.1    Ruban .....                                                                                | 7    |

| 1.1.2    Compensation .....                                                                         | 8    |

| 1.1.3    MicroCoax .....                                                                            | 9    |

| 1.1.4    Conclusion liaison par fil .....                                                           | 11   |

| 1.2    Puce retournée .....                                                                         | 11   |

| 1.2.1    Billes de soudures .....                                                                   | 13   |

| 1.2.2    Piliers de cuivre .....                                                                    | 15   |

| 1.2.3    Billes d'or .....                                                                          | 17   |

| 1.2.4    Alternative .....                                                                          | 19   |

| 1.2.5    Conclusion puce retournée .....                                                            | 20   |

| 1.3    Conclusion de la Revue .....                                                                 | 22   |

| CHAPITRE 2 DÉVELOPPEMENT DES STRUCTURES INDIVIDUELLES<br>D'UNE INTERCONNEXION PUCE À SUBSTRAT ..... | 25   |

| 2.1    Choix des technologies .....                                                                 | 26   |

| 2.1.1    Substrat .....                                                                             | 26   |

| 2.1.2    Puce .....                                                                                 | 28   |

| 2.2    Développements et analyses au niveau du substrat .....                                       | 31   |

| 2.2.1    Considérations et choix préliminaires .....                                                | 31   |

| 2.2.2    Mitigation des modes de substrat parasites .....                                           | 39   |

| 2.2.2.1    Mode des plaques parallèles (PPL) .....                                                  | 41   |

| 2.2.2.2    Mode guide d'onde rectangulaire (TE10) .....                                             | 47   |

| 2.3    Développements et analyses au niveau des puces .....                                         | 49   |

| 2.3.1    Considérations et choix préliminaires .....                                                | 49   |

| 2.3.2    Effet de proximité .....                                                                   | 52   |

| 2.4    Présentations des Billes/Piliers .....                                                       | 55   |

| 2.5    Performance des structures individuelles .....                                               | 57   |

| CHAPITRE 3 DÉVELOPPEMENT DES TRANSITIONS PUCE À SUB-<br>STRATS PAR PUCE RETOURNÉE .....             | 59   |

| 3.1    Modèles initiaux .....                                                                       | 60   |

| 3.1.1    Présentation .....                                                                         | 60   |

| 3.1.2    Caractéristiques et performances .....                                                     | 61   |

| 3.2    Étude par variation .....                                                                    | 68   |

| 3.2.1    Variation des trous de liaison (via) .....                                                 | 69   |

| 3.2.2    Patron de masse .....                                                                      | 72   |

|                                                  |                                                                                          |            |

|--------------------------------------------------|------------------------------------------------------------------------------------------|------------|

| 3.2.3                                            | Pastilles (Pads) .....                                                                   | 75         |

| 3.2.4                                            | Performances en fonction des piliers .....                                               | 76         |

| 3.3                                              | Compensation de l'impédance .....                                                        | 77         |

| 3.3.1                                            | Méthode(s) utilisée(s) .....                                                             | 79         |

| 3.3.2                                            | Modèles optimisés .....                                                                  | 81         |

| <b>CHAPITRE 4 VALIDATION EXPÉRIMENTALE .....</b> |                                                                                          | <b>85</b>  |

| 4.1                                              | Structures de puces retournées sélectionnées .....                                       | 85         |

| 4.2                                              | Équipements de mesure .....                                                              | 86         |

| 4.3                                              | Fabrication et caractérisation du substrat .....                                         | 88         |

| 4.3.1                                            | Topologie .....                                                                          | 88         |

| 4.3.2                                            | Structures de calibration .....                                                          | 90         |

| 4.3.3                                            | Première itération de fabrication .....                                                  | 93         |

| 4.3.3.1                                          | Inspection .....                                                                         | 94         |

| 4.3.3.2                                          | Mesures des TRL .....                                                                    | 96         |

| 4.3.4                                            | Deuxième itération de fabrication .....                                                  | 99         |

| 4.3.4.1                                          | Inspection .....                                                                         | 99         |

| 4.3.4.2                                          | Mesures des TRL .....                                                                    | 100        |

| 4.4                                              | Fabrication et caractérisation des puces .....                                           | 103        |

| 4.4.1                                            | Fabrication No. 1 .....                                                                  | 103        |

| 4.4.1.1                                          | Inspection .....                                                                         | 104        |

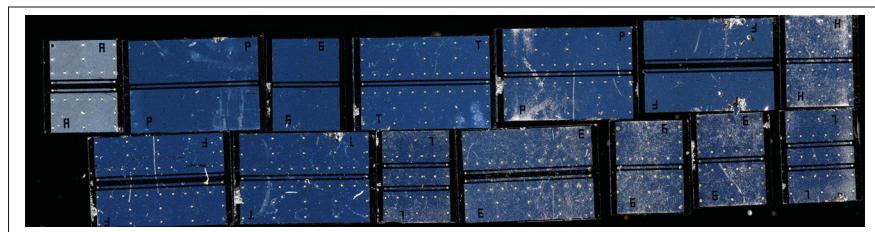

| 4.4.2                                            | Fabrication No. 2 .....                                                                  | 107        |

| 4.4.2.1                                          | Inspection .....                                                                         | 107        |

| 4.4.2.2                                          | Mesures .....                                                                            | 107        |

| 4.5                                              | Assemblage et caractérisation des puces retournées .....                                 | 114        |

| 4.5.0.1                                          | Inspection .....                                                                         | 114        |

| 4.5.1                                            | Mesures .....                                                                            | 115        |

| 4.5.1.1                                          | Ligne simple .....                                                                       | 115        |

| 4.5.1.2                                          | Ligne différentielle .....                                                               | 117        |

| 4.5.2                                            | Performances équivalentes sur gaufre de silicium haute résistivité<br>(simulation) ..... | 118        |

| 4.6                                              | Conclusion expérimental .....                                                            | 123        |

| <b>CONCLUSION ET RECOMMANDATIONS .....</b>       |                                                                                          | <b>125</b> |

| <b>BIBLIOGRAPHIE .....</b>                       |                                                                                          | <b>129</b> |

## LISTE DES TABLEAUX

|             | Page                                                                                                                                                                                            |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 | Tableau comparatif des technologies d’interconnexion .....                                                                                                                                      | 22  |

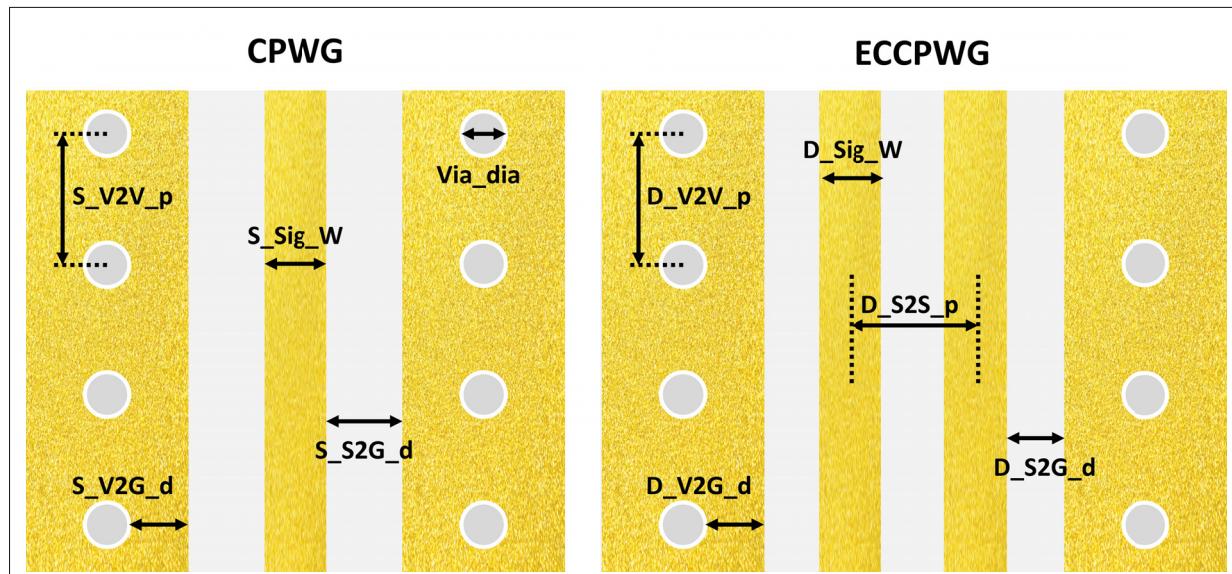

| Tableau 2.1 | Dimensions des modèles des lignes CPWG et ECCPWG du substrat .....                                                                                                                              | 39  |

| Tableau 2.2 | Fréquence d’atteinte de 1% de perte en puissance sur 4.8 mm en fonction du diamètre et de la distance centre à centre des trous de liaison (via) sur les deux types de lignes du substrat ..... | 44  |

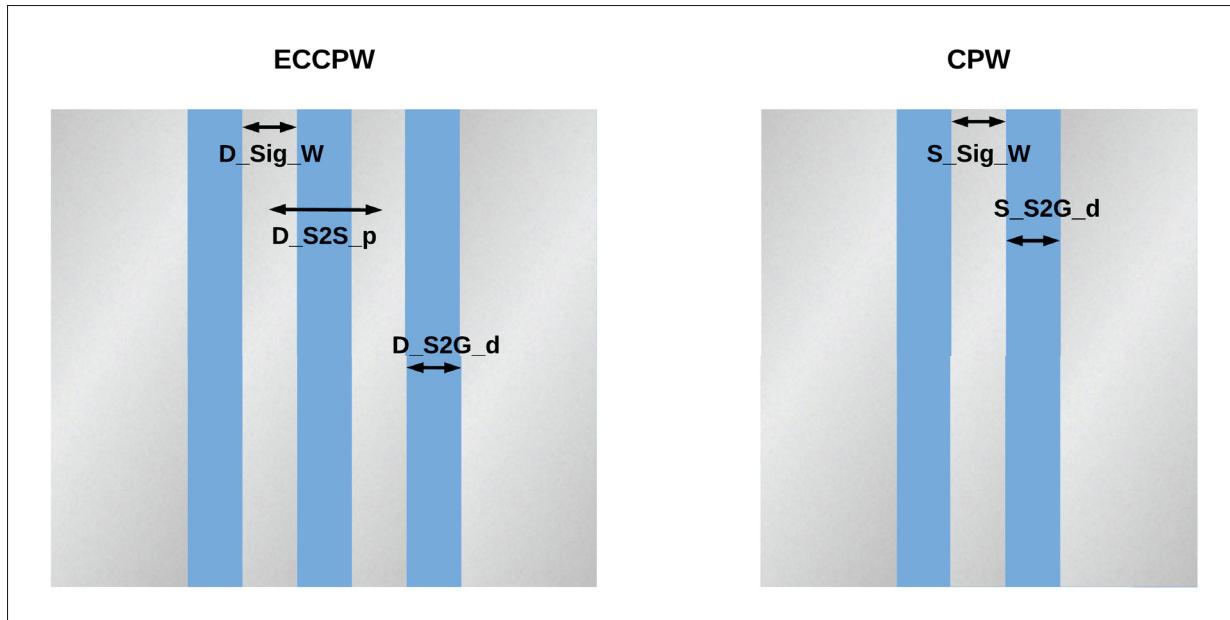

| Tableau 2.3 | Dimensions des modèles des lignes CPW et ECCPW des puces pour une propagation avec de l’air au-dessus .....                                                                                     | 52  |

| Tableau 2.4 | Dimensions des largeurs de signal des lignes CPW et ECCPW des puces avec le substrat .....                                                                                                      | 57  |

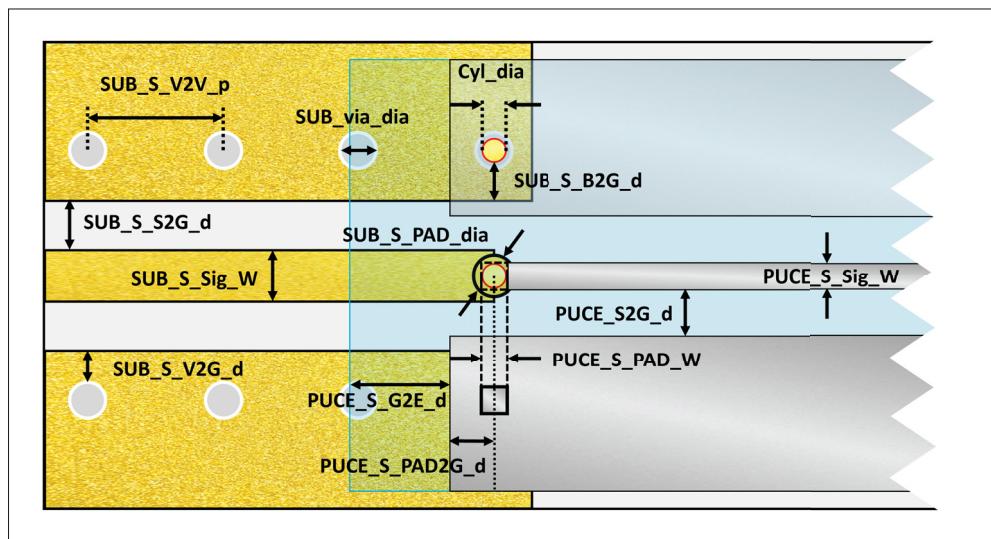

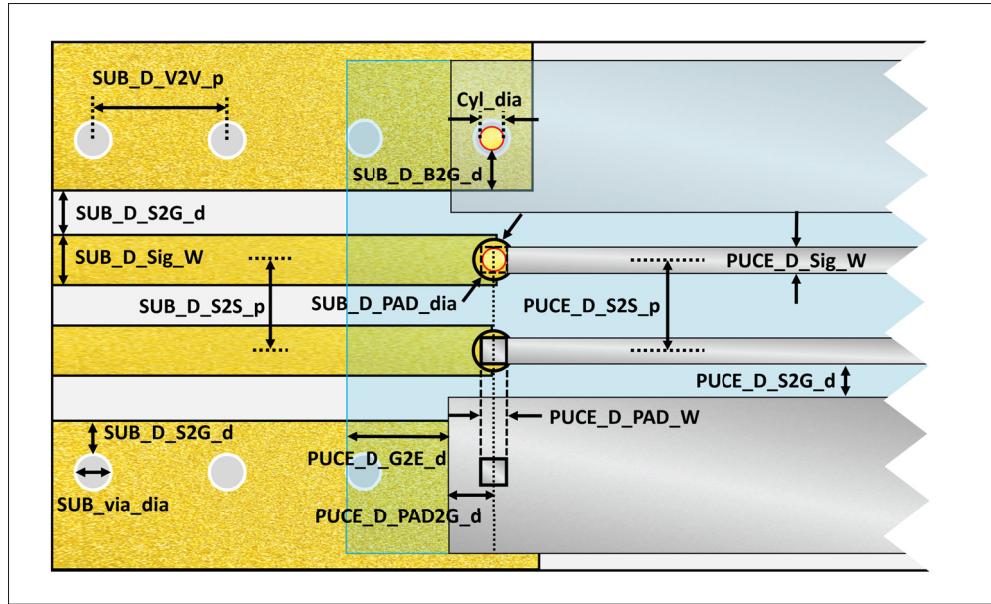

| Tableau 3.1 | Dimensions principales des modèles initiaux de puce retournés .....                                                                                                                             | 62  |

| Tableau 3.2 | Tableau comparatif du rétrécissement des dimensions .....                                                                                                                                       | 73  |

| Tableau 3.3 | Techniques de compensation utilisées dans les modèles adaptés présentés avec leurs dimensions .....                                                                                             | 84  |

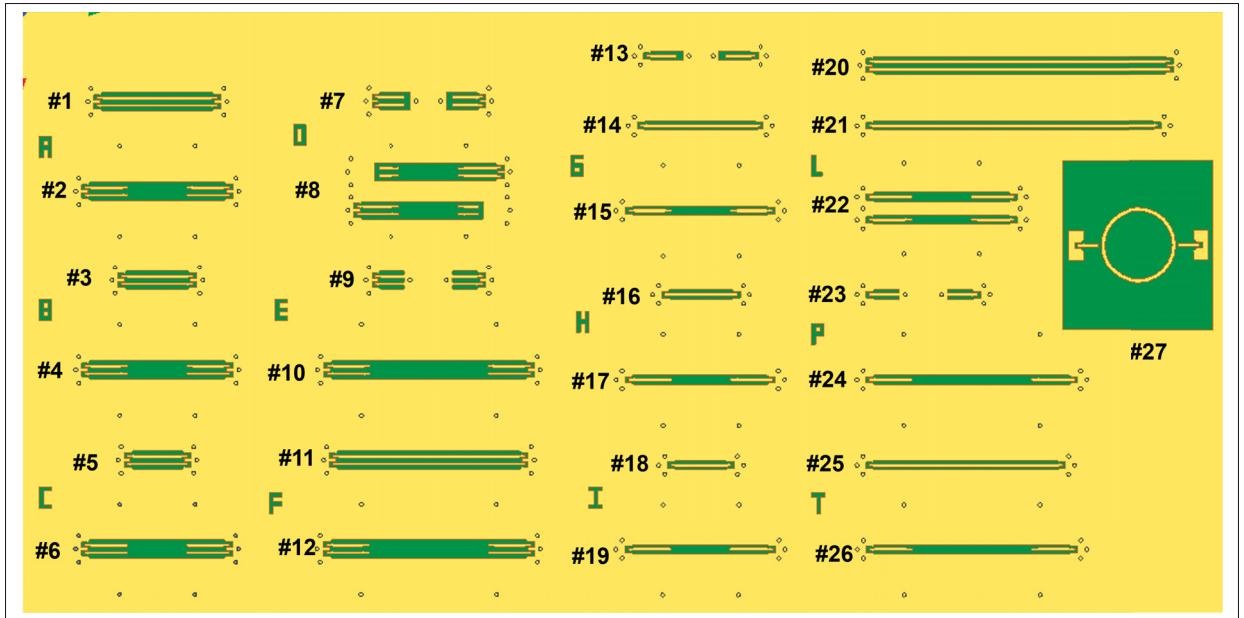

| Tableau 4.1 | Tableau d’identification des structures présentées dans la topologie de fabrication du substrat .....                                                                                           | 89  |

| Tableau 5.1 | Tableau comparatif des technologies d’interconnexion .....                                                                                                                                      | 127 |

## LISTE DES FIGURES

|            | Page                                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1 | Exemple d'interconnexion par ruban (Shireen, Shi, Yao & Prather, 2011) ..... 7                                                                            |

| Figure 1.2 | Exemple de compensation LC d'une liaison par fil (Valenta <i>et al.</i> , 2015) ..... 9                                                                   |

| Figure 1.3 | Étapes de fabrication pour un MicroCoax (Cahill, Sanjuan & Levine, 2006) ..... 10                                                                         |

| Figure 1.4 | Exemple de puce retournée avec billes de soudure DC-250 GHz de CPW vers guide d'onde à ruban (stripline) (Monayakul <i>et al.</i> , 2015) ..... 15        |

| Figure 1.5 | Exemple de puce retournée avec pilier de cuivre (Farid, Ahmed, Simsek & Rodwell, 2021) ..... 16                                                           |

| Figure 1.6 | Exemple de puce retournée avec billes d'or (cylindrique) de DC à 170 GHz avec son modèle équivalent (Khan, Ulusoy, Schmid & Papapolymerou, 2014) ..... 18 |

| Figure 1.7 | Exemple de billes d'or (sphérique) empilées (Testa, Morath, Goran, Carta & Ellinger, 2019) ..... 19                                                       |

| Figure 1.8 | Exemple de transition QUILT (Fay <i>et al.</i> , 2014) ..... 20                                                                                           |

| Figure 1.9 | Exemple de transition 3D par jet d'aérosol (Qayyum, Abt, Roch, Ulusoy & Papapolymerou, 2017) ..... 20                                                     |

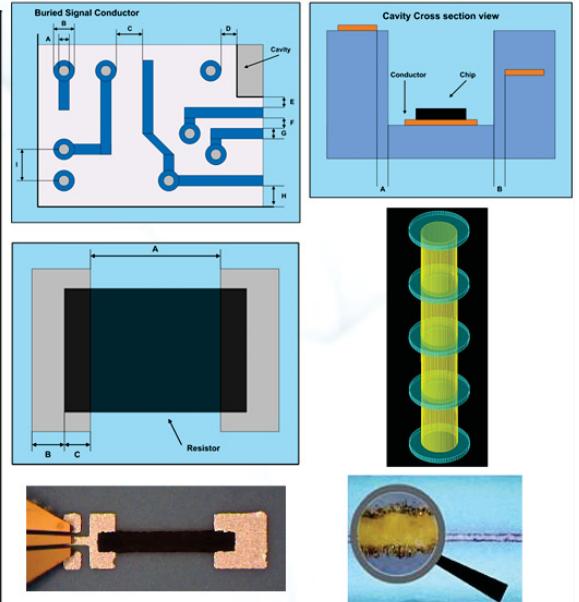

| Figure 2.1 | Règle de conception du procédé LTCC au LACIME (voir Note) ..... 27                                                                                        |

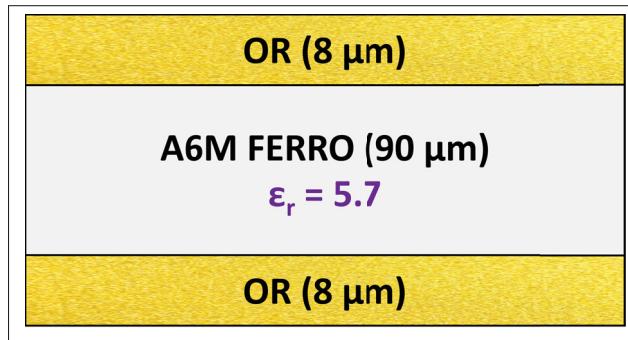

| Figure 2.2 | Propriétés mécaniques et électromagnétiques des bandes A6M ..... 28                                                                                       |

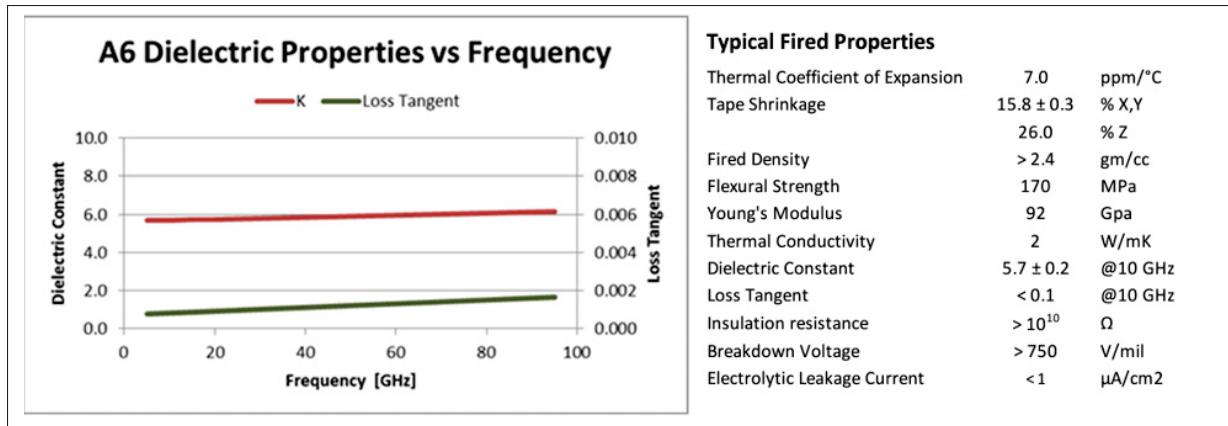

| Figure 2.3 | Technologies SiGe BiCMOS offertes par STMicroelectronics (STMicroelectronics, 2023) ..... 30                                                              |

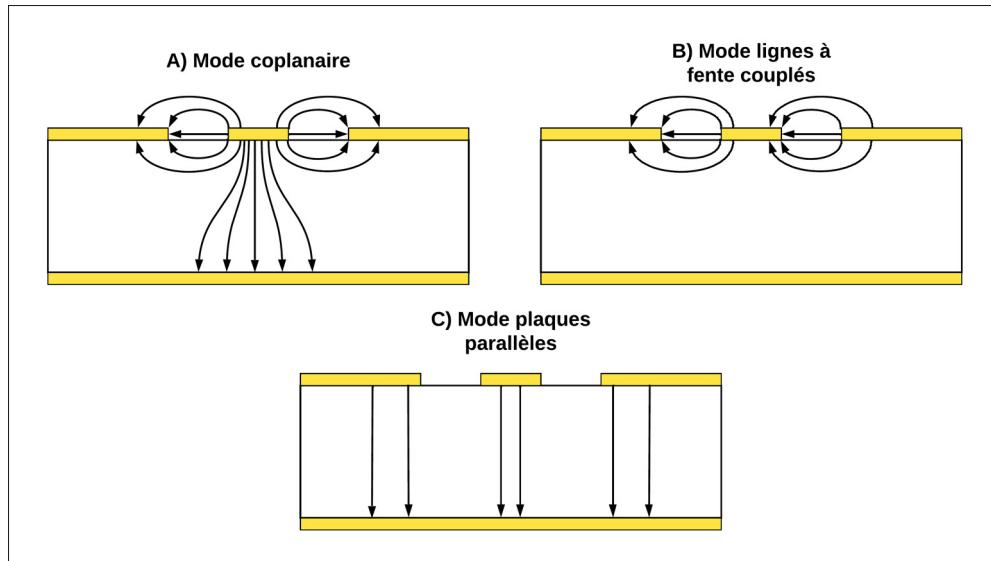

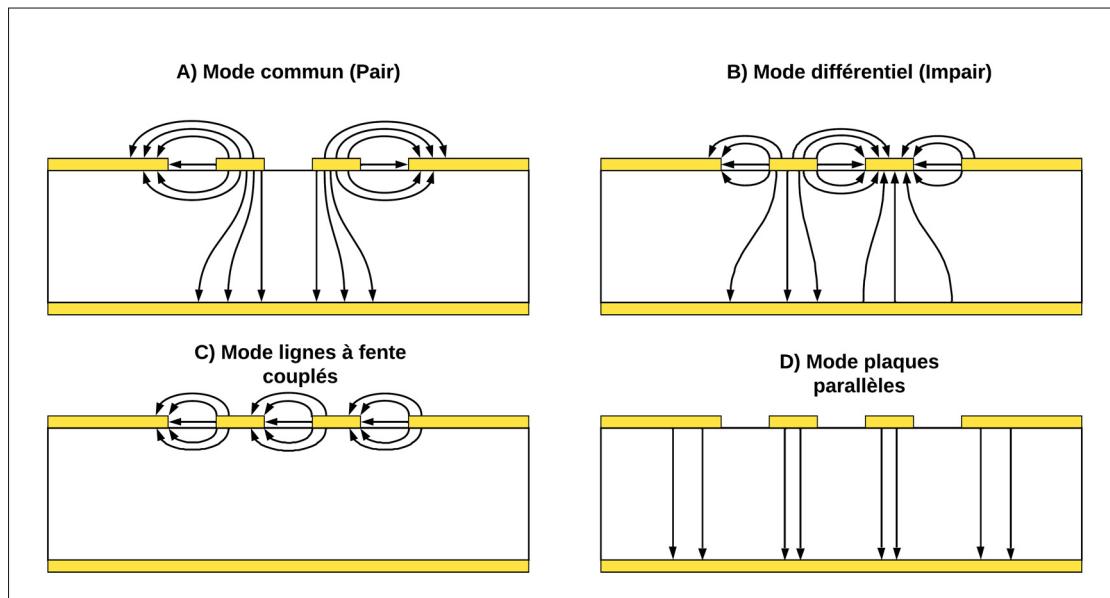

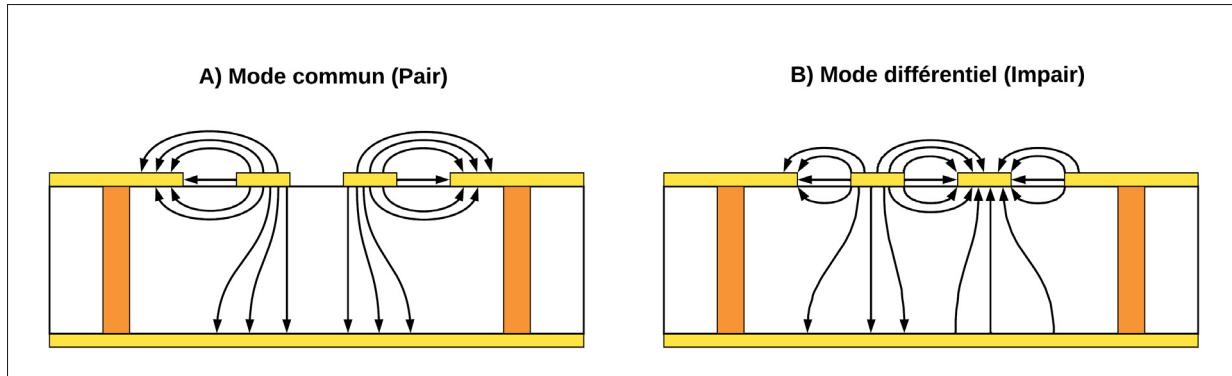

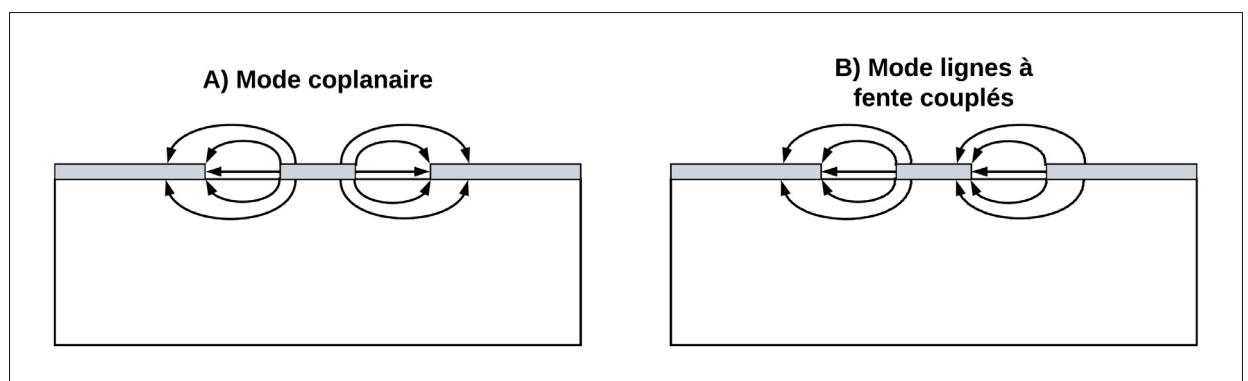

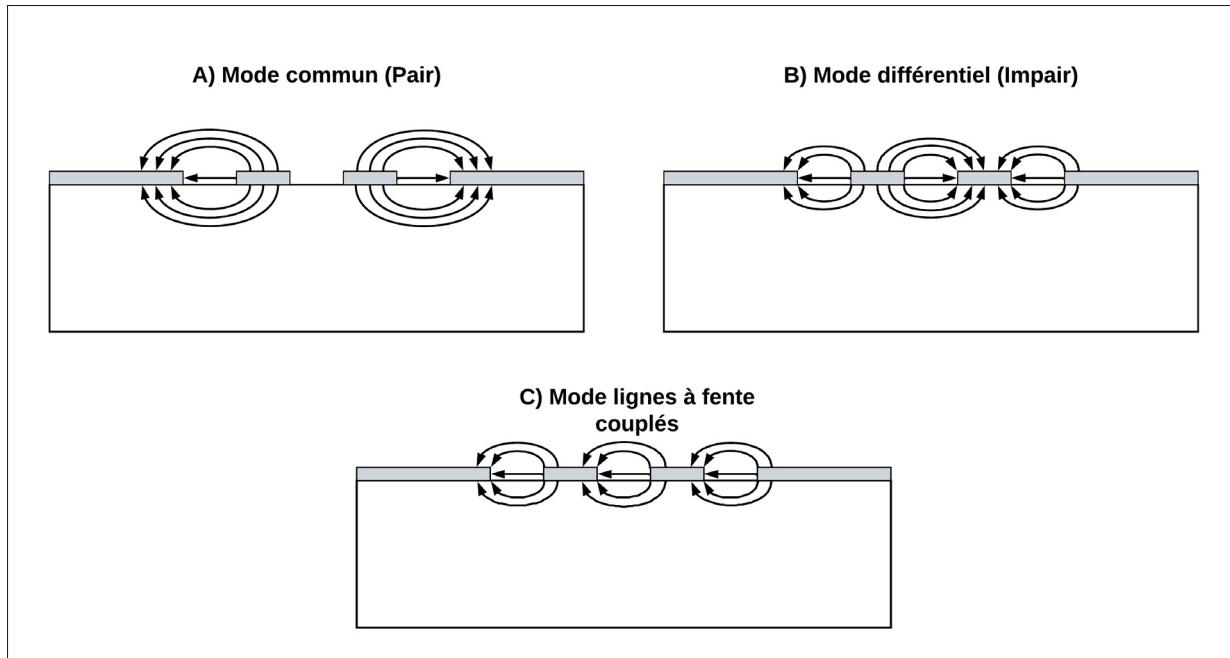

| Figure 2.4 | Ligne de champs électrique des modes pouvant propager à toute fréquence sur un CPWG ..... 32                                                              |

| Figure 2.5 | Ligne de champs électrique des modes pouvant propager à toute fréquence sur un ECCPWG ..... 32                                                            |

| Figure 2.6 | Ligne de champs électrique des modes pouvant propager à toute fréquence sur un CPWG avec trous de liaison (via) ..... 34                                  |

|             |                                                                                                                                                                                                 |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.7  | Ligne de champs électrique des modes pouvant propager à toute fréquence sur un CPWG avec trous de liaison (via) .....                                                                           | 34 |

| Figure 2.8  | Schéma du mode guide d'onde rectangulaire dans une ligne coplanaire avec référence à la masse inférieure et clôture de trous de liaison (via) .....                                             | 36 |

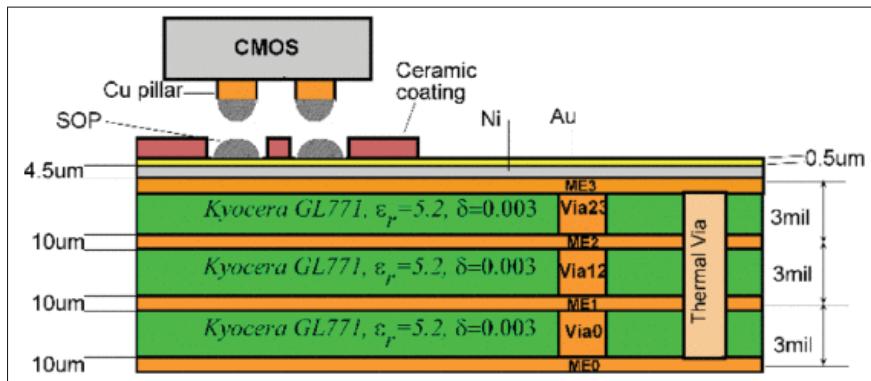

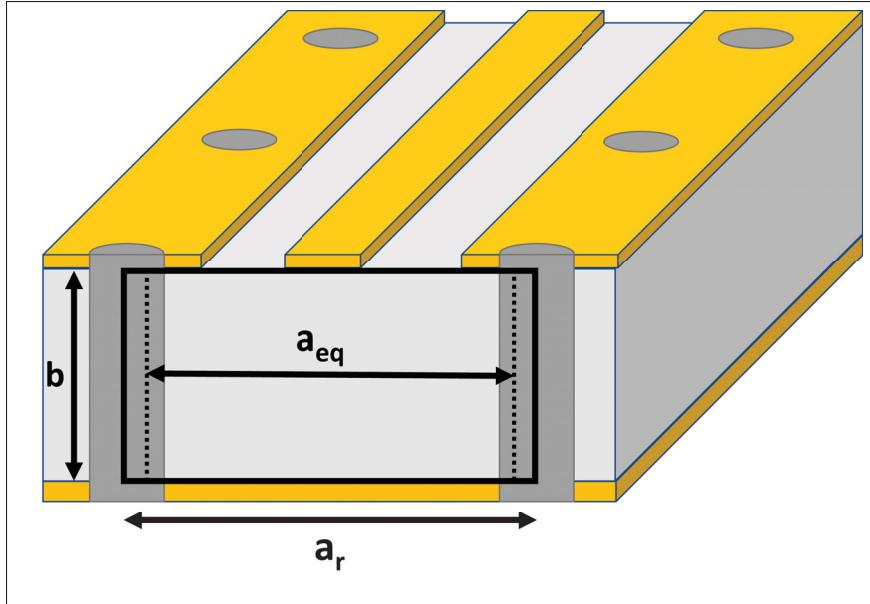

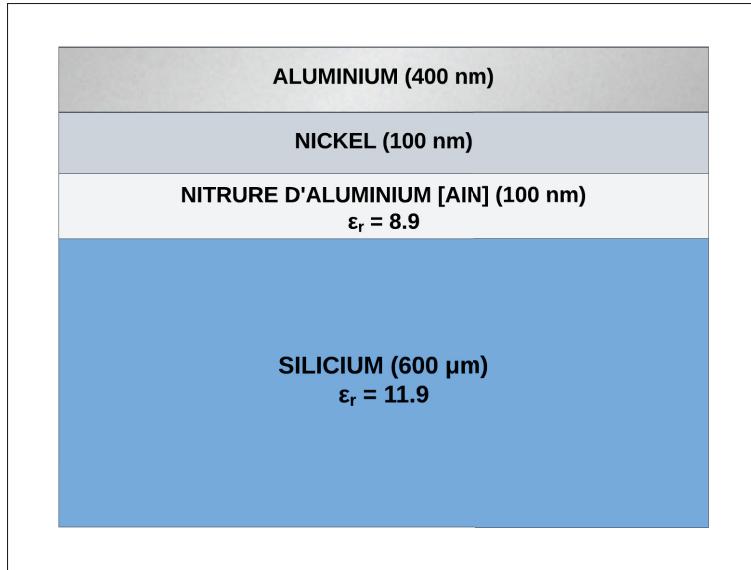

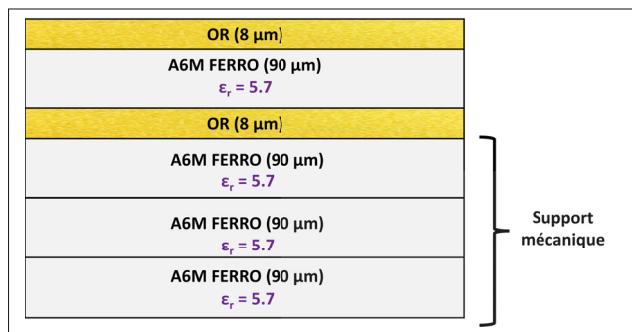

| Figure 2.9  | Schéma d'empilement des couches du substrat .....                                                                                                                                               | 37 |

| Figure 2.10 | Schéma des modèles initiaux des lignes CPWG et ECCPWG vues de haut du substrat .....                                                                                                            | 38 |

| Figure 2.11 | Légende se rapportant aux annotations sur les graphiques des sections suivantes .....                                                                                                           | 41 |

| Figure 2.12 | Schéma des lignes annotées des valeurs nominales des variables utilisées pour l'étude des modes d'ordre supérieurs .....                                                                        | 41 |

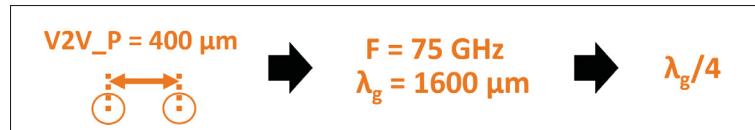

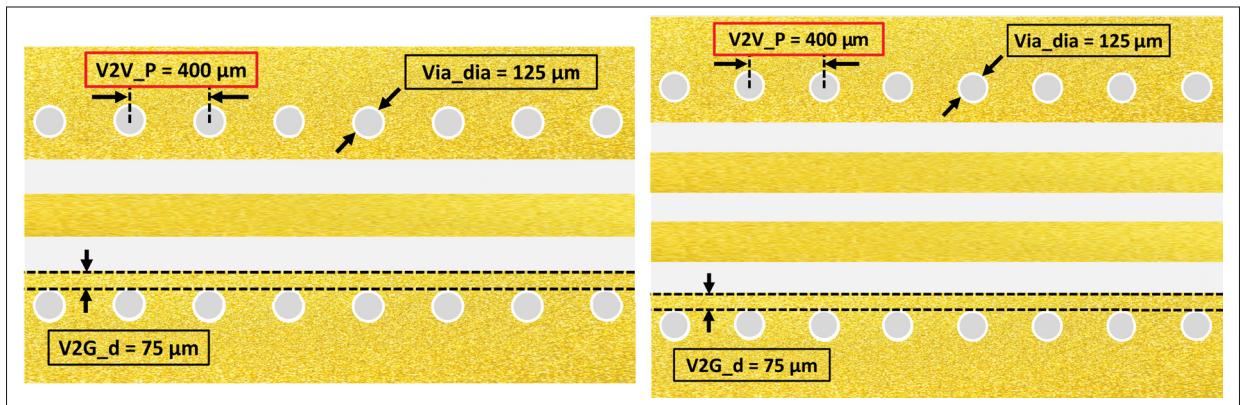

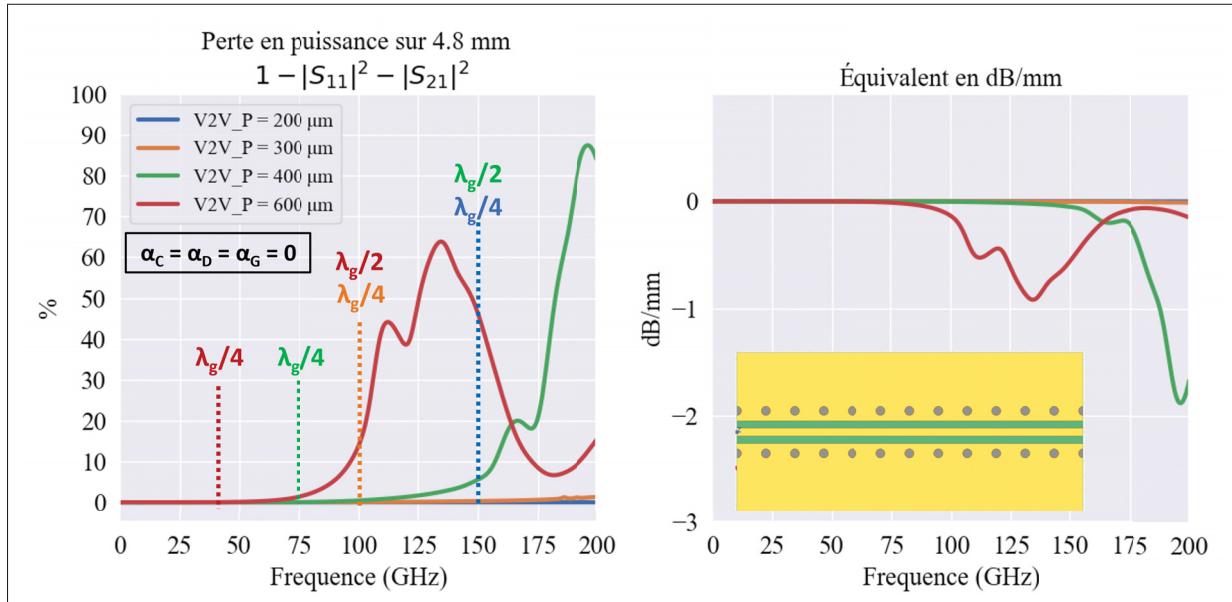

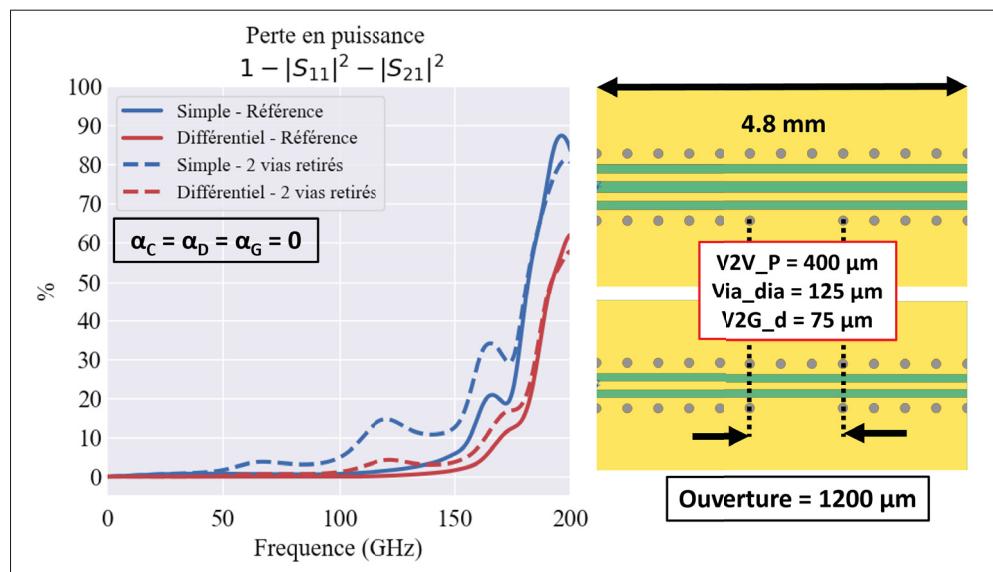

| Figure 2.13 | Perte en puissance en simulation de la ligne simple du substrat en fonction de la distance centre à centre des trous de liaisons (via) avec $V2V_P = 400\mu\text{m}$ .....                      | 42 |

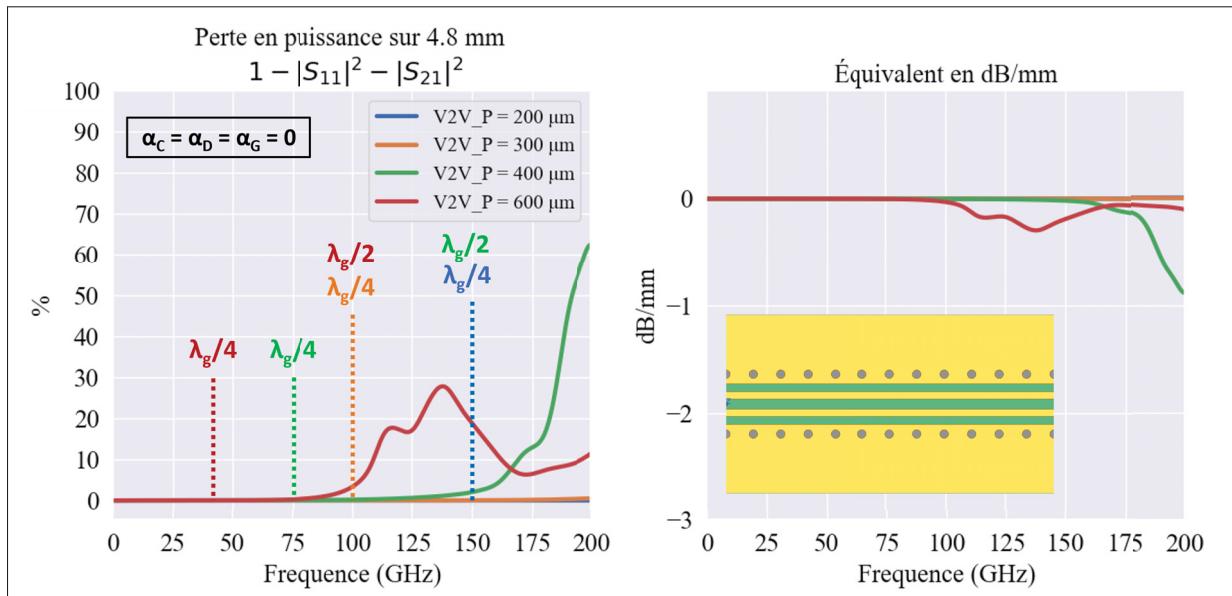

| Figure 2.14 | Perte en puissance en simulation de la paire différentielle du substrat en fonction de la distance centre à centre des trous de liaisons (via) .....                                            | 42 |

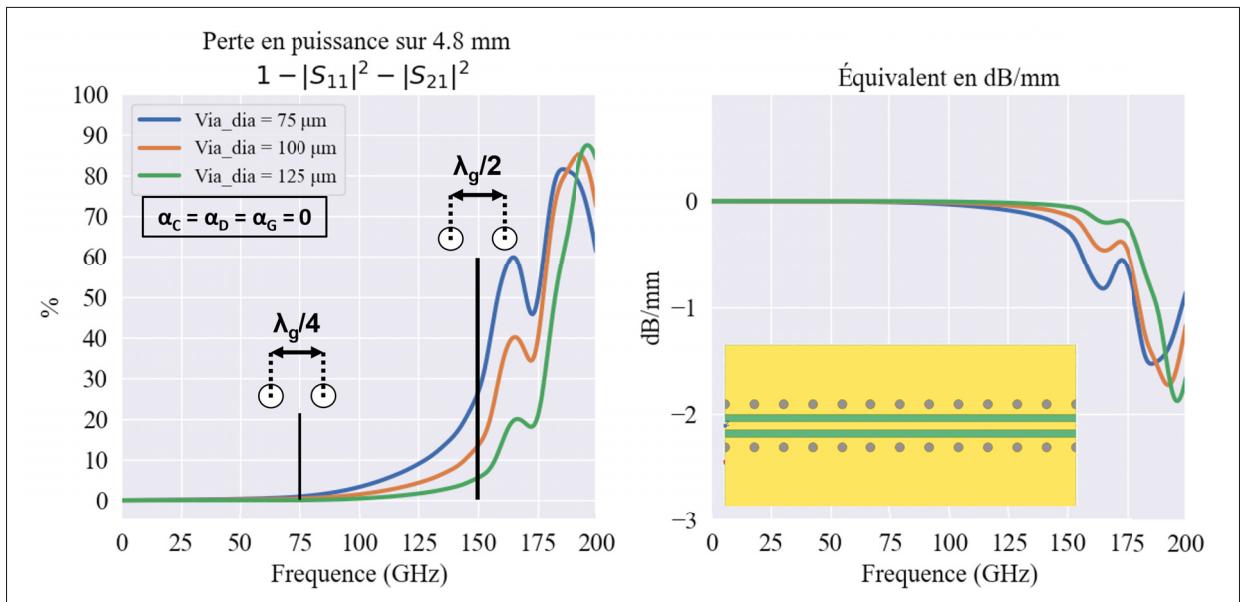

| Figure 2.15 | Perte en puissance en simulation de la ligne simple du substrat en fonction du diamètre des trous de liaisons (via) .....                                                                       | 43 |

| Figure 2.16 | Perte en puissance en simulation des lignes simple et différentielle du substrat lors d'une discontinuité au niveau de la clôture de trous de liaison .....                                     | 45 |

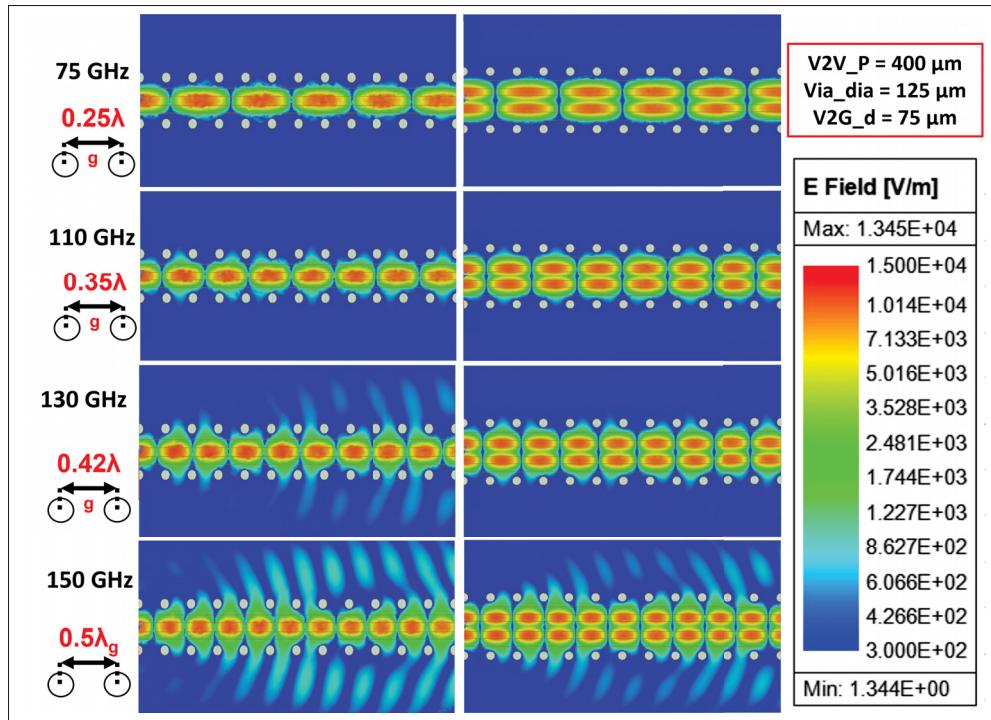

| Figure 2.17 | Comparaison des champs électriques dans le substrat pour la ligne simple et différentielle en fonction de la fréquence pour $V2V_p = 400\mu\text{m}$ et $Via\_dia = 125\mu\text{m}$ .....       | 46 |

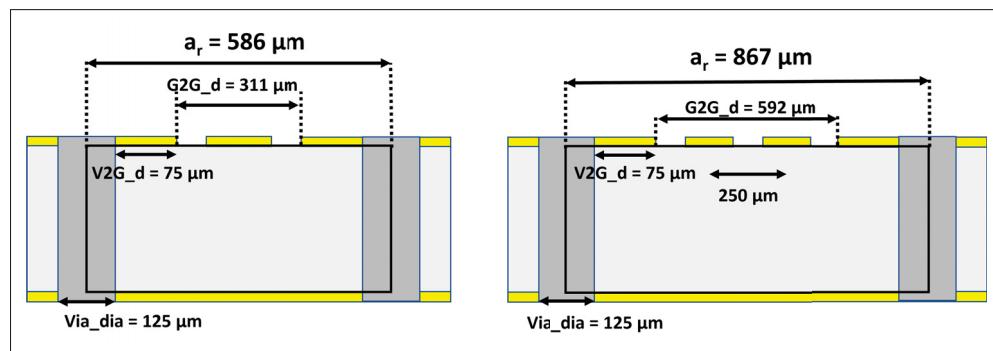

| Figure 2.18 | Meilleur cas de largeur du guide d'onde dans le substrat pour la ligne simple (Gauche) et différentielle (Droite) selon les dimensions nominales minimums de la présente fabrication LTCC ..... | 47 |

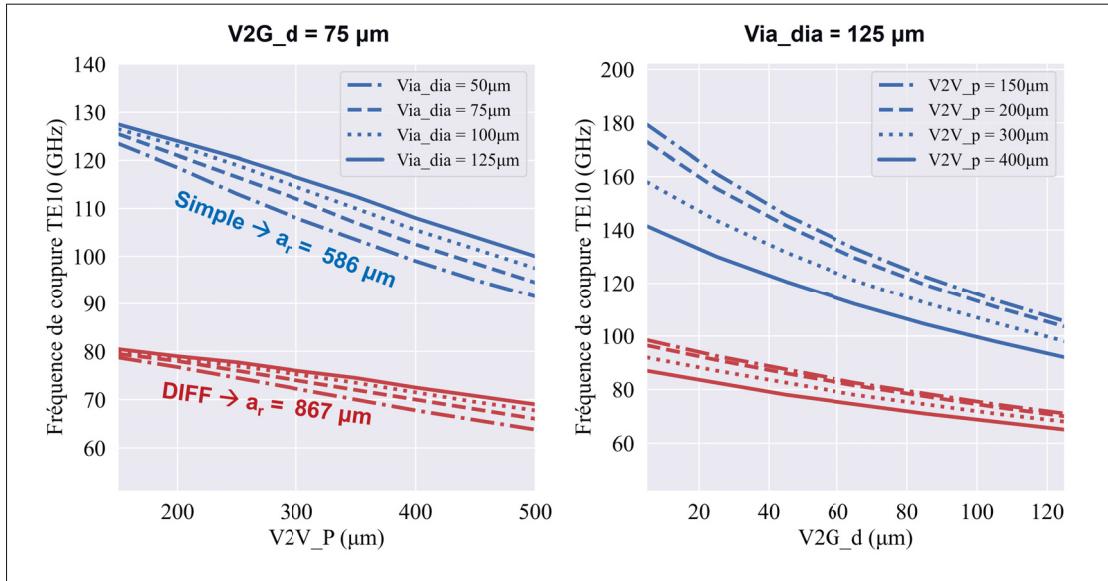

| Figure 2.19 | Fréquence de coupure du mode TE10 dans le substrat en fonction des paramètres des clôtures de trous de liaison (via) simulé sur MATLAB .....                                                    | 48 |

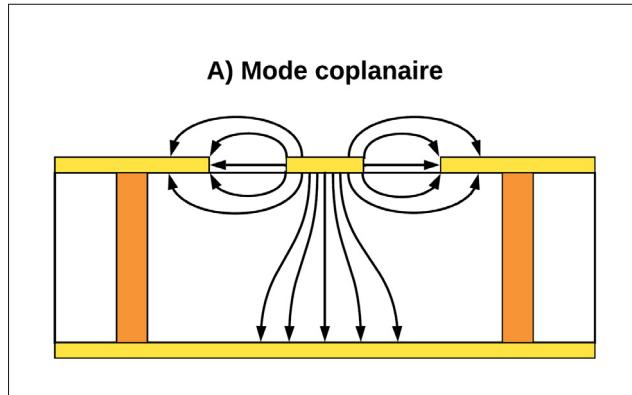

| Figure 2.20 | Mode pouvant propager à toute fréquence sur un CPW .....                                                                                                                                        | 49 |

|             |                                                                                                                                                                                                                        |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.21 | Mode pouvant propager à toute fréquence sur un ECCPW .....                                                                                                                                                             | 50 |

| Figure 2.22 | Schéma d'empilement des couches des puces .....                                                                                                                                                                        | 51 |

| Figure 2.23 | Schéma des modèles initiaux des lignes ECCPW et CPW vues de haut des puces .....                                                                                                                                       | 52 |

| Figure 2.24 | Schéma du modèle utiliser dans la simulation de l'effet de proximité .....                                                                                                                                             | 53 |

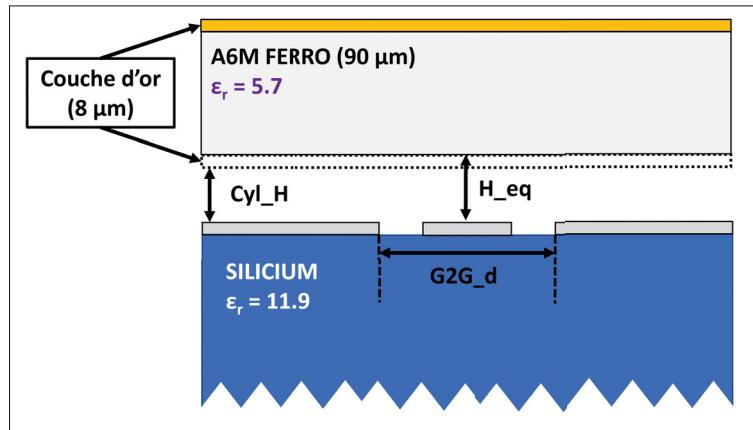

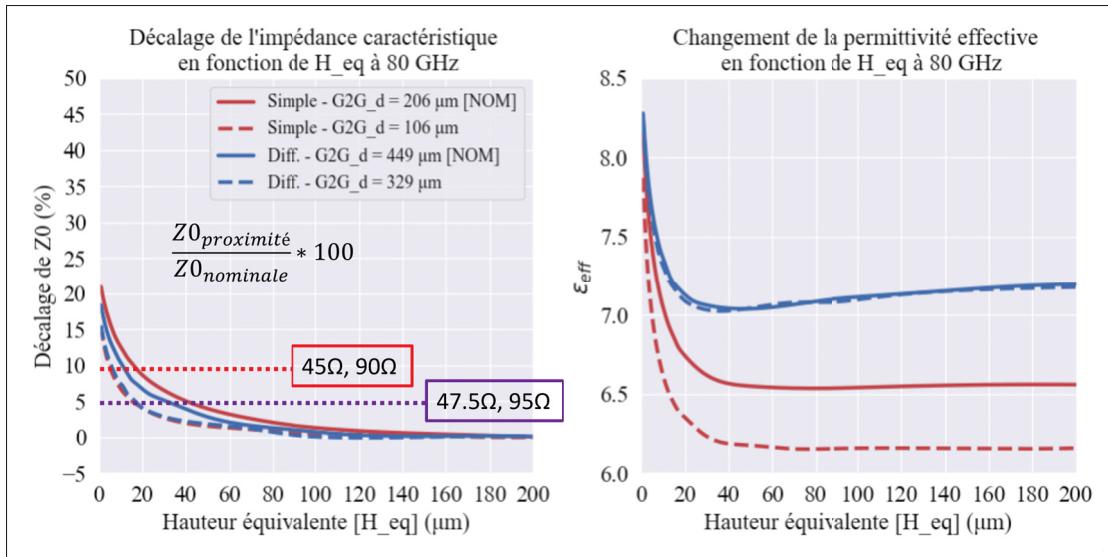

| Figure 2.25 | Simulation du décalage de l'impédance caractéristique et de la permittivité effective en fonction de la distance séparant le substrat de la puce .....                                                                 | 54 |

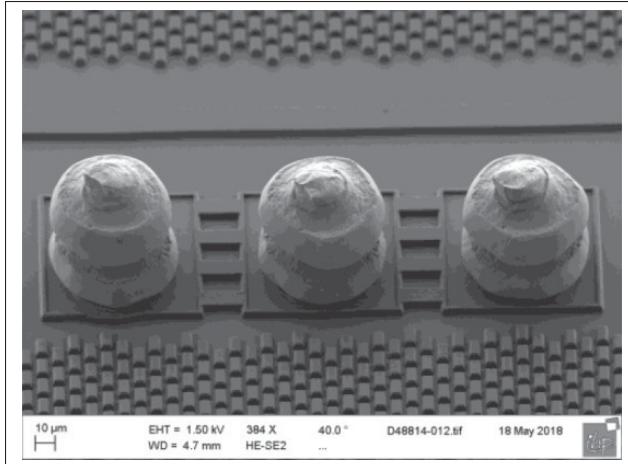

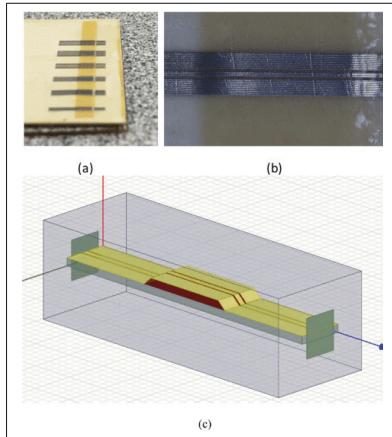

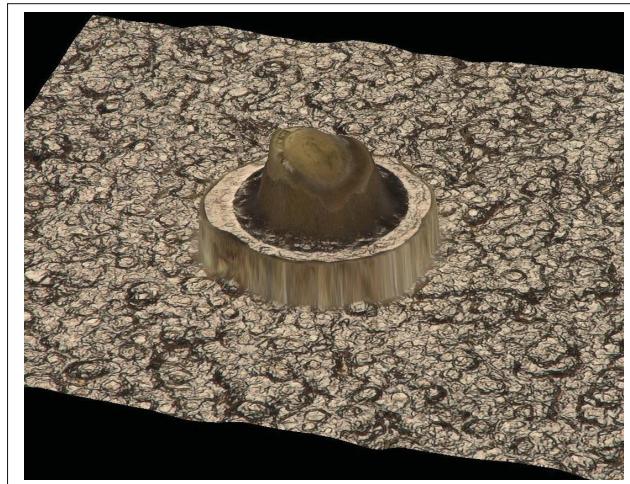

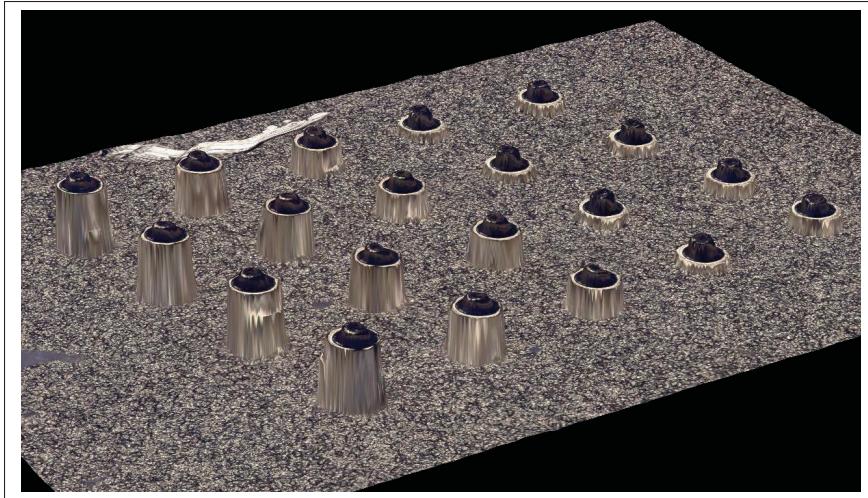

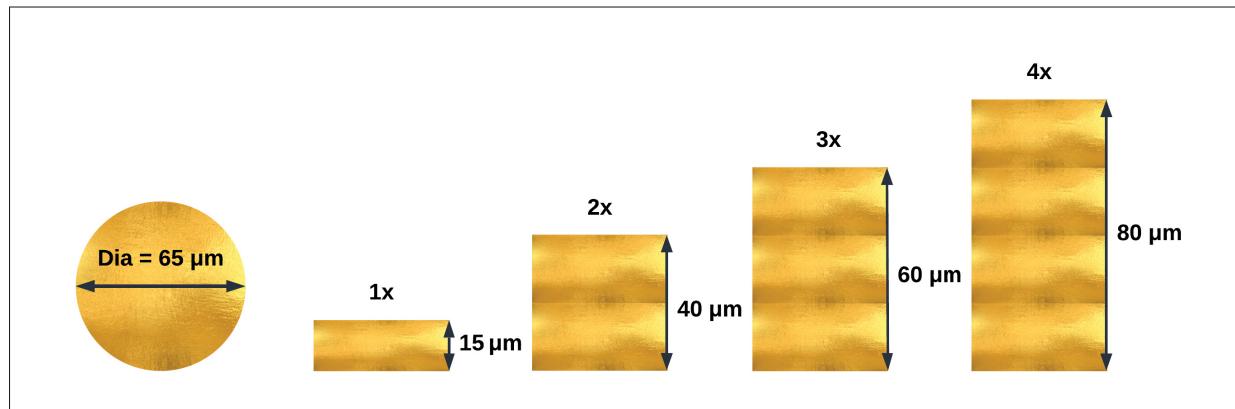

| Figure 2.26 | Photo d'un pilier d'or .....                                                                                                                                                                                           | 55 |

| Figure 2.27 | Photo de différentes configurations de piliers empilés .....                                                                                                                                                           | 56 |

| Figure 2.28 | Schéma des dimensions des piliers d'or .....                                                                                                                                                                           | 56 |

| Figure 2.29 | Performances individuelles des lignes du substrat .....                                                                                                                                                                | 57 |

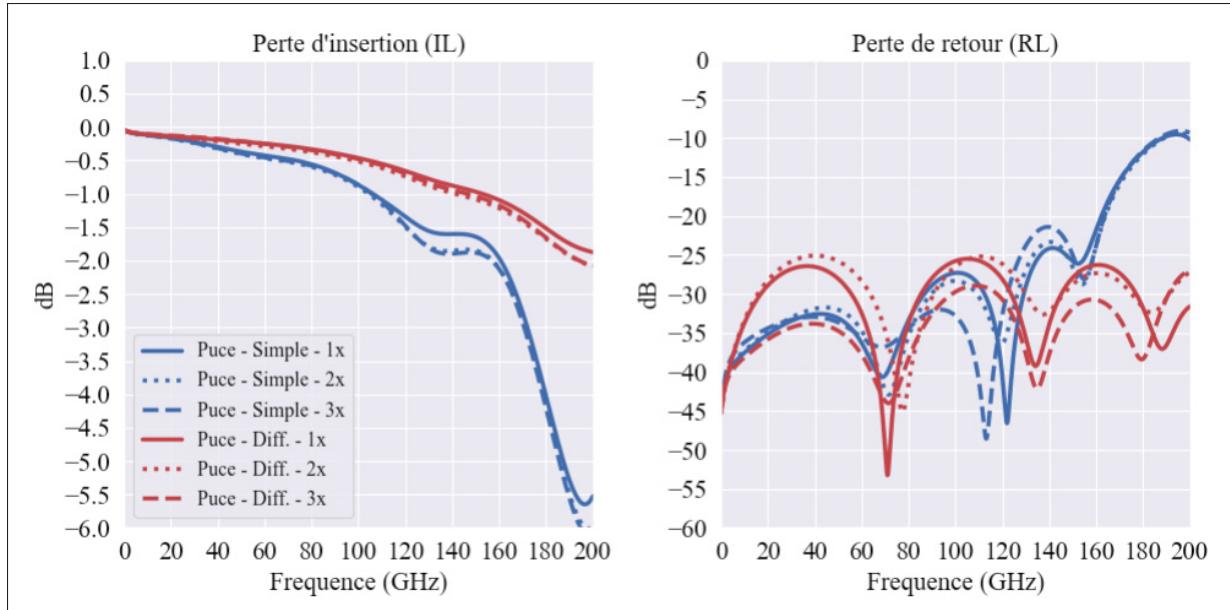

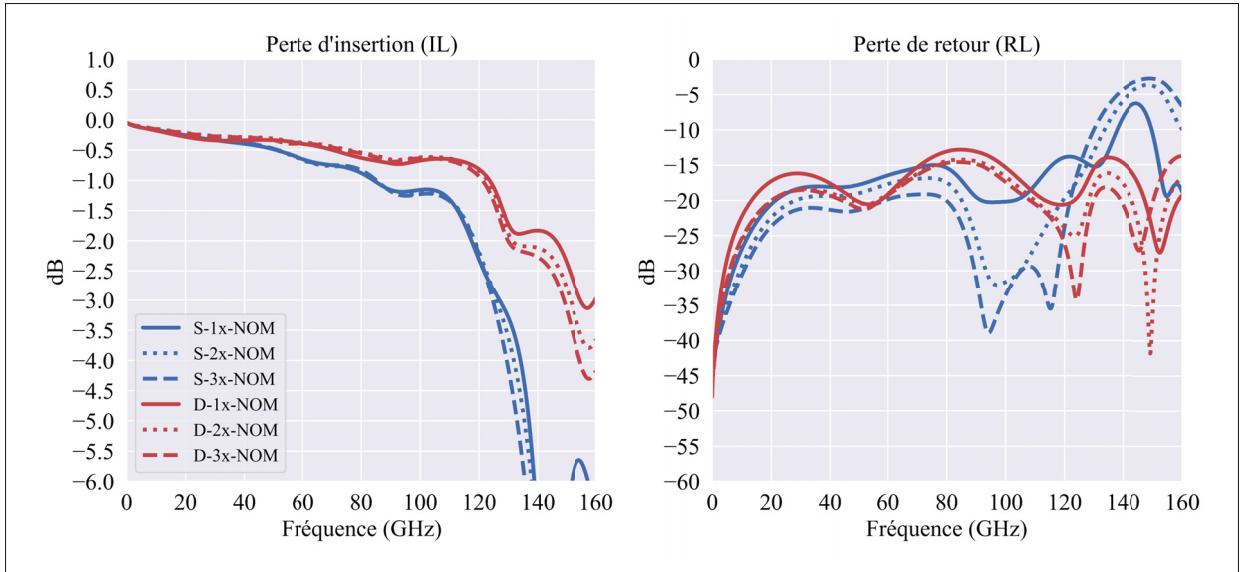

| Figure 2.30 | Performances individuelles des lignes des puces (Nomenclature : 1x = 1 cylindre, 2x = 2 cylindres, 3x = 3 cylindres) .....                                                                                             | 58 |

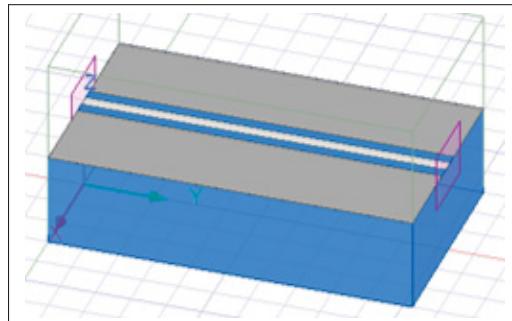

| Figure 3.1  | Schéma du modèle initial de puce retournée avec ligne simple .....                                                                                                                                                     | 60 |

| Figure 3.2  | Schéma du modèle initial de puce retournée avec paire différentielle .....                                                                                                                                             | 61 |

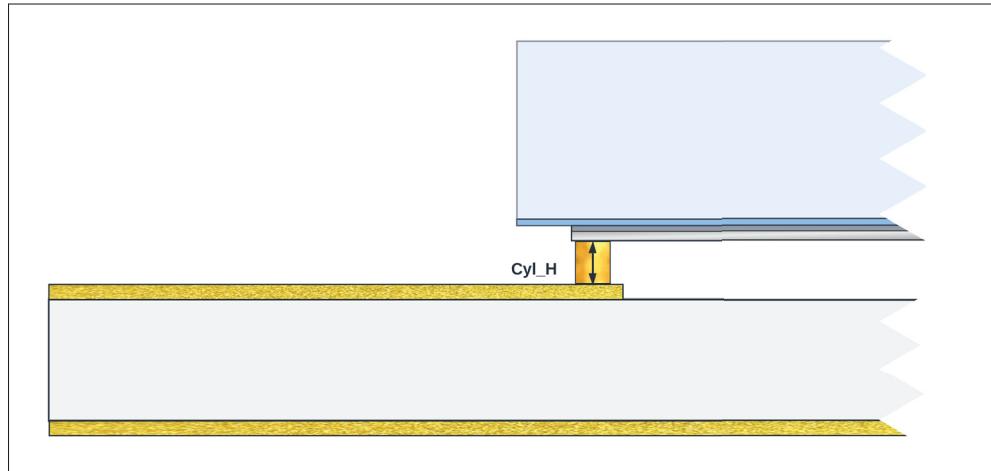

| Figure 3.3  | Schéma du modèle initial de la puce retournée vue de côté .....                                                                                                                                                        | 61 |

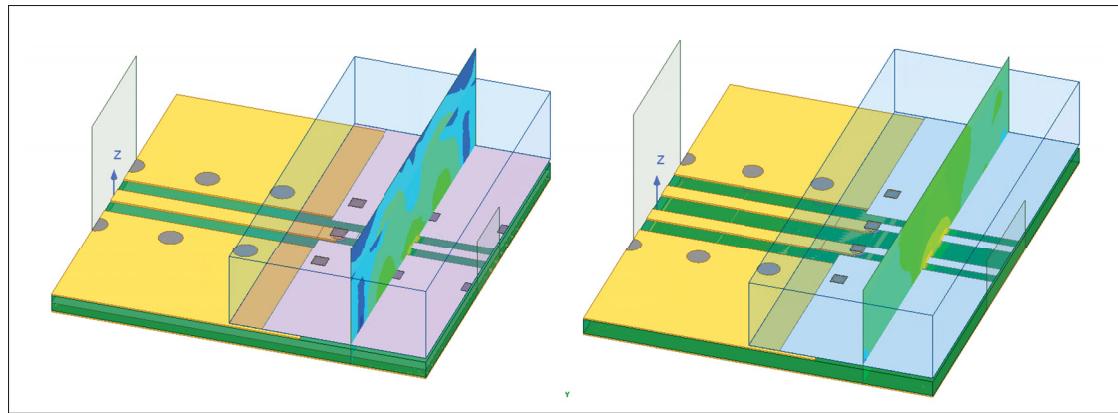

| Figure 3.4  | Modèles de simulation des puces retournées initiaux pour la ligne simple (Gauche) et la paire différentielle (Droite) .....                                                                                            | 63 |

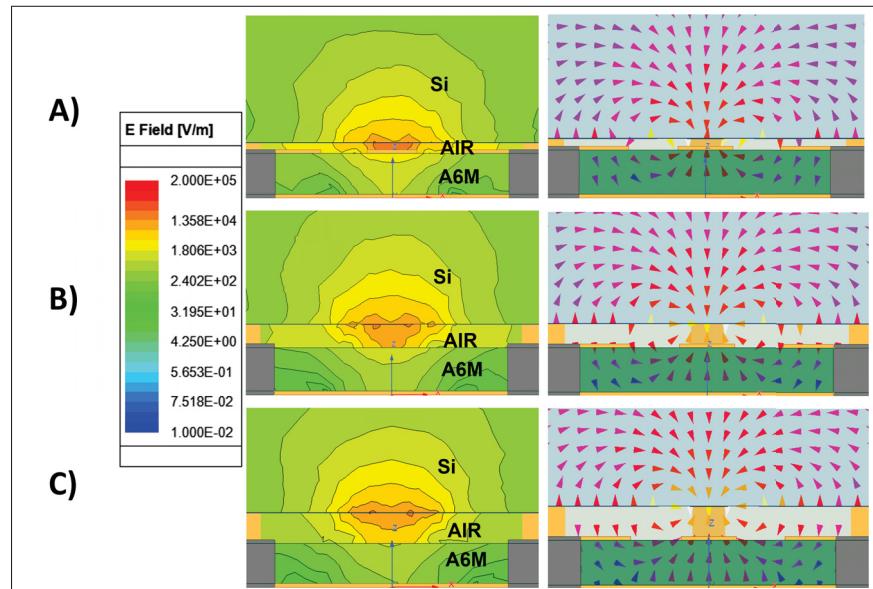

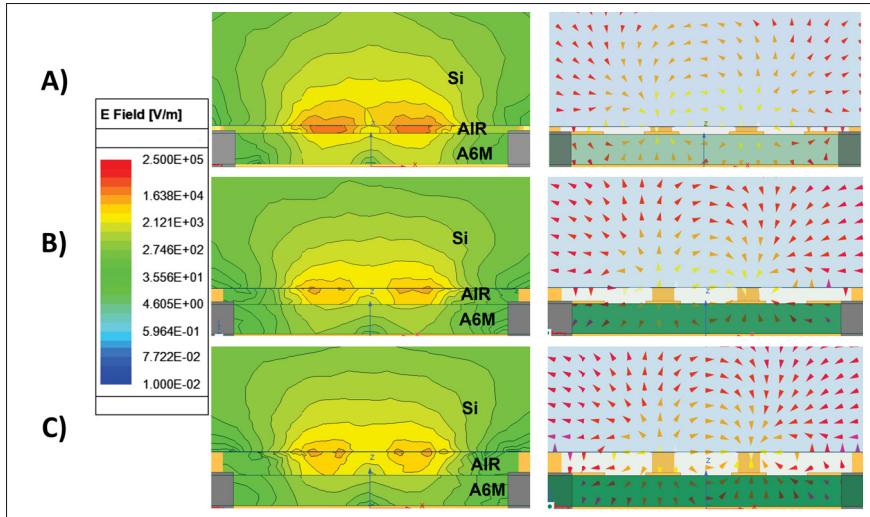

| Figure 3.5  | Champs électriques du mode coplanaire de la ligne simple sur la puce pour les structures de puces retournées initiales à 80 GHz en fonction du nombre de piliers. A) 1 pilier , B) 2 piliers et C) 3 piliers .....     | 63 |

| Figure 3.6  | Champs électriques du mode impair de la ligne différentielle sur la puce pour les structures de puces retournées initiales à 80 GHz en fonction du nombre de piliers. A) 1 pilier , B) 2 piliers et C) 3 piliers ..... | 64 |

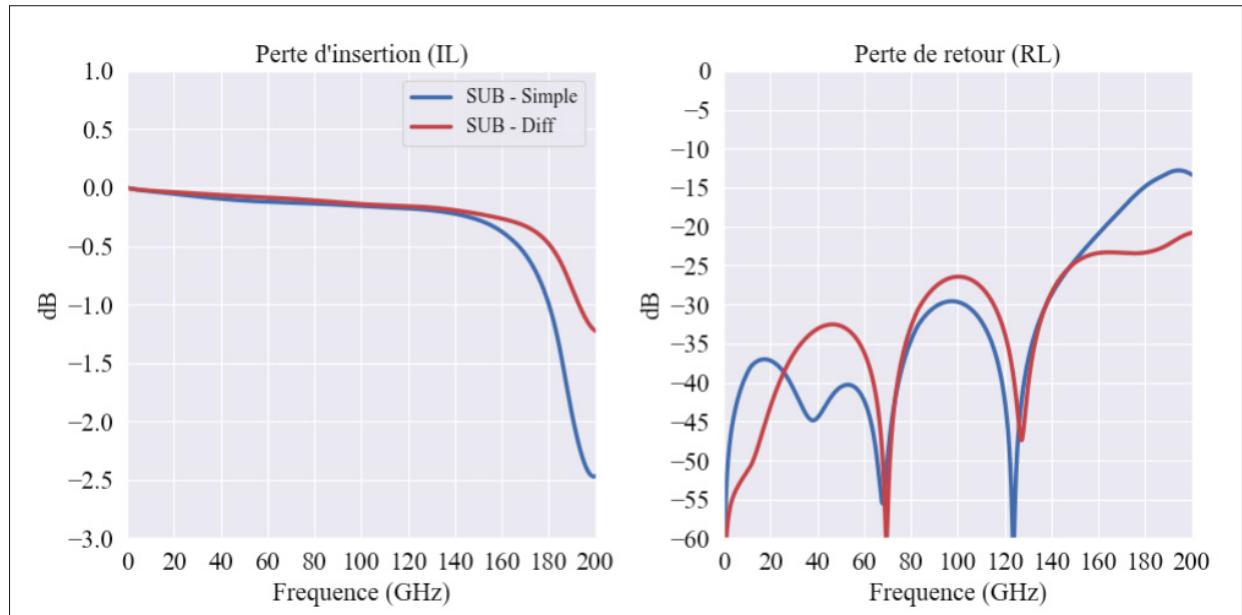

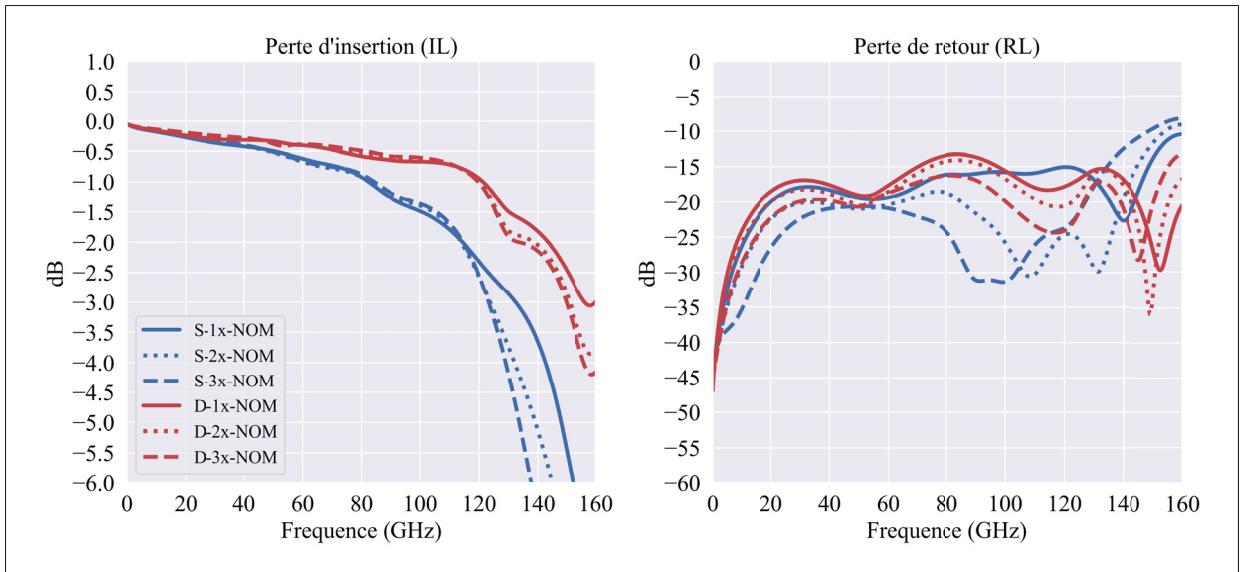

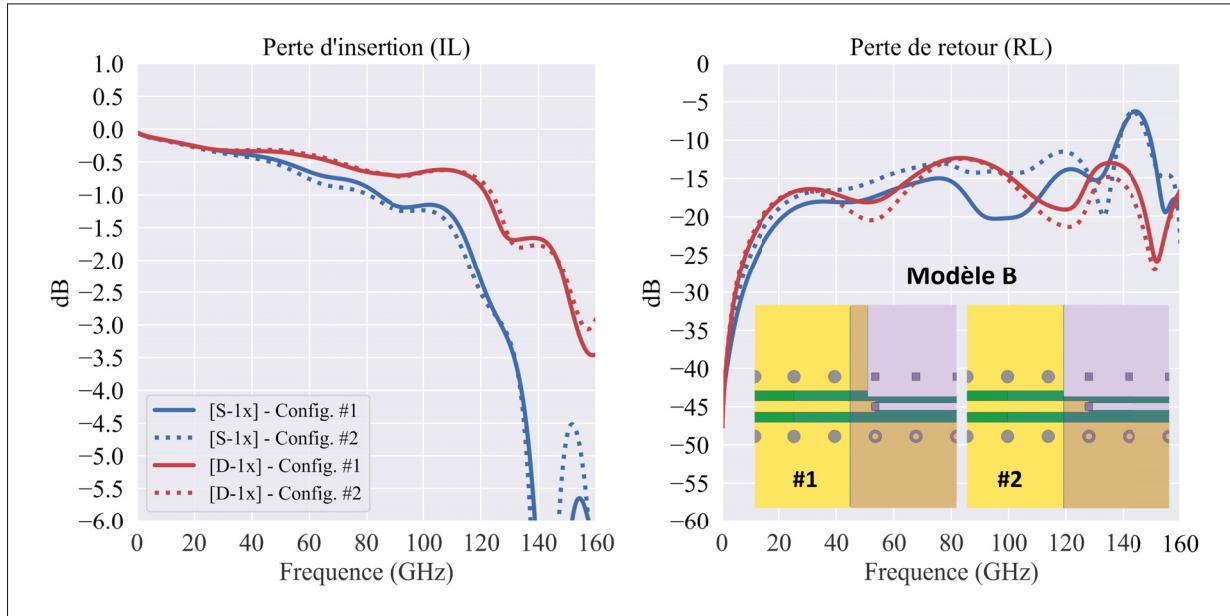

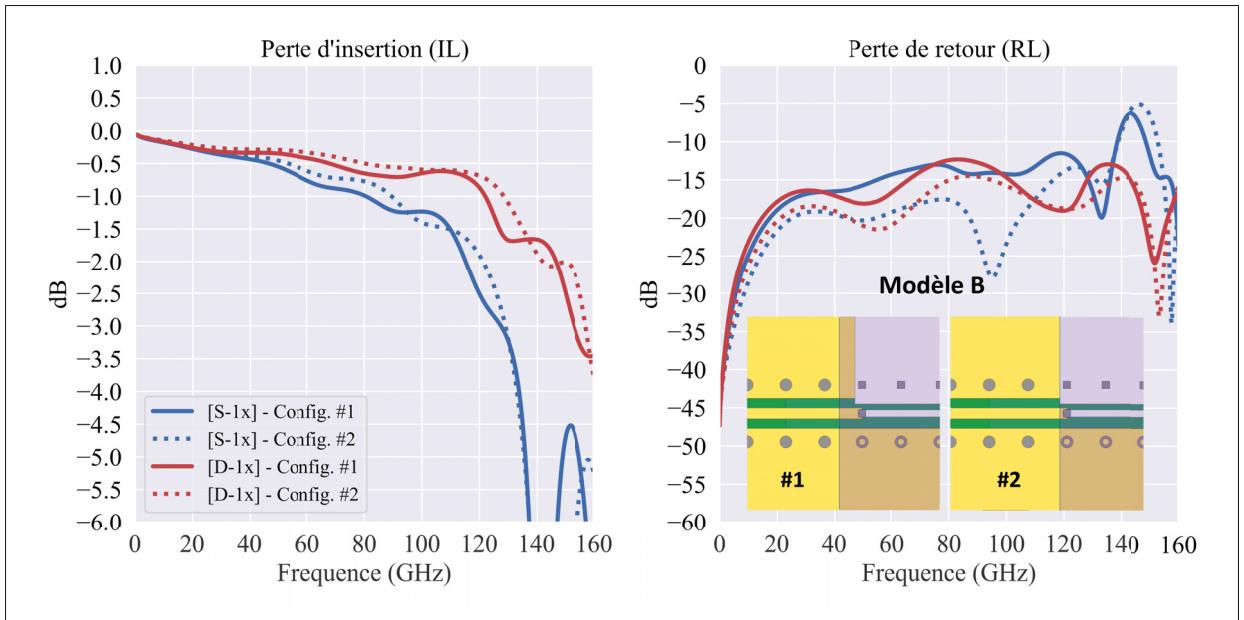

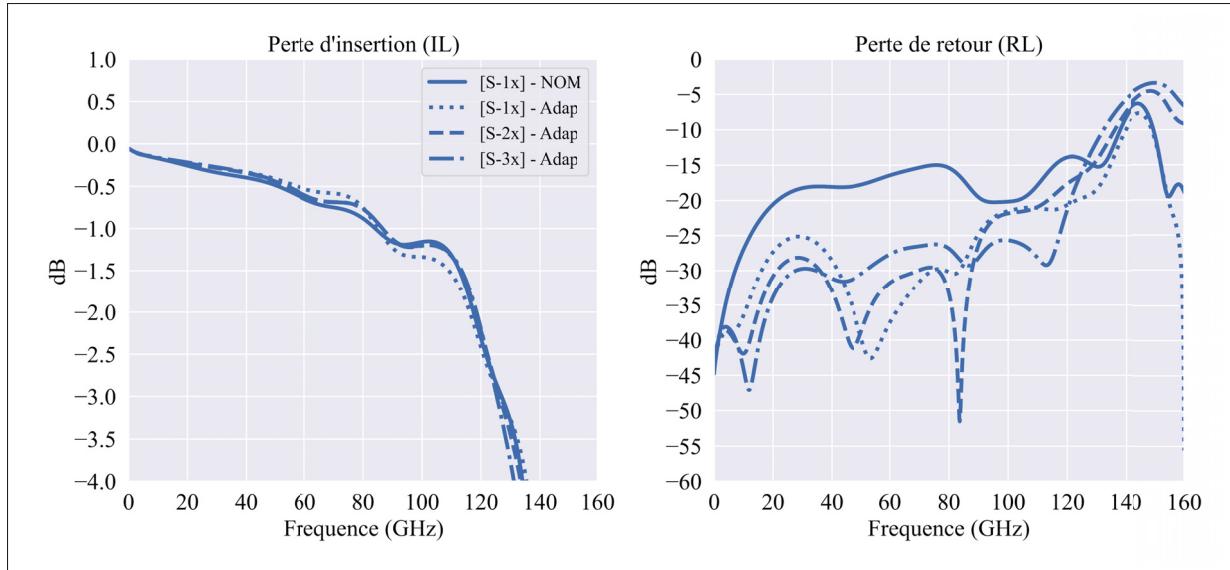

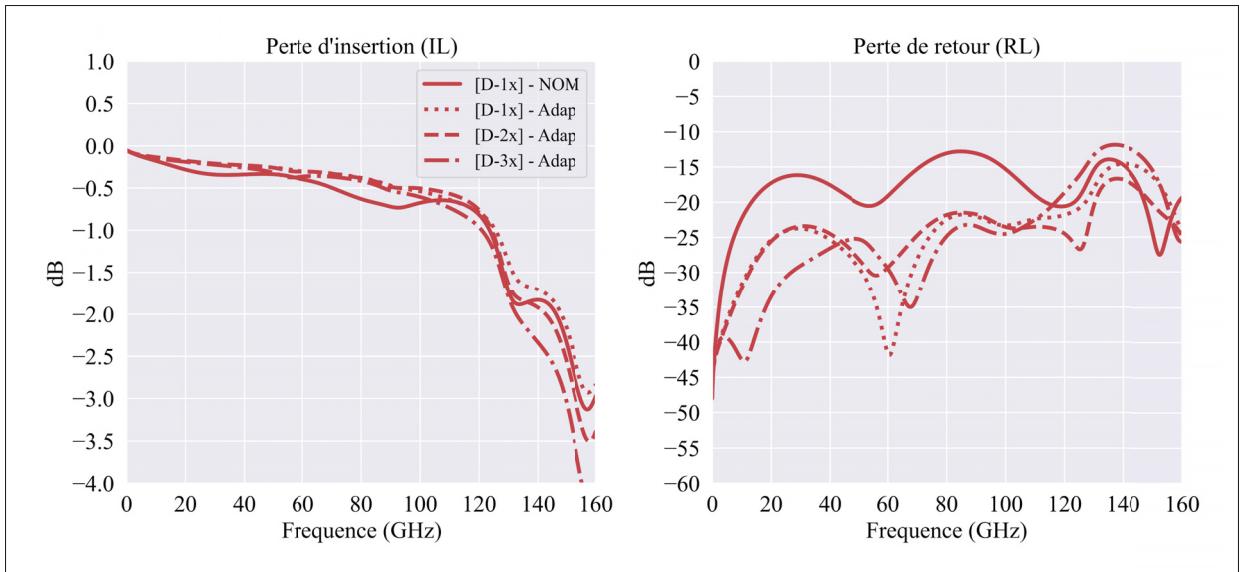

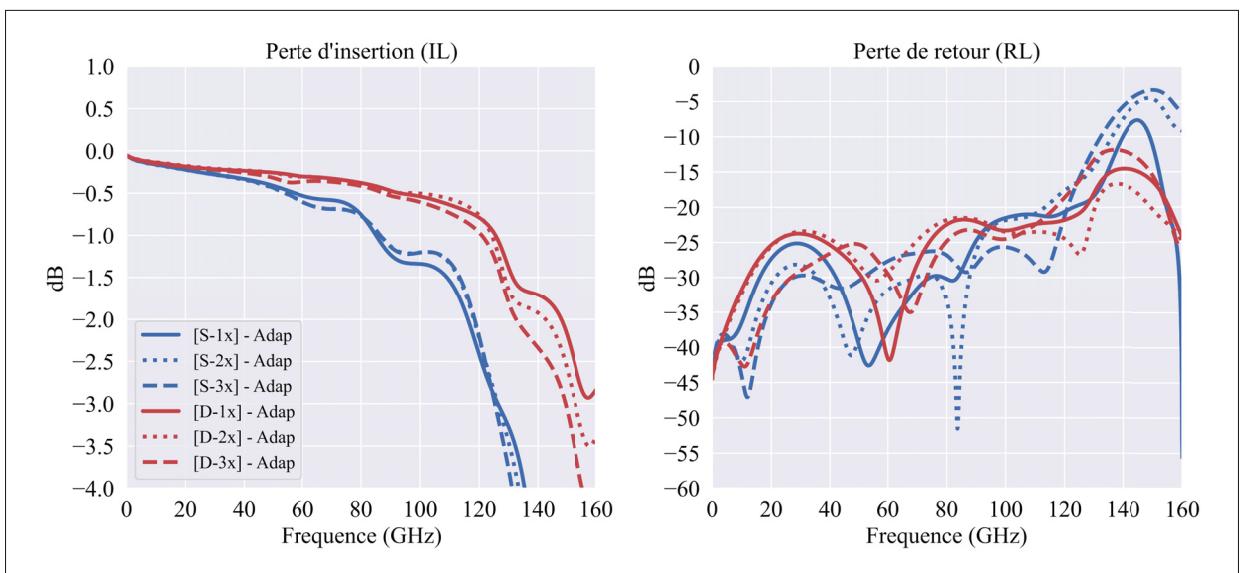

| Figure 3.7  | Simulation des pertes de retour et des pertes d'insertion des variantes initiales pour la ligne simple (Bleu) et différentielle (rouge) .....                                                                          | 65 |

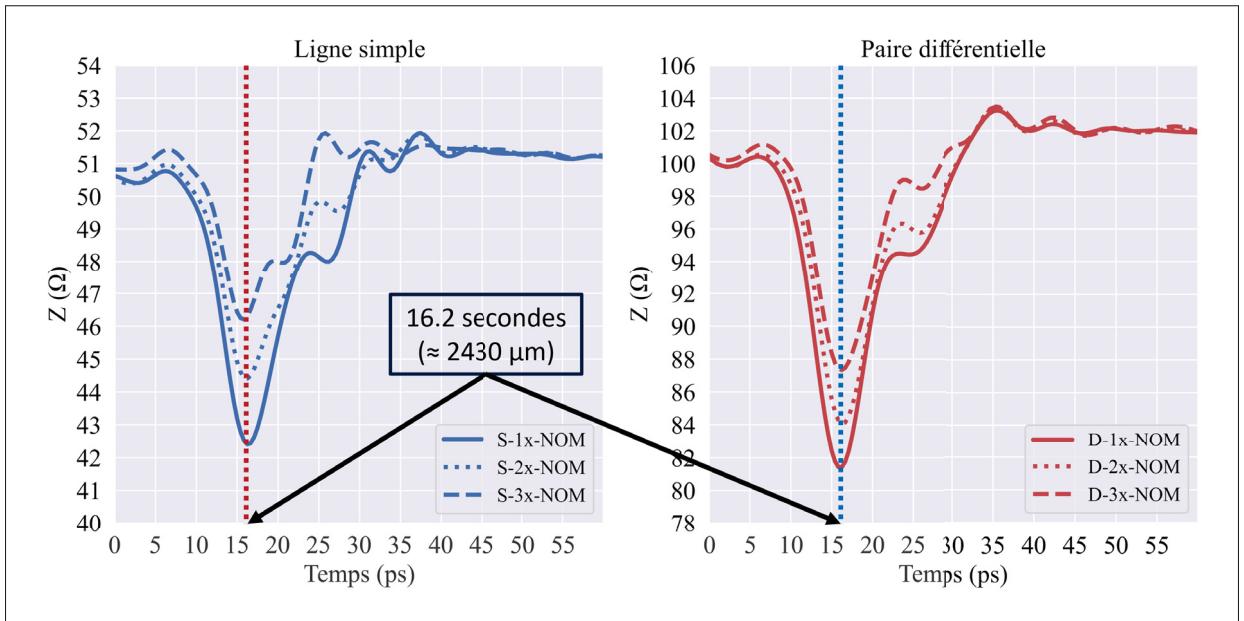

| Figure 3.8  | TDRZ( $S_{11}$ ) des lignes simples et différentielles nominales en fonction de la hauteur des piliers .....                                                                                                           | 67 |

|             |                                                                                                                                                                                                                         |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

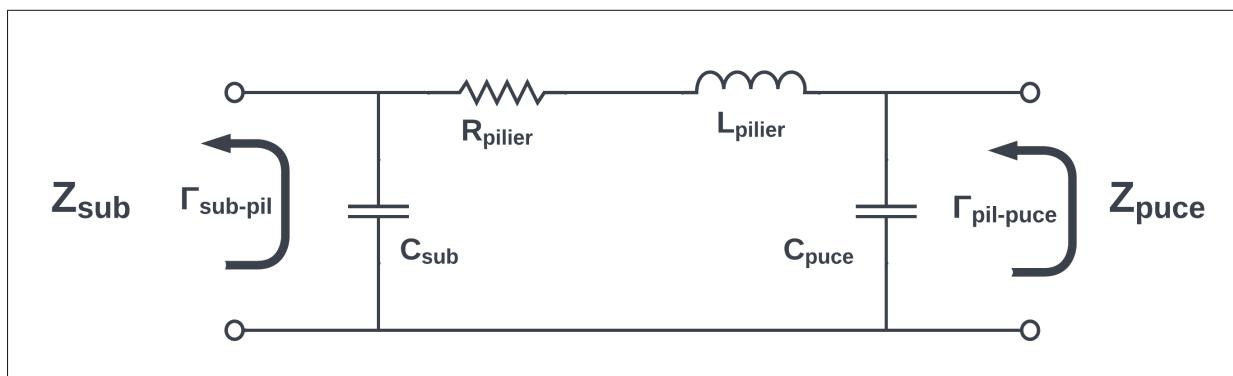

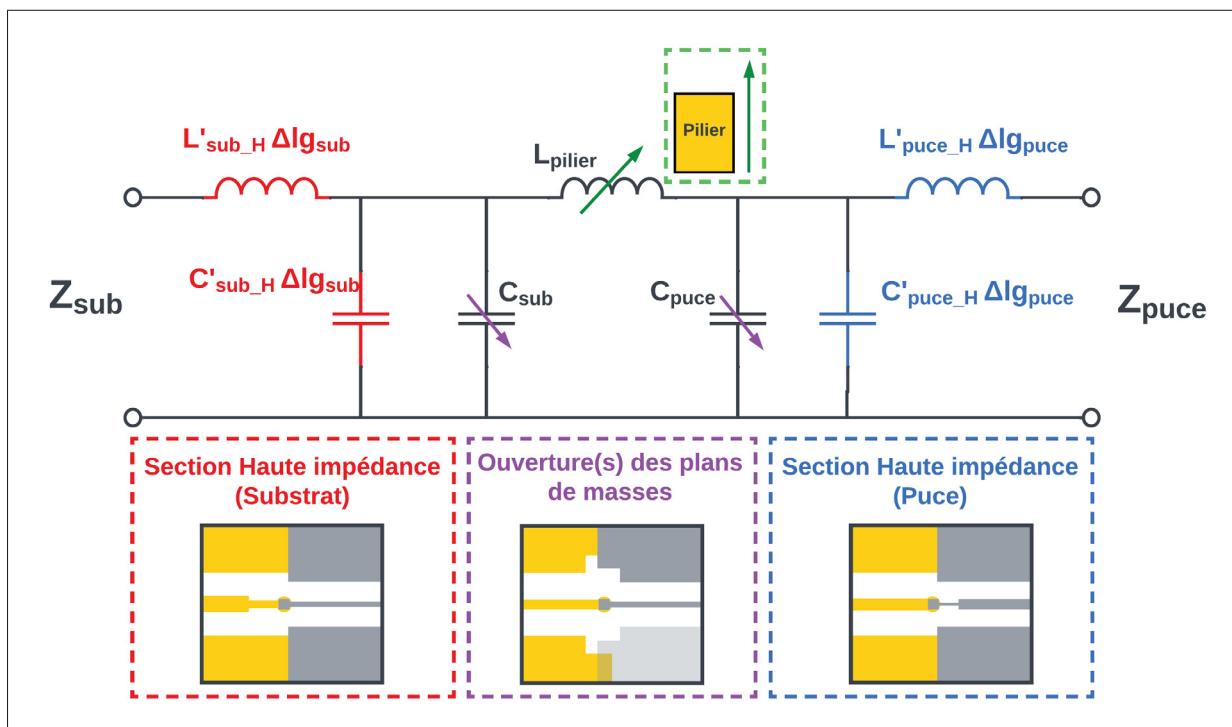

| Figure 3.9  | Schéma du circuit équivalent de la transition sur puce retournée initiale .....                                                                                                                                         | 68 |

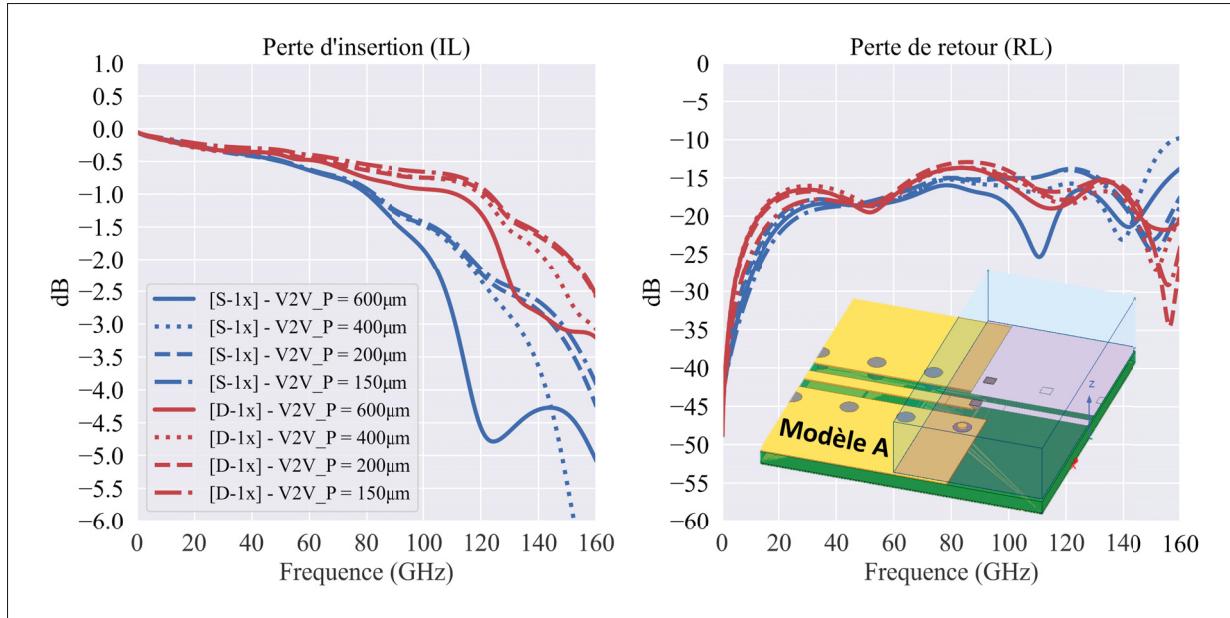

| Figure 3.10 | Simulation de la variation de la distance centre à centre des trous de liaison (via) pour les structures de puces retournées [Modèle A] .....                                                                           | 70 |

| Figure 3.11 | Variation de la distance centre à centre des trous de liaison (V2V_p) ET de la distance entre l'extrémité des clôtures et l'extrémité du plan de masse (V2G_d) pour les structures de puces retournées [Modèle A] ..... | 71 |

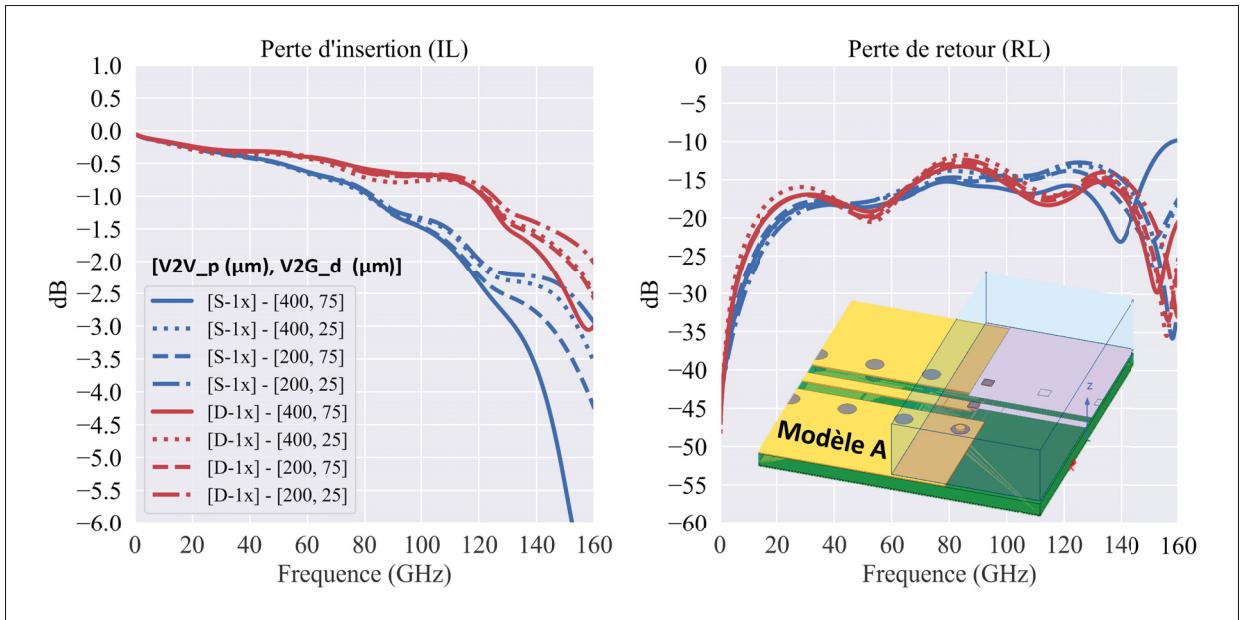

| Figure 3.12 | Cas spéciaux ne respectant pas les règles de conceptions LTCC (Rétrécissement des dimensions) [Modèle A] .....                                                                                                          | 72 |

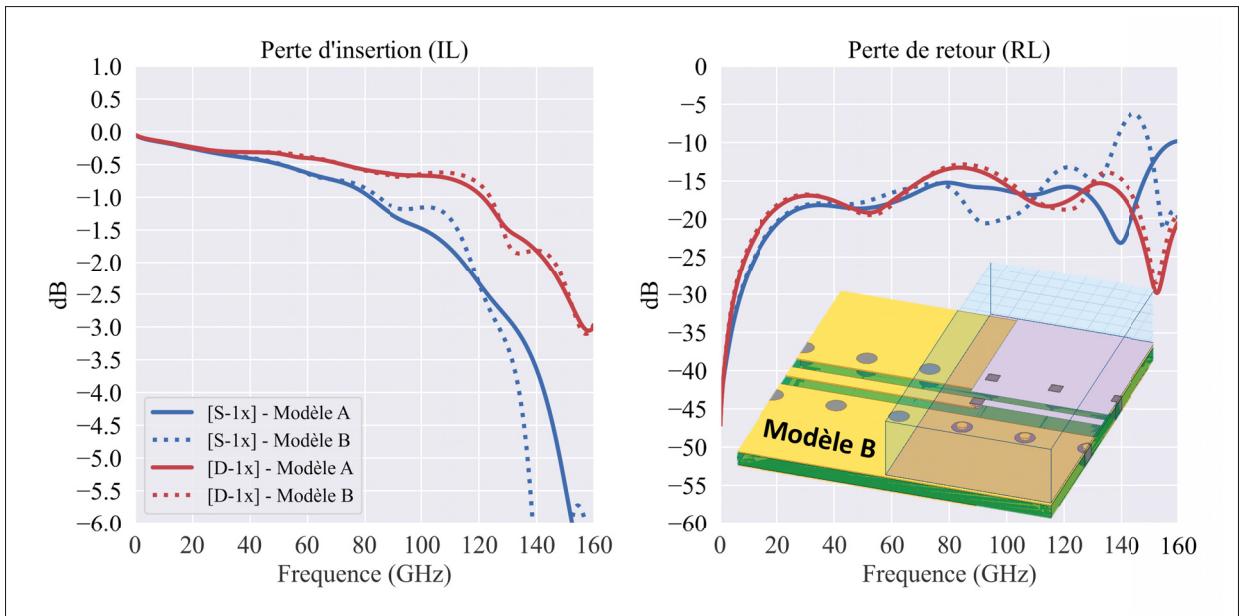

| Figure 3.13 | Effet du prolongement des plans de masse périphériques du substrat en dessous de la puce [Modèle A vs Modèle B] .....                                                                                                   | 73 |

| Figure 3.14 | Effet du prolongement des plans de masse périphériques sur la puce [Modèle B] .....                                                                                                                                     | 74 |

| Figure 3.15 | Effet du retrait de la longueur supplémentaire au niveau du silicium de la puce [Modèle B] .....                                                                                                                        | 75 |

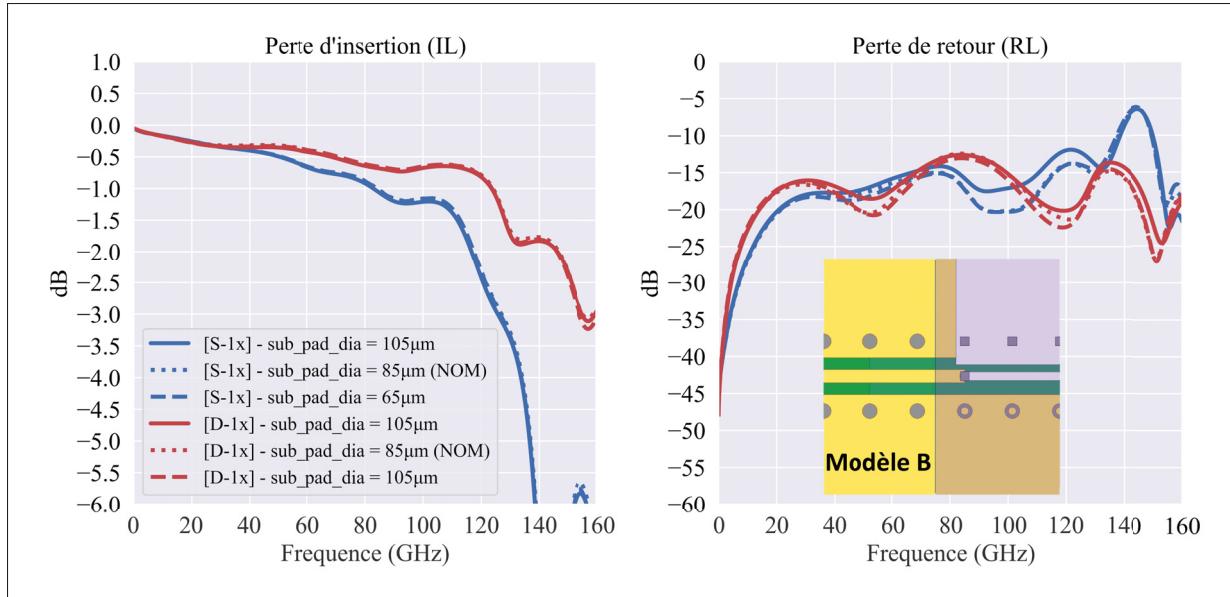

| Figure 3.16 | Effet de la taille des pastilles de réceptions au niveau du substrat [Modèle B] .....                                                                                                                                   | 76 |

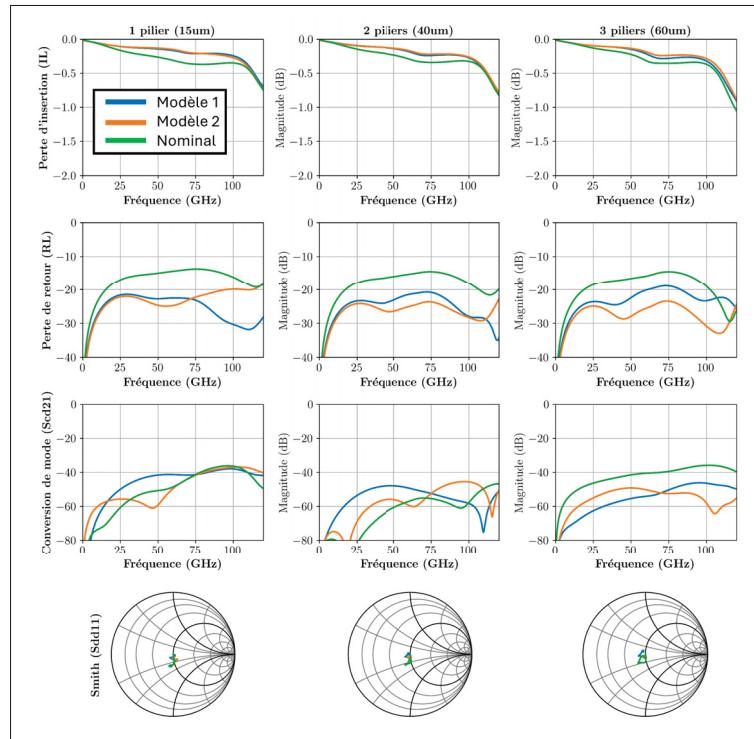

| Figure 3.17 | Simulations des structures pour chacune des configurations de hauteur de piliers pour le Modèle B .....                                                                                                                 | 77 |

| Figure 3.18 | Circuit équivalent d'une transition sur puce retournée incluant les structures de compensations conventionnelles de la capacitance .....                                                                                | 78 |

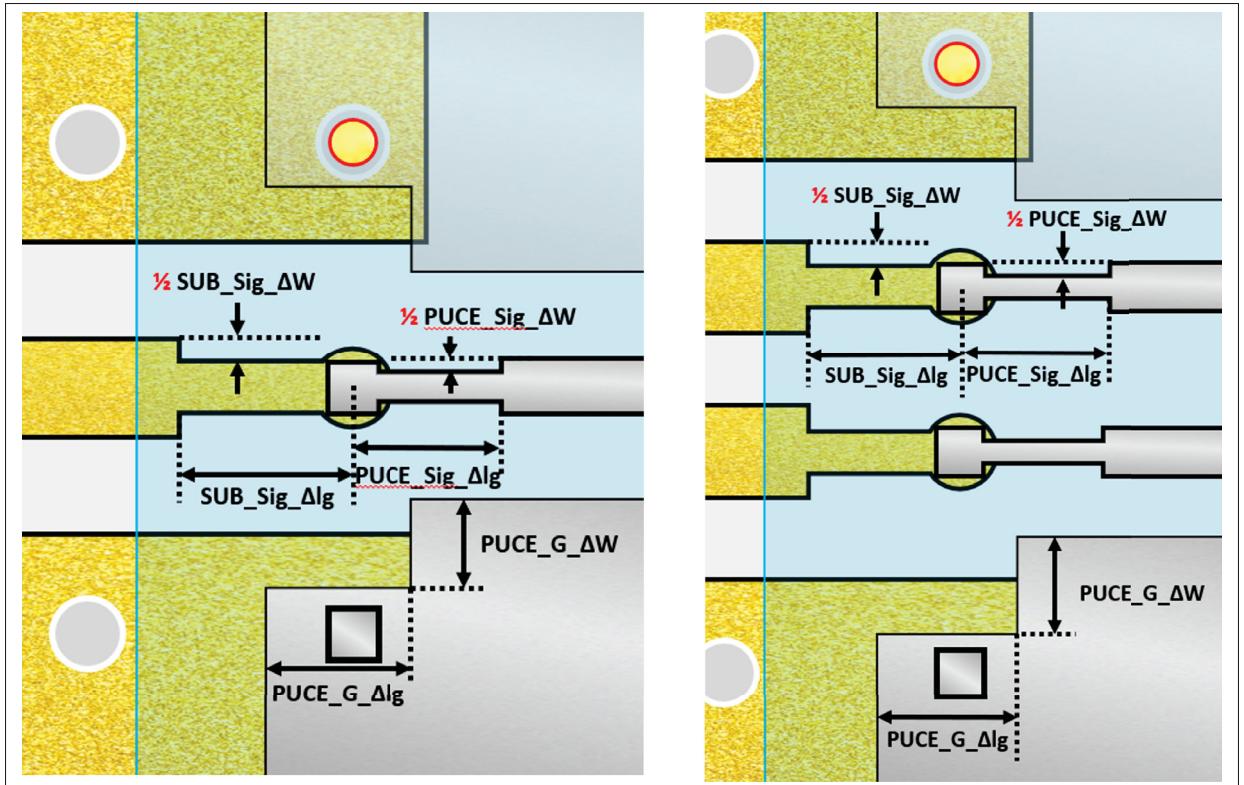

| Figure 3.19 | Schéma incluant les possibles configurations permettant de compenser l'aspect capacitif excédentaire de la transition. ....                                                                                             | 81 |

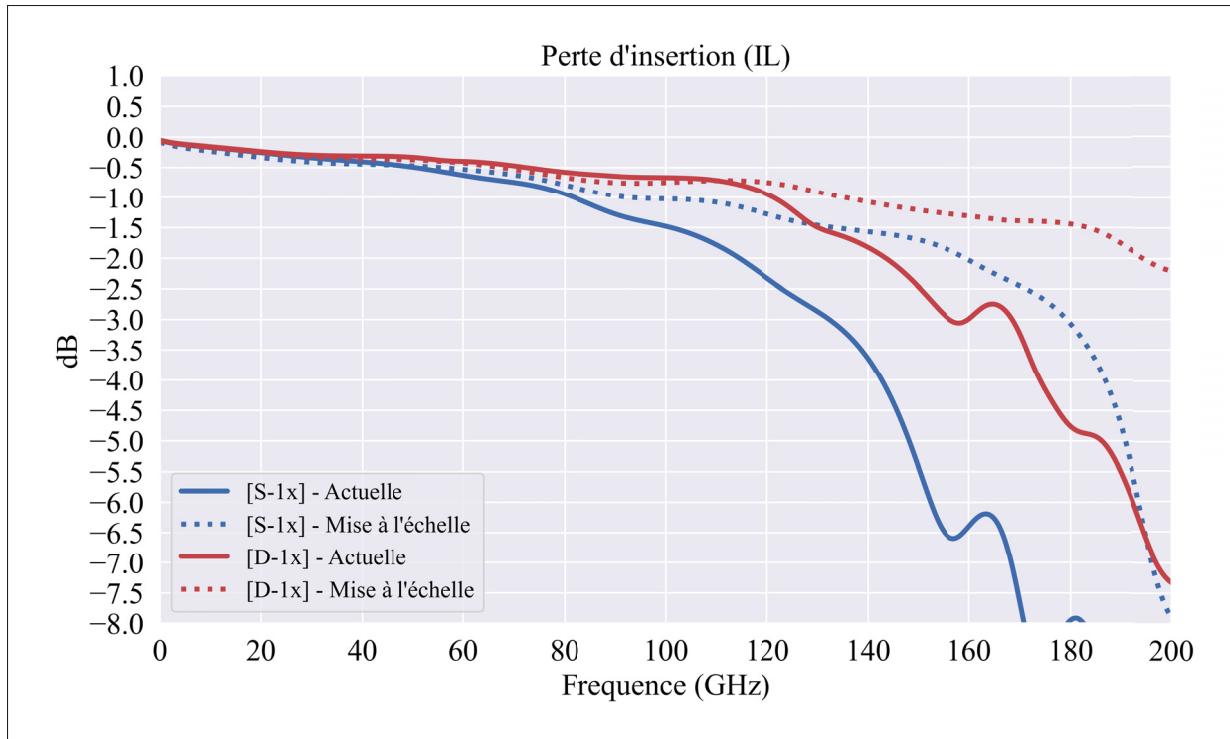

| Figure 3.20 | Comparaison des modèles adaptés avec le modèle initial à 1x pilier pour la ligne simple .....                                                                                                                           | 82 |

| Figure 3.21 | Comparaison des modèles adaptés avec le modèle initial à 1x pilier pour la paire différentielle .....                                                                                                                   | 83 |

| Figure 3.22 | Comparaison des modèles adaptés de la ligne simple avec ceux de la paire différentielle .....                                                                                                                           | 83 |

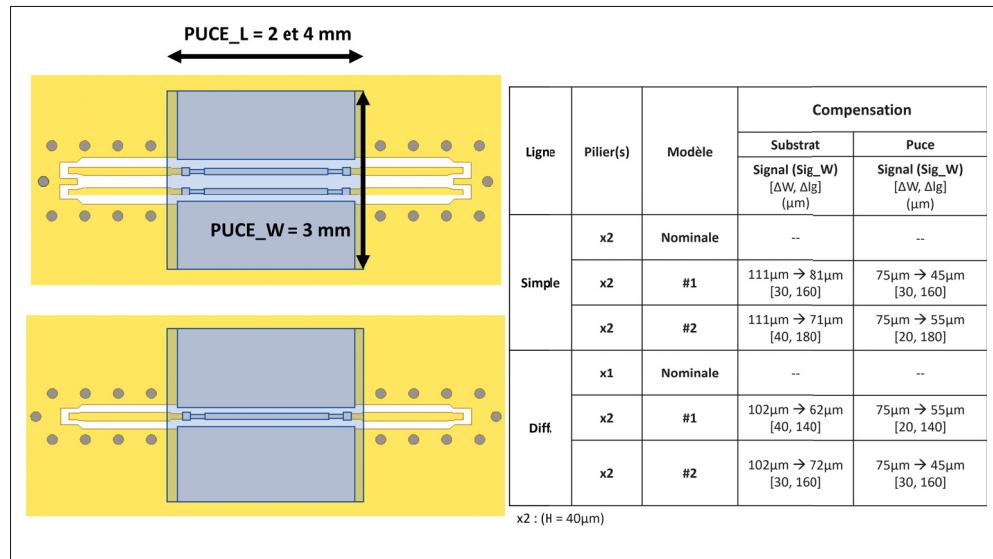

| Figure 4.1  | Modèles de puces retournées choisis pour la validation expérimentale .....                                                                                                                                              | 85 |

|             |                                                                                                                                                                                       |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2  | Installation pour les mesures (Photo #1) .....                                                                                                                                        | 86 |

| Figure 4.3  | Installation pour les mesures (Photo #2) .....                                                                                                                                        | 87 |

| Figure 4.4  | Installation pour les mesures (Photo #3) .....                                                                                                                                        | 87 |

| Figure 4.5  | Schéma d'empilement des couches du substrat pour la fabrication .....                                                                                                                 | 88 |

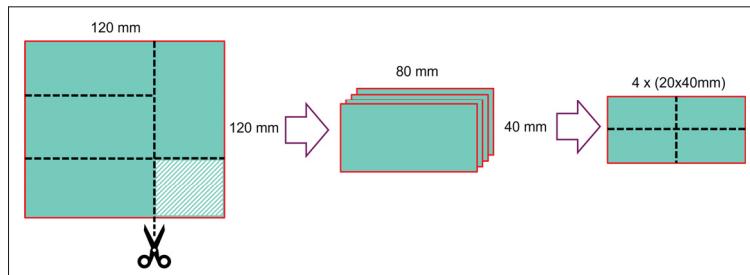

| Figure 4.6  | Modèle de configuration du substrat pour la fabrication .....                                                                                                                         | 88 |

| Figure 4.7  | Topologie globale pour la fabrication du substrat (sans les trous de liaison) .....                                                                                                   | 89 |

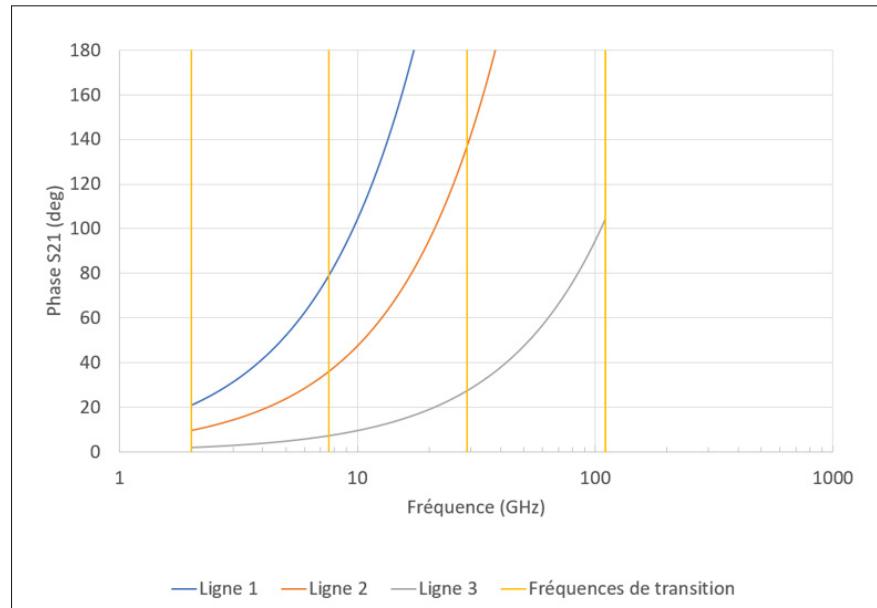

| Figure 4.8  | Phase des trois longueurs de lignes proposées pour la calibration TRL par le calculateur de Microwave101 .....                                                                        | 91 |

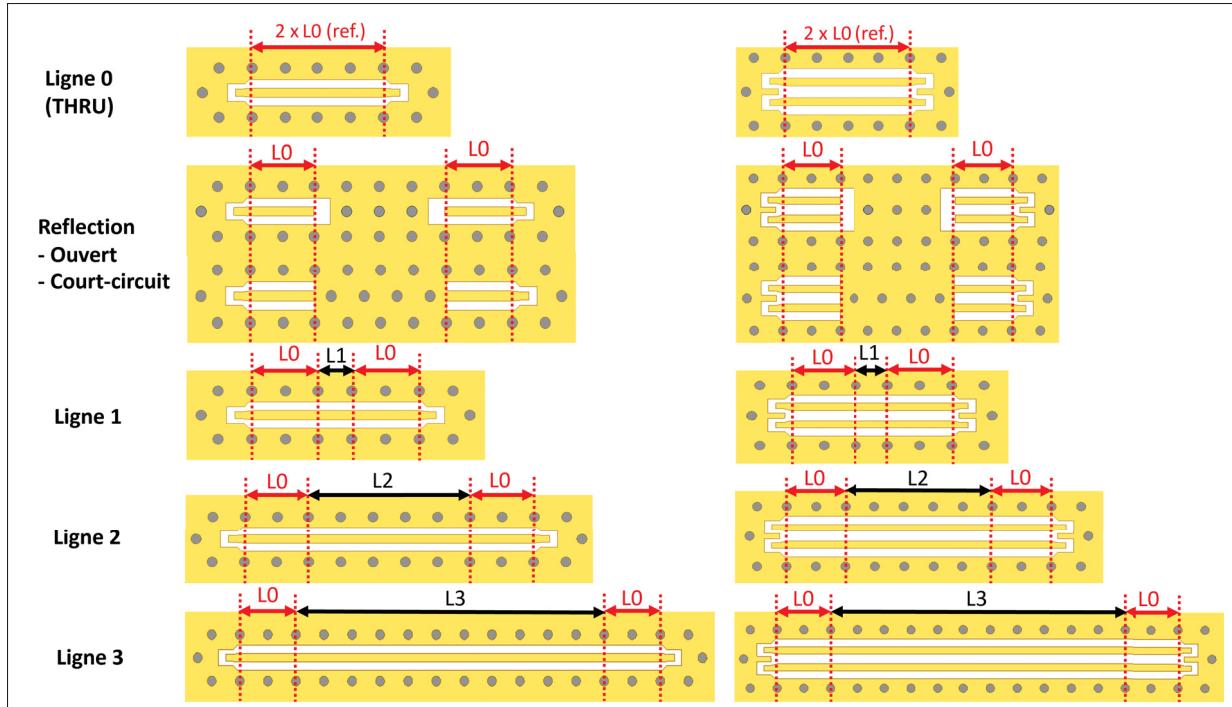

| Figure 4.9  | Schéma des standards de calibration pour le TRL à multiples lignes du substrat pour la ligne simple (gauche) et différentielle (droite) .....                                         | 92 |

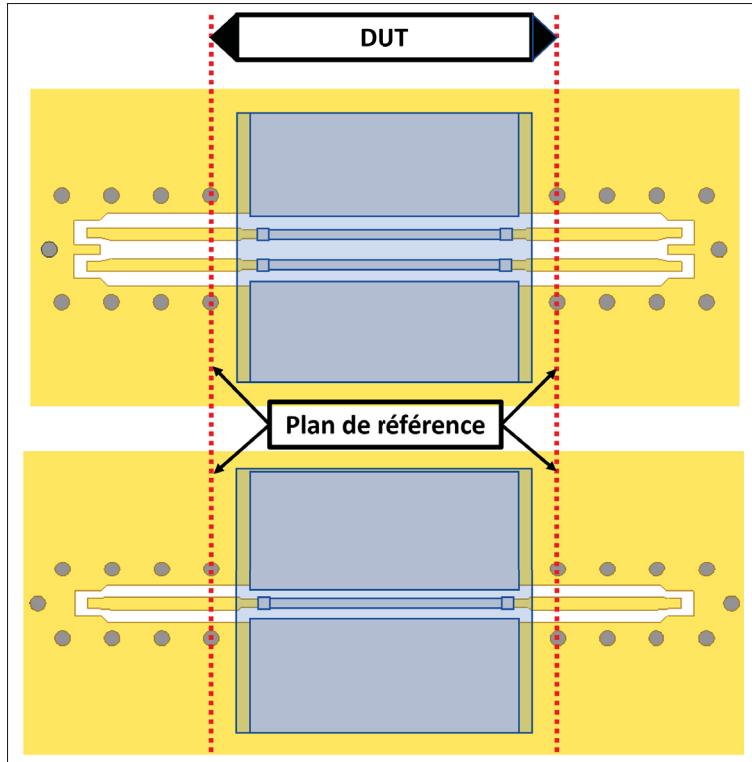

| Figure 4.10 | Schéma du plan de référence sur substrat pour les unités de puces retournées (DUT) de la ligne simple et différentielle .....                                                         | 93 |

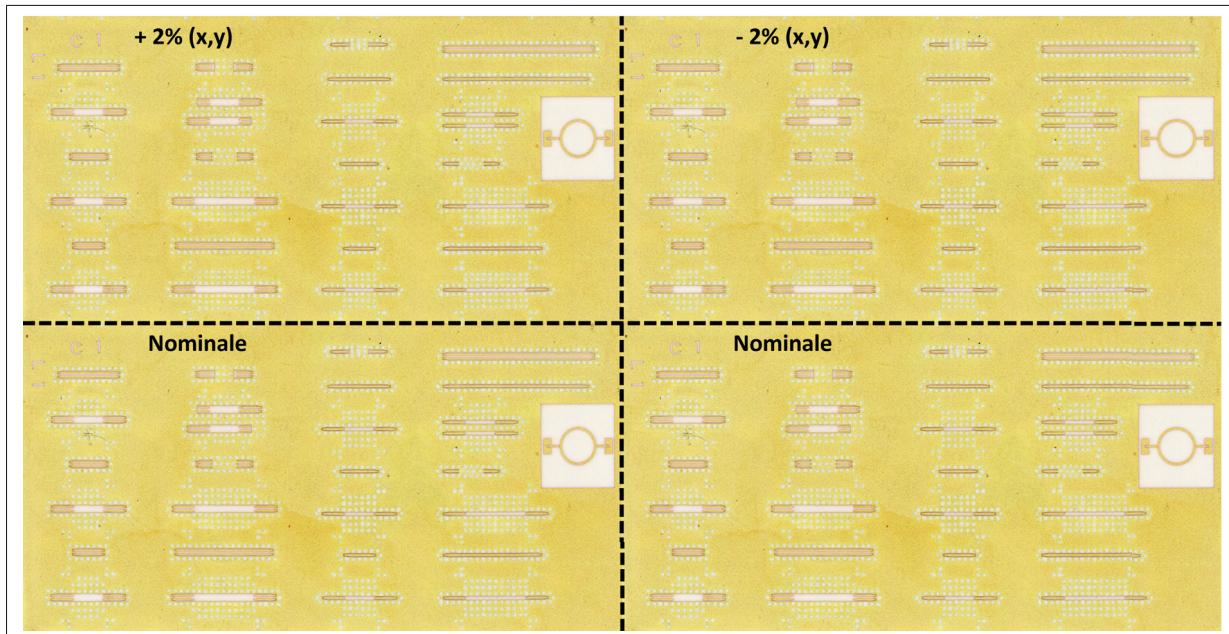

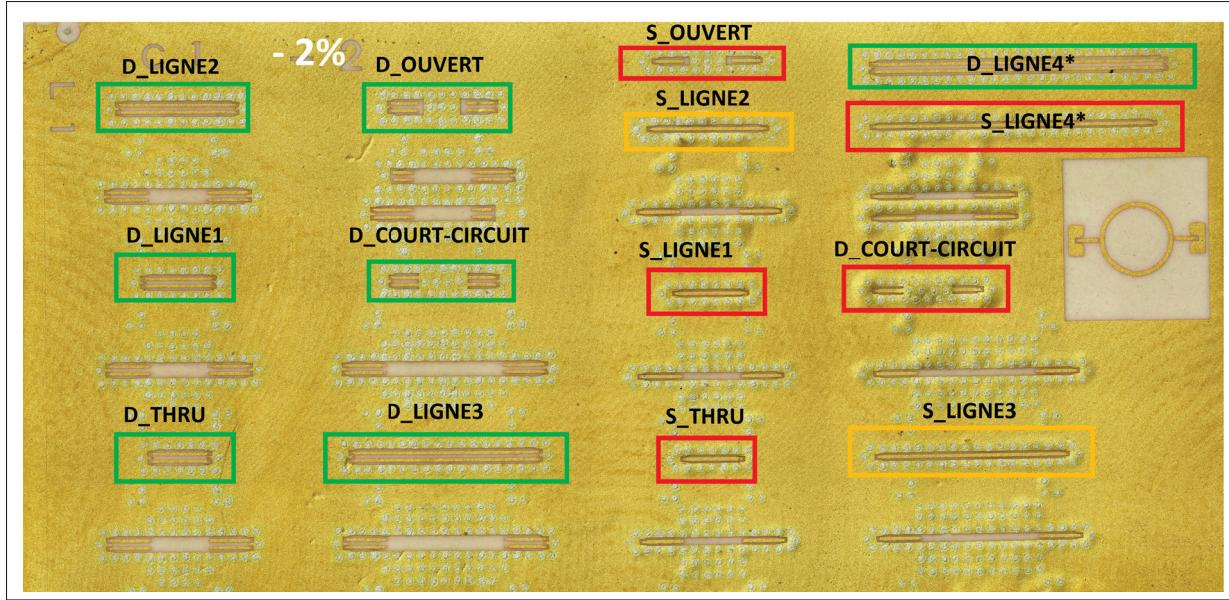

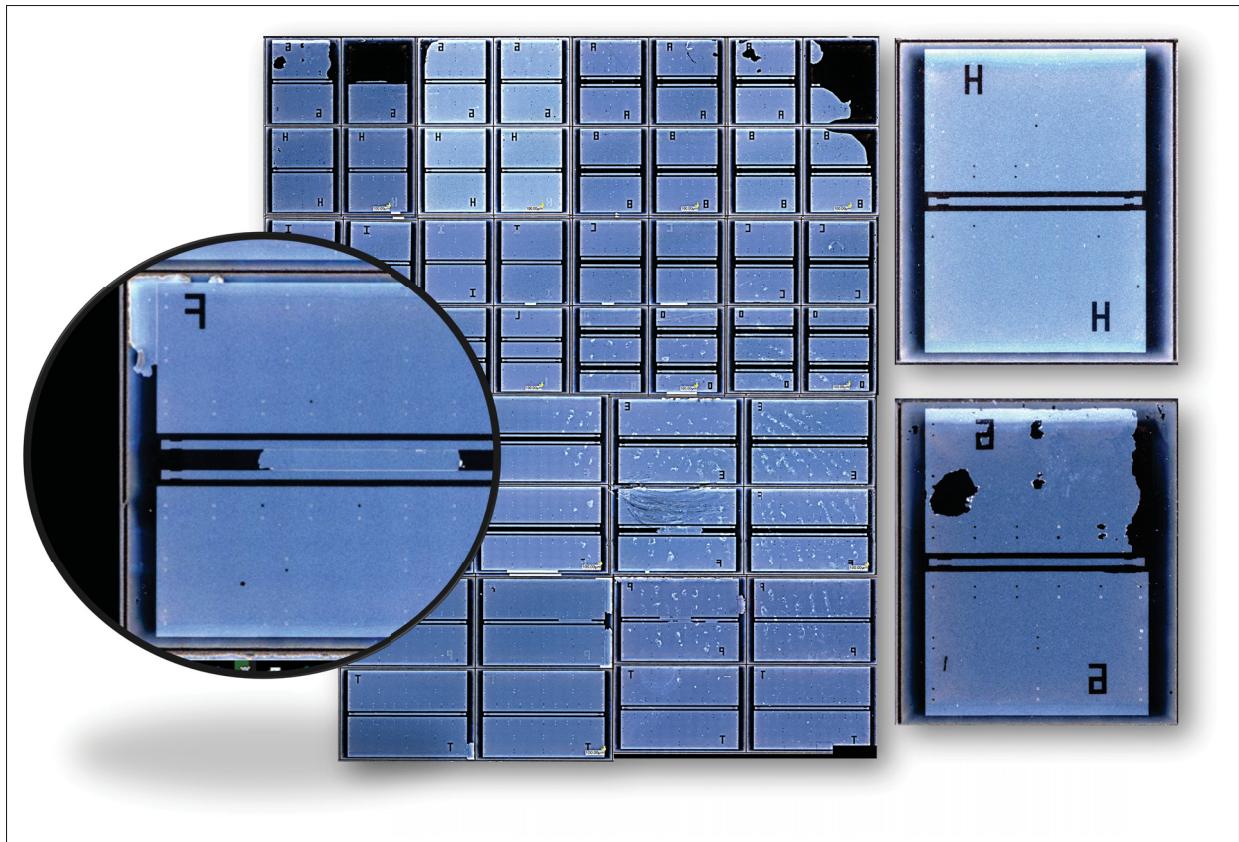

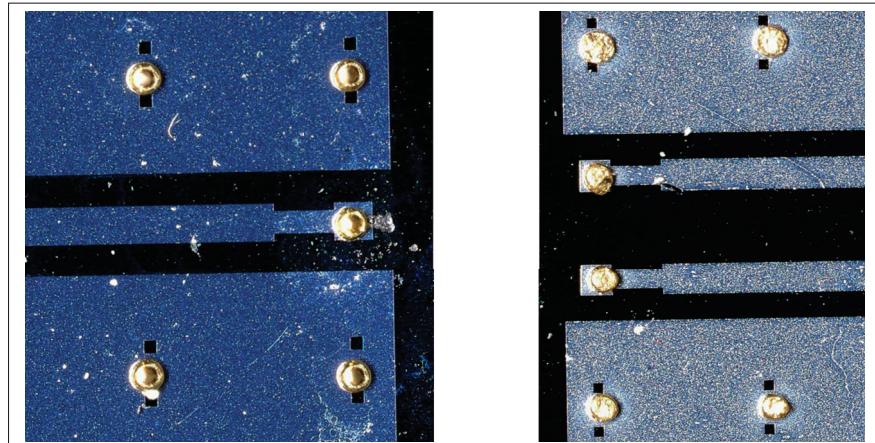

| Figure 4.11 | Photo des quatre substrats LTCC de la première itération de fabrication .....                                                                                                         | 94 |

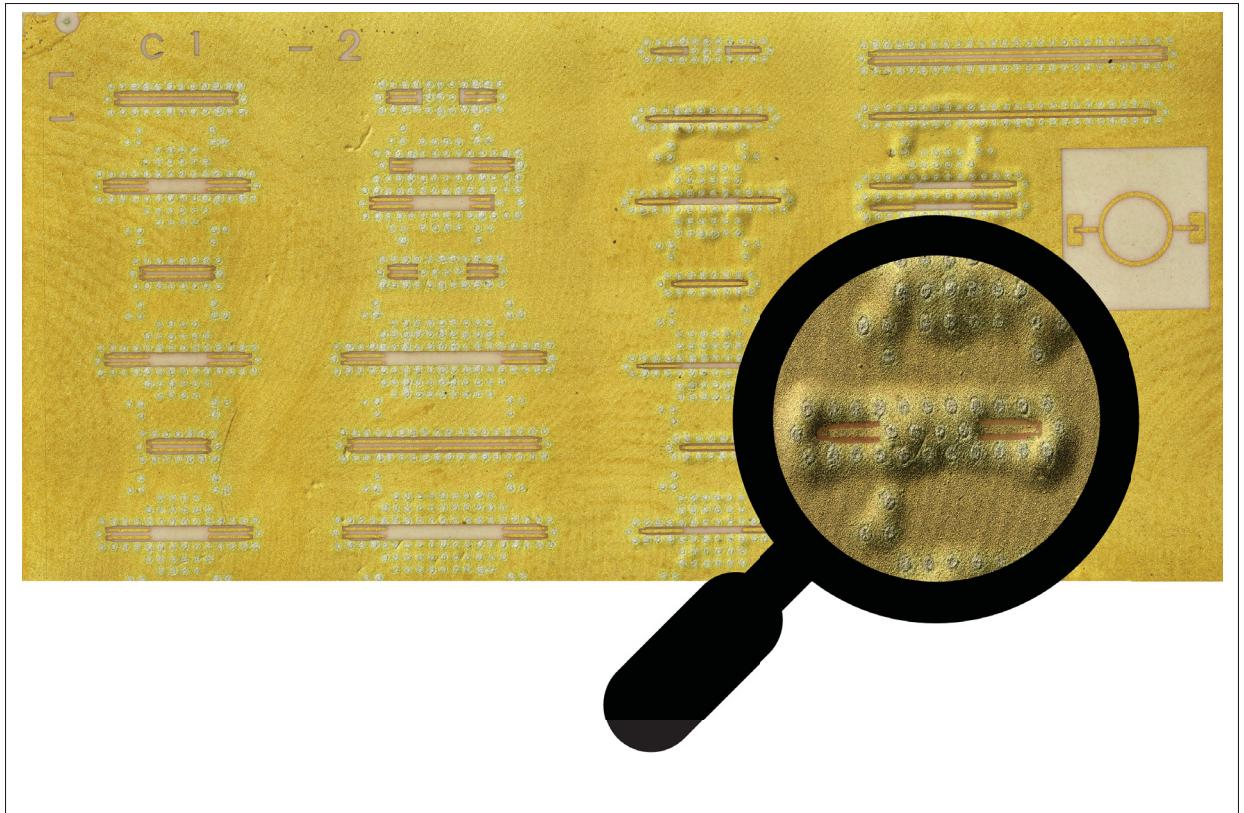

| Figure 4.12 | Photo du substrat -2% de la première itération de fabrication avec une fonction d'imitation de la technologie SEM sur microscope numérique KEYENCE .....                              | 95 |

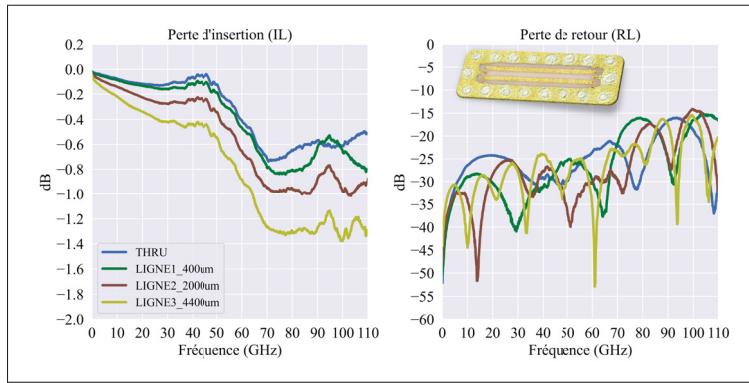

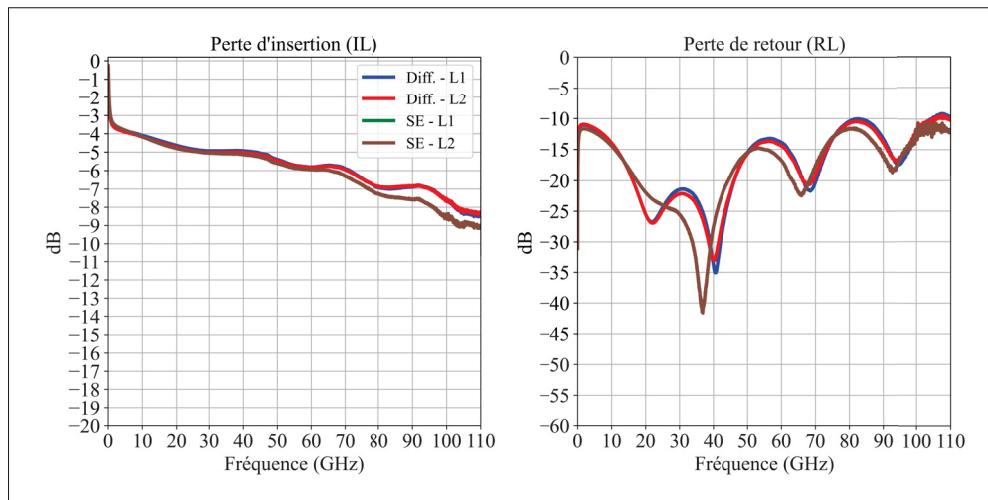

| Figure 4.13 | Mesures des standards TRL de la ligne différentielle du substrat -2% de la première itération de fabrication .....                                                                    | 96 |

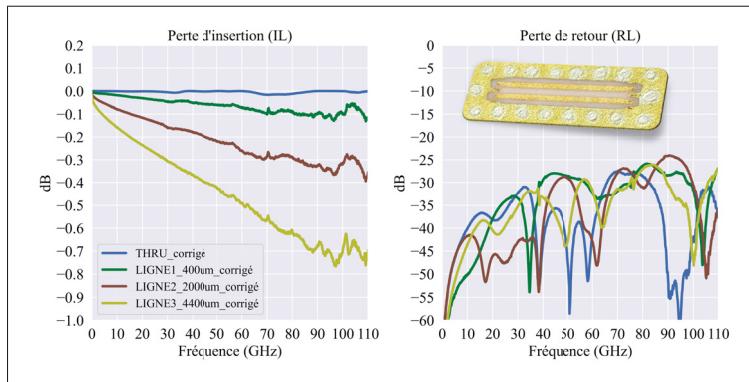

| Figure 4.14 | Mesures des standards TRL <b>corrigés</b> différentiels du substrat -2% de la première itération de fabrication .....                                                                 | 96 |

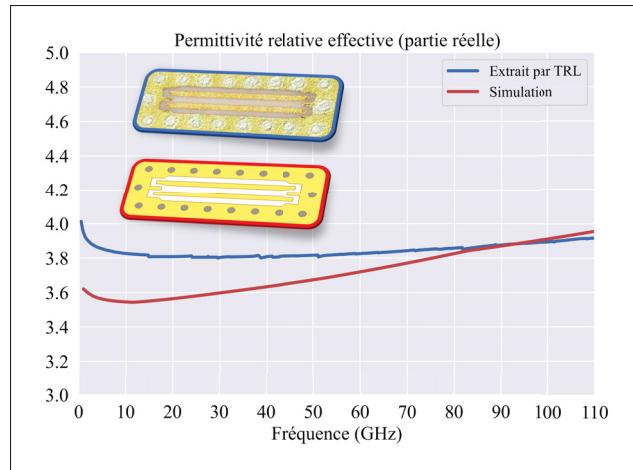

| Figure 4.15 | Valeur de la permittivité relative effective pour la ligne différentielle du substrat extraite à partir du TRL de la première itération de fabrication (version -2%) .....            | 97 |

| Figure 4.16 | Mesures des standards TRL simples du substrat -2% de la première itération de fabrication .....                                                                                       | 97 |

| Figure 4.17 | Photo du substrat -2% avec l'identification des standards TRL via un code de couleur en fonction des performances en mesure (rouge = médiocre, orange = mauvaise, vert = bonne) ..... | 98 |

|             |                                                                                                                                                                                          |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.18 | Photo du substrat LTCC nominal de la deuxième itération de fabrication .....                                                                                                             | 100 |

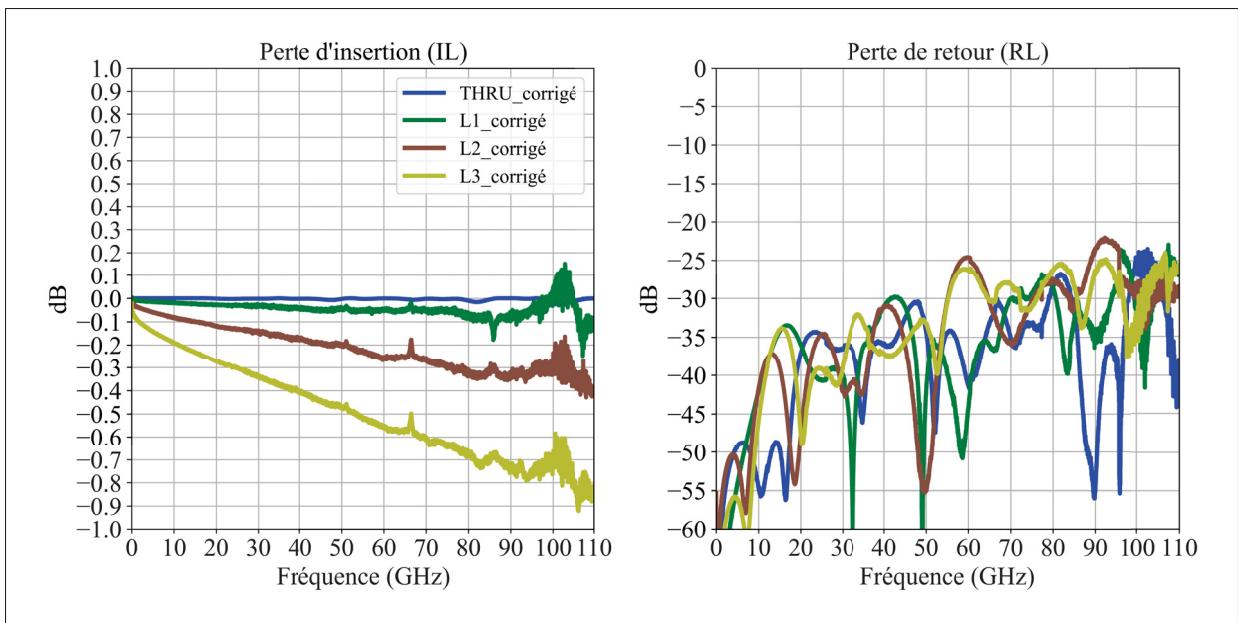

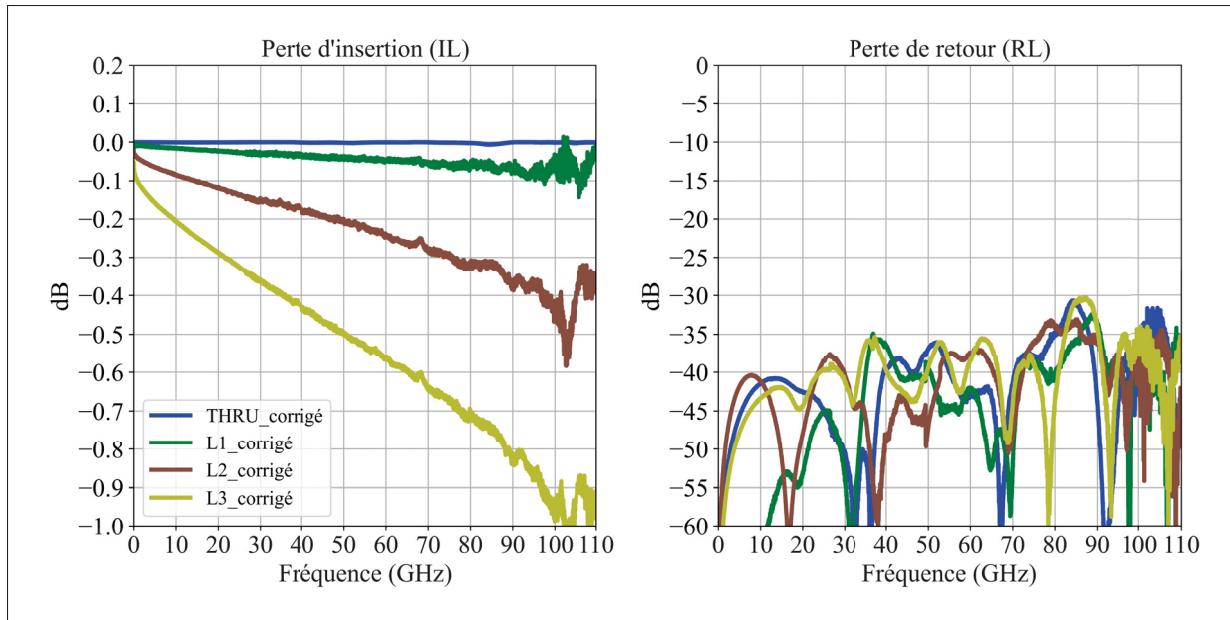

| Figure 4.19 | Standards TRL corrigés de la fabrication 2 pour la ligne simple .....                                                                                                                    | 101 |

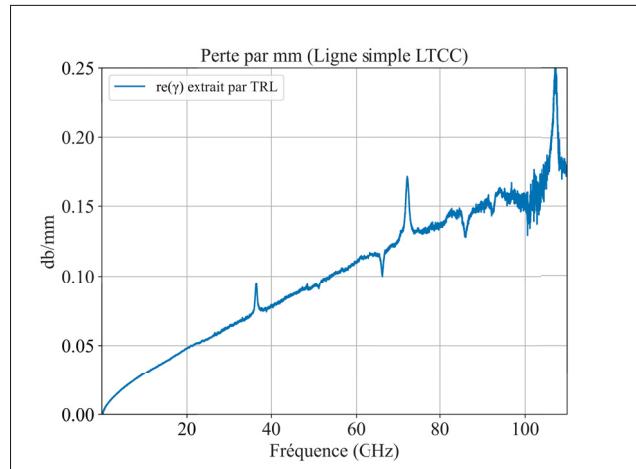

| Figure 4.20 | Perte par mm de la ligne simple LTCC .....                                                                                                                                               | 101 |

| Figure 4.21 | Standards TRL corrigés de la fabrication 2 pour la ligne différentielle .....                                                                                                            | 102 |

| Figure 4.22 | Perte par mm de la ligne différentielle LTCC .....                                                                                                                                       | 102 |

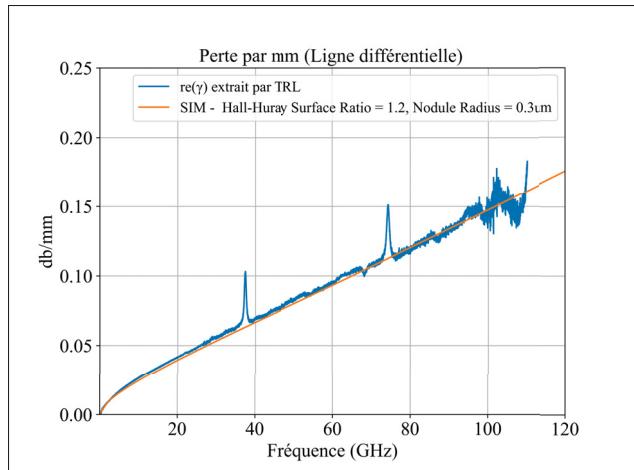

| Figure 4.23 | Ajustement des pertes par mm du modèle de simulation à partir des mesures TRL de la ligne différentielle .....                                                                           | 103 |

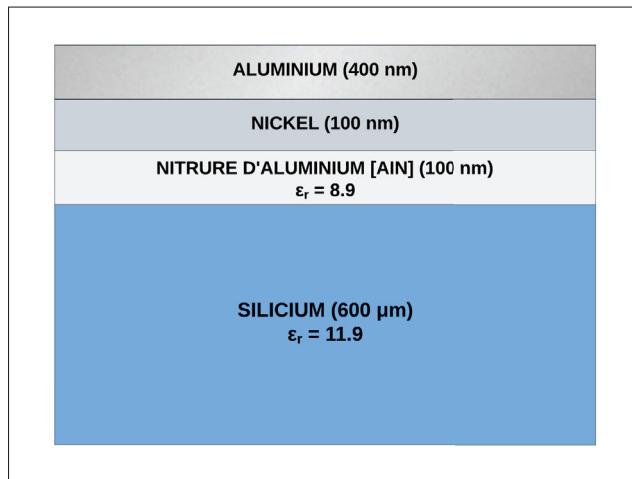

| Figure 4.24 | Schéma d'empilement des couches des puces .....                                                                                                                                          | 104 |

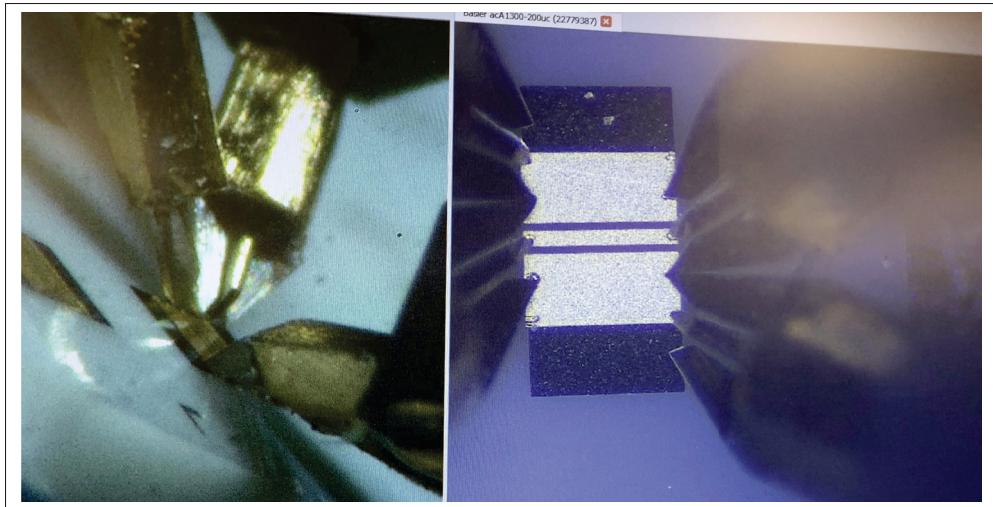

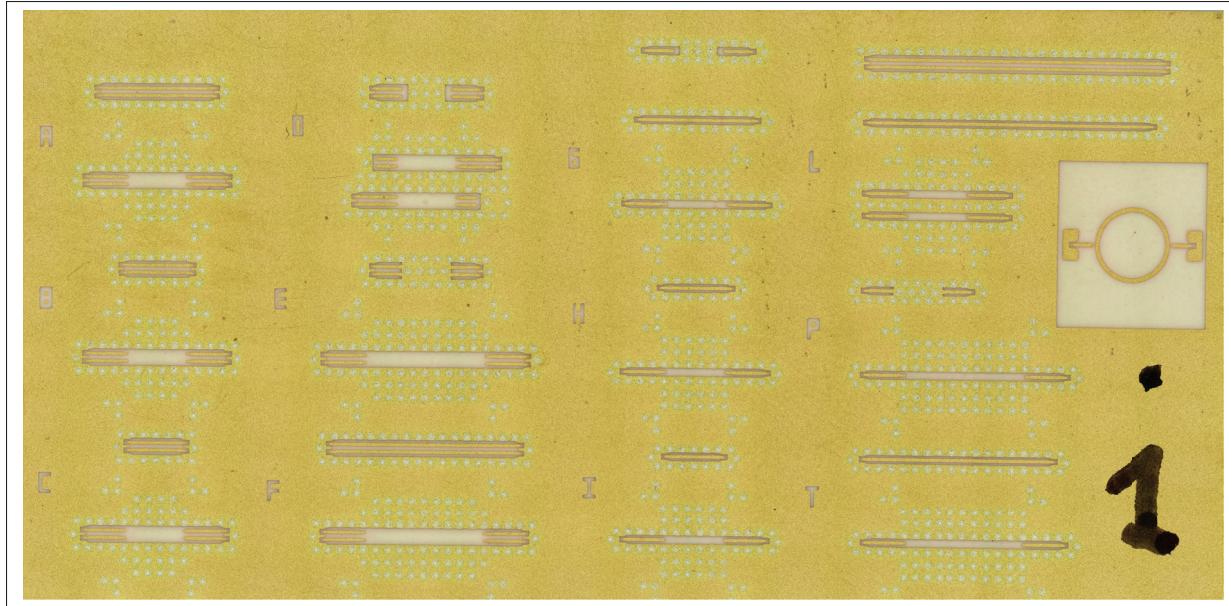

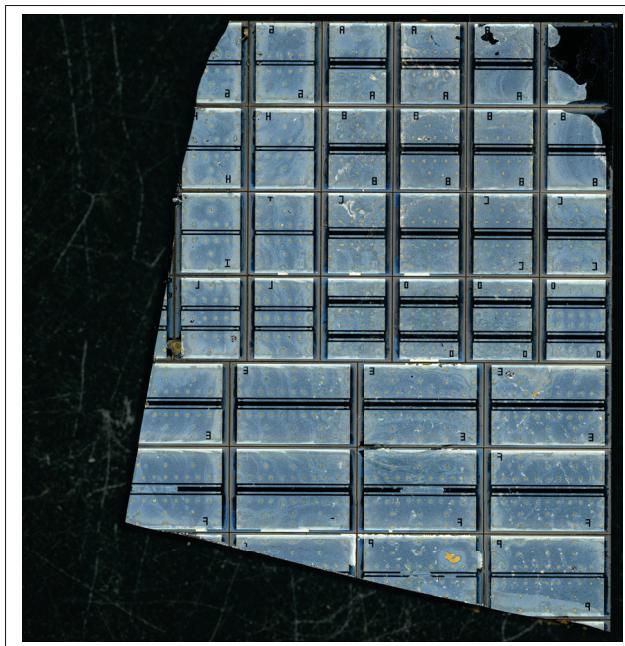

| Figure 4.25 | Photo de la première itération de puces fabriquées encore sur la gaufre de silicium .....                                                                                                | 105 |

| Figure 4.26 | Photo de la portion de gaufre avec billes d'or reçues de l'ETS .....                                                                                                                     | 106 |

| Figure 4.27 | Exemple de puce reçue de l'ETS avec l'absence de billes sur les pastilles de signaux .....                                                                                               | 106 |

| Figure 4.28 | Photo de certains échantillons de puces non installées provenant du 3IT (fabrication No. 2) .....                                                                                        | 107 |

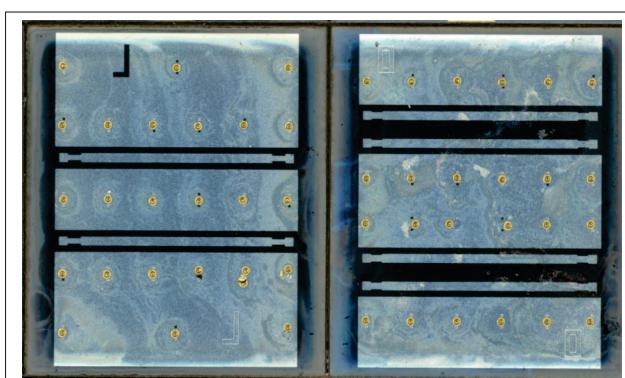

| Figure 4.29 | Photo des billes d'or sur les puces (fabrication No. 2) .....                                                                                                                            | 107 |

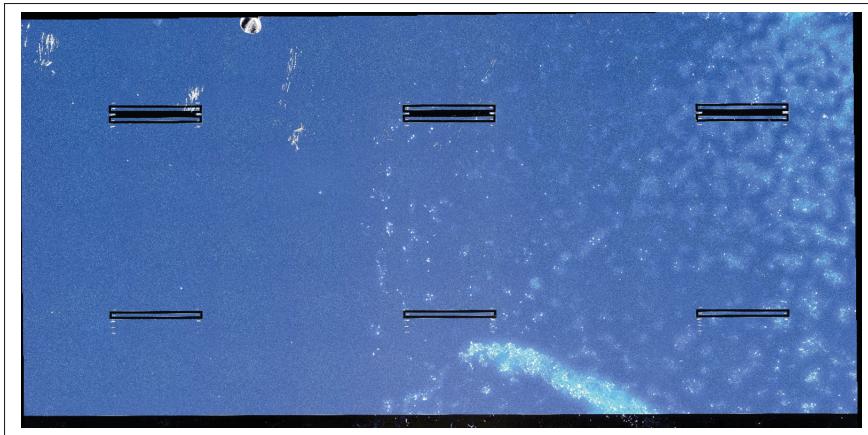

| Figure 4.30 | Photo des lignes de test de 2 mm représentant les lignes de transmission des puces sur silicium .....                                                                                    | 108 |

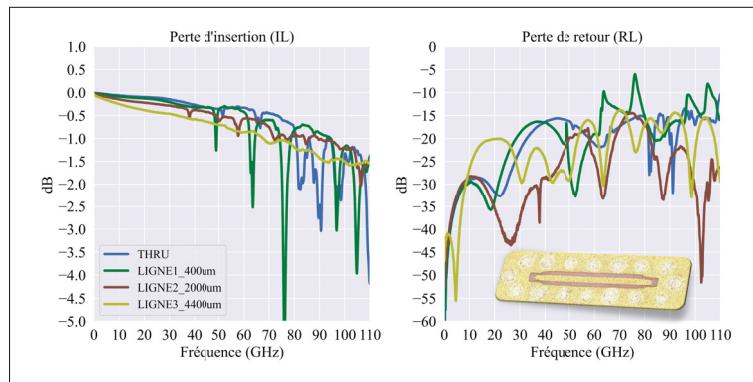

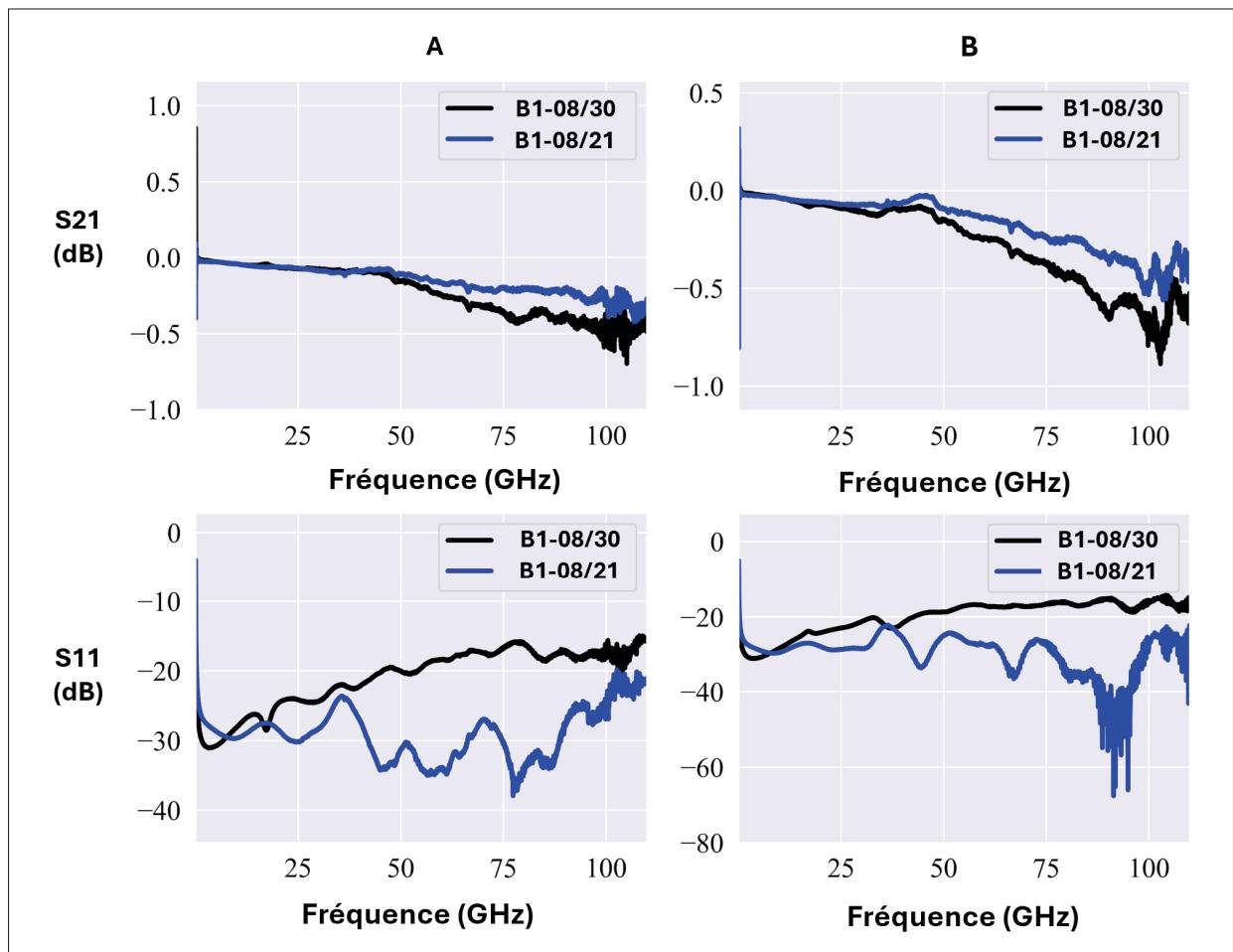

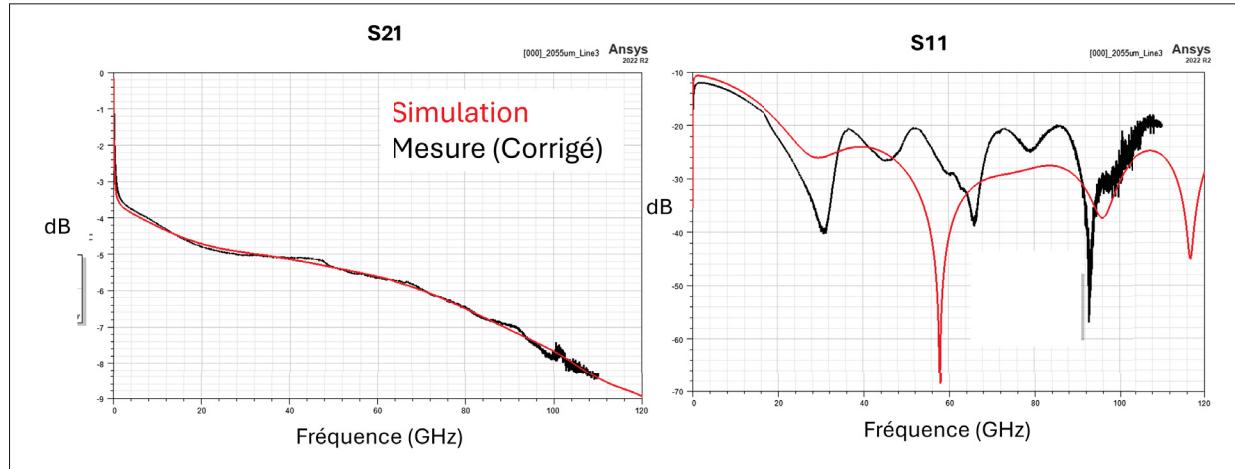

| Figure 4.31 | Mesures des lignes de test sur silicium (S11 S21) .....                                                                                                                                  | 108 |

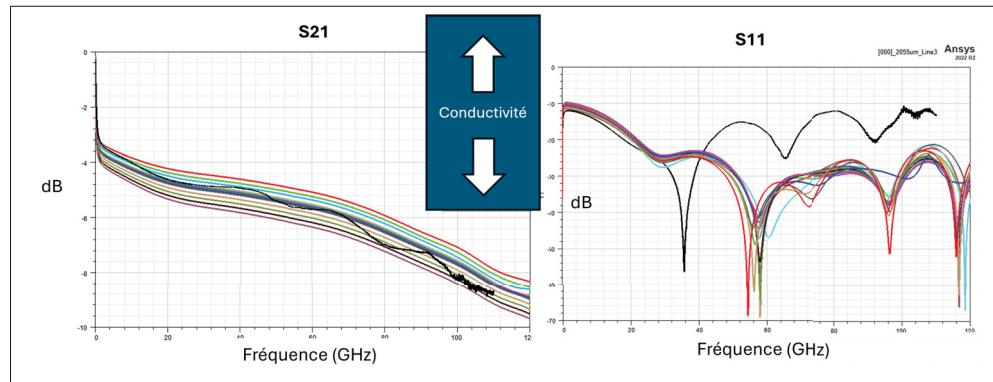

| Figure 4.32 | Mesures des lignes de test sur silicium (S11 S21) .....                                                                                                                                  | 109 |

| Figure 4.33 | Mesures des lignes de test sur silicium (S11 S21) .....                                                                                                                                  | 109 |

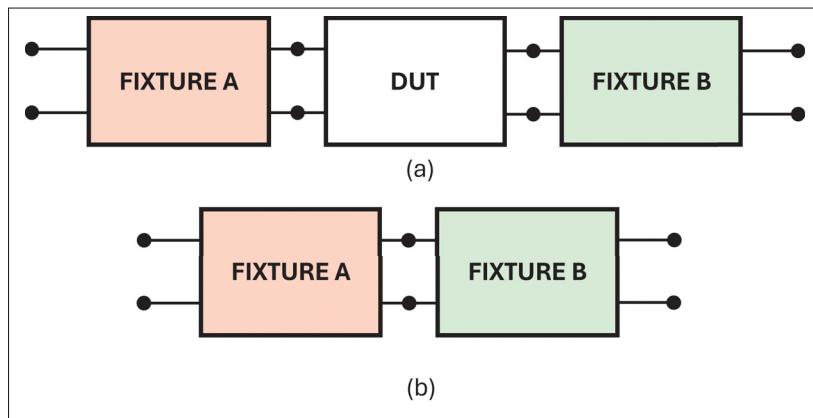

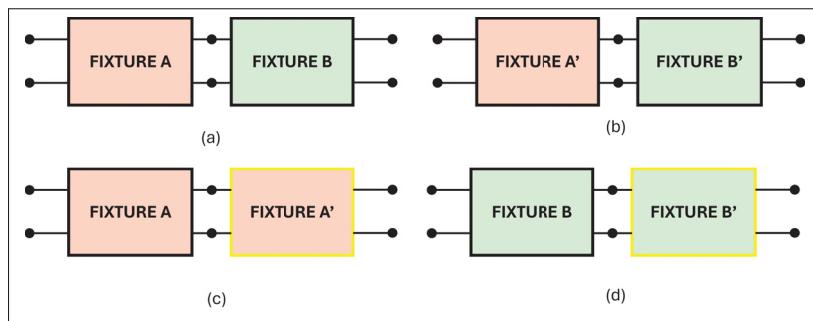

| Figure 4.34 | (a) Schéma de la décomposition matricielle d'une mesure d'unité sous test. (b) Les fixtures A et B extraites par TRL (2x thru) .....                                                     | 110 |

| Figure 4.35 | (a) Fixtures A et B de la calibration #1, (b) fixtures A et B de la calibration #2, (c, d) opération matricielle effectuée pour extraire la différence entre les deux calibrations ..... | 110 |

| Figure 4.36 | Delta des calibrations TRL (lignes simples) .....                                                                                                                                        | 111 |

|             |                                                                                                                                         |     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.37 | Mesure de la ligne de test simple sur silicium corrigée et ajustée à la mesure .....                                                    | 112 |

| Figure 4.38 | Mesure de la ligne de test différentielle sur silicium corrigé et comparé avec la simulation utilisant 6.9 S/m comme conductivité ..... | 113 |

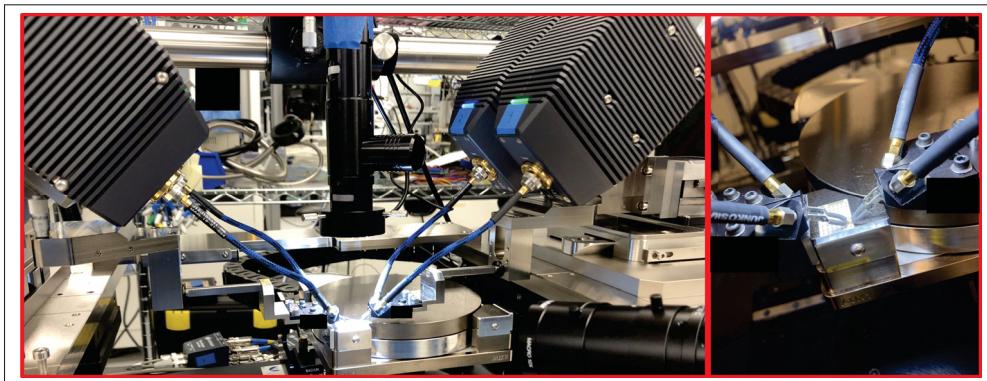

| Figure 4.39 | Photo du substrat B1 avec les puces retournées installées .....                                                                         | 114 |

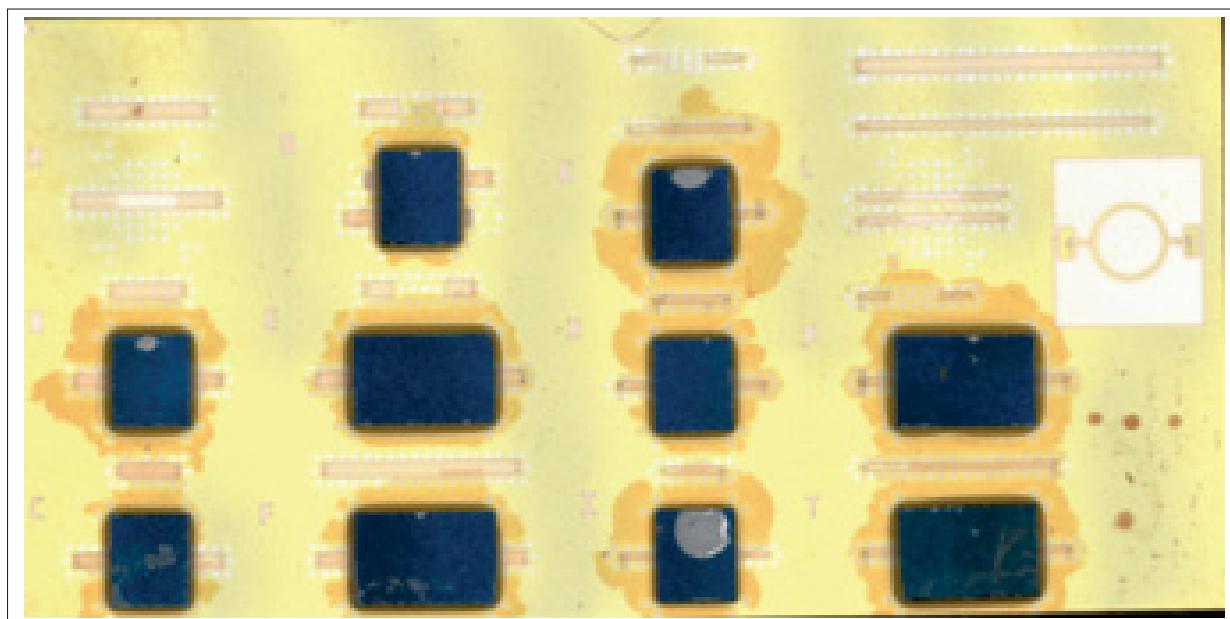

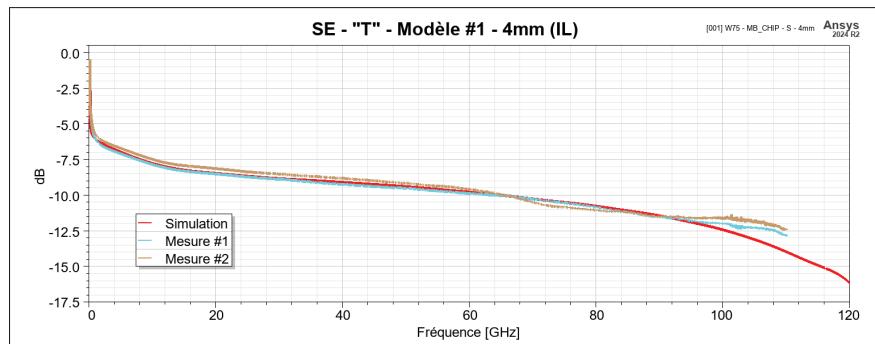

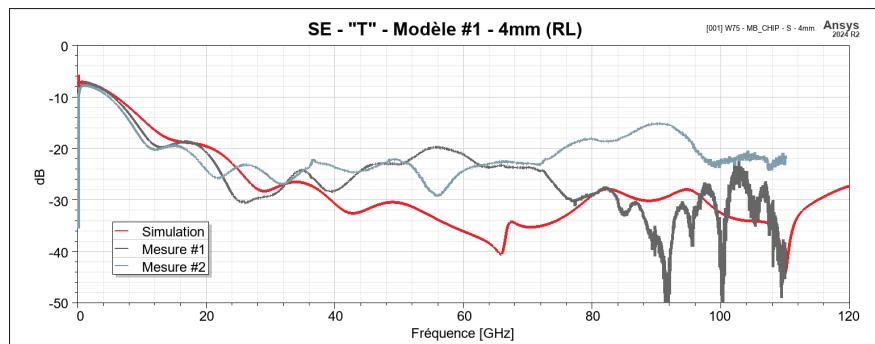

| Figure 4.40 | Pertes de transmission du modèle compensé #1 "T" (ligne simple 4 mm) .....                                                              | 115 |

| Figure 4.41 | Pertes de réflexion du modèle compensé #1 "T" (ligne simple 4 mm) .....                                                                 | 115 |

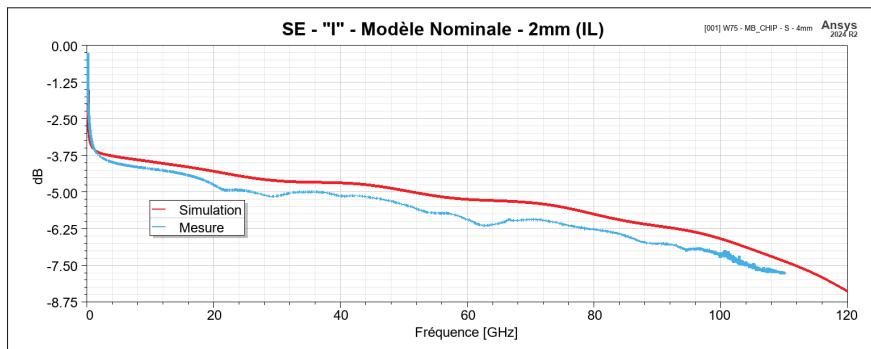

| Figure 4.42 | Pertes de transmission du modèle non compensé "I" (ligne simple 2 mm) .....                                                             | 116 |

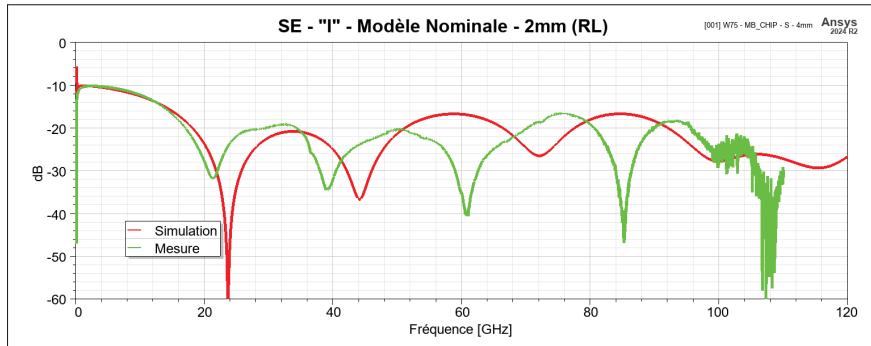

| Figure 4.43 | Pertes de réflexion du modèle non compensé "I" (ligne simple 2 mm) .....                                                                | 116 |

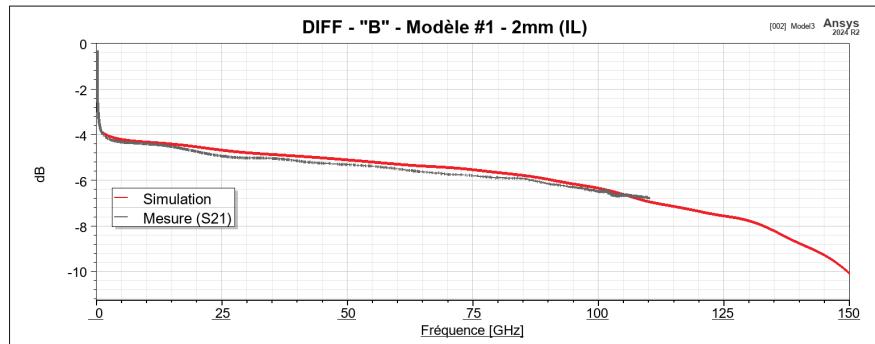

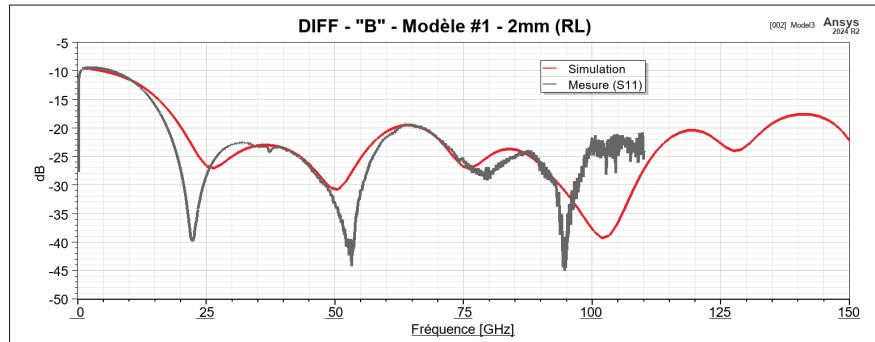

| Figure 4.44 | Pertes de transmission du modèle compensé #1 "B" (ligne différentielle 2 mm) .....                                                      | 117 |

| Figure 4.45 | Pertes de réflexion du modèle compensé #1 "T" (ligne différentielle 2 mm) .....                                                         | 117 |

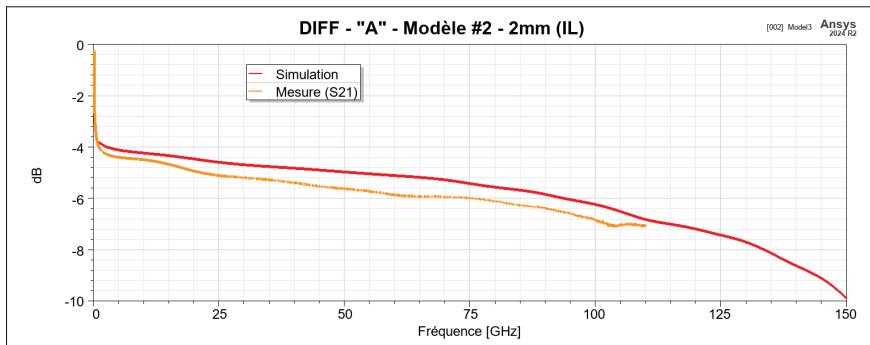

| Figure 4.46 | Pertes de transmission du modèle compensé #2 "A" (ligne différentielle 2 mm) .....                                                      | 118 |

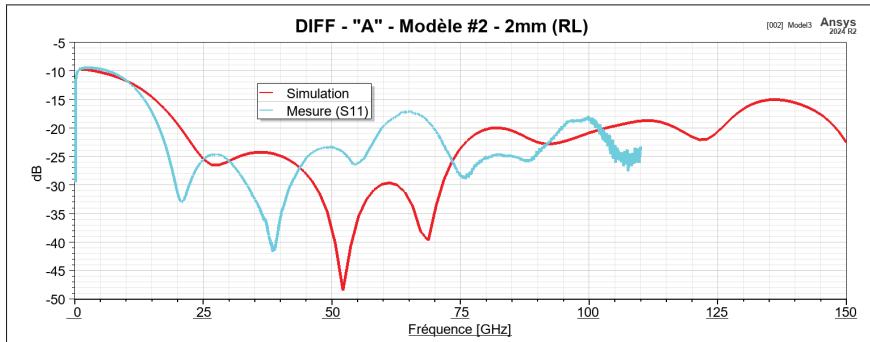

| Figure 4.47 | Pertes de réflexion du modèle compensé #2 "A" (ligne différentielle 2 mm) .....                                                         | 118 |

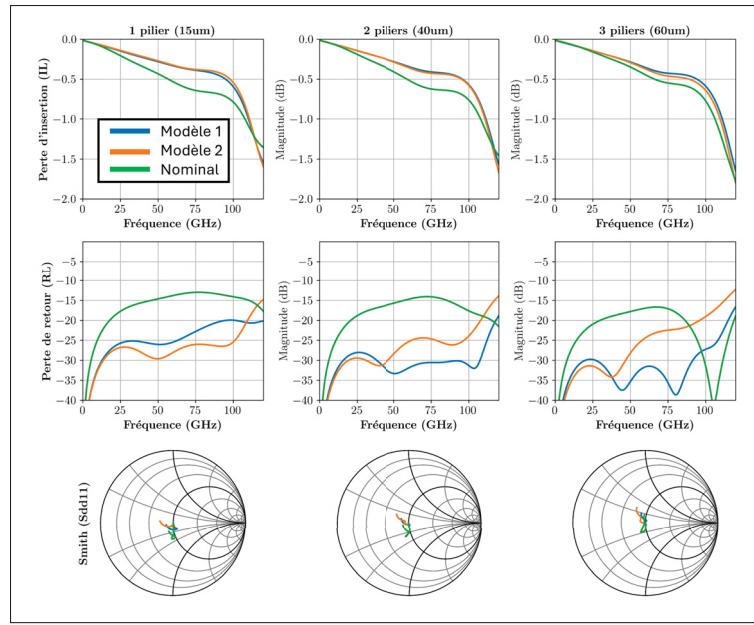

| Figure 4.48 | Simulation du modèle ajusté de la ligne simple avec silicium haute résistivité .....                                                    | 119 |

| Figure 4.49 | Simulation du modèle ajusté de la ligne différentielle avec silicium haute résistivité .....                                            | 119 |

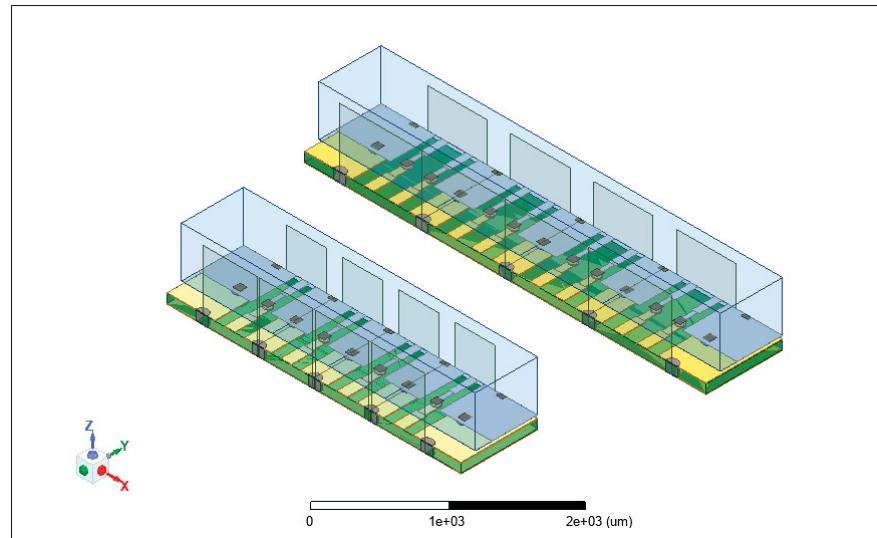

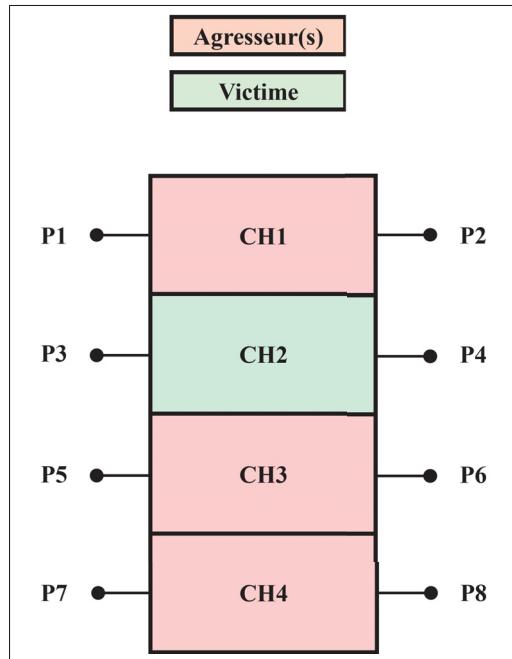

| Figure 4.50 | Modèles de simulation pour l'évaluation de la diaphonie .....                                                                           | 121 |

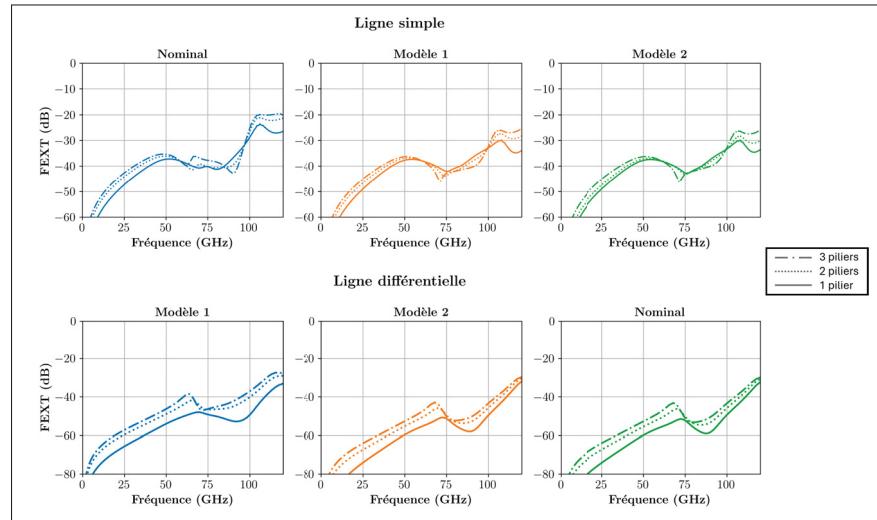

| Figure 4.51 | Simulation de la diaphonie des modèles ajustés des deux types de lignes avec silicium haute résistivité .....                           | 121 |

| Figure 4.52 | Schéma de l'arrangement de la simulation pour l'évaluation de la diaphonie .....                                                        | 122 |

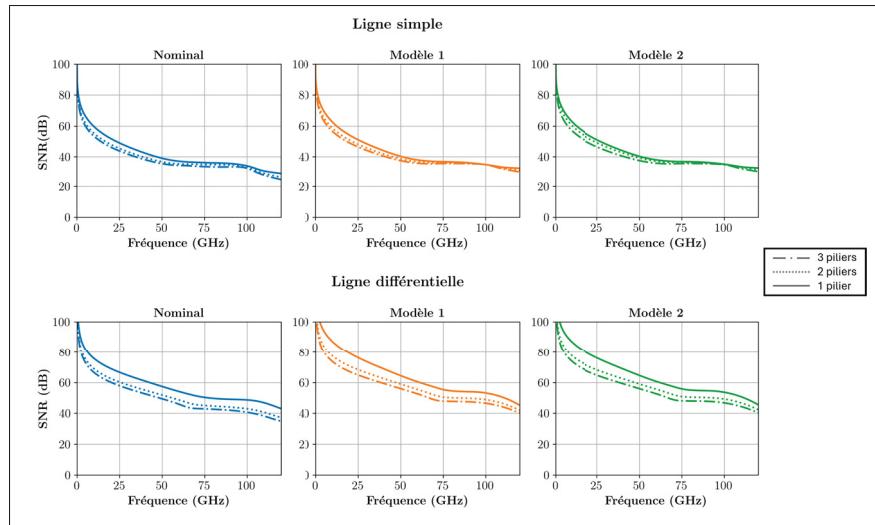

| Figure 4.53 | Rapport signal sur bruit (RSB) simulé avec modèles ajustés pour la ligne simple et la ligne différentielle .....                        | 123 |

## LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

|           |                                                              |

|-----------|--------------------------------------------------------------|

| ADC       | Convertisseur analogique à digitale                          |

| ASIC      | Circuit intégré pour application spécifique                  |

| BCB       | Benzocyclobutène                                             |

| BGA       | Matrice de billes                                            |

| BOL       | Lié sur plomb                                                |

| BOP       | Lié sur pastille                                             |

| C2        | Pilier en cuivre                                             |

| C4        | Bille de connexion de puce à effondrement contrôlé           |

| CDM       | Amplificateur modulateur cohérent                            |

| COAX      | Coaxiale                                                     |

| CPW       | Guide d'onde coplanaire                                      |

| GCPW      | Guide d'onde coplanaire avec référence à la masse inférieure |

| CTE       | Coefficient d'expansion thermique                            |

| Cu-Pillar | Pilier en cuivre                                             |

| DAC       | Convertisseur digital à analogique                           |

| dB        | Decibel                                                      |

| Dk        | Permittivité relative                                        |

| Df        | Facteur de dissipation diélectrique                          |

| EOM       | Modulateur électro-optique                                   |

| ETS       | École de Technologie Supérieure                              |

| eWLB      | Matrice de billes intégrées sur gaufre                       |

| FC        | Puce retournée                                               |

| GND       | Mise à la terre                                              |

| HFSS      | Logiciel de simulation électromagnétique haute fréquence     |

| HTCC      | Céramique cuite à haute température                          |

|        |                                                        |

|--------|--------------------------------------------------------|

| IC     | Circuit intégré                                        |

| IEEE   | Institut des ingénieurs électriciens et Électroniciens |

| LNA    | Amplificateur faible bruit                             |

| LTCC   | Céramique cuite à basse température                    |

| MB     | Carte mère                                             |

| MMIC   | circuit intégré monolithique hyperfréquence            |

| mmWave | Onde millimétrique                                     |

| MS     | Micro-Ruban                                            |

| MZM    | Modulateur Mach-Zehnder                                |

| PCB    | Carte de circuit imprimé                               |

| PD     | Photodiode                                             |

| PIC    | Circuit intégré photonique                             |

| PNA    | Analyseur de réseau en fréquence                       |

| RF     | Radio fréquence                                        |

| RLC    | Résistance/Inductance/Capacitance                      |

| Tand   | Facteur de perte tangente diélectrique                 |

| TE     | Transverse électrique                                  |

| TM     | Transverse magnétique                                  |

| TEM    | Transverse électromagnétique                           |

| VNA    | Analyseur de réseau vectoriel                          |

## INTRODUCTION

Les interconnections de circuits intégrés au sein de module complet dans un boîtier représentent, dans le domaine de l'encapsulation électronique, un aspect fondamental permettant la conversion des fonctions individuelles en fonctionnalité système. Dans le monde des radiofréquences, cet élément clef représente un des bloquants majeurs pour plusieurs applications visant l'opération dans les ondes millimétriques et/ou avec de très larges bandes passantes.

Au cours des dernières décennies, les avancées en termes de technologies semi-conductrices et de photonique sur silicium ont permis d'atteindre de nouveaux sommets en termes de fréquences limites d'utilisation et de bande passante. En effet, plusieurs composants atteignent désormais des fréquences dépassant les 100 GHz, et ce, avec de très larges bandes passantes. À ce jour, le bloquant principal se trouve dans le raccordement de ces composants au sein de système complet. Que ce soient les connexions entre les circuits intégrés, avec le boîtier ou bien simplement l'interfaçage avec le monde extérieur, les solutions d'interconnexion large bande représentent l'aspect limitant majeur pour les prochaines générations de systèmes/produits pour les applications visant l'opération dans les THz avec large bande passante.

Encore aujourd'hui, la liaison par fil d'or est l'une des solutions d'interfaçage qui dominent le monde de l'encapsulation pour les interconnexions de premier niveau, soit d'une puce vers une autre puce ou d'une puce vers le substrat du boîtier. Toutefois, cette solution est de moins en moins d'actualité en raison de la dégradation de ses performances lorsque la fréquence d'utilisation dépasse les 50 GHz. En effet, pour dépasser cette limite, le caractère inductif de ces minces fils force l'utilisation de structures de compensations qui donne généralement lieu à des transitions de type passe-bande étroites. Évidemment, il est possible d'atteindre de plus haute fréquence en limitant la longueur des fils et avec des techniques de compensation large bande, mais ces solutions sont très souvent très sensibles aux variations, et donc, non appropriées à la production de masse.

Une solution intéressante qui gagne du terrain dans le domaine de l'encapsulation pour des applications hautes fréquences depuis plusieurs années est l'interconnexion par puce retournée. En effet, en raison de son rapport hauteur-largeur avantageux, la puce retournée n'est pas sujette aux mêmes limitations que la liaison par fils. De ce fait, cette technologie est un candidat très prometteur pour l'intégration de composants photoniques au sein de systèmes.

Afin de résumer le tout, la problématique, les objectifs et l'organisation de la thèse seront présentés ou reformulés de manière synthèse.

## **Problématique**

Avec l'arrivée de nouveaux composants optiques possédant des bandes passantes de plus de 100 GHz, le défi principal se trouve dans le raccordement et l'encapsulation de tels composants au sein de modules complets. En effet, les interconnexions de premier niveau des puces vers le substrat principal représentent le bloquant majeur pour les applications visant l'opération dans les THz.

## **Objectifs**

L'objectif principal de cette recherche est de trouver une solution d'interconnexion simple et efficace large bande jusqu'à plus de 100 GHz. Les critères sont une faible complexité, une grande flexibilité d'adaptation, une grande accessibilité, une possibilité de production de masse, un faible coût et des performances RF respectant des critères précis. De plus, puisque certains composants haute vitesse d'une chaîne de communication sont opérés différemment, il serait nécessaire que la solution d'interconnexions fonctionne autant pour une transition simple que pour une transition différentielle. Au niveau des pertes de transmission (IL), celles-ci doivent être minimisées au maximum. Ensuite, au niveau des pertes de retour, l'objectif minimal absolu est de -10 dB, mais l'idéal serait d'être plus petit que -15 dB sur toute la bande. Pour finir, cette transition doit fonctionner pour des interconnexions de type puce à substrat de premier niveau, soit d'une puce vers le substrat du boîtier.

## Organisation de la thèse

Le **chapitre 1** couvre l'étude bibliographique effectuer pour ce projet de recherche. Cette section regroupe les avancées les plus récentes et prometteuses proposées dans la littérature en lien avec la problématique d'interconnexion large bande efficace jusqu'à des fréquences de plus de 100 GHz. Cette revue est divisée entre les principales catégories d'interconnexion, soit la liaison par fil (Wirebond), la puce retournée (Flip-Chip) et d'autres alternatives atypiques. Chacune des solutions présentées sera évaluée de manières critiques par rapport aux objectifs poursuivis.

Le **chapitre 2** couvre le développement individuel des éléments nécessaires à cette recherche, soit les puces, les substrats de réception et les billes/piliers d'or. Au niveau des deux structures à interconnecter, la conception des lignes de transmissions ainsi que les considérations/limitations en fonction de la fréquence maximale d'opération visée sont présentées. Au niveau des piliers, l'aspect empilable et son impact sur l'effet de proximité sont présentés. Ultimement, cette section couvre la portion dimensionnement des éléments individuels à l'aide d'études analytiques théoriques et de courtes simulations afin d'atteindre des fréquences de plus de 100 GHz.

Le **chapitre 3** représente la portion du document consacrée à la conception et l'étude complète d'une interconnexion par puce retournée de type puce à substrat large bande de DC à plus de 100 GHz sur pilier d'or avec hauteur flexible. Dans cette section, les modèles complets de puce retournée sont étudiés et optimisés selon plusieurs paramètres à l'aide de concepts théoriques et de simulations électromagnétiques 3D complètes. Finalement, les meilleurs candidats pour la validation expérimentale sont présentés.

Le **chapitre 4** couvre la portion expérimentale de ce projet de recherche. Les itérations de fabrications des puces et des substrats de réceptions sont présentées individuellement et leurs mesures sont comparées avec les simulations. L'aspect assemblage ainsi que les problèmes et

défis rencontrés lors de la fabrication sont aussi abordés. Les mesures de structures assemblées sont ensuite comparées avec les résultats de simulations attendues.

## CHAPITRE 1

### REVUE DE LITTÉRATURE

La croissance constante des demandes en termes de débits de données dans les liens de communications hautes vitesses modernes intensifie l'effort de recherche sur le développement de composants RF et électro-optiques opérant sur de très larges bandes passantes, et ce, jusqu'à dans les fréquences THz. Toutefois, un aspect essentiel concernant l'intégration de ces composants au sein de système complet est négligé. En effet, le bloquant majeur se trouve dans le manque de solution d'interconnexion large bande et avec de bonnes performances jusqu'à plus de 100 GHz. Cette problématique est directement observable dans les systèmes de communication haut débit moderne avec l'arrivée de modulateur optique atteignant des bandes passantes de plus 100 GHz sur silicium photonique hybride qui ne peuvent être raccordés simplement et efficacement avec les solutions d'interfaçage actuelles. Les objectifs poursuivis définissant une interconnexion simple et efficace large bande jusqu'à plus de 100 GHz sont une faible complexité, une grande flexibilité d'adaptation, une grande accessibilité, une possibilité de production de masse, un faible coût et des performances RF respectant des critères précis. De plus, puisque certains composants haute vitesse d'une chaîne de communication sont opérés différentiellement, il serait nécessaire que la solution d'interconnexions fonctionne autant pour une transition simple que pour une transition différentielle. Le critère au niveau des pertes de transmission est qu'elles soient minimisées au maximum. Ensuite, au niveau des pertes de retour, l'objectif minimal absolu est de -10 dB, mais l'idéal serait d'être plus petit que -15 dB sur toute la bande. Pour finir, cette transition doit fonctionner pour des interconnexions de type puce à substrat de premier niveau, soit d'une puce vers le substrat du boîtier. Dans la littérature, plusieurs recherches ont été effectuées sur diverses techniques d'interconnexion puce à substrat et puce à puce large bande jusqu'à plus de 100 GHz. Cependant, plusieurs solutions sont extrêmement complexes, non accessibles (artisanales) et/ou très coûteuses. L'objectif de cette présente revue est de cibler les études récentes les plus prometteuses en plus de définir des balises générales à respecter en vue d'obtenir de bonnes performances tout en respectant les objectifs mentionnés ci-haut. L'organisation du présent chapitre est définie de manière à

présenter individuellement les diverses catégories d'interconnexions générales, soit la liaison par fil (Wirebond), la puce retournée (Flip-Chip) et d'autres alternatives atypiques.

### 1.1 Liaison par fil

Encore aujourd'hui, la liaison par fil est de loin la technologie d'interconnexion la plus répandue, toute application RF confondues. Cette technologie d'interconnexions permet la propagation d'un signal DC ou d'ondes électromagnétiques en radiofréquence d'une entité à un autre en reliant des pastilles de contact via un mince filament conducteur. Ce type d'interconnexion est particulièrement utilisé comme interconnexion de premier niveau, soit pour des connexions puce à puce ou des connexions puce à substrat. La popularité de la liaison par fil est en raison des avantages que cette technologie offre :

- Rendement et fiabilité supérieurs

- Flexibilité : Peut s'adapter à la plupart des configurations spatiales

- Faible coût d'implémentation

- Alloue une grande densité de signaux

- Technologie accessible dans virtuellement toutes les usines de fabrications et d'assemblages

- Bonne performance RF large bande jusqu'à certaines fréquences

Malgré tous ces avantages, l'utilisation de fils à des fréquences dépassant les 100 GHz est extrêmement difficile en raison de leurs caractères inductifs. Concrètement, un fil circulaire à une inductance qui peut être approximée par l'équation suivante (Terman, 1943) (Gupta, Garg & Chadha, 1981) :

$$L_W = 2 \times 10^2 \ell (\ln (4\ell/d) - 1 + \mu_r E) \quad (1.1)$$

$\ell$  : Longueur du fil (m)

d : Diamètre du fil (m)

$\mu_r$  : Perméabilité relative du conducteur

E : Facteur d'ajustement de l'effet pelliculaire («skin-effect»)

L : Inductance du fil en nanohenrys (nH)

Évidemment, cette équation n'est valable que pour un fil circulaire droit isolé «flottant» dans l'air.

Lorsque cette équation est résolue et convertie en réactance inductive pour un fil d'or typique, il est possible de constater que la longueur du fil doit être extrêmement courte afin d'avoir une valeur de réactance à 100 GHz suffisamment petite pour permettre de bonne performance dans un système de  $50 \Omega$ . Avec cette problématique en tête, la prochaine étape est de présenter les récentes solutions prometteuses proposées dans la littérature. Parmi celles-ci on retrouve l'utilisation de ruban, la compensation et l'utilisation d'une technologie nommée MicroCoax.

### 1.1.1 Ruban

Le fil en ruban est une solution très intéressante pour minimiser l'inductance en comparaison avec le fil circulaire (Gupta *et al.*, 1981) (Harman, 2010). Une étude présente l'utilisation de ruban comme interconnexion de DC à 100 GHz (Shireen *et al.*, 2011).

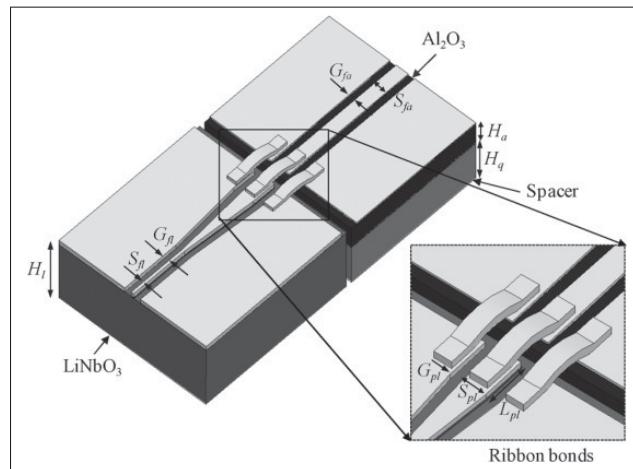

Figure 1.1 Exemple d'interconnexion par ruban (Shireen *et al.*, 2011)

La transition présentée est de type puce à substrat (CPW-CPW) et relie une puce en LiNbO<sub>3</sub> à une céramique Al<sub>2</sub>O<sub>3</sub>. Les pertes de retour sont meilleures que -10 dB et les pertes de transmissions à 100 GHz sont d'environ 2.5 dB. La longueur des rubans est de 180  $\mu$ m. Incontestablement, une longueur de 180  $\mu$ m est extrêmement courte comme distance et il est très complexe d'avoir une distance pastille à pastille aussi petite entre les 2 entités à interconnecter. De plus, -10 dB de  $S_{11}$  à 100 GHz semblent être les meilleures performances obtenues puisqu'un seul échantillon est présenté, ce qui indique qu'avec des variations, les performances pourraient sans aucun doute être non suffisantes.

### 1.1.2 Compensation

Une autre solution est la compensation de l'inductance. Il existe plusieurs structures efficaces de compensation permettant d'optimiser une transition sur une certaine bande de fréquence. Le problème avec la compensation est que la majorité des techniques donne lieu à des transitions de type passe-bande étroit qui ne sont pas appropriées aux applications large bande. Une des techniques large bande pour la liaison par fil consiste en l'utilisation de plusieurs fils en parallèle de manière à diviser le courant entre eux et ainsi réduire l'inductance. Des chercheurs ont étudié cette technique pour des transitions puce à substrat sur une plage de DC jusqu'à 92 GHz (Jiang, Krozer, Bach, Mekonnen & Johansen, 2013) et 100 GHz (Wu, Yu, Li & Kuo, 2015). La meilleure transition est celle jusqu'à 92 GHz avec des pertes de retour maximal de -11.2 dB. Cependant, les pertes d'insertions sont de -3 dB à 92 GHz, ce qui est particulièrement élevé pour un seul interconnexion.

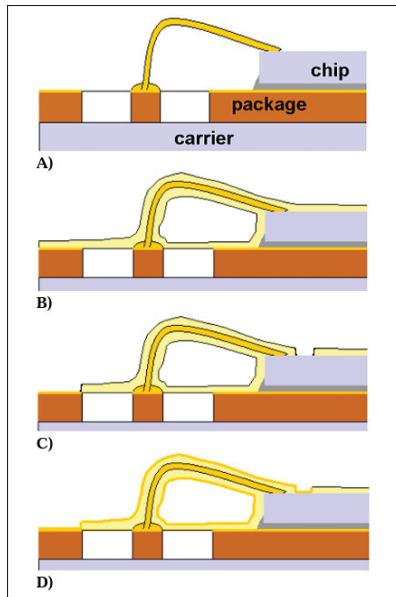

Une autre solution de compensation large bande est l'utilisation de réseaux LC. Des chercheurs ont réussi à atteindre des performances RF très impressionnantes avec des fils circulaires dans la bande DC-170 GHz (Valenta *et al.*, 2015). La transition présentée est de type puce à puce (CPW-CPW) et permet de relier deux puces de silicium BiCMOS 0.13  $\mu$ m. Afin de mitiger l'effet de l'inductance à haute fréquence, une topologie de compensation C-L-C-L-C-L-C est utilisée avec des fils de 150  $\mu$ m. Avec cette technique, les pertes de retours et les pertes d'insertions sont meilleures que -12 dB et 1 dB respectivement jusqu'à 140 GHz. De plus, ils ont démontré la

répétabilité avec plusieurs échantillons. Il semblerait que ce soit les meilleures performances d'interconnexions par fil «typique» large bande démontrées à ce jour. Cependant, la complexité du montage global est très élevée. En effet, la longueur du fil de  $150 \mu\text{m}$  représente un grand défi sans mentionner la complexité de la topologie de compensation qui pourrait ne pas être aisée à adapter au besoin précis d'un autre type de transition avec des paramètres différents.

Figure 1.2 Exemple de compensation LC d'une liaison par fil (Valenta *et al.*, 2015)

Dans un autre ordre d'idée, l'utilisation de la compensation des fils de liaison pour des applications nécessitant des bandes étroites au-delà de 100 GHz a été démontrée pour des transitions simples et différentielles (Beer *et al.*, 2011) (Valenta *et al.*, 2015), (Simsek *et al.*, 2020). À l'évidence, des performances en bande étroite ne satisfont pas les critères de cette étude.

### 1.1.3 MicroCoax

Dans un autre ordre d'idée, une solution intéressante proposée il y a quelques années est celle de convertir le fil nu en câble coaxial.

Figure 1.3 Étapes de fabrication pour un MicroCoax (Cahill *et al.*, 2006)

Le MicroCoax consiste en un fil recouvert d'un diélectrique et d'une couche de métal extérieur pour le plan de masse. Essentiellement, c'est un câble coaxial miniature. Avec cette technique il est possible de contrôler l'impédance de la transition de manière à atteindre des fréquences plus élevées sans nécessiter des fils extrêmement courts. De plus, le niveau de radiation est beaucoup plus faible, ce qui permet entre autres de réduire la distance minimale entre 2 transitions en raison de la faible diaphonie. La technologie du MicroCoax permettrait d'atteindre de très bonne performance RF de DC jusqu'à plus de 100 GHz (Devlin, 2014). Un microcoax de 2.2mm mesuré démontre des pertes d'insertions de moins de 0.7 dB jusqu'à 115 GHz. Les pertes de retour sont quant à elles meilleures que -20 dB sur la majorité de la bande avec une valeur maximale de -17 dB à 60 GHz. Malgré ses performances très impressionnantes, cette technologie n'est pas très accessible, puisque très peu d'endroits dans le monde sont en mesure de réaliser ce type d'interconnexions.

### 1.1.4 Conclusion liaison par fil

Pour conclure la revue sur la liaison par fil comme solution d’interconnexions large bande jusqu’à plus de 100 GHz, il semble qu’aucune des solutions proposées ne respecte les objectifs poursuivis pour plusieurs raisons. Les problèmes se situent autour de la complexité, les mauvaises performances large bande, ou du manque d’accessibilités des propositions présentées ci-haut. De plus, ces solutions risquent d’être très sensibles aux variations et ne pas être efficaces pour des productions de masse. Jusqu’à preuve du contraire, vu la date la plus récente de papier proposant une liaison par fil jusqu’à 100 GHz qui remonte en 2015, il est possible de conclure que ce sujet de recherche précis n’est plus d’actualité.

### 1.2 Puce retournée

La puce retournée (Flip-Chip), comme son nom l’indique, consiste en la connexion d’une puce retournée face vers le bas à un substrat ou une autre puce via des billes ou des structures cylindriques faites en matériaux conducteurs. C’est en 1961 que la compagnie IBM a inventé cette nouvelle technologie en raison du manque de technologie d’interconnexion existante permettant de satisfaire leurs besoins en termes de performances, de densité de signaux et de miniaturisation pour leurs systèmes informatiques hautes performances (Tong, Lai & Wong, 2013). Afin de réduire la lourdeur de cette section, voici plusieurs ouvrages de référence couvrant le portrait global de la technologie en présentant la vaste majorité des variantes existantes à ce jour (Heinrich, 2005) (Tong *et al.*, 2013) (Lau, 2017) (Heinrich *et al.*, 2021).

L’avantage de la puce retournée en comparaison avec la liaison par fil est que la transition se fait verticalement sur une très courte distance, et donc, l’inductance parasite qui dépend de la hauteur de la transition est beaucoup plus petit et ajustable en manipulant la taille des billes/cylindres. Il est cependant important de mentionner qu’une transition puce retournée a aussi une contribution capacitive importante qui se forme au niveau des pastilles. En fait, en opposition aux liaisons par fil, ce type d’interconnexion est, dans la quasi-totalité des cas, plus capacitif qu’inductif (Heinrich, 2005). De toute évidence, l’aspect capacitif doit être contrôlé minutieusement afin

d'avoir de bonne performance jusqu'à plus de 100 GHz. Plusieurs autres aspects importants à considérer sont présentés dans la littérature et résumés dans quelques papiers (Heinrich, 2005) (Heinrich *et al.*, 2021). Les points essentiels seront retranscrits dans le prochain paragraphe.

Tout d'abord, il existe un phénomène appelé l'effet de proximité qui peut se manifester sous la forme d'un changement dans l'environnement de propagation des lignes de transmission présentent à la surface d'une puce retournée en raison d'une trop grande proximité avec le substrat de réception. Ce changement dans l'environnement de propagation se traduit par une augmentation de la permittivité effective qui cause à la fois une modification de la longueur d'onde et de l'impédance caractéristique ( $Z_0$ ) par rapport au cas nominal attendu. Conséquemment, l'un des effets néfastes résultants est une augmentation de la réflexion aux interfaces. Ensuite, dans le cas de puces avec circuit actif comme les amplificateurs, ce phénomène affecte le gain en plus de dégrader les performances à haute fréquence (Ito, Maruhashi, Kusamitsu, Morishita & Ohata, 1999). Évidemment, ce phénomène dépend de plusieurs facteurs, soit les dimensions de la ligne de transmission, les constantes diélectriques relatives des substrats/diélectriques ainsi que la distance entre les deux entités. Parmi les solutions à ce problème, la première est de ne pas retourner la puce en utilisant des cylindres conducteurs verticaux spéciaux traversant le diélectrique d'une puce sur semiconducteur (TSV ou hot-via). Une autre est de minimiser les dimensions des lignes de transmission qui sont présentes à la surface de la puce. Ensuite, il est aussi possible de prendre en compte l'effet de proximité lors de la conception des lignes de surfaces de la puce. Finalement, une autre solution intéressante est de choisir une technologie de bille/cylindre offrant une hauteur flexible de manière à choisir l'élévation nécessaire. L'avantage particulier de cette dernière solution est le fait qu'elle ne nécessite pas de contrôle des dimensions de la puce, et donc, qu'elle est réalisable même lorsque la puce n'est pas conçue à l'interne. Il est aussi important de préciser que la proximité peu aussi affecter les lignes de surface du substrat de réception lors de chevauchement avec le diélectrique, mais cet aspect est généralement moins problématique en raison des courtes distances sur lequel l'effet se produit. Dans un autre ordre d'idée, un autre aspect important est la compatibilité des coefficients d'expansion thermique (CTE) entre les différentes puces et le substrat. Si ces derniers ont des écarts significatifs de

CTE, la dilatation thermique des entités n'est pas cohérente et le risque de fracture du système via un stress mécanique devient important lors de variation en température. Afin de réduire ce risque, il est important de vérifier la cohérence de ces constantes et, au besoin, sélectionner un matériel de remplissage («Underfill») à insérer entre les entités. Pour terminer, un aspect important nécessitant une attention particulière dans des transitions à plus de 100 GHz est la discontinuité qui se forme dans l'environnement de propagation. Cette discontinuité peut mener, entre autres, à l'excitation de mode de radiation, à l'excitation de modes d'ordres supérieurs dans le diélectrique/substrat guidé ou radiatif, ou encore à de la réflexion, et donc, des ondes stationnaires. De ce fait, il est important de considérer tous ces aspects lors d'une conception, et ce, en fonction de la fréquence maximale visée.

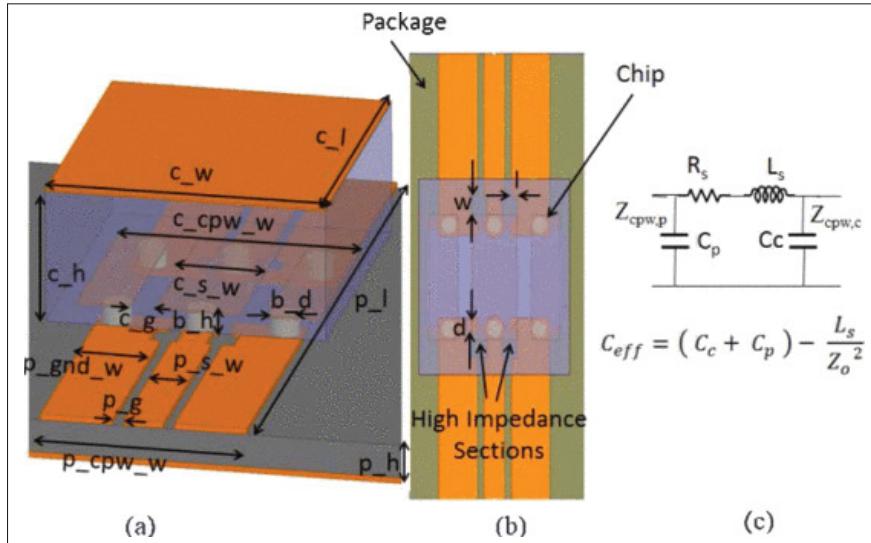

Les sous-sections suivantes serviront à présenter les solutions large bande jusqu'à plus de 100 GHz proposés dans la littérature. L'objectif est de vérifier si une solution respectant les critères poursuivis a été publiée. Ces études seront présentées selon le type de bille/cylindre utilisé, soit les billes de soudures, les billes d'or («Gold stud»), les piliers de cuivre («Copper pillar») et d'autres alternatives artisanales («In house»). Naturellement, les techniques de compensation et les règles de conceptions seront extraites lorsque fournies. De plus, les modèles équivalents simples de puce retournée publiés dans la littérature seront aussi présentés.

### 1.2.1 Billes de soudures

Les billes de soudures se définissent par l'utilisation d'un alliage avec un point de fusion plus petit que 450 °C. Ce type de bille est principalement utilisé pour de l'encapsulation puce retournée de type boîtier matriciel à billes (Ball grid array), une méthode permettant une grande densité d'interconnexions via le dessous d'une puce ou d'un substrat de boîtier. Pendant plusieurs décennies, les billes de soudures qui dominaient le marché de la puce retournée étaient le type C4 avec un alliage en SnAg. À ce jour, d'autres types de billes sont utilisés comme les microbilles en AuSn permettant d'atteindre de plus petites dimensions et une variante appelée le pilier de cuivre qui sera abordé un peu plus loin dans le texte. Pour des puces, cette technologie est

souvent utilisée conjointement avec des couches de redistribution (RDL) ou des interposeurs afin de rediriger les connexions.

Une étude démontre l'utilisation de bille de soudure de DC jusqu'à 100 GHz (Bessemoulin *et al.*, 2022). Ces billes sont utilisées sous forme de boîtier à billes (BGA) pour connecter une puce GaAs encapsulée pour montage en surface (CMS/SMT) sur un PCB, soit une interconnexion du deuxième niveau boîtier à PCB. Le montage expérimental complet inclus des «hot-via», des visas traversant le GaAs permettant de garder la puce face vers le haut et éviter l'effet de proximité. Les mesures incluent 2 transitions consécutives. Les pertes d'insertions incluant les pertes de lignes sont de près de -2.5 dB à 100 GHz et les pertes de retour sont meilleures qu'environ -10 dB sur toute la bande. Malheureusement, très peu de détails sont fournis sur la transition boîtier à billes (BGA), l'alliage et les dimensions de la bille ne sont pas fournis. Il serait donc très difficile pour un concepteur de reproduire le modèle.

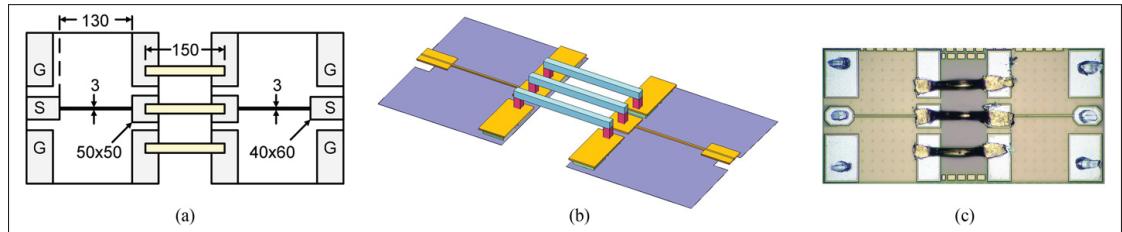

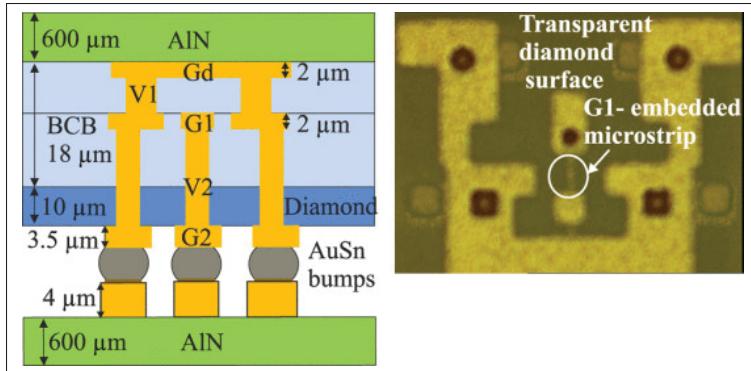

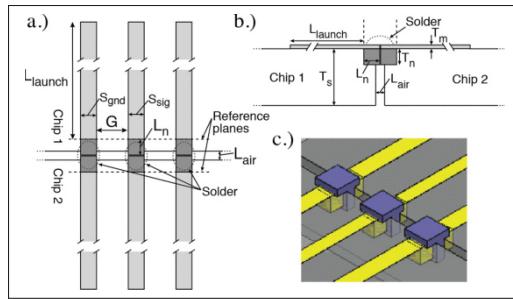

D'autre part, une équipe de chercheurs a présenté la meilleure transition puce retournée démontrée expérimentalement à ce jour avec de bonnes performances de DC à 500 GHz (Sinha *et al.*, 2017). L'interconnexion est de type puce à puce et permet de relier une puce en AlN à une puce en silicium. Les deux lignes de transmissions sont des guides d'ondes à ruban (stripline) fabriquées dans une couche intermédiaire de benzocyclobutene (BCB) présent sur le dessus des deux puces. La puce en AlN a quant à elle une fine couche de diamant supplémentaire pour la dissipation de chaleur des transistors. Les billes utilisées sont des microbilles en AuSn avec un diamètre de 10  $\mu\text{m}$  et une hauteur de 2  $\mu\text{m}$ . Une autre étude par les mêmes auteurs présente une transition très semblable de CPW vers guide d'onde à ruban jusqu'à 250 GHz (Monayakul *et al.*, 2015).

Figure 1.4 Exemple de puce retournée avec billes de soudure DC-250 GHz de CPW vers guide d'onde à ruban (stripline) (Monayakul *et al.*, 2015)