# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAITRISE EN GÉNIE ÉLECTRIQUE M Ing.

# PAR YASSINE SALIH ALJ

CONCEPTION D'UN SYSTÈME D'ACQUISITION GPS RAPIDE

MONTRÉAL, LE 15 DÉCEMBRE 2003

© droits réservés de Yassine Salih Alj

# CE MÉMOIRE A ÉTÉ ÉVALUÉ PAR UN JURY COMPOSÉ DE :

François Gagnon, directeur de mémoire Département de génie électrique à l'École de technologie supérieure

René Jr. Landry, codirecteur de Mémoire Département de génie électrique à l'École de technologie supérieure

Christian Gargour, président du jury Département de génie électrique à l'École de technologie supérieure

Jean-Claude Lanoue, jury externe CMC Électronique

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 12 DÉCEMBRE 2003

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### CONCEPTION D'UN SYSTÈME D'ACQUISITION GPS RAPIDE

#### Yassine Salih Ali

#### **SOMMAIRE**

Dans ce travail plusieurs techniques nouvelles pour le GPS ont été explorées et appliquées. La première est la technique de traitement par blocs qui est utilisée habituellement dans le domaine du traitement d'images. Cette méthode a été appliquée pour le traitement du signal GPS et a démontré des résultats encourageants. Elle est basée sur l'utilisation de FFT permettant de calculer la fonction de corrélation rapidement par une simple multiplication dans le domaine fréquentiel. L'architecture proposée sur la base de cette méthode a été retenue selon ses performances démontrées, et ce pour remplacer la structure actuelle du récepteur GPS.

Une autre méthode étudiée, consiste en l'application d'un algorithme complexe basé sur la transformée de Walsh Hadamard. Cette dernière permettrait d'accélérer 26 fois le calcul de la fonction corrélation, et ce par rapport à la transformée de Fourier rapide FFT. Malheureusement, cette transformée n'est pas directement applicable aux séquences de Gold utilisées en GPS. Ainsi cette technique n'a pas été retenue pour cette application.

La troisième technique utilisée est une méthode de conception connue dans le domaine de la microélectronique, à savoir la structure systolique. Ce nouveau mécanisme parallélisé a été appliqué et testé pour l'acquisition du signal GPS. En terme de rapidité et de complexité, cette technique est fort avantageuse. Le système d'acquisition proposé qui est à la base de sa conception et de son mécanisme de fonctionnement se distingue par son architecture simple et compacte, une vitesse de traitement de l'ordre de 1 ms et des performances d'estimation remarquables. Donc, cette méthode a été considérée comme étant la meilleure solution pour remplacer la structure du récepteur GPS actuel.

Finalement, l'évaluation de la complexité des deux architectures retenues a confirmé l'efficacité de la nouvelle architecture proposée, basée sur le mécanisme systolique. Sa complexité pour une implémentation directe, ne consomme pas plus de 54 % des ressources d'une puce Virtex-II Pro XC2VP125. Cette complexité peut être réduite permettant ainsi l'utilisation de puces de plus petite taille telle que la Virtex-II Pro XC2VP7, et ce au prix de l'utilisation d'une horloge plus rapide. Ceci est réalisable en effectuant un traitement par blocs qui permettra d'emmagasiner les bits entrants dans des tampons pour pouvoir alimenter ensuite un nombre réduit de cellules dans le corrélateur systolique. Pour un réseau avec un nombre de cellules réduit à 100, l'horloge utilisée doit être dix fois plus rapide. Ceci permet de conserver le même temps de réponse du

système d'acquisition, mais avec une complexité dix fois plus petite en terme de "slices". Dans ce cas, une puce aussi petite que la Virtex-II Pro XC2VP4 pourrait suffire, et ce avec une exploitation de moins de 4.76 % de ses ressources de mémoires RAM. La méthode proposée a permis d'améliorer davantage les performances du récepteur GPS qui y est issu, et ce en terme de vitesse de traitement, de qualité des estimations et de flexibilité d'implémentation. L'architecture qui découle de la première technique basée sur l'utilisation des FFT, nécessite une plus grande surface de silicium, et exige ainsi d'utiliser plus d'une puce programmable FPGA pour l'implémentation complète du système d'acquisition.

#### **DESIGN OF A GPS FAST ACQUISITION SYSTEM**

#### Yassine Salih Ali

#### **ABSTRACT**

In this work, several new techniques for GPS were studied and simulated. The first one was block-processing technique that is usually used for image processing. This method was applied for the GPS signal processing and has shown interesting results. By using the Fast Fourier Transform (FFT), the calculation of the correlation function is implemented with simple multiplications in the frequency domain, which allows to considerably speed up the computation time. Based on this approach, an architecture for such a system is proposed and simulated. The results are clearly satisfactory and the proposed architecture is believed to be able to replace the current structure of receiver GPS.

Another technique, which is based on Walsh Hadamard transform, is presented. The simulation results show that it is possible to accelerate the calculation of the correlation function 26 times compared to the Fast Fourier Transform (FFT). Unfortunately, this technique is not directly applicable to Gold sequences used in GPS systems; and for this reason, it is not retained.

A new system architecture is presented. It is based on a structure that is used in microelectronics, namely the systolic structure. This new paralleled mechanism was applied and tested for the acquisition of GPS signal. In terms of speed and complexity, this technique is extremely advantageous. The proposed acquisition system is characterized by its simple and compact architecture, a processing speed of about 1 ms and similar performances of estimation. Therefore, this method was regarded as being the best solution to replace the structure of current GPS receivers.

In addition to the analysis of the performances, an evaluation of the complexity of the two selected architectures has been carried out. The results clearly demonstrate the superiority of the systolic architecture. Indeed, its complexity for a direct implementation, does not consume more than 54 % of the resources of a Virtex-II Pro XC2VP125 and it becomes possible to implement the system in a smaller chip such as Virtex-II Pro XC2VP7, with a faster clock. This is realizable by carrying out a treatment per blocks, which will allow storing the bits entering in buffers and then feeding a reduced number of cells in the systolic correlator. For a network having one hundred (100) cells, the clock used must be ten times faster. This will allow preserving the same response time of the acquisition system, but with a complexity ten times smaller in terms of slices. In this case, a chip as small as a Virtex-II Pro XC2VP4 can be enough to

implement the whole system with an exploitation of less than 4.76 % of the RAM resources. Thus, by using this proposed technique, it becomes possible to improve the performance of GPS receivers in terms of processing speed, quality of the estimation and flexibility of implementation. For the first technique based on the FFT, it requires a larger silicon area and necessitates more than one FPGA chip for a complete implementation of the acquisition process.

#### REMERCIEMENTS

#### Monsieur François Gagnon

Votre esprit de rigueur professionnelle remarquable lors de votre encadrement vigilant n'a rien à envier à votre constante chaleur humaine. Vos conseils et votre soutien tout au long de ce travail m'ont été si précieux. Votre suivi exemplaire et votre apport au bon moment des moyens suffisants, à la fois matériels et moraux, m'ont facilité la tâche, et seront pour moi inoubliables. Je n'ai pas de mots pour vous remercier comme il se doit de votre assistance. Veuillez croire en toute ma gratitude.

#### Monsieur René Jr. Landry

Je vous exprime ma grande gratitude non seulement pour avoir accepté de codiriger ce travail, mais aussi pour votre généreuse disponibilité exprimant votre intérêt pour le bon déroulement de ce travail. Je vous en remercie vivement.

#### Messieurs les membres du jury

Je vous remercie pour l'intérêt que vous avez voulu porter à ce travail en acceptant de l'évaluer. Veuillez croire en mon profond respect.

## TABLE DES MATIÈRES

|         |                                                  | Page |

|---------|--------------------------------------------------|------|

| SOMMA   | AIRE                                             | i    |

| ABSTR.  | ACT                                              | iv   |

| REMER   | CIEMENTS                                         | V    |

| TABLE   | DES MATIÈRES                                     | vi   |

| LISTE I | DES FIGURES                                      | ix   |

| LISTE I | DES ABRÉVIATIONS ET LEXIQUE                      | X    |

| INTROI  | DUCTION                                          | 1    |

| CHAPIT  | TRE 1 SYSTÈME DE POSITIONNEMENT GPS              | 6    |

| 1.1     | Étalement spectral et CDMA                       | 6    |

| 1.2     | Présentation du GPS                              |      |

| 1.2.1   | Séquences de Gold                                |      |

| 1.2.2   | Code C/A                                         |      |

| 1.2.3   | Structure du signal GPS                          |      |

| 1.3     | Traitement du signal GPS                         |      |

| 1.4     | Architecture du récepteur GPS                    |      |

| 1.4.1   | Section RF                                       |      |

| 1.4.2   | Boucles de poursuite                             | 18   |

| 1.4.3   | Phase d'acquisition                              |      |

| 1.5     | Principe de base du corrélateur                  | 22   |

| CHAPIT  | TRE 2 TECHNIQUES D'ACQUISITION                   | 24   |

| 2.1     | Stratégies classiques d'acquisition              | 24   |

| 2.1.1   | Région d'incertitude de l'acquisition            |      |

| 2.1.2   | Algorithmes de recherche                         |      |

| 2.2     | Description détaillée du processus d'acquisition |      |

| 2.2.1   | Architecture d'un module d'acquisition           |      |

| 222     | Processus de recherche                           | 22   |

| CHAPITI                                                     | RE 3                         | TECHNIQUE DE TRAITEMENT PAR BLOCS                | 38  |  |

|-------------------------------------------------------------|------------------------------|--------------------------------------------------|-----|--|

| 3.1<br>3.2                                                  | Présentation de la technique |                                                  |     |  |

| 3.3                                                         |                              | ure du signal                                    |     |  |

| 3.4                                                         |                              | lateur GPS rapide à base de FFT                  |     |  |

| 3.5                                                         | Archi                        | tecture du récepteur GPS rapide                  | 45  |  |

| CHAPIT                                                      | RE 4                         | UTILISATION DE LA TRANSFORMÉE DE WALSH           | 49  |  |

| 4.1                                                         | Séque                        | ences PN et transformée de Walsh                 | 49  |  |

| 4.2                                                         | _                            | ithme de convolution                             |     |  |

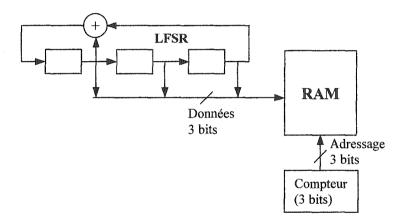

| 4.3                                                         |                              | mentation matérielle                             |     |  |

| 4.3.1                                                       |                              | rateurs de permutations                          |     |  |

| 4.3.2                                                       |                              | formée de Walsh                                  |     |  |

| 4.4                                                         |                              | paraison de Walsh à la FFT                       |     |  |

| 4.5                                                         | Walsh                        | n en GPS                                         | 59  |  |

| CHAPIT                                                      | RE 5                         | UTILISATION DE LA MÉTHODE D'ÉCHANTILLONNAGE      | 60  |  |

| 5.1                                                         | Prése                        | ntation de la méthode                            | 60  |  |

| 5.2                                                         | Insert                       | ion du zéro à la séquence de 1023 points         | 63  |  |

| 5.3                                                         | Échar                        | ntillonnage à 1024 points                        | 64  |  |

| 5.4                                                         | Archi                        | tecture proposée                                 | 65  |  |

| 5.4.1                                                       | Détec                        | teur du pic                                      | 67  |  |

| 5.4.2                                                       | Estim                        | ateur de la phase de fréquence                   | 69  |  |

| 5.5                                                         | Discu                        | ssion des performances et résultats              | 72  |  |

| CHAPITRE 6 ACQUISITION À BASE DE CORRÉLATEURS SYSTOLIQUES75 |                              |                                                  |     |  |

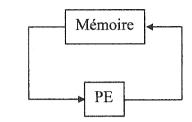

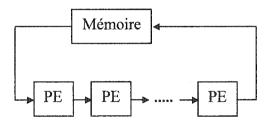

| 6.1                                                         | Princi                       | pe d'une architecture systolique                 | 75  |  |

| 6.2                                                         |                              | tecture proposée du corrélateur systolique       |     |  |

| 6.3                                                         |                              | ssion des performances et résultats              |     |  |

| CHAPIT                                                      | RE 7                         | ARCHITECTURES RETENUES                           | 90  |  |

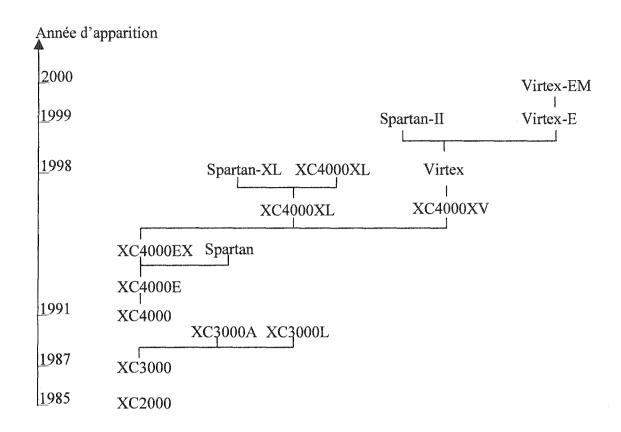

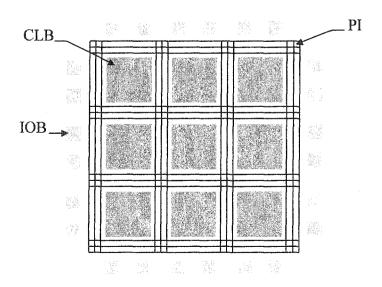

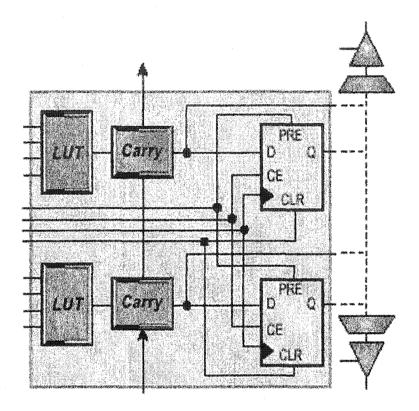

| 7.1                                                         | Anero                        | eu des puces programmables FPGA de Xilinx        | 90  |  |

| 7.2                                                         | Analy                        | se de complexité et validation des architectures | 94  |  |

| 7.2.1                                                       |                              | tecture du corrélateur GPS systolique            |     |  |

| 7.2.2                                                       |                              | tecture du corrélateur rapide à base de FFT      |     |  |

|                                                             |                              | GÉNÉRALE                                         |     |  |

|                                                             |                              |                                                  |     |  |

| RIBLIO(                                                     | FRAPE                        | HF 1                                             | 103 |  |

#### LISTE DES FIGURES

|           |                                                                    | Page |

|-----------|--------------------------------------------------------------------|------|

| Figure 1  | Exemple d'étalement spectral par séquence directe DSSS             |      |

| Figure 2  | Constellation du système GPS                                       | 8    |

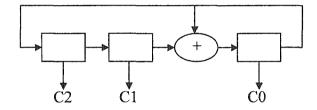

| Figure 3  | Générateur de code de Gold de longueur N = 31                      | 9    |

| Figure 4  | Générateur de code C/A                                             | 10   |

| Figure 5  | Illustration du déphasage entre les signaux civil et militaire     | 11   |

| Figure 6  | Fonction d'auto-corrélation normalisée du code C/A                 | 12   |

| Figure 7  | Spectre fréquentiel du signal GPS                                  | 13   |

| Figure 8  | Structure simplifiée du modulateur du signal L1                    | 14   |

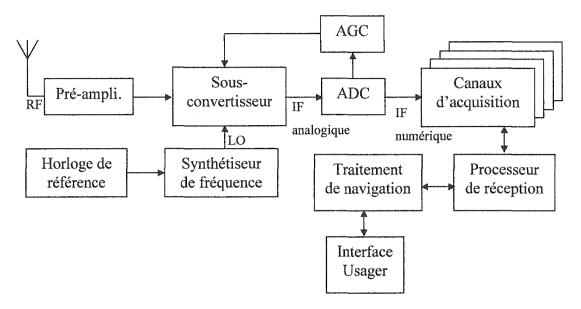

| Figure 9  | Schéma bloc d'un récepteur générique GPS                           | 17   |

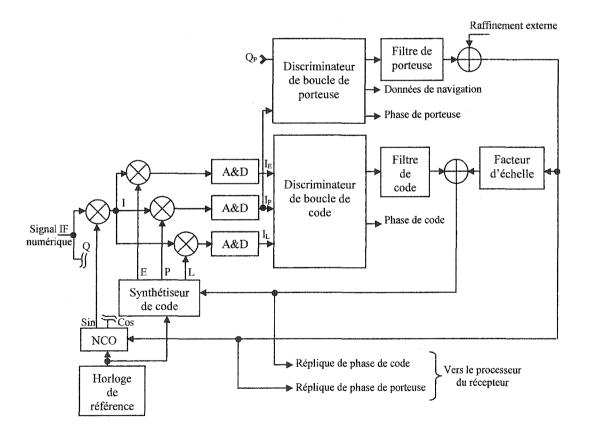

| Figure 10 | Schéma bloc d'un canal de poursuite générique GPS                  | 19   |

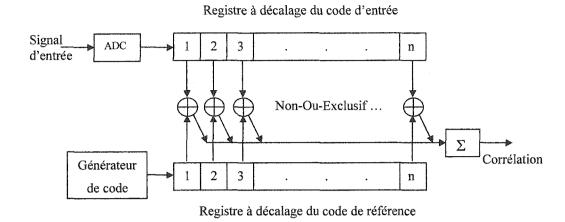

| Figure 11 | Structure d'un corrélateur à base de registres à décalage          | 23   |

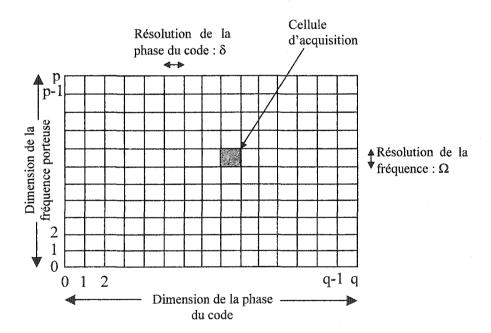

| Figure 12 | Espace de recherche pour l'acquisition du signal GPS               | 25   |

| Figure 13 | Structure des stratégies de recherche séquentielle d'énergie       | 26   |

| Figure 14 | Schéma bloc du système d'acquisition d'un code d'étalement         | 27   |

| Figure 15 | Fonctionnement de la Recherche en Double Périodes                  | 29   |

| Figure 16 | Configuration d'acquisition d'un canal de récepteur GPS            | 31   |

| Figure 17 | Région d'incertitude de la phase du code et du décalage Doppler    | 34   |

| Figure 18 | Recherche de phase de code par décalage de la séquence de code     | 34   |

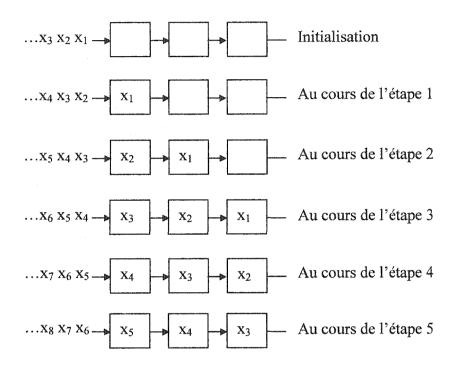

| Figure 19 | Illustration du traitement par blocs pour cinq échantillons / bloc | 39   |

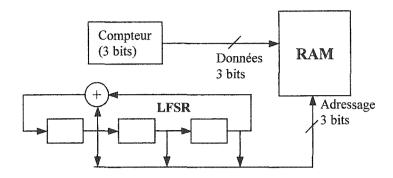

| Figure 20 | Système de collecte de données GPS-SPS                             | 40   |

| Figure 21 | Traitement par blocs                                               | 42   |

| Figure 22 | Schéma bloc d'un corrélateur GPS rapide                            | 44   |

| Figure 23 | Schéma bloc du système d'acquisition GPS                           | 45   |

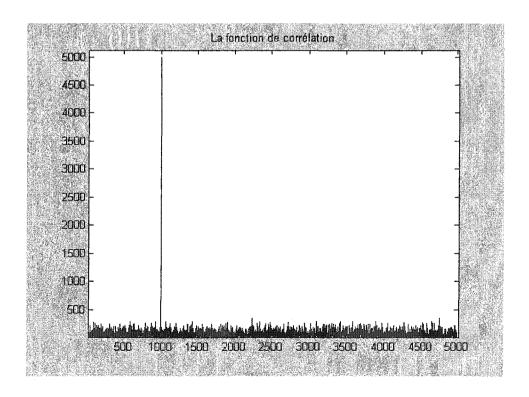

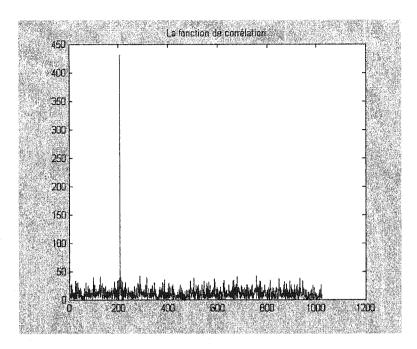

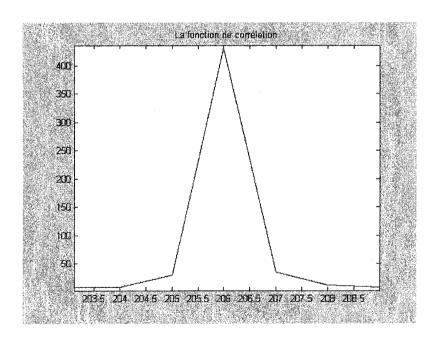

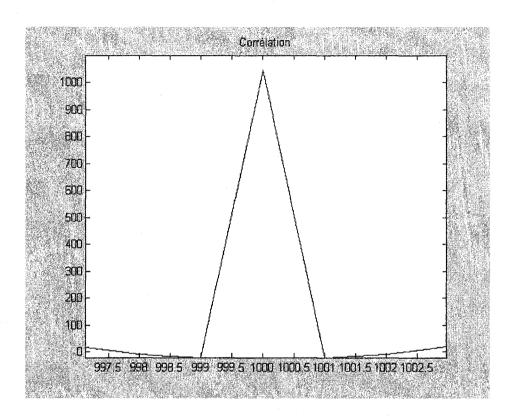

| Figure 24 | Résultat de corrélation rapide d'un signal GPS                     | 46   |

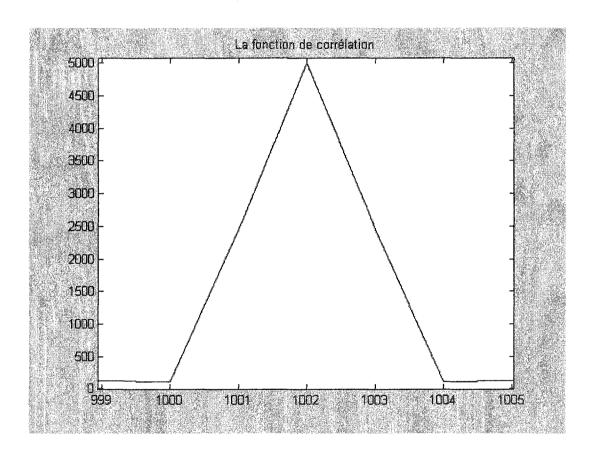

| Figure 25 | Forme triangulaire du pic de corrélation                         | 47 |

|-----------|------------------------------------------------------------------|----|

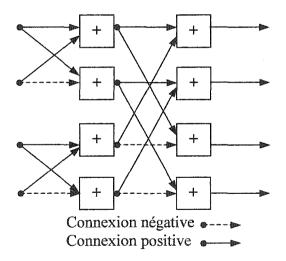

| Figure 26 | Illustration de l'algorithme de convolution basé sur WT          | 51 |

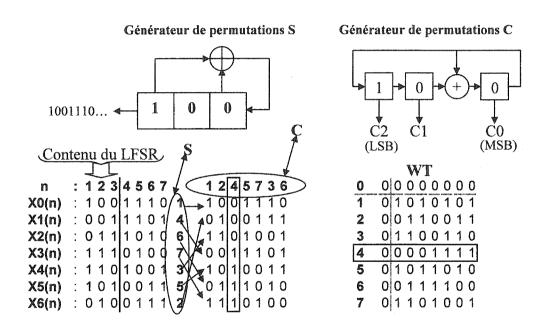

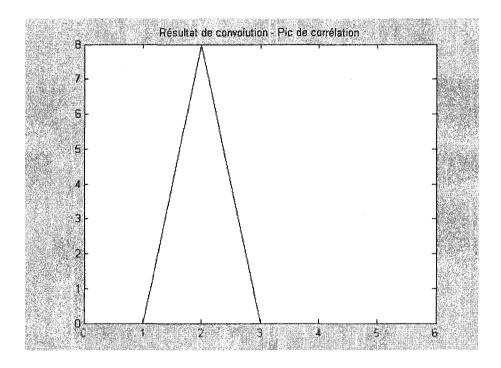

| Figure 27 | Corrélation rapide basée sur la transformée de Walsh             | 53 |

| Figure 28 | Implémentation d'un générateur de permutations S                 | 55 |

| Figure 29 | Implémentation d'un générateur de permutations S <sup>-1</sup>   | 56 |

| Figure 30 | Implémentation d'un générateur de permutations C                 | 56 |

| Figure 31 | Papillon de Walsh de 4 points                                    | 57 |

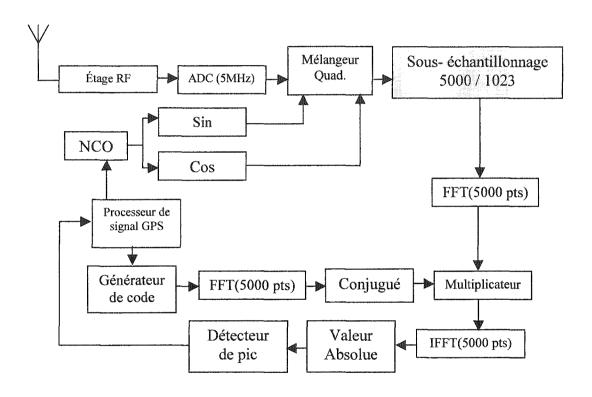

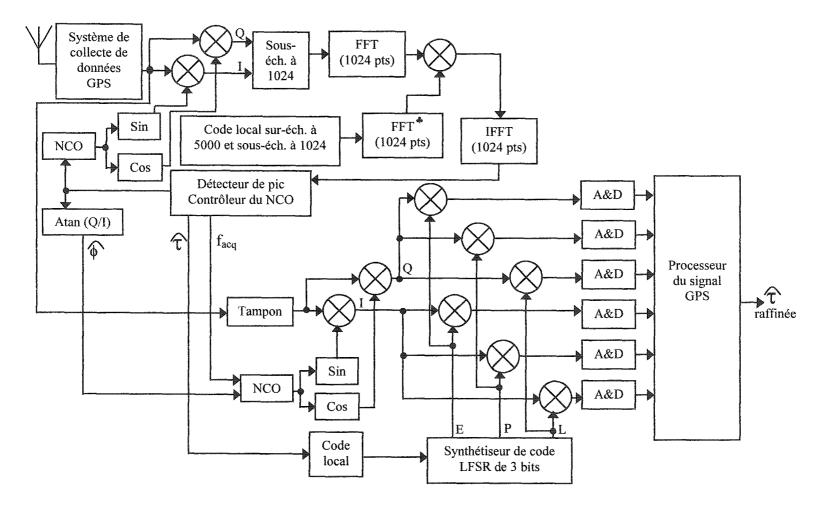

| Figure 32 | Schéma bloc du système d'acquisition                             | 61 |

| Figure 33 | Schéma bloc du récepteur GPS rapide                              | 66 |

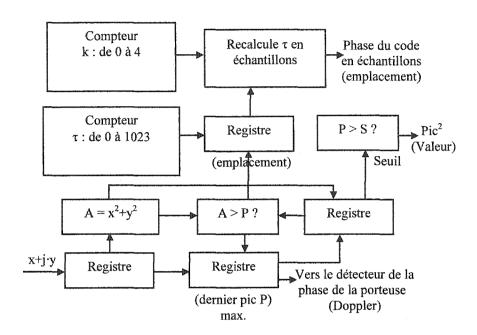

| Figure 34 | Diagramme de fonctionnement du détecteur de pic                  | 68 |

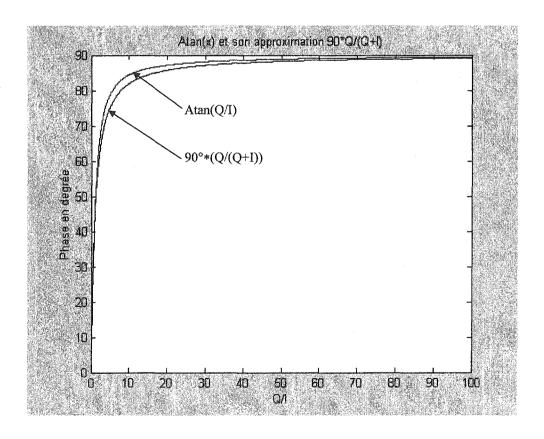

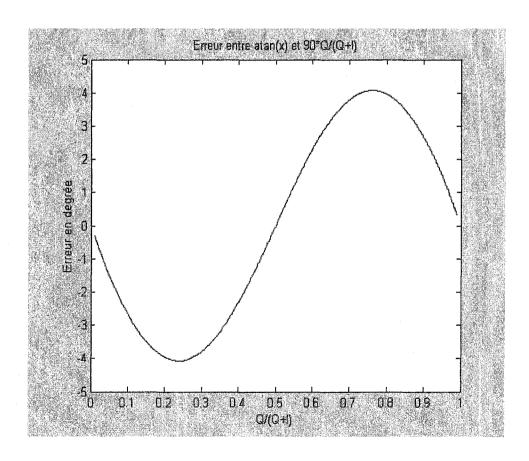

| Figure 35 | La fonction ATAN et son approximation                            | 70 |

| Figure 36 | Erreur d'approximation de la fonction ATAN(Q/I)                  | 71 |

| Figure 37 | Résultat de la corrélation rapide du signal GPS                  | 73 |

| Figure 38 | Illustration du mécanisme de systolisation                       | 76 |

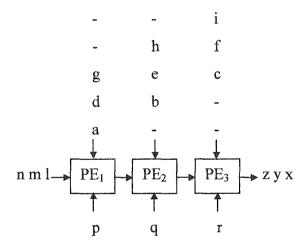

| Figure 39 | Évolution des données dans un réseau systolique                  | 77 |

| Figure 40 | Exemple d'utilisation du mécanisme systolique                    | 78 |

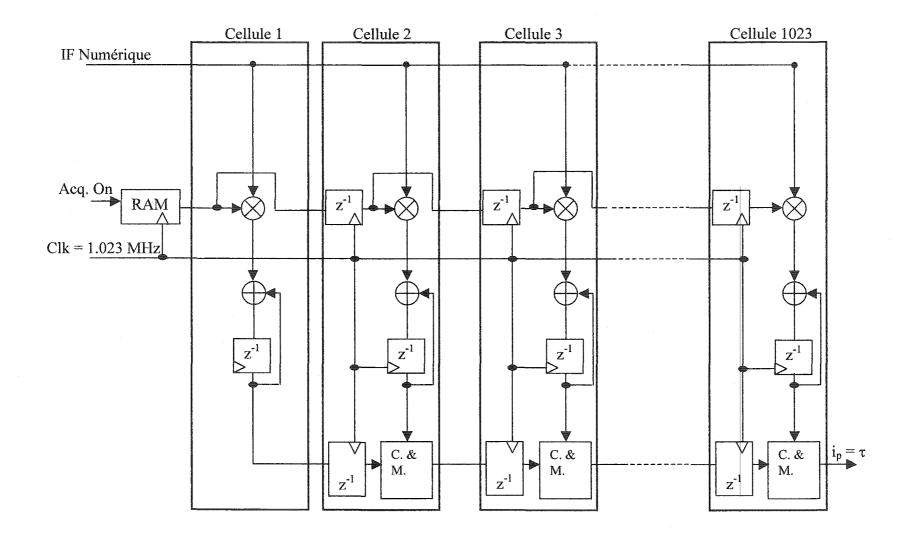

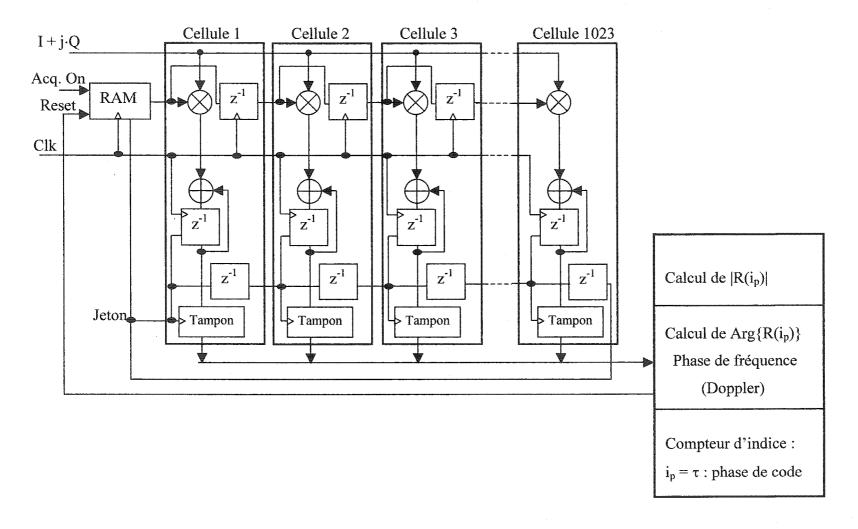

| Figure 41 | Architecture du corrélateur de code systolique                   | 80 |

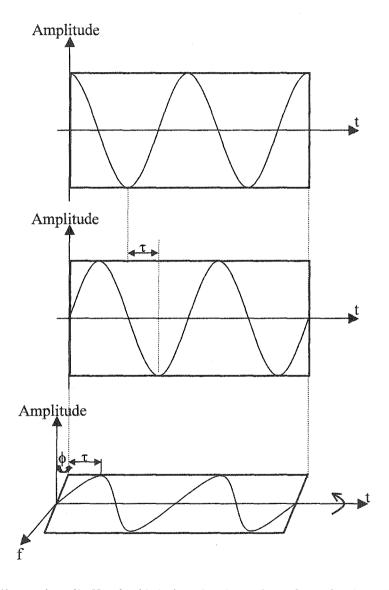

| Figure 42 | Illustration d'effet de déviation de phase de code               |    |

|           | et de phase Doppler                                              | 82 |

| Figure 43 | Illustration de l'architecture proposée du corrélateur           |    |

|           | GPS systolique avec son module de calcul                         | 84 |

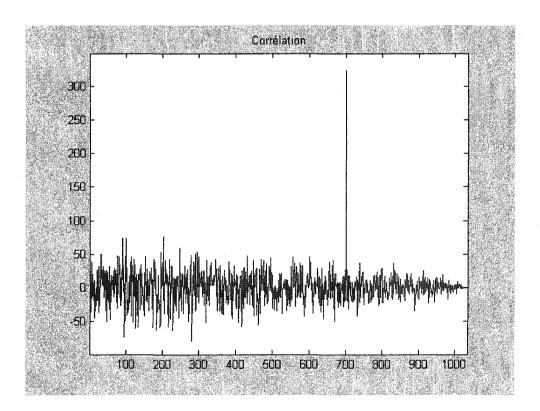

| Figure 44 | Résultat de corrélation obtenu pour un décalage de 700 chips     | 86 |

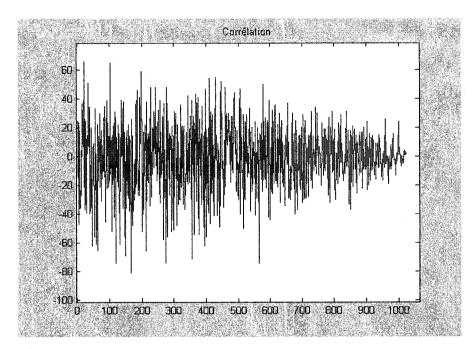

| Figure 45 | Résultat de corrélation obtenu pour un décalage de 1000 chips    | 88 |

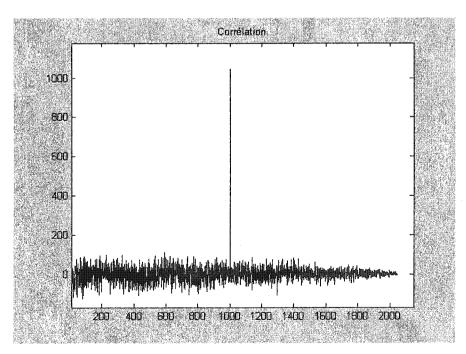

| Figure 46 | Forme triangulaire du pic de corrélation autour de l'indice 1000 | 89 |

| Figure 47 | Arbre généalogique des séries de générations de FPGA de Xilinx   | 91 |

| Figure 48 | Structure globale d'une puce FPGA                                | 91 |

| Figure 49 | Structure simplifiée d'une "slice"                               | 93 |

### LISTE DES ABRÉVIATIONS ET LEXIQUE

ADC Convertisseur analogique/numérique (Analog/Digital)

A&D Accumulation et blocage (Accumulate-and-Dump)

AGC Contrôle automatique de gain (Automatic Gain Control)

BPSK Modulation binaire par décalage de phase (Binary Phase Shift Keying)

C/A Code PRN du signal GPS de cadence 1.023 MHz (Coarse/Acquisition)

C&M Comparaison et Mémorisation permettant de garder l'indice de la

meilleure valeur comparée

CDMA Accès multiple par division de code (Code Division Multiple Access)

Chip Un signal qui peut être 0 ou 1 et qui pour le GPS est d'une durée de 997ns

constituant un code PRN

CLB Blocs d'éléments logiques configurables (Configurable Logic Blocks)

CORDIC Un algorithme de rotation (COrdinate Rotation DIgital Computer)

dB Décibel

DFT Transformée discrète de Fourier (Discrete Fourier Transform)

DLL Boucle à verrouillage de délais (Delay Lock Loop)

DSP Processeur de signaux numériques (Digital Signal Processing)

DSSS Étalement spectral par séquence directe (Direct Sequence Spread

Spectrum)

E/P/L Avance, phase et retard (Early / Prompt / Late)

FLL Boucle à verrouillage de fréquence (Frequency Lock Loop)

FFT Transformée rapide de Fourier (Fast Fourier Transform)

FPB Filtre Passe Bande

FPGA Puce de portes programmables (Field Programmable Gate Array)

GPS Système de positionnement par satellites (Global Positioning System)

HOW Message GPS de transfert (Hand-Over Word)

Hz Hertz

| En phase et en quadrature de phase (In-phase/Quadra-phase)             |  |

|------------------------------------------------------------------------|--|

| Fréquence intermédiaire (Intermediary Frequency)                       |  |

| Module de mesure inertielle (Inertial Measure Unit)                    |  |

| Blocs d'entrées/sorties d'une matrice FPGA (Input/Output Blocks)       |  |

| Fréquence porteuse égale à 1575.42 MHz                                 |  |

| Fréquence porteuse égale à 1227.60 MHz                                 |  |

| Registre à décalage avec rétroaction linéaire (Linear Feedback Shift   |  |

| Register)                                                              |  |

| Oscillateur local (Local Oscillator)                                   |  |

| Bit du poids faible (Least Significant Bit)                            |  |

| Elément de mémoire de FPGA (Look UP Tables)                            |  |

| Séquence à longueur maximale (Maximal Length Sequence)                 |  |

| Bit du poids fort (Most Significant Bit)                               |  |

| Oscillateur contrôlé numériquement (Numerically Controlled Oscillator) |  |

| Rapport bruit à signal (Noise to Signal Ratio)                         |  |

| Code PRN du signal GPS militaire de cadence 10.23 MHz (Precise)        |  |

| Cellule ou élément de traitement (Processing Element)                  |  |

| Blocs de connexions programmables (Programmable Interconnect)          |  |

| Circuit logique et programmable (Programmable Logic Device)            |  |

| Boucle à verrouillage de phase (Phase Lock Loop)                       |  |

| Service de positionnement précis (Precise Positioning Service)         |  |

| Bruit pseudo-aléatoire (Pseudo Random Noise)                           |  |

| Modulation par décalage de phase (Phase Shift Keying)                  |  |

| Mémoire à accès aléatoire (Random Access Memory)                       |  |

| Fréquence radio (Radio Frequency)                                      |  |

| Rapport signal à bruit (Signal to Noise Ratio)                         |  |

| Service de positionnement standard (Standard Positioning Service)      |  |

| Véhicule spatial (Space Vehicule)                                      |  |

|                                                                        |  |

Temps d'arrivée (Time Of Arrival)

TOA

#### INTRODUCTION

Le positionnement ou capacité de se localiser dans notre monde, a toujours jouit d'une importance cruciale et exceptionnelle. Depuis les premiers temps, les marins avaient forgé leurs propres moyens pour se localiser en utilisant les objets célestes afin de pouvoir naviguer sans se perdre.

Aujourd'hui, les systèmes GPS ("Global Positioning System") offrent des précisions centimétriques et sont largement utilisés pour la navigation, les communications sans fils et pour d'autres applications. Ces systèmes sont basés sur des satellites qui orbitent autour de la terre, et qui envoient des signaux RF aux récepteurs GPS. Ces derniers permettent à l'engin qui les porte de se localiser où qu'il soit, sur la surface de la terre, sous l'eau ou dans l'espace. Ceci est effectué en déterminant les coordonnées spatiales (x, y, z) du récepteur à partir du temps nécessité pour la propagation du signal GPS des satellites en vue, et ce à partir de leurs orbites dans l'espace.

#### Problématique

Le monde où nous vivons aujourd'hui est assujetti à un rythme d'évolution très élevé. Ainsi les changements doivent aussi s'y faire avec rapidité et efficacité afin de suivre la cadence du progrès exigé et répondre aux besoins dynamiques en matière de technologie de pointe. Le GPS est devenu très sollicité, voire indispensable dans plusieurs applications de notre 21 ème siècle. Cependant l'architecture actuelle des récepteurs GPS utilisés aujourd'hui est devenue un véritable obstacle devant les exigences de rapidité des nouvelles applications technologiques.

Les récepteurs GPS de nos jours sont basés sur les techniques de traitement séquentiel effectuant une saisie des échantillons un à la fois. Ce qui a un effet direct sur la qualité

de traitement de ce signal. Aussi, les éléments de base utilisés dans l'architecture de ces récepteurs standards, à savoir les boucles d'accrochage de phase PLL ("Phase Locked Loop"), de fréquence FLL ("Frequency Locked Loop") et de délai DLL ("Delay Locked Loop"), ont été utilisées pour des décennies. Ces boucles représentent un inconvénient majeur pour réduire le temps nécessaire au traitement du signal GPS reçu, car le signal traité reste parfois confiné dans ces boucles de poursuite. À titre d'exemple, en cas de décrochage de boucle le récepteur se voit dans l'obligation de recommencer à nouveau le processus d'acquisition, ce qui peut consommer inutilement le temps de traitement du signal GPS reçu et engendrer un temps de réponse de ce récepteur relativement long. Ainsi, ces récepteurs GPS standards ne représentent sans doute pas des solutions optimales en particulier pour les applications de haute vitesse dynamique ou en présence de problèmes de réflexions par trajet multiple ou d'interférences. D'autre part, le traitement du signal GPS à la réception se fait dans le domaine temporel. Or le calcul de la fonction de corrélation dans ce domaine est un processus qui consomme énormément du temps de traitement [Braasch99]. Ce qui n'est pas encore la manière optimale pour effectuer ce traitement, et ce dans l'objectif de réduire ce temps de réponse du récepteur GPS.

#### **Objectif**

Les nouvelles tendances de conception des récepteurs GPS se dirigent vers l'exploitation de nouvelles techniques pour le traitement du signal GPS. Ceci est effectué dans le but d'accélérer le processus d'acquisition en conservant les performances dans les conditions difficiles, et ce tout en optimisant l'architecture de ce récepteur GPS.

Au cours des dernières années, de nouvelles méthodes de traitement du signal GPS à la réception, ont été introduites. La technique de traitement par blocs, habituellement utilisée dans le traitement d'images, a été présentée pour le traitement du signal GPS. Celle-ci a permis de faire un grand saut par rapport au techniques standards utilisées

dans ce domaine. Le signal GPS reçu est traité par blocs d'échantillons permettant ainsi d'obtenir de meilleurs performances dans les conditions difficiles [Moeglein98]. Cette technique est basée sur le calcul de la fonction de corrélation dans le domaine fréquentiel, et ce en utilisant des transformées de Fourier discrètes DFT. Notons que le calcul de la fonction de corrélation de deux séquences de longueur de N, et ce en utilisant une simple multiplication dans le domaine fréquentiel, permet de réduire les calculs de N/logN fois, permettant ainsi d'accélérer significativement le processus d'acquisition et de faciliter l'acquisition en temps réel du signal GPS [VanNee91].

Le travail présenté ici a comme objectif d'explorer ces nouvelles techniques et de découvrir d'autres méthodes pouvant améliorer davantage le processus d'acquisition du signal GPS. Une des méthodes étudiées, consiste en l'application d'un algorithme basé sur la transformée de Walsh, et ce en concurrence avec l'utilisation de la transformée de Fourier rapide FFT. Aussi, un des buts principaux de ce travail est de trouver une structure parallélisée du corrélateur GPS permettant d'optimiser l'architecture du système d'acquisition ainsi que son fonctionnement. Ceci a été effectué en explorant les techniques utilisées pour la conception des architectures complexes des microprocesseurs. Ces derniers sont basés sur un mécanisme de fonctionnement systolique. Un réseau systolique est caractérisé par une architecture parallèle composée de cellules identiques, simples et interconnectées d'une façon régulière et locale. Les cellules évoluent en parallèle et sont cadencées par une horloge globale faisant en sorte que les calculs soient effectués simultanément. La régularité ainsi que la localité dont jouit ces réseaux les rendent particulièrement bien adaptés à être intégrés sur silicium.

Enfin, l'étude des nouvelles architectures proposées pour le système d'acquisition GPS devra inclure une évaluation de la complexité de celles-ci, et ce dans le but d'une implémentation sur une puce programmable FPGA. Ces puces sont connues pour leurs grande capacité d'intégration, de reconfigurabilité, et surtout par leurs fréquences d'opération élevées permettant ainsi une très grande vitesse de traitement.

#### Structure du mémoire

Ce mémoire est composé de sept chapitres. Le premier chapitre donne un aperçu sur les caractéristiques pertinentes du signal GPS en introduisant la technologie CDMA. Ensuite le code de Gold utilisé en GPS est présenté, suivi par les détails de ce code utilisé pour les applications civiles. Enfin la structure du signal GPS et son traitement à la réception sont discutés. L'architecture globale du récepteur est par la suite présentée, et ce à travers ses différents blocs constituants : l'étage RF, les boucles de poursuite de code et de la porteuse ainsi que le processus d'acquisition. Enfin, le principe de base du fonctionnement du corrélateur est discuté.

Dans le deuxième chapitre, les techniques d'acquisition et les processus de recherche utilisés pour les récepteurs séquentiels standards sont discutés en détail.

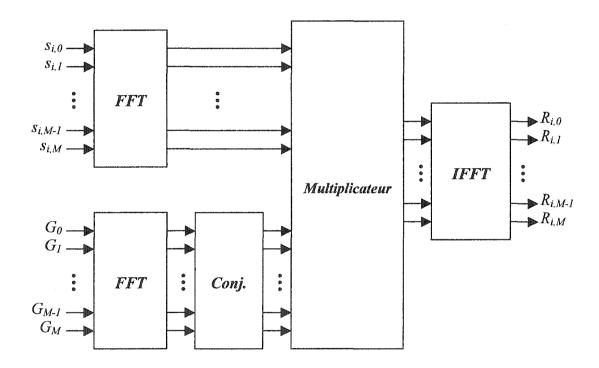

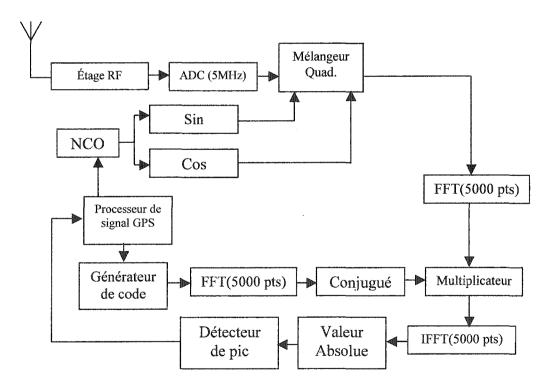

Le chapitre 3 explore la technique de traitement par blocs pour son utilisation en acquisition GPS. Les composants essentiels pour une structure du récepteur basé sur cette méthode seront étudiés. Finalement, une architecture à base de cette technique, faisant appel à l'usage des transformées de Fourier rapide FFT, sera présentée et simulée.

Le quatrième chapitre introduit une autre transformée à explorer, la transformée de Walsh. Son application à travers un algorithme complexe permettant de manipuler des séquences pour en déduire le déphasage est documentée et explicitée avec un exemple appuyé par son résultat de simulation. Les blocs nécessaires pour une conception basée sur cette technique seront ensuite étudiés. Et enfin, une mise en valeur des avantages de cette transformée par rapport à celle de la FFT sera présentée, suivie par les perspectives d'applicabilité de cette transformée de Walsh rapide pour l'acquisition du signal GPS.

Le chapitre 5 présente une méthode d'échantillonnage permettant d'améliorer l'architecture déjà présentée au chapitre 3. Nous y présenterons les solutions pertinentes essayées, et ce pour adapter cette méthode à la conception du corrélateur GPS rapide optimal tout en conservant ses performances. Enfin une solution sera retenue et une architecture finale sera proposée et commentée avec ses blocs importants. Nous conclurons finalement par une discussion des performances et résultats obtenus par simulations de cette architecture.

Le chapitre 6 présente une méthode originale pour la conception d'un système d'acquisition basé sur un corrélateur GPS rapide. Celui-ci est régit par le fonctionnement parallélisé du mécanisme systolique. Une architecture compacte du système d'acquisition basé sur ce corrélateur systolique sera proposée. Et enfin, les résultats de simulations ainsi que les performances de cette architecture seront présentés.

Dans le dernier chapitre l'étude de la complexité des architectures retenues sera réalisée. Le chapitre 7 commence par un bref aperçu sur les puces FPGA de Xilinx. Ceci est suivi par une analyse de complexité et une validation des architectures retenues. Suite à cette étude, une architecture se démarque des autres et est validée pour son implémentation.

Finalement, les chapitres sont suivis d'une conclusion générale avec quelques recommandations et perspectives de développement.

#### Contribution

Le travail présenté dans ce mémoire a contribué à l'amélioration du processus d'acquisition du signal GPS, et ce en explorant de nouvelles techniques et en concevant de meilleures architectures. Ces techniques utilisées pourraient même permettre la suppression totale des boucles de poursuites tout en accélérant le traitement et optimisant davantage la structure des architectures obtenues. L'architecture systolique

proposée pour la conception de ce système d'acquisition est nouvelle dans le domaine du GPS. En effet celle-ci a permis une nette amélioration par rapport à n'importe quelle autre structure connue des récepteurs GPS.

#### **CHAPITRE 1**

#### SYSTÈME DE POSITIONNEMENT GPS

#### 1.1 Étalement spectral et CDMA

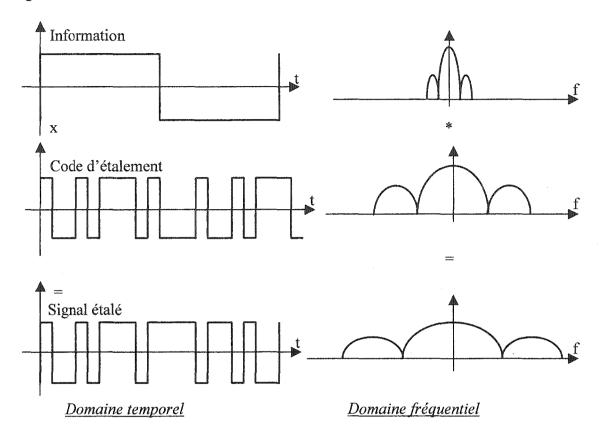

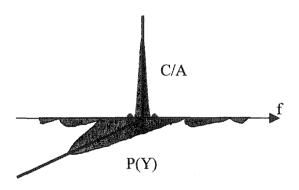

Un système de communication à étalement spectral utilise une largeur de bande plus grande que nécessite l'information à transmettre. Ainsi, la largeur de bande de transmission est beaucoup plus grande que celle de l'information [Peterson95]. La largeur de bande de transmission est obtenue en utilisant un signal d'étalement qui est indépendant des données de l'information. Les applications militaires ont commencé à utiliser les techniques d'étalement spectral il y'a plus de cinquante années pour leur avantageuse particularité permettant de rejeter l'interférence intentionnelle et involontaire [Gibson93]. En plus, l'étalement spectral permet un accès sélectif à des utilisateurs multiples et fournit une bande de haute résolution. Au cours de la dernière décennie, ces caractéristiques avaient accéléré l'intégration de cette technique aux différents systèmes de communications dans des applications commerciales diverses tels que les applications de radio mobiles, des communications par satellite, et des systèmes de positionnement. L'étalement spectral le plus largement utilisé est l'étalement spectral par séquence directe DSSS [Dixon94]. L'étalement DSSS est réalisé en multipliant une porteuse RF par un code pseudo aléatoire de bruit PRN. Par conséquent comme l'illustre la figure 1, la largeur de bande du signal étalé est supérieure à celle de l'information. Chaque utilisateur ou émetteur utilise un code différent qui est orthogonal aux codes des autres utilisateurs ou émetteurs. Cette méthode s'appelle l'accès multiple par division de code CDMA [Hassan98].

À l'émetteur, un code PRN est modulé par une séquence d'information en utilisant une modulation PSK. Une forme simple de l'étalement DSSS utilise la modulation BPSK.

Cette dernière fixe la phase de la porteuse à 180 degrés lorsqu'un chip du code PRN est égale à -1.

Figure 1 Exemple d'étalement spectral par séquence directe DSSS

#### 1.2 Présentation du GPS

Le système de positionnement GPS est un système de communications basé sur les satellites GPS qui orbitent autour de la terre. Ce système utilise le concept du temps d'arrivée TOA ("Time Of Arrival") avec un parcours à sens unique. Le temps de parcours est calculé par la multiplication de la vitesse de la lumière avec le retard du signal GPS qui voyage du satellite au récepteur [Braasch99]. Le calcul d'une position

tridimensionnelle exige l'utilisation de trois satellites. Un satellite additionnel est nécessaire pour synchroniser à son horloge atomique celle du récepteur [Trimble].

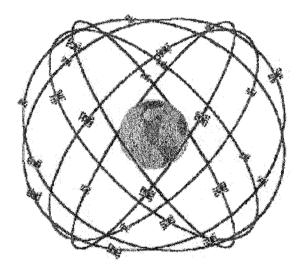

Comme montré à la figure 2, le système GPS utilise 24 satellites qui sont placés sur six plans orbitaux avec quatre satellites dans chaque plan [Kaplan96]. Il a été conçu par le département de la défense des États-Unis afin de fournir des informations précises de positionnement n'importe où dans le monde 24 heures sur 24.

Figure 2 Constellation du système GPS

L'émetteur dans chaque satellite envoie les données de navigation modulées avec un code de Gold spécifique en utilisant la technique d'étalement CDMA.

#### 1.2.1 Séquences de Gold

Les séquences pseudo-aléatoires PRN sont générées à l'aide de registres à décalage LFSR ("Linear Feedback Shift Register"). Selon le choix des coefficients "taps" des LFSR utilisés, les séquences PRN obtenues seront à période maximale MLS ("Maximal Length Sequence"), connues sous le nom de m-séquences [Viterbi95].

Une m-séquence a une période de  $N = 2^m - 1$ , sachant que m est la longueur du LFSR utilisé. Chaque période d'une m-séquence contient  $2^{m-1}$  chips égales à "1", et  $2^{m-1}$ -1 égale à "-1".

Les séquences de Gold sont construites par la combinaison de deux m-séquences d'une longueur  $N = 2^m - 1$ . La famille des séquences contenus dans l'ensemble G(u,v) défini par :

$$G(u,v) \equiv \{u,v,u \oplus v,u \oplus Z \cdot v,u \oplus Z^2 \cdot v,...,u \oplus Z^{N-1} \cdot v\}$$

(1.1) est une famille de séquences de Gold [Hamelin97]. Tel que  $u$  et  $v$  sont deux m-séquences de période  $N=2^m-1$ ,  $Z^q$  est un opérateur à décalage cyclique de  $Z$  vers la gauche, et  $\oplus$  est l'opérateur du ou-exclusif.

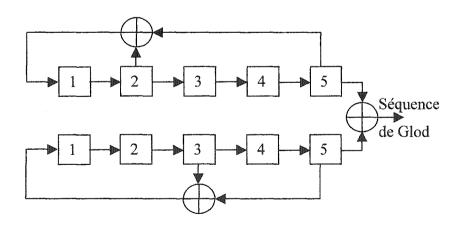

La figure 3 illustre un exemple de génération d'un code de Gold de longueur N=31 à partir de deux registres LFSR de longueur m=5.

Figure 3 Générateur de code de Gold de longueur N = 31

#### 1.2.2 Code C/A

Chaque satellite GPS a un code PRN unique qui est orthogonal aux autres codes des autres satellites. Ce code qui s'appelle le code C/A, appartient à la famille des codes de Gold. Sa période est de 2<sup>10</sup>-1 = 1023 chips transmis au rythme d'une séquence par 1 ms. Ce code est utilisé en GPS pour ses propriétés d'auto-corrélation et d'inter-corrélation.

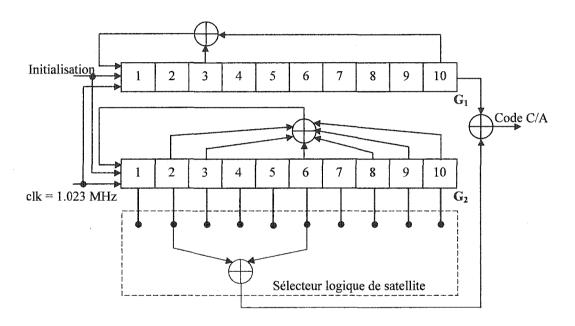

Figure 4 Générateur de code C/A

L'architecture d'un générateur de code C/A est montrée à la figure 4. Deux registres à décalage LFSR  $G_1$  et  $G_2$  génèrent des codes à période maximale MLS de  $2^{10}$ -1 = 1023 bits. Initialement  $G_1$  et  $G_2$  sont mis à "1", l'état zéro est illégal. Les taps des rétroactions des deux registres  $G_1$  et  $G_2$  sont définis respectivement par les polynômes suivants :

$$G_1(X) = 1 + X^3 + X^{10}$$

$$G_2(X) = 1 + X^2 + X^3 + X^6 + X^8 + X^9 + X^{10}$$

(1.2)

Le code C/A d'un satellite spécifique est généré par un ou-exclusif de la sortie du LFSR G<sub>1</sub>, et d'une version retardée de la sortie du LFSR G<sub>2</sub>. Cette version retardée est obtenue comme montrée à la figure 4, en calculant le ou-exclusif de deux niveaux donnés du LFSR G<sub>2</sub>. En d'autres termes, l'ajout d'une version décalée d'un code PRN donné à ce code même, donne le même code mais déphasé [Kaplan96].

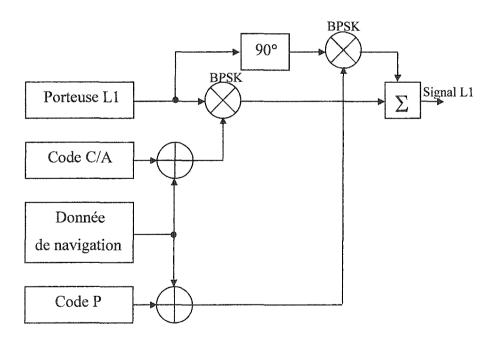

La figure 5 illustre le déphasage de 90 degrés existant entre le spectre du code civil C/A et celui du code militaire P modulés avec les données de navigation par la fréquence porteuse L1. Le lobe principal est de la forme d'un sinus cardinal, et il est de largeur de 2.046 MHz pour le code C/A, et de 20.46 MHz pour le code P.

Figure 5 Illustration du déphasage entre les signaux civil et militaire

Les données de navigation sont binaires et ont un débit de 50 bits/s. C'est à dire que chaque donnée contient 20 périodes de code, soit 20 ms. Ces données sont envoyées en utilisant la technique DSSS d'étalement spectral par séquence directe de CDMA. Grâce à sa large bande de fréquence, le signal obtenu jouit d'une grande résistance aux signaux brouilleurs [Broigniez96].

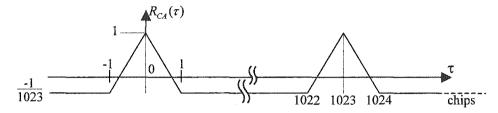

La fonction d'auto-corrélation du code C/A s'écrit :

$$R_{CA}(\tau) = \int_{-\infty}^{+\infty} C_i(t)C_i(t+\tau)dt$$

(1.3)

Où  $C_i$  est le code C/A du i<sup>ème</sup> satellite et  $\tau$  est une phase de décalage temporel.

Cette fonction d'auto-corrélation normalisée est représentée à la figure 6. Le pic de corrélation est répété à chaque période de code et l'intervalle de corrélation est sur deux chips.

Figure 6 Fonction d'auto-corrélation normalisée du code C/A

Les propriétés de cette fonction d'auto-corrélation sont utilisées pour synchroniser le code généré localement au récepteur avec le code du signal reçu. Il est important que la corrélation croisée entre deux codes C/A quelconques soit minimale, et ce pour n'importe quelle phase Doppler et durant toute la période de code. La corrélation croisée idéale est définie par :

$$R_{ij}(\tau) = \int_{-\infty}^{+\infty} C_i(t)C_j(t+\tau)dt = 0$$

(1.4)

Où  $C_i$  est le code C/A du  $i^{\text{ème}}$  satellite et  $C_j$  est le code C/A du  $j^{\text{ème}}$  satellite, avec  $i \neq j$ .

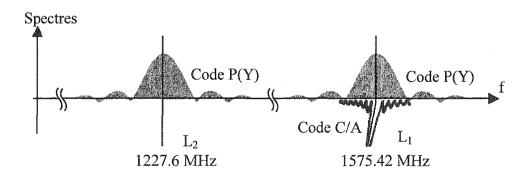

#### 1.2.3 Structure du signal GPS

Tous les satellites GPS utilisent deux fréquences connues sous le nom de L1 et L2. La composante L1, avec une fréquence porteuse de 1575.42 MHz, est utilisée conjointement pour les services de positionnement civil SPS (Standard) et militaire PPS (Précis). Tandis que L2, dont la porteuse est de 1227.6 MHz, est principalement utilisée pour le service de positionnement militaire [Kaplan96].

Le système GPS a une fréquence de base f<sub>o</sub> de 10.23 MHz à partir de laquelle ses deux fréquences porteuses sont construites :

L1 de 1575.42 MHz = 154 \*

$$f_o$$

L2 de 1227.60 MHz = 120 \*  $f_o$  (1.5)

La figure 7 illustre les spectres des codes civil et militaire en considérant ces deux fréquences porteuses utilisées en GPS.

Figure 7 Spectre fréquentiel du signal GPS

Une structure simplifiée du modulateur du signal L1 est montrée à la figure 8. Avant que la modulation BPSK soit appliquée, les valeurs {0,1} obtenues par le ou-exclusif sont

transformées en {-1,+1}. Un modèle simplifié du signal civil GPS-SPS transmis peut s'écrire comme suit :

$$s(t) = A \cdot G(t) \cdot D(t) \cdot \sin[2\pi f_{L1}t + \phi_0]$$

(1.6)

Où:

A: L'amplitude du signal transmis

G(t): Le code C/A du satellite (1.023 Mbps)

D(t): Le message de données de navigation (50 bps)

$f_{LI}$ : La fréquence porteuse d'émission,  $f_{LI}$  = 1575.42 MHz

$\phi_0$ : La déviation de phase de la porteuse

Figure 8 Structure simplifiée du modulateur du signal L1

À cause de l'effet du Doppler et du bruit, le signal reçu est différent. Un modèle simplifié du signal GPS-SPS reçu peut s'exprimer par :

$$r(t) = A \cdot G(t+\tau) \cdot D(t+\tau) \cdot \sin\left[2\pi \left(f_{L1} + \Delta f_{SV}\right) \cdot t + \Delta \phi\right] + n(t) \tag{1.7}$$

Où:

au : Le décalage temporel

$\Delta f_{SV}$ : La déviation fréquentielle du satellite due au Doppler

$\Delta \phi$  : La déviation de phase de la porteuse

n(t): Bruit blanc gaussien

#### 1.3 Traitement du signal GPS

Pour le traitement numérique du signal GPS au niveau de la réception, il faut disposer de ses deux composantes, I en phase et Q en quadrature. Ces composantes peuvent s'exprimer comme suit [Cooper86] :

$$I(\tau, \Delta f_{SV}) = R(\tau) \cdot \sqrt{1 - \sigma^2} \cdot \frac{\sin(\Delta f_{SV} \cdot T/2)}{\Delta f_{SV} \cdot T/2} \cdot \cos(\Delta f_{SV} \cdot T/2 + \Delta \phi) + N_I$$

$$Q(\tau, \Delta f_{SV}) = R(\tau) \cdot \sqrt{1 - \sigma^2} \cdot \frac{\sin(\Delta f_{SV} \cdot T/2)}{\Delta f_{SV} \cdot T/2} \cdot \sin(\Delta f_{SV} \cdot T/2 + \Delta \phi) + N_Q \qquad (1.8)$$

Où:

$$R(\tau) = \begin{cases} 1 - |\tau| ; |\tau| < 1 \\ 0 ; \text{ ailleurs} \end{cases}$$

(1.9)

$$\sigma^2 = 1 - \frac{1}{1 + NSR} = \frac{1}{1 + SNR} \tag{1.10}$$

Et:

$\tau$ : Le décalage temporel

$\Delta f_{SV}$ : La déviation fréquentielle du satellite due au Doppler

$\Delta \phi$  : La déviation de phase de la porteuse

T: Le temps d'intégration

$N_I, N_O$ : Bruits blancs gaussiens centrés de variance  $\sigma^2$

SNR: Le rapport signal à bruit (SNR = 1/NSR)

On constate alors que pour détecter un satellite à la réception, il faut évaluer le décalage temporel  $\tau$  et le déphasage de Doppler  $\Delta f_{SV}$ . Tandis que pour la déviation de la phase de la porteuse  $\Delta \phi$ , elle se voit éliminée en sommant le carré des signaux I et Q.

Dans le cas d'un démarrage à froid à la réception, il faut essayer toutes les combinaisons possibles du retard et du Doppler jusqu'à ce que le niveau du signal en sortie du corrélateur atteigne le seuil de détection du pic de corrélation. Cette opération est réalisée par des algorithmes de recherche bidimensionnels explicités dans le chapitre 2.

#### 1.4 Architecture du récepteur GPS

Afin de présenter les nouvelles techniques du traitement du signal GPS au niveau du récepteur, il est important de présenter l'architecture du récepteur standard séquentiel et de comprendre ses fonctionnalités. Les techniques de traitement à base de DSP, traitent les données à la réception un échantillon à la fois, ce qui est connu par la technique séquentielle d'où le nom du récepteur séquentiel.

Figure 9 Schéma bloc d'un récepteur générique GPS

La majorité des récepteurs GPS modernes échantillonnent le signal et réalisent les algorithmes de traitement du signal dans le module numérique [Parkinson96].

Dans le récepteur GPS, on peut distinguer trois parties principales, à savoir la section RF, les canaux d'acquisition et les boucles de poursuites. La figure 9 illustre ces trois dernières parties incluses dans le schéma bloc d'un récepteur générique GPS.

#### 1.4.1 Section RF

L'antenne reçoit le signal RF des satellites en vue. Selon le type de l'antenne, celle-ci peut capter uniquement le signal L1 ou les deux signaux L1 et L2 ensembles. Le niveau du signal RF capté est très faible. L'étage de pré-amplification amplifie ce signal sans dégrader sa qualité. La présence de filtres passe-bande à cet étage est nécessaire pour rejeter les interférences RF en dehors de la bande passante [Kaplan96]. Ces filtres peuvent être à large bande recouvrant les fréquences porteuses L1 et L2, ou bien

sélectifs à doubles bandes. Le choix de ces filtres dépend de l'application. Au minimum un filtre non sélectif est nécessaire pour supprimer les fréquences images du signal avant la transposition de fréquence. Le signal RF amplifié et filtré est sous-converti en IF grâce au produit par une sinusoïde pure, appelée oscillateur local LO, générée par un synthétiseur de fréquence qui est piloté par l'horloge de référence. Il est possible d'avoir plus d'un étage de sous conversion. Le signal IF analogique est numérisé par un échantillonnage dont le taux est déterminé selon la bande de fréquence de ce signal. Ce taux varie dans les différents récepteurs selon la façon du filtrage préalable du signal RF. Cependant les taux d'échantillonnage typiques varient entre 4 à 10 MHz. Pour le traitement du lobe principal du code C/A dont la largeur de bande est de 2.046 MHz, le taux d'échantillonnage nécessaire sera d'au moins 4.092 MHz.

La quantification du signal GPS ne prend pas plus de trois bits pour l'échantillonnage. Cependant un seul bit généralement suffit pour les récepteurs commerciaux à faibles coût, tandis que 1.5 bits à 3 bits sont généralement utilisés pour les récepteurs aux applications plus lourdes [Braasch99]. Pour plus d'un bit de quantification, un contrôleur automatique de gain AGC est nécessaire pour optimiser la plage d'entrée du convertisseur ADC. Une numérisation sur un seul bit, qui peut être réalisée par un comparateur de tension, simplifie l'architecture du module RF car le signal est écrêté.

Plus de détails sur l'architecture et l'implémentation d'un étage RF dédié aux applications GPS pourront être consultés dans l'article [Akos96].

#### 1.4.2 Boucles de poursuite

Dans la partie numérique du récepteur GPS, la poursuite est précédée d'une acquisition grossière du signal GPS. Les boucles de poursuites de porteuse et de code raffinent respectivement les mesures de la phase de la porteuse et celle du code, et suivent tout

changement sur celles-ci. Dans le cas de changements significatifs et brusques sur ces valeurs, le processus de poursuite échoue engendrant ce qu'on appelle un décrochage de boucles. Ceci nécessitera une ré-acquisition, soit un démarrage à chaud, afin de réévaluer les déphasages actualisés.

Les boucles de poursuites sont généralement effectuées par un microprocesseur ou dans un DSP, qui contrôle les NCO du code et de la porteuse. La boucle de code est habituellement une boucle de verrouillage de délai DLL, et la boucle de porteuse est soit une boucle de phase PLL ou une boucle à verrouillage de fréquence FLL.

Figure 10 Schéma bloc d'un canal de poursuite générique GPS

La figure 10 illustre un canal de poursuite générique GPS. Les boucles de code et de porteuse schématisées opèrent conjointement de façon à synchroniser la phase du code et la fréquence porteuse simultanément en réalisant une recherche bidimensionnelle. Ces boucles permettront de désétaler le signal en enlevant la porteuse et le code C/A et d'extraire finalement les données de navigation.

Les deux sous-sections suivantes décrivent les boucles de code et de porteuse respectivement.

#### 1.4.2.1 Boucle du code

Cette boucle de poursuite de la phase du code C/A consiste à comparer la réplique locale du code au signal entrant, et à en déduire une déviation de code, qui une fois filtrée, servira à contrôler le synthétiseur de code. La réplique du code devra être suffisamment précise dans une dimension d'un seul chip du signal entrant. Ceci est vrai car une déviation supérieure à un chip donne une corrélation nulle. Avec l'utilisation du résultat des corrélation, avance E, phase P et retard L, le discriminateur de la boucle de code détermine l'amplitude et la direction de la déviation du code local par rapport au signal entrant. Les répliques de code E et L sont décalées d'une moitié de chip par rapport au code en phase. La sortie du discriminateur qui est une phase de code bruitée, se voit lissée par un filtre ajouté spécialement pour cette fonction. En utilisant cette donnée filtrée, le synthétiseur de code doit avancer ou retarder sa réplique de code pour en arriver à un alignement maximal avec le code entrant. Ce type de boucle de poursuite est connu sous le nom de la boucle DLL.

#### 1.4.2.2 Boucle de la porteuse

Le signal IF numérique est mélangé en quadrature avec la réplique de porteuse pour le convertir en bande de base. Dans la boucle, le signal se verra ramené en bande de base sans suppression du déphasage Doppler  $\Delta f$ . La fonction de la boucle de porteuse est de

maintenir le NCO, le synthétiseur de porteuse, accroché à la fréquence porteuse entrante  $(f_{IF} + \Delta f)$  de telle sorte que la sortie du mélangeur n'ait aucune composante de porteuse. Cette opération est connue par la suppression de porteuse. Le signal est ensuite corrélé avec la réplique alignée du code C/A local et intégré en utilisant des circuits A&D ("Accumulate-and-Dump"). Ces circuits ont la particularité du comportement passe-bas, ce qui permet de rejeter le terme de fréquence double généré par le mélangeur quadratique. Ainsi, uniquement la valeur de corrélation est extraite. Le discriminateur de boucle de porteuse évalue l'amplitude et la direction de la déviation de fréquence à partir des composantes en phase I et en quadrature Q du signal. Après un filtrage passe-bas, ce décalage fréquentiel, qui est la réplique de déviation de fréquence porteuse  $\Delta f$ , est réalimenté vers le NCO afin de contrôler ce dernier.

Pour les deux architectures de boucles PLL et FLL utilisées pour la poursuite de fréquence, la largeur de bande de boucle est déterminée par le temps d'intégration "dwell Time"  $T_{DW}$  et par les caractéristiques du filtre de boucle utilisé.

La technique de lissage ou raffinement externe utilisée, équivaut mathématiquement à l'inclusion du terme de second degré de la série d'approximation. Cette technique fait appel à un système externe au système GPS, à savoir l'unité de mesure inertielle IMU, qui servira à améliorer la précision et la fiabilité de la boucle de poursuite.

La conception des boucles de poursuite est un sujet assez complexe dont l'étude dépasse l'objectif de ce travail. Cependant plus de détails concernant ces boucles de poursuites peuvent être trouvés dans [Kaplan96] et [Parkinson96].

#### 1.4.3 Phase d'acquisition

Le processus d'acquisition est exécuté lorsque le récepteur est mis en marche car les phases de code et de fréquence porteuse ne sont pas initialement connues. L'acquisition servira à en faire une estimation grossière, et ce en effectuant une recherche bidimensionnelle. Aussi, les 24 satellites ne sont pas tous en vue, alors l'acquisition devra chercher les satellites, caractérisés par leurs codes, dont les signaux sont présents à la réception. Le chapitre 2 suivant, présente ce processus en détails.

#### 1.5 Principe de base du corrélateur

Dans un système numérique, chaque signal peut être représenté par une série d'échantillons représentés sous forme de bits. L'intégrale de corrélation devient alors une somme finie. La multiplication est interprétée par un Non-Ou-Exclusif ou un Ou-Exclusif selon la représentation binaire des amplitudes. La fonction de corrélation de base est alors réalisée comme suit:

$$Corrélation = \Sigma (Di \oplus Ri)$$

(1.11)

La figure 11 illustre le principe trivial de cette corrélation, et ce à l'aide d'un corrélateur à base de registres à décalage LFSR.

Où:

Di est le ième bit de la trame de donnée.

Ri est le ième bit de la trame de référence.

n est le nombre total de bit.

Figure 11 Structure d'un corrélateur à base de registres à décalage

Dans le résultat de corrélation obtenu, l'emplacement du pic de corrélation traduit la déviation de code du signal entrant par rapport à la réplique locale de code. Ce déphasage de code est dû au temps nécessaire pour la réception du signal transmis dès le satellite.

D'autres formes plus complexes de l'architecture du corrélateur GPS seront proposées et étudiées dans les chapitres 3, 5 et 6. Toutefois le chapitre 2 suivant présente les techniques standards utilisées en acquisition, et ce pour une structure conventionnelle du récepteur GPS.

#### **CHAPITRE 2**

## TECHNIQUES D'ACQUISITION

## 2.1 Stratégies classiques d'acquisition

L'acquisition du signal GPS peut être identifiée comme étant un processus de recherche bidimensionnel. Il nécessite d'avoir une réplique exacte du code PRN et de la fréquence porteuse du signal du satellite. La distance entre le SV et le récepteur est déterminée par la synchronisation de la phase du code PRN d'entrée avec la phase du code PRN générée localement. Cette période de synchronisation est effectuée en deux étapes : un alignement des codes de façon grossière, puis fine. L'étape primaire d'acquisition permet d'aligner les deux codes à l'intérieur de l'intervalle d'un chip du code d'étalement. Et ensuite l'étape de poursuite du code réduit l'écart des phases à de faibles valeurs. Si au cours du processus de poursuite du code, l'erreur de l'écart des phases dépasse une valeur limite de la boucle de poursuite, un processus de ré-acquisition (démarrage à chaud) est amorcé puis il est suivi par le maintien précis du code.

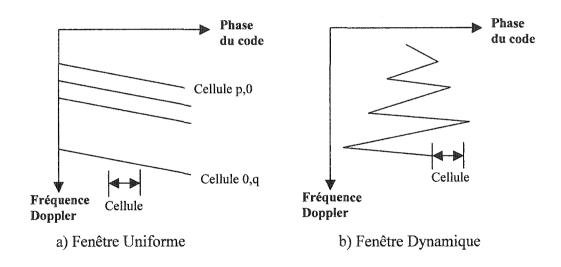

#### 2.1.1 Région d'incertitude de l'acquisition

Pour le code C/A de porteuse L1 de 1575.42 MHz, le processus d'acquisition inclut la synchronisation initiale de la phase du code et une estimation du décalage de la fréquence. Le décalage de la phase du code local et de l'écart de la fréquence Doppler est effectué par des sauts de valeurs discrètes, réalisés habituellement par un traitement numérique du signal. Cette région d'incertitude qui est constituée de la phase du code d'entrée et de l'écart Doppler, est divisée en des cellules de recherche de deux dimensions, où les références de la phase du code et de la fréquence sont détectées en

désétalant le signal reçu. Si l'estimation de la phase du code et de son décalage Doppler sont près des valeurs réelles, le processus de désétalement sera fonctionnel et le signal pourra être détecté. Par contre, dans le cas d'une mauvaise estimation, le processus de désétalement ne détectera pas le signal à l'entrée.

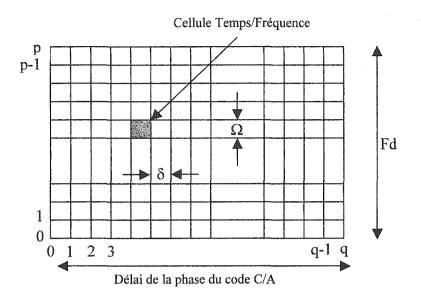

Le générateur de code local et le NCO seront décalés à une nouvelle valeur du délai de la phase du code et à une nouvelle estimation de l'écart Doppler, qui seront à leur tour évaluées jusqu'à ce qu'une synchronisation du code et de la fréquence Doppler soit obtenue. L'espace de recherche bidimensionnelle d'acquisition d'un SV donné est montré à la figure 12.

Figure 12 Espace de recherche pour l'acquisition du signal GPS

# 2.1.2 Algorithmes de recherche

À cause de l'incertitude uniforme de la phase du code C/A sur la période entière du code, il est préférable d'utiliser une méthode de recherche rectiligne du délai de la phase du code comme montré à la Figure 13a. Généralement, cette technique est utilisée dans le cas d'un démarrage à froid. La région d'incertitude est balayée presque entièrement afin de trouver la cellule qui correspond au maximum d'énergie. La recherche est poursuivie à l'intérieur de la cellule selon une direction et la région entière d'incertitude est balayée de cellule en cellule jusqu'à détection du signal.

Figure 13 Structure des stratégies de recherche séquentielle d'énergie

La même stratégie est utilisée pour la recherche du décalage Doppler si aucune information de celui-ci n'est disponible, sinon on présume une distribution non uniforme du décalage Doppler à l'intérieur de la région d'incertitude avec une densité de probabilité plus forte près de l'estimation initiale, et une densité de probabilité plus faible aux extrémités de la région d'incertitude. Cette technique est utilisée dans le cas d'un démarrage à chaud où la synchronisation avec le signal reçu vient juste d'être perdue. La recherche est effectuée ici dans une fenêtre s'agrandissant au cours du temps (Figure

13b) en partant de la cellule contenant l'estimation Doppler initiale et en avançant dans les deux directions [Landry98].

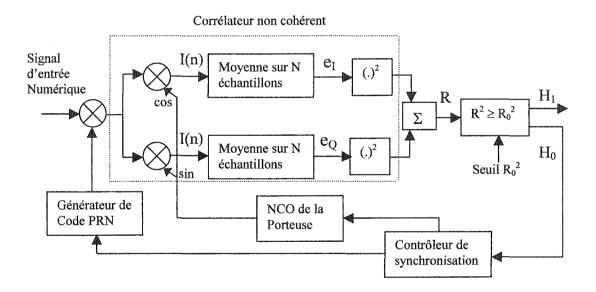

Le système d'acquisition pour la technique utilisée lors d'un démarrage à froid, consiste en un corrélateur de code non cohérent, un détecteur numérique d'alignement de phase et un système logique de synchronisation comme montrés à la Figure 14. Le but du corrélateur non cohérent est de désétaler le signal d'entrée avec un code de référence dont la phase a été décalée et en prenant une estimation du décalage Doppler.

Figure 14 Schéma bloc du système d'acquisition d'un code d'étalement

Le détecteur numérique évalue l'état de succès ou d'échec du processus de désétalement en comparant la sortie du corrélateur avec un seuil prédéfini. Si l'énergie de désétalement est insuffisante, le contrôleur de synchronisation passe à une autre cellule en affectant au générateur de code une nouvelle valeur du délai du code de référence et au NCO local, une nouvelle valeur de la fréquence de référence. Par contre, si l'énergie détectée est suffisante, le contrôleur de synchronisation arrête le processus de décalage dans la région d'incertitude et la synchronisation est atteinte [Landry98].

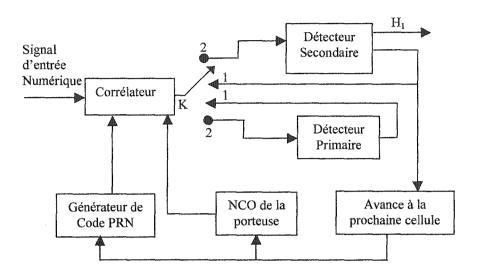

Une caractéristique importante des récepteurs GPS est leur temps d'acquisition moyen. Une procédure à double évaluation ("Double Dwell") est adoptée permettant une amélioration significative du temps d'acquisition estimé comparativement à une procédure à évaluation simple ("Single Dwell"). L'intervalle d'observation de la synchronisation de la phase du code consiste en deux périodes fixes dont chacune fait l'objet d'une évaluation préalable. La première période consiste en un petit intervalle de temps de la période de corrélation partielle permettant une décision rapide et l'élimination d'une cellule incohérente et de ce fait, réduit le temps moyen de recherche et d'acquisition. Ceci est d'autant plus significatif que le nombre de cellules à évaluer est grand. Si l'alignement de la phase des codes n'est pas détecté à la première période d'analyse, la cellule est rejetée (représenté par l'état H<sub>0</sub>) et le processus d'acquisition se poursuit à la cellule suivante. Cette courte période d'analyse peut augmenter la probabilité d'acquisition erronée PFA à cause d'un gain d'étalement faible obtenu sur une courte période de désétalement. Une acquisition erronée signifie que la phase des codes est alignée (représentée par l'état H1) et que le processus de synchronisation fine de la phase des codes est initié. Le temps de pénalité nécessaire à la boucle de maintien pour indiquer une acquisition erronée et pour réamorcer le processus d'acquisition est une variable aléatoire. Dans le but de réduire le coût du temps d'acquisition provenant de l'acquisition erronée, un mode de vérification utilisant la deuxième période d'évaluation ("Double Dwell") est initié lorsque l'état H1 est obtenu. Dans cette deuxième période d'évaluation, le corrélateur non cohérent conserve le même délai de la phase du code local et procède au traitement de corrélation avec les mêmes paramètres de décalage mais sur une période d'analyse plus longue comparativement à la première période d'évaluation. Il utilise le même détecteur que celui de la première période d'évaluation à l'exception du fait qu'il effectue séquentiellement plusieurs tests suite auxquels il prend une décision finale. Si une bonne proportion des tests effectués indique l'obtention d'une synchronisation, l'état H1 est vérifié et la boucle de maintien du code est activée. Autrement, le contrôleur de synchronisation réinitialise les phases pour passer à la

cellule voisine. La Figure 15 montre le schéma bloc de la stratégie d'acquisition d'une recherche à double période utilisée pour le cas d'un démarrage à chaud.

Figure 15 Fonctionnement de la Recherche en Double Périodes

Il faut noter que la stratégie d'une recherche à double périodes est aussi appliquée à l'acquisition des codes P. Pour l'acquisition des canaux L1-P et L2-P, l'estimation initiale du délai de la phase du code est obtenue à l'aide du délai de la phase du code L1-C/A et des informations HOW ("Hand-Over-Word") provenant du message de navigation GPS. Cette estimation peut être précise à quelques chips du code P. À cause de l'information a priori, une recherche sous forme de fenêtre en expansion est utilisée. Le maintien cohérent du code L1-C/A apporte aux canaux P soumis aux décalages Doppler, un domaine d'incertitude en fréquence étroit lors de l'acquisition des canaux P [Landry98].

# 2.2 Description détaillée du processus d'acquisition

Les récepteurs GPS conventionnels utilisent des méthodes de corrélation afin de déterminer l'écart bidimensionnel.

Un corrélateur classique multiplie le signal reçu par une réplique du code PRN approprié et ensuite intègre ou filtre par un passe-bas pour avoir le signal du pic de corrélation. La détection initiale de la présence de ce pic est connue sous le nom de « processus d'acquisition ».

Les récepteurs séquentiels utilisent le multiplexage temporel afin de dépister un nombre de satellites plus élevé que le nombre de canaux disponibles. De tels récepteurs sont ainsi plus lents dans le procédé d'acquisition. Le temps d'acquisition de moins d'une minute et allant jusqu'à 20 minutes, dépend du nombre de canaux disponibles, d'algorithmes utilisés, et des conditions relatives au rapport signal à bruit [Braasch99].

#### 2.2.1 Architecture d'un module d'acquisition

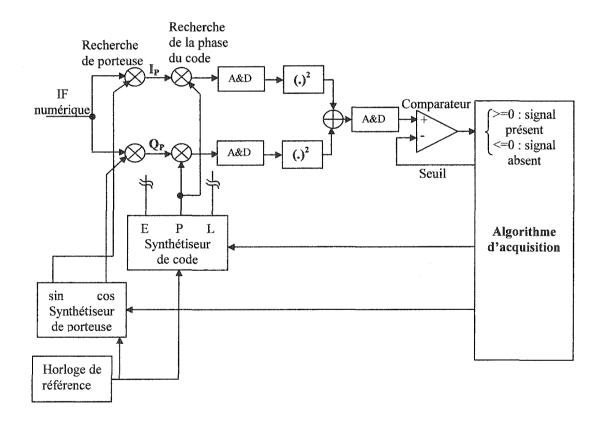

La figure 16 montre la structure d'un seul canal de corrélation. Pendant l'acquisition du signal, le canal opère en configuration de boucle ouverte. L'algorithme d'acquisition examine les combinaisons successives de la phase de code et de la fréquence porteuse pour en détecter un pic de corrélation donné par  $I^2 + Q^2$  (l'énergie de corrélation).

Un deuxième étage d'intégration est utilisé pour sommer les corrélations calculées sur des périodes de codes multiples afin de détecter le signal avec le plus bas rapport signal à bruit.

La valeur du seuil fixée à l'avance pour détecter la présence d'un signal d'un satellite, est calculée selon les probabilités  $P_{FA}$  ("False Acquisition") et  $P_{MD}$  ("Missed Detection"), requises pour l'application désirée.

Sur la figure 16, les branchements liés au point E "Early" (avance de phase) et L "Late" (retard de phase) sont omis uniquement pour éviter d'alourdir le schéma, cependant leur branchement avec les blocs qui en découlent est identique au point P "Prompt" (phase).

Le décalage du code en avance et en retard dans une dimension de longueur d'un chip, permet de raffiner l'ajustement de la réplique du code avec celui du signal reçu.

Figure 16 Configuration d'acquisition d'un canal de récepteur GPS

Le récepteur détecte le pic de corrélation en comparant l'amplitude de l'énergie de corrélation avec le seuil  $T_D$ . Si celui-ci est fixé trop haut, le récepteur ne pourra détecter les signaux faibles, ce qui induirait l'augmentation de la probabilité d'une détection manquée  $P_{MD}$ .

Dans le cas où ce seuil serait fixé bas, la probabilité d'une acquisition erronée  $P_{FA}$  se verra augmentée sous l'effet du bruit présent sur le signal.

Le seuil de détection  $T_D$  nécessaire peut être calculé en se basant sur la probabilité  $P_{FA}$  requise, et sur les distributions statistiques des paramètres du signal et du bruit [Feng99].

Afin de pouvoir distinguer l'amplitude d'un pic de corrélation par rapport à une fausse corrélation due au phénomène du bruit, la marge d'acquisition  $M_{Aq}$  est définie par l'équation 2.1 suivante :

$$M_{aq} = 10.\log\left(\frac{R_p}{R_N}\right) \quad (dB) \tag{2.1}$$

Où:

$R_P$ : L'amplitude du pic de corrélation

$R_N$ : L'amplitude du plus grand pic de bruit dans le bloc corrélé pour

une probabilité donnée.

Pour pouvoir faire l'acquisition sans erreur, le seuil de détection  $T_D$  doit être fixé inférieur au pic de corrélation d'un signal faible, mais aussi supérieur au plus grand pic de bruit.

#### 2.2.2 Processus de recherche

L'acquisition est un processus de recherche bidimensionnel. Ses dimensions sont : le code CDMA PRN du satellite et la fréquence porteuse du signal reçu.

Si le récepteur a les données Almanac lui permettant d'approximer l'orbite du satellite, la recherche d'un SV probable se fait plus rapidement. Si ceci n'est pas possible, le récepteur devra chercher parmi tous les codes PRN des 24 satellites ("Cold Start").

Sans aucune information a priori de la phase du code C/A, la région d'incertitude de la phase du code se résume à la période du code entière, c'est à dire 1023 chip. Cette région est quantifiée par un nombre fini de cellules dont la largeur de la cellule  $\delta$  correspond à une fraction de la période de chip (Tc), telle Tc/ $\alpha$  (où  $\alpha$ =2,4,8,...,16). Cette division du temps de décalage permet d'éviter de manquer la détection du maximum d'énergie de la corrélation et apporte une précision à cette mesure. Le nombre total des cellules q pour l'acquisition du code C/A est alors  $1023 \cdot Tc/\delta$ .

La Figure 17 montre la région d'incertitude de l'acquisition. La recherche de phase du code C/A par une méthode à base de registres à décalage est présentée à la figure 18.

La région d'incertitude du décalage Doppler (Fd) est le plus souvent de  $\pm 10$  KHz. Elle inclue l'effet Doppler entre le satellite et le récepteur qui se déplace et la perturbation de la fréquence due aux diverses bruits.

Si les éphémérides du satellite et une estimation sommaire de la position du récepteur sont connus, l'estimation initiale du décalage Doppler peut être calculée. Ce qui réduit significativement la région d'incertitude. Le choix de la largeur de la cellule dans la région d'incertitude des fréquences  $(\Omega)$  est fonction du temps de corrélation et on obtient finalement le nombre p des cellules fréquentielles  $(p = Fd/\Omega)$ .

Figure 17 Région d'incertitude de la phase du code et du décalage Doppler

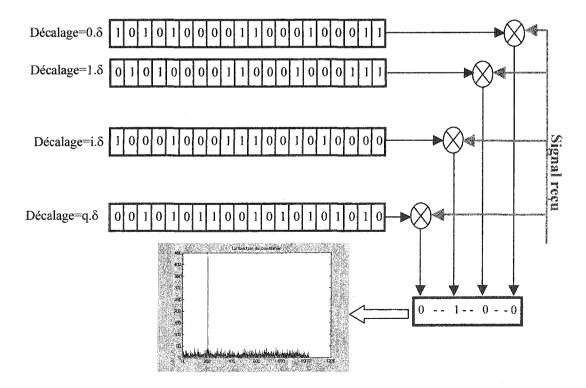

Figure 18 Recherche de phase de code par décalage de la séquence de code

Quand un satellite transmet en L1 (la fréquence porteuse est égale à 1575.42 MHz), le trajet satellite-récepteur étant dynamique cette fréquence est modifiée selon la ligne relative de la vitesse de vue  $v_r$ , causant un décalage de fréquence de Doppler  $\Delta f_D$ , donnée par :

$$\Delta f_D = \pm \left(\frac{v_r}{c - v_r}\right) f_0 \tag{2.2}$$

Où:

$f_0$  est la fréquence de la porteuse. c est la vitesse de la lumière.

Pour un récepteur stationnaire, la vitesse  $v_r$  est moins de 1500 m/s, ce qui correspond à un décalage de fréquence Doppler de  $\pm$  8 kHz.

En effet, pour la majorité des applications,  $\Delta f_D$  est moins de  $\pm$  10 kHz. Si le récepteur ne peut estimer ce décalage Doppler, il sera alors obligé de faire sa recherche dans l'intervalle [L1-10 kHz; L1+10 kHz] avec la résolution nécessaire pour la fréquence Doppler.

Pour pouvoir détecter le maximum de corrélation, le code généré au niveau du récepteur doit s'aligner dans la dimension d'un chip qui est exactement 977.5 ns, ainsi la résolution de la phase maximale est d'une moitié de chip, soit 488.75 ns.

Sachant que le code C/A contient 1023 chips en une période, il existe alors un minimum de 2046 plages de recherche dans la dimension de la phase du code.

Le récepteur doit intégrer sur au moins une période entière du code C/A, par conséquent le temps minimal d'évaluation "dwell" d'une corrélation est de 1 ms pour un haut rapport signal à bruit. Cependant, une période d'évaluation "dwell" plus longue devra être utilisée au cours d'un démarrage d'acquisition à froid "Cold Start". De même, les signaux faibles nécessitent une période d'évaluation "dwell" par cellule plus longue.

La résolution du Doppler doit être suffisamment bonne pour s'intercepter dans le lobe principal du  $sinc^2$  de la fonction de corrélation, dont la largeur dépend du temps "dwell". La résolution de la plage de Doppler peut être estimée par 2/3  $T_{DW}$ , où  $T_{DW}$  est le temps "dwell" par cellule. Le temps minimal "dwell" de 1 ms donne une résolution en fréquence Doppler de 667 Hz. Pour l'acquisition de faibles signaux, le temps "dwell" par cellule  $T_{DW}$  peut se prolonger à 20 ms, nécessitant ainsi une résolution en fréquence Doppler de 33 Hz [Kaplan96].

À titre d'exemple, dans le cas d'un démarrage d'acquisition à froid, si un récepteur effectue sa recherche dans l'intervalle [L1-10 kHz; L1+10 kHz] avec une résolution de 1 kHz, il devra alors essayer 21 combinaisons en dimension de fréquence porteuse. Étant donné la nécessité minimale de 2046 plages de recherche dans la dimension de la phase du code pour une résolution d'une moitié de chip, l'espace total de recherche dans le cas d'un démarrage à froid sera alors :

$$2(1023) \times \left(2\left(\frac{10kHz}{1kHz}\right) + 1\right) = (2046) \times (21) \approx 40000 \text{ cellules d'acquisition.}$$

(2.3)

Donc en supposant un temps "dwell" de 1 ms, le temps total de recherche prendra au pire cas 40 secondes.

Finalement, notons que les techniques d'acquisition présentées dans ce chapitre, sont des techniques basées sur le traitement séquentiel connues dans la littérature sous le nom de "stream processing". Parmi les inconvénients de ce traitement conventionnel, le temps d'acquisition relativement long et l'obligation de ré-acquisition du signal après un décrochage de boucle.

À cause de ces imperfections, cette méthode de traitement n'est pas une solution optimale dans les cas d'atténuations sévères du signal GPS, ou lorsque ce dernier est sujet à une haute vitesse dynamique, à des problèmes de réflexions par trajets multiples ou à des interférences dues au blocage involontaire, "unintentional jamming".

Ainsi, une technique de traitement alternative sera présentée au chapitre 3 suivant.

#### **CHAPITRE 3**

## TECHNIQUE DE TRAITEMENT PAR BLOCS

## 3.1 Présentation de la technique

La technique de traitement par blocs, connue sous le nom de "block processing", est utilisée habituellement en traitement d'image. Elle permet d'obtenir de meilleures performances dans les conditions difficiles [Moeglein98].

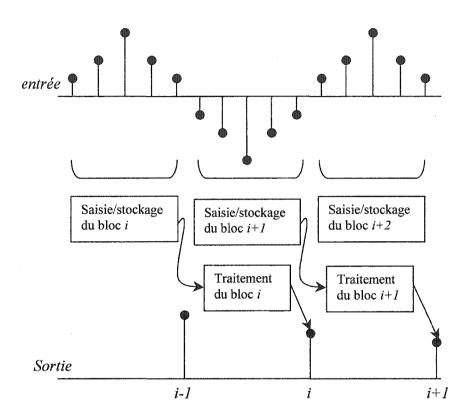

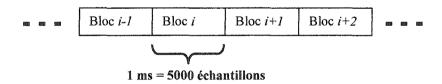

Un arrangement de "block processing" commence par emmagasiner les échantillons en blocs à leur arrivée. Après l'accumulation d'un nombre suffisant de ces échantillons, le traitement de ces blocs est amorcé. L'accès aux différents échantillons peut se faire aléatoirement et non pas séquentiellement puisque ces derniers sont disponibles simultanément. La figure 19 illustre un exemple de blocs de cinq échantillons, qui sont stockés dès leur arrivée. Quand le cinquième échantillon du bloc i arrive, le traitement de ce bloc commence. À ce point, deux activités sont réalisées en même temps : le traitement du bloc i, la saisie et le stockage du bloc i+1.

Le traitement par blocs peut être utilisé lorsque le taux d'échantillonnage de l'entrée est beaucoup plus grand que celui de la sortie [Ackenhusen99].

Pour un récepteur GPS, le traitement est effectué dans un bloc de données numériques IF pour obtenir la déviation de la phase du code et le déplacement Doppler de chaque satellite reçu. Un bloc doit contenir au moins une période entière de code PRN, à savoir plusieurs milliers d'échantillons, et la sortie est de seulement deux valeurs par satellite, soient la phase du code et la phase de la porteuse.

De cette façon, la condition pour l'utilisation de cette technique de traitement est vérifiée, soit le taux d'échantillonnage de l'entrée est plus grand que celui de la sortie.

Figure 19 Illustration du traitement par blocs pour cinq échantillons / bloc

# 3.2 Système de collecte de données GPS

Un étage RF sophistiqué permettant la collecte de données GPS a été présenté dans l'article [Feng99]. Ce système est conçu spécialement pour le signal GPS-SPS civil.

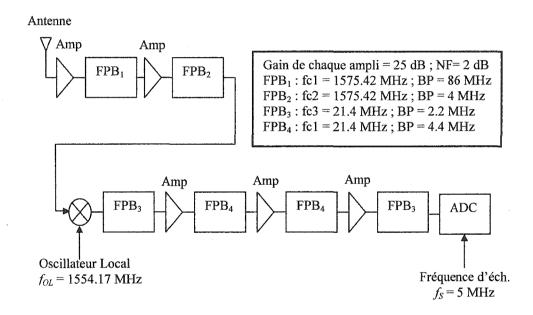

Le signal RF est échantillonné à un taux de 5 millions d'échantillons par seconde permettant de préserver toute information pertinente dans le signal. Ainsi, si une anomalie survient lors de la réception et le traitement du signal, les données abondantes autour de cet événement anormal faciliteront le rétablissement rapide de la synchronisation du récepteur. L'utilisation de ce système jumelé avec la technique de traitement par blocs, permet d'accroître la robustesse du récepteur GPS. Le schéma de cette tête RF est montré à la figure 20. Ce système RF comporte une antenne, des filtres passe-bas, des amplificateurs à faibles bruits, un mélangeur à un oscillateur local et un convertisseur analogique numérique, ADC, permettant de numériser le signal en des blocs de longueur de 1 ms et ayant 5000 échantillons chacun.

Figure 20 Système de collecte de données GPS-SPS

Le signal GPS est collecté par l'antenne. Un préamplificateur de 30 dB précède le premier filtre dont la fréquence centrale est égale à la fréquence porteuse L1 de 1575.42 MHz, et dont la largeur de bande à 3 dB est de 86 MHz. Le signal est encore amplifié et filtré avant d'être mélangé à un oscillateur local à 1554.17 MHz, réalisant ainsi une sous conversion à une fréquence intermédiaire IF de 21.25 MHz. Ensuite, le signal IF résultant est filtré afin de rejeter le terme de double fréquence obtenu après la sous conversion. La fréquence centrale de ce dernier filtre est de 21.4 MHz et sa largeur de bande à 3 dB est de 2.25 MHz. Après trois étages d'amplifications et filtrages, le

signal analogique IF de 21.25 MHz est numérisé par un ADC à un taux de 5 MHz, produisant ainsi un signal IF numérique de fréquence centrale  $f_{IF}$  de 1.25 MHz.

#### 3.3 Structure du signal

Le modèle standard du signal numérique IF GPS-SPS échantillonné, pour un bloc de traitement *i* est comme suit :

$$s_{i,k} = A_i G_{k,\tau_i} D_{i,\tau_i} \sin[2\pi (f_{IF} + \Delta f_i) T_S(m_i + k) + \phi_i] + n_{i,k}$$

(3.1)

Où:

i : Indice de bloc,  $i^{\text{ème}}$  bloc (i = 1,2,3,...)

k:  $k^{\text{ème}}$  échantillon commençant par le  $i^{\text{ème}}$  bloc (k = 1, 2, ..., M)

$m_i$ : Le nombre total d'échantillons avant le  $i^{\text{ème}}$  bloc  $m_i = (i-1).M$

M: Le nombre d'échantillons par bloc i

$\tau_i$ : Le retard dû à la transmission du signal pour le bloc i

$A_i$ : L'amplitude du signal pour le bloc i

$G_{k,\tau_i}$ : Le code C/A retardé en temps et échantillonné

$D_{k,\tau}$ : Le signe du bit de donnée de navigation pour le bloc i

$f_{IF}$ : La fréquence centrale du signal IF numérique, ( $f_{IF} = 1.25 \text{ MHz}$ )

$T_S$ : La période d'échantillonnage  $(1/f_S)$ ,  $(T_s = 0.2 \mu s)$