**ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC**

**MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE**

**COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA

MAÎTRISE EN GÉNIE ÉLECTRIQUE

M.Ing.**

**PAR

Sacha ATWAL**

**UN SYSTÈME DE COMMUNICATION À FAIBLE PROBABILITÉ D'INTERCEPTION

BASÉ SUR LA MODULATION CHAOTIQUE**

**MONTRÉAL, LE 20 DÉCEMBRE 2010**

**© Tous droits réservés, Sacha Atwal, 2010**

**PRÉSENTATION DU JURY**

**CE MÉMOIRE A ÉTÉ ÉVALUÉ**

**PAR UN JURY COMPOSÉ DE**

**M. François Gagnon, directeur de mémoire**

**Département de génie électrique à l'École de technologie supérieure**

**M. Claude Thibeault, codirecteur**

**Département de génie électrique à l'École de technologie supérieure**

**M. Gheorghe Marcel Gabrea, président du jury**

**Département de génie électrique à l'École de technologie supérieure**

**M. Ghyslain Gagnon, membre du jury**

**Département de génie électrique à l'École de technologie supérieure**

**IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC**

**LE 24 NOVEMBRE 2010**

**À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE**

## **REMERCIEMENTS**

J'aimerais remercier les professeurs François Gagnon et Claude Thibeault pour leurs aides tout au long de cette maîtrise.

# **UN SYSTÈME DE COMMUNICATION PEU IDENTIFIABLE BASÉ SUR LA MODULATION CHAOTIQUE**

Sacha ATWAL

## **RÉSUMÉ**

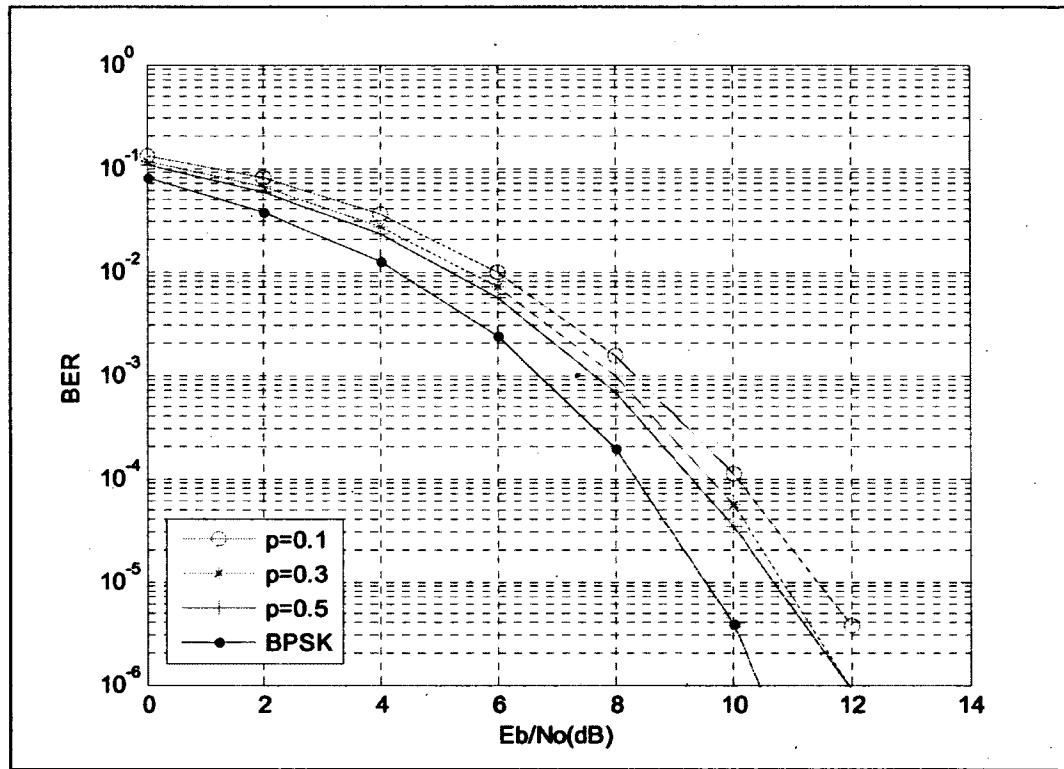

Dans un environnement militaire, il existe des situations dans lesquelles il est important d'utiliser des méthodes de communications avec faible probabilité d'interception (LPI) et de détection (LPD). Ce mémoire propose un système de communication LPI basé sur la modulation chaotique. Malheureusement, les signaux générés à partir de systèmes numériques basés sur la modulation chaotique sont cyclostationnaire [1]. Une technique d'introduction de phase aléatoire est évaluée afin de modifier les propriétés cyclostationnaires du signal modulé chaotiquement. Une analyse de la cyclostationnarité de deuxième ordre démontre que la technique d'introduction de phase aléatoire proposée réduit le degré de cyclostationnarité du signal chaotique résultant. Le modulateur chaotique est basé sur la symbolique dynamique. Le récepteur utilise un algorithme à maximum de vraisemblance afin d'estimer la séquence transmise. Une analyse des performances du système de communication en terme ("Bit Error Rate", BER) démontre une dégradation de performance de deux décibels par rapport à une modulation BPSK. De plus, afin de faire la démonstration de la faisabilité du système proposé, une analyse de l'implémentation du receveur chaotique dans un ("Field Prommable Gate Array", FPGA) est réalisée.

**Mots-clés :** Chaos, cyclostationnarité, Modulation, LPI

# **AN LPI COMMUNICATION SYSTEM BASED ON CHAOTIC MODULATION**

**Sacha ATWAL**

## **ABSTRACT**

In a military environment, there are situations in which it is important to use methods of communication with low probability of interception (LPI) and low probability of detection (LPD). This thesis proposes an LPI communication system based on chaotic modulation. Unfortunately, signal resulting from digital communication system based on chaotic modulation are cyclostationary [1]. A phase randomization technique is investigated in order to modify the cyclostationary properties of the chaotically modulated signal. Second-order statistical cyclostationary analysis shows that phase randomization reduce the degree of cyclostationarity of the chaotic signal. The chaotic modulation scheme is based on symbolic dynamics. The receiver estimates the transmitted sequence using the Maximum Likelihood (ML) estimation approach. The resulting bit error-rate (BER) of the proposed communication system show a performance that is two decibels lower than a BPSK modulation. In addition, the overall feasibility of such a scheme is presented by an analysis of the receiver complexity using field programmable gate array (FPGA) technologies.

**Keywords:** Chaos, cyclostationarity, Modulation, LPI

## TABLE DES MATIÈRES

Page

**INTRODUCTION .....**.....1

**CHAPITRE 1 COMMUNICATION LPI/LPD .....**.....3

|       |                                                                                   |    |

|-------|-----------------------------------------------------------------------------------|----|

| 1.1   | Communications LPI/LPD et signaux chaotiques .....                                | 3  |

| 1.1.1 | Résumé des caractéristiques d'un signal chaotique LPI/LPD .....                   | 4  |

| 1.2   | Méthodes de détection de la cyclostationnarité .....                              | 6  |

| 1.2.1 | Fonction de densité de corrélation spectrale .....                                | 6  |

| 1.2.2 | Spectre de densité de puissance de la transformation au carré du signal.....      | 9  |

| 1.3   | Revue de la littérature des méthodes de suppression de la cyclostationnarité..... | 9  |

| 1.3.1 | Filtre passe bas avec largeur de bande $1/2T$ .....                               | 10 |

| 1.3.2 | Signal avec enveloppe temporelle rectangulaire de durée T .....                   | 11 |

| 1.3.3 | Phase aléatoire .....                                                             | 12 |

| 1.4   | Conclusion .....                                                                  | 13 |

**CHAPITRE 2 MODULATION CHAOTIQUE.....**.....14

|       |                                                                      |    |

|-------|----------------------------------------------------------------------|----|

| 2.1   | Théorie du fonctionnement de la modulation chaotique.....            | 14 |

| 2.1.1 | Définition du chaos .....                                            | 17 |

| 2.1.2 | Symbolique dynamique .....                                           | 18 |

| 2.2   | Survol des méthodes de modulation et synchronisation chaotique ..... | 19 |

| 2.2.1 | Méthodes de modulation chaotique .....                               | 19 |

| 2.2.2 | Méthodes de synchronisation des systèmes chaotiques.....             | 22 |

| 2.3   | Choix du modulateur chaotique proposé .....                          | 24 |

| 2.4   | Conclusion .....                                                     | 26 |

**CHAPITRE 3 SYSTÈME CHAOTIQUE PROPOSÉ.....**.....27

|       |                                                                                            |    |

|-------|--------------------------------------------------------------------------------------------|----|

| 3.1   | Chaine de transmission du système chaotique.....                                           | 27 |

| 3.1.1 | Modulateur chaotique .....                                                                 | 28 |

| 3.1.2 | Introduction de phase aléatoire .....                                                      | 31 |

| 3.1.3 | Filtre de mise en forme .....                                                              | 32 |

| 3.1.4 | Démodulateur chaotique .....                                                               | 36 |

| 3.2   | Évaluation de la cyclostationnarité du signal de transmission.....                         | 42 |

| 3.2.1 | Résultats et analyse de la transformation au carré du signal de.....<br>transmission ..... | 44 |

| 3.2.2 | Résultats et analyse de la SCD du signal de transmission .....                             | 48 |

| 3.3   | Évaluation des performances du système de communication chaotique .....                    | 51 |

| 3.3.1 | Résultats et analyse des performances .....                                                | 52 |

| 3.4   | Conclusion .....                                                                           | 52 |

|                                                                                                               |            |

|---------------------------------------------------------------------------------------------------------------|------------|

| <b>CHAPITRE 4 ARCHITECTURE MATÉRIELLE DU DÉMODULATEUR CHAOTIQUE</b>                                           | <b>54</b>  |

| 4.1    Module série-parallèle .....                                                                           | 55         |

| 4.2    Module de calcul des métriques de branche BMU .....                                                    | 56         |

| 4.2.1    Générateur pseudo-aléatoire .....                                                                    | 60         |

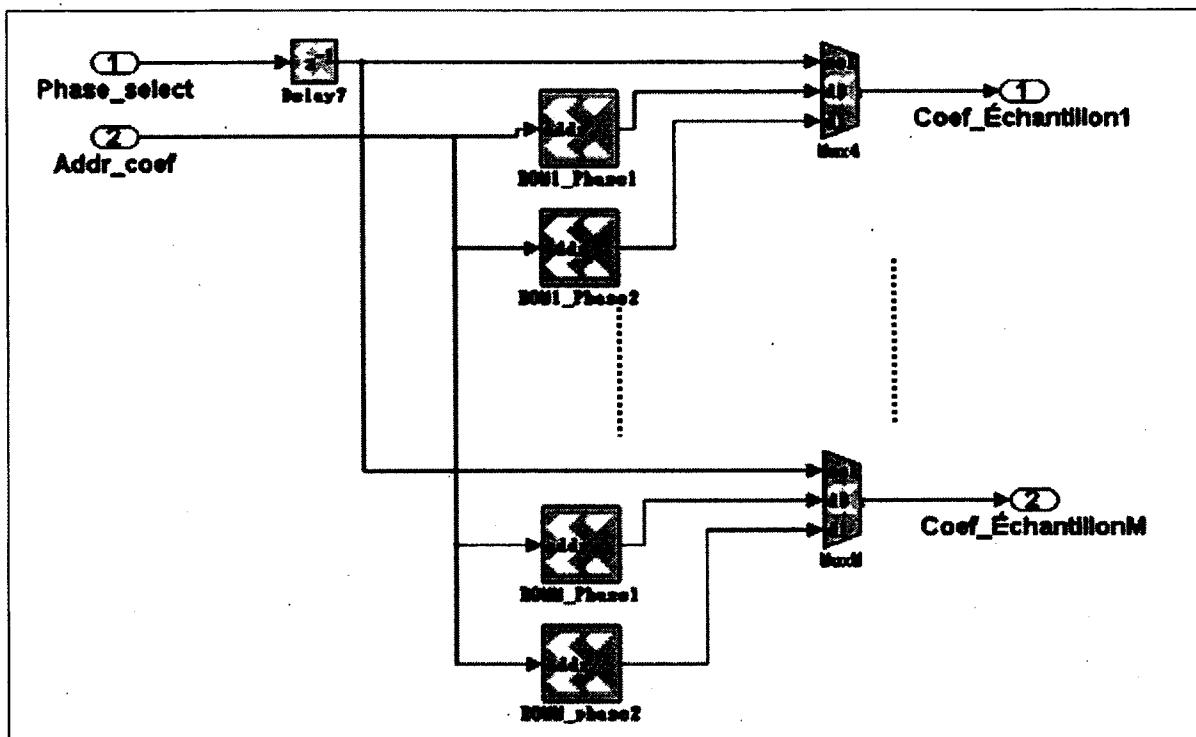

| 4.2.2    Module de filtre de mise en forme.....                                                               | 61         |

| 4.2.3    Générateur chaotique .....                                                                           | 63         |

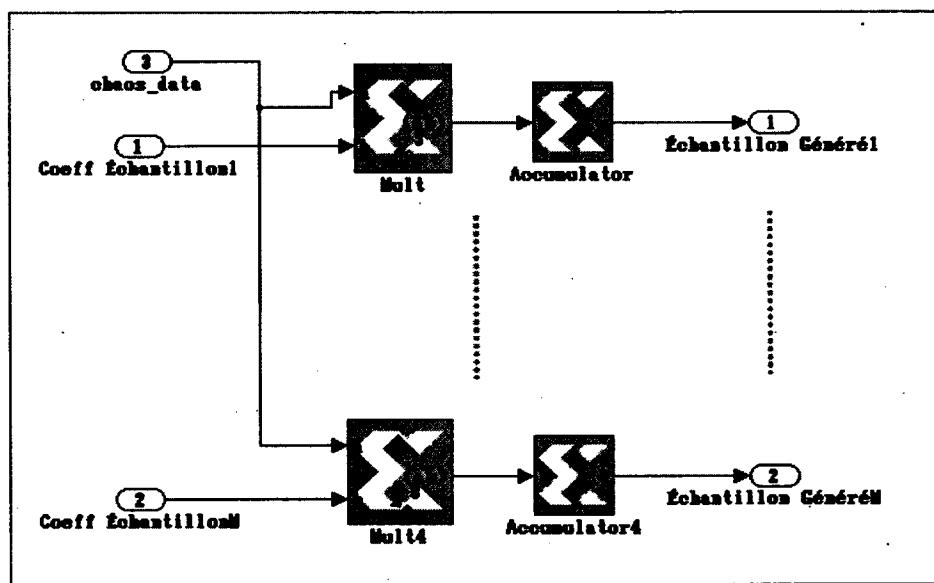

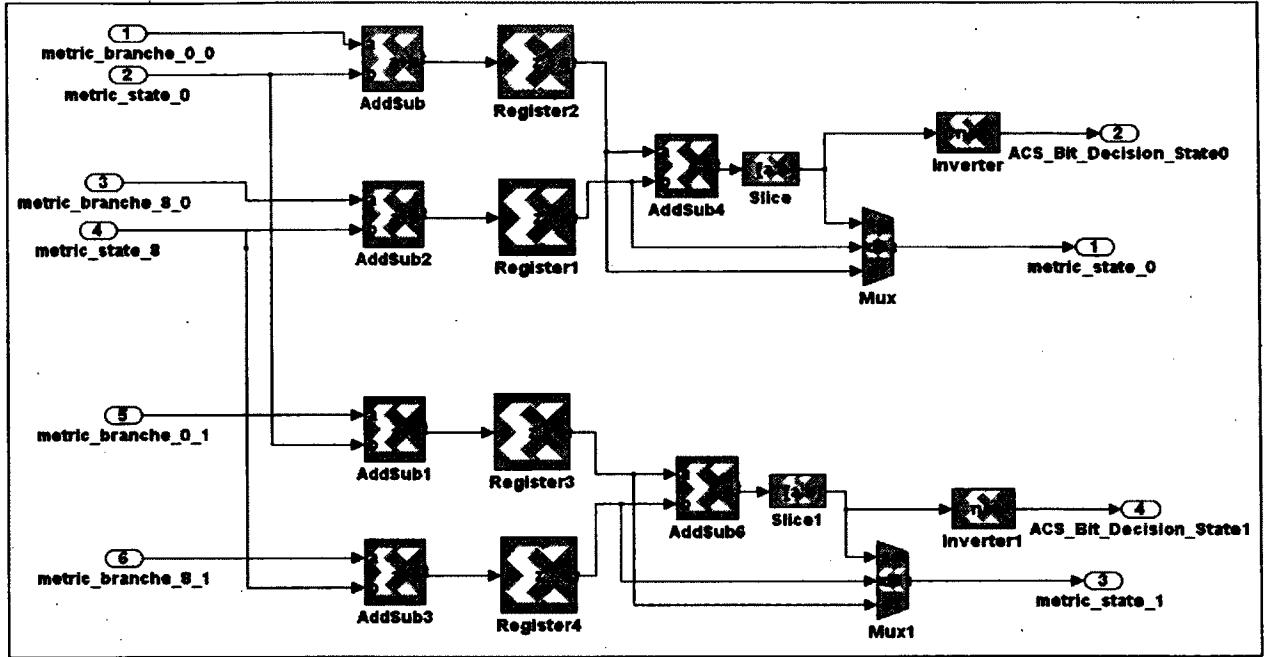

| 4.2.4    Module multiplication accumulation .....                                                             | 65         |

| 4.2.5    Calcul de la métrique euclidienne.....                                                               | 65         |

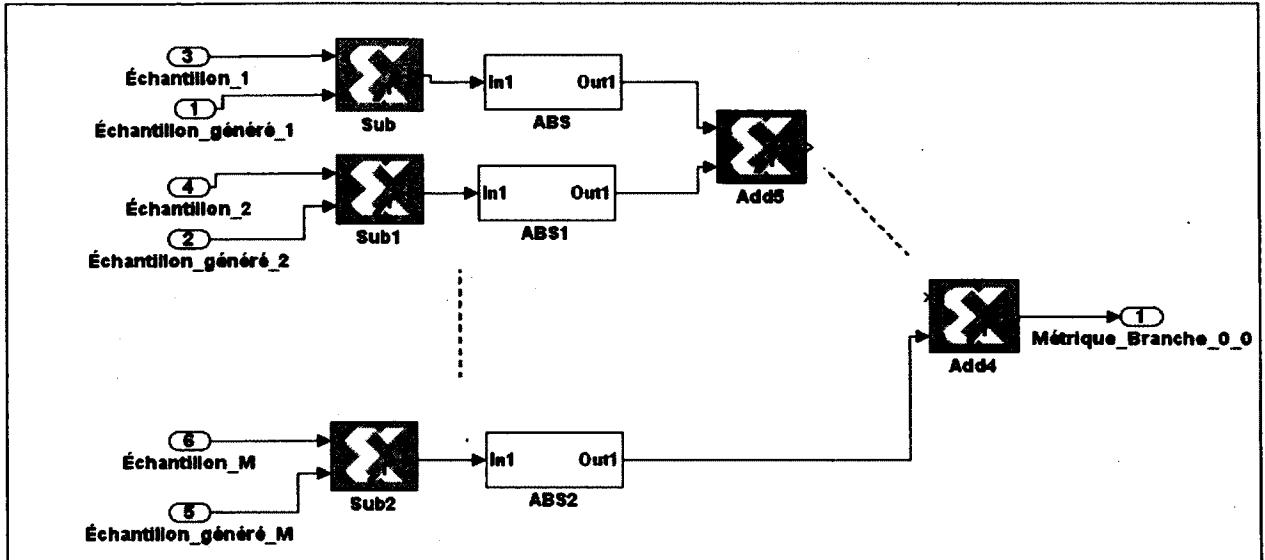

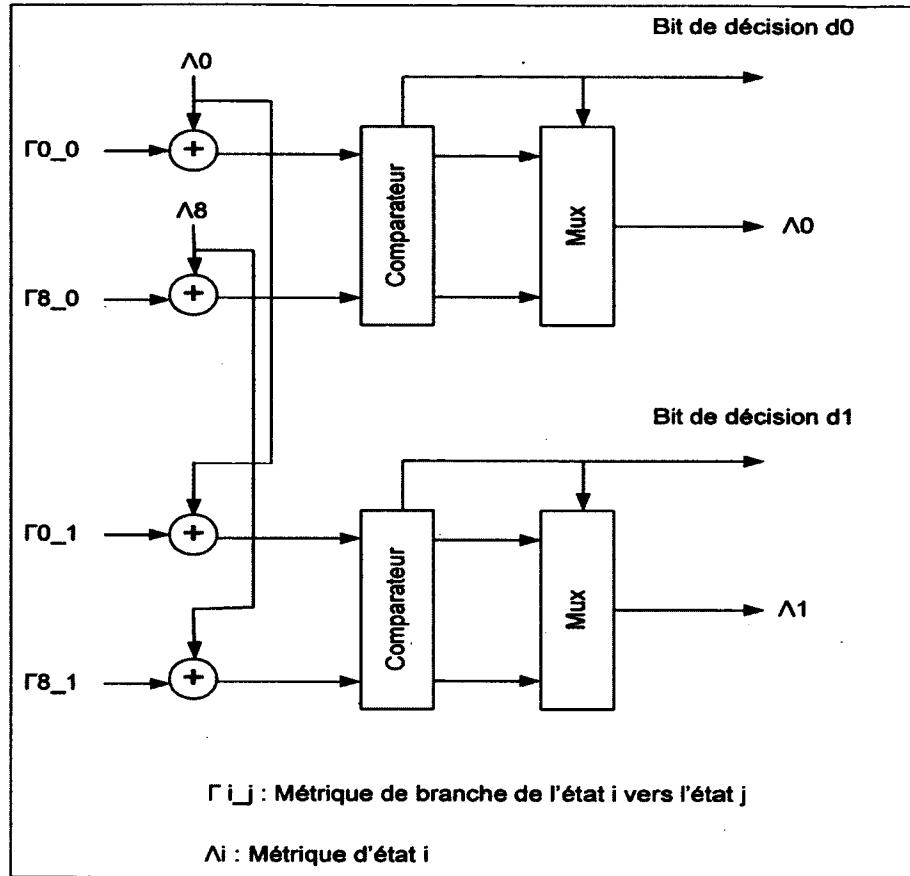

| 4.3    Module de l'Addition-Comparaison-Sélection ACS .....                                                   | 66         |

| 4.4    Unité de gestion de l'historique .....                                                                 | 68         |

| 4.4.1    Gestion de la mémoire .....                                                                          | 69         |

| 4.4.2    Principe de décodage .....                                                                           | 71         |

| 4.5    Unité LIFO.....                                                                                        | 72         |

| 4.6    Contrôle.....                                                                                          | 72         |

| 4.7    Conclusion .....                                                                                       | 75         |

| <b>CHAPITRE 5 IMPLÉMENTATION, TEST ET RÉSULTATS</b>                                                           | <b>76</b>  |

| 5.1    Stratégie d'implémentation.....                                                                        | 76         |

| 5.1.1    Quantification .....                                                                                 | 78         |

| 5.1.2    Plateforme de développement.....                                                                     | 78         |

| 5.2    Test et résultat .....                                                                                 | 79         |

| 5.2.1    Environnement de test.....                                                                           | 79         |

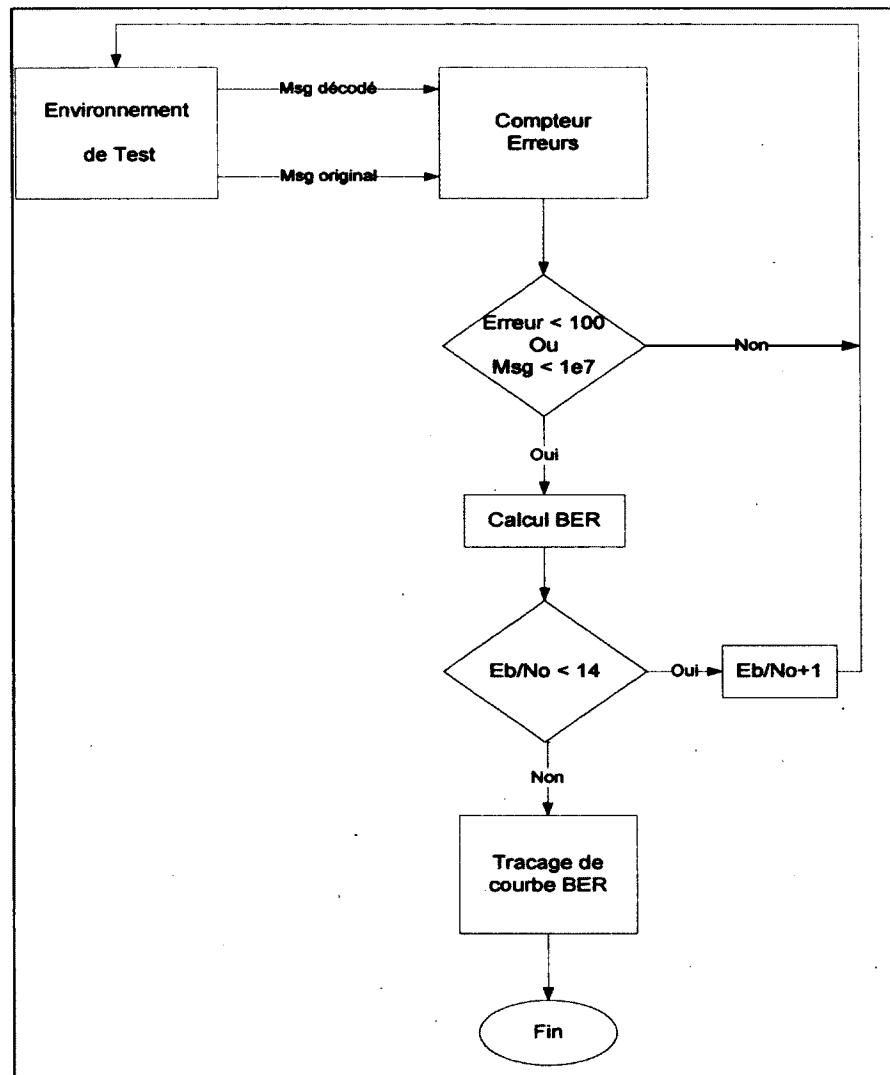

| 5.2.2    Procédure de test .....                                                                              | 81         |

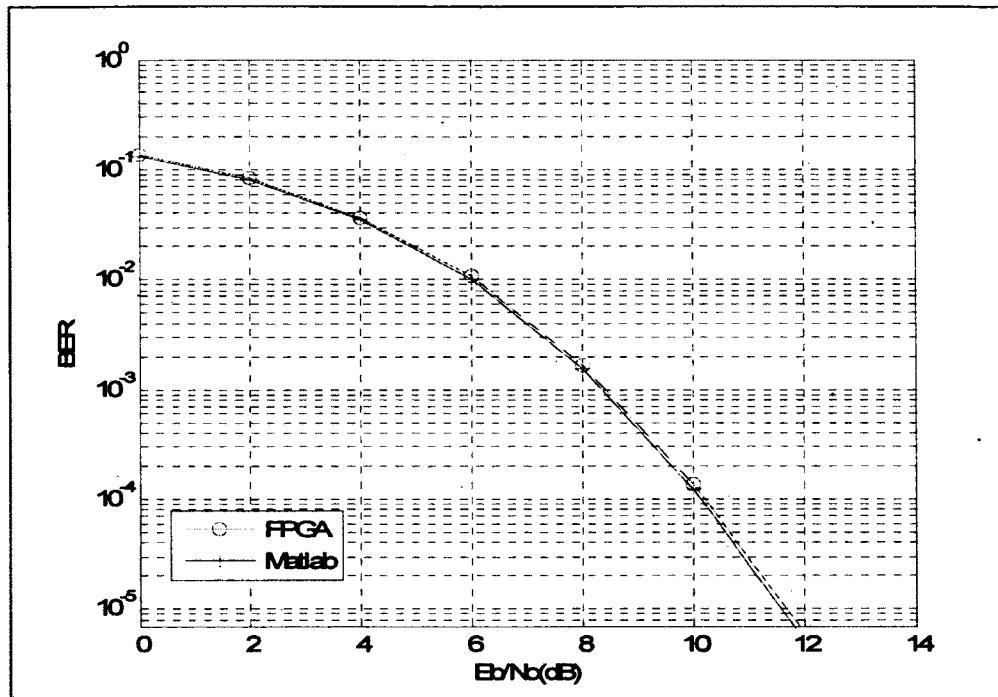

| 5.2.3    Résultat de co-simulation et comparaison avec modèle Matlab .....                                    | 82         |

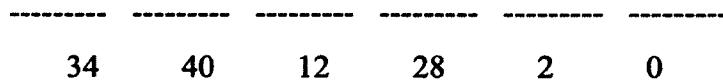

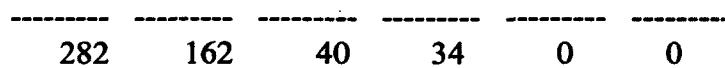

| 5.2.4    Rapport d'implémentation .....                                                                       | 83         |

| 5.3    Conclusion .....                                                                                       | 86         |

| <b>CONCLUSION</b> .....                                                                                       | <b>87</b>  |

| <b>RECOMMANDATIONS</b> .....                                                                                  | <b>89</b>  |

| <b>ANNEXE I RAPPORT APRÈS IMPLÉMENTATION ET ROUTAGE DU<br/>DÉMODULATEUR CHAOTIQUE ET DE SES MODULES</b> ..... | <b>90</b>  |

| <b>BIBLIOGRAPHIE</b> .....                                                                                    | <b>129</b> |

## **LISTE DES TABLEAUX**

|             | <b>Page</b>                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Tableau 4.1 | Initialisation des mémoires ROM .....63                                                                                                |

| Tableau 5.1 | Résumé des résultats après le placement et routage du démodulateur<br>chaotique et de ses modules, ( $D=4$ , $M=2$ , $p=0.1$ ) .....84 |

| Tableau 5.2 | Résumé des résultats après le placement et routage du module BMU<br>avec et sans DSP48, ( $D=4$ , $M=2$ , $p=0.1$ ) .....85            |

| Tableau 5.3 | Calcul du débit net du démodulateur chaotique, ( $D=4$ , $M=2$ , $p=0.1$ ).....86                                                      |

## LISTE DES FIGURES

|             | Page                                                                                     |

|-------------|------------------------------------------------------------------------------------------|

| Figure 1.1  | Implémentation de la SCD.....                                                            |

| Figure 1.2  | Spectre de densité de puissance de la transformation au carré du signal.....             |

| Figure 1.3  | Modulation en amplitude avec enveloppe de durée inférieure à T.....                      |

| Figure 1.4  | Spectre de densité de puissance $Sx^f$ .....                                             |

| Figure 1.5  | Modulation en amplitude avec enveloppe de durée T .....                                  |

| Figure 1.6  | Spectre de densité de puissance de $x(t)^2$ .....                                        |

| Figure 2.1  | Modulation chaotique. ....                                                               |

| Figure 2.2  | Exemple de fonction continue .....                                                       |

| Figure 2.3  | Diagramme de Cobweb.....                                                                 |

| Figure 2.4  | Signal chaotique de l'orbite $0^+(0.5)$ de $f(x)$ pour les itérations 60 à 90.....       |

| Figure 2.5  | Système de communication par masquage chaotique.....                                     |

| Figure 2.6  | Système de communication CSK cohérent.....                                               |

| Figure 2.7  | Système de communication de modulation chaotique basée sur la dynamique symbolique ..... |

| Figure 2.8  | Principe de synchronisation identique. ....                                              |

| Figure 2.9  | Fonction de $f(x)$ . ....                                                                |

| Figure 2.10 | Fonction inverse de $f(x)$ . ....                                                        |

| Figure 3.1  | Système de communication chaotique.....                                                  |

| Figure 3.2  | Fonction chaotique.....                                                                  |

| Figure 3.3  | Séquence chaotique pour $p=0$ , $p=0.5$ et $X[N]=0.65$ . ....                            |

| Figure 3.4  | Structure du modulateur chaotique.....                                                   |

|             |                                                                                                           |    |

|-------------|-----------------------------------------------------------------------------------------------------------|----|

| Figure 3.5  | Fonction chaotique inverse.....                                                                           | 30 |

| Figure 3.6  | Module de phase aléatoire.....                                                                            | 32 |

| Figure 3.7  | Signal $x[n]$ échantillonné par un facteur de $M=5$ .....                                                 | 32 |

| Figure 3.8  | Réponse fréquentielle du filtre cosinus surélevé.....                                                     | 33 |

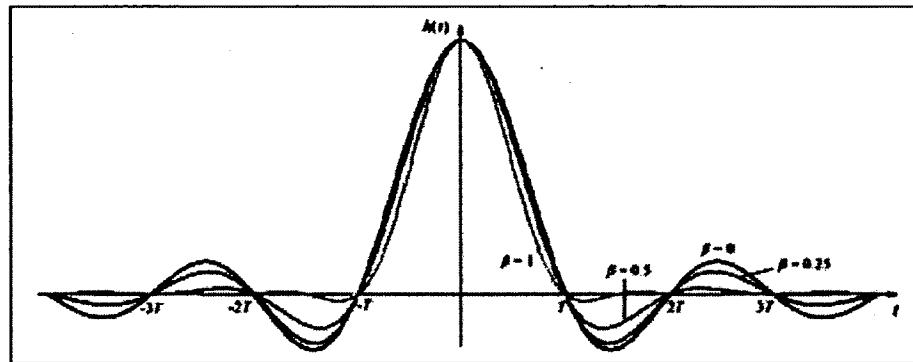

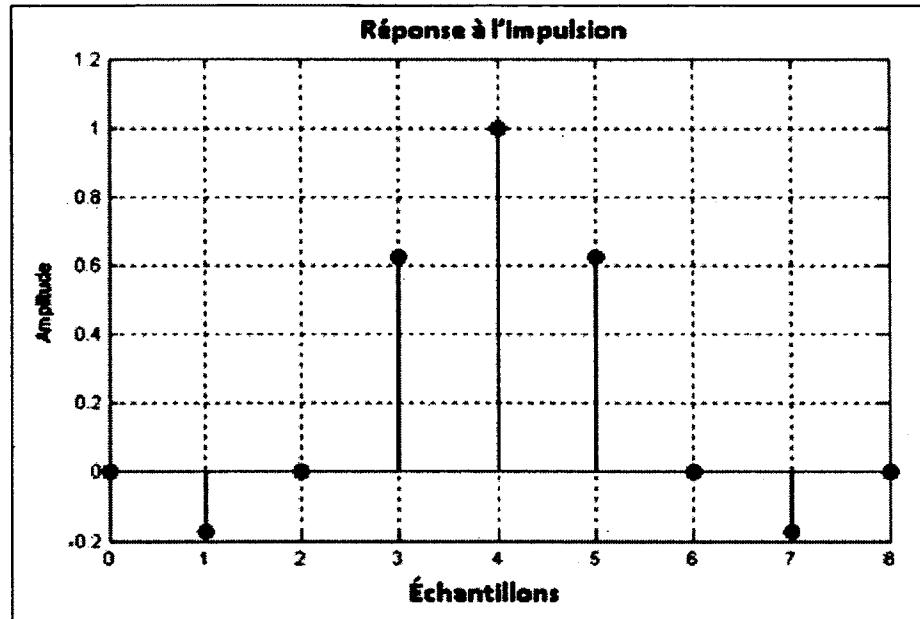

| Figure 3.9  | Réponse à l'impulsion du filtre cosinus surélevé.....                                                     | 34 |

| Figure 3.10 | Impulsions cosinus surélevé consécutives.....                                                             | 34 |

| Figure 3.11 | Mémoire induite par la phase aléatoire, $M=2$ , $D=4$ .....                                               | 36 |

| Figure 3.12 | Treillis utilisant deux états par itération de séquence chaotique.....                                    | 38 |

| Figure 3.13 | Diagramme de treillis adapté pour $h(t)$ et $\Theta(t)$ .....                                             | 39 |

| Figure 3.14 | ACS.....                                                                                                  | 42 |

| Figure 3.15 | Test de la cyclostationnarité du signal.....                                                              | 43 |

| Figure 3.16 | Paramètres du système.....                                                                                | 43 |

| Figure 3.17 | PSD de la transformation au carré du signal de transmission sans phase aléatoire, $M=3$ .....             | 44 |

| Figure 3.18 | PSD de la transformation au carré du signal de transmission avec phase aléatoire, $M=3$ .....             | 45 |

| Figure 3.19 | PSD de la transformation au carré du signal de transmission sans phase aléatoire, $M=5$ .....             | 45 |

| Figure 3.20 | PSD de la transformation au carré du signal de transmission avec phase aléatoire, $M=5$ .....             | 46 |

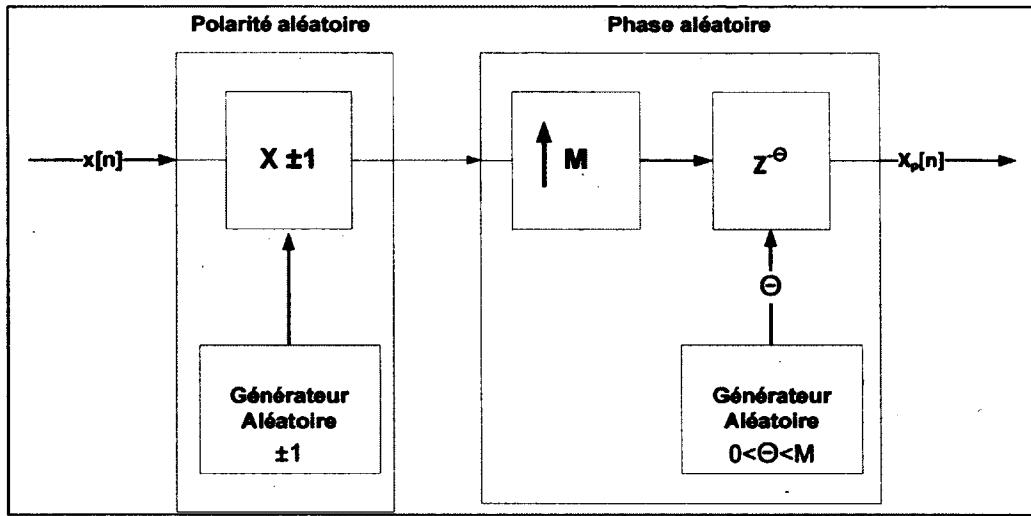

| Figure 3.21 | Module de polarité et phase aléatoire.....                                                                | 47 |

| Figure 3.22 | PSD de la transformation au carré du signal de transmission avec polarité et phase aléatoire, $M=3$ ..... | 47 |

| Figure 3.23 | PSD de la transformation au carré du signal de transmission avec polarité et phase aléatoire, $M=5$ ..... | 48 |

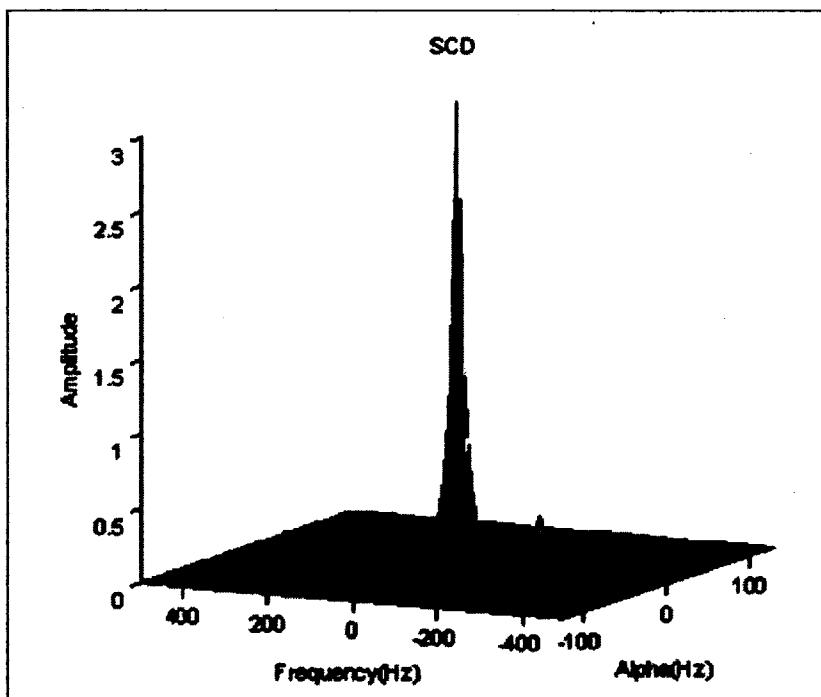

| Figure 3.24 | SCD sans polarité et phase aléatoire, $M=5$ .....                                                         | 49 |

| Figure 3.25 | SCD avec polarité et phase aléatoire, $M=5$ .....                                                         | 49 |

|             |                                                                   |    |

|-------------|-------------------------------------------------------------------|----|

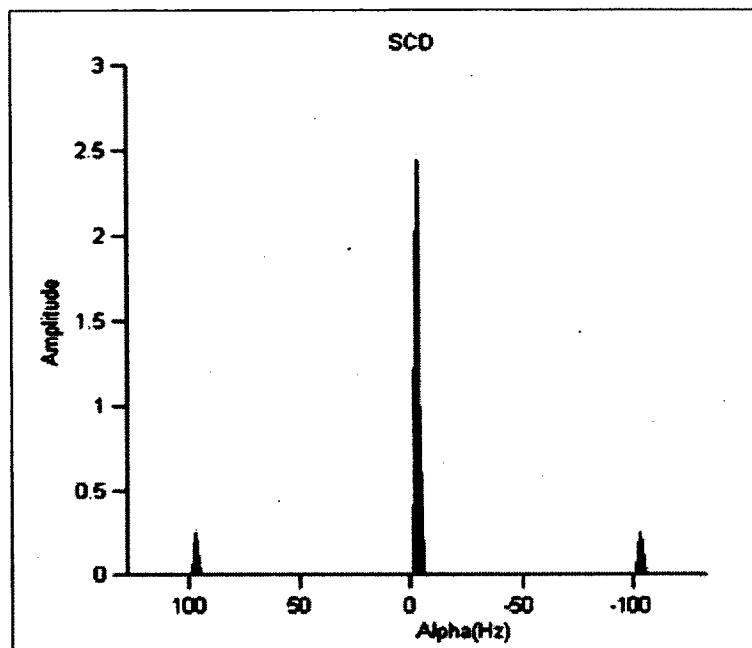

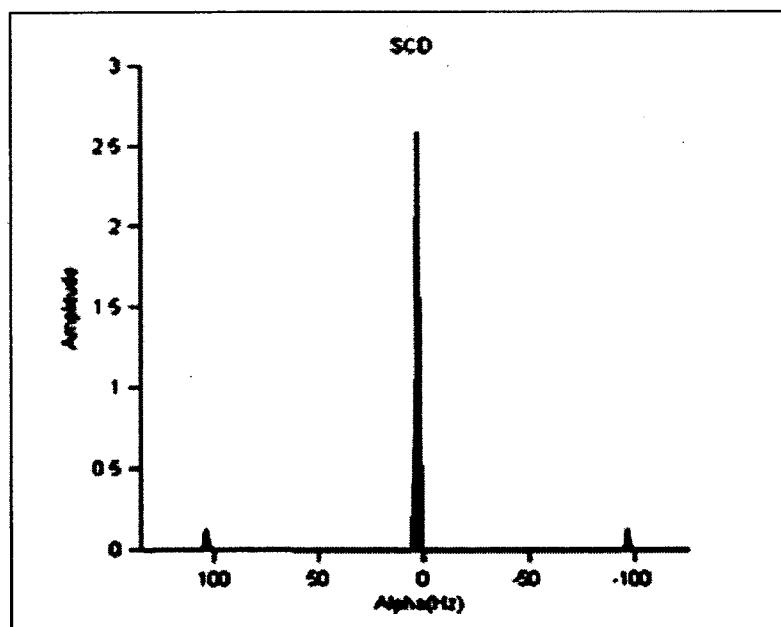

| Figure 3.26 | SCD vue alpha avec polarité et phase aléatoire, M=5 .....         | 50 |

| Figure 3.27 | SCD vue alpha sans polarité et phase aléatoire, M=5.....          | 50 |

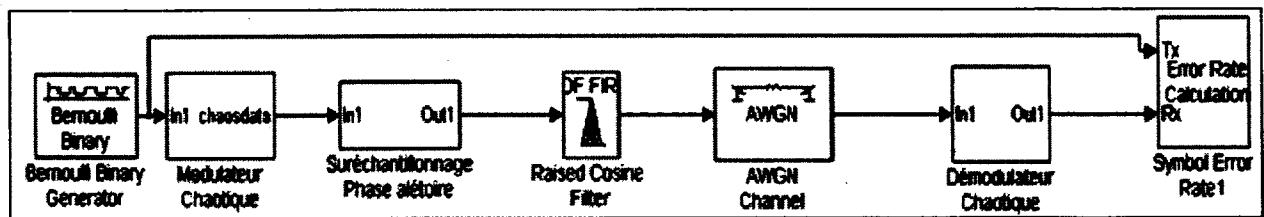

| Figure 3.28 | Environnement de test du système de communication chaotique. .... | 51 |

| Figure 3.29 | Paramètres du système. ....                                       | 51 |

| Figure 3.30 | Eb/No (dB).....                                                   | 52 |

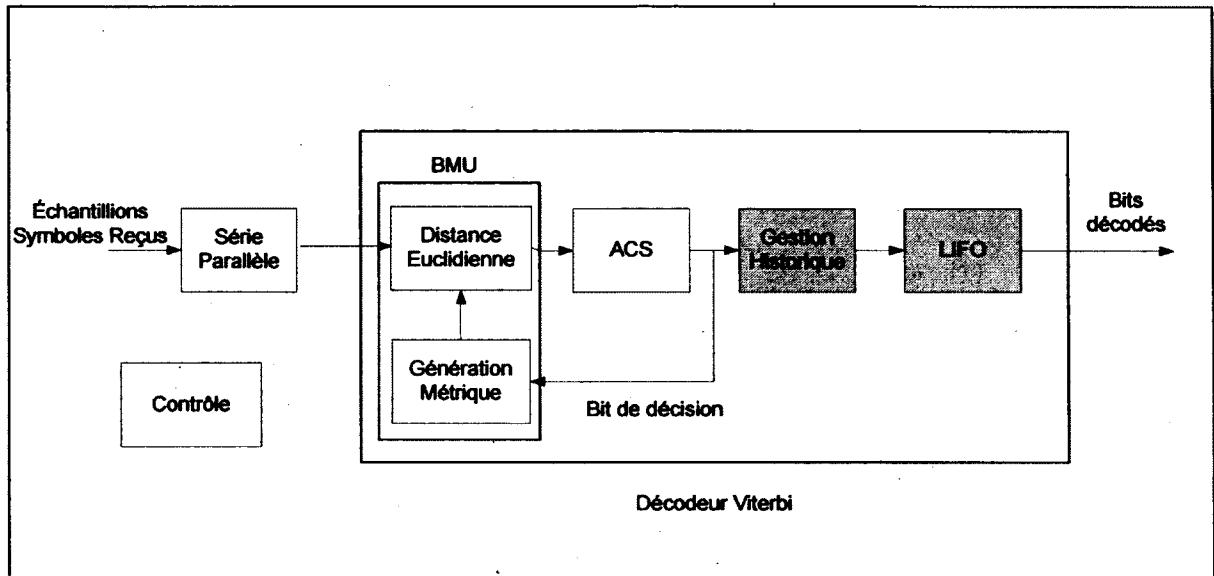

| Figure 4.1  | Schéma bloc du démodulateur. ....                                 | 55 |

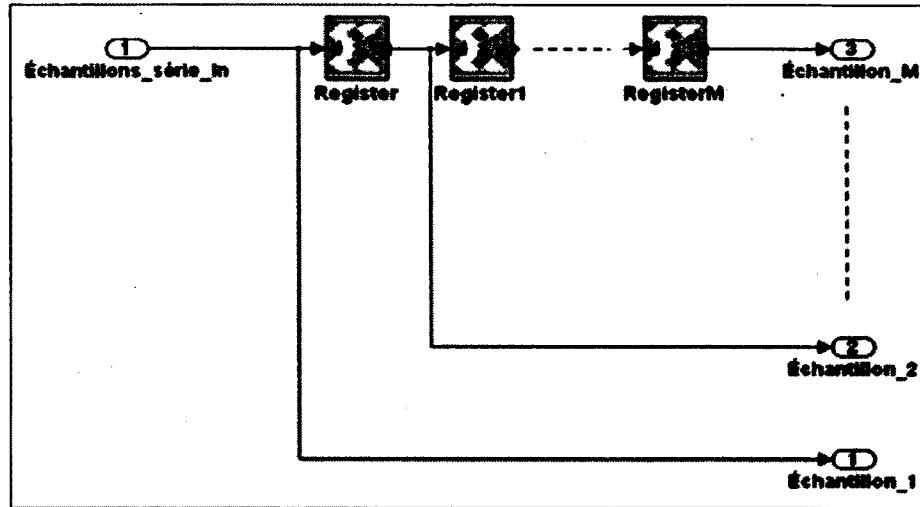

| Figure 4.2  | Schéma bloc(RTL) du module série-parallèle. ....                  | 56 |

| Figure 4.3  | Exemple d'interrelation treillis (D=4). ....                      | 57 |

| Figure 4.4  | Exemple d'initialisation treillis. ....                           | 58 |

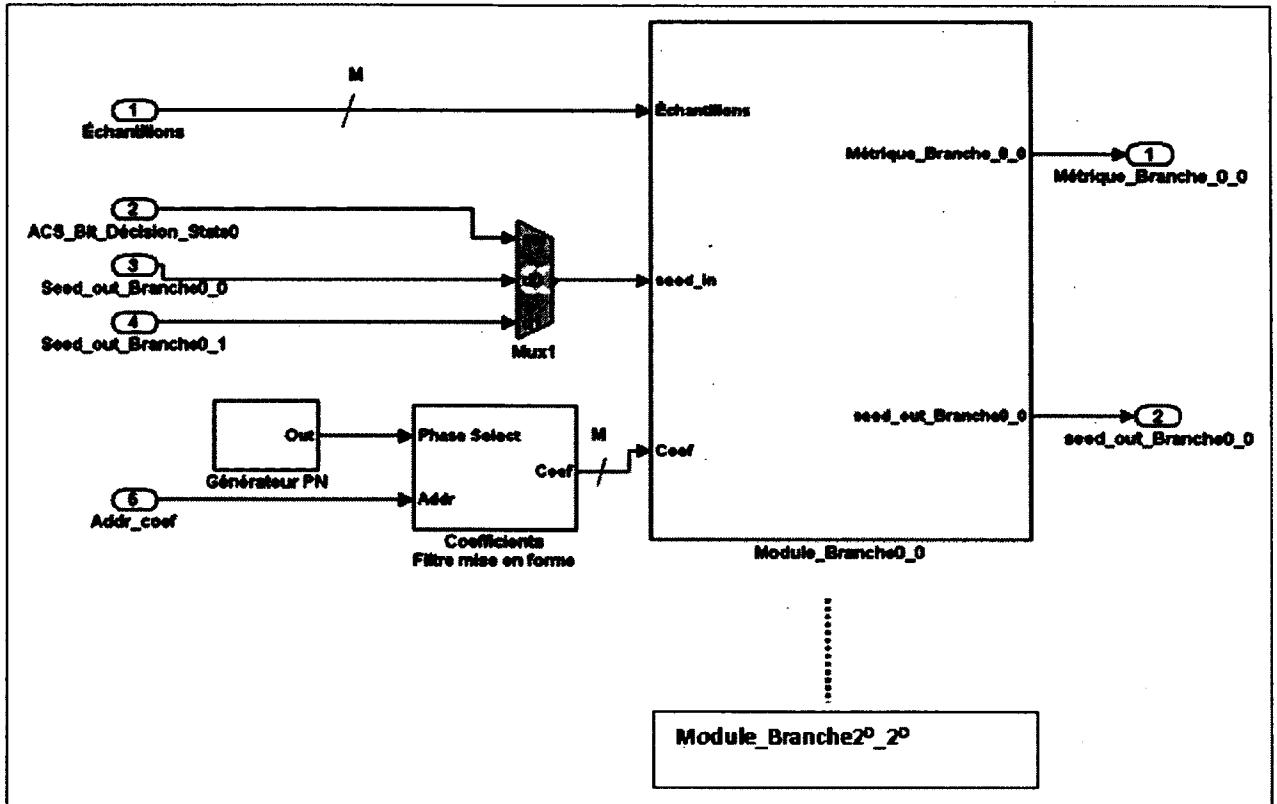

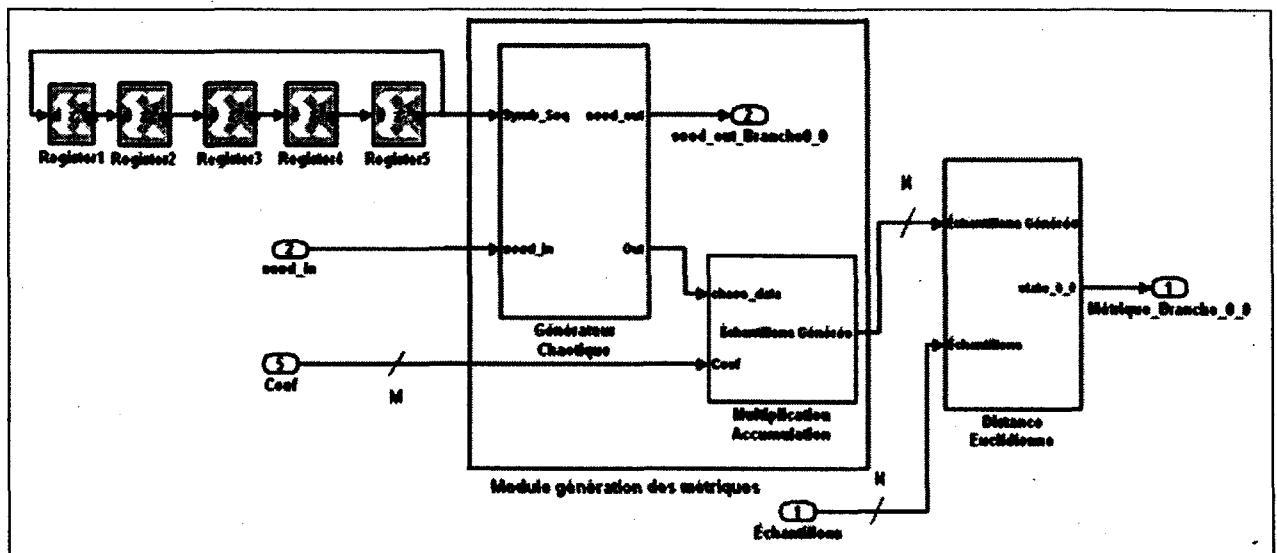

| Figure 4.5  | Diagramme bloc BMU.....                                           | 59 |

| Figure 4.6  | Diagramme bloc Branche. ....                                      | 60 |

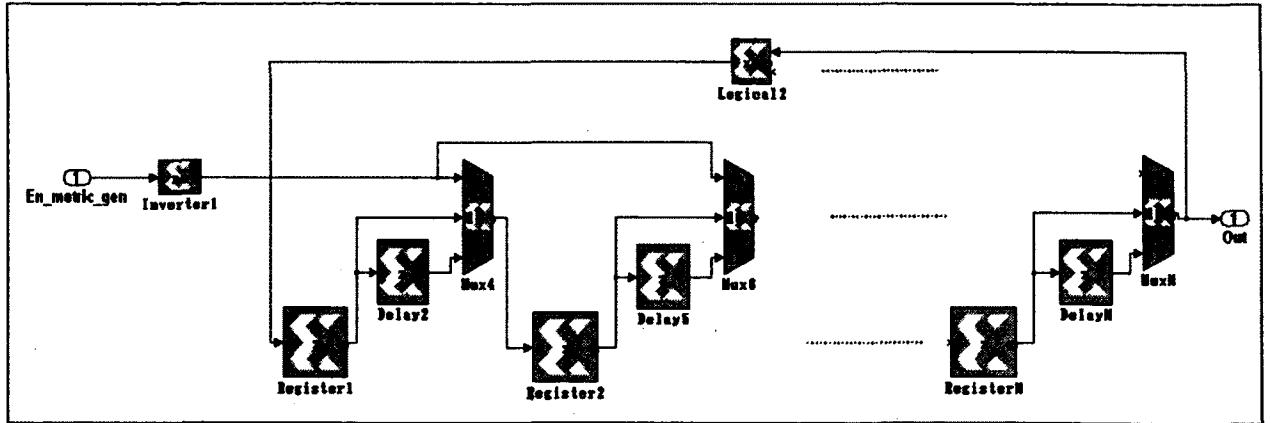

| Figure 4.7  | Module générateur pseudo-aléatoire.....                           | 61 |

| Figure 4.8  | Schéma RTL du module de filtre de mise en forme. ....             | 62 |

| Figure 4.9  | Réponse à l'impulsion $h(t)$ (M=2 D=4). ....                      | 63 |

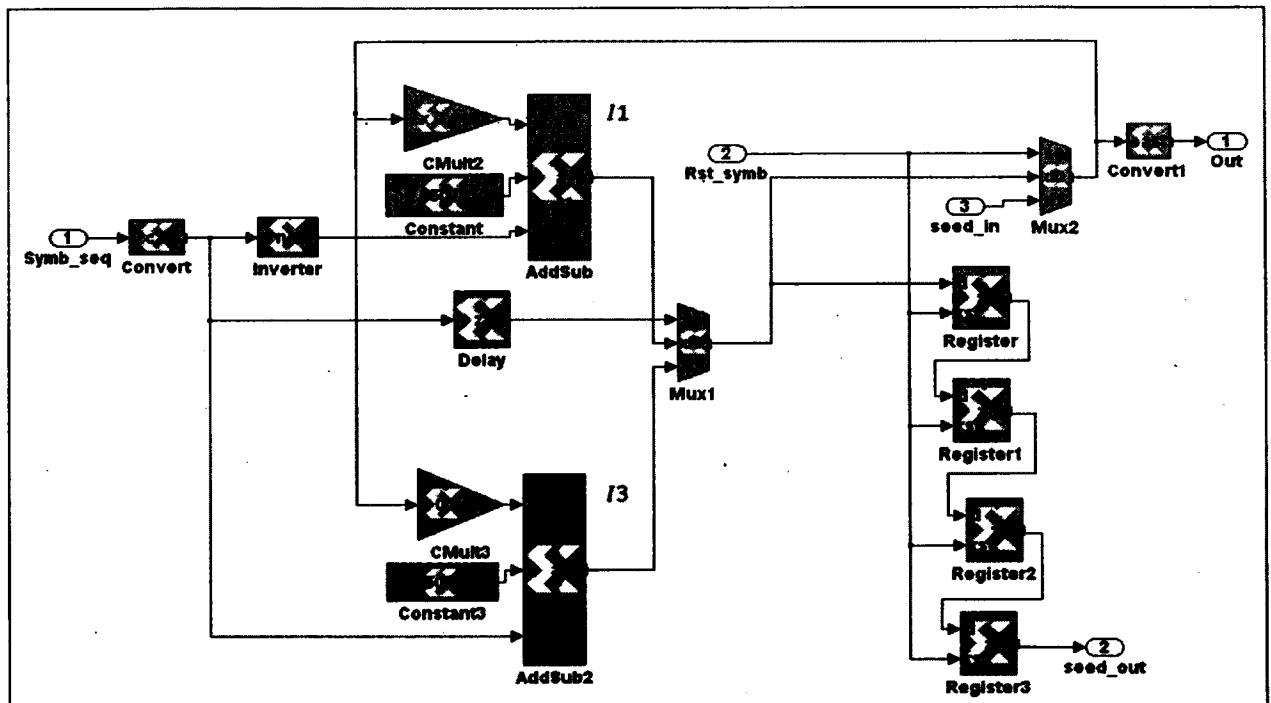

| Figure 4.10 | Schéma RTL du modulateur chaotique, $p=0.1$ . ....                | 64 |

| Figure 4.11 | Schéma RTL du module multiplication accumulation. ....            | 65 |

| Figure 4.12 | Schéma RTL du module distance euclidienne branche. ....           | 66 |

| Figure 4.13 | Module ACS. ....                                                  | 67 |

| Figure 4.14 | Schéma RTL du module ACS.....                                     | 68 |

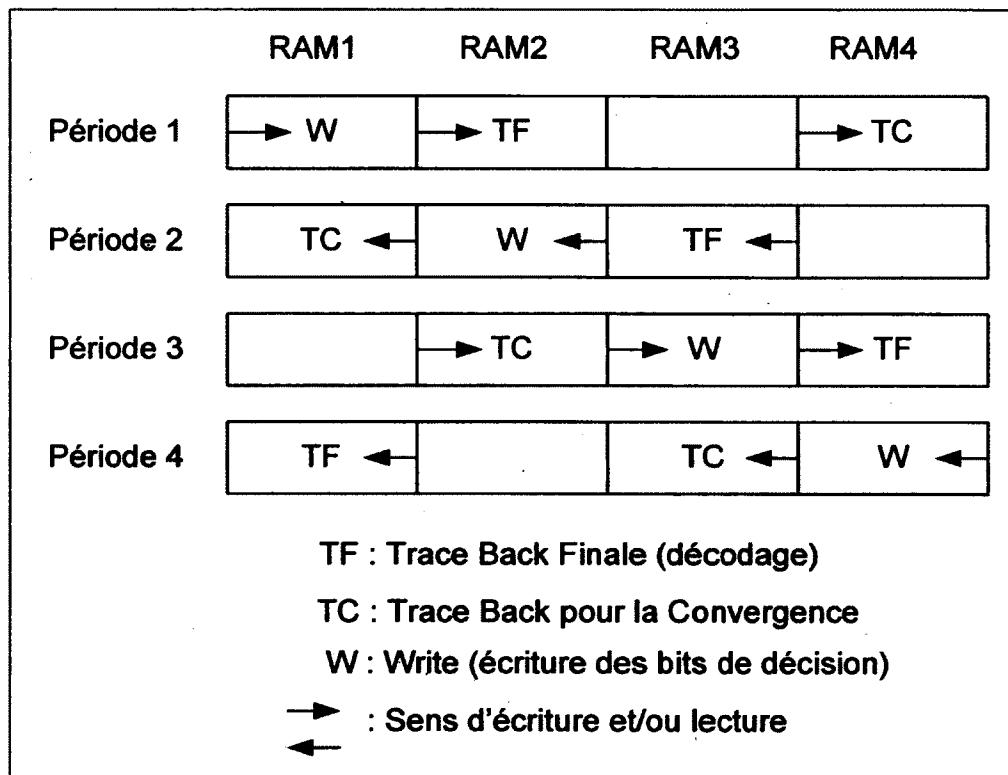

| Figure 4.15 | Flot de la mémoire du TB à quatre RAM. ....                       | 69 |

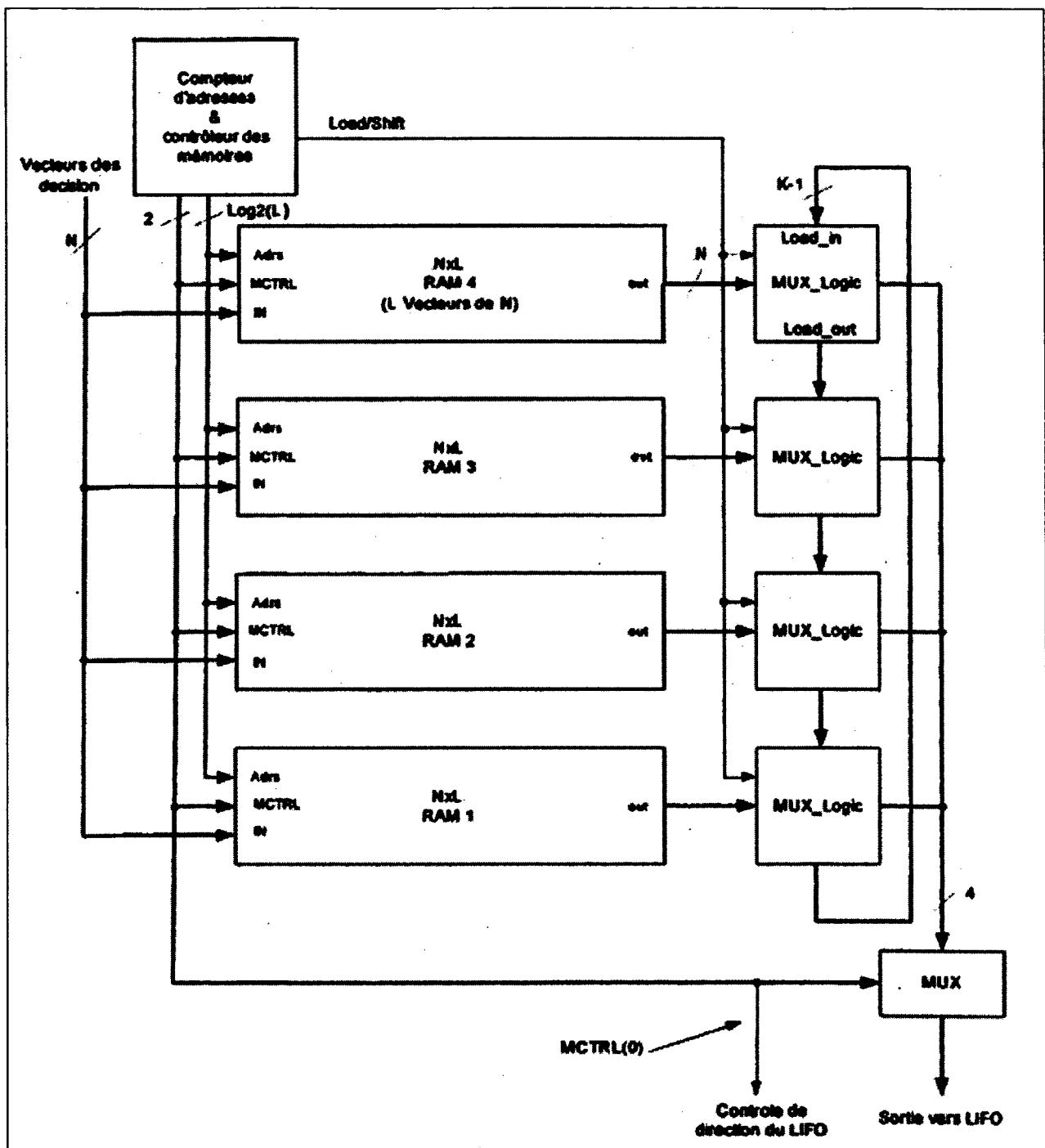

| Figure 4.16 | Diagramme bloc du TB.....                                         | 70 |

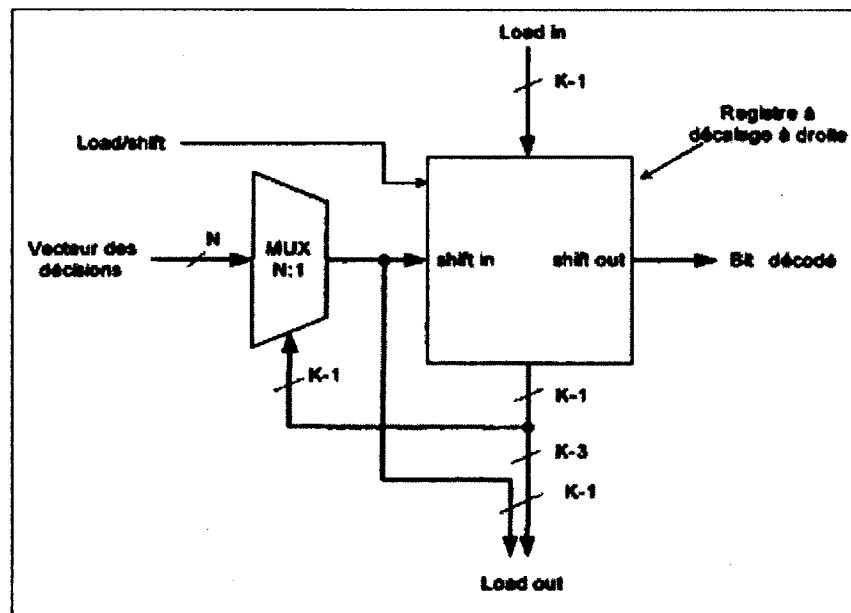

| Figure 4.17 | Bloc Mux_Logic. ....                                              | 71 |

| Figure 4.18 | Schéma RTL du module LIFO. ....                                   | 72 |

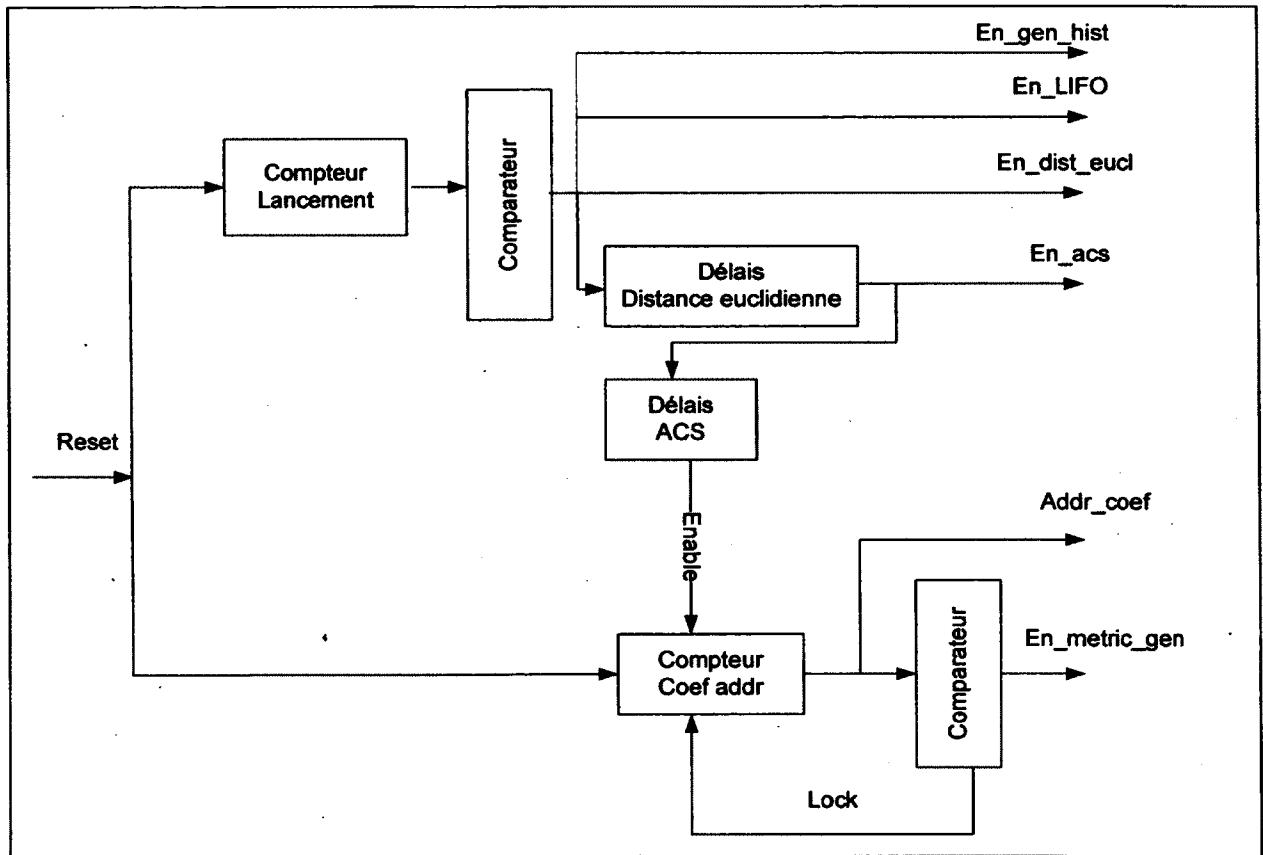

| Figure 4.19 | Schéma bloc du module de contrôle. ....                           | 73 |

|                    |                                                                                                        |           |

|--------------------|--------------------------------------------------------------------------------------------------------|-----------|

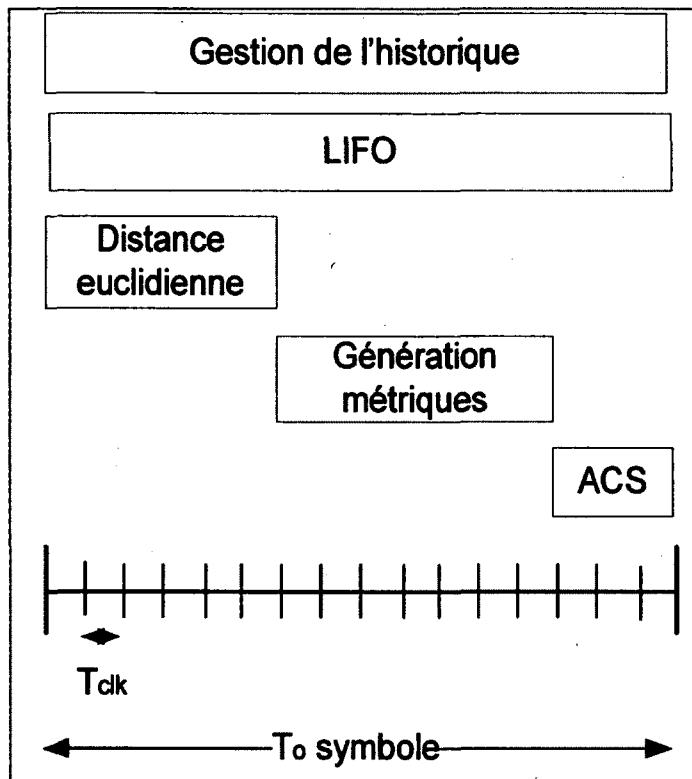

| <b>Figure 4.20</b> | <b>Séquence des opérations des modules du décodeur.....</b>                                            | <b>74</b> |

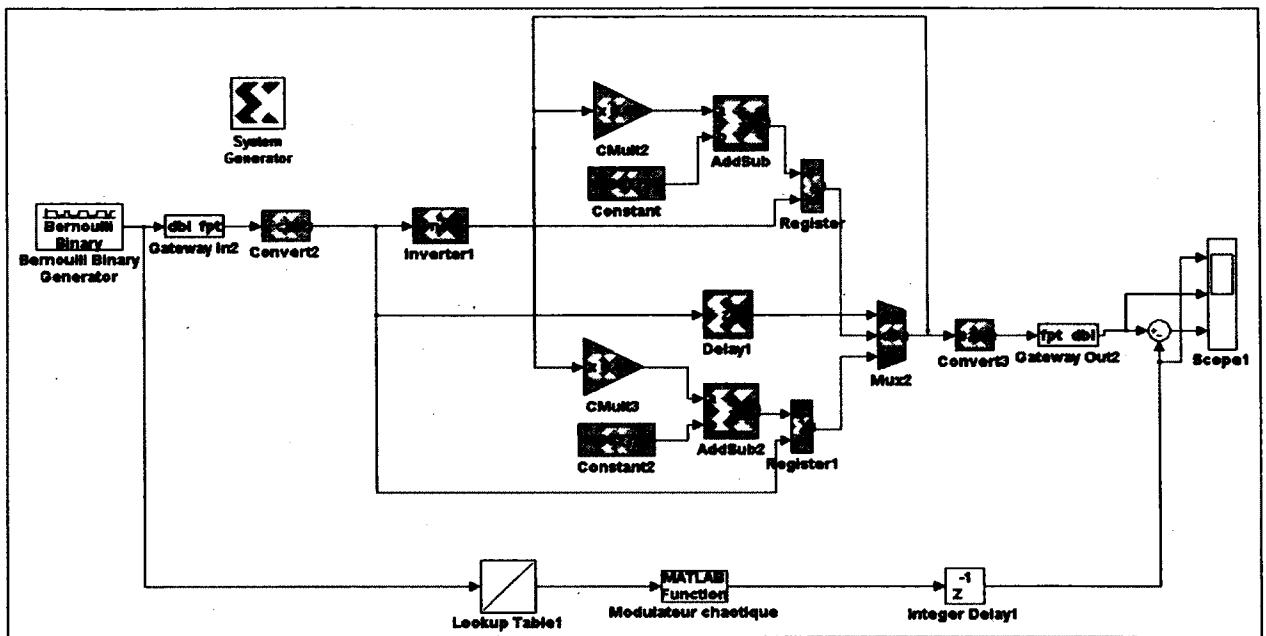

| <b>Figure 5.1</b>  | <b>Environnement de simulation Simulink/System Generator. Test du générateur chaotique, p=0.1.....</b> | <b>77</b> |

| <b>Figure 5.2</b>  | <b>Résultat de comparaison du modulateur chaotique version Matlab et System Generator.....</b>         | <b>77</b> |

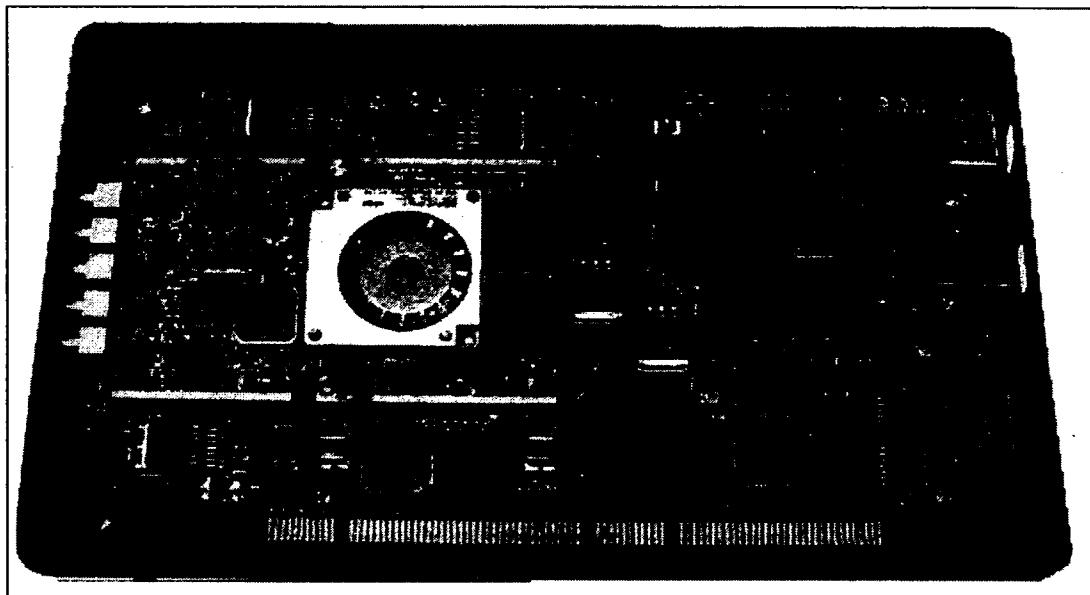

| <b>Figure 5.3</b>  | <b>XtremeDSP Development Kit-IV.....</b>                                                               | <b>79</b> |

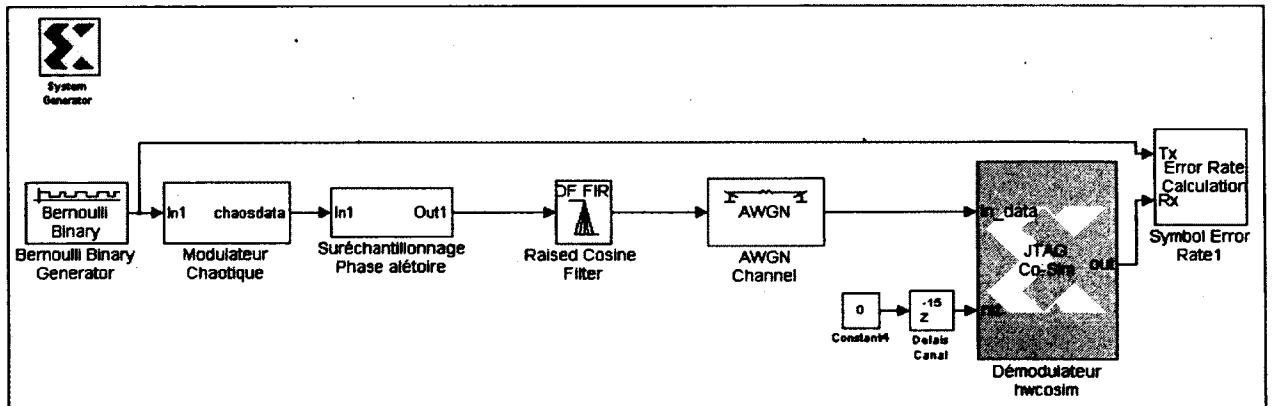

| <b>Figure 5.4</b>  | <b>Environnement de test du démodulateur chaotique.....</b>                                            | <b>80</b> |

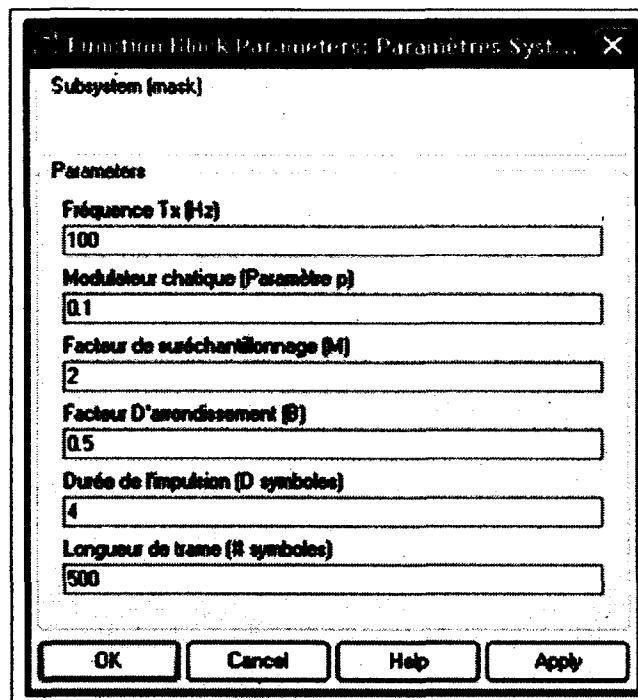

| <b>Figure 5.5</b>  | <b>Paramètres de simulation.....</b>                                                                   | <b>81</b> |

| <b>Figure 5.6</b>  | <b>Procédure de test.....</b>                                                                          | <b>82</b> |

| <b>Figure 5.7</b>  | <b>Courbes BER pour simulation Matlab et co-simulation sur circuit FPGA, (D=4, M=2, p=0.1) .....</b>   | <b>83</b> |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|             |                                             |

|-------------|---------------------------------------------|

| <b>ACS</b>  | Addition comparaison soustraction           |

| <b>BER</b>  | Bit error rate                              |

| <b>BMU</b>  | Branch Metric Unit                          |

| <b>BP</b>   | Bande passante                              |

| <b>CSK</b>  | Chaos shift keying                          |

| <b>FPGA</b> | Field programmable gate array               |

| <b>FW</b>   | Featureless waveform                        |

| <b>HIL</b>  | Hardware in the loop                        |

| <b>HOS</b>  | Higher-order cyclostationarity statistic    |

| <b>LFRS</b> | Linear feedback shift register              |

| <b>LIFO</b> | Last in first out                           |

| <b>LPD</b>  | Low probability of detection                |

| <b>LPI</b>  | Low probability of intercept                |

| <b>RAM</b>  | Random access memory                        |

| <b>RIF</b>  | Réponse à impulsion finie                   |

| <b>RTL</b>  | Register transfer level                     |

| <b>SCD</b>  | Spectre de corrélation de densité           |

| <b>SQNR</b> | Rapport de signal à bruit de quantification |

| <b>SNR</b>  | Rapport signal à bruit                      |

| <b>TB</b>   | Trace back                                  |

## **INTRODUCTION**

Dans un environnement militaire, il existe des situations dans lesquelles il est important d'utiliser des méthodes de communications avec faible probabilité d'interception ("Low probability of intercept", LPI) et de détection ("Low probability of detection", LPD). Les signaux modulés chaotiquement sont non linéaires, apériodiques, non corrélés et possèdent une apparence similaire au bruit. Ces caractéristiques en font des candidats idéaux pour des communications LPI et LPD. Malheureusement, les signaux générés à partir de systèmes numériques basés sur la modulation chaotique sont cyclostationnaire [1]. Cette caractéristique cyclostationnaire des signaux chaotiques peut facilement être exploitée lorsqu'ils sont assujettis à une transformation non-linéaire de degré supérieur à un. En effet, ce type de transformation génère des composantes périodiques qui peuvent facilement être détectées lors d'analyse spectrale.

L'objectif de ce mémoire est de proposer un système de communication LPI basée sur la modulation chaotique. Le modulateur chaotique est basé sur la symbolique dynamique. Une technique d'introduction de phase aléatoire appliquée au signal chaotique du système proposé est évaluée afin de rendre le signal chaotique LPI. Il est démontré que cette technique permet d'atténuer le degré de cyclostationnarité du signal modulé chaotiquement. Au récepteur, un algorithme à maximum de vraisemblance est proposé afin d'estimer la séquence transmise. Cet algorithme est un décodeur de Viterbi adapté pour la modulation chaotique basée sur la symbolique dynamique et à la technique d'introduction de phase aléatoire proposée. Ainsi, dans ce mémoire, deux contributions y sont faites. La première contribution porte sur une technique de phase aléatoire proposée dans le but de rendre le signal chaotique LPI. La deuxième contribution porte sur la modification du décodeur de Viterbi employé par [2] pour démoduler un signal chaotique sur lequel une phase aléatoire est appliquée et dont le modulateur est basé sur la symbolique dynamique.

Afin de faire la démonstration de la faisabilité du système proposé. Le démodulateur chaotique, le module le plus complexe du système de communication, est implémenté dans un ("Field Prommable Gate Array", FPGA) de type Virtex-4. Enfin, les performances en terme de ("Bit Error Rate", BER) entre le modèle du système de communication réalisé sous le logiciel Matlab et de son implémentation matérielle sont évaluées.

Le premier chapitre passe en revue les caractéristiques nécessaires pour que des communications soient LPI/LPD en plus de définir la problématique de l'utilisation de signaux modulés chaotiquement dans un contexte LPI/LPD. Le deuxième chapitre expose la théorie du fonctionnement de la modulation chaotique. Le troisième chapitre propose un système de communication sans-fil LPI basé sur la modulation chaotique. Une analyse du degré de cyclostationnarité du signal de transmission est réalisée en plus d'une évaluation des performances du système. Le quatrième chapitre présente l'architecture matérielle du démodulateur chaotique. Enfin, le cinquième et dernier chapitre évalue les performances du démodulateur chaotique implémenté dans un FPGA.

## **CHAPITRE 1**

### **COMMUNICATION LPI/LPD**

Ce chapitre passe en revue les caractéristiques nécessaires pour que des communications soient de faible probabilité d'interception ("Low probability of intercept", LPI) et de faible probabilité de détection ("Low probability of detection", LPD). La problématique de l'utilisation des signaux chaotiques dans un contexte LPI/LPD y est définie en plus des objectifs et hypothèses de ce projet.

#### **1.1 Communications LPI/LPD et signaux chaotiques**

Dans un environnement militaire, il existe des situations pour lesquelles il est important d'utiliser des méthodes de communications avec faible probabilité d'interception (LPI) et de détection (LPD). Par exemple, il serait néfaste qu'un receveur ennemi puisse détecter ou caractériser le signal de transmission afin de localiser le transmetteur ou d'en extraire de l'information.

Afin de bien définir la problématique, il est important de définir les termes LPI et LPD. Le terme LPD désigne un signal dont la présence est difficilement discernable de l'environnement qu'il partage avec un observateur ennemi qui possède des moyens de détection sophistiqués. Contrairement au signal LPD, un signal défini LPI est détectable. Cependant, un observateur ne peut extraire aucune information pouvant caractériser le signal transmis en termes de type, modulation, paramètres, fréquence de porteuse, fréquence de symbole, etc [3]. Ainsi, un signal LPI est un signal ne possédant aucun paramètre exploitable ("featureless waveforms", FW).

Généralement les signaux classés LPI/LPD tentent d'imiter des processus présents dans la nature comme le bruit thermique. Les caractéristiques les plus importantes sont, mais ne se limitent pas à : une distribution gaussienne avec une moyenne nulle, une auto-corrélation

impulsive, un spectre de puissance faible et uniformément distribué, une phase aléatoire, une amplitude aléatoire, et une nature apériodique.

Les signaux modulés chaotiquement sont non linéaires, apériodiques, non corrélés et possèdent une apparence similaire au bruit. Ces caractéristiques en font des candidats idéaux pour les communications LPI et LPD [4, 5]. Malheureusement, la majorité des signaux créés par l'homme possèdent des caractéristiques exploitables qui sont induites à partir de transformations périodiques comme l'échantillonnage, la modulation, le multiplexage et le codage, pour en nommer quelques-unes [6]. Ces signaux peuvent être modélisés comme étant cyclostationnaires. Bien qu'un signal cyclostationnaire ne soit pas périodique, quand il est assujetti à une transformation non linéaire de degré supérieur à un, il génère des composantes périodiques. Ces composantes périodiques résultant de transformations non linéaires peuvent être représentées par des raies spectrales et exploitées lors d'une analyse spectrale. Les signaux générés à partir de systèmes numériques basés sur la modulation chaotique sont cyclostationnaires [1]. Cette cyclostationnarité est induite par un taux de symbole constant du modulateur.

Ceci encapsule donc la problématique et justifie notre intérêt de créer une forme d'onde LPI basée sur la modulation chaotique. De plus, dans le cadre de ce projet, l'aspect LPD ne sera pas abordé étant donné qu'aucune technique d'étalement de spectre et de codage n'est utilisée afin de transmettre le signal de transmission sous le seuil du bruit thermique pour le rendre difficilement discernable de son environnement.

### **1.1.1 Résumé des caractéristiques d'un signal chaotique LPI/LPD**

Cette section présente de manière plus détaillée les caractéristiques LPI/LPD des signaux modulés chaotiquement.

### **Non-linéarité**

La nature non linéaire des systèmes chaotiques réduit leur vulnérabilité. Lors de l'analyse d'une séquence chaotique par un récepteur ennemi, il devient plus difficile de déduire la fonction qui permet de générer cette séquence. Par exemple, afin de rendre moins vulnérables les séquences pseudo aléatoires générées de façon linéaire, les sorties de différents étages de registre à décalage sont combinées de façon non linéaire. Ceci permet d'obtenir une séquence non linéaire dont il est plus difficile de déduire les interconnexions de rétroaction des registres[7].

### **Auto corrélation impulsive et faible inter corrélation**

L'intercorrélation entre deux séquences tend à être faible due à la propriété de sensibilité aux conditions initiales intrinsèques aux systèmes chaotiques. Les séquences générées à partir de deux conditions initiales différentes divergent exponentiellement. De plus, grâce à cette même propriété la fonction d'autocorrélation diminue rapidement. Le spectre de fréquence associé avec cette fonction d'autocorrélation est un signal à large bande avec un spectre de puissance uniformément distribué [8].

### **Nature apériodique**

Les conditions de sensibilité aux conditions initiales, de transitivité et de point périodique dense que doivent respecter les systèmes chaotiques les forcent à constamment visiter de nouvelles régions de leurs domaines générant ainsi de nouvelles séquences [9]. Ainsi, une séquence d'information transmise à répétition est représentée à chaque fois par une séquence chaotique différente. Les séquences générées sont apériodiques et généralement caractérisées comme ayant une apparence de bruit blanc ce qui les rend difficilement détectables par auto-corrélation.

## Cyclostationnarité

Tel que mentionné précédemment, les systèmes numériques basés sur la modulation chaotique sont cyclostationnaires dus à leur taux de symbole constant. Évidemment, cette caractéristique est indésirable puisqu'elle peut être exploitée par un récepteur ennemi. La suppression ou l'atténuation de cette caractéristique devient incontournable et, en fait, le but de ce projet afin d'obtenir un signal chaotique LPI. Un processus ne possédant aucune caractéristique cyclostationnaire est dit stationnaire. Le bruit thermique est un exemple de processus stationnaire.

### 1.2 Méthodes de détection de la cyclostationnarité

La théorie de la cyclostationnarité d'ordre deux forme la base à partir de laquelle la théorie de la cyclostationnarité d'ordre supérieur ("Higher-Order Cyclostationarity Statistic", HOCS) fut développée. Dans le cadre de ce projet, seules les propriétés cyclostationnaires de deuxième ordre sont abordées étant donné que les algorithmes utilisés par la théorie des HOCS demandent une puissance de calcul beaucoup plus importante [10].

Deux transformations quadratiques sont utilisées pour détecter et caractériser les propriétés cyclostationnaires d'ordre deux d'un signal: la fonction de densité de corrélation spectrale ("Spectral Correlation Density", SCD) et le spectre de densité de puissance de la transformation au carré du signal.

#### 1.2.1 Fonction de densité de corrélation spectrale

La fonction SCD (Voir Équation (1.6)) est présentée utilisant une approche non probabiliste basée sur la moyenne dans le temps [10]. Un processus  $x(t)$  à temps discret est dit cyclostationnaire si sa fonction d'autocorrélation est périodique (Voir Équation (1.1)).

$$R_x(t, \tau) = \langle x(t)x^*(t - \tau) \rangle \quad (1.1)$$

$$\langle \cdot \rangle \stackrel{\Delta}{=} \lim_{T \rightarrow \infty} \frac{1}{2T + 1} \sum_{t=-T}^T (\cdot) \quad (1.2)$$

Où \* représente le conjugué complexe. Étant donné que la fonction d'autocorrélation est périodique, elle peut être représentée par ses coefficients de Fourier (*Voir Équation (1.3)*). Le terme  $\exp[i\pi\alpha t]$  est introduit dans l'équation (1.3) afin que la théorie dans le domaine discret corresponde à la théorie dans le domaine continu [10]. L'équation (1.3) peut être réexprimée en factorisant le terme  $\exp[i\pi\alpha t]$ . On obtient alors l'équation (1.4) que l'on nomme fonction d'autocorrélation cyclique.

$$R_x^\alpha(\tau) = \langle x(t)x^*(t - \tau)e^{-i2\pi\alpha \cdot t} \rangle e^{i\pi\alpha \cdot t} \quad (1.3)$$

$$R_x^\alpha(\tau) = \left\langle [x(t)e^{-i\pi\alpha \cdot t}] \cdot [x(t - \tau)e^{+i\pi\alpha(t - \tau)}] \right\rangle \quad (1.4)$$

La fonction d'autocorrélation cyclique est une transformation quadratique et représente, pour toute fréquence cyclique  $\alpha \neq 0$ , l'intensité des composantes sinusoïdales de fréquence  $\alpha$  résultant de l'autocorrélation. Un processus est dit stationnaire si  $R_x^\alpha(\tau) = 0$  pour toute fréquence cyclique  $\alpha \neq 0$ . Un processus est purement cyclostationnaire d'ordre deux si la fonction d'autocorrélation cyclique est différente non-nulle,  $R_x^\alpha(\tau) \neq 0$ , pour tout  $\alpha$  multiple entier d'une seule fréquence fondamentale  $1/T$  et il est dit cyclostationnaire d'ordre deux dans le sens général si  $R_x^\alpha(\tau) \neq 0$  pour certains  $\alpha$  multiples entiers d'une seule fréquence fondamentale  $1/T$ . De plus, un processus est polycyclostationnaire d'ordre deux s'il possède plusieurs fréquences fondamentales. Ainsi, la période de cyclostationnarité peut correspondre, pour un signal modulé, au taux de symbole, à la fréquence de la porteuse, au taux de code d'étalement, etc [6].

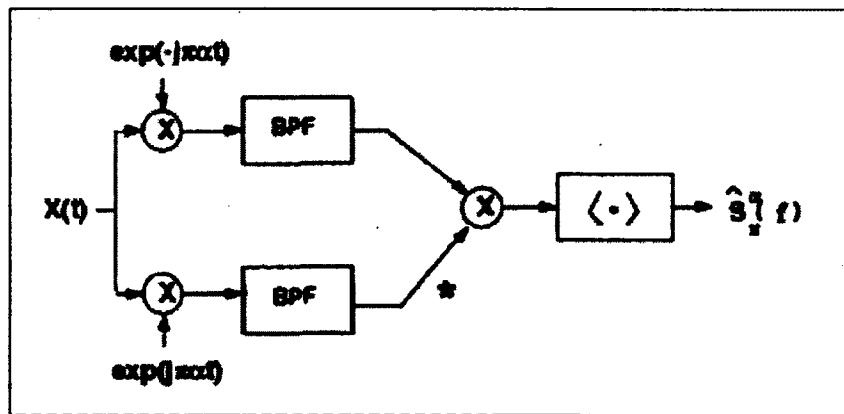

En utilisant la relation cyclique de Wiener, on obtient la fonction de densité spectrale (*Voir équation (1.5)*) et l'estimation de cette fonction représentée par l'équation (1.6) où  $N$  représente le nombre d'échantillons. Cette dernière exprime la fonction SCD comme étant la corrélation entre les composantes spectrales d'un signal  $x(t)$  translaté en fréquence de  $f + \alpha/2$  et  $f - \alpha/2$  pour  $\alpha = K/T$  (*Voir Figure 1.1*). De plus, pour  $\alpha \neq 0$  la SCD équivaut au spectre de densité spectral.

$$S_x^\alpha(f) = \sum_{\tau=-\infty}^{\infty} R_x^\alpha(\tau) e^{-i2\pi f\tau} \quad (1.5)$$

$$\tilde{S}_x^\alpha(f) = \frac{1}{N} \frac{1}{T} \sum_{n=-N/2}^{N/2} X_T(n, f + \frac{\alpha}{2}) X_T^*(n, f - \frac{\alpha}{2}) \quad (1.6)$$

$$X_T(n, f) = \int_{n-T/2}^{n+T/2} x(u) e^{-i2\pi fu} du \quad (1.7)$$

**Figure 1.1 Implémentation de la SCD.**

Tirée de Gardner (1994, p. 103)

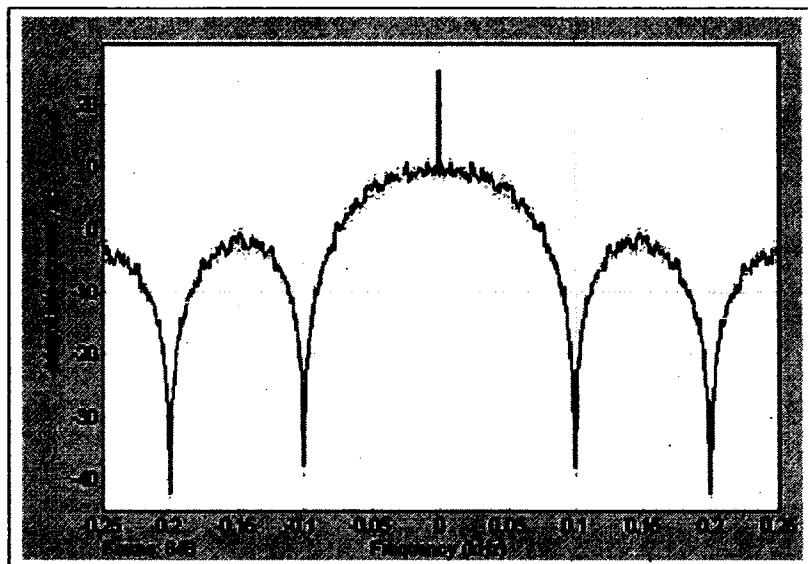

### 1.2.2 Spectre de densité de puissance de la transformation au carré du signal

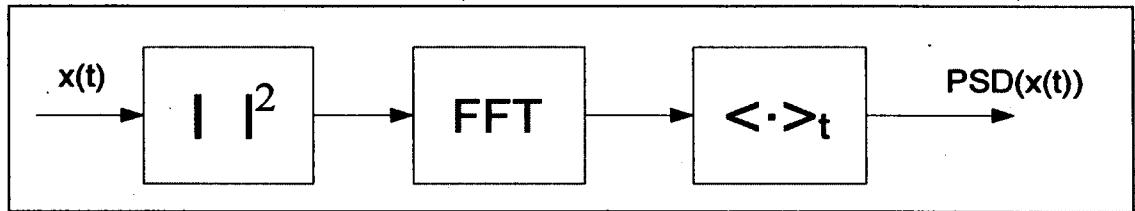

Cette transformation d'ordre deux est un cas particulier de la SCD [11]. Elle utilise les propriétés cyclostationnaires du signal reçu afin d'en extraire le taux de symbole à partir des raies spectrales générées par la transformation au carré du signal reçu (*Voir Figure 1.2*). De plus, cette transformation est utilisée par certains algorithmes de synchronisation de symbole, par exemple celui de Oerder et Meyr [12].

**Figure 1.2 Spectre de densité de puissance de la transformation au carré du signal.**

### 1.3 Revue de la littérature des méthodes de suppression de la cyclostationnarité.

La cyclostationnarité est une caractéristique indésirable pour les systèmes de transmissions LPI/LPD. Dû à la nature militaire des communications LPI/LPD, la documentation qui porte sur le sujet est souvent confidentielle. Ceci limite grandement l'information disponible dans ce domaine. Il suffit de penser aux techniques d'étalement de spectre qui, connues depuis les années 1940 par l'armée américaine, ont pris 60 ans avant d'être déclassifiées et utilisées pour usage commercial dans les années quatre-vingt.

La cyclostationnarité d'un signal modulé chaotiquement en bande de base est due au taux de symbole constant du modulateur [1]. Trois méthodes permettant de supprimer la cyclostationnarité fonction du taux de symbole sont présentées.

### 1.3.1 Filtre passe bas avec largeur de bande 1/2T

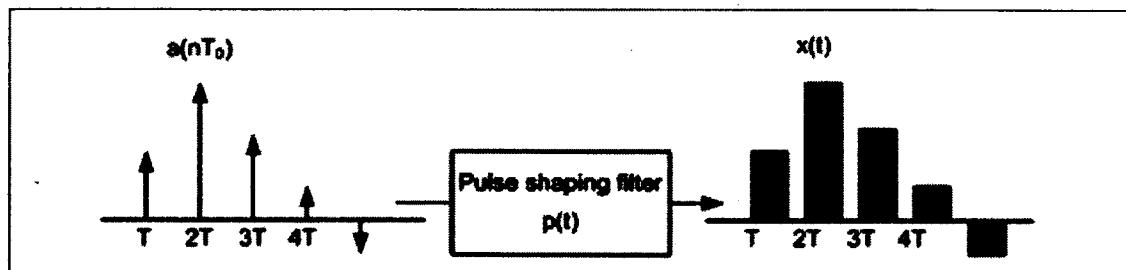

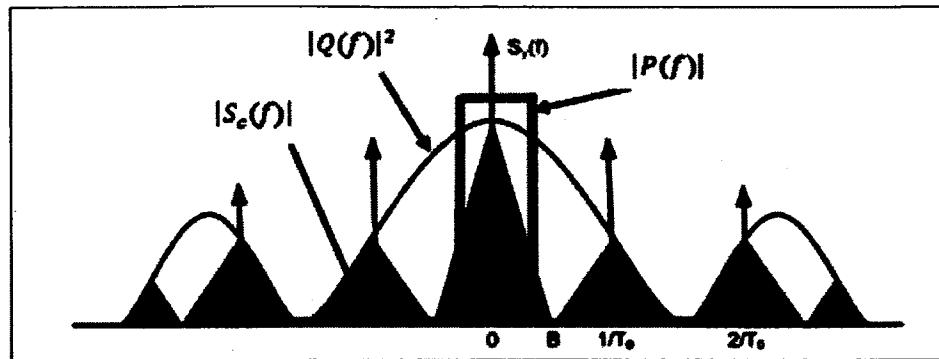

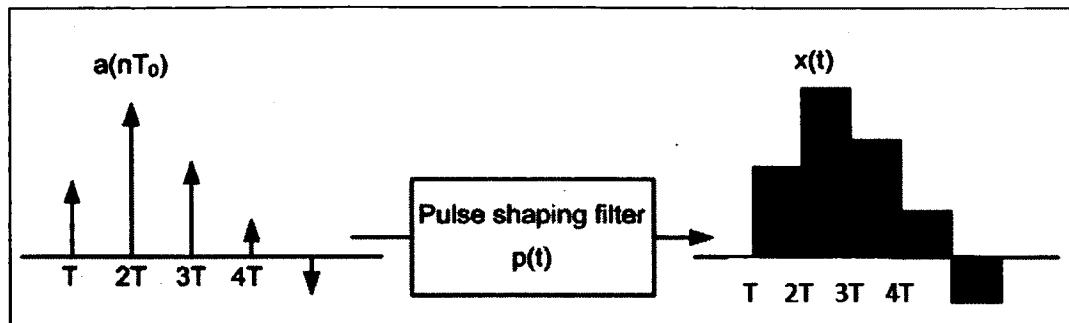

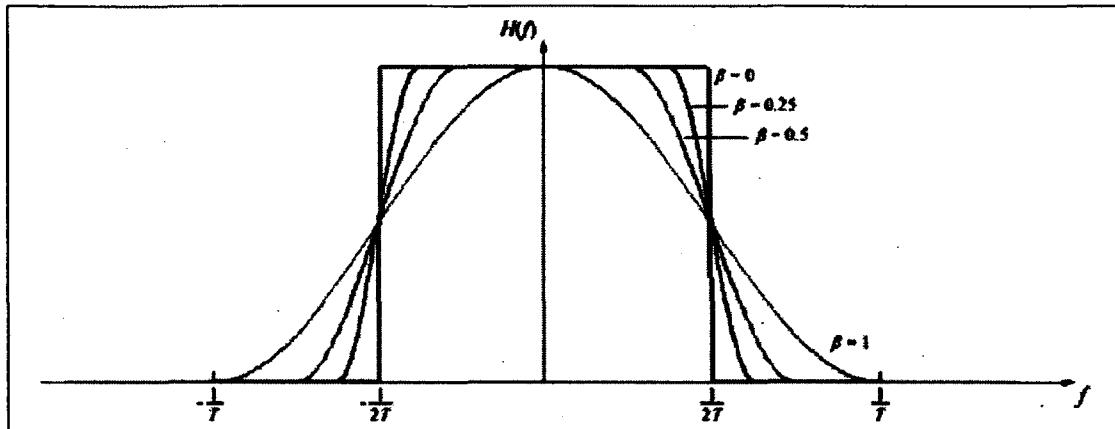

Limiter la largeur de bande d'un signal à  $1/2T$  élimine la cyclostationnarité d'ordre deux qui est fonction du taux de symbole  $1/T$ . La Figure 1.3 représente un signal modulé en amplitude  $x(t)$  (*Voir Équation (1.8)*) avec une enveloppe rectangulaire de durée inférieure à  $T$ . La Figure 1.4 représente le spectre de densité de puissance  $S_x(f)$  (*Voir Équation (1.9)*) de la transformation au carré du signal  $x(t)$ . Des raies spectrales à la fréquence de la fondamental et de ses harmoniques sont présentes. En utilisant un filtre rectangulaire idéal avec une largeur de bande limitée à  $1/2T$  (*Voir Équation (1.10)*), aucun dépassement spectral n'est possible, éliminant ainsi toutes raies spectrales. Cette méthode est impossible à implémenter étant donné qu'elle se traduit par un filtre passe-bas idéal. Cependant, l'utilisation d'un filtre à cosinus surélevé qui permet de limiter la largeur de bande du signal entre  $1/T \leq \beta \leq 1/2T$  en faisant varier le facteur d'arrondissement  $\beta$  entre  $0 \leq \beta \leq 1$ , permet de réduire considérablement les raies spectrales en choisissant le plus petit  $\beta$  permettant une implémentation physique du filtre.

**Figure 1.3 Modulation en amplitude avec enveloppe de durée inférieure à T.**

$$x(t) = \sum_n a(nT) p(t - nT) \quad (1.8)$$

**Figure 1.4 Spectre de densité de puissance  $S_x(f)$ .**

$$S_x(f) = \frac{1}{T} |Q(f)|^2 \sum_m \left\{ K \delta \left( f - \frac{m}{T} \right) + S_c \left( f - \frac{m}{T} \right) \right\} \quad (1.9)$$

$$P(f) = \begin{cases} 1 & \text{pour } -\frac{1}{2T} \leq f \leq \frac{1}{2T} \\ 0 & \text{autre} \end{cases} \quad (1.10)$$

### 1.3.2 Signal avec enveloppe temporelle rectangulaire de durée T

Un signal avec une enveloppe temporelle rectangulaire de durée  $T$ , force son spectre de densité de puissance à zéro à la fréquence de symbole  $1/T$  et de ses harmoniques. La Figure 1.5 représente un signal modulé en amplitude  $x(t)$  avec une enveloppe rectangulaire de durée  $T$ . La Figure 1.6 représente le spectre de densité de puissance de la transformation au carré du signal  $x(t)$  avec un taux de symbole de  $1/T=100Hz$ . Aucune raie spectrale à la fréquence de la fondamentale et de ses harmoniques n'est présente. Du point de vue de son implémentation, cette méthode est impossible à réaliser étant donné que cette forme d'onde demande une largeur de bande infinie et par le fait même cause beaucoup d'interférence entre symboles dans un canal limité en fréquence. De plus, l'interférence entre symboles dégrade les performances du système de transmission.

**Figure 1.5 Modulation en amplitude avec enveloppe de durée  $T$ .**

**Figure 1.6 Spectre de densité de puissance de  $x(t)^2$ .**

### 1.3.3 Phase aléatoire

Selon [13], la "phase randomization" est une technique utilisée afin de rendre stationnaire un processus cyclostationnaire. Ceci est accompli en introduisant une phase aléatoire  $\Theta$  statistiquement indépendante et uniformément distribuée sur chaque période  $T$  d'un processus  $x(t)$  (Voir Équation (1.11)). La période de symbole n'étant plus constante, la cyclostationnarité fonction du taux de symbole ne peut être détectée. Cette méthode est réalisable du point de vue de son implémentation et est donc retenue dans le cadre de ce projet.

$$y(t) = x(t + \Theta) \quad (1.11)$$

#### 1.4 Conclusion

Ce chapitre a, dans un premier temps, exposé les caractéristiques d'un système LPI et LPD nécessaire aux systèmes de communication sécurisée. Ceci a permis de définir la problématique de cyclostationnarité des signaux chaotiques. Dans un deuxième temps, les techniques de détection de la cyclostationnarité d'ordre deux, soit le spectre de densité de puissance de la transformation au carré du signal et la SCD ont été définies. Finalement, une revue des méthodes de suppression de la cyclostationnarité a été présentée. La méthode de phase aléatoire est retenue étant donné qu'elle est la seule à être réalisable du point de vue implémentation.

## CHAPITRE 2

### MODULATION CHAOTIQUE

Ce chapitre expose la théorie du fonctionnement de la modulation chaotique. Une revue des différentes méthodes de modulation chaotique les plus rencontrées dans la littérature est présentée. Le concept de synchronisation dans le domaine du chaos est abordé. Finalement, une configuration de modulateur chaotique est proposée.

#### 2.1 Théorie du fonctionnement de la modulation chaotique

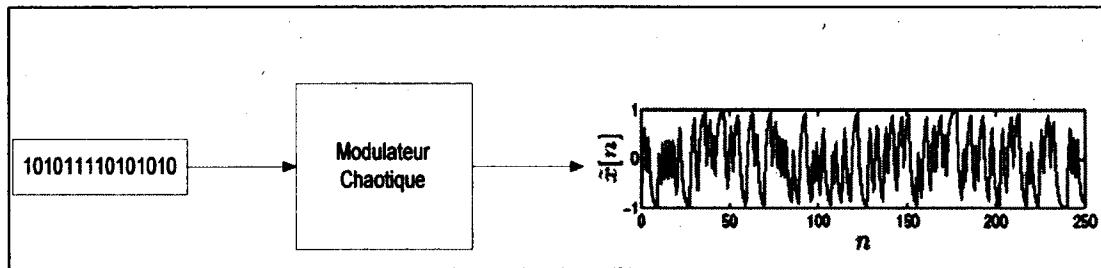

La modulation chaotique consiste à assigner les bits d'informations aux états d'un signal qui varie chaotiquement (*Voir Figure 2.1*).

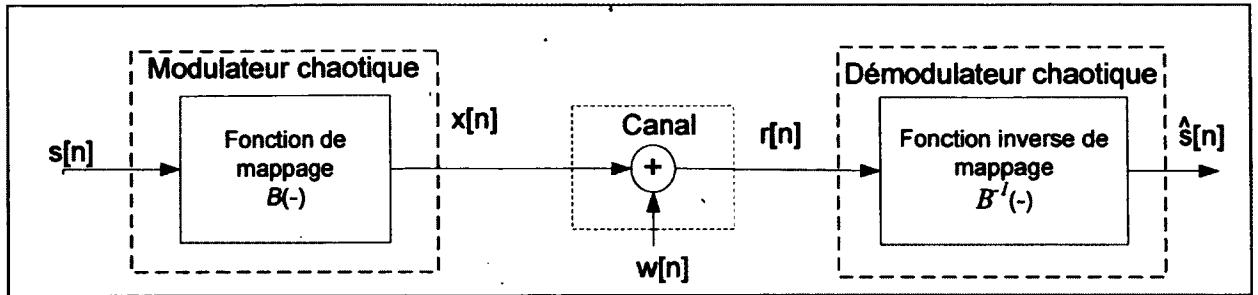

Figure 2.1 Modulation chaotique.

Une séquence chaotique est générée à partir de systèmes dynamiques non linéaires possédant un comportement pouvant sembler complètement imprévisible, même aléatoire. Ce régime chaotique est dû à un phénomène d'instabilité numérique appelé sensibilité aux conditions initiales. Un système dynamique est un système qui évolue de façon causale et déterministe [14], c'est-à-dire qu'une évolution dans le temps à partir d'une condition initiale définit une seule et unique séquence d'états futurs. L'évolution déterministe de ces systèmes peut être représentée par une équation différentielle dans le domaine continu (*Voir Équation (2.1)*) ou par une fonction de récurrence dans le domaine discret (*Voir Équation (2.2)*).

$$\frac{dx(t)}{dt} = f(x(t)) \quad x(t) \in R^m \quad (2.1)$$

$$x[n] = f(x[n-1]) \quad x[n] \in R^m \quad (2.2)$$

où  $x$  est le vecteur d'état,  $R^m$  représente l'espace des phases, soit l'ensemble de tous les états pouvant être pris par le système, et  $m$  est l'ordre du système. L'ensemble des points résultants de l'évolution d'une fonction  $f(x)$  à partir d'une condition initiale pour un système dynamique discret est appelé orbite de  $x[0]$  et dénoté  $O^+(x[0])$  (*Voir Équation (2.3)*).

$$O^+(x[0]) = x[1] = f(x[0]), x[2] = f(x[1]) \dots x[n] = f(x[n-1]) \quad x[n] \in R \quad (2.3)$$

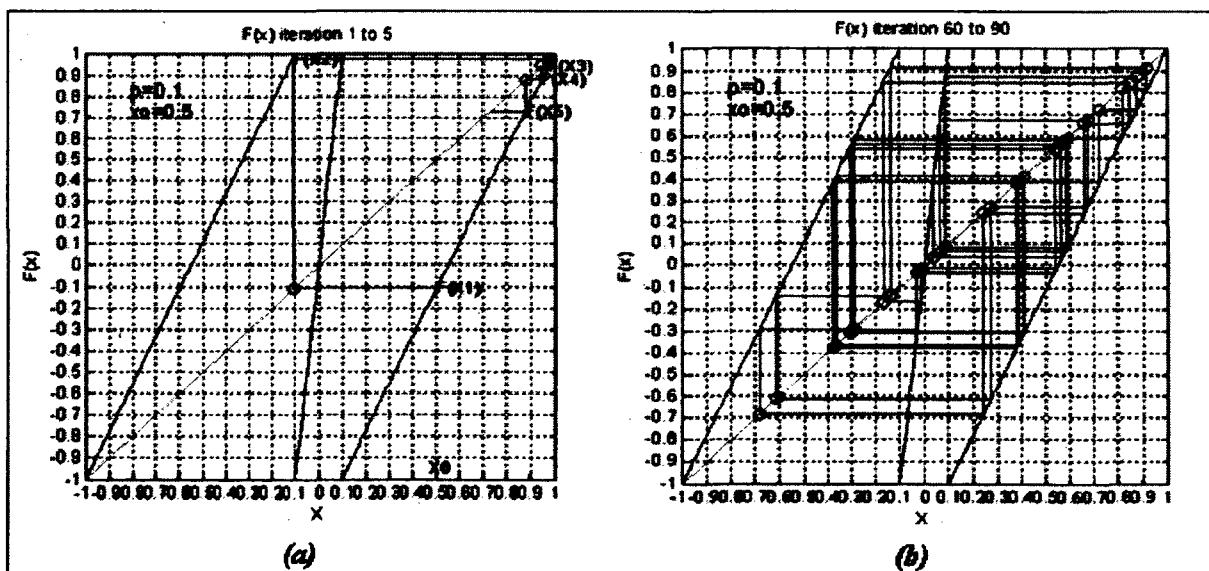

Dans le cadre de ce projet, seuls les systèmes discrets sont considérés. Les systèmes dynamiques discrets non linéaires sont représentés par des fonctions continues ou continues par morceau (*Voir Figure 2.2*) aussi appelé fonctions chaotiques. Le comportement de l'orbite  $O^+(x[0])$  qui décrit la dynamique du système peut être représenté géométriquement sur une fonction chaotique en affichant les valeurs d'entrées-sorties en fonction de chaque itération. Cette méthode de présentation géométrique de la dynamique du système est appelée diagramme de Cobweb. Le diagramme de Cobweb de l'orbite  $O^+(0.5)$  de  $f(x)$  est illustré à la Figure 2.3 et le signal chaotique décrit par ce diagramme de Cobweb est illustré à la Figure 2.4.

**Figure 2.2 Exemple de fonction continue par morceau.**

Tirée de Luengo (2005, p. 2)

**Figure 2.3 Diagramme de Cobweb a) orbite  $0^+(0.5)$  de  $f(x)$  pour les cinq premières itérations b) orbite  $0^+(0.5)$  de  $f(x)$  pour les itérations 60 à 90.**

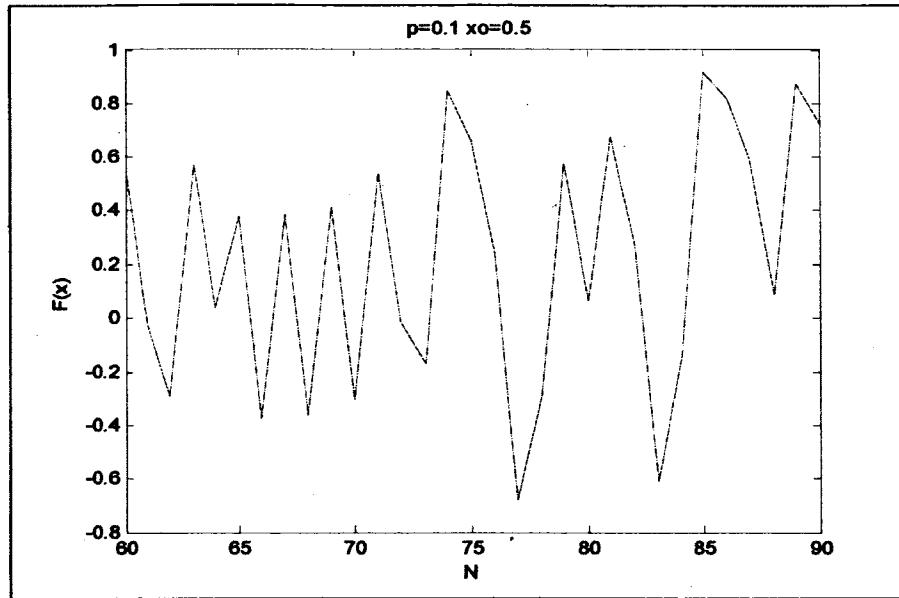

**Figure 2.4 Signal chaotique de l'orbite  $0^+(0.5)$  de  $f(x)$  pour les itérations 60 à 90.**

### 2.1.1 Définition du chaos

Les systèmes dynamiques non linéaires possèdent une variété de régimes permanents tels que stationnaire, périodique, quasi périodique et chaotique. Certaines conditions doivent être respectées afin qu'un système dynamique non linéaire soit en régime chaotique. Plusieurs définitions du chaos pour les systèmes dynamiques existent. La définition de Devaney [15] pour les systèmes discrets est l'une des plus populaires puisqu'elle s'applique à de nombreux exemples importants.

#### Théorème 2.1

Pour un ensemble  $R$ ,  $f: R \rightarrow R$  est dit chaotique sur  $R$  si

1.  $f$  est sensible aux conditions initiales, c.à.d, qu'il existe  $\delta > 0$  de telle sorte que, pour n'importe lequel  $x \in R$  et n'importe quel voisinage  $U$  de  $x$ , il existe  $y \in U$  et  $n \geq 0$  de sorte que  $|f^n(x) - f^n(y)| > \delta$ .

Ceci implique que deux orbites initialisées avec deux conditions initiales légèrement différentes divergent de façon exponentielle l'une de l'autre.

2.  $f$  est typologiquement transitive, c.à.d que pour n'importe quelle paire d'ensembles  $V, W \subset R$  il existe  $k > 0$  de telle sorte que  $f^k(V) \cap W \neq \emptyset$ .

Une fonction typologiquement transitive possède des points qui se déplacent d'une région de l'espace des phases vers n'importe quelle autre région de l'espace des phases.

3. les points périodiques de  $f$  sont denses en  $R$ , c.à.d que pour n'importe quel  $x \in R$  et n'importe quel voisinage  $U$  de  $x$ , il existe  $y \in U$  et  $n \geq 0$  de telle sorte que  $f^n(x) = y$ .

Ceci implique que le chaos est caractérisé par de fortes instabilités localement mais qu'il reste borné globalement.

### 2.1.2 Symbolique dynamique

La symbolique dynamique est un outil qui permet de caractériser la dynamique des systèmes chaotiques par une séquence de symboles. L'espace des phases  $R$  est d'abord partitionné en  $I$  intervalles disjoints (*Voir Équation (2.4)*).

$$R = R_1 \cup R_2 \cup \dots \cup R_{I-1} \quad (2.4)$$

Où chaque intervalle est un homéomorphisme soit  $f|R_i : R_i \rightarrow f(R_i)$ . En associant à chaque intervalle  $R_i$  un symbole  $v_i$ , une séquence symbolique peut être définie comme étant une séquence de régions que le signal chaotique visite durant son évolution dans le temps (*Voir*

Équation (2.5)). Ainsi, l'orbite de  $x[0]$ , normalement représentée par une infinité d'états possibles, peut aussi être représentée par une séquence contenant un nombre fini de symboles (*Voir l'équation (2.6)*).

$$S(x[n]) = v_i \leftrightarrow x[n] \in R_i \quad (2.5)$$

$$S(x[0]) = S(f(x[0])), S(f(x[1])), \dots Sf(x[n-1]) \quad (2.6)$$

## 2.2 Survol des méthodes de modulation et synchronisation chaotique

Dans cette section, les méthodes de modulation et de synchronisation chaotiques les plus communément retrouvées dans la littérature sont présentées. Les techniques de modulation par masquage chaotique [16], chaos shift keying (CSK) [17] et les modulations basées sur la symbolique dynamique [18] sont présentées dans un premier temps. Deuxièmement, les techniques de synchronisation chaotique les plus utilisées sont énumérées et un exemple de synchronisation par couplage est présenté afin d'illustrer le concept de la synchronisation chaotique.

### 2.2.1 Méthodes de modulation chaotique

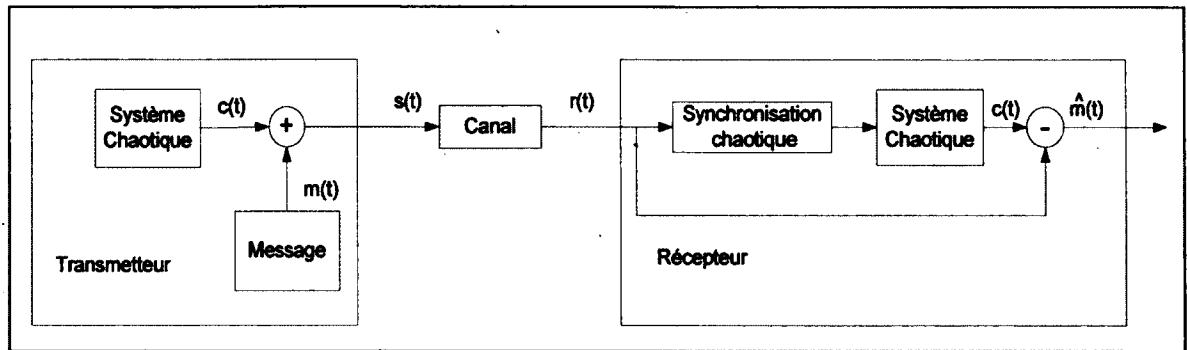

#### Masquage chaotique

La modulation par masquage chaotique (*Voir Figure 2.5*) est l'une des premières méthodes appliquées aux communications chaotiques [19]. Cette technique est basée sur le principe de synchronisation par couplage entre deux générateurs chaotiques. Le transmetteur additionne le signal chaotique  $c(t)$  avec un signal d'information  $m(t)$ , possédant une amplitude beaucoup plus petite, cachant ainsi le signal d'information.

Au récepteur, le signal reçu  $r(t)$  sert à synchroniser un générateur chaotique avec celui du transmetteur. Le message d'information reçue  $m(t)$  est décodé par la différence entre le signal

$r(t)$  reçu et une copie du signal chaotique  $c(t)$  généré localement. L'inconvénient de ce système est la grande sensibilité au bruit de l'unité de synchronisation et de son effet sur la faible amplitude du signal d'information [20].

**Figure 2.5 Système de communication par masquage chaotique.**

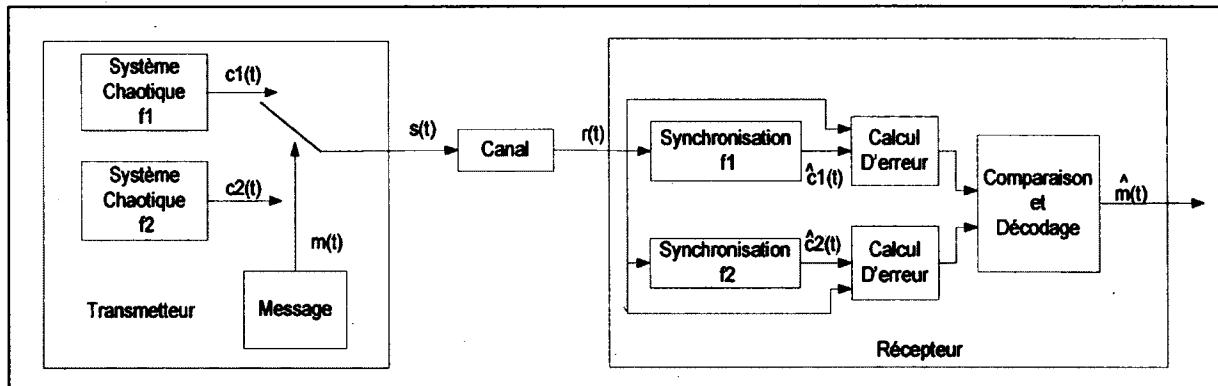

### Chaos shift keying

La modulation de type chaos shift keying (CSK) est une autre technique basée sur la synchronisation par couplage [21]. La Figure 2.6 montre le schéma bloc d'un système de communication CSK cohérent. Un signal d'information binaire encode les bits "0" et "1" sur deux signaux chaotiques statistiquement similaires  $c1(t)$  et  $c2(t)$  respectivement. Les signaux  $c1(t)$  et  $c2(t)$  peuvent être générés par une fonction chaotique définie par des paramètres différents résultant ainsi en deux générateurs chaotiques  $f1$  et  $f2$ .

Le récepteur cohérent contient une copie des deux générateurs du transmetteur. Le signal reçu  $r(t)$  sert à synchroniser un des deux générateurs chaotiques afin de générer les signaux chaotiques  $c1(t)$  et  $c2(t)$  en fonction de la transmission d'un bit "0" ou "1". Le message original est décodé soit en calculant l'erreur ou par corrélation entre le signal reçu et les signaux  $\hat{c}1(t)$  et  $\hat{c}2(t)$  générés localement.

Contrairement au système CSK cohérent, un système de communication CSK non cohérent n'a pas besoin de générer les séquences chaotiques localement pour démoduler l'information.

Il se base plutôt sur la différence en énergie des séquences chaotiques reçues pour distinguer les différents symboles transmis [22]. À chaque bit d'information "0" ou "1" est associée une séquence chaotique d'énergie différente  $c1(t)$  et  $c2(t)$ . Les séquences  $c1(t)$  et  $c2(t)$  sont générées à partir de deux générateurs chaotiques ayant des énergies différentes ou par un générateur avec un gain d'énergie différent pour les bits "0" ou "1". L'énergie du signal reçu est estimée par un processus de corrélation intégration et le message original est décodé en comparant l'énergie de chaque symbole avec un seuil.

Bien que beaucoup plus robuste au bruit que la modulation par masquage chaotique, la modulation CSK a comme principal inconvénient sa faible sécurité étant donné qu'il serait facile de distinguer la différence en distribution de  $f1$  et  $f2$  pour le système cohérent et la différence en énergie pour le système non cohérent [20].

**Figure 2.6 Système de communication CSK cohérent.**

### Modulation chaotique basée sur la dynamique symbolique

Cette modulation encode les bits d'informations sur les états d'un signal qui varie chaotiquement en utilisant la dynamique symbolique. La Figure 2.7 montre un exemple d'architecture de modulation chaotique basée sur la dynamique symbolique. Le signal d'information  $s[n]$  forme une séquence symbolique. Une fonction de mappage  $B(\cdot)$  établie la relation entre chaque symbole ou un regroupement de symboles et un état  $x[n]$  correspondant d'une fonction chaotique.

**Figure 2.7 Système de communication de modulation chaotique basée sur la dynamique symbolique.**

Le récepteur utilise une fonction inverse de mappage  $B'(\cdot)$  afin d'associer un symbole à chaque échantillon  $r[n]$  reçu. La symbolique dynamique étant une représentation plus générale de la dynamique d'un système chaotique, ceci permet au récepteur d'utiliser un algorithme à maximum de vraisemblance afin de décoder la séquence symbolique la plus vraisemblable transmise par le transmetteur [2].

### 2.2.2 Méthodes de synchronisation des systèmes chaotiques

Dans les systèmes de communication numérique conventionnelle, la synchronisation de porteuse sert à retrouver la phase et la fréquence de la porteuse de transmission qui est un signal périodique. Par contre, une porteuse chaotique n'est pas périodique. De plus, deux systèmes chaotiques identiques initialisés avec des conditions légèrement différentes produisent des trajectoires chaotiques qui divergent rapidement dues à leurs sensibilités aux conditions initiales. La synchronisation chaotique a pour but de synchroniser deux systèmes chaotiques afin que leurs orbites convergent asymptotiquement l'une avec l'autre lorsque  $t$  tend vers l'infini. Une fois le transmetteur et le récepteur synchronisés, la démodulation du signal chaotique est possible. Toutefois, il est à noter que la synchronisation chaotique n'est pas nécessaire pour les systèmes de communication chaotique dont le modulateur est basé sur la dynamique symbolique et utilisant une fonction chaotique inverse. Un exemple d'un tel système est proposé à la prochaine section.

Plusieurs méthodes de synchronisation chaotique existent. La plus utilisée est la méthode de synchronisation identique [23] aussi appelée synchronisation par couplage. Cette méthode a été réalisée par Pecora et Carroll [24, 25] afin de démontrer pour la première fois que deux systèmes chaotiques peuvent se synchroniser. Par la suite, plusieurs méthodes dérivées de cette dernière ont été proposées, par exemple la synchronisation généralisée [26, 27], synchronisation de phase [28, 29], synchronisation par rétroaction d'erreur [30], etc.

Toutes ces méthodes de synchronisation ont été réalisées pour des systèmes chaotiques dans le domaine continu qui, rappelons-le, sont des systèmes basés sur des équations différentielles. Afin de réaliser ces systèmes numériquement, deux méthodes d'intégration numérique soit Runge-Kutta et Euler sont les plus fréquemment utilisées. De plus, dans le domaine discret ces techniques de synchronisation peuvent être appliquées aux fonctions chaotiques.

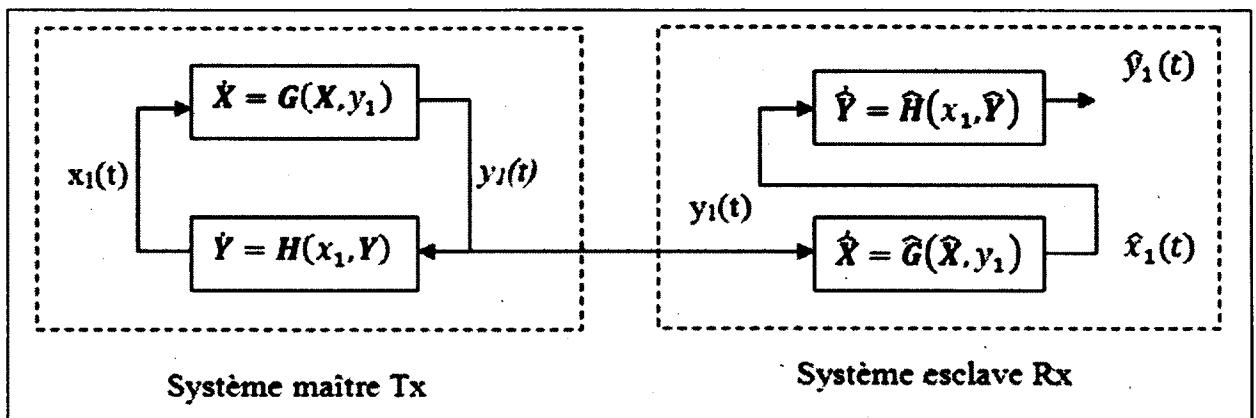

### Synchronisation identique

La technique de synchronisation identique telle que proposée par Pecora et Carroll consiste à diviser un système chaotique de  $n$  dimensions en deux sous-systèmes.

$$\dot{\mathbf{U}}(\mathbf{t}) = \mathbf{F}(\mathbf{U}(\mathbf{t})) \Leftrightarrow \begin{cases} \dot{\mathbf{X}} = \mathbf{G}(\mathbf{X}, \mathbf{y}_1) & (\text{dimension } m) \\ \dot{\mathbf{Y}} = \mathbf{H}(\mathbf{x}_1, \mathbf{Y}) & (\text{dimension } k) \end{cases} \quad (2.7)$$

où  $\mathbf{U} = [u_1, \dots, u_m]$

avec  $\mathbf{X} = [u_1, \dots, u_m] = [x_1, \dots, x_m]$

et  $\mathbf{Y} = [u_{m+1}, \dots, u_n] = [y_1, \dots, y_p]$

tel que  $n = m + k$

Ainsi,  $X$  et  $Y$  sont les variables d'états des sous-systèmes  $G$  et  $H$  respectivement et  $x_1(t)$  et  $y_1(t)$  sont les variables servant à relier les deux sous-systèmes en boucle fermée. La synchronisation par couplage consiste donc à utiliser les deux sous-systèmes  $G$  et  $H$  en boucle fermée comme système maître et une copie des ces derniers en boucle ouverte comme système esclave à la réception (*Voir Figure 2.8*). Le signal  $y_1(t)$  du système maître sert à piloter le système esclave et les trajectoires convergentes asymptotiquement (*Voir Équation (2.8)*).

(2.8)

**Figure 2.8 Principe de synchronisation identique.**

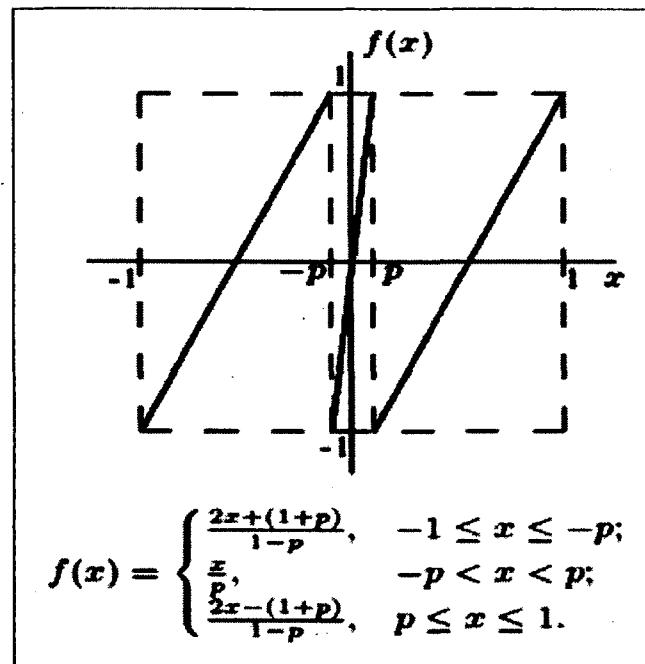

### 2.3 Choix du modulateur chaotique proposé

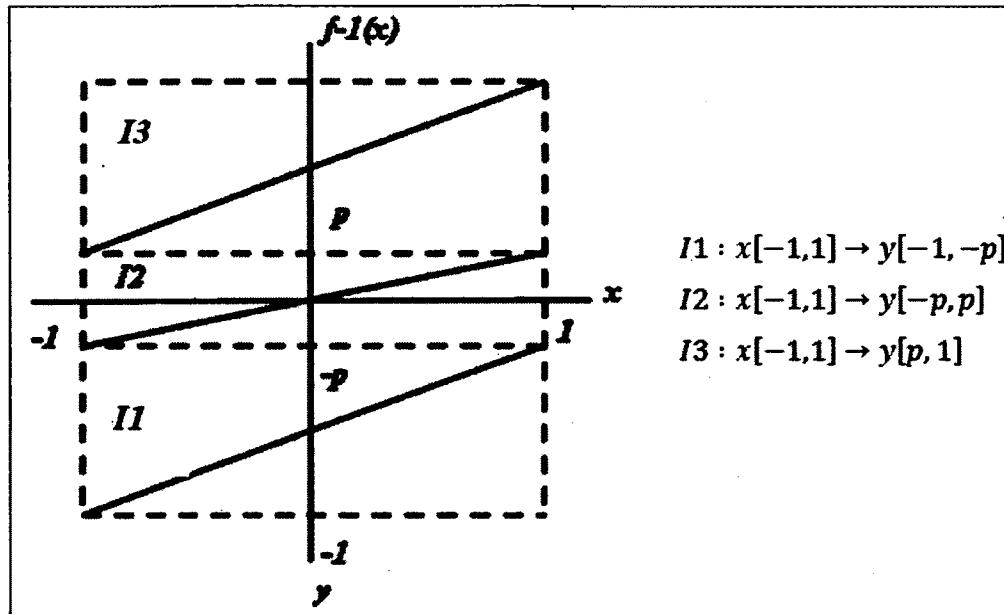

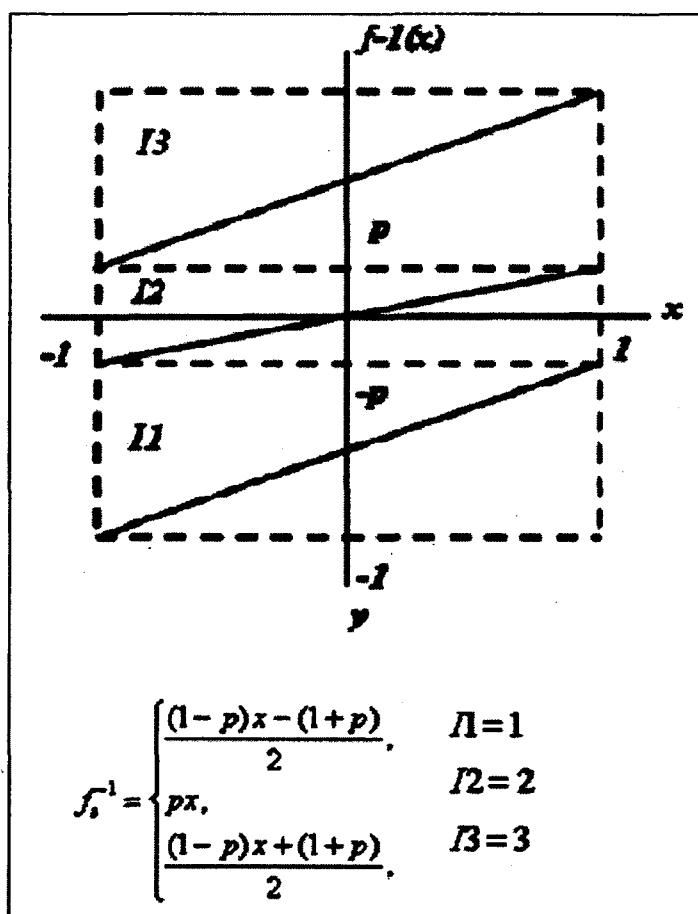

La structure du modulateur chaotique retenue dans le cadre de ce projet est basée sur la symbolique dynamique. Plus précisément, le modulateur chaotique retenu est celui de [2] dont le fonctionnement est détaillé au chapitre 3. Ce modulateur a pour avantage d'éviter l'utilisation de techniques de synchronisation chaotiques. Ceci est possible en itérant sur la fonction chaotique inverse, itération guidée par la symbolique dynamique (*Voir Équation (2.9)*).

$$x[n] = f_{s[n]}^{-1}(x[n-1]) = \dots = f_{s[n], \dots, s[N-1]}^{-1}(x[N]) \quad (2.9)$$

où  $f^{-1}$  dénote la fonction inverse et  $s[n]$  l'intervalle de la fonction de la prochaine itération. Pour une séquence symbolique de longueur  $N$ , la condition initiale  $x[0]$  est contenue dans un intervalle défini par l'équation (2.10). Plus la longueur de la séquence symbolique augmente, plus l'intervalle qui contient la condition initiale diminue. Si  $N$  tend vers l'infini, l'intervalle contient un unique point initial [31]. De plus, il peut être démontré que pour chaque point de l'espace des phases est associée une séquence symbolique de longueur  $N$ . Ceci démontre qu'une séquence chaotique peut-être générée en partant d'un point  $x[N]$  quelconque et en itérant sur l'inverse de la fonction chaotique, en utilisant la symbolique dynamique [2].

$$I = \cap_{n=0}^{N-1} f^{-n}(R_{I_n}) \quad (2.10)$$

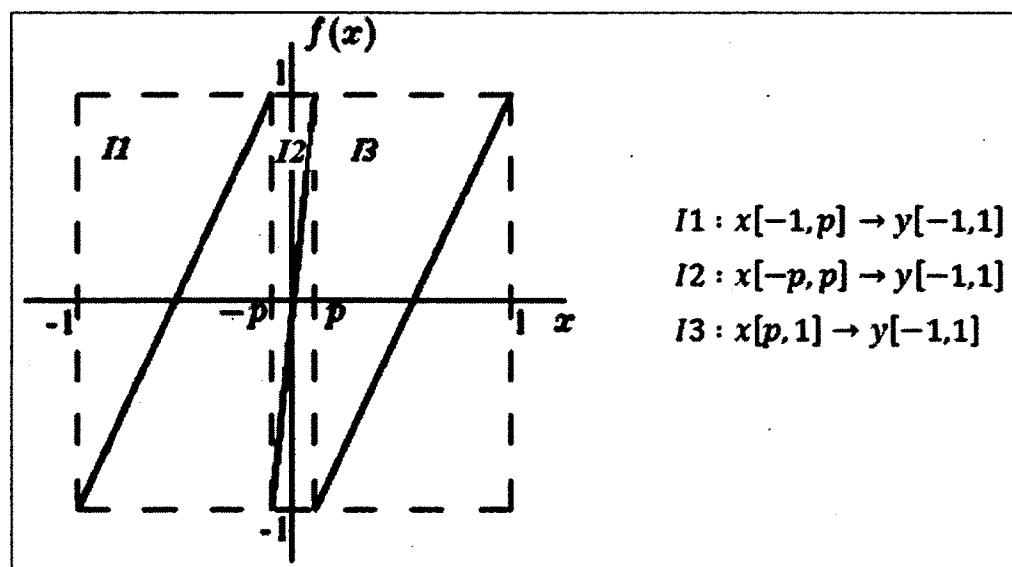

Le fait d'itérer sur la fonction chaotique inverse (Voir Figure 2.9 et Figure 2.10) force chaque intervalle  $I_1$ ,  $I_2$  et  $I_3$  à mapper leur ensemble de départ  $x$  vers un ensemble d'arrivé  $y$  inférieur. Étant donné que la fonction inverse se contracte à chaque itération, le problème de sensibilité aux conditions initiales est éliminé.

**Figure 2.9 Fonction de  $f(x)$ .**

Adaptée de Luango (2005, p. 2)

Figure 2.10 Fonction inverse de  $f(x)$ .

## 2.4 Conclusion

Dans ce chapitre, la théorie de fonctionnement de la modulation chaotique a été abordée. Parmi les différentes méthodes de modulation chaotique les plus populaires, une configuration de modulation basée sur la symbolique dynamique est retenue puisqu'elle permet d'utiliser un algorithme à maximum de vraisemblance au récepteur en plus d'éviter l'utilisation d'un module de synchronisation chaotique.

## **CHAPITRE 3**

### **SYSTÈME CHAOTIQUE PROPOSÉ**

Dans ce chapitre, nous proposons un système de communication sans fil LPI basé sur la modulation chaotique. Chaque module du système y est présenté en détail. Une analyse de la cyclostationnarité d'ordre deux du signal de transmission est présentée. Cette analyse permet d'évaluer la méthode de phase aléatoire retenue au chapitre 1, méthode ayant pour but d'éliminer la caractéristique cyclostationnaire du signal de transmission induite par le taux de symbole constant du modulateur chaotique. Enfin, les performances du système de communication proposé sont présentées et comparées avec un système de communication BPSK à titre de référence.

#### **3.1 Chaine de transmission du système chaotique**

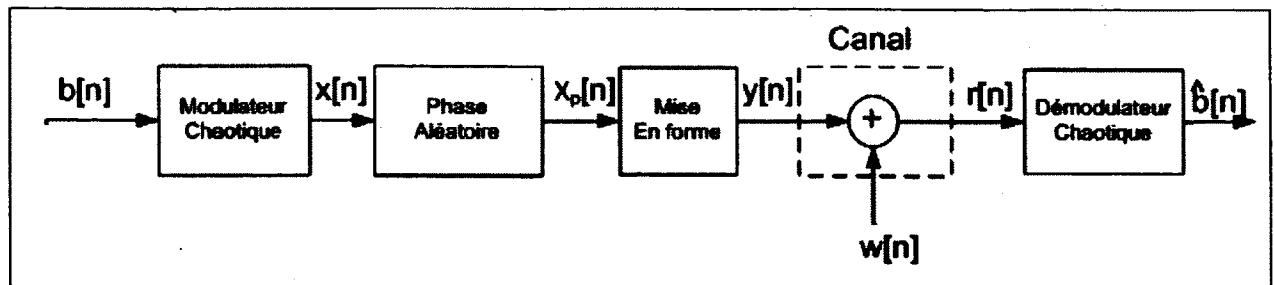

Dans le présent chapitre, un système de communication chaotique est proposé tel que présenté à la Figure 3.1. Un train d'information binaire  $b[n]$  est modulé sur une séquence chaotique à l'aide d'un modulateur (chaotique). Une phase aléatoire est introduite pour chaque symbole de la séquence chaotique  $x[n]$  afin d'éliminer la périodicité introduite par un taux de symbole constant. Avant d'être transmis, le signal  $x_p[n]$  est filtré par un filtre de mise en forme afin de limiter la bande passante du signal chaotique. Le canal de transmission ajoute un bruit blanc gaussien  $w[n]$  au signal  $y[n]$  transmis. À la réception, le démodulateur utilise un estimateur à maximum de vraisemblance pour décoder le train d'information original.

**Figure 3.1 Système de communication chaotique.**

### 3.1.1 Modulateur chaotique

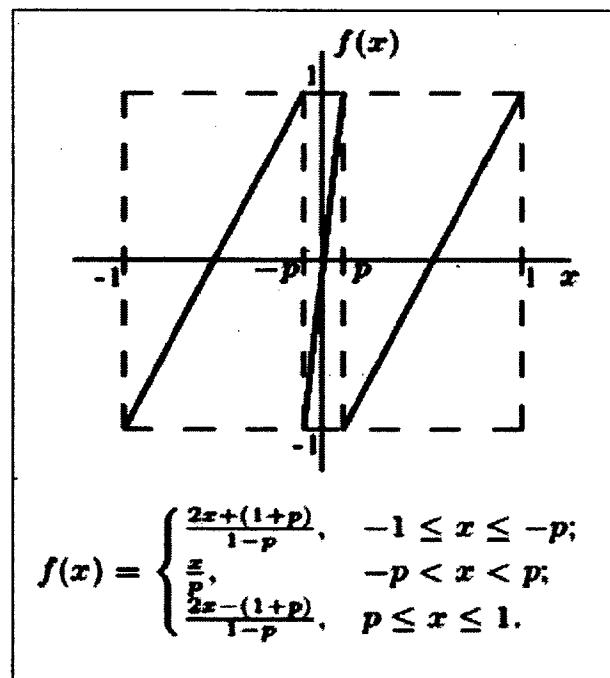

Le modulateur chaotique employé dans ce système est celui de [2]. Le modulateur chaotique est basé sur la symbolique dynamique et utilise une fonction chaotique continue par morceau (*Voir Figure 3.2*). Un paramètre  $p$  permet de contrôler une zone tampon définie pour l'intervalle  $-p \leq x \leq p$  dans laquelle aucune itération n'est réalisée.

**Figure 3.2 Fonction chaotique.**

La zone tampon permet dans un premier temps d'assurer une distance minimum entre les symboles des deux régions  $I_1$  et  $I_3$  en plus de modifier le comportement de la séquence chaotique générée. Plus le paramètre  $p$  augmente, plus la distance euclidienne entre les symboles chaotiques de la séquence générée augmente, entraînant ainsi de meilleures performances du système. Il est à noter que ce gain en performance est fait au détriment d'une moins bonne immunité à l'identification du signal. En effet, plus le paramètre  $p$  augmente, plus il est facile de distinguer dans quelle région de  $f(x)$  les symboles de la séquence chaotique proviennent. De plus, le vide dans la distribution d'amplitude pourrait être détecté. La Figure 3.3 illustre deux séquences chaotiques pour deux valeurs  $p$  différentes.

**Figure 3.3 Séquence chaotique pour  $p=0$ ,  $p=0.5$  et  $X[N]=0.65$ .**

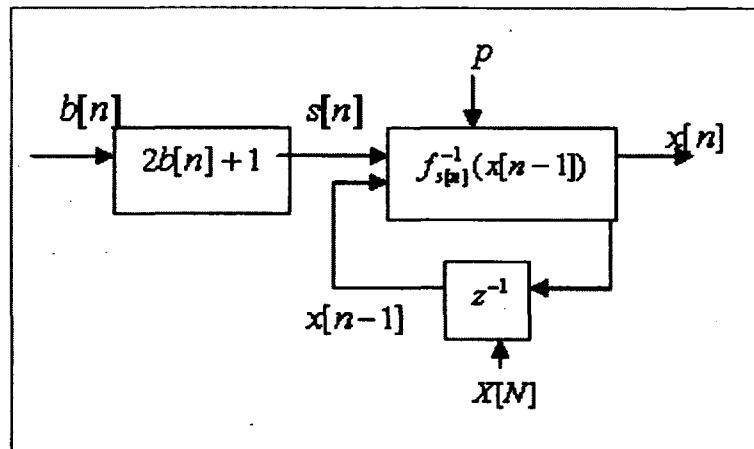

La structure du modulateur chaotique est présentée à la Figure 3.4. Le train d'information binaire  $b[n]$  forme une séquence symbolique  $s[n]$  contrainte aux zones  $I_1$  et  $I_3$  de la fonction chaotique. La séquence chaotique  $x[n]$  est générée à partir d'une condition initiale  $X[0]$  en itérant sur la fonction inverse de  $f(x)$  (Voir Figure 3.5) et en utilisant la séquence symbolique  $s[n]$  comme itinéraire.

**Figure 3.4 Structure du modulateur chaotique.**

Tirée de Luango (2005, p. 2)

**Figure 3.5 Fonction chaotique inverse.**

### 3.1.2 Introduction de phase aléatoire

Le signal à la sortie du modulateur chaotique est généré avec une période de symbole constante le rendant ainsi cyclostationnaire. Dans cette section, une méthode de phase aléatoire est proposée.

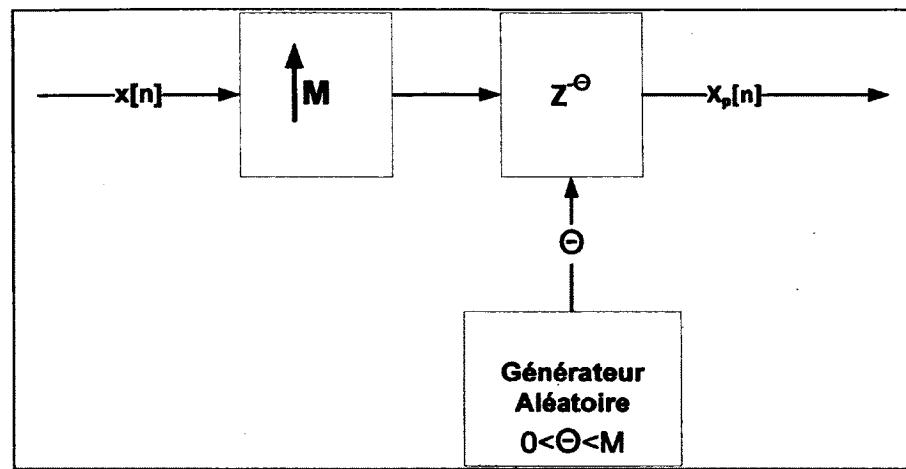

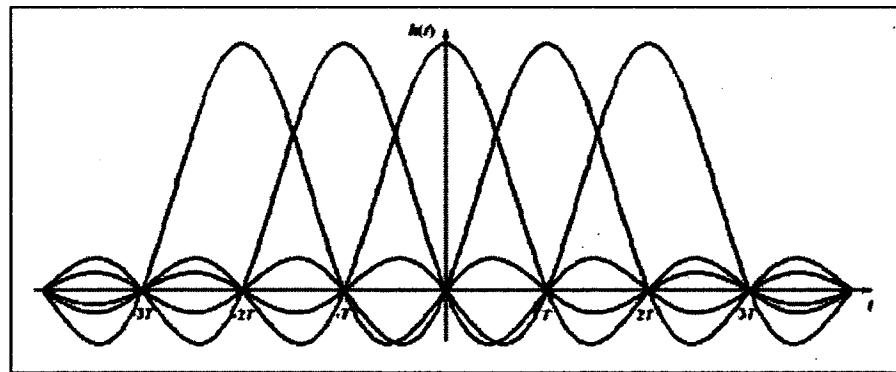

Sachant qu'un suréchantillonnage doit être accompli afin que le signal  $x(t)$  puisse être mis en forme pour la transmission, une phase aléatoire  $\Theta$  est introduite en effectuant un échantillonnage à des instants choisis aléatoirement à l'intérieur d'une période de symboles (*Voir Équation (3.1) et (3.2)*). Le signal peut alors être modélisé par l'équation (3.3) qui représente un signal  $x_p(t)$  échantilloné par un train d'impulsion auquel une phase aléatoire est introduite à chaque période de symbole  $T_0$ .

$$x_p(t) = x(t)p(t) \quad (3.1)$$

$$p(t) = \sum_{n=-\infty}^{\infty} \delta(t - nT_0 + \Theta(n)) \quad (3.2)$$

$$x_p(t) = \sum_{n=-\infty}^{\infty} x(nT_0 + \Theta(n)) \delta(t - nT_0 + \Theta(n)) \quad \text{où } \Theta < T_0 \quad (3.3)$$

La structure du module d'introduction de phase aléatoire proposé est représentée à la Figure 3.6. Le signal est suréchantillonné par un facteur  $M$  au minimum deux fois supérieur au taux de symbole du signal d'entrée. Un générateur de nombres aléatoires permet d'introduire un délai de  $\Theta$  échantillons, où  $0 < \Theta < M$ , permettant ainsi de sélectionner l'une des  $M$  phases possibles d'un symbole suréchantilloné (*Voir Figure 3.7*).

**Figure 3.6 Module de phase aléatoire.**

**Figure 3.7 Signal  $x[n]$  échantillonné par un facteur de  $M=5$ .**

### 3.1.3 Filtre de mise en forme

Généralement, les systèmes de transmission sans fil doivent opérer dans des bandes de fréquences qui leur sont allouées. Ces contraintes sont souvent imposées par des règles gouvernementales ou de designs. Il est donc important de limiter la bande passante du signal transmis. Le filtre de mise en forme le plus souvent utilisé est le filtre en cosinus surélevé

(Voir Figure 3.8). La réponse fréquentielle et la bande passante (BP) du filtre en cosinus surélevé sont définies par les équations (3.4) et (3.5).

**Figure 3.8 Réponse fréquentielle du filtre cosinus surélevé.**

Tirée de Wikipedia (2010)

$$H(f) = \begin{cases} T_0, & |f| \leq \frac{1-\beta}{2T_0} \\ \frac{T_0}{2} \left[ 1 + \cos \left( \frac{\pi T_0}{\beta} \left[ |f| - \frac{1-\beta}{2T_0} \right] \right) \right], & \frac{1-\beta}{2T_0} < |f| \leq \frac{1+\beta}{2T_0} \\ 0, & \text{autre} \end{cases} \quad (3.4)$$

$$BP = \frac{1}{2T_0} (1 + \beta) \quad (3.5)$$

où  $T_0$  représente la période de symbole et  $\beta$  représente le facteur d'arrondissement compris entre  $0 \leq \beta \leq 1$  permettant de limiter la BP entre la fréquence de Nyquist  $1/(2T_0)$  et le taux de symbole  $1/T_0$ .

Pour le système proposé, le filtre de mise en forme est implémenté à l'aide d'un filtre numérique à réponse à l'impulsion finie (RIF). Les coefficients sont définis par la réponse à l'impulsion du cosinus surélevé représenté par l'équation (3.6). Comme l'illustre la Figure 3.9, la réponse à l'impulsion  $h(t)$  s'étend sur  $D$  symboles et passe à zéro à chaque période de

symbole  $T_0$ . Cette dernière caractéristique permet d'éliminer l'interférence inter-symbole à chaque période  $T_0$  (Voir Figure 3.10).

$$h(t) = \text{sinc}\left(\frac{t}{T_0}\right) \frac{\cos\left(\frac{\pi\beta t}{T_0}\right)}{1 - \frac{4\beta^2 t^2}{T_0^2}} \quad (3.6)$$

**Figure 3.9 Réponse à l'impulsion du filtre cosinus surélevé.**

Tirée de Wikipedia (2010)

**Figure 3.10 Impulsions cosinus surélevé consécutives.**

Tirée de Wikipedia (2010)

Le degré avec lequel la réponse à l'impulsion  $h(t)$  est approximée est fonction du nombre  $N$  de coefficients utilisés. Généralement  $N$  est un multiple entier du facteur  $M$  de suréchantillonnage (Voir Équation (3.7)). Ceci permet d'obtenir un nombre  $N$  qui couvre un nombre entier de symboles  $D$ .

$$N = D * M \quad (3.7)$$

Évidemment, plus  $D$  et  $M$  sont grand, meilleure est l'approximation de la réponse idéale. Cependant,  $D$  est proportionnel à la complexité du filtre qui souvent est un facteur que l'on veut minimiser. En résumé, la réalisation d'un filtre numérique en cosinus surélevé pour une réponse fréquentielle donnée dépend du facteur d'arrondissement  $\beta$ , du nombre de symboles  $D$  que couvre la réponse à l'impulsion, du facteur de suréchantillonnage  $M$  et de l'ordre du filtre soit le nombre de coefficients  $N$ . Cependant, il est à noter que le facteur de suréchantillonnage a peu d'influence sur les performances du filtre [33].

La réponse à l'impulsion étant définie, le signal chaotique à la sortie du filtre en cosinus surélevé est modélisé par les équations (3.8) et (3.9). Tel qu'illustré à la Figure 3.11, la phase aléatoire  $\Theta$  introduite par  $p(t)$ , induit une mémoire sur  $D+1$  symboles. Chaque symbole de  $M$  échantillons subi l'interférence de  $D/2$  symboles passés et  $D/2$  symboles futurs.

$$y(t) = [x(t)p(t)] \otimes h(t) \quad (3.8)$$

$$y(n) = \sum_{n=-\infty}^{\infty} x(nT_0 + \Theta(n)) h(t - nT_0 + \Theta(n)) \quad (3.9)$$

**Figure 3.11 Mémoire induite par la phase aléatoire, M=2, D=4.**

### 3.1.4 Démodulateur chaotique

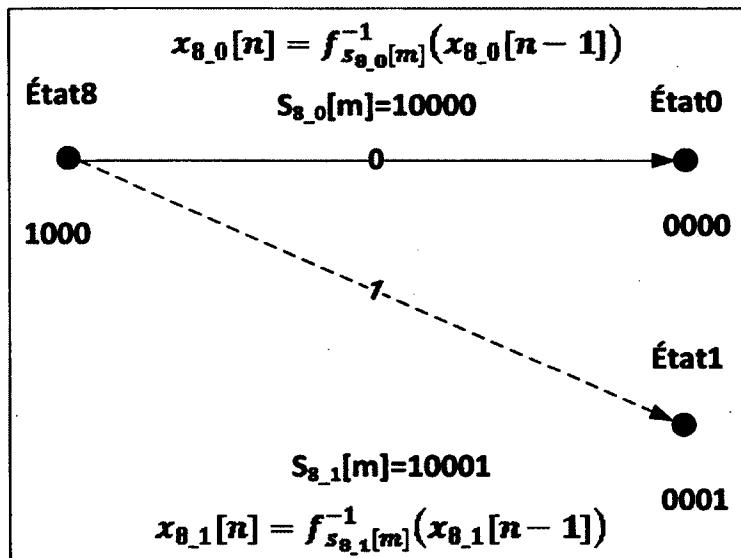

#### Représentation par diagramme de treillis

Le concept de base du démodulateur chaotique repose sur la représentation en diagramme de treillis de la trajectoire de la séquence chaotique. Selon [2], un treillis avec deux états peut être utilisé. Soit un état pour chaque région  $I_1$  et  $I_3$  de la fonction chaotique utilisée par le modulateur présenté à la section précédente. Ce concept est justifié par le fait que la fonction chaotique  $f^{-1}(x)$  employée se contracte à chaque itération. Ainsi, les bits précédents d'une

séquence symbolique ont peu d'importance sur l'estimation des bits futurs. Ceci est démontré par l'exemple suivant.

Considérons deux échantillons différents,  $x_1[n]$  et  $x_2[n]$  où  $0 \leq n \leq N$ , qui partagent un même itinéraire  $s_1[n] = s_2[n] = s[n]$  sur la fonction chaotique  $f^{-1}(x)$ . Les échantillons futurs  $x_1[n+1]$  et  $x_2[n+1]$  sont donnés par les équations (3.10) et (3.11) respectivement.

$$x_1[n+1] = \frac{(1-p)x_1[n] + (s[n+1]-2)(1+p)}{2} \quad (3.10)$$

$$x_2[n+1] = \frac{(1-p)x_2[n] + (s[n+1]-2)(1+p)}{2} \quad (3.11)$$

La distance entre deux échantillons après une itération peut alors être calculée avec l'équation (3.12). Le résultat indique qu'indépendamment de leur position, la distance entre deux échantillons après une itération diminue par un facteur de  $(1-p)/2$ .

$$d[n+1] = |x_2[n+1] - x_1[n+1]| = \frac{1-p}{2} d[n] \quad \text{où } d[n] = |x_2[n] - x_1[n]| \quad (3.12)$$

Ainsi, il est démontré que la distance entre les deux séquences diminue de façon exponentielle après  $k$  itérations (Voir équation (3.13)). Ceci prouve donc que les bits passés d'une séquence symbolique ont peu d'influence sur les échantillons futurs d'une séquence chaotique et justifie l'utilisation d'un treillis à deux états pour représenter l'itinéraire du système chaotique.

$$d[n+k] = \left( \frac{1-p}{2} \right)^k d[n] \quad (3.13)$$

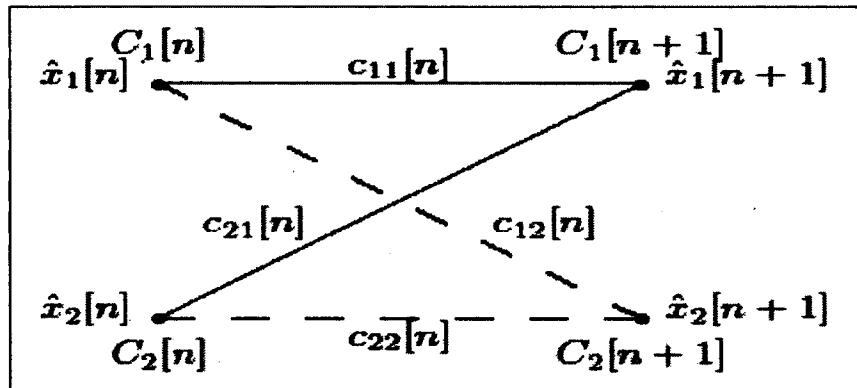

La Figure 3.12 illustre le treillis à deux états auquel l'algorithme de Viterbi est appliqué. La métrique de branche  $c_{ij}[n]$  pour une branche  $j$  partant d'un état  $i$  est représentée par l'équation (3.14). La métrique d'état  $C_i$  est représentée par l'équation (3.15). Le terme  $r[n]$

représente l'échantillon reçu et  $\hat{x}_i[n]$  représente l'échantillon chaotique de l'itération précédente généré par la métrique de branche  $c_{ij}[n]$  ayant le plus petit cumul avec la métrique d'état correspondante. L'échantillon  $\hat{x}_i[n + 1]$  représente donc l'échantillon chaotique le plus vraisemblable entre deux branches du treillis menant au même état.

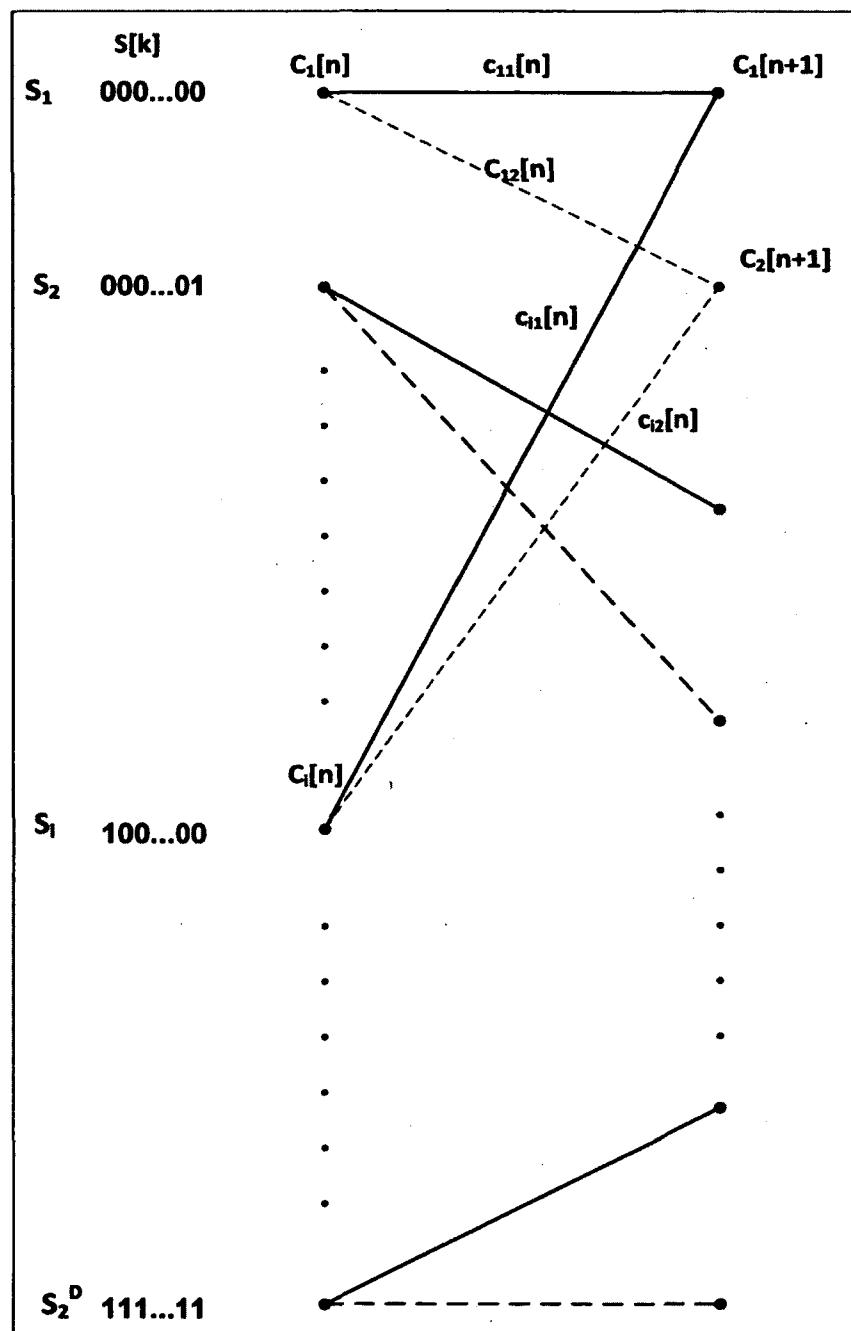

**Figure 3.12 Treillis utilisant deux états par itération de séquence chaotique.**

Tirée de Luango (2005, p. 3)

$$c_{ij}[n] = |r[n] - f_j^{-1}(\hat{x}_i[n])| \quad (3.14)$$

$$C_i[n + 1] = \min_{j=1,2} \{C_j[n] + c_{ji}[n]\} \quad (3.15)$$

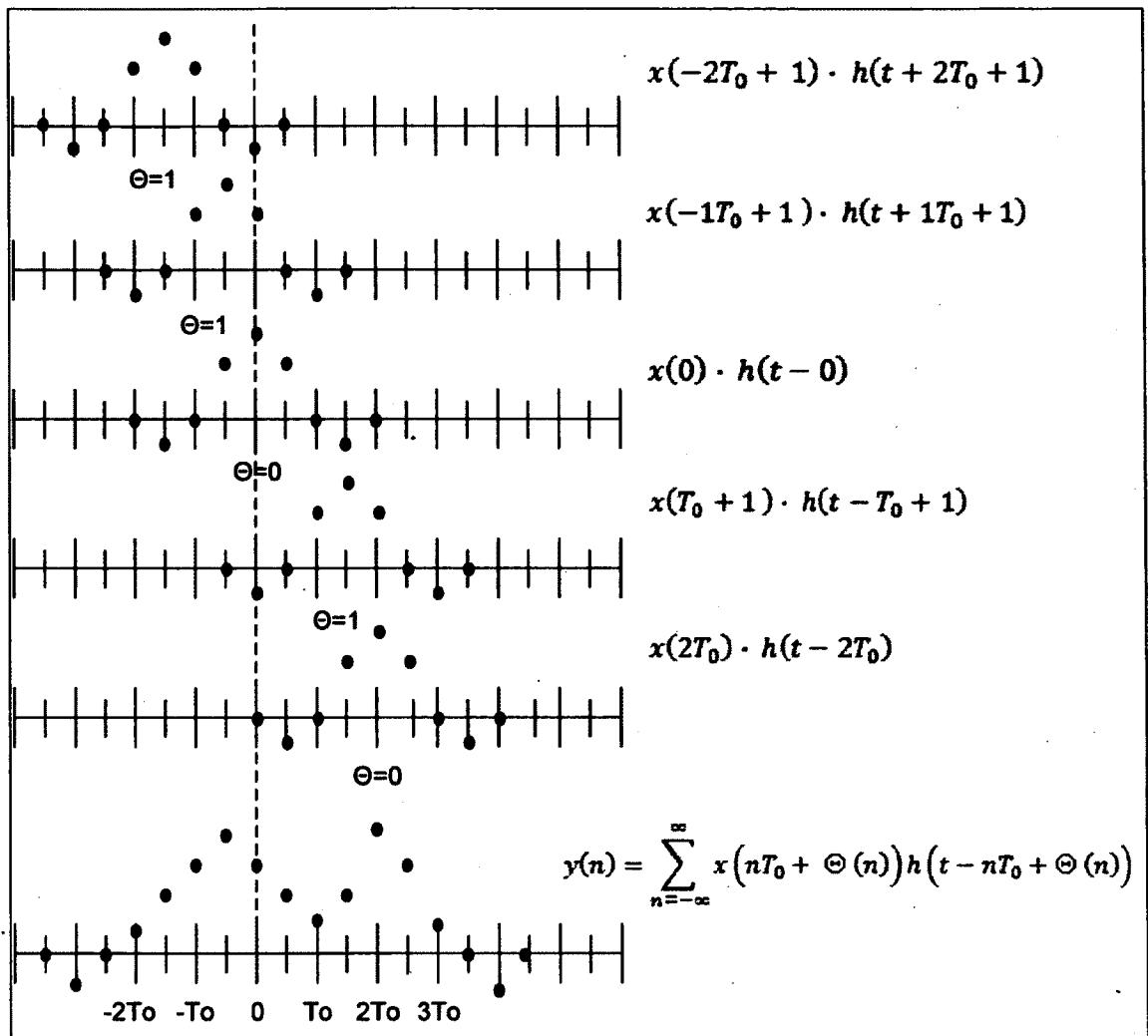

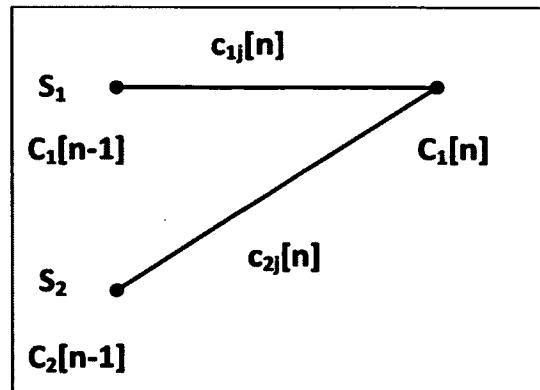

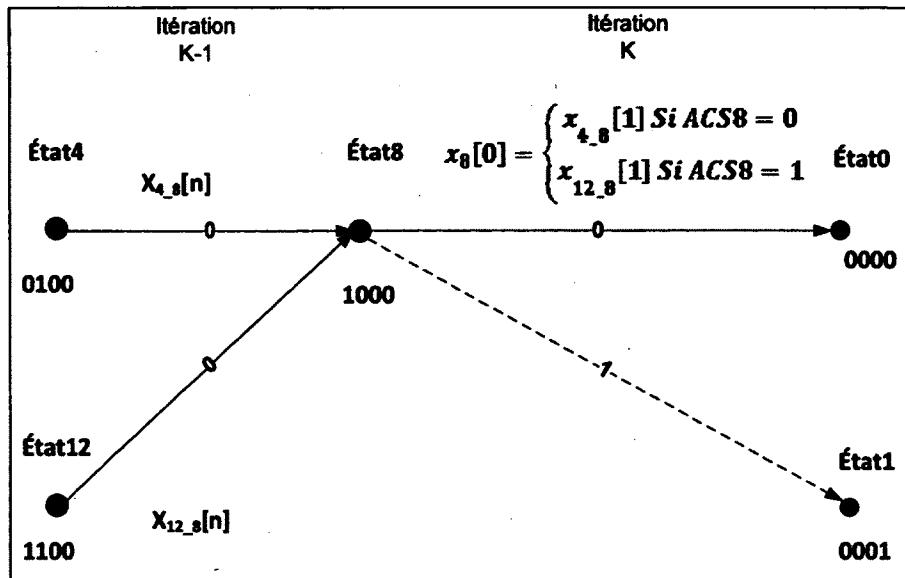

### Expansion du diagramme de treillis

Afin d'estimer le signal  $y(t)$  à la sortie du transmetteur, le diagramme de treillis est modifié pour accommoder la mémoire induite par le filtre de mise en forme ainsi que la séquence de gigue de phase  $\Theta(t)$  du transmetteur. Le nombre d'états du treillis résultant, pour un filtre de mise en forme pour lequel la réponse à l'impulsion couvre  $D$  symboles, augmente à  $2^D$  états (*Voir Figure 3.13*). Les  $D$  bits de chaque état représentent un segment possible de la séquence symbolique  $S/k$  transmise. Étant donné que la séquence symbolique est formée de valeurs binaires assignées aux régions  $I1$  et  $I3$  de la fonction chaotique, seulement deux branches de transition entrent et quittent chaque état  $i$ . Chaque branche  $j$  du treillis représente le prochain

symbole possible de la séquence symbolique. La transition entre l'état présent et le prochain est donc déterminée par la dynamique symbolique. Le diagramme du treillis permet ainsi de représenter n'importe quelle séquence symbolique par un chemin unique constitué de branches successives.

**Figure 3.13 Diagramme de treillis adapté pour  $h(t)$  et  $\Theta(t)$ .**

Ainsi pour chacune des branches du treillis, une séquence chaotique  $x_{ij}[m]$  (*Voir Équation (3.16)*) est générée à l'aide de la séquence symbolique  $sd[m]$  (*Voir Équation (3.17)*). Connaissant la fonction  $f^{-1}(x)$  du modulateur,  $h(t)$  du filtre de mise en forme et  $\Theta(t)$  de la séquence de phase aléatoire du transmetteur, chaque branche du treillis permet de générer un symbole  $y_{ij}[n]$  (*Voir Équation (3.18)*) de  $M$  échantillons ayant subi l'interférence de  $D/2$  symboles passés et futurs afin d'estimer l'échantillon reçus  $r[n]$ . La métrique de branche est maintenant exprimée par l'équation (3.19) et la métrique d'état reste telle que présentée par l'équation (3.15).

$$x_{ij}[m] = f_{sd[m]}^{-1}(x_{ij}[m-1]) \quad (3.16)$$

$$sd[m] = [s[k], j] \quad (3.17)$$

$$y_{ij}[n] = \sum_{m=1}^{D+1} \left( x_{ij} \left( mT_o + \Theta(m) \right) h \left( t - mT_0 + \Theta(m) \right) \right) \quad (3.18)$$

$$c_{ij}[n] = \sum_M |r[n] - y_{ij}[n]| \quad (3.19)$$

### L'algorithme de Viterbi

L'algorithme de Viterbi, un algorithme à maximum de vraisemblance, est utilisé afin de sélectionner la séquence la plus vraisemblable du treillis. Soit  $Y$  une séquence de  $M$  échantillons d'un symbole transmis dans un canal gaussien de variance  $\sigma^2$ , et  $X$  une séquence de  $M$  échantillons d'une des branches du treillis. De plus, on dénote les échantillons de  $Y$  par  $r_m$  et  $X$  par  $c_{jm}$  où l'index  $m$  indique le  $m^{\text{th}}$  échantillon et  $j$  indique la branche  $j$  du treillis.

Selon [7], une métrique de branche pour une branche  $j$  d'un chemin  $U$  du treillis est définie par la fonction log-vraisemblance (*Voir Équation (3.20)*).

$$c_j^u = \log P(Y/X_j^u) = \frac{1}{\sqrt{2\pi}\sigma} \exp \left\{ -\frac{[r_m - c_{jm}^u]^2}{2\sigma^2} \right\} \quad (3.20)$$

Si on simplifie et on néglige tout les termes communs aux métriques de branche du treillis on obtient l'équation (3.21).

$$c_j^u = \log P(Y/X_j^u) = \sum_{m=1}^M [r_m - c_{jm}^u]^2 \quad (3.21)$$

Ainsi, pour un signal à une dimension, la métrique de branche est la distance absolue au carré entre le symbole reçu et celui correspondant à la branche  $j$  d'un chemin  $U$  du treillis. De plus, maximiser la probabilité d'une décision correcte revient à minimiser la distance absolue entre un symbole reçu  $Y$  et un symbole  $Z$  de la branche donnée.

Une métrique d'état pour un état  $i$ , au temps  $n$  d'une séquence de  $N$  symboles, est définie par le cumul le plus faible des métriques de branche d'un chemin  $U$  menant à cet état. La métrique d'état est calculée récursivement à partir de la métrique d'état de l'itération précédente (*Voir Équation (3.22)*).

$$C_i[n] = \min_j \{C_j[n-1] + c_{ji}[n]\} \quad (3.22)$$

où  $C_j[n-1]$  est la métrique minimum de l'état  $i$  à l'instant  $n-1$  et  $c_{ji}[n]$  est la branche  $j$  menant à l'état  $i$ . Cette opération est appelée "Add-Compare-Select" (ACS) (*Voir Figure 3.14*).

**Figure 3.14 ACS.**

La métrique d'état finale  $C_i[N]$ , aussi appelée métrique de chemin, est la plus petite métrique de tous les chemins  $U$  qui entrent dans cet état. Ainsi, la séquence la plus vraisemblable du treillis est la séquence avec la plus petite métrique de chemin.

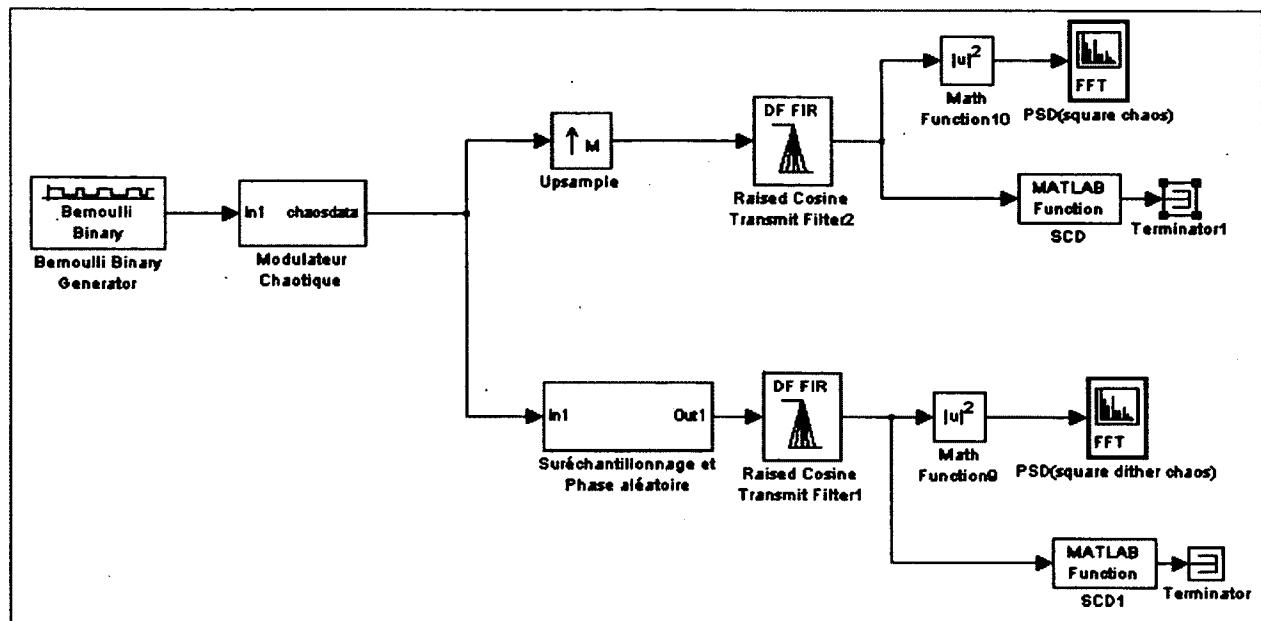

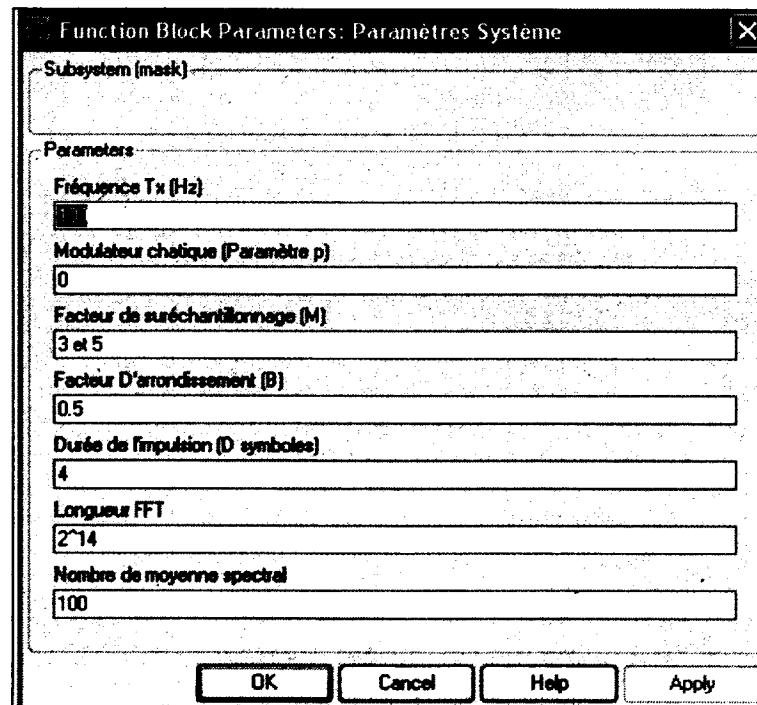

### 3.2 Évaluation de la cyclostationnarité du signal de transmission

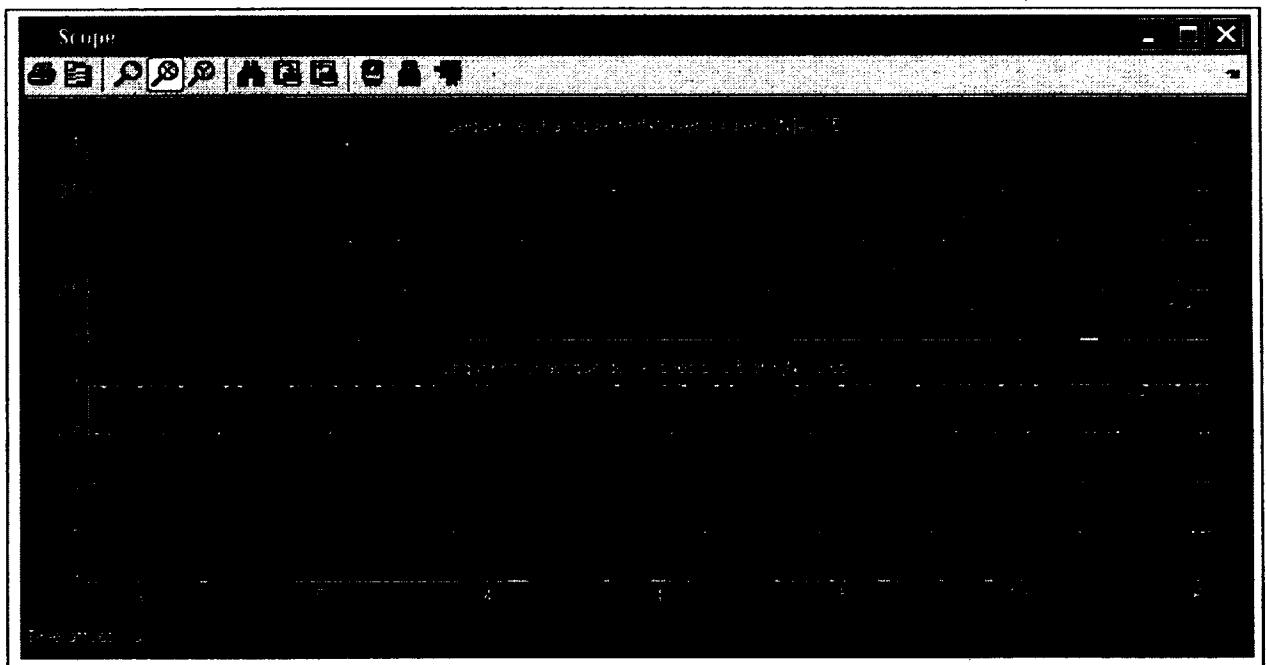

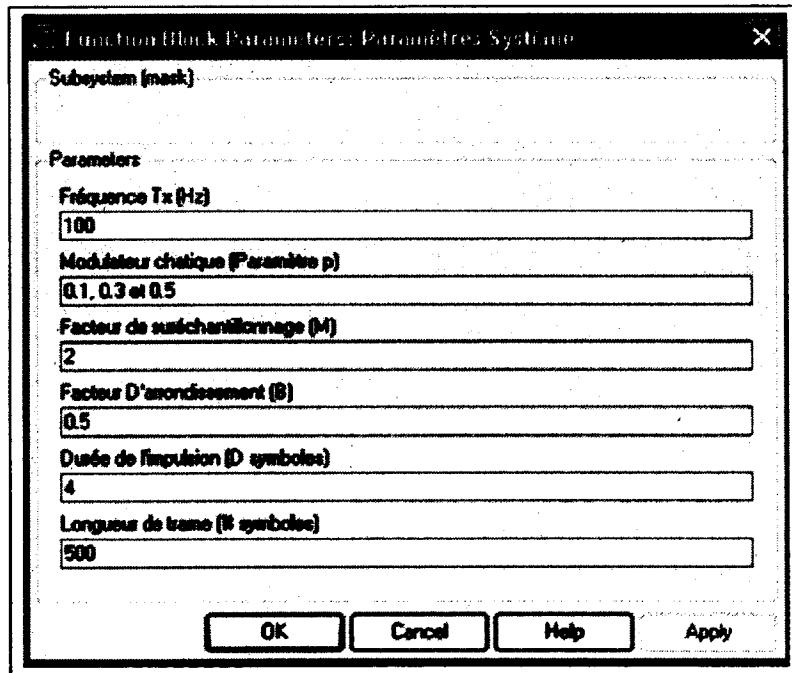

L'évaluation de la cyclostationnarité du signal de transmission est effectuée à l'aide de deux transformations quadratiques soit la fonction de densité de corrélation spectrale ("Spectral Correlation Density", SCD) et la transformation au carré du signal de transmission telle que vue au chapitre un. L'évaluation est réalisée dans l'environnement *Simulink* de *Matlab* (*Voir Figure 3.15*). La Figure 3.16 résume les paramètres de simulation. L'analyse est réalisée pour des facteurs  $M$  de suréchantillonnage de trois et cinq choisis arbitrairement.

**Figure 3.15 Test de la cyclostationnarité du signal.**

**Figure 3.16 Paramètres du système.**

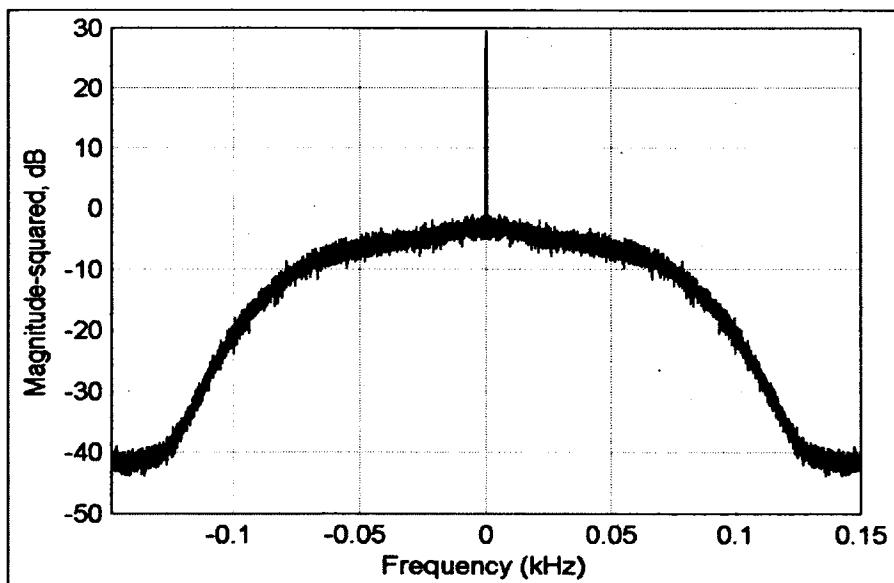

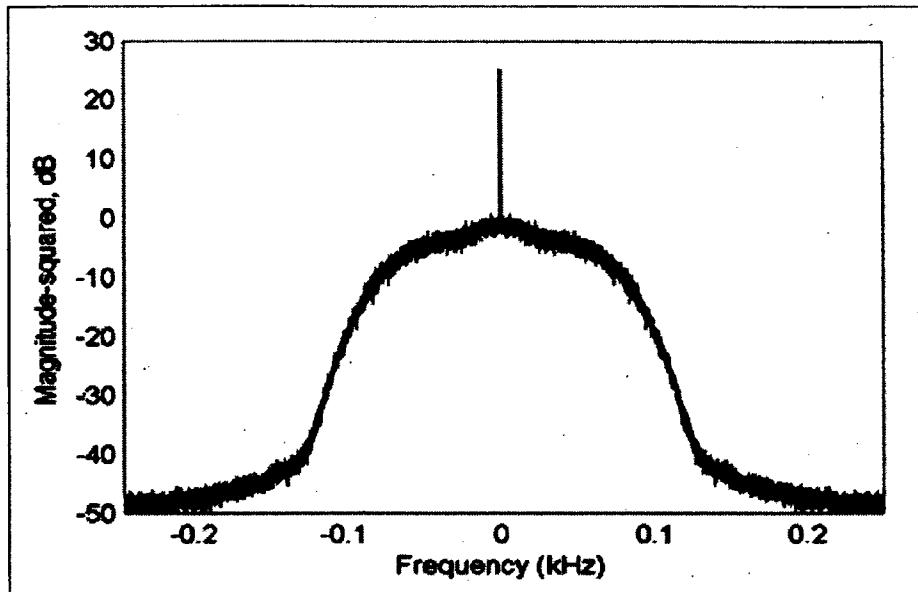

### 3.2.1 Résultats et analyse de la transformation au carré du signal de transmission

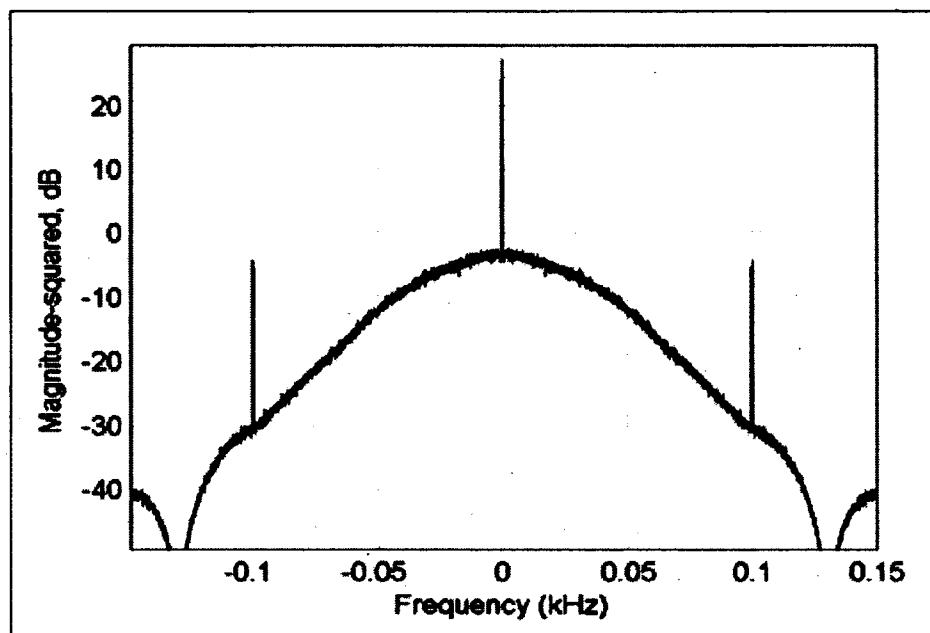

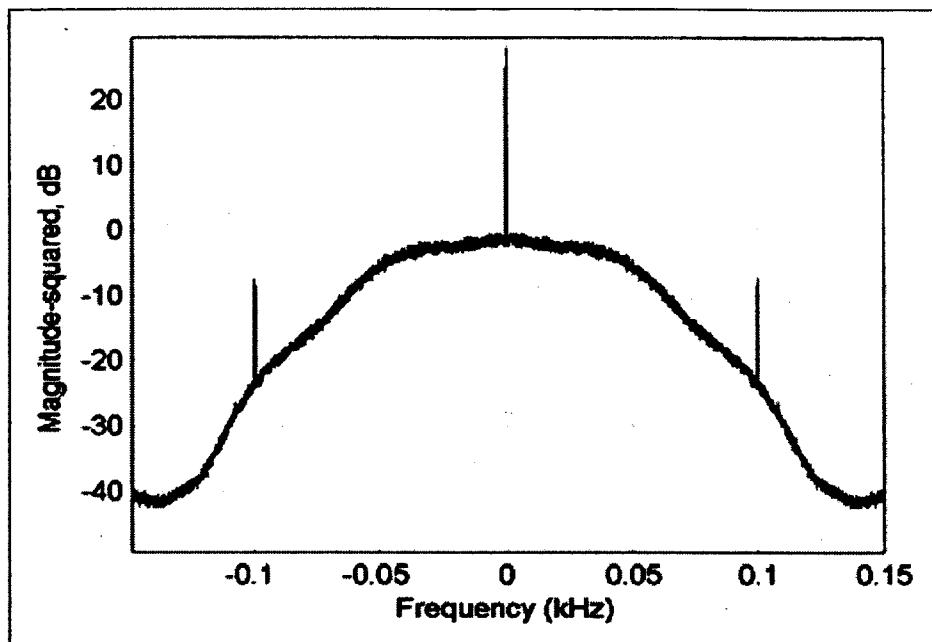

Pour les facteurs de suréchantillonnage de trois et cinq, avec et sans phase aléatoire, les résultats sont présentés aux Figure 3.17, Figure 3.18, Figure 3.19 et Figure 3.20 respectivement. Dans les deux cas, une faible atténuation des raies spectrales à la fréquence de symbole du modulateur chaotique est observée.

**Figure 3.17 PSD de la transformation au carré du signal de transmission sans phase aléatoire,  $M=3$ .**

**Figure 3.18 PSD de la transformation au carré du signal de transmission avec phase aléatoire,  $M= 3$ .**

**Figure 3.19 PSD de la transformation au carré du signal de transmission sans phase aléatoire,  $M= 5$ .**

**Figure 3.20 PSD de la transformation au carré du signal de transmission avec phase aléatoire, M=5.**

Après analyse des résultats, une hypothèse suggère que l'impossibilité d'atténuer complètement les raies spectrales à la fréquence de symbole vient du fait que la fonction continue par morceau  $f^1\theta$  employée induit une caractéristique cyclostationnaire fonction du taux de symbole. Cette caractéristique cyclostationnaire est introduite par un taux de variation en amplitude constant. Cette variation en amplitude constante est due aux pentes linéaires de la fonction  $f^1\theta$ . Afin d'éliminer cette périodicité, le même principe employé pour éliminer la cyclostationnarité induite par un taux de symbole constant est appliqué en amplitude. Comme illustrée pour la Figure 3.21, une séquence aléatoire permet de varier aléatoirement la polarité de la séquence chaotique  $x[n]$  générée par le modulateur chaotique. Le module de phase aléatoire permet ensuite d'éliminer la cyclostationnarité induite par le taux de symbole constant.

**Figure 3.21 Module de polarité et phase aléatoire.**

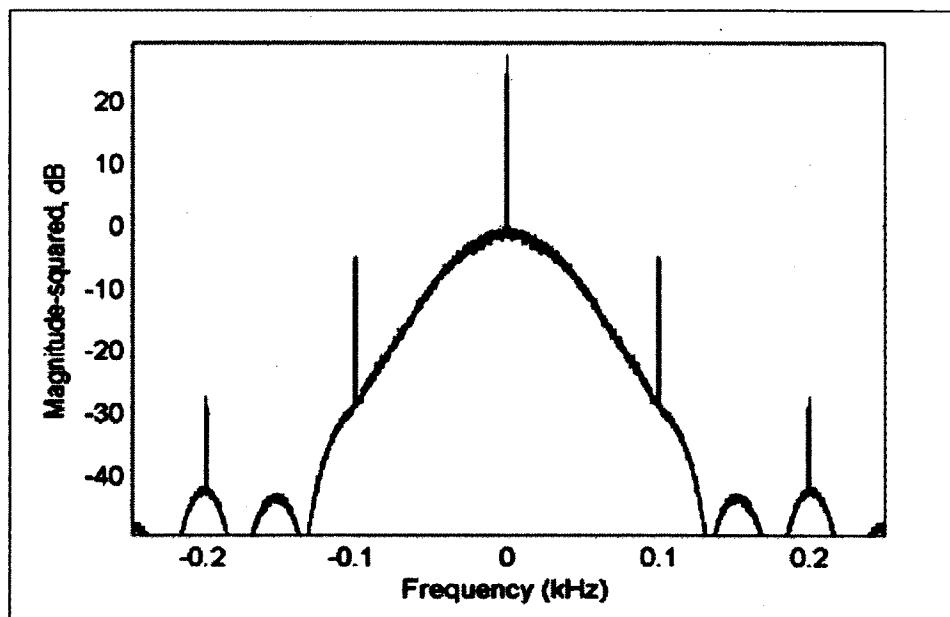

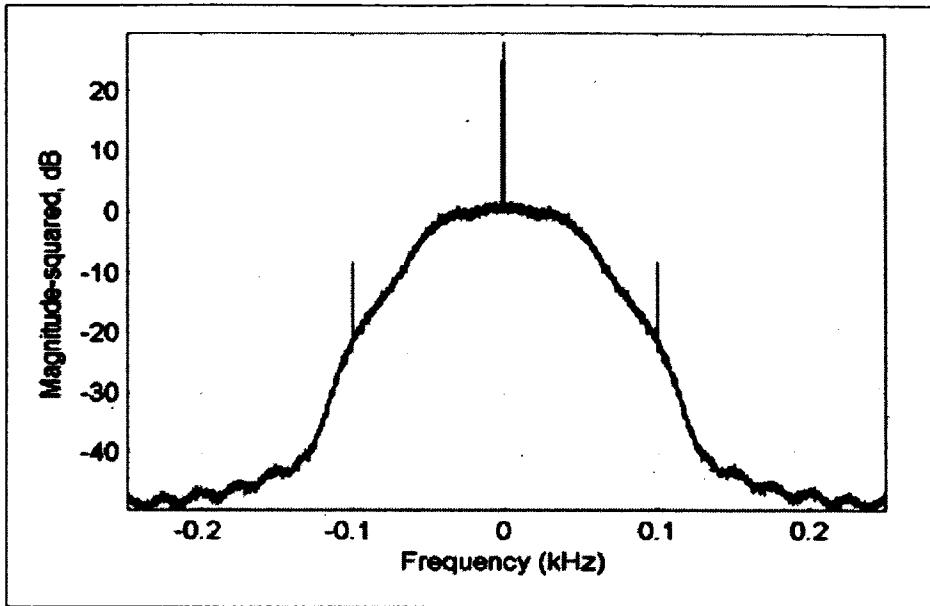

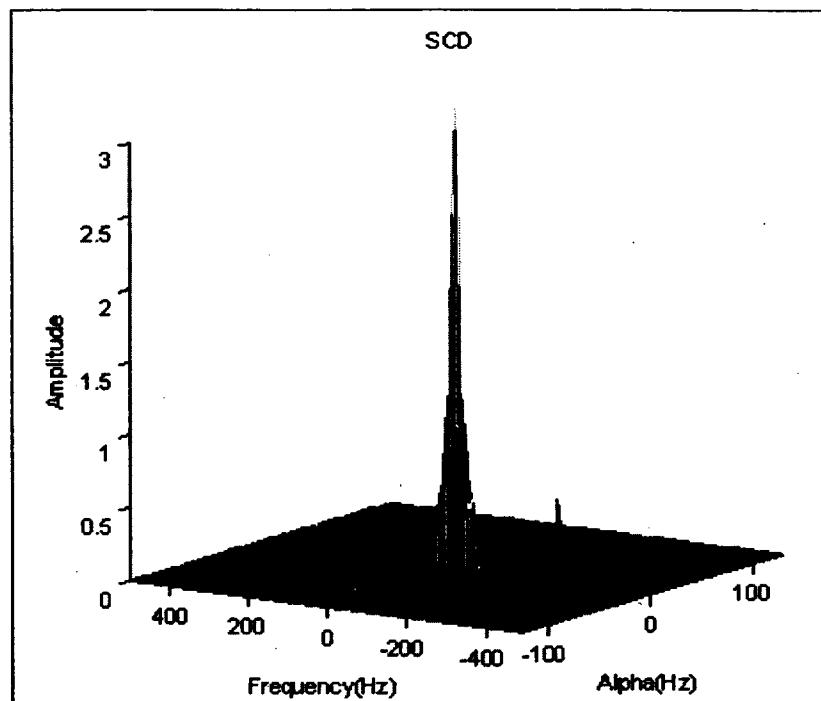

Les Figure 3.22 et Figure 3.23, représentent le spectre de densité spectrale de la transformation au carré du signal de transmission pour lequel une polarité et phase aléatoire sont appliquées. Pour les facteurs de suréchantillonnage de trois et cinq respectivement, il est possible de constater que les caractéristiques cyclostationnaires qui sont fonction du taux de symbole sont complètement éliminées.

**Figure 3.22 PSD de la transformation au carré du signal de transmission avec polarité et phase aléatoire, M=3.**

**Figure 3.23 PSD de la transformation au carré du signal de transmission avec polarité et phase aléatoire, M=5.**

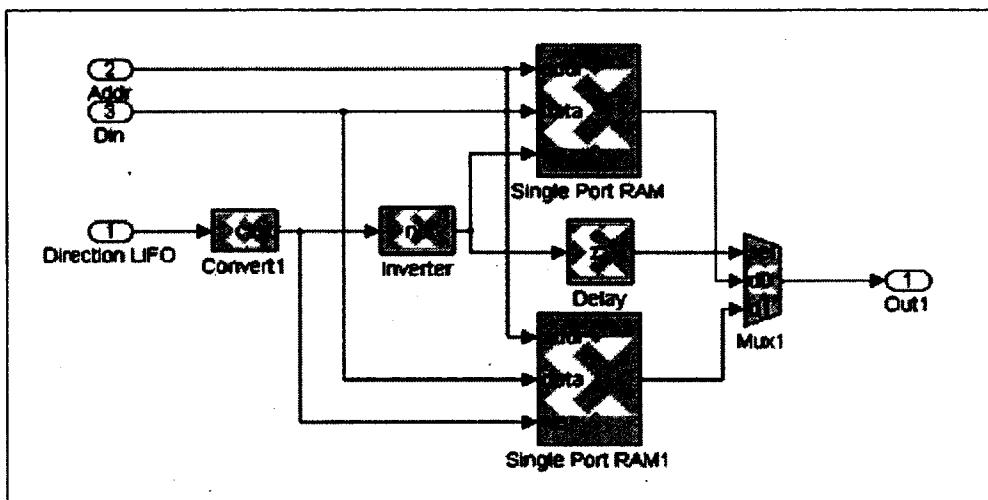

### 3.2.2 Résultats et analyse de la SCD du signal de transmission