# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF THE MASTERS IN ELECTRICAL ENGINEERING M.Sc.A

BY Nicolas KAMEL

OPTIMIZATION OF VERY LOW TIME STEP FPGA-BASED SIMULATIONS USING A FIXED ADMITTANCE MATRIX APPROACH

MONTREAL, "DECEMBER 19, 2014"

© Copyright 2014 reserved by Nicolas KAMEL

#### **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS:

Mr. Handy Fortin-Blanchette, PhD, ing., Thesis Supervisor Département de génie électrique de l'École de technologie supérieure

Mr. Kamal Al-Haddad, PhD, ing., President of the Board of Examiners Département de génie électrique de l'École de technologie supérieure

Mr. Olivier Tremblay, MscA, ing, External Examiner Institut de recherche d'Hydro-Québec

Mr. Jean Bélanger, External Examiner OPAL-RT technologies

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON "DECEMBER 11, 2014"

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **ACKNOWLEDGEMENTS**

First, I would like to thank Handy Fortin-Blanchette, my research supervisor, for challenging my assumptions, encouraging my ideas, and sharing with me his wisdom as a researcher. I would also like to express my gratitude to Jean Bélanger, the CEO of Opal-RT Technologies for giving me the opportunity to conduct my research in such an innovative company. I extend my thanks to every else at OPAL-RT who assisted me in my research, in particular Amine Yamane and Luc-André Grégoire. I also thank NSERC and FQRNT for their financial support. Finally, I thank my parents for their support and for instilling in me a sense of work ethic, without which this work would not have been possible.

# OPTIMIZATION OF VERY LOW TIME STEP FPGA-BASED SIMULATIONS USING A FIXED ADMITTANCE MATRIX APPROACH

Nicolas KAMEL

#### **ABSTRACT**

This research is dedicated to the study of the fixed admittance matrix approach presented by Pejovic and Maksimovic (1994). More specifically, this work has three objectives. First, to study and quantify the effects of this method on simulation accuracy. Second, to use this knowledge to develop a method to tune the  $G_s$  parameter without relying on a trial and error process. An algorithm is proposed to automatically optimize the  $G_s$  parameter which has been validated on three topologies: a two level inverter, a three level NPC inverter, and a direct matrix converter. Third, to explore possible solutions that conserve the advantages of a fixed admittance matrix approach (small time step, low memory consumption) while mitigating its drawbacks (loss of simulation accuracy). A method is proposed which offers the accuracy of a variable admittance matrix approach, but with significantly less memory consumption. This method has been validated offline, however, it remains to be seen if it is a viable candidate for real time implementation and more research must be done.

**Keywords:** Real time simulation, fixed admittance matrix, power electronics, FPGA

# OPTIMISATION D'UNE SIMULATION FPGA À PETIT PAS DE CALCUL EN UTILISANT UNE MATRICE D'ADMITTANCE FIXE

#### Nicolas KAMEL

#### **RÉSUMÉ**

Cette recherche est dédiée à l'étude de la méthode présentée par Pejovic and Maksimovic (1994). Plus précisément, ce travail a trois objectifs. Premièrement, d'étudier et de quantifier les effets de cette méthode sur la précision des simulations. Deuxièmement, à partir de cette information, de développer une méthode pour optimiser le paramètre  $G_s$  sans avoir recours à l'essaie et l'erreur. Un algorithme est donc proposé pour optimiser d'une manière automatique le paramètre  $G_s$ . Cette méthode a été validée sur trois topologies différentes, soient un onduleur deux niveaux, un onduleur trois niveaux NPC et un convertisseur matricielle directe. Troisièmement, d'explorer des solutions possibles qui conservent les avantages d'utiliser une matrice d'admittance fixe (petit pas de calcul, faible consommation de mémoire) tout en réduisant ses inconvénients (simulations moins précises). Une méthode est proposée qui offre la précision d'une matrice d'admittance variable, mais avec un requis de mémoire beaucoup plus faible. Cette méthode à été validée en temps différé, mais il reste à déterminer si elle peut être implémenter sur FPGA avec un pas de calcul assez petit.

**Mot-clés :** Simulation en temps réel, matrice d'admittance fixe, électronique de puissance, FPGA

# **CONTENTS**

|      |           |                                                              | Page |

|------|-----------|--------------------------------------------------------------|------|

| INTR | ODUCTI    | ON                                                           | 1    |

| СНАІ | PTER 1    | LITERATURE REVIEW                                            | 3    |

| 1.1  | Fundan    | nentals of circuit simulation                                |      |

| 1.2  | CPU an    | nd GPU based simulation                                      | 4    |

| 1.3  | FPGA 1    | based simulation                                             | 4    |

| 1.4  | Precom    | puting the inverses of a variable admittance matrix          | 6    |

| 1.5  | Incorpo   | orating a priori knowledge                                   | 7    |

| 1.6  |           | switch models                                                |      |

| 1.7  | Conclu    | sion                                                         | 9    |

| CHAI | PTER 2    | EFFECT OF $G_S$ PARAMETER ON SIMULATION ACCURACY             |      |

|      |           | FOLLOWING A COMMUTATION                                      |      |

| 2.1  | Explana   | ation of the Pejovic method                                  |      |

|      | 2.1.1     | Switch model                                                 |      |

|      | 2.1.2     | Calculating the value of the memory current source           |      |

|      | 2.1.3     | Switch update rules                                          |      |

|      |           | 2.1.3.1 Turn ON                                              |      |

|      |           | 2.1.3.2 Turn OFF                                             |      |

|      | 2.1.4     | Drawbacks of the model                                       |      |

|      | 2.1.5     | Pejovic's error analysis                                     |      |

| 2.2  |           | tical commutation process                                    |      |

|      | 2.2.1     | $sw_1$ turn OFF and $sw_2$ turn ON process                   |      |

|      | 2.2.2     | sw <sub>1</sub> turn ON and sw <sub>2</sub> turn OFF process |      |

| 2.3  |           | ntation process using Pejovic method                         |      |

|      | 2.3.1     | Notation conventions                                         |      |

|      | 2.3.2     | Equations for the switch voltage and current                 |      |

|      | 2.3.3     | sw <sub>1</sub> turn ON and sw <sub>2</sub> turn OFF process |      |

|      |           | 2.3.3.1 Interval 1: $sw_1$ is ON and $sw_2$ is ON            |      |

|      | 2.2.4     | 2.3.3.2 Interval 2: $sw_1$ is ON and $sw_2$ is OFF           |      |

|      | 2.3.4     | $sw_1$ turn OFF and $sw_2$ turn ON process                   |      |

|      |           | 2.3.4.1 Interval 1: $sw_1$ is OFF and $sw_2$ is ON           |      |

| 2.4  | C 1       | 2.3.4.2 Effect of dead time                                  |      |

| 2.4  | Conclu    | sion                                                         | 33   |

| CHAI | PTER 3    | EFFECT OF $G_S$ PARAMETER ON FUNDAMENTAL COMPONENT           |      |

|      |           | OF OUTPUT CURRENT AND ON COMMUTATION LOSSES                  |      |

| 3.1  | Effect of | of $G_s$ parameter on $i_{load_1}$                           | 35   |

| 3.2  |           | of $G_s$ parameter on commutation losses                     |      |

| 3.3  | Conclu    | sion                                                         | 40   |

| CHA   | PTER 4  | OPTIMIZATION METHOD AND VALIDATION                           | 43  |

|-------|---------|--------------------------------------------------------------|-----|

| 4.1   | Optimi  | zation method                                                | 43  |

|       | 4.1.1   | Implementation of the algorithm                              | 44  |

|       | 4.1.2   | Analytical expression for the case of the two level inverter | 44  |

|       | 4.1.3   | Relationship between the proposed algorithm and simulation   |     |

|       |         | accuracy following a commutation                             | 45  |

| 4.2   | Optimi  | zation methods validation                                    |     |

|       | 4.2.1   | Summary of results                                           |     |

|       | 4.2.2   | Two level inverter                                           |     |

|       |         | 4.2.2.1 Example analytical calculation of $G_s$              |     |

|       |         | 4.2.2.2 Waveforms at optimal $G_s$                           |     |

|       | 4.2.3   | Three level NPC inverter                                     |     |

|       |         | 4.2.3.1 Waveforms at optimal Gs                              |     |

|       | 4.2.4   | Direct matrix converter                                      |     |

|       |         | 4.2.4.1 Waveforms at optimal Gs                              |     |

| 4.3   | Conclu  | sion                                                         |     |

| СНА   | PTER 5  | HYBRID FIXED-VARIABLE ADMITTANCE MATRIX METHOD               |     |

| 01111 | 1 12110 | 67                                                           |     |

| 5.1   | The Sh  | erman-Morrison-Woodbury identity                             | 67  |

| 5.2   |         | ation of the proposed method                                 |     |

| 5.3   | _       | ed memory calculation                                        |     |

|       | •       | •                                                            |     |

| CON   | CLUSIO  | N                                                            | 73  |

| BIBI  | JOGR AP | НҮ                                                           | 74  |

| דעוע  |         | ±±±                                                          | / 🎞 |

# LIST OF TABLES

|           |                                           | Page |

|-----------|-------------------------------------------|------|

| Table 4.1 | Summary of results at optimal Gs          | 47   |

| Table 4.2 | Two level inverter parameter values       | 48   |

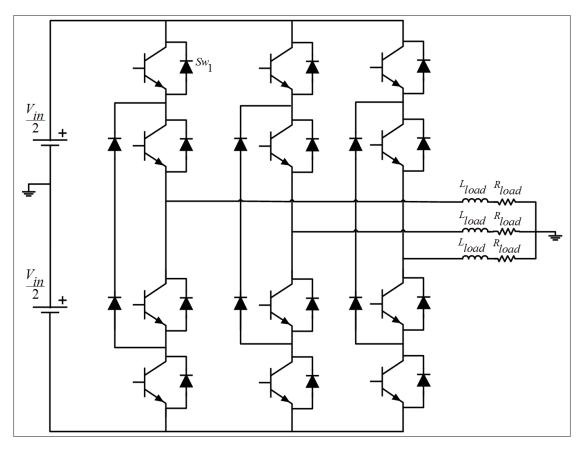

| Table 4.3 | Three level NPC inverter parameter values | 55   |

| Table 4.4 | Direct matrix converter parameter values  | 60   |

| Table 5.1 | Precomputed matrix dimensions             | 71   |

# LIST OF FIGURES

|             | P                                                                                                                                                                                         | age  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Matrix vector multiplication implemented on an FPGA                                                                                                                                       | 6    |

| Figure 2.1  | The Pejovic switch model. The continuous time representations of the switches when OFF and ON are shown on the left, and their equivalent discrete representations are shown on the right | . 12 |

| Figure 2.2  | Pejovic's analysis of the behaviour of the commutation of one arm                                                                                                                         | . 14 |

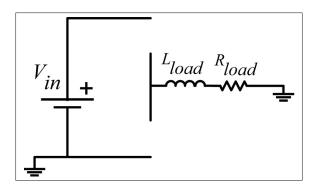

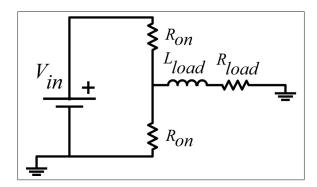

| Figure 2.3  | Schematic of a two level inverter. Note that the AC side of the converter is grounded. This will cause the load current to always be positive                                             | . 16 |

| Figure 2.4  | Theoretical commutation process from ON-OFF to OFF-ON                                                                                                                                     | . 17 |

| Figure 2.5  | Theoretical commutation process from OFF-ON to ON-OFF                                                                                                                                     | . 18 |

| Figure 2.6  | Equivalent circuit of one arm of a two-level inverter modeled using the Pejovic method. Note that $R_s$ is simply $\frac{1}{G_s}$                                                         | . 19 |

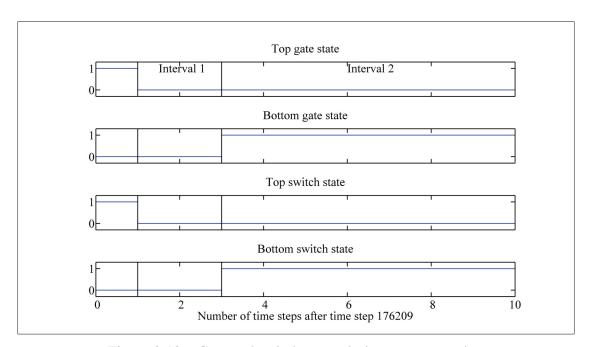

| Figure 2.7  | Gate and switch states during a commutation from OFF-ON to ON-OFF using the Pejovic method                                                                                                | . 21 |

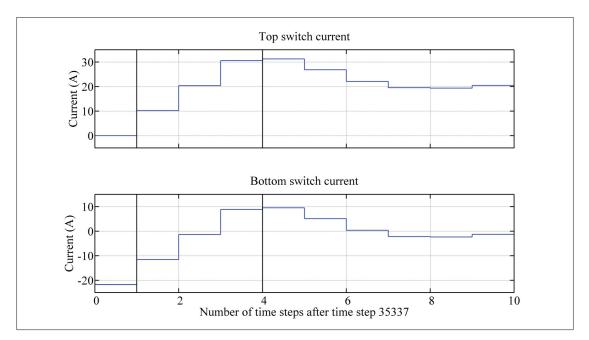

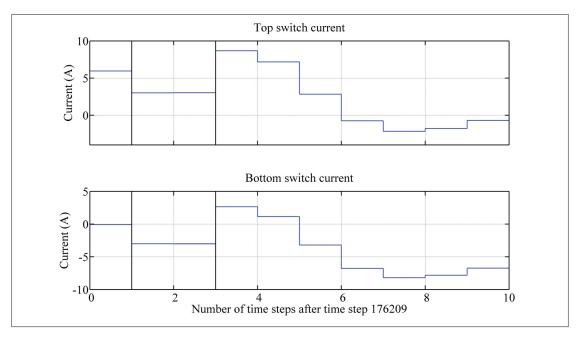

| Figure 2.8  | Switch currents during a commutation from OFF-ON to ON-OFF using the Pejovic method                                                                                                       | . 22 |

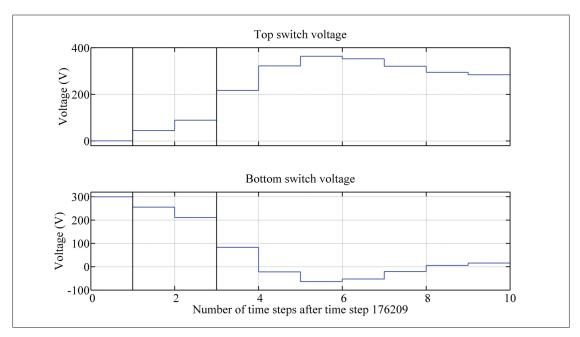

| Figure 2.9  | Switch voltages during a commutation from OFF-ON to ON-OFF using the Pejovic method                                                                                                       | . 22 |

| Figure 2.10 | Continuous time representation of the transition from OFF-ON to the ON-ON intermediate interval                                                                                           | . 23 |

| Figure 2.11 | Continuous time representation of the circuit for the second interval                                                                                                                     | . 26 |

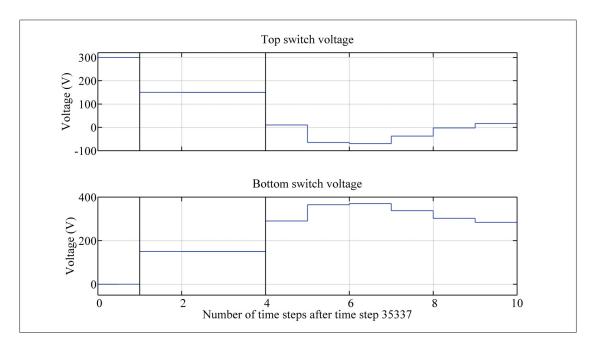

| Figure 2.12 | Gate and switch states during a commutation from ON-OFF to OFF-ON using the Pejovic method                                                                                                | . 30 |

| Figure 2.13 | Switch currents during a commutation from ON-OFF to OFF-ON using the Pejovic method                                                                                                       | . 31 |

| Figure 2.14 | Switch voltages during a commutation from ON-OFF to OFF-ON using the Pejovic method                                                                                                       | 31   |

| Figure 3.1  | Approximate circuit representation for a 2 level inverter with a very low value of $G_s$                                | 35 |

|-------------|-------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2  | Approximate circuit representation for a 2 level inverter with a very high value of $G_s$                               | 36 |

| Figure 3.3  | Waveforms for a 2 level inverter with a very high value of $G_s$                                                        | 37 |

| Figure 3.4  | Visualization of the commutation losses introduced by the Pejovic method                                                | 38 |

| Figure 4.1  | Schematic of two level inverter                                                                                         | 48 |

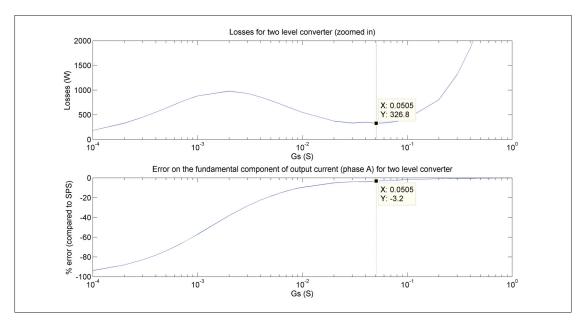

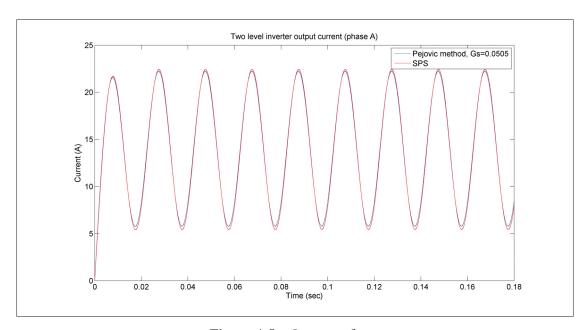

| Figure 4.2  | Losses and error on $i_{load_1}$ for different Gs values for a two level inverter                                       | 49 |

| Figure 4.3  | Error on the DC component of the output current for different Gs values for a two level inverter                        | 49 |

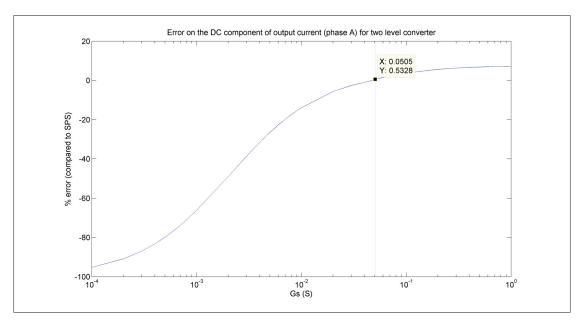

| Figure 4.4  | Sum of % losses and % error on the fundamental output current for different Gs values for a two level inverter          | 51 |

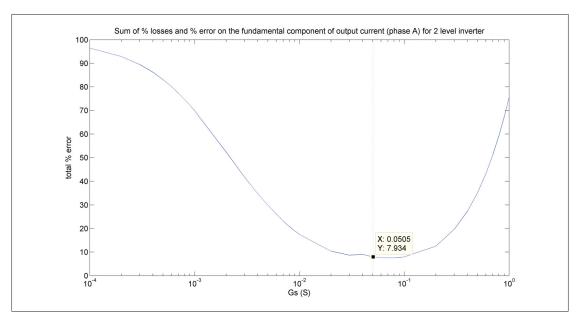

| Figure 4.5  | I <sub>out</sub> waveform                                                                                               | 52 |

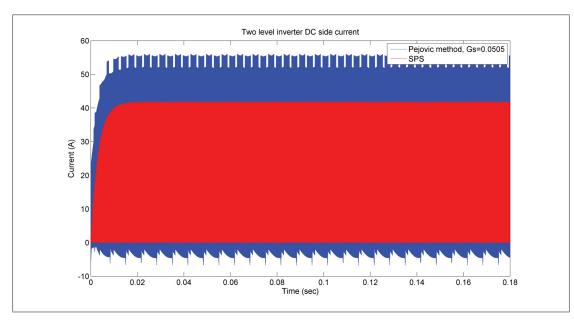

| Figure 4.6  | DC side current waveform.                                                                                               | 53 |

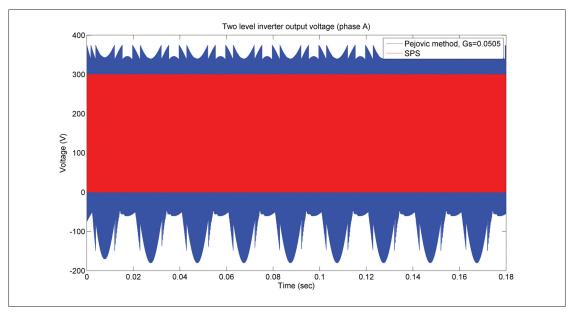

| Figure 4.7  | V <sub>out</sub> waveform                                                                                               | 53 |

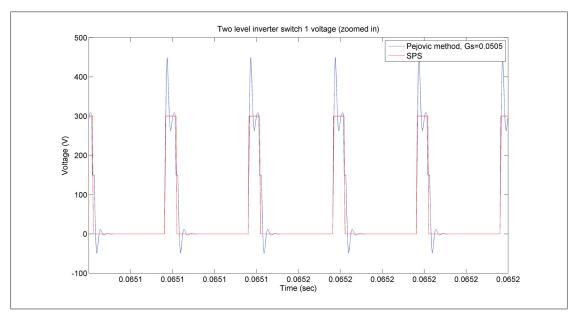

| Figure 4.8  | $v_{sw_1}$ waveform.                                                                                                    | 54 |

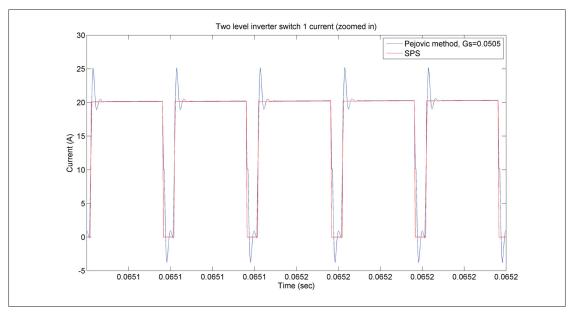

| Figure 4.9  | $i_{sw_1}$ waveform                                                                                                     | 54 |

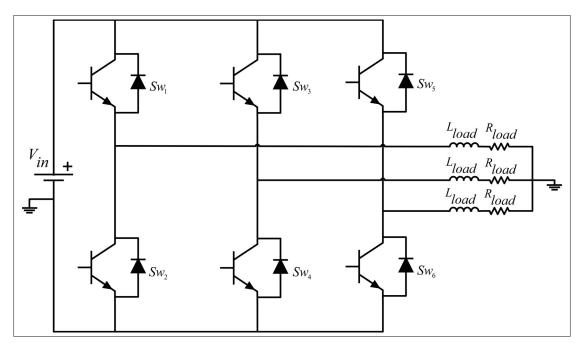

| Figure 4.10 | Schematic of three level NPC inverter                                                                                   | 55 |

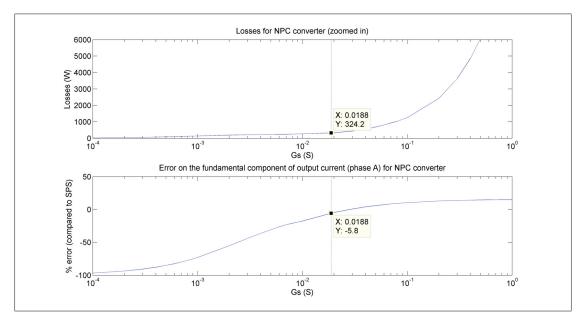

| Figure 4.11 | Losses and error on the fundamental current for different Gs values for a three level NPC inverter                      | 56 |

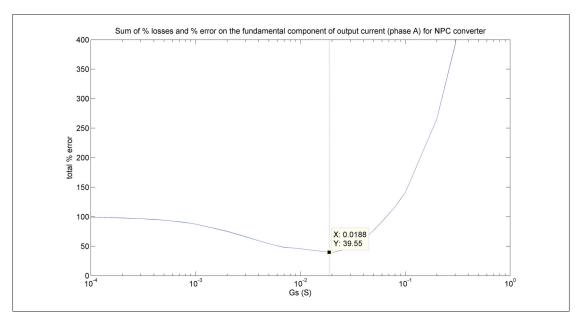

| Figure 4.12 | Sum of % losses and % error on the fundamental output current for different $G_s$ values for a three level NPC inverter | 57 |

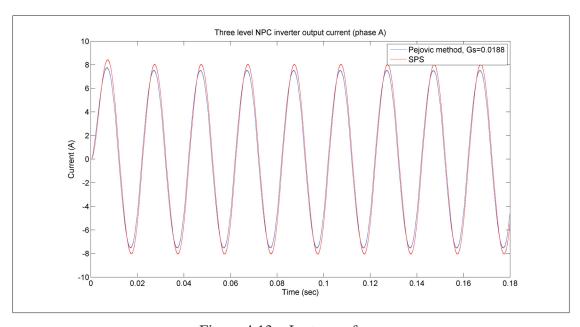

| Figure 4.13 | Iout waveform                                                                                                           | 57 |

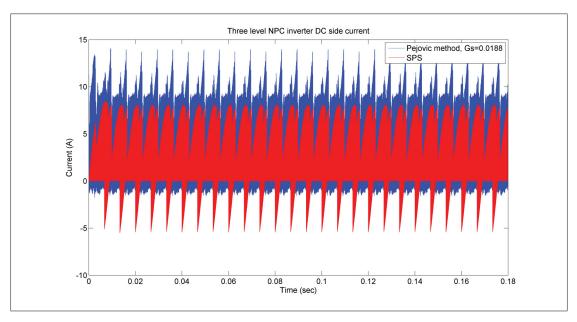

| Figure 4.14 | DC side current waveform.                                                                                               | 58 |

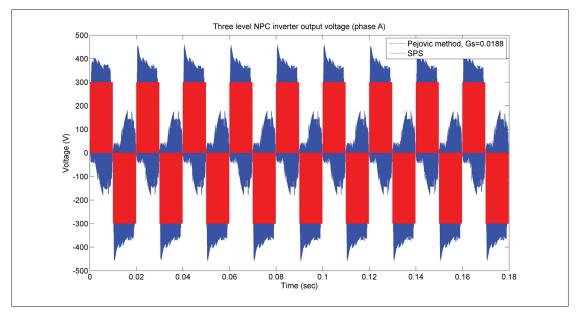

| Figure 4.15 | Vout waveform                                                                                                           | 58 |

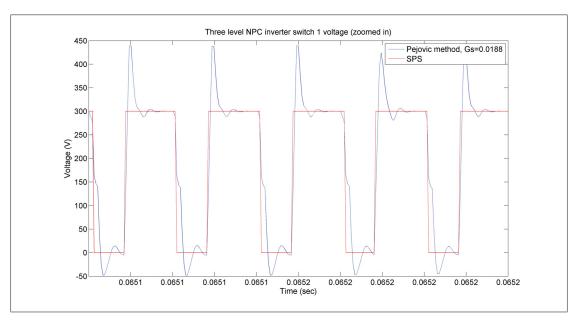

| Figure 4.16 | $v_{sw_1}$ waveform                                                                                                     | 59 |

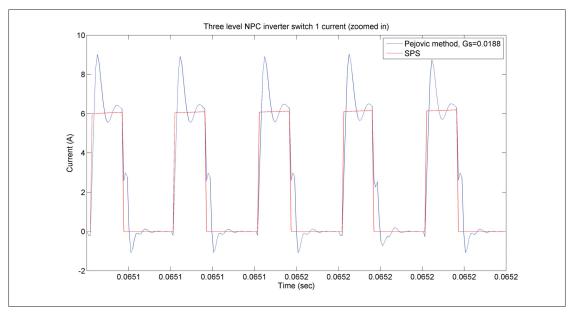

| Figure 4.17 | $i_{SW_1}$ waveform                                                                                                 | 59 |

|-------------|---------------------------------------------------------------------------------------------------------------------|----|

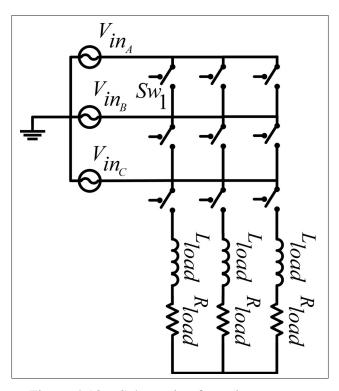

| Figure 4.18 | Schematic of matrix converter                                                                                       | 60 |

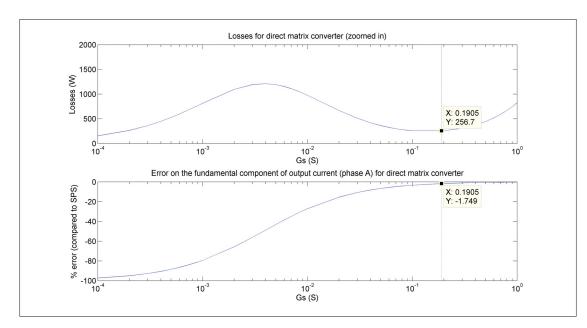

| Figure 4.19 | Losses and error on the fundamental current for different Gs values for a direct matrix converter                   | 61 |

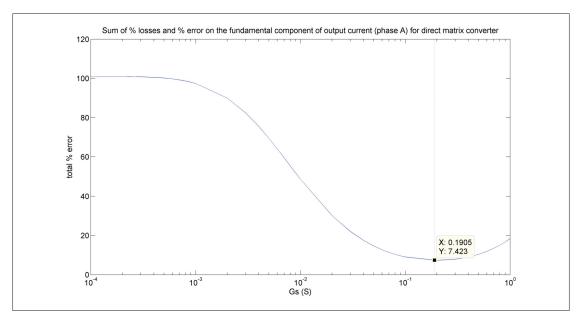

| Figure 4.20 | Sum of % losses and % error on the fundamental output current for different Gs values for a direct matrix converter | 61 |

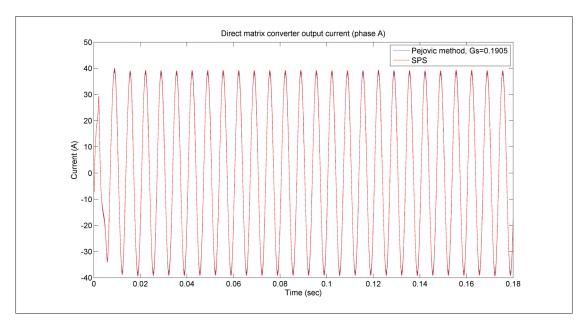

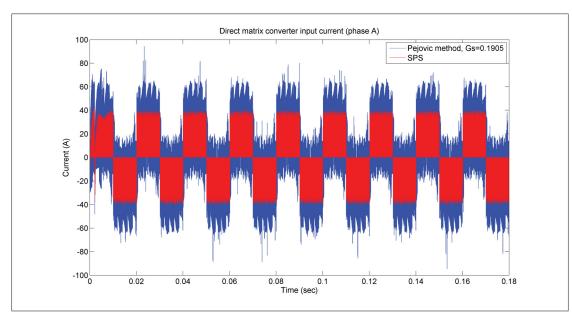

| Figure 4.21 | I <sub>out</sub> waveform                                                                                           | 62 |

| Figure 4.22 | I <sub>in</sub> waveform                                                                                            | 63 |

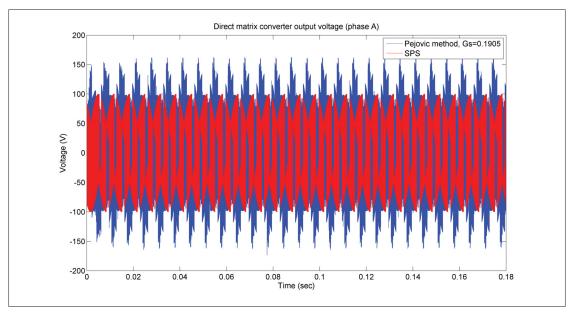

| Figure 4.23 | V <sub>out</sub> waveform                                                                                           | 63 |

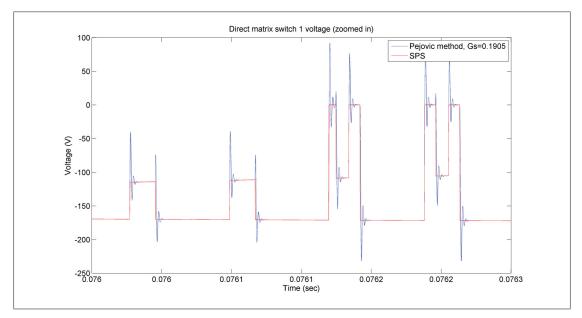

| Figure 4.24 | $v_{sw_1}$ waveform                                                                                                 | 64 |

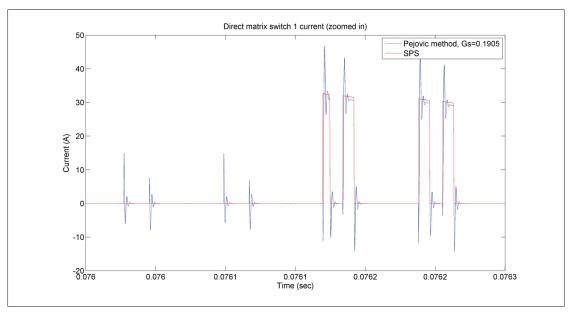

| Figure 4.25 | $i_{sw_1}$ waveform                                                                                                 | 64 |

# LIST OF ABREVIATIONS

CPU Central processing unit

ETS École de Technologie Supérieure

FPGA Field-programmable gate array

GPU Graphics processing unit

KCL Kirchoff's current law

KVL Kirchoff's voltage law

MNA Modified nodal analysis

SPS SimPowerSystems

#### INTRODUCTION

The real time simulation of power electronics is particularly challenging due to the low time steps that must be reached in order to accurately simulate high frequency phenomena. In order to achieve such time steps, computationally expensive operations such as matrix inversion must be avoided. The fixed admittance matrix method proposed by Pejovic and Maksimovic (1994) (hereby referred to simply as the "Pejovic method") eliminates these expensive operations by modeling a switch as a capacitor when it is OFF and an inductor when it is ON. Moreover, the algorithm's structure allows it to be hardware accelerated with an FPGA implementation. It is therefore a promising simulation technique for the real time simulation of converters operating at frequencies of 20kHz and higher and it has been successfully used in commercial applications. Unfortunately, this method has two main drawbacks which limit its adoption in industry. First, the value of a parameter named  $G_s$  must be chosen when performing simulations. The  $G_s$ parameter controls the value of the capacitance and inductance of the modeled switch. It therefore has a critical effect on simulation accuracy, and unfortunately its optimal value depends on a multitude of variables such as the converter topology, the nature of the load, the value of the input source, etc. Currently, this parameter must be tuned manually through trial and error which is a time consuming and sometimes inaccurate process. The second drawback of the Pejovic method is that even for an optimal value of the parameter, the simulation accuracy may not be acceptable. This work is dedicated to the study of the Pejovic method, with the goal of mitigating the drawbacks of the method and increasing its commercial potential. The first chapter of this thesis is dedicated to a literature review of the various methods used for the real time simulation of power electronics. In the second chapter, the Pejovic method is explained in detail and the effect of the  $G_s$  parameter on simulation accuracy following a commutation is studied. In the third chapter, the effect of the  $G_s$  parameter on the output load current and commutation losses is examined. In the fourth chapter, a method to automatically optimize the  $G_s$  parameter is derived and validated for three case studies. Finally, in the fifth chapter, a hybrid fixed-variable admittance matrix method is proposed. This method lessens the memory required when precomputing and storing all the possible matrix inverses of a variable admittance matrix. However, the minimum time step achievable with this method on FPGA has not yet been assessed and this a potential path for future researchers.

#### **CHAPTER 1**

#### LITERATURE REVIEW

#### 1.1 Fundamentals of circuit simulation

The simulation of electrical circuits is fundamental to the areas of electronic design automation, power systems, and power electronics where the behavior of circuits is tested and analyzed prior to manufacturing. (Najm, 2010, p.3) explains how this behavior can be quantified for the use of circuit simulators: "The behavior of a circuit is captured by a set of equations that are formulated by combining the element equations and Kirchoff's Current and Voltage Laws (KCL and KVL). In general, this results in a set of simultaneous non-linear first-order differential equations." The first step is to form this system of equations using a systematic method such as Modified Nodal Analysis (MNA). Then, this system of equations is discretized using a numerical integration method such as Backward-Euler at a certain time step. As Belanger et al. (2010) explains, this system is solved at every time step with the output states of a given time step becoming the input states of the next time step. The required length of the time step is determined by the bandwidth of the system to be simulated. If the simulator is to accurately replicate high frequency phenomena, a low time step must be chosen. This poses a problem for real-time simulation, where the time required to solve the network equations must be less than or equal to the simulation time step. Furthermore, in hardware-in-the-loop (HIL) simulations in which a physical controller is connected to the simulator, not only must be the network equations be solved at every step, but the simulated output must be sent to the controller and the controller input must be sent to the simulator. Therefore, the time it takes to solve the network equations in addition to the I/O latency between the simulator and the controller must be less than or equal to the simulation time step.

#### 1.2 CPU and GPU based simulation

A commonly followed guideline for power electronics established by Gole *et al.* (1997) is to choose a time step equal to 1% of the commutation period. Since high frequency converters are becoming more and more common, this poses a challenge. If a converter is to be simulated with a switching frequency of 70 kHz, then a time step of about 143 ns is required. According to Blanchette *et al.* (2012), modern CPUs can only achieve time steps around  $5\mu$ s. Although CPUs have high clock frequencies, their parallelism is limited, and it takes a significant amount of time for the simulated output to be sent from the CPU to the controller.

GPUs are becoming popular in the area of scientific computing due to their massively parallel architecture. Jalili-Marandi and Dinavahi (2009) used GPUs to accelerate the simulation of large power systems. They reported speed-ups of up to 344.8 over a CPU implementation. However, it is important to note that despite the speed-up, it did not reach real-time performance, and according to Lustig and Martonosi (2013) a main disadvantage of the GPU is the overhead when transferring data to and from it.

#### 1.3 FPGA based simulation

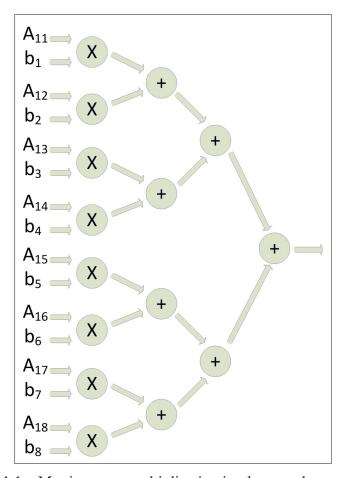

Another massively parallel device that has become popular in the world of real time simulation is the FPGA. FPGAs have a very high degree of parallelism that allows certain types of operations such as matrix multiplication to be significantly accelerated. This principle is explained

below. Consider the following matrix-vector multiplication:

$$\begin{bmatrix} A_{11} & A_{12} & A_{13} & A_{14} & A_{15} & A_{16} & A_{17} & A_{18} \\ A_{21} & A_{22} & A_{23} & A_{24} & A_{25} & A_{26} & A_{27} & A_{28} \end{bmatrix} \begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \\ b_6 \\ b_7 \\ b_8 \end{bmatrix}$$

$$(1.1)$$

On an FPGA, the dot product between the first row of the matrix A with the vector b and the dot product between the second row of the matrix A with the vector b can be computed in parallel. The calculation of the product between the first row of the matrix A and the vector b is illustrated in figure 1.1. First, each entry of the first row of the matrix must be multiplied with the corresponding entry of the vector. On an FPGA, these eight multiplications can be done in parallel, a speed up of eight over a sequential implementation. It is important to note however, that the speed-up potential of the FPGA is limited by the fact that the results of these multiplications must be summed together. Since an addition operation can only take two inputs, multiple sequential layers of addition are required (in this example, 3), which increases the calculation time. That being said, the speed-up offered by FPGAs for matrix vector multiplication is still significant. In addition, the latency between the FPGA and the physical I/Os is very low.

Unfortunately, solving a system of equations is a more complex process than a matrix vector multiplication, and even on an FPGA, the time it requires often exceeds the allowed time step. Indeed, for a 5x5 matrix, Dohi *et al.* (2012) reported latencies of 3.05 and 8.69 microseconds for solving a system of five equations using Gauss-Jordan elimination and Cramer's rule, respectively. Mahapatra *et al.* (2012) reported performing a 4x4 matrix inversion in 290ns, a relatively small time step. However, in order the solve the system of equations, the inverse

Figure 1.1 Matrix vector multiplication implemented on an FPGA

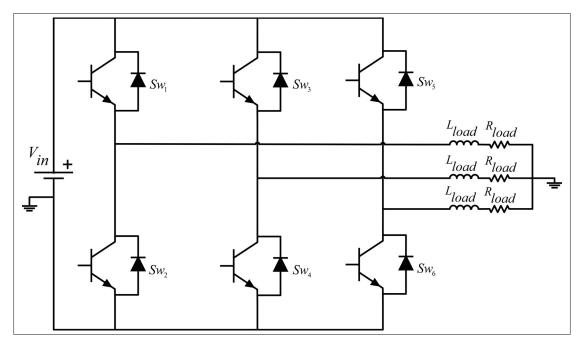

would have to be multiplied by the input vector which would increase the time step. Furthermore, 4x4 and 5x5 matrices are small by power electronics standards. For example, the system matrix of the boost converter formed by Pejovic and Maksimovic (1994) (which contains only two switches) is 7x7. Therefore, solving the system matrix at every step is not feasible for high frequency power electronics, regardless of whether a CPU, GPU, or FPGA is used.

## 1.4 Precomputing the inverses of a variable admittance matrix

A method to quickly solve the network equations is to precompute the inverse of the system matrix before the start of the simulation as explained by Bachir *et al.* (2010). Therefore, the outputs can be obtained at every step by simply multiplying the input vector by the inverse matrix, a task that can be accomplished very quickly on an FPGA as was previously explained.

However, the system matrix of a power converter changes every time a commutation occurs. The approach of precomputing the inverse can still be used as long as the inverses of all possible system matrices are precomputed and stored in the FPGA's memory. For a power converter with n switches, there are  $2^n$  possible system matrices. As the number of switches increases, the amount of memory required on the FPGA grows exponentially. Blanchette  $et\ al.\ (2012)$  reported that this approach is only viable for converters limited to 6 or 7 switches. Although external DDR3 memory can be added to the FPGA, the time required to read from the memory is too long for real time simulation. Due to these constraints, other techniques have been proposed to simulate high frequency converters with over seven switches in real-time.

## 1.5 Incorporating a priori knowledge

One such method is to incorporate a priori knowledge about the converter to be simulated into the real time simulator. Indeed, the complexity of the converter to simulate can be significantly reduced if assumptions are made about its modes of operation. This has been used for the simulation of MMCs. Gregoire *et al.* (2011) determined a priori the conditions that would result in a cell of the MMC being ON, OFF, or in high-impedance mode. Then, functions were elaborated that determined the current through the cell's inductor and the voltage across its output capacitor based upon the state of the cell. By doing this, 60 cells composed of two IGBT/diodes each were simulated on an FPGA with a time step of 250ns. For this large number of switches, such a low time step would not be achievable if the system of equations were formed and had to be solved at each step. However, the above method is not generalizable to other topologies.

Myaing and Dinavahi (2011) simulated a three level voltage source inverter on an FPGA with a very low time step. The possible switching combinations of the converter were determined a priori, excluding faulted states. For example, for the four IGBTs in one arm, only five valid states were considered, instead of the theoretically possible sixteen. At every time step of the simulation, based on the polarity of the output current and the current switching state of the converter, the output voltage and input current were calculated. Using this approach a

time step of 12.5ns was reported. Despite this impressive time step, this method suffers from the same drawback of the MMC method: lack of generality. If, for example, one wishes to simulate a faulted state of the converter, then this model is no longer valid. Furthermore, for more complicated topologies, establishing the flow of converter switching states becomes an elaborate undertaking. For a general purpose solver, another approach must be used.

# 1.6 Special switch models

One approach is to use switch models that allow the system matrix to contain certain characteristics. Blanchette *et al.* (2012) modeled each switch as a resistance in parallel with a capacitance. When the switch is ON, the value of the resistance is low, and when the switch is OFF, the value of the resistance is high; therefore the admittance matrix is variable. For converters with a low number of switches, the capacitance is chosen to match the physical parasitic capacitance of the switch and the circuit is simulated by precomputing the inverses of the variable admittance matrix. When this no longer becomes feasible for higher number of switches, the system equations are solved using an iterative approach. Gauss-Seidel was used, which, according to the authors, converged in two iterations and they reported a time step 75ns for a boost converter. However, in order to guarantee convergence, the switch's parasitic capacitance had to be set to a value that ensured that the system matrix was diagonally dominant. This can affect the simulation accuracy since large capacitances may be required to ensure diagonal dominance if the time step is large.

Another switch model proposed by Pejovic and Maksimovic (1994) consisted of an inductor when the switch was ON and a capacitor when the switch was OFF. This representation allows the system matrix to remain constant, regardless of the switch states. This method will be explained by detail in the next chapter.

#### 1.7 Conclusion

It can be seen that the real time simulation of high frequency power converters is limited by numerous constraints. Indeed, the limited memory on board FPGAs prevents precomputing the inverses of converters with more than a few number of switches. The computational complexity of solving a system of equations results in unacceptably high time steps. Making use of a priori knowledge results in simulators that cannot be easily extend to different cases. Finally, as will be explored at length in the subsequent chapters, using special switch models reduces simulation accuracy.

#### **CHAPTER 2**

# EFFECT OF $G_S$ PARAMETER ON SIMULATION ACCURACY FOLLOWING A COMMUTATION

In this chapter, the nature of the  $G_s$  parameter will be explained. Then, the theoretical commutation of a two level inverter will be compared and contrasted to its commutation when it is simulated with the Pejovic method, and it the effect of the  $G_s$  parameter during commutation will be examined.

#### 2.1 Explanation of the Pejovic method

The method presented by Pejovic and Maksimovic (1994) is popular in the field of real time simulation because low time steps can be achieved due to the fact that the admittance matrix is constant for all switch combinations. In this section, this method will be presented in detail.

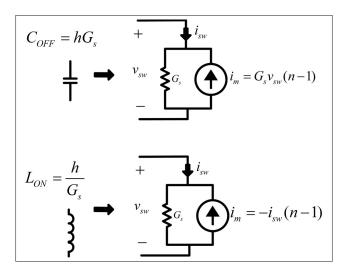

#### 2.1.1 Switch model

Pejovic and Maksimovic (1994) guaranteed a constant system matrix by modeling each switch as a conductance (denoted as  $G_s$ ) in parallel with a current source. This method benefits from the fact that the discrete companion models of the inductor and the capacitor are both represented as a conductance in parallel with a current source. The only difference between the two components is how the value of the current source is determined. With the Pejovic method, a switch is modeled as an inductor when ON ( $L_{ON}$ ) and a capacitor when OFF ( $C_{OFF}$ ). This is illustrated in figure 2.1. On the left side are the switch representations in continuous time, and on the right side are the discrete companion models. It can also be seen that the value of the  $L_{ON}$  and  $C_{OFF}$  depend on the value of  $G_s$ .

Figure 2.1 The Pejovic switch model. The continuous time representations of the switches when OFF and ON are shown on the left, and their equivalent discrete representations are shown on the right

#### 2.1.2 Calculating the value of the memory current source

If Backward-Euler numerical differentiation is used, when the switch is OFF, the current source  $i_m(n)$  is equal to  $G_s v_{sw}(n-1)$  and when the switch is ON,  $i_m(n)$  is equal to  $-i_{sw}(n-1)$ . The benefit of modeling switches in such a manner is that only the value of  $G_s$  appears in the system matrix; the value of the current source appears in the input vector. If a constant value of  $G_s$  is chosen, the matrix is constant for all possible switch combinations and the inverse of the admittance matrix needs to be computed only once at the beginning of the simulation.

#### 2.1.3 Switch update rules

In order to calculate the value of the memory current source, the states of the switches must be known. The conditions under which a switch will turn ON or OFF are explained below.

#### 2.1.3.1 Turn ON

An ideal switch turns ON the same step that its gate turns ON. A diode turns ON the step after the voltage across it becomes positive. With the Pejovic method, a pair consisting of a

switch and an antiparellel diode can be modelled as one component. This component turns ON the same step that its gate turns ON or, if the gate is OFF, the step after the voltage across it becomes negative.

#### 2.1.3.2 Turn OFF

An ideal switch turns OFF the same step that its gate turns OFF. A diode turns OFF the step after the current through it becomes negative. If its gate is OFF, a switch/diode pair turns OFF the step after the current through the pair becomes positive.

#### 2.1.4 Drawbacks of the model

In order to maximize the simulation accuracy, the values of  $L_{ON}$  and  $C_{OFF}$  should be kept as small as possible. From figure 2.1 it can be seen that the only way to do so is to reduce the size of the time step h. However, the minimum time step is limited by the speed at which the FPGA can multiply the precomputed inverse of the admittance matrix by the input vector. Despite being able to perform each dot product operation in parallel, for a given dot product, a series of sequential additions is required which limits the minimum possible time step as shown in figure 1.1. Belanger  $et\ al.\ (2013)$  simulated several converters on an FPGA using the Pejovic method with time steps in the order of 100ns. With a time step of 100ns, and a  $G_s$  set to 1,  $L_{ON}$  is equal to 100nH and  $C_{OFF}$  is equal to 100nF, values which are not negligible. The other parameter that the determines the size of the parasites is the switch conductance,  $G_s$ .  $C_{OFF}$  is directly proportional to  $G_s$  and  $L_{ON}$  is inversely proportional to  $G_s$ , so by varying the value of  $G_s$ , the value of one parasite can be reduced, at the cost in an increase of the magnitude of the other parasite. The value of  $G_s$  therefore has an important effect on simulation accuracy, and it can be very time consuming empirically choosing its optimal value for a given simulation. This is the motivation for developing an automatic method to optimize the  $G_s$  parameter.

## 2.1.5 Pejovic's error analysis

Pejovic and Maksimovic (1994) analyzed the commutation of two ideal switches from ON-OFF to OFF-ON. This situation is illustrated in figure 2.2.

Figure 2.2 Pejovic's analysis of the behaviour of the commutation of one arm

When this scenario was simulated using the Pejovic method, Pejovic and Maksimovic (1994) observed that there were errors on the switches' voltage and current due to the parasitic  $L_{ON}$  and  $C_{OFF}$  and they quantified the error as follows:

$$e_{v_{sw_2}}(n) = V_{in}(f(n) - f(n-1)) - \frac{I_{load}}{G_s f(n)}$$

(2.1)

$$e_{i_{sw_1}}(n) = I_{load}(f(n) - f(n-1)) + G_s V_{in} f(n)$$

(2.2)

where

$$f(n) = \frac{\sin(\frac{n\pi}{4})}{2^{\frac{n}{2}}} \tag{2.3}$$

They observed that these errors eventually decayed towards zero and that the instantaneous current error was directly proportional to the value of  $G_s$  while the instantaneous voltage error was inversely proportional to  $G_s$ . Based on their experiments with DC-DC converters, they determined that the optimal value of  $G_s$  was equal to  $\frac{I_{load}}{V_{in}}$ .

As can be seen, this analysis was performed for a circuit consisting of only ideal switches whose states changed simultaneously. Recall from section 2.1.3 that the state of an ideal switch changes during the same time step that its gate changes. However, most power electronic circuits consist of diodes and diode/switch pairs instead of ideal switches. This complicates the analysis since the states of the diodes and diode/switch pairs depend on the currents and voltages at the previous step. In other words, even if the gates of the two switch/diode pairs are changed simultaneously, the states of the switch/diode pairs will not necessarily change at the same time. In section 2.3, the original analysis of Pejovic and Maksimovic (1994) will be augmented by taking this effect into account. Beforehand, however, the theoretical behavior of a power electronic circuit undergoing a commutation will be examined. The analysis will be performed on one arm of the two level inverter shown in figure 2.3. The purpose of this analysis is to highlight the errors that the Pejovic method introduces when a commutation occurs. Quantifying these errors with respect to the  $G_s$  parameter is an essential step for developing an algorithm to automatically find the  $G_s$  value that minimizes the simulation error.

Figure 2.3 Schematic of a two level inverter. Note that the AC side of the converter is grounded. This will cause the load current to always be positive

## 2.2 Theoretical commutation process

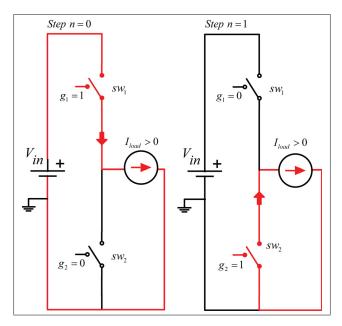

In this section, it will be assumed that no dead time is used and that the gates of the two switches in the arm change simultaneously. The effect of dead time will be covered in section 2.3.4.2. It will also be assumed the load current varies slowly with respect to the duration of the commutation. Hence, the inductive load current is approximated by a constant current source  $I_{load}$  as shown in figure 2.4. The symbols used in the following subsections are also identified on figure 2.4.

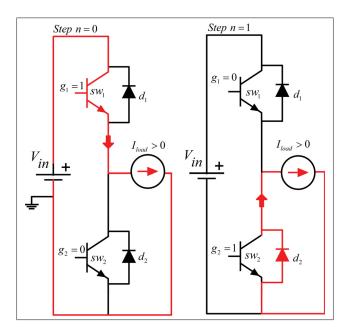

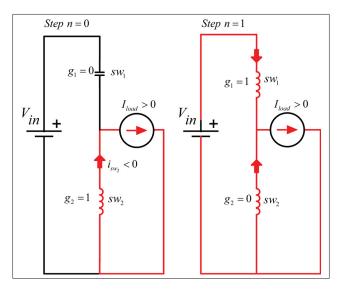

## 2.2.1 sw<sub>1</sub> turn OFF and sw<sub>2</sub> turn ON process

At some time step n = 0, the following conditions are assumed: the gate of the top switch  $sw_1$  is ON  $(g_1 = 1)$ , the gate of the bottom switch  $sw_2$  is OFF  $(g_2 = 0)$  and the load current  $I_{load}$  is positive. Since  $g_1 = 1$  and  $I_{load} > 0$ ,  $I_{load}$  must flow through  $sw_1$ . Since  $g_2 = 0$ , no current flows through  $sw_2$  or  $d_2$ . If at the next step, n = 1, the gate signals are changed such that  $g_1 = 0$

and  $g_2 = 1$ , no current flows through  $sw_1$  or  $d_1$  and  $I_{load}$  must flow through  $d_2$  ( $d_2$  turns ON). This process is shown in figure 2.4.

Figure 2.4 Theoretical commutation process from ON-OFF to OFF-ON

# 2.2.2 sw<sub>1</sub> turn ON and sw<sub>2</sub> turn OFF process

At some time step n = 0, the following conditions are assumed:  $g_1 = 0$ ,  $g_2 = 1$  and  $I_{load} > 0$ . Since  $g_1 = 0$ , no current flows through sw1 or  $d_1$ . Since  $g_2 = 1$  and  $I_{load} > 0$ ,  $I_{load}$  flows through  $d_2$ . If at the next step, n = 1, the gate signals are changed such that  $g_1 = 1$  and  $g_2 = 0$ ,  $I_{load}$  flows through  $sw_1$  and no current flows through  $sw_2$  or  $d_2$  ( $d_2$  turns OFF). This process is shown in figure 2.5.

Figure 2.5 Theoretical commutation process from OFF-ON to ON-OFF

# 2.3 Commutation process using Pejovic method

It can be observed that in the theoretical case, when a commutation occurs the switches and diodes changed states the moment the gate signals changed. In the Pejovic method, that is not the case. It will be shown that there are situations in which the switch/diode pairs update several steps after the gate signals change.

## 2.3.1 Notation conventions

Throughout this work, the following conventions will be used:  $(t_{k_x})$  marks the moments throughout a simulation when an OFF-ON to ON-OFF commutation begins;  $(t_{k_y})$  marks the moments throughout a simulation when an ON-OFF to OFF-ON commutation begins;  $(t_{k_i})$  corresponds to the moments when a switch turns OFF.

## 2.3.2 Equations for the switch voltage and current

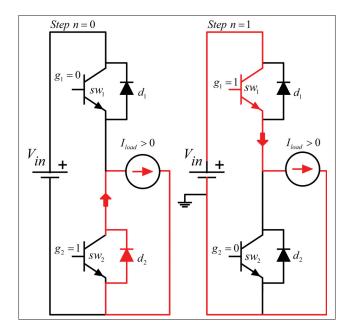

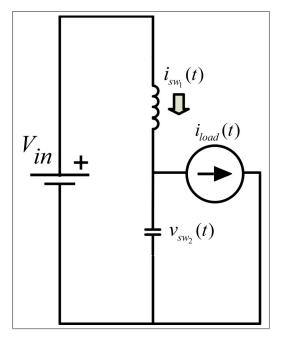

The inverter arm modeled using the Pejovic method is presented in figure 2.6. Each switch/diode pair is replaced by a current source in parallel with a resistance. Recall from section 2.1.3 that in order to update the state of a switch/diode pair the pair's current and voltage at the previous time step are required. Thus, in order to analyze the commutation process of a two-level inverter, the equations for the switch/diode pair's current and voltage will be formulated.

Figure 2.6 Equivalent circuit of one arm of a two-level inverter modeled using the Pejovic method. Note that  $R_s$  is simply  $\frac{1}{G_s}$

First, KCL is applied at the node where the three current sources meet.

$$i_{R_{s1}}(n) = i_{m_1}(n) + i_{R_{s2}}(n) - i_{m_2}(n) + i_{load}(n)$$

(2.4)

where  $i_{m_1}$  and  $i_{m_2}$  are the values of the current sources (memory elements) of the upper and lower switches, respectively,  $i_{R_{s1}}$  and  $i_{R_{s2}}$  are the values of the current flowing through the parallel resistance of the equivalent model of the upper and lower switch/diode pairs, respectively.  $i_{load}(n)$  is the value of the inductive load current.

Then KVL is applied around the loop composed of  $V_{in}$ ,  $R_{s_1}$ , and  $R_{s_2}$ .

$$V_{in} = R_{s_1} i_{R_{s_1}}(n) + R_{s_2} i_{R_{s_2}}(n)$$

(2.5)

where  $R_{s_1}i_{R_{s_1}}(n)$  is the voltage across the top switch/diode pair and  $R_{s_2}i_{R_{s_2}}(n)$  is the voltage across the bottom switch/diode pair.

Substituting equation (2.4) into equation (2.5), and rearranging yields:

$$i_{R_{s2}}(n) = \frac{V_{in} - R_{s_1}(i_{m_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}}$$

(2.6)

Substituting equation (2.6) into equation (2.4), and simplifying yields:

$$i_{R_{s1}}(n) = \frac{V_{in} + R_{s_2}(i_{mem_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}}$$

(2.7)

The current flowing through switch/diode pairs can be expressed as

$$i_{SW_1}(n) = i_{R_{s1}}(n) - i_{m_1}(n)$$

(2.8)

$$i_{sw_2}(n) = i_{R_{s2}}(n) - i_{m_2}(n)$$

(2.9)

Substituting (2.6) into (2.9) yields:

$$i_{sw_2}(n) = \frac{V_{in} - R_{s_1}(i_{m_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}} - i_{m_2}(n)$$

(2.10)

Similarly, substituting (2.7) into (2.8) yields:

$$i_{sw_1}(n) = \frac{V_{in} + R_{s_2}(i_{m_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}} - i_{m_1}(n)$$

(2.11)

The expressions for the voltages across the switch/diode pairs are

$$v_{sw_1}(n) = R_{s_1}(i_{sw_1}(n) + i_{m_1}(n)) = R_{s_1} \frac{V_{in} + R_{s_2}(i_{m_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}}$$

(2.12)

$$v_{sw_2}(n) = R_{s_2}(i_{sw_2}(n) + i_{m_2}(n)) = R_{s_2} \frac{V_{in} - R_{s_1}(i_{m_1}(n) - i_{m_2}(n) + i_{load}(n))}{R_{s_1} + R_{s_2}}$$

(2.13)

Equations 2.10 to 2.13 represent the voltages and currents of the two switches at a given time step in terms of the values of the current memory sources  $i_{m_1}(n)$  and  $i_{m_2}(n)$ . This representation is important since the way in which the memory current sources are calculated depends on the state of the switches. In the next subsection these expressions will be used to gain a deeper understanding into the behaviour of the switches voltages and currents following a commutation and how the  $G_s$  parameter affects the accuracy of these quantities.

# **2.3.3** $sw_1$ turn ON and $sw_2$ turn OFF process

In this subsection, the behavior of the inverter arm will be analyzed for the case when the top switch turns ON and the bottom switch turns OFF.

## **2.3.3.1** Interval 1: $sw_1$ is ON and $sw_2$ is ON

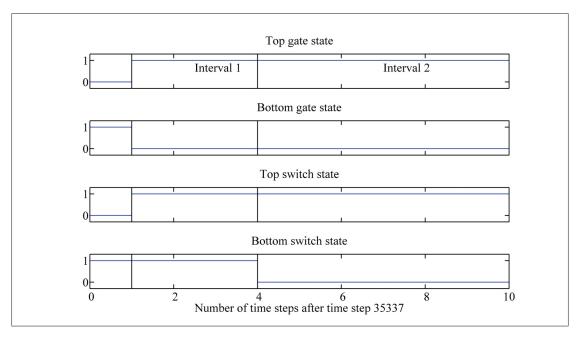

Figure 2.7 Gate and switch states during a commutation from OFF-ON to ON-OFF using the Pejovic method

Figure 2.8 Switch currents during a commutation from OFF-ON to ON-OFF using the Pejovic method

Figure 2.9 Switch voltages during a commutation from OFF-ON to ON-OFF using the Pejovic method

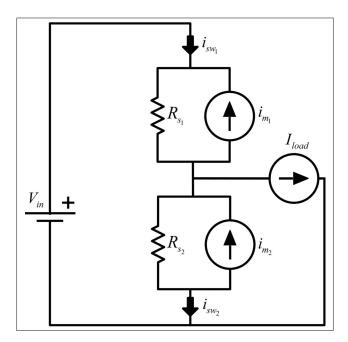

The behavior of the circuit during a sample OFF-ON to ON-OFF commutation is illustrated in figures 2.7, 2.8, and 2.9. It is assumed that the value of  $i_{load}(n)$  varies little during the commutation from OFF-ON to ON-OFF. Therefore,  $i_{load}(n)$  is approximated by current source  $I_{load}(t_{k_x})$  whose value is constant during the commutation beginning at moment  $t_{k_x}$ . At some time step n = 0, it is assumed that  $g_1 = 0$  and the top switch/diode pair is OFF ( $sw_1 = 0$ ). Also,  $g_2 = 1$  and the bottom diode/switch pair is ON ( $sw_2 = 1$ ), conducting a negative current with the same magnitude as  $I_{load}(t_{k_x})$ . This is shown on the left of side of figure 2.10. At the next step, n = 1, the gate signals are changed such that  $g_1 = 1$  and  $g_2 = 0$  causing  $sw_1$  to turn ON.

Figure 2.10 Continuous time representation of the transition from OFF-ON to the ON-ON intermediate interval

Since at the previous time step,  $i_{sw_2}$  was negative,  $sw_2$  remains ON. Therefore, both the top and bottom switches are ON, and since each ON switch is modeled as an inductor, the continuous time representation of the circuit consists of two inductors in series as shown in the right hand side of figure 2.10. Referring back to the discretized circuit shown in figure 2.6, during this interval,  $i_{m_1}(n) = -i_{sw_1}(n-1)$  and  $i_{m_2}(n) = -i_{sw_2}(n-1)$ . Substituting the values of  $i_{m_1}(n)$  and  $i_{m_2}(n)$  into (2.10) and simplifying yields:

$$i_{sw_2}(n) = \frac{V_{in}}{R_{s_1} + R_{s_2}} + i_{sw_2}(n-1)$$

(2.14)

Equations (2.12) and (2.13) reduce to

$$v_{sw_1}(n) = R_{s_1} \frac{V_{in}}{R_{s_1} + R_{s_2}}$$

(2.15)

$$v_{sw_2}(n) = R_{s_2} \frac{V_{in}}{R_{s_1} + R_{s_2}}$$

(2.16)

This is simply a voltage divider, and if the two switch resistances are the same (meaning that the same value of  $G_s$  is used for each switch), then the two switch voltages will be equal to half of the input voltage. These equations are valid as long as both switches in the arm are ON. Equation (2.14) reveals that every time step during interval 1 (when both switches are ON),  $i_{sw_2}$  will increase by a certain value. This can be expressed as:

$$\Delta i_{sw_2} = \frac{V_{in}}{R_{s_1} + R_{s_2}} \tag{2.17}$$

Recall that  $R_{s_1}$  and  $R_{s_2}$  are simply  $\frac{1}{R_{s_1}}$  and  $\frac{1}{R_{s_2}}$  respectively. If the same value of  $G_s$  is used for both switches, then 2.17 reduces to:

$$\Delta i_{sw_2} = 0.5 V_{in} G_s \tag{2.18}$$

Eventually,  $i_{sw_2}$  will become positive (in the example shown in figures 2.7,2.8, and 2.9, this occurs at the 3<sup>rd</sup> time step). Since  $g_2$  is OFF, the step after  $i_{sw_2}$  becomes positive,  $sw_2$  turns OFF (in the example case, the 4<sup>th</sup> step) and the circuit enters the second interval which will be described in the next section. This behaviour is different from the theoretical case in two ways. First, instead of  $sw_2$  immediately turning OFF and conducting no current when  $g_2$  turns OFF, with the Pejovic method,  $sw_2$  remains ON and the value of  $i_{sw_2}$  will increase over a certain number of time steps. Second, before  $sw_2$  turns OFF,  $i_{sw_2}$  will become positive for one time step. This does not occur in the theoretical case because when  $g_2 = 0$ ,  $i_{sw_2} = 0$  and  $i_{d_2}$  can only conduct negative current. In other words, with the Pejovic method,  $i_{sw_2}$  will overshoot the zero value of current. The number of steps during which both switches remain ON is equal to the number of steps it takes  $i_{sw_2}$  to become positive. Recalling that the value of  $i_{sw_2}$  at the beginning

of the commutation was  $-I_{load}(t_{k_x})$ , the duration of the first interval can be expressed as:

$$\operatorname{ceil}(\frac{I_{load}(t_{k_x})}{\Delta i_{sw_2}}) \tag{2.19}$$

where ceil indicates to round up the expression inside the parentheses. The value by which  $i_{sw_2}$  increased during the ON-ON interval is equal to  $\operatorname{ceil}(\frac{I_{load}(t_{k_x})}{\Delta i_{sw_2}})\Delta i_{sw_2}$ . The value of the positive overshoot of  $i_{sw_2}$  is determined by simply subtracting the value of the load current from the previous expression. Therefore, if the last step of interval 1 is denoted as  $\operatorname{int}_{end}^1$ , then the value of the current error at  $\operatorname{int}_{end}^1$  is given by:

$$e_i(int_{end}^1) = \operatorname{ceil}(\frac{I_{load}(t_{k_x})}{\Delta i_{sw_2}}) \Delta i_{sw_2} - I_{load}(t_{k_x})$$

(2.20)

From equation 2.18 it can be seen that as  $G_s$  increases,  $\Delta i_{sw_2}$  increases as well. In addition, the duration of the first interval (the number of steps where  $sw_1$  and  $sw_2$  are ON simultaneously) will decrease, but the overshoot at the end of this interval will increase.

## **2.3.3.2** Interval 2: $sw_1$ is ON and $sw_2$ is OFF

The step after  $i_{sw_2}$  becomes positive,  $sw_2$  turns OFF and the second interval begins. Throughout the second interval,  $sw_1$  is ON and  $sw_2$  is OFF. Although the analysis of the first interval was performed directly on the Pejovic model of the circuit presented in figure 2.6, for the second interval it will be more straightforward to first consider the continuous time representation of the circuit and then analyze the effect of backward-Euler discretization. The continuous time representation of the circuit during the second interval is shown in figure 2.11.

The equations describing the behavior of this circuit can be written in the state-space form:

$$\dot{x}(t) = Ax(t) + Bu(t) \tag{2.21}$$

Figure 2.11 Continuous time representation of the circuit for the second interval

This representation will be useful in quantifying the oscillating behavior of the circuit during the second interval. For the inverter arm, equation 2.21 is equivalent to

$$\begin{bmatrix} \frac{di_{sw_1}(t)}{dt} \\ \frac{dv_{sw_2}(t)}{dt} \end{bmatrix} = \begin{bmatrix} 0 & -\frac{1}{L} \\ \frac{1}{C} & 0 \end{bmatrix} \begin{bmatrix} i_{sw_1}(t) \\ v_{sw_2}(t) \end{bmatrix} + \begin{bmatrix} 0 & \frac{1}{L} \\ -\frac{1}{C} & 0 \end{bmatrix} \begin{bmatrix} i_{load}(t) \\ V_{in} \end{bmatrix}$$

(2.22)

The next step is to obtain the equivalent discrete time state-space representation of the circuit. As explained by (Cellier and Kofman, 2006, p.38), the backward-Euler numerical integration algorithm can be written as

$$x_{n+1} = x_n + h\dot{x}(n+1) \tag{2.23}$$

Substituting 2.21 into 2.23, the following expression is obtained:

$$x_{n+1} = x_n + hAx_{n+1} + hBu (2.24)$$

This can be rewritten as:

$$x_{n+1} = (I - hA)^{-1}x_n + h(I - hA)^{-1}Bu$$

(2.25)

or

$$x_{n+1} = A_d x_n + B_d u (2.26)$$

where

$$A_d = (I - hA)^{-1} (2.27)$$

and

$$B_d = h(I - hA)^{-1}B (2.28)$$

Substituting the A matrix from 2.22 into 2.27 yields:

$$A_d = \frac{1}{1 + \frac{h^2}{LC}} \begin{bmatrix} 1 & -\frac{h}{L} \\ \frac{h}{C} & 1 \end{bmatrix}$$

(2.29)

Recall that with the Pejovic method  $C = hG_s$  and  $L = \frac{h}{G_s}$ . Equation 2.29 can therefore be rewritten as:

$$A_d = \frac{1}{2} \begin{bmatrix} 1 & -G_s \\ \frac{1}{G_s} & 1 \end{bmatrix} \tag{2.30}$$

or:

$$A_d = \frac{1}{\sqrt{2}} \begin{bmatrix} \frac{1}{\sqrt{2}} & -\frac{G_s}{\sqrt{2}} \\ \frac{1}{\sqrt{2}G_s} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(2.31)

This can be rewritten as

$$A_d = \frac{1}{\sqrt{2}} \begin{bmatrix} \cos \alpha & -G_s \sin \alpha \\ \frac{1}{G_s} \sin \alpha & \cos \alpha \end{bmatrix}$$

(2.32)

where  $\alpha$  is 45 degrees. Similarly, it can be shown that:

$$B_d = \frac{1}{\sqrt{2}} \begin{bmatrix} \sin \alpha & G_s \cos \alpha \\ -\frac{1}{G_s} \cos \alpha & \sin \alpha \end{bmatrix}$$

(2.33)

Inserting 2.32 and 2.33 into 2.26

$$\begin{bmatrix} i_{sw_1}(n+1) \\ v_{sw_2}(n+1) \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} \cos \alpha & -G_s \sin \alpha \\ \frac{1}{G_s} \sin \alpha & \cos \alpha \end{bmatrix} \begin{bmatrix} i_{sw_1}(n) \\ v_{sw_2}(n) \end{bmatrix} + \begin{bmatrix} = \frac{1}{\sqrt{2}} - \sin \alpha & G_s \cos \alpha \\ \frac{1}{G_s} \cos \alpha & \sin \alpha \end{bmatrix} \begin{bmatrix} i_{load} \\ V_{in} \end{bmatrix}$$

(2.34)

Equation 2.34 describes how the values of the switches' voltage and current change from one step to another. The switches' voltage and currents k steps after the circuit has entered the second interval are represented by the following equations:

$$i_{sw_1}(k) = I_{load}(t_{k_x}) + 2^{-\frac{k}{2}} ((i_{sw_1}(0) - I_{load}(t_{k_x})) \cos(k\alpha) - G_s(v_{sw_2}(0) - V_{in}) \sin(k\alpha))$$

(2.35)

$$v_{sw_2}(k) = V_{in} - 2^{-\frac{k}{2}} \left( \frac{(-i_{sw_1}(0) + I_{load}(t_{k_x}))}{G_s} \sin(k\alpha) + (-v_{sw_2}(0) + V_{in}) \cos(k\alpha) \right)$$

(2.36)

where  $i_{sw_1}(0)$  and  $v_{sw_2}(0)$  are the initial values of the  $L_{ON}$  and  $C_{OFF}$ , respectively, during the second interval. The initial value of the  $L_{ON}$  during the second interval is equal to the current through  $sw_1$  at the end of the first interval. Similarly, the initial value of the  $C_{OFF}$  during the second interval is equal to the voltage across  $sw_2$  at the end of the first interval. This can be expressed as:

$$i_{sw_1}(0) = i_{sw_1}(int_{end}^1) (2.37)$$

and:

$$v_{sw_2}(0) = v_{sw_2}(int_{end}^1) (2.38)$$

The correct value of  $i_{sw_1}$  is  $I_{load}(t_{k_x})$  and the correct value of  $v_{sw_2}$  is  $V_{in}$ . Equations 2.35 and 2.36 show that  $i_{sw_1}$  is equal to  $I_{load}(t_{k_x})$  plus an erroneous oscillatory term and  $v_{sw_2}$  is equal to  $V_{in}$  minus an erroneous oscillatory term:

$$i_{sw_1}(k) = \underbrace{I_{load}(t_{k_x})}_{\text{correct value of } i_{sw_1}} + \underbrace{2^{-\frac{k}{2}}}_{\text{damping factor}} \underbrace{((i_{sw_1}(0) - I_{load}(t_{k_x}))\cos(k\alpha) - G_s(v_{sw_2}(0) - V_{in})\sin(k\alpha))}_{\text{oscillatory error term}}$$

$$v_{sw_2}(k) = \underbrace{V_{in}}_{\text{correct value of } v_{sw_2}} - \underbrace{2^{-\frac{k}{2}}}_{\text{damping factor}} \underbrace{\left(\frac{(-i_{sw_1}(0) + I_{load}(t_{k_x}))}{G_s} \sin(k\alpha) + (-v_{sw_2}(0) + V_{in}) \cos(k\alpha)\right)}_{\text{oscillatory error term}}$$

The magnitude of the error on  $i_{sw_1}$  is directly proportional to  $G_s$  and the magnitude of the error on  $v_{sw_2}$  is inversely proportional to  $G_s$ . Given enough time these oscillations will be damped to zero. Indeed, at every step, they are damped by  $\sqrt{2}$ . This damping is purely numeric since in theory an LC circuit should oscillate forever. If the initial conditions  $i_{sw_1}(0)$  and  $v_{sw_2}(0)$  are set to zero, then equations 2.35 and 2.36 reduce to equations 2.1 and 2.2 formulated by Pejovic and Maksimovic (1994). This is logical since they did not consider the  $L_{ON}$ - $L_{ON}$  interval.

# 2.3.4 sw<sub>1</sub> turn OFF and sw<sub>2</sub> turn ON process

In this subsection, the behavior of the inverter arm will be analyzed for the case when the top switch turns OFF and the bottom switch turns ON.

### **2.3.4.1** Interval 1: $sw_1$ is OFF and $sw_2$ is ON

It is assumed that the value of  $i_{load}(n)$  varies little during the commutation from ON-OFF to OFF-ON. Therefore,  $i_{load}(n)$  is approximated by current source  $I_{load}(t_{k_y})$  whose value is constant during the commutation beginning at moment  $t_{k_y}$ . At some time step n=0,  $g_1=1$  and  $g_2=0$ .  $sw_2$  is OFF, with  $v_{sw_2}=V_{in}$ .  $sw_1$  is ON with  $i_{sw_1}=I_{load}(t_{k_y})$ . At the next step, n=1, the gate signals are changed such that  $g_1=0$  and  $g_2=1$ . From the update rules described in 2.1.3, since  $g_2=1$ , the bottom switch/diode pair turns ON. In addition, since  $g_1=0$  and  $i_{sw_1}(n-1)>0$ ,  $sw_1$  turns OFF. The circuit is therefore represented by a  $C_{OFF}$  in series with an  $L_{ON}$ . The behavior is described by the following equations::

$$i_{sw_2}(k) = I_{load}(t_{k_y}) + 2^{-\frac{k}{2}}((i_{sw_2}(0) - I_{load}(t_{k_y}))\cos(k\alpha) - G_s(v_{sw_1}(0) - V_{in})\sin(k\alpha))$$

(2.39)

$$v_{sw_1}(k) = V_{in} - 2^{-\frac{k}{2}} \left( \frac{(-i_{sw_2}(0) + I_{load}(t_{k_y}))}{G_s} \sin(k\alpha) + (-v_{sw_1}(0) + V_{in}) \cos(k\alpha) \right)$$

(2.40)

In this case, the initial values  $i_{sw_2}(0)$  and  $v_{sw_1}(0)$  are set to zero since there is no intermediate interval.

### 2.3.4.2 Effect of dead time

Recall, that for the transition from  $g_1 = 0$ ,  $g_2 = 1$  to  $g_1 = 1$ ,  $g_2 = 0$ , there was an intermediate interval where both switch/diode pairs were ON. This interval is purely an artifact of the simulation algorithm. It can also be observed that for the  $g_1 = 1$ ,  $g_2 = 0$  to  $g_1 = 0$ ,  $g_2 = 1$  transition, there is no such intermediate interval. While this is true for the case with no dead time, if a dead time is added, an artificial intermediate interval will present itself.

# **2.3.4.2.1** Interval 1: $sw_1$ is OFF and $sw_2$ is OFF

Figure 2.12 Gate and switch states during a commutation from ON-OFF to OFF-ON using the Pejovic method

Figure 2.13 Switch currents during a commutation from ON-OFF to OFF-ON using the Pejovic method

Figure 2.14 Switch voltages during a commutation from ON-OFF to OFF-ON using the Pejovic method

The behavior of the circuit during a sample ON-OFF to OFF-ON transition with deadtime is illustrated in figures 2.12, 2.13, and 2.14. It is assumed that at some time step n=0,  $g_1=1$  and  $g_2=0$ . As in the case with no dead time,  $sw_2$  is OFF with  $v_{sw_2}=Vin$  and  $sw_1$  is ON with  $i_{sw_1}=I_{load}(t_{k_y})$ . At the next step, n=1, the gate signals are changed such that  $g_1=0$  and  $g_2=0$ . In theory, when both the gates turn OFF, the bottom diode will turn ON so that the inductive load current is not interrupted. However, with the Pejovic method, this is not the case. As in the case with no dead time,  $sw_1$  turns OFF. However, instead of turning ON,  $sw_2$  will remain OFF as well. This is due to the fact that at n=0, the voltage across  $sw_2$  was positive. The continuous time representation of the circuit therefore consists of two  $C_{OFF}$  in series. As explained in subsection 2.1.2,  $i_{m_1}(n) = \frac{v_{sw_1}(n-1)}{R_{s_1}}$  and  $i_{m_2}(n) = \frac{v_{sw_2}(n-1)}{R_{s_2}}$ . By inserting these into equations (2.12) and (2.13), and simplifying, the following expressions are obtained:.

$$v_{sw_1}(n) = v_{sw_1}(n-1) + \Delta v_{sw}$$

(2.41)

$$v_{sw_2}(n) = v_{sw_2}(n-1) - \Delta v_{sw}$$

(2.42)

Where

$$\Delta v_{sw} = \frac{R_{s_1} R_{s_2}}{R_{s_1} + R_{s_2}} I_{load}(t_{k_y})$$

(2.43)

is the rate of change of the switch voltage. If the values of  $R_{s_1}$  and  $R_{s_2}$  are the same, then:

$$\Delta v_{sw} = \frac{I_{load}(t_{k_y})}{2G_s} \tag{2.44}$$

It can be seen that the value  $\Delta v_{sw}$  will vary through the simulation as the value of  $I_{load}(t_{k_y})$  changes. It is also interesting to note that  $\Delta v_{sw}$  is inversely proportional to  $G_s$ . Recall that during the first interval of the  $sw_1$  turn ON and  $sw_2$  turn OFF process,  $\Delta i_{sw}$  is directly proportional to  $G_s$ . This is consistent with the pattern so far: increasing  $G_s$  improves some cases, but causes a deterioration in others. The switch currents are

$$i_{sw_1}(n) = \frac{R_{s_2}}{R_{s_1} + R_{s_2}} I_{load}(t_{k_y})$$

(2.45)

$$i_{sw_2}(n) = -\frac{R_{s_1}}{R_{s_1} + R_{s_2}} I_{load}(t_{k_y})$$

(2.46)

If the values of  $R_{s_1}$  and  $R_{s_2}$  are the same, then the current through both switches is of the same magnitude and equal to half of the load the current. Unlike the  $L_{ON}$ - $L_{ON}$  interval, there will be an overshoot at the end of the  $C_{OFF}$ - $C_{OFF}$  interval only if  $v_{sw_2}$  becomes negative before the deadtime elapsed. If the deadtime elapses first, then there is no overshoot at the end of this phase. If the last step of the first interval is denoted as  $int_{end}^1$ , then the value of the current error at  $int_{end}^1$  (if the dead time hasn't elapsed) is given by:

$$e_{v}(int_{end}^{1}) = \operatorname{ceil}(\frac{V_{in}}{\Delta V_{sw}}) \Delta V_{sw_{2}} - V_{in}$$

(2.47)

where:  $\operatorname{ceil}(\frac{V_{in}}{\Delta V_{sw}})$  is the number of steps where both switches are OFF.

$sw_2$  will turn ON and the circuit will enter the second interval the step after  $v_{sw_2}$  becomes negative or the step when the dead time period elapses (when  $g_2 = 1$ ), whichever comes first. In the example shown in figures 2.12, 2.13, and 2.14, the deadtime elapses by the 3<sup>rd</sup> step which is before  $v_{sw_2}$  becomes negative. Therefore, on the 3<sup>rd</sup> step,  $sw_2$  turns ON.

## **2.3.4.2.2** Interval 2: $sw_1$ is OFF and $sw_2$ is ON

The behaviour of the circuit during the second interval is described by equations 2.39 and 2.40, with the initial values  $i_{sw_2}(0)$  and  $v_{sw_1}(0)$  set to their values at the end of the first interval.

## 2.4 Conclusion

As seen in the above analysis, the Pejovic method introduces artificial intervals ( $L_{ON}$ - $L_{ON}$  and  $C_{OFF}$ - $C_{OFF}$ ). At the end of these intervals, there will be an error on the switch waveforms due to the switch/diode pairs requiring values of the previous time step in order to update. It was shown that the value of  $G_s$  has an effect on this error. For the  $sw_1$  turn ON and  $sw_2$  turn OFF transition, the error on the switch current at the end of the  $L_{ON}$ - $L_{ON}$  interval is directly proportional to  $G_s$ . For the  $sw_1$  turn OFF and  $sw_2$  turn ON transition, the error on the switch

voltage at the end of the  $C_{OFF}$ - $C_{OFF}$  interval is inversely proportional to  $G_s$  (if the deadtime hasn't elapsed yet). It is therefore clear that a compromise must be made. It was also shown that the Pejovic method introduces oscillations during the second interval. During this interval, the voltage oscillations is inversely proportional to  $G_s$ , while the magnitude of the current oscillations is directly proportional to  $G_s$ . Once again, a compromise must be when selecting the appropriate value of  $G_s$ . In the next chapter, the effect of the  $G_s$  parameter on the output current and the commutation losses will be examined.

#### **CHAPTER 3**

# EFFECT OF $G_S$ PARAMETER ON FUNDAMENTAL COMPONENT OF OUTPUT CURRENT AND ON COMMUTATION LOSSES

In the previous chapter, the error introduced by the Pejovic method during commutations was analyzed. In this chapter, the error introduced by the Pejovic method on the fundamental component of the output current  $(i_{load_1})$  and on the commutation losses will be analysed.

# **3.1** Effect of $G_s$ parameter on $i_{load_1}$

The effect of  $G_s$  on  $i_{load_1}$  is clearly illustrated by examining extreme values of  $G_s$ . For very low values of  $G_s$ , one arm will always be composed of a large inductance  $(L_{ON} = \frac{h}{G_s})$  and small capacitance  $(C_{OFF} = hG_s)$ . The very small  $C_{OFF}$  will charge very quickly with respect to the switching frequency and the very large  $L_{ON}$  will charge very slowly, meaning that both components can be approximated as open circuits. This approximation is illustrated in figure 3.1.

Figure 3.1 Approximate circuit representation for a 2 level inverter with a very low value of  $G_s$

It can be seen that there is an open circuit between  $V_{in}$  and the load, and the load current will therefore be zero. This is clearly different from an actual inverter were the load current is sinusoidal and its fundamental component assumes a certain non-zero value. For very large

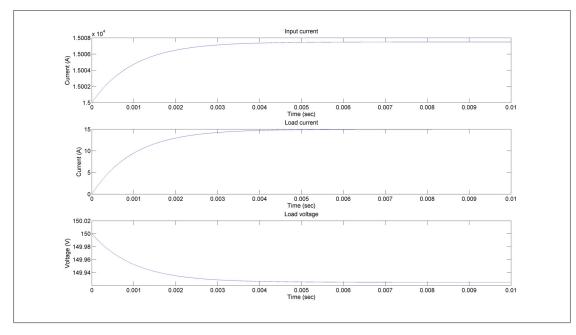

values of  $G_s$ , one arm will always be composed of a small inductance and large capacitance. The very large  $C_{OFF}$  will charge very slowly with respect to the switching frequency and the very small  $L_{ON}$  will charge very quickly, meaning that both components can be approximated as short circuits circuits. This approximation is illustrated in figure 3.2.

Figure 3.2 Approximate circuit representation for a 2 level inverter with a very high value of  $G_s$

It can be seen that the input voltage source is essentially shorted (the only resistance across it will be two  $R_{ON}$ , the very small ON resistances of the switches). Hence,  $sw_1$  and  $sw_2$  will conduct a large amount of current and the input power drawn from the DC voltage source will be very high. Since the value of  $R_{ON}$  is negligible compared to the load impedance, the voltage across the load will be approximately  $\frac{V_{in}}{2}$ . Therefore the output current will have the same form of the current in a series RL circuit driven by a DC voltage source. This means that as time goes on, it will approach a DC value which is once again significantly different from the case of the theoretical inverter. This situation is illustrated in figure 3.3.

Once again, a compromise must be made. Selecting too high of a value of  $G_s$  will cause the input power drawn to be enormous. Selecting too low of a value of  $G_s$  will cause the output current and power to be too low.

Figure 3.3 Waveforms for a 2 level inverter with a very high value of  $G_s$

# 3.2 Effect of $G_s$ parameter on commutation losses

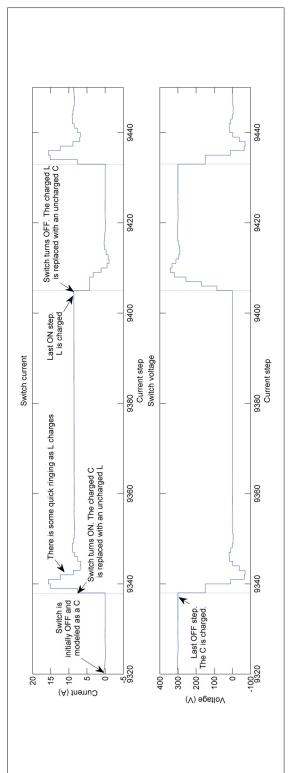

Whenever a commutation occurs during a simulation using the Pejovic method, energy is lost. This processes is illustrated in figure 3.4. It is assumed that at some step n the top switch is OFF (and modeled as a capacitor) and the bottom switch is ON (and modeled as an inductor). It is also assumed that the top switch has been OFF long enough for the oscillations across it to have been damped out.

Figure 3.4 Visualization of the commutation losses introduced by the Pejovic method

Hence,  $i_{sw_1}(n) = 0$  and  $v_{sw_1}(n) = V_{in}$ . The  $C_{OFF}$  is therefore storing an energy equal to  $0.5Cv_{sw_1}^2(n)$ . Concretely, this stored energy manifests itself in the form of the memory current source which has a value equal to  $i_{m_1}(n) = G_sV_{sw_1}(n-1)$ . At n+1, suppose the gates change such that  $g_1 = 1$  and  $g_2 = 0$ . As explained previously, the top switch turns ON so that it is now modelled as an inductor. The value of its current source memory element is equal to  $i_{m_1}(n) = -i_{sw_1}(n-1)$ . However, since the current at the previous time step was zero, the magnitude of the current source is zero, meaning that it contains no charge. It can therefore be seen that a charged  $C_{OFF}$  is replaced by an uncharged  $L_{ON}$ , meaning that the energy stored in the  $C_{OFF}$  at step n is lost. Similarly, during turn OFF, a charged  $L_{ON}$  is replaced by a  $C_{OFF}$  with an initial memory value of  $i_{m_1}(n) = G_s v_{sw_1}(n-1)$ . As shown in section 2.2.4,  $v_{sw_1}(n-1) = 0$ . Therefore, the  $C_{OFF}$  is uncharged. Therefore energy is lost every time a commutation occurs. The total losses for a given switch during turn ON can be represented by:

$$\sum_{i}^{I} 0.5CV_{sw}^{2}(t_{k_{i-1}}) \tag{3.1}$$

where  $t_{k_i}$  are the turn ON moments of the switch during the course of the simulation. Similarly, the total losses during turn OFF are:

$$\sum_{i}^{J} 0.5 L I_{sw}^{2}(t_{k_{j-1}}) \tag{3.2}$$

where  $t_{k_j}$  are the turn OFF moments of the switch during the course of the simulation. As was shown in the previous section, the values of  $i_{sw}$  and  $v_{sw}$  are affected by the value of  $G_s$ . The

<sup>&</sup>lt;sup>1</sup>This equation is valid for continuous time (it is derived by integrating the power of the capacitor with respect to time). Since in discrete time integration is approximate, the energy stored in a capacitor or inductor is not necessarily  $0.5Cv(t)^2$  or  $0.5Li(t)^2$ , but empirically this discrepancy did not affect the optimization results.

<sup>&</sup>lt;sup>2</sup>It should be noted that the losses of the bottom switches are different from those of the top ones. As was explained in section 2.2.3, the bottom switch only turns OFF after a  $L_{ON} - L_{ON}$  intermediate interval during which the voltage across it is  $\frac{V_{in}}{2}$  and not the zero volts across the top switch prior to OFF. Therefore, during turn OFF, unlike the case of the top  $L_{ON}$  which was replaced by an uncharged  $C_{OFF}$ , the bottom  $L_{ON}$  is replaced by a  $C_{OFF}$  that contains some initial charge  $(i_{m_2} = G_s \frac{V_{in}}{2})$ . Hence, the losses for the bottom switches are lower than the losses of the top switches. For the purpose of this work, this discrepancy will be ignored.

total energy lost in the switch during the simulation can be expressed as a function of  $G_s$

$$E_{loss}(G_s) = \sum_{i=1}^{I} 0.5hG_s v_{sw}^2(G_s, t_{k_{i-1}}) + \sum_{i=1}^{J} 0.5 \frac{h}{G_s} i_{sw}^2(G_s, t_{k_{j-1}})$$

(3.3)

As mentioned previously, this equation is approximate due to the effect of discretization on the energy calculation. The extent of this approximation was studied on the two level inverter with the parameter values listed in table 4.2 with a  $G_s$  of 0.0505. The true energy loss was determined using the following equation:

$$E_{loss} = \sum_{n=1}^{N} i_{sw}(n) v_{sw}(n) h \tag{3.4}$$

where h is the size of the simulation time step and N is the number of steps during the simulation. The energy loss calculated using this equation was 68.29J compared to a loss of only 22.96J calculated by equation 3.3. While this is a significant difference between the two calculation methods, they are still within an order of magnitude of each other, and, as will be shown in the final chapter, the approximation is sufficiently adequate for the optimization algorithm to provide optimal values of  $G_s$ . It is also important to point out that the turn ON losses are directly proportional to  $G_s$  and that the turn OFF losses are inversely proportional to  $G_s$ . Again, it is seen that a compromise must be made when choosing a value of  $G_s$ .

### 3.3 Conclusion

In this chapter, the effect of the  $G_s$  parameter on the output current was examined. It was found that selecting too high or too low of a  $G_s$  value completely alters the behavior of the circuit. The effect of the  $G_s$  parameter on the commutation losses was also examined. It was shown that selecting too high or too low of a  $G_s$  value results in unacceptable losses. Therefore a compromise must be made. This is consistent with the analysis of chapter 2, which showed that too high or too low of a  $G_s$  value results in inaccurate switch voltage or current waveforms following a commutation. This effect of the  $G_s$  on multiple aspects of the circuits behaviour explains why choosing an appropriate value of  $G_s$  through trial and error is so difficult. In the

next chapter, a method to automatically find the optimal value of  $G_s$  is proposed and validated for three case studies.

### **CHAPTER 4**

#### OPTIMIZATION METHOD AND VALIDATION

In this chapter, a method to automatically optimize the value of the  $G_s$  parameter is proposed and its is performance assessed for three case studies.

# 4.1 Optimization method

In the previous chapter, the following equation was derived for the commutation losses accrued during the simulation:

$$E_{loss}(G_s) = \sum_{i=1}^{I} 0.5hG_s v_{sw}^2(G_s, t_{k_{i-1}}) + \sum_{j=1}^{I} 0.5 \frac{h}{G_s} i_{sw}^2(G_s, t_{k_{j-1}})$$

(4.1)

In order to simplify the optimization problem, it will be assumed that near the optimal value of  $G_s$   $i_{sw}$  and  $v_{sw}$  are independent of  $G_s$ . Therefore, equation 4.1 can be rewritten as:

$$E_{loss}(G_s) = 0.5hG_s V_{SQ} + 0.5\frac{h}{G_s} I_{SQ}$$

(4.2)

where

$$I_{SQ} = \sum_{j}^{J} I_{sw}^{2}(t_{k_{j-1}}) \tag{4.3}$$

$$V_{SQ} = \sum_{i}^{I} V_{sw}^{2}(t_{k_{i-1}}) \tag{4.4}$$

An expression for the value of  $G_s$  that minimizes this loss can be obtained by evaluating the following derivative:

$$\frac{dE_{loss}(G_s)}{dG_s} = 0 (4.5)$$

Evaluating this expression yields:

$$0.5hV_{SQ} - 0.5\frac{h}{G_s^2}I_{SQ} \tag{4.6}$$

Rearranging and simplifying yields:

$$G_s = \sqrt{\frac{I_{SQ}}{V_{SQ}}} \tag{4.7}$$

# 4.1.1 Implementation of the algorithm

From equation 4.7, it can be seen that in order to find the optimal  $G_s$ , the values of  $I_{SQ}$  and  $V_{SQ}$  must be determined. The values will be determined by running a reference SPS simulation and measuring the switch voltages and currents at the moments  $t_{k_{j-1}}$  and  $t_{k_{i-1}}$ . It is important to note the basis for this algorithm is the assumption of hard switching, that is that at the moments before the commutation  $(t_{k_{j-1}} \text{ and } t_{k_{i-1}})$  the switch voltage/current is non-zero. If that is not the case, then the proposed algorithm is not applicable and further investigation for this case is needed. For example, in the case of a boost converter operating in discontinuous conduction mode (DCM), the diode will turn OFF at a zero crossing of current. In order words, when the  $L_{ON}$  is replaced by the  $C_{OFF}$ , no energy is lost. Therefore,  $I_{SQ}$  will be equal to zero, and the  $G_s$  calculated by the script will be zero. Another way of seeing the situation is that the algorithm chooses a  $G_s$  that makes the  $L_{ON}$  and  $C_{OFF}$  losses equal to each other. However, since in this case the  $L_{ON}$  losses are zero, the algorithm will calculate a  $G_s$  of zero.

## 4.1.2 Analytical expression for the case of the two level inverter

For certain cases, the optimal  $G_s$  can be calculated directly from an analytical expression without having to use the proposed optimization algorithm. The grounded two level inverter shown in figure 4.1 that has been studied in this work is such a case. For this converter, in theory, the switch current is equal to the load current when it is ON and the switch voltage is equal to the input voltage when it is OFF. By assuming that the load current varies slowly from one step to another,  $I_{SQ}$  can be rewritten as

$$I_{SQ} = \sum_{j}^{J} I_{load}^2(t_{k_j}) \tag{4.8}$$

and  $V_{SQ}$  can be rewritten as

$$V_{SQ} = \sum_{i}^{I} V_{in}^2 \tag{4.9}$$

The number of turn ON and turn OFF moments are equal (or there will be a difference of at most 1 between them), so I = J. Therefore,  $G_s$  can be expressed as:

$$G_s = \sqrt{\sum_{j}^{J} \frac{I_{load}^2(t_{k_j})}{V_{in}^2}}$$

(4.10)

This can be rewritten as

$$G_s = \frac{I_{load_{RMS}}(t_{k_j})}{V_{in}} \tag{4.11}$$

If the switching frequency is much higher than the load current frequency, then equation 4.11 can be rewritten as