ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA

MAÎTRISE AVEC MÉMOIRE EN GÉNIE

DES TECHNOLOGIES DE L'INFORMATION

M. Sc. A.

PAR

Ghassen ZAGDENE

MISE EN PLACE D'UN CLUSTER DE SYSTÈMES ARM

POUR DES SOLUTIONS DE SÉCURITÉ

MONTRÉAL, LE 27 AVRIL 2016

©Tous droits réservés,Ghassen ZAGDENE, 2016

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE :

M. Chamseddine Talhi, directeur de mémoire

Département de génie logiciel et TI à l'École de technologie supérieure

M. Abdelouaheb Gherbi, président du jury

Département de génie logiciel et TI à l'École de technologie supérieure

M. Carlos Vázquez, membre du jury

Département de génie logiciel et TI à l'École de technologie supérieure

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 10-05-2016

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

Tout d'abord, je remercie mon directeur de recherche, M. Chamseddine Talhi pour l'encadrement de qualité et le soutien qu'il m'a offerts, ainsi que pour sa disponibilité et ses conseils qui m'ont été précieux tout le long de ma maîtrise.

Je tiens à remercier ma fiancée, Mariem Jelassi qui m'a apporté son soutien et m'a motivé surtout dans les moments difficiles et à qui je dois en partie ma réussite.

Je remercie aussi mon frère, Oussama Boudar qui a toujours été présent et qui m'a apporté son appui ainsi que mes collègues et amis du laboratoire LASI :Hanine Tout, Maroua Ben Attia, Manel Abdeltif, Mahdi Elarbi et à leur tête ILYES Lahmar.

Je tiens aussi à exprimer ma profonde gratitude pour ma famille qui m'a consacré tous les moyens et supports nécessaires au bon déroulement et à la réussite de mes études, particulièrement mes parents Hamadi et Najla, ainsi que mes grands-parents Hassan et Assia et sans oublier mon petit frère Khalil.

Par la même, je remercie également les membres du jury d'avoir accepté d'évaluer mon mémoire.

Enfin, je tiens également à remercier l'ensemble du corps enseignant de l'École de technologie supérieure pour toutes les connaissances et pratiques m'ayant été transmises de leur part lors de ma maîtrise.

# **MISE EN PLACE D'UN CLUSTER DE SYSTÈMES ARM POUR DES SOLUTIONS DE SÉCURITÉ**

Ghassen ZAGDENE

## **RÉSUMÉ**

Le monde de l'informatique de haute performance (HPC) a évolué ces dernières années surtout après l'apparition des clusters Beowulf qui consistent à utiliser les PC conventionnels pour les interconnecter et récolter leur puissance de calcul. La réduction du coût du matériel nécessaire a rendu l'informatique de haute performance accessible à un plus large public, et certaines entreprises mettent en place leurs propres cluster et centres de données en se basant sur les clusters Beowulf. Cependant, même avec de l'équipement conventionnel, ces clusters et centres de données restent relativement chers, occupent de l'espace et consomment beaucoup d'énergie.

L'approche proposée par la présente étude vise à réduire les coûts de la mise en place d'un cluster destiné au HPC en utilisant des ordinateurs mono-cartes à architecture ARM. La particularité de cette dernière est sa faible consommation d'énergie par rapport aux autres architectures. Ainsi, nous mettons en place un cluster ARM sur lequel nous exécutons des algorithmes liés à la sécurité. De plus, puisque combiner les clusters et la virtualisation offre des avantages non négligeables, nous déployons docker sur certaines cartes ARM, qui est une nouvelle solution de virtualisation afin de mesurer l'impact sur les performances du système.

Les résultats montrent que les appareils ARM délivrent de bons résultats à condition de bien choisir l'environnement de développement et de bien équilibrer la charge au sein du cluster. Docker n'a pas d'impact significatif sur les performances du système, mais il n'est pas encore adapté à l'architecture ARM.

**Mots clés :** architecture ARM; sécurité; cluster beowulf; HPC; virtualisation; docker

# **SETTING UP AN ARM-BASED CLUSTER FOR SECURITY SOLUTIONS**

Ghassen ZAGDENE

## **ABSTRACT**

The world of high performance computing (HPC) evolved these past years, especially after the appearance of the beowulf clusters which consist of commodity equipment interconnected to harvest their computing power. This cost reduction, made HPC accessible to a large public and some companies built their own cluster and datacenters based on the Beowulf concept. However, the costs are still relatively high and the clusters still consume a lot of energy.

In this study, we aim to provide a low-cost, low-energy cluster based on ARM devices. This architecture (ARM) is known to be more energy-efficient than any other architecture. Also, we implement security-related algorithms and execute them on our cluster to test its efficiency. Since combining clustering and virtualization has proved to provide notable advantages, we deploy Docker, a new lightweight virtualization solution, on some ARM boards to test its impact on system performance.

The results have shown that the ARM based cluster can deliver good performance, given the right message passing environment and load-balancing strategy. As for virtualization support, Docker had little impact on the board's performance but is not yet adapted for the ARM architecture.

**Keywords:** ARM architecture; beowulf cluster; security; HPC; virtualization; Docker

## TABLE DES MATIÈRES

|                                                      | Page |

|------------------------------------------------------|------|

| INTRODUCTION .....                                   | 1    |

| CHAPITRE 1 NOTIONS DE BASE.....                      | 9    |

| 1.1    Introduction.....                             | 9    |

| 1.2    Informatique de haute performance .....       | 9    |

| 1.2.1    Généralités .....                           | 9    |

| 1.2.2    Gestion de la mémoire .....                 | 10   |

| 1.2.3    Cluster Beowulf .....                       | 11   |

| 1.2.4    Mécanismes de passage des messages.....     | 12   |

| 1.3    Appareils ARM .....                           | 20   |

| 1.3.1    Historique.....                             | 20   |

| 1.3.2    Évolution de l'architecture ARM .....       | 21   |

| 1.4    Virtualisation.....                           | 24   |

| 1.4.1    Définition .....                            | 25   |

| 1.4.2    Types de virtualisation.....                | 25   |

| 1.4.3    Docker.....                                 | 29   |

| 1.5    Conclusion .....                              | 32   |

| CHAPITRE 2 REVUE DE LITTÉRATURE .....                | 33   |

| 2.1    Introduction.....                             | 33   |

| 2.2    Cluster beowulf.....                          | 33   |

| 2.2.1    Usage des clusters beowulf.....             | 33   |

| 2.2.2    Cluster ARM.....                            | 36   |

| 2.3    MPI vs PVM .....                              | 40   |

| 2.3.1    Différences entre les deux approches .....  | 40   |

| 2.3.2    Comparaison des caractéristiques .....      | 42   |

| 2.4    Déchargement des traitements de sécurité..... | 46   |

| 2.5    Technologies de virtualisation .....          | 48   |

| 2.6    Équilibrage de la charge.....                 | 50   |

| 2.7    Conclusion .....                              | 52   |

| CHAPITRE 3 ARCHITECTURE.....                         | 55   |

| 3.1    Introduction.....                             | 55   |

| 3.2    Architecture du cluster .....                 | 55   |

| 3.3    Module de monitoring.....                     | 57   |

| 3.3.1    Métriques .....                             | 57   |

| 3.3.2    Architecture et implémentation.....         | 59   |

| 3.3.3    Visualisation temps-réel.....               | 60   |

| 3.4    Équilibrage de la charge.....                 | 61   |

| 3.5    Algorithmes.....                              | 62   |

| 3.5.1    AES .....                                   | 62   |

|                                                |                                                           |     |

|------------------------------------------------|-----------------------------------------------------------|-----|

| 3.5.2                                          | Correspondance de patrons .....                           | 67  |

| CHAPITRE 4 EXPÉRIMENTATIONS ET RÉSULTATS ..... |                                                           | 71  |

| 4.1                                            | Introduction.....                                         | 71  |

| 4.2                                            | Environnement.....                                        | 72  |

| 4.2.1                                          | Matériel utilisé .....                                    | 72  |

| 4.2.2                                          | Environnement logiciel .....                              | 77  |

| 4.3                                            | Défis techniques.....                                     | 77  |

| 4.3.1                                          | Installation des environnements.....                      | 78  |

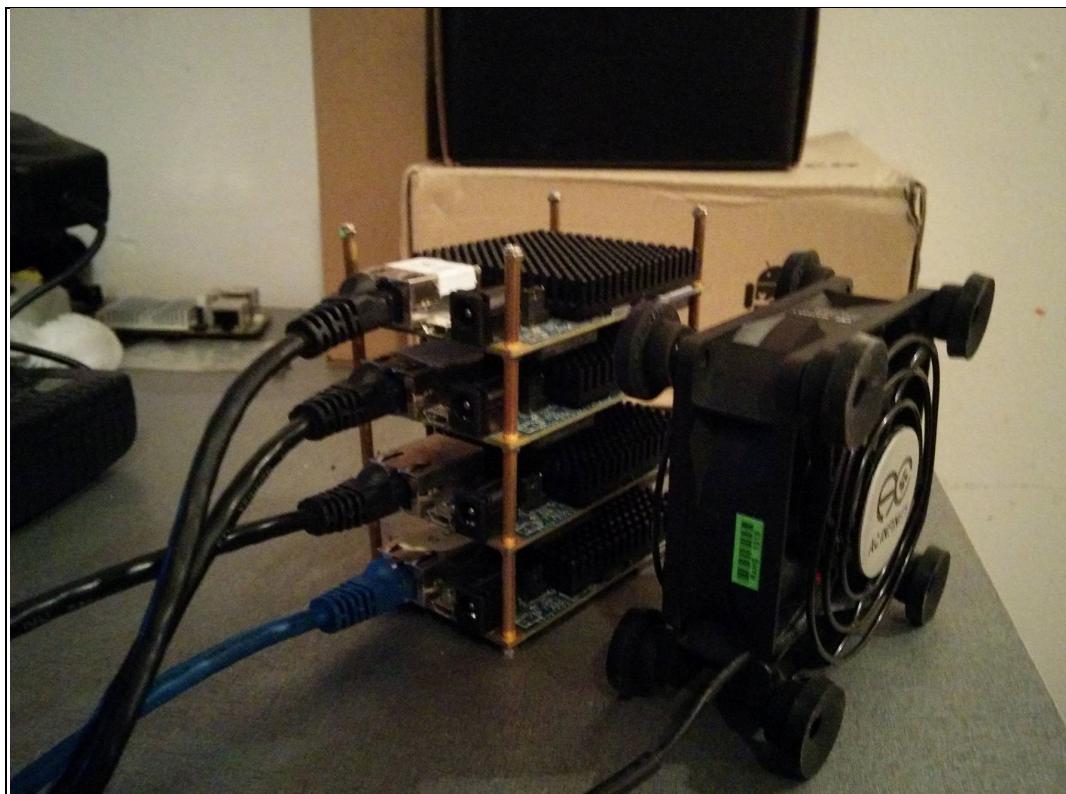

| 4.3.2                                          | Surchauffe des Parallelia.....                            | 79  |

| 4.3.3                                          | OMAP5432 et KVM.....                                      | 81  |

| 4.3.4                                          | Déploiement de Docker .....                               | 81  |

| 4.3.5                                          | OpenMPI et Parallelia.....                                | 82  |

| 4.4                                            | AES .....                                                 | 82  |

| 4.4.1                                          | Distribution naïve.....                                   | 83  |

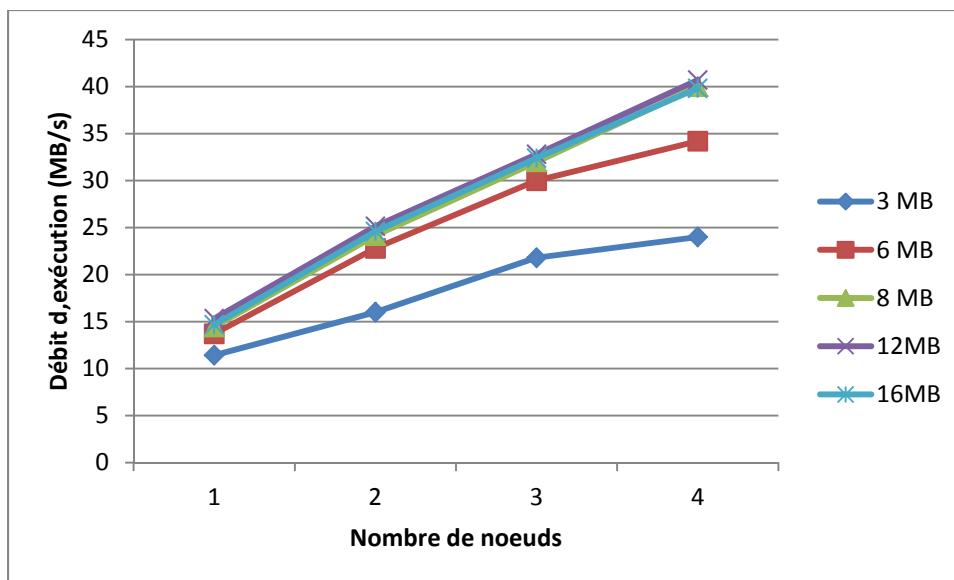

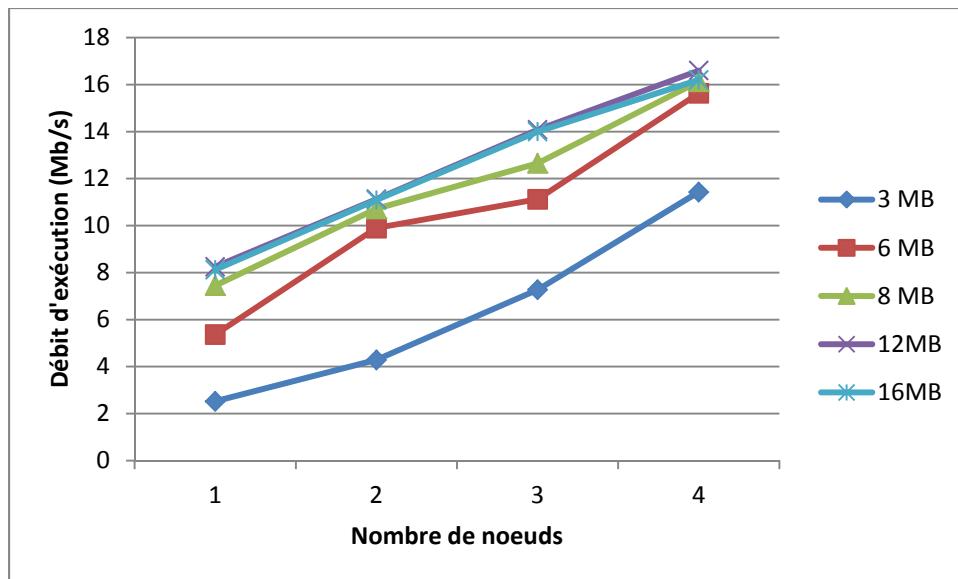

| 4.4.2                                          | Débit d'exécution .....                                   | 86  |

| 4.4.3                                          | Équilibrage de la charge.....                             | 86  |

| 4.5                                            | Correspondance de patrons .....                           | 89  |

| 4.5.1                                          | Distribution naïve.....                                   | 90  |

| 4.5.2                                          | Équilibrage de la charge.....                             | 93  |

| 4.6                                            | AES parallèle .....                                       | 96  |

| 4.7                                            | Résultats de la virtualisation .....                      | 97  |

| 4.7.1                                          | Choix de la technologie et l'installation de docker ..... | 97  |

| 4.7.2                                          | Tests de performance .....                                | 100 |

| 4.8                                            | Conclusion .....                                          | 105 |

| CONCLUSION .....                               |                                                           | 107 |

| BIBLIOGRAPHIE .....                            |                                                           | 111 |

## LISTE DES TABLEAUX

|             | Page                                                              |

|-------------|-------------------------------------------------------------------|

| Tableau 2.1 | Comparaison PVM-MPI .....                                         |

| Tableau 4.1 | Spécifications de la parallella .....                             |

| Tableau 4.2 | Spécifications de la PandaBoard.....                              |

| Tableau 4.3 | Spécifications de la Odroid-U3.....                               |

| Tableau 4.4 | Spécifications de la beaglebone .....                             |

| Tableau 4.5 | Temps d'exécution en secondes selon le nombre de processeurs..... |

| Tableau 4.6 | Coefficient d'exécution selon le type de la carte.....            |

| Tableau 4.7 | Coefficient d'exécution des nœuds. ....                           |

| Tableau 4.8 | Perte de paquets lors d'un transfert UDP .....                    |

## LISTE DES FIGURES

|                                                                                            | Page |

|--------------------------------------------------------------------------------------------|------|

| Figure 0.1 Projection de la part de marché de l'architecture ARM.....                      | 3    |

| Figure 0.2 Méthodologie de notre étude .....                                               | 7    |

| Figure 1.1 Exemple de cluster Beowulf.....                                                 | 11   |

| Figure 1.2 Communication dans PVM. ....                                                    | 14   |

| Figure 1.3 Architecture de PVM.....                                                        | 15   |

| Figure 1.4 Mémoire distribuée.....                                                         | 17   |

| Figure 1.5 Architecture hybride.....                                                       | 17   |

| Figure 1.6 Communication collective dans MPI. ....                                         | 20   |

| Figure 1.7 Architecture Cortex A15. ....                                                   | 22   |

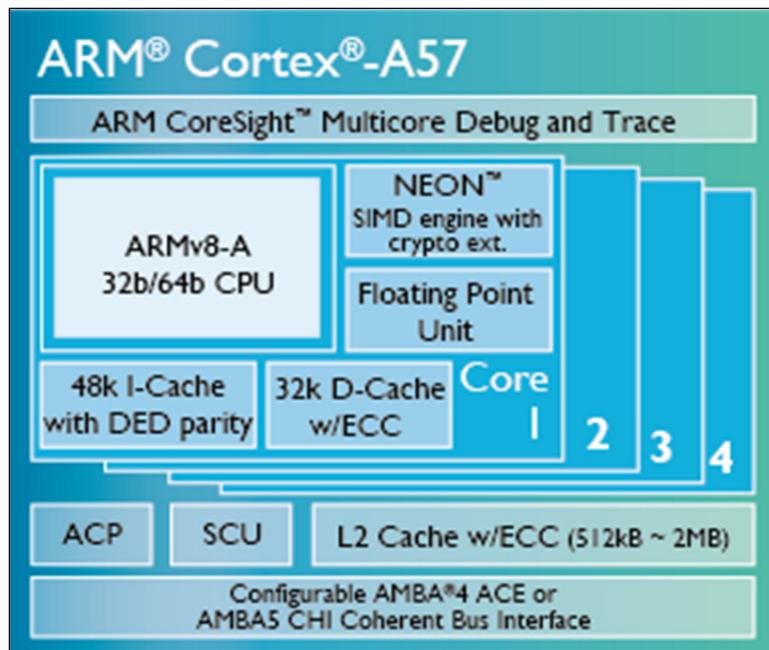

| Figure 1.8 Architecture Cortex A57. ....                                                   | 23   |

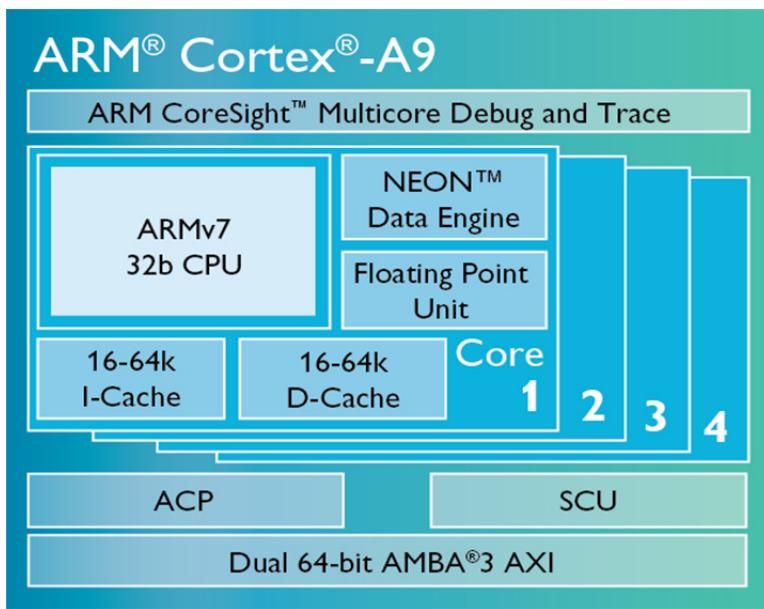

| Figure 1.9 Architecture Cortex A9 .....                                                    | 24   |

| Figure 1.10 Hyperviseur de type 1. ....                                                    | 26   |

| Figure 1.11 Hyperviseur de type 2.....                                                     | 27   |

| Figure 1.12 Virtualisation niveau noyau.....                                               | 27   |

| Figure 1.13 Techniques et logiciels de virtualisation. ....                                | 29   |

| Figure 1.14 Architecture Docker. ....                                                      | 31   |

| Figure 2.1 Accélération et efficacité de la multiplication des matrices .....              | 34   |

| Figure 2.2 Architecture d'un cluster beowulf.....                                          | 35   |

| Figure 2.3 Ratio performance/énergie du cluster ARM selon différentes configurations. .... | 38   |

| Figure 2.4 Calcul du ratio énergie/performance. ....                                       | 39   |

| Figure 2.5 processus d'envoi et de réception de données standard de PVM et MPI. ....       | 41   |

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2.6 Topologie virtuelle de 12 processus en grille avec les coordonnées .....           | 44 |

| Figure 2.7 Entrée/sortie disque. ....                                                         | 49 |

| Figure 2.8 Calcul du facteur d'assignation pour un noeud j. ....                              | 51 |

| Figure 2.9 Stratégies d'exécution au sein du cluster. ....                                    | 52 |

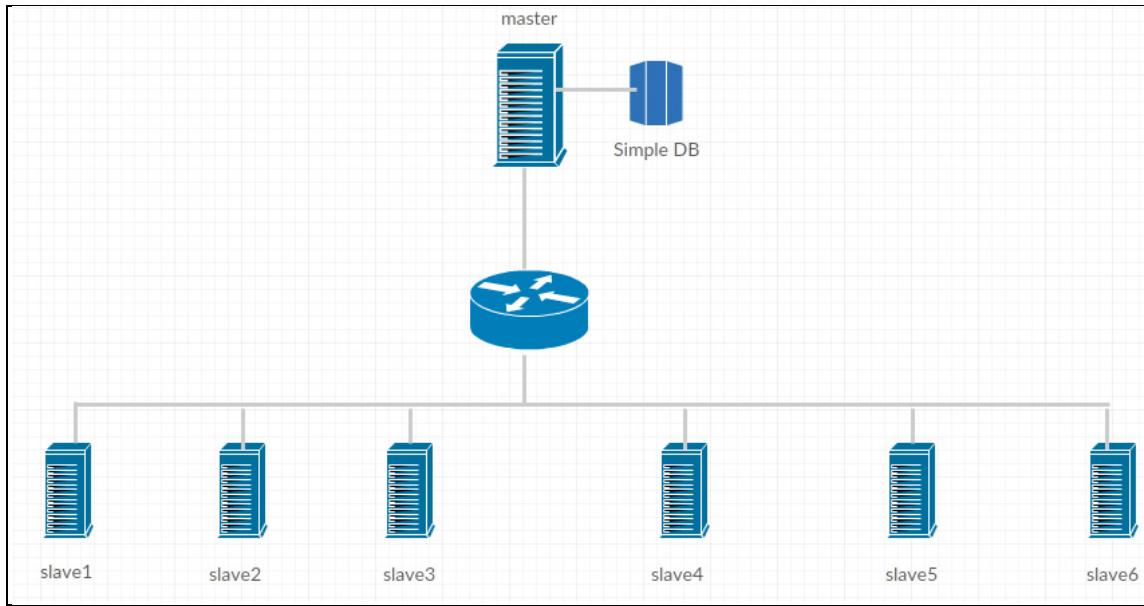

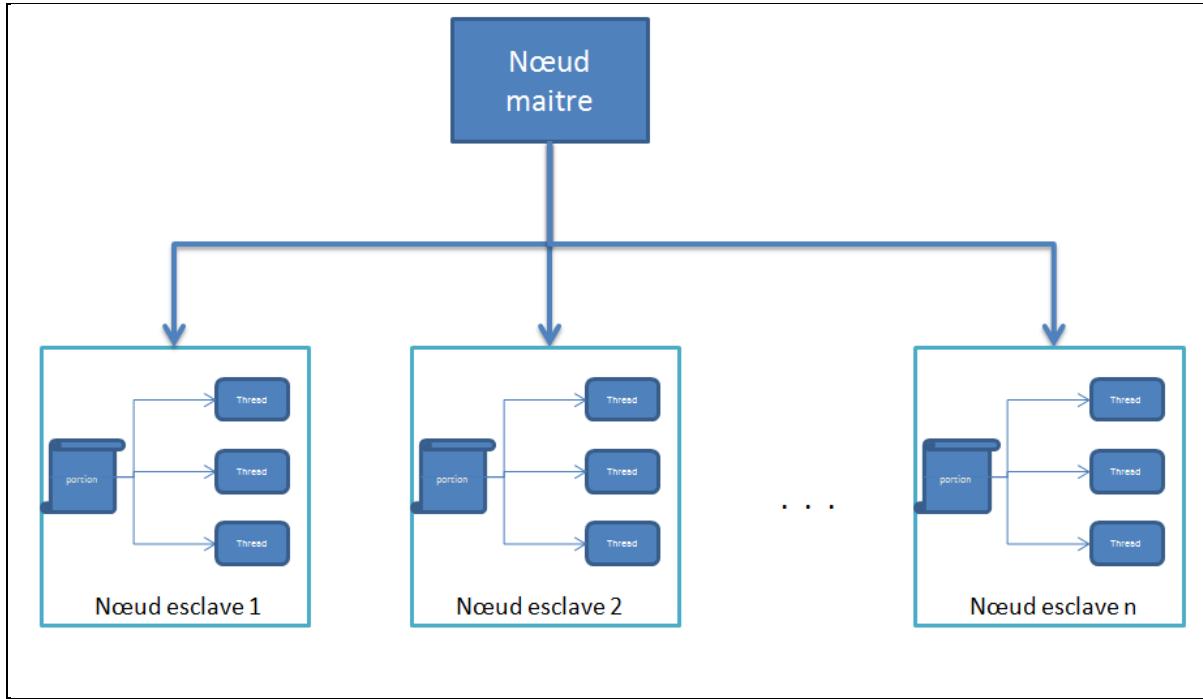

| Figure 3.1 Architecture du cluster .....                                                      | 56 |

| Figure 3.2 Mode détaillé de la surveillance de la CPU.....                                    | 58 |

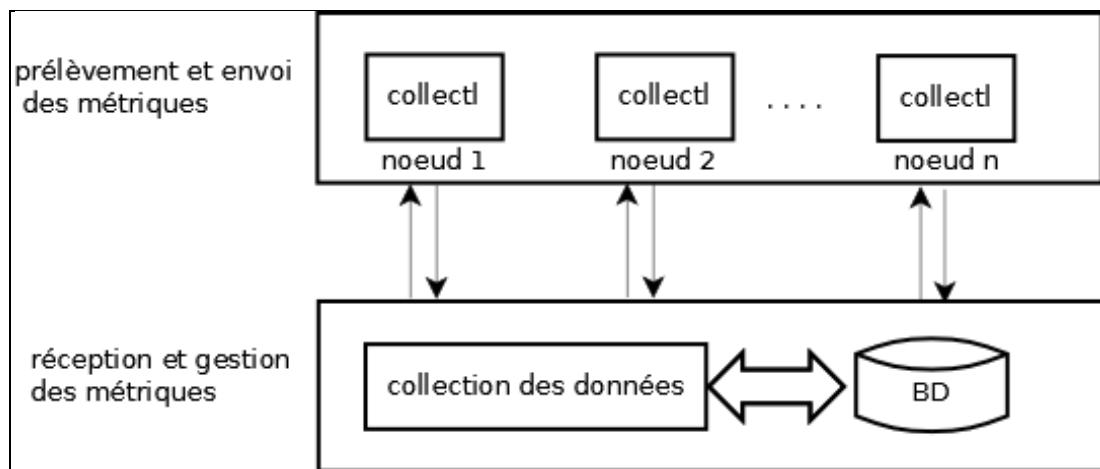

| Figure 3.3 Architecture du système de surveillance. ....                                      | 59 |

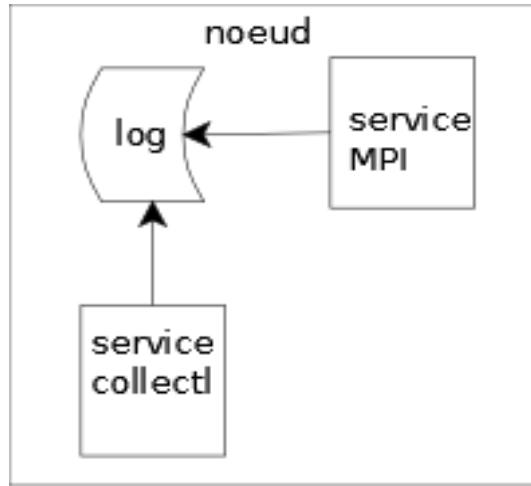

| Figure 3.4 Collecte des données au niveau d'un nœud. ....                                     | 60 |

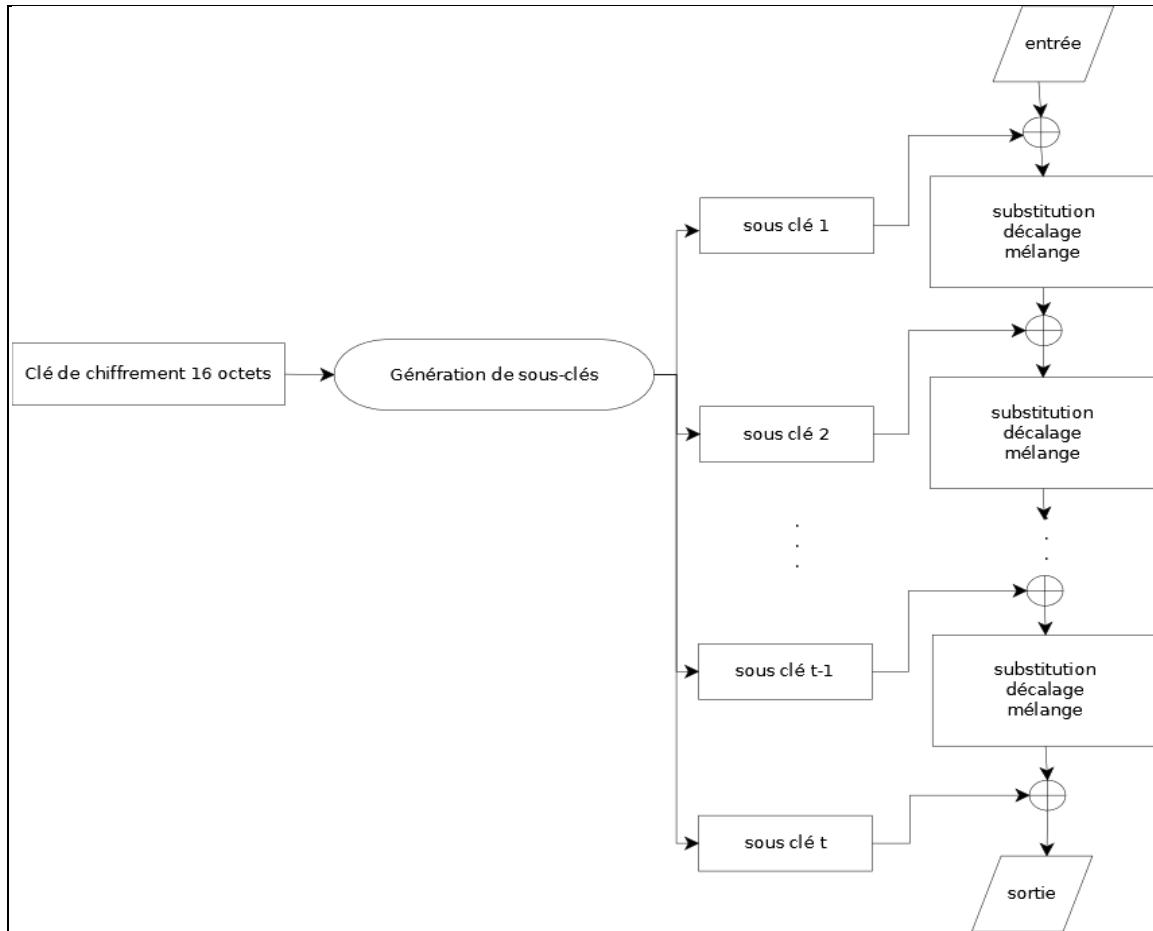

| Figure 3.5 Chiffrement d'un bloc avec AES .....                                               | 64 |

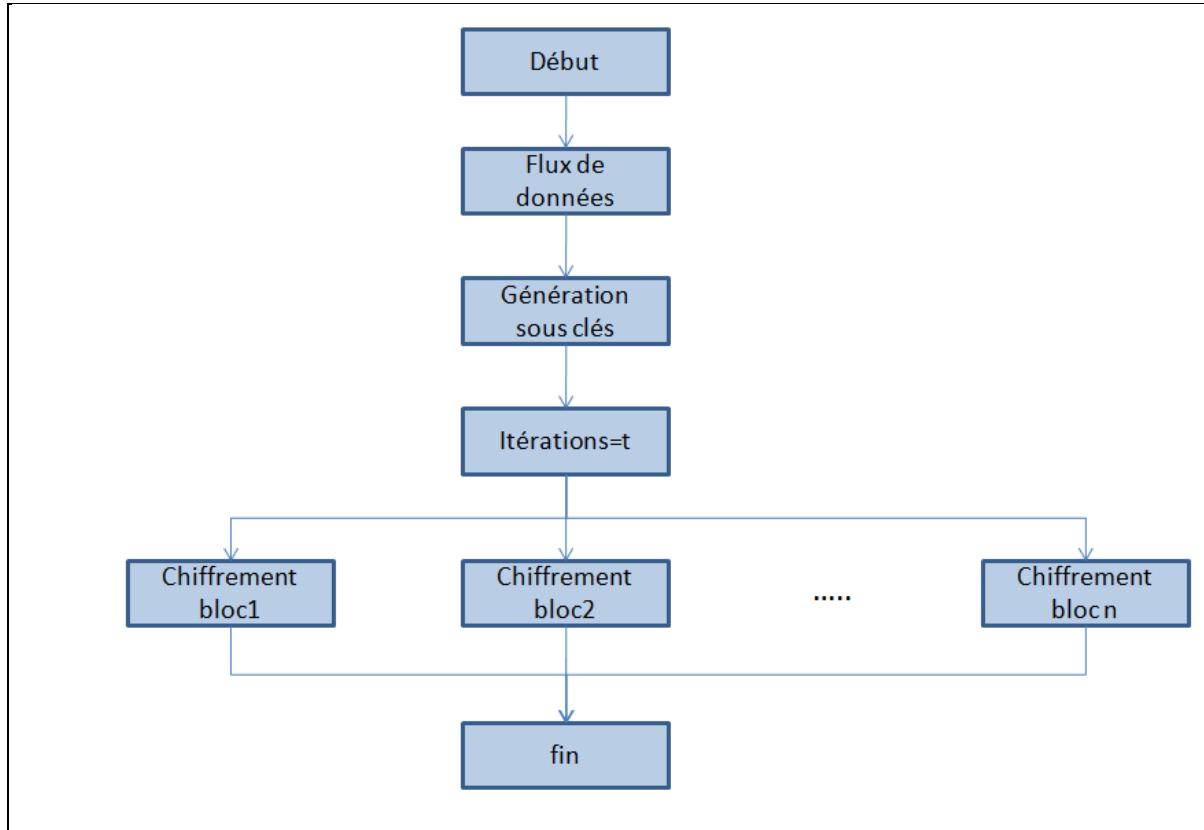

| Figure 3.6 Diagramme PAES. ....                                                               | 66 |

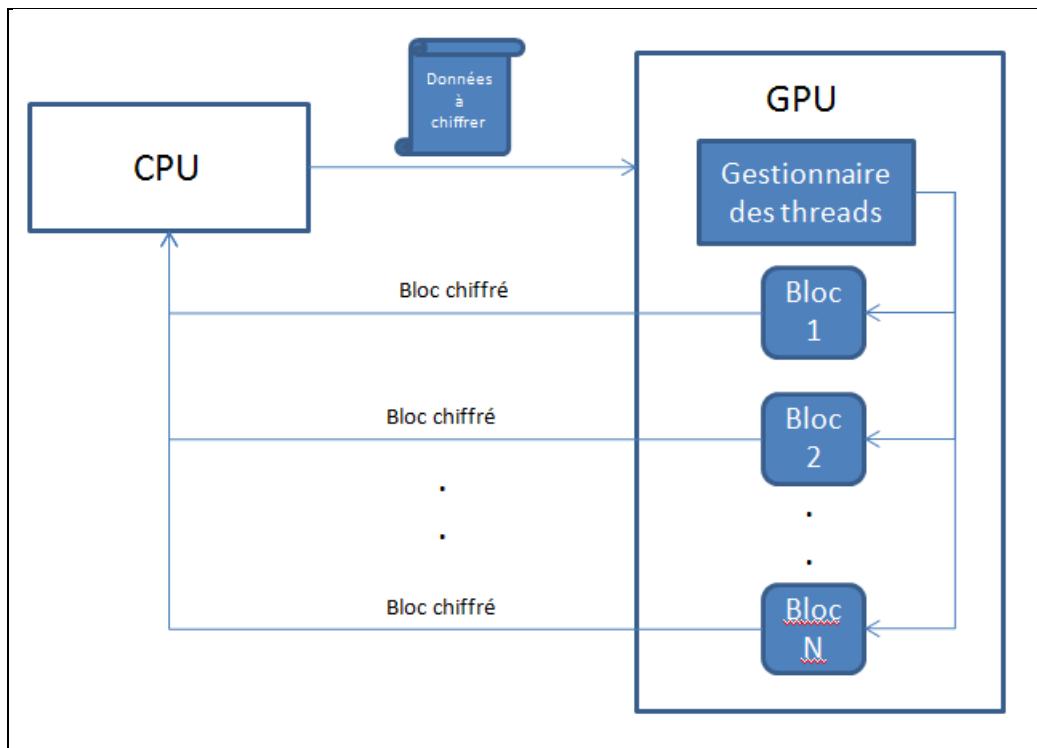

| Figure 3.7 AES parallèle sur GPU.....                                                         | 67 |

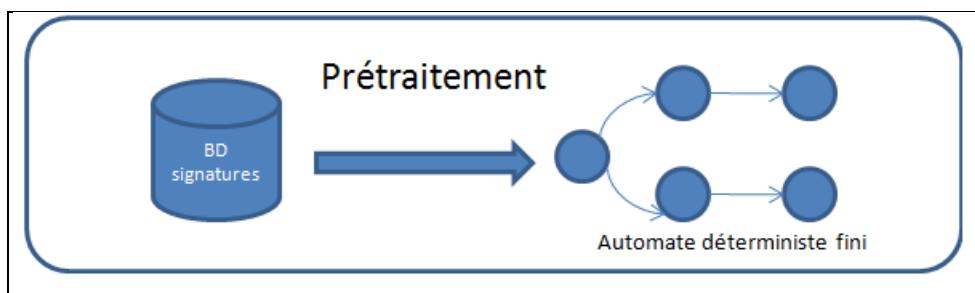

| Figure 3.8 Processus de prétraitement du module de détection des malware.....                 | 68 |

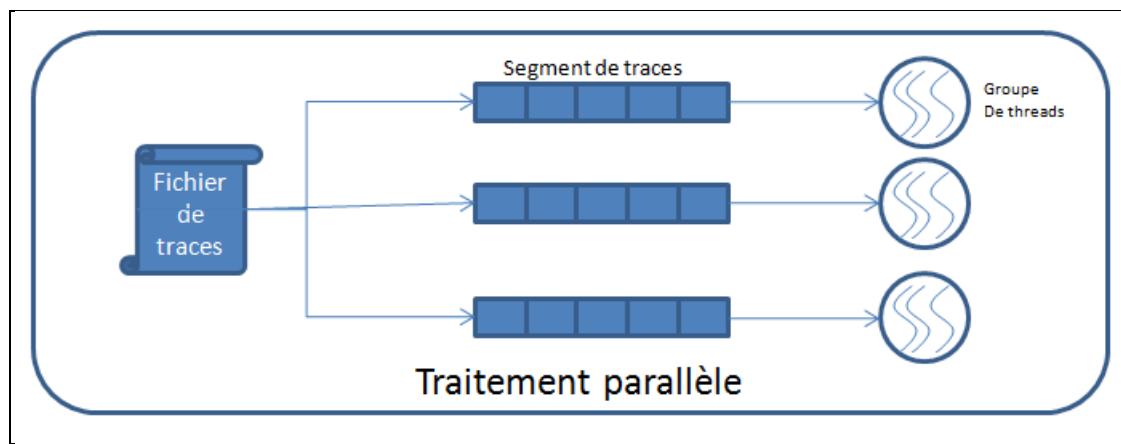

| Figure 3.9 Bloc de traitement parallèle dans la GPU.....                                      | 69 |

| Figure 4.1 Carte Parallella. ....                                                             | 73 |

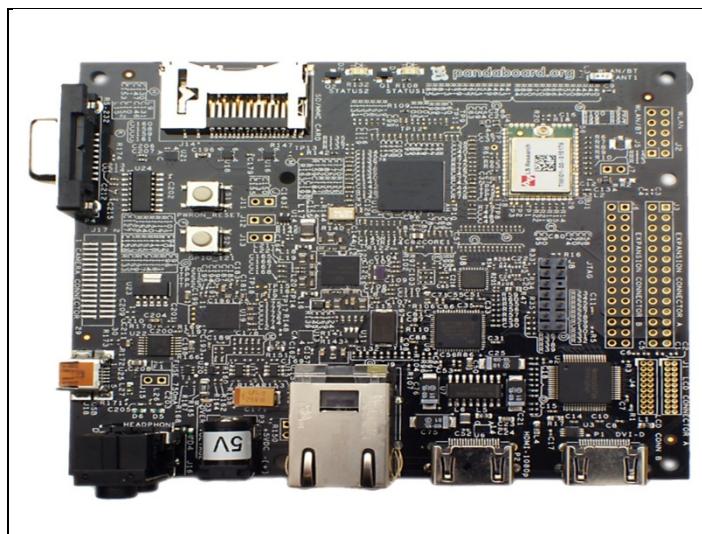

| Figure 4.2 PandaBoard.....                                                                    | 74 |

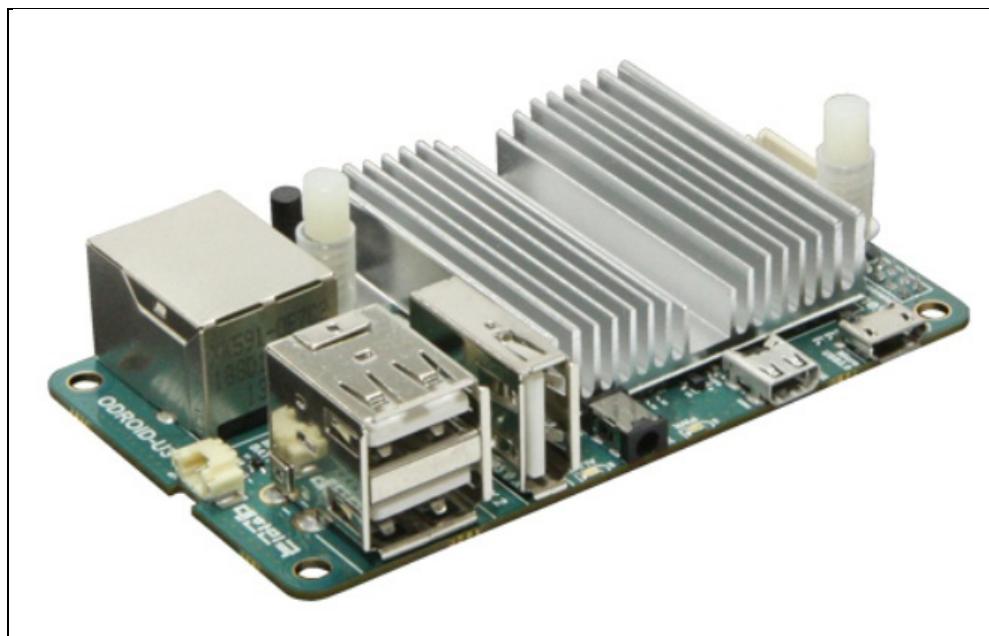

| Figure 4.3 Odroid-U3.....                                                                     | 75 |

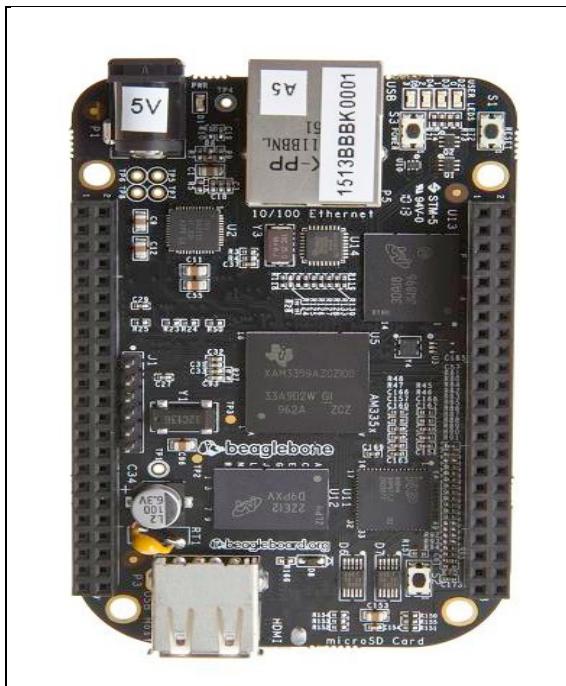

| Figure 4.4 Beaglebone. ....                                                                   | 76 |

| Figure 4.5 Assemblage des cartes Parallella.....                                              | 80 |

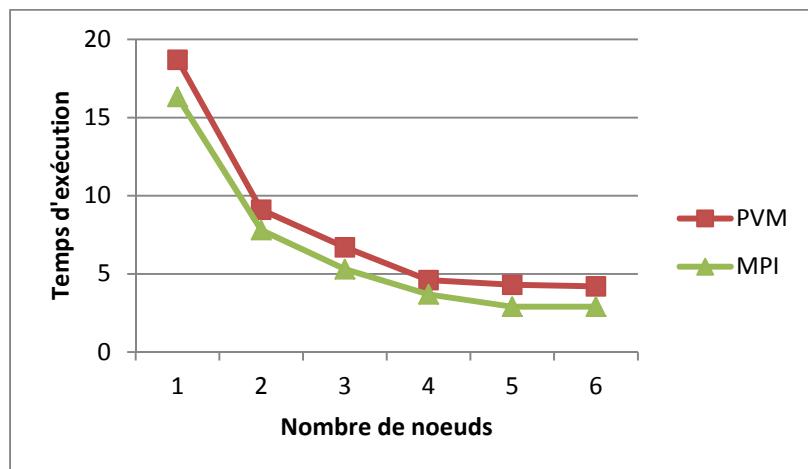

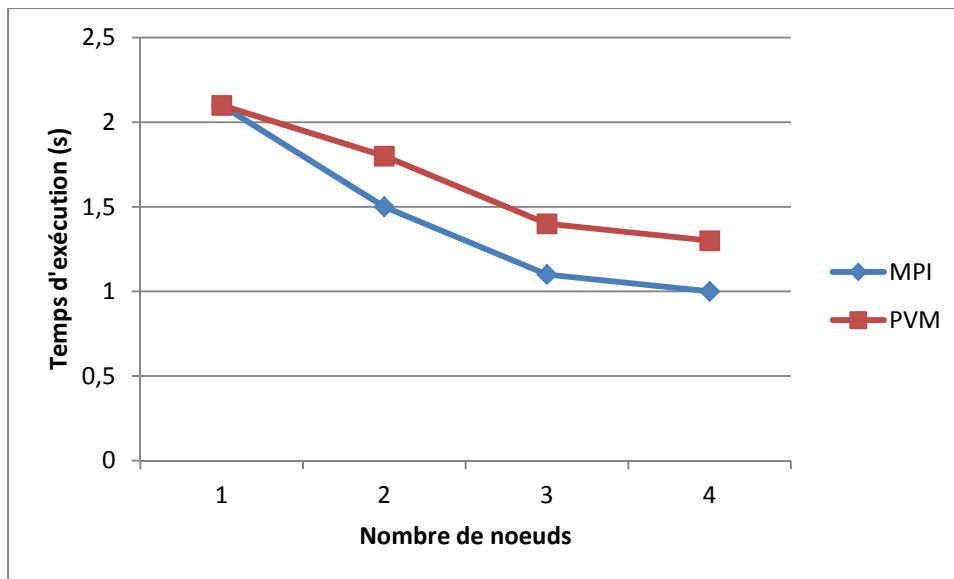

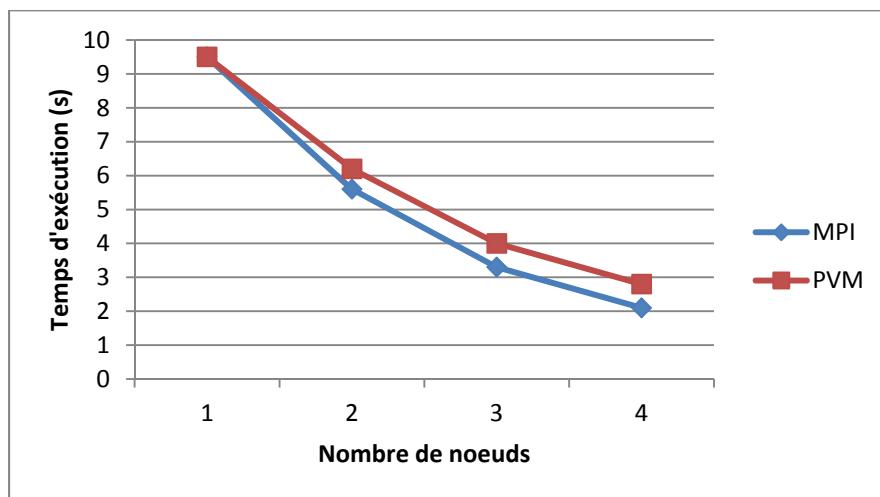

| Figure 4.6 Temps d'exécution en fonction du nombre de nœuds. ....                             | 85 |

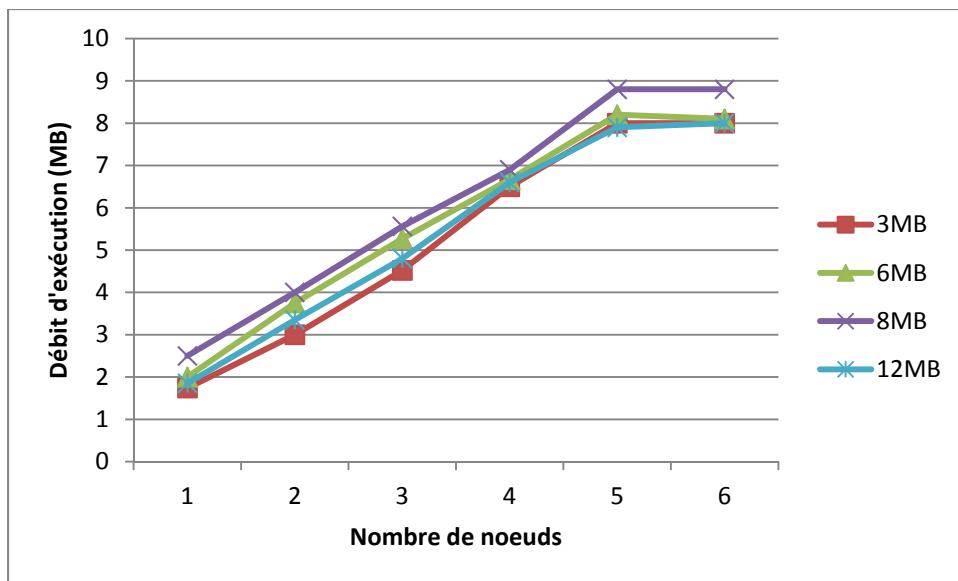

| Figure 4.7 Débit d'exécution en fonction du nombre de nœuds et de la taille de l'entrée. .... | 86 |

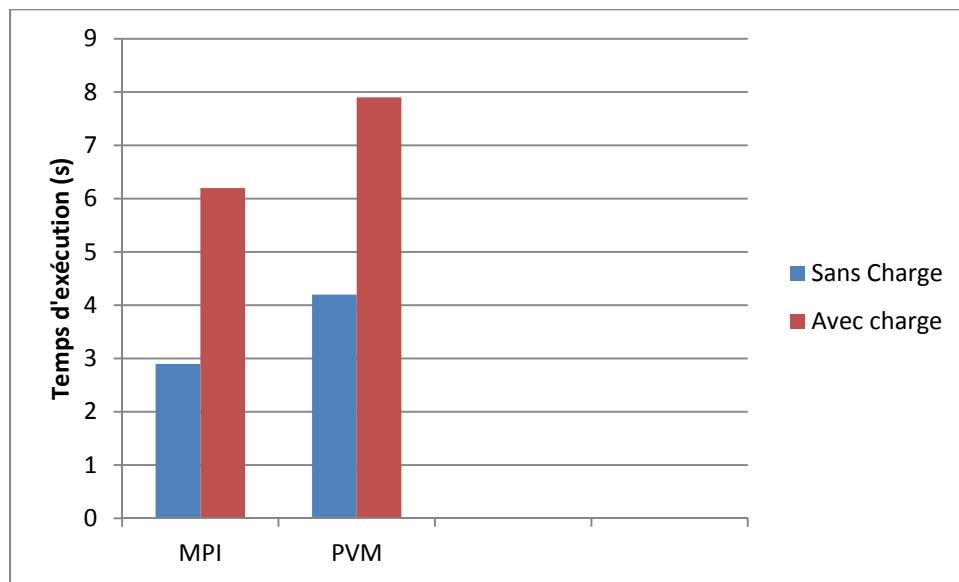

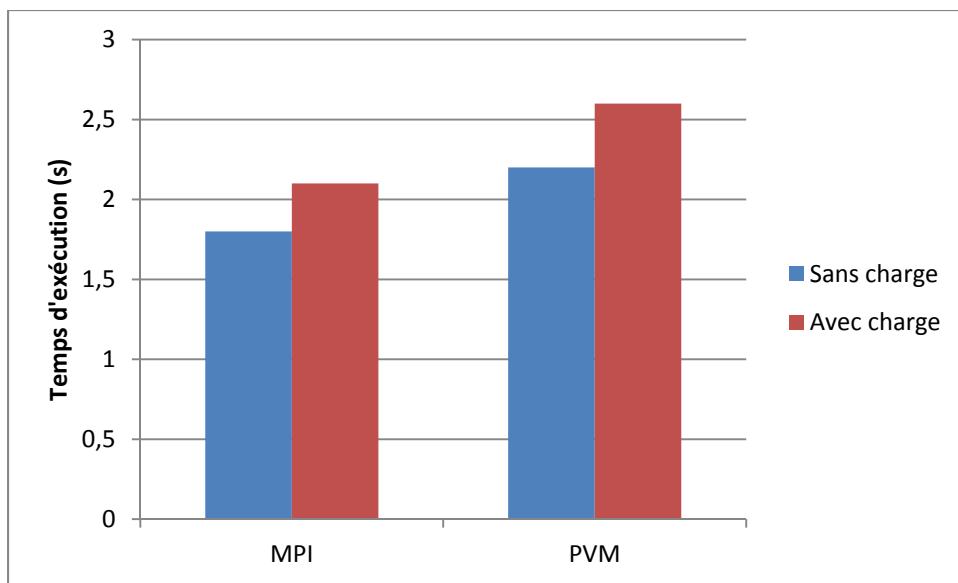

| Figure 4.8 Effet de la charge supplémentaire sur le temps d'exécution.....                    | 87 |

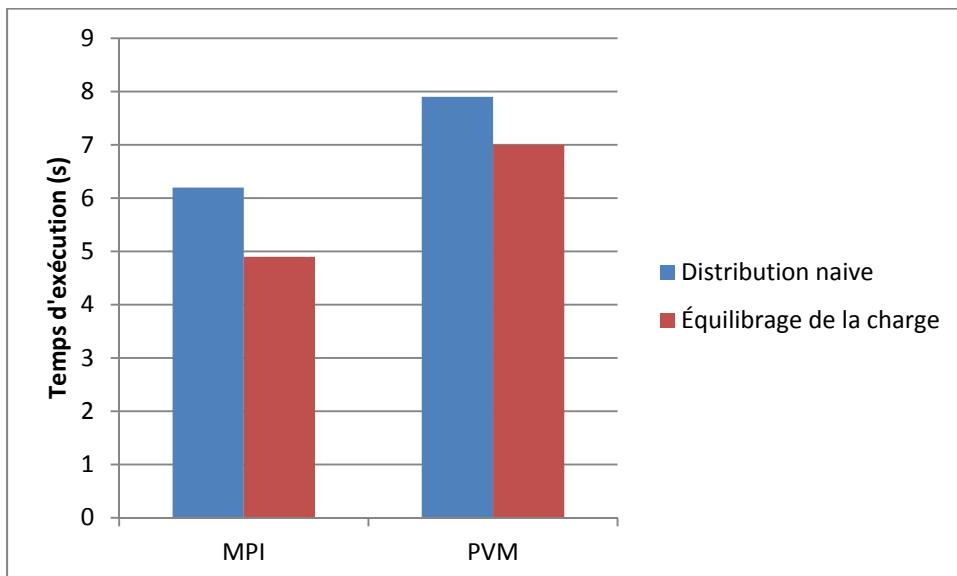

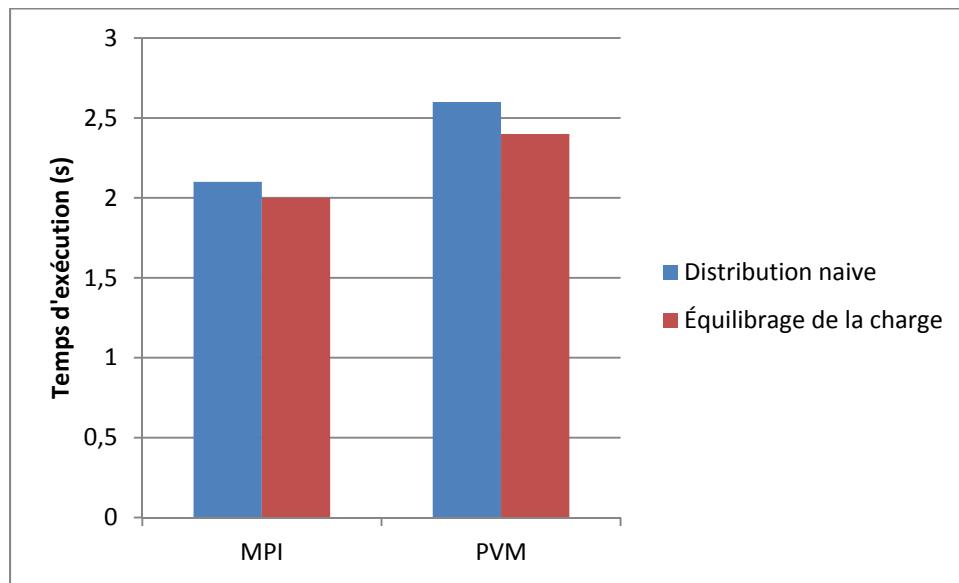

| Figure 4.9 Effet de l'équilibrage de la charge. ....                                          | 88 |

| Figure 4.10 Parallélisation de l'algorithme de correspondance des patrons. ....               | 90 |

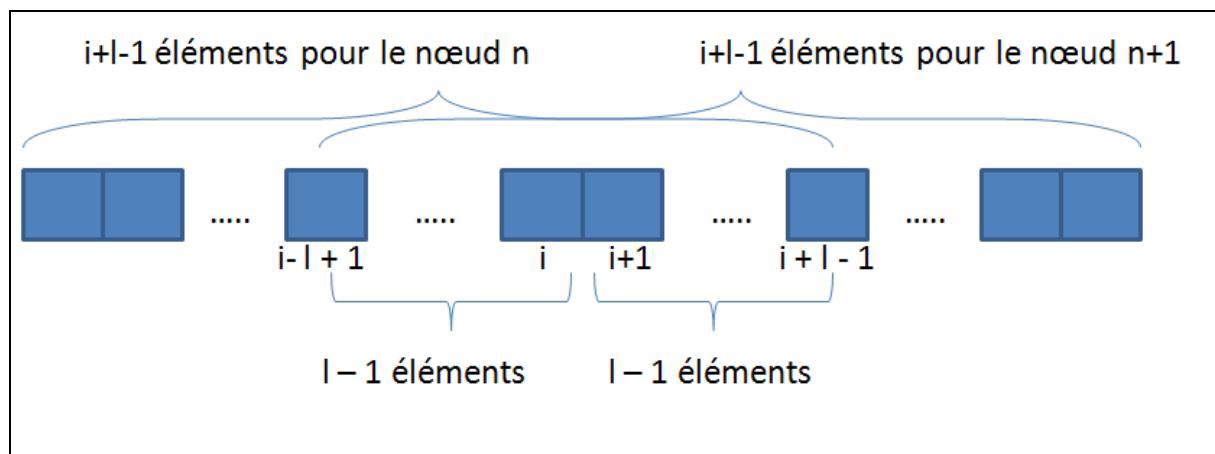

| Figure 4.11 Découpage des portions pour la correspondance des patrons. ....                   | 91 |

|                                                                                           |     |

|-------------------------------------------------------------------------------------------|-----|

| Figure 4.12 Temps d'exécution en fonction du nombre de nœuds.                             | 92  |

| Figure 4.13 Débit d'exécution en fonction du nombre de nœuds et de la taille des entrées. | 92  |

| Figure 4.14 Effet de l'addition de la charge sur le temps d'exécution.                    | 94  |

| Figure 4.15 Effet de l'équilibrage de la charge.                                          | 95  |

| Figure 4.16 L'exécution de PAES en fonction du nombre de nœuds.                           | 96  |

| Figure 4.17 Variation du débit d'exécution en fonction de la taille                       | 97  |

| Figure 4.18 Modules nécessaires pour exécuter Docker                                      | 99  |

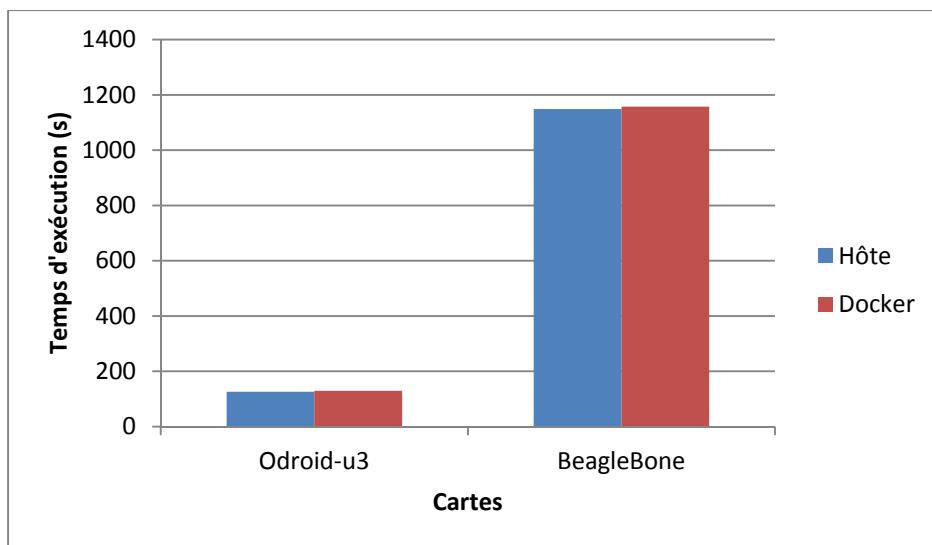

| Figure 4.19 Test d'encodage FLAC mesurant la performance CPU                              | 101 |

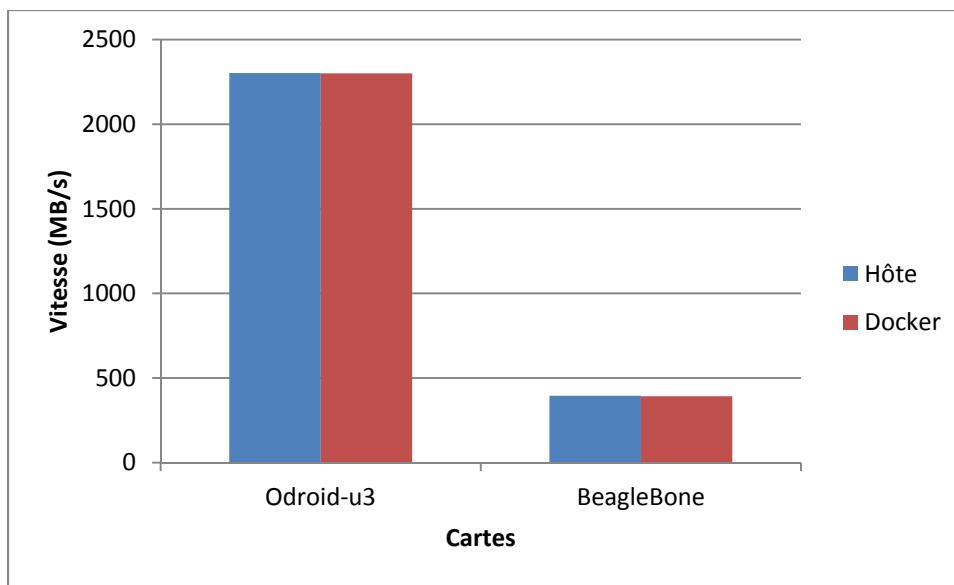

| Figure 4.20 Test RAMspeed mesurant la vitesse d'accès à la RAM.                           | 102 |

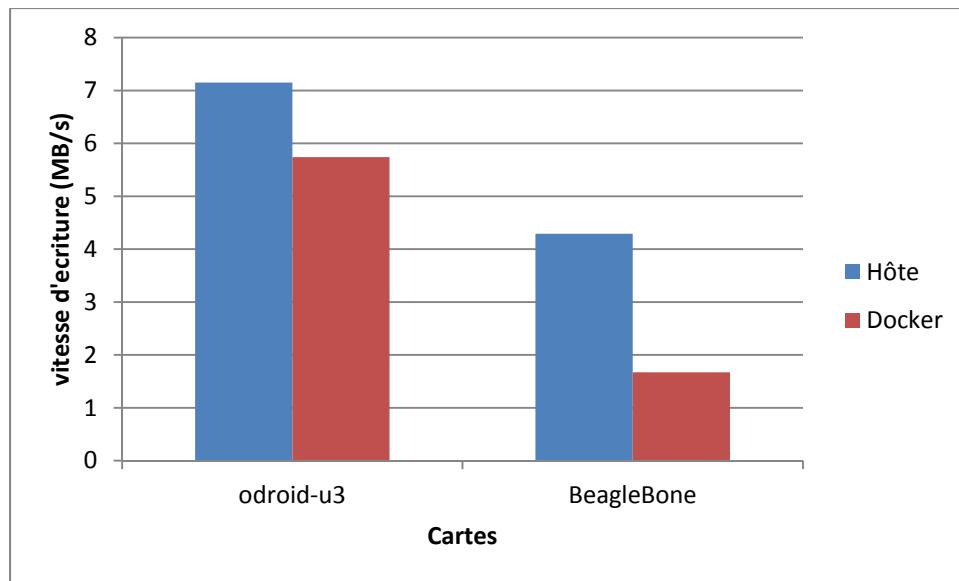

| Figure 4.21 Test IOzone d'écriture sur le disque                                          | 103 |

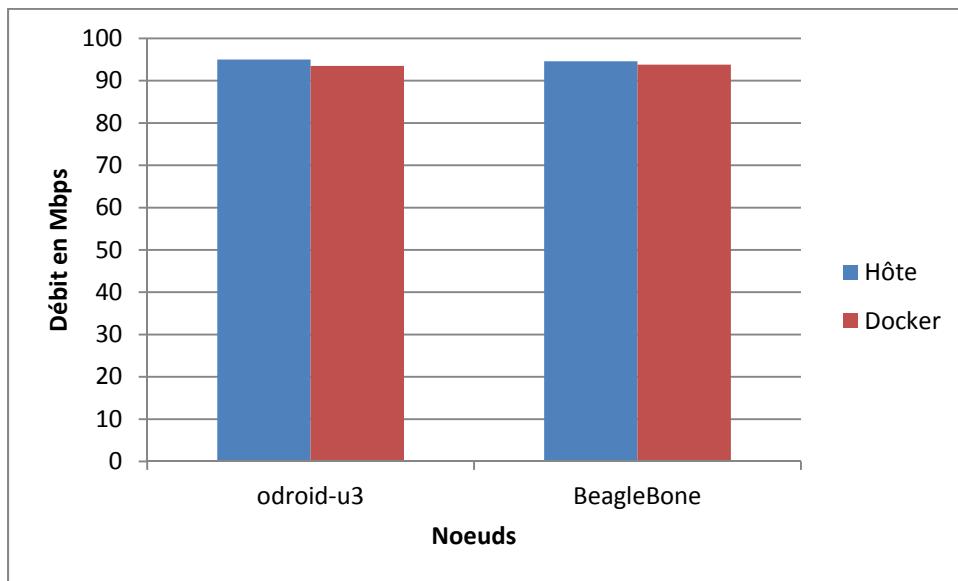

| Figure 4.22 Débit de transfert TCP                                                        | 104 |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|      |                                           |

|------|-------------------------------------------|

| ARM  | Advanced Risc Machines                    |

| CPU  | Central Processing Unit (processeur)      |

| GPU  | Graphic Processing Unit                   |

| HDFS | Hadoop Distributed File System            |

| HPC  | High Performance Computing                |

| IPC  | Inter-Process Communication               |

| KVM  | Kernel-based Virtual Machine              |

| LXC  | Linux Containers                          |

| MPI  | Message Passing Interface                 |

| OS   | Operating System (système d'exploitation) |

| PAES | Parallel Advanced Encryption Standard     |

| PID  | Process Identifier                        |

| PVM  | Parallel Virtual Machine                  |

| RAM  | Random Access Memory                      |

## **LISTE DES SYMBOLES ET UNITÉS DE MESURE**

|     |                                                                       |

|-----|-----------------------------------------------------------------------|

| O   | octet                                                                 |

| Mb  | Megabyte, Mo (Mégaoctet)                                              |

| Gb  | Gigabyte, Go (Gigaoctet)                                              |

| Kb  | Kilobyte, Ko (Kilooctet)                                              |

| MHZ | Mégahertz, unité de mesure de fréquence du Système international (SI) |

| Ms  | Milliseconde                                                          |

| S   | Seconde                                                               |

## INTRODUCTION

### Mise en contexte

Ces dernières années, le monde de l'informatique connaît un besoin grandissant en terme de vitesse de calcul, de traitement, ainsi que de stockage de données. L'exécution de tâches nécessitant une large puissance de calcul appartient au monde de l'informatique de haute performance et a été longtemps réservée aux entreprises et organisations possédant des moyens financiers considérables.

Le calcul de haute performance bénéficie de plus en plus à un nombre grandissant de domaines autres que l'informatique elle-même. Ces domaines incluent l'imagerie, la médecine, la mécanique et d'autres domaines de l'ingénierie qui ont un besoin de simuler de larges problèmes. À ce jour, les outils les plus performants pour le domaine de l'informatique de haute performance sont sans doute les supercalculateurs qui sont composés de milliers de processeurs travaillant en parallèle à la résolution de problèmes liés par exemple aux origines de l'univers et au développement de remèdes pour le cancer. Mais, ces supercalculateurs ont un coût élevé qui avoisine les 20M\$ (insidehpc, 2016b) et ne sont pas donc accessibles à n'importe qui. De plus, ces supercalculateurs consomment énormément d'énergie.

L'un des secteurs qui peut bénéficier de la puissance offerte par le HPC, est celui de la sécurité. En effet, de nombreuses applications liées à la sécurité, telles que le chiffrement ou la détection de malwares<sup>1</sup> demandent une puissance de calcul qui n'est pas toujours disponible sur les systèmes où s'exécutent ces algorithmes. En effet, dans le cas des téléphones mobiles ou autres systèmes embarqués, les ressources sont limitées et effectuer des analyses de détection de malwares ou exécuter des algorithmes de chiffrement affectent grandement les performances du système d'où le besoin de les "décharger" et les exécuter dans un environnement moins contraignant.

---

<sup>1</sup> Logiciel malveillant

D'un autre côté, la technologie de la virtualisation apporte de nombreux avantages dont le déploiement rapide et à distance d'environnements de développements. Cette dernière est l'une des fondations sur lesquels reposent les centres de données grâce à la facilité de gestion des ressources et l'isolation des environnements des différents serveurs qu'elle offre.

Combiner la technologie des clusters avec la virtualisation serait grandement bénéfique du point de vue de l'exploitation de toutes les ressources offertes par un cluster. De plus, plusieurs types d'applications pourraient s'exécuter sur un cluster, chacune demandant un environnement différent. La virtualisation permettrait à ces applications de tourner sur un même nœud physique, sans avoir à dédier un nœud à chaque application ce qui augmente la flexibilité du cluster. Ce dernier peut aussi bénéficier de la haute disponibilité et de la tolérance aux fautes qu'offre la virtualisation, puisque l'échec d'une machine virtuelle ne signifie pas l'échec de tout le système.

Un autre avantage de la combinaison des clusters et de la virtualisation est la sécurité. En effet, l'isolation offerte par la virtualisation permettrait à plusieurs applications de s'exécuter sur le même cluster physique, en parallèle tout en étant complètement isolées les unes des autres.

Pour les deux technologies citées ci-dessus, il existe des objectifs en commun,dont le besoin de réduire le coût du matériel ainsi que la consommation d'énergie. En effet, selon(Hamilton, 2009), plus de 35% du coût total des centres de données est lié à l'énergie électrique consommée, aux opérations de refroidissement ainsi qu'aux installations physiques. Réduire ces coûts est alors une nécessité.

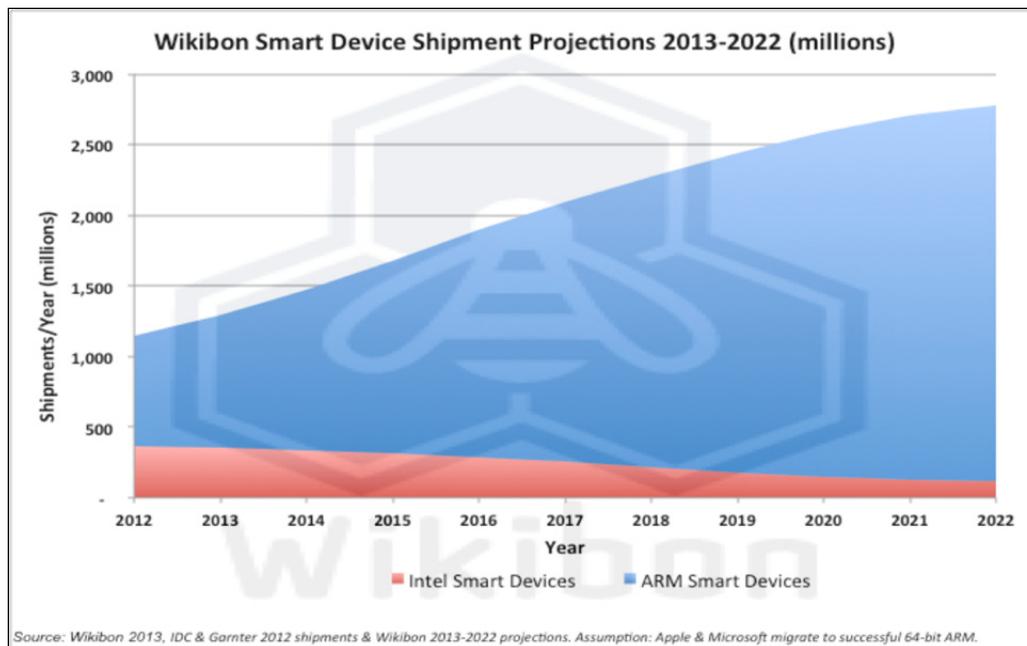

Dans cette optique, l'intérêt pour la technologie ARM est de plus en plus grandissant en vue des avantages qu'offrent les appareils présentant cette architecture. En effet, cette architecture équipe la plupart des téléphones portables sur le marché et d'autres systèmes embarqués. Dernièrement elle vient de dépasser l'architecture x86 dans la part de marché et les projections prévoient que cette tendance va s'accroître comme le montre la figure suivante.

Figure 0.1 Projection de la part de marché de l'architecture ARM en comparaison avec Intel Tirée de (Foyer, 2013).

Parmi les raisons de cette popularité est la faible consommation d'énergie des appareils ARM et le ratio performance/coût qui est très réduit. En plus des téléphones intelligents de nouvelle génération, l'architecture ARM offre des cartes de développement avec des caractéristiques intéressantes. En effet, ces derniers sont l'équivalent d'une carte mère comportant toutes les composantes nécessaires à l'exécution d'un système d'exploitation puisqu'elles possèdent des processeurs multicoeurs, une mémoire RAM décente ainsi que d'autres périphériques.

Est-il alors possible de tirer profit des avantages qu'offre l'architecture ARM et les appliquer dans le domaine de l'informatique de haute performance dans le but d'exécuter des algorithmes de sécurité? Est-ce qu'en combinant plusieurs de ces cartes, on arriverait à avoir des résultats satisfaisants en comparaison avec les systèmes conventionnels? D'autre part, est-il possible de virtualiser les appareils ARM et garder d'assez bonne performance afin de faciliter la gestion et la sécurisation des cluster et considérer l'usage de ces derniers dans le cadre d'un centre de données?

C'est dans ce cadre que s'inscrit la présente étude, où nous testons dans un premier temps l'efficacité de ces cartes dans l'exécution d'algorithmes de sécurité (chiffrement et détection de malwares) de manière individuelle puis en formant un cluster avec plusieurs cartes. Dans un second temps, nous déployons une technique de virtualisation légère sur les cartes et les testons pour mesurer l'impact sur les performances du système.

## Problématique

Notre problématique de recherche se divise en deux grandes parties :

- Est-il possible d'utiliser les ordinateurs mono-cartes possédant l'architecture ARM pour exécuter des algorithmes de cryptographie et de détection de logiciels malveillants?

- Est-il possible d'adapter la technologie de virtualisation sur les appareils ARM sans que cela n'impacte leur fonctionnement?

La première partie de la problématique implique des sous-problématiques que nous tentons de résoudre dans ce travail:

- Quelles sont les difficultés techniques liées à l'utilisation des appareils ARM?

- Quels sont les outils les mieux adaptés aux appareils ARM pour implémenter une architecture HPC?

- Est-il possible d'améliorer la performance en équilibrant la charge entre les appareils ARM?

Afin de répondre à ces questions, nous mettons en place dans un premier temps un cluster constitué de plusieurs ordinateurs mono-cartes possédant l'architecture ARM. Nous implementons pour ce dernier un système de monitorage adéquat pour les systèmes à ressources limitées. Afin de déterminer l'outil le mieux adapté pour le passage de message au sein de ce cluster, nous adaptons différents algorithmes aux deux principaux outils sur le marché à savoir MPI et PVM, et testons les performances de ces deux derniers. Nous implementons deux algorithmes de chiffrement sur le cluster qui sont le AES et le AES

parallèle ainsi qu'un algorithme de correspondance des patrons malicieux. Nous proposons aussi une solution d'équilibrage de la charge et testons son efficacité.

Pour ce qui est de la virtualisation, la plupart des cartes ARM n'étant pas adaptées à toutes les technologies de virtualisation, nous choisissons la solution la plus prometteuse sur le marché actuel et la testons sur deux types de cartes qui permettent de l'exécuter. Par la suite, nous effectuons des tests afin de déterminer l'impact de la virtualisation sur le fonctionnement du système.

## **Objectifs**

Les objectifs que nous nous sommes donc fixés sont les suivants:

- Installer les environnements adéquats pour le fonctionnement des cartes ARM.

- Implémenter les algorithmes de sécurité sur les cartes.

- Mettre en place un cluster composé des cartes ARM en utilisant des mécanismes de passage de message.

- Améliorer le cluster en ajoutant un module de monitorage et un mécanisme d'équilibrage de la charge.

- Déployer la virtualisation sur les cartes ARM.

## **Méthodologie suivie**

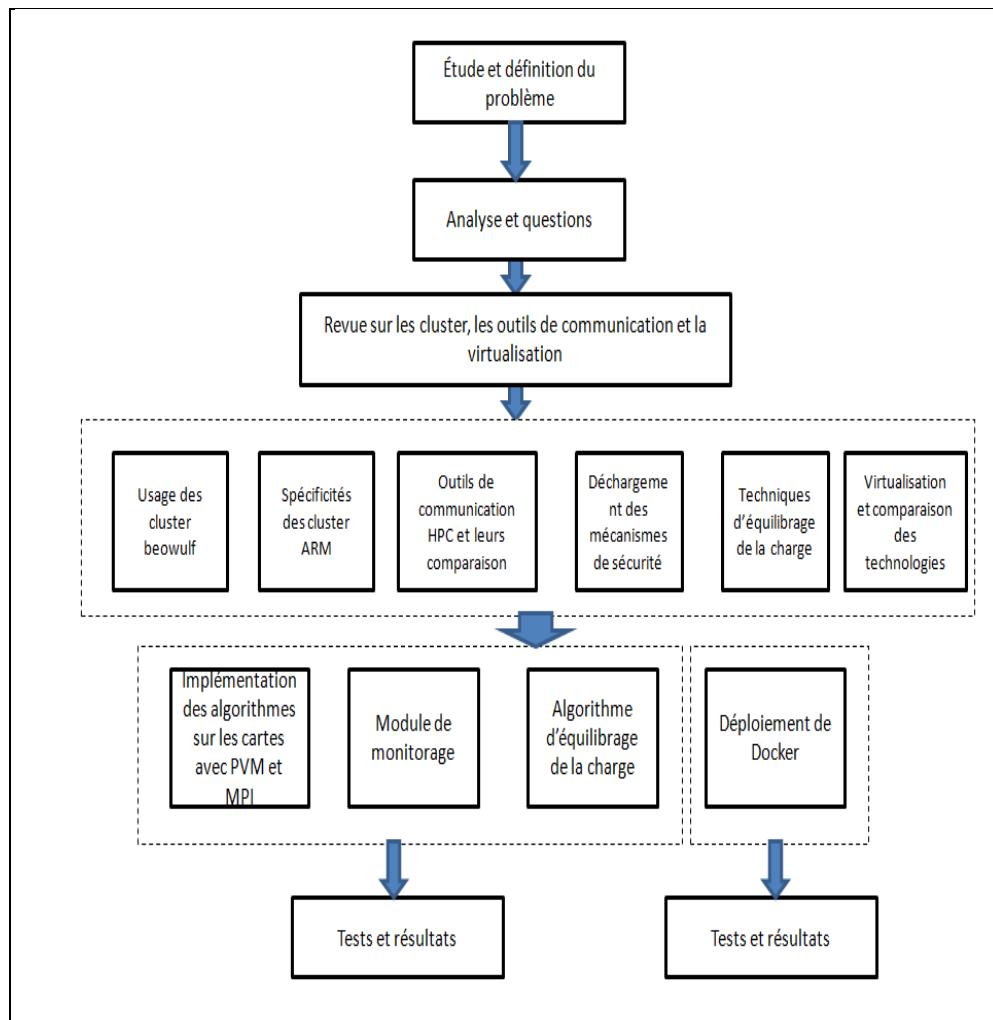

La méthodologie suivie est décrite par la figure 1-2. Cette dernière consiste à définir la problématique de recherche, ensuite nous avons recherché les différents exemples dans la littérature liés à notre étude. Les documents et articles recherchés concernent l'usage des cluster Beowulf ainsi que des clusters constitués par les appareils ARM. Nous investiguons dans la littérature le meilleur mécanisme de passage de message au sein d'un cluster et nous concluons qu'il n'y a pas de consensus quant à ce sujet. Nous recherchons les travaux qui s'intéressent aux traitements de sécurité sur des systèmes limités et qui proposent de les décharger vers des environnements disposant de plus de ressources. Nous consultons aussi les techniques d'équilibrage de la charge présents dans la littérature.

Afin de choisir la méthode de virtualisation à déployer sur les cartes ARM, nous recherchons les documents et articles liés aux différentes technologies de virtualisation et les différences entre ces dernières.

Nous avons par la suite mis en place un cluster implémentant trois algorithmes liés à la sécurité en utilisant les deux approches de passages de messages MPI et PVM. Afin que le cluster soit complet, nous le dotons d'un module de monitorage qui ne consomme beaucoup de ressources afin d'être adapté aux appareils ARM. Nous implementons aussi un mécanisme d'équilibrage pour la distribution de la charge au sein du cluster. Pour ce qui est de la virtualisation, nous effectuons la configuration nécessaire afin de déployer Docker sur les cartes.

Finalement, nous testons les résultats de l'implémentation pour le cluster en comparant le temps d'exécution de chaque algorithme selon différentes configurations et selon les deux implémentations MPI et PVM.

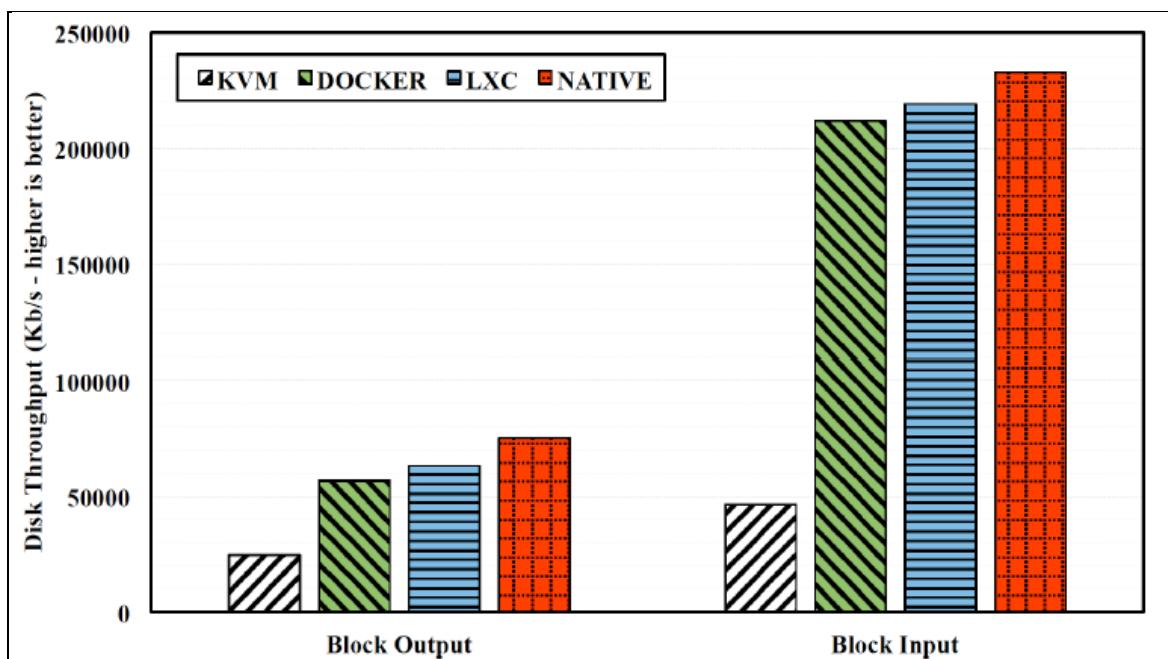

Pour les tests de la virtualisation, nous exécutons plusieurs benchmark sur les cartes ARM afin de déterminer l'impact de la virtualisation sur l'accès à la RAM, à la CPU, au disque ainsi qu'aux interfaces réseau.

Figure 0.2 Méthodologie de notre étude

## Organisation du rapport

Le rapport est organisé comme suit : dans la première partie, nous présentons les notions de base nécessaires à la compréhension des concepts principaux de notre étude. Ceci inclut la notion de cluster, de HPC, la technologie ARM et les technologies de virtualisation.

Le second chapitre comporte la revue de littérature des travaux liés à notre étude. Nous présentons les recherches ayant été effectuées sur les cluster Beowulf et notamment ceux réalisés avec des appareils ARM. Par la suite, nous présentons les comparaisons faites dans la

littérature entre les deux plateformes de développement pour les clusters qui sont PVM et MPI. De plus, nous détaillons le concept de distribution de la charge au sein d'un cluster hétérogène. Nous présentons par la suite les travaux qui ont proposé de décharger les traitements liés à la sécurité vers des environnements disposant d'assez de ressources. Et enfin, nous citons les travaux qui ont été faits sur la comparaison des technologies de virtualisation.

Le troisième chapitre détaille l'architecture du cluster que nous avons mis au point ainsi que les algorithmes de sécurité que nous avons implémentés dessus, à savoir la correspondance des patrons et l'AES séquentiel et parallèle. Aussi, nous présentons l'architecture du mécanisme de monitorage et l'algorithme de distribution de la charge.

Le quatrième chapitre est celui des résultats où nous présentons les résultats des différentes expérimentations pour déterminer l'efficacité du cluster ARM à travers les différents algorithmes implémentés, et ce avec PVM et MPI. Nous faisons des benchmarks pour déterminer l'impact de la virtualisation avec Docker sur les performances des cartes ARM.

Finalement, nous donnons une conclusion quant aux résultats obtenus et les contributions apportées par ce travail.

# **CHAPITRE 1**

## **NOTIONS DE BASE**

### **1.1 Introduction**

Dans ce chapitre, nous allons présenter les notions de base essentielles à la compréhension de ce travail. Ces notions consistent en l'informatique hautement parallèle qui est en constante évolution avec les progrès technologiques et dont l'accessibilité au grand public en a fait un centre d'intérêt de plusieurs travaux de recherche. Les points les plus importants du HPC sont la notion de cluster et les mécanismes de communication au sein d'un environnement hautement parallèle.

La deuxième notion importante est l'architecture ARM, et plus précisément les appareils ARM et leur utilisation dans le domaine des clusters. Nous allons présenter entre autres les différents types de processeurs et leur évolution et aborder les environnements que peuvent offrir ces cartes.

La dernière partie de ce chapitre concerne la virtualisation. Nous présentons la définition de ce concept ainsi que les différentes techniques qui existent en matière de virtualisation, notamment Docker<sup>2</sup>.

### **1.2 Informatique de haute performance**

#### **1.2.1 Généralités**

Le calcul à haute performance consiste à rassembler la puissance de calcul de plusieurs processeurs de manière à surpasser la puissance de calcul que pourrait offrir un seul ordinateur conventionnel afin de résoudre des problèmes plus ou moins importants et exigeants en ingénierie, mathématiques...

---

<sup>2</sup><https://www.docker.com/>

Durant les dernières années, l'importance des HPC dans le domaine de la mécanique (calcul de la mécanique des fluides), pharmaceutique (conception de médicaments), traitement d'image médical et d'autres domaines pouvant bénéficier d'une grande puissance de calcul a été cruciale (warwick, 2015).

Le rassemblement de la puissance de plusieurs processeurs se fait en général de manière à ce que ces derniers travaillent en collaboration ou en 'parallèle', on parle alors de programmation parallèle. Cette dernière prévoit deux paradigmes qui sont :

- Instruction unique plusieurs données : Comme son nom l'indique, une seule instruction est appliquée à différentes données afin de produire plusieurs résultats.

- Instructions multiples, données multiples :Différentes instructions sont appliquées à différentes données.

### **1.2.2 Gestion de la mémoire**

Il existe trois architectures principales selon lesquelles la mémoire est gérée dans un environnement HPC (insidehpc, 2016a).

- Mémoire partagée : On parle de mémoire partagée lorsque les cpu travaillant en parallèle se partagent le même espace d'adressage physique. Ce type de mémoire dispose de deux manières d'accès Uniform Memory Access et On cache-coherent nonUniform Memory Access.

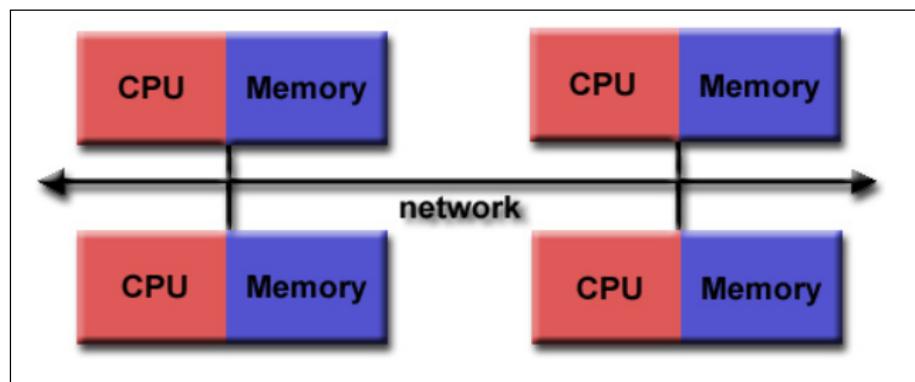

- Mémoire distribuée : L'espace d'adressage est séparé (physiquement et logiquement), chaque processeur possède son propre espace adressage et les processus peuvent communiquer entre eux en utilisant la communication réseau, plus précisément des mécanismes de passage de message qu'on abordera dans la prochaine partie.

- Système hybride : On parle de système hybride lorsque les deux types de mémoires (partagée et distribuée) sont utilisés. Cela consiste en plusieurs blocs (processeurs multicoeurs) partageant une mémoire et qui sont interconnectés en réseau. Cette topologie est la plus utilisée en pratique.

### 1.2.3 Cluster Beowulf

À ses débuts, le monde du HPC consistait en d'imposants supercalculateurs utilisés principalement dans les départements de défense et certains laboratoires de recherche. Ces appareils étaient non seulement très coûteux, mais aussi difficiles à programmer et à entretenir ce qui nécessitait des experts propres à l'architecture de chaque supercalculateur. Tous ces facteurs faisaient en sorte que le calcul hautement parallèle était inaccessible aux scientifiques et autres personnes ne disposant pas d'importantes ressources financières(Senning, 2016).

Cette limitation a changé avec l'apparition d'une nouvelle approche et l'émergence de supercalculateurs formés par des clusters de machines conventionnelles. Cette architecture a été appelée Beowulf et consiste en un ensemble de PC connectés en réseaux et disposant de certaines bibliothèques (MPI ou PVM) nécessaires à la distribution des tâches et la communication. Le premier prototype, qui a été réalisé à la NASA en 1994 et était composé de 16 processeurs DX4 connectés via Ethernet, a été un tel succès que les universitaires l'ont adopté(Merkey, 2015).

Figure 1.1 Exemple de cluster Beowulf.

Tirée de (Senning, 2016).

Certains facteurs ont contribué à la popularité que connaît le cluster Beowulf aujourd'hui, parmi lesquels le grand nombre de constructeurs de PC et d'autres composantes destinées au grand public qui a induit une forte concurrence faisant baisser les prix considérablement. D'autre part, le monde des logiciels libres a connu une grande évolution, notamment Linux et les librairies MPI et PVM dont dépendent les clusters Beowulf. Aussi, les technologies réseau n'ont cessé de se développer depuis le premier prototype de cluster en 1994 où à l'époque les processeurs étaient trop rapides pour une seule connexion Ethernet et les switchs Ethernet n'étaient pas à la portée de tout le monde.

Ce qui constitue l'un des points forts des clusters Beowulf est le fait que le modèle de programmation ne dépend pas des composantes matérielles telles que les processeurs ou la vitesse du réseau, ce qui lui procure une grande flexibilité. Cela est dû en grande partie aux protocoles de communication qu'on verra dans le paragraphe suivant.

#### 1.2.4 Mécanismes de passage des messages

L'un des concepts les plus importants dans le HPC est le mécanisme de passage des messages entre les différents nœuds. En effet, tout le système est dépendant de la bonne communication des données et des instructions, une mauvaise communication nuirait gravement aux performances et pourrait rendre le tout obsolète. La clé d'une bonne communication réside dans l'outil de passage choisi ainsi que la configuration des nœuds. Au sein d'un programme de passage de messages, chaque processeur exécute une tâche séparément avec des variables qui lui sont privées et donc locales. La communication se fait à travers des fonctions propres au système de passage de messages qui peut varier d'une simple variable à des structures plus complexes que nous verrons par la suite (Barney, 2015).

En général, l'envoi d'un message nécessite la connaissance de plusieurs éléments qui sont les suivants :

- l'expéditeur

- type de données à envoyer

- taille des données

- le destinataire

Cette liste peut varier d'une implémentation à une autre et inclure plus d'éléments tels que les rangs des destinataires, le type d'envoi...

Afin d'implémenter un tel mécanisme, il existe deux approches qui permettent le passage de messages dans un environnement distribué : PVM et MPI.

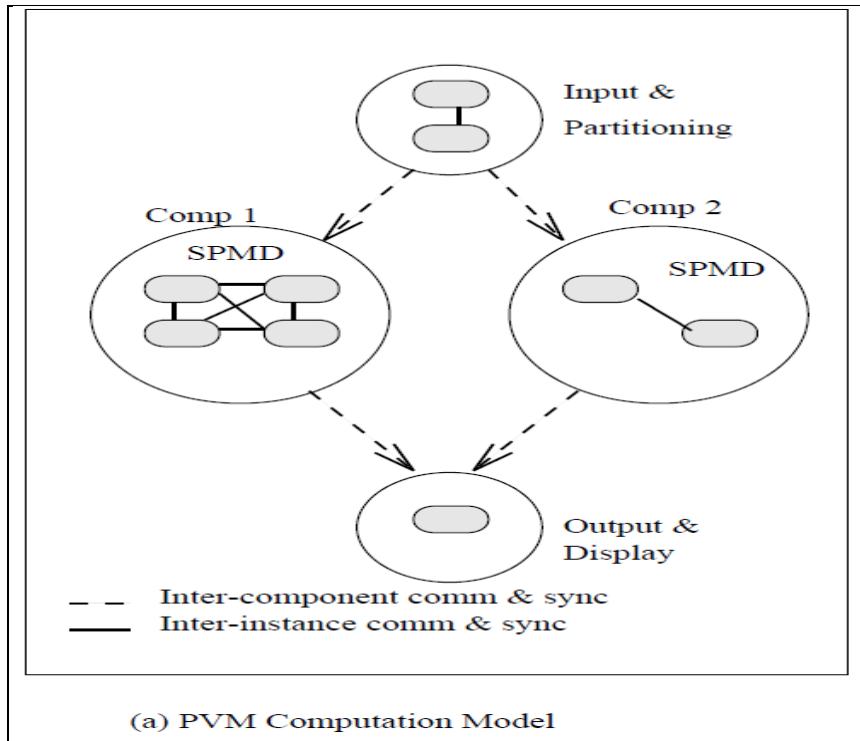

#### 1.2.4.1 PVM

PVM (Parallel Virtual Machine) consiste comme son nom l'indique en une machine virtuelle qui fait abstraction du réseau connectant plusieurs équipements (ordinateurs, serveurs...). Il a été développé en 1989 à Oak Ridge National Laboratory. Cette approche mise sur l'hétérogénéité du système, en effet elle permet à différents types d'ordinateurs d'être vus en tant qu'une seule machine virtuelle où PVM gère lui-même la communication des données, le routage ainsi que la planification des tâches à travers le réseau de manière transparente. Un deamon<sup>3</sup> est exécuté sur chaque ordinateur composant le réseau, ces processus fonctionnent de manière concurrente et permettent ainsi de simuler un seul système(Al Geist, 1994).

PVM se veut simple d'utilisation pour l'utilisateur qui se contente d'écrire son programme en forme de tâches qui coopèrent entre elles. Ces tâches ont accès aux ressources PVM à travers une bibliothèque de fonctions standard. Ces fonctions permettent d'organiser les tâches, c'est-à-dire le lancement ou la terminaison d'une tâche, la gestion de la concurrence et de la synchronisation. Les primitives de passage de messages disponibles offrent la possibilité d'envoyer des structures données en différents modes : envoi simple ou multiple. Les tâches font ici office d'unités de calcul pour PVM et sont semblables aux processus dans les systèmes UNIX. Plusieurs utilisateurs peuvent définir chacun sa propre machine virtuelle et leurs applications peuvent s'exécuter simultanément.

---

<sup>3</sup> Processus qui s'exécute en arrière plan

Figure 1.2 Communication dans PVM.

Tirée de (Al Geist, 1994).

Le modèle de calcul de PVM est basé sur la décomposition des applications en plusieurs tâches qui s'occuperaient chacune d'une partie du traitement. Une des manières serait de décomposer selon les fonctions présentes dans l'application où chaque fonction serait une tâche (e.g une tâche pour la lecture des données, une tâche pour l'affichage...). Cette façon de faire est appelée parallélisme fonctionnel. Il existe un autre moyen plus utilisé pour la décomposition appelé parallélisme de données où toutes les tâches seraient semblables, mais chacune travaillerait sur une partie distincte des données. La figure 1.2 montre un exemple d'interaction des tâches dans PVM où les deux modèles parallélisme sont utilisés.

L'architecture de PVM permet aux tâches de s'échanger des messages, et suppose que n'importe quelle tâche a la possibilité de communiquer avec toutes les autres sans restrictions sur le nombre ou la taille des messages échangés. La taille des buffers alloués est donc dynamique et ne dépend que de la mémoire disponible dans le système, et dans le cas où l'utilisateur essaie d'envoyer des données de taille supérieures à la mémoire disponible, PVM

retourne une erreur sans pour autant interrompre l'exécution. En effet, le modèle de communication implémenté par PVM permet différents modes d'envoi :

- Envoi asynchrone bloquant : ce mode d'envoi permet le retour de la fonction d'envoi dès que le tampon d'envoi est libéré (toutes les données ont été envoyées) et indépendamment de l'état du destinataire.

- Réception non bloquante : dans ce mode, la fonction de réception retourne immédiatement soit avec les données ou avec un flag indiquant la non-réception de celles-ci.

- Réception asynchrone bloquante : La fonction de réception ne retourne que quand les données sont dans le tampon de réception.

Ces trois modes concernant la communication point à point, PVM permet aussi la communication de groupe tel que le broadcast et le multicast à un groupe de nœud prédéfini.

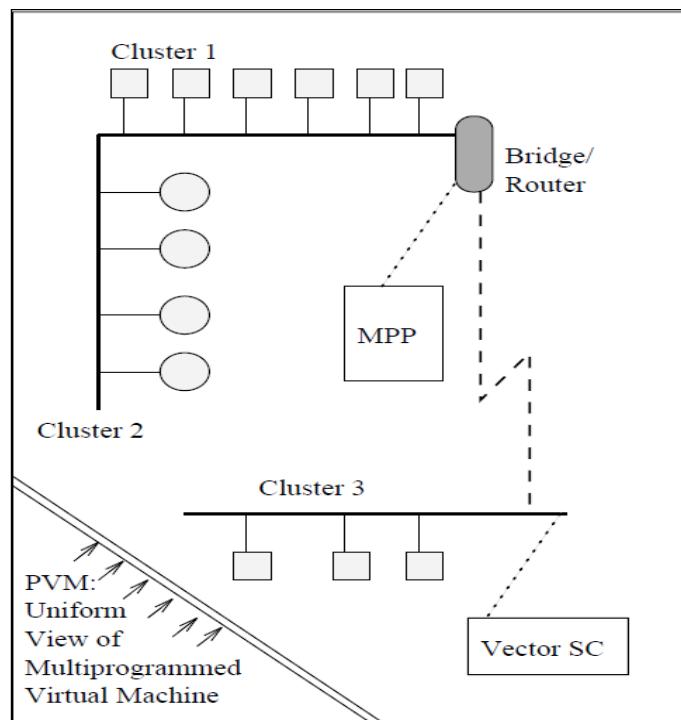

Figure 1.3 Architecture de PVM.

Tirée de (Al Geist, 1994).

La figure 1.3 représente l'architecture globale de PVM et met en valeur l'hétérogénéité du système où on peut voir des clusters de PC connectés avec une machine massivement parallèle.

#### 1.2.4.2 MPI

MPI est une librairie standard de passage de messages développée lors du forum MPI regroupant plus de 40 organisations incluant des chercheurs, des développeurs de librairies logicielles ainsi que des utilisateurs. Les travaux ont débuté en 1992 et la première version de MPI a été achevée en mai 1994(Forum, 2012).

Le but derrière la réalisation de MPI est d'offrir un standard pour l'écriture de programmes de passage de message qui soit pratique, portable, efficace et flexible. Pour cela, des objectifs ont été fixés :

- MPI doit être une librairie permettant de développer des applications parallèles et non un système d'exploitation distribué.

- MPI doit donner la capacité de développer des applications hautement performantes quand déployé sur des systèmes de haute performance. C'est pour cela que les copies de mémoires ne sont pas obligatoires.

- Afin de favoriser la portabilité, MPI doit être modulaire. Cette modularité implique des choix de développements tels que toutes les références doivent être relatives à des modules et non au programme en entier.

- MPI doit être extensible afin de satisfaire aux éventuels besoins futurs, ce qui implique de ne pas viser un seul langage orienté objet, mais plutôt un ensemble de concepts orienté objet.

- MPI doit supporter l'hétérogénéité, c'est-à-dire fonctionner sur plusieurs types d'architectures en parallèle.

- MPI devrait donner les moyens de gérer la concurrence entre les processus.

Toutes ces conditions ont été prise en compte pour le développement de la première version de MPI qui était compatible avec C,C++ et Fortran.

#### 1.2.4.3 Modèle de programmation

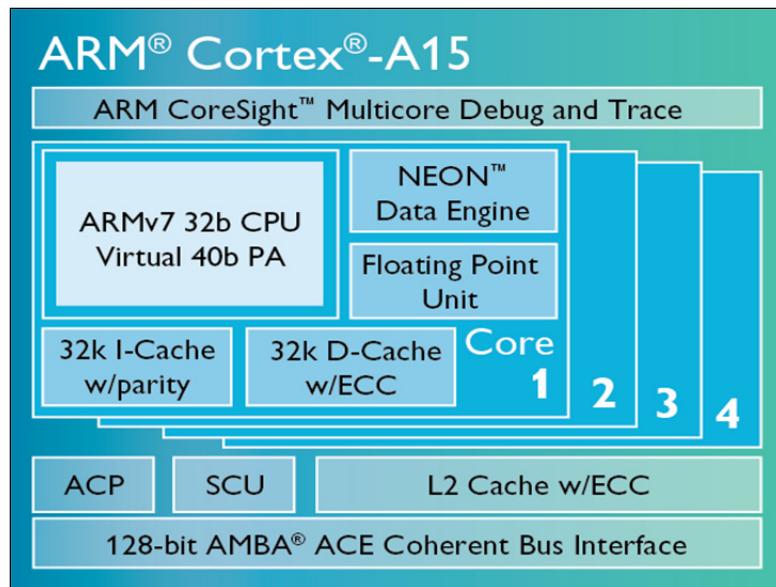

Au départ, MPI a été pensé pour les systèmes à mémoire distribuée, vu qu'ils étaient de plus en plus populaires ce qui donnait l'architecture de la figure 1.4 où chaque nœud possède sa propre mémoire locale.

Figure 1.4 Mémoire distribuée.

Tirée de (Barney, 2015).

Avec l'apparition des multiprocesseurs symétriques, il a été possible de les combiner afin d'avoir un architecture hybride comme le montre la figure 1.5.

Figure 1.5 Architecture hybride.

Tirée de (Barney, 2015).

MPI est capable de s'adapter aux deux types d'architectures et ses développeurs ont pris en compte différents types de protocoles et d'interconnexions. Cependant , le modèle de programmation est essentiellement basé sur un système à mémoire distribuée, et ce indépendamment de l'architecture sous-jacente, de plus, tout parallélisme doit être implémenté par le programmeur.

#### **1.2.4.4 Abstraction**

Le standard MPI définit un API de haut niveau qui fait abstraction des couches de transport. En effet, le programmeur n'a pas besoin de connaître le protocole réseau utilisé pour communiquer entre les différents processus, il a juste besoin d'utiliser une primitive MPI qui serait sous la forme 'Le processus de rang x veut envoyer les données de type k au processus de rang y'. Les données sont transférées sans aucune mention de connexion établie et sans que le programmeur ait à spécifier une adresse réseau. Cette abstraction a pour effet de cacher au niveau applicatif l'architecture sous-jacente qui pourrait s'avérer complexe et alléger ainsi le code. D'autre part, une telle approche vise à augmenter la portabilité vers différentes plateformes et protocoles de transport.

#### **1.2.4.5 Communication**

MPI définit plusieurs modes de communication entre les processus qui se divisent essentiellement en deux types: point à point et communication de groupe(Forum, 2012).

##### **A. Point à point**

- Envoi et réception bloquants : Cette fonction ne retourne que lorsque le buffer d'envoi est vide et prêt à l'écriture et que toutes les données ont été reçues. Ce mode permet de savoir si toutes les données ont été reçues et qu'ils peuvent être utilisés.

- Envoi et réception non bloquants : Cette fonction retourne sans attendre la fin de l'opération, ce qui permet d'accélérer le calcul parallèle tout en limitant les possibilités de blocage.

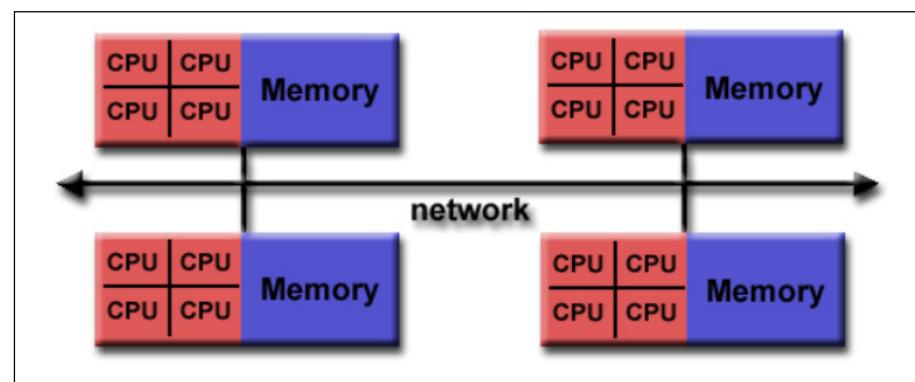

## B. Communication de groupe

La communication de groupe ou collective s'effectue en invoquant la même routine dans les différents processus d'un même groupe. Les mêmes arguments doivent être mentionnés pour les émetteurs et les récepteurs, et l'un des plus importants est le communicateur qui sert à définir le groupe concerné. Certaines opérations ont comme source d'envoi ou point de destination un seul processus, il est alors considéré comme processus 'root' et certains arguments ne sont pris en considération que par ce dernier.

Les routines de communication collective, schématisées dans la figure 1.6 sont les suivantes :

- Broadcast : Les mêmes données sont envoyées d'un nœud vers tous les autres nœuds du groupe.

- Scatter : Partitionne les données d'un nœud et envoie chaque portion vers un autre nœud.

- Gather : L'opposé de scatter, rassemble les données depuis différentes sources vers un seul nœud.

- AllGather : Envoie toutes les données de tous les nœuds vers tous les nœuds du groupe. À la fin de cette opération, tous les nœuds auront le même ensemble de données.

Figure 1.6 Communication collective dans MPI.

Tirée de (Kendall, 2016).

## 1.3 Appareils ARM

### 1.3.1 Historique

ARM est l'acronyme pour *Advanced RISC Machines* (Machines RISC Avancées) dont le projet a été lancé par Acorn Computers Ltd et le premier processeur ARM1 a vu le jour en 1985. Cette première version visait à offrir une faible latence et être économique afin de concurrencer le 6502 de MOS Technology(Levy et Promotions, 1990).

Le succès était tel, que Acorn a ouvert une nouvelle compagnie consacrée uniquement à ces nouveaux processeurs ARM Inc. Par la suite, en 1992, Apple a pu bénéficier de cette technologie en collaborant avec ARM pour le développement de ARM6 avec lequel ses agendas électroniques ont été équipés. C'est alors que la liste des fabricants ayant une licence ARM a commencé à s'élargir pour inclure Intel, LG, Marvell, Microsoft, Nvidia, Qualcomm, Samsung, Sharp, ST microelectronics, Symbios Logic, Texas Instruments, VLSI Technology, Yamaha, Zilabs(Levy et Promotions, 1990).

De nos jours, ARM est l'architecture la plus utilisée au monde avec 98% des Smartphones qui contiennent au moins un processeur ARM et 10 milliards de processeurs produits en 2013(Shilov, 2014).

### 1.3.2 Évolution de l'architecture ARM

Les objectifs derrière l'architecture ARM sont les suivants :

- Optimiser le rapport performance/prix au lieu d'essayer de concurrencer les microprocesseurs présents sur le marché en terme de performance pure. En effet, contrairement à l'architecture CISC, RISC a besoin de moins de silicium tout en offrant une performance similaire à d'autres processeurs de la même gamme.

- Réduire le temps de conception en offrant une bibliothèque de cellules standard qui permet, à l'aide d'un logiciel appelé QuickDesign de concevoir des processeurs personnalisés grâce à des macros. Les microprocesseurs ARM supportent l'architecture 32-bit (ARMv7) et 64-bit (ARMv8).

- Réduire la consommation d'énergie. Ceci est d'ailleurs l'avantage principal des processeurs ARM et son argument de vente le plus important. Ceci est rendu possible grâce au jeu d'instructions simplifié de l'architecture RISC (qui nécessite notamment moins de transistors).

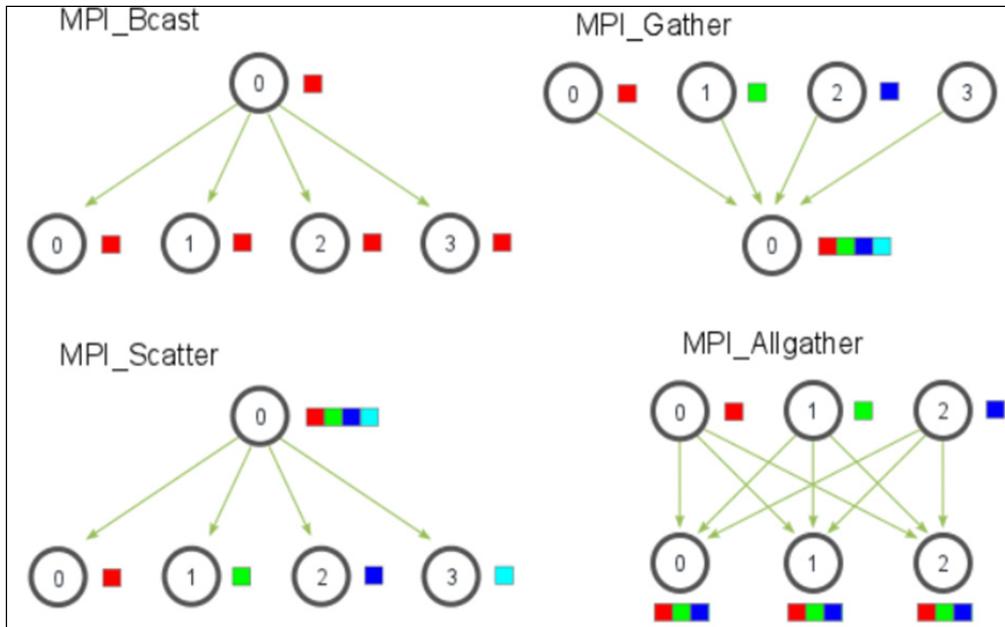

ARM a commencé par fournir des processeurs exclusivement 32 bits avec le cortex A15 (voire figure 1.7) comme sa version la plus rapide. Par la suite, la compagnie s'est lancée dans l'architecture 64-bit avec le cortex A53 et le cortex A57 (figure 1.8). Cet intérêt pour le 64 bit s'est manifesté du fait du développement des appareils mobiles et de l'émergence de nouvelles technologies telles que la reconnaissance vocale, les jeux 3D avec un rendu de plus en plus réaliste et un affichage haute résolution. Ces avancées ont vite poussé l'architecture 32 bit à ses limites d'où la nécessité de passer au 64 bit(arm, 2015a).

Figure 1.7 Architecture Cortex A15.

Tirée de(arm, 2015b).

En passant au 64 bit, ARM a fait en sorte que ses nouveaux processeurs soient capables d'exécuter aussi bien des applications 32 bit que des applications 64 bit. Dans le cas des appareils tournant sous android par exemple, il suffit que le noyau soit adapté pour du 64 bit pour que le reste (les bibliothèques, les applications...) soit du 32 bit ou du 64 bit. Toutefois, le passage du 32 bit au 64 bit ne veut pas dire une plus haute consommation d'énergie. Comme cité plus haut, l'un des objectifs principaux de l'architecture ARM est l'économie d'énergie. En effet, dans certains cas, un processeur 64 bits pourrait s'avérer plus économique qu'un 32 bit puisqu'il est plus rapide et met moins de temps à réaliser les calculs.

Figure 1.8 Architecture Cortex A57.

Tirée de (arm, 2015b).

Malgré le fait que le Cortex-A15 soit l'architecture ARM la plus rapide, elle est relativement récente et n'est pas encore largement utilisée comparée au Coretx-A9. Ce dernier a été introduit depuis 2008 et équipe la majorité des Smartphones, tablettes et systèmes embarqués. Sa caractéristique principale est son ratio performance/énergie qui est élevé par rapport aux autres architectures (arm, 2015b). La figure 1.9 montre l'architecture Cortex-A9.

Figure 1.9 Architecture Cortex A9

Tirée de (arm, 2015b).

## 1.4 Virtualisation

La virtualisation est une technologie qui a attiré de plus en plus de professionnels et de chercheurs dans le monde de la technologie de l'information. Les avantages apportés par cette technologie sont si nombreux qu'elle suscite un intérêt de plus en plus grandissant cette dernière décennie. En effet, parmi les raisons qui ont suscité cet intérêt, on peut citer des facteurs comme l'économie des ressources, l'économie d'énergie et l'augmentation de la compétition(Marshall, 2016).

La virtualisation est donc utilisée par les entreprises afin de réduire le coût d'éventuels centres de données, diminuer la consommation d'énergie ainsi que l'espace nécessaire pour le déploiement du matériel physique. De plus, cette technologie permet d'assurer une haute disponibilité pour les applications jugées critiques. Ceci simplifie les opérations telles que la migration et le déploiement des applications(Burger, 2012).

### 1.4.1 Définition

La virtualisation consiste à exécuter sur un seul ordinateur physique, un ou plusieurs systèmes d'exploitation comme un (des) simple(s) logiciel(s), séparément les uns des autres. Chaque machine virtuelle (système d'exploitation) partageant les ressources de cet ordinateur physique dans plusieurs environnements. La virtualisation peut être effectuée sur plusieurs types d'entités tels que les ordinateurs de bureau, les unités de stockage et les serveurs.

Afin d'accomplir la virtualisation, plusieurs méthodes sont disponibles. Même s'ils ont pour but ultime la virtualisation, ces derniers se différencient par leur approche et leur architecture, ainsi que par le matériel qu'ils visent à virtualiser. Dans ce qui suit, nous présentons les différents types de virtualisation(Vmware, 2016).

### 1.4.2 Types de virtualisation

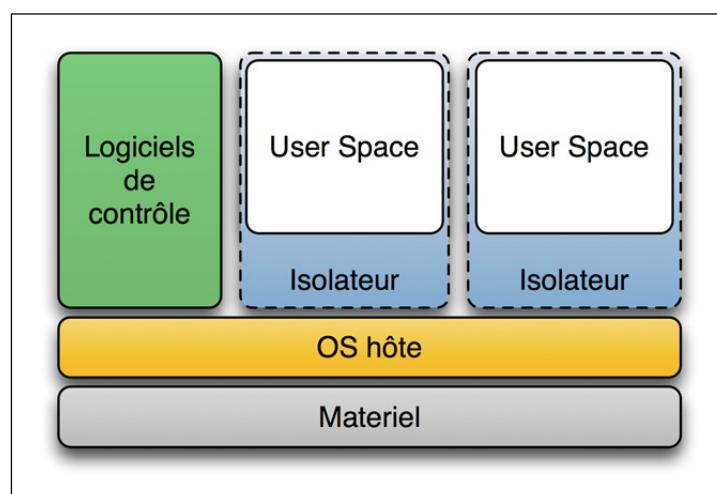

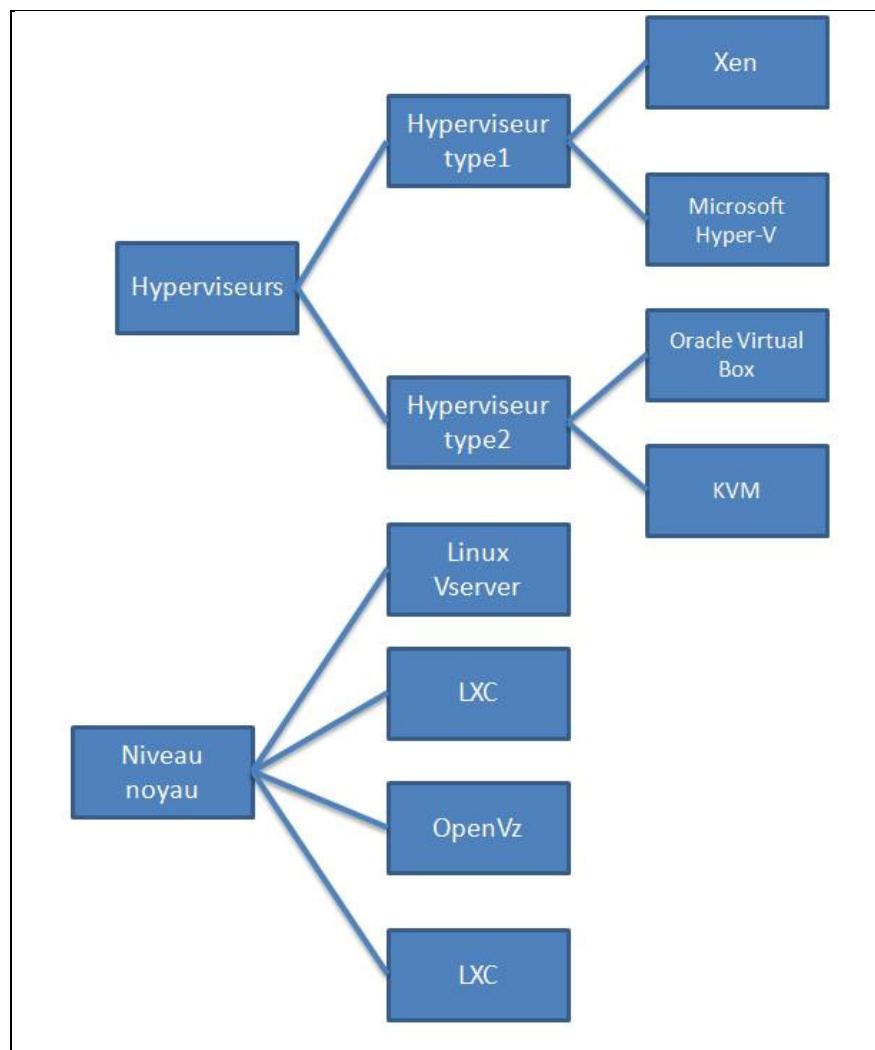

Nous distinguons trois importantes techniques de virtualisation : la virtualisation au niveau du noyau, la virtualisation par hyperviseur de type 1 et la virtualisation par hyperviseur de type 2(Redhat, 2016).

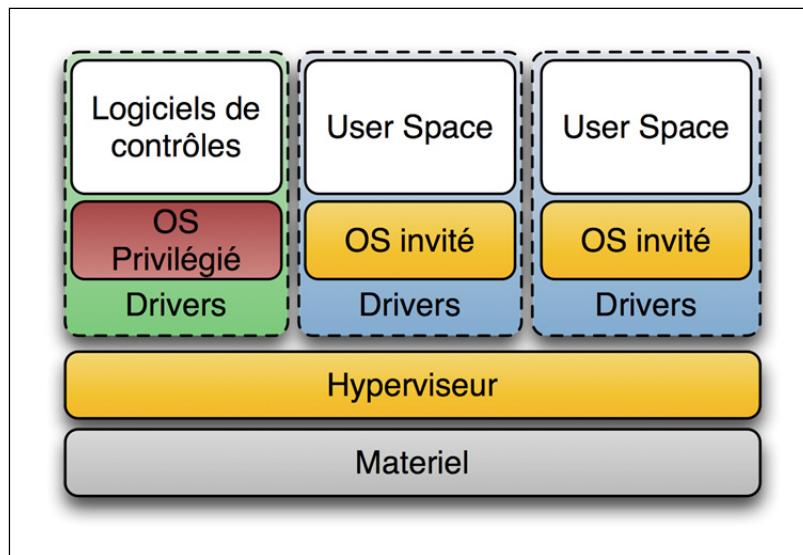

#### 1.4.2.1 Virtualisation par hyperviseur de type 1

Les hyperviseurs de type 1 s'exécutent directement au-dessus du matériel pour gérer les systèmes d'exploitation virtuels. En raison de cela, cet hyperviseur est aussi appelé natif. Il consiste en un noyau hôte allégé et optimisé sur lequel peuvent s'exécuter des systèmes d'exploitations "invités". Ces derniers peuvent être "conscients" du fait qu'ils sont virtuels et ils feront des appels directement à l'hyperviseur pour accéder au matériel, une telle technique s'appelle paravirtualisation. Des exemples d'hyperviseur de type 1 sont : Xen, Microsoft Hyper-V, VMware ESXi.

Figure 1.10 Hyperviseur de type 1.

Tirée de (Securityguy, 2014).

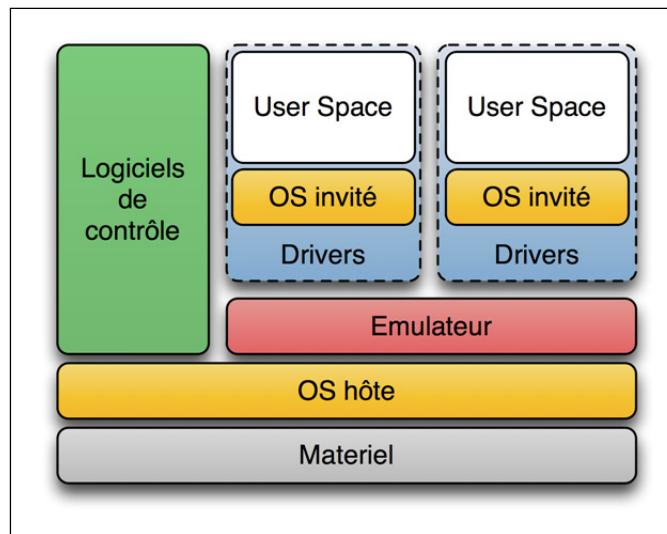

#### 1.4.2.2 Virtualisation par hyperviseur de type 2

Les hyperviseurs de type 2 quant à eux s'exécutent comme un processus au sein d'un système d'exploitation hôte. Ils constituent une couche d'abstraction au-dessus de ce dernier. À la différence de la paravirtualisation, les systèmes invités n'ont pas conscience d'être virtuels et croient communiquer directement avec le matériel. Des exemples d'hyperviseurs de type 2 sont VMWare Player, Oracle VirtualBox et KVM.

Figure 1.11 Hyperviseur de type 2.

Tirée de (Securityguy, 2014).

#### 1.4.2.3 Virtualisation au niveau de noyau

La virtualisation au niveau noyau du système d'exploitation aussi appelée virtualisation par isolation est une technique permettant de partitionner le système d'exploitation en plusieurs domaines. Cette technique repose surtout sur l'usage des Cgroups qu'offre le noyau Linux.

Figure 1.12 Virtualisation niveau noyau.

Tirée de (Securityguy, 2014).

La principale différence avec les autres techniques de virtualisation est qu'elle ne permet de virtualiser qu'un seul type de OS à la fois. Ceci est dû au fait que les différentes instances partagent le même noyau. Cependant, cet inconvénient est comblé par le fait que le coût supplémentaire (overhead) relatif au fait que chaque système virtualisé exécute tout un système d'exploitation est absent. En effet, un seul système d'exploitation s'occupe des appels destinés au matériel.

La figure 1.12 présente les différents types de virtualisation et leurs différentes implémentations. Nous nous intéresserons dans ce travail à la technologie de virtualisation dite la plus légère, à savoir la virtualisation au niveau noyau.

Figure 1.13 Techniques et logiciels de virtualisation.

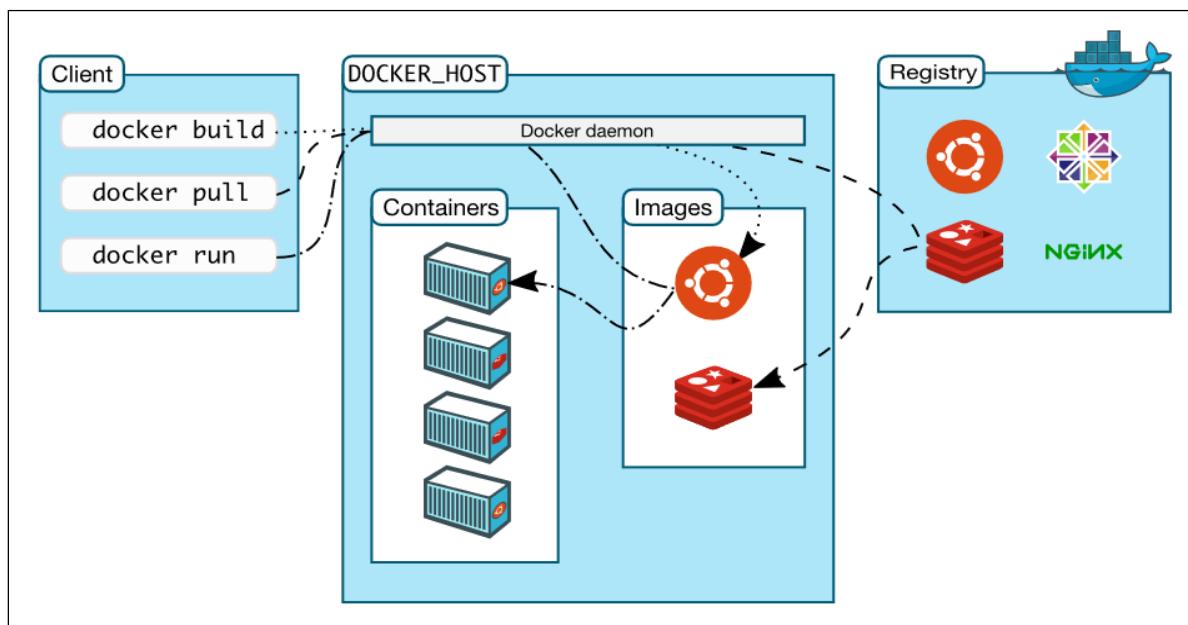

#### 1.4.3 Docker

Nous avons vu dans la partie précédente les différentes techniques de virtualisation, celles nécessitant un hyperviseur et celle au niveau du noyau qui s'appelle aussi isolation. Nous nous intéressons à cette dernière puisqu'elle offre le moins de coût supplémentaire comparée aux autres techniques (Morabito et al., 2015).

La technique de virtualisation au niveau du noyau a été introduite par les containers Linux qui elle-même se base sur le concept des espaces de nommage au niveau du noyau.

#### 1.4.3.1 Espace de nommage

La fonctionnalité espace de nommage au niveau du noyau a été introduite dans les distributions Linux depuis la version 2.6.24 (RIDWAN, 2015). Cette dernière permet d'isoler un processus (ou un ensemble de processus) en donnant à chacun une différente vue du système. Il existe six implémentations de cet espace de nommage(Biederman, 2006):

- Espace de nommage pid : Permet de séparer les processus en différentes vues. Les processus appartenant à un même espace de nommage ne peuvent pas voir ou interagir avec des processus hors de cet espace.

- Espace de nommage réseau : L'utilité de cet espace est de pouvoir multiplexer l'interface réseau physique entre plusieurs processus. Les processus de différents espaces de nommage verront des interfaces réseau différentes.

- Espace de nommage de montage: Le système Linux possède une structure de données dans laquelle il stocke les différentes partitions du disque qui sont montées, l'endroit où ils ont été montés et d'autres informations comme les permissions... l'espace de nommage de montage permet de cloner cette structure pour chaque espace de nommage de façon à ce qu'un processus appartenant à un certain espace de nommage puisse modifier sa propre copie sans affecter la structure de montage des autres processus du système.

- Espace de nommage utilisateur: Cet espace de nommage permet de donner à un utilisateur les priviléges root au sein de son espace de nommage sans lui donner la possibilité d'interagir avec les processus hors de son espace de nommage.

- Espace de nommage IPC: Cet espace de nommage permet d'isoler un processus en lui donnant ses propres ressources d'intercommunication (messages POSIX ou system V IPC)

- Espace de nommage UTS: cet espace de nommage permet à un processus d'avoir sa propre copie du nom d'hôte et du nom de domaine NIS de façon à pouvoir les changer sans affecter le reste du système.

En prenant avantage du fonctionnement de ces différents espaces de nommage, il est possible de séparer les processus ainsi que les ressources du système en des groupes plus ou moins isolés appelés containers. C'est le principe de la virtualisation avec Linux containers.

#### 1.4.3.2 Architecture de Docker

Docker est une implémentation de l'isolation par containers offerte par le noyau Linux. Les concepteurs de Docker présentent ce dernier comme une plateforme pour les développeurs et les administrateurs système afin de développer, envoyer et exécuter leurs applications (Docker, 2016).

Figure 1.14 Architecture Docker.

Tirée de(Docker, 2016).

Le fonctionnement de docker repose sur la notion d'image et de containers. L'idée est que pour développer une application, le programmeur n'a pas besoin de toutes les fonctionnalités de son système d'exploitation, mais seulement de quelques librairies, API... Une image est donc une version très réduite d'un système d'exploitation ne contenant que l'application et l'environnement nécessaire à son exécution. Cette image peut ensuite être lancée dans un

container isolé. Plusieurs containers de la même image peuvent être lancés simultanément. La figure 1.13 montre l'architecture de docker.

Docker est composé de trois modules, à savoir le registre qui héberge les différentes images, un daemon qui tourne sur l'hôte et qui gère la création des containers à partir des images et enfin le client à travers duquel on communique avec le daemon pour lui indiquer de lancer, stopper, interrompre des containers.

L'une des raisons qui motive notre choix de déployer Docker et le tester sur les cartes ARM est sa facilité de déploiement comme le démontre son architecture.

## 1.5 Conclusion

Dans ce chapitre, nous avons abordé les différentes notions essentielles à la compréhension de ce travail. Nous avons abordé l'informatique de haute performance et la notion du cluster puisqu'une importante partie de ce projet tournera autour de ce concept. Nous avons aussi abordé l'architecture ARM ainsi que le principe de virtualisation, les différentes techniques de virtualisation et docker comme implémentation d'une de ces techniques.

Dans ce qui suit, nous présenterons la revue de littérature relative à la virtualisation des appareils ARM ainsi que les outils utilisés pour implémenter le passage de messages au sein d'un cluster.

## **CHAPITRE 2**

### **REVUE DE LITTÉRATURE**

#### **2.1 Introduction**

Nous présentons dans ce chapitre la revue de littérature relative à notre travail. Entre autres, nous visons dans ce projet à tester les performances des ordinateurs mono-cartes ARM en mettant en place un cluster Beowulf. Pour cela, nous abordons dans un premier temps les études qui ont été faites sur les clusters Beowulf et notamment ceux basés sur les appareils ARM afin de situer le cadre de notre contribution. De plus, nous décidons du meilleur outil en terme de passage de messages en testant les deux principales plateformes utilisées, ainsi nous citons les travaux qui ont visé à comparer PVM et MPI. Aussi, nous mentionnons les études ayant été faites sur le déchargement des traitements de sécurité dans le cas des systèmes à ressources limitées. De plus, nous présentons des techniques d'équilibrage de la charge mentionnées dans la littérature.

Notre seconde contribution consistant à appliquer la virtualisation sur les appareils ARM, nous abordons ensuite les études qui ont comparé les différentes technologies de virtualisation.

#### **2.2 Cluster Beowulf**

Depuis le premier cluster Beowulf réalisé en 1994 par la NASA (Merkey, 2015), le domaine du HPC est devenu de plus en plus accessible au grand public. En effet, l'idée est que tout particulier peut avoir accès à une puissance de calcul plus ou moins importante en alliant plusieurs des équipements qui ne coûtent pas très cher.

##### **2.2.1 Usage des clusters Beowulf**

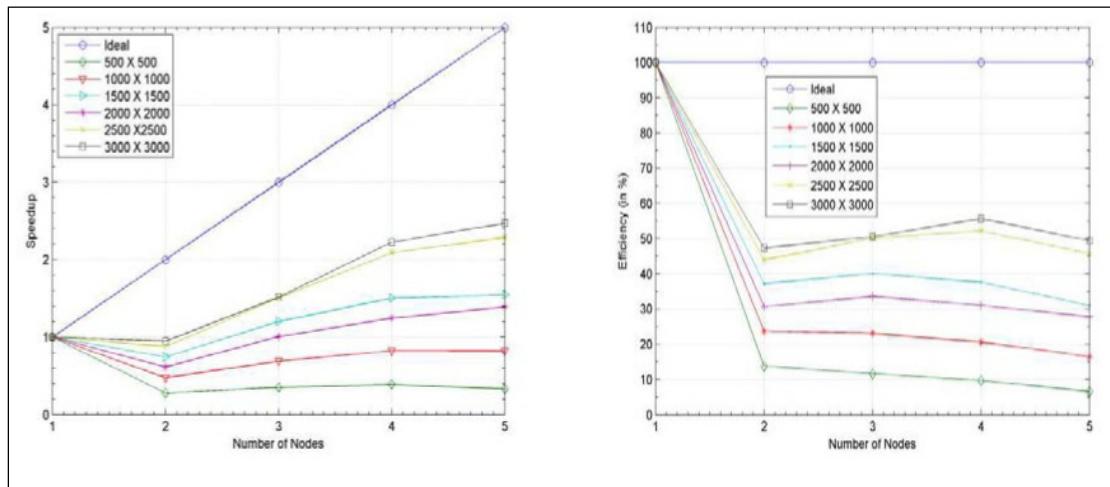

Plusieurs exemples existent dans la littérature qui décrivent l'utilité des clusters Beowulf, (Datti, Umar et Galadanci, 2015) ont construit un cluster à but éducatif. En effet, les

universités n'ont généralement pas les moyens de s'offrir un supercalculateur et le cluster Beowulf de (Datti, Umar et Galadanci, 2015) permet aux étudiants de s'initier aux HPC. Ce dernier délivre des performances satisfaisantes selon les auteurs qui testent dans un premier des multiplications de matrices et dans un second temps exécutent un algorithme qui trouve les nombres premiers dans un intervalle donné. Le cluster est composé de 5 nœuds et les résultats montre une augmentation maximale de 2,472 fois par rapport à l'exécution sur un seul nœud (séquentiel) pour la multiplication de matrice et de 2,459 pour la recherche des nombres premiers. La figure 2.1 montre l'accélération ainsi que l'efficacité dans le temps d'exécution de la multiplication de matrice selon le nombre de nœuds du cluster.

Figure 2.1 Accélération et efficacité de la multiplication des matrices selon le nombre de nœuds et la taille des matrices.

Tirée de (Datti, Umar et Galadanci, 2015)

Bien que le cluster cité ci-dessus soit limité par le nombre de nœuds, il donne un bon exemple de l'accessibilité de l'informatique haute performance, puisque le matériel utilisé est constitué d'ordinateurs déjà disponibles dans l'université et les logiciels utilisés sont libres.

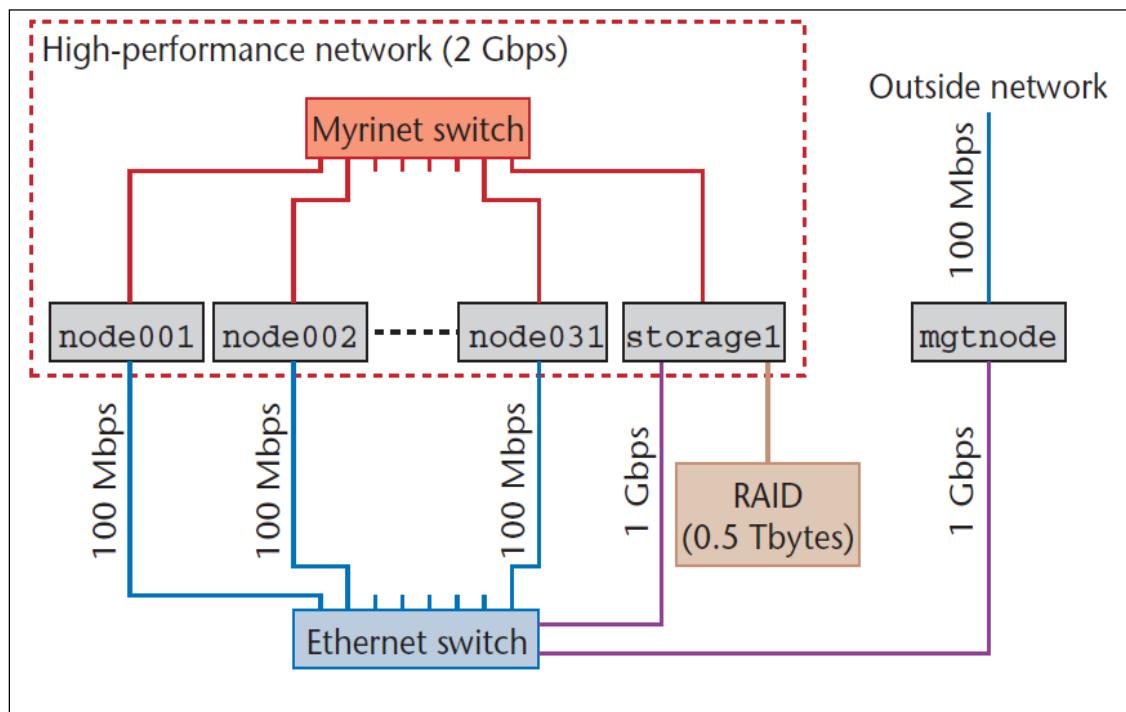

L'exemple suivant, un cluster Beowulf plus performant a été mis en place. (Matthias, 2005) ont mis en place un cluster Beowulf avec 64 processeurs (interconnexion de 32 doubles processeurs) et utilisent un lien Myrinet pour l'interconnexion. Ce dernier est beaucoup plus rapide que les liens Ethernet traditionnels avec un débit de 2 Gbps. De plus, un disque dur

externe RAID (grande vitesse) est relié à l'un des nœuds à travers un lien de 1 Gbps. Un autre nœud sert d'interface d'utilisation et de gestion du cluster et est connecté à ce dernier à travers un lien de 1 Gbps. La figure 2.2 montre l'architecture du cluster de (Matthias, 2005).

Figure 2.2 Architecture d'un cluster Beowulf.

Tirée de (Matthias, 2005).

Les auteurs ont proposé de résoudre des équations différentielles à l'aide de leur cluster Beowulf, bien que l'article se concentre sur les méthodes utilisées pour optimiser l'algorithme de calcul parallèle, il présente les résultats de l'accélération du temps d'exécution selon les différentes grandeurs du problème. Le temps d'exécution est réduit d'un facteur maximum de 30 par rapport à une exécution séquentielle.

Bien que les auteurs présentent leur cluster comme étant Beowulf, le matériel utilisé n'est pas à la portée de tous les budgets, en effet l'interconnexion se fait à travers un lien Gigabit qui est relativement cher. Le coût reste tout de même négligeable devant celui d'un supercalculateur.

Dans ce qui suit, nous présentons les cluster Beowulf composés de nœuds ayant des processeurs ARM.

## **2.2.2 Cluster ARM**

Dans la littérature nous pouvons trouver deux exemples pertinents de l'utilisation des appareils ARM dans la construction d'un cluster : Le premier type est le cluster destiné au traitement de grands fichiers de données, ce qu'on appelle Big Data, le second type est un cluster sur lequel les applications suivantes ont été déployées : serveur web, transcodage vidéo et une base de données en mémoire. Bien que ces deux types de cluster puissent sembler similaires à première vue, il n'en est rien. Leur point en commun est de rassembler la puissance de plusieurs appareils ARM afin d'accomplir des tâches conséquentes. Cependant, la différence fondamentale est que le traitement de larges fichiers de données implique des ressources et des approches différentes que le traitement de trois applications du second cluster. Dans ce qui suit, nous présentons les études qui se sont intéressées à ces deux types de cluster.

### **2.2.2.1 Cluster Bigdata**

L'étude de (Kaewkasi et Srisuruk, 2014) s'est intéressée à la possibilité de l'utilisation des appareils ARM dans le contexte du BigData. Leur motivation est que les serveurs traditionnels des centres de données sont gourmands en énergie et qu'ils nécessitent de plus des systèmes de refroidissement coûteux.

De ce fait, une entreprise de petite ou moyenne taille ne peut se permettre d'installer et de maintenir un tel matériel localement et se voit contrainte de recourir aux services du cloud où, d'après (Kaewkasi et Srisuruk, 2014) les menaces de sécurité sont importantes. Les auteurs démontrent qu'une entreprise de petite taille peut mettre en place son propre centre de donnée et avoir une meilleure sécurité puisqu'elle a accès à tout le matériel qu'elle utilise, qui n'est pas le cas pour les services cloud.

L'application choisie pour tourner sur le cluster est Hadoop qui est une plateforme servant à traiter les données structurées et semi-structurées. La spécificité de Hadoop est qu'il utilise le patron d'architecture MapReduce et système de fichiers HDFS (*Hadoop Distributed File System*) inspirés des deux publications de Google (Chang et al., 2008) et (Dean et Ghemawat, 2008). Cette plateforme présentant de bonnes performances dans le traitement de larges fichiers de données, elle est très répandue dans le domaine du cloud.

L'équipement utilisé par (Kaewkasi et Srisuruk, 2014)est constitué de 22 ordinateurs monocartes ARM équipés chacun d'un processeur cortex-A8 à 1 GHz de fréquence et 1GB de mémoire RAM. Chaque nœud est connecté à un disque dur de 60GB. De plus, 5 sources de courants sont utilisées pour alimenter les nœuds.

Étant donné que Hadoop est écrit en langage Java, son fonctionnement dépend des paramètres de la machine virtuelle Java JVM. Puisque Hadoop a été pensé pour tourner sur des serveurs possédant de grandes capacités, ses paramètres par défaut ne sont pas adaptés pour bien fonctionner sur les processeurs ARM. Dans leur article, (Kaewkasi et Srisuruk, 2014)expliquent la démarche suivie pour modifier les paramètres par défaut du JDK afin d'adapter le fonctionnement de hadoop dans un environnement ARM.

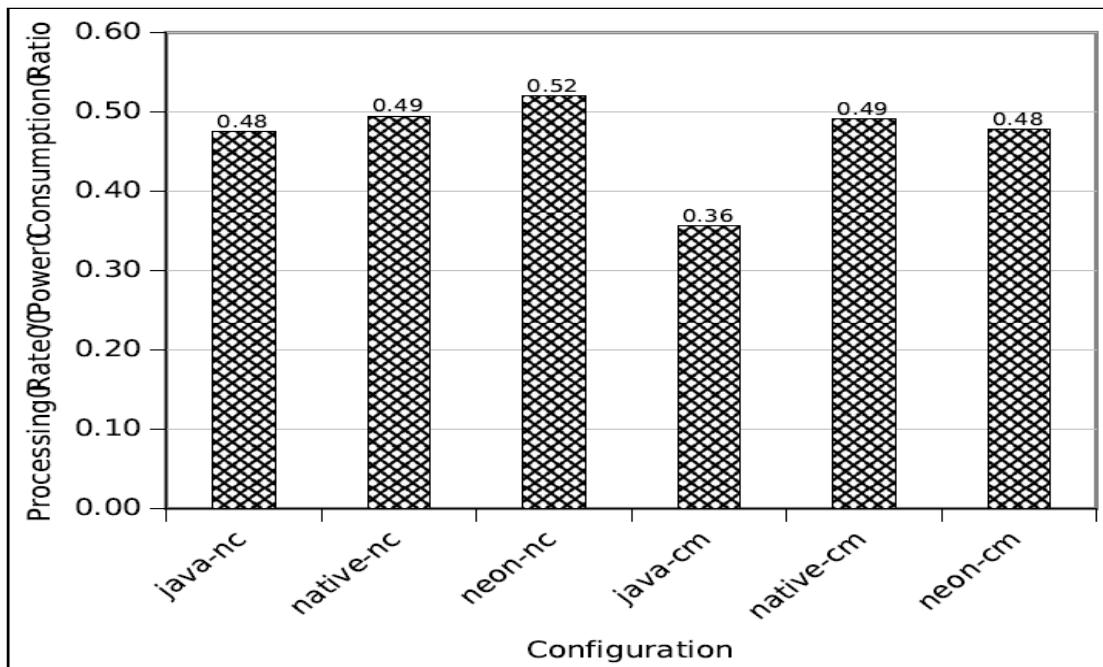

En se basant sur les modifications apportées aux paramètres par défaut du JDK , les auteurs présentent les résultats obtenus en utilisant les différentes configurations qui sont au nombre de six pour en choisir la meilleure en terme de performance et en terme de consommation d'énergie. Parmi les configurations, les auteurs proposent de changer une partie de Hadoop et de la remplacer par une bibliothèque C qui aurait pour effet d'utiliser les instructions des processeurs ARM lors de la compression des données.

Figure 2.3 Ratio performance/énergie du cluster ARM selon différentes configurations.

Tirée de(Kaewkasi et Srisuruk, 2014).

Afin de déterminer la meilleure configuration, les auteurs calculent le ratio performance/énergie comme le montre la figure 2.3 et concluent que l'utilisation des instructions Neon du processeur ARM donnait le meilleur ratio.

Les auteurs concluent que gérer des traitements de Big Data à l'aide des systèmes ARM peut être faisable, mais qu'il faut apporter de grandes modifications.

Il est à noter que notre travail dans ce mémoire vient compléter le travail présenté dans (Kaewkasi et Srisuruk, 2014) puisque nous abordons une autre particularité utilisée dans les centres de données qui est la virtualisation.

#### **2.2.2.2 Mesure du rapport coût/efficacité d'un cluster ARM**

Dans (Ou et al., 2012), les auteurs se proposent de comparer un cluster composé d'ordinateurs mono-cartes ARM avec une station de travail Intel x86. La motivation derrière

leur travail est que l'utilisation des machines traditionnelles dans les centres de données en tant que serveurs est de plus en plus répandue ces dernières années (Barroso, Clidaras et Hoelzle, 2013), cependant ces machines n'étant pas été créée avec l'idée d'économiser l'énergie, leur consommation de courant devient problématique.

C'est dans l'optique de trouver une solution au problème de consommation d'énergie que(Barroso, Clidaras et Hoelzle, 2013)s'intéressent aux systèmes embarqués ARM, en comparant leur ratio de coût/efficacité et énergie/efficacité avec un ordinateur traditionnel.

Le cluster ARM est composé de 4 cartes PandaBoard avec chacune un processeur ARM cortex-A9 à 1 Ghz, 1 GB de RAM et une carte SD de 16 GB. La station de travail Intel x86 possède un processeur intel core2 Q9400 avec 2.66 Ghz de fréquence, 8 GB de RAM et un disque dur de 250 GB.

Les auteurs définissent le ratio énergie/performance de la façon suivante :

$$EE = \frac{Work}{Energy} = \frac{Work}{Power * Time} = \frac{Performance}{Power}$$

Figure 2.4 Calcul du ratio énergie/performance.

Tirée de (Ou et al., 2012).

En effectuant les benchmarks sur les trois applications déployées, les auteurs concluent que l'efficacité énergétique du cluster ARM est supérieure à celle de la station de travail Intel dans les trois cas étudiés. Aussi, le modèle de consommation d'énergie des appareils ARM peut être considéré linéaire à l'utilisation de la CPU, alors que celui d'Intel ne l'est pas.

En ce qui concerne le ratio coût/performance, les auteurs ont utilisé le modèle de (Hamilton, 2009)afin d'évaluer le coût de construction d'un centre de données avec des appareils ARM et un autre avec des stations de travail Intel. Leurs estimations prévoient un ratio en faveur du centre de données avec des appareils ARM lorsque les tâches à traiter sont légères, mais cet avantage est perdu au fur et à mesure que les tâches sont lourdes et demandent beaucoup de capacités de calcul.

L'étude de (Ou et al., 2012) est intéressante du fait qu'elle traite de la faible consommation d'énergie des appareils ARM en comparaison avec les ordinateurs possédant l'architecture Intel. Cependant, les auteurs ont diversifié les applications testées sans pour autant diversifier les cartes ARM sur lesquels elles ont été déployées. En effet, les ordinateurs mono-cartes ARM ne sont pas tous conçus dans le même but, par exemple, les cartes PandaBoard ne sont pas optimisées pour l'encodage vidéo alors que des cartes telles que la Parallelia, du fait que son coprocesseur est mieux adapté à ce genre de calcul.

## 2.3 MPI vs PVM

Nous avons introduit dans le chapitre précédent les deux principaux environnements servant à déployer des systèmes parallèles, à savoir PVM et MPI. Ces deux outils ont des approches plus ou moins différentes pour collecter la puissance de calcul de plusieurs processeurs et les utiliser de façon parallèle. En effet, PVM est une machine virtuelle alors que MPI est une librairie standard de passage de messages. Les différences ne s'arrêtent pas là et quelques études se sont intéressées à la comparaison entre PVM et MPI et JAVA.

### 2.3.1 Différences entre les deux approches

Avec le regain de popularité de la programmation parallèle, les utilisateurs de cette technologie se sont vu offrir le choix entre PVM et MPI, (Sunderam et al., 2001) se sont intéressés aux points communs et aux différences entre les deux outils. (Sunderam et al., 2001) ont aussi effectué une comparaison entre PVM, MPI, mais aussi JAVA, cette étude est plutôt superficielle et n'est pas allée en profondeur pour discuter de l'architecture de ces approches. Les chercheurs ont mis d'un côté PVM et MPI et de l'autre JAVA en présentant les principes généraux de programmation avec ces outils ainsi que les différentes fonctions pour envoyer et recevoir des messages.

| PVM:                                               | MPI:                                              |

|----------------------------------------------------|---------------------------------------------------|

| <i>Start:</i> int pvm_mytid();                     | <i>Start:</i> MPI_Init();                         |

| <i>Send:</i> pvm_initsend(int encoding);           | <i>Send:</i> MPI_Send(void *message, int size,    |

| pvm_pk...(datatype *ptr, int size, int stride);    | MPI_Datatype datatype, int destination, int tag,  |

| pvm_send(int task_id, int msgtag);                 | MPI_Comm communicator);                           |

| <i>Receive:</i> pvm_recv(int task_id, int msgtag); | <i>Receive:</i> MPI_Recv(void *message, int size, |

| pvm_upk...(datatype *ptr, int size, int stride);   | MPI_Datatype datatype, int source, int tag,       |

| <i>Shut down:</i> pvm_kill(int task_id);           | MPI_Comm communicator, MPI_Status status);        |

| pvm_exit();                                        | <i>Shut down:</i> MPI_Finalize();                 |

Figure 2.5 processus d'envoi et de réception de données standard de PVM et MPI.

Tirée de (Sunderam et al., 2001).

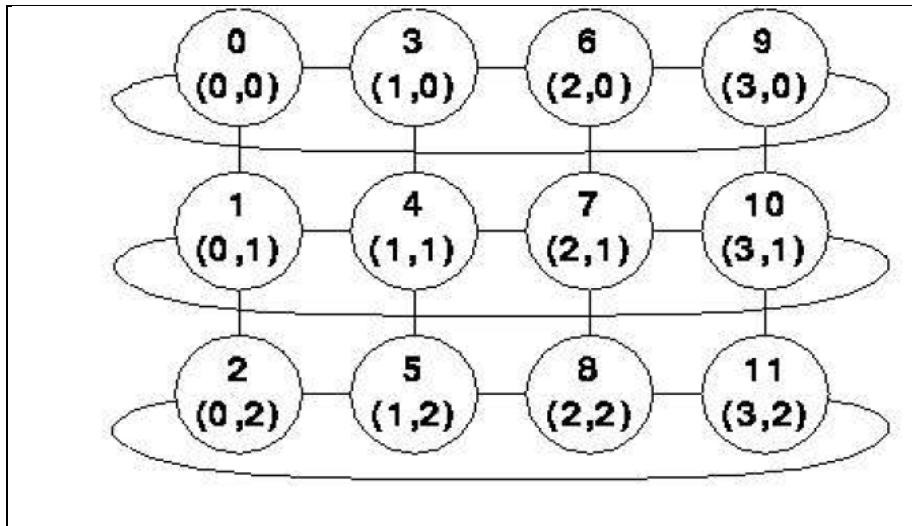

La figure 2.5 montre que la séquence de code pour initialiser l'environnement, envoyer et recevoir les données est à peu près la même pour PVM et MPI. Ils en concluent donc que ces deux approches sont similaires du point de vue de l'écriture des programmes. Par contre, (Sunderam et al., 2001) affirment que JAVA est différent puisque la programmation parallèle à l'aide de ce dernier est réalisée grâce aux RMI (l'appel distant aux méthodes) et au threading de ce langage. Cependant, une version de MPI a été adaptée pour JAVA et (Baker, Grove et Shafi, 2006) le comparent à MPI de point de vue performance et portabilité. Nous allons aborder ceci dans la partie suivante.