# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

## THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

BY Sabeur LAFI

A NEW HARDWARE ABSTRACTION-BASED RADIOFREQUENCY DESIGN METHODOLOGY: FOUNDATIONS AND CASE STUDIES

MONTREAL, NOVEMBER 15, 2016

© Copyright Sabeur Lafi, 2016 All rights reserved

# © Copyright Reproduction, saving or sharing of the content of this document, in whole or in part, is prohibited. A reader who wishes to print this document or save it on any medium must first obtain the author's permission.

### **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Ammar Kouki, Thesis Supervisor Département de Génie Électrique at École de technologie supérieure

Mr. Jean Belzile, Thesis Co-supervisor Département de Génie Électrique at École de technologie supérieure

Mr. Roger Champagne, Chair, Board of Examiners Département de Génie Logiciel at École de technologie supérieure

Mr. Claude Thibeault, Member of the jury Département de Génie Électrique at École de technologie supérieure

Mr. Roni Khazaka, External Evaluator Electrical and Computer Engineering Department at McGill University

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

SEPTEMBER 16, 2016

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

### **ACKNOWLEDGMENTS**

First and foremost, I would like to express my sincerest and deepest gratitude to my supervisor Prof. Ammar Kouki for his continuous and generous support of my PhD studies and research. I immensely appreciate his understanding, motivation and patience as well as his efforts for providing me with the required resources and an excellent atmosphere for doing my research. I also acknowledge his vast expertise, and immense knowledge, which added considerably to my graduate experience. His valuable guidance and advices helped me in all my research activities and throughout the writing process of this thesis.

Besides my advisor, I would like to thank my co-supervisor Prof. Jean Belzile for his constant encouragement, insightful guidance, and continuous support all over my graduate studies and research. I particularly appreciate his significant contribution to this research work and his focused comments that enhanced the quality of my text.

I extend my gratitude to the rest of my thesis committee: Prof. Roger Champagne, Prof. Claude Thibeault, and Prof. Roni Khazaka, for their encouragement, insightful comments, and kind acceptance to evaluate my PhD work.

My sincere thanks goes also to Mr. Frank Ditore, Mr. Rulon Vandyke, and all the Alpharetta-based team of Keysight Technologies Inc., for offering me an extended summer internship in 2012 and leading my work on diverse exciting projects.

I also acknowledge the generous financial support of LACIME (Laboratoire de Communications et d'Intégration de la Microélectronique), the BREM (Bureau du Recrutement Étudiant et de la Mobilité de l'ÉTS), and CREER (Centre de Recherche En Électronique Radiofréquence) in conjunction with FQRNT (Fonds de Recherche du Québec – Nature et Technologies).

Last but not the least, I thank all my fellow labmates at LACIME and in particular, Ahmed Elzayet, for his valuable comments and remarks. I am also grateful to LACIME staff for providing an excellent work atmosphere.

Finally, I would like to thank my parents and family for their faithful encouragement, unceasing support and best wishes and in particular, I must acknowledge the role of my wife and best friend, Fatma, without whose love, devotion and understanding, I would not have finished this thesis.

# NOUVELLE MÉTHODOLOGIE BASÉE SUR L'ABSTRACTION MATÉRIELLE POUR LA CONCEPTION RADIOFRÉQUENCE: BASES ET ÉTUDES DE CAS

Sabeur LAFI

### RÉSUMÉ

Les dispositifs de communication sans fils connaissent une croissance soutenue due au succès et à la popularité des téléphones portables auprès du grand public. De plus, l'émergence d'applications et services mobiles semble accroître les attentes du consommateur concernant les performances et les fonctionnalités des prochaines générations d'appareils sans fils. En outre, la multitude des normes de télécommunications, l'encombrement du spectre électromagnétique et les interférences complexifient la conception des systèmes radios. Pour réduire cette complexité, des avancées ont été enregistrées au niveau des technologies, des outils et des processus de conception de la partie numérique de la radio. Toutefois, bien que plusieurs technologies prometteuses soient en cours de mise au point au niveau de la partie radiofréquence, les améliorations des approches de conception et des outils qui y sont associés reçoivent beaucoup moins d'attention. Ce travail vise à pallier à ce déficit en s'attaquant particulièrement aux problématiques de productivité et de collaboration entre concepteurs des systèmes radiofréquences ainsi qu'à l'automatisation des tâches de conception.

Pour atteindre cet objectif, nous cherchons à explorer une approche de conception réduisant la dépendance aux détails physiques et élevant le niveau d'abstraction de manière à découpler la fonctionnalité à concevoir de la technologie d'implémentation. De ce fait, nous proposons dans cette thèse une nouvelle approche de conception des circuits et systèmes radiofréquences se basant sur l'abstraction matérielle. Dans un premier lieu, nous présentons une revue critique des approches actuelles. Ensuite, nous détaillons les concepts de l'approche proposée, notamment son cycle de conception, la stratégie d'abstraction matérielle qui lui est associée et la matrice Q. Puis, nous finissons ce travail par des études de cas où nous essayons de valider les concepts susmentionnées.

**Mots-clés:** méthodologie de conception radiofréquence, abstraction matérielle, matrice Q, modélisation en SysML, vérification de cohérence, transformation de modèles

### A NEW HARDWARE ABSTRACTION-BASED RADIOFREQUENCY DESIGN METHODOLOGY: FOUNDATIONS AND CASE STUDIES

Sabeur LAFI

### **ABSTRACT**

The need for radio systems is in growth due to the particular success of cellular and wireless devices. On the one hand, the emergence of new applications and services raises consumer expectations regarding future radio systems' performance. On the other hand, radio design is becoming more challenging due to multi-standard functionality, spectrum crowdedness and harsh operating environments. In order to keep pace with the emerging requirements, notable advances have taken place in digital design either in implementation technologies or in design approaches and tools. On the radiofrequency side, many promising technologies are being developed to enhance radio systems capability but little interest is dedicated to the improvement of design approaches and tools. To bridge this gap, several design challenges should be addressed especially in terms of productivity, design collaboration, automation and reuse as well as ensuring better technology insertion.

To tackle all these challenges, it is necessary to ameliorate the design approaches, overcome technology-dependence and raise the abstraction level in today's radiofrequency design practice in order to decouple the radio functionality from the underlying technology. In the light of this observation, we dedicate this thesis to the elaboration of a new radiofrequency design methodology based on hardware abstraction. Its first section investigates the limitations of current RF design tools and approaches. The following one presents an alternative framework that tackles the issues of automation, design collaboration and reuse. The proposed framework is based on a comprehensive abstraction strategy that combines intensive modeling activity and handful abstraction mechanisms to enable higher design automation and agility. The last section is dedicated to the validation of the proposed framework through selected case studies.

**Keywords:** RF design methodology, hardware abstraction, Q-matrix, functional description, SysML modeling, coherence verification, model-to-model transformation

# **TABLE OF CONTENTS**

|      |          |                                                             | Page  |

|------|----------|-------------------------------------------------------------|-------|

| INTI | RODUCTIO | ON                                                          | 1     |

| СНА  | PTER 1   | BACKGROUND                                                  | C     |

| 1.1  |          | etion                                                       |       |

| 1.2  |          | the Beginnings of Wireless and Mobile Communications        |       |

| 1.4  | 1.2.1    | -                                                           |       |

|      | 1.2.2    | 1                                                           |       |

| 1.3  |          | Frends in Wireless and Mobile Communications and Subsequent |       |

| 1.0  |          | on Technology and Design Approaches and Tools               | 17    |

|      | 1.3.1    | Trends in Wireless and Mobile Communications                |       |

|      | 1.3.2    | Impact on Technology and Design Approaches and Tools        |       |

| 1.4  | Challeng | ges in Wireless and Mobile Radio Design                     |       |

| 1.5  |          | sion                                                        |       |

|      |          |                                                             |       |

| CHA  | PTER 2   | COMPARATIVE STUDY OF COMMON DESIGN APPROAC                  | HES43 |

| 2.1  |          | ction                                                       |       |

| 2.2  | Commo    | n Design Approaches and Future Requirements in Design Tools |       |

|      | 2.2.1    | Common Design Approches                                     |       |

|      | 2.2.2    | Future Requirements in Design Tools                         |       |

| 2.3  |          | to be learned from Current Design Practice                  |       |

|      | 2.3.1    | Digital Design                                              |       |

|      | 2.3.2    | Analog and Mixed-Signal Design                              |       |

|      | 2.3.3    | RF and Microwave Design                                     |       |

| 2.4  |          | ative Study of Design Practice through Domains              |       |

| 2.5  | Conclus  | sion                                                        | 77    |

| СНА  | PTER 3   | THE PROPOSED FRAMEWORK FOR RF AND                           |       |

|      |          | MICROWAVE DESIGN                                            | 79    |

| 3.1  | Introduc | etion                                                       |       |

| 3.2  |          | nd Objectives                                               |       |

| 3.3  |          | l of a New Framework to Bridge Existing Design Gaps         |       |

|      | 3.3.1    | A Five-Step Design Scheme                                   |       |

|      | 3.3.2    | Functional Description                                      | 82    |

|      | 3.3.3    | Analysis                                                    | 90    |

|      | 3.3.4    | Synthesis                                                   |       |

|      | 3.3.5    | Q-matrix                                                    |       |

|      | 3.3.6    | Summary View of the Proposed Design Flow                    |       |

| 3.4  | Mapping  | g Framework Provisions to Designated Design Challenges      | 124   |

| 3 5  | Conclus  | ion                                                         | 127   |

| СНА  | PTER 4     | HARDWARE ABSTRACTION-BASED STRATEGY FOR                 | 100 |

|------|------------|---------------------------------------------------------|-----|

| 4.1  | Introduct  | RF AND MICROWAVE DESIGN                                 |     |

| 4.2  |            | e Abstraction in Various Domains                        |     |

| 4.2  | 4.2.1      | Definition and Advantages                               |     |

|      | 4.2.1      | Hardware Abstraction in Digital and Mixed-Signal Design |     |

|      | 4.2.2      | Hardware Abstraction in Computer Engineering            |     |

|      | 4.2.4      | Hardware Abstraction in Software Engineering            |     |

|      | 4.2.4      | Hardware Abstraction in Other Domains                   |     |

| 4.3  |            | I RF and Microwave Hardware Abstraction Strategy        |     |

| 4.3  | 4.3.1      | Scope and Objectives                                    |     |

|      | 4.3.1      | Basic Definitions                                       |     |

|      | 4.3.2      | Functional Description of RF and Microwave Systems:     | 101 |

|      | 4.3.3      | Black-Box Model                                         | 182 |

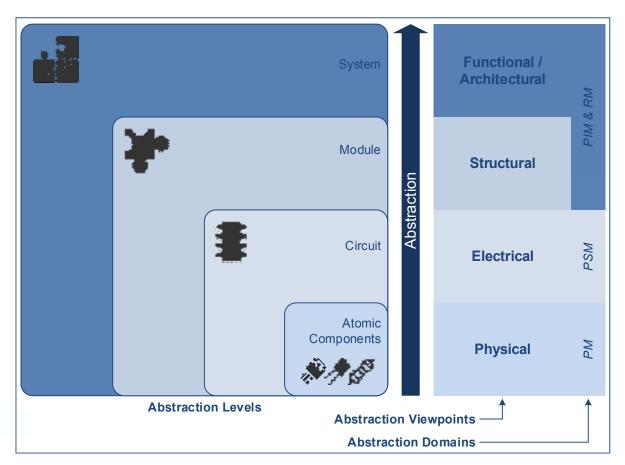

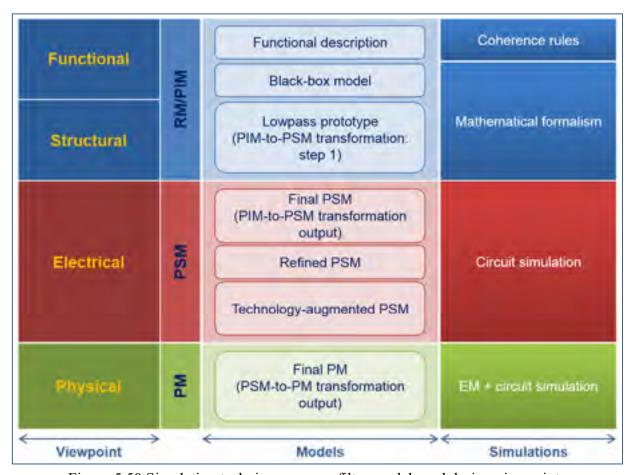

|      | 4.3.4      | Abstraction Levels, Viewpoints and Views                |     |

|      | 4.3.5      | Transition between Abstraction Levels                   |     |

| 4.4  |            | ion to RF and Microwave Design                          |     |

| 4.5  |            | Profile for RF Devices                                  |     |

| 4.5  | 4.5.1      | RF Stereotypes                                          |     |

|      | 4.5.1      | Coherence Rules and Requirements                        |     |

|      | 4.5.2      | Profile Extension and Usage                             |     |

| 4.6  |            | on of RF and Microwave Hardware Abstraction Strategy in | 240 |

| 4.0  |            | osed Design Framework                                   | 251 |

| 4.7  |            | of the RF and Microwave Hardware Abstraction Strategy   | 231 |

| т. / |            | e Proposed Design Framework                             | 254 |

| 4.8  |            | on                                                      |     |

| 7.0  | Conclusi   | 01                                                      | 25  |

| СНА  | PTER 5     | VALIDATION OF THE PROPOSED FRAMEWORK THROUGH            |     |

|      |            | SELECTED CASE STUDIES                                   | 261 |

| 5.1  | Introduct  | tion                                                    | 261 |

| 5.2  | Practical  | Implementation of the Proposed Framework                | 262 |

| 5.3  | Case Stu   | dies                                                    | 267 |

|      | 5.3.1      | Frequency Selection Device                              |     |

|      | 5.3.2      | Power Attenuation Device                                |     |

|      | 5.3.3      | Frequency Translation Device                            | 392 |

| 5.4  | Conclusi   | on                                                      |     |

| CON  | ICI LISION |                                                         | 125 |

| CON  | CLUSION    |                                                         | 423 |

| APP  | ENDIX I    | HISTORY AND ADVANTAGES OF MODERN ELECTRONIC             |     |

|      |            | DESIGN AUTOMATION TOOLS                                 | 433 |

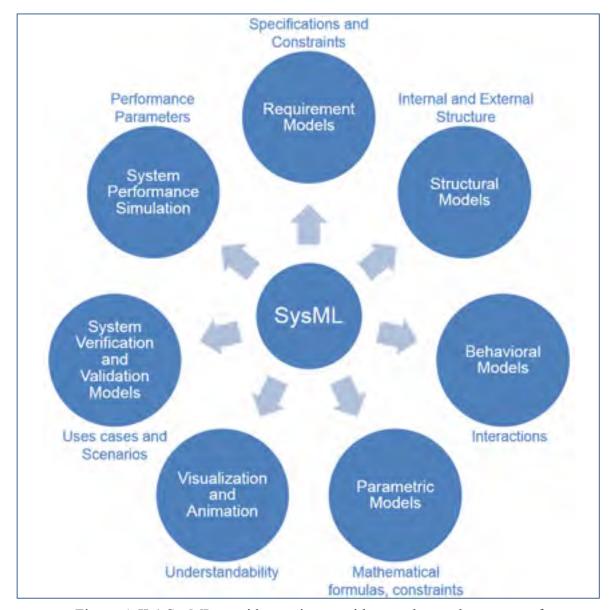

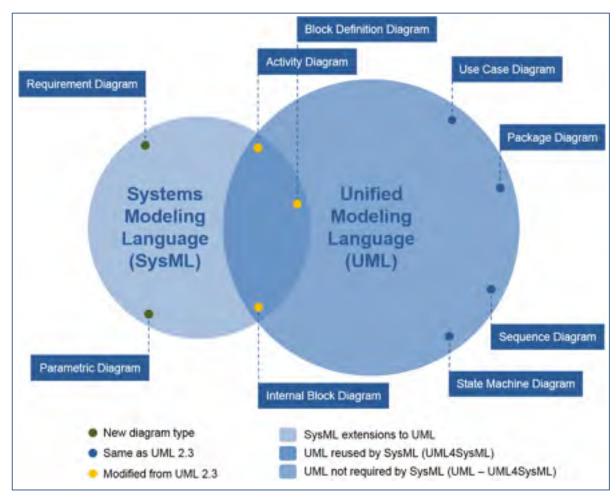

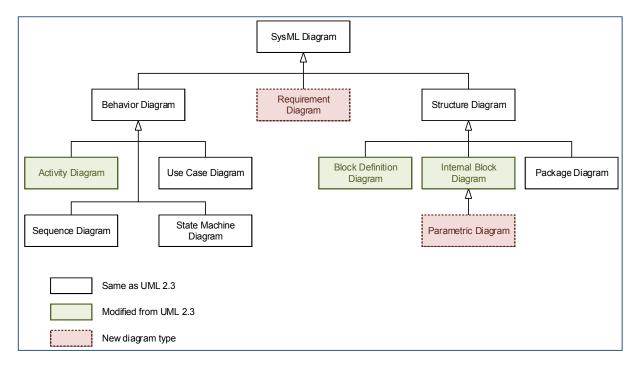

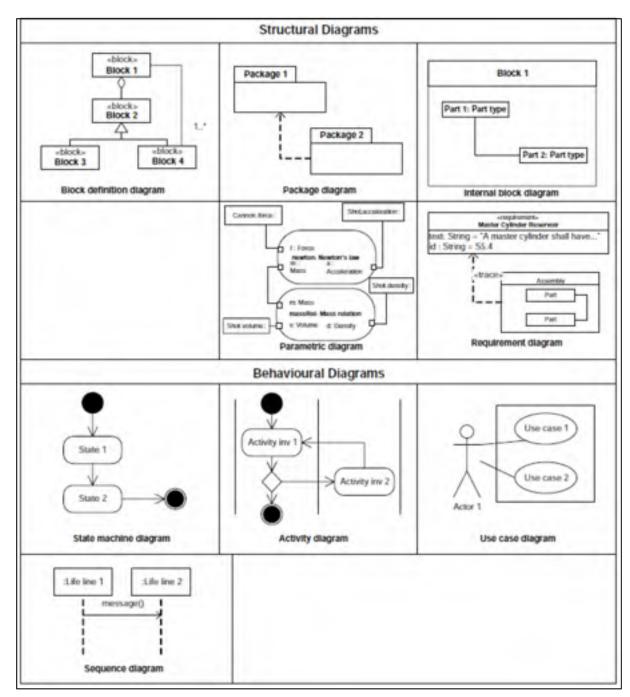

| APP  | ENDIX II   | OVERVIEW OF SYSTEMS MODELING LANGUAGE                   | 439 |

|      |            |                                                         | 107 |

| APP  | ENDIX III  | SUMMARY OF EQUATIONS AND FORMULAS USED IN               |     |

|      |            | CASE STUDIES                                            | 451 |

| LIST OF REFERENCES | 46 | 61 | j |

|--------------------|----|----|---|

|--------------------|----|----|---|

# LIST OF TABLES

|           |                                                                                                     | Page |

|-----------|-----------------------------------------------------------------------------------------------------|------|

| Table 1.1 | Strengths and weaknesses in digital, analog/mixed-signal and RF/microwave design                    | 40   |

| Table 1.2 | Strengths and weaknesses in digital, analog/mixed-signal and RF/microwave design (Table 1.1 cont'd) | 41   |

| Table 2.1 | Comparison between bottom-up and top-down design approaches                                         | 47   |

| Table 2.2 | Comparison of some characteristics of digital, analog/mixed-signal and RF/microwave domains         | 74   |

| Table 2.3 | Comparison of digital, analog/mixed-signal and RF/microwave design practice                         | 78   |

| Table 3.1 | Summary of the properties that the intended RF design framework is expected to support              | 81   |

| Table 3.2 | An example of XML structure to capture the SysML model of Figure 3.4                                | 89   |

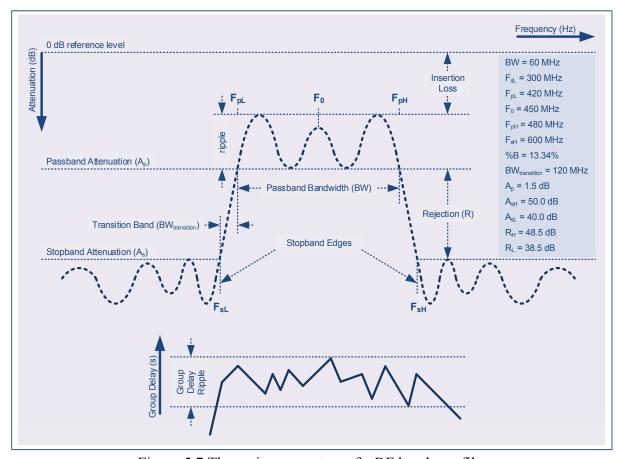

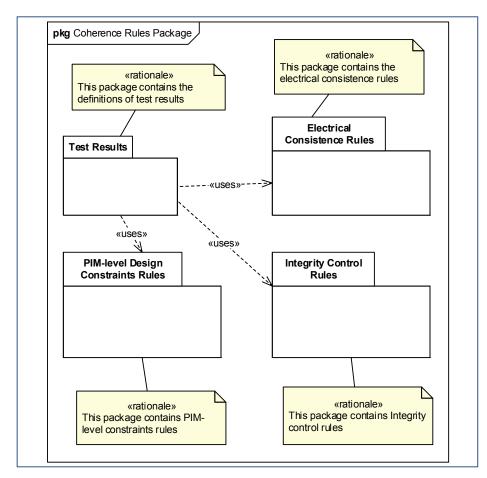

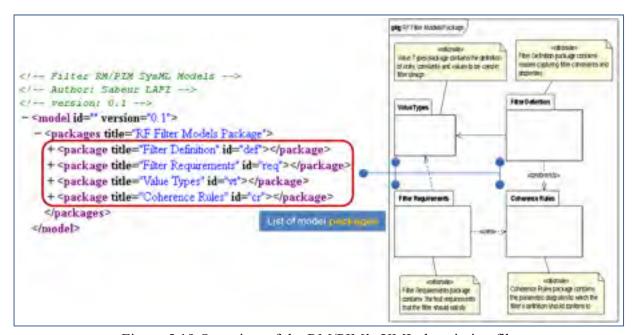

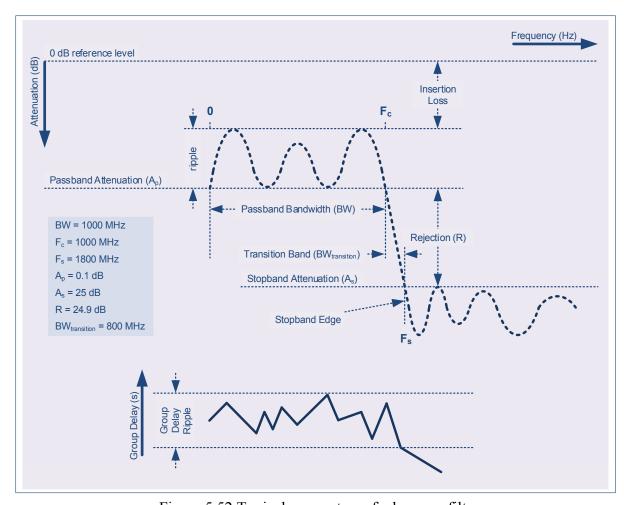

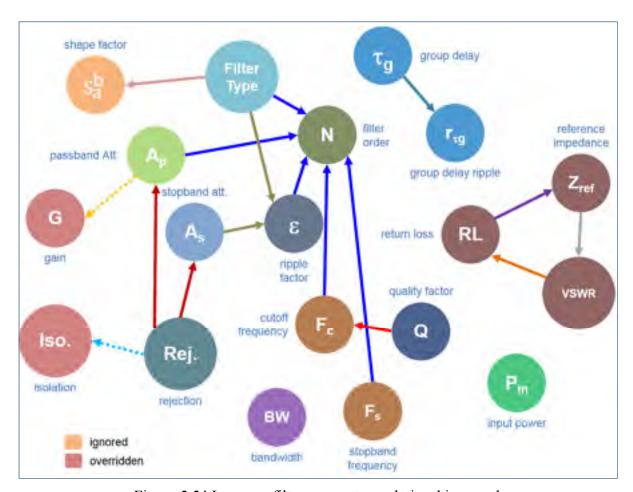

| Table 3.3 | Relationships between bandpass filter parameters given in Figure 3.6                                | 94   |

| Table 3.4 | An example of coherence rules to validate a typical RF filter functional description                | 94   |

| Table 3.5 | A selection of RF filter integrity control rules                                                    | 94   |

| Table 3.6 | Overview of the Q-matrix XML data structure                                                         | 111  |

| Table 3.7 | How the proposed framework addressed the requirements expressed in Table 3.1                        | 126  |

| Table 4.1 | Views are associated to viewpoints and models                                                       | 172  |

| Table 4.2 | RF systems can be viewed as black-boxes with inputs and outputs                                     | 185  |

| Table 4.3 | RF and microwave systems can be modeled using response functions                                    | 188  |

| Table 4.4 | Atomic components' layer is composed of atomic components (i.e., RF indivisible devices)            | 201  |

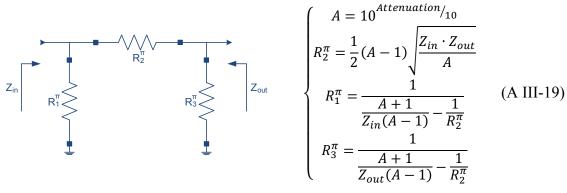

| Table 4.5 | Examples of equation-based transformations for T- and $\pi$ -pad attenuators design                 | 215  |

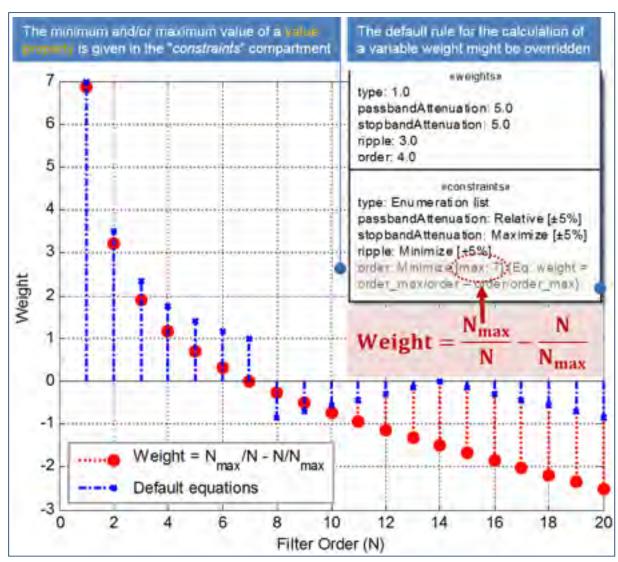

| Table 4.6  | Variable weights Xi are estimated based on property constraints                                                                                     | 224 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.7  | Performance details of two candidate design solutions for the GPS bandpass filter of Figure 3.4                                                     | 226 |

| Table 4.8  | Calculation of the objective function for each candidate design solution                                                                            | 227 |

| Table 4.9  | Comparison between the proposed abstraction strategy for RF/microwave design and those adopted for MDE/MDA, digital, analog and mixed-signal design | 256 |

| Table 4.10 | How the proposed hardware abstraction helps the framework in tackling the requirements given in Table 3.1                                           | 257 |

| Table 5.1  | List of case studies                                                                                                                                | 270 |

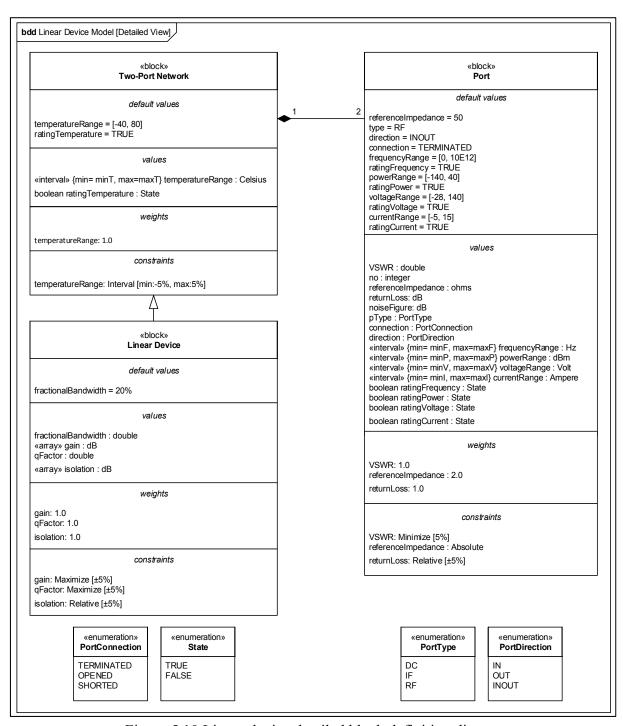

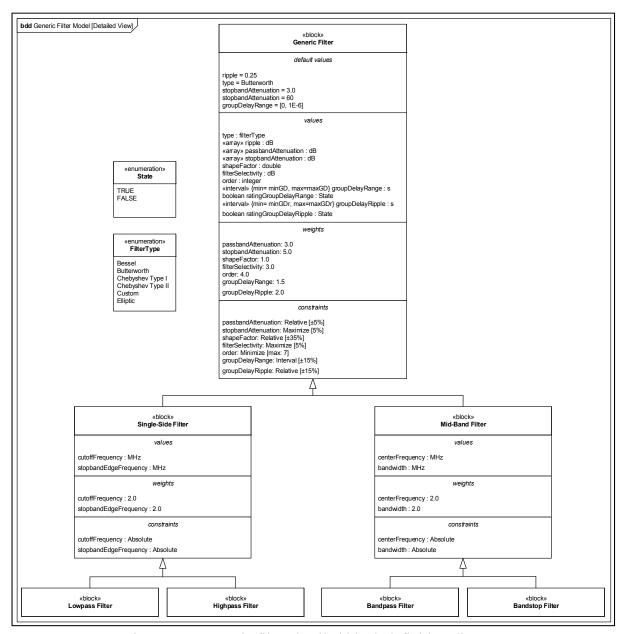

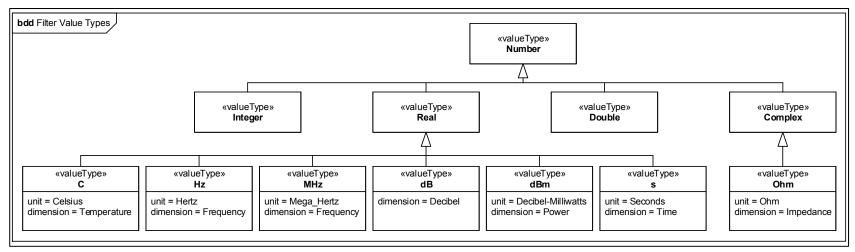

| Table 5.2  | Typical bandpass filter requirements for a 450-MHz satellite radio                                                                                  | 275 |

| Table 5.3  | List of bandpass filter value properties as presented in the bdds of Figure 5.10 and 5.11                                                           | 282 |

| Table 5.4  | List of bandpass filter port value properties as presented in the bdd of Figure 5.10                                                                | 283 |

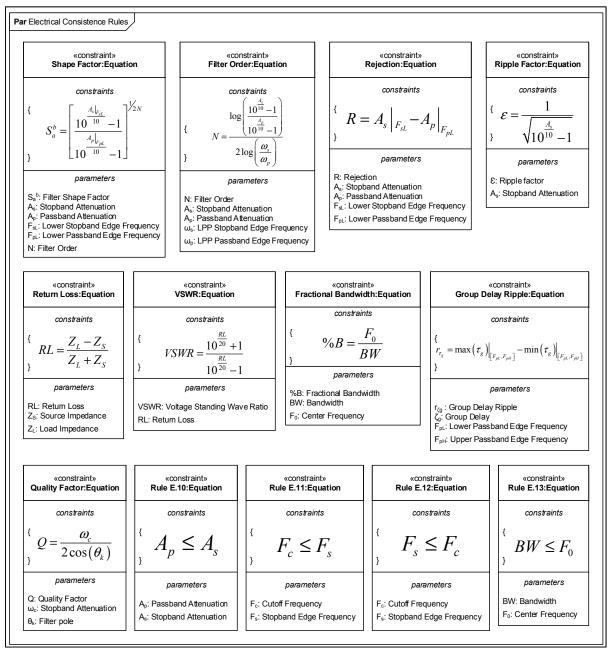

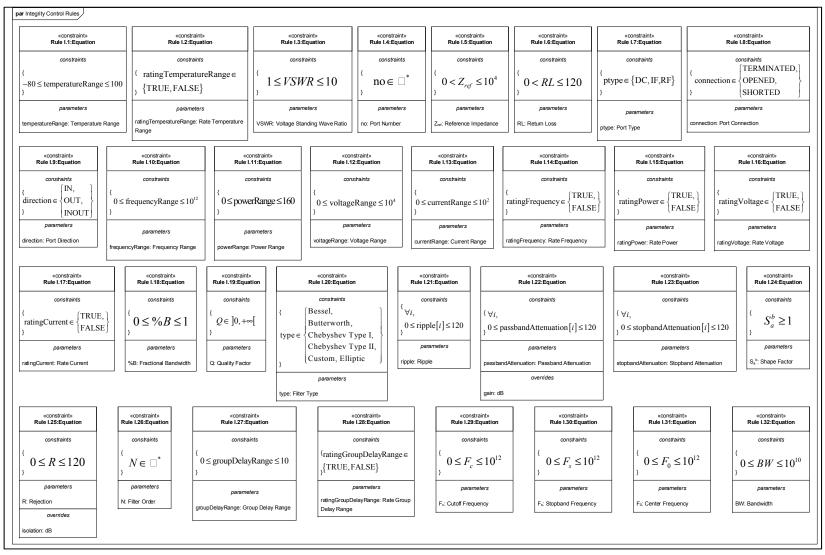

| Table 5.5  | Relationships between bandpass filter parameters given in Figure 5.24                                                                               | 297 |

| Table 5.6  | Main filter electrical consistence rules                                                                                                            | 297 |

| Table 5.7  | Bandpass filter PIM-level design constraints rules                                                                                                  | 299 |

| Table 5.8  | Bandpass filter integrity control rules                                                                                                             | 299 |

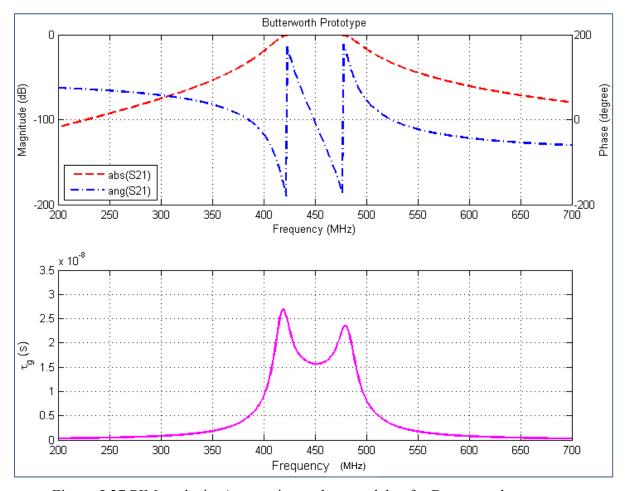

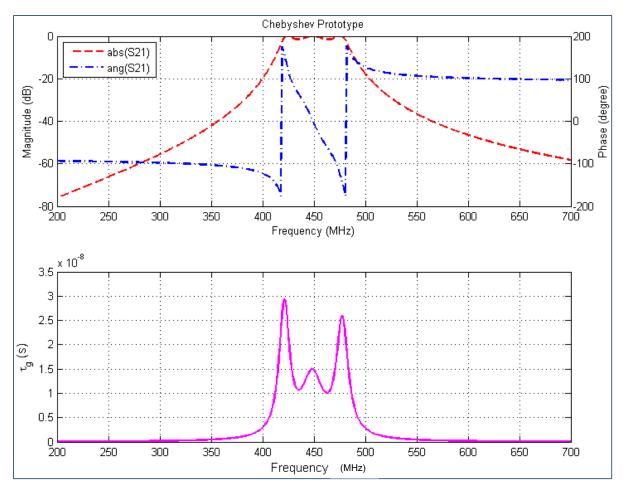

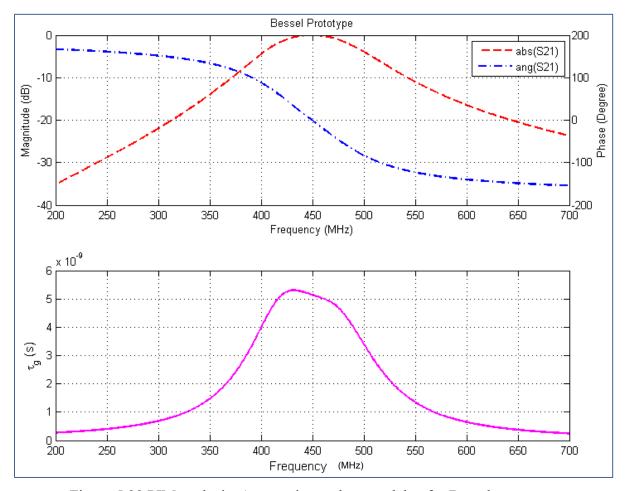

| Table 5.9  | Black-box model: performance summary of the four filter prototypes                                                                                  | 305 |

| Table 5.10 | Constant weights and property constraints for each decision variable                                                                                | 307 |

| Table 5.11 | Objective function calculations for each filter prototype                                                                                           | 310 |

| Table 5.12 | PIM-to-PSM transformation (target platform: LC/distributed lines)                                                                                   | 311 |

| Table 5.13 | Overview of the intra-view transformation for granularity refinement                                                                                | 316 |

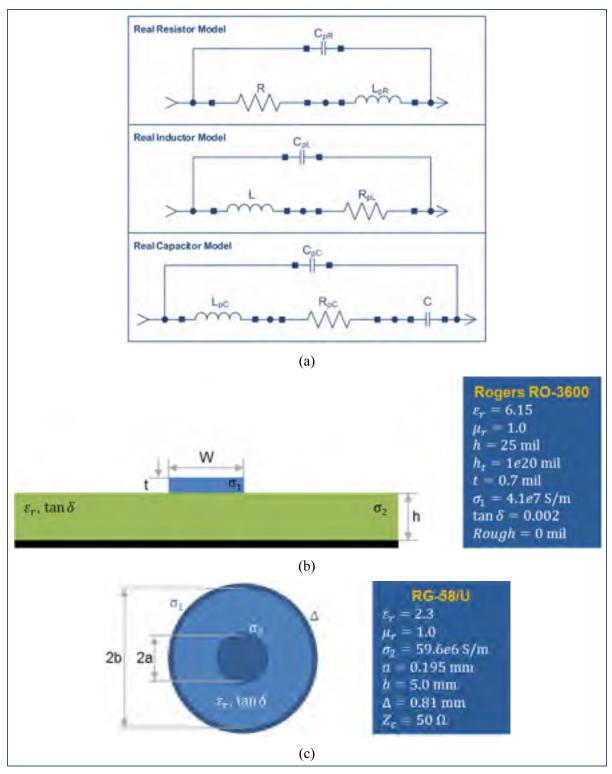

| Table 5.14 | Electrical models for non-ideal inductors and capacitors                                                                                            | 319 |

| Table 5.15 | List of inductors found in the technology library during automated technology mapping                                                               | 326 |

| Table 5.16 | List of capacitors found in the technology library during automated technology mapping | 327 |

|------------|----------------------------------------------------------------------------------------|-----|

| Table 5.17 | Comparison of PCB areas required to hold the generated platform models                 | 333 |

| Table 5.18 | Lowpass filter specifications                                                          | 343 |

| Table 5.19 | List of lowpass filter value properties (port value properties are not considered)     | 346 |

| Table 5.20 | Relationships between lowpass filter value properties given in Figure 5.54             | 349 |

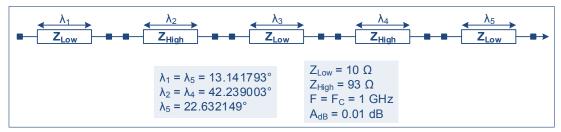

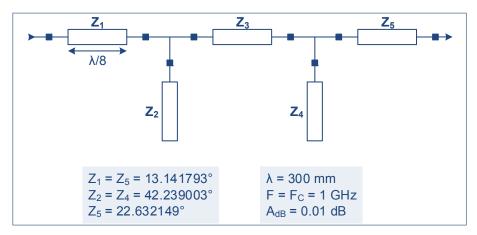

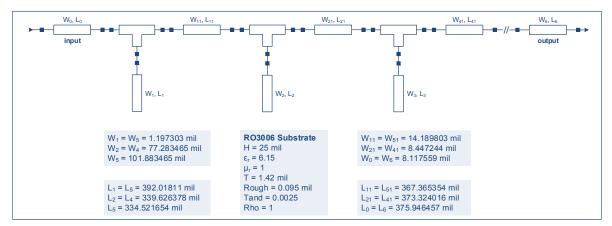

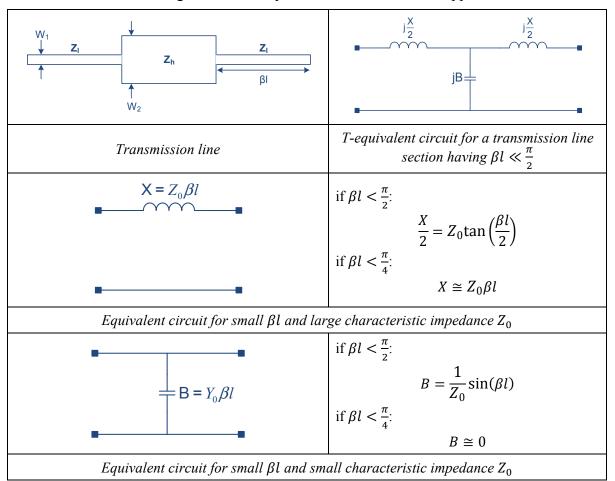

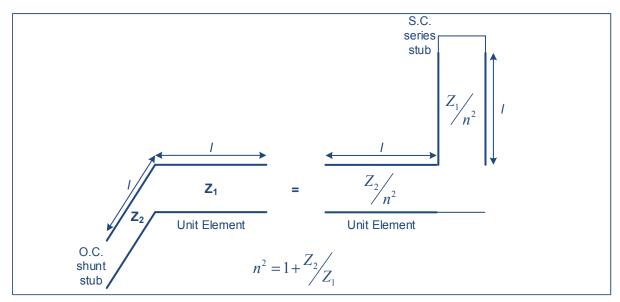

| Table 5.21 | A PIM to PSM transformation for stepped-impedance lowpass filters                      | 352 |

| Table 5.22 | A PIM-to-PSM transformation based on open-end circuit stubs                            | 353 |

| Table 5.23 | Calculations resulting from the stepped-impedance-based (PIM-to-PSM) transformation    | 354 |

| Table 5.24 | Main properties of the RO3006 substrate                                                | 354 |

| Table 5.25 | Lowpass stepped-impedance filter PM form factor                                        | 355 |

| Table 5.26 | Calculations resulting from the open-end stub-based transformation                     | 359 |

| Table 5.27 | Lowpass open-end stub-based filter PM form factor                                      | 360 |

| Table 5.28 | Typical specifications of a 3-dB RF attenuator                                         | 362 |

| Table 5.29 | List of values of « Attenuator » block                                                 | 367 |

| Table 5.30 | List of values of each « Port » block                                                  | 368 |

| Table 5.31 | Relationships between attenuator parameters given in Figure 5.71                       | 372 |

| Table 5.32 | Attenuator integrity control rules                                                     | 372 |

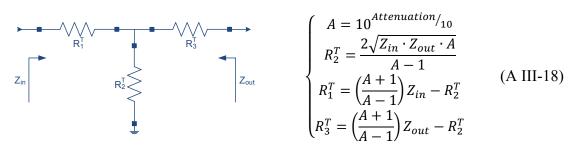

| Table 5.33 | PIM-to-PSM transformation for T and Π resistive attenuators                            | 375 |

| Table 5.34 | Values of resistors for T and $\Pi$ attenuators                                        | 375 |

| Table 5.35 | T attenuator initial resistors                                                         | 384 |

| Table 5.36 | Π attenuator initial resistors                                                         | 384 |

| Table 5.37 | T attenuator alternative resistors                                                     | 385 |

| Table 5.38 | Π attenuator alternative resistors                                                          | 386 |

|------------|---------------------------------------------------------------------------------------------|-----|

| Table 5.39 | Form factor of initial and refined PIMs for both T and $\Pi$ attenuators                    | 387 |

| Table 5.40 | Intra-view transformation used for the attenuators' PSM granularity refinement              | 388 |

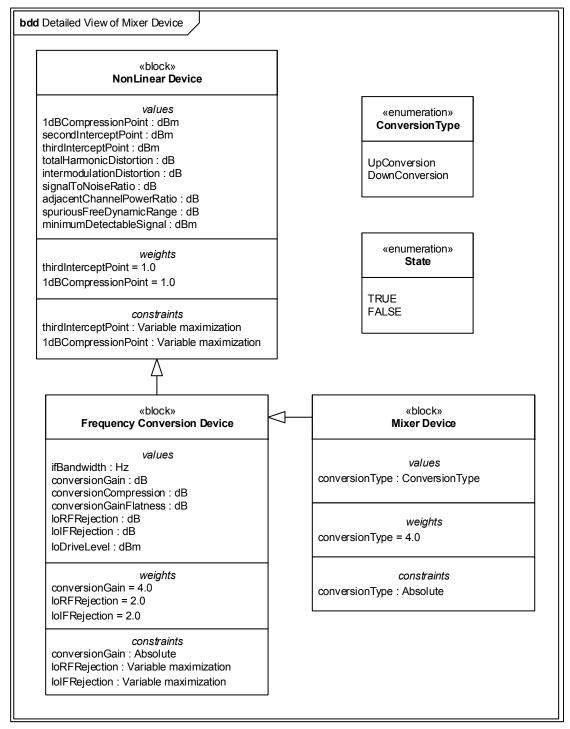

| Table 5.41 | Mixer specifications                                                                        | 392 |

| Table 5.42 | List of mixer value properties as presented in the corresponding bdds                       | 396 |

| Table 5.43 | List of mixer port value properties as enumerated in the SysML models                       | 397 |

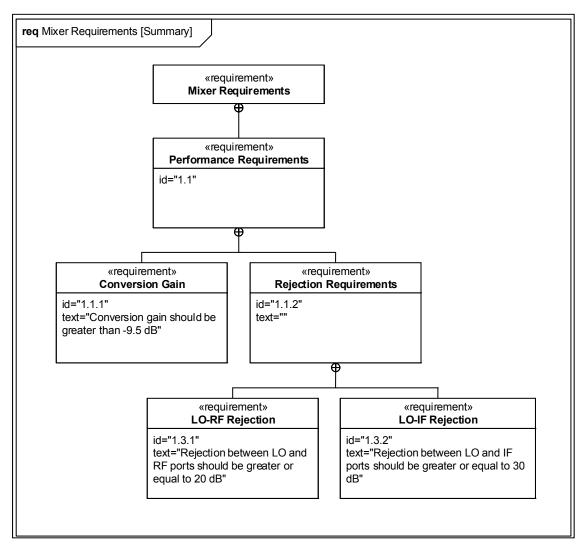

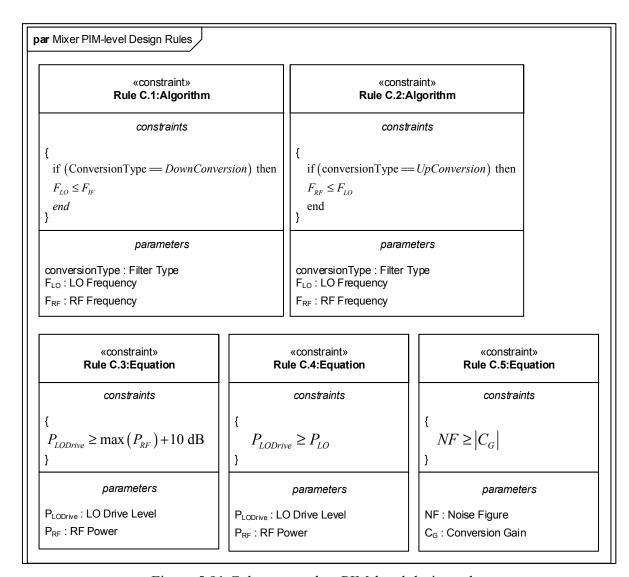

| Table 5.44 | Mixer PIM-level design constraints rules                                                    | 401 |

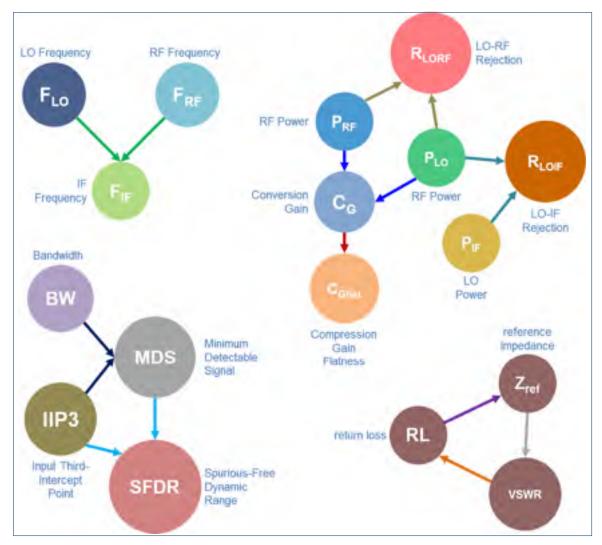

| Table 5.45 | Common relationships between mixer parameters given in Figure 5.87                          | 403 |

| Table 5.46 | Mixer integrity control rules                                                               | 403 |

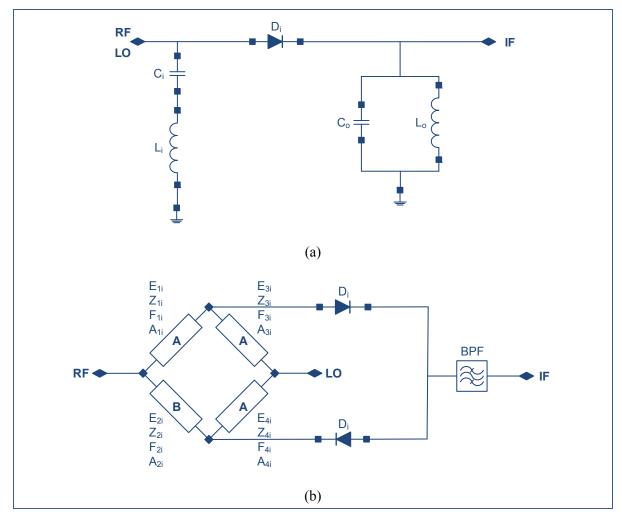

| Table 5.47 | Passive diode mixer PIM-to-PSM transformation                                               | 407 |

| Table 5.48 | Rat-race Mixer PIM to PSM transformation                                                    | 407 |

| Table 5.49 | Generated PSMs: Summary of both mixer PSMs performance characteristics                      | 413 |

| Table 5.50 | Generated PSMs: Objective function calculations for each filter prototype                   | 413 |

| Table 5.51 | Properties of the synthesized rat-race microstrip sections (RO3006 substrate)               | 414 |

| Table 5.52 | List of suitable diode parts found in the technology library                                | 415 |

| Table 5.53 | List of inductor parts found in the technology library during automated technology mapping  |     |

| Table 5.54 | List of capacitor parts found in the technology library during automated technology mapping | 417 |

| Table 5.55 | Comparison of the performance of the three PSM prototypes                                   | 418 |

| Table 5.56 | Technology mapped PSM: Objective function calculations for each rat-race mixer prototype    | 419 |

# LIST OF FIGURES

|             |                                                                                                                    | Page |

|-------------|--------------------------------------------------------------------------------------------------------------------|------|

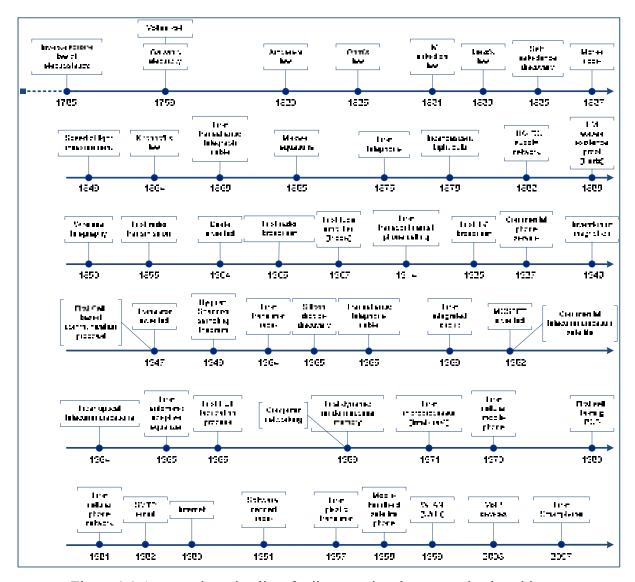

| Figure 1.1  | A non-exhaustive list of milestones in telecommunications history                                                  | 12   |

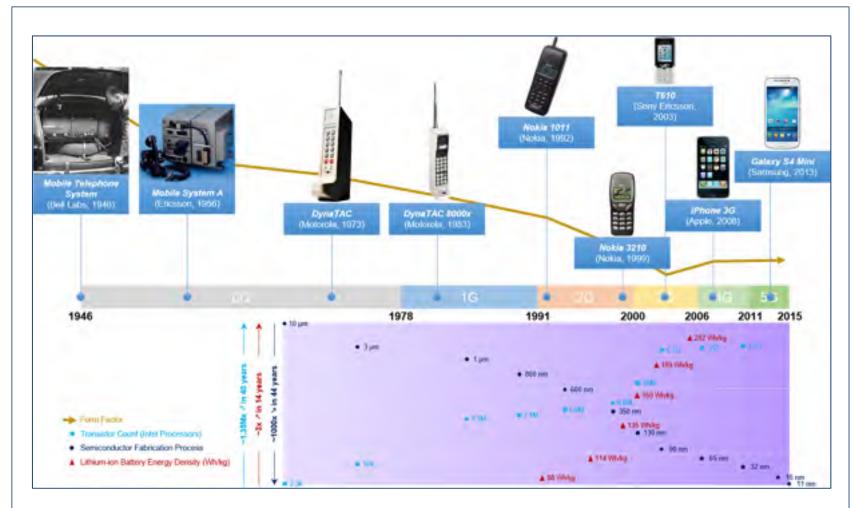

| Figure 1.2  | A comparison between the first handheld mobile phone and a recent smartphone                                       | 14   |

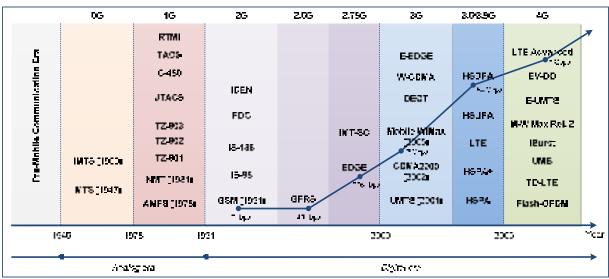

| Figure 1.3  | Evolution of wireless and mobile standards                                                                         | 16   |

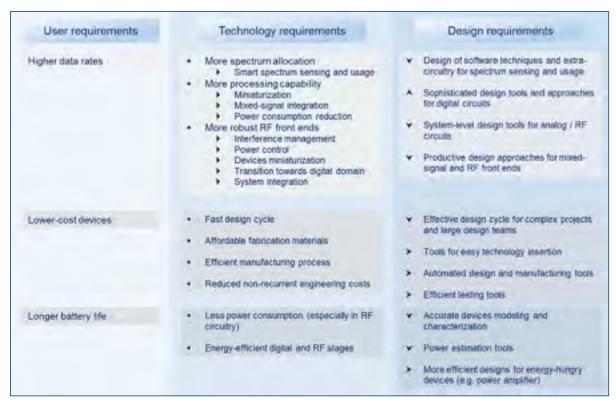

| Figure 1.4  | User expectations can be derived into technology and design requirements                                           | 21   |

| Figure 1.5  | Radio-communication technology is evolving at a growing pace                                                       | 28   |

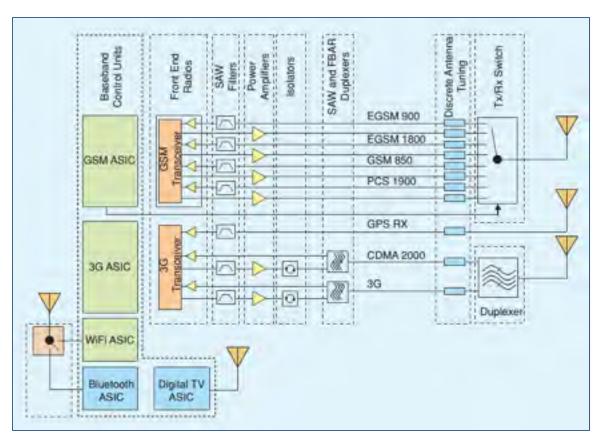

| Figure 1.6  | A typical multimode, multi-band handset block diagram                                                              | 29   |

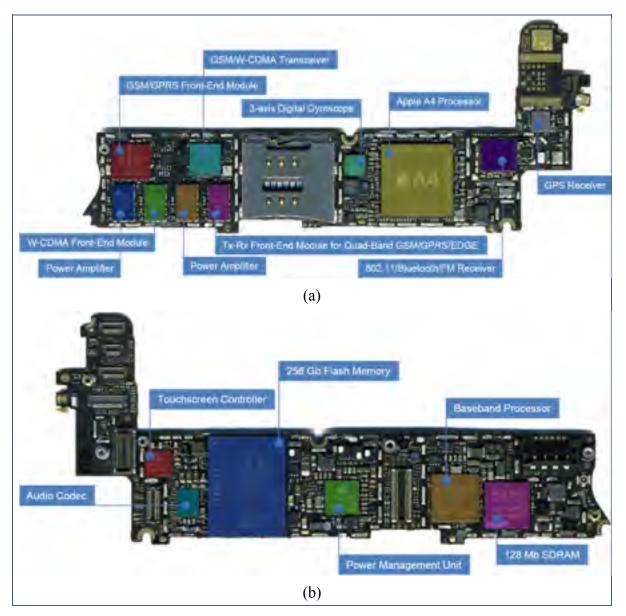

| Figure 1.7  | iPhone 4 PCB Layout: (a) Front Panel: Front-End components (b) Back Panel: Baseband components                     | 30   |

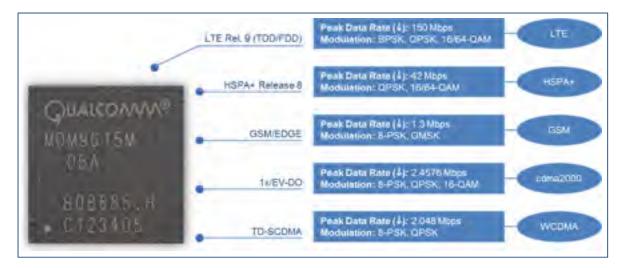

| Figure 1.8  | A typical multi-standard multi-mode multi-band baseband chip:<br>Qualcomm MDM9615M baseband modem used in iPhone 5 | 31   |

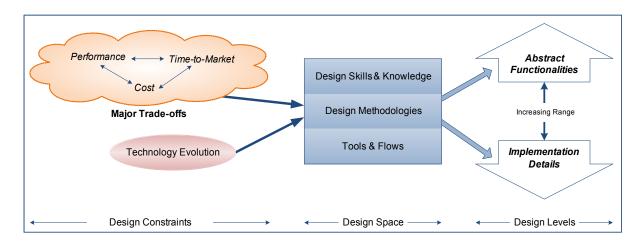

| Figure 1.9  | Interaction between design constraints, methodologies and abstraction levels                                       | 31   |

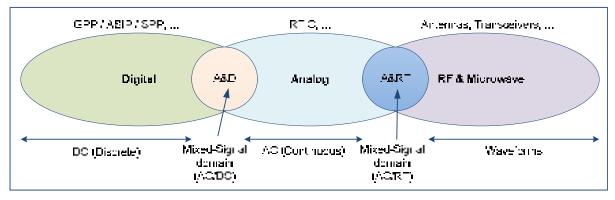

| Figure 1.10 | Design domains                                                                                                     | 32   |

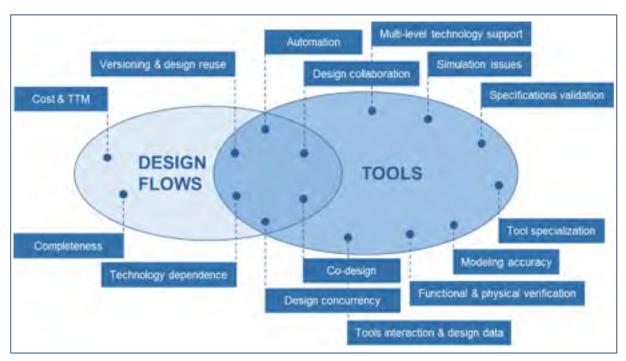

| Figure 1.11 | Challenges in RF design can be fully or partially related to either the design flows or tools in use               | 37   |

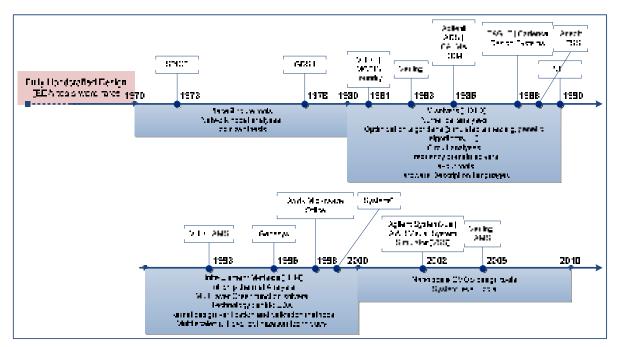

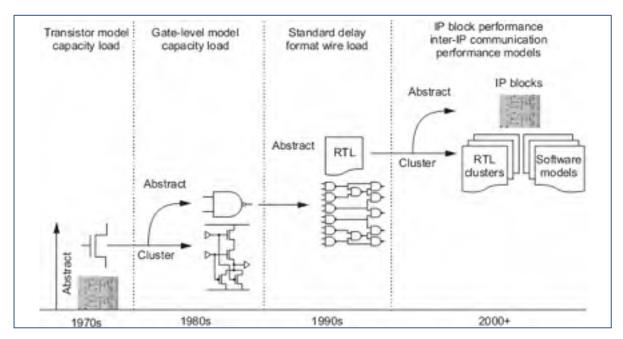

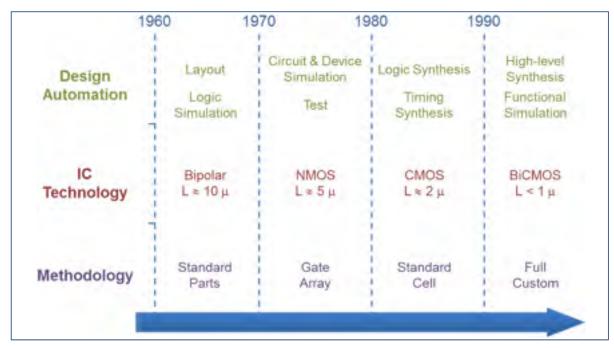

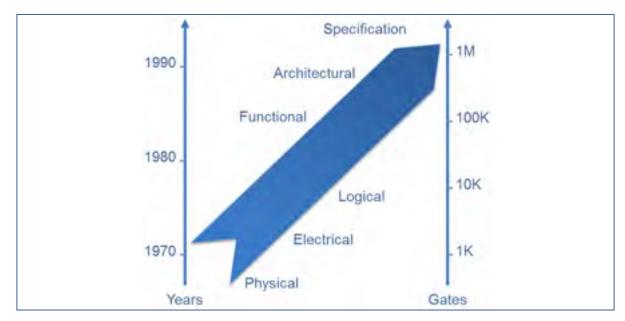

| Figure 2.1  | An overview of EDA history                                                                                         | 49   |

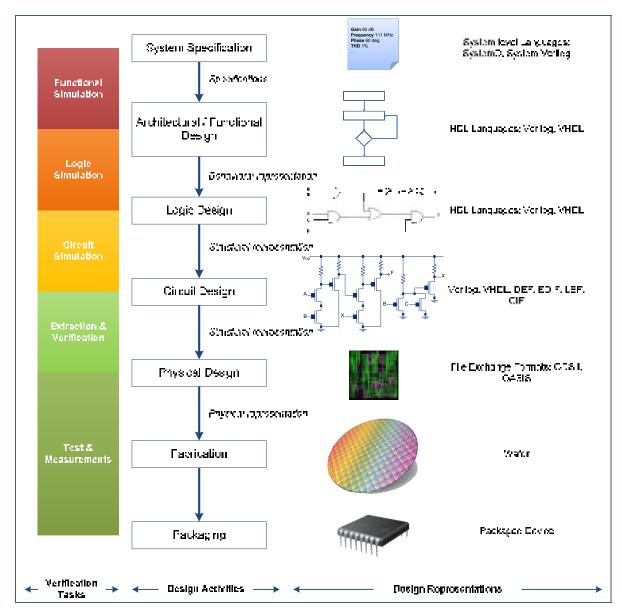

| Figure 2.2  | Typical design flow for digital circuits                                                                           | 53   |

| Figure 2.3  | Typical analog design flow using Cadence commercial package                                                        | 57   |

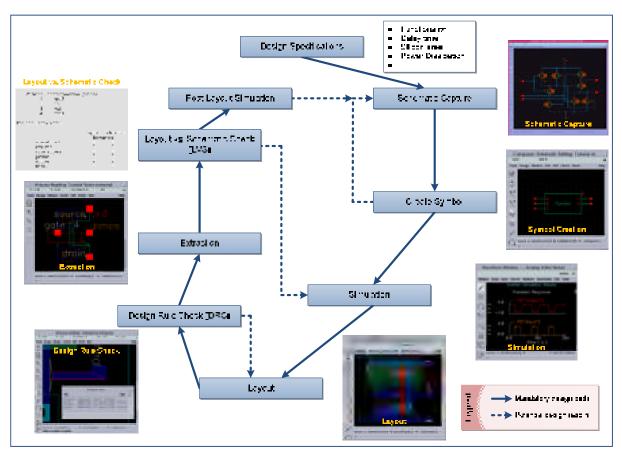

| Figure 2.4  | Typical analog and mixed-signal design cycle including common EDA tools in use                                     | 59   |

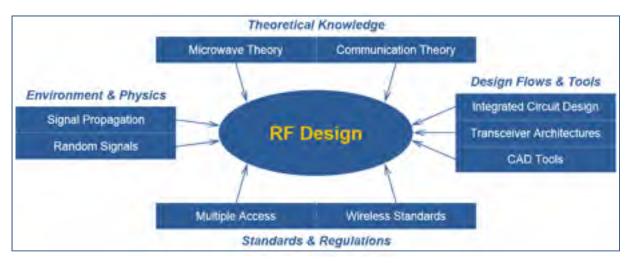

| Figure 2.5  | Main disciplines related to RF design                                                                              | 61   |

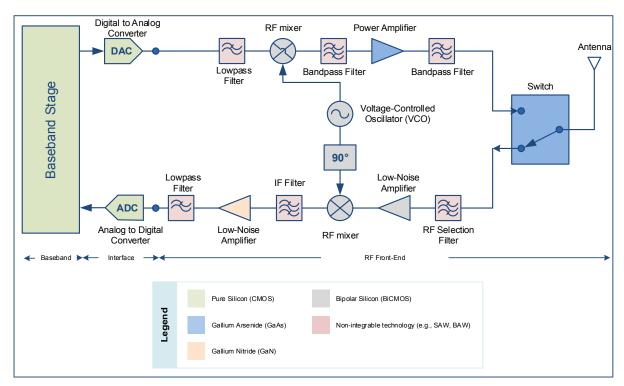

| Figure 2.6  | Overview of some technologies of which typical components in a direct-conversion transceiver are made              | 63   |

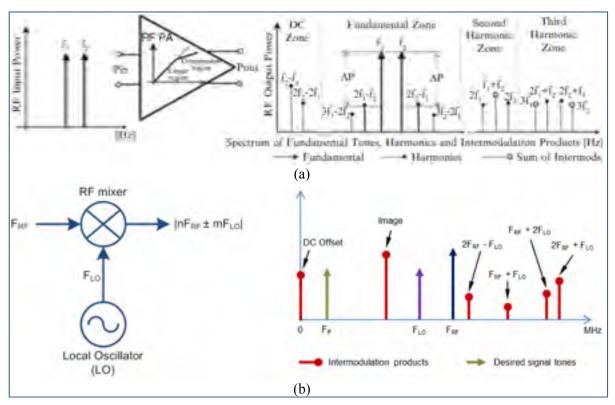

| Figure 2.7  | and intermodulation and nonlinearity: (a) Output power compression and intermodulation distortion in RF amplifier (b) RF mixer spurious products                                                                                          | 64 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

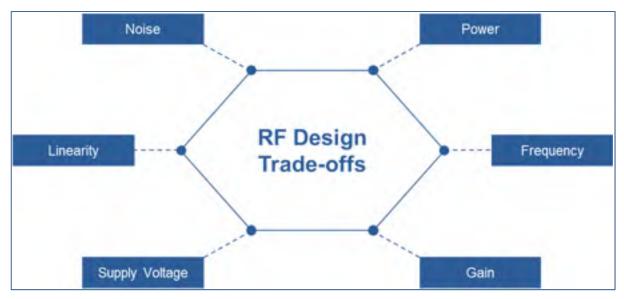

| Figure 2.8  | Multiple antagonistic parameters are tuned in RF design                                                                                                                                                                                   | 65 |

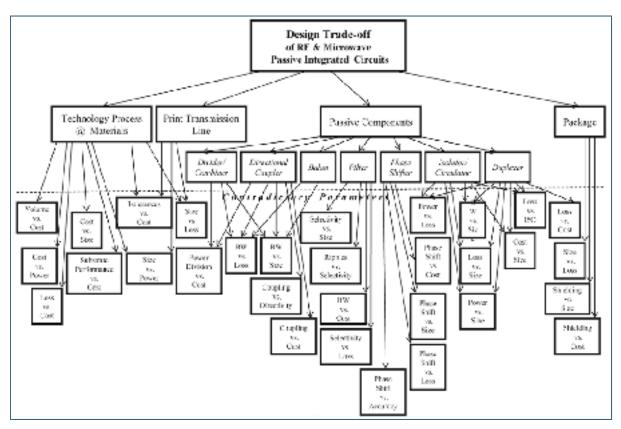

| Figure 2.9  | Common trade-offs encountered in RF passives design                                                                                                                                                                                       | 66 |

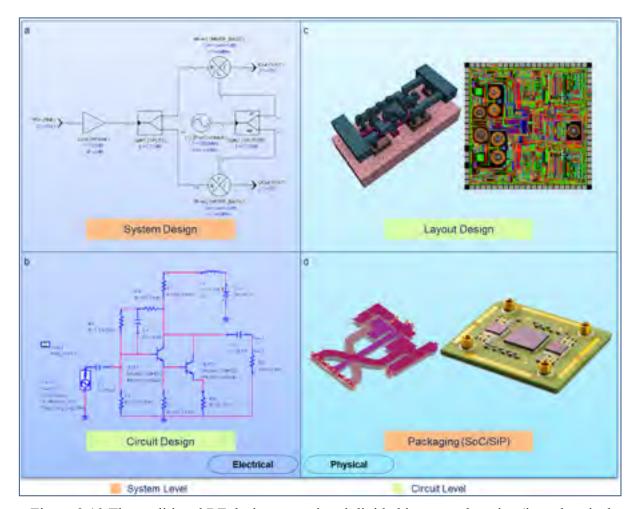

| Figure 2.10 | The traditional RF design space is subdivided into two domains (i.e., electrical and physical) with two corresponding representations (i.e., system and circuit)                                                                          | 67 |

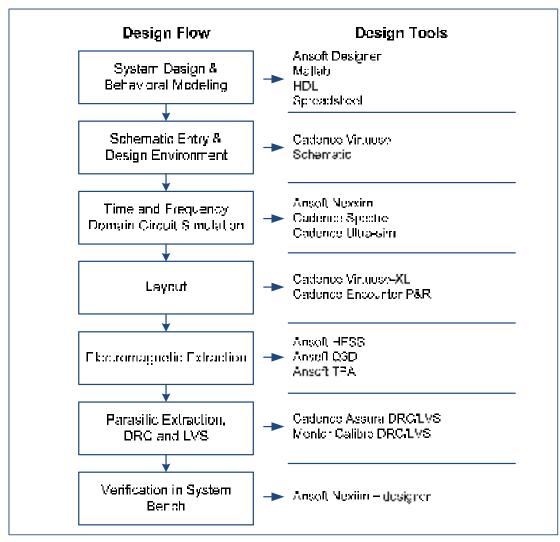

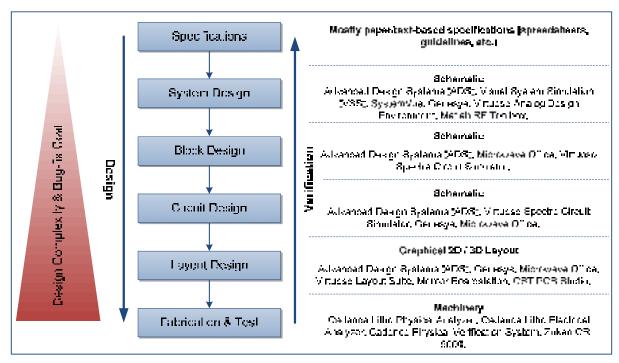

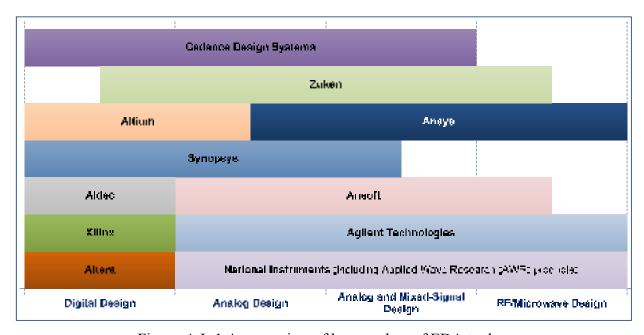

| Figure 2.11 | Typical RF design scheme and some EDA tools in use for each design stage                                                                                                                                                                  | 68 |

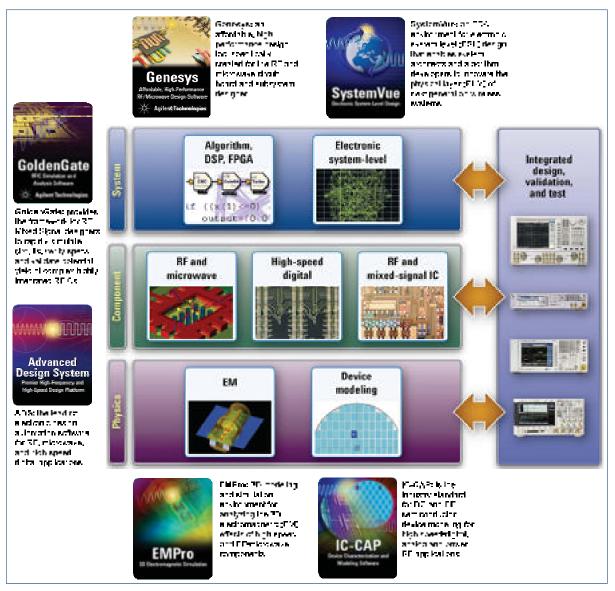

| Figure 2.12 | EDA tools from Agilent Technologies                                                                                                                                                                                                       | 70 |

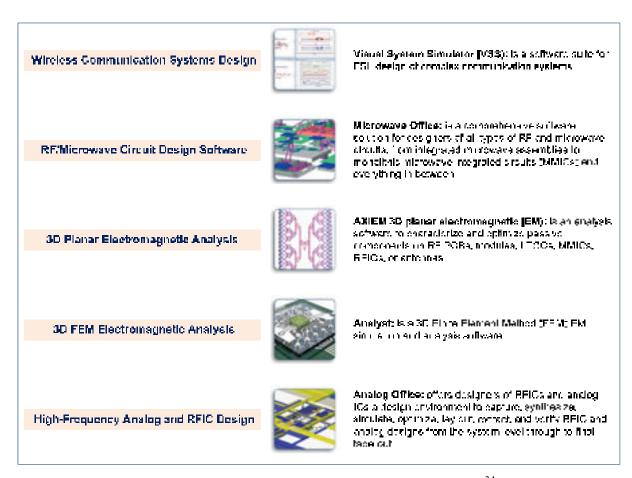

| Figure 2.13 | EDA tools from Applied Wave Research                                                                                                                                                                                                      | 71 |

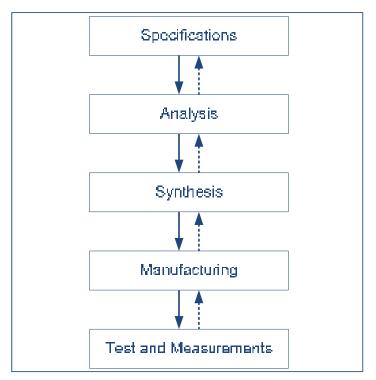

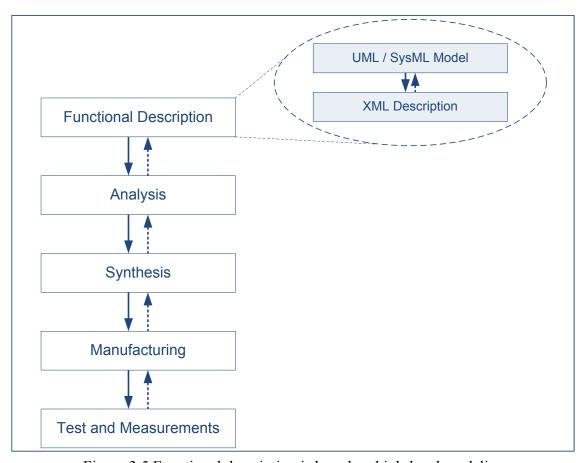

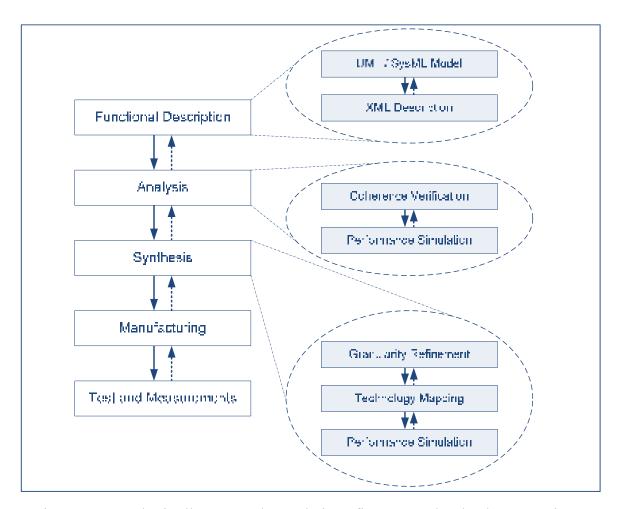

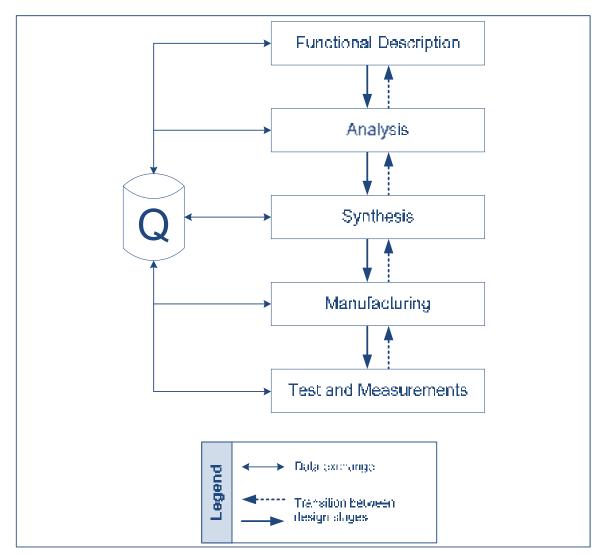

| Figure 3.1  | The design flow consists of five distinct design stages                                                                                                                                                                                   | 83 |

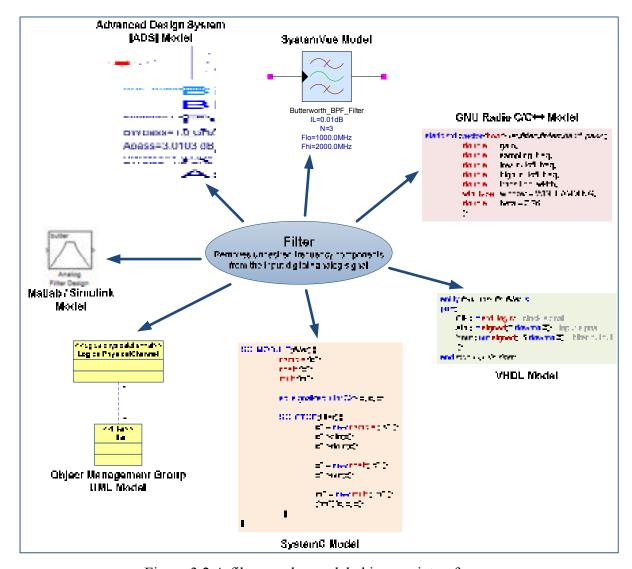

| Figure 3.2  | A filter can be modeled in a variety of ways                                                                                                                                                                                              | 85 |

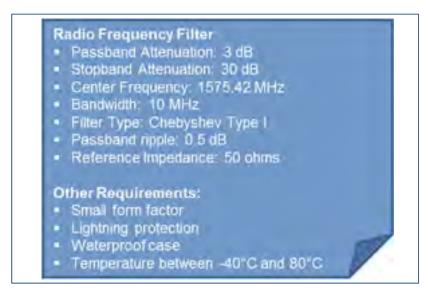

| Figure 3.3  | Typical specifications of a GPS L1 RF filter                                                                                                                                                                                              | 87 |

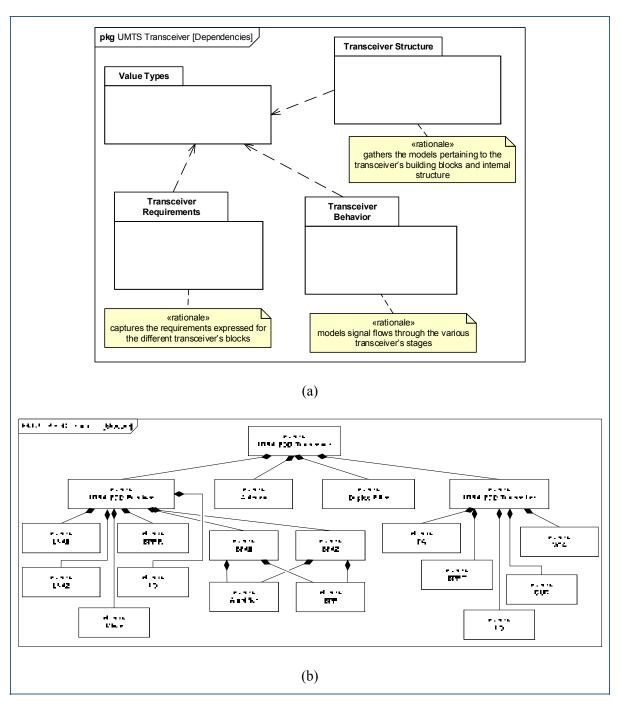

| Figure 3.4  | An example of SysML model for a RF filter: (a) the package diagram (b) the value types package (c) the block definition diagram of the filter (d) the requirements diagram                                                                | 88 |

| Figure 3.5  | Functional description is based on high-level modeling                                                                                                                                                                                    | 90 |

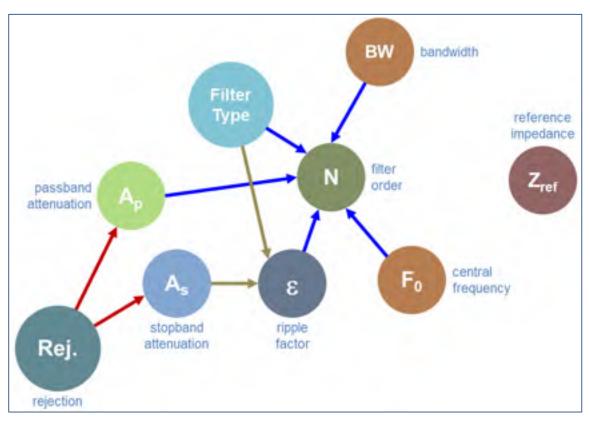

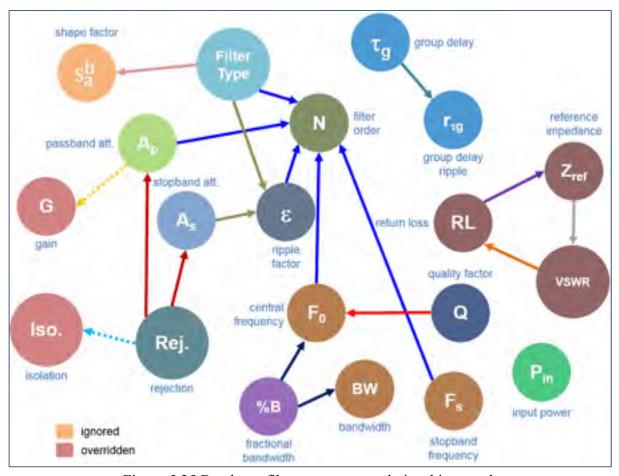

| Figure 3.6  | Parameters relationships graph corresponding to the GPS bandpass filter of Figure 3.4                                                                                                                                                     | 93 |

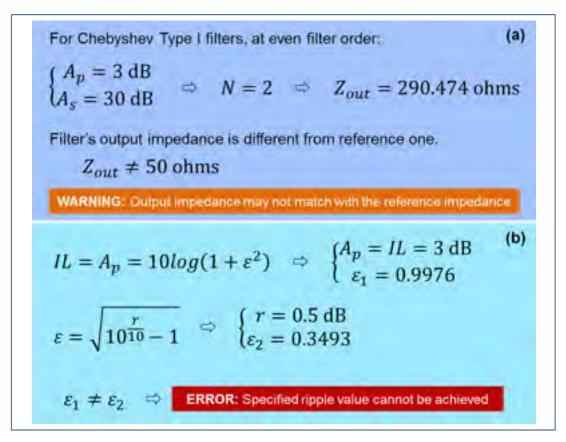

| Figure 3.7  | Example of coherence rules to validate a RF filter functional description:  (a) A warning results from a rule that detects a minor consistency issue, while (b) an error indicates a major incoherence that makes the design not feasible | 95 |

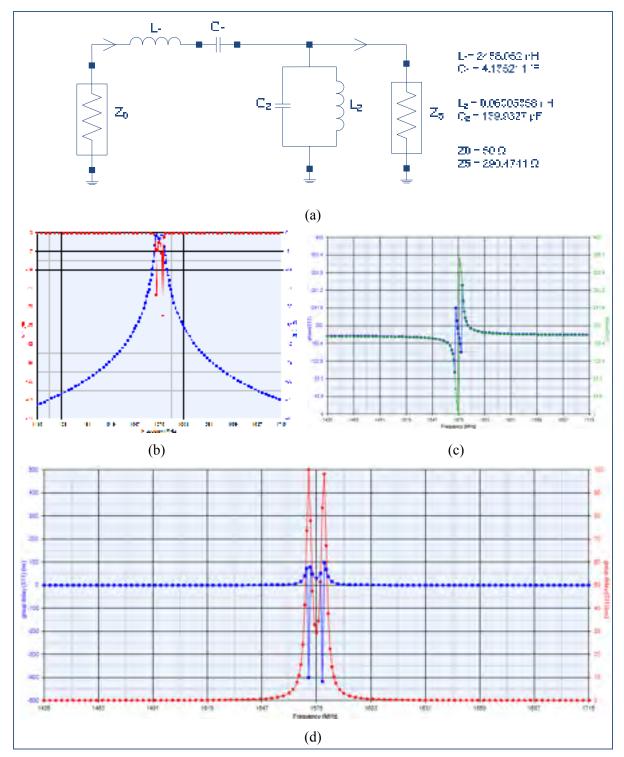

| Figure 3.8  | Example of system-level analyses related to the GPS L1 bandpass filter (considering a 3-dB ripple): (a) ideal filter network (b) transmission and reflection magnitude, (c) phase and (d) group delay                                     | 97 |

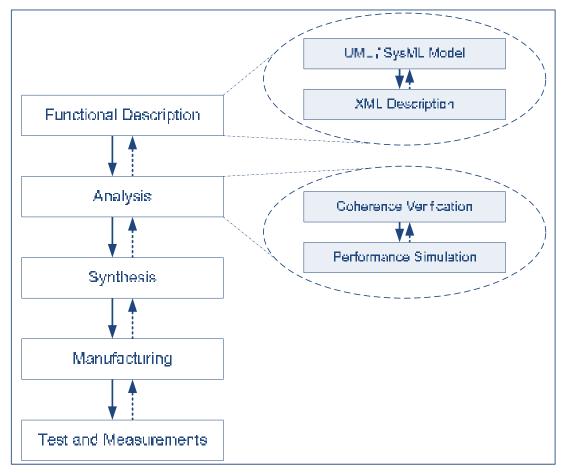

| Figure 3.9  | "Analysis" step includes "Coherence Verification" and system-level "Performance Simulation"                                                                                                                                               | 98 |

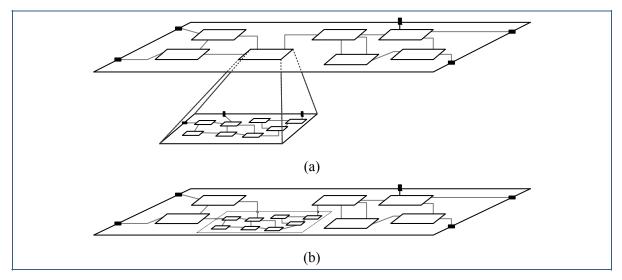

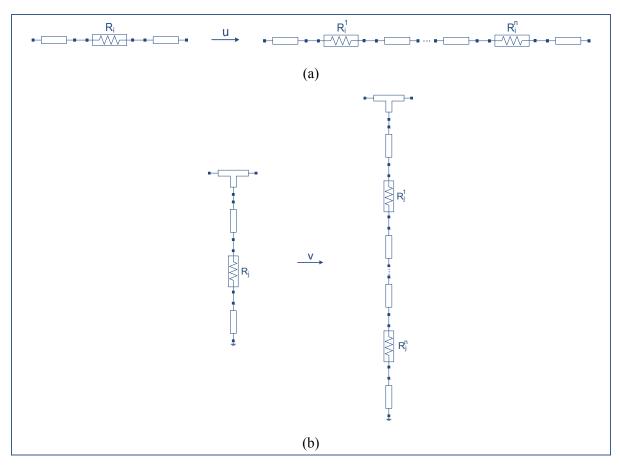

| Figure 3.10 | Illustration of the granularity refinement concept: (a) and (b) RF amplifier structures, (c) and (d) RF duplexer structures                                                                                                                                   | 99  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

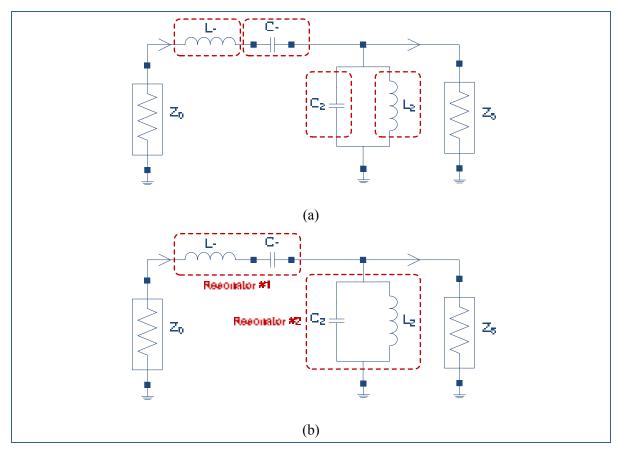

| Figure 3.11 | Granularity concept applied to the GPS L1 bandpass filter: (a) four lumped-component elements or (b) two resonators                                                                                                                                           | 100 |

| Figure 3.12 | Some technology parameters required for (a) lumped-component (b) microstrip and (c) coaxial-cable circuits' implementation                                                                                                                                    | 102 |

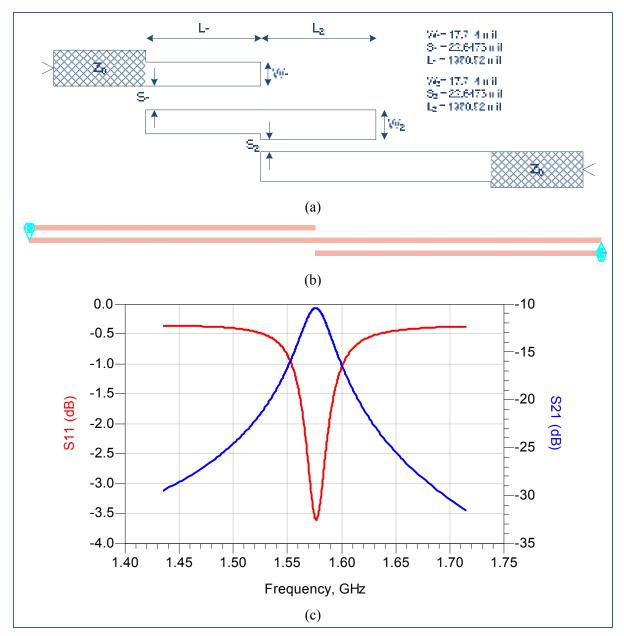

| Figure 3.13 | The layout corresponding to microstrip coupled-line realization of the GPS L1 bandpass filter: (a) microstrip physical dimensions (considering a FR-4 substrate), (b) the layout produced using Agilent ADS and (c) its performance simulation using Momentum | 103 |

| Figure 3.14 | Synthesis allows nested granularity refinement and technology mapping in order to build ready-for-manufacturing implementations from an elaborated functional description                                                                                     | 104 |

| Figure 3.15 | Linking the different design stages with the Q-matrix to handle data exchange                                                                                                                                                                                 | 107 |

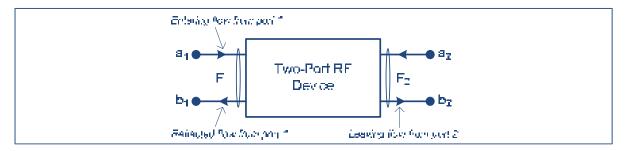

| Figure 3.16 | Conventions used in a typical two-port RF network where $F1 \neq F2$                                                                                                                                                                                          | 108 |

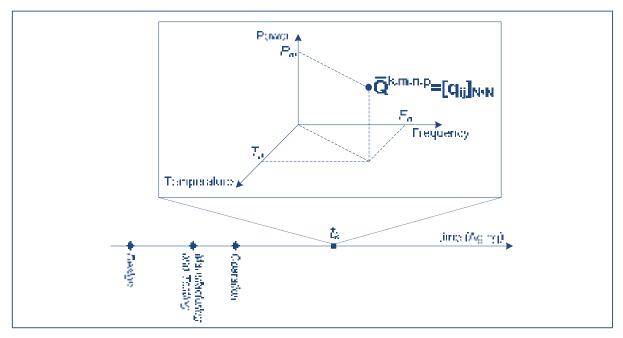

| Figure 3.17 | Generalized Q-matrix is a function of frequency, power, temperature and time                                                                                                                                                                                  | 110 |

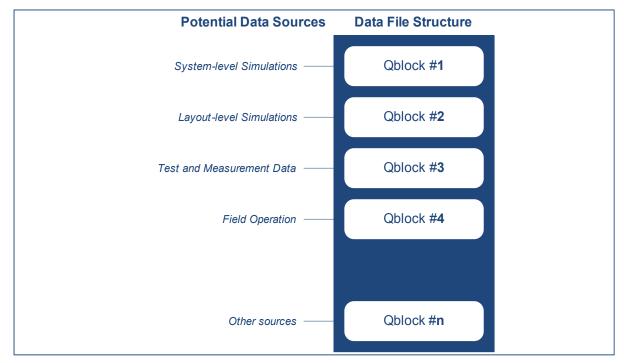

| Figure 3.18 | The file consists of various data blocks composing data of different sources                                                                                                                                                                                  | 112 |

| Figure 3.19 | Q-matrix data blocks from different data sources                                                                                                                                                                                                              | 112 |

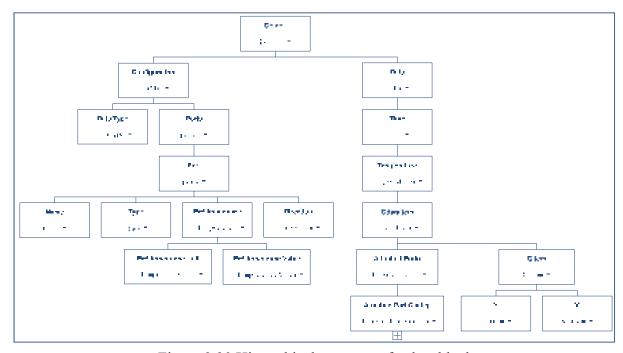

| Figure 3.20 | Hierarchical structure of a data block                                                                                                                                                                                                                        | 113 |

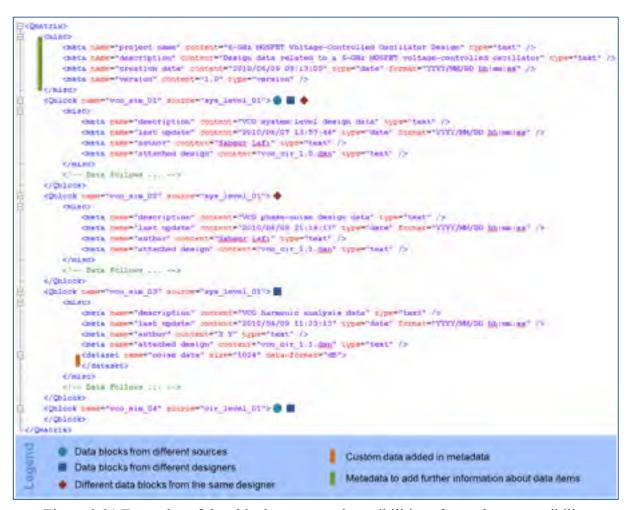

| Figure 3.21 | Examples of data blocks usage and possibilities of metadata extensibility.                                                                                                                                                                                    | 114 |

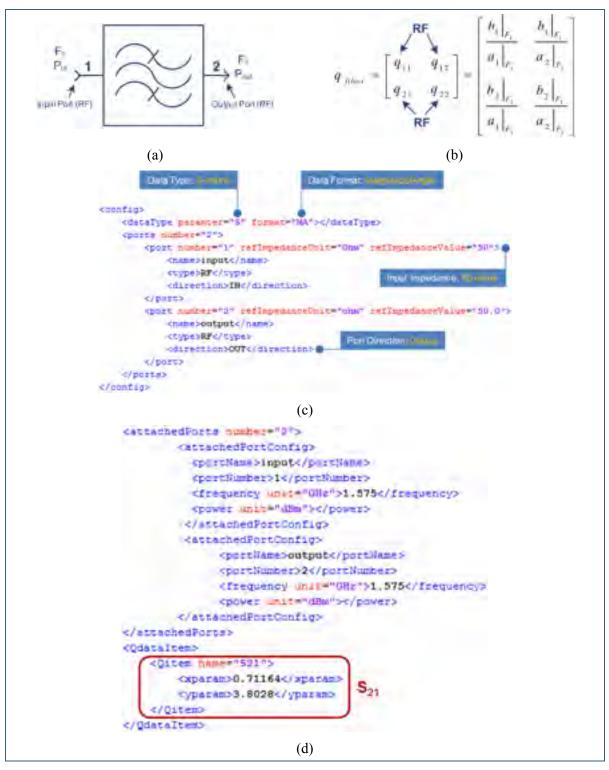

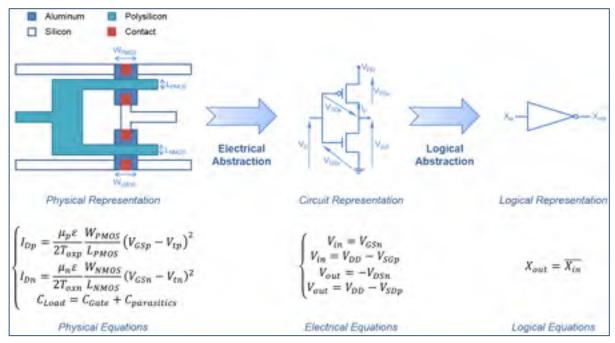

| Figure 3.22 | A usage example showing how the Q-matrix XML structure captures passive device's linear response: (a) RF filter model, (b) its corresponding Q-matrix and (c) data representation                                                                             | 116 |

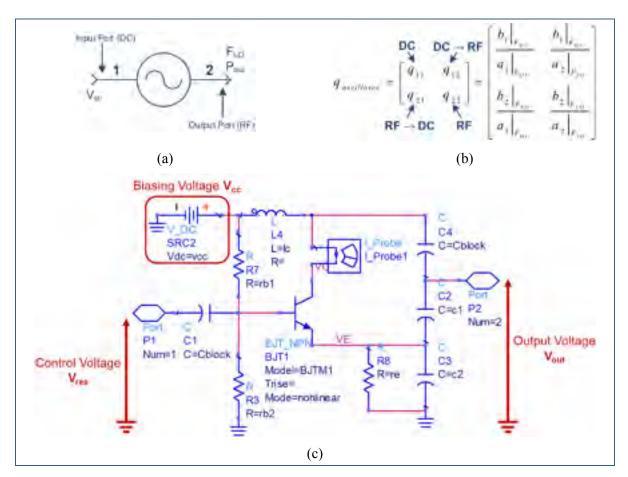

| Figure 3.23 | VCO's Q-matrix XML structure: (a) A voltage-controlled oscillator model, (b) its formal Q-matrix, (c) an example of a VCO circuit                                                                                                                             | 117 |

| Figure 3.24 | VCO's Q-matrix XML structure (cont'd): (a) the configuration section and (b) the data section (limited to only two points of control and output voltages)                                                                                                     | 118 |

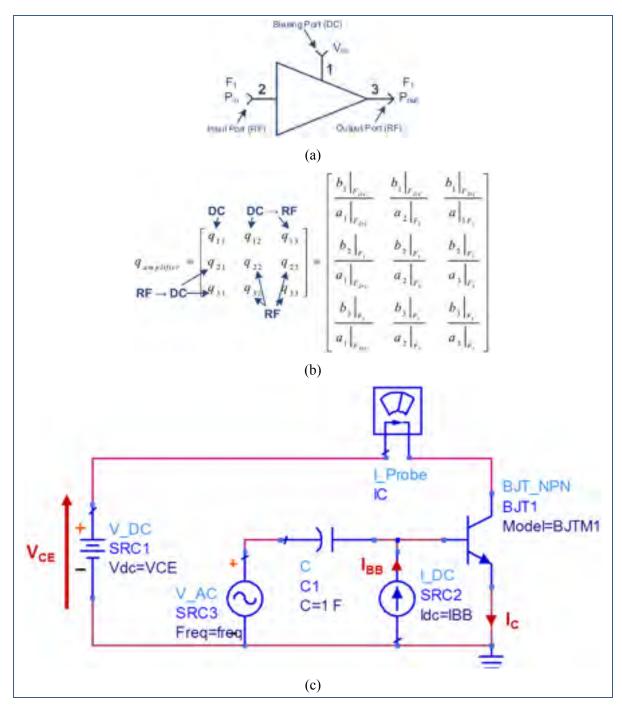

| Figure 3.25 | Q-matrix XML structure is also able to capture amplifier I-V data:  (a) Amplifier model, (b) its corresponding Q-matrix and  (c) an example of an amplifier circuit                                                      | 120 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.26 | Q-matrix XML structure is also able to capture amplifier I-V data: The data file corresponding to the amplifier model of Figure 3.25                                                                                     | 121 |

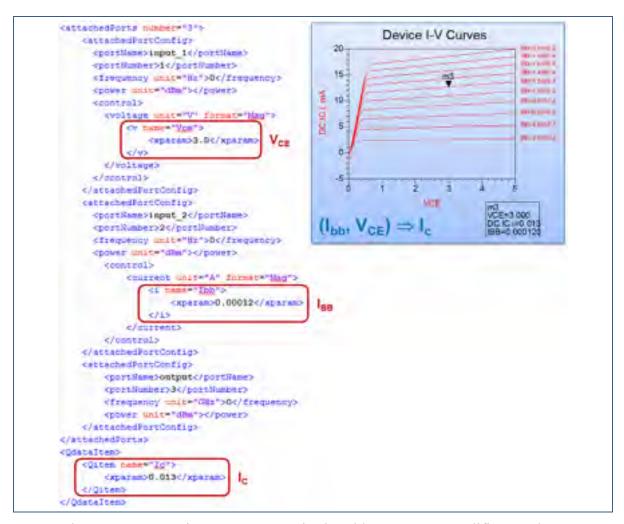

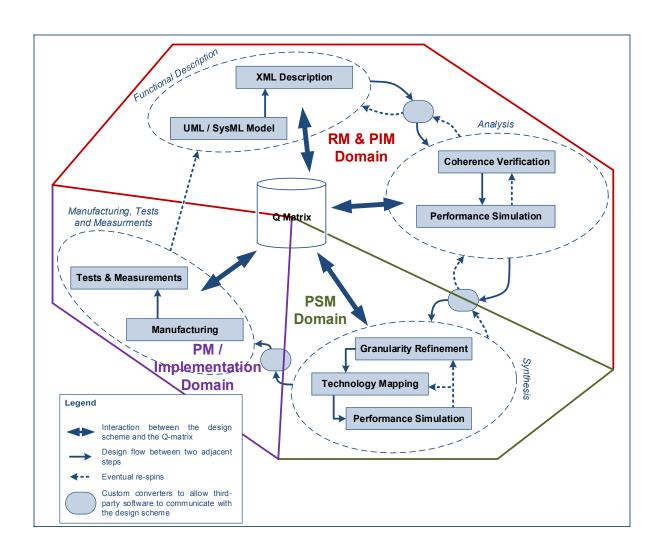

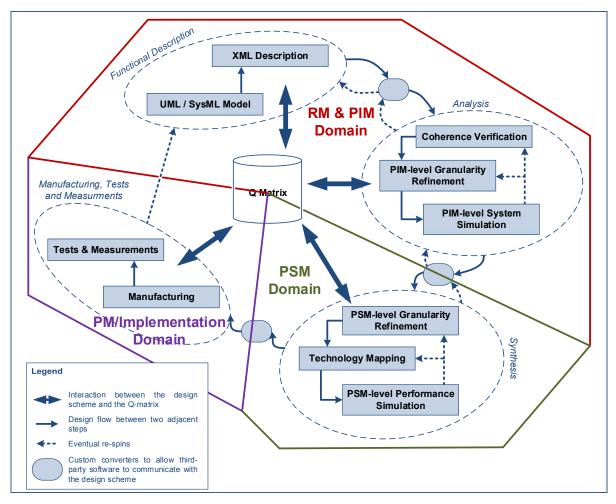

| Figure 3.27 | The proposed framework for RF and microwave design                                                                                                                                                                       | 123 |

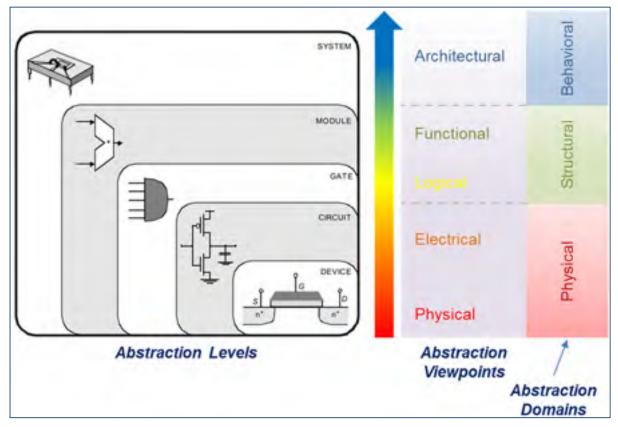

| Figure 4.1  | Every abstraction level corresponds to a new representation (i.e., model)                                                                                                                                                | 134 |

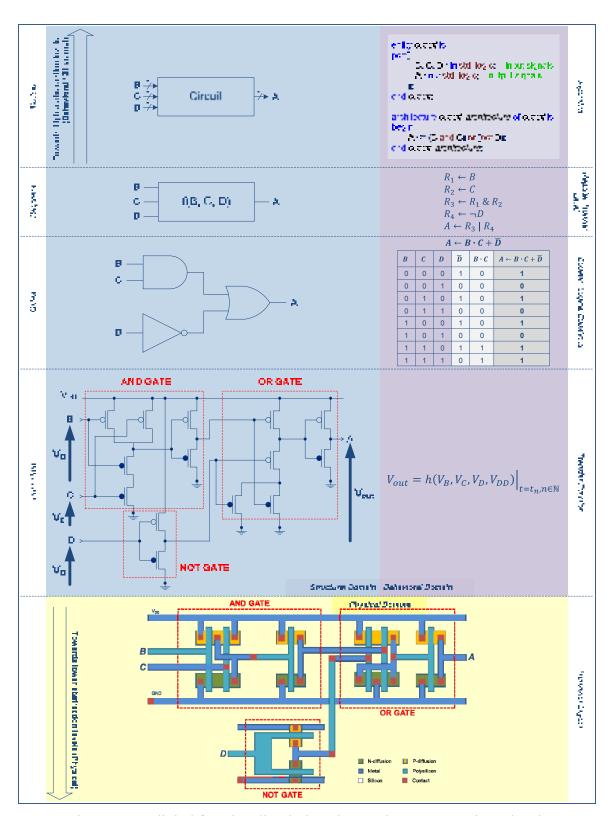

| Figure 4.2  | The five abstraction levels in digital circuit design correspond to five abstraction views subdivided into three distinct design domains                                                                                 | 137 |

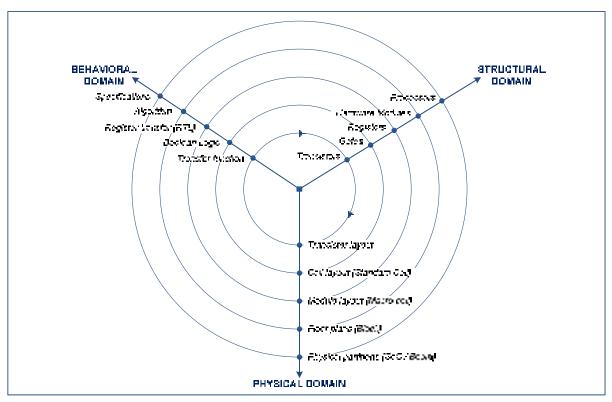

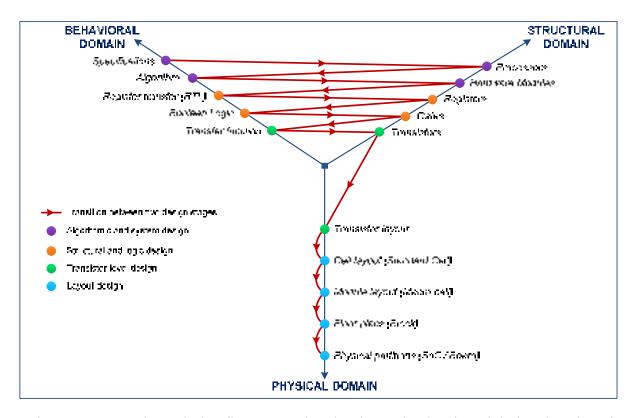

| Figure 4.3  | The three-domain five-abstraction-level Gajski-Kuhn's Y-chart                                                                                                                                                            | 138 |

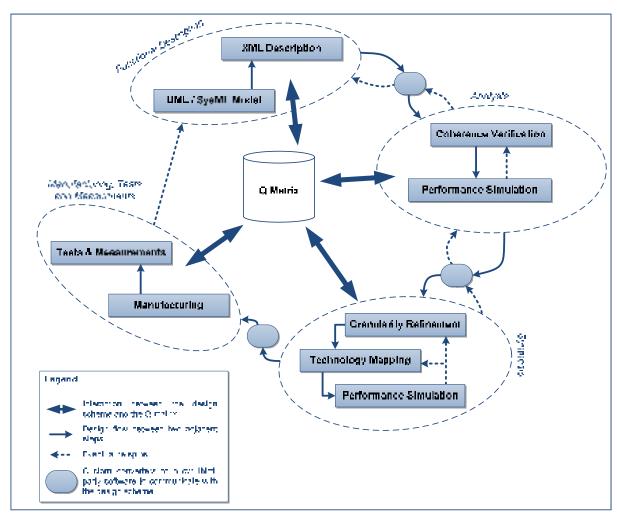

| Figure 4.4  | A digital functionality design changes its representation when it gradually goes through the behavioral, structural and physical domains                                                                                 | 141 |

| Figure 4.5  | A top-down design flow mapped to the abstraction levels and design domains of Gajski-Kuhn's Y-chart results in a back and forth top-down process.                                                                        | 142 |

| Figure 4.6  | Raising the abstraction levels allowed more complex device models                                                                                                                                                        | 142 |

| Figure 4.7  | Design automation tools, IC technologies and design methodologies in microelectronics have evolved jointly with abstraction levels                                                                                       | 143 |

| Figure 4.8  | Higher abstraction levels enable the design of more complex chips                                                                                                                                                        | 143 |

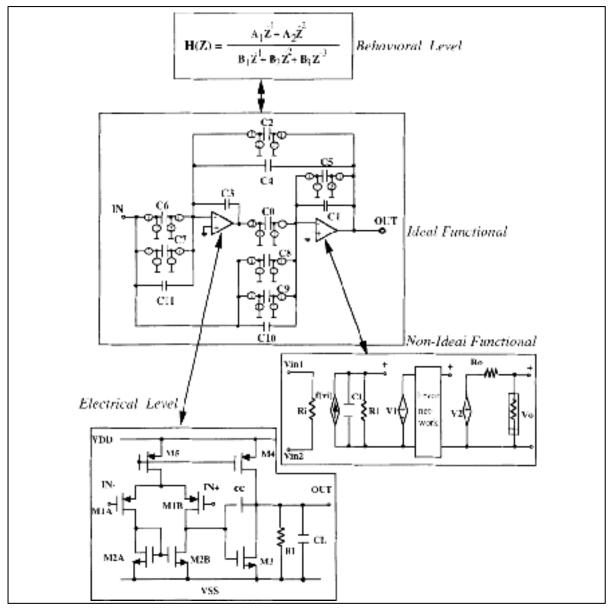

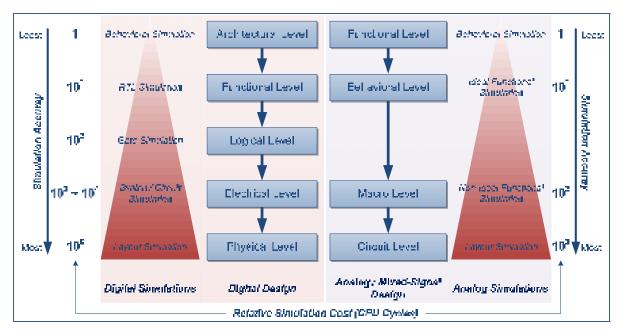

| Figure 4.9  | Notable differences between abstraction levels in digital and analog/mixed-signal design                                                                                                                                 | 145 |

| Figure 4.10 | A specific simulation type corresponds to each abstraction levels in analog/mixed-signal design                                                                                                                          | 146 |

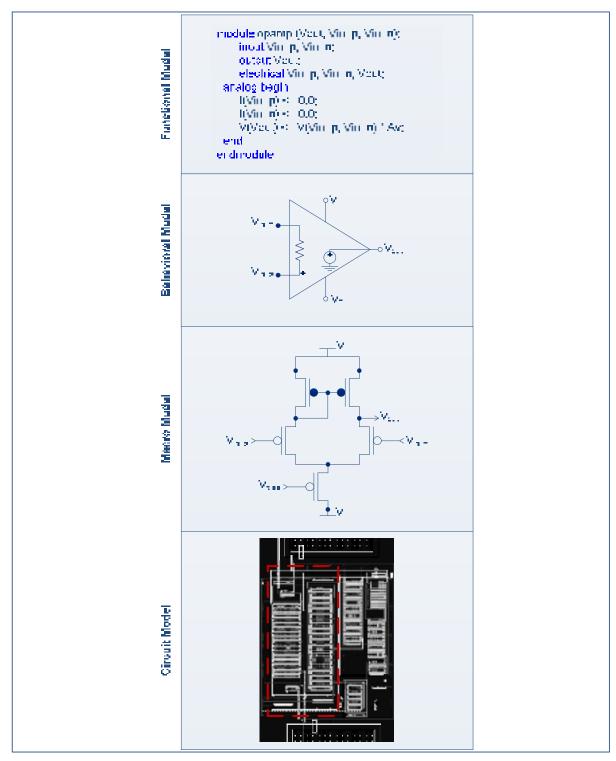

| Figure 4.11 | An example of how abstraction levels are applied to analog/mixed-signal design: A differential operational amplifier design starts as HDL description at functional level and ends with a useful layout at circuit level | 147 |

| Figure 4.12 | Each abstraction level corresponds to simulation type that is more time-consuming but accurate from higher to lower levels                                                                                               | 148 |

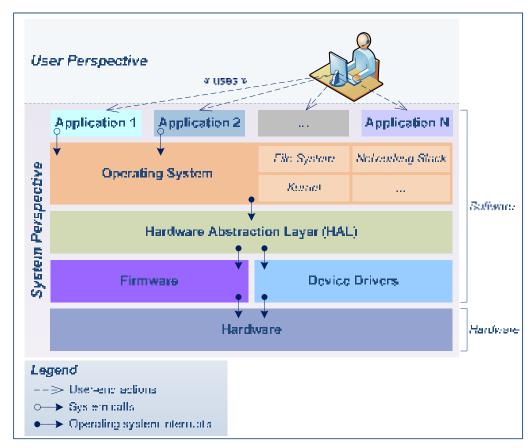

| Figure 4.13 | The hardware abstraction layer plays a mediation role between the operating system (and user applications) and the physical hardware                                                                                     | 150 |

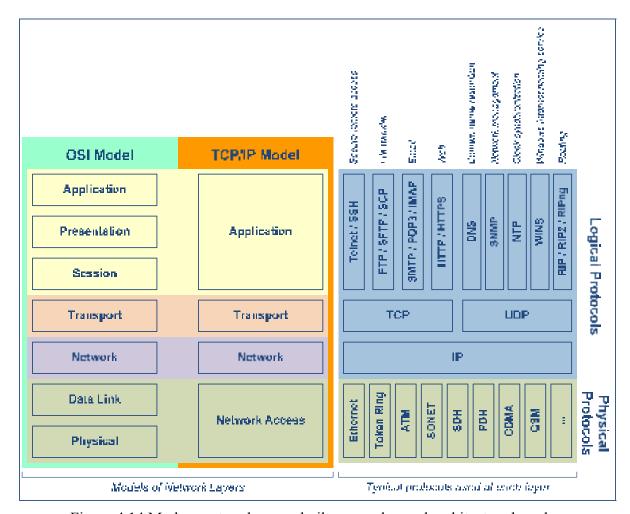

| Figure 4.14 | Modern networks were built upon a layered architecture based on OSI and TCP/IP networking models                                                                                                                                                     | 151 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

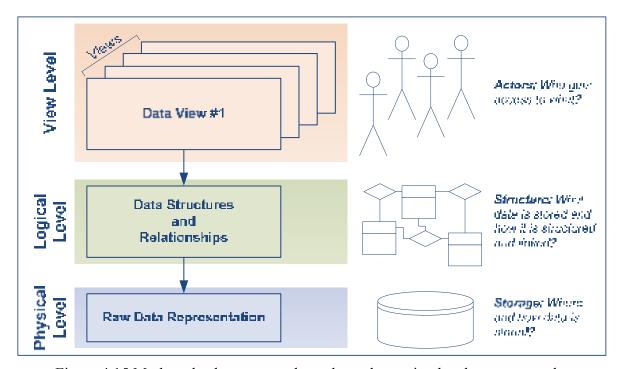

| Figure 4.15 | Modern databases use at least three abstraction levels to manage the stored data and control the interaction of users with them                                                                                                                      | 152 |

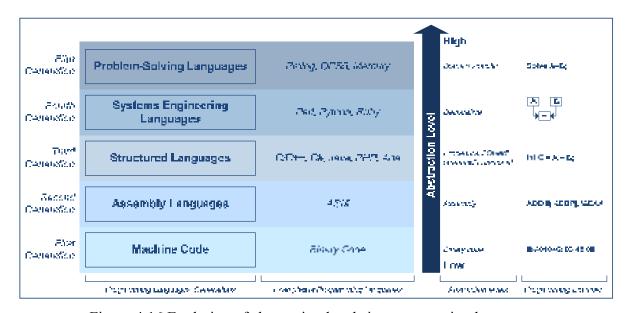

| Figure 4.16 | Evolution of abstraction levels in programming languages                                                                                                                                                                                             | 156 |

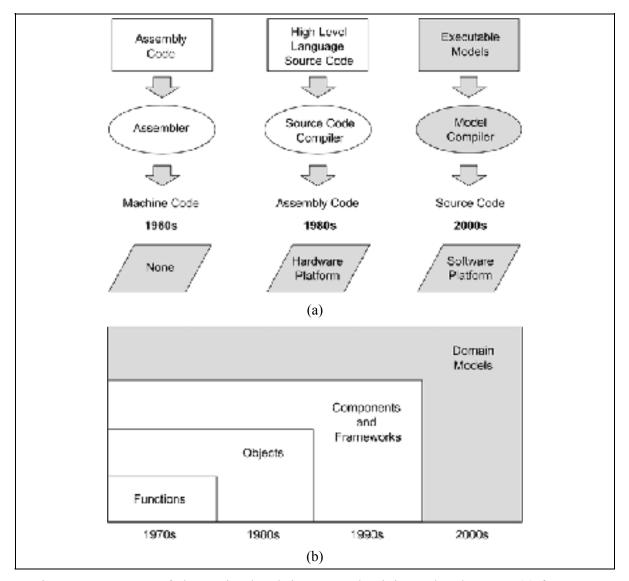

| Figure 4.17 | Impact of abstraction level rise on productivity and code reuse: (a) from one source for one system architecture to one model to multiple hardware/software platforms (b) Source code reuse started with functions and evolved towards domain models | 158 |

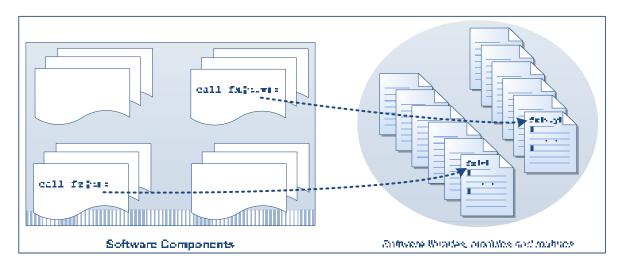

| Figure 4.18 | The modular programming paradigm subdivides a software system into independent, shared and reusable components                                                                                                                                       | 159 |

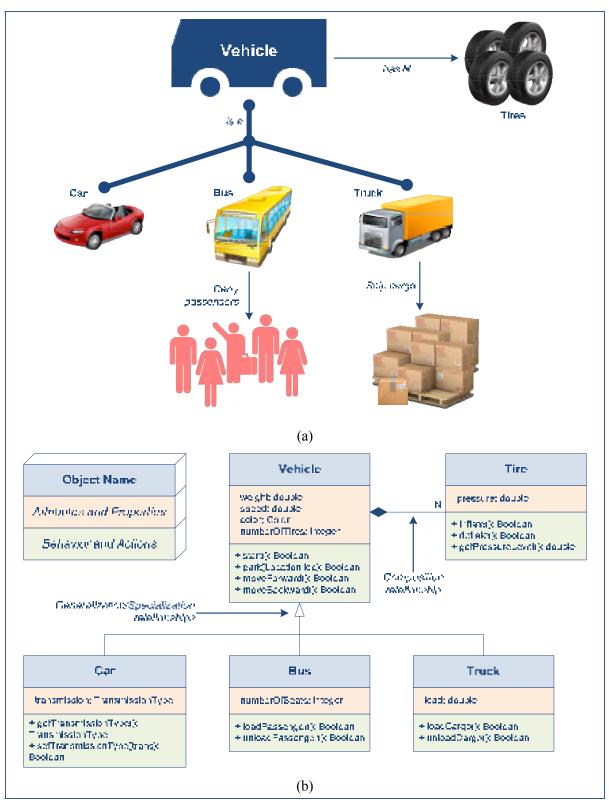

| Figure 4.19 | Abstraction through objects and classes: (a) real-world objects and (b) how they are modeled using a UML class diagram                                                                                                                               | 162 |

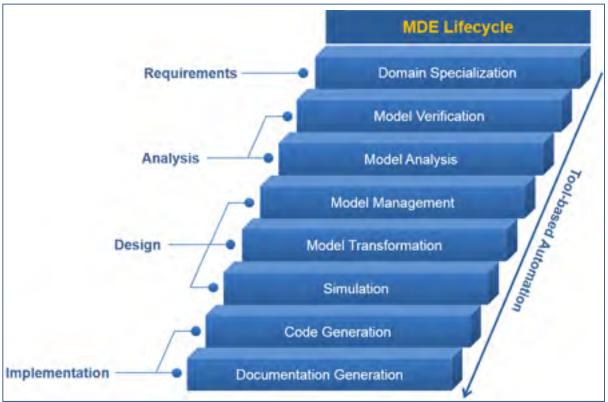

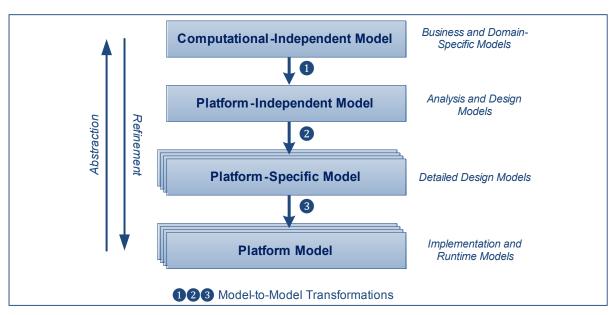

| Figure 4.20 | MDE enables the use of automated model-to-model transformation tools to enhance the automation of design steps                                                                                                                                       | 167 |

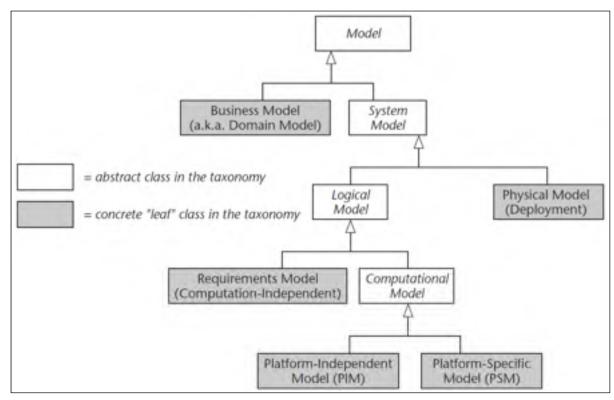

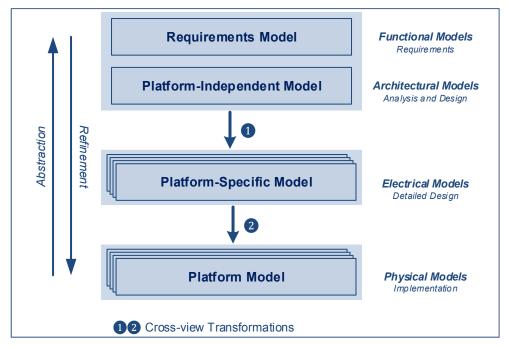

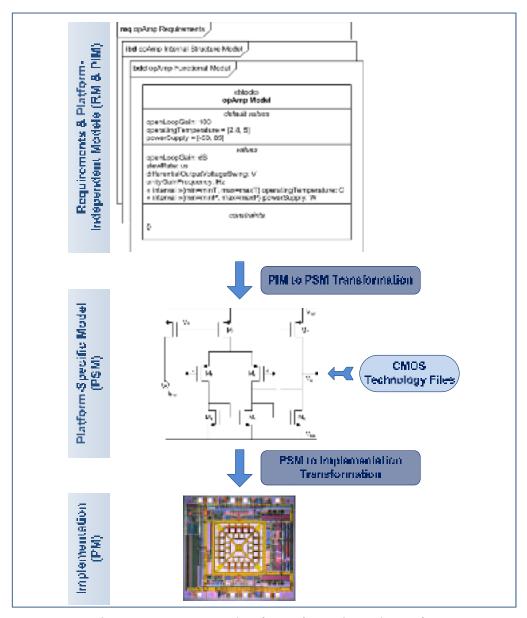

| Figure 4.21 | The model-driven architecture defines two types of models at different abstraction levels                                                                                                                                                            | 169 |

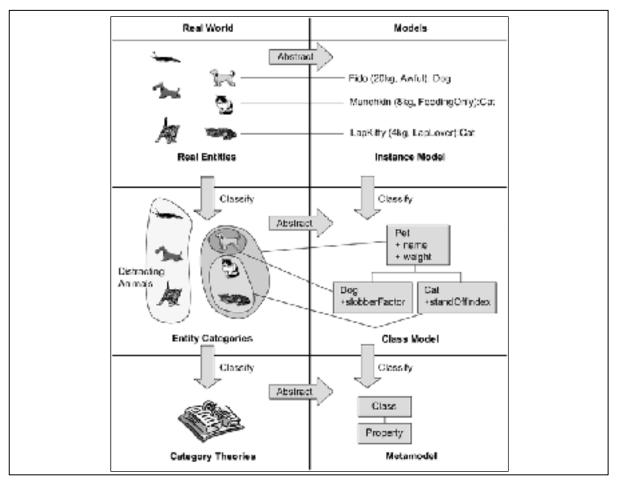

| Figure 4.22 | In MDE/MDA, a meta-model abstracts a model which itself abstracts a real-world reality                                                                                                                                                               | 171 |

| Figure 4.23 | Automation process in MDE/MDA framework encompasses four abstraction levels and three model-to-model transformations                                                                                                                                 | 175 |

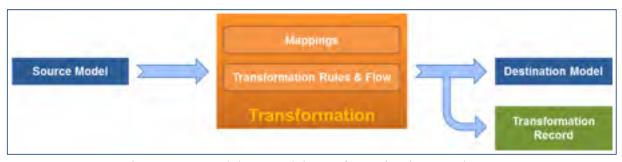

| Figure 4.24 | Model-to-Model transformation in MDE/MDA                                                                                                                                                                                                             | 175 |

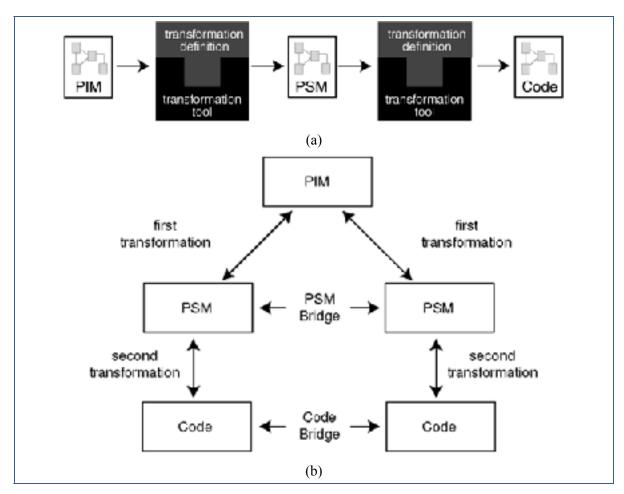

| Figure 4.25 | Model-to-Model transformation: (a) PIM to PSM transformation and (b) transformation bridges                                                                                                                                                          | 176 |

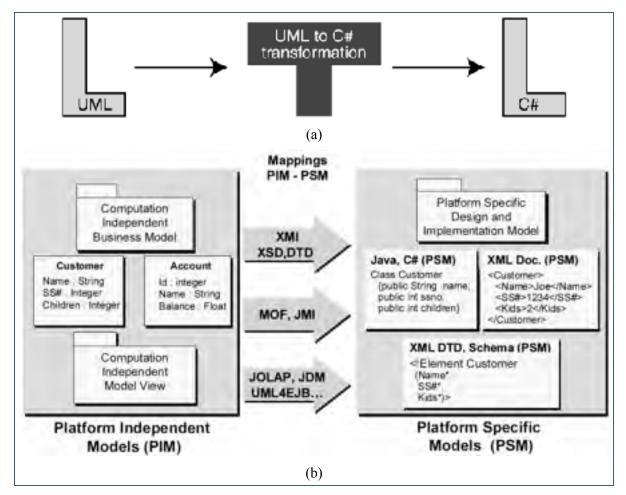

| Figure 4.26 | An example of PIM to PSM mapping: (a) UML to C# Transformation (b) The same PIM (i.e., UML models) is transformed into three PSMs (corresponding to three different source code representations) given the relevant platform specifications          | 177 |

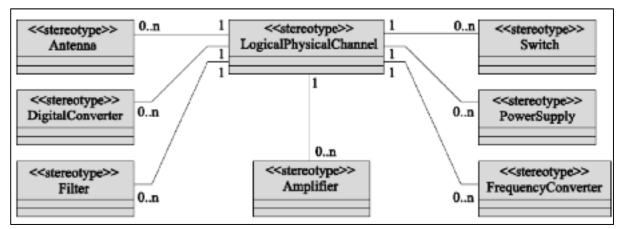

| Figure 4.27 | An excerpt of the UML profile for software radios: a logical-physical channel stereotype abstracts devices that provide analog communications (e.g., RF)                                                                                             | 179 |

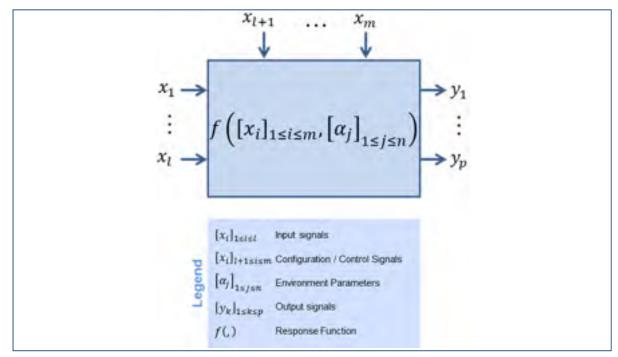

| Figure 4.28 | A black-box view considers a RF system as an entity which is defined by its inputs/outputs and its response function                                                                                                                                 | 183 |

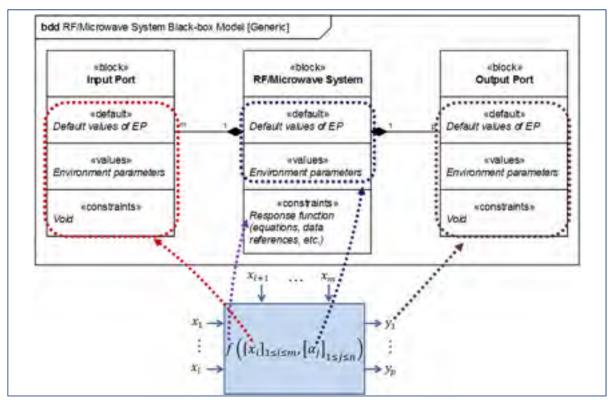

| Figure 4.29 | SysML black-box model of a RF system                                                                                                                                                                                                                                     | 192 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

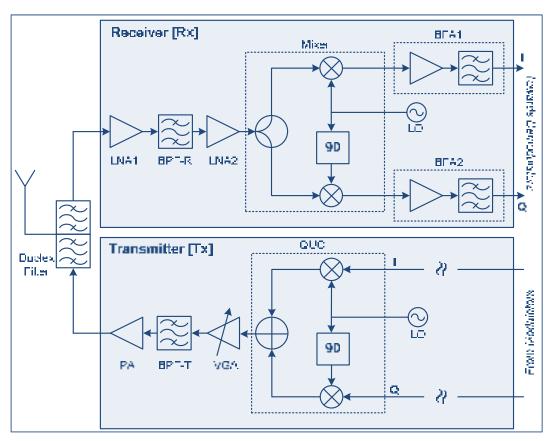

| Figure 4.30 | The block diagram of a UMTS FDD transceiver                                                                                                                                                                                                                              | 193 |

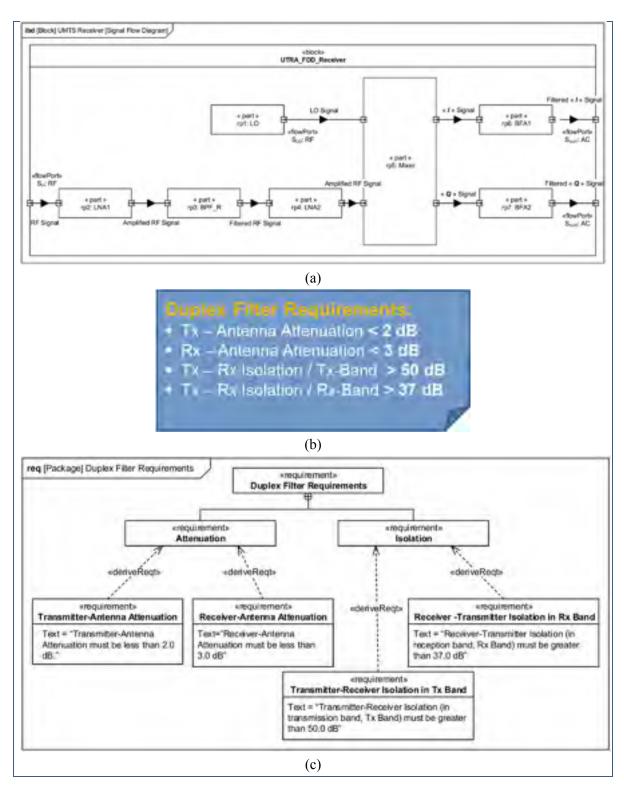

| Figure 4.31 | SysML allows the expression of different aspects in RF systems:  (a) package diagram (b) the transceiver's associated block definition diagram                                                                                                                           | 194 |

| Figure 4.32 | SysML allows the expression of different aspects in RF systems (cont'd): (a) the receiver's internal block diagram (b) the duplex filter specifications (c) the duplex filter requirements diagram                                                                       | 195 |

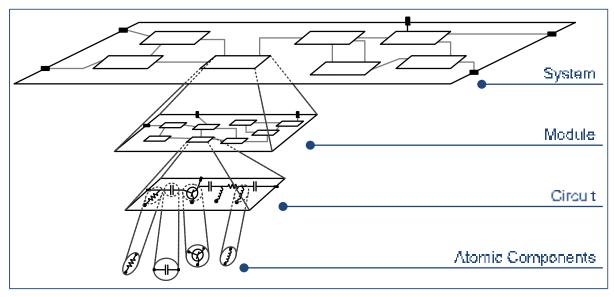

| Figure 4.33 | Four abstraction levels are considered in the proposed RF hardware abstraction strategy: System, module, circuit and atomic components                                                                                                                                   | 200 |

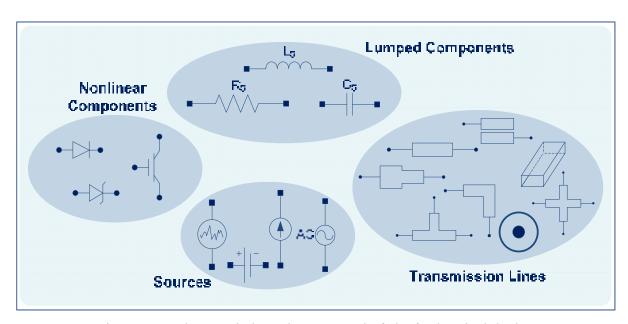

| Figure 4.34 | The atomic layer is composed of "leaf" electrical devices whose functions are not indivisible                                                                                                                                                                            | 201 |

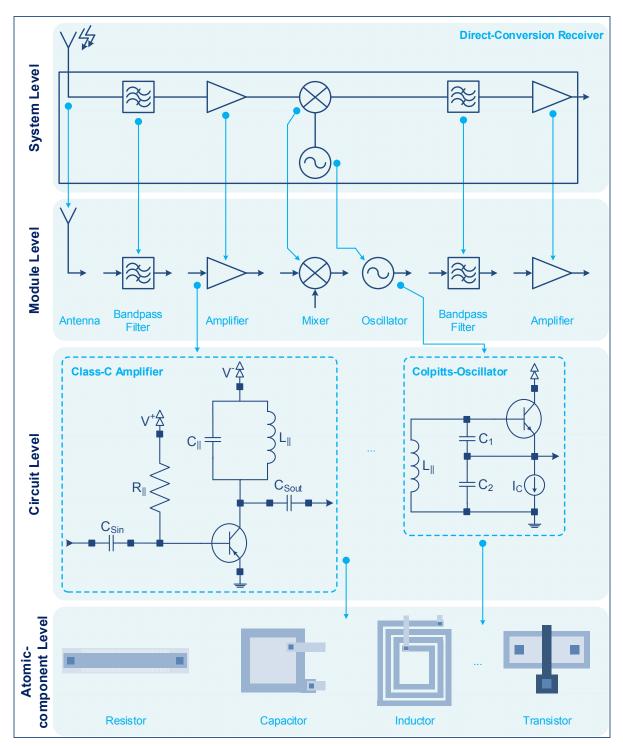

| Figure 4.35 | An example of how the different abstraction levels are considered in a typical RF system                                                                                                                                                                                 | 205 |

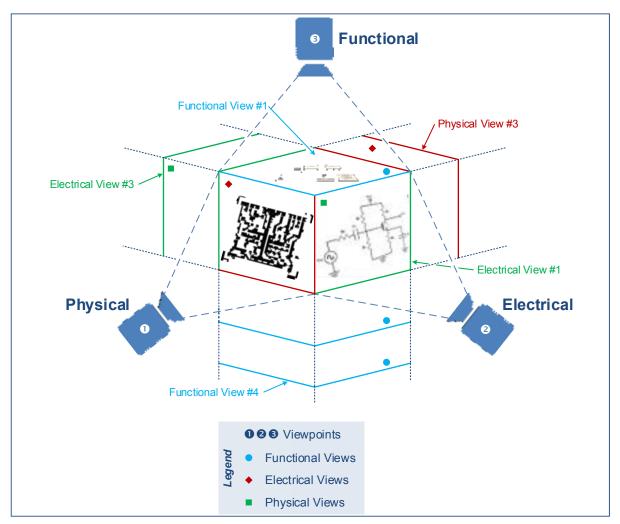

| Figure 4.36 | A viewpoint corresponds to an abstract design perspective while a view specifies a representation (i.e., model) which complies with that design perspective                                                                                                              | 207 |

| Figure 4.37 | Four abstraction views are associated to four abstraction viewpoints and four abstraction levels                                                                                                                                                                         | 209 |

| Figure 4.38 | Two transformations are defined to move from system requirements throughout implementation                                                                                                                                                                               | 210 |

| Figure 4.39 | Cross- and intra-view transformations                                                                                                                                                                                                                                    | 214 |

| Figure 4.40 | Granularity is all about the level of detail within an abstraction view:  (a) the system is composed of seven blocks (b) one of these seven blocks can be broken up into eight other parts                                                                               | 216 |

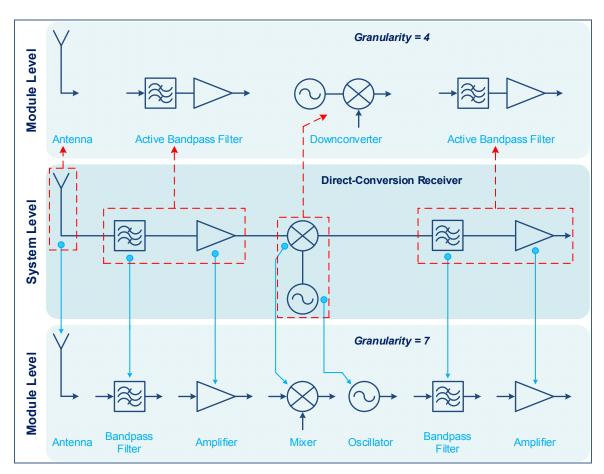

| Figure 4.41 | A system-level model of a direct-conversion receiver can be partitioned in modules in different ways of different granularity levels                                                                                                                                     | 217 |

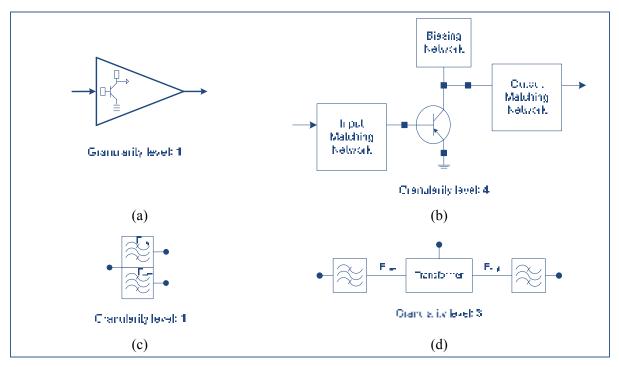

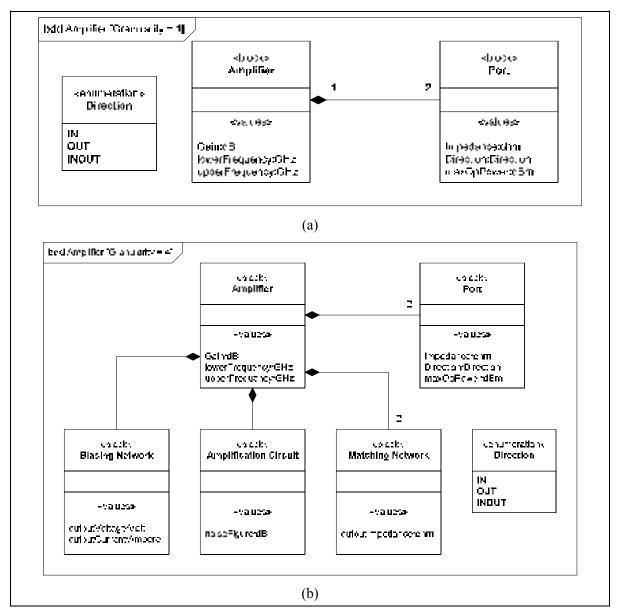

| Figure 4.42 | Two examples of granularity level expressed using SysML block definition diagram: (a) An amplifier is considered as whole [Granularity level = 1] (b) An amplifier is considered as an assembly of amplification, matching, and biasing networks [Granularity level = 4] | 219 |

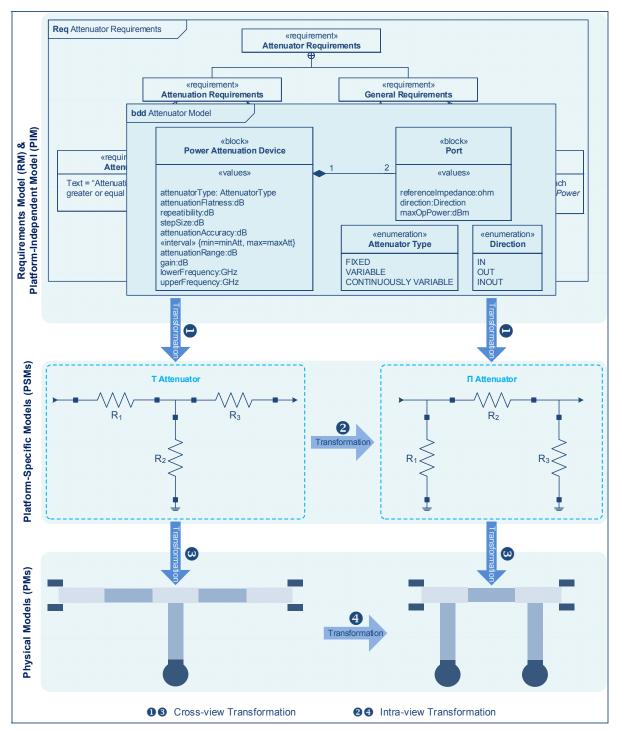

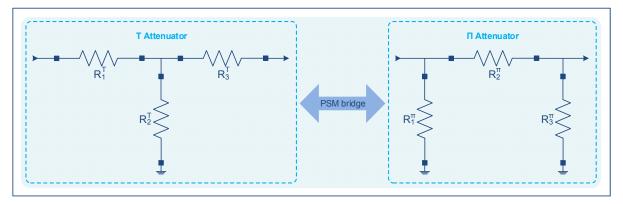

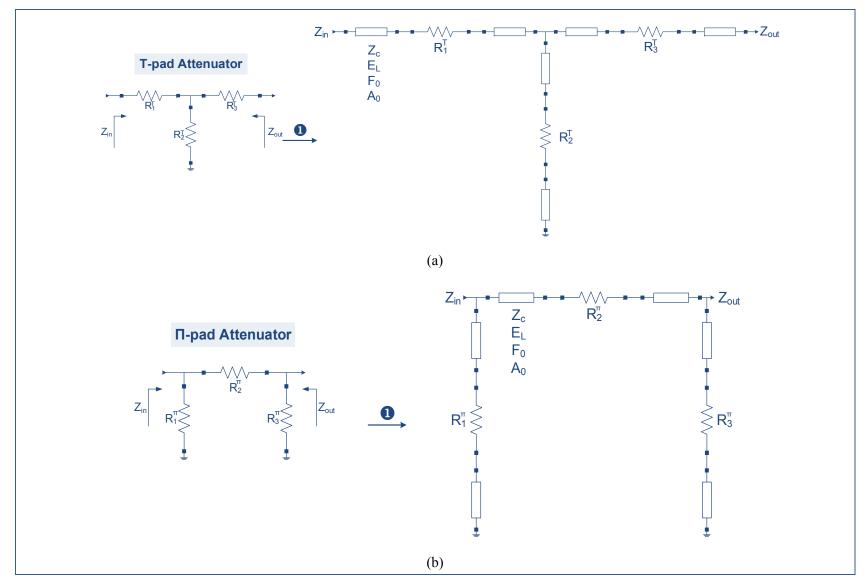

| Figure 4.43 | Reversible platform-specific model for resistive attenuators                                                                                                                                                                                                             | 220 |

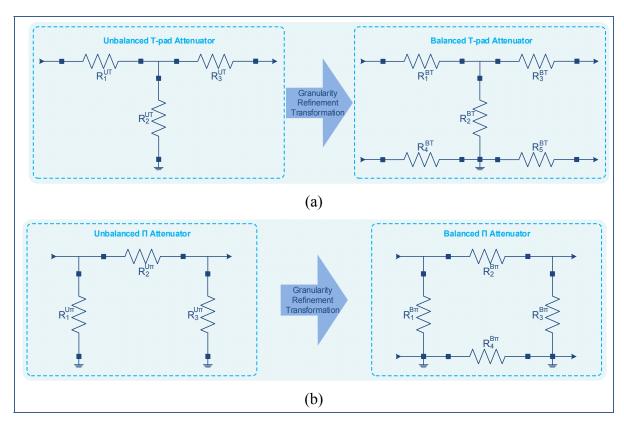

| Figure 4.44 | Granularity refinement: (a) Unbalanced to balanced T and (b) $\pi$ attenuator transformations                       | 222 |

|-------------|---------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.45 | An example of overriding a default constraint property using a new equation for the calculation of variable weights | 225 |

| Figure 4.46 | The four abstraction views can be mapped to traditional passive RF filters design steps                             | 229 |

| Figure 4.47 | An example of transformation scheme for operational amplifier design                                                | 232 |

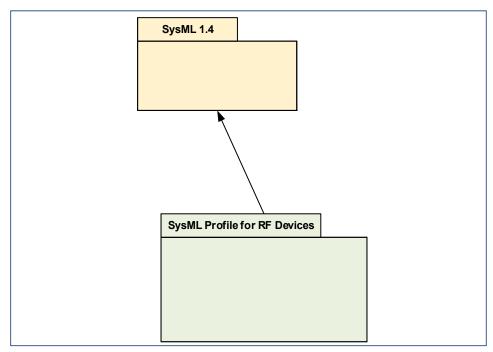

| Figure 4.48 | The proposed profile extends SysML standard (version 1.4) with specific constructs that are intended for RF domain  | 234 |

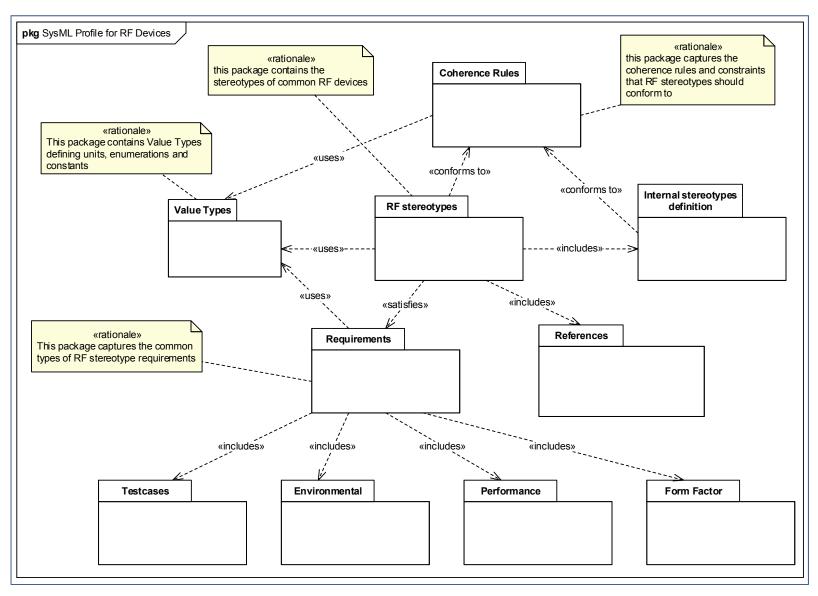

| Figure 4.49 | The package diagram describing the structure of and the relationships within the proposed SysML profile             | 236 |

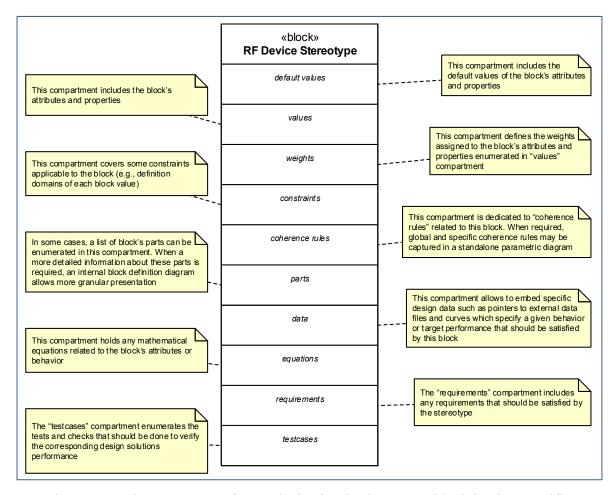

| Figure 4.50 | The stereotype of a RF device is a basic SysML block having specific compartments for RF modeling                   | 237 |

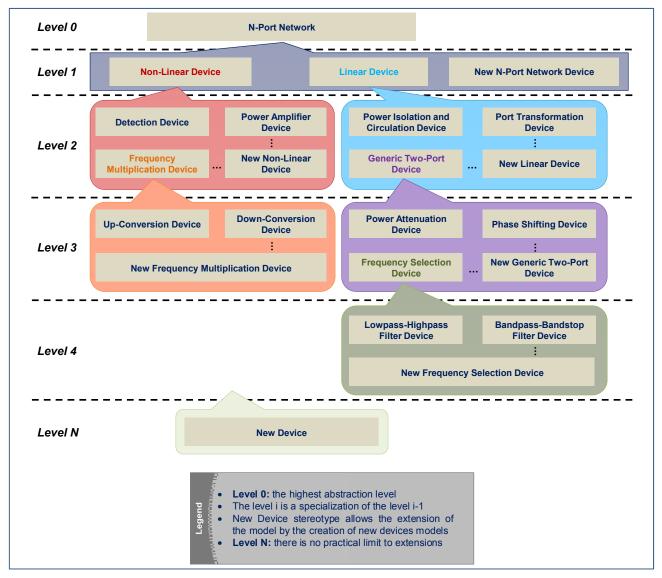

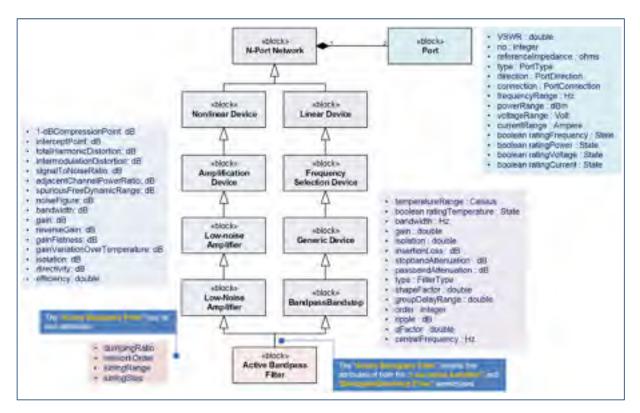

| Figure 4.51 | At the functional level, RF stereotypes are hierarchically structured                                               | 241 |

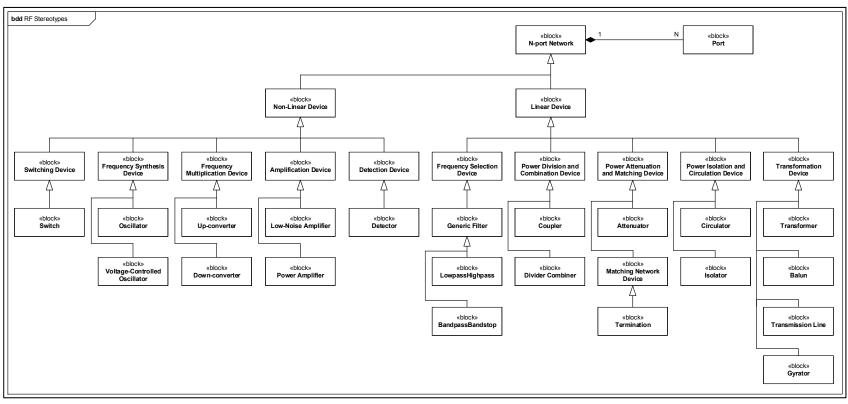

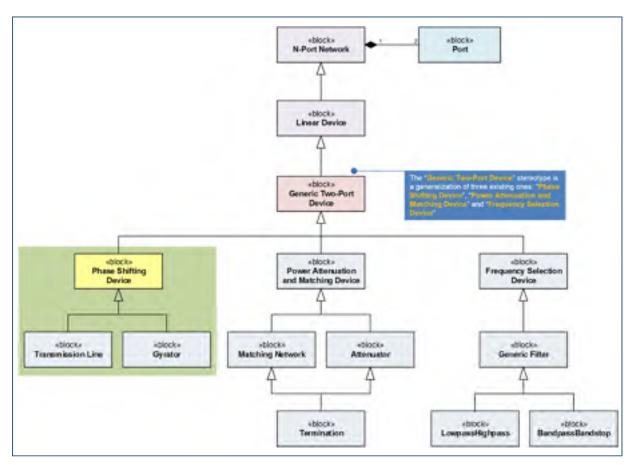

| Figure 4.52 | A SysML bdd depicting a generic view of RF stereotypes                                                              | 242 |

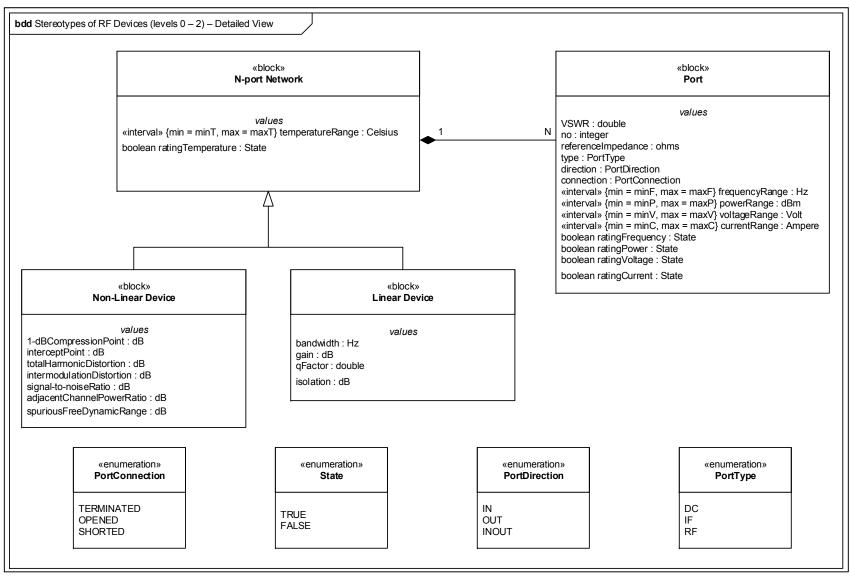

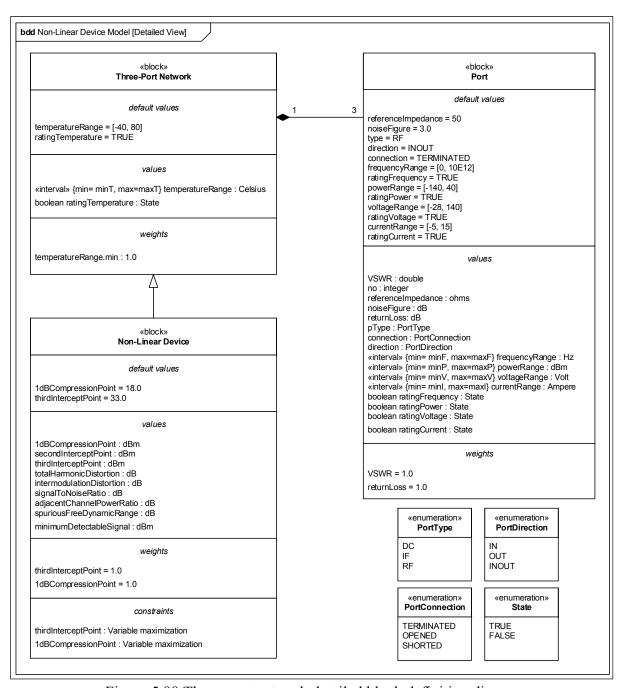

| Figure 4.53 | N-port network stereotype                                                                                           | 243 |

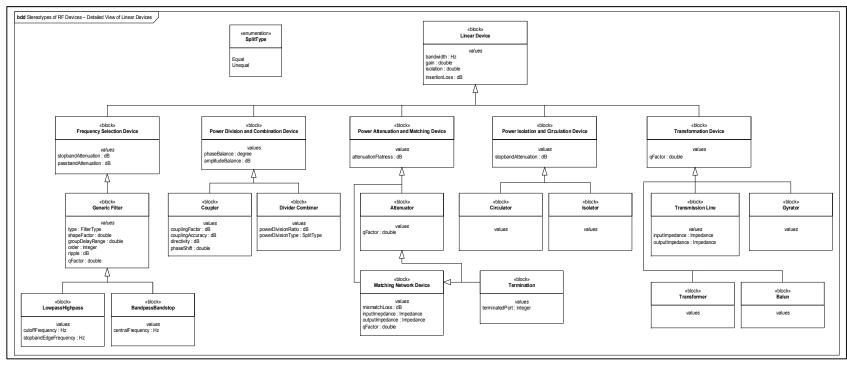

| Figure 4.54 | Value properties of linear devices                                                                                  | 244 |

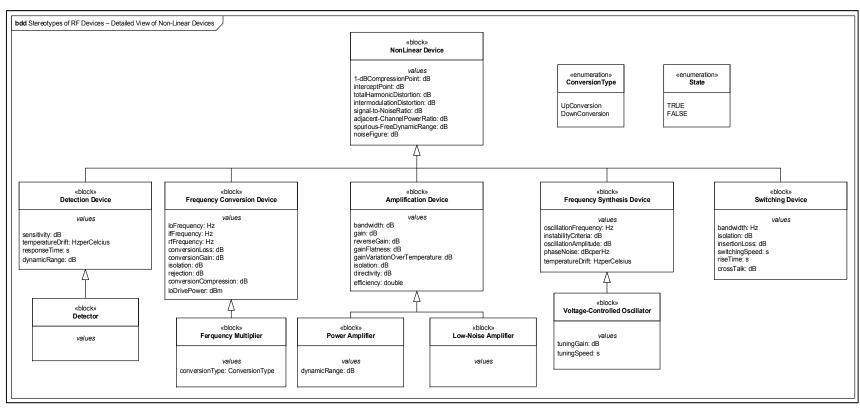

| Figure 4.55 | Value properties of nonlinear devices                                                                               | 245 |

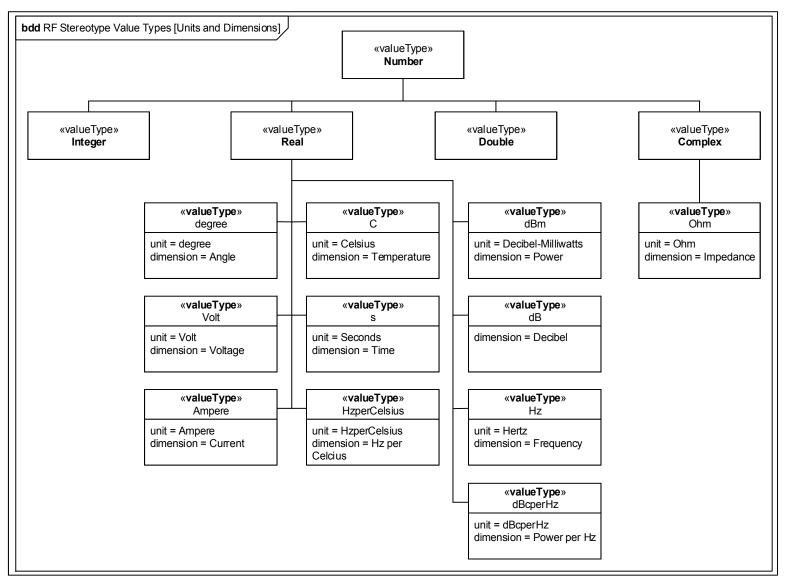

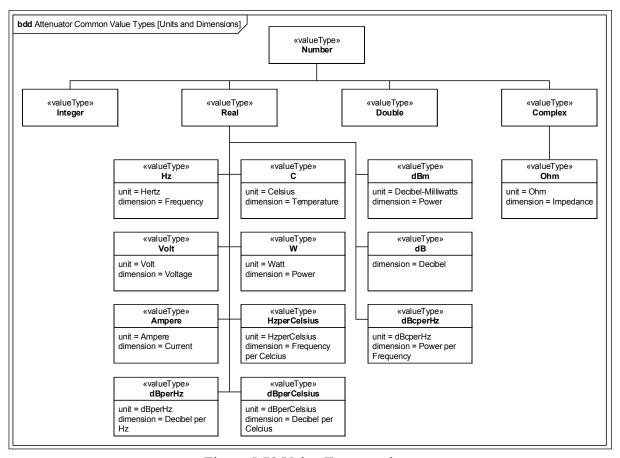

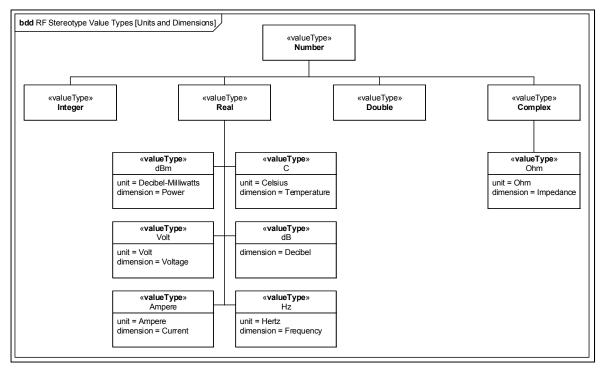

| Figure 4.56 | Common units and dimensions used in RF design are part of the Value Types package to avoid ambiguity                | 246 |

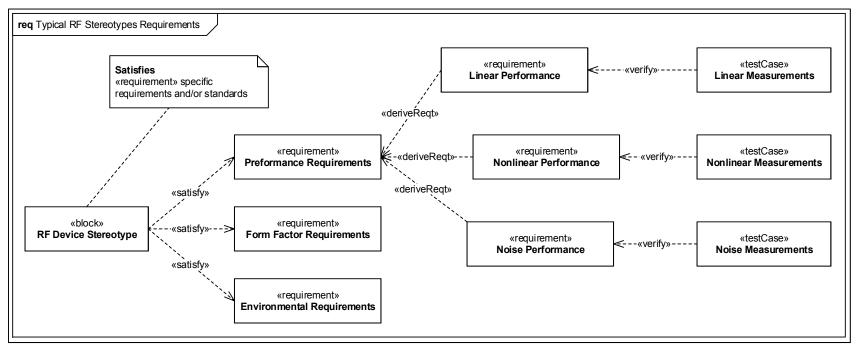

| Figure 4.57 | Common requirements and testcases required for RF devices design                                                    | 247 |

| Figure 4.58 | The constructs of the proposed SysML profile are subject to extension and modification                              | 249 |

| Figure 4.59 | An active bandpass filter block extends and reuses "Low-noise Amplifier" and "BandpassBandstop" stereotypes         | 250 |

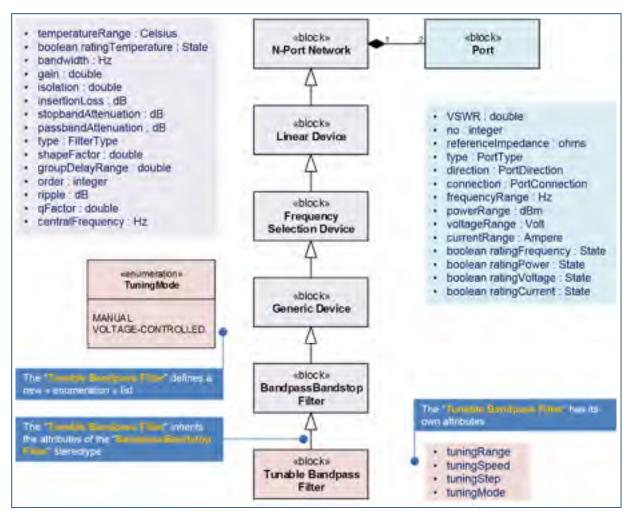

| Figure 4.60 | A tunable bandpass filter extends and reuses the block "BandpassBandstop"                                           | 251 |

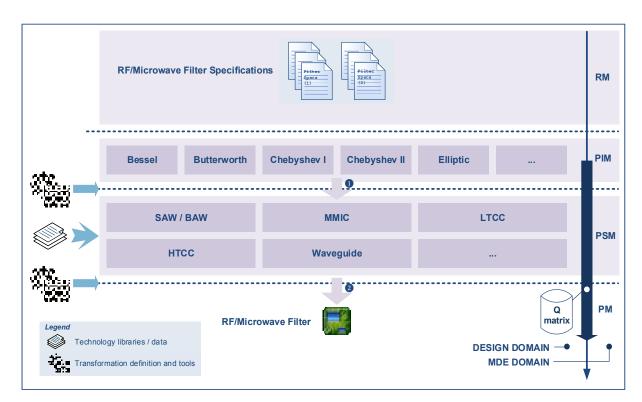

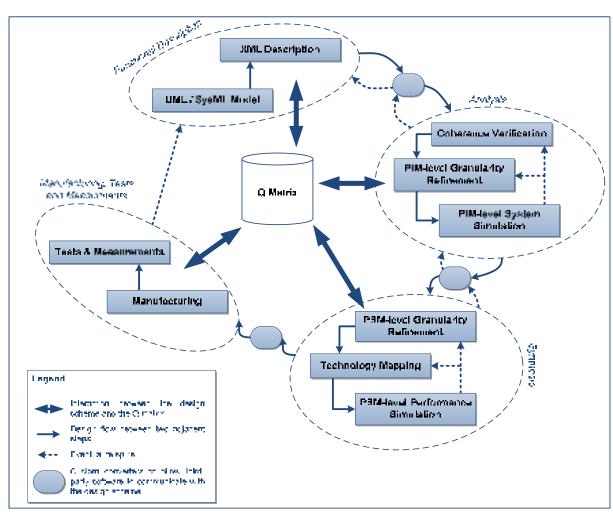

| Figure 4.61 | Streamlining the proposed design framework with the RF/microwave abstraction strategy                               | 254 |

| Figure 4.62 | Introducing granularity refinement at PIM-level to enhance design space exploration and at PSM-level to improve physical implementation | 254 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.63 | Streamlining the proposed design framework with the RF/microwave abstraction strategy                                                   | 255 |

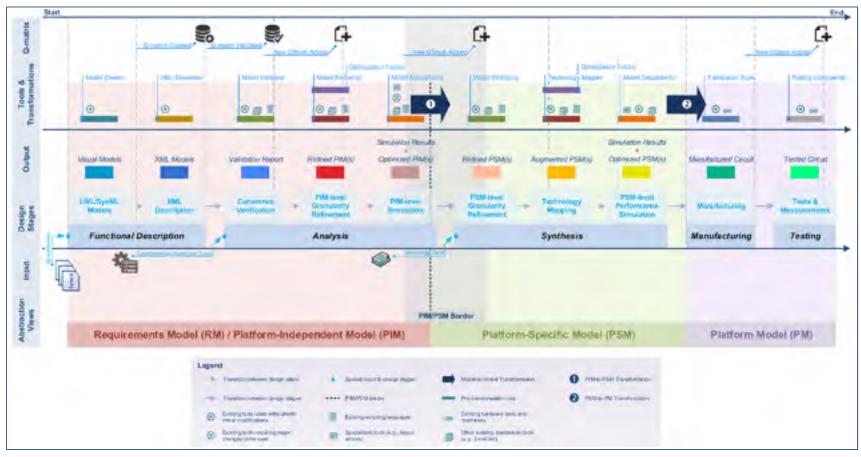

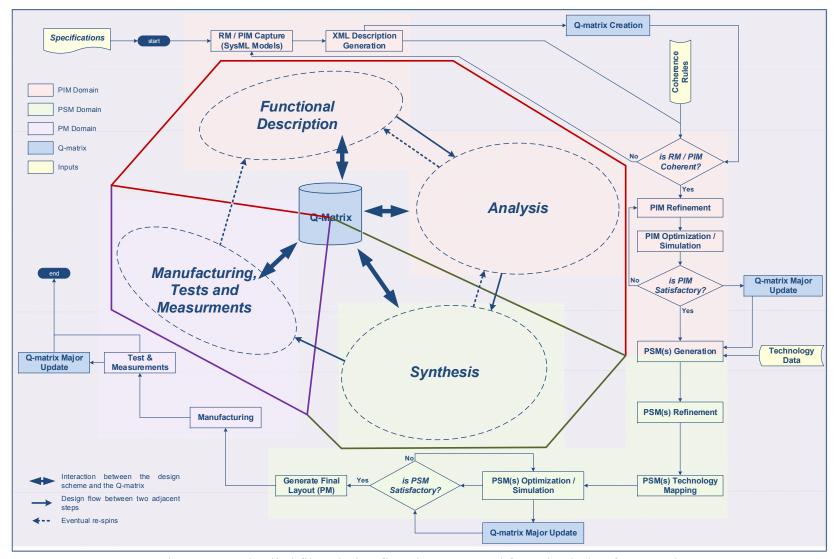

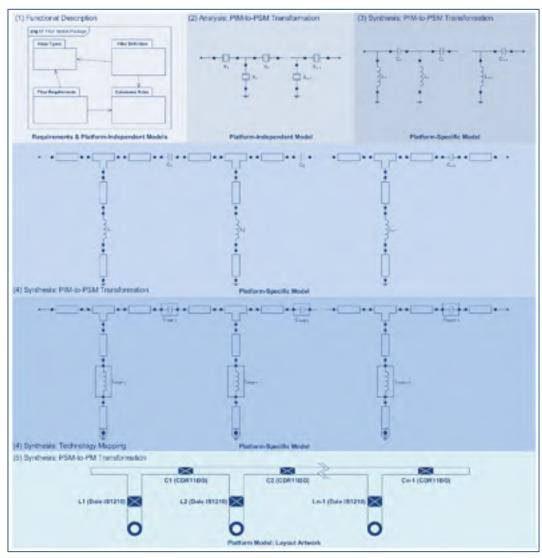

| Figure 5.1  | Detailed flowchart of the proposed design framework                                                                                     | 268 |

| Figure 5.2  | A detailed filter design flowchart extracted from the design framework                                                                  | 269 |

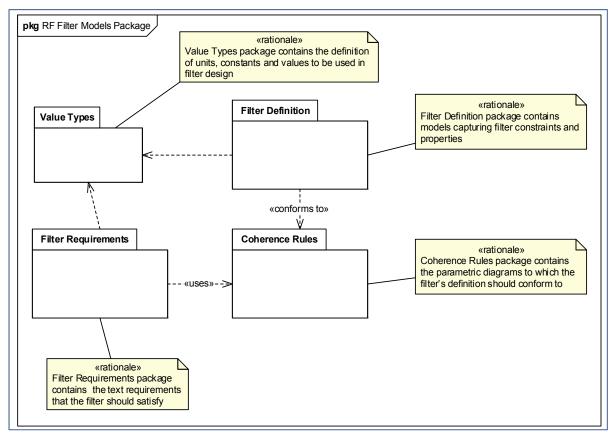

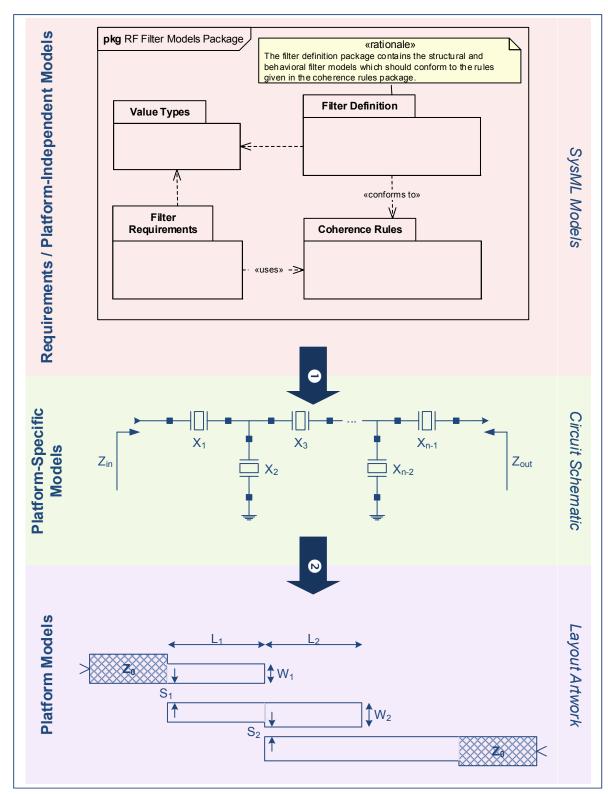

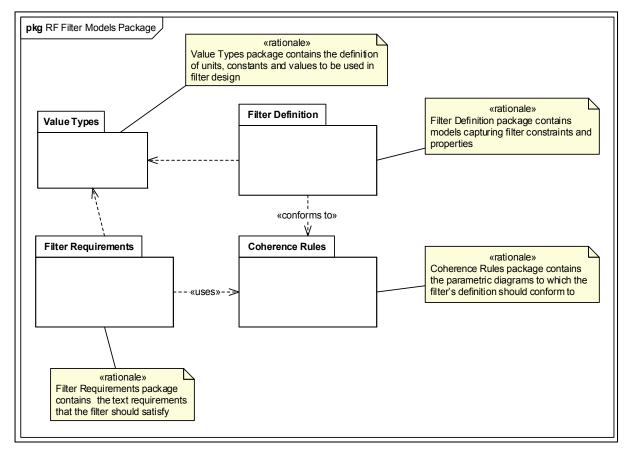

| Figure 5.3  | This package diagram gives an overview of the filter's SysML RM/PIM models                                                              | 272 |

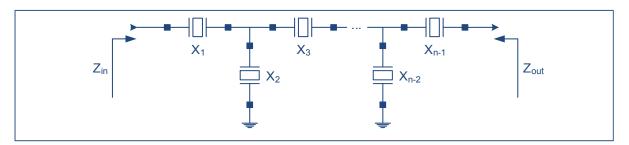

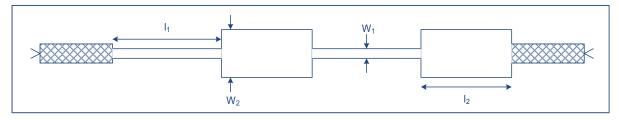

| Figure 5.4  | The filter's PSM consists of an ideal resonators' network                                                                               | 272 |

| Figure 5.5  | A distributed-line layout artwork is a potential filter PM model                                                                        | 272 |

| Figure 5.6  | Model-to-model transformations convert RM/PIM to PSMs and PSMs into PMs                                                                 | 273 |

| Figure 5.7  | The main parameters of a RF bandpass filter                                                                                             | 274 |

| Figure 5.8  | An overview of filter RM/PIM models developed in SysML                                                                                  | 277 |

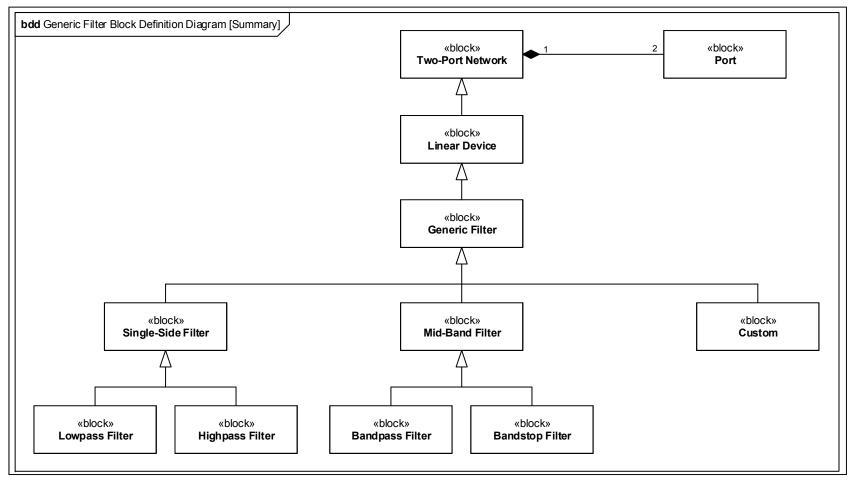

| Figure 5.9  | A filter is a two-port linear device                                                                                                    | 278 |

| Figure 5.10 | Linear device detailed block definition diagram                                                                                         | 279 |

| Figure 5.11 | Generic filter detailed block definition diagram                                                                                        | 280 |

| Figure 5.12 | Value types captured in a bdd for the filter's RM/PIM models                                                                            | 281 |

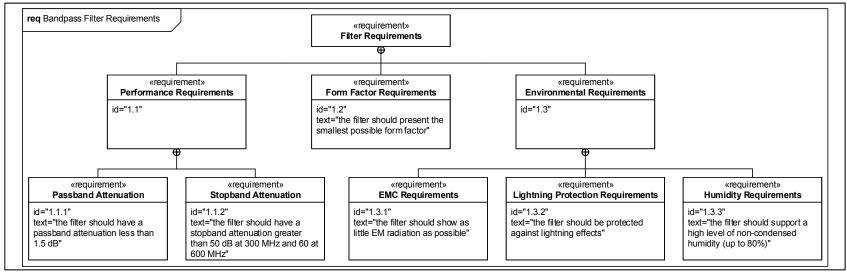

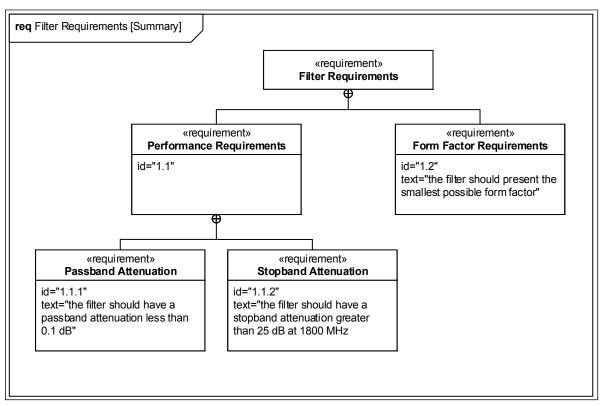

| Figure 5.13 | Detailed filter requirements diagram.                                                                                                   | 281 |

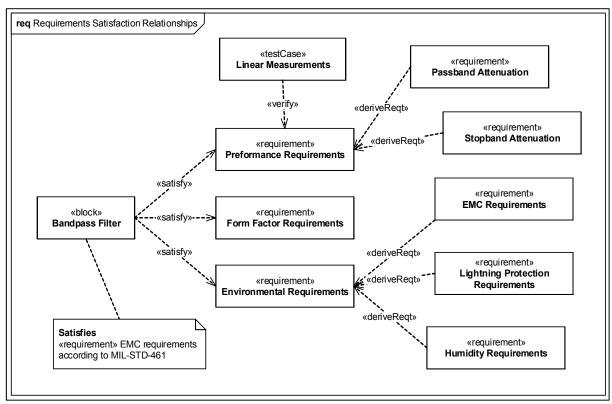

| Figure 5.14 | The bandpass filter might be explicitly associated to its requirements and testcases                                                    | 282 |

| Figure 5.15 | The bandpass filter coherence rules package consists of four interrelated sub-packages                                                  | 285 |

| Figure 5.16 | Electrical consistence rules illustrated in a parametric diagram                                                                        | 286 |

| Figure 5.17 | Integrity control rules captured using in a parametric diagram                                                                          | 287 |

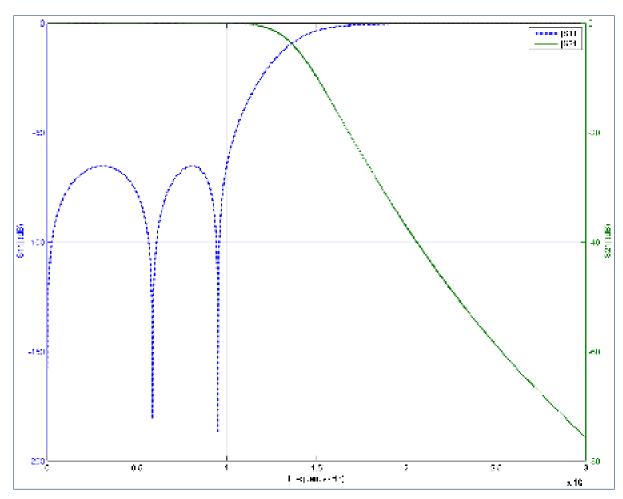

| Figure 5.18 | Parametric diagram has multiple uses (a) PIM-level design constraints, (b) Mapping of equations' parameters                             | 288 |

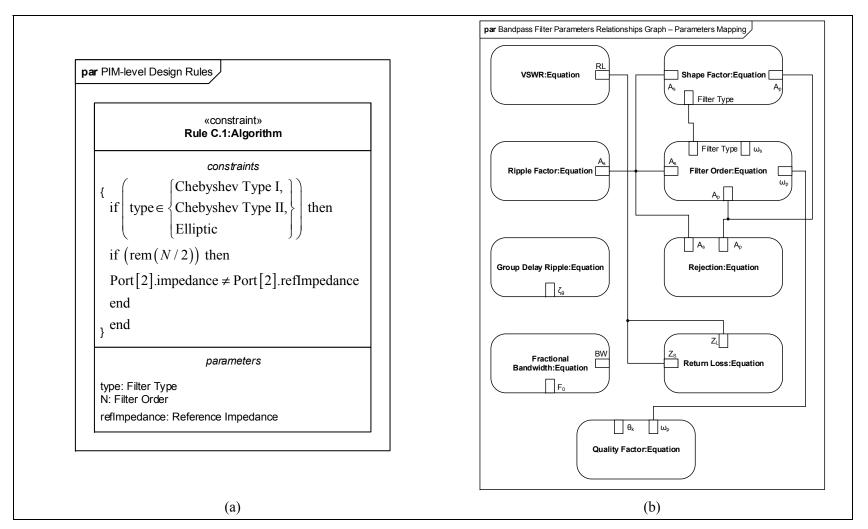

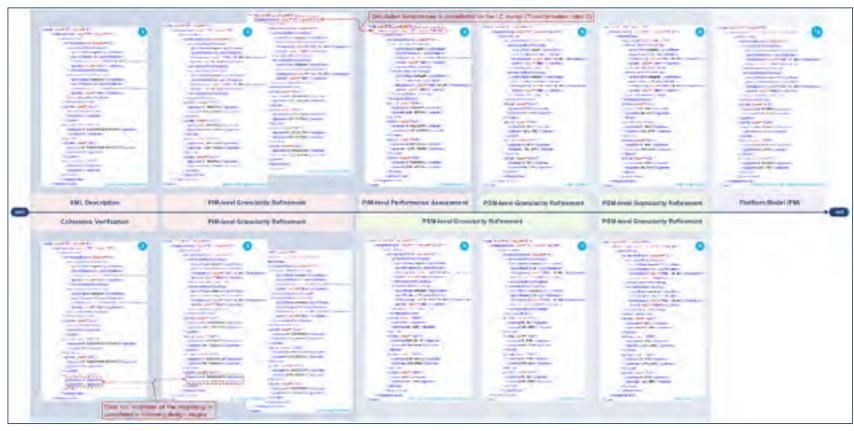

| Figure 5.19 | Overview of the RM/PIM's XML description file                                                                                           | 289 |

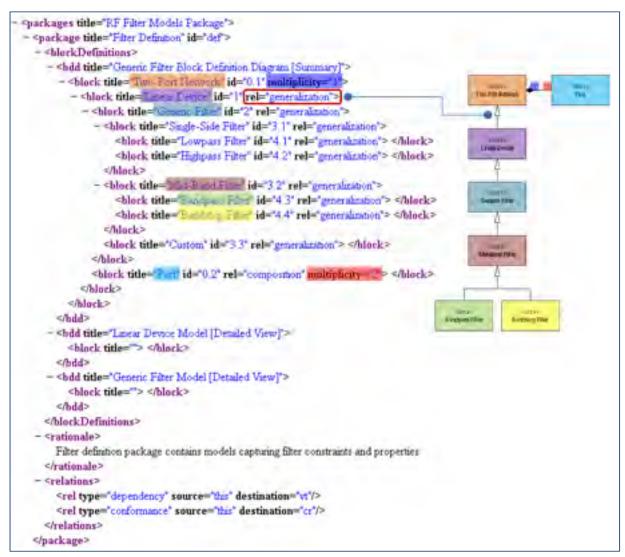

| Figure 5.20  | The XML description corresponding to the "Filter Definition" package                                         | 290 |

|--------------|--------------------------------------------------------------------------------------------------------------|-----|

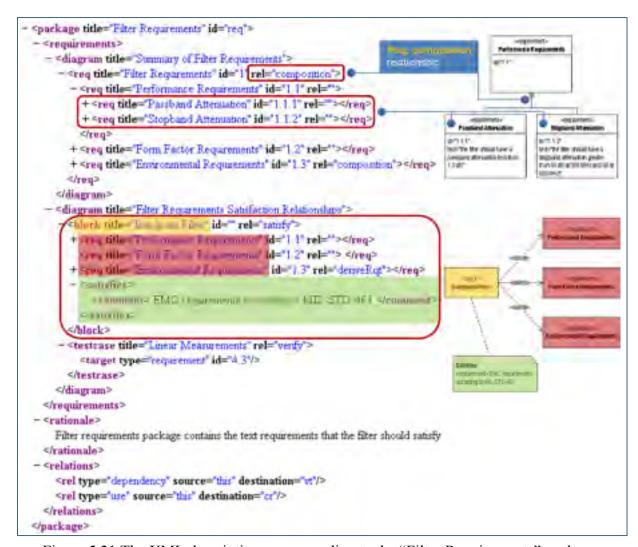

| Figure 5.21  | The XML description corresponding to the "Filter Requirements" package                                       | 291 |

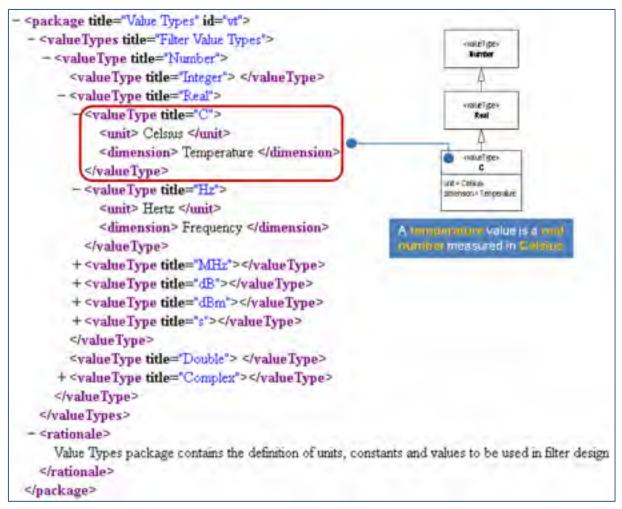

| Figure 5.22  | The XML description corresponding to the "Value Types" package                                               | 292 |

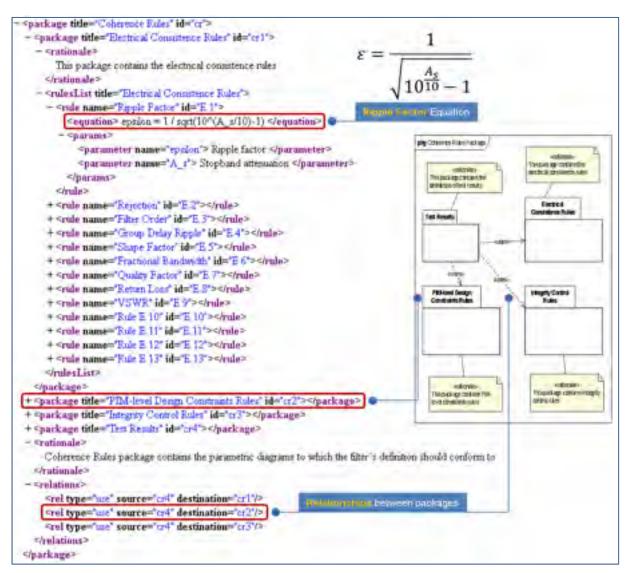

| Figure 5.23  | The XML description corresponding to the "Coherence Rules" package                                           | 293 |

| Figure 5.24  | A snippet from the created Q-matrix showing initial electrical data item at 420 MHz.                         | 294 |

| Figure 5.25  | Bandpass filter parameters relationships graph                                                               | 298 |

| Figure 5.26  | Bandpass filter coherence verification report                                                                | 300 |

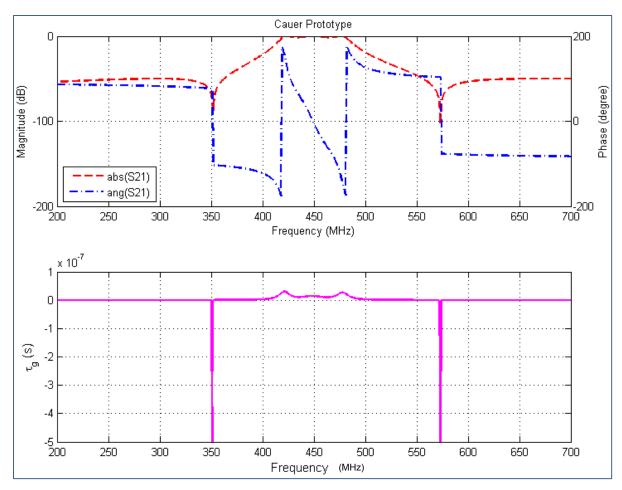

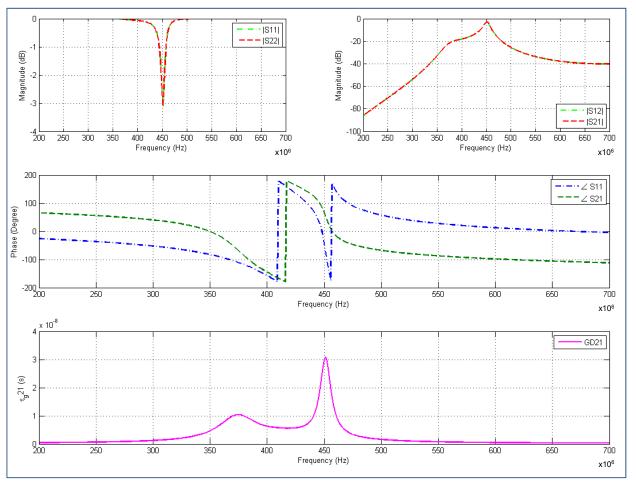

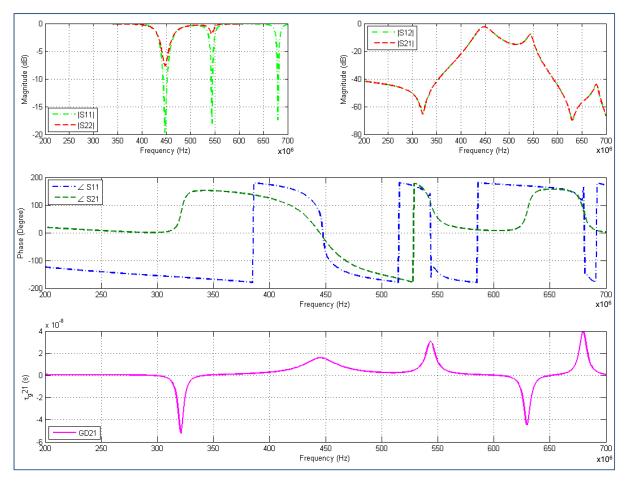

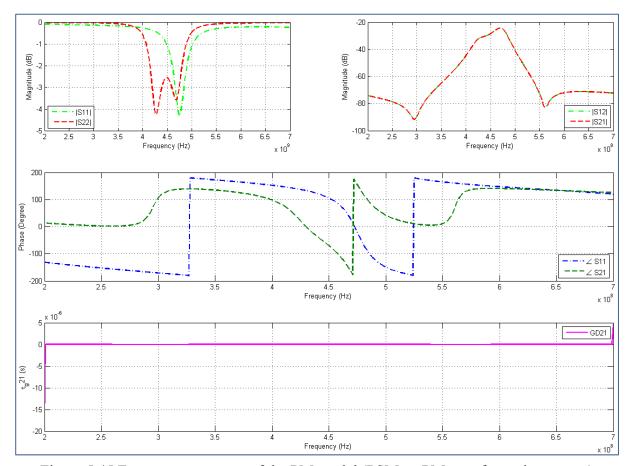

| Figure 5.27  | PIM analysis: Attenuation and group delay for Butterworth prototype                                          | 302 |

| Figure 5.28  | PIM analysis: Attenuation and group delay for Chebyshev type I prototype                                     | 303 |

| Figure 5.29  | PIM analysis: Attenuation and group delay for Bessel prototype                                               | 304 |

| Figure 5.30  | PIM analysis: Attenuation and group delay for Elliptic prototype                                             | 305 |

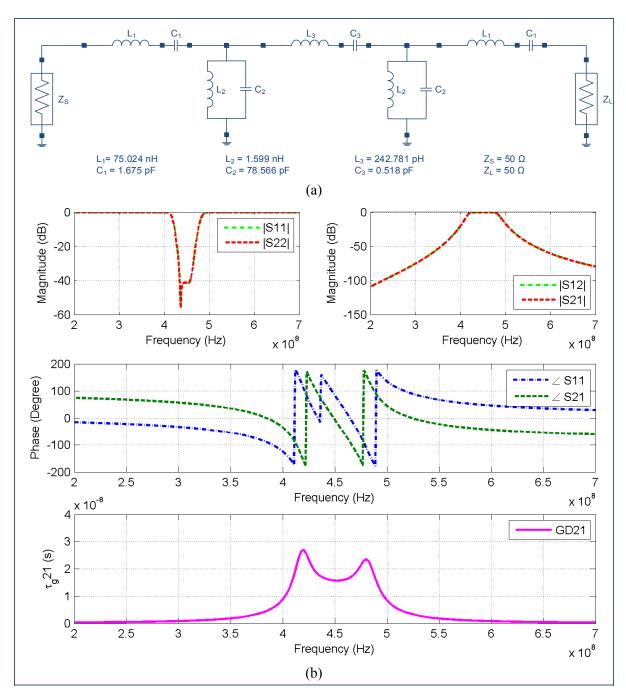

| Figure 5.31  | Transformation (step 2): (a) the LC model and its (b) frequency response                                     | 312 |

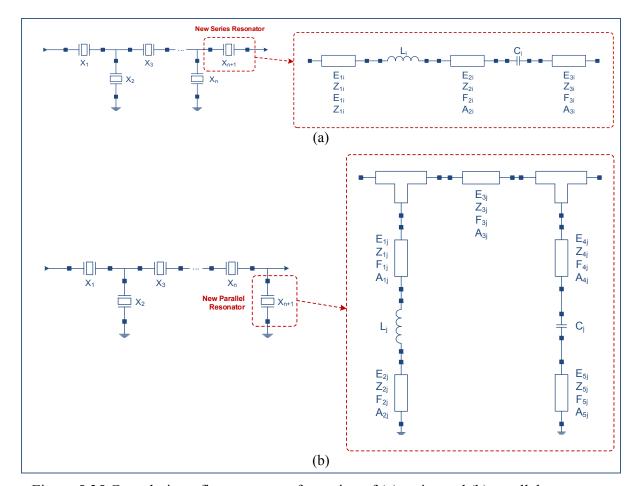

| Figure 5.32  | Generation of lumped-component filter circuit topology: (a) series and (b) parallel resonators               | 313 |

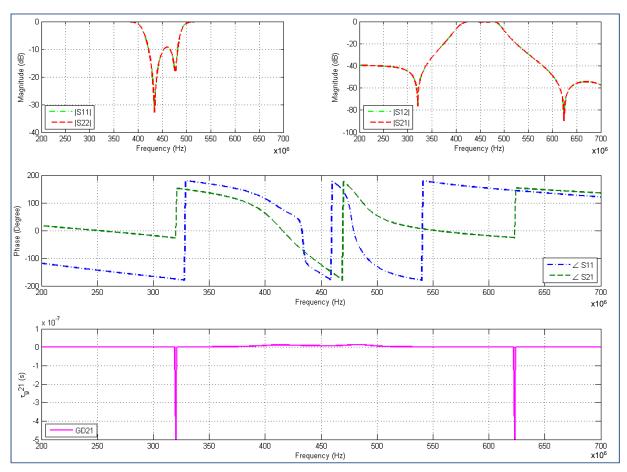

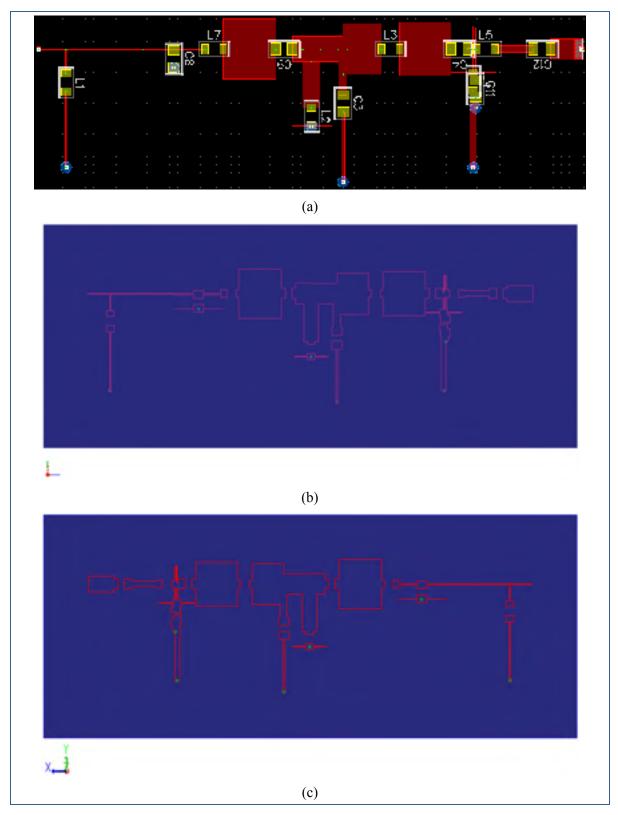

| Figure 5.33  | PSM evolution: (a) transformation output $(N = 5)$ (b) refined $(N = 6)$ and (c) technology-mapped $(N = 6)$ | 314 |

| Figure 5.34  | The frequency response of the PSM resulting from step 3 of the PIM-to-PSM transformation ( $N = 5$ )         | 315 |

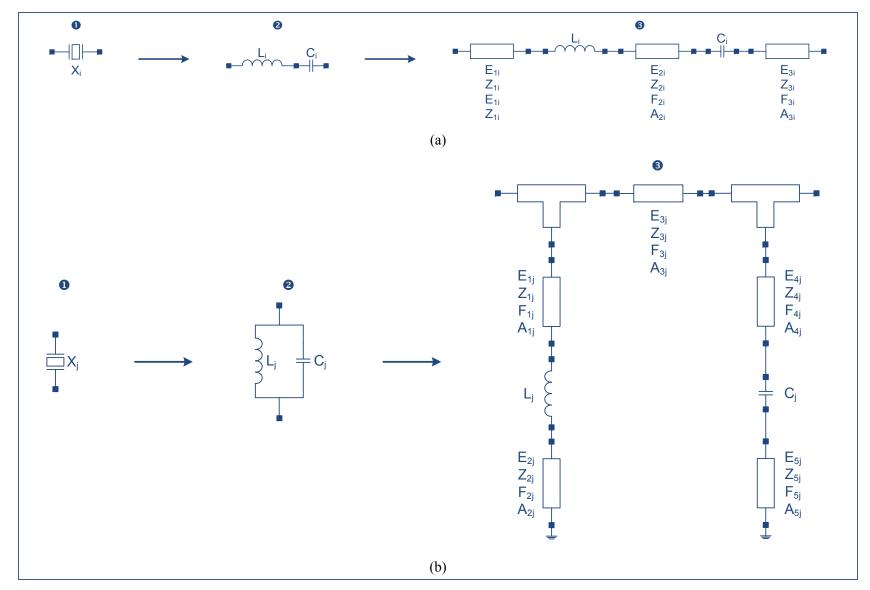

| Figure 5.35  | Granularity refinement: transformation of (a) series and (b) parallel resonators                             | 317 |

| Figure 5.36  | The frequency response of the optimized design solution after PSM granularity refinement                     | 318 |

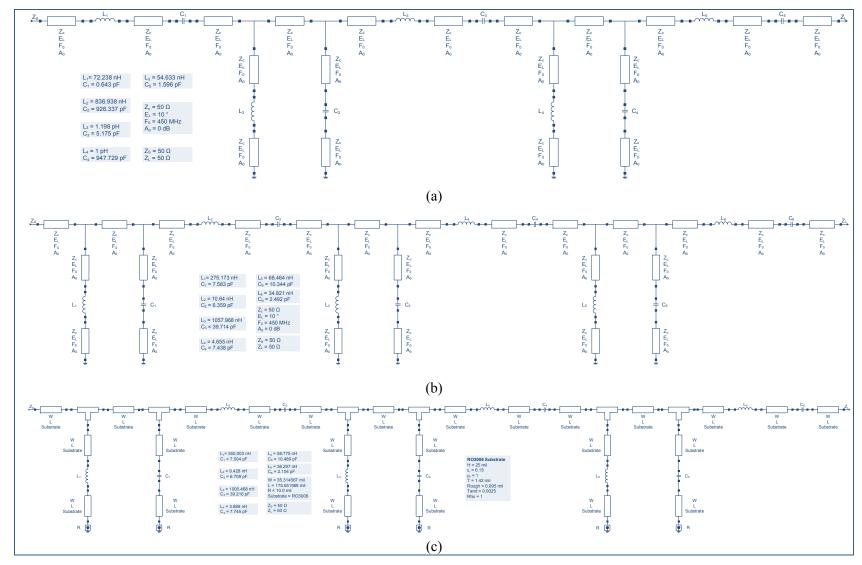

| Figure 5.37  | Technology files: (a) Lumped components (b) Microstrip substrate                                             | 320 |

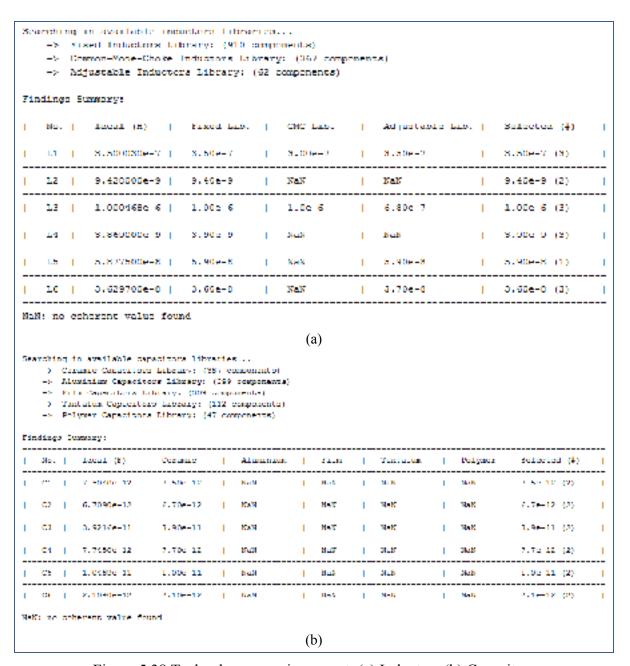

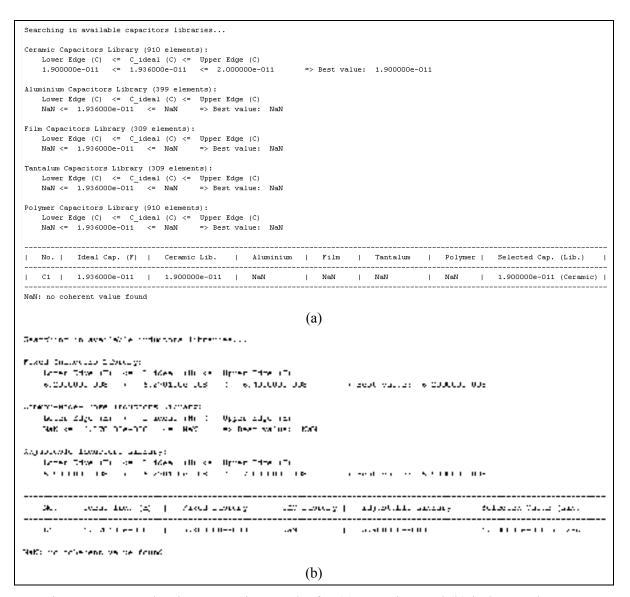

| Figure 5.38  | Technology mapping report: (a) Inductors (b) Capacitors                                                      | 322 |

| Figure 5. 39 | Technology mapping report: Transmission lines synthesis                                                      | 323 |

| Figure 5.40 | The PSM's frequency response after technology mapping                                                                        | 328 |

|-------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.41 | First candidate solution (optimization round 1)                                                                              | 329 |

| Figure 5.42 | First candidate solution (optimization round 2)                                                                              | 330 |

| Figure 5.43 | Platform model (first optimized PSM): (a) 2D layout (b) 3D layout top and (c) bottom views                                   | 331 |

| Figure 5.44 | Platform model (second optimized PSM): (a) 2D layout (b) 3D layout top and (c) bottom views                                  | 332 |

| Figure 5.45 | Frequency response of the PM model (PSM-to-PM transformation output)                                                         | 334 |

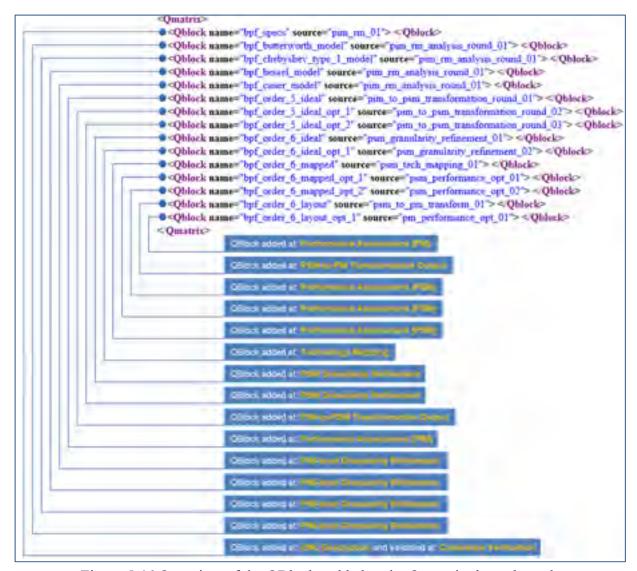

| Figure 5.46 | Overview of the QBlocks added to the Q-matrix throughout the filter's design process                                         | 335 |

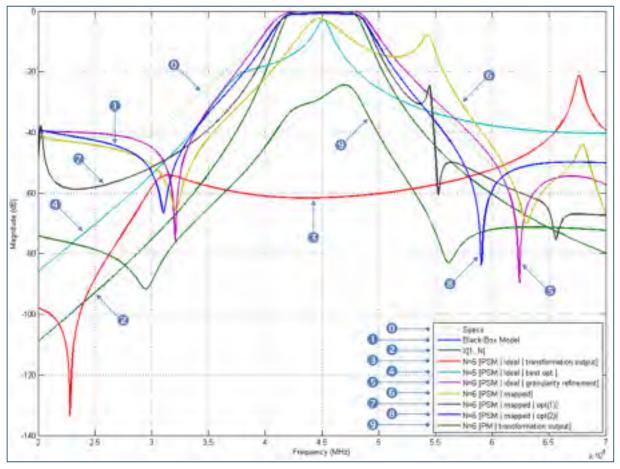

| Figure 5.47 | The Q-matrix centralizes design data, which allows for example to make performance comparisons throughout the design process | 336 |

| Figure 5.48 | An overview of Q-matrix QBlocks evolution throughout the design cycle                                                        | 339 |

| Figure 5.49 | The evolution of the filter models throughout the design cycle                                                               | 340 |

| Figure 5.50 | Simulation techniques versus filter models and design viewpoints                                                             | 341 |

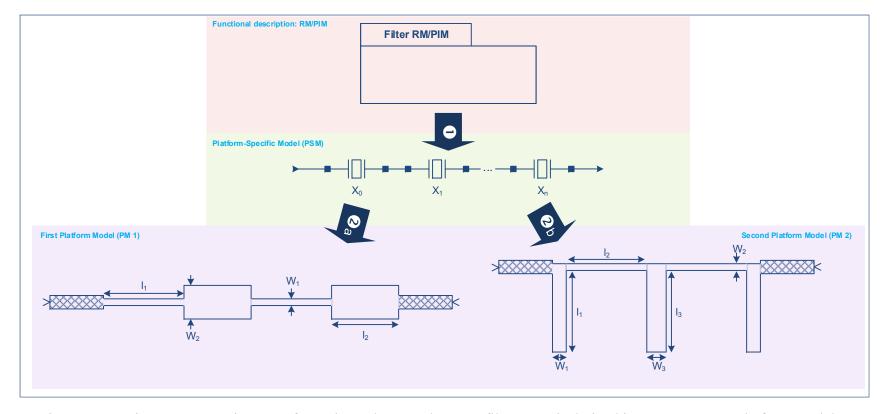

| Figure 5.51 | Using two cross-view transformations, the same lowpass filter PSM is derived into two separate platform models               | 342 |

| Figure 5.52 | Typical parameters of a lowpass filter                                                                                       | 345 |

| Figure 5.53 | The requirements diagram of the lowpass filter                                                                               | 346 |

| Figure 5.54 | Lowpass filter parameters relationships graph                                                                                | 348 |

| Figure 5.55 | Lowpass filter coherence verification report                                                                                 | 350 |

| Figure 5.56 | Black-box model frequency response: Chebyshev Type I approximation                                                           | 351 |

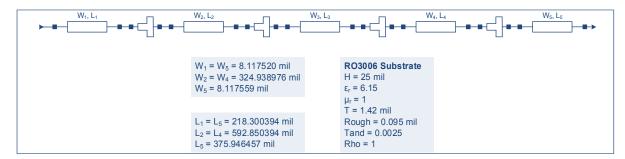

| Figure 5.57 | First PSM: The stepped-impedance lowpass filter                                                                              | 354 |

| Figure 5.58 | First PSM after technology mapping                                                                                           | 355 |

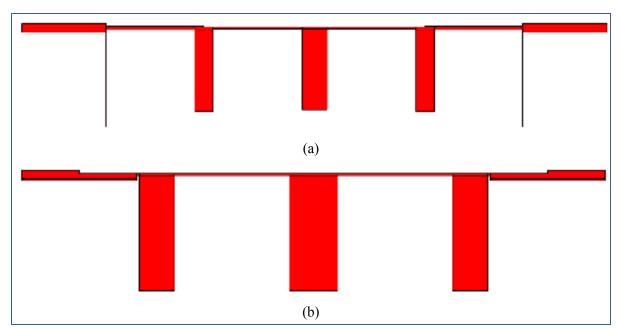

| Figure 5.59 | Lowpass filter stepped-impedance platform model: (a) transformed, (b) first- and (c) second-round optimizations              | 356 |

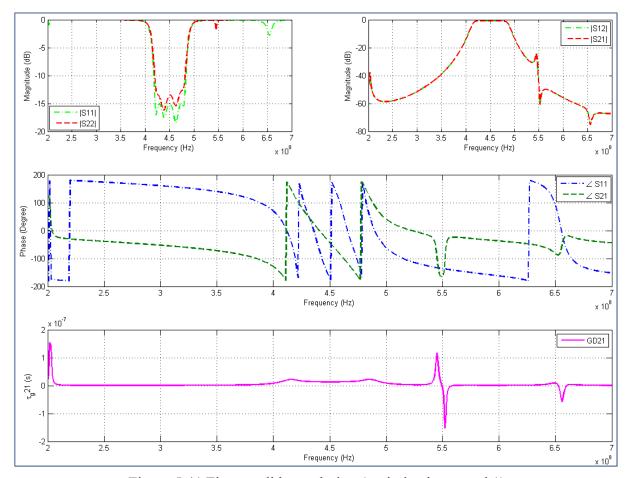

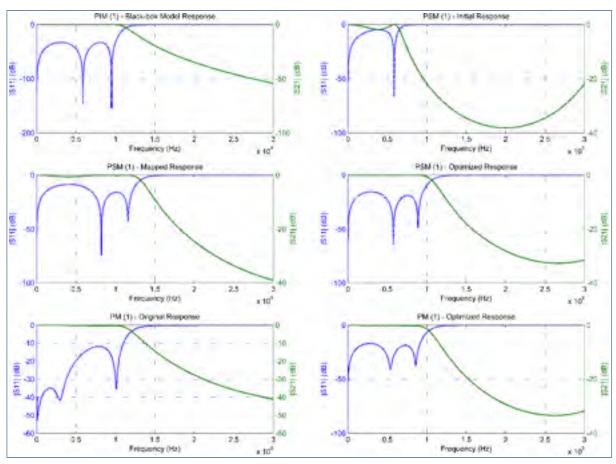

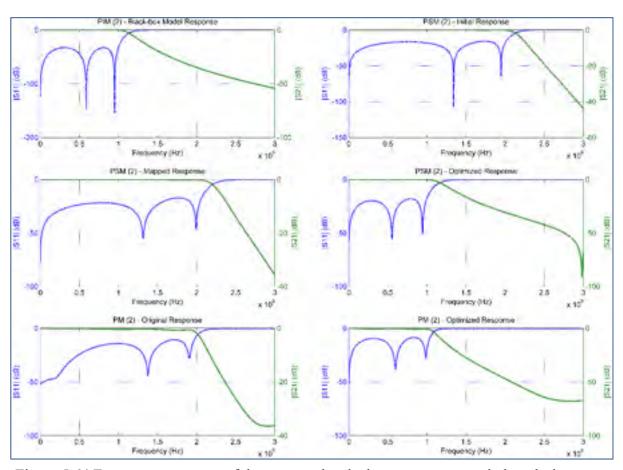

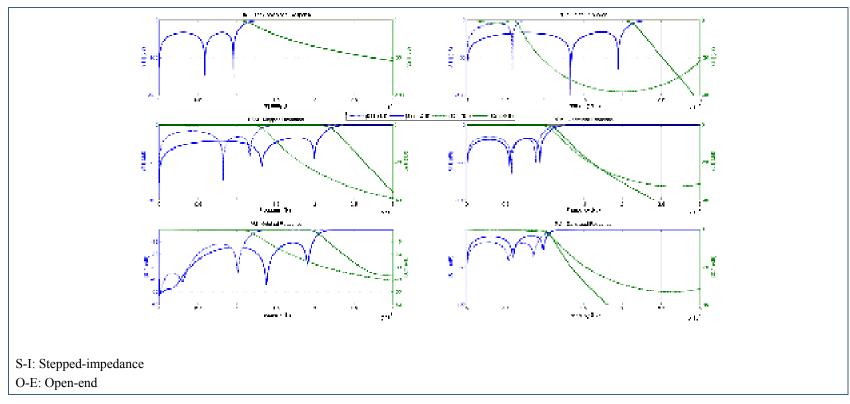

| Figure 5.60 | Frequency response of the stepped-impedance lowpass prototype in key design steps                                                                        | 357 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

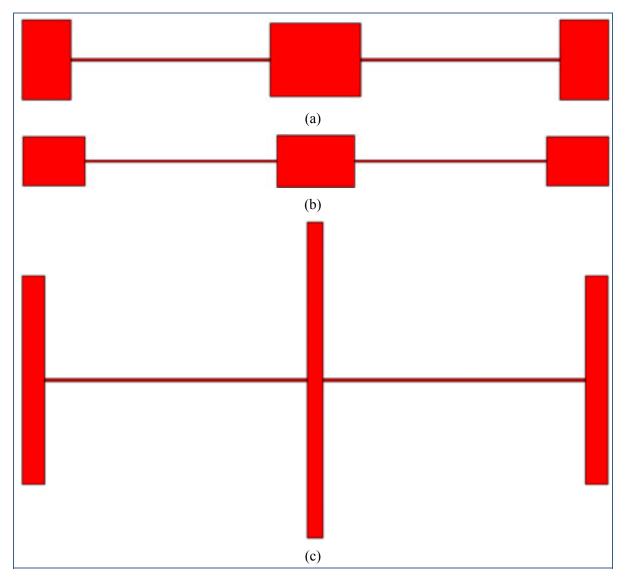

| Figure 5.61 | Second PSM: The open-end stub lowpass filter                                                                                                             | 358 |

| Figure 5.62 | Second PSM after technology mapping                                                                                                                      | 358 |

| Figure 5.63 | Lowpass filter open-end stub-based platform model: (a) transformed, (b) best optimization round                                                          | 360 |

| Figure 5.64 | Frequency response of the open-end stubs lowpass prototype in key design steps                                                                           | 361 |

| Figure 5.65 | Overview of the Qblocks added to the filter's Q-matrix through the design cycle                                                                          | 362 |

| Figure 5.66 | Comparison between the performance of the stepped-impedance and open-end stub-based filter prototypes in different design stages                         | 363 |

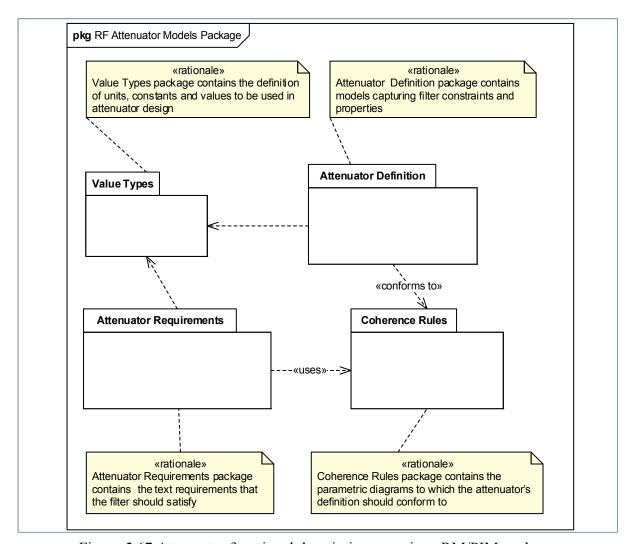

| Figure 5.67 | Attenuator functional description overview: RM/PIM packages                                                                                              | 365 |

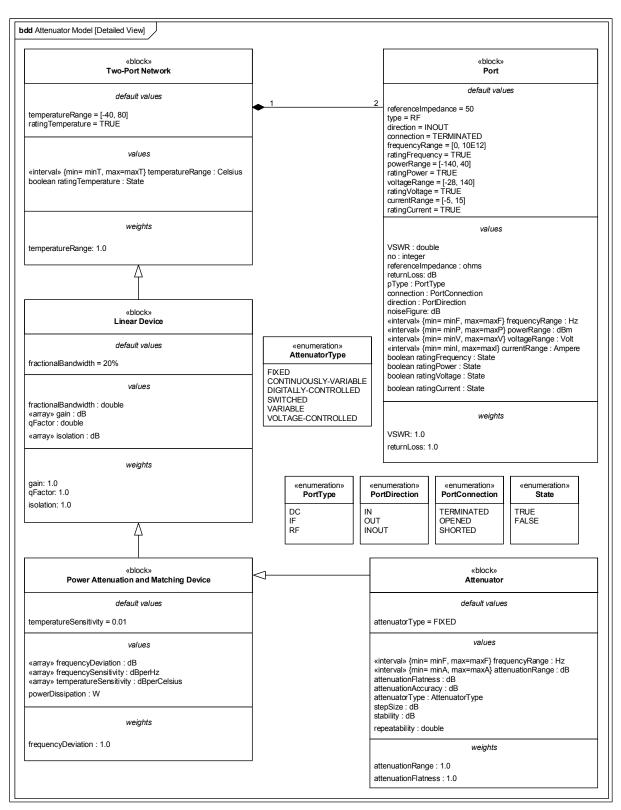

| Figure 5.68 | The detailed attenuator's block definition diagram                                                                                                       | 366 |

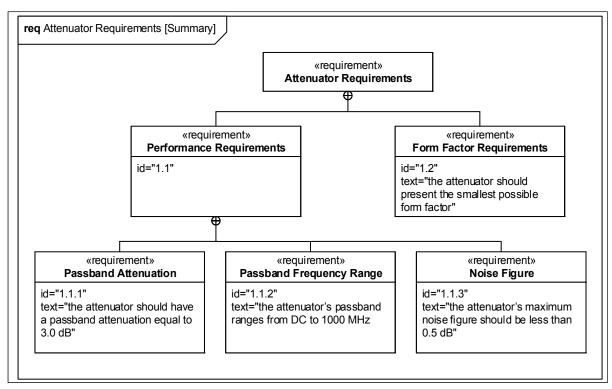

| Figure 5.69 | The main attenuator requirements depicted in the associated SysML diagram                                                                                | 369 |

| Figure 5.70 | Value Types package                                                                                                                                      | 370 |

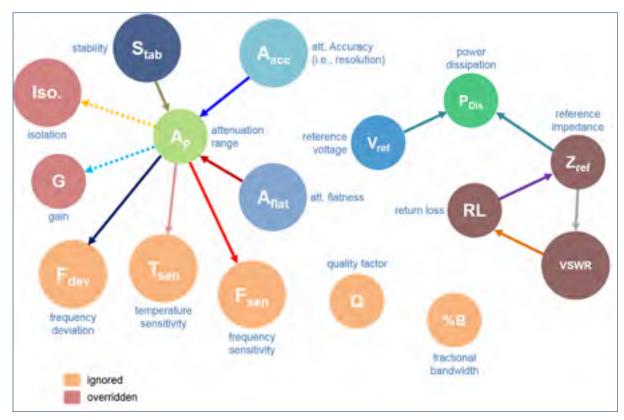

| Figure 5.71 | Attenuator's parameters relationships graph                                                                                                              | 371 |

| Figure 5.72 | Attenuator coherence verification report                                                                                                                 | 374 |

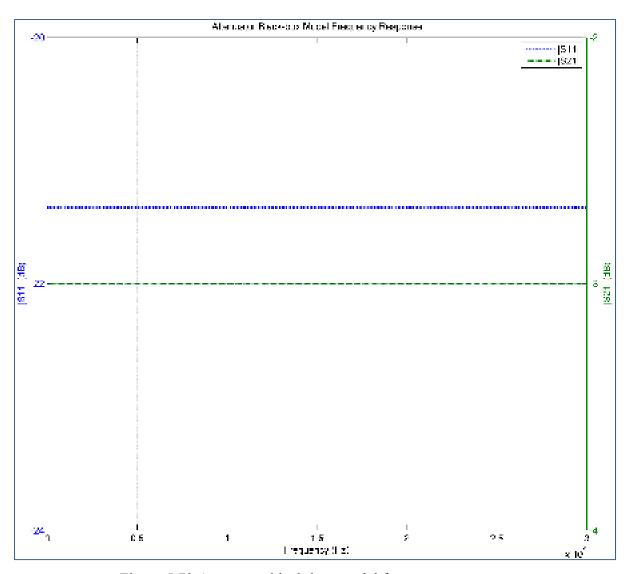

| Figure 5.73 | Attenuator black-box model frequency response                                                                                                            | 374 |

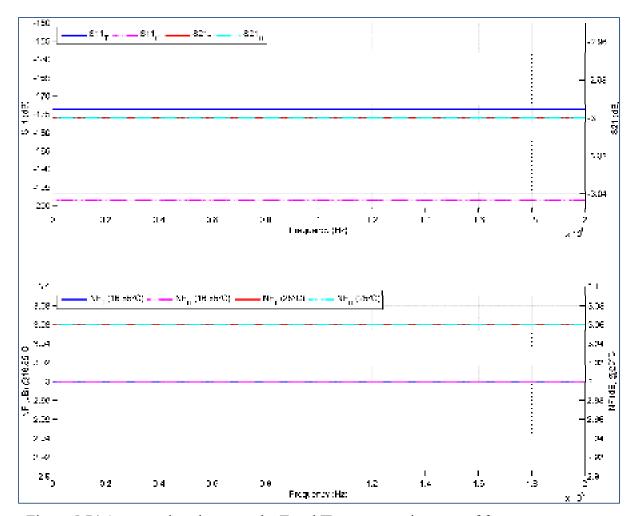

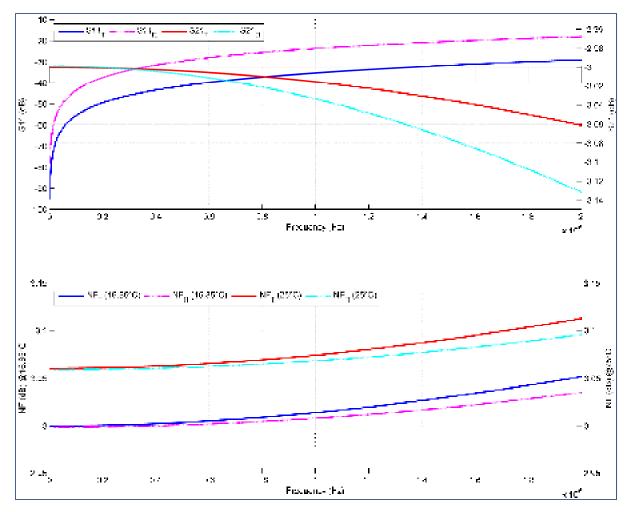

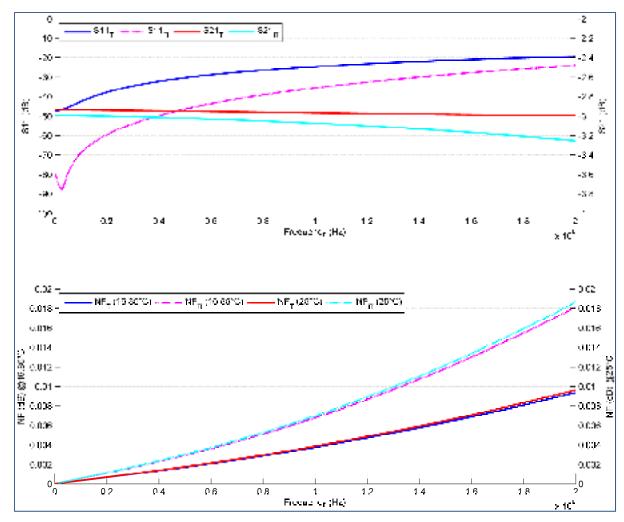

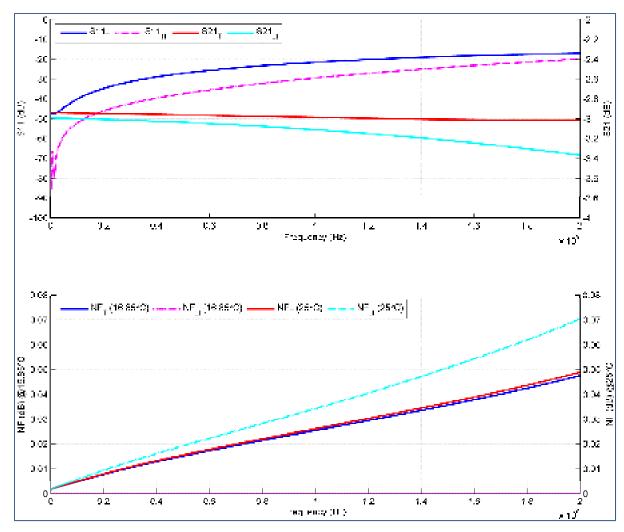

| Figure 5.74 | A comparison between the T and $\Pi$ attenuators in terms of frequency response and noise levels (at the end of step 1 of the PIM-to-PSM transformation) | 377 |

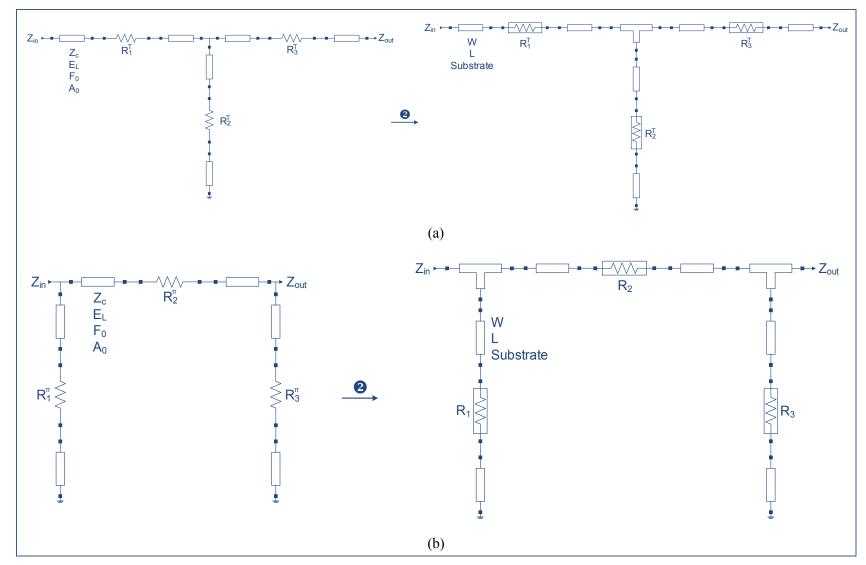

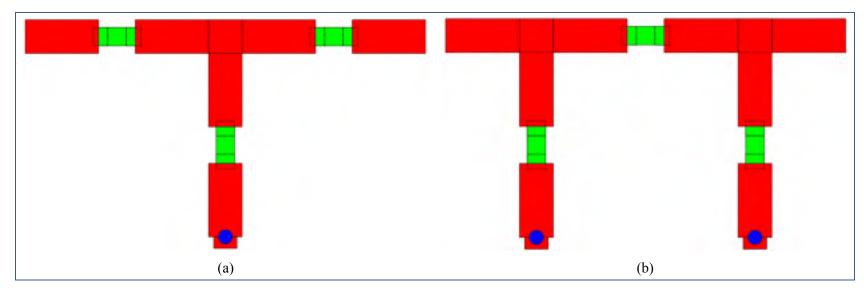

| Figure 5.75 | PIM-to-PSM transformation: (a) T and (b) Π attenuators                                                                                                   | 378 |

| Figure 5.76 | Technology mapping: (a) T and (b) Π attenuators                                                                                                          | 379 |

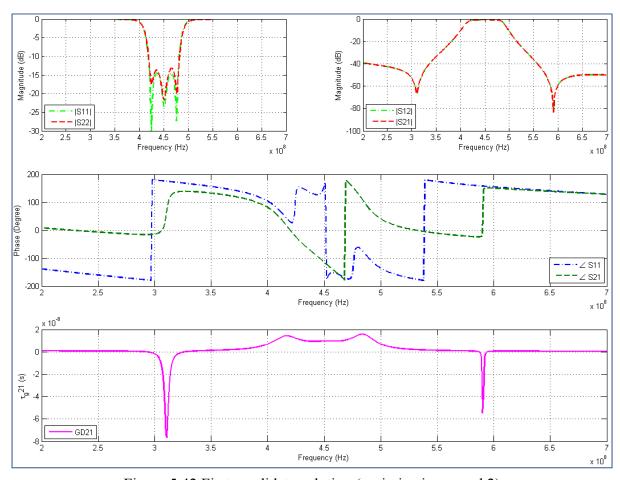

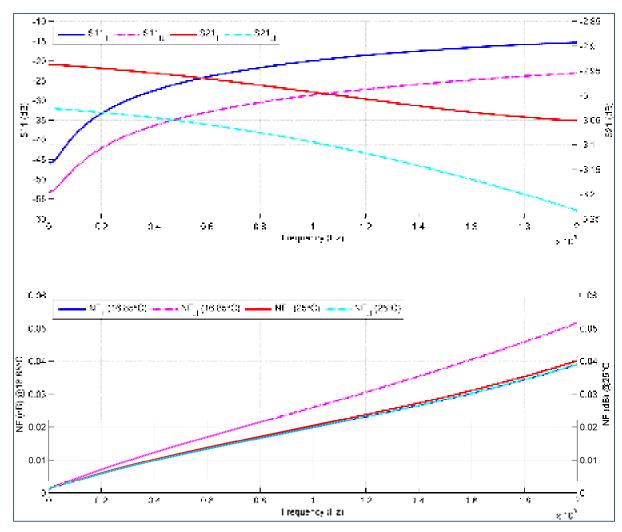

| Figure 5.77 | A comparison between the T and $\Pi$ attenuators in terms of frequency response and noise levels (at the end of step 2 of the PIM-to-PSM transformation) | 380 |

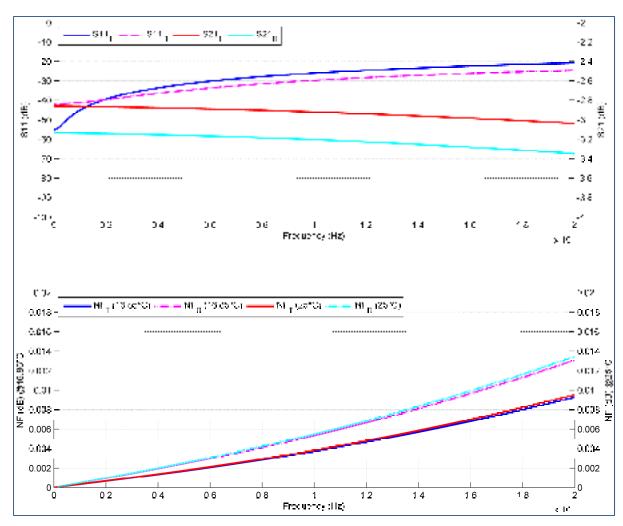

| Figure 5.78 | A comparison between the T and $\Pi$ attenuators in terms of frequency response and noise levels (initial technology mapping)                            | 381 |

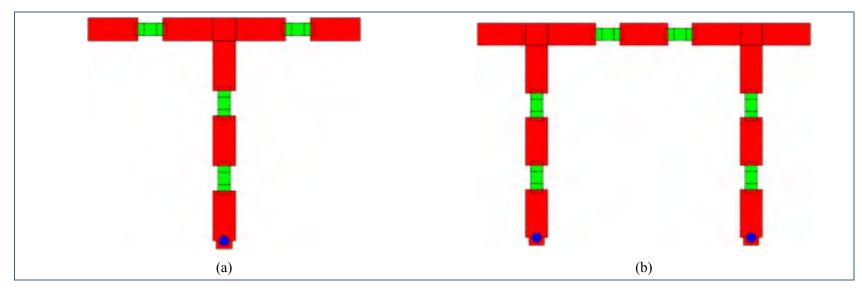

| Figure 5.79  | Intra-view transformation: (a) series (b) shunt                                                                                          | 382 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.80  | A comparison between the T and $\Pi$ attenuators in terms of frequency response and noise levels (after granularity refinement)          | 383 |

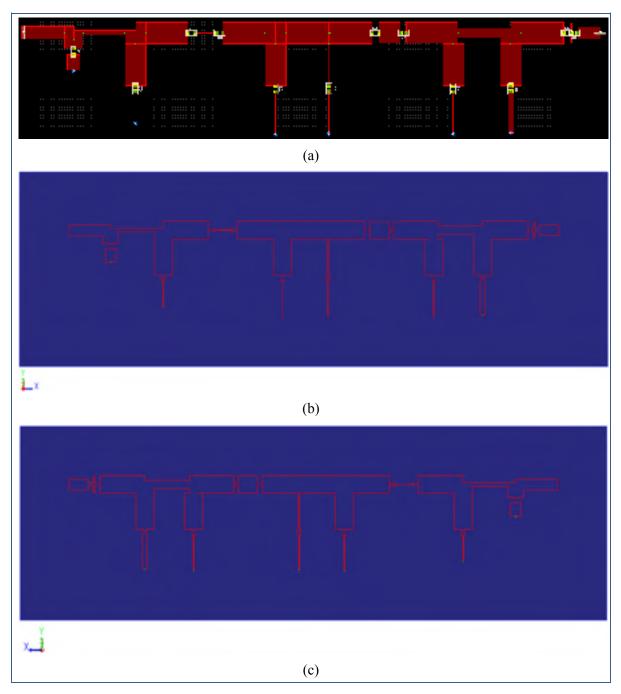

| Figure 5.81  | Resulting PM: (a) T and (b) Π attenuator layouts                                                                                         | 385 |

| Figure 5.82  | Resulting PM after granularity refinement: (a) T and (b) Π attenuator layouts                                                            | 386 |

| Figure 5.83  | A comparison between the T and Π attenuators in terms of frequency response and noise levels (Final PM 1)                                | 389 |

| Figure 5.84  | A comparison between the T and $\Pi$ attenuators in terms of frequency response and noise levels (final PM after granularity refinement) | 390 |

| Figure 5.85  | Noise data is supported in the Qmatrix through metadata                                                                                  | 391 |

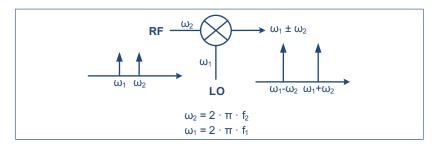

| Figure 5.86  | A mixer makes a frequency translation                                                                                                    | 392 |

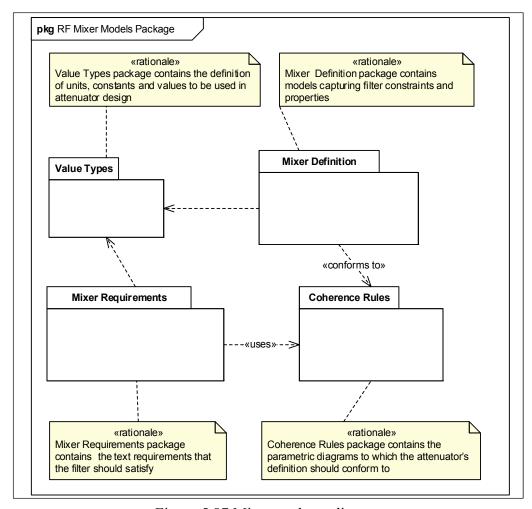

| Figure 5.87  | Mixer package diagram                                                                                                                    | 393 |

| Figure 5.88  | Three-port network detailed block definition diagram                                                                                     | 394 |

| Figure 5.89  | Mixer is a nonlinear frequency conversion device (Figure 5.88 cont'd)                                                                    | 395 |

| Figure 5.90  | Summary of mixer requirements                                                                                                            | 398 |

| Figure 5.91  | Coherence rules: PIM-level design rules                                                                                                  | 399 |

| Figure 5.92  | Mixer value types package                                                                                                                | 401 |

| Figure 5.93  | Mixer parameters relationships graph                                                                                                     | 402 |

| Figure 5.94  | Mixer coherence verification report                                                                                                      | 405 |

| Figure 5.95  | Black-box model frequency response                                                                                                       | 406 |

| Figure 5.96  | PSM topology: passive (a) single-ended diode and (b) rat-race mixer                                                                      | 408 |

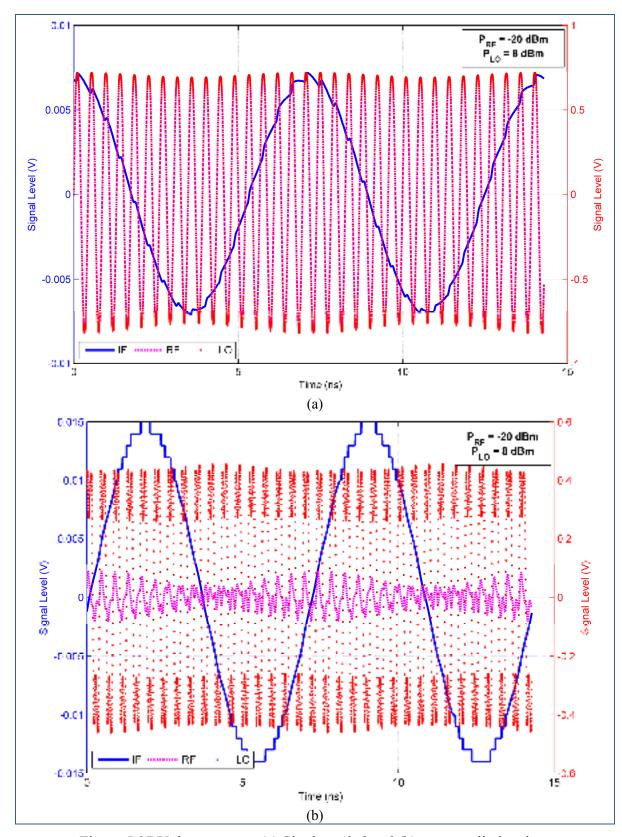

| Figure 5.97  | Voltage waves: (a) Single-ended and (b) rat-race diode mixer                                                                             | 409 |

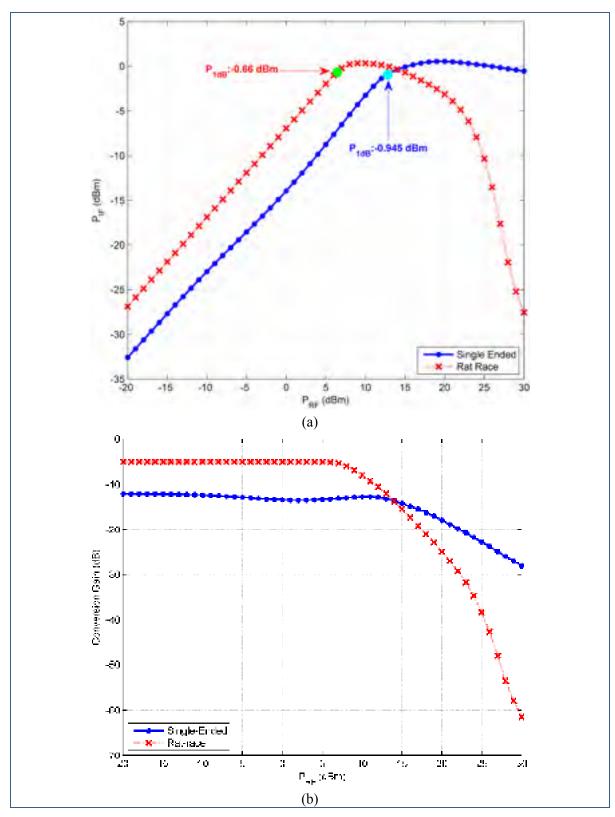

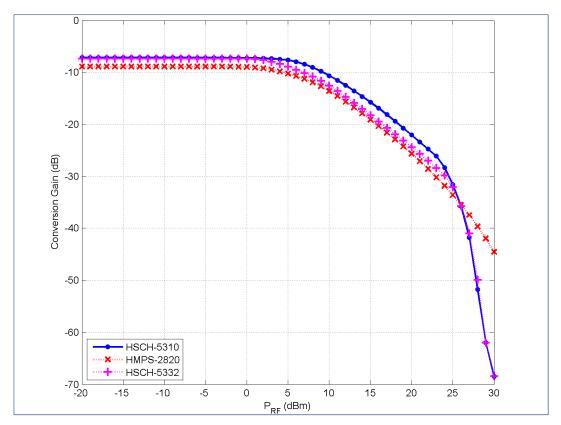

| Figure 5.98  | (a) Output versus input power and (b) conversion gain of both mixers                                                                     | 410 |

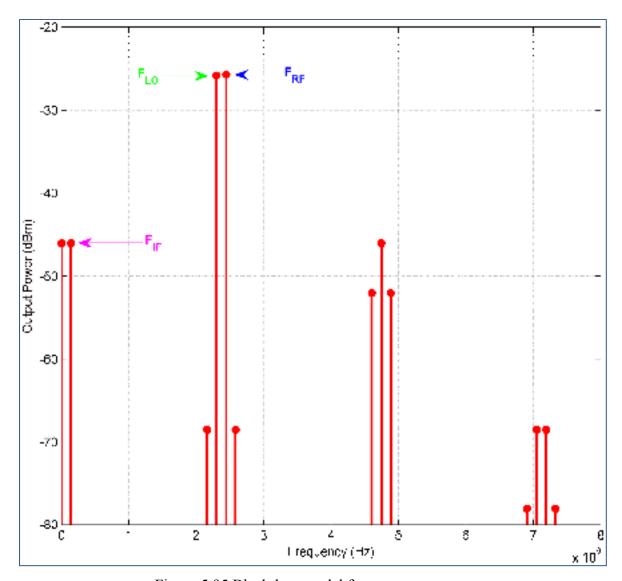

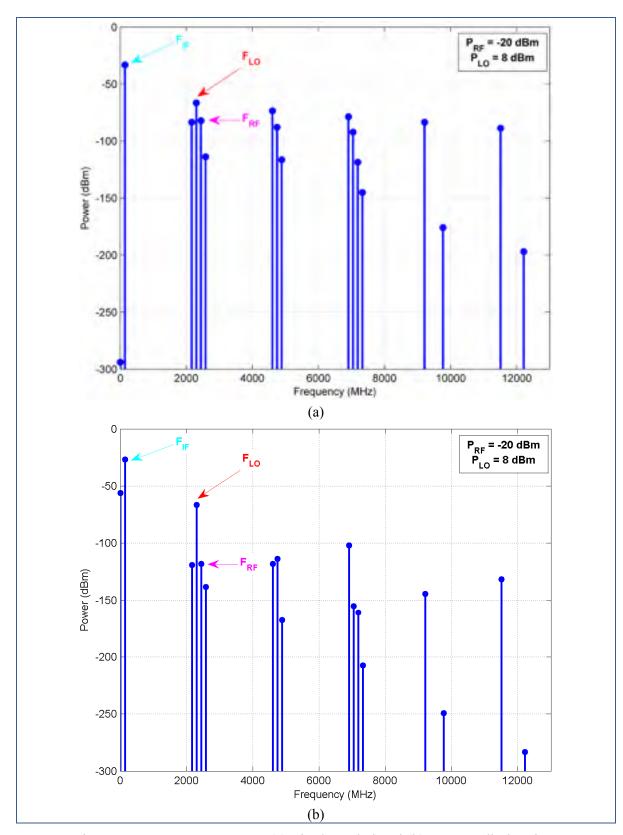

| Figure 5.99  | Output Spectrum: (a) Single-ended and (b) rat-race diode mixer                                                                           | 411 |

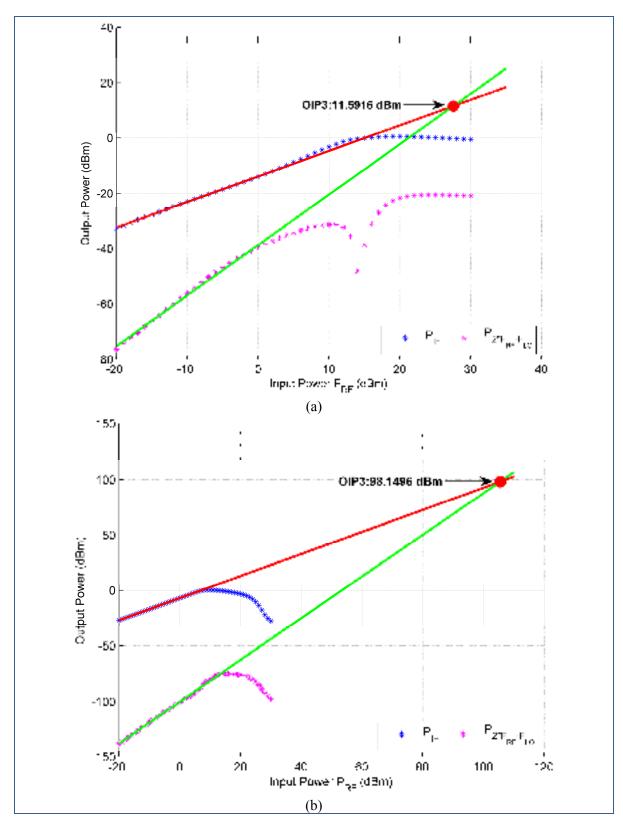

| Figure 5.100 | Output Third-Intercept Point: (a) Single-ended and (b) rat-race diode mixer                                                              | 412 |

| Figure 5.101 | Technology mapping results for (a) capacitor and (b) inductor elements | 416 |

|--------------|------------------------------------------------------------------------|-----|

| Figure 5.102 | Conversion gain of the generated PSMs after technology mapping         | 419 |

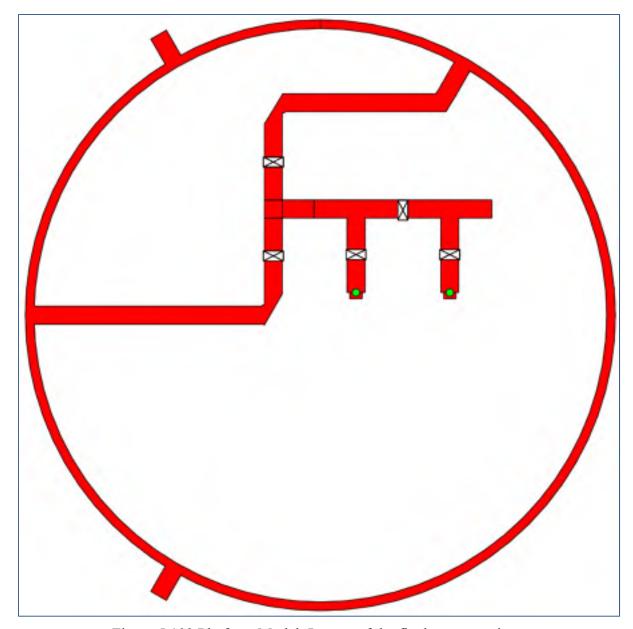

| Figure 5.103 | Platform Model: Layout of the final rat-race mixer                     | 420 |

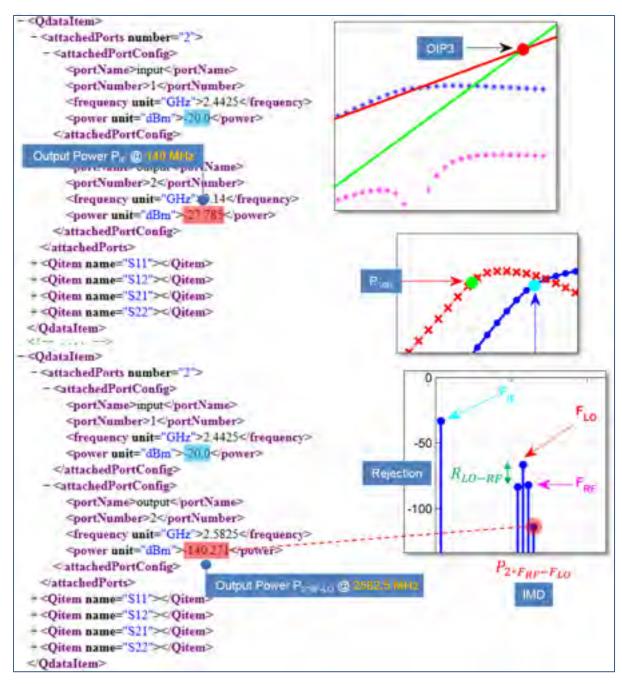

| Figure 5.104 | The Q-matrix stores both linear and nonlinear data                     | 421 |

| Figure 5.105 | The Q-matrix stores data that can be interpreted in different ways     | 422 |

### LIST OF ABREVIATIONS

3D Three-Dimensional

3GPP Third-Generation Partnership Project

AC Alternate Current

ADC Analog-to-Digital Converter

ADS Advanced Design System

AMS Analog-Mixed Signal

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

AWR Applied Wave Research

BAW Bulk Acoustic Wave

BGA Ball Grid Array

CAGR Compound Annual Growth Rate

CANCER Computer Analysis of Nonlinear Circuits, Excluding Radiation

CMOS Complementary Metal-Oxide Semiconductor

CR Cognitive Radio

DAC Digital-to-Analog Converter

DC Direct Current

EDA Electronic Design Automation

EDGE Enhanced Data Rates for GSM Evolution

ESL Electronic System-Level

FSM Finite-State Machine

GDSII Graphic Database System II

GPP General-Purpose Processor

GPRS General Packet Radio Service

GPS Global Positioning System

GSM Global System for Mobile Communications

HDL Hardware Description Language

HSPA High-Speed Packet Access

HTCC High-Temperature Co-fired Ceramic

### **XXXIV**

IC Integrated Circuit

ICT Information and Communication Technology

IEEE Institute of Electrical and Electronics Engineers

IF Intermediate Frequency

IP Internet Protocol

IPs Intellectual Properties

ITU International Telecommunication Union

LAN Local Area Network

LEF Library Exchange Format

LNA Low-Noise Amplifier

LTCC Low-Temperature Co-fired Ceramic

LTE Long-Term Evolution

LVS Layout versus Schematic

M2M Machine-to-Machine

MCM Multi-chip Module

MIMO Multiple-Input Multiple Output

MMIC Monolithic Microwave Integrated Circuits

MOSIS Metal-Oxide Semiconductor Implementation Service

MTTF Mean Time To Failure

NGN Next-Generation Network

NI National Instruments

OASIS Open Artwork System Interchange Standard

OEM Original Equipment Manufacturer

OFDM Orthogonal Frequency Division Multiplexing

OMG Object Management Group

PA Power Amplifier

PAN Personal-Area Network

PCB Printed-Circuit Board

PGA Pin Grid Array

PIM Platform-Independent Model

PM Platform Model

**PSM** Platform-Specific Model

QoS Quality of Service

**RAM** Random Access Memory RAN Radio Access Network

RF Radiofrequency

**RFFE** RF Front-End

SDR

**RFIC** RF Integrated Circuit SAW Surface Acoustic Wave Software-Defined Radio

SiP System in Package

SOI Silicon-On-Insulator

**SPICE** Simulation Program with Integrated Circuit Emphasis

SPP Single-Purpose Processor SWaP Size, Weight and Power

SysML Systems Modeling Language

**TCAD** Technology Computer-Aided Design

TTM Time-to-Market

**UMA** Unlicensed Mobile Access Ultra-Mobile Broadband **UMB**

**VHDL** Very High-Speed Integrated Circuits Hardware-Description Language

**VNA** Vector Network Analyzer VNI Visual Networking Index

VoIP Voice-over-IP

WIF Wireless Innovation Forum

WiMAX Worldwide Interoperability for Microwave Access

WLAN Wireless Local Area Network XML Extensible Markup Language

#### INTRODUCTION

The need for radio systems is growing due to the particular success of consumer communication services. The wide adoption of cellular and wireless systems in the last decades is particularly driving the Information and Communication Technology (ICT) market, giving birth to new applications and services (e.g., machine-to-machine, over-the-top services, etc.) and fueling the increasing convergence between fixed- and mobile-broadband communications (ITU, 2013). Naturally, end-user expectations in terms of quality of service are evolving. At affordable costs, it is expected that future radio systems provide higher data rates and lower power consumption in increasingly harsher radio environments where spectrum is getting more crowded and regulations are becoming tougher (Costa-Perez et al., 2013; Nortel, 2008).

In order to keep pace with the emerging requirements, the challenges that should be addressed are related to implementation technology and radio design flows. On technology level, most future radios will be built with multi-standard, multi-band and multimode transceivers to provide a seamless connectivity to various mobile and wireless networks (Chia et al., 2008). This requires higher processing capability for baseband stages and more robust radiofrequency (RF) front-ends in order to support multiple communication standards and accommodate various radio transmission scenarios. Higher levels of miniaturization and integration are also needed to keep the form factor within an acceptable range for consumers. In addition, all this should have a very low-energy-consumption profile. Remarkable efforts are being deployed in both industry and academia in order to come up with relevant solutions that effectively address these issues. However, is this enough to leverage the encountered challenges? While several new technologies are being developed to enhance radio systems capability (i.e., the "what-to-do"), less interest is dedicated to design approaches and tools (i.e., the "how-to-do") improvement.

On radio design level, there are particularly tangible disparities between digital baseband and RF front-end design cycles. In digital design, it is possible to integrate very complex circuits during a reasonable timeframe. Digital designers have adopted a structured design approach that is backed by a set of tools allowing the automation of most design steps from concept to