Mise en œuvre et validation d'une méthodologie estimant la sensibilité des blocs d'entrée/sortie des FPGA à base de SRAM face aux radiations

par

Fatima Zahra TAZI

THÈSE PRÉSENTÉE À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION

DU DOCTORAT EN GÉNIE

Ph. D.

MONTRÉAL, LE 28 AOÛT 17

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

## **PRÉSENTATION DU JURY**

**CETTE THÈSE A ÉTÉ ÉVALUÉE**

**PAR UN JURY COMPOSÉ DE :**

**M. Claude Thibeault, directeur de thèse**

Département de génie électrique à l'École de technologie supérieure

**M. Yvon Savaria, codirecteur de thèse**

Département de génie électrique à l'École Polytechnique

**M. Philippe Bocher, président du jury**

Département de génie mécanique à l'École de technologie supérieure

**M. Jean-François Boland, membre du jury**

Département de génie électrique à l'École de technologie supérieure

**M. Ghyslain Gagnon, membre du jury**

Département de génie électrique à l'École de technologie supérieure

**M. Amine Miled, membre externe indépendant**

Département de génie électrique et de génie informatique à l'Université Laval

**ELLE A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC**

**LE 5 JUILLET 2017**

**À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE**

## REMERCIEMENTS

Je tiens tout d'abord à remercier mon directeur de thèse, le Professeur Claude Thibeault, pour ses conseils, sa grande compétence, sa rigueur intellectuelle, son dynamisme, son efficacité et aussi son soutien financier et moral tout le long de ces années de thèse. Je suis certaine que je ne pourrai jamais oublier Mr Thibeault. Soyez assuré de mon attachement et de ma profonde gratitude.

J'aimerai aussi remercier mon co-directeur de thèse, le professeur Yvon Savaria pour son expérience scientifique, ses conseils pertinents, ses remarques constructives et sa présence permanente. Je remercie également les membres du jury pour leur collaboration durant l'examen de ce travail, leurs conseils et leur participation à la soutenance.

Mes remerciements vont aussi à tous mes collègues et ami(e)s du laboratoire LACIME et à toutes les personnes formidables que j'ai rencontrées par le biais de l'ÉTS. Je remercie spécialement et chaleureusement mes amies Khadija, Najla et Sana pour leur présence et leurs encouragements.

Enfin, les mots les plus simples étant les plus forts, j'adresse toute mon affection à ma famille, au Canada et au Maroc. Un grand merci à ma maman chérie, Touria, qui m'a toujours épaulée et aimée. Je remercie également mes deux grands amours, mon mari Yassine et ma petite princesse Rita, pour leur amour, leur présence dans ma vie et surtout pour le soutien et l'encouragement que mon mari m'a donné. J'adresse aussi mes remerciements à ma sœur bien-aimée Imane et à mes deux frères chéris Mohammed et Hassan d'avoir toujours cru en moi. Je ne peux pas laisser passer cette occasion sans remercier ma belle-famille et spécialement ma belle-mère Lalla Fatima, Kenza, Amina, Aziza et Pierre. Merci pour votre patience, votre soutien et votre présence dans ma vie. Je vous aime.

A la mémoire de ma grand-mère Hajja Ghita El Ouazzani et mon père Haj Said Tazi.

Une pensée pour terminer ces remerciements pour vous (May et Papa) qui n'avez pas vu l'aboutissement de mon travail mais je sais que vous en auriez été très fiers de votre fille ! ! !

# **MISE EN ŒUVRE ET VALIDATION D'UNE MÉTHODOLOGIE ESTIMANT LA SENSIBILITÉ DES BLOCS D'ENTRÉE/SORTIE DES FPGA À BASE DE SRAM FACE AUX RADIATIONS**

Fatima Zahra TAZI

## **RÉSUMÉ**

De nos jours, l'effet des radiations cosmiques sur l'électronique est devenu la préoccupation par excellence des intervenants qui sont intéressés par la robustesse des circuits intégrés. Plusieurs études ont été menées dans cette optique, essentiellement pour les applications spatiales où les environnements sont denses en ce qui a trait aux particules qui peuvent engendrer le dysfonctionnement voir la destruction de ces applications, lorsque ces particules interagissent avec les circuits intégrés. Les circuits tolérants aux radiations semblent être une bonne solution pour améliorer la robustesse de ces circuits. Cependant, ces circuits sont généralement plus coûteux et ils ont quelques nœuds technologiques en retard sur les circuits non tolérants. Les concepteurs préfèrent alors utiliser des circuits conventionnels et appliquer des méthodes de mitigation afin d'améliorer la tolérance aux erreurs passagères.

Afin d'améliorer la tolérance et la fiabilité des circuits conventionnels, il est indispensable d'analyser la vulnérabilité de ces circuits dans les différents niveaux du flot de conception. Ceci se traduit par une adaptation des méthodes de conception conventionnelles afin d'intégrer la tolérance aux erreurs causées par les radiations.

Dans cette thèse, nous sommes principalement intéressés à élaborer, mettre en œuvre et valider une approche méthodique permettant d'estimer la sensibilité des ressources requises pour l'implémentation d'applications avioniques dans les circuits intégrés programmables (FPGA) à base de mémoire SRAM, par rapport aux événements singuliers (Single Event Upset, SEU) et multiples (Multiple Bit Upset, MBU). En effet, les FPGA à base de mémoire SRAM sont de plus en plus utilisés par l'industrie de l'aérospatial grâce à leurs caractéristiques de prototypage rapide et de reconfiguration sur site bien qu'ils soient vulnérables aux radiations. Nous proposons une nouvelle méthodologie qui étudie les effets des événements singuliers (SEU et MBU) sur les blocs d'entrée/sortie (IOB) des FPGA à base de SRAM. Plus précisément, cette étude propose un modèle de pannes de délai permettant de caractériser l'impact de ces événements sur les IOB.

Dans ce contexte, cette thèse s'est appuyée sur l'étude de deux FPGA (Virtex-5 et Artix-7) de la société Xilinx. Deux différentes techniques ont été utilisées pour générer des SEU, à savoir l'injection de pannes et les expériences réelles d'irradiation. Les résultats obtenus durant les expériences d'irradiation ont montré l'existence de délais dans les IOB induits par les SEU de l'ordre de 6.2 ns pour le Virtex-5 et 3.8 ns pour l'Artix-7. Ces résultats ont été validés aussi par injection de pannes au moyen de l'utilitaire SEU Controller.

Cette thèse présente aussi une étude plus poussée de l'effet des radiations sur les délais observés dans les IOB des FPGA à base de SRAM. Plus spécifiquement, cette recherche a

proposé et validé des modèles de pannes permettant de décrire et de mieux comprendre les mécanismes pouvant mener aux délais observés dans les IOB.

Un dernier aspect de cette thèse réside dans l'étude de la fiabilité de la robustesse de quelques techniques de mitigation appliquées à l'intérieur des IOB des FPGA à base de SRAM. Des observations importantes ont révélé que les SEU qui affectent les IOB peuvent rendre les techniques de correction et de reconfiguration (*Scrubbing*) insuffisantes pour corriger et éviter l'accumulation de plusieurs erreurs. Ces observations ont lancé une réflexion sur le type de technique de mitigation adéquat qui doit être utilisé dans les IOB en présence des SEU.

**Mots clés:** FPGA à base de SRAM, SEU, MBU, IOB, effets des radiations, électronique embarquée, techniques de mitigation.

# **MISE EN ŒUVRE ET VALIDATION D'UNE MÉTHODOLOGIE ESTIMANT LA SENSIBILITÉ DES BLOCS D'ENTRÉE/SORTIE DES FPGA À BASE DE SRAM FACE AUX RADIATIONS**

Fatima Zahra TAZI

## **ABSTRACT**

Nowadays, the effects of cosmic rays on electronics have become the pre-eminent concern of researchers who are interested in the robustness of integrated circuits. Many researches have been elaborated in this direction, mainly for aerospace applications where the environments are dense in terms of particles which can lead to the dysfunction or even to the destruction of these applications, when interacting with integrated circuits. Radiation tolerant circuits seem to be a good solution to improve the robustness of these circuits. However, those circuits are generally more expensive and their technologies often lag a few generations behind non-tolerant circuits. Designers prefer to use conventional circuits and apply mitigation techniques to improve the tolerance of soft errors.

To improve the tolerance and the reliability of conventional circuit, it is necessary to analyze the vulnerability of these circuits in different levels of abstraction in the design flow. Conventional design methodologies need to be adapted in order to evaluate the tolerance to errors caused by radiation.

In this Thesis, we are mainly interested to elaborate and validate a methodology allowing the estimation of the sensibility of resources required to implement avionics applications in SRAM-based FPGA, against single events (SEU) and multiple events (MBU). In fact, the SRAM-based FPGA are increasingly used by the aerospace community due to their rapid prototyping and on-site reconfiguration characteristics, although they are vulnerable to radiation. We propose a new methodology to study the effects of single events (SEU and MBU) on the input/output blocs (IOB) of SRAM-based FPGA. More precisely, this study propose a delay model to characterize the impacts of these events on IOBs.

In the same context, this Thesis is based on the study of two Xilinx FPGAs (Virtex-5 and Artix-7). Two different techniques were used to generate SEUs, namely fault injection and irradiation experiments. The results from irradiation showed the existence of delays in the IOBs up to 6.2 ns for the Virtex-5 and up to 3.8 ns for the Artix-7. Those results were validated by fault injection using the SEU Controller.

This thesis also presents a further study of the effect of radiations on the delays observed in the IOBs of SRAM-based FPGAs. More precisely, this research propose and validate delay models allowing to describe and better understand the mechanisms that can lead to the delays observed in IOBs.

A final aspect of this thesis is the study of the reliability and the robustness of some mitigation techniques applied inside the IOBs of SRAM-based FPGAs. Important observations have

revealed that the SEUs affecting the IOBs can make the correction and reconfiguration techniques (Scrubbing) insufficient to correct and avoid the accumulation of several errors. These observations led to a reflection on the type of adequate mitigation technique that must be used in IOBs in the presence of SEUs.

**Keywords:** SRAM-based FPGA, SEU, MBU, IOB, Radiation effects, Embedded electronics, Mitigation techniques.

## TABLE DES MATIÈRES

|                                                                                                                           | Page |

|---------------------------------------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                                                        | 1    |

| CHAPITRE 1 NOTIONS DE BASE .....                                                                                          | 5    |

| 1.1 Environnement radiatif naturel .....                                                                                  | 5    |

| 1.1.1 Environnement radiatif spatial .....                                                                                | 5    |

| 1.1.2 Environnement radiatif atmosphérique .....                                                                          | 8    |

| 1.2 Effets des radiations sur les circuits électroniques : les événements singuliers .....                                | 10   |

| 1.2.1 Événements singuliers .....                                                                                         | 10   |

| 1.3 Architecture des FPGA à base de SRAM .....                                                                            | 12   |

| 1.3.1 FPGA à base de mémoire SRAM ( <i>Static Random Access Memory</i> ) .....                                            | 13   |

| 1.3.2 FPGA à base de mémoire Flash .....                                                                                  | 14   |

| 1.3.3 FPGA à base d'anti-fusibles .....                                                                                   | 14   |

| 1.3.4 Architecture détaillée des FPGA à base de SRAM de la famille<br>Virtex-5 .....                                      | 15   |

| 1.4 Techniques d'injection de pannes .....                                                                                | 19   |

| 1.5 Techniques de mitigation .....                                                                                        | 27   |

| 1.5.1 Triplication Modulaire (Triple Modular Redundancy TMR) .....                                                        | 27   |

| 1.5.2 Reconfiguration “ <i>Scrubbing</i> ” .....                                                                          | 29   |

| 1.6 Conclusion .....                                                                                                      | 30   |

| CHAPITRE 2 REVUE DE LITTÉRATURE .....                                                                                     | 31   |

| 2.1 Effets des événements singuliers sur toutes les ressources des FPGA à base<br>de SRAM (routage, logique et IOB) ..... | 31   |

| 2.2 Effets des événements singuliers sur les blocs d'entrée/sortie (IOB) des FPGA<br>à base de SRAM .....                 | 36   |

| 2.3 Conclusion .....                                                                                                      | 44   |

| CHAPITRE 3 GÉNÉRATION DES PANNES DE DÉLAIS DANS LES BLOCS<br>D'ENTRÉE/SORTIE DES FPGA À BASE DE SRAM .....                | 47   |

| 3.1 Injection de pannes par émulation .....                                                                               | 48   |

| 3.2 Résultats d'émulation .....                                                                                           | 50   |

| 3.3 Expériences d'irradiation .....                                                                                       | 52   |

| 3.4 Premiers résultats d'irradiation .....                                                                                | 54   |

| 3.5 Comparaison des résultats d'irradiation avec les résultats d'émulation .....                                          | 58   |

| 3.6 Distribution des ODC sur les IOB .....                                                                                | 62   |

| 3.7 Portabilité de notre méthodologie de détection de délai .....                                                         | 62   |

| 3.8 Conclusion .....                                                                                                      | 66   |

| CHAPITRE 4 MODÈLE DE PANNES DE DÉLAIS .....                                                                               | 69   |

| 4.1 Modèles analytiques .....                                                                                             | 70   |

| 4.1.1 Modèle logique d'un oscillateur en boucle et quelques définitions .....                                             | 70   |

|                                                                                                                                                                                                  |                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|

| 4.1.2                                                                                                                                                                                            | Modèle RC d'un inverseur CMOS .....                                                                      | 74  |

| 4.1.3                                                                                                                                                                                            | Modèle RC de l'oscillateur en boucle et modèles de pannes de délai .....                                 | 75  |

| 4.2                                                                                                                                                                                              | Simulations HSPICE.....                                                                                  | 79  |

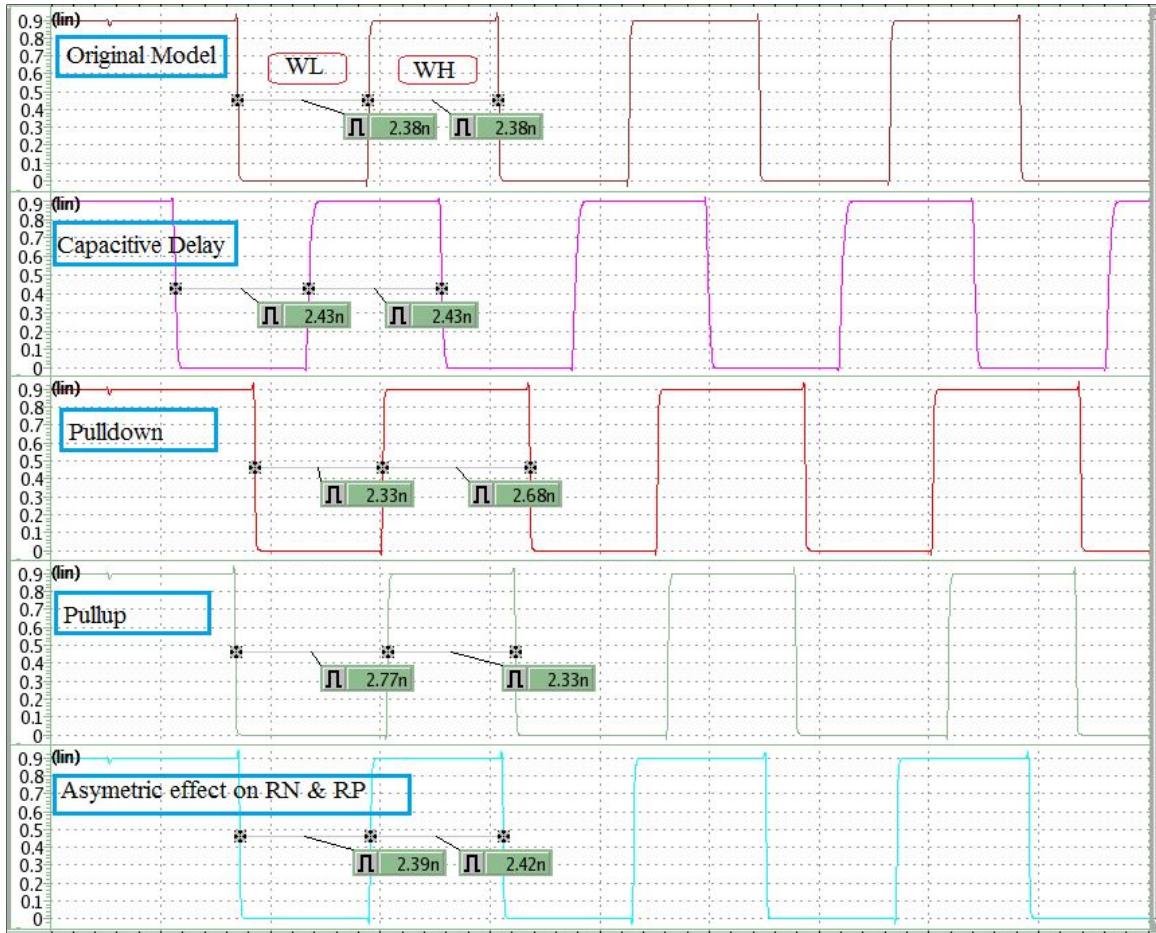

| 4.3                                                                                                                                                                                              | Expériences d'émulation.....                                                                             | 81  |

| 4.4                                                                                                                                                                                              | Conclusion .....                                                                                         | 84  |

| <br>CHAPITRE 5     OBSERVATIONS SUR L'IMPACT DES RADIATIONS SUR LA<br>ROBUSTESSE DE QUELQUES TECHNIQUES DE MITIGATION<br>À L'INTÉRIEUR DES BLOCS D'ENTRÉE/SORTIE DES FPGA<br>À BASE DE SRAM..... |                                                                                                          |     |

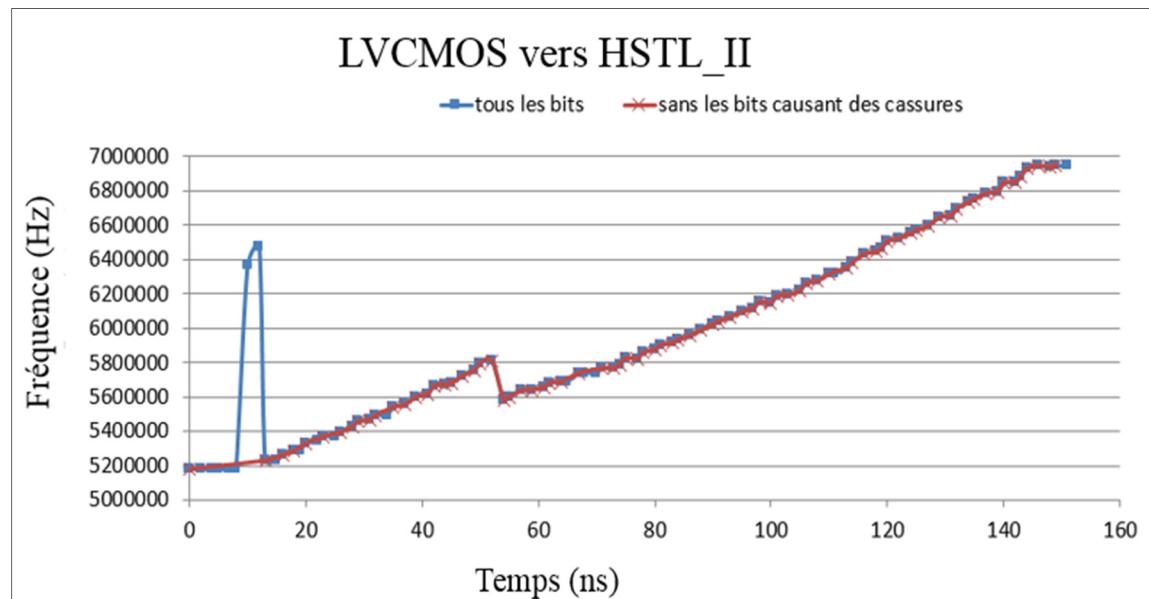

| 5.1                                                                                                                                                                                              | Distribution des délais.....                                                                             | 86  |

| 5.2                                                                                                                                                                                              | Observations sur la robustesse des TMR face aux radiations dans les IOB<br>des FPGA à base de SRAM ..... | 90  |

| 5.3                                                                                                                                                                                              | Effet mémoire .....                                                                                      | 98  |

| 5.4                                                                                                                                                                                              | Conclusion .....                                                                                         | 104 |

| <br>CONCLUSION.....                                                                                                                                                                              |                                                                                                          |     |

| 107                                                                                                                                                                                              |                                                                                                          |     |

| <br>RECOMMANDATIONS .....                                                                                                                                                                        |                                                                                                          |     |

| 111                                                                                                                                                                                              |                                                                                                          |     |

| ANNEXE I                                                                                                                                                                                         | INTERFACE D'INJECTION DE PANNES .....                                                                    | 113 |

| ANNEXE II                                                                                                                                                                                        | PREMIÈRE LISTE DE BITS DE CONFIGURATION.....                                                             | 115 |

| ANNEXE III                                                                                                                                                                                       | DEUXIÈME LISTE DE BITS DE CONFIGURATION.....                                                             | 117 |

| <br>LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES.....                                                                                                                                                    |                                                                                                          |     |

| 118                                                                                                                                                                                              |                                                                                                          |     |

## LISTE DES TABLEAUX

|             | Page                                                                                                                                     |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 2.1 | Fréquence des MBU induits par une radiation à base de protons (63.3 MeV).....                                                            | 33  |

| Tableau 2.2 | Comparaison des deux techniques utilisées pour tester les effets.....                                                                    | 44  |

| Tableau 3.1 | La valeur absolue des plus grands ODC observés versus le changement des paramètres des IOB; les changements sont soulignés en vert ..... | 52  |

| Tableau 4.1 | Résultats obtenus par émulation .....                                                                                                    | 83  |

| Tableau 5.1 | Résultats des mesures de délais .....                                                                                                    | 88  |

| Tableau 5.2 | Liste des IOB utilisés pour le montage de la figure 5.4.....                                                                             | 91  |

| Tableau 5.3 | Résultats d'inversion pour les 3 RO en partant du mode HSTL_II.....                                                                      | 94  |

| Tableau 5.4 | Résultats d'inversion pour RO11, RO12 et RO13 en partant du HSTL_II .....                                                                | 95  |

| Tableau 5.5 | IOB utilisés dans chaque FPGA pour les 4 RO .....                                                                                        | 100 |

| Tableau 5.6 | Changements observés sur les 4 RO suite au bit-flip des186 bits en partant de LVCMOS25 en mode accumulation .....                        | 103 |

| Tableau 5.7 | Changements observés sur les 4 RO suite au bit-flip des186 bits en partant de LVCMOS25 en mode singulier.....                            | 104 |

## LISTE DES FIGURES

|             | Page |

|-------------|------|

| Figure 1.1  | 6    |

| Figure 1.2  | 7    |

| Figure 1.3  | 8    |

| Figure 1.4  | 9    |

| Figure 1.5  | 11   |

| Figure 1.6  | 13   |

| Figure 1.7  | 14   |

| Figure 1.8  | 15   |

| Figure 1.9  | 16   |

| Figure 1.10 | 17   |

| Figure 1.11 | 18   |

| Figure 1.12 | 19   |

| Figure 1.13 | 24   |

| Figure 1.14 | 26   |

| Figure 1.15 | 28   |

| Figure 1.16 | 29   |

| Figure 2.1  | 32   |

| Figure 2.2  | 34   |

| Figure 2.3  | 35   |

|             |                                                                                                                                 |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.4  | résultat d'irradiation de 6 ODC d'une valeur respective de 58, 46, 58, 70, 58 et 58 ps. Un délai total de 358 ps .....          | 36 |

| Figure 2.5  | Structure de la TMR recommandée par Xilinx.....                                                                                 | 38 |

| Figure 2.6  | Nouvelle structure des TMR (quasi-TMR).....                                                                                     | 38 |

| Figure 2.7  | Architecture de la méthodologie de test.....                                                                                    | 39 |

| Figure 2.8  | Architecture de la technique basée sur la duplication des IOB .....                                                             | 40 |

| Figure 2.9  | 1 <sup>er</sup> montage « <i>NoTMR</i> » implémentant un simple montage composé d'une entrée et d'une sortie sans TMR .....     | 42 |

| Figure 2.10 | 2 <sup>e</sup> montage « <i>Full TMR</i> » dérivant du montage de la figure 3.9 en insérant une TMR complète .....              | 42 |

| Figure 2.11 | 3 <sup>e</sup> montage « <i>TMR In-only</i> » dérivant du montage de la figure 3.9 en insérant une TMR partielle .....          | 43 |

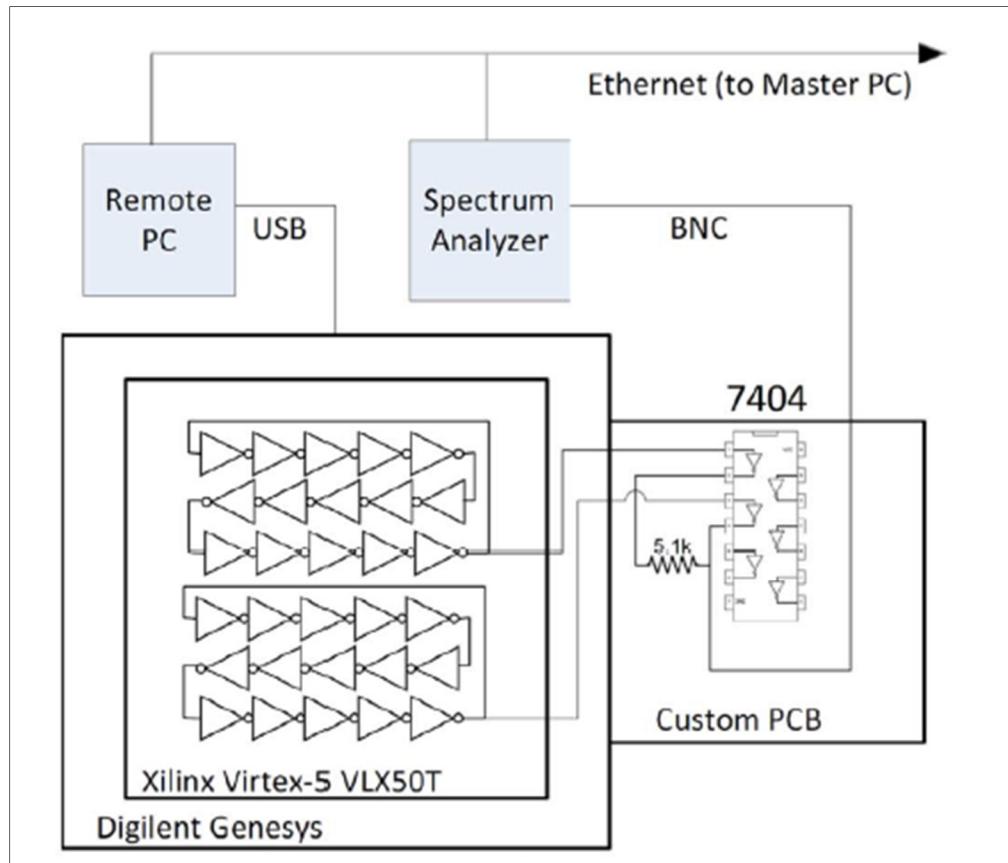

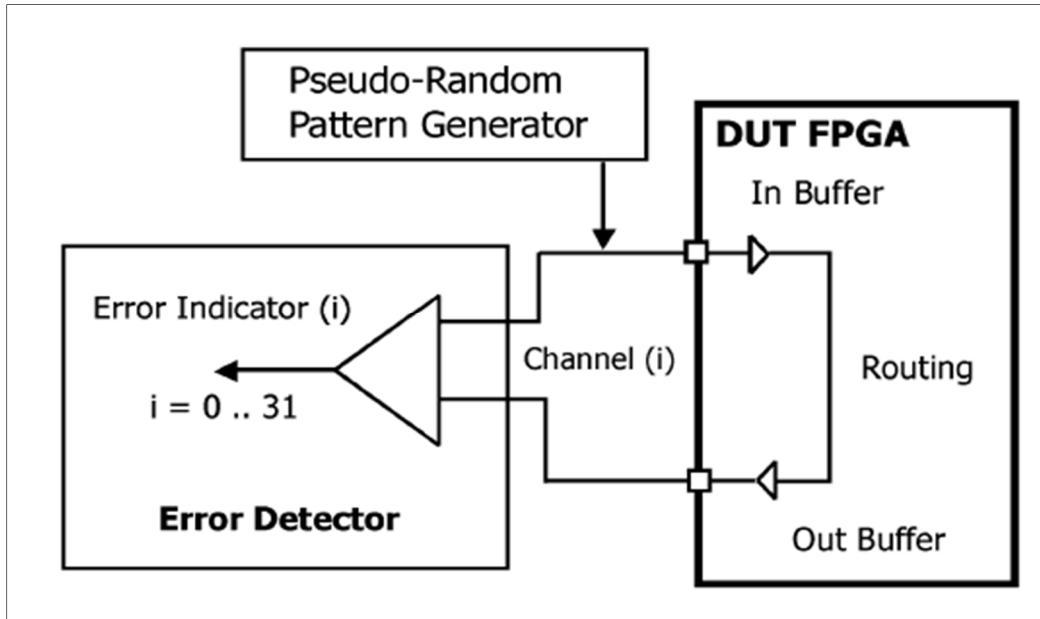

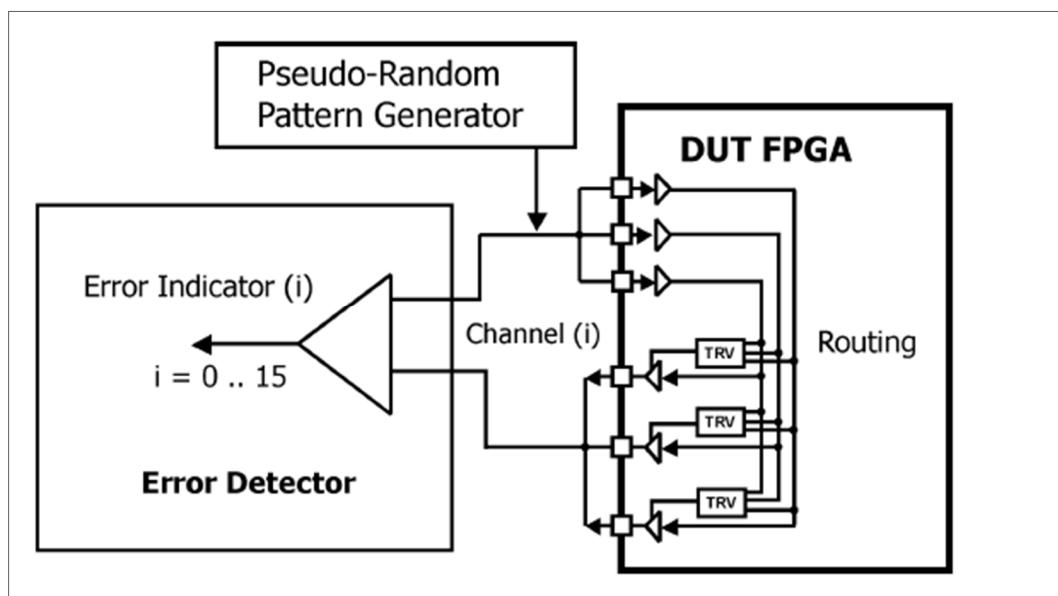

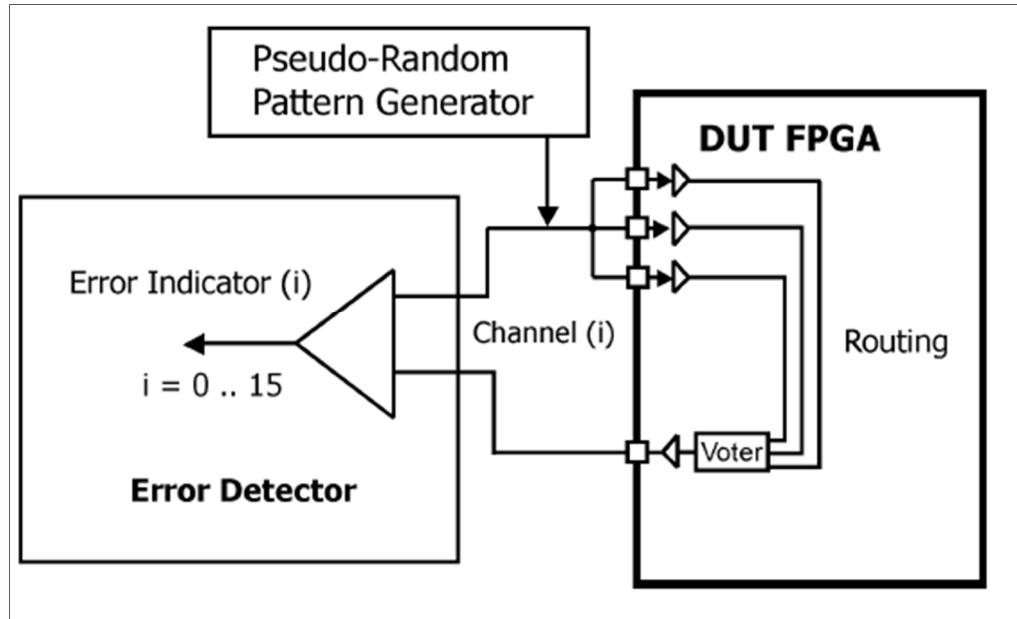

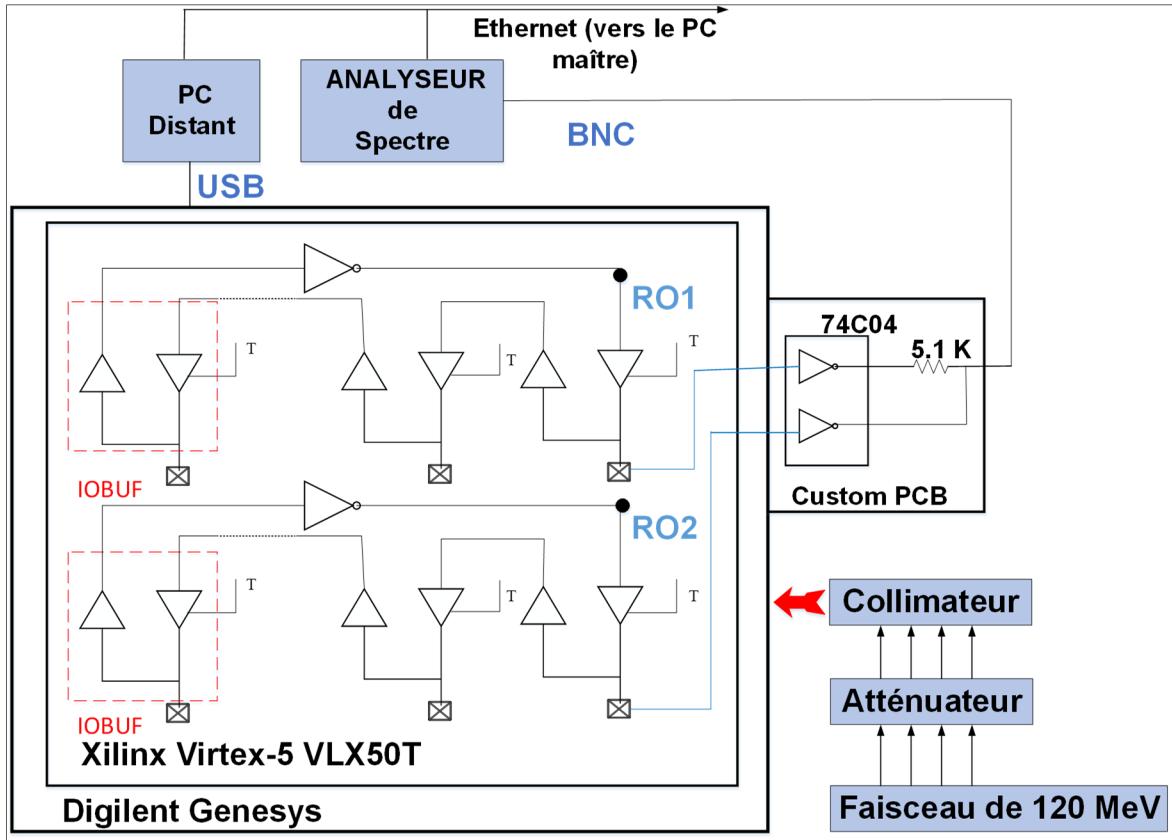

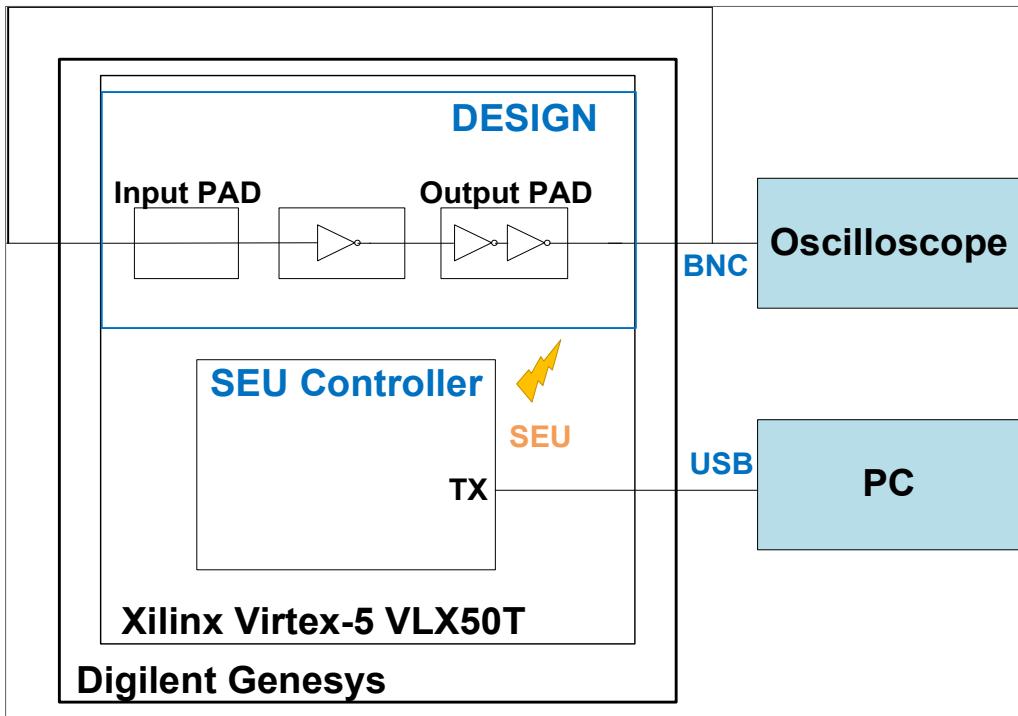

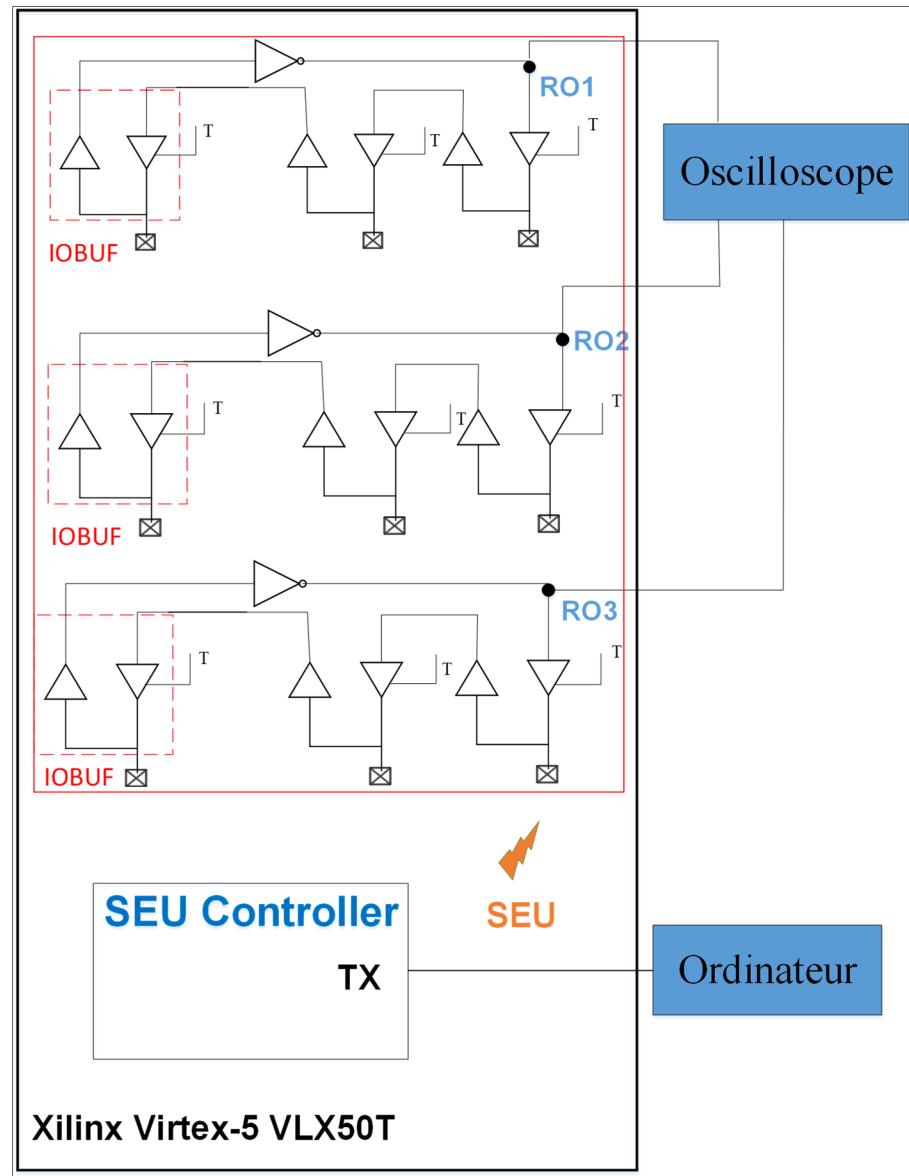

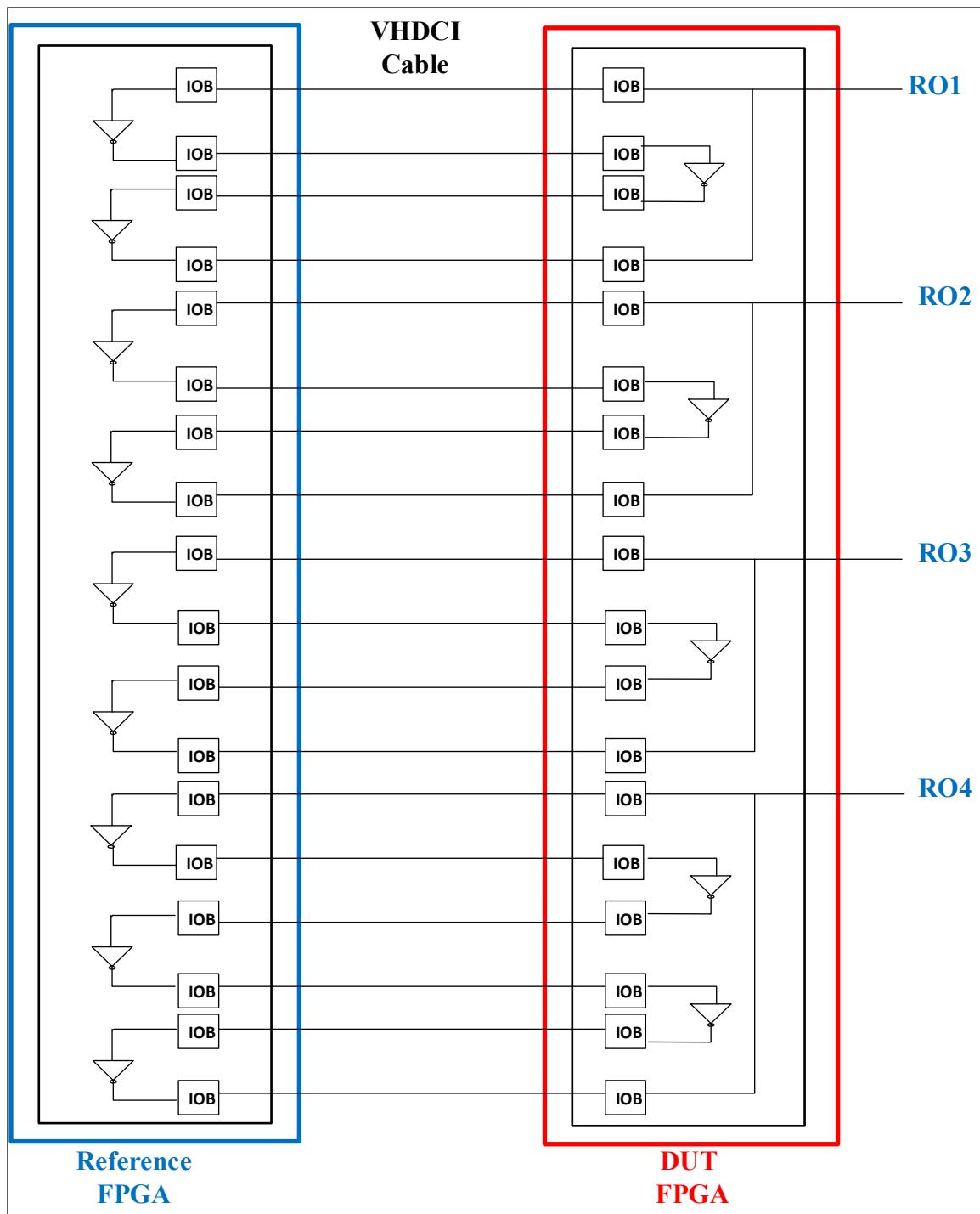

| Figure 3.1  | Montage d'émulation .....                                                                                                       | 49 |

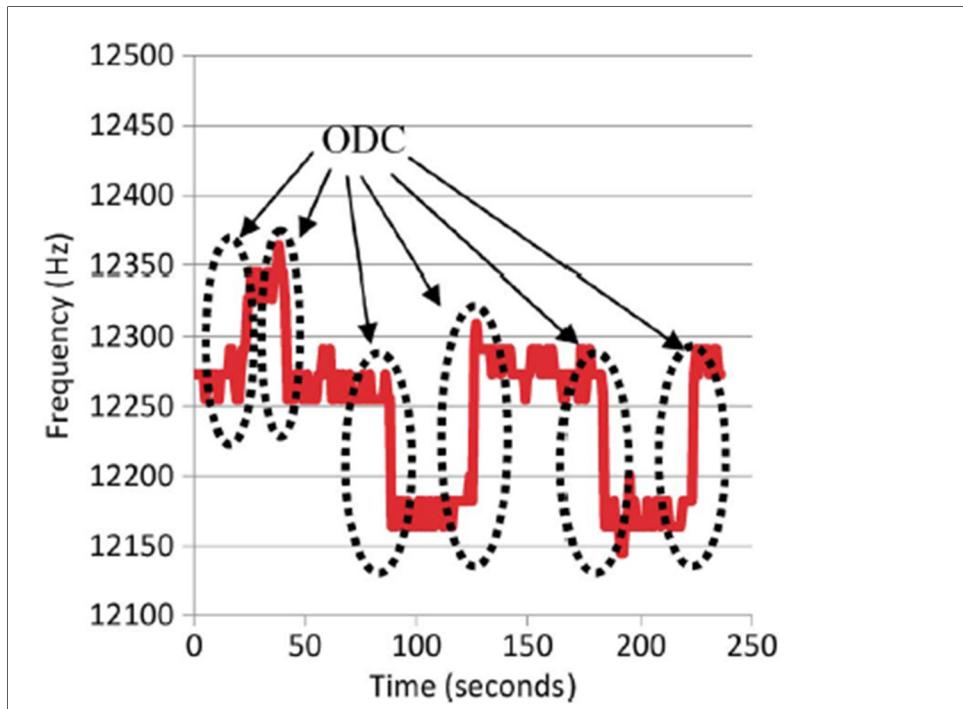

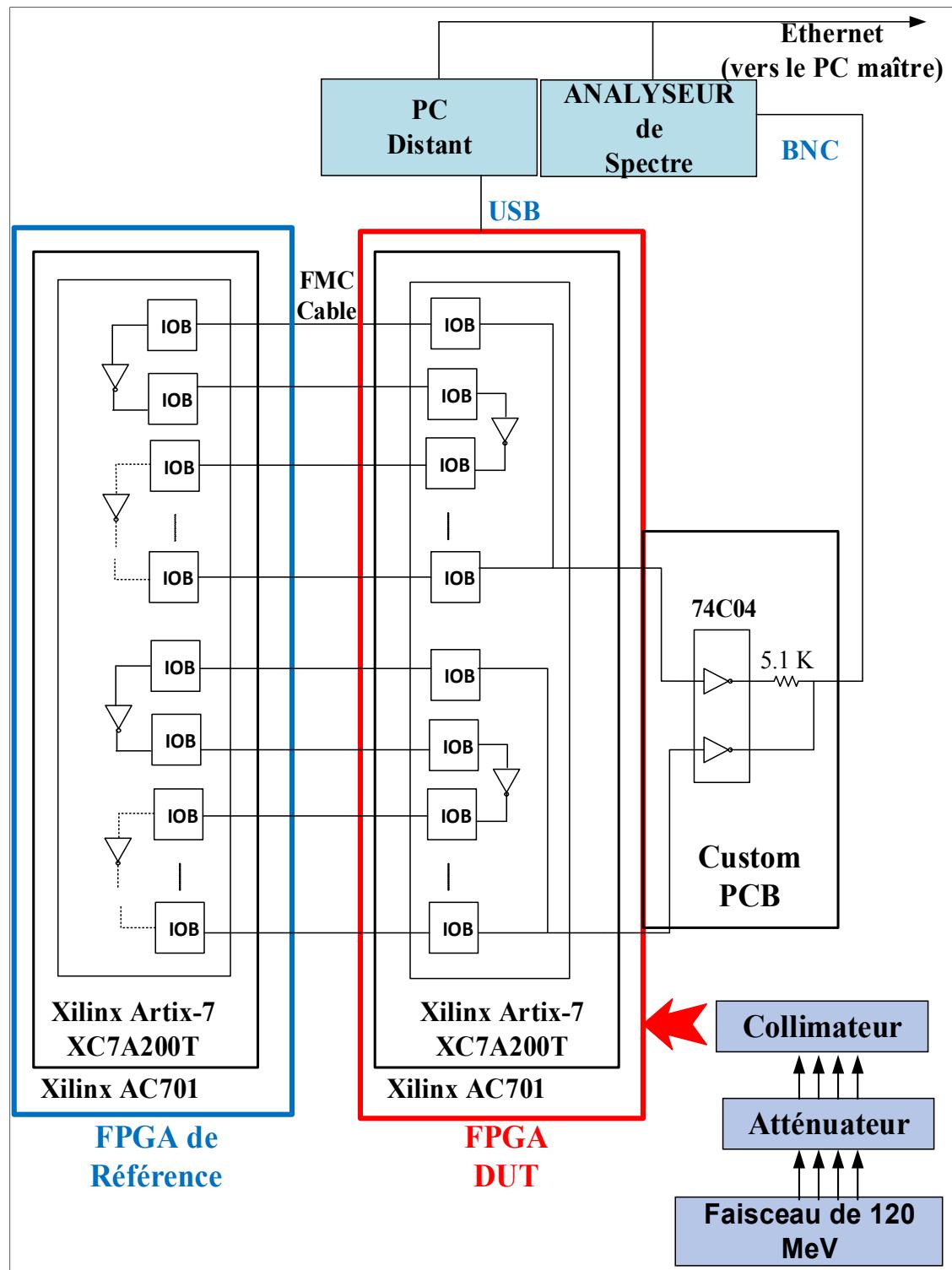

| Figure 3.2  | Premier montage expérimental utilisé à TRIUMF .....                                                                             | 54 |

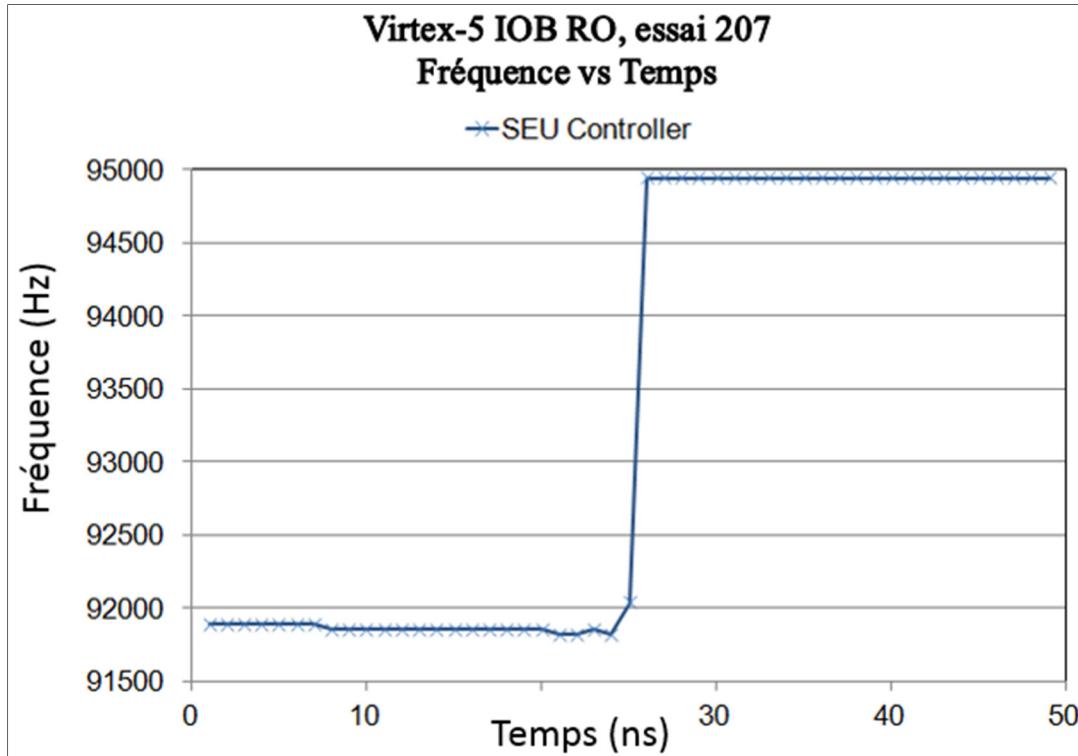

| Figure 3.3  | Graphique montrant un ODC d'une valeur de 3.9 ns .....                                                                          | 56 |

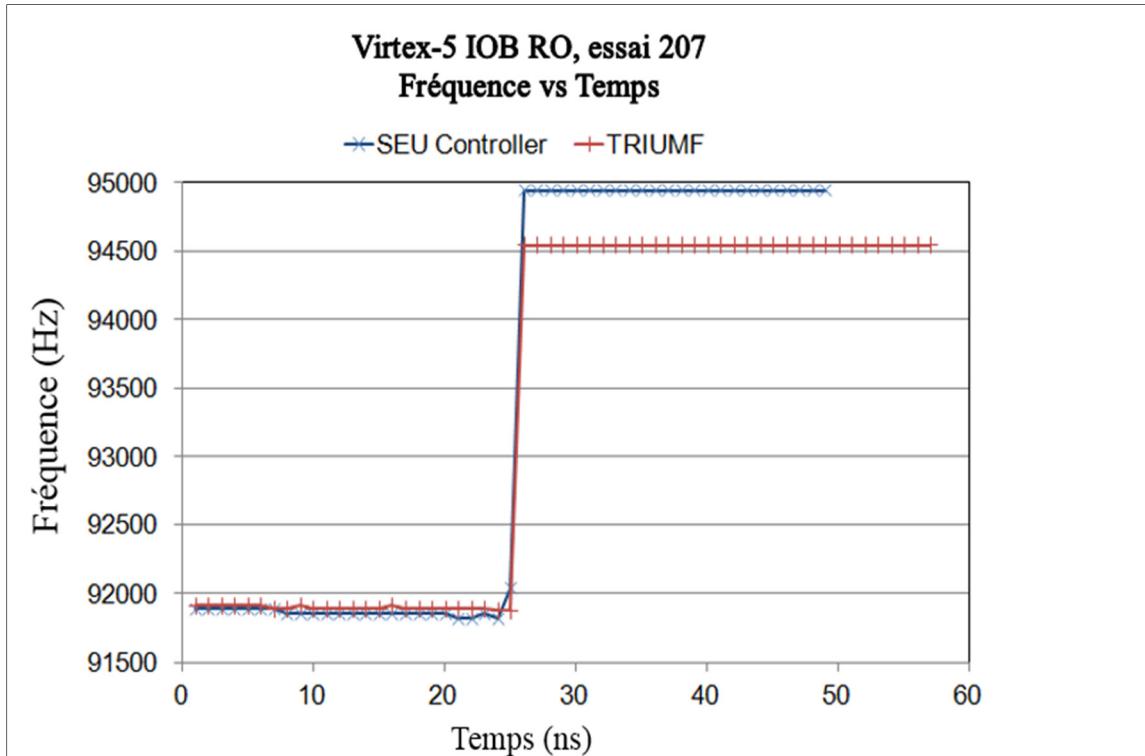

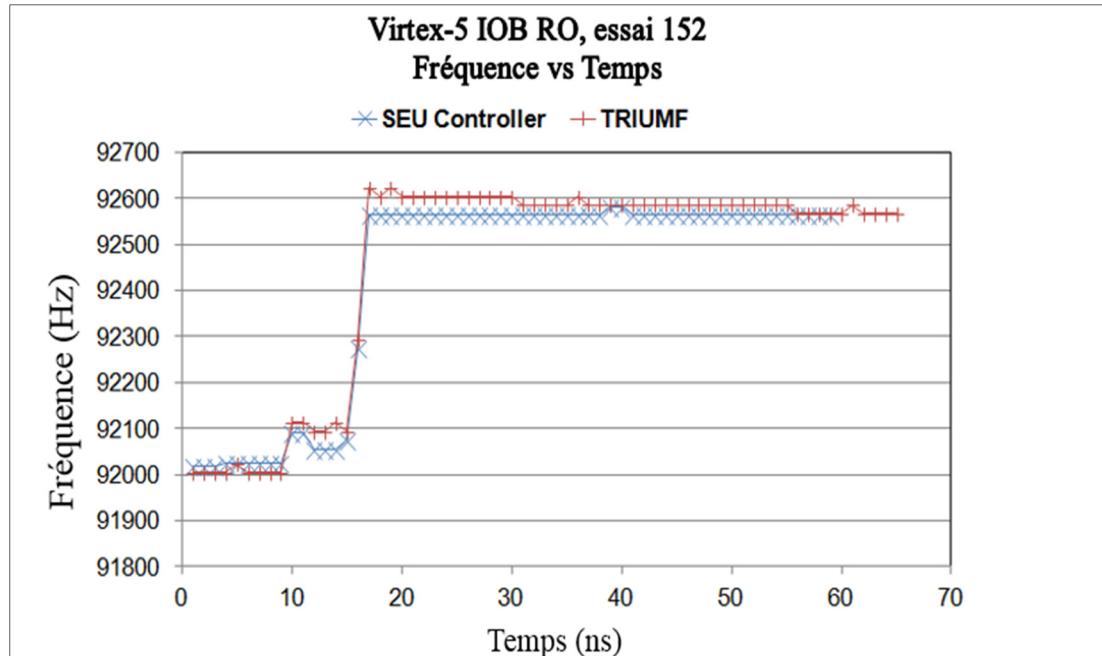

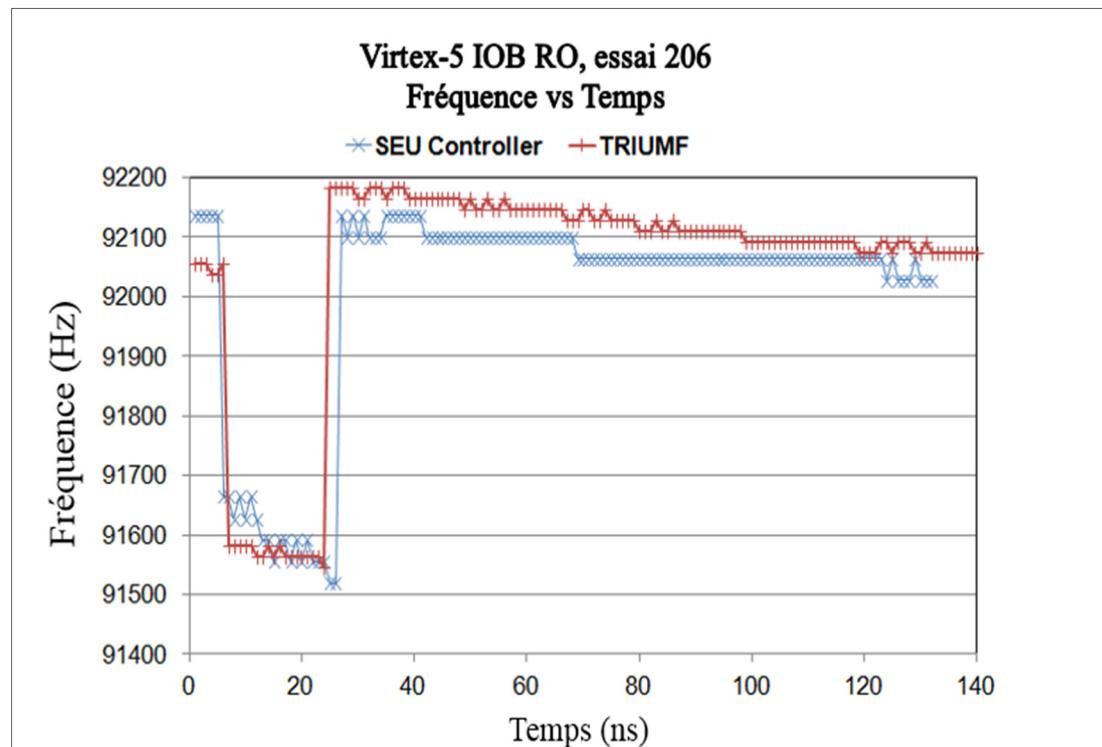

| Figure 3.4  | Comparaison entre les résultats d'émulation et d'irradiation; .....                                                             | 60 |

| Figure 3.5  | Résultats d'émulation vs irradiation; essai 152 .....                                                                           | 61 |

| Figure 3.6  | Résultats d'émulation vs irradiation; essai 206 .....                                                                           | 61 |

| Figure 3.7  | Montage expérimental de l'Artix-7 .....                                                                                         | 65 |

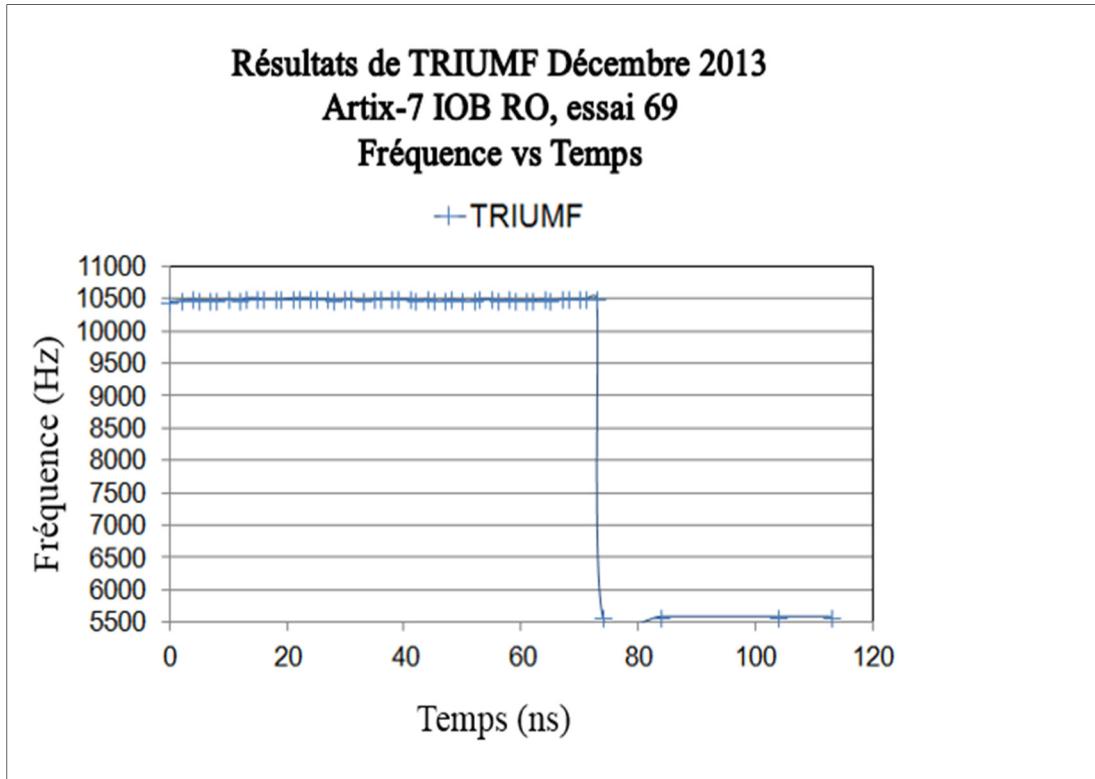

| Figure 3.8  | Résultats expérimentaux obtenus à TRIUMF; ODC égal à 3.8 ns .....                                                               | 66 |

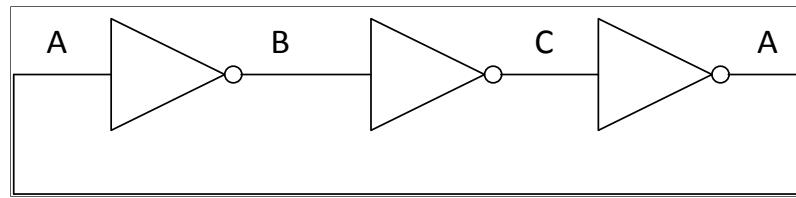

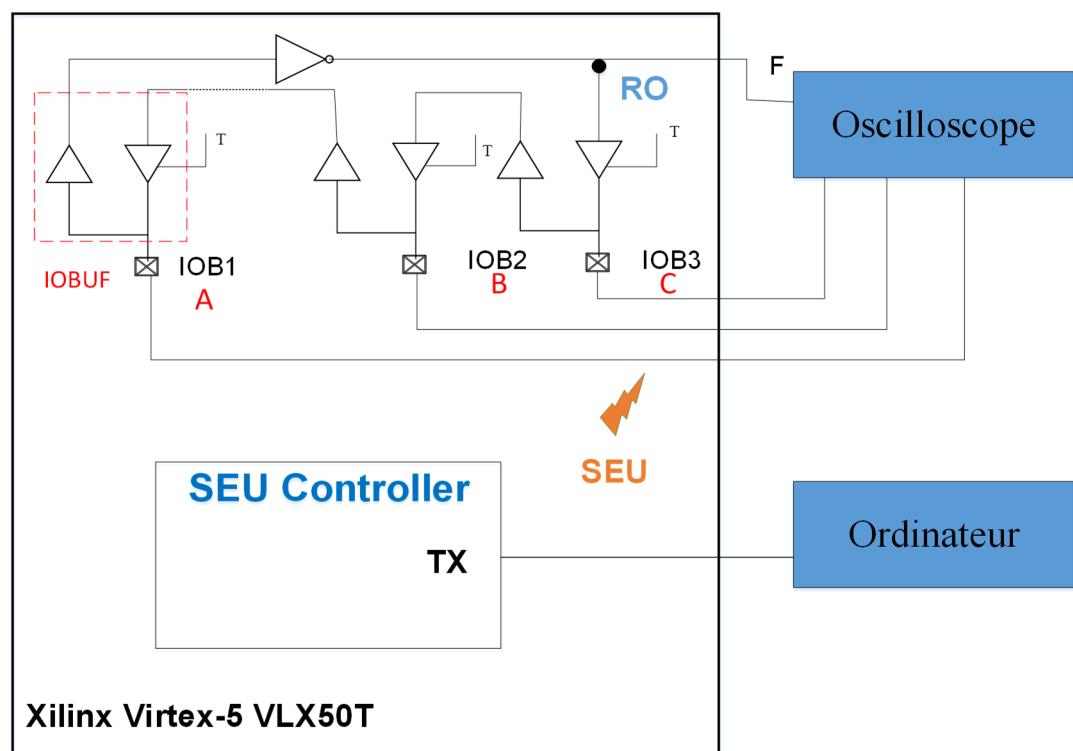

| Figure 4.1  | Oscillateur en boucle (RO) de 3 étages.....                                                                                     | 71 |

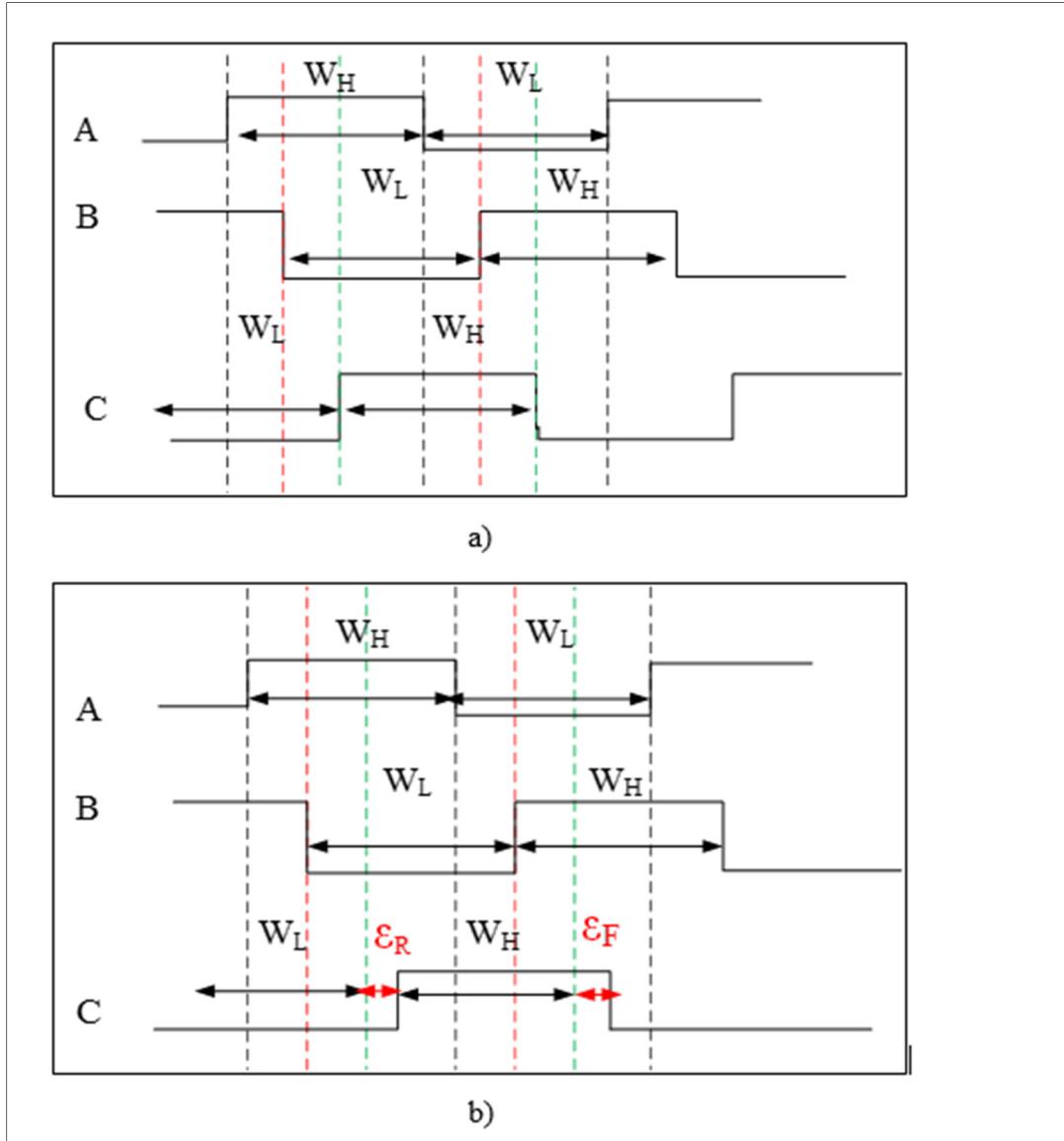

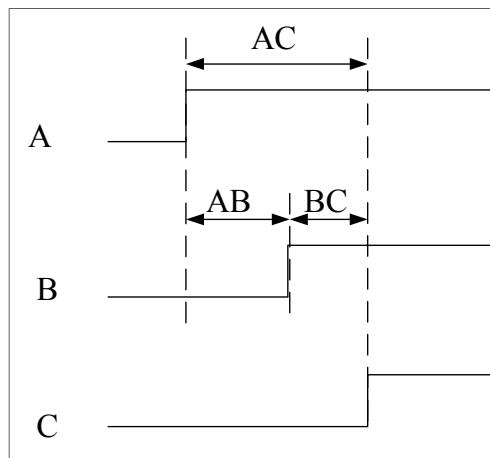

| Figure 4.2  | Chronogrammes simplifiés du RO de la figure 4.1 : a) Sans les délais induits par les radiations; b) avec ces mêmes délais ..... | 72 |

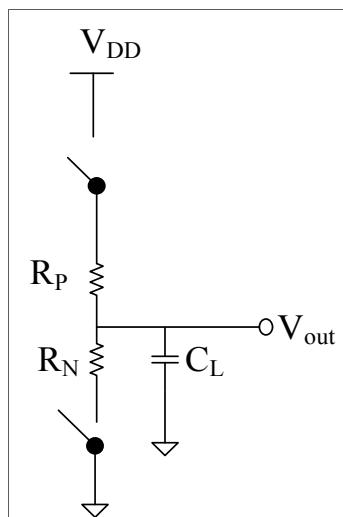

| Figure 4.3  | Modèle RC d'un inverseur CMOS .....                                                                                             | 74 |

| Figure 4.4  | Modèle RC de 1 <sup>er</sup> ordre équivalent au RO de la figure 4.1 .....                                                      | 76 |

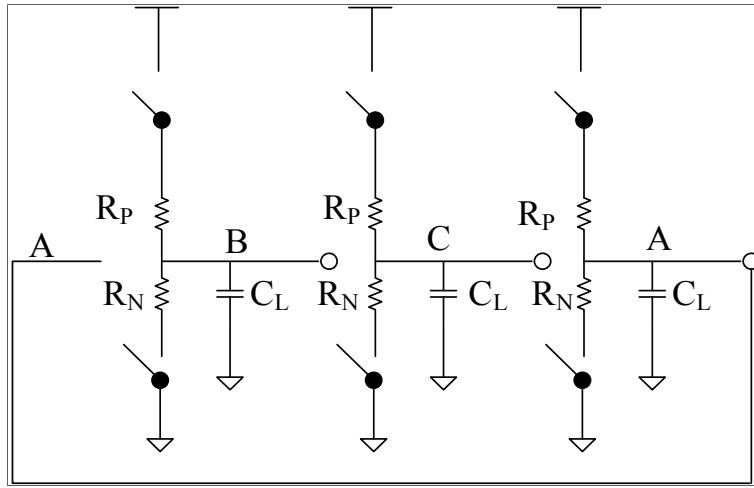

| Figure 4.5  | Résultats d'une simulation HSPICE des 4 modèles de délais .....                                                                 | 80 |

| Figure 4.6  | Montage expérimental de l'émulation .....                                                                                       | 82 |

|            |                                                                                                              |     |

|------------|--------------------------------------------------------------------------------------------------------------|-----|

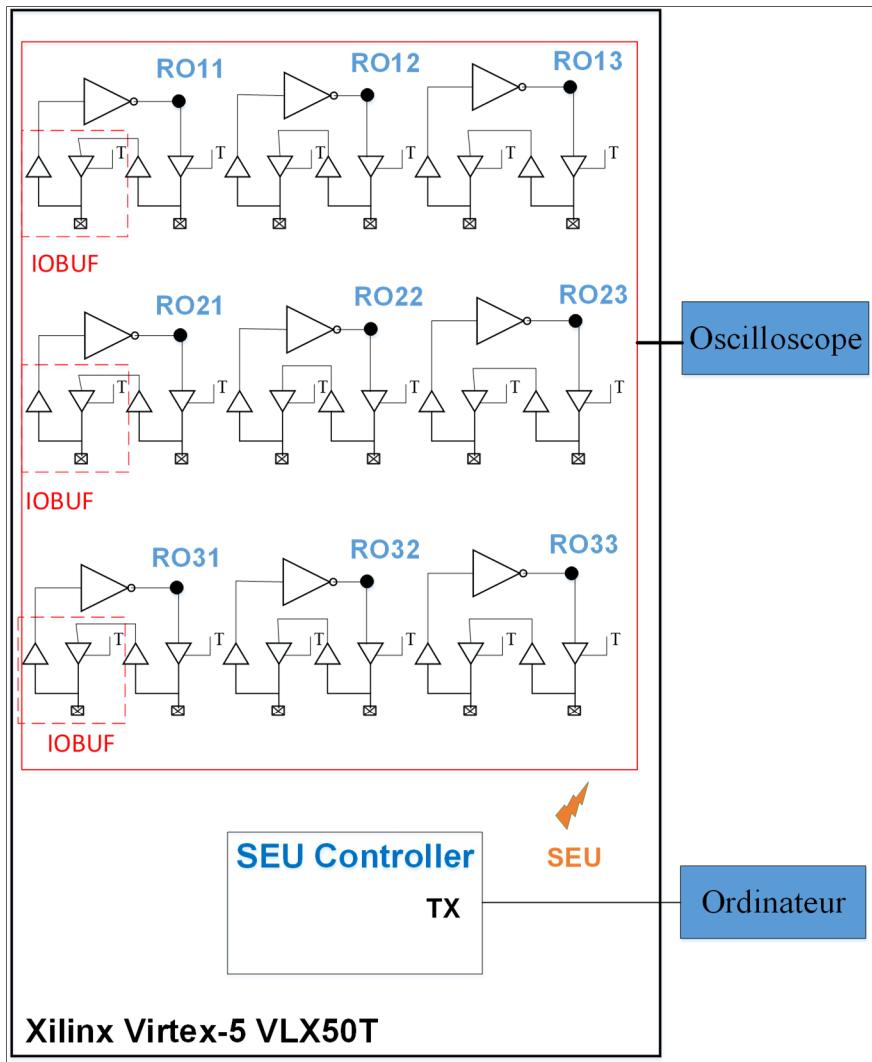

| Figure 5.1 | Montage utilisé pour mesurer la distribution des délais .....                                                | 87  |

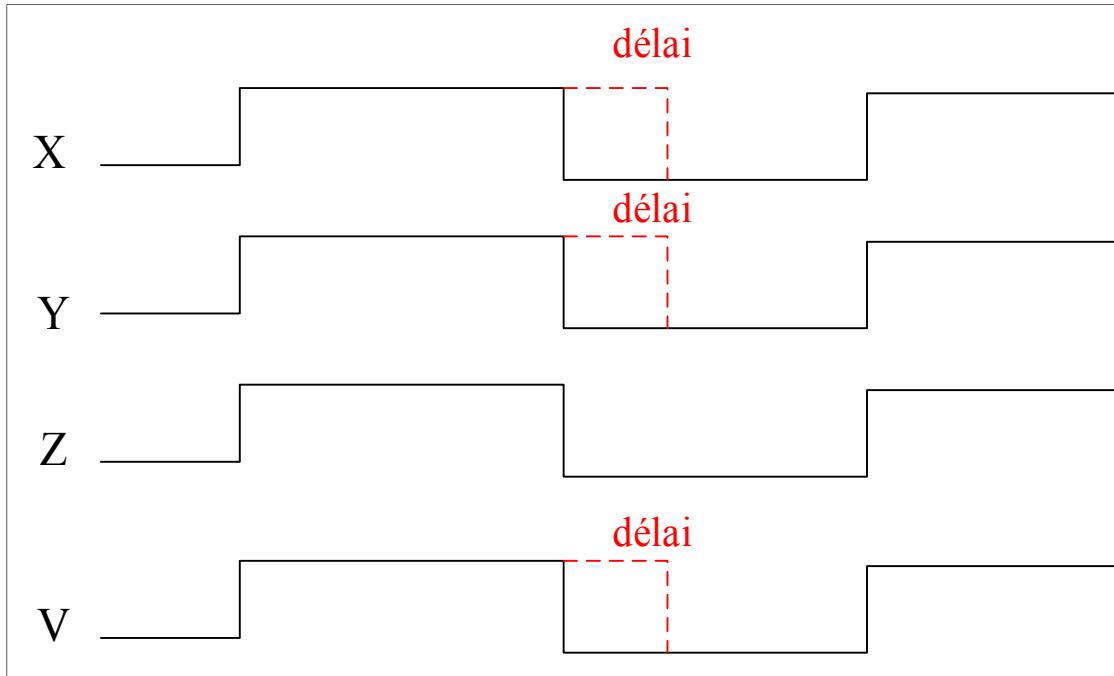

| Figure 5.2 | Mesure de délai .....                                                                                        | 88  |

| Figure 5.3 | Accumulation de délai réalisée par Labview .....                                                             | 89  |

| Figure 5.4 | Montage utilisé pour les expériences sur la robustesse .....                                                 | 93  |

| Figure 5.5 | Montage dérivé de celui de la figure 5.4 .....                                                               | 96  |

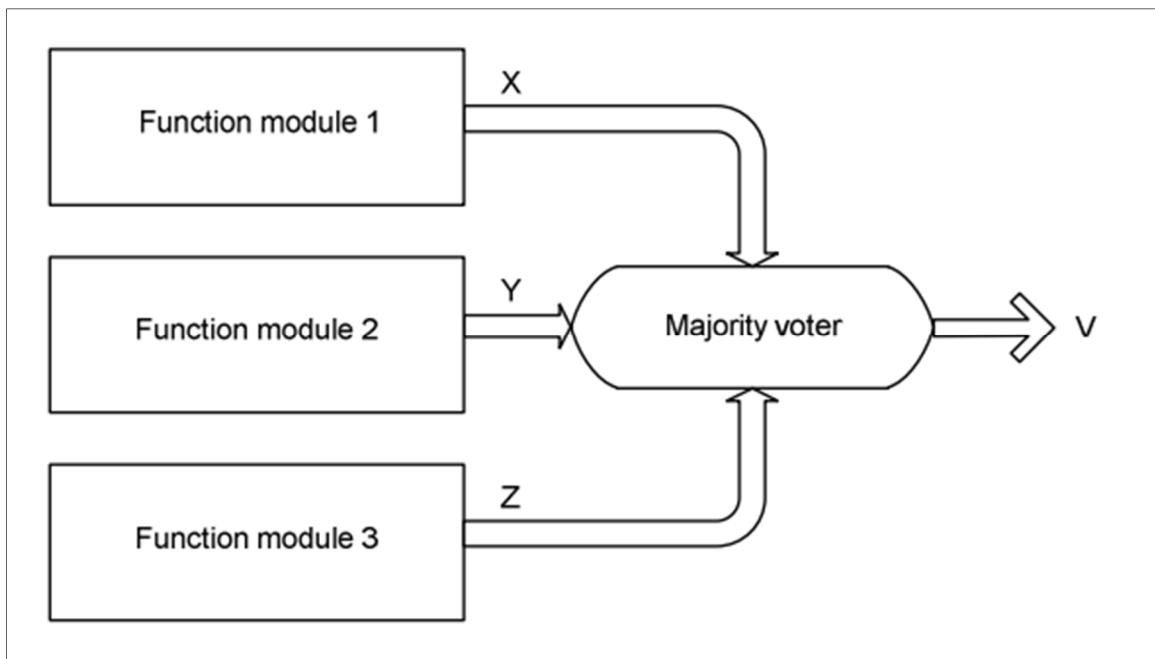

| Figure 5.6 | Diagramme bloc de le TMR .....                                                                               | 97  |

| Figure 5.7 | Chronogramme montrant la sortie du voteur dans le cas où 2 copies de la TMR sont touchées par un délai ..... | 98  |

| Figure 5.8 | Montage utilisé pour deux cartes FPGA de Xilinx .....                                                        | 101 |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|      |                                         |

|------|-----------------------------------------|

| ACM  | Auto Correction Mode                    |

| ASIC | Application Specific Integrated Circuit |

| BRAM | Block Random Access Memory              |

| CLB  | Configurable Logic Block                |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| CRC  | Cyclic Redundancy Check                 |

| DOM  | Detection Only Mode                     |

| DUT  | Device Under Test                       |

| FPGA | Field Programmable Gate Arrays          |

| IOB  | Input/Output Block                      |

| JTAG | Joint Test Action Group                 |

| LUT  | Look Up Table                           |

| MBU  | Multiple Bit Upset                      |

| MCU  | Multiple Cell Upset                     |

| NCD  | Native Circuit Description              |

| ODC  | Observable Delay Change                 |

| RO   | Ring Oscillator                         |

| ROB  | Ring Oscillator Break                   |

| RTL  | Register Transfert Level                |

| SEE  | Single Event Effect                     |

| SEFI | Single Event Functional Interrupt       |

| SEGR | Single Event Gate Rupture               |

|      |                                             |

|------|---------------------------------------------|

| SEL  | Single Event Latch-up                       |

| SER  | Single Event Rate                           |

| SES  | Single Event Snapback                       |

| SET  | Single Event Transient                      |

| SEU  | Single Event Upset                          |

| SHE  | Single event Hard Error                     |

| SRAM | Static Random Access Memory                 |

| TCL  | Tool Command Language                       |

| TMR  | Triple Modular Redundancy                   |

| UART | Universal Asynchronous Receiver Transmitter |

| VHDL | VHSIC Hardware Description Language         |

| XDL  | Xilinx Design Language                      |

## INTRODUCTION

L'incessante réduction de la taille des transistors rend l'électronique généralement plus sensible à l'effet des radiations cosmiques, ce qui a un impact sur la fiabilité des systèmes embarqués sujets à ces radiations. Certains intervenants du secteur de l'aéronautique n'hésitent pas à identifier les radiations comme une cause importante des dysfonctionnements des équipements. Ces dysfonctionnements disparaissent typiquement après que les équipements fautifs ont été réinitialisés. Cette sensibilité accrue des modules électroniques face aux radiations a même poussé les fournisseurs d'équipements à usage ininterrompu utilisés au niveau du sol, tels les serveurs informatiques, à s'y intéresser. Une des pistes de solutions pouvant être envisagées est l'utilisation des circuits intégrés qualifiés dits résistants aux radiations. Cependant, leur coût est souvent trop élevé par rapport à celui des circuits intégrés conventionnels. De plus, ils offrent une capacité d'intégration et une performance bien inférieures, car ils ont généralement quelques nœuds technologiques en retard sur les circuits commerciaux conventionnels en raison des modifications à apporter aux procédés de fabrication. Par conséquent, même les concepteurs de systèmes embarqués exposés aux radiations (ex. technologie spatiale) sont de plus en plus intéressés à utiliser des circuits intégrés conventionnels (non qualifiés), dont les circuits programmables de type FPGA.

La tolérance aux radiations n'est pas en soi un sujet nouveau. Il existe donc déjà plusieurs stratégies de tolérance qui ont été développées, en particulier pour les modules spatiaux. L'aspect nouveauté réside dans l'adaptation de ces stratégies au domaine de l'avionique. Comme l'intensité de radiations est moindre aux altitudes visées (par rapport aux orbites spatiales), il faut s'assurer d'avoir le bon niveau de protection, et ce très rapidement dans le processus de conception. Il devient donc important de pouvoir estimer de manière hâtive la sensibilité aux radiations des architectures proposées. Cette estimation de la sensibilité nécessite une estimation hâtive des ressources requises pour la mise en œuvre des applications avioniques ciblées.

Ce projet de thèse a démarré dans le cadre du projet CRIAQ AVIO403 qui vise à adapter les méthodologies conventionnelles d'intégration des systèmes embarqués avioniques afin de tenir compte de l'effet des radiations cosmiques, et ce lorsqu'elles sont réalisées à l'aide de circuits programmables de type FPGA. Ce projet se divise en quatre sous objectifs :

- l'élaboration et la mise en œuvre d'une stratégie de validation architecturale et d'exploration à haut-niveau de l'espace de conception;

- l'élaboration et la mise en œuvre d'une stratégie de vérification à niveaux d'abstraction multiples supportant la simulation de pannes liées à l'effet des radiations;

- l'élaboration et la mise en œuvre d'une stratégie de conception facilitant les tests en pré-certification pour la robustesse à l'égard des radiations;

- l'élaboration et la mise en œuvre d'une stratégie pour l'exploration de la tolérance aux pannes basée sur des systèmes industriels complexes.

L'objectif principal de ce projet de thèse, qui s'inscrit à l'intérieur du premier sous-objectif du projet AVIO403, est l'élaboration, la mise en œuvre et la validation d'une approche méthodique permettant d'estimer la sensibilité des ressources, requises pour l'implémentation d'applications avioniques dans les circuits cibles (FPGA), par rapport aux événements singuliers (Single Event Upset, SEU) et multiples (Multiple Bit Upset, MBU). Cette recherche étudie principalement la sensibilité des blocs d'entrée/sortie (IOB) des FPGA à base de mémoire SRAM (*SRAM-based FPGA*). Dans ce contexte particulier, l'effet des SEU et des MBU est de modifier le contenu des cellules de mémoires SRAM, de 0 vers 1 ou de 1 vers 0.

Ainsi, la contribution majeure de cette thèse est d'étudier les effets de ces événements singuliers (SEU) et multiples (MBU) sur les IOB des FPGA à base de SRAM. Plus précisément, cette thèse vise à établir un modèle de pannes de délai permettant de caractériser l'impact de ces événements (SEU et MBU) affectant les IOB. Quelques travaux ont été effectués dans ce domaine (Iturbe et al., 2009), (Napier et al., Sept. 2004), (Quinn et al., 2005), (Rollins et al., 2002), (Swift et al., 2004). Cependant, ils n'analysent pas en détail tous les effets possibles engendrés dans les IOB; par exemple l'étude du comportement des IOB face à une panne de délai.

Afin de répondre à cette problématique, cette thèse s'est appuyée sur l'étude de deux FPGA (Virtex-5 et Artix-7) du fabricant Xilinx. Deux différentes techniques ont été utilisées pour générer des SEU, à savoir l'injection de pannes et les expériences réelles d'irradiation. L'injection de pannes a été réalisée avec le SEU Controller, un outil fourni par Xilinx et qui permet de détecter et corriger un SEU, mais aussi d'injecter des pannes sur les bits de configuration. Tandis que les expériences réelles de radiation ont été faites au laboratoire TRIUMF à Vancouver en utilisant un faisceau de protons.

Ces travaux de thèse ont mené à 3 contributions :

- (Tazi et al., 2014), a montré l'existence des délais additionnels induits par les radiations dans les blocs d'entrée/sortie des FPGA à base de SRAM. Ces délais ont été obtenus par deux approches différentes : expérimentalement avec des tests accélérés en irradiation et avec émulation en utilisant le SEU Controller. De plus, cet article fournit une meilleure compréhension du comportement des IOB sous l'effet des radiations;

- (Tazi, Thibeault et Savaria, 2016) a présenté une étude plus poussée de l'effet des radiations sur les délais observés dans les IOB des FPGA à base de SRAM. Plus spécifiquement, cette recherche a proposé et validé des modèles de pannes permettant de décrire et de mieux comprendre les mécanismes pouvant mener aux délais observés dans les IOB;

- l'étude approfondie des effets des événements singuliers (SEU) sur les techniques de mitigation (TMR et *Scrubbing*) lorsqu'elles sont appliquées à l'intérieur des blocs d'entrée/sortie (IOB) des FPGA à base de SRAM.

Cette thèse est organisée comme suit :

Le premier chapitre présente des notions de base expliquant les différentes connaissances nécessaires à la compréhension de ce sujet de thèse. Les rayons cosmiques ainsi que les pannes qui en découlent sur les circuits numériques y sont d'abord décrits. Ensuite, l'architecture des FPGA à base de SRAM ainsi que les effets des radiations sur ce type de circuits y sont présentés. Finalement, les différentes techniques d'injection de pannes et de mitigation sont décrites.

Le deuxième chapitre présente la revue de littérature effectuée, se concentrant notamment au niveau de l'effet des SEU sur la logique et sur le routage des FPGA basés sur des SRAM, ainsi que sur les IOB.

Le troisième chapitre présente la première contribution, à savoir l'existence des pannes de délais dans les IOB. Il décrit aussi la méthodologie suivie pour démontrer l'existence de ces pannes. Il explique par la suite le processus d'injection de pannes par émulation, avec les expériences réelles d'irradiation ainsi que les résultats obtenus dans les deux cas. À la fin, il donne une comparaison entre les deux techniques d'injection de pannes et montre la portabilité de notre méthodologie sur plusieurs familles de FPGA.

Le quatrième chapitre présente la deuxième contribution, à savoir les différents modèles de pannes permettant de décrire et de mieux comprendre les mécanismes pouvant mener aux délais observés dans les IOB. Il explique aussi les différents modèles théoriques et expérimentaux.

Le dernier chapitre décrit la troisième et dernière contribution, à savoir l'étude de la robustesse des techniques de mitigation dans les IOB. Le processus, la méthodologie ainsi que les différents montages y sont présentés, de même que les résultats obtenus. Ces résultats ont montré que les techniques de mitigation, spécialement les TMR, peuvent être affectées aussi par les SEU lorsqu'elles sont appliquées à l'intérieur des IOB et donc elles deviennent inefficaces pour la mitigation de ce type de pannes. Ces résultats ouvrent une grande porte de réflexion sur le type de technique de mitigation à utiliser dans les IOB en présence des SEU. Cette thèse se conclut par une discussion sur les pistes envisageables pour d'éventuels travaux futurs.

# CHAPITRE 1

## NOTIONS DE BASE

### 1.1 Environnement radiatif naturel

Les circuits intégrés modernes sont confrontés à des environnements radiatifs naturels différents. Ces derniers sont généralement décomposés en deux sous catégories (Boudenot, 1995) : l'environnement radiatif naturel spatial et l'environnement radiatif naturel atmosphérique. Le premier est relié aux applications spatiales et émet des particules énergétiques différentes qui comprennent essentiellement des électrons, des protons et des ions lourds. Le deuxième concerne les applications terrestres et aéronautiques et il est composé des interactions entre l'atmosphère et les particules spatiales.

#### 1.1.1 Environnement radiatif spatial

L'environnement radiatif spatial peut être décomposé en quatre catégories : le rayonnement cosmique, le vent solaire, les éruptions solaires et les ceintures de radiations.

##### 1) Rayonnement cosmique

Le rayonnement cosmique a été découvert pour la première fois par V. Hess en 1912 (Bocquillon, 2009). L'origine de ce rayonnement n'est pas très bien connue. Par contre, il a été supposé qu'il provient de deux sources : galactique et extragalactique.

Ce rayonnement est constitué de plusieurs particules. Les ions, qui sont les particules les plus énergétiques et dont l'énergie varie de quelques MeV à plusieurs GeV, représentent 1 % du flux observé. Les protons constituent 87 % du rayonnement cosmique et les noyaux d'hélium en forment 12 %.

Les flux des particules composant le rayonnement cosmique sont modulés par le cycle d'activité du Soleil. Lorsque le Soleil est en pleine activité, le vent solaire s'oppose aux flux de rayons cosmiques.

## 2) Vent solaire

Le vent solaire est un flot de particules chargées s'échappant en permanence de la haute atmosphère (couronne) du Soleil (Foucard, 2010). Il est composé essentiellement de protons, d'électrons et de noyaux d'Hélium. Il s'échappe continuellement et dans toutes les directions de la surface du Soleil et baigne l'ensemble du système solaire. La densité de ces particules varie de  $10^{12}$  particules/cm<sup>3</sup> au niveau du soleil jusqu'à 10 particules/cm<sup>3</sup> au niveau de l'orbite terrestre.

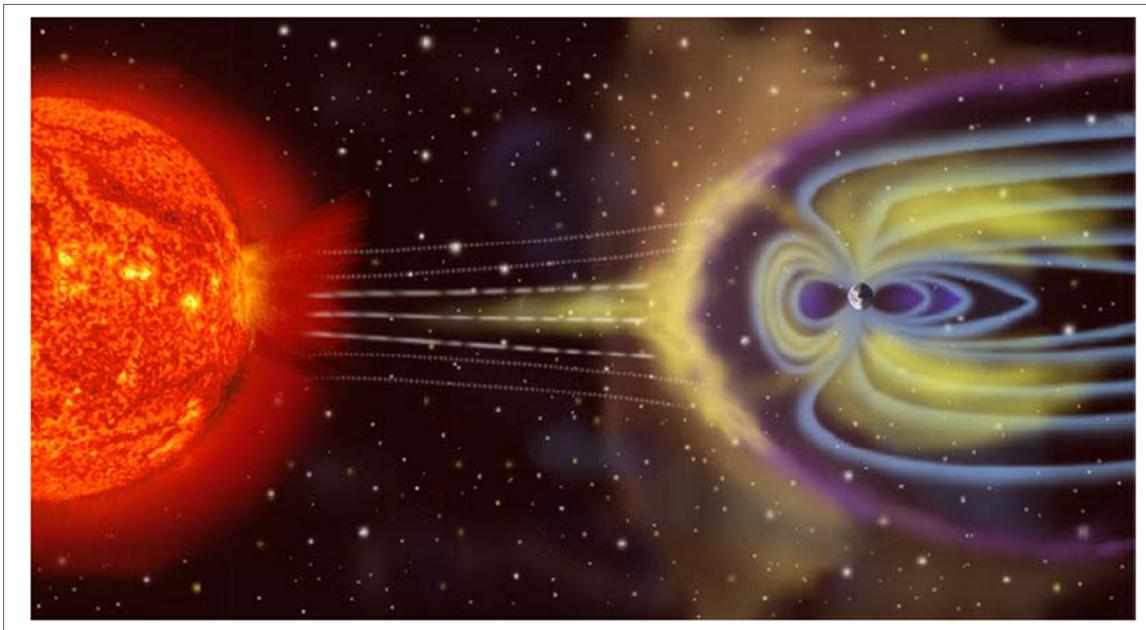

Le vent solaire peut créer des cavités magnétosphériques lorsqu'il interagit avec les planètes du système solaire en général et avec la Terre en particulier. La figure 1.1 montre la forme de cette magnétosphère terrestre.

Figure 1.1 Effet du vent solaire sur la magnétosphère terrestre

Tirée de Barth (1999)

### 3) Éruptions solaires

Une éruption solaire est un événement primordial de l'activité du Soleil (Bocquillon, 2009). La variation du nombre d'éruptions solaires permet de définir un cycle solaire d'une période moyenne de 11 ans. Ce cycle solaire est composé de deux périodes essentielles: une période de 4 ans qui caractérise l'activité faible du Soleil et une autre de 7 ans relative à son activité haute. La période haute est ponctuée par les éruptions solaires qui s'affirment par des émissions importantes de particules énergétiques. Deux types d'éruptions solaires peuvent être distingués, selon la nature de ces particules :

- les éruptions solaires à protons, dont l'émission principale est composée de protons d'énergie considérable (jusqu'à quelques centaines de MeV). Cette émission ne dure seulement que quelques heures à quelques jours;

- les éruptions solaires à ions lourds, dont l'émission principale est composée d'ions lourds. Cette émission dure seulement quelques heures.

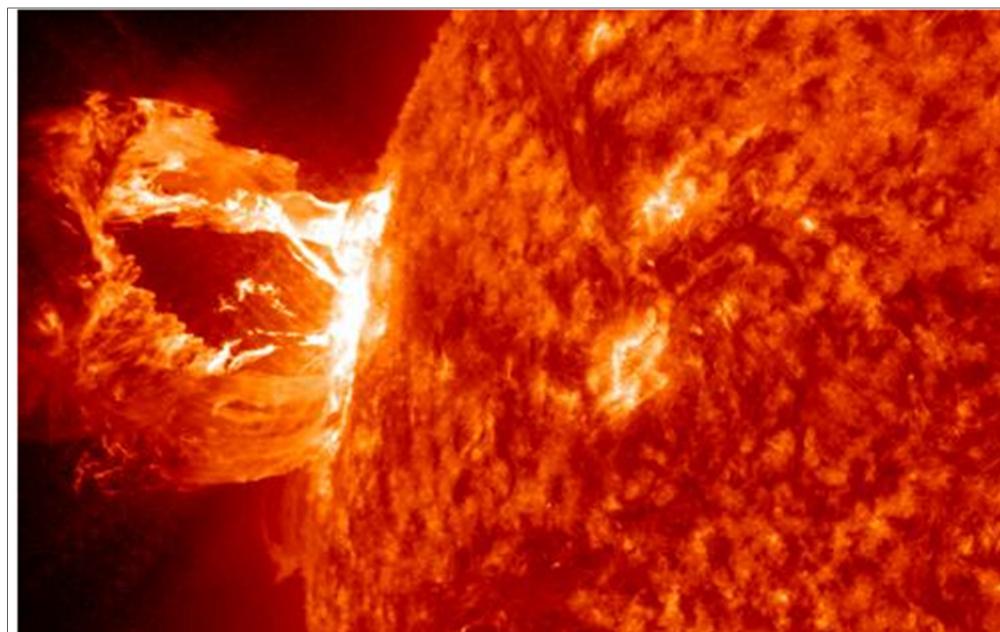

La figure 1.2 montre une image d'une éruption solaire capturée par la NASA.

Figure 1.2 Exemple d'éruption solaire

Tirée de Bocquillon (2009)

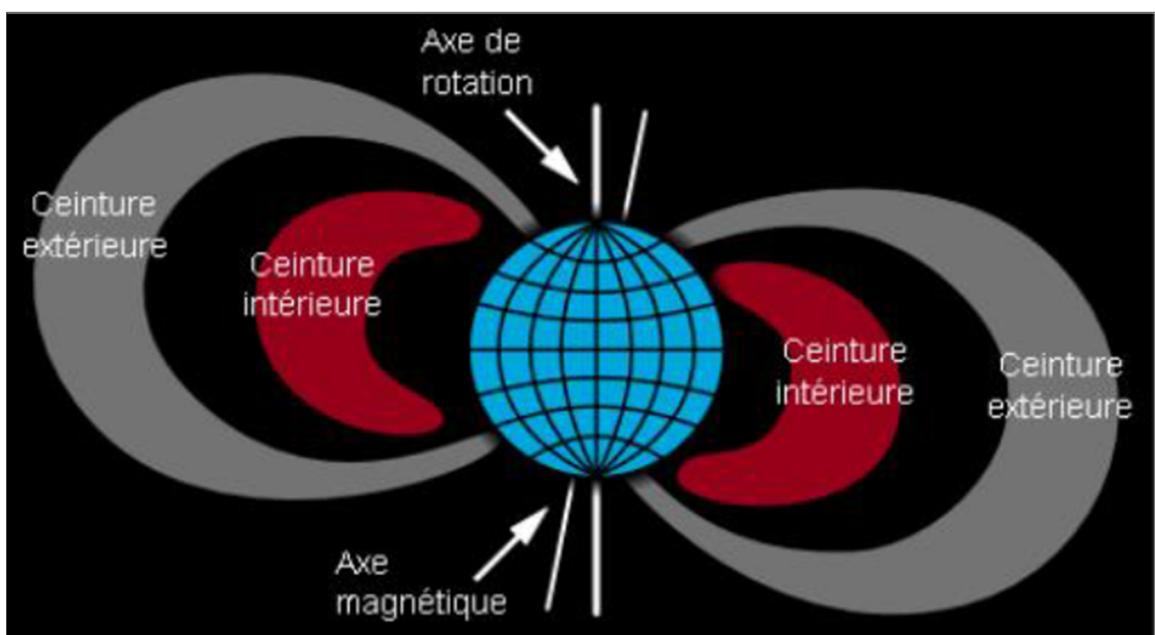

#### 4) Ceintures de radiation

Les ceintures de radiation sont des zones toroïdales de la magnétosphère terrestre contenant une grande densité de particules énergétiques (Souari, 2016). Elles sont nommées aussi ceintures de Van Allen en l'honneur du physicien qui les a découvertes. Elles sont constituées principalement de deux ceintures nommées ceinture interne et ceinture externe. La première est située à une altitude variant entre 700 km et 10000 km et est principalement constituée de protons à haute énergie (plusieurs centaines de MeV). La deuxième s'étend de 13000 km à 65000 km et est essentiellement composée de neutrons de quelques MeV d'énergie. La figure 1.3 donne la forme des ceintures de Van Allen.

Figure 1.3 La forme de ceinture de Van Allen

Tirée de Souari (2016)

##### 1.1.2 Environnement radiatif atmosphérique

L'atmosphère terrestre est le protecteur par excellence de la terre et de son environnement contre les radiations spatiales (Ziegler et al., 1994). Seulement une petite partie de ces radiations peut pénétrer dans l'atmosphère terrestre. Ce type de radiations est appelé radiations

atmosphériques et elles sont dues à l'interaction entre les radiations cosmiques et les atomes qui composent l'atmosphère, à savoir l'azote et l'oxygène.

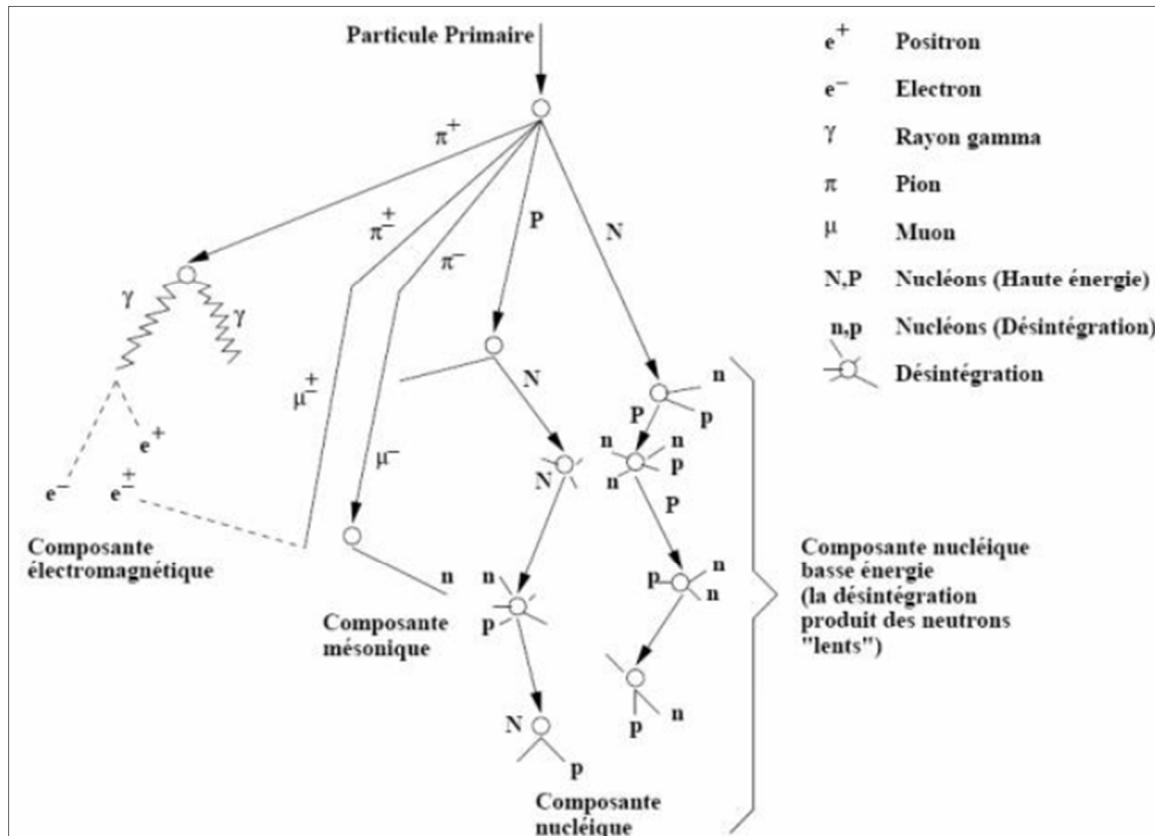

Les particules de l'atmosphère peuvent réagir selon deux modes : soit elles perdent une partie de leur énergie par ionisation, soit elles créent le phénomène de la douche magnétosphérique, qui est une cascade de particules secondaires. La figure 1.4 montre ce phénomène et présente les principales particules à savoir les électrons, les protons, les muons, les photons et les pions.

Le flux de ces radiations dépend de l'altitude et de la latitude. Il est moins important quand il se rapproche du sol et donc il est 300 fois moins fort au niveau de la mer. Aussi, il est 4 fois plus fort aux pôles qu'à l'équateur.

Figure 1.4 Présentation de la cascade magnétosphérique et la production des particules secondaires

Tirée de Ziegler et al. (1994)

Les altitudes des vols commerciaux sont les plus importants pour notre recherche et la radiation dominante à cette altitude est constituée de neutrons. Ces particules peuvent engendrer des pannes pour les équipements électroniques quand elles intérgissent avec les particules qui composent ces composants. Le flux des neutrons qui contribuent aux erreurs au niveau du sol est estimé à 10 particules par  $\text{cm}^2$  par heure. Par contre, il est estimé à  $10^4$  particules par  $\text{cm}^2$  par heure au niveau des vols commerciaux (ASSOCIATION, 2006).

## 1.2 Effets des radiations sur les circuits électroniques : les événements singuliers

Les radiations cosmiques peuvent engendrer des erreurs sur les composants électroniques. Ces erreurs peuvent être transitoires, permanentes ou destructives. Elles sont classées en deux catégories : les événements singuliers et les effets de dose (Bocquillon, 2009).

### 1.2.1 Événements singuliers

Les événements singuliers appelés aussi « Single Event Effects » (SEEs), sont des erreurs causées par une seule particule nucléaire entrant en collision avec les composantes des circuits intégrés. Elles peuvent être classées en deux types : effets destructifs (permanents) et non destructifs (*soft error*) (Gaillard, 2011).

Les erreurs permanentes et irréversibles ou erreurs matérielles (Single Event Latch-up (SEL), Single Event Gate Rupture (SEGR), Single Event Snapback (SES)) ne seront pas détaillées dans le cadre de cette thèse, considérant que ces erreurs sont pratiquement absentes aux altitudes ciblées. Par contre, les effets non destructifs sont détaillés dans ce qui suit.

#### Effets non destructifs

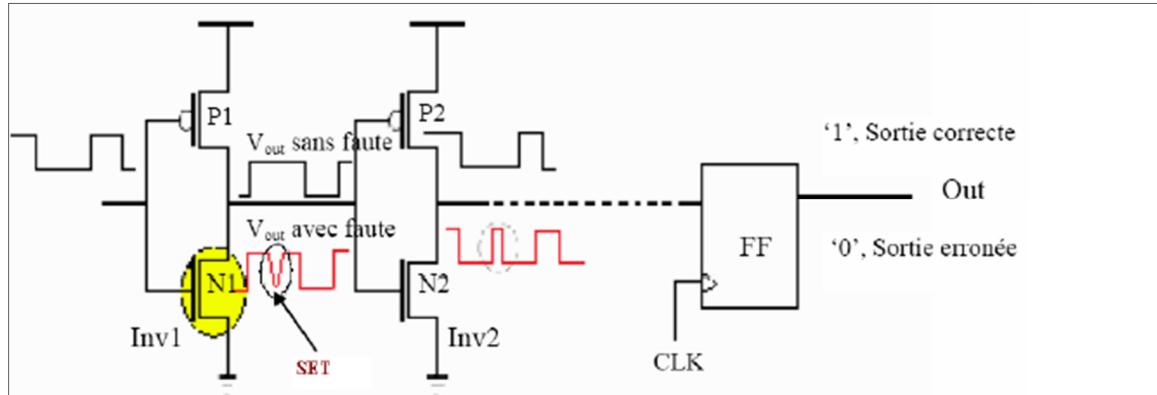

**SET (Single Event Transient)** (Mavis et Eaton, 2000) : Le SET est une impulsion de courant transitoire qui peut se propager dans un circuit logique et qui est éventuellement capturée dans une cellule mémoire (ex. bascule). La figure 1.5 montre un exemple d'un SET se propageant

entre deux inverseurs. Si le SET est mémorisé, il peut devenir un SEU. Dans cette thèse, nous ne nous intéressons pas directement aux SET.

Figure 1.5 Exemple d'un SET propageant entre deux inverseurs

Tirée de Bocquillon (2009)

**SEU (Single Event Upset):** le SEU est un type d'évènement singulier qui affecte principalement les éléments mémoire (SRAM). Il consiste à changer l'état logique d'un bit de la cellule mémoire à son complémentaire.

Un SEU n'est pas destructif et il peut être corrigé par une simple réécriture.

**MCU (Multiple Cell Upset) :** le MCU est un type d'erreur causé par une seule particule qui engendre le changement de plusieurs points mémoires géographiquement voisins. La diminution de la taille des transistors engendre l'augmentation de la probabilité des MCU dans les circuits intégrés.

La diminution de la taille des transistors agit sur deux paramètres (Bocquillon, 2009) :

- 1) la diminution de la charge critique par bit. En effet la charge critique nécessaire pour inverser un bit de mémoire diminue avec la diminution de la tension d'alimentation et des capacités parasites dans la cellule mémoire;

- 2) la diminution de la distance entre les zones de collection de charge.

**MBU (Multiple Bit Upset) :** le MBU est un cas particulier de MCU qui correspond au changement d'état de plusieurs nœuds de mémoires appartenant au même mot logique et qui

est provoqué par la même particule. Plusieurs études se sont intéressées à l'étude de ce type d'erreur (Gasiot, Giot et Roche, 2007), (Quinn et al., 2005), (Tipton et al., 2008), (Violante et al., 2007).

**SEFI (Single Event Functional Interrupt) (Serpone et al., 2007)** : Ce type de panne se manifeste par une perte de la fonctionnalité d'un système. Dans le cas des FPGA, le SEFI est causé par un SEU qui n'est corrigé que par une intervention extérieure au niveau du FPGA.

### 1.3 Architecture des FPGA à base de SRAM

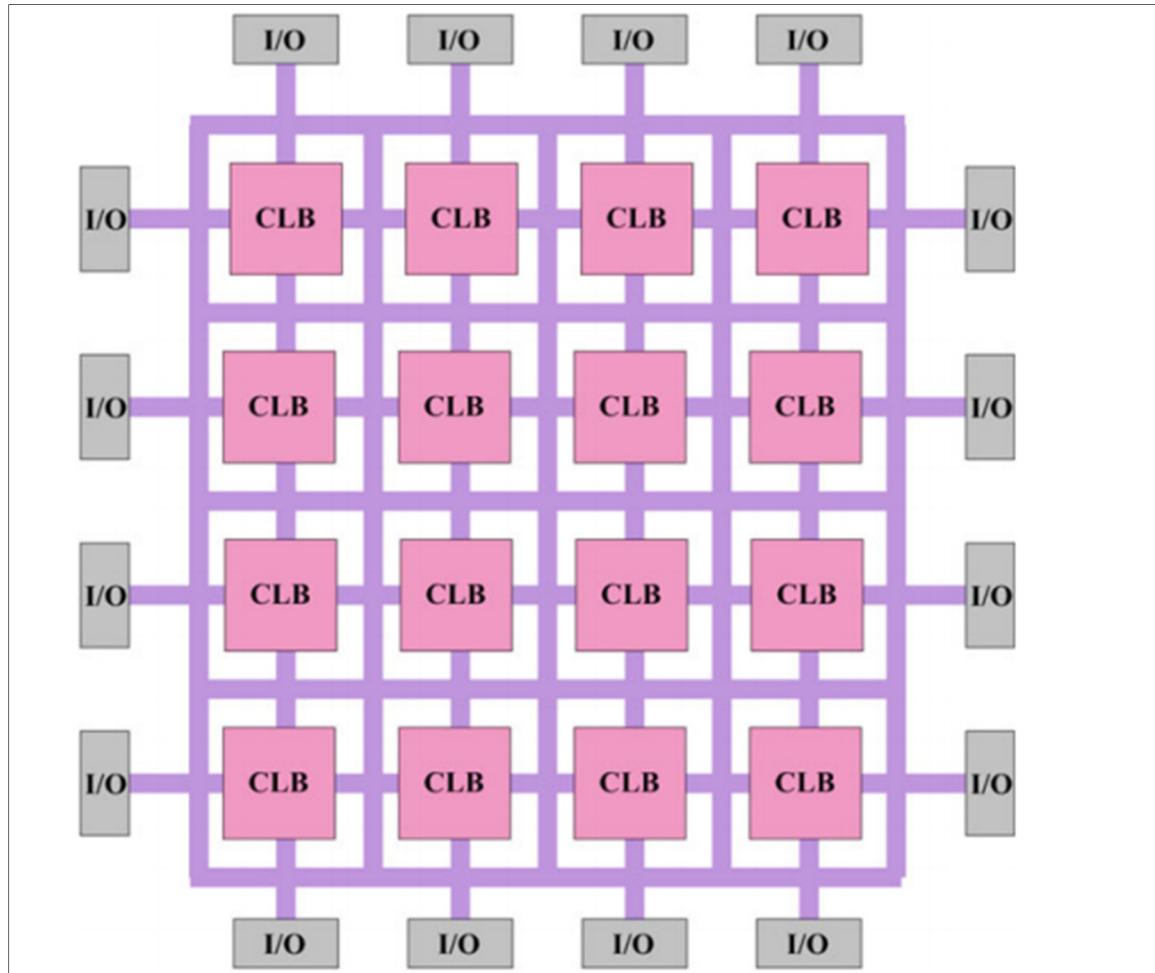

Les FPGA sont des circuits intégrés programmables et reconfigurables qui offrent des solutions rapides et non coûteuses comparés aux ASIC qui demandent beaucoup de ressources en termes de temps de conception et de coût. Les FPGA contiennent des blocs logiques programmables (CLB) qui implémentent les fonctions logiques; des ressources de routage programmables qui connectent les fonctions logiques entre elles et des blocs d'entrée/sortie (I/O) qui sont connectés aux blocs logiques via les ressources de routage et qui assurent la communication du FPGA avec les systèmes extérieurs.

La figure 1.6 présente un exemple général de l'architecture d'un FPGA.

Figure 1.6 Exemple d'architecture d'un FPGA

Tirée de Umer, Marrakchi et Mehrez (2012)

Il existe 3 principales technologies utilisées pour assurer la reconfiguration des FPGA : mémoire statique (SRAM), mémoire flash et anti-fusibles.

### 1.3.1     FPGA à base de mémoire SRAM (*Static Random Access Memory*)

Les mémoires statiques sont les cellules de base utilisées dans les FPGA à base de SRAM qui assurent principalement les fonctions suivantes :

- programmer les ressources de routage des FPGA qui sont généralement contrôlés par des multiplexeurs;

- programmer les blocs logiques (CLB) qui sont utilisés pour implémenter les fonctions logiques.

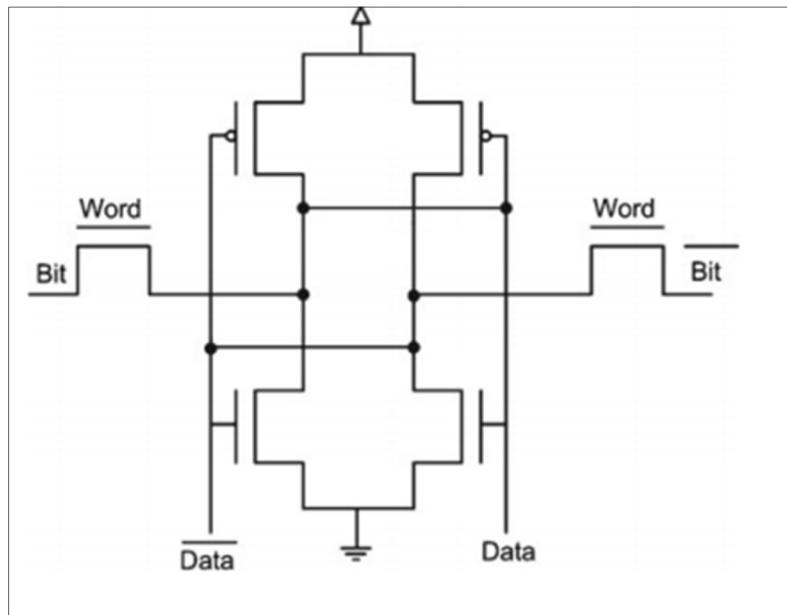

La figure 1.7 montre l'exemple d'une cellule SRAM.

Figure 1.7 Exemple d'une cellule SRAM

Tirée de Umer, Marrakchi et Mehrez (2012)

### 1.3.2 FPGA à base de mémoire Flash

La technologie basée sur les mémoires Flash est une bonne alternative à celle utilisant les mémoires SRAM. Cette technologie a l'avantage d'être non volatile et aussi moins gourmande en termes de consommation d'énergie. Les FPGA à base de Flash sont aussi reconfigurables par contre, ils ne peuvent pas l'être infiniment.

### 1.3.3 FPGA à base d'anti-fusibles

Cette technologie diffère des deux autres (SRAM et Flash) en ce qu'elle n'est ni volatile ni reprogrammable. Par contre, les FPGA à base d'anti-fusibles sont plus robustes face aux radiations que les FGPA à base de SRAM ou Flash.

Les FPGA à base de SRAM de Xilinx (Virtex-5 et Artix-7) sont les FPGA utilisés dans toutes les expériences réalisées dans le cadre de cette thèse. Le choix de ces FPGA se justifie par le fait qu'ils sont rapides et reconfigurables bien qu'ils soient sensibles aux événements singuliers. Aussi ils permettent d'avoir des coûts d'ingénierie non récurrents par rapport aux circuits VLSI non-programmables. Notons de plus que le Virtex-5 (CMOS 65 nm) a déjà été utilisé par d'autres membres de l'équipe du projet AVIO403, et que l'Artix-7 (CMOS 28 nm) était le FPGA le plus récent disponible au début des travaux liés à cette thèse.

Dans ce qui suit, une description détaillée du FPGA à base de SRAM et surtout du Virtex-5 est présentée.

### 1.3.4 Architecture détaillée des FPGA à base de SRAM de la famille Virtex-5

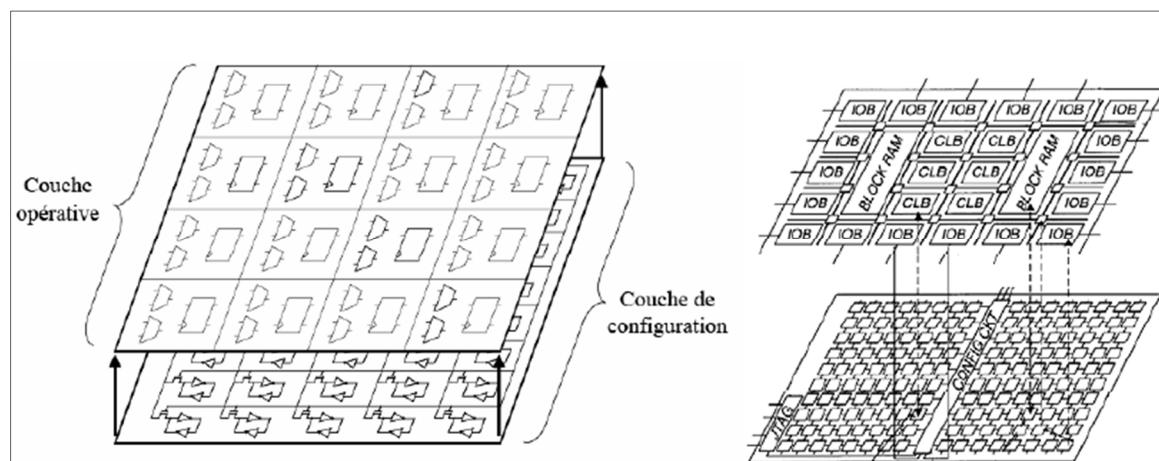

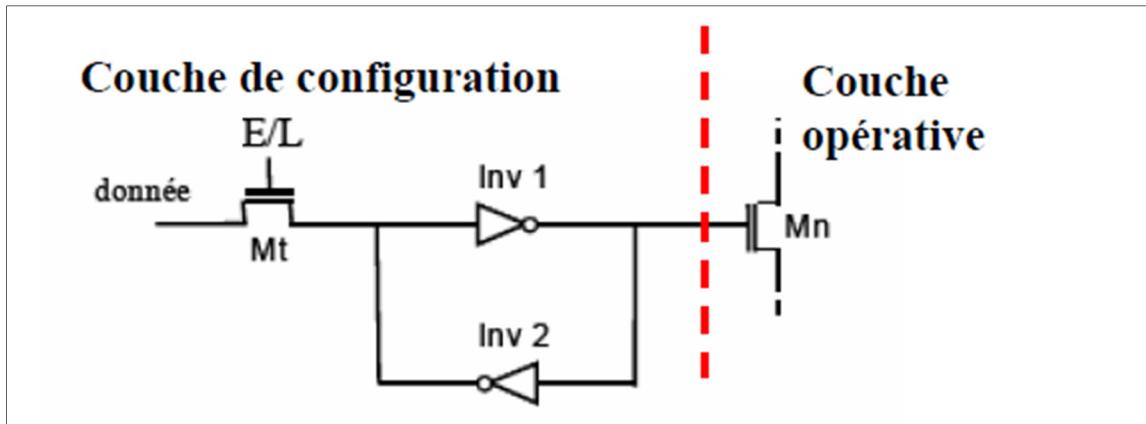

Ce type de FPGA peut être décomposé en deux couches : couche opérative et couche de configuration comme montré dans la figure 1.8 (Herrera-Alzu et Lopez-Vallejo, 2013).

La couche opérative ou couche applicative permet d'implémenter les fonctions logiques (combinatoires ou séquentielles) à l'intérieur des FPGA. Cette couche est constituée principalement des blocs logiques configurables (CLB) qui sont entourés par des blocs d'entrée/sortie (IOB).

Figure 1.8 Deux couches composant un FPGA à base de SRAM

Tirée de Bocquillon (2009)

La couche de configuration est constituée de cellules mémoires SRAM chargées d'activer ou non les ressources appartenant à la couche applicative (CLB, IOB, etc). Les cellules mémoire SRAM de la couche de configuration ont une architecture différente de celle d'une cellule SRAM ordinaire (figure 1.7). L'architecture de ce type de mémoire est présentée à la figure 1.9. Elle contient deux inverseurs rebouclés et un seul transistor NMOS qui assurent les différentes opérations de lecture ou d'écriture.

Figure 1.9 Architecture d'une cellule SRAM de configuration

Tirée de Souari (2016)

## CLB

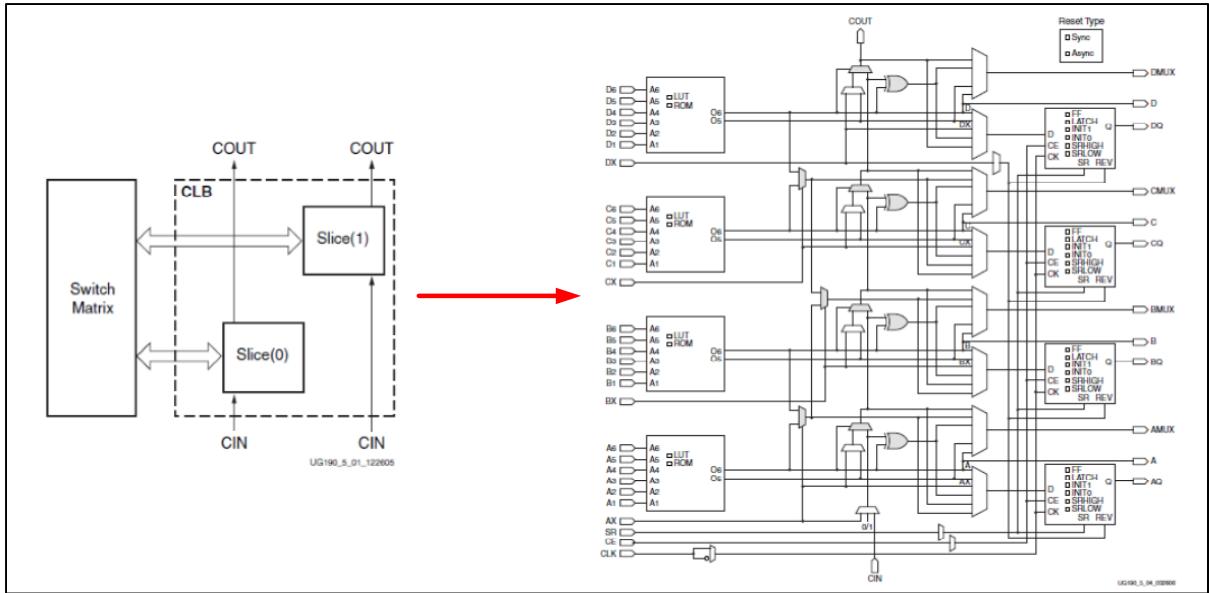

Les blocs logiques de configuration (CLB) constituent les composants fondamentaux d'un FPGA qui permettent aux utilisateurs d'implémenter n'importe quelle fonction logique (Borisov et Stoianova, 2009). Chaque CLB contient deux slices (SLICEM et SLICEL), qui à leur tour, sont composés de 4 LUT à 6 entrées, 4 bascules ainsi que des multiplexeurs et des portes logiques. Ces éléments servent à implémenter des fonctions logiques, arithmétiques et de mémoire.

La figure 1.10 montre l'architecture d'un CLB du FPGA Virtex-5.

Figure 1.10 Architecture d'un CLB du Virtex-5

Tirée de Borisov et Stoianova (2009)

## IOB

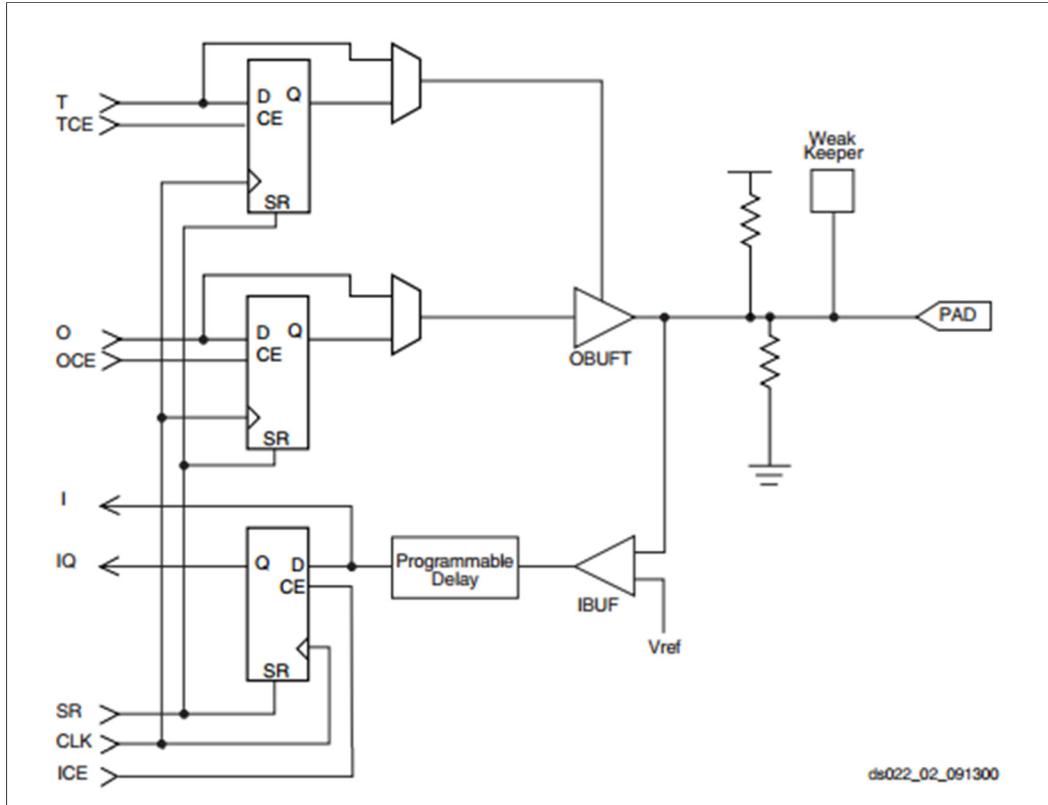

Les blocs d'entrée/sortie (IOB) sont des blocs qui permettent de connecter les broches du FPGA à la logique interne implémentée à l'intérieur du même circuit (UG190, 2012). Ils sont distribués sur tout le périphérique du FPGA où chaque IOB contrôle une broche du circuit. Chaque IOB peut être configuré comme entrée, sortie, signal bidirectionnel ou laissé tout simplement inutilisé (haute impédance). La figure 1.11 montre l'architecture d'un IOB du Virtex-5 qui contient des tampons d'entrée/sortie, des bascules, des résistances, un bloc de délai programmable et un contrôleur de temps de transition (*slew rate controller*).

Figure 1.11 Architecture d'un IOB du Virtex-5

Tirée de Xilinx. (2002)

### Configuration du FPGA Virtex-5

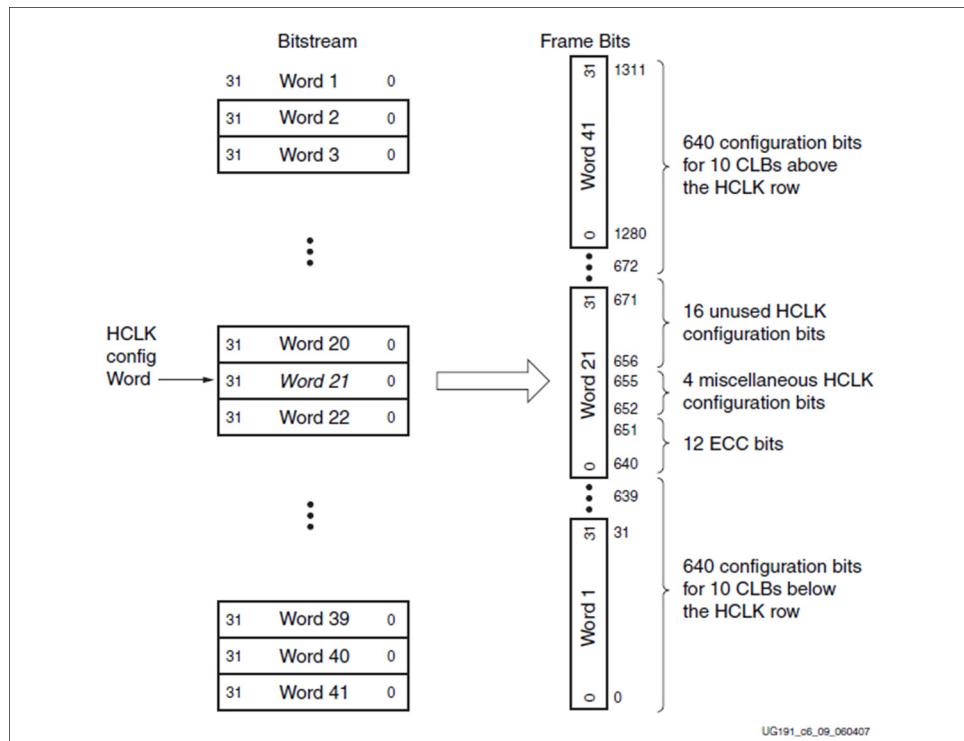

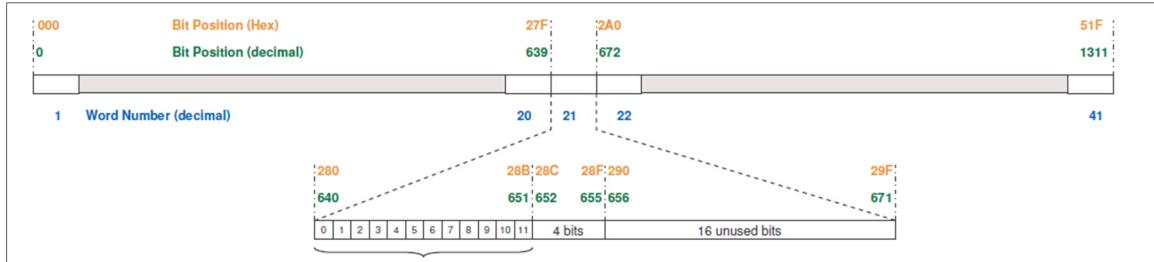

La configuration du Virtex-5 se fait au moyen d'un fichier qui contient les données de configuration, appelé *bitstream*, et qui est chargé dans la mémoire interne du FPGA (UG191, 2011). Cette mémoire de configuration est structurée en colonnes de mémoires appelés trames (*frames*) qui représentent les plus petits segments configurables. Chaque trame est composée de 1312 bits distribués sur 41 mots (32 bits pour chaque mot). L'organisation de la mémoire de configuration selon des trames permet d'effectuer la reconfiguration partielle qui consiste à reconfigurer une ou plusieurs trames.

La figure 1.12 montre la structure d'une trame en matière de mots et de bits.

La configuration du Virtex-5 peut se faire selon deux façons différentes : interne et externe. La configuration externe est réalisable à l'aide des interfaces *SelectMap* ou JTAG (UG191, 2011) et la configuration interne se fait à travers le port de configuration interne ICAP (*Internal Configuration Access Port*). ICAP permet de réaliser les opérations de lecture et écriture à l'intérieur de la mémoire de configuration.

Figure 1.12 Structure d'une trame du Virtex-5

Tirée de UG191 (2011)

#### 1.4 Techniques d'injection de pannes

Il existe une panoplie de techniques d'injection de pannes qui permettent de tester les circuits électroniques qui sont sujets aux événements singuliers.

Dans cette thèse, nous nous intéressons spécialement à l'injection matérielle et logicielle de pannes. Plus précisément, l'injection de pannes par reconfiguration est la technique d'injection utilisée dans le cadre de notre recherche.

Ce type d'injection peut être divisé en 3 approches :

- approche physique d'injection de pannes;

- injection de pannes par simulation;

- injection de pannes par émulation.

### **1) approche physique d'injection de pannes**

Il existe différentes approches associées à ce type d'injection.

- **injection des pannes à travers les broches d'entrées/sorties** : Cette approche consiste à injecter des pannes dans les entrées/sorties d'un circuit en utilisant des sondes. Il existe plusieurs outils qui permettent d'injecter des pannes au niveau des broches. Le premier outil qui a été développé pour cette fin est MESSALINE (Arlat, 1990). La panne est injectée directement sur l'une des bornes du circuit intégré où une sonde force un niveau logique bas ou haut dans la broche sélectionnée. Il a été développé au sein du laboratoire LAAS en France. Cet outil a subi plusieurs améliorations pour donner naissance à RIFLE (Madeira et al., 1994) et AFIT (Martinez et al., 1999);

- **injection de pannes par corruption de la mémoire** : cette approche permet d'injecter des pannes dans la mémoire d'un processeur. Ces pannes peuvent être permanentes ou transitoires. DEFI (Michel et al., 1994) est un exemple d'outil utilisé par ce type d'injection de pannes;

- **injection de pannes par perturbation de l'alimentation** : cette approche consiste à ajouter un transistor MOS entre l'alimentation et la masse Vcc (Karlsson et al., 1991). L'alimentation est perturbée par la modification de la tension de la grille de ce transistor.

### **2) injection de pannes par simulation**

Cette technique consiste à injecter des pannes dans les différents niveaux d'abstraction du flux de conception d'un circuit intégré. Quatre approches d'injection de pannes à base de simulation, selon le niveau d'abstraction, peuvent être distinguées :

- **simulation des pannes au niveau système**

Cette approche consiste à analyser la fiabilité des systèmes très tôt dans le flot de conception (Bolchini, Castro et Miele, 2009), (Lajolo et al., 2000), (Lu et Radetzki, 2011)). Plusieurs langages permettent d'effectuer ce genre de simulation, tels que SystemC et les langages fournis par Mathworks, qui est destinée principalement aux systèmes sur puces (*System-on-Chip*). Cette approche offre la rapidité de simulation par contre, elle manque de précision pour l'estimation de la sensibilité des systèmes concernés;

- **simulation des pannes au niveau RTL**

Plusieurs études se sont intéressées à ce type de simulation (Bombieri, Fummi et Guarnieri, 2011), (Chen, Mishra et Kalita, 2012). Cette approche est réalisée au niveau RTL selon deux techniques : la modification de la description du circuit et le forçage de ses nœuds internes en utilisant les commandes du simulateur. Nombreux sont les outils qui utilisent les commandes du simulateur. Nous pouvons citer MEPHISTO (*Multi level Error/Fault Injection Simulation Tool*) (Jenn et al., 1994), MEFISTO-L (Boue, Petillon et Crouzet, 1998) ou aussi d'autres outils basés sur les langages TCL (Tool Command Langage) et Perl. L'outil MEPHISTO effectue une simulation normale jusqu'à un cycle d'arrêt nommé cycle d'injection. L'arrêt de la simulation est commandé avec la commande *wait* du VHDL. MEFISTO-L est un outil développé par le laboratoire LAAS et qui permet de réaliser une simulation instrumentée. Cette simulation a pour but d'ajouter des saboteurs et des sondes afin de rajouter un délai sur les signaux cibles ou de modifier leurs valeurs;

- **simulation des pannes au niveau portes logiques**

Il existe plusieurs outils qui permettent d'injecter des pannes au niveau des portes logiques. L'outil FAST (Fault Simulator for Transients) (Cha et al., 1996) est un outil qui se base sur l'utilisation des modèles réalistes de pannes. Il est composé de deux simulateurs; le premier assure la simulation des pannes de délai au niveau portes et le deuxième permet d'observer l'effet des pannes sur les sorties du système. L'outil, VERIFY (*VHDL-based Evaluation of Reliability by Injecting Faults efficiently*) (Sieh, Tschache et Balbach, 1997) permet l'injection de pannes au niveau porte logique et au niveau RTL. Un autre outil appelé ROBAN (Alexandrescu, Anghel et Nicolaidis, 2004) permet l'injection et la simulation des pannes

transitoires dans les circuits combinatoires. Cet outil a pour but d'analyser la probabilité qu'une panne transitoire se propage jusqu'à la sortie d'un registre;

- **simulation des pannes au niveau transistor**

Cette approche permet d'injecter des pannes dans la description au niveau transistor d'un circuit (*Netlist*). Ce type de simulation présente un grand inconvénient au niveau du temps de simulation. De plus, il exige d'avoir accès à cette description, ce qui n'est pas le cas pour les circuits FPGA de Xilinx.

### 3) injection de pannes par émulation

L'injection de pannes par émulation basée sur le prototypage par FPGA a été proposée pour réduire le temps considérable consommé par l'injection par simulation (Haissam, Ayoubi et Velazco, 2004). Cette technique est devenue de plus en plus utilisée de nos jours en raison de sa rapidité, son faible coût et sa performance. Deux types d'injection peuvent découler de cette catégorie à savoir l'injection par reconfiguration et l'injection par instrumentation (KHATRI et al., 2014). Le premier groupe d'injection profite des fonctionnalités fournies par les FPGA à savoir la reconfiguration totale et partielle. Dans ce cas, les pannes sont injectées en changeant les bits dans le fichier de configuration (*bitstream*). Le deuxième groupe d'injection, qui est l'injection par instrumentation, est réalisée en ajoutant un circuit additionnel ou en modifiant le code original. L'injection de pannes par reconfiguration est détaillée davantage dans ce qui suit parce que c'est la technique utilisée dans le cadre de notre recherche.

#### Injection des pannes par reconfiguration

La configuration des FPGA à base de SRAM se fait à travers un fichier de configuration qui contient toutes les données et commandes de configuration. Une fois que le FPGA est configuré, il peut être reconfiguré par la suite selon deux modes : reconfiguration statique et reconfiguration dynamique.

La reconfiguration statique consiste, à chaque modification, à reconfigurer et ré-synthétiser les modules modifiés et par la suite régénérer le fichier de configuration et le charger sur le FPGA.

La reconfiguration dynamique, quant à elle, permet de reconfigurer un FPGA pendant son fonctionnement. Cette configuration peut être globale quand tout le circuit est reconfiguré ou bien partielle si seulement une partie de ce circuit est reconfigurée. En général, cette reconfiguration permet d'économiser le temps induit par la reconfiguration statique.

Il existe plusieurs travaux qui utilisent la reconfiguration dynamique comme moyen d'injection de pannes (Antoni, Leveugle et Feher, 2003), (Carlo et al., 2014), (Ghaffari et al., 2014). Cette reconfiguration est basée sur l'utilisation des plateformes qui sont composées d'un ou plusieurs FPGA. Dans la catégorie des plateformes à plusieurs FPGA, nous pouvons citer Flipper (Alderighi et al., 2009), Thesic+ (Faure, Velazco et Peronnard, 2005) ou aussi FT-UNSHADES (Guzmán-Miranda, Barrientos-Rojas et Aguirre, 2016).

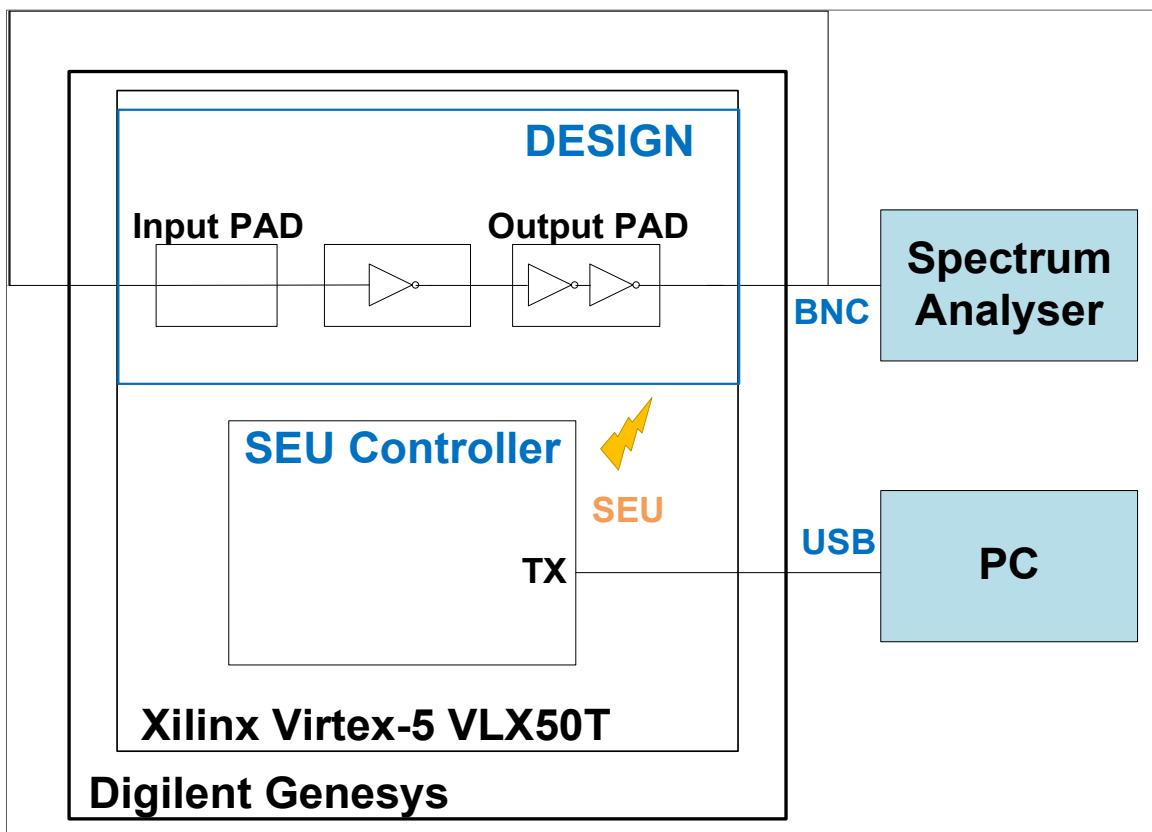

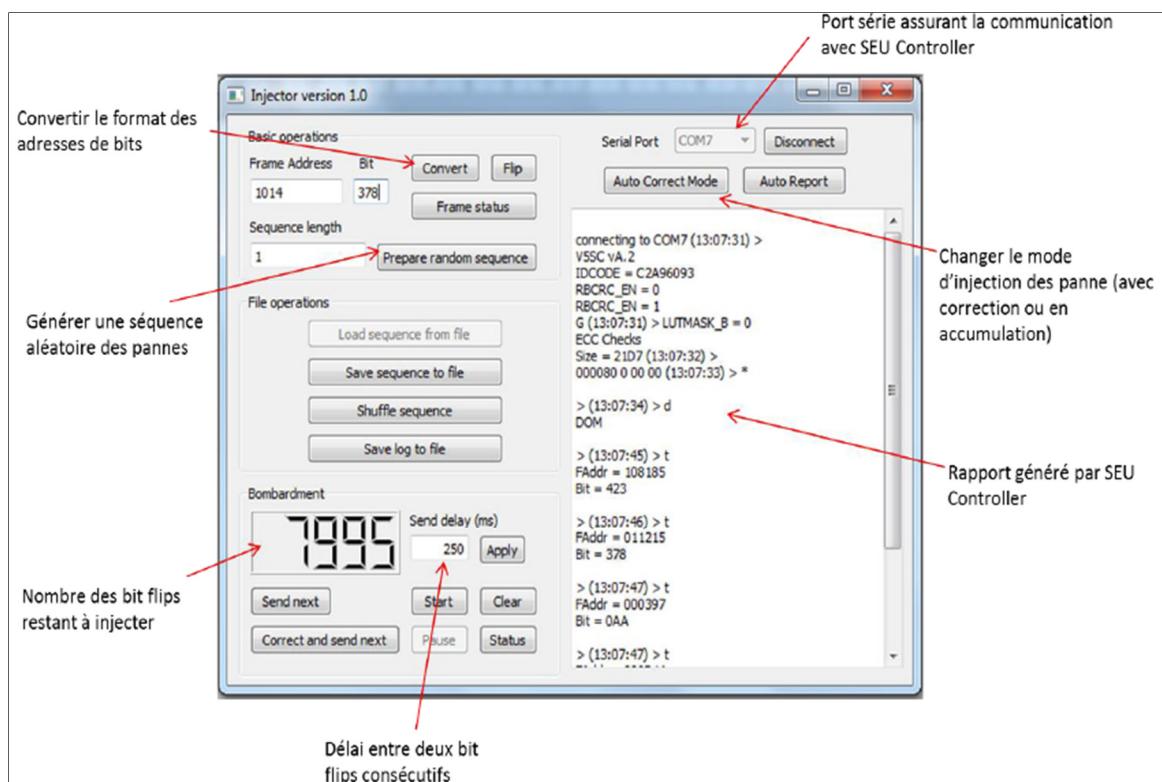

Plusieurs travaux ont utilisé la plateforme à un seul FPGA, à savoir (Bernardi et al., 2004), (Lee et Sedaghat, 2008), (Ebrahimi et al., 2014) et (Chapman, 2010a). Dans le cadre de cette thèse, nous sommes intéressés à l'outil d'injection de pannes, appelé **SEU Controller**, qui est présenté dans (Chapman, 2010a).

### **SEU Controller**

Le SEU Controller est un utilitaire développé par Xilinx, pouvant être instancié avec n'importe quel design implémenté à l'intérieur d'un FPGA de la famille Virtex-5 ou des familles plus récentes. Le rôle principal de cet utilitaire est de corriger les erreurs de configuration causées par les SEU aussitôt qu'elles sont détectées. Le deuxième rôle est de fournir un moyen pour émuler les SEU à l'intérieur de la mémoire de configuration des Virtex-5.

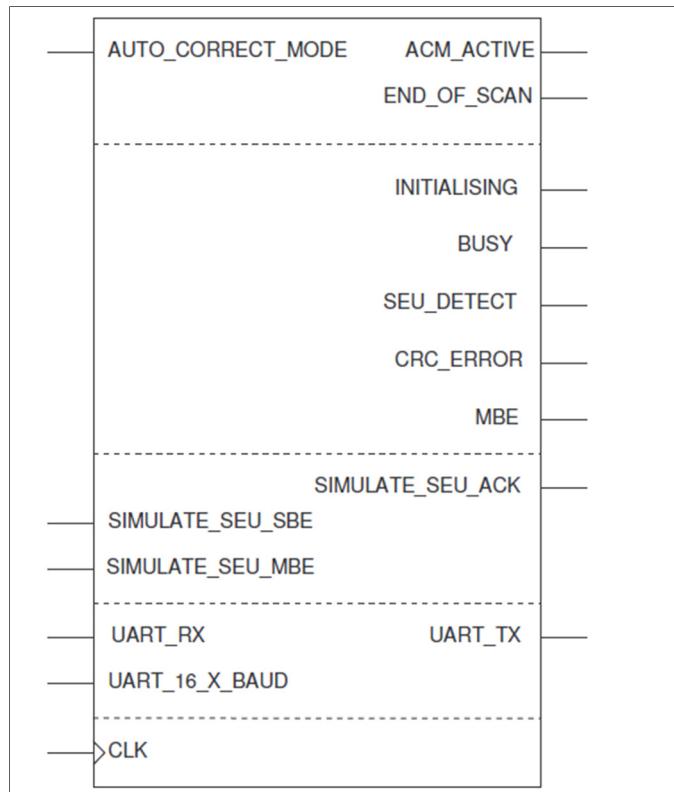

Le SEU Controller est capable de fournir des rapports détaillés des SEU injectés, du nombre de trames (*frames*) balayées et du nombre d'erreurs de configuration corrigées. Les ports d'entrées/sorties du SEU Controller sont présentés à la figure 1.13.

Figure 1.13 Entrées/sorties du SEU Controller

Tirée de Chapman (2010a)

Les entrées/sorties du SEU Controller sont décrites comme suit (Chapman, 2010a) :

- ***AUTO\_CORRECT\_MODE*** : donne le mode de fonctionnement du SEU Controller. Deux modes sont supportés : mode singulier où un bit est corrigé avant d'inverser un autre et le mode d'accumulation où les inversions sont faites sans correction;

- ***ACM\_ACTIVE*** : indique que le *SEU Controller* est en mode *Automatic Correction Mode* (ACM);

- ***END\_OF\_SCAN*** : indique que l'opération de *Readback CRC* est en train de balayer le composant;

- ***INITIALISING*** : indique que le *SEU Controller* est dans la phase d'initialisation. Ce signal est actif après la configuration du composant;

- ***BUSY***: indique que l'outil est occupé avec la correction ou l'injection d'erreurs;

- **SEU\_DETECT** : signifie qu'une erreur de configuration a été détectée ou non par le circuit *Readback CRC*;

- **CRC\_ERROR** : indique qu'une erreur de configuration a été détectée par le circuit *Readback CRC*;

- **MBE** : indique qu'une erreur multiple (*Multiple Bit Error*) est détectée dans la mémoire de configuration et qu'elle ne peut pas être corrigée;

- **SIMULATE\_SEU\_SBE & SIMULATE\_SEU\_MBE** : indiquent que l'utilitaire est entrain de simuler une erreur simple (*Single Bit*) ou multiple (*Multiple Bit Error*), respectivement;

- **SIMULATE\_SEU\_ACK** : indique le début de l'opération d'injection d'erreur;

- **UART\_TX** : permet de rapporter des informations sur l'état du SEU Controller;

- **UART\_RX** : permet de contrôler le *SEU Controller* en lui envoyant les commandes à exécuter;

- **CLK** : signal d'horloge.

Le SEU Controller est composé de deux primitives fournies par Xilinx : ICAP\_VIRTEX5 et FRAME\_ECC\_VIRTEX5 (Chapman, 2010b). La première primitive, ICAP\_VIRTEX5, permet d'accéder à la mémoire de configuration du FPGA et d'inverser certains bits de configuration. La deuxième primitive, FRAME\_ECC\_VIRTEX5, permet la détection et l'identification d'erreurs simples et doubles.

Il est important de noter que, dans certains cas, les inversions de bits de configuration ne causent pas d'erreurs. En effet, chaque trame à l'intérieur du FPGA contient 1312 bit dont 16 bits inutilisés comme montré à la figure 1.14. Donc, si les inversions affectent ces bits inutilisés, aucune erreur ne sera détectée. De plus, le SEU Controller n'accède pas aux bits de configuration contrôlant les tables de conversions (LUT) utilisées comme mémoire distribuée dans un design ni à ceux des mémoires BRAM. Aussi, le SEU Controller utilise moins de 1%

des ressources du FPGA, ce qui correspond à 350 LUT, 330 registres et une seule BRAM pour un Virtex-5.

Figure 1.14 Structure d'une trame du Virtex-5 montrant les bits utilisés et ceux inutilisés

Tirée de Chapman (2010c)

Le SEU Controller est aussi sensible aux SEU qui peuvent lui causer deux types d'erreurs : des erreurs qui affectent ses bits de configuration et d'autres qui touchent sa mémoire de données. Il est capable de corriger les erreurs les moins critiques parce qu'il est capable de s'autoréparer. Par contre, les erreurs qui affectent ses deux primitives (ICAP et FRAME\_ECC) peuvent engendrer l'écriture des trames incorrectes dans la mémoire de configuration.

La communication avec le SEU Controller peut se faire de deux façons différentes :

- communication à travers les broches : en utilisant les ressources disponibles (boutons, interrupteurs ...) sur la carte sur laquelle le FPGA est embarqué;

- communication à travers l'UART : en envoyant des commandes via la connexion série RS232 à partir d'un ordinateur.

Dans le cadre de cette thèse, la communication avec le SEU Controller est réalisée à travers l'UART en utilisant une session *Hyperterminal*. Mais, afin de faciliter et automatiser la communication avec le *SEU Controller* et par la suite faciliter la procédure d'injection des pannes, une interface nommée *Injector* a été développée par Simon Pichette (voir Annexe I).

## 1.5 Techniques de mitigation

Dans cette section, un aperçu sur les techniques de mitigation les plus utilisées dans les FPGA à base de SRAM est présenté.

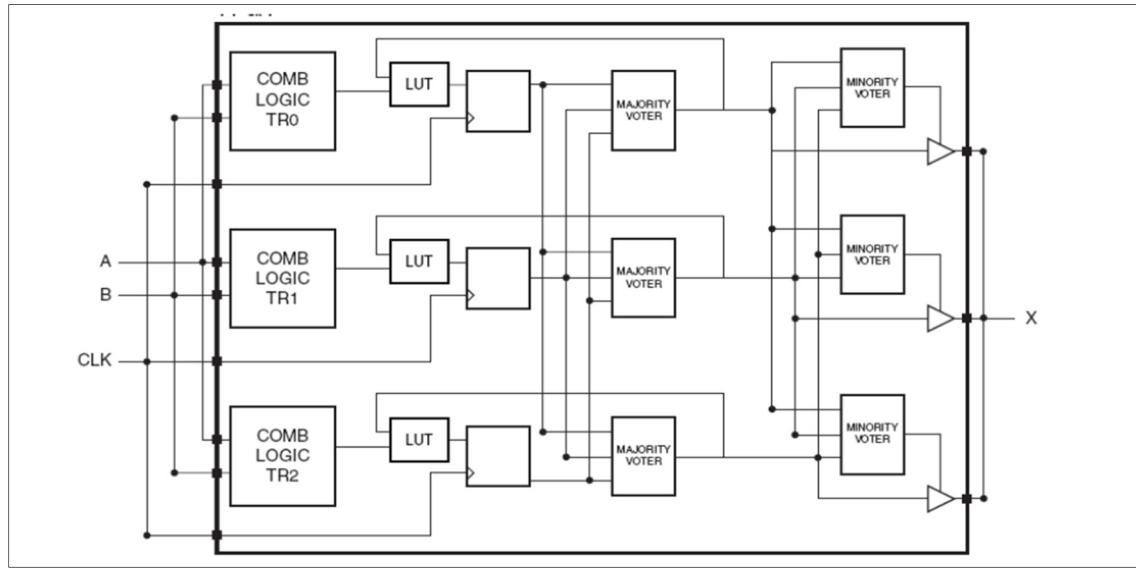

### 1.5.1 Triplication Modulaire (Triple Modular Redundancy TMR)

La triplication modulaire ou TMR est une technique de mitigation implémentée via la synthèse et qui a pour but de réduire la sensibilité des FPGA face aux SEU.

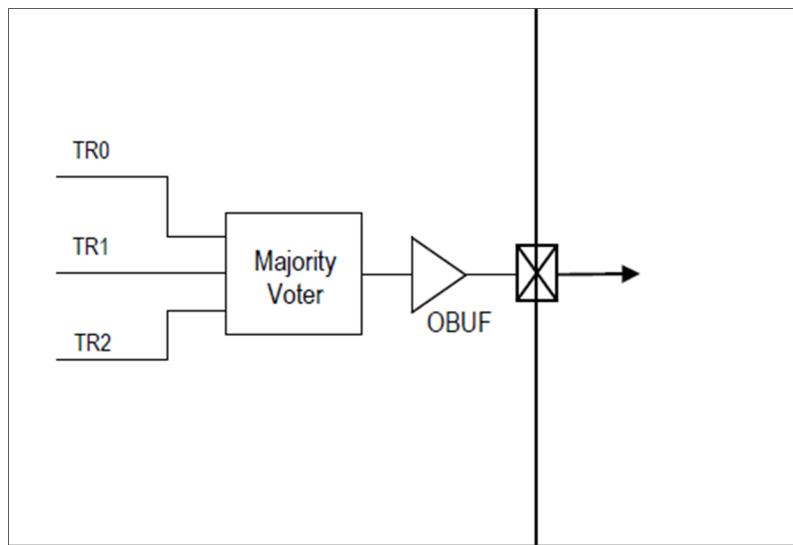

La figure 1.15 présente l'architecture de la TMR développée par Xilinx. Cette architecture est caractérisée par l'utilisation de trois différents voteurs ainsi que la triplication de tous les blocs fonctionnels. Il est nécessaire d'avoir un chemin de retour (*Feedback path*), comme montré à la figure 1.15, pour corriger le contenu des flip-flops vu que la configuration « *scrubbing* » ne peut pas corriger le contenu des blocs logiques configurables (CLB). Le choix de l'implémentation de ce chemin de retour revient à l'utilisateur qui peut décider de l'implémenter pour toutes les flip-flops ou seulement pour quelques unes utilisées par l'application à implémenter. De plus, cette technique nécessite 3 domaines d'horloge séparés.

Figure 1.15 Architecture de la technique TMR proposée par Xilinx

Tirée de Adell et al. (2008)

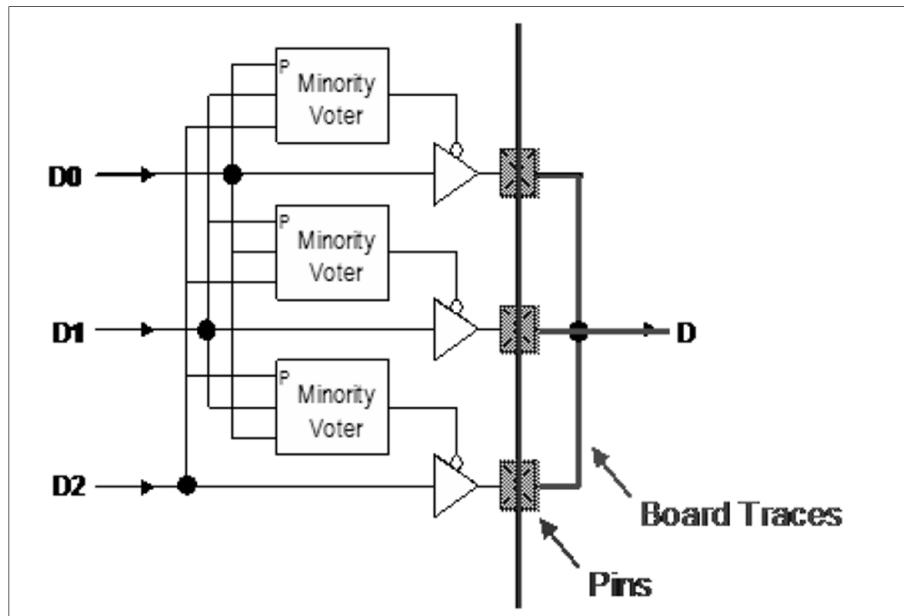

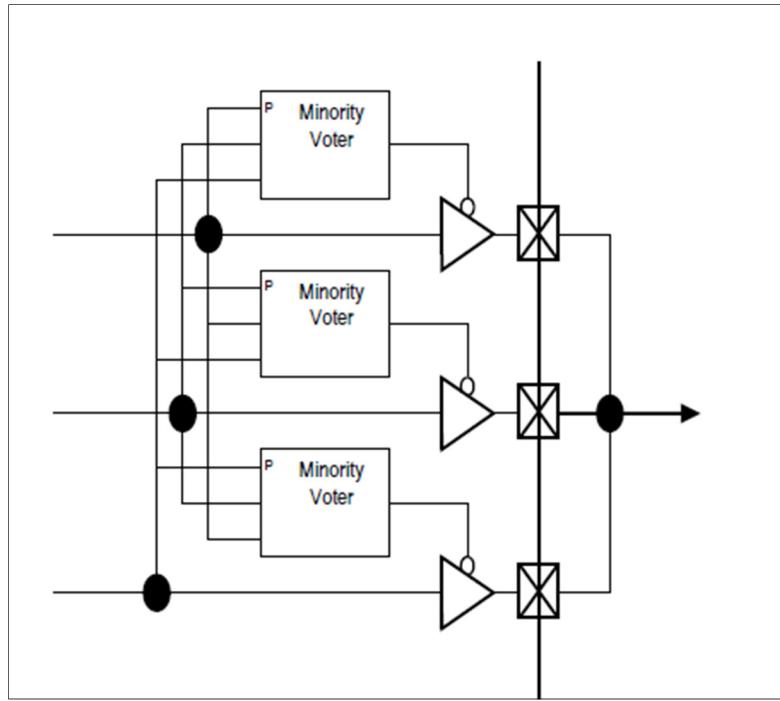

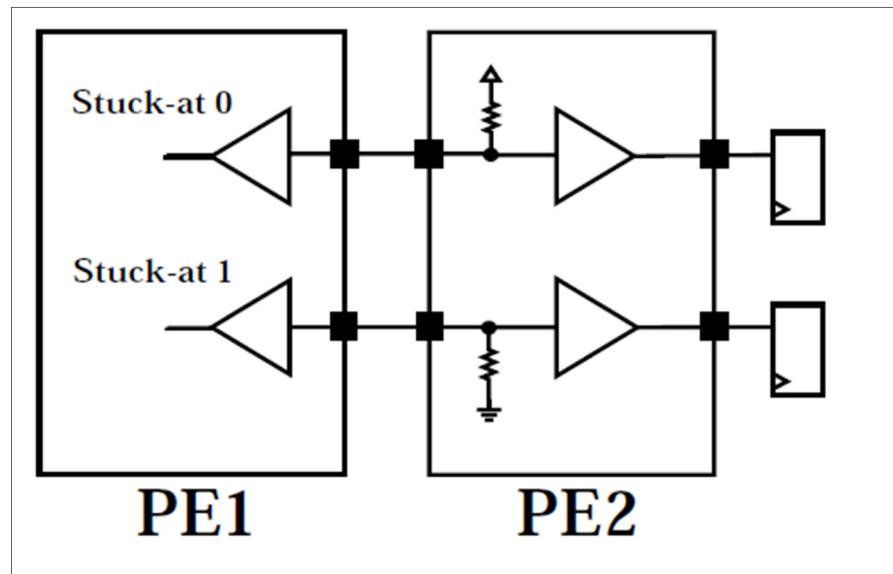

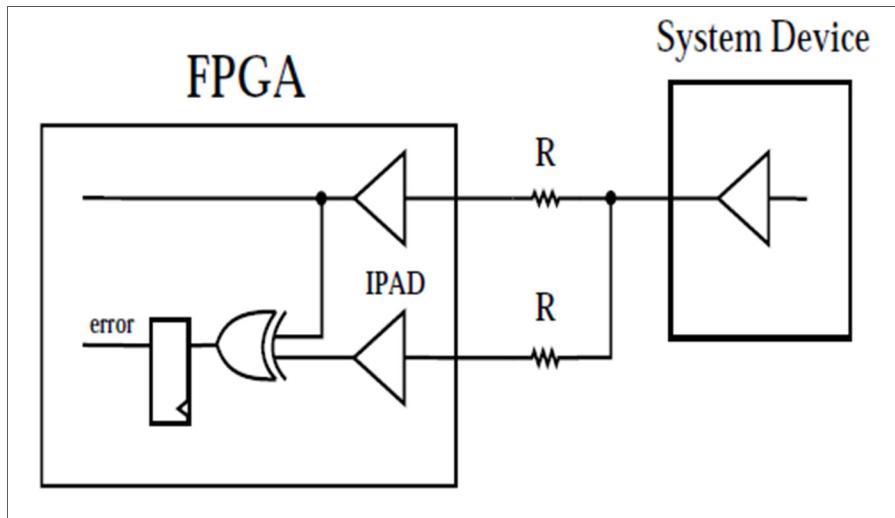

En plus des CLB, les entrées et sorties peuvent aussi être triplées. L'approche utilisée pour les sorties est présentée à la figure 1.16. Les sorties sont liées entre elles à l'aide des voteurs minoritaires (*minority voting*).

Figure 1.16 Approche utilisée pour tripler les sorties

Tirée de Adell et al. (2008)

### 1.5.2 Reconfiguration “Scrubbing”

L'utilisation de la redondance matérielle toute seule n'est pas suffisante pour éviter les erreurs dans les FPGA; il est obligatoire de recharger périodiquement le fichier de configuration (*bitstream*) pour éviter l'accumulation de pannes. Ce rechargement continu est appelé « *scrubbing* ». Le *scrubbing*, comme expliqué par Xilinx (Adell et al., 2008), permet à un système de réparer les inversions de bits (bit-flips) à l'intérieur de la mémoire de configuration sans perturber le fonctionnement du système. La mémoire de configuration contient les cellules mémoires qui configurent les LUT, le routage et les CLB. Le *scrubbing* permet de prévenir l'accumulation de plusieurs erreurs de configuration et aussi de réduire le temps de fonctionnement permis pour une configuration invalide.

Les systèmes qui implémentent les techniques de mitigation basées sur la redondance, comme les TMR, doivent utiliser aussi le *scrubbing* pour éviter l'accumulation de pannes et par ailleurs l'échec de la redondance.

Xilinx (Adell et al., 2008) recommande une fréquence de *scrubbing* 10 fois plus grande que le taux d'occurrence des SEU. Le « *scrubber* » peut être externe ou même interne au FPGA.

## 1.6 Conclusion

Ce chapitre a été consacré à l'étude détaillée des radiations cosmiques et leurs effets sur les circuits intégrés en général et sur les FPGA en particulier. En premier lieu, des informations pertinentes concernant les différentes sources de radiation, les différents types d'erreurs causées par ces radiations ainsi que la sensibilité des circuits numériques face à ces erreurs ont été présentées. En second lieu, un aperçu sur les FPGA à base de SRAM, leur architecture ainsi que leur sensibilité face aux radiations a été détaillée. De plus, les différentes techniques d'injection de pannes ont été explorées. Finalement, les techniques de mitigation les plus utilisées pour les FPGA de Xilinx ont été présentées.

## CHAPITRE 2

### REVUE DE LITTÉRATURE

Ce chapitre présente une revue de littérature qui étudie les travaux en lien avec notre recherche. En effet, il explore en détails les outils et techniques s'intéressant aux effets des événements singuliers sur toutes les ressources des FPGA à base de SRAM (logique, routage et IOB). De plus, la littérature a été prospectée afin de trouver les travaux s'intéressant spécifiquement à l'étude des effets des événements singuliers sur les IOB des FPGA à base de SRAM.

#### 2.1 **Effets des événements singuliers sur toutes les ressources des FPGA à base de SRAM (routage, logique et IOB)**

Cette thèse s'intéresse aux événements singuliers qui ont des effets non destructifs. Plus particulièrement les SEU (*Single Event Upset*) et les MBU (*Multiple Bit Upset*). Les SEU et les MBU constituent le genre de pannes qui arrivent le plus souvent dans les FPGA à base de SRAM (Foucard, 2010), le type de circuits cibles de notre recherche.

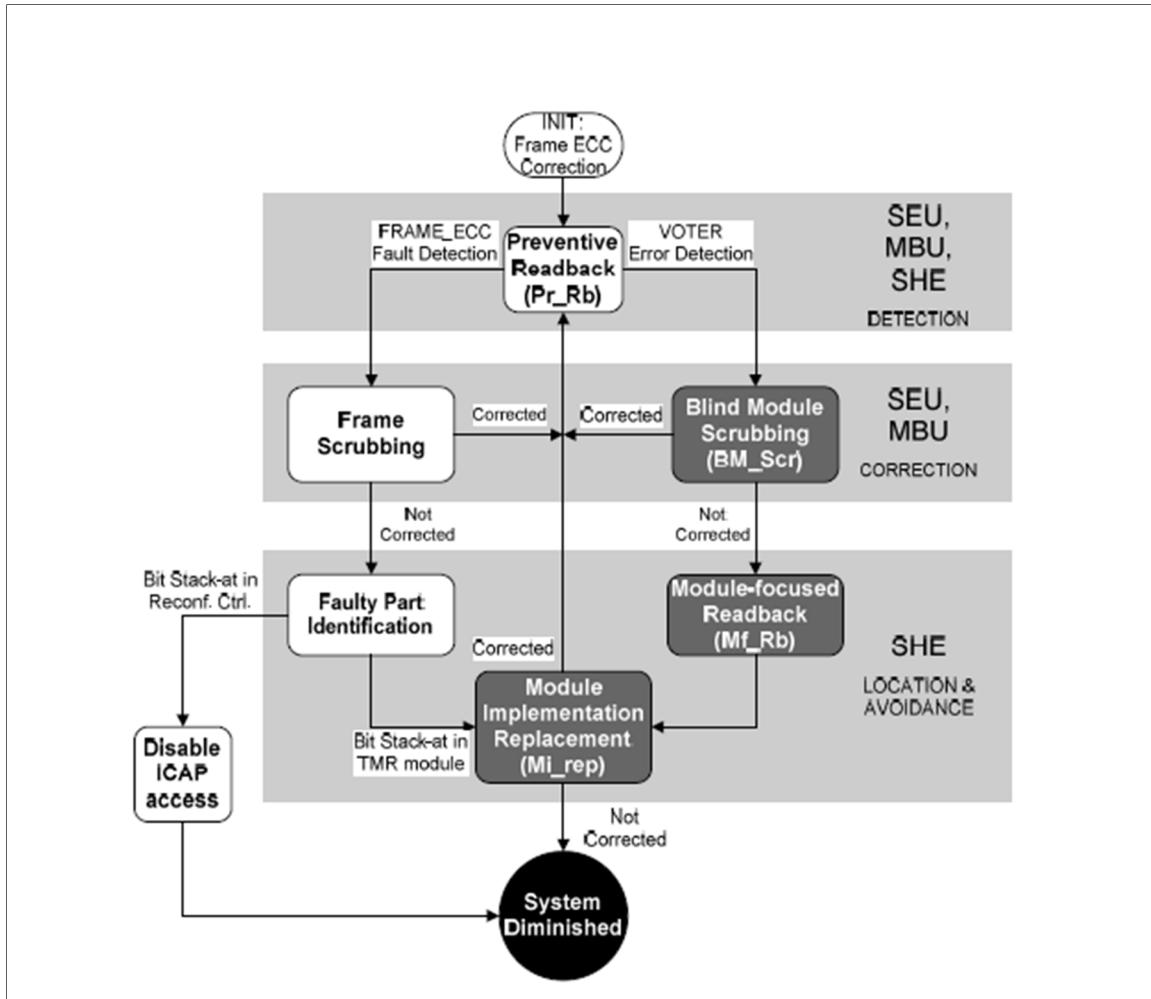

Dans (Iturbe et al., 2009), les auteurs présentent une nouvelle stratégie de gestion de pannes qui augmente l'efficacité des techniques de mitigation à redondance triple (TMR) pour qu'elles soient capables de diminuer, à la fois, l'occurrence des SEU, MBU et SHE (*Single Hardware Error*) à l'intérieur des FPGA de type Virtex-4 de Xilinx. Cette stratégie combine deux techniques, à savoir la relecture des trames du FPGA (*Frame Read back*) basée sur les codes de correction d'erreur (ECC) et la reconfiguration continue (*Scrubbing*) du FPGA. La reconfiguration continue est effectuée avec l'outil SEU Controller et c'est un point en commun entre cette recherche et nos travaux. La figure 2.1 présente l'organigramme de cette stratégie.

Figure 2.1 Organigramme de la stratégie de validation appliquée pour les Virtex-4

Tirée de Iturbe et al. (2009)

Cet organigramme montre que cette stratégie est capable de détecter les trois types de pannes. Par contre, elle ne peut corriger que les SEU et les MBU. Pour les SHE, elle peut seulement déterminer leurs positions et essayer de les éviter pour les prochaines implémentations.

Ce travail nous a aidés dans la compréhension du fonctionnement du SEU Controller. Par contre, il s'intéresse à toutes les ressources du FPGA, mais il ne détaille pas les pannes dans les IOB. De plus, le but principal de ce travail est de présenter une nouvelle stratégie de mitigation pour les Virtex-4 et non d'étudier en profondeur la nature des pannes observées dans les IOB. Pour ces raisons, ce travail diffère du nôtre.

Dans (Quinn et al., 2005), les auteurs proposent une méthodologie pour estimer la section efficace statique des protons et des ions engendrant des MBU dans les FPGA à base de SRAM de Xilinx. Ils présentent aussi une méthodologie pour déterminer les effets des MBU sur les TMR. Cette méthodologie s'est intéressée principalement à l'étude de 4 différentes familles de FPGA de Xilinx, à savoir Virtex, Virtex-2, Virtex-2 Pro et Virtex-4. Elle a montré l'existence des MBU dans ces 4 familles de FPGA et aussi dans la majorité des ressources composant chaque FPGA, à savoir les blocs configurables logiques (CLB), les mémoires (BRAM), les mémoires d'interconnexion (BRAMi) et les blocs d'entrée/sortie (IOB). Le tableau 2.1 montre la fréquence des MBU pour chaque type de ressource et pour chaque FPGA et cela pour des erreurs causées par un faisceau de radiation à base de protons à une énergie égale à 63.3 MeV.

Tableau 2.1 Fréquence des MBU induits par une radiation à base de protons (63.3 MeV)

Tiré de Quinn et al. (2005)

| <b>Family</b> | <b>BRAM Events</b> | <b>BRAMi Events</b> | <b>IOB Events</b> | <b>CLB Events</b> |

|---------------|--------------------|---------------------|-------------------|-------------------|

| Virtex        | 0                  | in CLB              | 8                 | 286               |

| Virtex-2      | 162                | 1230                | 252               | 2404              |

| Virtex-2 Pro  | 4                  | 15                  | 4                 | 115               |

| Virtex-4      | 640                | Unknown             | 673               | 3246              |

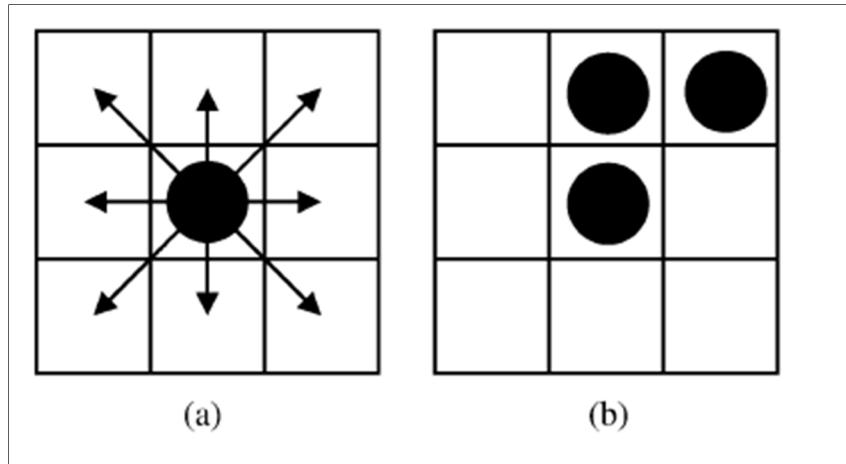

Ces MBU se divisent en deux types selon leurs emplacements dans une cellule mémoire et selon le nombre de particules qui les ont causées : 1) les MBU réels (*true MBU*) qui sont causés par la même particule et 2) les faux MBU (*false MBU*) qui sont causés par plusieurs particules. Ainsi, ces MBU peuvent être engendrés par plusieurs inversions (2 bit-flips, 3 bit-flips, etc.). La figure 2.2 illustre l'effet des MBU sur des cellules adjacentes.

Cet article a inspiré notre recherche vu qu'il a montré l'existence des MBU dans les IOB mais il n'a pas investigué davantage le comportement des IOB face à ces erreurs.

Figure 2.2 (a) Illustration de l'effet d'une particule causant un MBU dans les cellules mémoires adjacentes d'un même mot logique, (b) illustration d'un MBU à trois bits flippés causé par 3 particules

Tirée de Quinn et al. (2005)