Nouvelle technique de test de type délai plus robuste à la

variation d'impédance du réseau de distribution

d'alimentation

Par

Ali LOUATI

MÉMOIRE PRÉSENTÉ À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE À L'OBTENTION DE LA MAÎTRISE

AVEC MÉMOIRE EN GÉNIE ÉLECTRIQUE

M. Sc. A.

MONTRÉAL, LE 8 AOÛT 2017

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE :

M. Claude Thibeault, directeur de mémoire

Département de génie électrique à l'École de technologie supérieure

M. Ghyslain Gagnon, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Ricardo Izquierdo, membre du jury

Département de génie électrique à l'École de technologie supérieure

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 3 AOÛT 2017

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

En guise de reconnaissance, je tiens à témoigner mes sincères remerciements à toutes les personnes qui ont contribué de près ou de loin au bon déroulement de ce mémoire.

Je tiens à remercier mon directeur de mémoire, le professeur Claude Thibeault pour son aide, pour ses conseils pertinents, pour sa vaste expérience et pour le soutien et la confiance qu'il m'a accordée tout au long de ce mémoire.

Je tiens à remercier également les membres du jury pour leur collaboration et leur participation à la soutenance.

Dans l'impossibilité de citer tous les noms, je remercie mes collègues du laboratoire LACIME et toutes les personnes qui ont permis par leurs conseils et leurs compétences la réalisation de ce mémoire. Je tiens à remercier Ana Maria Medina pour son soutien inconditionnel et quotidien et pour ses encouragements.

Finalement, ma plus profonde gratitude envers ma famille et mes amis qui ont toujours cru en moi, soutenu mes choix et conseillé tout au long de mes études : mon père Mohamed, ma mère Sihem, mon frère Iheb et mes sœurs Ichrak et Donia. Je vous aime énormément.

# **NOUVELLE TECHNIQUE DE TEST DE TYPE DÉLAI PLUS ROBUSTE À LA VARATION D'IMPÉDANCE DU RÉSEAU DE DISTRIBUTION D'ALIMENTATION**

Ali LOUATI

## **RÉSUMÉ**

De nos jours, le test de balayage à vitesse nominale (SBAST, Scan Based at-Speed Testing) est l'approche de test de type délai la plus dominante. Ce type de test vient avec certains inconvénients, comme le bruit de tension d'alimentation (PSN, *Power Supply Noise*) produit pendant le mode test, qui diffère de celui induit pendant le mode fonctionnel. Quelques techniques de test de type SBAST ont été développées pour réduire cette chute de tension. Mais un aspect particulier a été négligé dans la littérature, à savoir l'impact de la variation d'impédance du réseau de distribution d'alimentation (PDN, *Power Delivery Network*) sur les tests de type délai.

Ce projet de maîtrise présente une nouvelle technique de test SBAST, nommée (OCAS, *One Clock Alternated Shift*) pour minimiser l'impact potentiel de la variation d'impédance du réseau de distribution d'alimentation. La stratégie derrière cette nouvelle technique est d'imiter autant que possible le signal d'horloge du mode fonctionnel. Le but de cette imitation est d'obtenir des conditions de distribution d'alimentation similaires à celle du mode fonctionnel pour protéger le circuit en mode test contre les variations de Vdd dues aux variations d'impédance. Comme cas d'étude, nous considérons la variation d'impédance du PDN qui peut se produire avec les circuits intégrés 3D avec la variation du nombre de puces du circuit sous test (CUT, *Circuit Under Test*).

Les résultats des simulations HSPICE montrent que la technique OCAS est moins sensible à une telle variation d'impédance et qu'elle surpasse les principales techniques existantes de SBAST. De plus, les résultats de la couverture des pannes de transition de la technique OCAS obtenue avec les outils (ATPG, *Automatic Test Pattern Generation*) sont fort acceptables. Cependant, le nombre de vecteurs de test nécessaires pour y parvenir sont plus élevés, en raison des limitations de ces outils.

**Mots clés :** Test de balayage à vitesse nominale, Impédance, circuit intégré 3D, mode fonctionnel, mode structurel, délai, ATPG.

# **NOUVELLE TECHNIQUE DE TEST DE TYPE DÉLAI PLUS ROBUSTE À LA VARATION D'IMPÉDANCE DU RÉSEAU DE DISTRIBUTION D'ALIMENTATION**

Ali LOUATI

## **ABSTRACT**

Nowadays, Scan Based at-Speed Testing (SBAST) is the most dominant delay testing approach. This type of test comes with some drawbacks, such as power supply noise (PSN) produced during the test mode, which differs from that induced during the functional mode. Some SBAST techniques have been proposed to reduce PSN. However, one particular aspect has been overlooked in the literature, namely the impact of Power Distribution Network (PDN) impedance variation on delay testing.

This thesis presents a new SBAST test technique, called One Clock Alternated Shift (OCAS), to minimize the potential impact of the PDN impedance variation. The strategy behind this new technique is to mimic as much as possible the clock signal of the functional mode. The purpose behind this strategy is to obtain power distribution conditions similar to those of the functional mode in order to protect the circuit under test mode against power variations due to impedance variation. As a case study, we consider the PDN impedance variation that can occur with 3D integrated circuits, more specifically when a top die under test is bounded over a stack of different sizes.

HSPICE simulation results show that the OCAS is less sensitive to such impedance variation and outperformed from an overall perspective the main existing SBAST techniques. Moreover, results obtained with ATPG tools (Automatic Test Pattern Generation) show that OCAS fault coverage is very acceptable for all simulated cases. However, it comes at the expense of additional test patterns, due to the ATPG tool limitations.

**Keywords:** Scan Based at-Speed Testing, Impedance, 3D Integrated Circuit, functional mode, structural mode, ATPG.

## TABLE DES MATIÈRES

|                                                                                                                      | Page      |

|----------------------------------------------------------------------------------------------------------------------|-----------|

| INTRODUCTION .....                                                                                                   | 1         |

| <b>CHAPITRE 1 NOTIONS DE BASE ET REVUE DE LITTÉRATURE .....</b>                                                      | <b>5</b>  |

| 1.1 Introduction.....                                                                                                | 5         |

| 1.2 Notions de base sur le test des circuits intégrés.....                                                           | 5         |

| 1.2.1 Test fonctionnel .....                                                                                         | 6         |

| 1.2.2 Test structurel.....                                                                                           | 6         |

| 1.2.3 Modèles de pannes.....                                                                                         | 7         |

| 1.2.4 Génération automatique de vecteurs de test (ATPG) .....                                                        | 8         |

| 1.2.5 Conception en vue de test .....                                                                                | 9         |

| 1.2.6 Test de transition avec insertion de registres de balayages.....                                               | 11        |

| 1.2.7 Launch on Shift.....                                                                                           | 12        |

| 1.2.8 Launch on Capture.....                                                                                         | 12        |

| 1.3 Circuits intégrés 3D .....                                                                                       | 13        |

| 1.4 Revue de littérature .....                                                                                       | 15        |

| 1.4.1 Sequential Broad Side (SeBoS) .....                                                                            | 16        |

| 1.4.2 BurstMode.....                                                                                                 | 18        |

| 1.4.3 Pseudo-functional K Longest Path per Gate (PKLPG).....                                                         | 20        |

| 1.5 Conclusion .....                                                                                                 | 22        |

| <b>CHAPITRE 2 MODÈLES DE SIMULATION ET EXPÉRIMENTATIONS PRÉLIMINAIRES .....</b>                                      | <b>23</b> |

| 2.1 Introduction.....                                                                                                | 23        |

| 2.2 Modèle du réseau de distribution d'alimentation (PDN).....                                                       | 23        |

| 2.2.1 Réseau de distribution d'alimentation utilisé.....                                                             | 24        |

| 2.2.2 Modèle équivalent du PDN complet.....                                                                          | 25        |

| 2.3 Description des simulations HSPICE .....                                                                         | 27        |

| 2.3.1 Circuit de mesure de délai.....                                                                                | 27        |

| 2.3.2 Principe de fonctionnement du circuit de mesure de délai .....                                                 | 28        |

| 2.4 Simulations préliminaires .....                                                                                  | 29        |

| 2.4.1 Cas d'étude.....                                                                                               | 29        |

| 2.4.2 Simulation AC .....                                                                                            | 30        |

| 2.4.3 Mesure de délai en mode fonctionnel .....                                                                      | 32        |

| 2.4.4 Interprétation des résultats .....                                                                             | 34        |

| 2.5 Conclusion .....                                                                                                 | 34        |

| <b>CHAPITRE 3 RÉSULTATS DE SIMULATION EN MODE TEST POUR LES PRINCIPALES TECHNIQUES DE TEST SBAST EXISTANTES.....</b> | <b>37</b> |

| 3.1 Introduction.....                                                                                                | 37        |

| 3.2 Métrique de test.....                                                                                            | 37        |

| 3.3 Résultats de simulation pour les techniques Launch on Capture et Launch on Shift ..                              | 39        |

|                                                                                                           |                                                                                                   |           |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|

| 3.4                                                                                                       | Résultats de simulation pour la technique Sequential Broadside Side (SeBoS).....                  | 41        |

| 3.5                                                                                                       | Résultats de simulation pour la technique BurstMode .....                                         | 43        |

| 3.6                                                                                                       | Résultats de simulation pour la technique Pseudo-functional K Longest Paths per Gate (PKLPG)..... | 46        |

| 3.7                                                                                                       | Conclusion .....                                                                                  | 47        |

| <b>CHAPITRE 4 NOUVELLE TECHNIQUE DE TEST PROPOSÉE ET COMPARAISON AVEC LES TECHNIQUES EXISTANTES .....</b> |                                                                                                   | <b>49</b> |

| 4.1                                                                                                       | Introduction.....                                                                                 | 49        |

| 4.2                                                                                                       | Nouvelle technique de test OCAS .....                                                             | 49        |

| 4.3                                                                                                       | Résultats de simulation .....                                                                     | 51        |

| 4.4                                                                                                       | Comparaison et analyse des résultats avec les techniques existantes .....                         | 53        |

| 4.5                                                                                                       | Conclusion .....                                                                                  | 58        |

| <b>CHAPITRE 5 GÉNÉRATION AUTOMATIQUE DE VECTEURS DE TEST .....</b>                                        |                                                                                                   | <b>61</b> |

| 5.1                                                                                                       | Introduction.....                                                                                 | 61        |

| 5.2                                                                                                       | Conception en vue du test et génération automatique de vecteurs de test .....                     | 61        |

| 5.3                                                                                                       | Génération automatique de vecteurs de test pour les techniques LOC, LOS et BurstMode.....         | 64        |

| 5.4                                                                                                       | Procédure de test développée pour SeBoS et OCAS .....                                             | 68        |

| 5.4.1                                                                                                     | Procédure de test développée pour SeBoS.....                                                      | 68        |

| 5.4.2                                                                                                     | Procédure de test développée pour OCAS.....                                                       | 72        |

| 5.5                                                                                                       | Résultats de simulation des différentes techniques de test .....                                  | 77        |

| 5.6                                                                                                       | Conclusion .....                                                                                  | 82        |

| <b>CONCLUSION .....</b>                                                                                   |                                                                                                   | <b>83</b> |

| <b>RECOMMANDATIONS .....</b>                                                                              |                                                                                                   | <b>85</b> |

| <b>ANNEXE I</b>                                                                                           | <b>MODÈLE ORIGINAL DU CIRCUIT ÉQUIVALENT CI-3D .....</b>                                          | <b>87</b> |

| <b>ANNEXE II</b>                                                                                          | <b>RÉSULTATS DE MESURE DE DÉLAI DE PROPAGATION DES PRINCIPALES TECHNIQUES DE de SBAST.....</b>    | <b>89</b> |

| <b>LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES.....</b>                                                          |                                                                                                   | <b>95</b> |

## LISTE DES TABLEAUX

|             | Page                                                                                                                                                           |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau 2.1 | Mesure de délai de propagation en mode fonctionnel avec les trois scénarios.....                                                                               | 34 |

| Tableau 3.1 | $M_{R/Tmm}$ (%) en fonction de la fréquence d'horloge $F_{mm}$ des techniques LOC et LOS, et les 3 scénarios considérés .....                                  | 39 |

| Tableau 3.2 | RMSE en fonction de la fréquence d'horloge $F_{mm}$ des techniques LOC et LOS .....                                                                            | 40 |

| Tableau 3.3 | $M_{R/Tmm}$ (%) en fonction de la fréquence d'horloge $F_{mm}$ et $F_{nscc}$ , pour la technique SeBoS, et les 3 scénarios considérés .....                    | 42 |

| Tableau 3.4 | $M_{R/Tmm}$ (%) en fonction de la fréquence d'horloge $F_{mm}$ pour la technique BurstMode, et les 3 scénarios considérés .....                                | 45 |

| Tableau 3.5 | $M_{R/Tmm}$ (%) en fonction de la fréquence d'horloge $F_{mm}$ pour la technique PKLPG, et les 3 scénarios considérés .....                                    | 47 |

| Tableau 4.1 | $M_{R/Tmm}$ (%) en fonction de la fréquence d'horloge $F_{mm}$ pour la technique OCAS, les deux moments de capture et les 3 scénarios.....                     | 52 |

| Tableau 4.2 | Comparaison de $M_{R/Tmm}$ (%) entre les différentes techniques de test en fonction de la fréquence d'horloge $F_{mm}$ et les 3 scénarios considérés .....     | 54 |

| Tableau 4.3 | Max ( $M_{R/Tmm}$ ) – Min ( $M_{R/Tmm}$ ) (%) en fonction de la fréquence d'horloge $F_{mm}$ et les différentes technique de test.....                         | 57 |

| Tableau 5.1 | Caractéristiques des circuits benchmark d'ITC 99 .....                                                                                                         | 64 |

| Tableau 5.2 | Résultats de simulation des trois étapes générées par FastScan en fonction de deux copies de b01 .....                                                         | 76 |

| Tableau 5.3 | Exemple de calcul de la couverture de pannes de transition avec la combinaison d'OCAS et les deux copies du circuit b01.....                                   | 77 |

| Tableau 5.4 | Résultats de simulation du pourcentage de la couverture de test de transition (%) des techniques SBAST en fonction de deux copies des circuits Benchmark ..... | 79 |

| Tableau 5.5 | Nombre de vecteurs de test des techniques SBAST en fonction de deux copies des circuits Benchmark.....                                                         | 81 |

## LISTE DES FIGURES

|             | Page                                                                                              |    |

|-------------|---------------------------------------------------------------------------------------------------|----|

| Figure 0.1  | Organisation du mémoire.....                                                                      | 4  |

| Figure 1.1  | Approche de test des circuits intégrés.....                                                       | 6  |

| Figure 1.2  | Illustration d'une structure DFT avant et après l'ajout des circuits de balayage .....            | 11 |

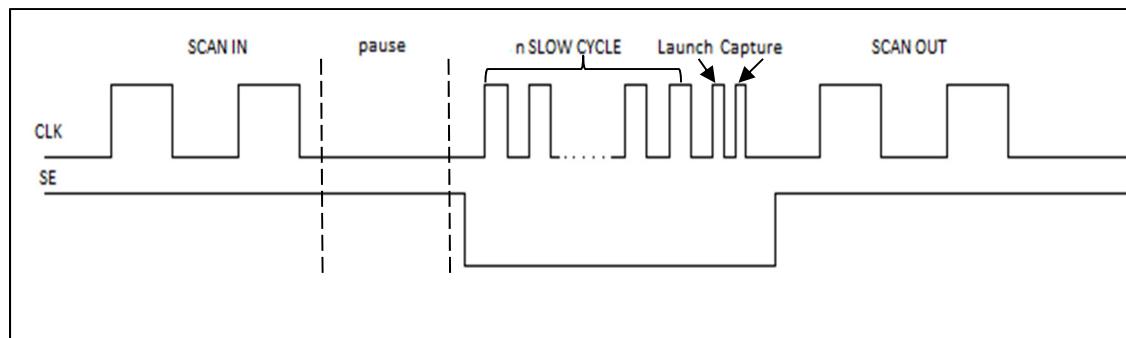

| Figure 1.3  | Chronogramme des techniques LOS et LOC.....                                                       | 13 |

| Figure 1.4  | Circuit intégré 3D basé sur des TSV.....                                                          | 14 |

| Figure 1.5  | Chronogramme de la technique SeBoS .....                                                          | 17 |

| Figure 1.6  | Exemple de forme d'onde de la technique <i>BurstMode</i> .....                                    | 20 |

| Figure 1.7  | Chronogramme de la technique PKLPG.....                                                           | 21 |

| Figure 2.1  | Schéma fonctionnel d'un réseau de distribution d'alimentation.....                                | 23 |

| Figure 2.2  | Modèle PDN du processeur Intel Pentium IV .....                                                   | 24 |

| Figure 2.3  | Cellule unitaire de la grille P/G sur-puce et le modèle de circuit équivalent correspondant ..... | 25 |

| Figure 2.4  | Modèle équivalent PDN du CI-3D avec trois puces.....                                              | 26 |

| Figure 2.5  | Circuit de mesure de délai.....                                                                   | 27 |

| Figure 2.6  | Mesure des délais.....                                                                            | 29 |

| Figure 2.7  | Scénarios étudiés lors des simulations .....                                                      | 30 |

| Figure 2.8  | Modèle PDN simplifié pour la simulation d'impédance .....                                         | 31 |

| Figure 2.9  | Impédance simulée du PDN 3D pour les 3 scénarios considérés .....                                 | 32 |

| Figure 2.10 | Exemple de forme d'onde générée par HSPICE du scénario S1 à 200 MHz en mode fonctionnel .....     | 33 |

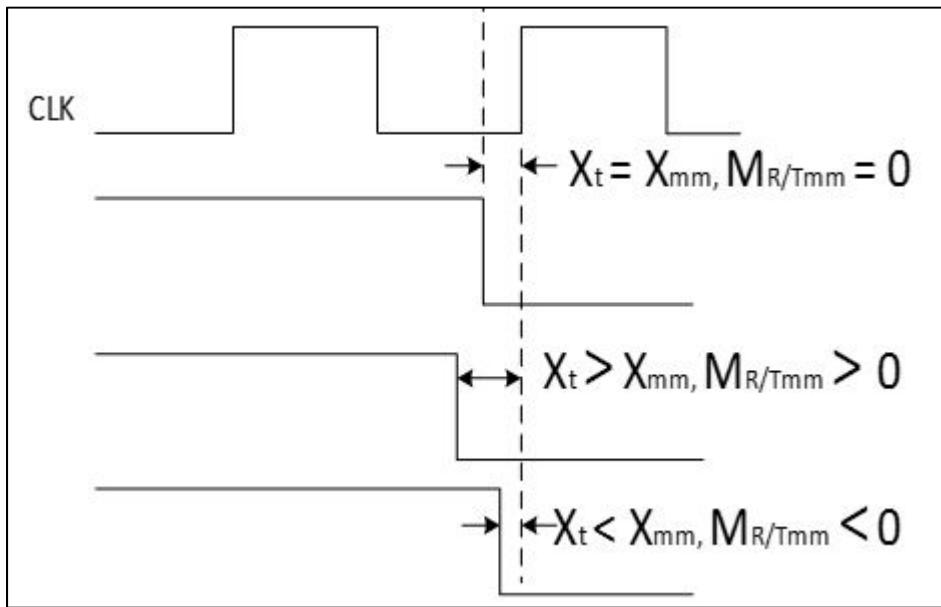

| Figure 3.1  | Métrique basée sur la marge de synchronisation de délai du mode test et du mode fonctionnel.....  | 38 |

|             |                                                                                                                                         |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2  | Chronogramme de trois séquences d'horloge simulées avec la technique SeBoS .....                                                        | 41 |

| Figure 3.3  | Chronogramme de cinq <i>bursts</i> simulés avec la technique BurstMode .....                                                            | 44 |

| Figure 3.4  | Chronogramme de la technique PKLPG simulée .....                                                                                        | 46 |

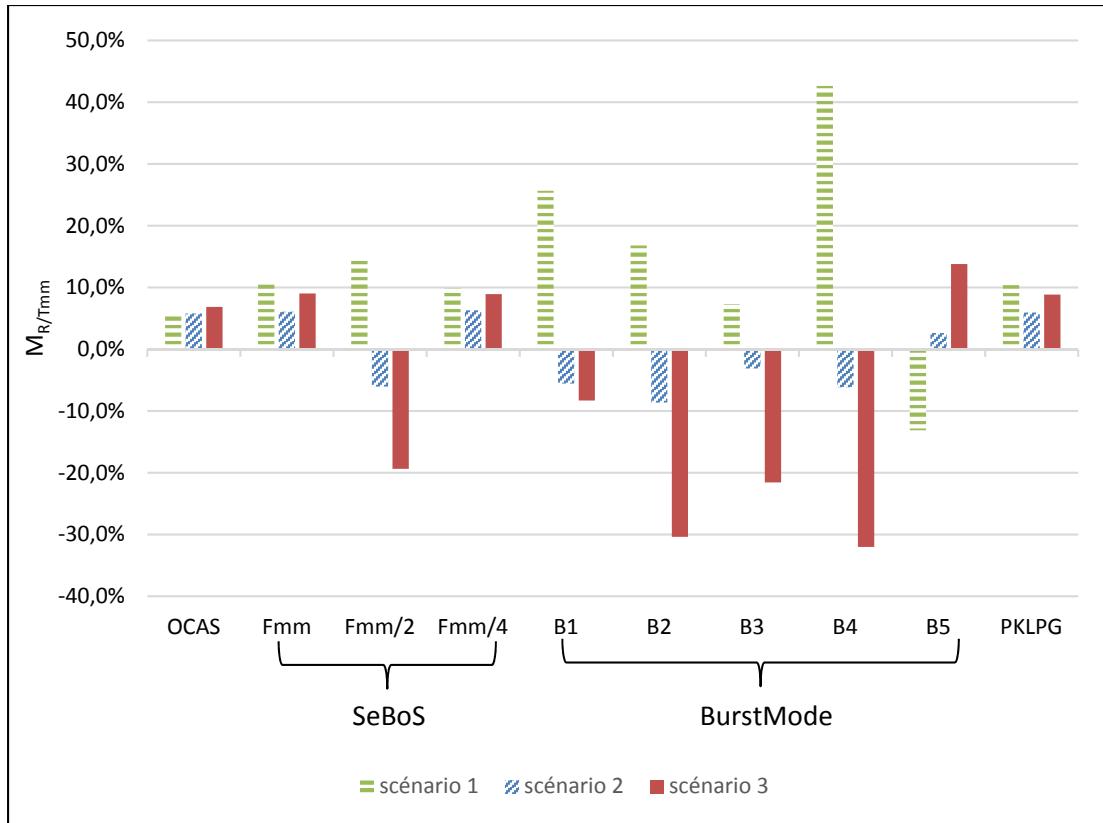

| Figure 4.1  | Chronogramme de la technique proposée OCAS .....                                                                                        | 50 |

| Figure 4.2  | $M_{R/T_{mm}}$ de différentes techniques de test en fonction des 3 scénarios considérés à 400 MHz.....                                  | 56 |

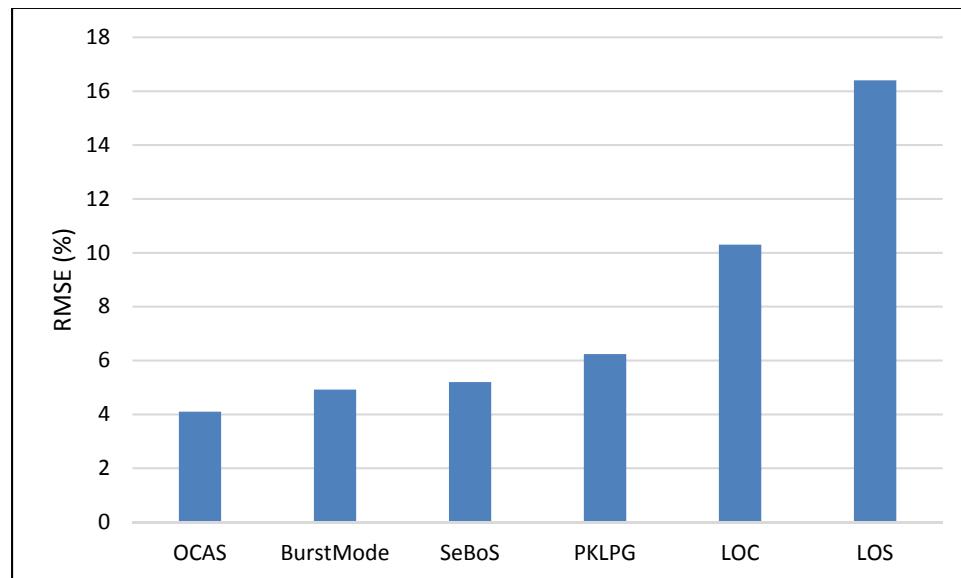

| Figure 4.3  | Comparaison de RMSE des différentes techniques .....                                                                                    | 57 |

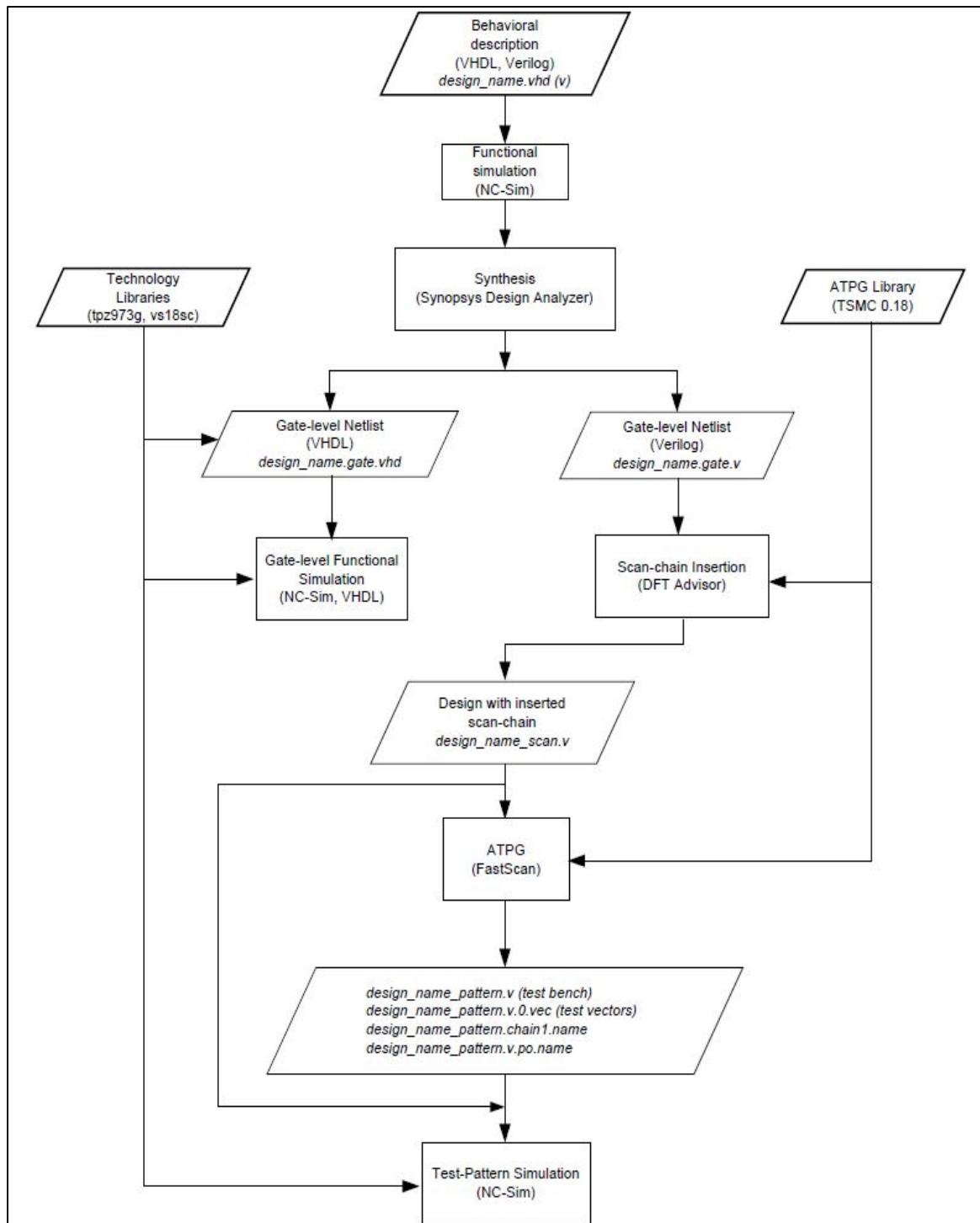

| Figure 5.1  | Flot de conception, de la capture du design à l'insertion des chaînes de balayage et de génération automatique de vecteurs de test..... | 63 |

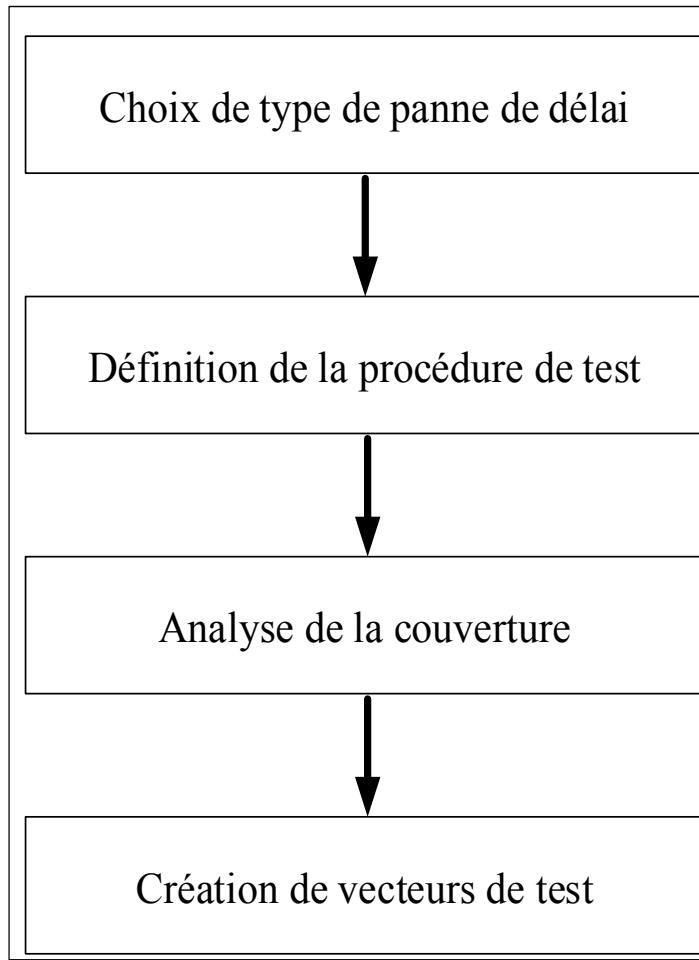

| Figure 5.2  | Flux de création de test de délai.....                                                                                                  | 66 |

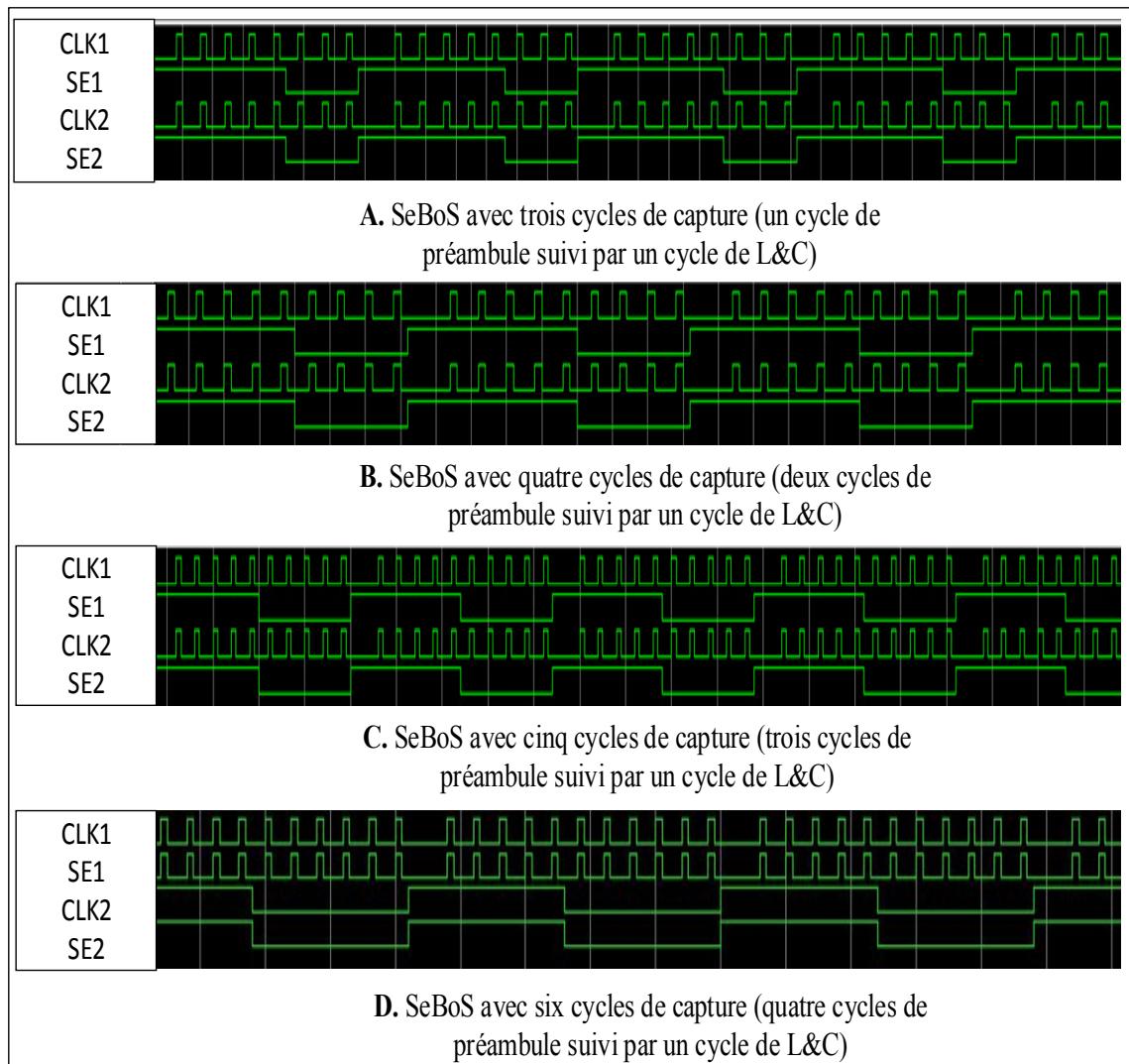

| Figure 5.3  | Exemples de formes d'onde simulées avec la technique SeBoS .....                                                                        | 69 |

| Figure 5.4  | Exemple d'une partie de la procédure de test généré par DftAdvisor avec 2 copies de b01 .....                                           | 70 |

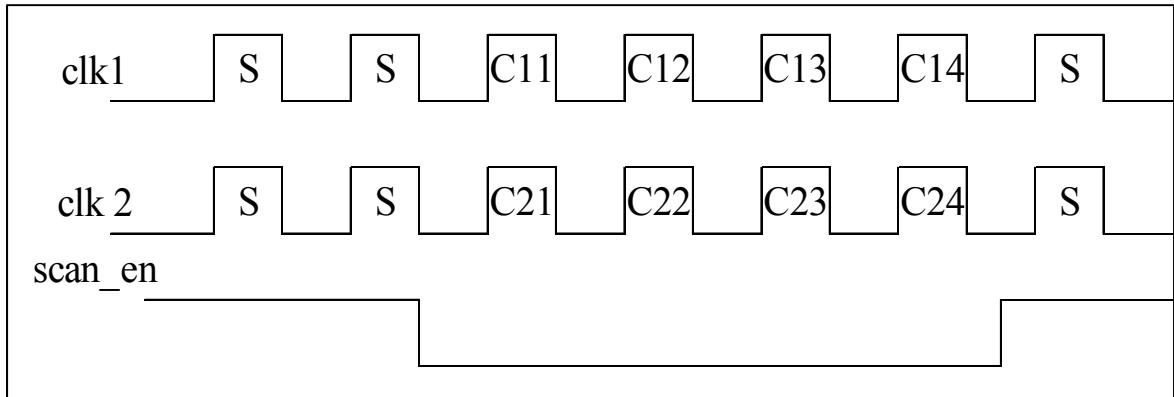

| Figure 5.5  | Chronogrammes de la technique SeBoS B avec quatre impulsions de capture appliquées à deux copies des circuits Benchmark ITC' 99.....    | 71 |

| Figure 5.6  | Procédure de capture de la technique SeBOS B .....                                                                                      | 72 |

| Figure 5.7  | Procédure de capture de la technique OCAS .....                                                                                         | 73 |

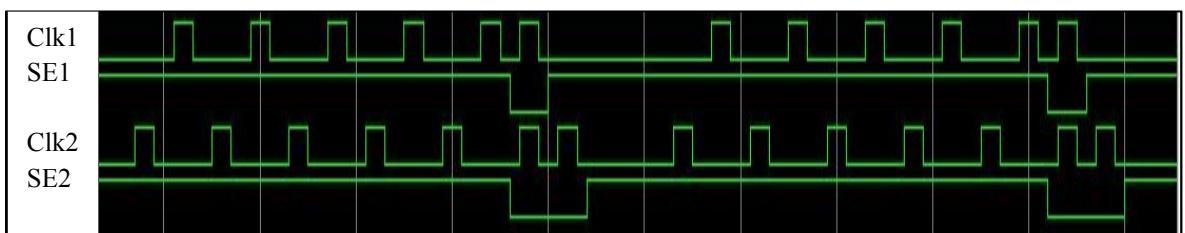

| Figure 5.8  | Exemple de forme d'onde simulée de la technique OCAS après la génération des vecteurs de test avec deux copies de b01.....              | 73 |

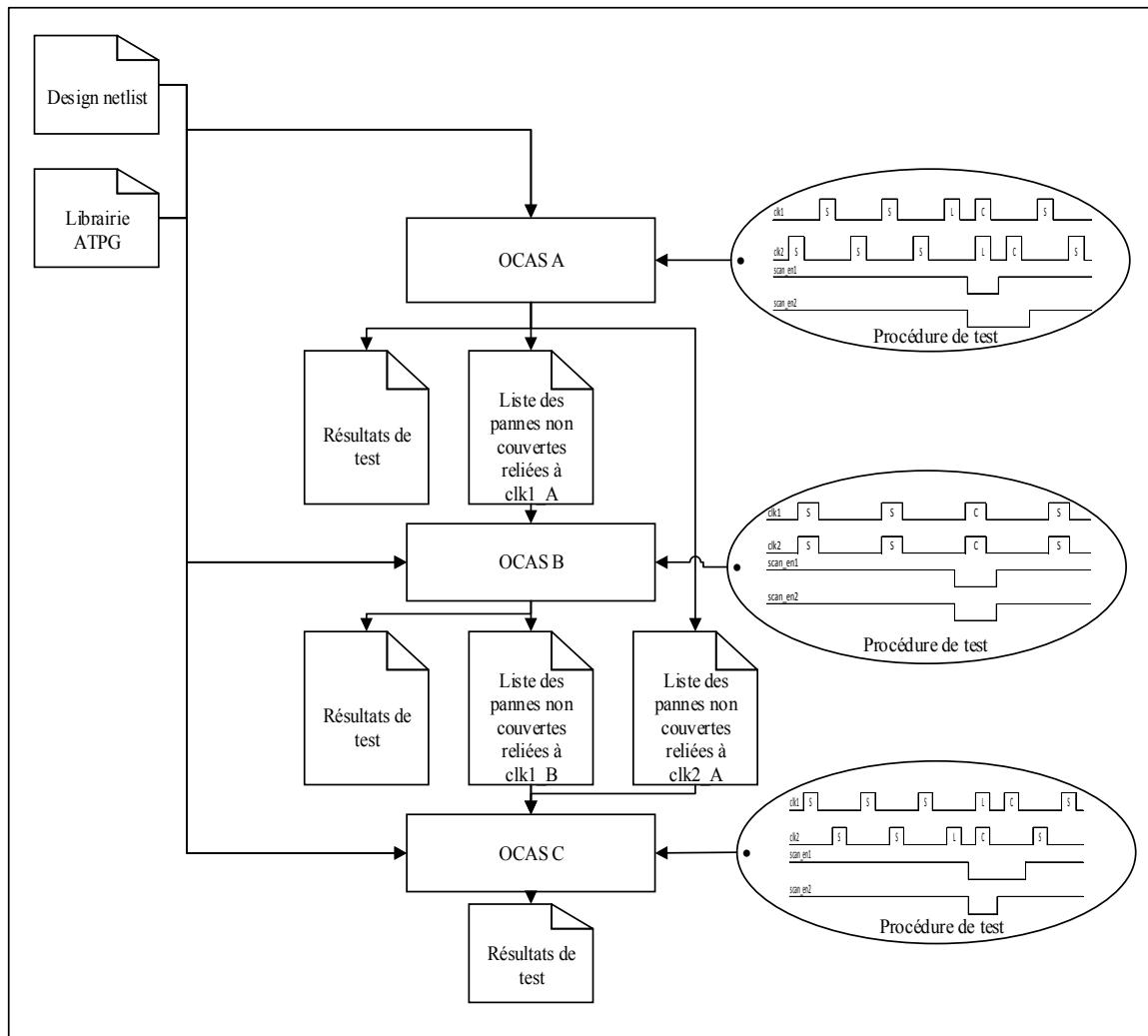

| Figure 5.9  | Combinaison de tests développée pour OCAS .....                                                                                         | 75 |

| Figure 5.10 | Exemple d'un rapport de statistiques généré par FastScan.....                                                                           | 76 |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|       |                                           |

|-------|-------------------------------------------|

| ATE   | Automatic Test Equipment                  |

| ATPG  | Automatic Test Pattern Generation         |

| BCC   | Burst Clock Controller                    |

| CI-3D | Circuit intégré trois dimensionnel        |

| CMOS  | Complementary Metal Oxide Semiconductor   |

| CUT   | Circuit Under Test                        |

| DFT   | Design for Test                           |

| FPGA  | Field Programmable Gate Arrays            |

| LOC   | Launch On Capture                         |

| LOS   | Launch On Shift                           |

| OCAS  | One Clock Alternated Shift                |

| PDN   | Power Delivery Network                    |

| PKLPG | Pseudo-functional K Longest Path per Gate |

| PSN   | Power Supply Noise                        |

| RTL   | Register Transfer Level                   |

| SA    | Switching Activity                        |

| SBAST | Scan Based at-Speed Testing               |

| SE    | Scan Enable                               |

| SeBoS | Sequential Broad Side                     |

| STF   | Slow-To-Fall                              |

| STR   | Slow-To-Rise                              |

| TC    | Test Coverage                             |

| TSV   | Trough Silicon Via                        |

| VHDL  | VHSIC Hardware Description Language       |

| VRM   | Voltage Regulator Module                  |

## INTRODUCTION

Depuis la création de l'industrie microélectronique vers la fin des années 1950, le nombre de transistors intégrés dans une puce n'a pas cessé d'augmenter suivant la fameuse prédiction de Moore, qui a prévu en 1965 que la densité des transistors devrait doubler toutes les deux années. Au fur et à mesure que le nombre de transistors augmente, de nouveaux défis surgissent pour les ingénieurs de test. Les effets submicroniques sont de plus en plus importants avec le rétrécissement de la taille des transistors, ce qui augmente la probabilité de défectuosités liées au comportement temporel du circuit. En conséquence, pour assurer des puces de haut niveau, des tests à vitesse nominale sont nécessaires pour détecter les défectuosités liées au comportement temporel du circuit. Dans le passé, les modèles fonctionnels ont été utilisés pour le test à vitesse nominale. Cependant, la génération de tests fonctionnels est difficile et prend beaucoup de temps pour les conceptions complexes. De plus, les modèles fonctionnels ont une faible couverture de pannes et nécessitent un grand effort afin de générer les vecteurs de test (Tehranipoor, Peng et Chakrabarty, 2011). Une alternative rentable était alors d'utiliser les tests structurels. Ces tests détectent les défectuosités de fabrication d'une puce en se basant sur des modèles de pannes. Ils se caractérisent par une courte durée du test, par une grande couverture de test et par un nombre de vecteurs de test inférieur à celui de tests fonctionnels (Wang, Wu et Wen, 2006).

Le test de balayage à vitesse nominale (SBAST, Scan Based at Speed Testing) est l'approche de test de type délai la plus utilisée (Moghaddam et al., 2010). Ce test détecte les pannes qui peuvent se produire lorsqu'un circuit fonctionne à une cadence d'horloge lente, puis échoue à vitesse nominale, ce qui entraîne des variations de délai de propagation causé par la conductivité partielle des transistors (Tehranipoor, Peng et Chakrabarty, 2011). Autrement dit, ce test émule le fonctionnement normal de la puce en vitesse nominale pour s'assurer que les délais de propagation de ces transitions respectent la période d'horloge de leur domaine de fréquence respectif (Larche, 2013).

Le grand défi des tests SBAST est de diminuer la différence entre le délai de propagation produit pendant le mode test et pendant le mode fonctionnel. Cette différence est induite généralement par le bruit de tension d'alimentation (PSN, *Power Supply Noise*), l'inconvénient majeur du test SBAST. La différence de PSN entre le mode fonctionnel et le mode structurel peut conduire à une différence de la fréquence de fonctionnement d'une de plus de 30 % (Zhang et Walker, 2014). Lorsqu'une puce est en mode test, de grandes baisses de tension se produisent et affectent les délais de propagation et peuvent réduire la fréquence maximale du circuit (Pant et Skeels, 2011) (Jha et Gupta, 2003). Ces baisses de tension d'alimentation peuvent conduire au phénomène d'étirement d'horloge de telle sorte que le circuit sous test « CUT, *Circuit Under Test* ») apparaît plus rapide (Rearick et Rodgers, 2005).

La plupart des travaux qui ont traité des problèmes liés au PSN ont concentré leur attention sur la chute de tension d'alimentation et ont proposé différentes techniques pour réduire la chute de tension. Ces techniques consistent à modifier le schème des techniques principales de SBAST (LOC, *Launch On Capture* et LOS, *Launch On Shift*) avec l'augmentation de la longueur de la séquence de lancement ou de capture de l'horloge. Les techniques les plus pertinentes proposées dans la littérature sont : SeBoS (Lin et al., 2013; Pant et Zelman, 2009), BurstMode (Nadeau-Dostie, Takeshita et Cote, 2008) et PKLPG (Zhang et Walker, 2013).

Bien que les chercheurs aient développé plusieurs techniques de test SBAST, un aspect particulier a été négligé dans la littérature ; la variation de l'impédance du réseau d'alimentation (PDN, *Power Distribution Network*) et son impact sur la marge de propagation de délai. En effet, la variation d'impédance du PDN peut avoir une influence significative sur le comportement du circuit en mode fonctionnel et en mode test. De plus l'utilisation des circuits intégrés 3D peut amplifier le problème à cause de différents moments de test (*pre-bond*, *mid-bond* et *post-bond*) appliqués sur ce type de circuit.

L'objectif principal de ce mémoire est de montrer que le changement d'impédance du PDN peut affecter la manière avec laquelle le circuit se comporte en mode fonctionnel ou en mode test. Afin de réaliser l'objectif principal de ce projet, d'autres objectifs ont été définis :

- montrer que les techniques existantes de SBAST souffrent de la variation d'impédance du réseau d'alimentation;

- proposer une nouvelle technique de test de type SBAST plus robuste à la variation d'impédance qui imite de façon proche le mode fonctionnel;

- montrer que la couverture de pannes de transition de la technique proposée est comprise entre celle du LOS et celle du LOC.

À notre connaissance, les recherches portant sur l'impact de la variation d'impédance du PDN sur le test de délai sont inexistantes. Les contributions majeures de ce travail sont la démonstration d'un nouveau problème négligé dans la littérature et le développement d'une nouvelle technique de test SBAST moins sensible à une telle variation. De plus, certains résultats présentés dans ce mémoire ont fait l'objet de l'article (Thibeault et Louati, 2017).

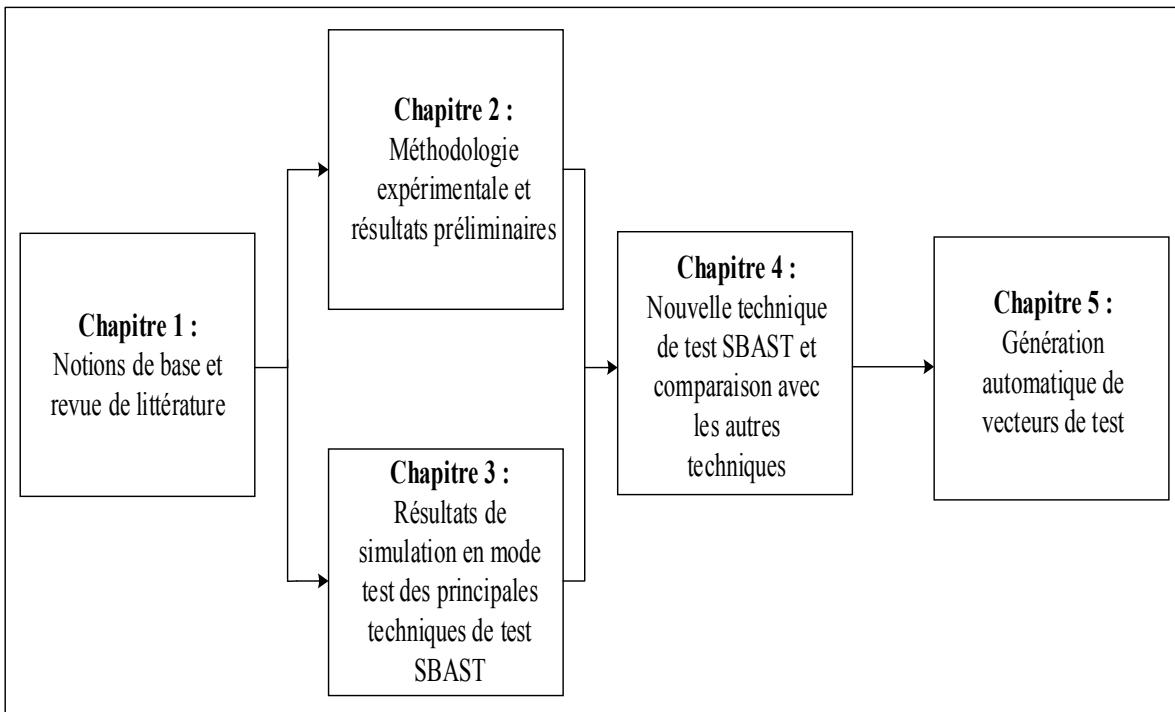

Ce mémoire présente le travail réalisé pour atteindre les objectifs de ce projet, il s'organise en cinq chapitres. Le chapitre 1 présente différents concepts nécessaires à la compréhension de ce mémoire ainsi qu'une revue de littérature qui explique les différentes techniques de test de balayage à vitesse nominale trouvées dans la littérature. Le chapitre 2 détaille les différentes étapes de réalisation de ce projet ainsi que quelques résultats préliminaires pour montrer que le changement d'impédance du PDN peut affecter le comportement de circuit en mode fonctionnel. Ces résultats seront considérés comme une référence lors de la comparaison des différentes techniques de SBAST. Le chapitre 3 présente les résultats de simulation des principales techniques de test SBAST ainsi qu'une analyse de ces résultats permettant de valider l'hypothèse de ce projet. Le chapitre 4 permet de décrire la nouvelle technique de test développée et présente les résultats de simulation avec cette technique ainsi qu'une analyse comparative de ces résultats avec ceux trouvés dans le chapitre 3. Le chapitre 5 présente une nouvelle série de résultats pour comparer la couverture des pannes de transition de la technique OCAS avec celle des techniques existantes, ainsi que la procédure de test développée pour cette technique avec les outils ATPG. Une conclusion générale et des recommandations complètent ce mémoire.

La figure 0.1 illustre l'organisation des chapitres de ce mémoire.

Figure 0.1 Organisation du mémoire

## **CHAPITRE 1**

### **NOTIONS DE BASE ET REVUE DE LITTÉRATURE**

#### **1.1 Introduction**

Les travaux effectués dans ce projet de maîtrise se concentrent sur le domaine du test des circuits intégrés et plus précisément sur les tests de type délai. La première partie de ce chapitre présente les concepts de base permettant de comprendre le test des circuits intégrés. La deuxième partie décrit les circuits intégrés en 3D et justifie leur utilisation dans ce projet. La troisième partie discute les différentes techniques présentées dans la littérature de test de balayage à vitesse nominale.

#### **1.2 Notions de base sur le test des circuits intégrés**

La réduction de la taille des transistors a permis aux industriels et aux chercheurs de concevoir et de développer des circuits intégrés très complexes dotés d'un nombre toujours croissant de composants et de portes logiques. Du point de vue des industriels et des consommateurs, un circuit doit fonctionner correctement en respectant toutes les exigences fonctionnelles conçues à l'origine.

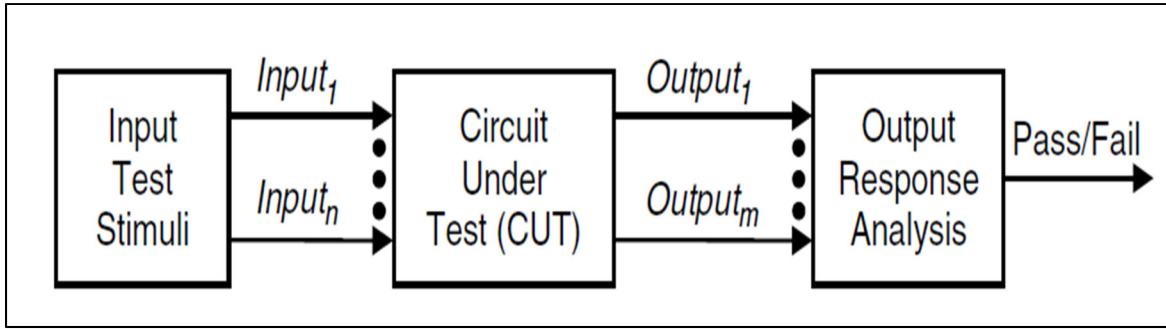

Le test sert à vérifier le fonctionnement d'une puce et à respecter toutes les spécifications de conception (Jha et Gupta, 2003). Il permet d'identifier les pannes de fabrication pour assurer une bonne qualité du produit. Il consiste à stimuler l'intérieur d'un circuit à partir de ses broches d'entrées et d'observer la réponse sur les broches de sorties du circuit. La figure 1.1 illustre l'approche de tests des circuits intégrés. Le circuit sous test (CUT, *Circuit Under Test*) réussit le test si les valeurs des signaux de sorties sont égales aux valeurs attendues, sinon le circuit est déclaré défectueux (Wang, Wu et Wen, 2006).

Figure 1.1 Approche de test des circuits intégrés

Tirée de Wang, Wu et Wen (2006)

Il existe principalement deux types de tests des circuits intégrés : le test fonctionnel et le test structurel.

### 1.2.1 Test fonctionnel

Le test fonctionnel consiste à vérifier le bon fonctionnement d'une puce à sa vitesse nominale. Il permet de s'assurer de la conformité des spécifications pour lesquelles le circuit a été conçu (Wang, Wu et Wen, 2006). Ce type de test considère le circuit comme étant une boîte noire sans s'intéresser à sa structure interne. Le test fonctionnel applique des vecteurs de test sur les signaux d'entrées d'une puce et compare les valeurs obtenues sur les signaux de sorties avec les valeurs logiques attendues, le tout à vitesse nominale. Une puce est défectueuse si les valeurs logiques observées sur les signaux de sortie sont différentes des valeurs attendues. Le test fonctionnel donne une faible couverture de pannes et nécessite un grand effort afin de générer les vecteurs de test, ce qui a graduellement mené à son remplacement par le test structurel (Tehranipoor, Peng et Chakrabarty, 2011).

### 1.2.2 Test structurel

Le test structurel est une approche de test largement utilisée pour tester les circuits intégrés (Mir, 2004). Ce type de test vérifie la structure du circuit, alors que le test fonctionnel vérifie la fonctionnalité du circuit. Le but de ce test est de détecter les défauts de fabrication

d'une puce en se basant sur des modèles de pannes. Ce test se caractérise par une courte durée du test. En effet, le nombre de vecteurs de tests associé est inférieur à celui de test fonctionnel (Wang, Wu et Wen, 2006).

### **1.2.3 Modèles de pannes**

Un modèle de panne est une représentation des défectuosités et des défaillances physiques d'un circuit intégré (Wang, Wu et Wen, 2006). Les principaux modèles de pannes de test structurel sont : le modèle de collage, le modèle de court-circuit et le modèle de délai.

#### **1.2.3.1 Modèle de collage**

Une panne collée-à (*stuck-at*) affecte le comportement logique du système (Mei, 1974). Ces pannes affectent l'état logique des signaux (entrées et sorties) des portes logiques. Une panne collée-à transforme la valeur correcte sur un nœud du signal défectueux pour apparaître collée à une valeur logique, 0 (SA0) ou 1 (SA1).

#### **1.2.3.2 Modèle de court-circuit**

Le modèle de panne de court-circuit représente les défectuosités qui se produisent en réponse à un contact accidentel entre deux équipotentiels distincts (Wang, Wu et Wen, 2006) :

- à l'intérieur d'une porte ;

- entre les nœuds (entrée/sortie de porte).

#### **1.2.3.3 Modèle de délai (retard)**

Les pannes de délai affectent le comportement temporel d'un circuit. Ils ajoutent un délai excessif le long d'un chemin combinatoire de sorte que les signaux se propagent lentement ou rapidement. Les pannes de délai sont de plus en plus présentes dans les circuits intégrés en raison de la miniaturisation de ces derniers. Ces pannes provoquent un dysfonctionnement du circuit à haute vitesse (Wang, Wu et Wen, 2006). L'effet principal de ces pannes est de ralentir

les transitions qui se propagent dans un circuit. Les modèles de délai sont divisés en deux sous catégories : les pannes de délai de chemin (*path delay fault*) et les pannes de transition.

Le modèle de pannes de chemin suppose que le délai additionnel causé par la panne est réparti sur tout le chemin. Ce modèle de pannes est habituellement utilisé pour représenter l'effet des variations du procédé de fabrication et pour tester les chemins les plus critiques. Un circuit est défectueux si le délai de l'un de ces chemins combinatoires excède la limite de délai spécifié (Smith, 1985).

Le modèle de pannes de transition, quant à lui, suppose que la panne affecte un seul nœud du circuit, de manière ponctuelle (Waicukauski et al., 1987). Par exemple, si une panne de délai est identifiée sur un nœud logique, toute transition de signal passant par ce nœud est retardée au-delà de la période d'horloge. Ces pannes sont modélisées comme un retard du temps de montée ou de descente des transitions des signaux au niveau des portes logiques.

Selon (Waicukauski et al., 1987), il existe deux types de pannes de transition : la panne de transition lente à monter (STR, *slow-to-rise fault*) et la panne de transition lente à descendre (STF, *slow-to-fall fault*). Une panne STR signifie que toute transition de  $0 \rightarrow 1$  sur un nœud ne produit pas un résultat correct lorsque le circuit fonctionne à fréquence nominale. Une panne STF signifie que toute transition de  $1 \rightarrow 0$  sur un nœud ne produit pas un résultat correct lorsque le circuit fonctionne à fréquence nominale.

Ce mémoire traite uniquement les pannes de délais et, plus particulièrement, les pannes de transition. Par conséquent, le test de délai de transition est le type de test utilisé lors de nos expérimentations.

#### 1.2.4 Génération automatique de vecteurs de test (ATPG)

Les vecteurs de test, appelé aussi patrons de test, sont des ensembles de 0 et 1 logiques placés aux broches des entrées primaires d'un CUT. Ils permettent de contrôler les pannes à partir des

entrées primaires et de les observer sur les sorties primaires. Lors de l’application des vecteurs de test, les équipements automatiques de test (ATE, *Automatic Test Equipment*) déterminent s’il existe des pannes de fabrication sur un CUT en comparant les réponses de ses sorties primaires à celles d’un circuit sans panne (*fault-free circuit*). L’objectif de la génération automatique de vecteurs de test (ATPG, *Automatic Test Pattern Generation*) est de créer un ensemble de vecteurs de test pour atteindre une couverture de pannes adéquate (Tessent, 2014). La couverture de test (TC) est une mesure pour évaluer l’efficacité de test. La couverture de test est le pourcentage du nombre de pannes détectées divisé par le nombre total de pannes de circuit (équation 1.1).

$$TC = 100 \cdot \frac{\text{Nombre de pannes détectées par la séquence de test}}{\text{Nombre total de pannes du circuit}} \quad (1.1)$$

L’ATPG utilise des vecteurs de test déterministes pour détecter autant de pannes que possible avec un effort raisonnablement faible. Il génère des vecteurs de test qui sont destinés à montrer si le système exécute sa fonction spécifiée. Ces vecteurs de test détectent les pannes définies par des modèles de pannes spécifiques. Pour détecter une panne, l’ATPG insère une panne à un nœud dans le CUT. Deux procédures sont appliquées à la panne ciblée : l’activation des pannes et la propagation des pannes. L’activation des pannes impose une valeur logique, au niveau du nœud ciblé, opposé à la valeur de la panne. La panne se propage par la suite à travers les portes logiques, pour atteindre les sorties primaires (Tremblay, 2007).

### 1.2.5 Conception en vue de test

Traditionnellement, le processus du test était considéré uniquement après le processus de conception. Mais avec les flux actuels de conception, ces deux processus sont maintenant combinés. Cette combinaison est appelée conception en vue de test (DFT, *Design for Test*). De plus, la plupart des circuits numériques sur le marché sont des circuits séquentiels, dans lesquels les signaux internes sont difficiles à observer et à contrôler. En conséquence, il est difficile de les tester. Le but de la DFT est de rendre le test des circuits plus faciles et plus efficaces (Hobeika, 2011). Les techniques de DFT les plus utilisées sont la technique d’autotest

(BIST, Built in-it-Self Test) et la technique de test basé sur l’insertion des registres de balayage (SBT, *Scan Based Test*).

L’autotest (BIST) permet aux circuits de se tester eux-mêmes. BIST est capable de générer des vecteurs de test à l’intérieur du CUT et de vérifier la fonctionnalité interne du circuit (Hobeika, 2011).

Le SBT est une technique DFT largement utilisée qui permet de contrôler et d’observer les bascules en ajoutant un mode de balayage au circuit. Lorsque le circuit est en mode de balayage, toutes les bascules forment un ou plusieurs registres à décalage, également appelés chaînes de balayage. Ce processus réduit le cout du test en transformant un circuit séquentiel en un circuit combinatoire à des fins de test.

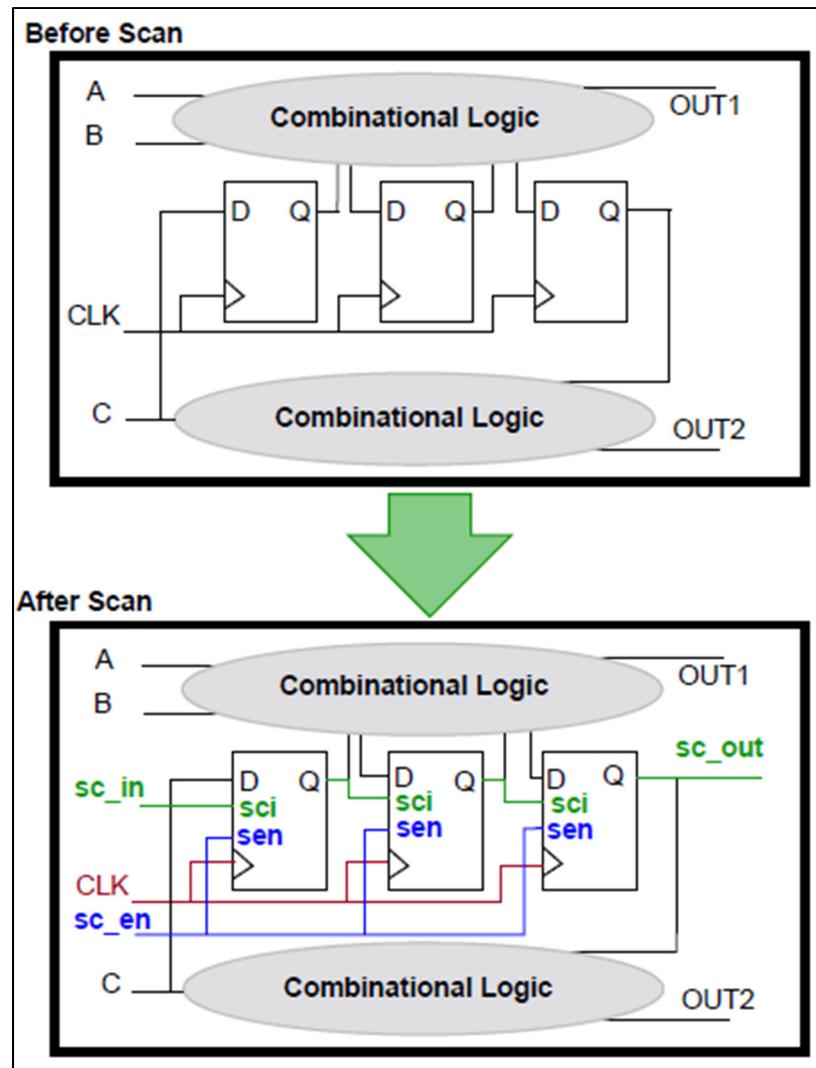

La figure 1.2 illustre une structure DFT avant et après l’ajout des circuits de balayage. Le SBT consiste à insérer des bascules de balayage à la place des bascules présentes sur le design (un multiplexeur et une bascule forment une bascule de balayage). Le signal (SE, *Scan Enable*) détermine si le système est en mode normal ( $SE = 0$ ) ou mode de balayage ( $SE = 1$ ). Les vecteurs de test peuvent être décalés vers l’intérieur (à travers *sc\_in*) ou vers l’extérieur (à travers *sc\_out*) à travers des chaines de balayage, tandis que les autres entrées (A,B,C) sont encore fournies par des entrées primaires (Hobeika, 2011). De cette façon, chaque entrée peut être contrôlée bit par bit, et chaque sortie peut être observée plus clairement. Par conséquent, le circuit séquentiel avec la technique SBT a une meilleure contrôlabilité et une meilleure observabilité. Les deux derniers termes peuvent affecter la qualité de test (Hobeika, 2011). La contrôlabilité est une mesure de la facilité d’imposer au niveau logique d’un nœud du circuit un état logique donné (0 ou 1). L’observabilité est une mesure de la facilité d’observer le niveau logique d’un nœud aux broches de sortie du CUT.

Figure 1.2 Illustration d'une structure DFT avant et après l'ajout des circuits de balayage

Tirée de Tessent (2014)

### 1.2.6 Test de transition avec insertion de registres de balayages

Le test de transition est utilisé pour garantir un comportement temporel correct du circuit. Il consiste à appliquer une paire de vecteurs ( $V_1, V_2$ ) (Park et McCluskey, 2008).  $V_1$  est le vecteur qui initialise un nœud à une valeur logique.  $V_2$  est le vecteur suivant qui lance une transition de valeurs logiques ( $0 \rightarrow 1$  ou  $1 \rightarrow 0$ ) à un nœud correspondant. Par la suite, l'effet de la transition se propage vers une sortie primaire ou une bascule de balayage (*scan flip-flop*).

En d'autres termes, il consiste à appliquer un ensemble de vecteurs de test qui testent une panne de transition à la sortie ou à l'entrée d'une porte logique telle que :

- une transition désirée est lancée sur le site de la panne;

- si la panne est STR, V2 est un test pour une panne collé à 0, et si la panne est une panne STF, V2 est un test pour une panne collée à 1.

Il existe deux techniques principales qui génèrent et appliquent les tests de transition avec insertion de registres de balayage : (LOC, *Launch On Capture*) (Savir et Patil, 1994) et (LOS, *Launch on Shift*) (Savir et Patil, 1993). Ce qui suit explique brièvement le principe de fonctionnement de ces deux techniques.

### **1.2.7      Launch on Shift**

La technique LOS est connue aussi sous le nom de (*skewed-load*) (Park et McCluskey, 2008; Savir et Patil, 1993). Cette technique exige que la dernière impulsion de décalage (*shift*) qui lance la transition soit suivie immédiatement par une impulsion rapide de capture pour capturer la réponse du circuit. La deuxième impulsion d'horloge de capture est exécutée à la fréquence de fonctionnement nominale (*at-speed*) du circuit (figure 1.3). Cette technique exige que le signal SE (*Scan Enable*) commute très rapidement *at-speed*, entre le moment de lancement et le moment de capture de l'impulsion d'horloge.

### **1.2.8      Launch on Capture**

La technique LOC, aussi connue sous le nom (*broadside*) (Savir et Patil, 1994), utilise deux cycles de capture consécutifs pour lancer la transition et pour capturer la réponse de sortie du circuit (figure 1.3). Cette technique n'impose aucune exigence de vitesse sur le signal SE, contrairement à la technique LOS. De plus, le cycle de lancement de transition est séparé du cycle de décalage. Une fois que le vecteur de test est chargé (phase de décalage), SE est désactivé. Par la suite, les cycles de lancement et de capture sont appliqués. LOC nécessite plus de vecteurs de test et a une couverture de pannes plus faible par rapport au LOS.

Cependant, LOC est utilisé plus que LOS dans les circuits à grande vitesse vu qu'il n'a pas d'exigence de vitesse sur le signal SE (Park and McCluskey 2008).

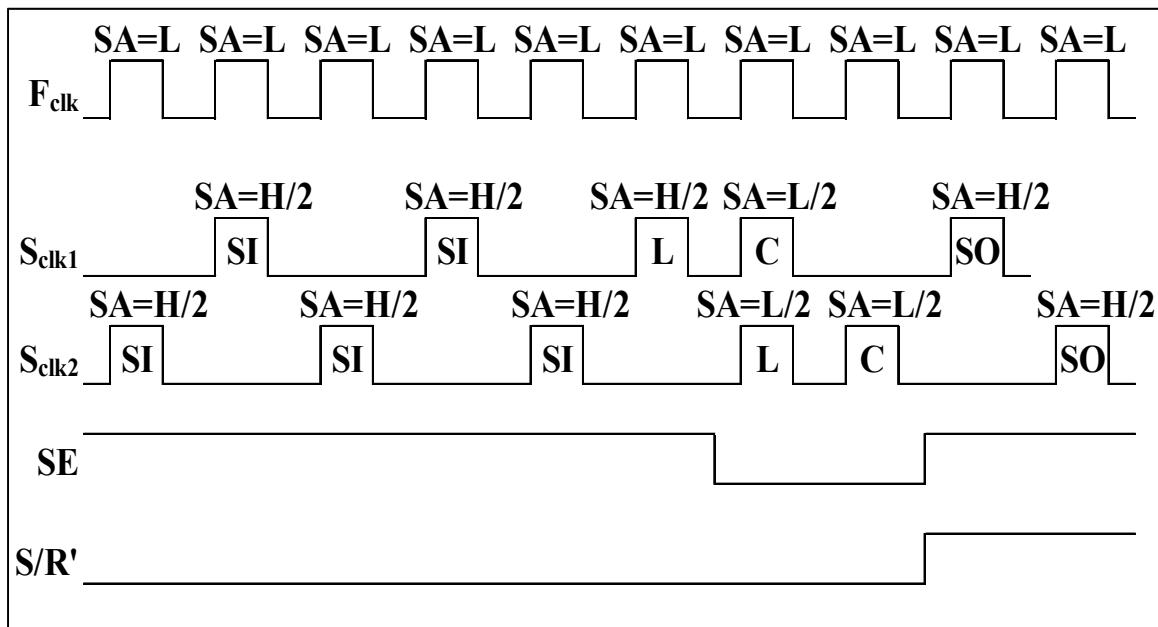

Figure 1.3 Chronogramme des techniques LOS et LOC

Tirée de Xu et Singh (2006)

### 1.3 Circuits intégrés 3D

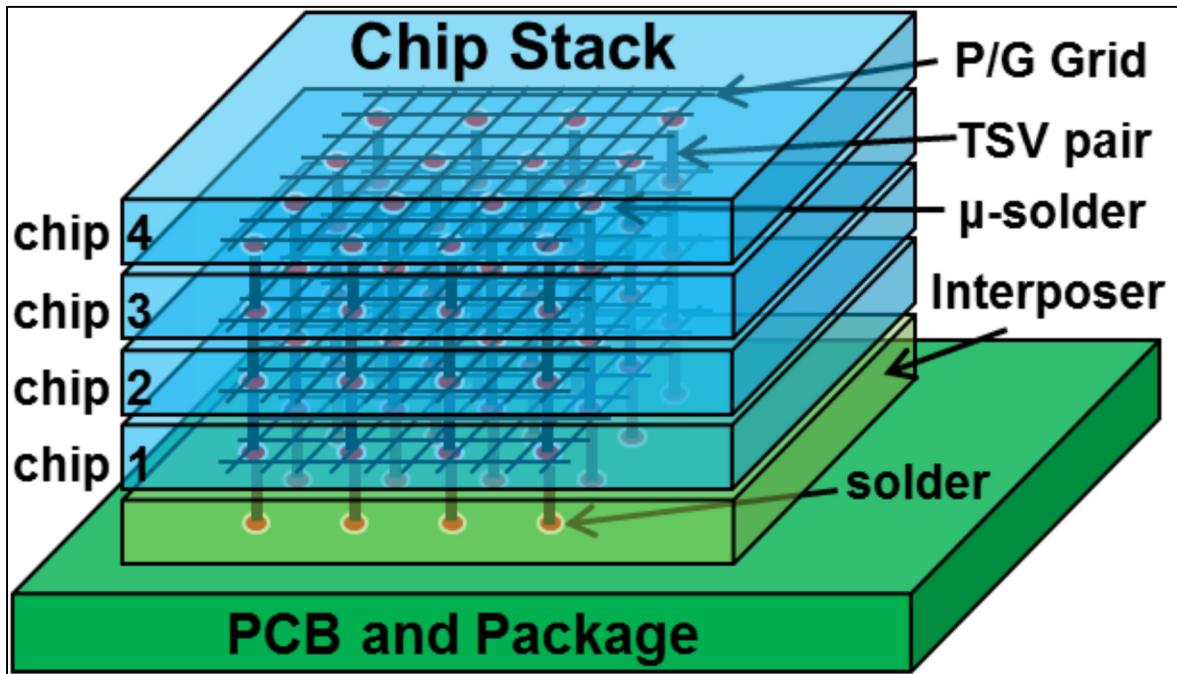

La miniaturisation des transistors et les contraintes de performance des interconnections ont conduit à l'empilage de plusieurs couches de circuits intégrés connu sous le nom d'intégration en 3D. Cet empilement vertical a donné aux concepteurs une fenêtre d'opportunité pour intégrer plus de fonctionnalités dans un seul boîtier (*package*).

L'intégration tridimensionnelle consiste à intégrer des puces et des dispositifs sans se limiter à une seule surface, plus précisément, empiler et connecter simultanément divers technologies et composants fonctionnels pour former des circuits intégrés 3D.

Les circuits intégrés 3D représente une réponse aux limitations définies par les interconnections en empilant plusieurs couches de silicium. Ces couches empilées verticalement conduisent à une réduction de la taille et du nombre d'interconnections. Par

conséquent, ils offrent une augmentation significative des performances et une diminution de la consommation d'énergie. Les circuits intégrés 3D offrent d'autres avantages par rapport aux circuits intégrés 2D (Sharma et Choi, 2014). Ceux-ci incluent :

- plus grande densité d'intégration ;

- zone plus petite (empreinte).

Figure 1.4 Circuit intégré 3D basé sur des TSV

Tirée de He (2015)

L'intégration 3D repose sur des technologies d'interconnexions émergentes. Les CI-3D utilisent des interconnexions verticales pour la communication. Il existe différents types de technologies d'interconnexions verticales comme les microbulles (*microbumps*), les interconnexions sans fil à l'aide d'un couplage capacitif/inductif et les via de silicium (TSV, *Through Silicon Via*). La figure 1.4 montre un circuit intégré 3D utilisant des interconnexions de type TSV. Les TSV sont des interconnexions qui traversent verticalement le silicium pour relier les puces entre elles. (Marinissen et Zorian, 2009) considèrent les TSV comme la technologie la plus prometteuse des CI-3D. Les TSV offrent des liaisons électriques courtes et

à faible perte avec une densité élevée. L'utilisation de TSV offre des avantages fonctionnels, comme la réduction du nombre et de la longueur des fils.

La complexité des circuits intégrés 3D pose des défis pour le test en raison du processus de fabrication de pointe et des limitations d'accès physique. Les problèmes liés au processus de fabrication émergent de plus en plus surtout avec l'augmentation de la vitesse de fonctionnement. Il est nécessaire d'améliorer le processus de test afin d'identifier et éliminer plus de pannes du processus de fabrication et pour garantir une haute qualité de fabrication des puces (Marinissen et Zorian, 2009). Tout comme le test des CI-2D (deux moments de test), le test des CI-3D doit être effectué à la fois au niveau du gaufre (*wafer*) et après l'assemblage et la mise en boîtier. Cependant, il existe de nombreuses étapes de fabrication des CI-3D comme l'empilement des puces et la liaison TSV, qui nécessite plus d'étapes de test. Pour un CI-3D composé de  $n$  puces, il existe  $2n$  moments de test (Marinissen et Zorian, 2009) :

- test des puces juste après leur fabrication (KGD, *Known good die*) ;

- tests intermédiaires à chaque fois qu'une nouvelle puce est empilée (KGS, *Known good Stack*) ;

- test final de produit mis en boîtier.

La variation d'impédance du réseau d'alimentation d'un circuit peut affecter la manière avec laquelle le circuit se comporte en mode test ou en mode fonctionnel. En partant de cette hypothèse, un circuit intégré en 3D a été utilisé comme un cas d'étude de ce projet. En effet, les circuits intégrés en 3D se caractérisent par l'empilement vertical de plusieurs couches de puce. Ce type de circuit peut voir son impédance changer à chaque fois qu'une nouvelle puce est empilée.

## 1.4 Revue de littérature

Les tests de balayage à vitesse nominale (SBAST) sont considérés comme la méthode de test de délai la plus dominante des tests structurels (Moghaddam et al., 2010). Ce type de test vient avec certains inconvénients comme le bruit de tension d'alimentation (PSN, *Power Supply Noise*) produit pendant le mode test et qui diffère de celui induit pendant le mode fonctionnel.

La cause de cette différence est l'augmentation du niveau d'activité de commutation dans le circuit d'un facteur de 3 à 4 pendant les tests SBAST (Arabi, Saleh et Meng, 2007). L'augmentation de la fréquence et la diminution des durées de transition (montée ou descente) des CI provoquent plus d'activité de commutation dans un petit intervalle de temps. Elle entraîne une augmentation de la densité de courant et une chute de tension. Le PSN peut être introduit par des paramètres inductifs ou résistifs, ou par une combinaison des deux. De plus, le schème des techniques SBAST peut aussi conduire à cette différence. En effet, l'horloge de test est composée de deux cycles ; un cycle de décalage fonctionnant à des vitesses lentes suivi par deux impulsions rapides (deuxième cycle) pour lancer et capturer la transition.

Le PSN a été traité par plusieurs chercheurs. Leurs travaux portaient sur la chute de tension d'alimentation. L'effet principal de cette chute est la modification de temps de propagation des signaux. Elle peut conduire au phénomène d'étirement d'horloge de telle sorte que le CUT apparaît plus rapide (Rearick, 2001). Les états de transition et les chutes de tension lors du mode test conduisent à des dégradations des fréquences d'horloges. Ces dégradations sont dues à l'augmentation de l'activité de circuit ainsi qu'à la consommation d'énergie (Rearick, 2001).

L'une des options proposées dans la littérature pour réduire la chute de tension est d'augmenter la longueur de la séquence de lancement ou de capture et d'appliquer les premiers cycles de capture à des vitesses plus lentes. Les techniques les plus pertinentes proposées sont : SeBoS (Lin et al., 2013; Pant et Zelman, 2009), BurstMode (Nadeau-Dostie, Takeshita et Cote, 2008) et PKLPG (Zhang et Walker, 2013).

#### **1.4.1 Sequential Broad Side (SeBoS)**

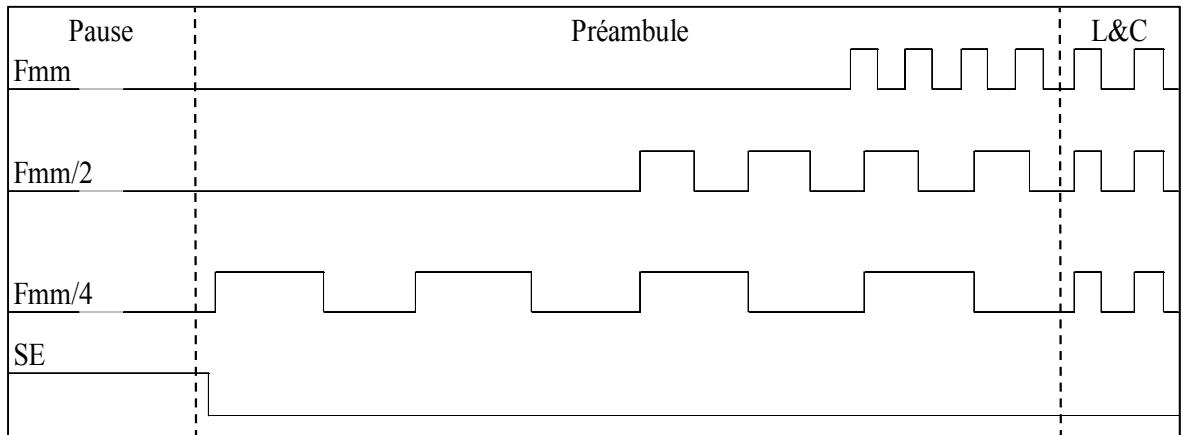

La technique SeBoS consiste à minimiser les conditions de sur test (*over-testing*) de la chute IR (*IR-droop*) et pour éviter les états illégaux de mode fonctionnel. SeBoS consiste à appliquer plusieurs cycles d'une horloge lente, suivis par une phase de lancement et de capture à vitesse nominale pendant les deux derniers cycles. Autrement dit, LOC est étendue à des cycles de lancement et de capture supplémentaires (Liu et al., 2008).

SeBoS a été légèrement modifiée en insérant une pause (temps mort) entre la phase de décalage (*shift-in*) et avant les  $n$  cycles d'horloge lente (Pant et Zelman, 2009) (figure 1.5). Cette pause permet de stabiliser la tension d'alimentation, en laissant au circuit assez de temps pour atteindre un état de repos avant le premier cycle de capture. En effet, lorsqu'un test de délai est lancé, la grille d'alimentation (*power grid*) subit une chute de tension en raison du bruit inductif  $dI/dt$ . Ce bruit force le circuit à performer à des vitesses plus faibles des spécifications fonctionnelles. Les auteurs ont montré que l'application de multiples cycles fonctionnels à mi-vitesse (préambule), avant le cycle de lancement et de capture de la transition, peut minimiser le bruit  $dI/dt$  (de façon à imiter le mode fonctionnel).

Figure 1.5 Chronogramme de la technique SeBoS

Adaptée de Pant et Zelman (2009)

De plus, le centre d'intérêt de leurs expérimentations était relié aux 3 types de chutes de tension d'alimentation : à haute fréquence, à fréquences moyennes et à fréquences faibles. Ils ont montré qu'à haute fréquence, la chute de tension est plus sévère que dans les deux autres cas.

Les auteurs ont utilisé quatre différentes fréquences d'horloge pour les  $n$  cycles d'horloge lente appliquée après la pause en respectant la fréquence du mode fonctionnel ( $F_{mm}$ ) :

- la première fréquence est celle du mode fonctionnel (*at-speed*) ( $F_{mm}$ ) ;

- la deuxième fréquence est à moitié de la fréquence du mode fonctionnel ( $F_{mm}/2$ ) ;

- la troisième fréquence est à un tiers de la fréquence du mode fonctionnel ( $F_{mm}/3$ ) ;

- la quatrième fréquence est à un quart de la fréquence du mode fonctionnel ( $F_{mm}/4$ ).

La technique SeBoS permet d'atteindre un environnement proche à celui du mode fonctionnel. L'activité de commutation du circuit est élargie entre la pause et les premiers cycles de captures. Les auteurs se sont penchés sur le problème de la non représentativité du mode test par rapport au mode fonctionnel et ont proposé la technique SeBoS pour rendre le mode test plus représentatif du mode fonctionnel. Cependant, SeBoS utilise une approche LOC qui augmente la complexité de génération de test et réduit la couverture des pannes de transition. Il a été démontré que le nombre de vecteurs de test requis pour tester les pannes de transition est significativement grand avec LOC. L'augmentation de nombre des vecteurs de test et la perte de couverture de panne sont plus importantes lors de l'ajout de  $n$  cycles à horloge lente (à partir de deux cycles) (Nadeau-Dostie, Takeshita et Cote, 2008).

Pant et Zelman (2009) se sont intéressés à investiguer l'impact de bruit de tension d'alimentation sur le test de délai et la représentativité du mode test par rapport au mode fonctionnel. Mais un aspect bien important a été négligé qui est la variation d'impédance du réseau d'alimentation. Cet aspect a un impact sur le test de délai car il peut influencer les délais de propagation lors du mode test.

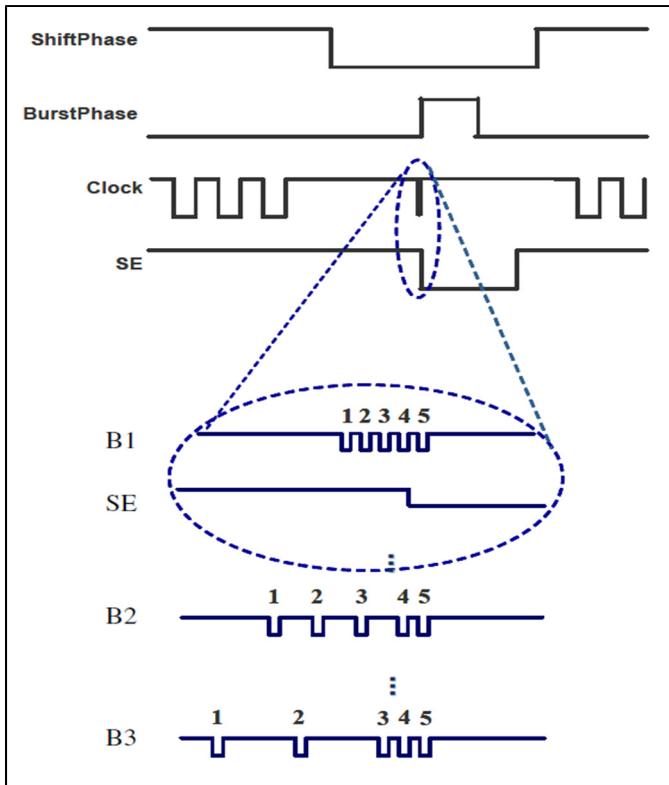

#### 1.4.2      **BurstMode**

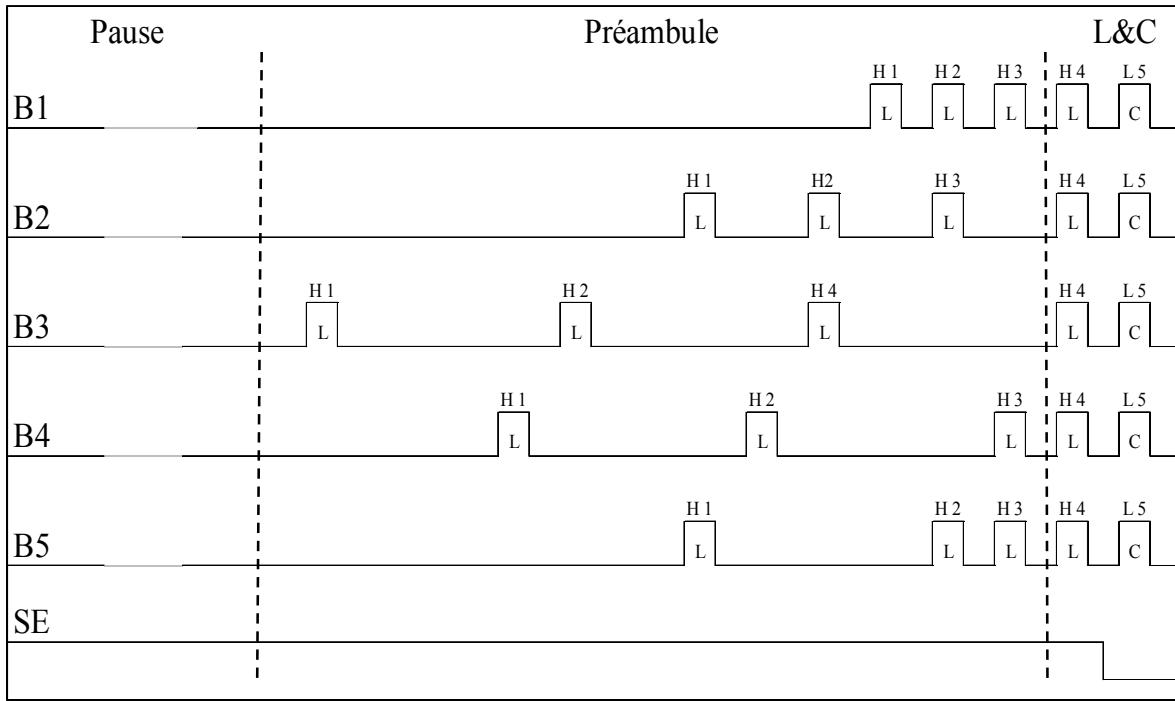

La technique *BurstMode* a été proposée dans (Nadeau-Dostie, Takeshita et Cote, 2008) pour éviter le changement soudain de l'état du circuit entre la phase de shift et la phase de capture. Cette technique utilise une séquence d'impulsions d'horloge (*burst*) pour stabiliser la chute de tension d'alimentation en augmentant progressivement l'activité de commutation de circuits pendant la phase de capture. La technique *BurstMode* permet de contrôler l'activité du circuit et la variation de tension d'alimentation, et d'imiter le mode fonctionnel pendant le SBAST. Les auteurs ont montré qu'il faut utiliser un nombre de *burst* supérieur à deux pour traiter les problèmes liés à la chute IR (*IR-droop*). Un contrôleur programmable d'horloge à *burst* (BCC, *Burst Clock Controller*) est ajouté dans le design pour contrôler la fréquence d'horloge de shift et les *burst*. Le BCC est composé d'un système de conditionnement (*gating*) d'horloge et par une machine d'états finis. Habituellement, la tension d'alimentation a le temps de se stabiliser

au moment des derniers cycles de décalage et de capture, qui sont les plus critiques. Cependant, dans certains cas, les effets  $dI/dt$  induits par la modification soudaine de l'activité du circuit provoquent une baisse de tension d'alimentation dépassant la chute d'IR attendue. Les *burst* peuvent être ralenti par le BCC (sauf pour les deux derniers *burst* de capture) pour permettre une augmentation graduelle de l'activité du circuit et pour réduire les effets  $dI/dt$ .

La figure 1.6 montre un exemple de formes d'onde de la technique *BurstMode*. Le burst B1 se compose de cinq cycles consécutifs à haute vitesse (*at-speed*) appliqués après une phase de décalage et une pause de l'horloge. B2 et B3 sont des exemples où les cycles de shift ont été ralenti. Pour B2, la fréquence des trois premiers cycles de décalage est à la moitié de la fréquence d'horloge du système. Pour B3, les deux premiers cycles sont appliqués à un quart de la fréquence d'horloge du système. Cette technique utilise le schème LOS pour maximiser la couverture des pannes de délai et pour avoir un nombre minimal de vecteurs de test.

La technique *BurstMode* permet de réduire la baisse de la tension d'alimentation de la dernière impulsion de capture. Cependant, elle nécessite des changements au niveau du design pour intégrer le contrôleur BCC. De plus, l'utilisation de LOS rend difficile d'implémenter cette technique à cause de la nécessité d'un signal (SE) rapide pour propager les transitions. De plus, le phénomène de variation d'impédance du PDN n'a pas été pris en considération lors d'expérimentations conduites dans ce projet.

Figure 1.6 Exemple de forme d'onde de la technique *BurstMode*

Tirée de Nadeau-Dostie, Takeshita et Cote (2008)

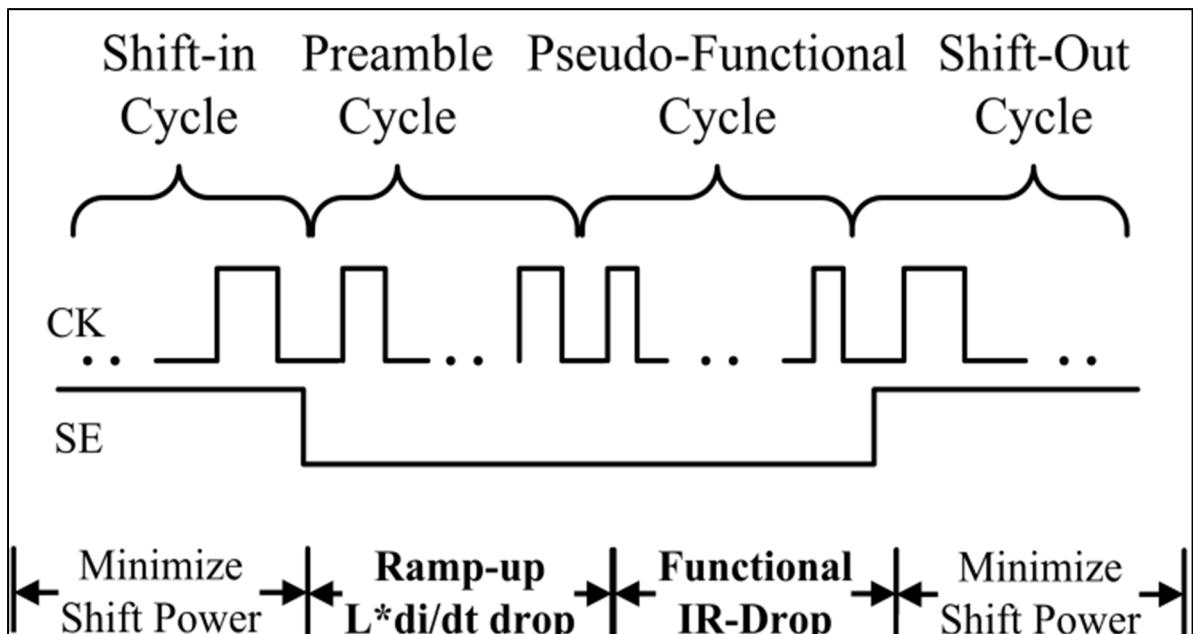

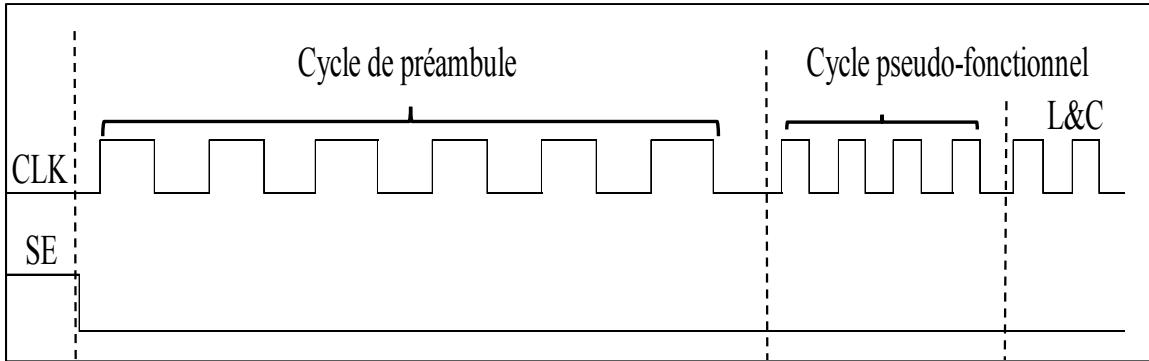

#### 1.4.3 Pseudo-functional K Longest Path per Gate (PKLPG)

La technique de test pseudo-fonctionnel KLPG (PKLPG) a été proposée dans (Zhang et Walker, 2013) pour tester les chemins les plus longs tout en ayant un bruit d'alimentation similaire à celui observé lors du mode fonctionnel.

Les auteurs partent du principe que pendant le passage du mode de balayage au mode fonctionnel (lorsque le signal SE commute) les courants hors puce (*off-chip*) dans la grille d'alimentation atteignent un état de repos. Lorsque les cycles de lancement et de capture à vitesse sont appliqués, la demande de courant augmente. L'inductance hors puce empêche une augmentation soudaine du courant sur les broches du CUT, de sorte que le courant doit être fourni par la capacité de la grille d'alimentation sur puce (*on-chip*). Le phénomène  $dI/dt$  fait

que la grille d'alimentation subit une chute de tension. Cela fait que la puce fonctionne à une vitesse inférieure à la spécification fonctionnelle. La solution à ce problème est d'appliquer un certain nombre de cycles de préambule à moyenne vitesse pour ramener les courants hors puce aux niveaux fonctionnels.

La figure 1.7 montre le schème de la technique PKLPG. Les auteurs affirment que la technique PKLPG a le potentiel d'améliorer de manière significative la qualité du test de délai. PKLPG utilise la technique LOC qui est étendue pour inclure une série de cycles plus lents que les cycles *at-speed* (préambule) avant les cycles de lancement et de capture. Les cycles de préambule filtrent la plupart des états illégaux des vecteurs de test. Le fait que le circuit soit initialisé dans un état proche du mode fonctionnel augmente la corrélation entre le test structurel et le test fonctionnel. Cependant, la technique PKLPG peut souffrir de phénomène de sous-test, puisque l'activité de commutation du CUT diminue rapidement pendant les cycles fonctionnels initiaux. Le PSN observé par le test à vitesse est proche de celui de mode fonctionnel. (Zhang et Walker, 2013).

Figure 1.7 Chronogramme de la technique PKLPG

Tirée de Zhang et Walker (2013)

Cette technique est basée sur un algorithme nommé (iBF, *improved Bit-Flip*) pour maximiser le bruit d'alimentation fonctionnel pendant le test de délai de chemin (*Path delay*). Il combine le basculement aléatoire des vecteurs de test pour contrôler le PSN (Zhang et Walker, 2014).

La technique PKLPG ressemble à la technique SeBoS (la version de (Pant et Zelman, 2009)), en remplaçant la pause par un préambule (style LOC) à plus basse vitesse. Elle a été développée pour le modèle de délai de chemin et elle est limitée à un nombre très restreint de chemins couverts. Encore une fois, l'impact de la variation d'impédance de PDN sur le test a été négligé.

## 1.5 Conclusion

Dans ce chapitre, des concepts de base de test des circuits intégrés permettant la compréhension de projet ont été présentés dans la première partie. Puis, une description brève des circuits intégrés en 3D a été le sujet de la deuxième partie. Une revue de littérature identifiant les techniques pertinentes de test de balayage à vitesse nominale a été le sujet de la troisième partie. En révisant la littérature, nous avons constaté que le phénomène de variation d'impédance de PDN n'était pas étudié ou bien négligé. Cela était la motivation derrière le développement d'une nouvelle technique de test SBAST plus robuste à la variation d'impédance. De plus, les trois techniques citées de test SBAST s'intéressent à l'effet de PSN lors du mode test et à la représentativité du mode fonctionnel par rapport au mode test. Dans ce mémoire, nous allons montrer que la variation d'impédance du PDN amplifie le problème de la non-représentativité du mode test par rapport au mode fonctionnel.

## CHAPITRE 2

### MODÈLES DE SIMULATION ET EXPÉRIMENTATIONS PRÉLIMINAIRES

#### 2.1 Introduction

Ce chapitre présente les différents modèles utilisés pour estimer les délais de propagation lors du mode test et du mode fonctionnel. La première partie décrit le modèle du réseau de distribution d'alimentation d'un circuit intégré 3D. La deuxième partie décrit le circuit de mesure de délai. La troisième partie présente les premiers résultats obtenus après une simulation AC et la dernière partie, une première série de résultats résultant d'une analyse transitoire du circuit en mode fonctionnel.

#### 2.2 Modèle du réseau de distribution d'alimentation (PDN)

Un réseau de distribution d'alimentation est habituellement composé d'un module de régulation de tension (VRM, *Voltage Regulator Module*), d'un circuit imprimé (*board*), d'un boîtier (*package*) et d'une puce. Le schéma fonctionnel d'un réseau de distribution d'alimentation est présenté sur la figure 2.1.

Figure 2.1 Schéma fonctionnel d'un réseau de distribution d'alimentation

Adaptée de Vaisband et al. (2016)

La fonction du module de régulation de tension est de maintenir un niveau de tension typique. Le circuit imprimé (*board*) comporte des broches métalliques pour alimenter le boîtier. L'alimentation entre dans le boîtier par ces broches d'alimentation et les broches de la masse.

L'alimentation passe à l'intérieur du boîtier et finalement à la puce à travers des fils de liaison métalliques (Vaisband et al., 2016).

Le PDN est composé de deux parties :

- un PDN hors puce qui inclut le VRM, le circuit imprimé et le boîtier, modélisés via des réseaux RLC;

- un PDN sur-puce qui comprend le modèle du réseau RLC de la puce connectée au boîtier.

### 2.2.1 Réseau de distribution d'alimentation utilisé

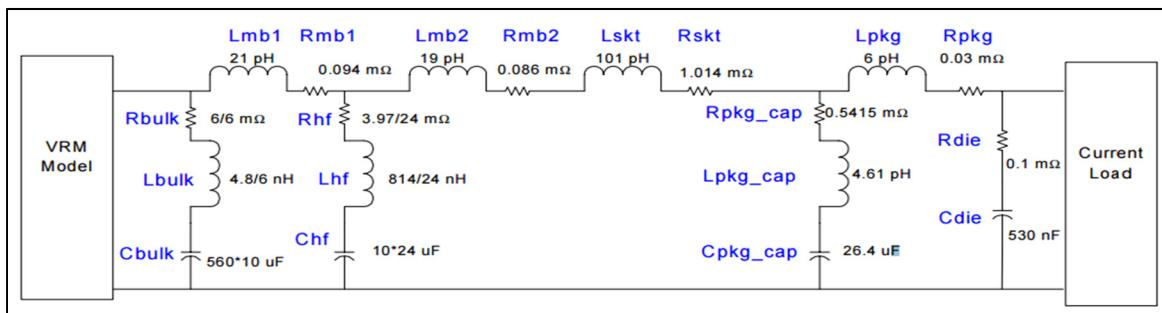

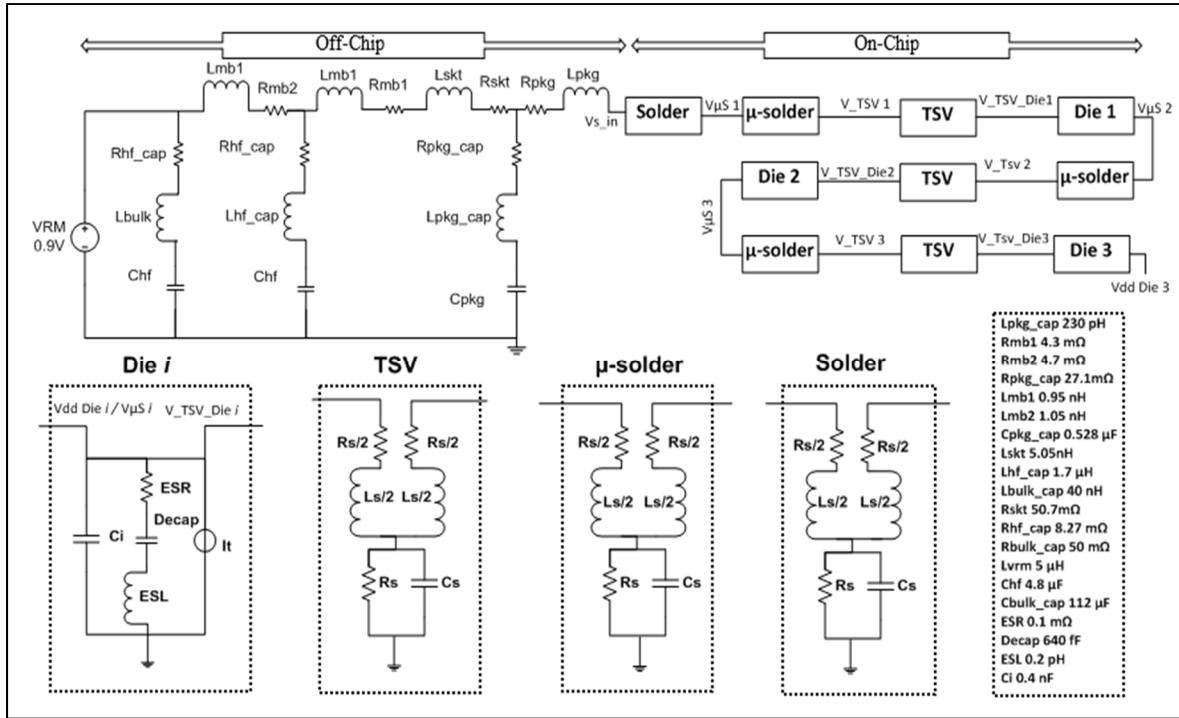

Des simulations HSPICE ont été établies dans ce travail afin de mesurer l'impact de la variation d'impédance de PDN sur la marge de délai. Nous avons utilisé un modèle PDN d'un CI-3D comme cas d'étude. Les simulations sont basées sur un modèle RLC du réseau de distribution d'alimentation tiré de (He, Gu et Lu, 2014).

#### 2.2.1.1 PDN hors-puce

Le modèle PDN hors puce est une version RLC du processeur Pentium IV (Figure 2.2) modifié par He, Gu et Lu (2014). Cette modification a été faite pour que le courant total supporté par le PDN hors puce soit ajusté avec la taille de la puce modifiée en fonction de la consommation de courant et de la taille de la puce. Les valeurs des résistances, des capacités et des inductances ont été modifiées en fonction de la taille de la puce ou de la consommation de courant du circuit (He, 2015).

Figure 2.2 Modèle PDN du processeur Intel Pentium IV

Tirée de Intel (2002)

### 2.2.1.2 PDN sur-puce

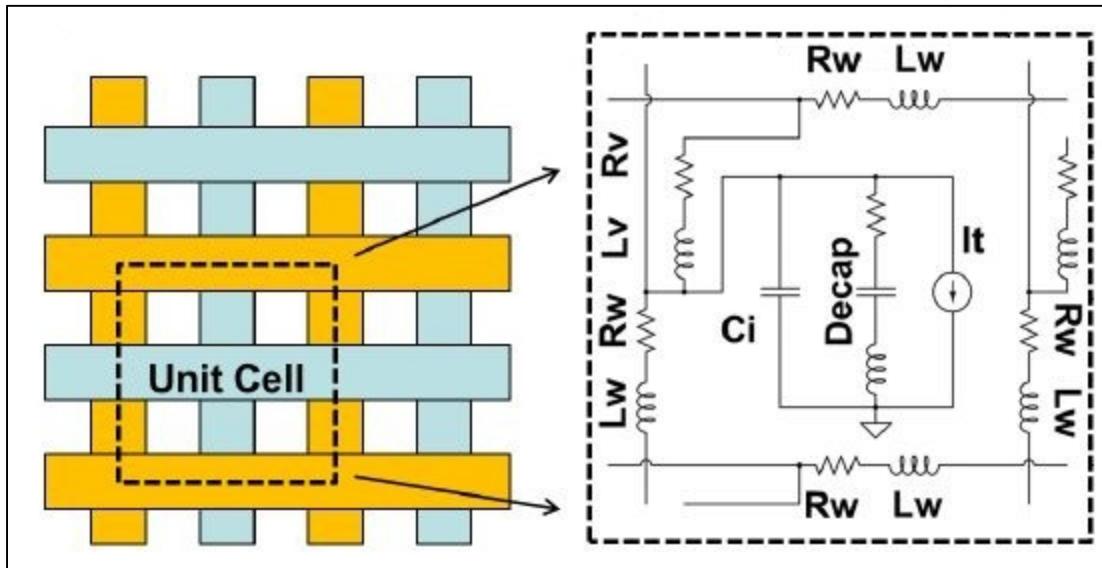

Figure 2.3 Cellule unitaire de la grille P/G sur-puce et le modèle de circuit équivalent correspondant

Tirée de He, Gu et Lu (2014)

La figure 2.3 illustre une cellule unitaire de la grille d'alimentation sur-puce. Le PDN sur-puce contient des cellules unitaires composées de capacités de découplage (Decap), de résistances et inductances de fils et de via, une charge de courant ( $I_t$ ) et une capacité ( $C_i$ ). La résistance parasite et l'inductance du Decap sont respectivement modélisées par une résistance série équivalente (ESR) et une inductance série équivalente (ESL) (He, Gu et Lu, 2014). Une seule cellule unitaire peut représenter une puce. Pour plus de détails sur la caractérisation et l'analyse du PDN, nous référons le lecteur à la thèse d'He (2015).

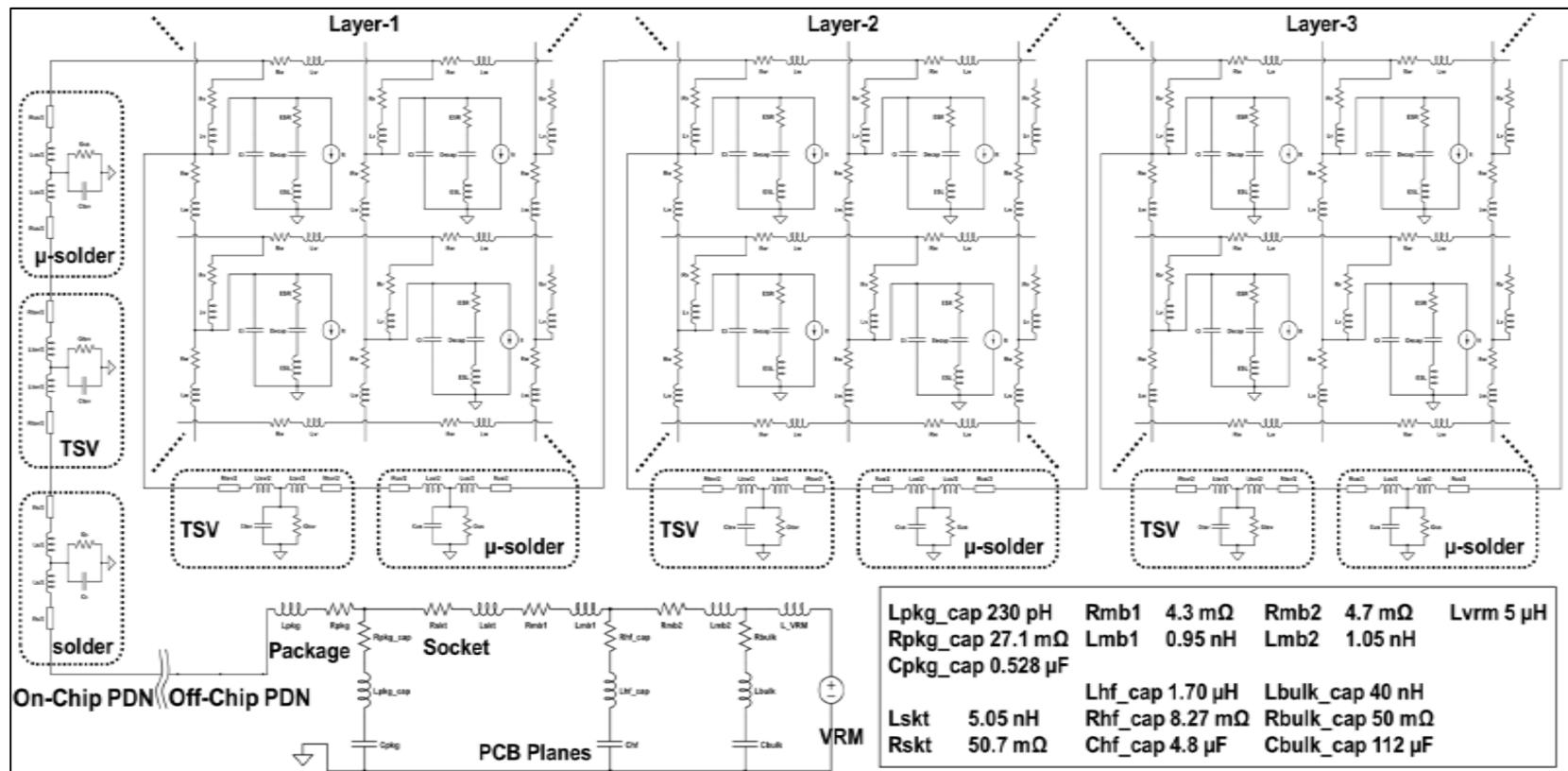

### 2.2.2 Modèle équivalent du PDN complet

Le modèle équivalent du PDN complet est composé de plusieurs puces identiques (trois puces dans ce projet). Ces puces sont empilées face vers le bas (*face to down*) par l'intermédiaire d'interconnections TSV, de microbilles et de microsoudures (*micro-solder*). Le modèle original (Annexe I) a été un peu modifié pour répondre à nos besoins.

La figure 2.4 montre le modèle PDN équivalent utilisé dans ce travail ainsi que les valeurs de ces composants. Le modèle adapté est composé d'un PDN hors puce et d'un PDN sur-puce utilisant des composants regroupés. Le VRM est modélisé en tant que source de tension délivrant 0.9 V aux nœuds.

Figure 2.4 Modèle équivalent PDN du CI-3D avec trois puces

Adaptée de He, Gu et Lu (2014)

Dans le modèle original, He, Gu et Lu (2014) utilisent une source d'impulsion de courant, remplacée ici par une charge de courant DC pour pouvoir connecter le PDN à la ligne de délai ainsi qu'au réseau de distribution d'horloge. Les résistances et les inductances des fils reliant les différentes couches de puce ont été négligées. Finalement, une seule cellule unitaire a été utilisée pour la modélisation de chaque puce.

## 2.3 Description des simulations HSPICE

Pour la validation de l'hypothèse de ce projet, des simulations HSPICE ont été effectuées. Un circuit de mesure de délai connecté au modèle PDN a été simulé avec une librairie de cellules et des transistors basés sur une technologie CMOS 90 nm.

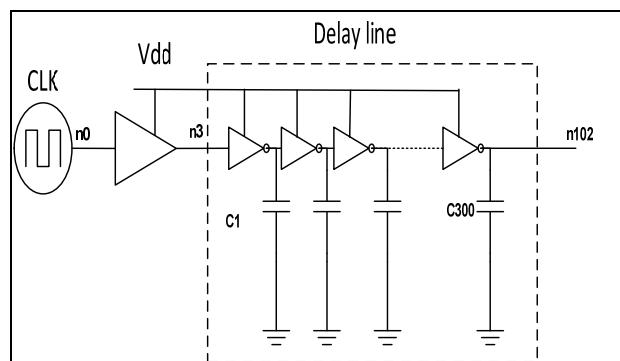

### 2.3.1 Circuit de mesure de délai

Le circuit de mesure de délai est composé d'un réseau de distribution d'horloge (RDH) connecté en parallèle à une ligne de délai.

Le modèle de ligne de délai utilisé dans les simulations a été conçu et validé pour qu'il corresponde au réseau de distribution d'horloge d'un FPGA (Xilinx Spartan 3). Ce modèle est constitué de 300 étages comportant chacun un inverseur et une capacité. Le nombre d'étages est ajusté pour l'obtention d'un délai de 95 % de la période d'horloge. La figure 2.5 présente le circuit de mesure de délai utilisé dans ce mémoire.

Figure 2.5 Circuit de mesure de délai

Tirée de Thibeault et Louati (2017)

Le réseau de distribution d'horloge, représenté par un seul amplificateur (*buffer*) à la figure 2.5, est composé de 2,5 lignes. Chaque ligne est constituée de 12,75 branches et chaque branche contient 3 amplificateurs connectés en série (Thibeault et Louati, 2017).

Le nombre de lignes choisi permet de pouvoir respecter le rapport entre un niveau haut d'activité de commutation du circuit (représentatif de la phase de chargement d'un vecteur de test dans le registre à balayage) et un niveau bas de l'activité de commutation du circuit (représentatif du mode de fonctionnement normal du circuit). La valeur 2,5 de ce rapport,  $R_{H/L}$ , a été choisie en fonction deux paramètres importants :

- la proportion de la puissance dynamique du réseau de distribution d'horloge ( $P_{DP CDN}$ ) : Jairam et al. (2008) ont montré que le réseau de distribution d'horloge consomme de 30 % à 50 % de la puissance dynamique totale d'une puce;

- le rapport de l'activité de commutation des bascules du circuit ( $R_{FFSA}$ ) du mode test sur celle du mode fonctionnel : Arabi, Saleh et Meng (2007) ont montré que l'activité de commutation est typiquement 3 à 4 fois supérieure à celle du mode fonctionnel (le rapport  $R_{FFSA}$  est compris entre 3 et 4).

De plus, la valeur 2,5 correspond, dans une première approximation, à différents cas réalistes :

- $P_{DP CDN} = 50\%$  et  $R_{FFSA} = 4$ ;

- $P_{DP CDN} = 40\%$  et  $R_{FFSA} = 3,5$ ;

- $P_{DP CDN} = 33\%$  et  $R_{FFSA} = 3,25$ .

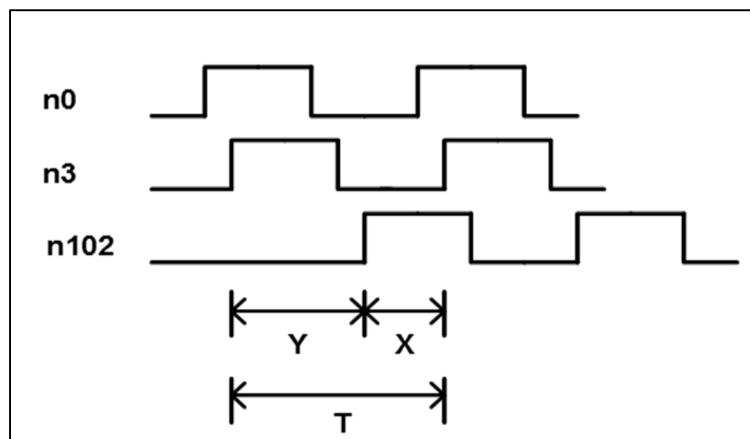

### **2.3.2 Principe de fonctionnement du circuit de mesure de délai**

Rappelons que l'un des objectifs de ce projet est d'examiner l'influence de la variation d'impédance sur les délais de propagation. Pour ce faire, un circuit de mesure de délai a été utilisé (figure 2.5). Ce qui suit décrit le principe de fonctionnement de ce circuit.

Le signal d'horloge (CLK) est connecté au RDH, sur le nœud n0. Le RDH est activé par le front montant du signal d'horloge. La période effective du signal d'horloge est définie en regardant la montée du signal au point final du RDH (n3). Chaque fois que le signal traverse un inverseur de la ligne de délai à partir du nœud n3, un délai s'y ajoute. Le premier coup d'horloge qui arrive à n3 se propage dans la ligne de délai et sera comparé au premier front montant du signal du nœud n102. Cette comparaison permet de mesurer le délai de propagation

nommé Y sur la figure 2.6. Y représente le délai de propagation le long de la ligne à délai, du nœud n3 au nœud n102. X est la marge de synchronisation de délai entre l'arrivée d'une transition à la fin de la ligne de délai (n102) et l'arrivée de la prochaine impulsion d'horloge au nœud n3. Autrement dit, X est la différence entre le premier front montant du signal sur le nœud n102 et le deuxième front montant du signal sur le nœud n3.

Figure 2.6 Mesure des délais

## 2.4 Simulations préliminaires

### 2.4.1 Cas d'étude

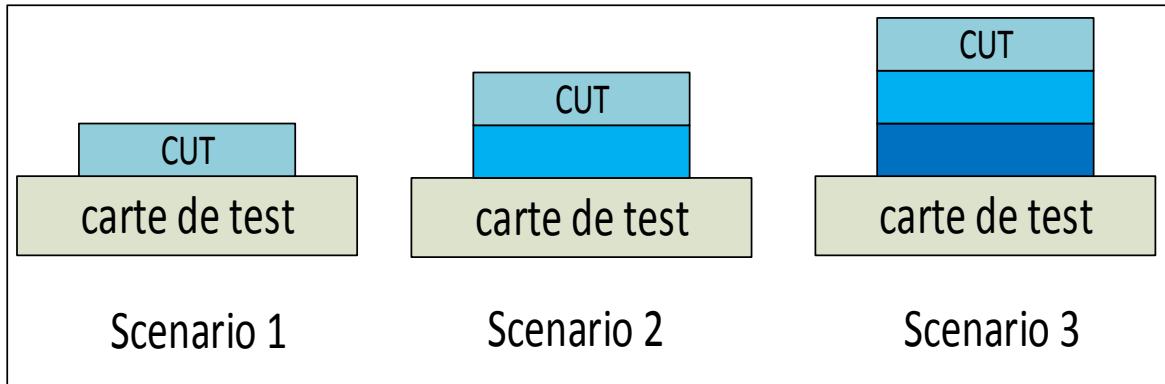

Ce travail a étudié l'impact de la variation d'impédance sur le test en changeant le nombre de puces du PDN. Autrement dit, nous voulions étudier l'effet de la variation d'impédance dans différents scénarios d'encapsulation 2D/3D. Trois scénarios ont été considérés :

- **scénario 1 (S1)** : CUT composé d'une seule puce (l'équivalent d'un CI-2D);

- **scénario 2 (S2)** : CUT composé de deux puces;

- **scénario 3 (S3)** : CUT composé de trois puces.

La figure 2.7 montre les trois scénarios simulés. Pour ces trois cas de figure, seulement la puce de haut est connectée au circuit de mesure de délai. Pour les trois scénarios, les puces empilées

sont identiques. Par exemple, pour le scénario 3 la broche (Vdd Die 3) du PDN (figure 2.4) est connectée à la broche Vdd du circuit de mesure de délai (figure 2.5).

Figure 2.7 Scénarios étudiés lors des simulations

#### 2.4.2 Simulation AC

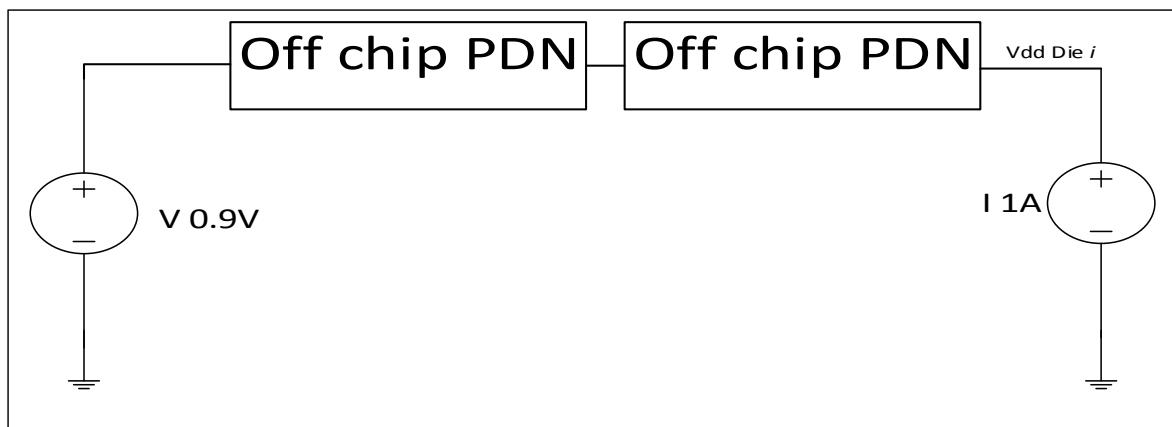

L’analyse du comportement AC du circuit a permis d’obtenir une première série de résultats. Le but de cette analyse est de déterminer les fréquences de résonance du circuit pour les trois scénarios. Dans HSPICE, l’impédance du PDN peut être simulée au moyen de la définition de l’impédance (équation 2.1) : le rapport de tension par rapport au courant.

$$\text{Impedance } (\Omega) = \frac{V}{I} \quad (2.1)$$

La figure 2.8 montre un modèle PDN simplifié pour la simulation d’impédance. Une source de courant DC est connectée au port Vdd die  $i$  ( $i$  est l’indice du nombre de puces utilisées) du modèle PDN (figure 2.4). La valeur du courant total  $I$  a été choisie égale à 1 A de sorte que la tension simulée sur un port de tension (Vdd Die  $i$ ) donne directement la valeur d’impédance.

Figure 2.8 Modèle PDN simplifié pour la simulation d’impédance

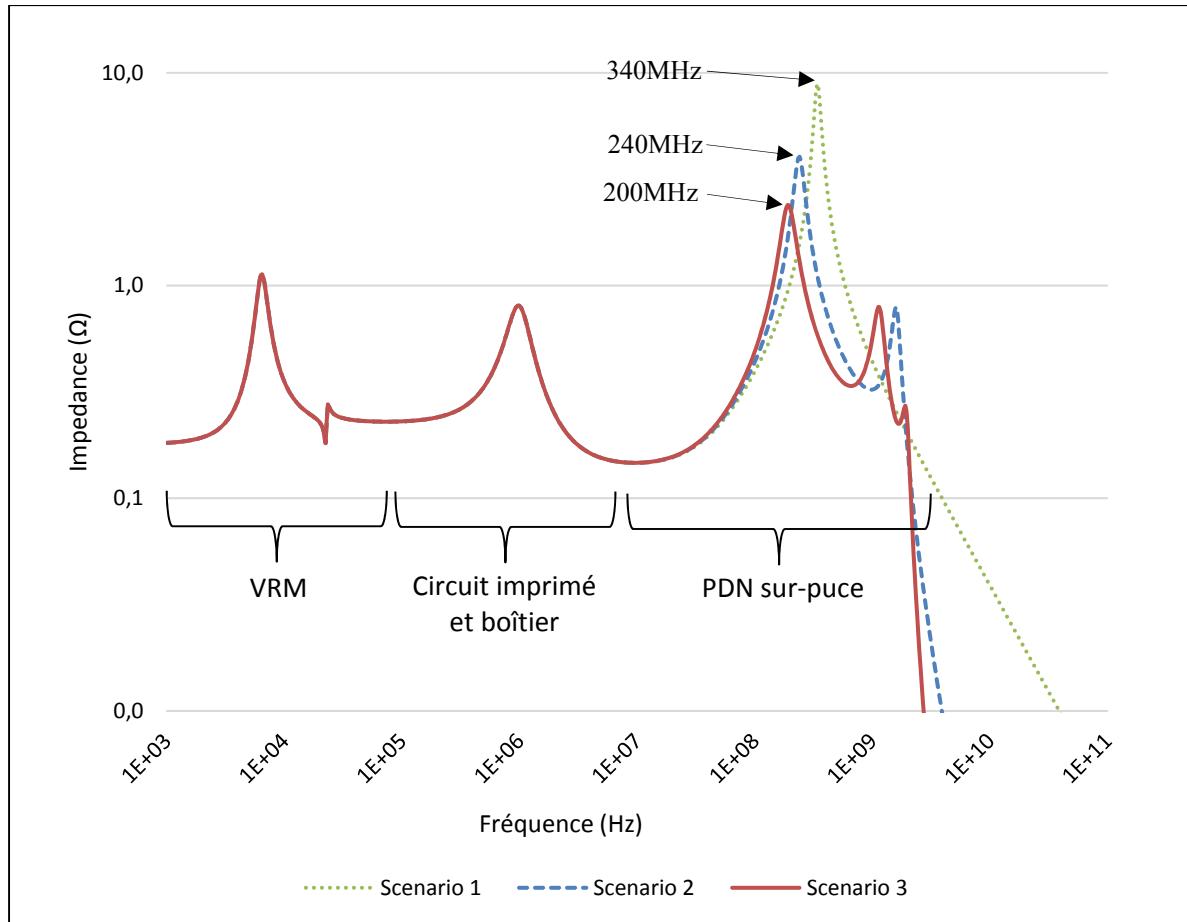

La figure 2.9 trace l’impédance du modèle PDN des trois scénarios. Elle montre différentes zones de fréquence. Le module de régulateur de tension (VRM) a des fréquences de réponse dans la gamme des kHz, ce qui est beaucoup plus faible que les fréquences de PDN complet. L’impédance du circuit imprimé (*board*) et le boîtier (*package*) se situent dans la zone des MHz. Le PDN sur puce couvre la gamme de fréquences supérieures à 100 MHz. Cette figure montre aussi les trois pics de résonance associés aux trois scénarios (zone de PDN sur-puce). Le circuit avec une puce (scénario 1) a une fréquence de résonance égale à 340 MHz, le circuit à 2 puces (scénario 2) une fréquence de résonance de 240 MHz et 200 MHz pour le circuit à 3 puces (scénario 3). Cette figure montre que le pic d’impédance se déplace vers des fréquences plus basses lorsque le nombre de puces augmente.

Figure 2.9 Impédance simulée du PDN 3D pour les 3 scénarios considérés

Adaptée de Thibeault et Louati (2017)

### 2.4.3 Mesure de délai en mode fonctionnel

#### 2.4.3.1 Résultats de mesure

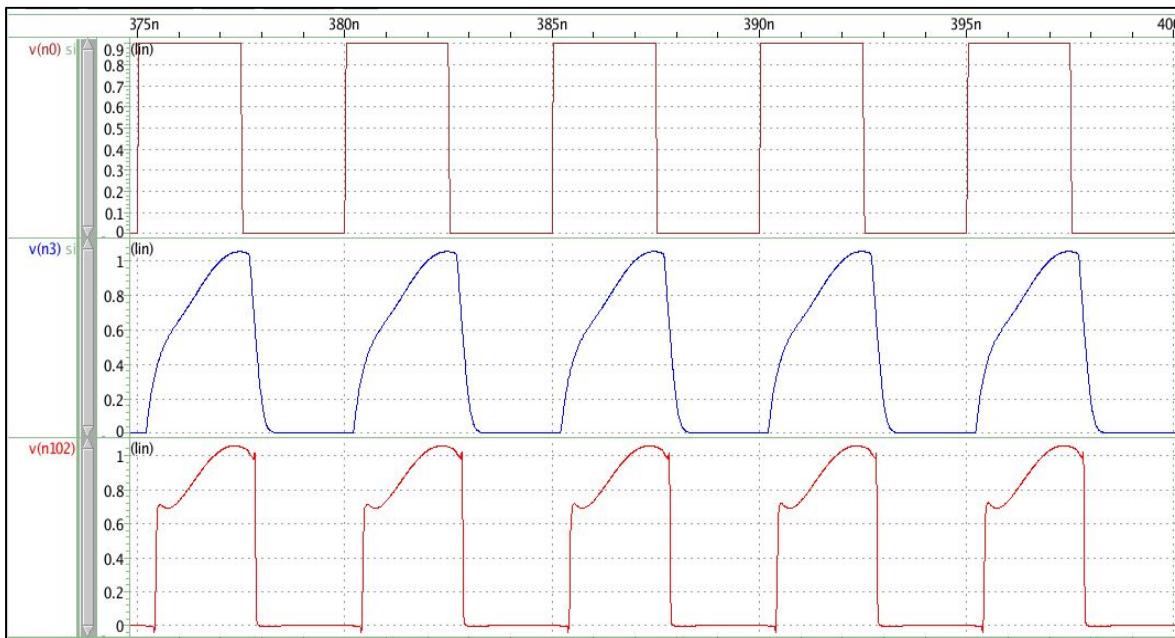

Cette partie présente les résultats de simulation des mesures de délai en mode fonctionnel. Pour ce faire, une analyse transitoire a été simulée avec HSPICE. Elle a permis de calculer la marge de synchronisation de délai X et le délai de propagation Y. Une fenêtre de 400 ns a été utilisée pendant ce mode. Cette fenêtre permet d'acquérir des états stables tout en gardant le temps de simulation dans des marges acceptables.

La figure 2.10 trace les formes d'onde des signaux n0, n3 et n102 (du haut en bas) pendant le mode fonctionnel (5 dernières périodes). Ces formes d'onde résultent d'une simulation à 200 MHz et avec le scénario S1.

Figure 2.10 Exemple de forme d'onde générée par HSPICE du scénario S1 à 200 MHz en mode fonctionnel

Le tableau 2.1 présente les mesures des délais du modèle PDN pour les 3 scénarios S1, S2 et S3. Cette simulation a été faite avec un seul domaine d'horloge. Les résultats ont été obtenus par variation de la fréquence du circuit en mode fonctionnel. La première ligne de tableau présente les fréquences de fonctionnement utilisées (178, 200, 213, 228, 240, 265, 316, 340, 400 et 680 MHz). Les valeurs  $Y_{mm}$  représentent les délais de propagation du signal d'horloge. Les valeurs  $X_{mm}$  représentent les valeurs de la marge de synchronisation (figure 2.6); elles représentent la marge minimale observée pendant les 50 dernières périodes d'horloge de la fenêtre de stabilisation choisie (400 ns d'activité en mode fonctionnel). De plus, toutes les simulations de mesure (X et Y) ont été effectuées lorsque les signaux d'horloge sur les nœuds n3 et n102 de la figure 2.6 atteignaient la valeur de tension  $Vdd/2$ .

Tableau 2.1 Mesure de délai de propagation en mode fonctionnel avec les trois scénarios

| <b>F<sub>mm</sub> (MHz)</b> |                            | 178  | 200  | 213  | 228  | 240  | 265  | 316  | 340  | 400  | 680   |

|-----------------------------|----------------------------|------|------|------|------|------|------|------|------|------|-------|

| <b>S1</b>                   | <b>Y<sub>mm</sub> (ns)</b> | 5,50 | 4,76 | 4,56 | 3,92 | 3,69 | 3,36 | 3,12 | 2,54 | 2,60 | 1,5   |