# New Circuits for Time-Domain Signal Processing in Low-Voltage CMOS

by

# Soheyl ZIABAKHSH SHALMANI

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, "NOVEMBER 1, 2018"

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

#### THIS THESIS HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS:

Prof. Ghyslain Gagnon, Thesis Supervisor Department of Electrical Engineering, École de technologie supérieure

Prof. Gordon W. Roberts, Thesis Co-supervisor Department of Electrical and Computer Engineering, McGill University

Prof. Jérémie Voix, President of the Board of Examiners Department of Mechanical Engineering, École de technologie supérieure

Prof. Frédéric Nabki, Member of the jury Department of Electrical Engineering, École de technologie supérieure

Prof. Mohamad Sawan, External Independent Examiner Department of Electrical Engineering, École Polytechnique, University of Montreal

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON "SEPTEMBER 5, 2018"

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my deepest gratitude and respect to my supervisor, Professor Ghyslain Gagnon, for his never ending guidance, encouragement, and support both on a professional level and a personal level through the years we worked together. Thank you for accepting me as your Ph.D. student at ÉTS. It has been an absolute pleasure for me to work with you, and I have truly appreciated your constructive comments throughout my Ph.D. studies. Thank you for giving me all the freedom to pursue my research topic and sharing your thoughts and concern. I wish to acknowledge the Natural Sciences and Engineering Research Council of Canada (NSERC) for their outstanding financial support to Professor Ghyslain Gagnon.

I wish to acknowledge and thank my co-supervisor, Professor Gordon W. Roberts, for all of his tremendous and kind-hearted support over the years that I worked in his Lab. I greatly appreciate for all of the intellectual discussions that we had about my research topic, and I am extremely grateful for all the questions and challenges at every step of my work to give my best. Research discussions with you have always been interesting for me. Thank you very much for patiently reading my papers and sharing your own experiences to help me succeed in my work.

I would also like to thank my Ph.D. committee members, Professor Mohamad Sawan, Professor Frédéric Nabki, and Professor Jérémie Voix for their critical and constructive feedback on this research.

A big thank you to my wife Hasti for her extraordinary love and confidence in my ability to succeed. This thesis would not have been possible without her unwavering support and patience.

I would like to especially thank my parents Zinat and Bahman, my brother Saman, and my families who never hesitate to support me during this journey. Your unconditional love and

support during all the years have been my unique motivation to move forward regardless of setbacks.

I would like to thank Mr. Mohammad Honarparvar for his intuitive and lengthy discussions we had in my first two years at ÉTS. Thank you for your help and encouragement. I hope that we can continue to work on analog and mixed-signal circuit design for the years to come. I would also like to thank Mr. Mohamed Ali who engaged in interesting discussions about the layout design. Thank you very much Mohamed Ali. Without your help, I wouldn't have finished the Layout before the deadline.

Last but not least, I want to thank my friends at LACIME, ÉTS and VLSI, McGill. I have been extremely lucky to be surrounded by a inspiring and brilliant colleagues that have commented on my research work and making our Lab a nice place to study. In particular, thank you to Hassan Mousavi, Mehdi Mozayan, Amir Shahshahani, Moataz Abdelfattah, Ahmed Kira, Mahmood Mohammed, Ahmed Emara.

I dedicate this work to my parents and my wife.

# LES NOUVEAUX CIRCUITS POUR LA TRAITEMENT DE SIGNAL DANS LE DOMAINE TEMPOREL SUR DES CMOS DE BASSE TENSION

#### Soheyl ZIABAKHSH SHALMANI

#### **RÉSUMÉ**

Le dimensionnement agressif des technologies CMOS dans des procédés inférieurs à 100 nanomètres est la motivation de remplacer des circuits de traitement de signal en mode-tension et en mode-courant par des approches en mode temporel qui utilise des circuits numériques pour réaliser le traitement de signal. Puisque la différence de temps entre deux signaux est indépendante de leur amplitude, intuitivement, une représentation des signaux en mode temporel (« time-mode » ou TM) est censée d'être plus compatible avec les nouveaux procédés CMOS qui opèrent à des niveaux d'alimentation plus faibles. L'objectif des concepteurs de circuits TM et des chercheurs est d'identifier des nouvelles architectures de circuits pouvant exécuter l'opération élémentaire de traitement de signaux comme des additions, des soustractions, des multiplications, etc. Au cœur de ces efforts est la nécessité d'identifier des circuits TM qui pouvant exécuter ce type d'opération à de hauts niveaux de performance; le niveau qui est égal ou supérieur des circuits en mode-tension (VM) à des niveaux de puissances similaires.

Dans la première partie de la thèse, une revue exhaustive de la littérature est présentée. La revue inclut les spécifications des convertisseurs analogique-numérique-(ADC) et tous les développements majeurs dans le domaine des convertisseurs  $TM\Delta\Sigma$  au cours de la dernière décennie. Ensuite, nous présentons une comparaison rigoureuse des circuits TM discrets aux circuits TM continus afin d'identifier les lacunes qui à besoin d'être rempli. Comme première contribution, nous proposons une expression analytique pour l'effet de bruit sur la grille de retard de transistors TM0S-NMOS de TM1 et TM2, menant à l'expression du pic-SNR des deux architectures. La théorie proposée sur le bruit est appliquée à différent procédés TM3 et comparés dans Spectre. En plus, nous fournissons l'implémentation du TM3 avec les résultats de mesuré pour vérifier les résultats de l'analyse.

Ensuite, comme seconde contribution, nous proposons des nouveaux sous-systèmes TM et une extension de certaines ancienne architectures diminuant les défis associés aux technologies CMOS modernes, sans affecter les métriques de performances. Le premier défi est la nécessité de délais d'une demi-période et d'une période complète pour les circuits TM, le second défi est le besoin pour les circuits TM d'effectuer des opérations arithmétiques de base (c.-à-d., addition ou soustraction) dans une large gamme linéaire et le troisième défi est de trouver comment réaliser une rétroaction négative dans le domaine du temps et le processus des signaux de haute fréquence autour de la fréquence intermédiaire (IF).

Comme troisième contribution, nous présenterons une réalisation complétement numérique d'un résonateur basé en intégrateur discret sans perte (LDI) en mode TM. Le résonateur est construit avec des sous-systèmes TM dans une configuration de rétroaction négative. Ce résonateur accomplit du traitement de signal en mode temporel de haute vitesse sans les limitations imposées par des techniques de circuits par commutation du condensateur (SC), tel que

des adaptations de condensateur pour réaliser des gains de signaux précis. La précision du circuit proposé est plutôt assurée par un circuit de délai adaptatif ajustant le délai de boucle dans une large bande de fréquence d'échantillonnage. L'opération du résonateur basé sur LDI du TM est validée avec des simulations au niveau du transistor et comparée au niveau système dans Simulink/MATLAB.

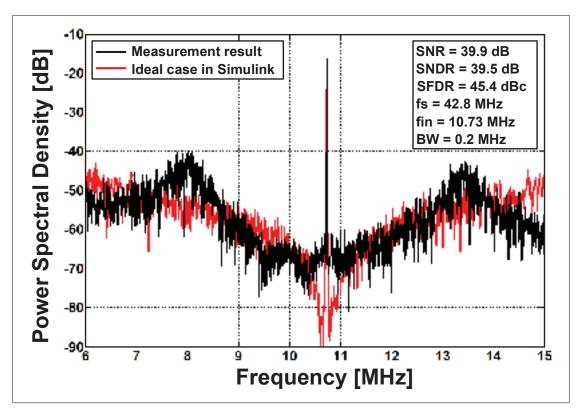

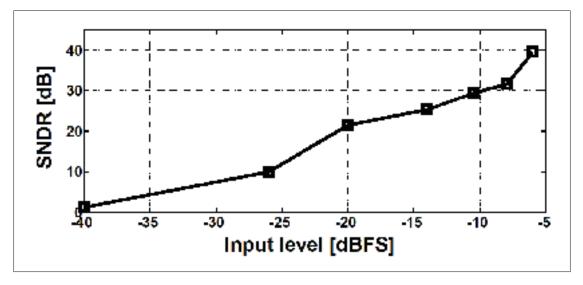

Finalement, nous proposons une nouvelle BPΔΣTDC hautement digital pour des applications IF. Dans un premier temps, l'architecture de la conception proposée est présentée; ainsi que la présentation les performances métriques attendu. Le BPΔΣTDC est capable de modeler le bruit de quantification dans une configuration à rétroaction négative, et n'exige aucun circuit complexe de calibration pour compenser des erreurs de synchronisation. En outre, pour la première fois dans les TMSP, une compensation « direct feed-forward » est utilisée dans un circuit TDC pour atteindre un grand rapport signal sur bruit et rapport de distorsion (SNDR). Nous démontrons le circuit TDC proposé dans le procédé CMOS 130nm d'IBM pour une tension d'alimentation aussi basse que 1.2 V. Une gamme de fréquence d'échantillonnage continue de 4 MHz à 42.8 MHz est réalisée pour numériser un signal centré à un quart de la fréquence d'échantillonnage. Cette conception atteint un sommet de SNDR de 39.5 dB sur une bande passante de 0.2 MHz pour une fréquence d'échantillonnage maximale de  $f_s$ =42.8 MS/s tout en consommant une puissance moins faible que 5 mW. De plus, nous identifions des orientations de recherche futures pour des conceptions de circuits en TM et dans la réalisation d'ordre élevé de BPΔΣTDC pour recherche.

**Mots-clés:** Retard adaptatif, convertisseur de Numérique-à-Temps, VCDU à deux fronts, unité de retard de demi période, gigue de phase, intégrateur discret sans perte, rétroaction négative en mode temporel, mise en forme du bruit, BPΔΣTDC de deuxième ordre, unité de commutation de retard, synchronisation, amplificateur de différence de temps, cellule de mémoire TM, mode Tension.

# NEW CIRCUITS FOR TIME-DOMAIN SIGNAL PROCESSING IN LOW-VOLTAGE CMOS

#### Soheyl ZIABAKHSH SHALMANI

#### **ABSTRACT**

Aggressive scaling of CMOS technology in sub-100 nm process motivates the replacement of voltage or current-mode signal processing with time-mode approaches which uses digital circuits to perform signal processing. As the time difference between two signals is independent of the amplitude of either signal, intuitively, a time-mode (TM) signal representation is believed to be more compatible with newer CMOS processes that operate at lower power supply levels. It is the objective of TM circuit architects and researchers to identify new circuit architectures that can perform basic signal processing operations such as adding, subtracting, multiplications, etc. At the heart of these efforts is the need to identify TM circuits that perform such operation at high performance levels; levels that equal or exceed those of voltage-mode (VM) circuits at similar power levels.

In the first phase of this thesis, an intensive review of the literature is presented. The review includes  $\Delta\Sigma$  analog-to-digital converter (ADC) specifications and all the major developments in the area of  $TM\Delta\Sigma$  converters in the last decade. Then we present a rigorous comparison between discrete-time TM circuits and continuous-time VM circuits to identify gaps that need to be filled. As a first contribution, we provide an analytical expression for the noise operation of both a VM and TM PMOS-NMOS transistor stack, leading to the expression of the peak-SNR of both architectures. The proposed noise theory is applied to different CMOS process and compared in Spectre. In addition, we provide IC implementations with measurement results to verify the analysis finding.

Then, as a second contribution, we propose new TM building blocks and extensions to some old ones that alleviate the challenges imposed by modern CMOS technologies, without affecting the performance metrics. The first challenge is the need for half-period delay and full-period delay unit for TM circuits; the second challenge is the need for TM circuits to perform basic arithmetic operations (i.e., addition or subtraction) in wide linear range; and the third challenge is how to realize negative feedback in time-domain and process signals at higher frequency around intermediate frequency (IF).

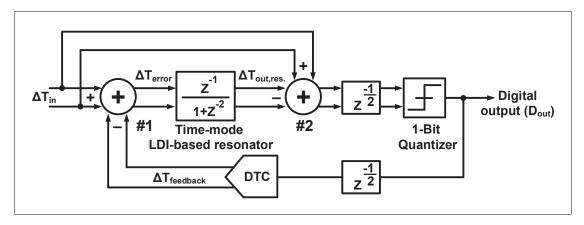

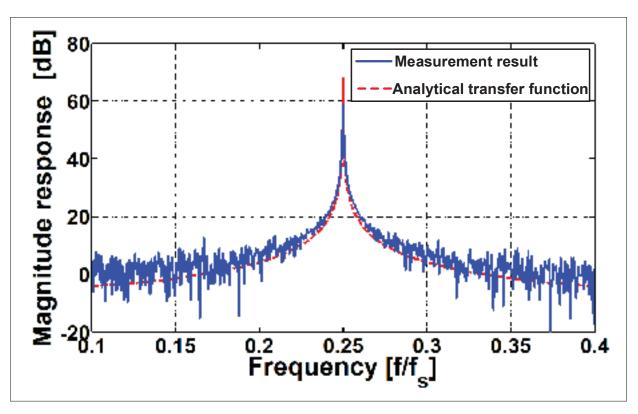

As a third contribution, an all-digital realization of a TM lossless discrete integrator (LDI)-based resonator is presented. The resonator is constructed by new TM building blocks in a negative feedback configuration. This achieves high-speed time-mode signal processing without the limitations imposed by switched-capacitor (SC) circuit techniques such as the matching of capacitors to realize precise signal gains. Instead, circuit precision is realized using an adaptive delay circuit to adjust the loop delay in a wide range of sampling frequencies. The operation of the TM LDI-based resonator is validated with transistor-level simulations and compared with system-level in Simulink/MATLAB.

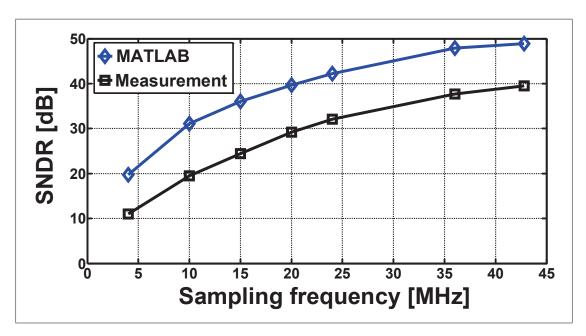

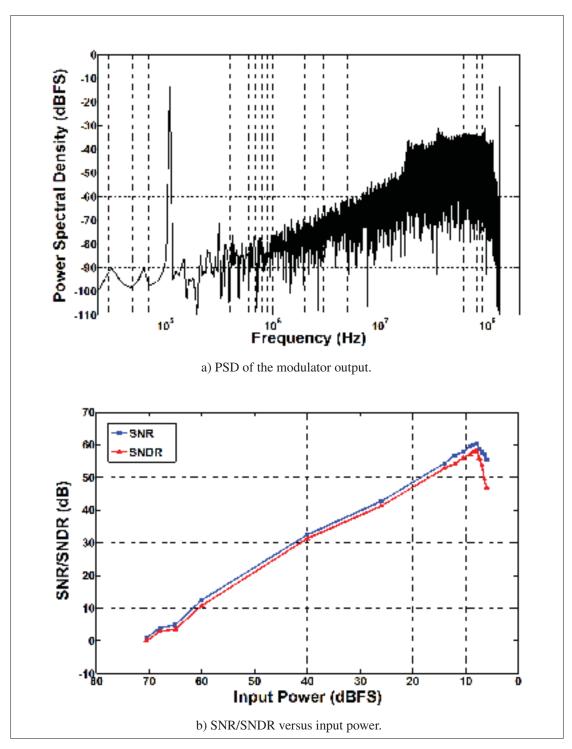

Finally, we propose a novel highly-digital BP $\Delta$   $\Sigma$ TDC for IF applications. It first introduces the system architecture of the proposed design and presents the expected performance metrics. The BP $\Delta\Sigma$ TDC is able to shape the quantization noise in a negative feedback configuration, and it does not require any complex calibration circuit to compensate for timing errors. In addition, for the very first time in TMSP, a direct feed-forward compensation is utilized in the TDC to achieve high signal-to-noise and distortion ratio (SNDR). We demonstrate the proposed TDC in an IBM 130 nm CMOS process, while operating from a supply voltage as low as 1.2 V. A continuous sampling frequency range from 4 MHz to 42.8 MHz is achieved to digitize an input signal that is centered at one-quarter of sampling frequency. It achieves a 39.5 dB peak SNDR over a 0.2 MHz signal bandwidth at maximum sampling frequency  $f_s$  =42.8 MS/s while consuming lower than 5 mW power. Furthermore, we identify future directions in TM circuit design and high-order realization of BP $\Delta$   $\Sigma$ TDC for research.

**Keywords:** Adaptive Delay, Digital-To-Time Converter, Double-Edge VCDU, Half-Period Delay Unit, Jitter, Lossless Discrete Integrator, Negative Time-Mode Feedback, Noise-Shaping, Second-Order BP $\Delta\Sigma$ TDC, Switched-Delay Unit, Synchronization, Time Difference Amplifier, TM Memory Cell, Voltage-Mode

## TABLE OF CONTENTS

|      |         |                                                                    | Page |

|------|---------|--------------------------------------------------------------------|------|

| INTR | ODUCT   | ION                                                                | 1    |

| CHAI | PTER 1  | FUNDAMENTALS OF TMΔΣ MODULATORS                                    | 9    |

| 1.1  | Introdu | ection                                                             | 9    |

| 1.2  | Theory  | of $\Delta\Sigma$ Modulators                                       | 9    |

|      | 1.2.1   | Basic Principles of a $\Delta\Sigma$ Modulator                     | 10   |

|      | 1.2.2   | Some ADC Performance Metrics                                       | 16   |

|      |         | 1.2.2.1 Sampling Frequency                                         | 17   |

|      |         | 1.2.2.2 Dynamic range                                              | 17   |

|      |         | 1.2.2.3 Resolution                                                 | 19   |

|      |         | 1.2.2.4 Distortion                                                 | 19   |

|      |         | 1.2.2.5 Power Dissipation and Chip Area                            | 20   |

|      |         | 1.2.2.6 Stability Considerations                                   | 20   |

| 1.3  | First-o | rder Single-Bit TM $\Delta\Sigma$ Modulators                       | 21   |

|      | 1.3.1   | VCDU-Based $\Delta\Sigma$ Modulator                                | 21   |

|      | 1.3.2   | Open-loop TM $\Delta\Sigma$ Modulators                             | 24   |

|      |         | 1.3.2.1 VCO-Based Open-Loop TM $\Delta\Sigma$ Modulator            |      |

|      |         | 1.3.2.2 GRO-Based Open-Loop TM $\Delta\Sigma$ Modulators           |      |

|      |         | 1.3.2.3 Vernier GRO-Based (VGRO) TM $\Delta\Sigma$ ADC             | 37   |

|      |         | 1.3.2.4 Switched-Ring Oscillator-Based TM ΔΣADC                    | 44   |

| 1.4  | High-o  | rder TM $\Delta\Sigma$ Modulators                                  | 45   |

|      | 1.4.1   | VCO-Based Closed-Loop TM $\Delta\Sigma$ Modulator                  |      |

|      | 1.4.2   | TM ΔΣADC Using DLL-Like Structure                                  | 48   |

|      | 1.4.3   | High-Order TM $\Delta\Sigma$ ADC Modulator With Voltage-Controlled |      |

|      |         | GRO (VCGRO)                                                        | 50   |

|      | 1.4.4   | High-Order TM $\Delta\Sigma$ ADC Modulator Using A Relaxation      |      |

|      |         | Oscillator Technique                                               |      |

| 1.5  |         | Design Issues                                                      |      |

|      | 1.5.1   | VCDU Nonlinearity                                                  |      |

|      | 1.5.2   | Component Mismatches                                               |      |

|      | 1.5.3   | Jitter-Induced Noise                                               |      |

|      | 1.5.4   | DFF Design Challenges                                              |      |

| 1.6  |         | rison of TM Versus VM $\Delta\Sigma$ Modulators                    |      |

| 1.7  | Summa   | ary                                                                | 59   |

| CHAI | PTER 2  | THE PEAK-SNR PERFORMANCES OF VOLTAGE-MODE                          |      |

|      |         | VERSUS TIME-MODE CIRCUITS: THE PMOS-NMOS STACK                     |      |

|      |         | USE CASE                                                           |      |

| 2.1  |         | ection                                                             |      |

| 2.2  | PMOS-   | -NMOS Transistor Stack: Performance Definitions                    | 63   |

|       | 2.2.1    | Voltage-Mode Analysis                                        | 64  |

|-------|----------|--------------------------------------------------------------|-----|

|       | 2.2.2    | Time-Mode Analysis                                           | 66  |

| 2.3   | Simulat  | ion Results                                                  | 71  |

| 2.4   | Experir  | nental Validation of Proposed Theory                         | 76  |

| 2.5   | -        | ry                                                           |     |

|       |          |                                                              |     |

| CHAI  | PTER 3   | A SECOND-ORDER BANDPASS $\Delta\Sigma$ TIME-TO-DIGITAL       |     |

|       |          | CONVERTER WITH NEGATIVE TIME-MODE FEEDBACK                   |     |

| 3.1   |          | ction                                                        |     |

| 3.2   |          | M Building Blocks And Extensions To Some Old Ones            |     |

|       | 3.2.1    | Previous Work                                                |     |

|       | 3.2.2    | Half-Period Delay Unit                                       | 85  |

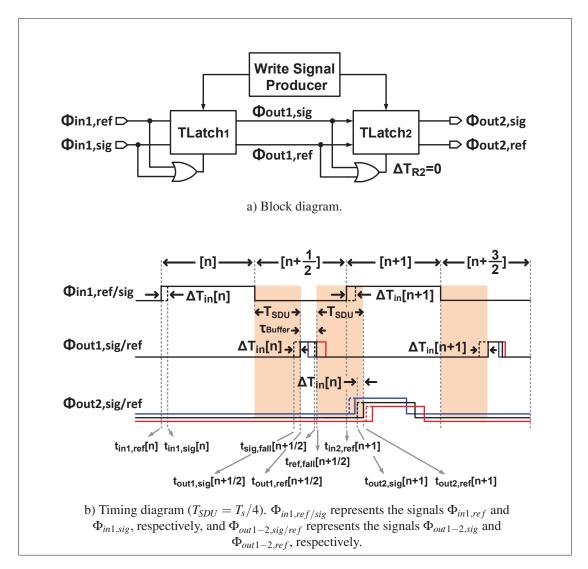

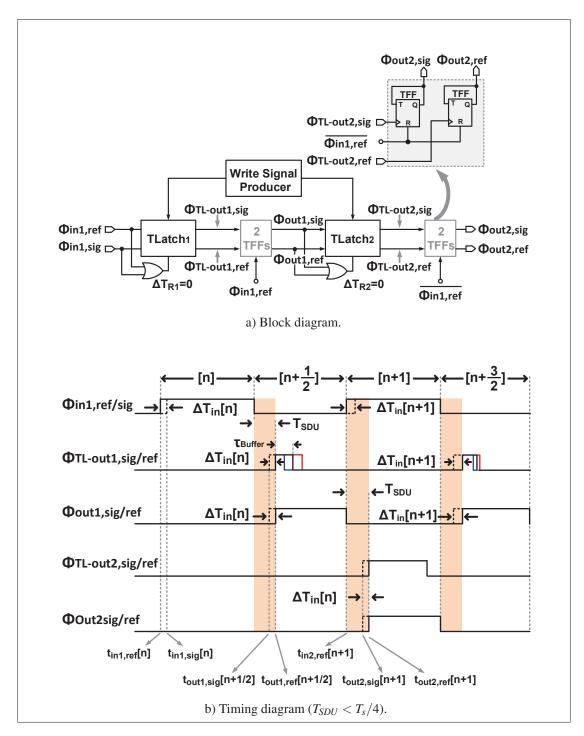

|       | 3.2.3    | Cascading Of Two Half-Period Delay Units                     | 88  |

|       | 3.2.4    | Adaptive Time Offset Correction                              | 94  |

|       | 3.2.5    | TM Subtractor                                                | 99  |

|       | 3.2.6    | Half-Period Delay DTC                                        | 101 |

| 3.3   | TM LD    | I-Based Resonator                                            | 107 |

| 3.4   | Second   | -Order BPΔΣTDC Circuit Implementation And Simulation Details | 112 |

| 3.5   |          | nental Setup                                                 |     |

|       | 3.5.1    | Measurement Results                                          | 119 |

| 3.6   | Summa    | ry                                                           |     |

| CITAI |          | NEW HARDOVE VENT TECHNICIES FOR MODIL AND TO                 | 100 |

|       | PTER 4   | NEW IMPROVEMENT TECHNIQUES FOR VCDU AND TDA                  |     |

| 4.1   |          | ction                                                        |     |

| 4.2   |          | inear Range VCDU                                             |     |

|       | 4.2.1    | Basic Concepts                                               |     |

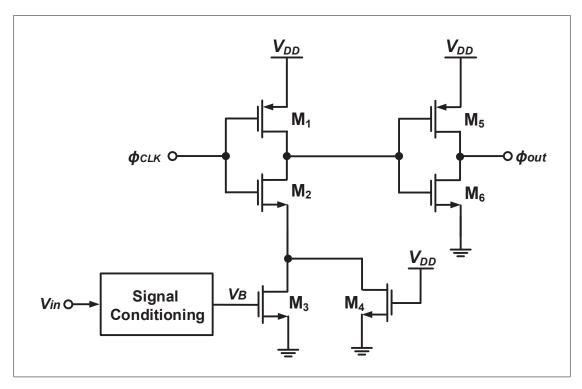

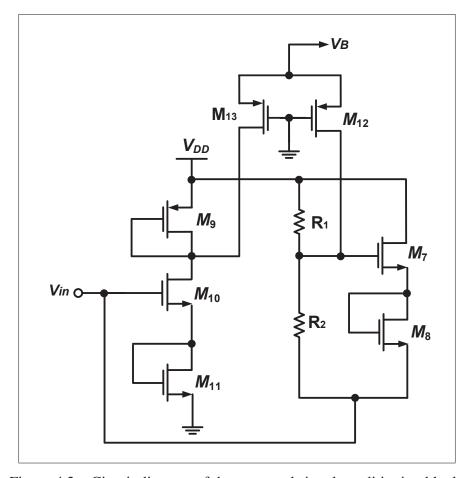

|       | 4.2.2    | Proposed VCDU Design                                         |     |

|       | 4.2.3    | Simulation Results                                           |     |

|       | 4.2.4    | Application To $\Delta\Sigma$ Modulation                     |     |

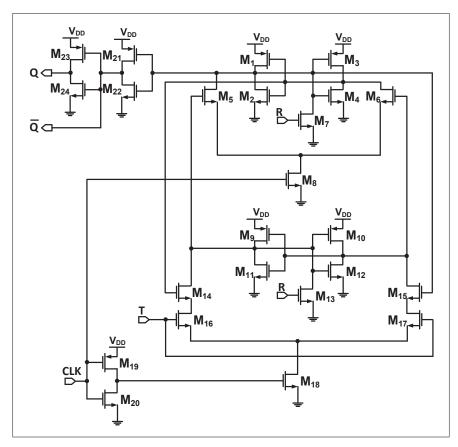

| 4.3   |          | Digital High-Resolution Programmable TDA Based on Time Latch |     |

|       | 4.3.1    | Basic Concepts                                               |     |

|       | 4.3.2    | Proposed TDA                                                 | 141 |

|       |          | 4.3.2.1 2×TDA Basic Operation                                | 141 |

|       |          | 4.3.2.2 Digitally-Controlled TDA                             | 142 |

|       | 4.3.3    | Simulation results                                           | 145 |

| 4.4   | Conclu   | sion                                                         | 148 |

| CON   |          | I AND DECOMMENDATIONS                                        | 151 |

|       |          | N AND RECOMMENDATIONS                                        |     |

| 5.1   |          | Summary                                                      |     |

| 5.2   | Kecomi   | mendation for Future Works                                   | 153 |

| APPE  | NDIX I   | CIRCUIT DESIGN PARAMETERS FOR ALL CIRCUITS                   | 157 |

| RIRI  | IOGR A D | НҮ                                                           | 174 |

| שעוע  |          | LI I                                                         | 1/4 |

## LIST OF TABLES

|           |                                                                                   | Page |

|-----------|-----------------------------------------------------------------------------------|------|

| Table 2.1 | Initial transistor sizes and optimized sizes for simulation                       | 72   |

| Table 2.2 | Physical parameters of the CMOS transistors used in simulations                   | 72   |

| Table 2.3 | Theoretical prediction and simulation results for the VM and TM device parameters | 72   |

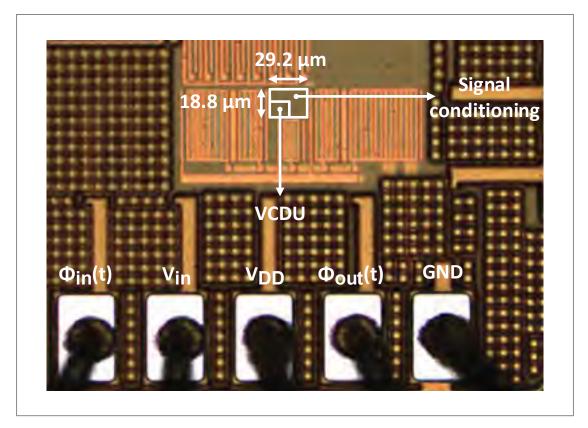

| Table 2.4 | Component values of the implemented VCDU                                          | 77   |

| Table 3.1 | Performance summary of the proposed BP $\Delta\Sigma$ TDC                         | 122  |

| Table 3.2 | Comparison of state-of-the-art TDCs with similar specifications                   | 122  |

| Table 4.1 | Performance summary and comparison.                                               | 135  |

| Table 4.2 | Performance summary and comparison.                                               | 146  |

# LIST OF FIGURES

|             |                                                                                                        | Page |

|-------------|--------------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Basic architecture of a conventional $\Delta\Sigma$ modulator                                          | 10   |

| Figure 1.2  | Two types of ADC schemes.                                                                              | 11   |

| Figure 1.3  | Filter requirement.                                                                                    | 12   |

| Figure 1.4  | Illustrating the quantization process                                                                  | 13   |

| Figure 1.5  | Illustrating the effect of oversampling and noise-shaping on the PSD of an ideal quantizer.            | 14   |

| Figure 1.6  | High-order noise shaping and its effect on the output quantization noise PSD                           | 17   |

| Figure 1.7  | High-order noise shaping and its effect on the output quantization noise PSD                           | 18   |

| Figure 1.8  | First-order $\Delta\Sigma$ modulator                                                                   | 22   |

| Figure 1.9  | Time-mode single-ended $\Delta\Sigma$ modulator with VCDU                                              | 23   |

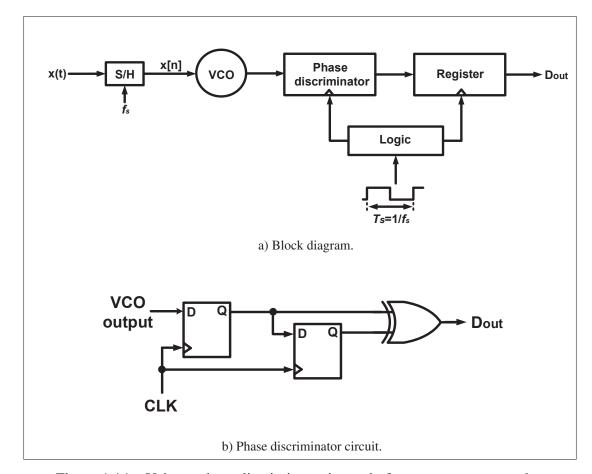

| Figure 1.10 | VCO-Based Open-Loop $\Delta\Sigma ADC$ .                                                               | 24   |

| Figure 1.11 | Timing diagram for the VCO-based $\Delta\Sigma ADC$                                                    | 26   |

| Figure 1.12 | Differential configuration of VCO-based $\Delta\Sigma ADC$                                             | 30   |

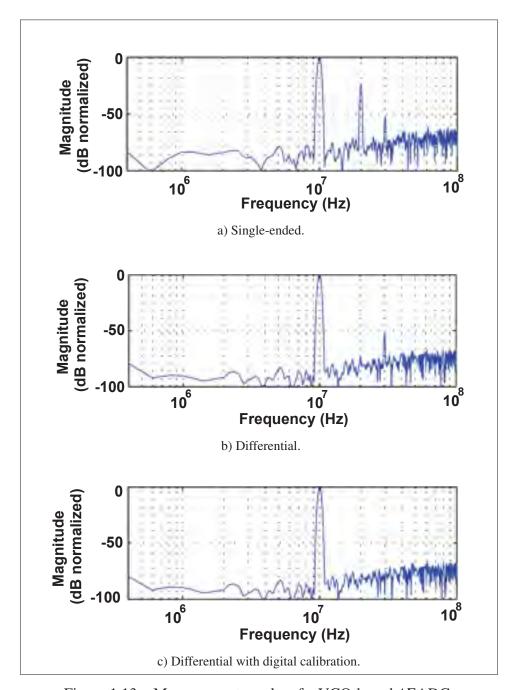

| Figure 1.13 | Measurement results of a VCO-based $\Delta\Sigma ADC$                                                  | 31   |

| Figure 1.14 | Using a phase discriminator instead of a counter to extract the VCO phase changes.                     | 33   |

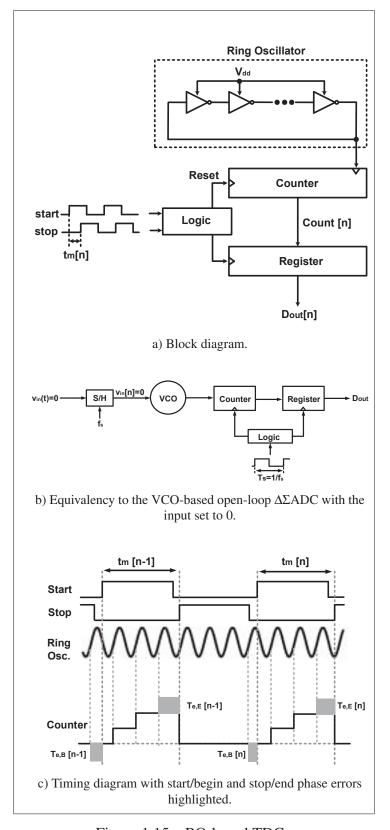

| Figure 1.15 | RO-based TDC.                                                                                          | 34   |

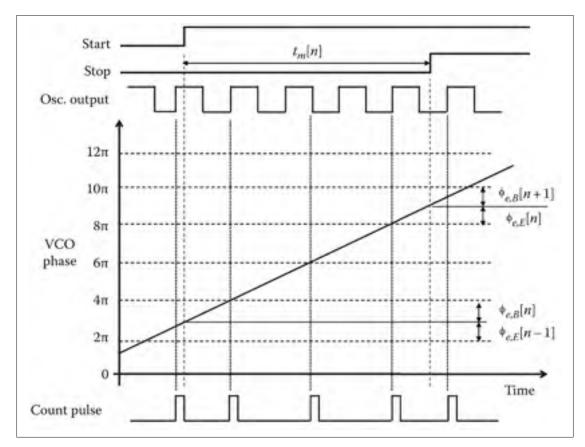

| Figure 1.16 | Timing diagram of the ring oscillator–based TDC with start/begin and stop/end phase errors highlighted | 36   |

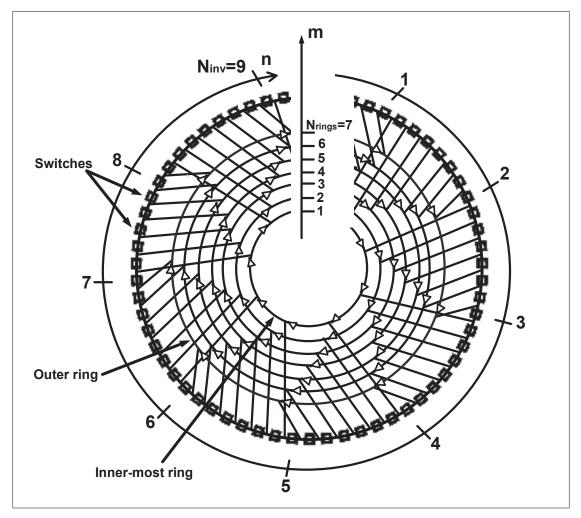

| Figure 1.17 | General implementation arrangement of a multiphase coupled oscillator configuration.                   | 38   |

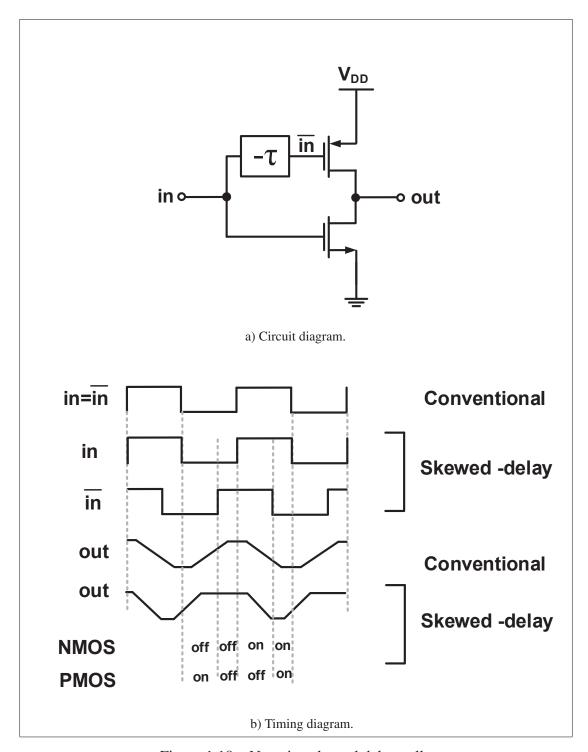

| Figure 1 18 | Negative-skewed delay cell                                                                             | 40   |

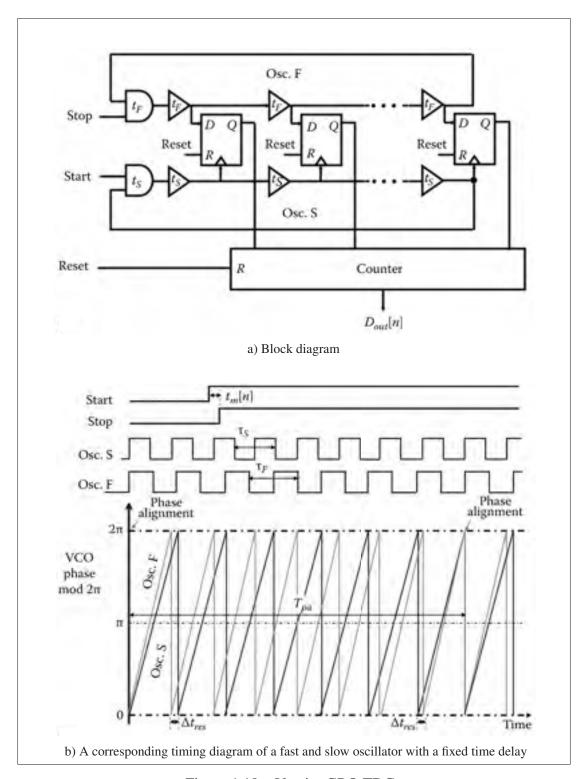

| Figure 1.19 | Vernier GRO TDC.                                                                                                                                 | 41 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.20 | Block diagram of SRO-based TM $\Delta\Sigma$ ADC.                                                                                                | 44 |

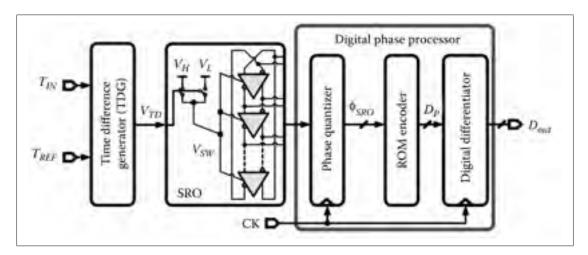

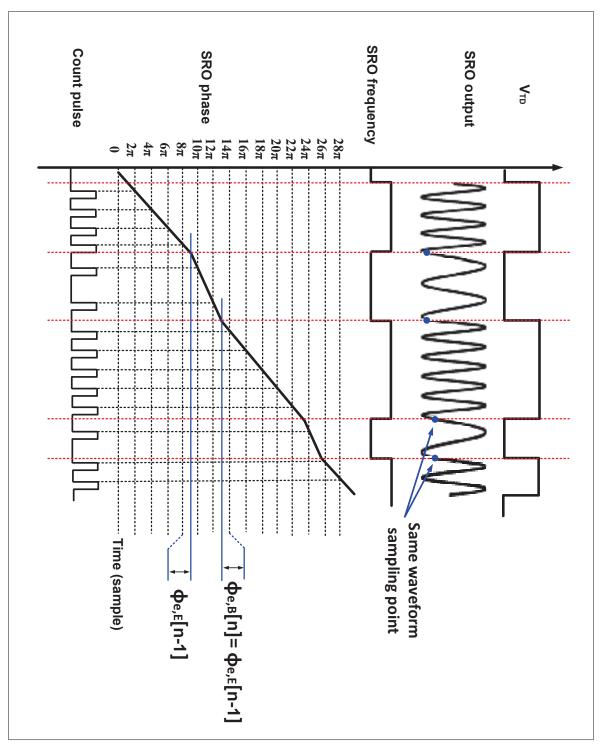

| Figure 1.21 | Illustrating the timing diagram for the SRO-based $\Delta\Sigma$ ADC and how the start/begin and stop/end phase errors are made equal            | 46 |

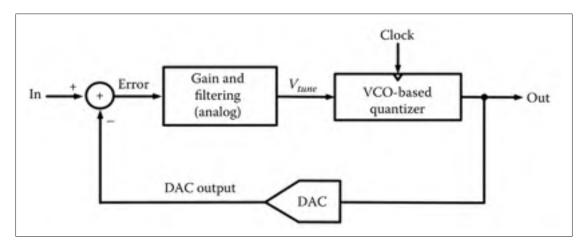

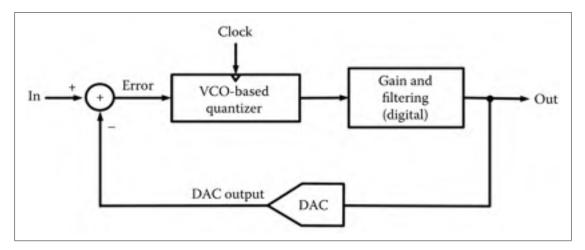

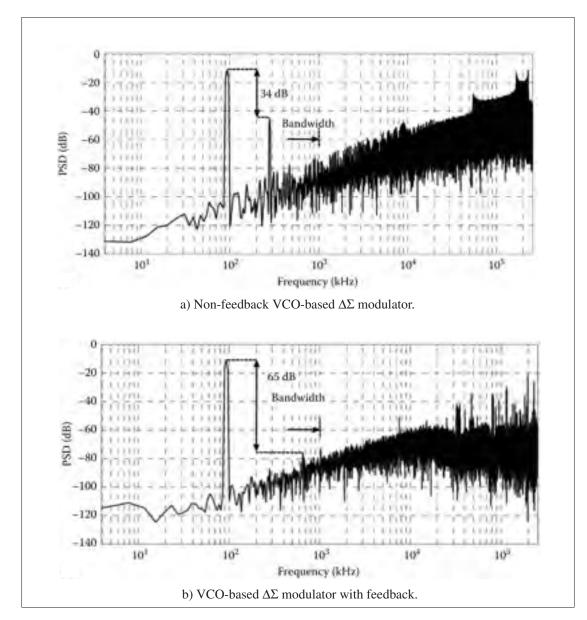

| Figure 1.22 | Block diagram of $VCO\Delta\Sigma ADC$ used in a closed-loop configuration.                                                                      | 47 |

| Figure 1.23 | TM VCO-based $\Delta\Sigma$ with tracking-loop quantizer                                                                                         | 48 |

| Figure 1.24 | PSD of the VCO-based $\Delta\Sigma$ modulator with a tracking-loop quantizer.                                                                    | 49 |

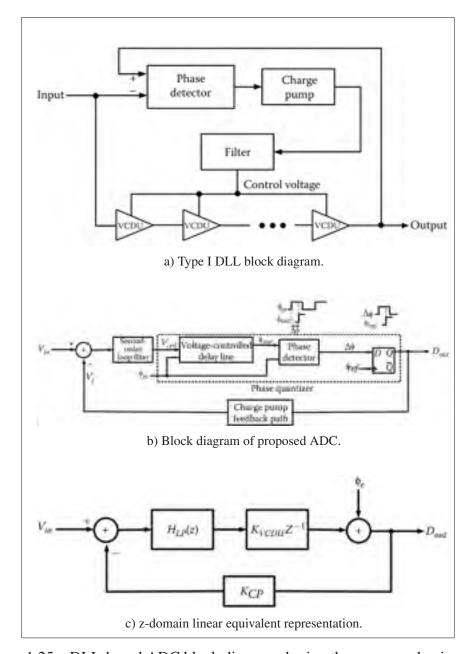

| Figure 1.25 | DLL-based ADC block diagram sharing the same mechanism as a conventional DLL.                                                                    | 51 |

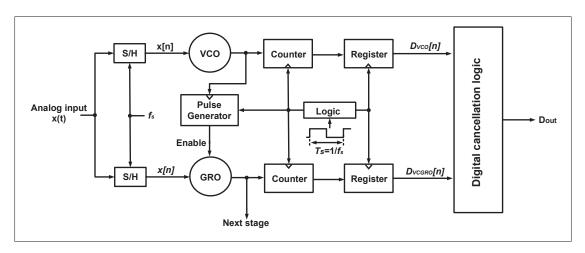

| Figure 1.26 | High-order $TM\Delta\Sigma$ modulator with MASH structure using VCO and VCGRO.                                                                   | 52 |

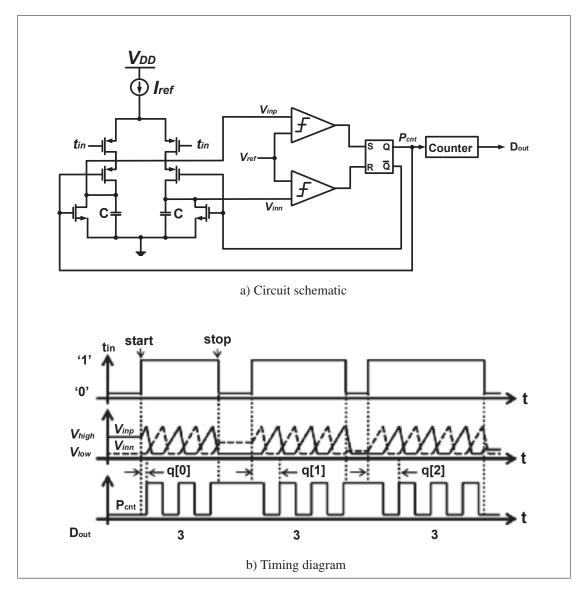

| Figure 1.27 | First-order $\Delta\Sigma$ modulator using a relaxation oscillator.                                                                              | 54 |

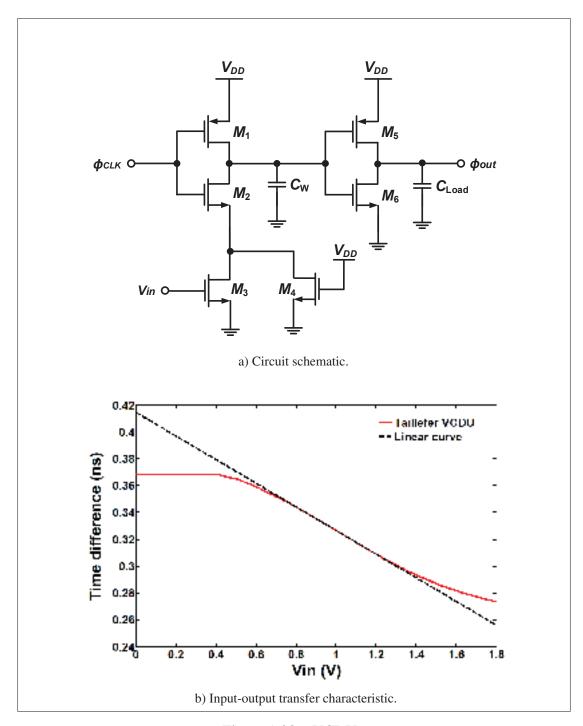

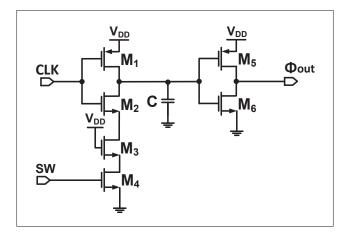

| Figure 1.28 | VCDU.                                                                                                                                            | 56 |

| Figure 1.29 | Jitter noise definition in $TM\Delta\Sigma$ modulators                                                                                           | 58 |

| Figure 1.30 | Historical performance comparisons.                                                                                                              | 60 |

| Figure 2.1  | Basic primitive circuit element consisting of a PMOS-NMOS transistor stack in presence of noise.                                                 | 64 |

| Figure 2.2  | PMOS-NMOS stack jitter analysis.                                                                                                                 | 68 |

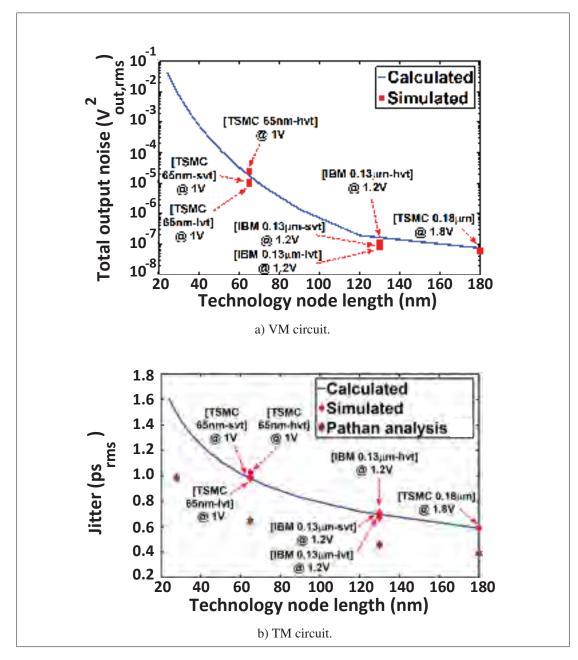

| Figure 2.3  | Output noise and jitter as a function of technology node length (lvt, std, and hvt are low, standard, and high threshold voltage, respectively). | 73 |

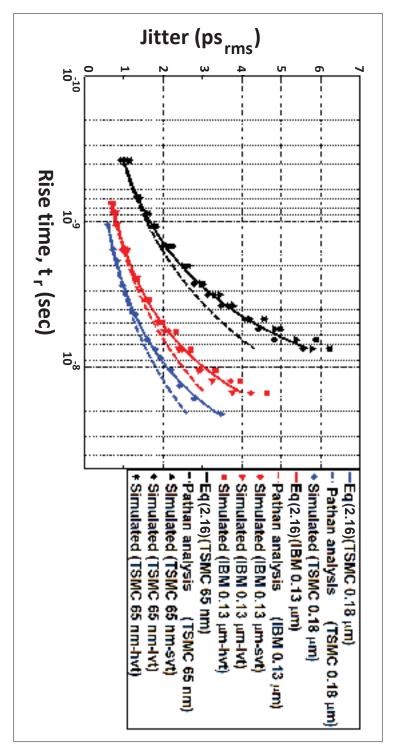

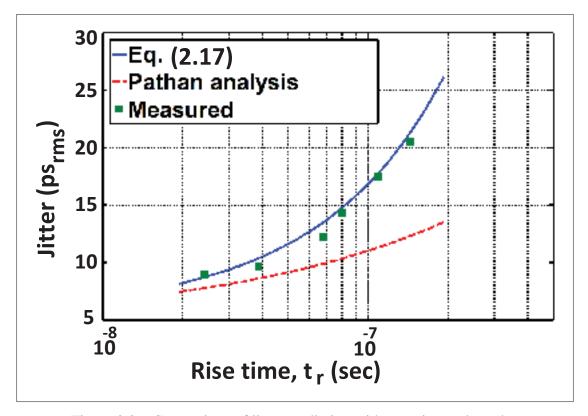

| Figure 2.4  | TM rms jitter versus rise time, $t_r$ .                                                                                                          | 75 |

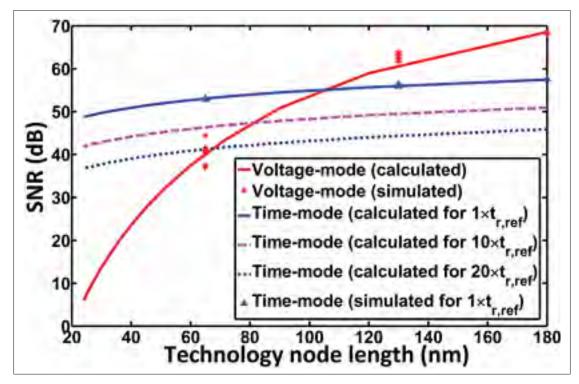

| Figure 2.5  | Peak-SNR performance for VM and TM PMOS-NMOS transistor stack versus technology node length ( $t_{r,ref}$ =250 ps)                               | 76 |

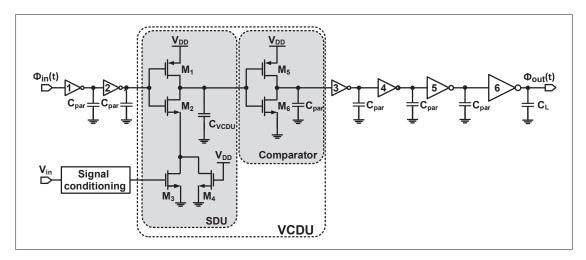

| Figure 2.6  | Schematic of the VCDU.                                                                                                                           | 77 |

| Figure 2.7  | Die photograph.                                                                                                                                  | 78 |

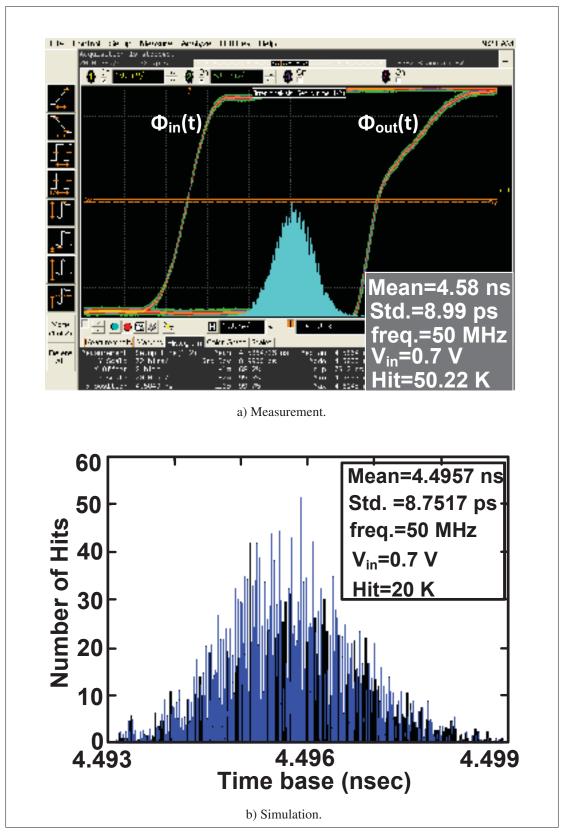

| Figure 2.8  | Jitter histogram of the VCDU.                                                                                                                                 | 79  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.9  | Comparison of jitter prediction with experimental results                                                                                                     | 80  |

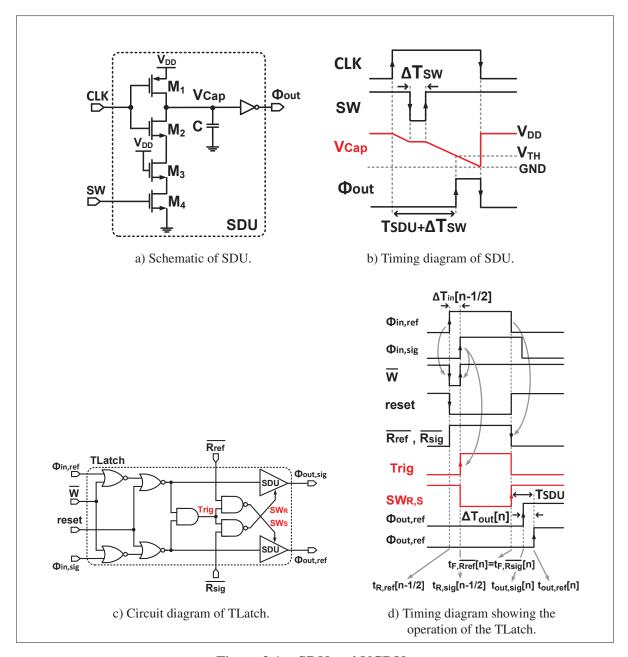

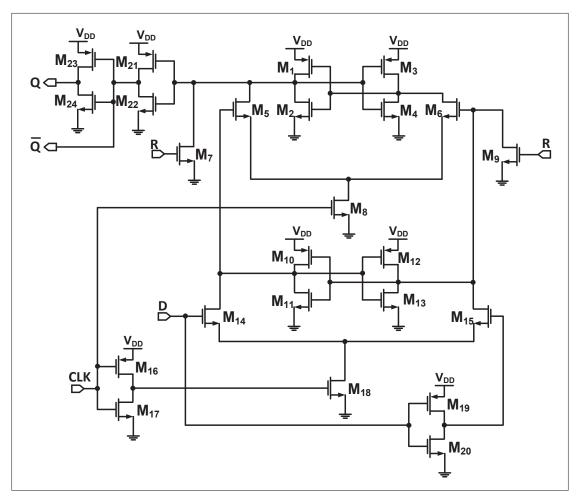

| Figure 3.1  | SDU and VCDU.                                                                                                                                                 | 84  |

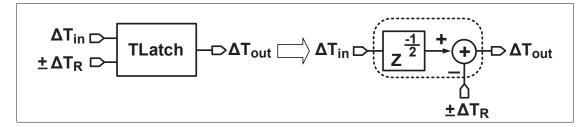

| Figure 3.2  | TLatch equivalent model in <i>z</i> -domain                                                                                                                   | 85  |

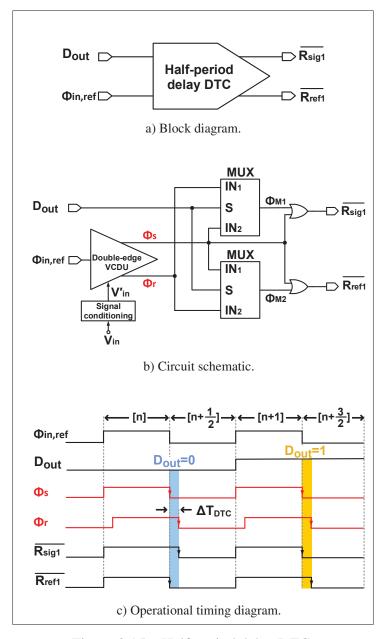

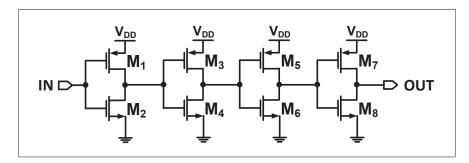

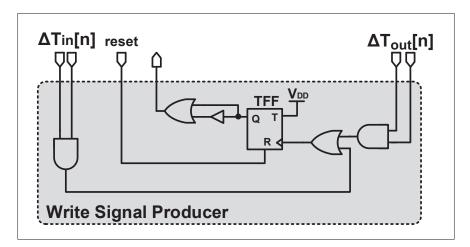

| Figure 3.3  | Half-Period Delay Unit.                                                                                                                                       | 86  |

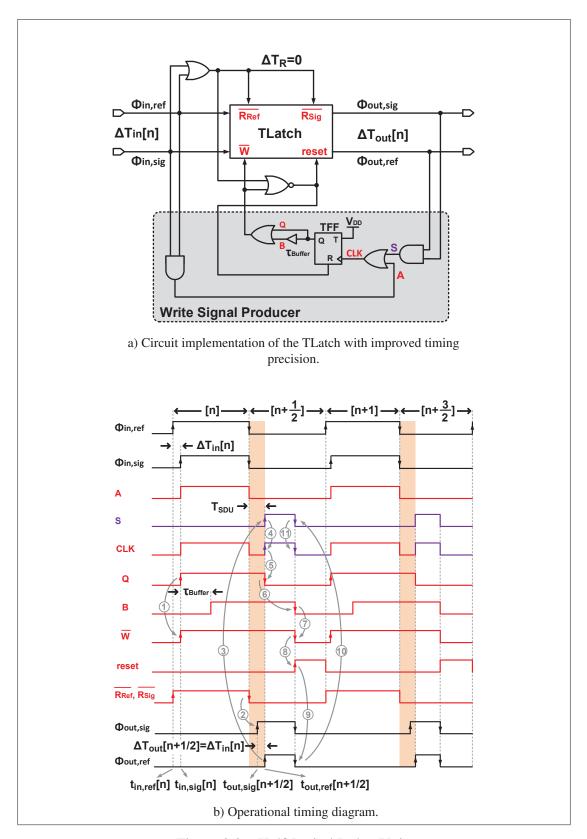

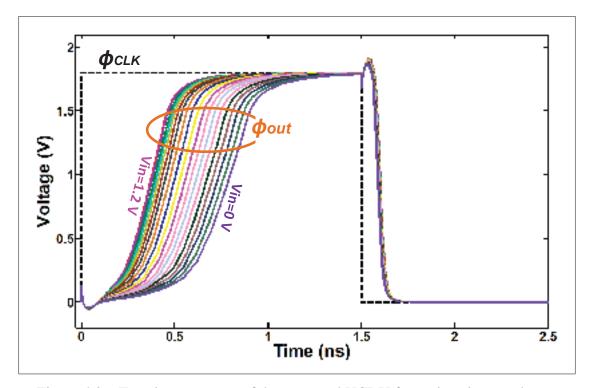

| Figure 3.4  | Simulation results.                                                                                                                                           | 88  |

| Figure 3.5  | Cascaded two half-period delays without TFFs                                                                                                                  | 89  |

| Figure 3.6  | Cascaded two half-period delays with TFFs.                                                                                                                    | 92  |

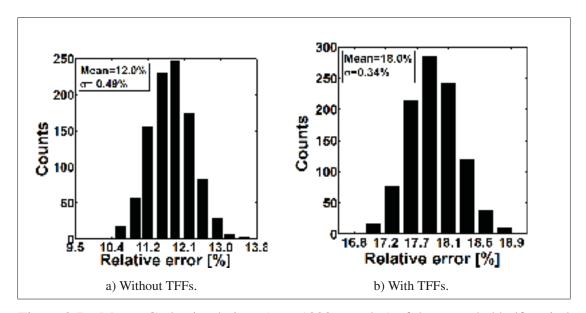

| Figure 3.7  | Monte-Carlo simulations ( $N = 1000$ samples) of the cascaded half-period delays.                                                                             | 93  |

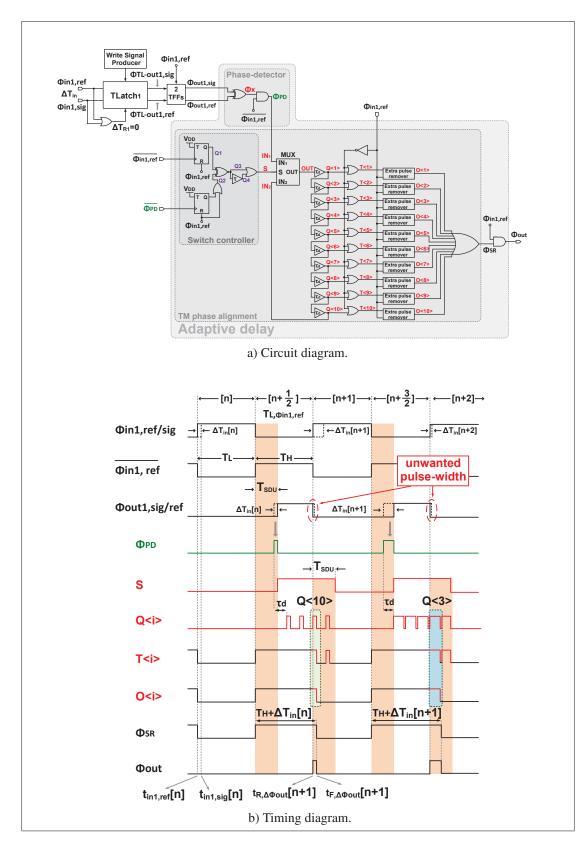

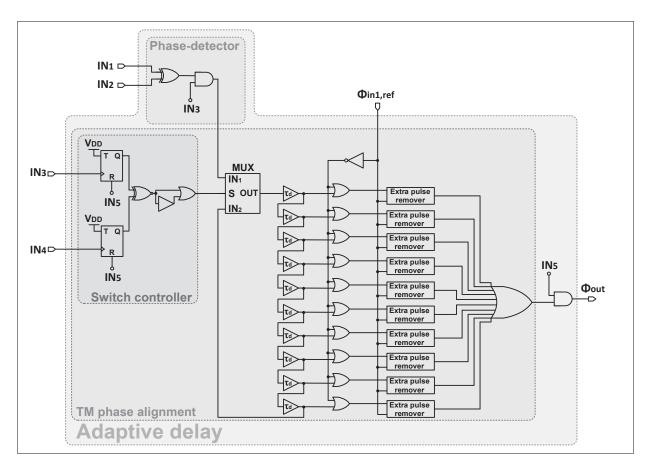

| Figure 3.8  | Cascaded half-period delay with an adaptive delay block                                                                                                       | 95  |

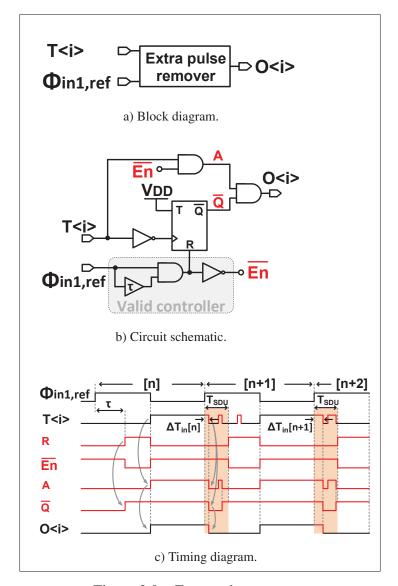

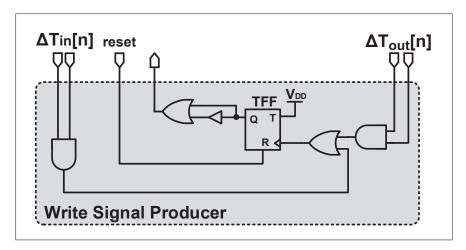

| Figure 3.9  | Extra pulse remover.                                                                                                                                          | 97  |

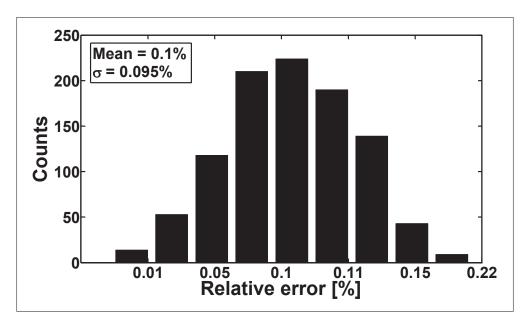

| Figure 3.10 | Monte-Carlo analysis (N = 1000 samples) for the transistor mismatches ( $\Delta T_{in} = 500 \text{ ps}$ , $T_{SDU} = T_s/8$ , and $f_s = 42.8 \text{ MHz}$ ) | 98  |

| Figure 3.11 | Simulation results of the adaptive delay with PVT variations                                                                                                  | 98  |

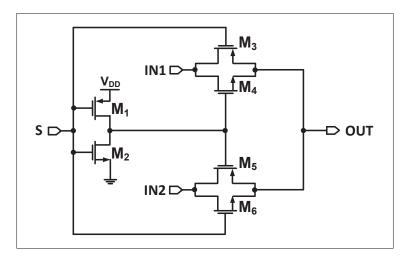

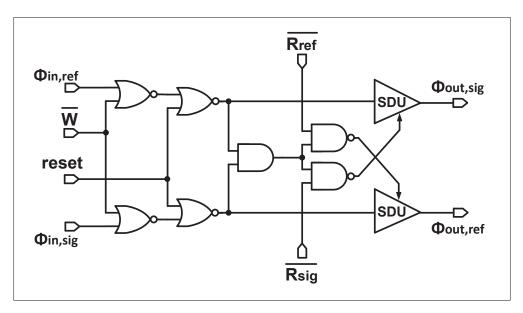

| Figure 3.12 | Modified TM subtractor.                                                                                                                                       | 100 |

| Figure 3.13 | Negative time-difference detector.                                                                                                                            | 102 |

| Figure 3.14 | Simulation results of the TM subtractor. $\Delta T_{\text{in}1}$ =100 ps at 42.8 MHz                                                                          | 103 |

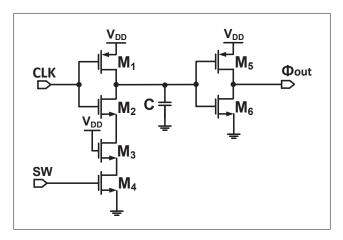

| Figure 3.15 | Half-period delay DTC.                                                                                                                                        | 104 |

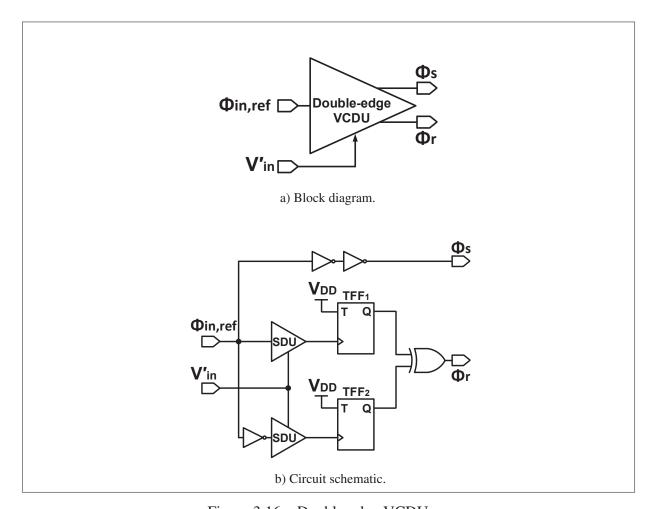

| Figure 3.16 | Double-edge VCDU.                                                                                                                                             | 105 |

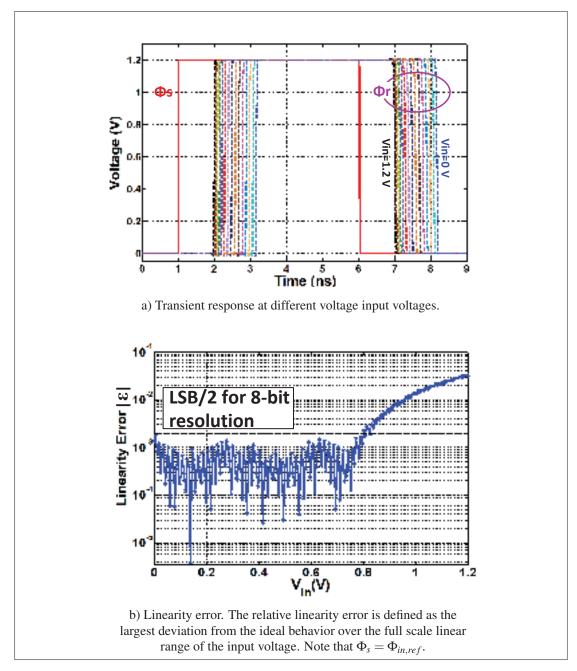

| Figure 3.17 | Transistor-level simulation results of the double-edge VCDU                                                                                                   | 106 |

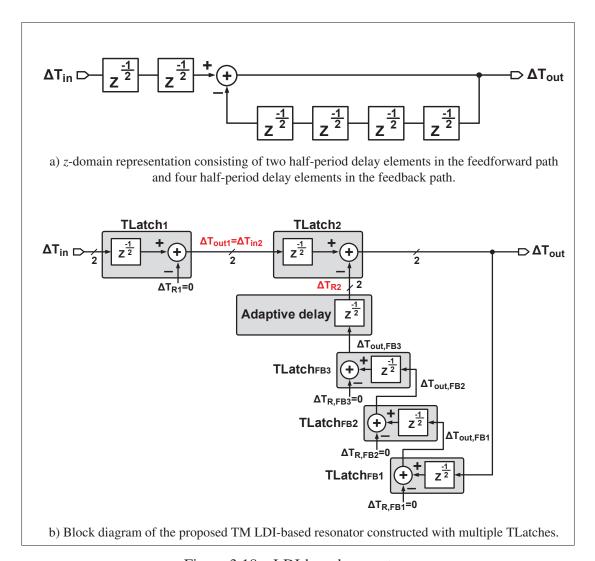

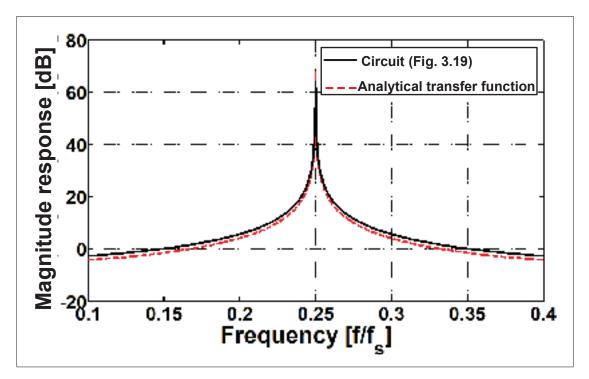

| Figure 3.18 | LDI-based resonator.                                                                                                                                          | 108 |

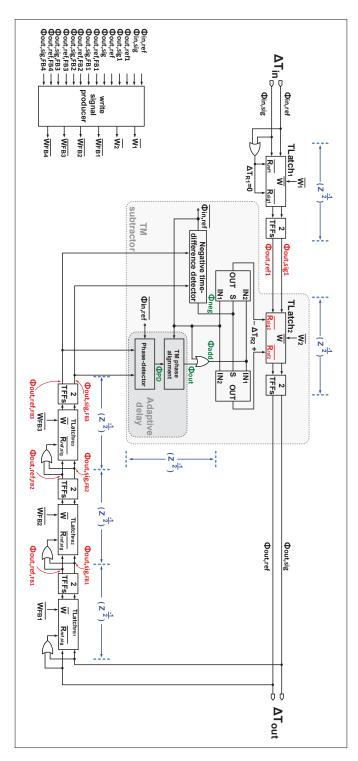

| Figure 3.19 | Circuit schematic of TM LDI-based resonator with negative TM signal detect circuitry.                                                                         | 110 |

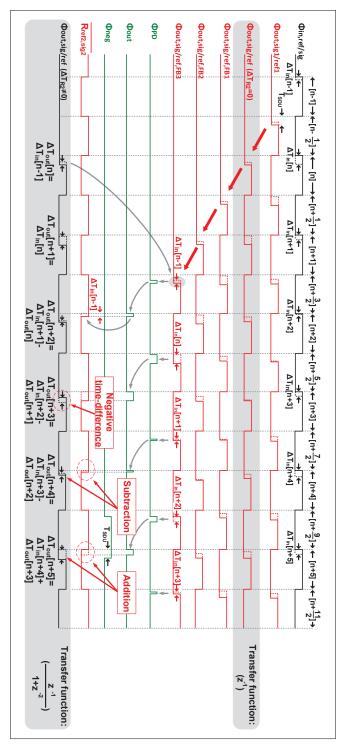

| Figure 3.20 | Timing diagram of TM LDI-based resonator. $\Phi_{out,sig/ref,FB1-3}$ in the timing diagram represents the signals $\Phi_{out,sig,FB1-3}$ and $\Phi_{out,ref,FB1-3}$ , respectively              | 111 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.21 | Simulation results of the step response of the circuit-level implementation in Figure 3.19.                                                                                                     | 112 |

| Figure 3.22 | Block diagram of the essential components in the proposed $BP\Delta\Sigma TDC$                                                                                                                  | 113 |

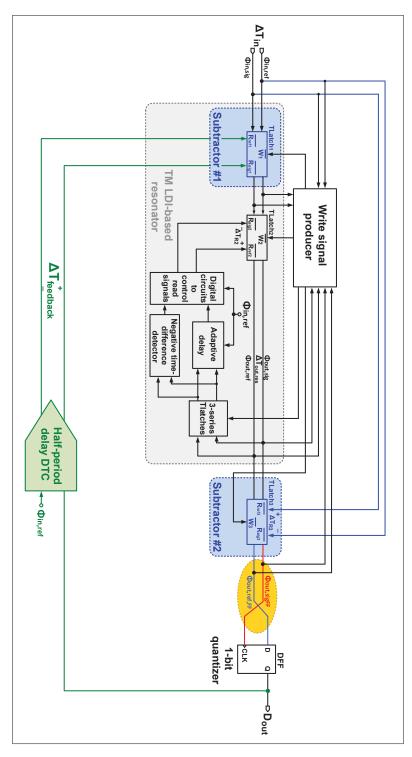

| Figure 3.23 | Top-level schematic of the proposed BP $\Delta\Sigma$ TDC. TFFs in the output of TLatch <sub>1</sub> and TLatch <sub>2</sub> are not shown for simplicity                                       | 114 |

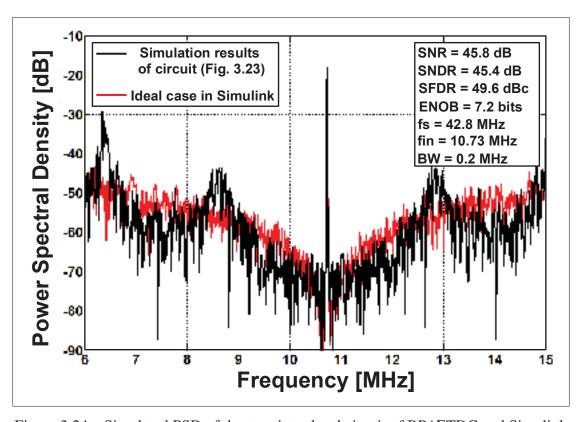

| Figure 3.24 | Simulated PSD of the transistor-level circuit of BP $\Delta\Sigma$ TDC and Simulink system-level BP $\Delta\Sigma$ modulator.                                                                   | 115 |

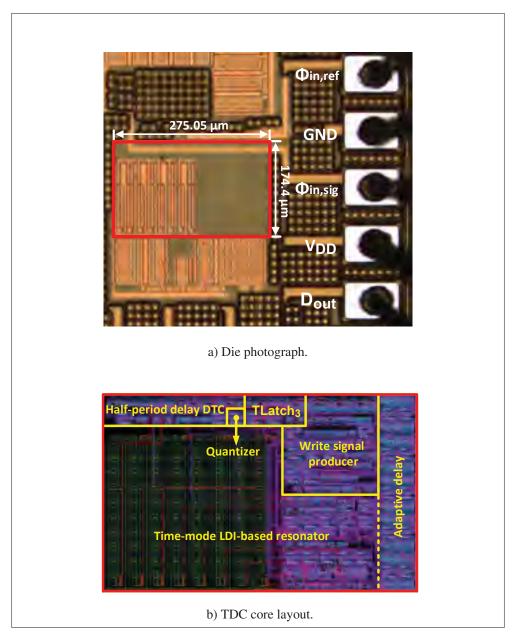

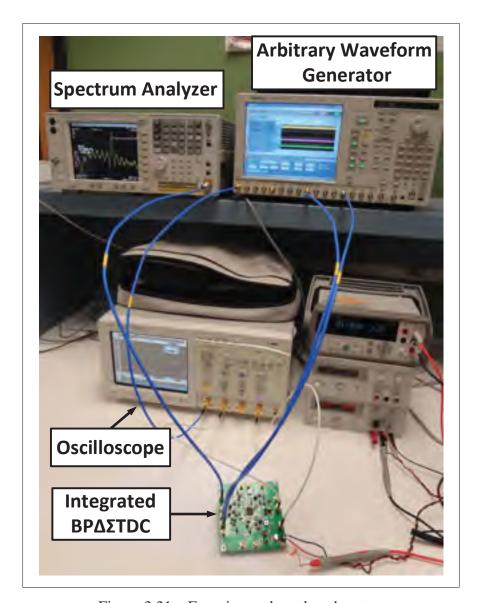

| Figure 3.25 | Experimental Prototype                                                                                                                                                                          | 117 |

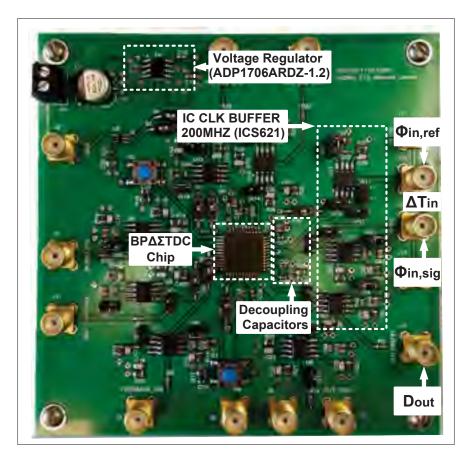

| Figure 3.26 | Photograph of the customized board to test the TDC circuit                                                                                                                                      | 118 |

| Figure 3.27 | Block diagram of the measurement setup                                                                                                                                                          | 118 |

| Figure 3.28 | System-level model of Instrument                                                                                                                                                                | 120 |

| Figure 3.29 | Measurement the time difference jitter ( $\Delta T_{in}$ =500 ps)                                                                                                                               | 121 |

| Figure 3.30 | Measurement results of the step response of the TM LDI-based resonator.                                                                                                                         | 123 |

| Figure 3.31 | Experimental test bench setup.                                                                                                                                                                  | 124 |

| Figure 3.32 | Experimental time-domain waveforms of the input signals ( $\Phi_{in,ref}$ and $\Phi_{in,sig}$ ) at sampling frequency 42.8 MHz and output bit-stream ( $D_{out}$ ).                             | 125 |

| Figure 3.33 | Measured output spectrum of the BP $\Delta\Sigma$ TDC with a 10.73 MHz input signal and 42.8 MHz sampling frequency. Each of the output spectrum are averaged to reduce the variance of the PSD | 126 |

| Figure 3.34 | Measured SNDR versus input signal level                                                                                                                                                         | 126 |

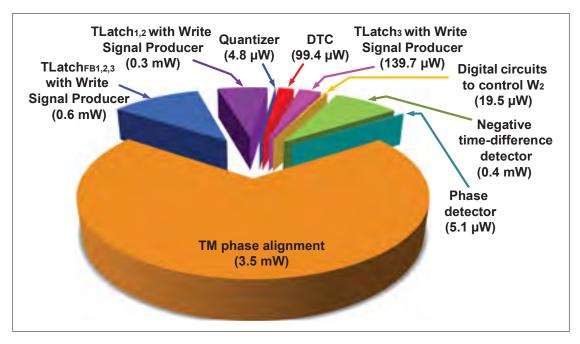

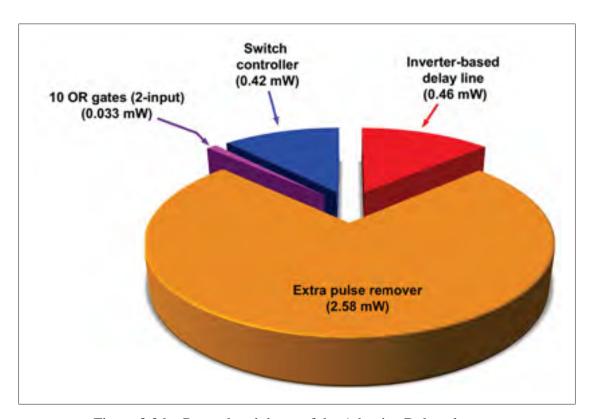

| Figure 3.35 | Power breakdown of the prototype TDC                                                                                                                                                            | 127 |

| Figure 3.36 | Power breakdown of the Adaptive Delay element                                                                                                                                                   | 128 |

| Figure 3.37 | MATLAB and Measured SNDR for different sampling frequency $(f_{in} = f_s/4)$ with $BW$ =0.2 MHz.                                             | 128 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

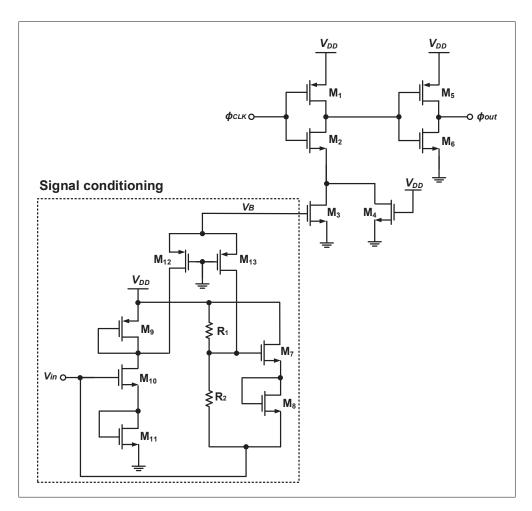

| Figure 4.1  | Schematic of the proposed VCDU with signal conditioning block                                                                                | 131 |

| Figure 4.2  | Circuit diagram of the proposed signal conditioning block                                                                                    | 133 |

| Figure 4.3  | Transient response of the proposed VCDU for various input voltages (circuit-level simulation results)                                        | 134 |

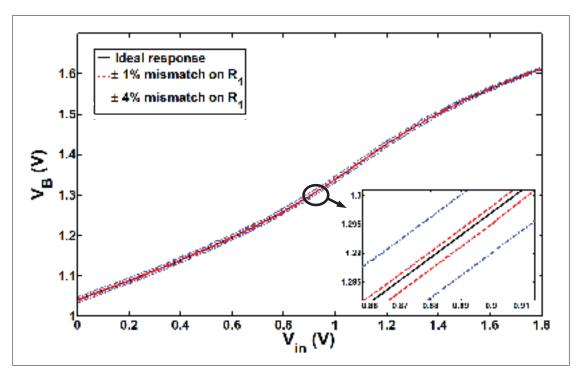

| Figure 4.4  | DC response of the signal conditioning block.                                                                                                | 135 |

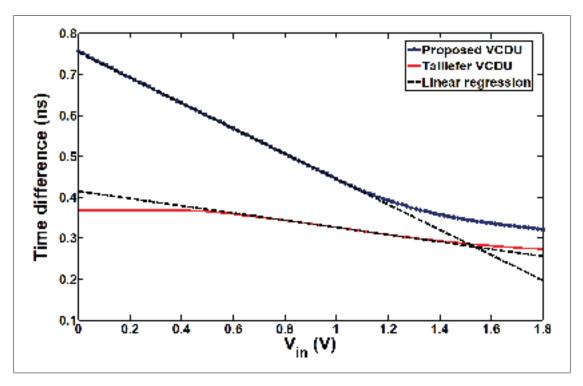

| Figure 4.5  | Transfer characteristic of Taillefer VCDU and proposed VCDU                                                                                  | 136 |

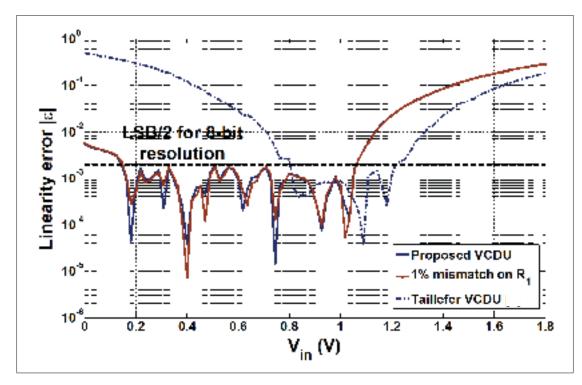

| Figure 4.6  | Linearity error of Taillefer VCDU and proposed VCDU.                                                                                         | 137 |

| Figure 4.7  | First-order single-bit time-mode $\Delta\Sigma$ modulator                                                                                    | 138 |

| Figure 4.8  | Simulation results of the first-order $\Delta\Sigma$ modulator using the proposed VCDU.                                                      | 139 |

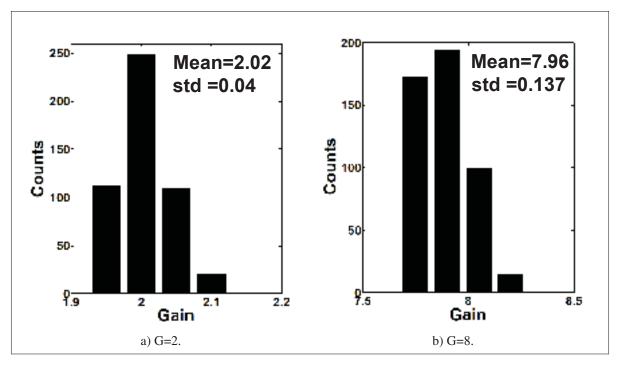

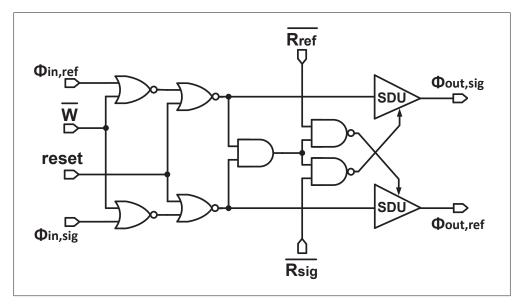

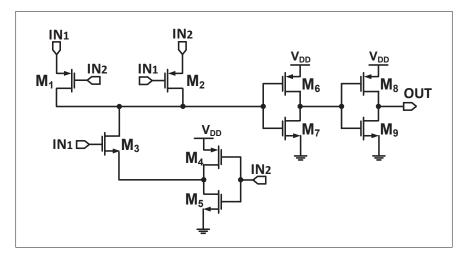

| Figure 4.9  | Architecture of the 2×TDA block                                                                                                              | 142 |

| Figure 4.10 | Circuit implementation of the programmable TDA.                                                                                              | 144 |

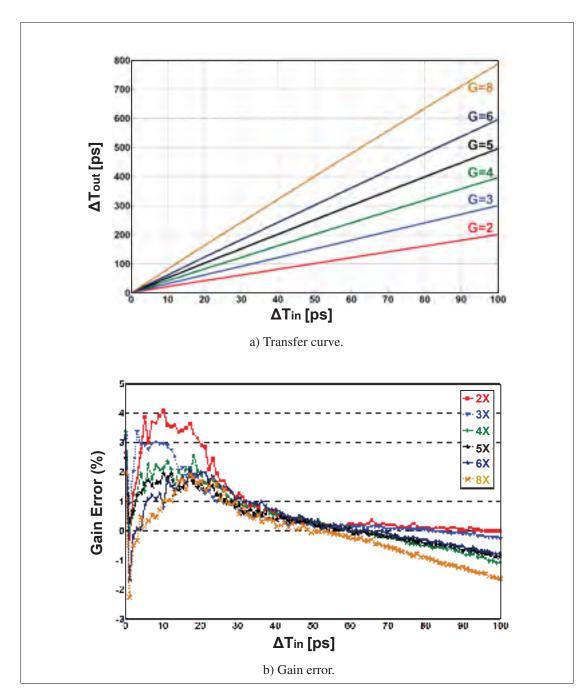

| Figure 4.11 | Simulation results of the proposed TDA.                                                                                                      | 147 |

| Figure 4.12 | Simulation results of the programmable TDA for $G=8\times$ with PVT variations.                                                              | 148 |

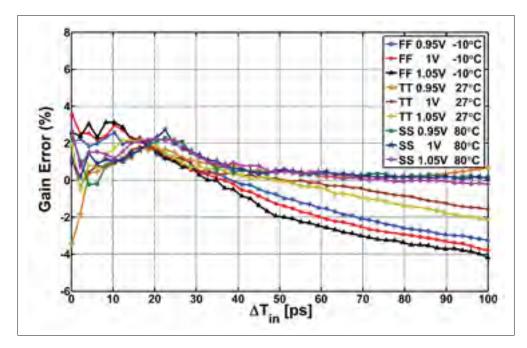

| Figure 4.13 | Monte-Carlo histograms of the programmable TDA (N=500). In this simulation, a constant input, $\Delta T_{in} = 500$ fs is applied to the TDA | 149 |

#### LIST OF ABREVIATIONS

ADC Analog-to-Digital Converter

ADPLL All-Digital Phase-Locked Loop

BPΔΣTDC BandPass Delta Sigma Time-To-Digital Converter

BSF Band Selection Filter

CMOS Complementary Metal Oxide Semiconductor

DFF D-type Flip Flop

DLL Delay-Locked Loop

DR Dynamic Range

DTC Digital-to-Time Converter

FOM Figure of Merit

GRO Gated Ring Oscillator

IC Integrated Circuit

IF Intermediate Frequency

LDI Lossless Discrete Integrator

LP Low-Pass

LSB Least Significant Bit

MASH Multi-Stage Noise-Shaping

MUX Multiplexer

OSR LosslessOversampling Ratio

PCB Printed Circuit Board

PSD Power Spectral Density

PVT Process, Voltage, and Temperature

MASH Multi-Stage Noise-Shaping

SDU Switched Delay Unit

SFDR Spurious-Free Dynamic Range

SNDR Signal-to-Noise-and-Distortion Ratio

SNR Signal-to-Noise Ratio

SRO Switched-Ring Oscillator

TVC Time-to-Voltage Converter

TDA Time-Difference Amplifier

TDC Time-to-Digital Converter

TFF T-type Flip Flop

TLatch Time Latch

TM Time-Mode

TMSP Time-mode Signal Processing

ToF Time-of-Flight

VTC Voltage-to-Time Converter

VCDU Voltage-Controlled Delay Unit

VM Voltage-Mode

#### INTRODUCTION

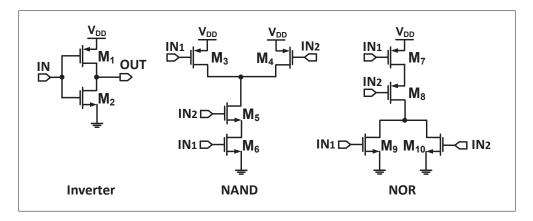

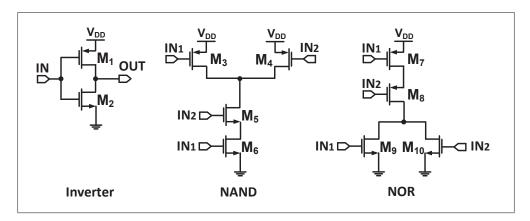

The demand for low-power mixed-signal circuits that can be integrated into nanoscale CMOS technologies is rising constantly. This is driven by the need for longer-lasting portable computing and sensory applications, like smart phones, tablets, IoT, etc.. However, the performance of analog circuits in nanoscaled CMOS processes is degraded due to numerous technological challenges such as a reduction in the intrinsic gain of transistors, increased switching noise because of the closer proximity of circuits, and increased power consumption to maintain the same level of performance as that achieved in older CMOS technologies (Park *et al.*, 2009; M. Ali-Bakhshian and G.W. Roberts, 2012). In contrast, digital circuits have proven to be quite amenable in advanced CMOS technologies working with transistors with such low gains. Billions of transistors are now being integrated on a single chip in the form of digital logic where they are used to realize reliable computing and signal processing algorithms. It is therefore the goal of this thesis to develop analog signal-processing techniques that use digital logic gates as their basic building blocks.

An alternative approach to minimize the aforementioned issues is time-mode signal processing (TMSP) whose performance scales well with advanced CMOS technology as it relies exclusively on the switching principle of digital logic circuits. In this approach, signal information is encoded as the time-difference between the rising edges of two independent digital step-like signals, with one of the digital signals acting as the reference (Yu *et al.*, 2014). As a consequence, the TMSP technique provides analog signal processing capabilities in advanced CMOS technologies such as FinFET technology that are digitally-enhanced using on-chip calibration techniques, phase-locked to the incoming reference signal. By doing so, CMOS circuits that are robust to process variations, supply level changes and temperature excursions, i.e., PVT effects, can be realized. Moreover, TMSP provides a circuit technique whose dynamic range improves with process scaling. For instance, the upper limit to the dynamic range (DR) of a VM circuit can be quantified as the ratio of the power supply level,  $V_{DD}$ , to the voltage noise

limit,  $\sqrt{KT/C}$ . With advances in technology scaling,  $V_{DD}$  must be reduced, hence the DR falls in a VM circuit. In contrast, the DR of a TM circuit, being the ratio of reference clock period  $T_s$  to the clock jitter, falls at a much slower rate than VM circuits (Figueiredo *et al.*, 2012). In addition, TMSP offers the opportunity to employ highly efficient digital circuits performing sampled-data analog applications, instead of the foreground SC circuits used in analog data converters (i.e., ADCs, DAC,  $\Delta\Sigma$  converters, etc.).

Recently, several TM data converters have been reported. Such efforts are exemplified in a VCDU-based ΔΣΜ (Taillefer and Roberts, 2009), multi-path gated ring oscillator TDC (Straayer and Perrott, 2009), voltage-controlled gated-ring oscillator (VC-GRO) (Yu *et al.*, 2013), voltage-controlled oscillator (VCO)-based with multi-bit quantizer (Kim *et al.*, 2010), delay-locked-loop (DLL) based with voltage-controlled delay line (VCDL) technique as a quantizer (Lin *et al.*, 2012), as well as circuits circuits that operates like a discrete-time filter (Guttman and Roberts, 2009). One of the key building blocks of the TM systems is the time-to-digital converter (TDC), has been used more and more frequently in many applications, such as time-of-flight (ToF) (Vornicu *et al.*, 2017), jitter measurement (Nose *et al.*, 2006), medical imaging (Chen *et al.*, 2017), all-digital PLL (ADPLL) (Cao *et al.*, 2012; Avivi *et al.*, 2017), and time-domain analog-to-digital converters (ADCs) (Naraghi *et al.*, 2010; Daniels *et al.*, 2010; Hsu, *et al.*, 2008; Yu, *et al.*, 2014).

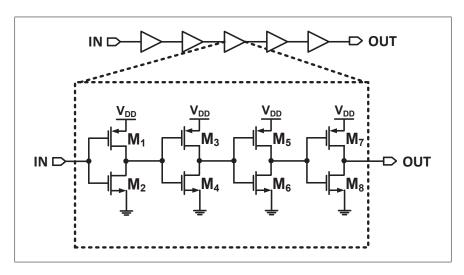

Different types of TDC architectures have been established to process TM information in the range of sub-nanosecond or even sub-picosecond resolution for instrumentation or audio applications. TDCs can be classified into two categories: 1) Nyquist-rate TDCs, which process the TM signals in a memory-less manner; and 2) the oversampled counterparts, which process the previous samples with present TM samples at a rate higher than the minimum Nyquist-rate (Hesener *et al.*, 2007; B. G. Lee, 2015). The simplest design of a Nyquist-rate TDC is a FLASH TDC, which can be implemented by an inverter-based delay-line and a comparator. The main

issue with the FLASH TDC is that its time resolution is limited by the propagation delay of each inverter (Jansson et al., 2009). To achieve a better resolution, pulse shrinking TDC (Chen et al., 2000) and vernier delay line (VDL) TDC (Lu et al., 2012) architectures were developed, where the effective time resolution has been improved to the sub-gate 1 propagation delay timing resolution. Despite these improvements, they consume more power and silicon area as the dynamic range of TDC increases. Another drawback of this approach is that the mismatch between vernier delay elements, limits the application of such designs. In order to facilitate circuit integration and reduce the mismatch, a DLL vernier TDC and vernier-ring oscillator TDC were proposed to stabilize the delay chain in the conventional design against process, voltage, and temperature (PVT) variations (Roberts and Ali-Bakhshian, 2010; Yu et al., 2010). However, time resolution and power consumption in such types of TDCs are identical to the conventional vernier design. To alleviate the aforementioned problems in Nyquist-rate TDCs, two and three dimension vernier TDCs were developed to reduce the length of delay cells for a given full scale range, thus leading to an improvement in reducing the integral nonlinearity (INL) error and jitter (Vercesi et al., 2010; Yu et al., 2010) performance metrics. The main disadvantage of these TDCs is that the frequency range is limited to DC up to a few tens-of-kilo-Hertz.

Oversampling TDCs with quantization noise shaping have recently emerged as a viable alternative approach to improve the time-resolution and overall conversion dynamic range, as in (Young *et al.*, 2010; Gande *et al.*, 2012), that have achieved second-order and third-order noise shaping, respectively. However, these TM $\Delta\Sigma$ TDCs rely on analog intensive approaches as the TM signals are converted back and forth between voltage or current signals. These approaches are less attractive in advanced CMOS processes with low supply voltage and relatively unchanged threshold voltage ( $V_{TH}$ ). For instance, the non-linearity effect of time-to-voltage converter (TVC) or voltage-to-time conversion (VTC) limits the dynamic range of such TDCs. To address this issue, a gated-ring oscillator (GRO) based you TDC was implemented in an

<sup>&</sup>lt;sup>1</sup> sub-gate is a mismatch between two inverter's individual delay values.

all-digital solution (Straayer *et al.*, 2009). This approach nearly halves the chip area and power consumption compared to the conventional designs. However, the GRO-based TDC has some performance limitations, such as limited time-resolution and skew error due to a dead-zone in its hold-time.

In (Elshazly *et al.*, 2014), an open-loop noise-shaping switched-ring oscillator TDC (SROTDC) has been shown to achieve high time resolution with a high oversampling ratio (OSR). In this architecture, the TDC toggles between two high and low frequencies in order to decrease the skew error and charge leakage effects. In (Yu, *et al.*, 2015), a closed-loop 1-3 multistage noise-shaping (MASH) TDC was proposed to increase the order of modulator to achieve better performance (e.g., time resolution, rms noise voltage, bandwidth, SNDR). Although this closed-loop TDC topology is elegant, some drawbacks remain. The first-stage of the proposed MASH architecture is always limited to the first-order noise shaping (i.e., 1-1, 1-2, 1-3 MASH architecture) and there is no opportunities to realize 2-1, 2-2, or 3-2 MASH architecture. In addition, the linearity of GRO-based TDC is restricted by the intrinsic errors of the GRO during the hold time.

#### **Thesis Scope and Contributions**

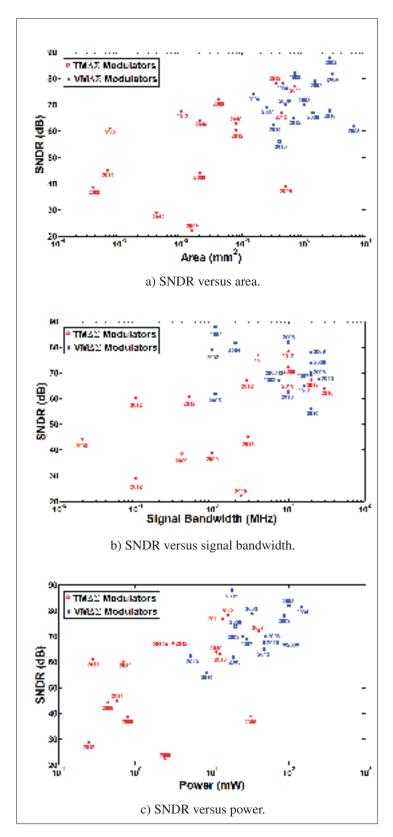

This thesis investigates the performance limitations of an existing type of  $TM\Delta\Sigma$  modulators and compare their performances with the  $VM\Delta\Sigma$  modulators in term of SNDR, silicon area, signal bandwidth, and power consumption. In addition, the maximum achievable SNR of a PMOS-NMOS transistor stack, used as amplifier (VM) or as delay element (TM) is analyzed and examined. This analysis provides new observation in the design of TM circuits in new technology nodes. It addresses how TM circuit could potentially achieve better SNR with technology scaling. Then, we study TM building blocks and how they used in the development of a complex TM mixed-signal circuits. Then, we propose new TM circuits able to cope with the challenges associated with the previous works. This thesis reveals that by adopting TM

circuits a LDI-based resonator and  $BP\Delta\Sigma TDC$  can be implemented using only digital gates. This will prove beneficial in digitization at higher frequency with little power budget, little chip area, and possibility of high-speed operational frequency.

The main contributions of this thesis which led to a book chapter, two journal papers, and three conference papers could be listed as follows:

(a) A comprehensive surveying and comparing of most recent TM $\Delta\Sigma$  modulators is reported (see Chapter 1).

#### **Related publication:**

- S. Ziabakhsh, G. Gagnon, G. W. Roberts, "Book chapter: Time-Mode Delta-Sigma Converters" of book entitled "Time-Mode Delta-Sigma Converters", by author Fei Yuan., CRC Press, Technology and Engineering 412 pages, 2015.

- (b) An analytical expression for the noise operation of both VM and TM PMOS-NMOS transistor stack is proposed (see Chapter 2).

## **Related publication:**

- S. Ziabakhsh, G. Gagnon, G. W. Roberts, "The Peak-SNR Performances of Voltage-Mode versus Time-Mode Circuits: the PMOS-NMOS Stack Use Case," *IEEE Transactions on Circuits and Systems II: Express Briefs*, Accepted March 7, 2018.

- (c) Design, fabrication, and measurement of a TM second-order BP $\Delta\Sigma$ TDC is presented (see Chapter 3).

#### **Related publications:**

S. Ziabakhsh, G. Gagnon, G. W. Roberts, "A Second-Order Bandpass  $\Delta\Sigma$  Time-to-Digital Converter with Negative Time-Mode Feedback," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Submitted April 19, 2018.

- S. Ziabakhsh, G. Gagnon, G. W. Roberts, "A Time-Mode LDI-Based Resonator for a Band-Pass Delta-Sigma TDC", 60th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Boston, USA, 2017.

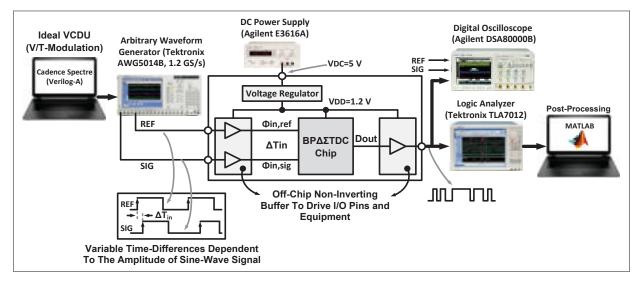

- (d) New measurement setup to validate the operation of BPΔΣTDC is reported. In this measurement, phase modulated signals are produced in Cadence Spectre and imported to the arbitrary waveform generator. Subsequently, there is no non-linearity effect associated to the input TM signals (see chapter 4).

- (e) The new design of VCDU that converts the analog signal into a time-difference signal is proposed. This is achieved by using a signal conditioning circuit to extend the input voltage linear range with very low linearity error (see chapter 5).

#### **Related publication:**

- S. Ziabakhsh, G. Gagnon, G. W. Roberts, "Wide linear range voltage-controlled delay unit for time-mode signal processing", *IEEE International Symposium on Circuits and Systems (ISCAS)*, Portugal, 2015.

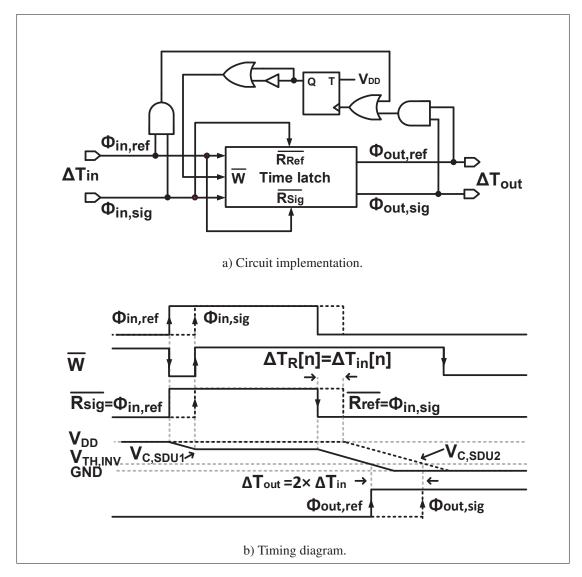

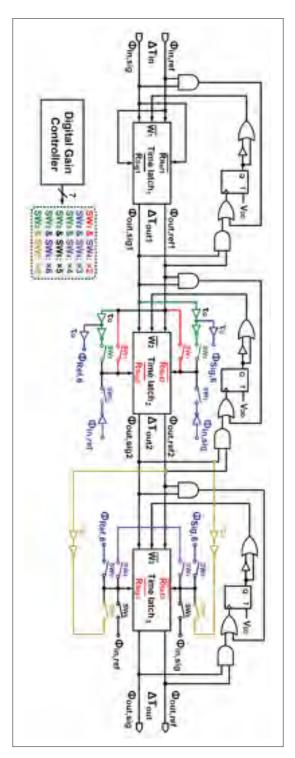

- (f) A novel programmable TLatch-based TDA with femtosecond resolution is presented. The proposed circuit uses three TLatches in its structure with digital switches to control the gain of circuit easily (see chapter 5).

#### **Related publication:**

S. Ziabakhsh, G. Gagnon, G. W. Roberts, "An All-Digital High-Resolution Programmable Time-Difference Amplifier Based on Time Latch", *IEEE International Symposium on Circuits and Systems (ISCAS)*, Italy, 2018.

#### **Thesis Outline**

The thesis is organized into five chapters as follows:

In the first chapter, an overview of the fundamental theory of  $\Delta\Sigma$  modulators and important ADC performance metrics are identified and categorized. It explains the concepts of dynamic range, resolution, distortion, and stability. It also describes the first-order, high-order, and multibit TM  $\Delta\Sigma$  modulators. Chapter two also presents the TM  $\Delta\Sigma$  design issues (i.e., non-linearity, mismatch, etc.) and provides a comparison between TM and VM  $\Delta\Sigma$  modulators.

The second chapter extends the discussion of comparison of VM versus TM circuits and provides a noise analysis for a PMOS-NMOS transistor stack. It presents a detailed noise analysis which includes both thermal and flicker noises in both domains across different technology nodes. The accuracy of the proposed analysis is demonstrated by measurement results and transistor-level transient noise simulations in Spectre. We end the chapter by showing the maximum achievable SNR for both VM and TM circuits in future CMOS technologies.

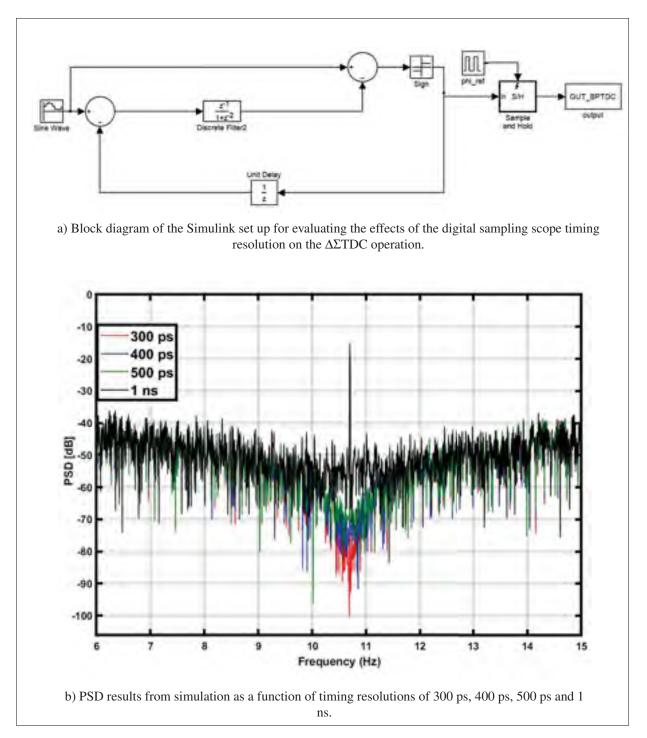

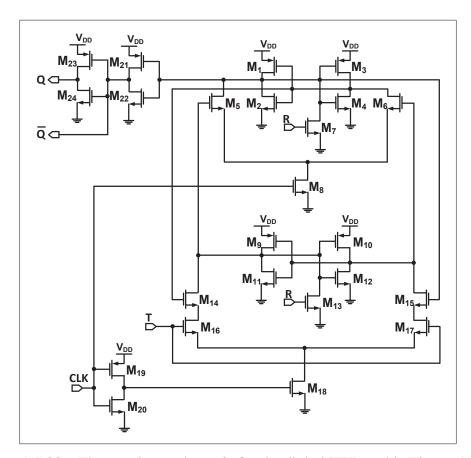

Chapter three covers the design of the individual building blocks of the TM LDI-based resonator; namely the half-period delay unit, cascading of two half-period delay units, adaptive time offset correction, TM subtractor, and half-period delay DTC. For each of the aforementioned TM circuits, we present the principle operation, non-idealities, timing-diagram, and transfer characteristic. Monte-Carlo analysis in Spectre of each of these blocks are presented and discussed. In this chapter, a top-down approach for the design of second-order BP $\Delta\Sigma$ TDC is presented. The design methodology is based on a system-level approach in Simulink/MAT-LAB and modeling each block with the transistor-level design.

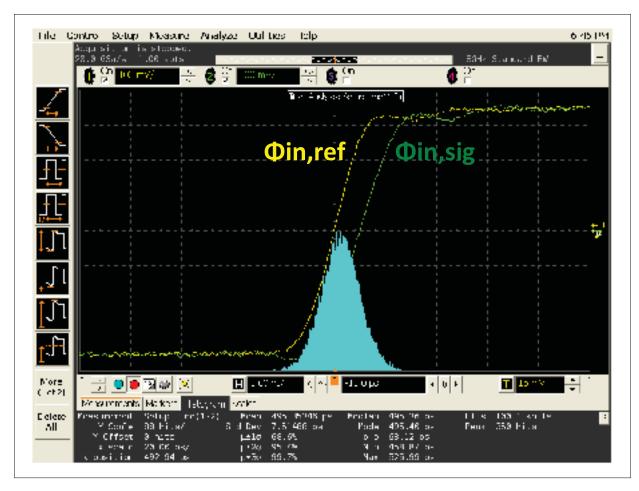

In the fourth chapter, the experimental setup of the  $BP\Delta\Sigma TDC$  is presented. Measurement results from the fabricated chip and simulation results in Spectre and MATLAB are compared and discussed. The TDC covers a sampling frequency range from 4 MHz to 42.8 MHz, and consumed 4.98 mW while operating from a 1.2 V supply voltage.

In chapter five, the design of the wide linear range VCDU needed for the TMSP applications is demonstrated. By doing so, the VCDU utilized a signal conditioning circuit that significantly increases the linear range operation and enhances the SNDR when it is used in a VCDU-based  $\Delta\Sigma$  modulator. Furthermore, a novel all-digital time-difference amplifier (TDA) using time latches was proposed which achieves accurate, high resolution, and programmable gains. Simulation results are provided to verify the operation principles of the two circuits.

Finally, this thesis is concluded where the work is summarized and future advancements of the proposed approach are offered.

#### **CHAPTER 1**

#### FUNDAMENTALS OF TMΔΣ MODULATORS

#### 1.1 Introduction

The aim of this chapter is to describe delta-sigma ( $\Delta\Sigma$ ) converters that adopt TMSP techniques. Recently, several studies on TM $\Delta\Sigma$  converters have been conducted showing that such methodology has high potential in low-voltage design. The noise-shaping behavior demonstrated by this technique can be implemented and extended in various ways, including VCDU or GRObased implementations of TM $\Delta\Sigma$  converters. In this chapter, after a brief review of  $\Delta\Sigma$  ADC specifications, we will discuss different architectures of TM $\Delta\Sigma$  converters that have been recently proposed. The following chapter is based on:

S. Ziabakhsh, G. Gagnon, G. W. Roberts, "Book chapter: Time-Mode Delta-Sigma Converters" of book entitled "Time-Mode Delta-Sigma Converters," by author Fei Yuan., CRC Press, Technology and Engineering-412 pages, 2015.

#### **1.2** Theory of $\Delta\Sigma$ Modulators

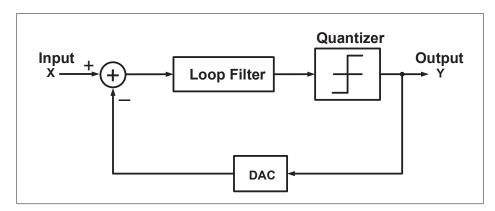

The basic architecture of a conventional  $\Delta\Sigma$  modulator is shown in Figure 1.1. It consists of a difference amplifier, loop filter and an one-bit quantizer in the feed-forward path, and a one-bit digital-to-analog converter (DAC) in the feedback signal path. The front-end difference amplifier and loop filter are often realized using a high-performance SC circuit, and the quantizer is often realized using a high-speed latched comparator circuit. As the DAC provides only one-bit conversion, a simple set of analog switches is used to realize this element. Through the negative-feedback action provided by the feedback path, the effects of non-linearities in the feed-forward signal path are reduced by the loop gain. This action has come to be known in the  $\Delta\Sigma$  modulator literature as noise-shaping (Pavan *et al.*, 2017; Jose *et al.*, 2011; Kozak *et al.*, 2003), where the quantization noise introduced by the quantizer is pushed or shaped away in frequency from the signal band.

In multibit  $\Delta\Sigma$  modulators, the quantizer and the DAC operate on more than two levels and, correspondingly, require a more complicated circuit realization. An important implementation issue with the multibit DAC is the requirement for high linearity. To achieve this result over multiple manufacturing runs, very good element matching is required. However, as the dimensions of CMOS transistors scale downward, matching becomes more difficult to achieve (Yuan *et al.*, 2014). In the following, the basic principles of a  $\Delta\Sigma$  modulator will be described along with its various performance metrics.

Figure 1.1 Basic architecture of a conventional  $\Delta\Sigma$  modulator.

#### **1.2.1** Basic Principles of a $\Delta\Sigma$ Modulator

The process of converting an analog continuous-time signal x(t) into a sequence of digital numbers y[n] requires a front-end anti-aliasing filter circuit, a sample-and-hold (S/H) circuit, and the corresponding multilevel quantizer or ADC circuit as illustrated in Figure 1.2. The front-end low-pass (LP) filter is used to minimize the potential threat of unwanted highfrequency signals from aliasing into the base-band frequency region that the desired signal occupies. The anti-aliasing filter is designed to have a bandwidth equal to the incoming desired signal and a stop-band region very near to one-half the sampling frequency, fs—also referred to the Nyquist frequency. In contrast, an ADC constructed using a  $\Delta\Sigma$  modulator takes on a slightly different realization. While the front-end requires an anti-aliasing filter and an S/H circuit, the quantizer

is realized using a  $\Delta\Sigma$  modulator, followed by a LP brick-wall digital filter used to remove the noise-shaped quantization noise. Unlike a Nyquist-rate ADC that samples the input signal at

Figure 1.2 Two types of ADC schemes.

twice its signal bandwidth, that is,  $f_s = 2 \times f_{BW}$ , a  $\Delta\Sigma$ -based ADC oversamples the incoming signal at a rate much greater than twice the signal bandwidth. The ratio of one-half of the sampling rate to the signal bandwidth  $f_{BW}$  is defined as the OSR, that is,

$$OSR = \frac{f_s/2}{f_{RW}} \tag{1.1}$$

An important advantage of oversampling the incoming signal is that it relaxes the requirements on the anti-aliasing filter circuit. In fact, the anti-aliasing filter is typically implemented with a simple low-order filter that requires little power (Jose *et al.*, 2011). As a means to compare the filter requirements for the two types of ADC schemes, an illustration of the anti-aliasing filter magnitude response is provided in Figure 1.3. In Figure 1.3(a), the magnitude response for the Nyquist-rate ADC filter is shown, and Figure 1.3(b) presents the corresponding response for

the  $\Delta\Sigma$ -based ADC implementation. While each filter has the same analog bandwidth, as it is assumed that each ADC will see the same incoming signal, the transition region of the filter is quite different. The stop-band region for the  $\Delta\Sigma$ -based ADC would be much higher than that required for the Nyquist-rate ADC. This greatly reduces the complexity of the anti-aliasing filter as mentioned earlier. The error between the information carried by the input analog signal

Figure 1.3 Filter requirement.

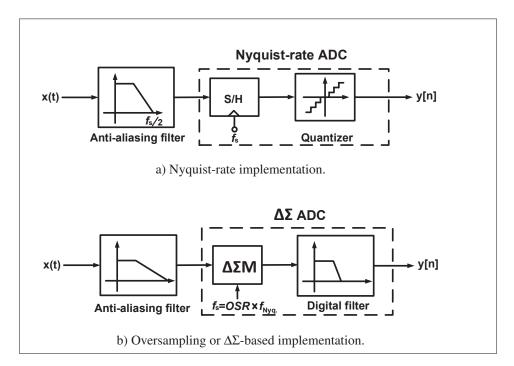

x(t) and the information carried by an ideal quantized output digital signal y[n] is defined as the quantization error. Such a situation is depicted in Figure 1.4 where the transfer characteristic of an ideal quantizer is shown in Figure 1.4(a). Here we see the quantizer has a staircase-like shape with the width of each staircase equal to  $\Delta$ , also referred to as the least-significant bit (LSB) of the analog-to-digital conversion process. When subtracted from a perfect conversion process (one without error, as depicted by the dashed line in Figure 1.4(a)), the quantization error curve results as shown in Figure 1.4(b). The quantization error is bounded between  $-\Delta/2$

and  $+\Delta/2$  for any level of analog input. Also we see that the average error is zero and it has an RMS error defined by

$$e_{rms}^2 = \int_0^1 \left[ e\left(v_{in}\right) \right]^2 dv_{in} = \frac{\Delta^2}{12}$$

(1.2)

Through careful construction, one can show that under certain conditions, this quantization

Figure 1.4 Illustrating the quantization process.

noise power is uniformly distributed in the frequency range (0,  $f_s/2$ ). Based on this criterion, the single-sided quantization noise power spectral density expressed in terms  $V^2/Hz$  can be

defined simply as

$$N_q = \frac{\Delta^2}{6f_s} \tag{1.3}$$

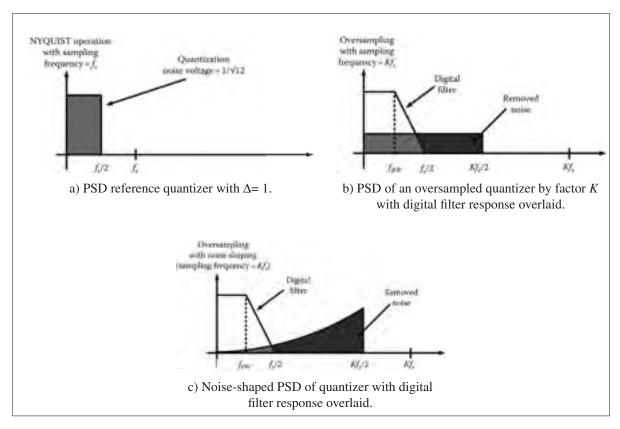

Figure 1.5(a) illustrates the uniform power-spectral density (PSD) of the ideal quantizer with  $\Delta$ = 1. Here the total noise power is equal to 1/12  $V^2$ , which is equivalent to an RMS noise voltage of  $1/\sqrt{12} V$ .

Figure 1.5 Illustrating the effect of oversampling and noise-shaping on the PSD of an ideal quantizer.

From (1.3), the magnitude of the RMS quantization error can be reduced by decreasing the step size of the quantizer. Another approach would be to increase the sampling rate of the quantizer, say by a factor of K, and pass the quantizer output through a LP filter with a bandwidth equal to the signal bandwidth  $f_{BW}$ . By doing so, according to (1.3), the PSD of the quantization noise

will be spread over a larger frequency range  $(0, Kf_s/2)$  with magnitude

$$N_q' = \frac{\Delta^2}{6} \frac{1}{K f_s} \tag{1.4}$$

Since the noise power is uniform over the frequency range  $(0, f_{BW})$ , and since the factor K is equivalent to the OSR parameter introduced earlier, then the total output quantization noise power reduces to

$$e'_{rms} = N'_{q} \times \frac{f_{BW}}{K \times f_{s}/2} = N'_{q} \times \frac{f_{BW}}{OSR \times f_{s}/2}$$

$$(1.5)$$

For a digital filter with transfer function  $H_d(z)$ , the in-band noise power that passes through the filter would be more correctly represented by the integral equation,

$$n_0^2 = \int_{f_1}^{f_2} |H_d(f)| N_q' df \tag{1.6}$$

This situation is depicted in Figure 1.5(b) where the quantization noise PSD is spread over a bandwidth of  $Kf_s$ , but only a portion of the noise passes through the digital filter.

Equation (1.5) reveals two important facts related to oversampling, followed by LP filtering: (1) The higher the oversampling factor OSR, the smaller is the output RMS error, and (2) the smaller the signal bandwidth, the smaller is the RMS noise error. To gain, say, a 10 dB improvement in noise reduction would require a 10-fold increase in the sampling rate. Any further noise power reduction would come at the expense of impractical increases in the sampling rate of the quantizer.

$\Delta\Sigma$ -based analog-to-digital conversion provides an alternative means in which to reduce the magnitude of the quantization noise at the ADC output. Through the application of noise-shaping, the feedback loop established around the quantizer reduces the amount of quantization that makes its way to the output based on the amount of gain in the feedback loop. Mathematically, this effect can be quantified by writing an expression for the output signal Y(z) in the

z-domain in terms of the input signal X(z) and the quantization error signal E(z), according to

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(1.7)

where STF(z) and NTF(z) are denoted as the signal and noise transfer functions, respectively. For a first-order LP  $\Delta\Sigma$  modulator, the output signal in the z-domain is expressed as

$$Y_{LP}(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(1.8)

leading to  $STF = z^{-1}$  and  $NTF = 1 - z^{-1}$ . The signal transfer function (STF) simply signifies that the output will contain a one-clock period delay of the input signal, essentially with the input information unchanged. In the case of the noise transfer function (NTF), a transmission zero appears at DC, corresponding to a gain of 0. Likewise, at the Nyquist frequency, that is,  $f = f_s/2$ , the NTF has a gain of 2. For frequencies between DC and Nyquist, the NTF will have a high-pass behavior. Consequently, the quantization noise injected by the quantizer will have little effect on the incoming signal at low frequencies but doubles up for frequencies close to the Nyquist frequency. This situation is illustrated in Figure 1.5(c) whereby noise shaping combined with digital filtering greatly reduces the level of output quantization noise.

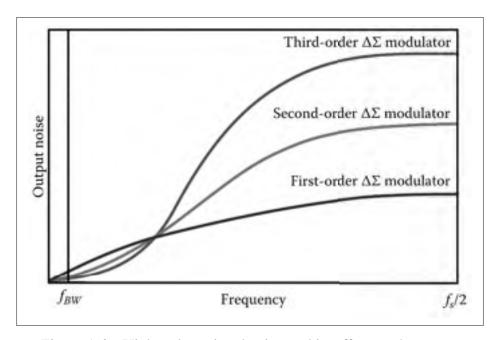

For higher-order modulators, whereby the NTF is of order greater than 1, even less quantization noise power will appear at the output. This is illustrated in Figure 1.6 where the quantization noise PSD appears at the output of the  $\Delta\Sigma$  modulator for orders of 1, 2, and 3. As is evident from this plot, the higher the modulator order, the lower is the quantization noise PSD at frequencies close to DC.

## 1.2.2 Some ADC Performance Metrics

The most commonly quoted ADC performance parameters are sampling frequency, DR, resolution, distortion, power dissipation, chip area, and stability. These metrics will be defined and discussed in the following.

Figure 1.6 High-order noise shaping and its effect on the output quantization noise PSD.

# 1.2.2.1 Sampling Frequency

Generally speaking, the sampling frequency is defined as the rate at which the sampling process takes place. This parameter in Nyquist-rate ADCs is set to twice the signal bandwidth and in  $\Delta\Sigma$ ADCs is set to higher values to significantly decrease the in-band quantization noise. On the other hand, higher sampling frequencies lead to higher power consumption and increased sensitivities to clock jitter issues. High-order and multibit  $\Delta\Sigma$  modulators are two techniques that can be used to compensate for these effects and lead to higher performance ADCs.

#### 1.2.2.2 Dynamic range

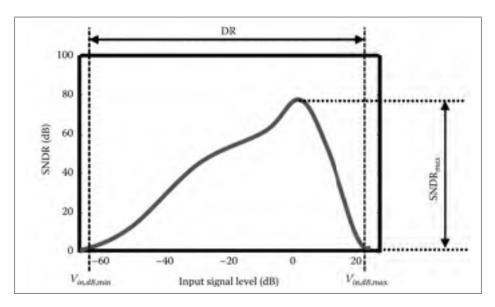

Dynamic range (DR) is defined as the ratio between the maximum applied sinusoidal input signal to the smallest that is discernible at the output of the ADC from any other unwanted or undesirable signal created by the ADC, for example, quantization and thermal noise, and distortion. The simplest manner in which to extract the DR metric is to measure the SNDR as a function of the input signal level, such as that shown in Figure 1.7. The DR metric expressed

in dB would then be defined as the difference in the maximum and minimum input levels in dB for which the SNDR=0 dB, that is,

$$DR|_{dB} = V_{in,max,dB} - V_{in,min,dB}$$

$$\tag{1.9}$$

Figure 1.7 High-order noise shaping and its effect on the output quantization noise PSD.

Often, in practice, the maximum input level will be limited by the power supply or some other upper limit instead of the SNDR value falling back to the 0 dB level. Nonetheless, Figure 1.7 conveys the general idea behind the DR metric.

As CMOS technology advances to smaller dimensions, one observes that the DR of ADCs tends to decrease, a result attributed to smaller transistor gate oxide, lower supply voltages, and greater transistor thermal noise levels. Novel signal processing methods like TMSP may help to resolve the DR issue in advanced CMOS processes (Taillefer, *et al.*, 2009).

#### 1.2.2.3 Resolution

The resolution of an N-bit ADC is defined as the smallest change in the analog input voltage that leads to a corresponding consistent change in the digital code output. In terms of our previous discussion related to Figure 1.4, the resolution of an ideal quantizer would simply be equal to the width of the staircase specified by  $\Delta$ . In the ideal case,  $\Delta$  would be defined in terms of the full-scale output range (FSR) and the total number of bits specified by the architecture, N, given by the following expression

$$\Delta = \frac{FSR}{2^N - 1} \tag{1.10}$$

A related metric, but one that is easier to extract in practice, is called the effective resolution of the ADC,  $\Delta_{eff}$ , and is defined in terms of the effective number of bits (ENOBs) of the ADC in the following way:

$$\Delta_{eff} = \frac{FSR}{2^{ENOB} - 1} \tag{1.11}$$

Here ENOB represents the maximum value of the SNDR plot (see Figure 1.7) converted from dBs to equivalent bits (Plassche *et al.*, 2013) using the following formula

$$ENOB = \frac{SNDR|_{max} - 1.76 \, dB}{6.02} \tag{1.12}$$

The effective ADC resolution is always less than the ideal ADC resolution, that is,  $\Delta_{eff} < \Delta$ .

#### **1.2.2.4 Distortion**

Signal distortion occurs with increasing input signal level on account of the general nonlinear nature of semiconductor devices, in addition to mismatches between ADC elements. One attractive technique to compensate for component mismatch effects is to include circuits that average out any component mismatch. Some of these approaches are: offset cancellation

(Razavi *et al.*, 1992), DLL (Roberts *et al.*, 2010), dynamic element matching (DEM) (Ninh *et al.*, 2011), and laser trimming during postpackaging manufacturing.

# 1.2.2.5 Power Dissipation and Chip Area

In the design of ADC circuits, there are two important requirements that must be taken into account. This includes both the ability to achieve good performance and low power operation, as well as a small silicon footprint. With the ongoing scaling-down of CMOS technology, power consumption is expected to decrease as the supply voltage must be reduced. On the other hand, reducing the supply voltage causes several drawbacks in the corresponding analog circuits (such as reducing DR, increasing the switching noise and gate leakage, etc.) especially when the performance requirements are to be maintained, for example, build a 12-bit ADC. One way to overcome these limitations in low-voltage design is to shift the analog design to the digital domain in an attempt to be more compatible with modern CMOS technologies. To this end, in this chapter, we offer several novel techniques that perform analog-to-digital conversion in the time-domain without consuming large amounts of power or die area—hopefully, fulfilling the goal of achieving high-resolution analog circuits in nanometer CMOS technologies.

## 1.2.2.6 Stability Considerations

It is well known by ADC designers that high-order  $\Delta\Sigma$  modulators can become unstable. In (Norsworthy *et al.*, 1997), the stability of a sixth-order modulator is evaluated. They show that changing the gain of quantizer can change the location of closed-loop poles and cause instability. The main reason is that for some unique values of quantizer gain, the poles move outside of the unit circuit in the z-domain and cause the modulator to go unstable. Several works have followed this line of reasoning and have attempted to model this effect in  $\Delta\Sigma$  modulators. The basic model is to replace the quantizer with a two-input adder, having one input from the quantizer and the other connected to a source of additive noise modeling the quantization process. While this model defines the noise-shaping process described earlier in the usual way, it places emphasis on the lack of knowledge related to the noise properties of

the quantizer and the fact that the stability of the modulator cannot be determined without this knowledge. Research is presently ongoing and further details can be found in (Bairdy *et al.*, 1994; Macii *et al.*, 2006; Lota *et al.*, 2014).

#### 1.3 First-order Single-Bit TM $\Delta\Sigma$ Modulators

It is the intent of this section to learn about various  $\Delta\Sigma$  modulators implemented using TMSP techniques that have been published in recent years. The various architectures have been classified according to either their key building block or some distinguishing architectural feature. This will include a discussion on a VCDU-based  $\Delta\Sigma$  modulator, an open-loop  $\Delta\Sigma$  modulator design approach, a DLL-based  $\Delta\Sigma$  modulator, and a TDC-based  $\Delta\Sigma$  modulator.

#### 1.3.1 VCDU-Based $\Delta\Sigma$ Modulator

$v_{in}$ .

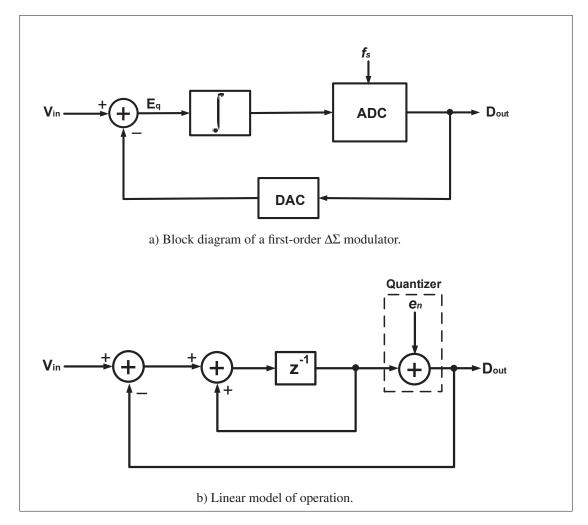

Let us begin by considering a first-order  $\Delta\Sigma$  modulator with sampled-data input signal,  $v_{in}[n]$ , whereby the loop filter is implemented with a first-order discretetime integrator, an analog summer, a quantizer with a 1-linear bit ADC with output  $D_{out}[n]$ , and a 1-bit DAC in the feedback path as shown in Figure 1.8(a). Assuming a linear model for the quantizer with error e[n], a first-order  $\Delta\Sigma$  modulator can be described with the block diagram shown in Figure 1.8(b). Writing the output signal  $D_{out}[n]$  in terms of the two inputs  $v_{in}[n]$  and e[n], one obtains the following time-difference equation

$$D_{out}[n] = v_{in}[n-1] + (e[n] - e[n-1])$$

(1.13)

The aforementioned equation reveals the error feedback nature of the  $\Delta\Sigma$  modulator whereby the digital output is a sum of the input and the first-order time difference of the quantizer error. If the quantizer errors e[n] and e[n-1] are similar, that is, through oversampling, their contribution will be small and the output  $D_{out}$  will be a very good approximation to the input

Figure 1.8 First-order  $\Delta\Sigma$  modulator

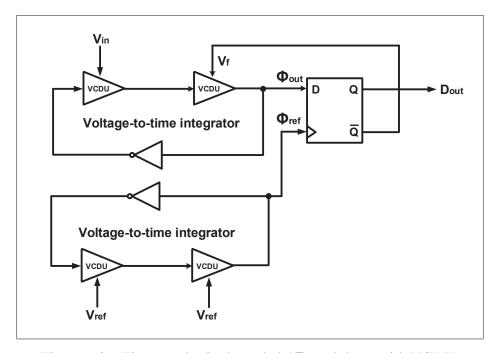

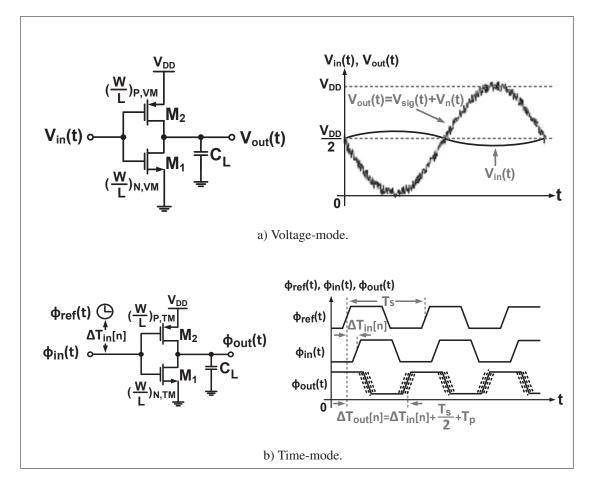

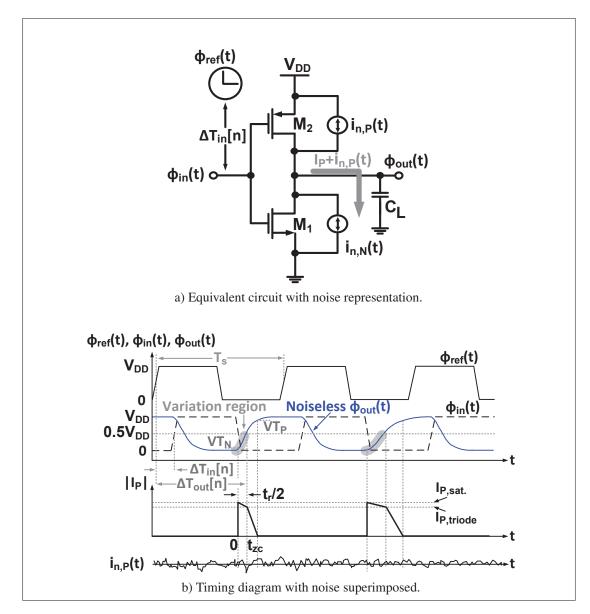

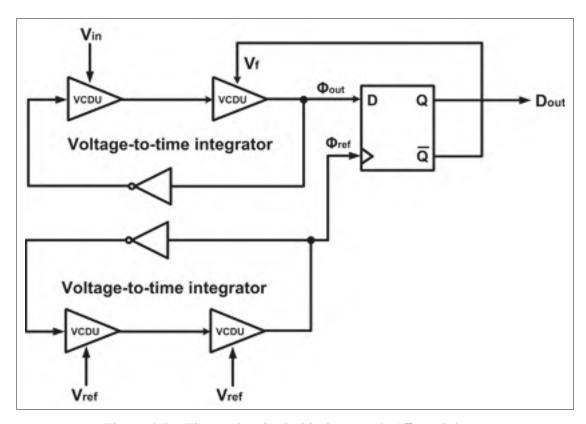

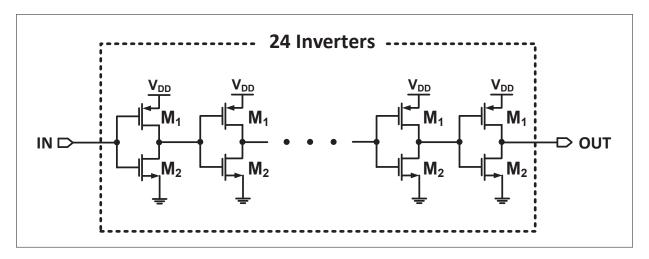

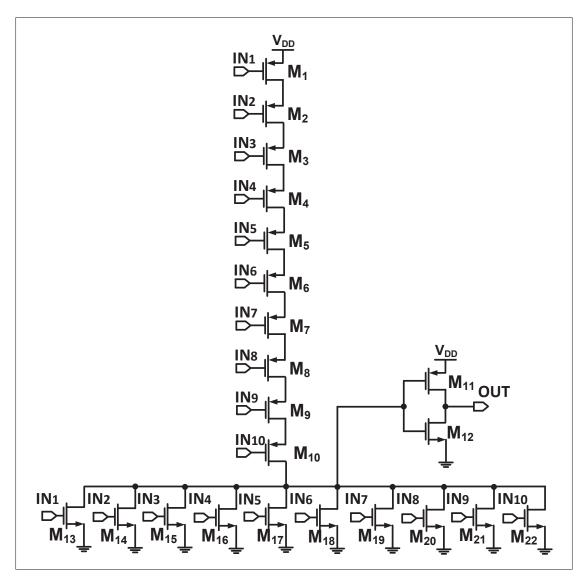

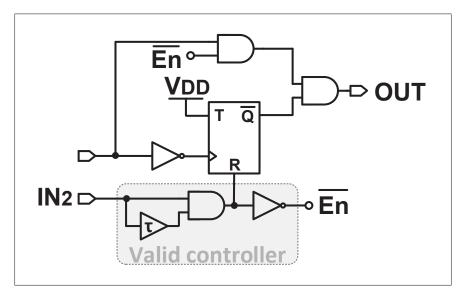

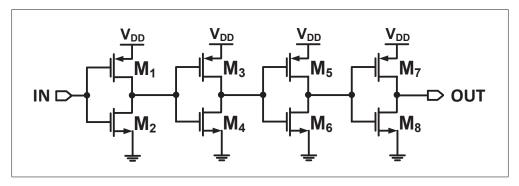

An approach introduced in (Taillefer *et al.*, 2009) that implements a similar first-order difference equation is shown in Figure 1.9. Here a noise-shaped error behavior is realized by two voltage-controlled ring oscillators that perform phase integration followed by a D-type flip-flop (DFF) and some digital inverters. The two ring oscillators are constructed using two sets of VCDUs whose output is fed back to its input via a single inverter circuit.

The DFF is employed as a 1-bit quantizer.

In this design, the period of oscillation of the bottom-most ring oscillator is governed by the reference voltage,  $V_{ref}$ . By keeping this quantity fixed to a constant value, the period or fre-

Figure 1.9 Time-mode single-ended  $\Delta\Sigma$  modulator with VCDU.

quency of this oscillator is held constant. The period of the top-most integrator is controlled by the input voltage  $v_{in}[n]$  and the digital output of the modulator through the two input control terminals via the VCDUs. The difference in phase of the leading edge of the two ring oscillators is compared by the DFF. If the phase of the reference oscillator output denoted by  $\Phi_{ref}$  lags the phase of the output of the input-controlled oscillator  $\Phi_{out}$ , the flip-flop will output logic 1, otherwise it will output logic 0. As the output of the flip-flop is also fed back to control the oscillation frequency of the top oscillator, a noise-shaping action occurs. Following the mathematical development given in (Taillefer *et al.*, 2009), the difference equation between the input and output of the  $\Delta\Sigma$  modulator is found to be

$$D_{out}[n] = v_{in}[n-1] + \frac{T_e[n] - T_e[n-1]}{G_{\phi}}$$

(1.14)

where

$G_{\phi}$  is the voltage-to-time conversion factor of the VCDUs

$T_e[n]$  is the error sequence made by DFF

When compared to the difference equation derived for the first-order modulator provided in (1.15), one finds that they have similar form.

#### 1.3.2 Open-loop $TM\Delta\Sigma$ Modulators

Another approach to perform analog-to-digital conversion is based on the application of a VCO or a GRO running in an open-loop manner followed by a digital counter or filter circuit (Kim *et al.*, 2006; Straayer *et al.*, 2008; Kim *et al.*, 2010; Si *et al.*, 2012; Yu *et al.*, 2013). These time-based architectures have some interesting features. For one, they all employ noise shaping but in a very simple and direct manner. Because of their simplicity, they require little power and are easily adapted to advanced CMOS processes. In this section, four types of open-loop approaches for TM $\Delta\Sigma$  modulation will be described: (1) VCO-based Open-Loop TM $\Delta\Sigma$  modulator, (2) GRO-based Open-Loop TM $\Delta\Sigma$  modulator, (3) vernier GRO-Based  $\Delta\Sigma$  modulator, and (4) SRO-based  $\Delta\Sigma$  modulator.

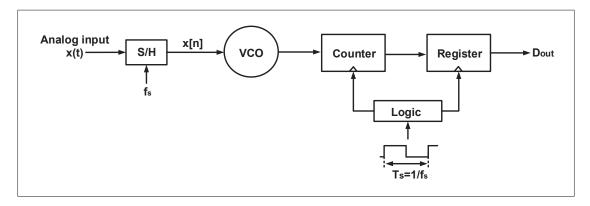

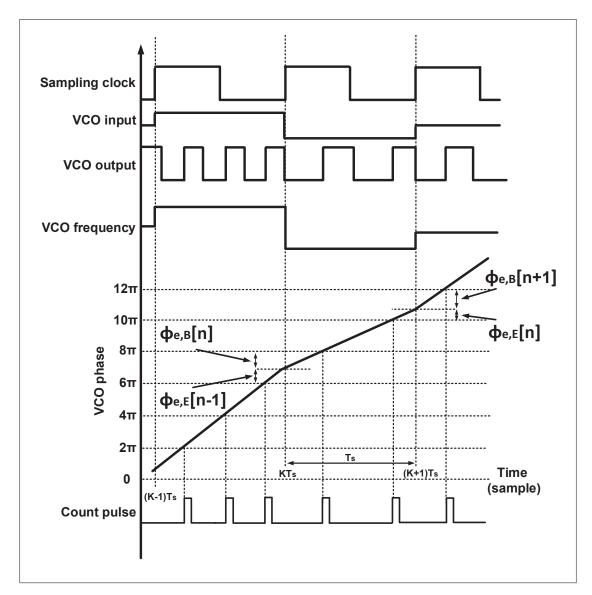

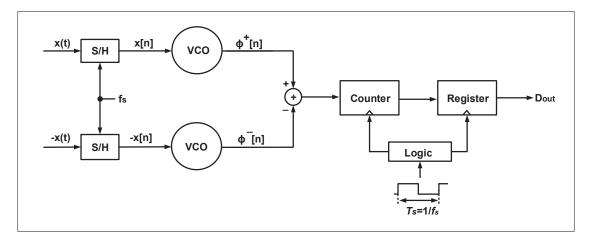

Figure 1.10 VCO-Based Open-Loop  $\Delta\Sigma$ ADC.

## 1.3.2.1 VCO-Based Open-Loop TMΔΣ Modulator

A VCO-based open-loop  $\Delta\Sigma$ ADC is shown in Figure 1.10, which consists of a front-end S/H stage, followed by a ring-VCO and a counter, register, and some logic (F. Yuan, 2014). Here the output digital count  $D_{out}[n]$  represents discrete samples of the input signal of x[n] in some

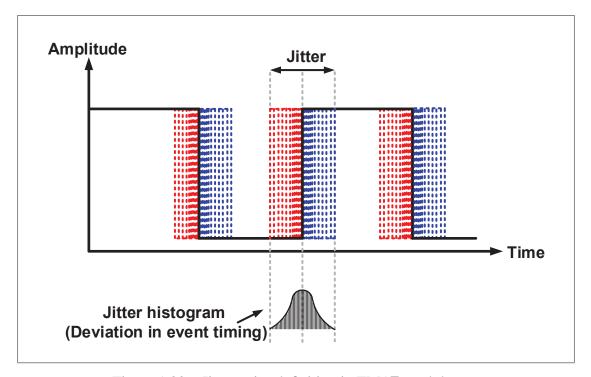

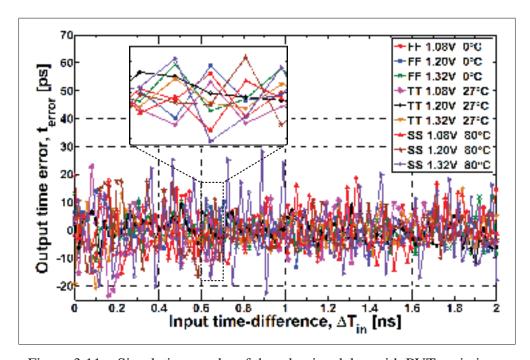

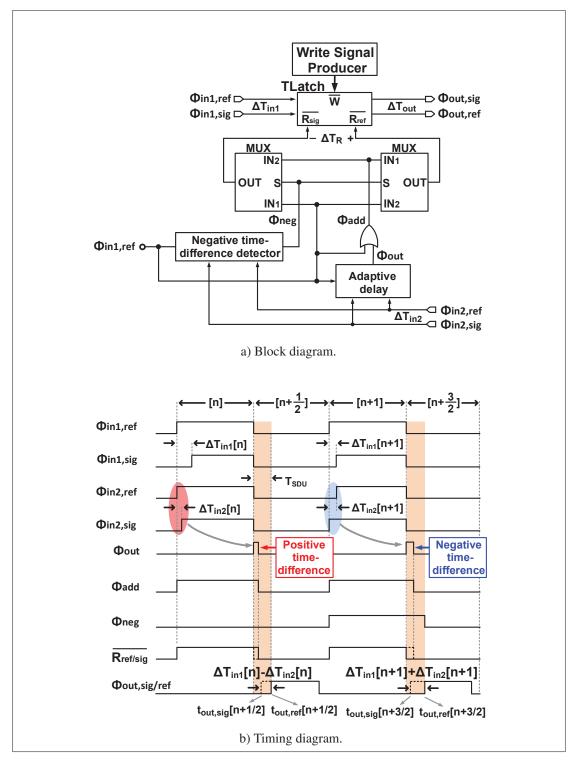

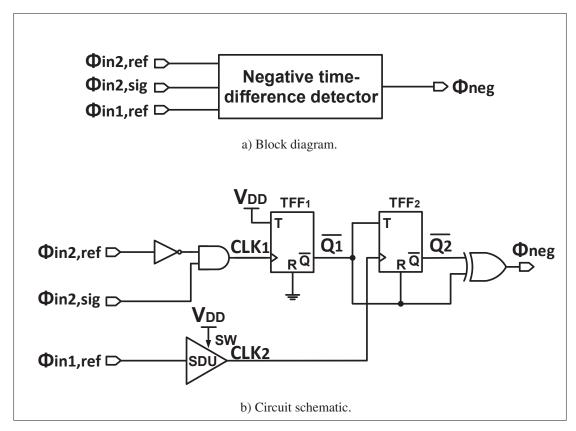

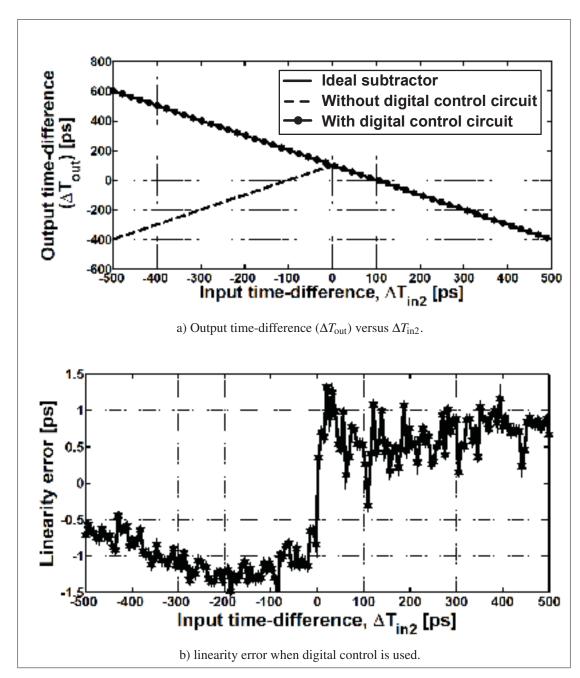

general form such as