ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

M.Ing.

PAR

RANDOLPH , Floris

CARACTÉRISATION DES CIRCUITS RF PAR DES DISPOSITIFS DE MESURE

INTÉGRÉS

MONTRÉAL, LE 6 DÉCEMBRE 2007

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE :

M. Ammar KOUKI, directeur de mémoire

Département de génie électrique à l'École de technologie supérieure

M. Vahé NERGUIZIAN, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Cevdet AKYEL, membre du jury

Département de génie électrique à l'École Polytechnique de Montréal

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 06 NOVEMBRE 2007

À L' ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

Je voudrais à travers ce mémoire exprimer ma profonde gratitude et mes remerciements à M. Ammar Kouki pour avoir accepté diriger ce travail. Ses critiques sincères et cohérentes m'ont permis de mener à bien ce projet. Sa capacité technique et son attention auditive m'ont aidé à orienter efficacement le déroulement de ce travail.

Je tiens également à remercier tous les professionnels, stagiaires et étudiants du Laboratoire de Communication et d'Intégration à la Micro Électronique (LACIME) de l'École de technologie supérieure qui ont d'une manière ou d'une autre contribué à la réalisation de ce travail. Plus particulièrement M. Christian Talbot qui a su guider mes premiers pas dans ce laboratoire de recherche.

J'exprime ma reconnaissance à Monsieur Cevdet Akyel, Professeur à l'École Polytechnique de Montréal et membre de jury pour ses conseils grâce auxquels j'ai énormément appris.

Je remercie Monsieur Vahé Nerguizian pour l'honneur qu'il m'a fait en acceptant être président de jury.

Enfin je remercie de tout mon cœur mes parents et amis pour le soutien moral indéfectible dont ils m'ont gratifié tout au long de ces années de recherche, en l'occurrence ma mère à qui je dédie ce mémoire.

# CARACTÉRISATION DES CIRCUITS RF PAR DES DISPOSITIFS DE MESURE INTÉGRÉS

Randolph Floris

## RÉSUMÉ

Le contexte actuel du marché des télécommunications connaît une demande sans cesse croissante des systèmes sans fils devant être dotés d'agilité, de flexibilité et de reconfigurabilité de sorte à s'affranchir de l'éternel problème de largeur de bande.

Étant donné que l'agilité peut entraîner des changements d'impédance et des performances des composantes radio fréquences, la section RF se veut alors la réalisation de tels systèmes tout en intégrant des technologies de moindres coûts. Pour ce faire, il faudra les caractériser en temps réel.

Notre travail se situe dans ce contexte de caractérisation embarquée en temps réel des circuits et composants RF. Le dispositif de caractérisation proposé dans ce mémoire consiste en un circuit intégrant le détecteur de phase et de gain AD8302 d'Analog Devices. Ce composant prend à ses entrées, deux signaux RF et produit deux tensions DC représentant leur rapport en amplitude ainsi que leur différence en phase.

L'extraction de ces paramètres offre plusieurs applications dont la calibration automatique d'un circuit de transmission par l'entremise d'une plateforme numérique, l'analyse de charges complexes à une fréquence précise ou sur une bande de fréquences donnée (100MHz à 2.7 GHz).

Le dispositif permettra de mesurer entre autre le coefficient de réfection à l'instar de l'analyseur de réseau, le gain d'un amplificateur, le déphasage entre les entrée et sortie d'un amplificateur ou d'un mélangeur, via des coupleurs. Une procédure de correction adéquate s'impose puis que les signaux deviennent couplés lorsqu'on utilise des coupleurs.

Le système est piloté par une interface de contrôle et d'acquisition de données développée sur HP-VEE.

Les mesures obtenues avec ce nouveau système ont été comparées et validées à l'analyseur de réseau vectoriel

# **EMBEDDED MEASUREMENTS OF RF INTELLIGENT CIRCUITS**

Randolph Floris

## **ABSTRACT**

The current context of the telecommunication's market is witnessing an increasing demand of wireless systems with additional requirements on agility, flexibility and reconfigurability. Such characteristics would help bring about more cost effective solutions to the age-old problem of bandwidth.

If such solutions are to be reached, then the RF section must meet these requirements while integrating technologies of low costs. One key step in this process is the real time characterization of RF circuits and subsystems so that their state may be adjusted reconfigured as needed to meet the system requirements.

In this paper, we present one possible characterization device using a low cost circuit integrating the gain and phase detector AD8302 of Analog Devices. This component requires two RF-coupled input signals and provides two output voltages proportional to the magnitude ratio and the phase difference of the RF signals. Tests show that when this circuit is driven by decoupled sources, i.e., two independent generators, relatively easy extraction of the complex ratio can be achieved. However, when used through couplers, as would be the case in actual applications, the signals input to the AD8302 are mixed. Consequently a proper procedure for error correction and de-embedding is necessary. Here we propose one such approach based on a characterization of the coupler used in addition to calibration of the AD8302 receiver through a power and phase shift sweep using two independent sources.

With this system in place, it will be used for several applications with the main one being coupling it to tunable MEMS circuit and a chip transistor to dynamically match an amplifier circuit for various operating conditions, namely at different frequencies in the range 700 MHz to 2.7 GHz.

## TABLE DES MATIÈRES

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| INTRODUCTION.....                                                                | 1  |

| CHAPITRE 1 SYSTÈMES ACTUELS DE CARACTÉRISATION DES CIRCUITS<br>MICRO -ONDES..... | 1  |

| 1.1    Introduction .....                                                        | 1  |

| 1.2    Les analyseurs de réseau hétérodynes .....                                | 1  |

| 1.2.1    Principe de fonctionnement.....                                         | 2  |

| 1.2.2    Avantages et inconvénients reliés au système hétérodyne.....            | 3  |

| 1.3    Les analyseurs de réseau homodynes.....                                   | 3  |

| 1.3.1    Principe de la méthode six- port.....                                   | 4  |

| 1.3.2    De la jonction six- port à l'analyseur de réseau six- port.....         | 6  |

| 1.3.3    Équations régissant le fonctionnement de la jonction six- port .....    | 7  |

| 1.3.4    Techniques de calibration de la jonction six- port .....                | 9  |

| 1.3.5    Étalonnage treize standards.....                                        | 11 |

| 1.3.6    Boîte d'erreur .....                                                    | 12 |

| 1.3.7    Mesure de performance du six- port .....                                | 13 |

| 1.3.8    Avantages et inconvénients des analyseurs de réseau homodynes .....     | 13 |

| 1.4    Nouvelle approche de caractérisation .....                                | 14 |

| 1.5    Conclusion.....                                                           | 15 |

| CHAPITRE 2 ÉTUDE ET CARACTÉRISATION DE LA CARTE AD8302 D' ANALOG<br>DEVICES..... | 16 |

| 2.1    Introduction .....                                                        | 16 |

| 2.2    Description du système .....                                              | 17 |

| 2.2.1    Principe de fonctionnement.....                                         | 17 |

| 2.2.2    Caractéristiques du DGP .....                                           | 19 |

| 2.2.3    Spécifications .....                                                    | 21 |

| 2.2.4    Applications .....                                                      | 23 |

| 2.3    Caractérisation du DPG.....                                               | 23 |

| 2.3.1    Présentation du logiciel HP VEE .....                                   | 23 |

| 2.3.2    Description de l'appareillage .....                                     | 24 |

| 2.3.2.1    Générateurs de signaux RF .....                                       | 24 |

| 2.3.2.2    Source d'alimentation .....                                           | 25 |

| 2.3.2.3    Multimètres .....                                                     | 25 |

| 2.3.3    Fonctions de transfert expérimentales.....                              | 25 |

| 2.3.3.1    Fonctions de transfert en amplitude .....                             | 27 |

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| 2.3.3.2 Fonctions de transfert en phase .....                                                      | 28 |

| 2.3.4 Mesure expérimentale de l'impédance d'entrée du DPG.....                                     | 30 |

| 2.4 Extraction d'amplitude et de phase .....                                                       | 31 |

| 2.4.1 Extraction d'amplitude.....                                                                  | 31 |

| 2.4.2 Extraction de phase .....                                                                    | 33 |

| 2.4.2.1 Techniques de résolution d'ambiguïté de phase .....                                        | 33 |

| 2.4.2.2 Présentation de résultats .....                                                            | 36 |

| 2.5 Étude de performance de la carte en modulation AM.....                                         | 37 |

| 2.5.1 Rappel théorique sur la modulation AM.....                                                   | 37 |

| 2.5.2 Résultats en modulation AM.....                                                              | 39 |

| 2.6 Conclusion.....                                                                                | 39 |

| <br>CHAPITRE 3 MESURES DE PARAMÈTRES S À L'AIDE DU DISPOSITIF DE<br>MESURE INTÉGRANT L'AD8302..... | 41 |

| 3.1 Introduction .....                                                                             | 41 |

| 3.2 Description du banc de test .....                                                              | 41 |

| 3.3 Technique de mesure de paramètres S .....                                                      | 43 |

| 3.4 Configuration en mode réfléctomètre .....                                                      | 44 |

| 3.4.1 Détermination de coefficient de réflexion.....                                               | 44 |

| 3.4.2 Diagramme de fluence .....                                                                   | 46 |

| 3.4.3 Règle de Mason .....                                                                         | 49 |

| 3.4.4 Expression mathématique de la réflexion .....                                                | 50 |

| 3.4.5 Réflectométrie à deux coupleurs .....                                                        | 52 |

| 3.4.6 Procédure d'étalonnage .....                                                                 | 56 |

| 3.5 Configuration en mode mesure de gain.....                                                      | 57 |

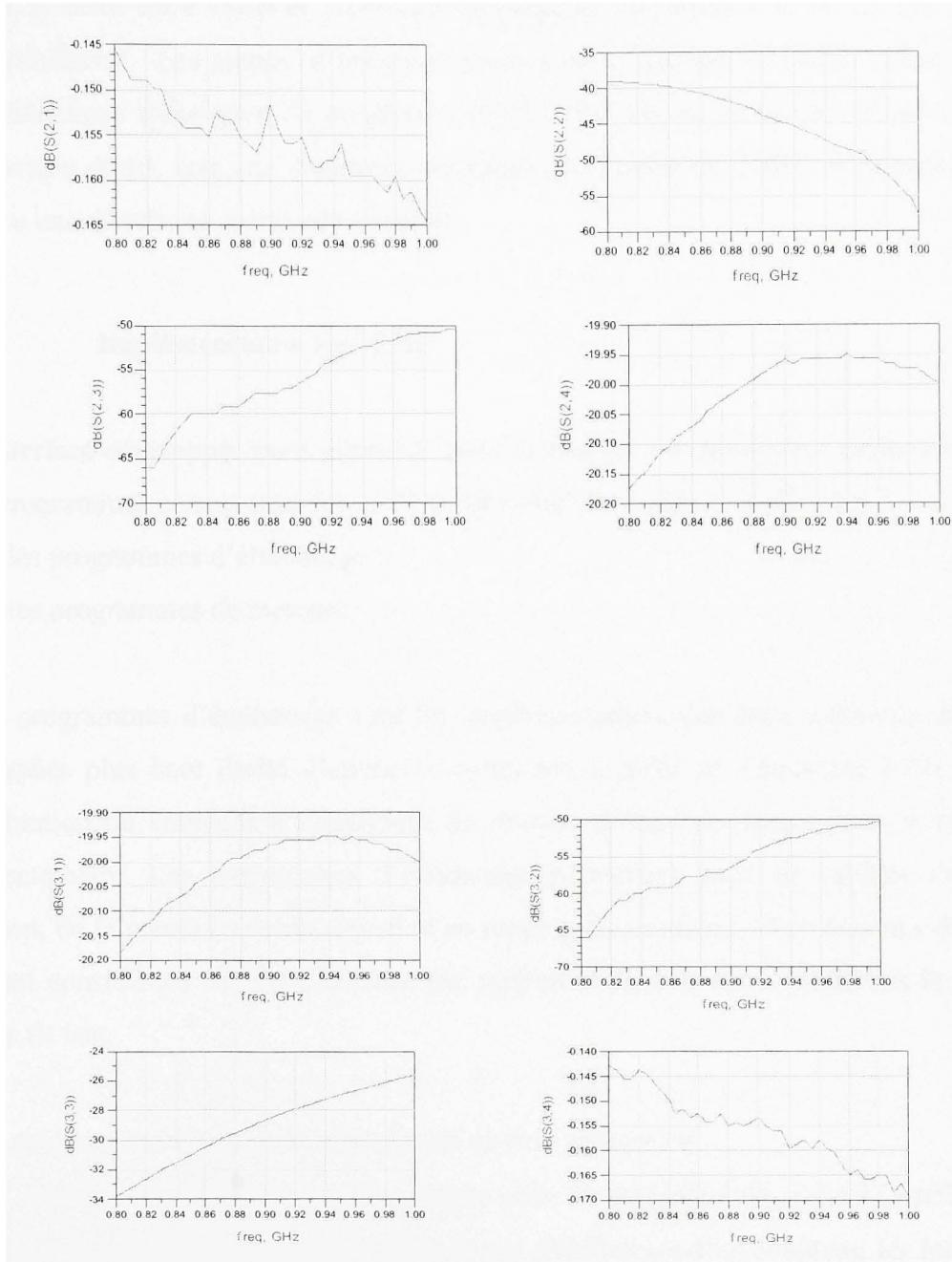

| 3.6 Choix et caractérisation des coupleurs .....                                                   | 60 |

| 3.7 Implémentation logicielle.....                                                                 | 64 |

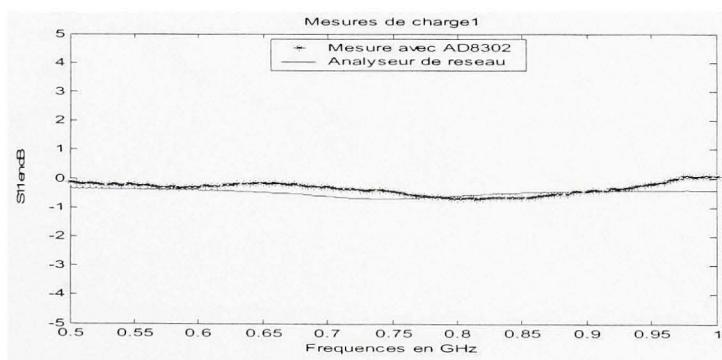

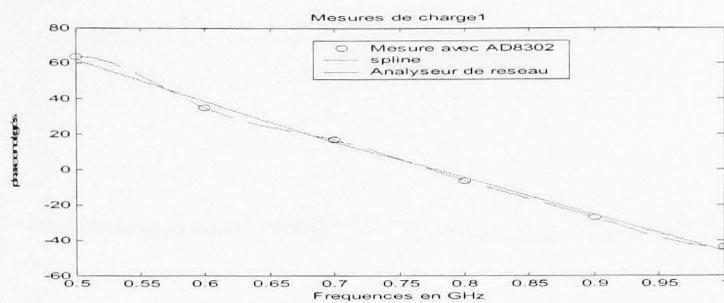

| 3.8 Validation de mesure de réflexion.....                                                         | 65 |

| 3.9 Validation de mesure de gain .....                                                             | 74 |

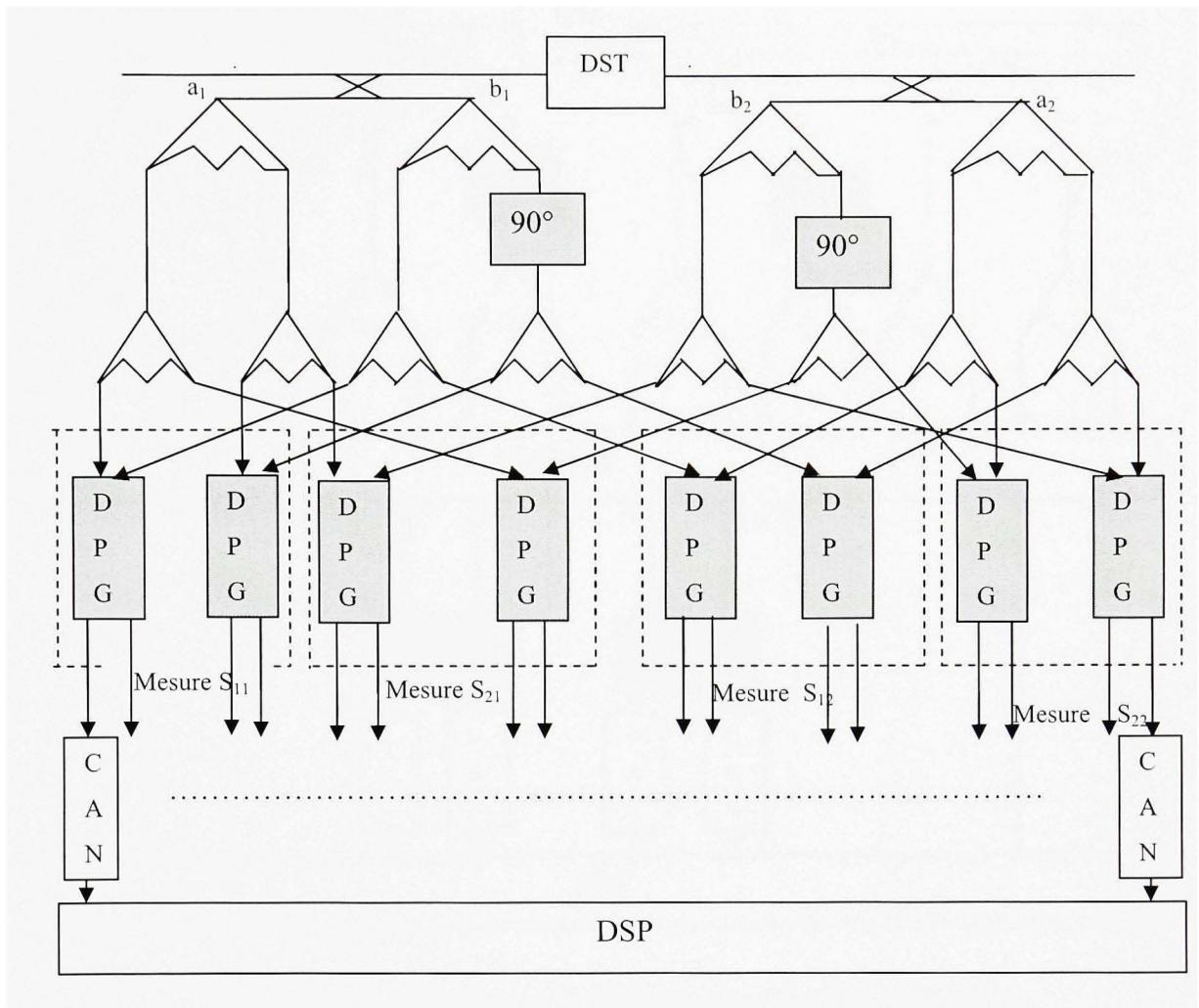

| 3.10 Mesure de paramètre S d'amplificateur .....                                                   | 77 |

| 3.11 Conclusion.....                                                                               | 79 |

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

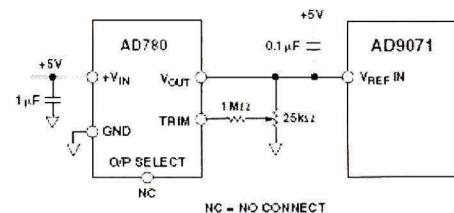

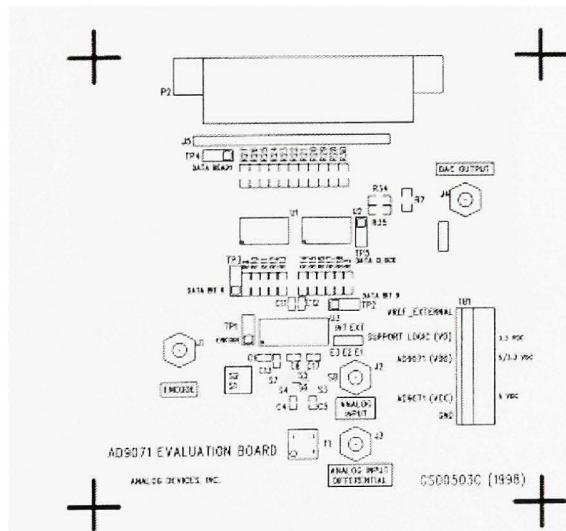

| CHAPITRE 4 APPLICATION AU SYSTÈME RF INTELLIGENT : MESURE<br>EMBARQUÉE..... | 80  |

| 4.1        Introduction .....                                               | 80  |

| 4.2        Les systèmes RF intelligents .....                               | 80  |

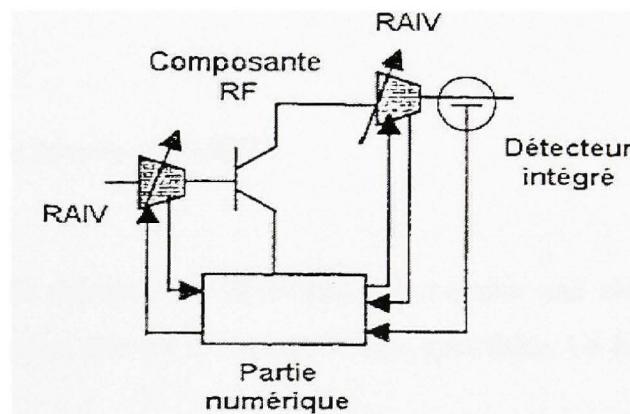

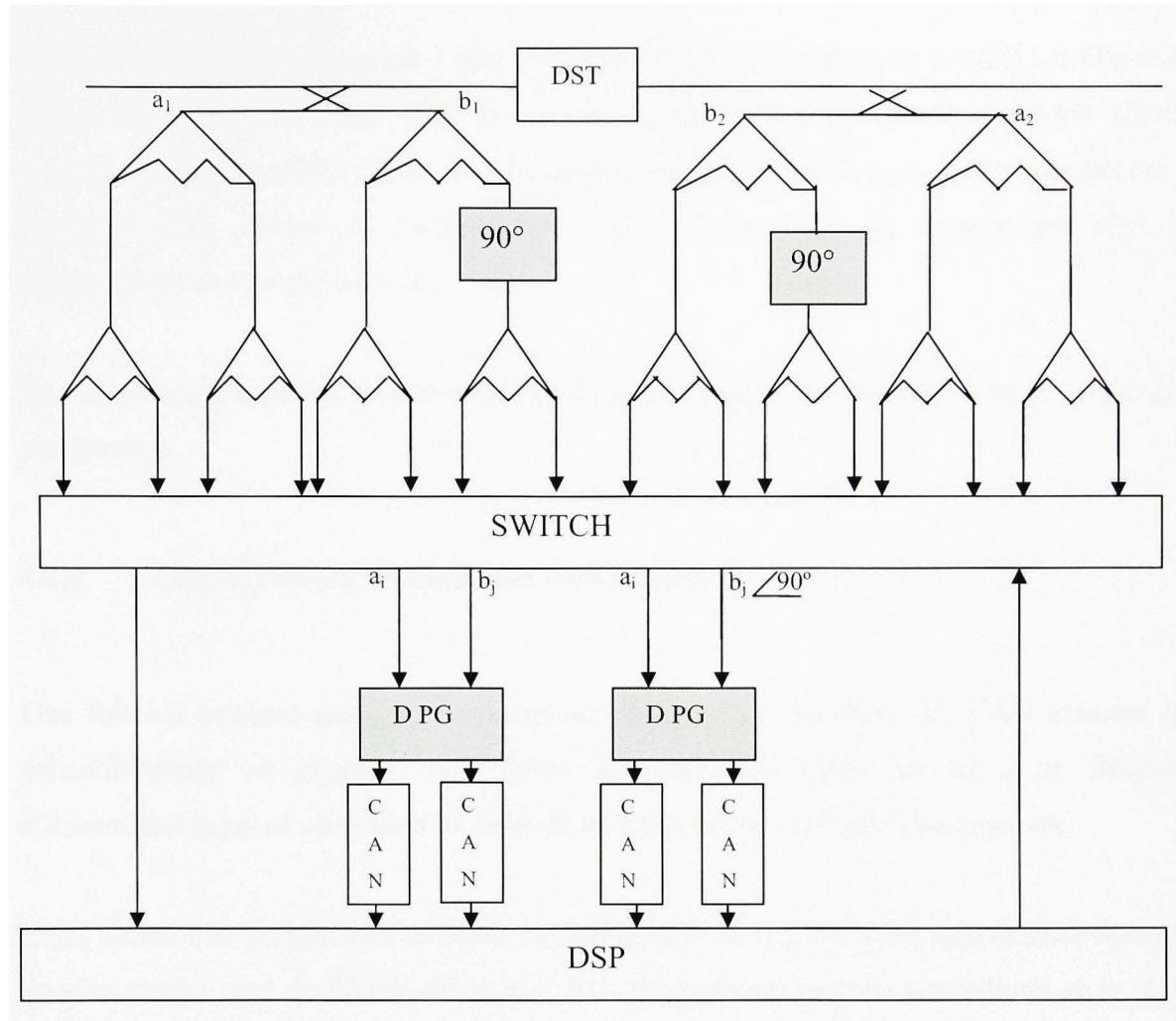

| 4.2.1    Architecture simplifiée des SRFI .....                             | 81  |

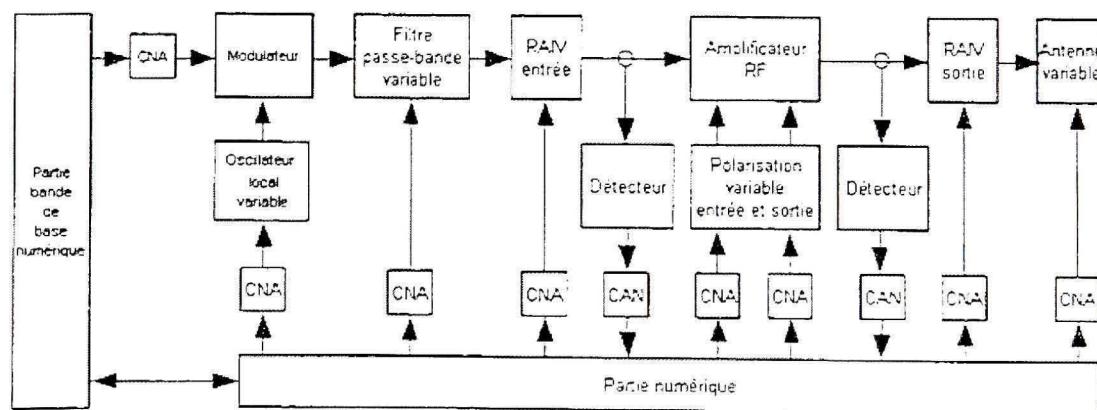

| 4.2.2    Architecture désirée des SRFI.....                                 | 82  |

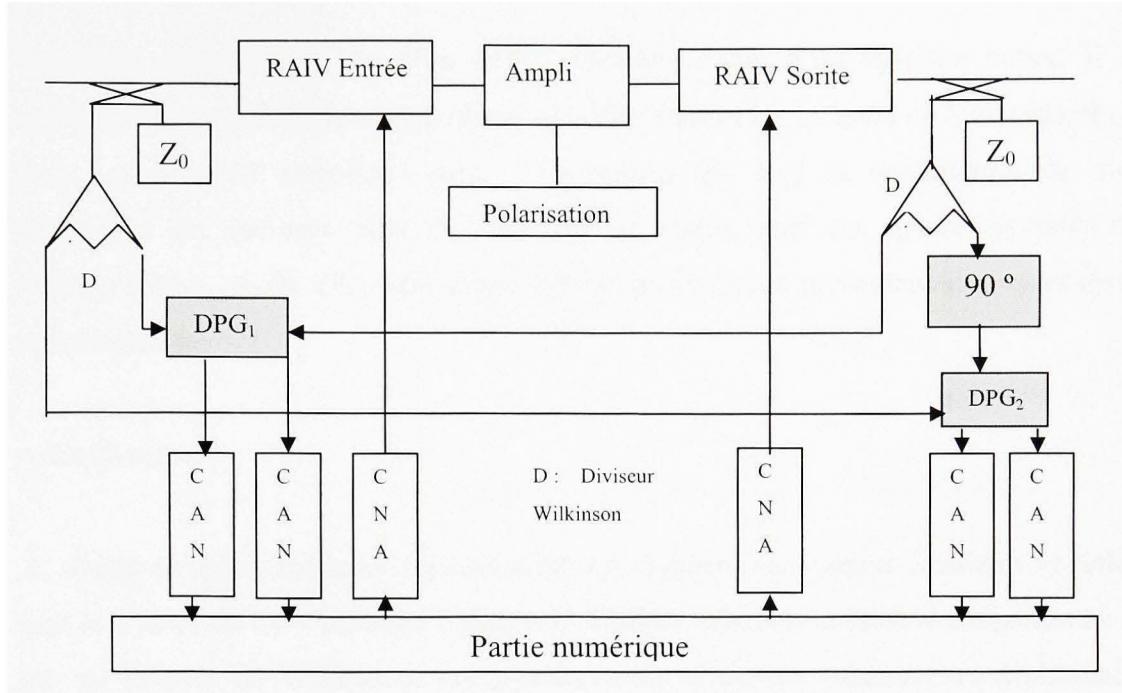

| 4.2.3    Mesure embarquée des SRFI .....                                    | 83  |

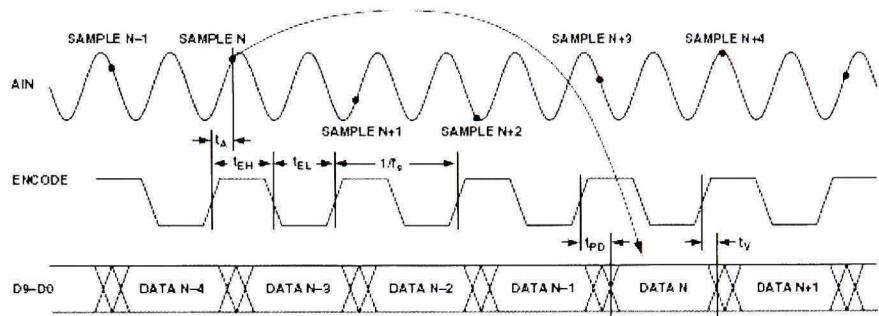

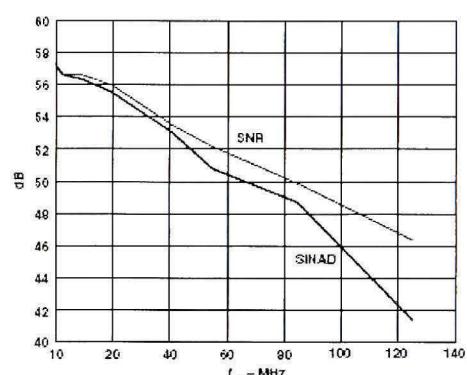

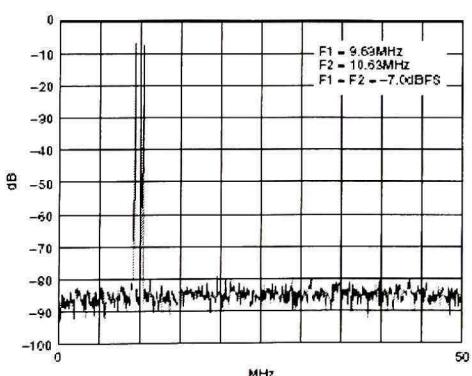

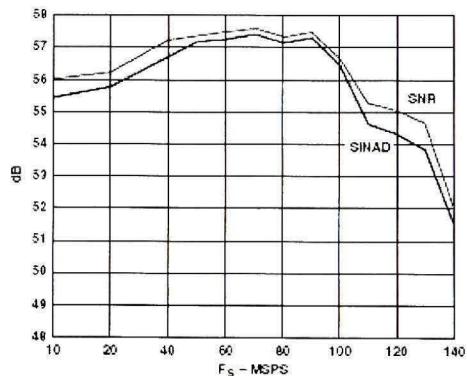

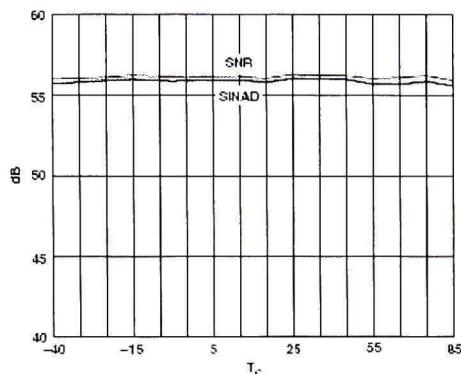

| 4.2.4    Convertisseurs Analogiques Numériques .....                        | 87  |

| 4.3        Conclusion.....                                                  | 88  |

| CONCLUSION .....                                                            | 89  |

| ANNEXE I      FICHE TECHNIQUE DU AD8302 .....                               | 91  |

| ANNEXE II     FORMULE DIAGRAMME DE FLUENCE .....                            | 102 |

| ANNEXE III    FICHE TECHNIQUE DU AD9071 .....                               | 103 |

| ANNEXE IV    PARAMÈTRES S DE L'AMPLIFICATEUR DE VALIDATION.....             | 113 |

| BIBLIOGRAPHIE .....                                                         | 114 |

## LISTE DES FIGURES

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Figure 1.1 Fonctionnement de l'analyseur .....                                      | 2  |

| Figure 1.2 Structure de la jonction six- port.....                                  | 4  |

| Figure 1.3 Circuit d'une jonction six- ports .....                                  | 5  |

| Figure 1.4 Analyseur de réseau homodyne .....                                       | 6  |

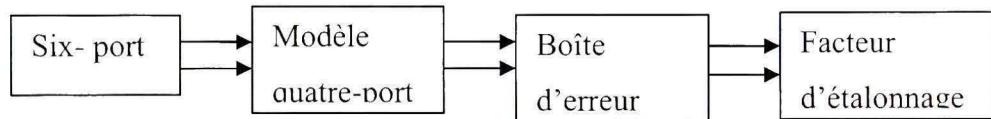

| Figure 1.5 Procédure de calibration .....                                           | 9  |

| Figure 1.6 Boîte d'erreur.....                                                      | 12 |

| Figure 1.7 Exemple de topologie de mesure avec le AD8302 .....                      | 14 |

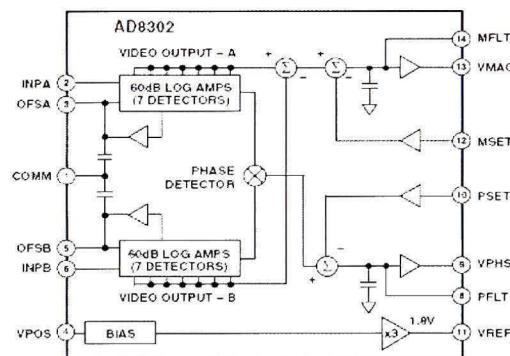

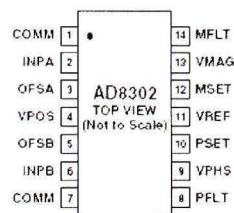

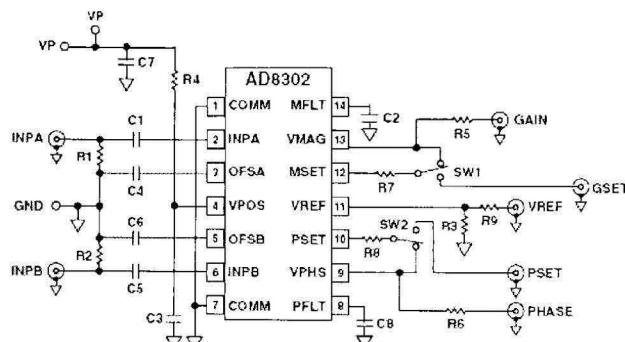

| Figure 2.1 Circuit simplifié du AD8302 .....                                        | 17 |

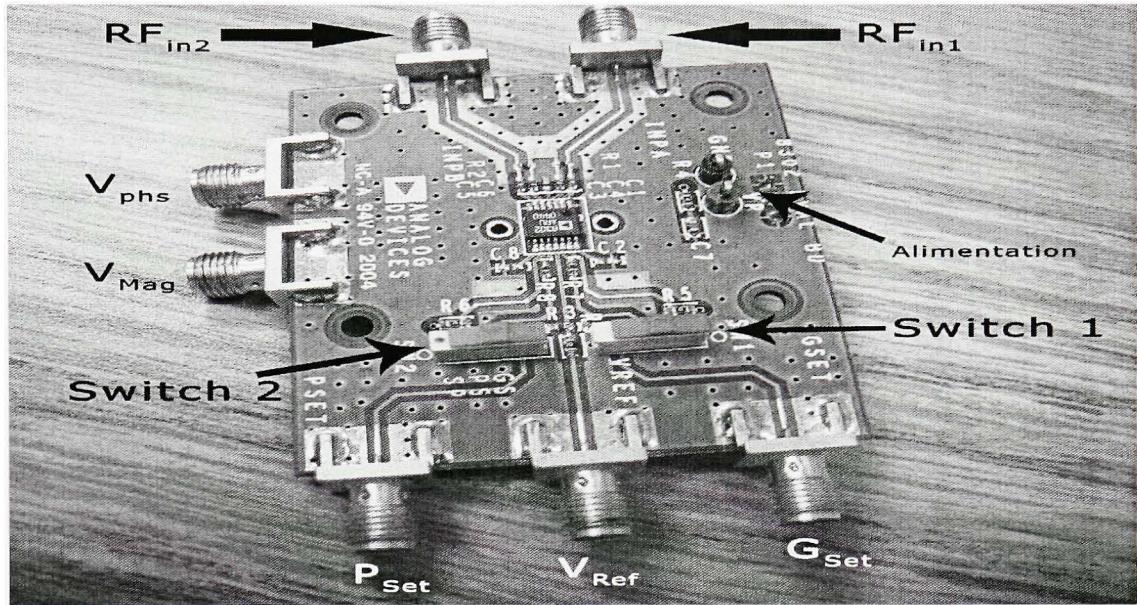

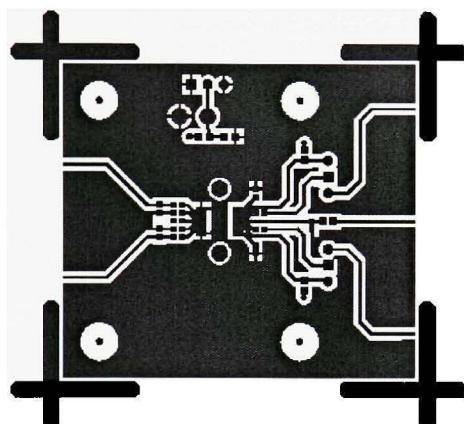

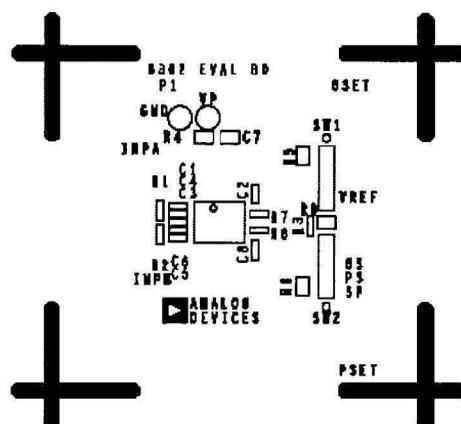

| Figure 2.2 Carte d'évaluation AD8302 (DPG) .....                                    | 19 |

| Figure 2.3 Fonction de transfert en amplitude du DPG .....                          | 20 |

| Figure 2.4 Fonction de transfert en phase du DPG .....                              | 22 |

| Figure 2.5 Impédances d'entrée du DPG en fonction de la fréquence.....              | 22 |

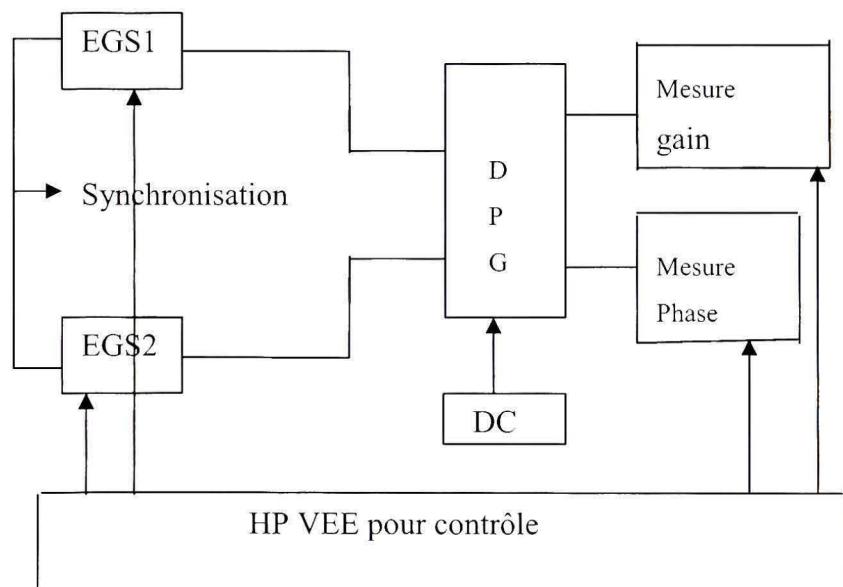

| Figure 2.6 Éléments de caractérisation du DPG .....                                 | 24 |

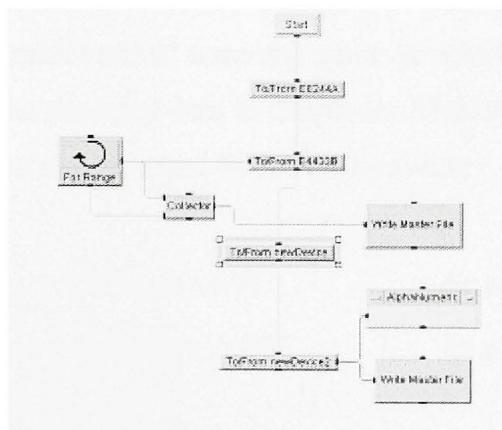

| Figure 2.7 Programme de fonction de transfert en amplitude.....                     | 26 |

| Figure 2.8 Fonction de transfert expérimentale en amplitude à 900MHz.....           | 27 |

| Figure 2.9 Fonction de transfert expérimentale en amplitude à 1.6GHz et 2GHz .....  | 28 |

| Figure 2.10 Programme de fonction de transfert en phase.....                        | 29 |

| Figure 2.11 Fonction de transfert en phase .....                                    | 30 |

| Figure 2.12 Mise en évidence de l'effet de la longueur des câbles sur la phase..... | 31 |

| Figure 2.13 Mesure de S11 aux ports RFin1 et RFin2.....                             | 32 |

| Figure 2.14 Procédure d'extraction d'amplitude.....                                 | 32 |

|                                                                                        |    |

|----------------------------------------------------------------------------------------|----|

| Figure 2.15 Erreur absolue commise en amplitude.....                                   | 33 |

| Figure 2.16 Première méthode de résolution d'ambiguïté de phase .....                  | 33 |

| Figure 2.17 Répartition de la fonction de transfert en zones .....                     | 33 |

| Figure 2.18 Algorithme de détection de signe .....                                     | 34 |

| Figure 2.19 Deuxième méthode de résolution d'ambiguïté de phase .....                  | 35 |

| Figure 2.20 Erreur absolue commise en phase.....                                       | 36 |

| Figure 2.21 Comparaison de fonction de transfert avec et sans modulation (Ka=0.9)..... | 37 |

| Figure 2.22 Comparaison de fonction de transfert avec et sans modulation (Ka=0.5)..... | 39 |

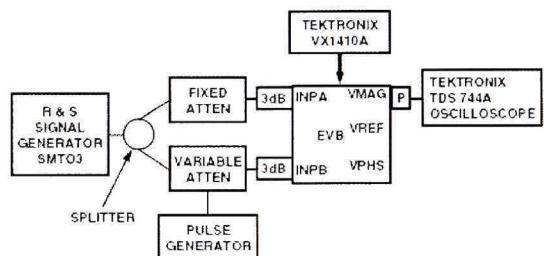

| Figure 3.1 Architecture simplifiée du banc de test .....                               | 42 |

| Figure 3.2 Architecture optimale du banc de test .....                                 | 43 |

| Figure 3.3 Configuration en mode réflectomètre.....                                    | 44 |

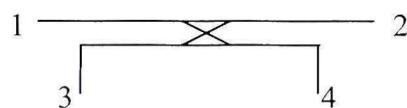

| Figure 3.4 Numérotation du coupleur .....                                              | 46 |

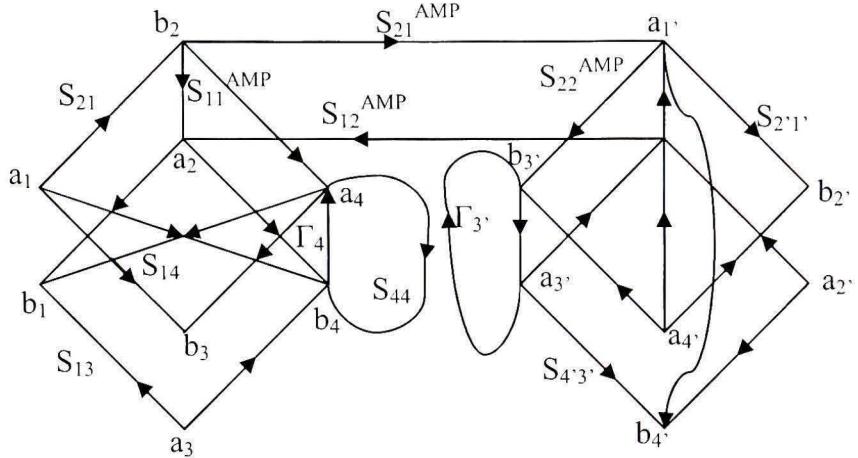

| Figure 3.5 Graphe de fluence du banc de test .....                                     | 47 |

| Figure 3.6 Utilisation des isolateurs.....                                             | 48 |

| Figure 3.7 Graphe de fluence en utilisant des isolateurs.....                          | 48 |

| Figure 3.8 Réflectométrie à deux coupleurs .....                                       | 52 |

| Figure 3.9 Graphe de fluence à deux coupleurs.....                                     | 53 |

| Figure 3.10 Étalonnage par boîte d'erreur .....                                        | 54 |

| Figure 3.11 Graphe de fluence de la boîte d'erreur .....                               | 55 |

| Figure 3.12 Schéma de mesure de gain.....                                              | 57 |

| Figure 3.13 Graphe de fluence en mode mesure de gain .....                             | 58 |

| Figure 3.14 Deuxième configuration de mesure de gain .....                             | 59 |

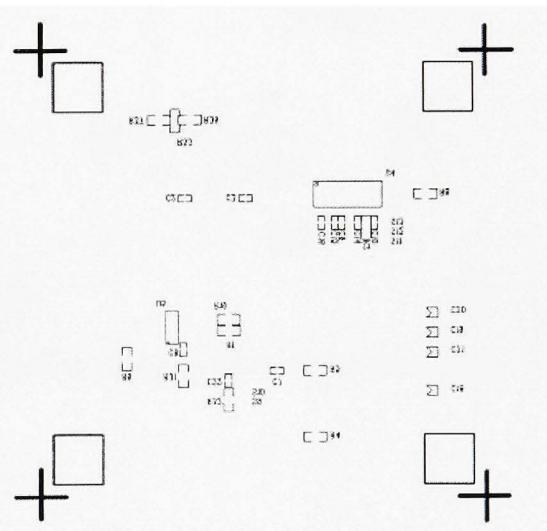

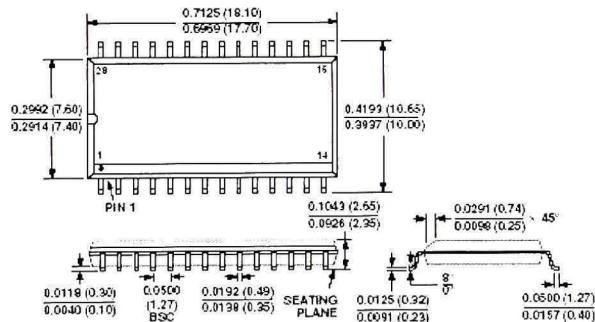

| Figure 3.15 Masque des coupleurs ANAREN choisis .....                                  | 61 |

| Figure 3.16 Principe de caractérisation des coupleurs .....                            | 62 |

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Figure 3.17 Paramètres S des coupleurs ANAREN.....                  | 63 |

| Figure 3.18 Mesure de réflexion de charge1 .....                    | 66 |

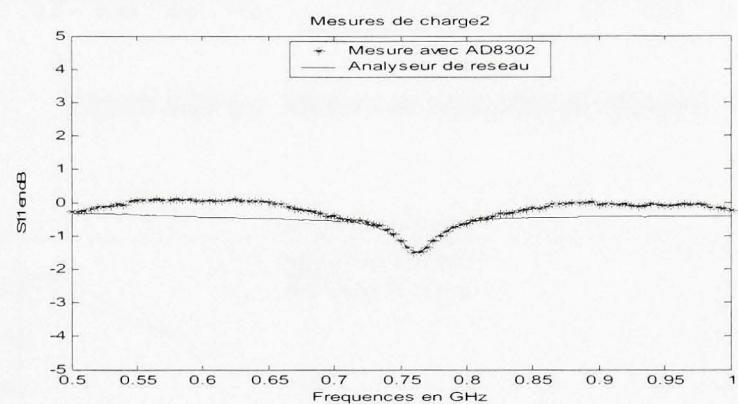

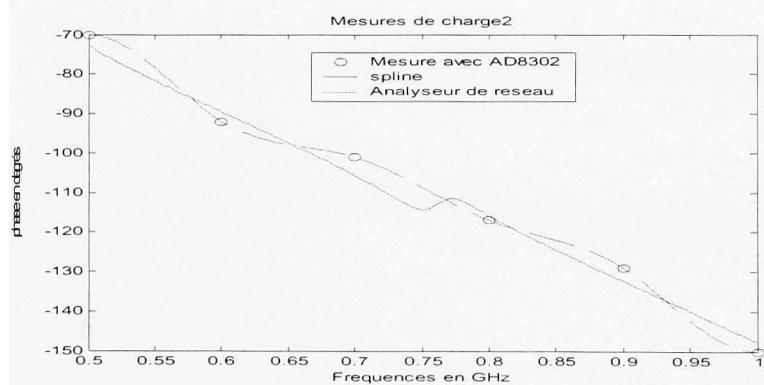

| Figure 3.19 Mesure de réflexion de charge2 .....                    | 66 |

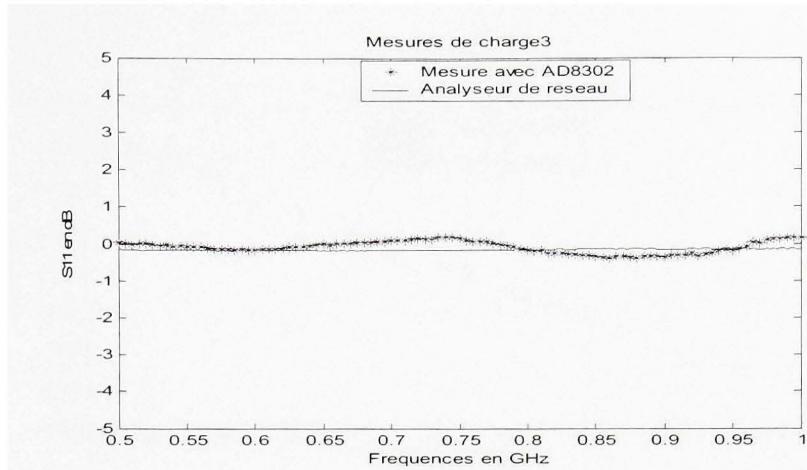

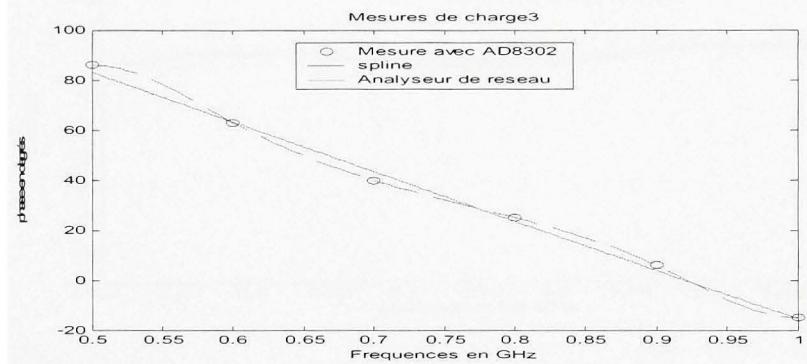

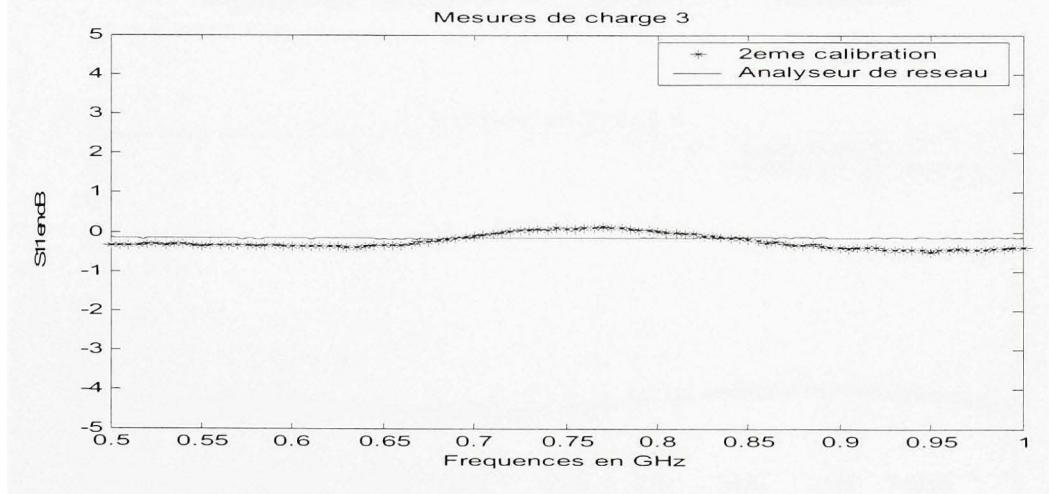

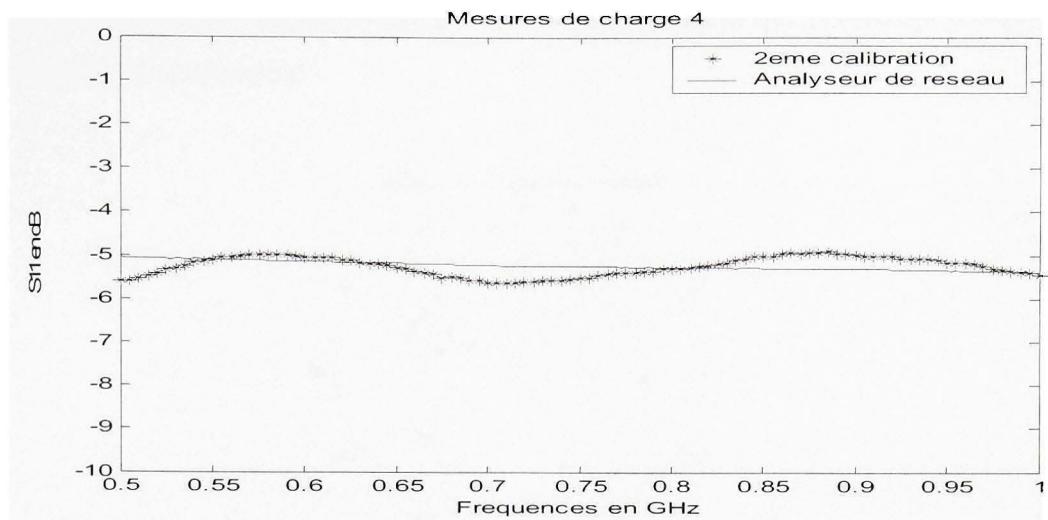

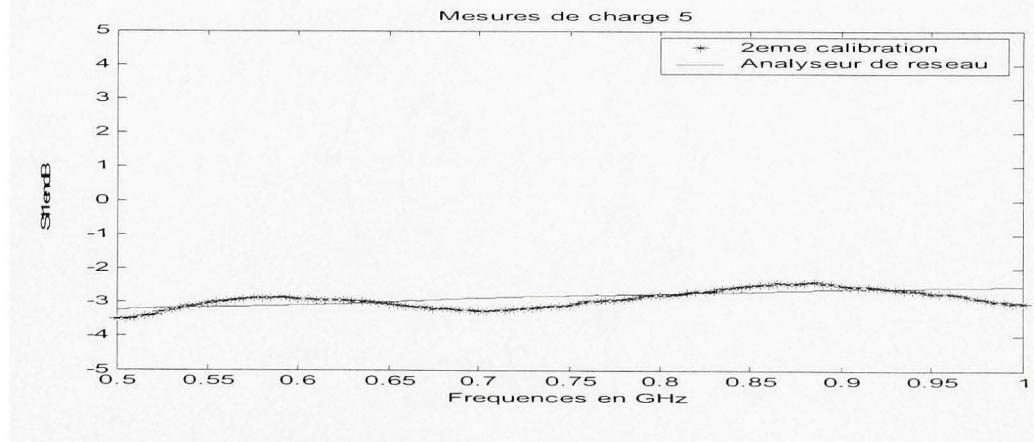

| Figure 3.20 Mesure de réflexion pour la charge3 .....               | 67 |

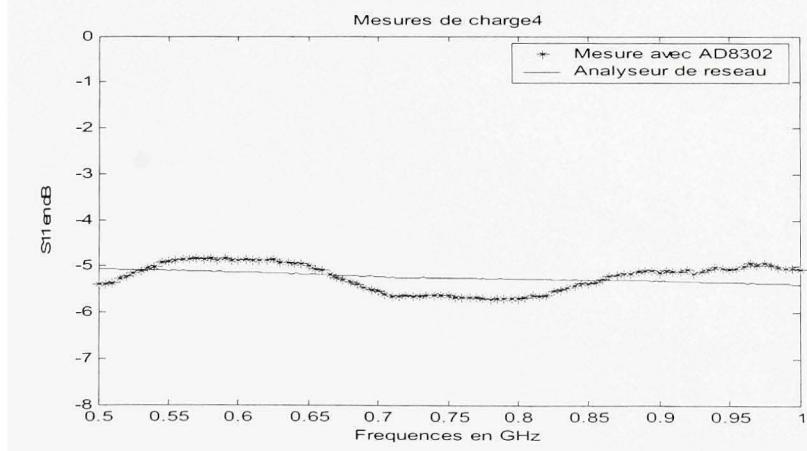

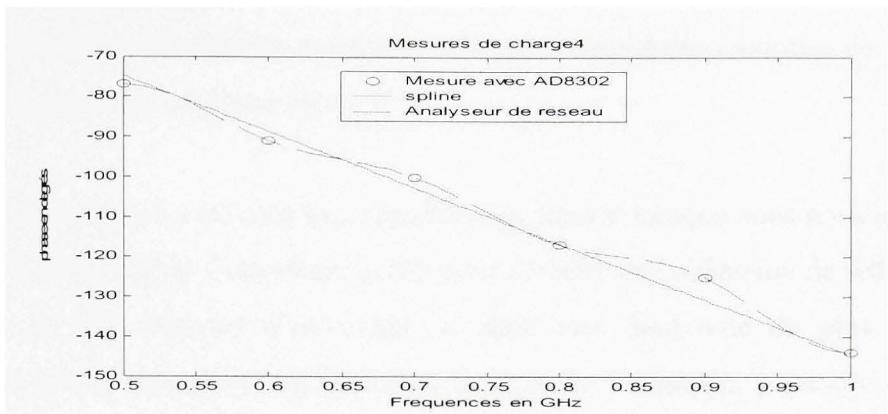

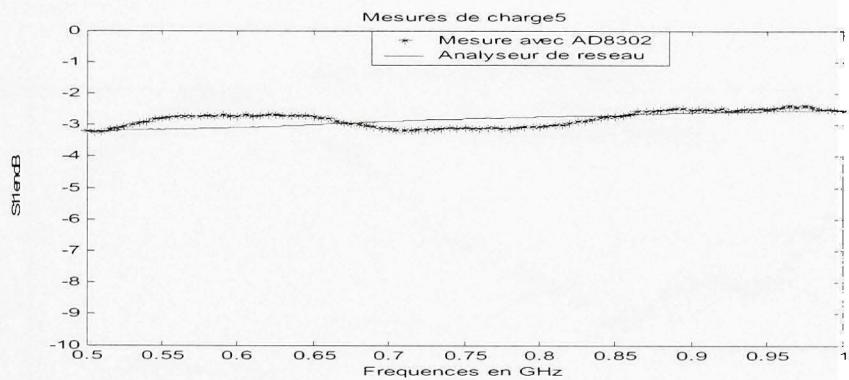

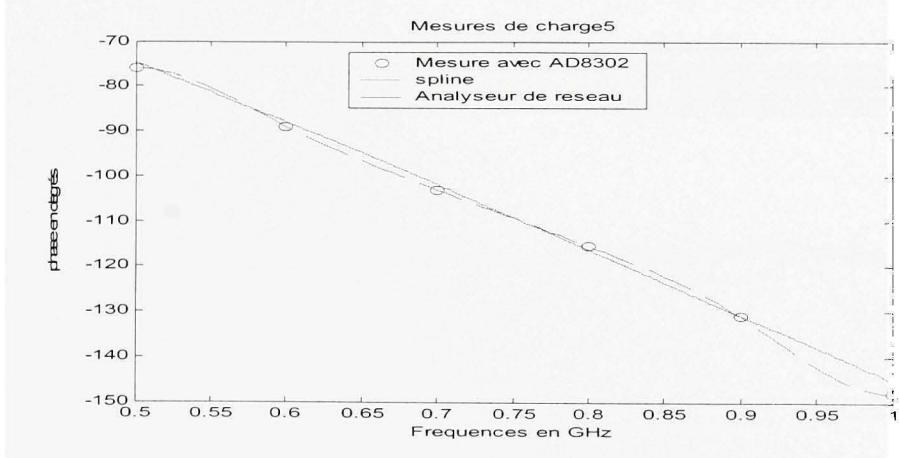

| Figure 3.21 Mesure de réflexion de charge4 .....                    | 69 |

| Figure 3.22 Mesure de réflexion pour la charge5 .....               | 69 |

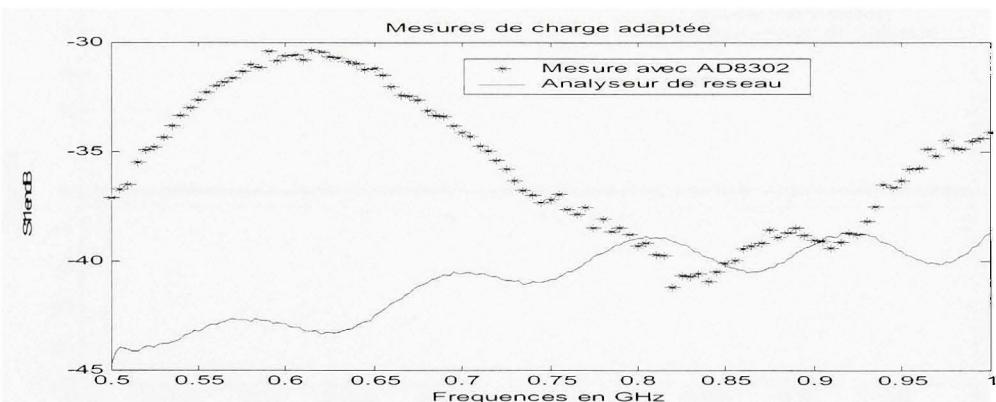

| Figure 3.23 Mesure de charge adaptée avec un coupleur .....         | 69 |

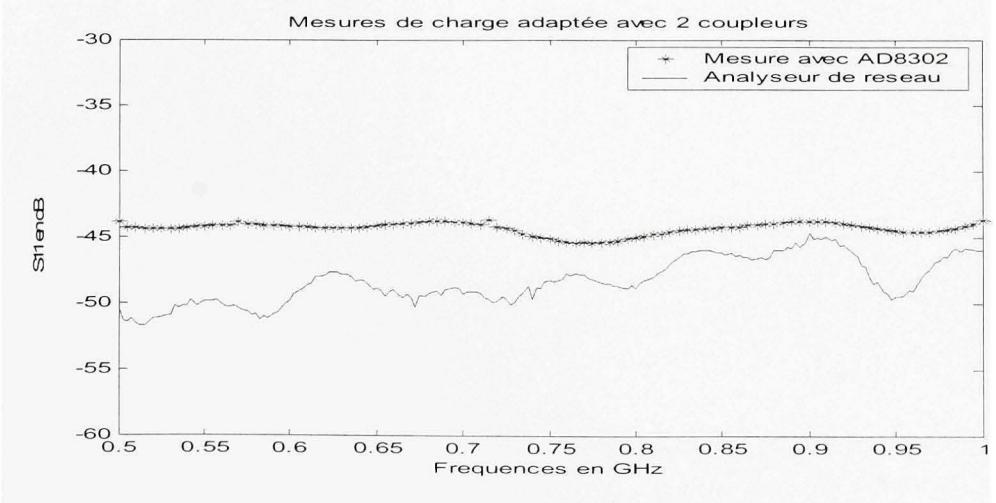

| Figure 3.24 Mesure de charge adaptée avec deux coupleurs .....      | 69 |

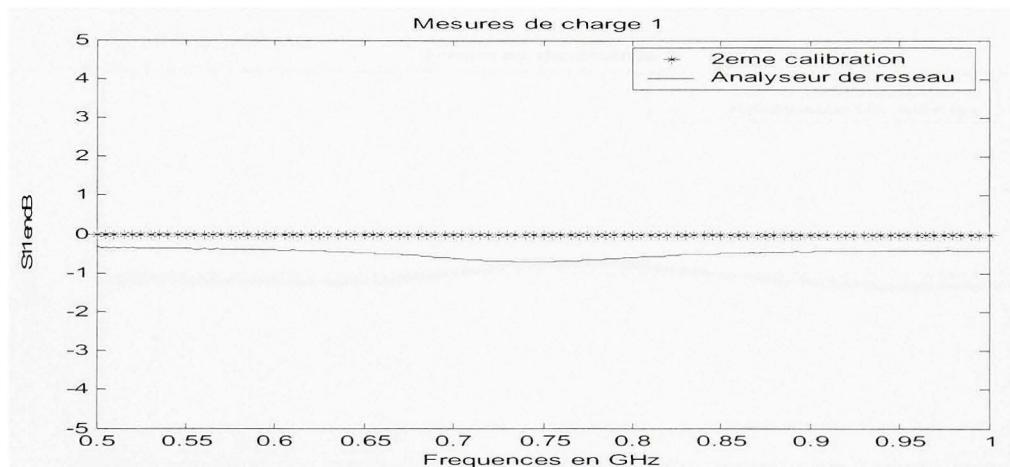

| Figure 3.25 Mesure de charge1 par la 2eme calibration .....         | 70 |

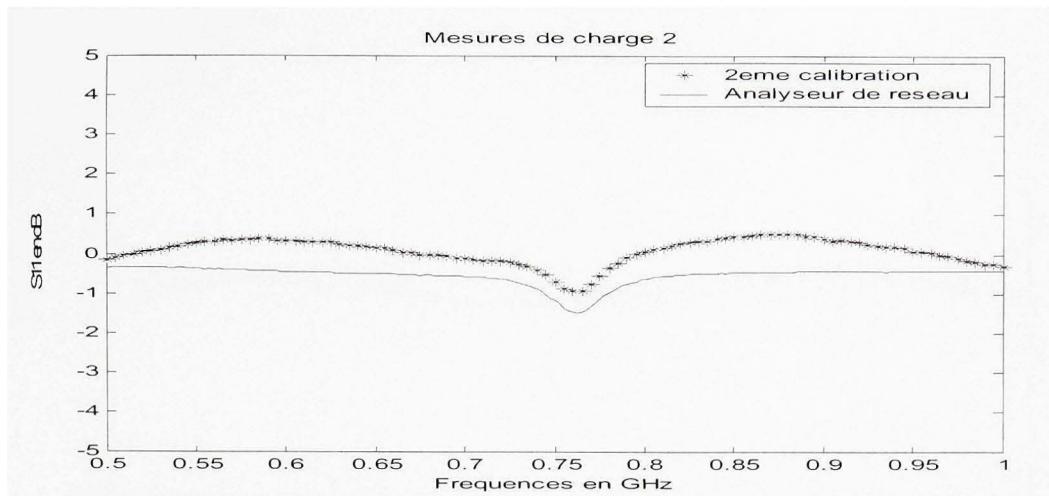

| Figure 3.26 Mesure de charge2 par la 2eme calibration .....         | 71 |

| Figure 3.27 Mesure de charge3 par la 2eme calibration .....         | 71 |

| Figure 3.28 Mesure de charge4 par la 2eme calibration .....         | 72 |

| Figure 3.29 Mesure de charge5 par la 2eme calibration .....         | 74 |

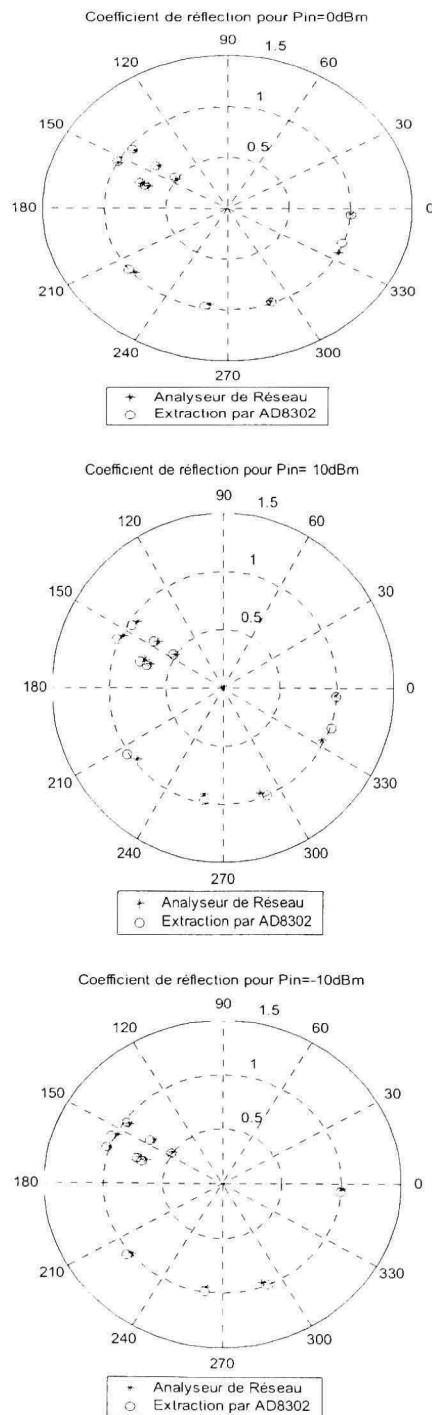

| Figure 3.30 Coefficients de réflexion pour Pin= 0, 10,-10 dBm.....  | 73 |

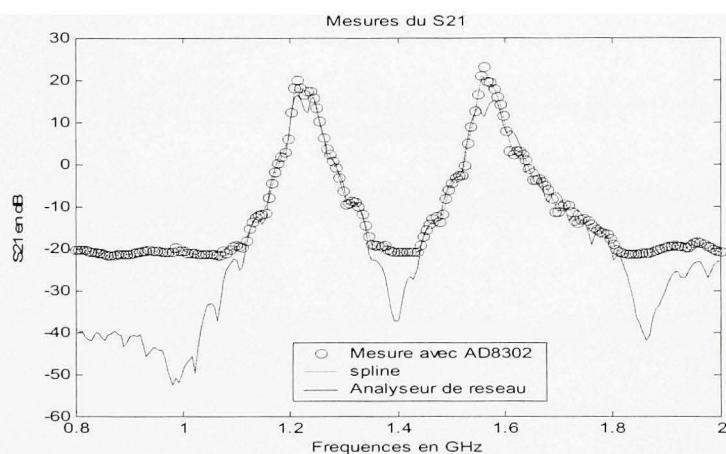

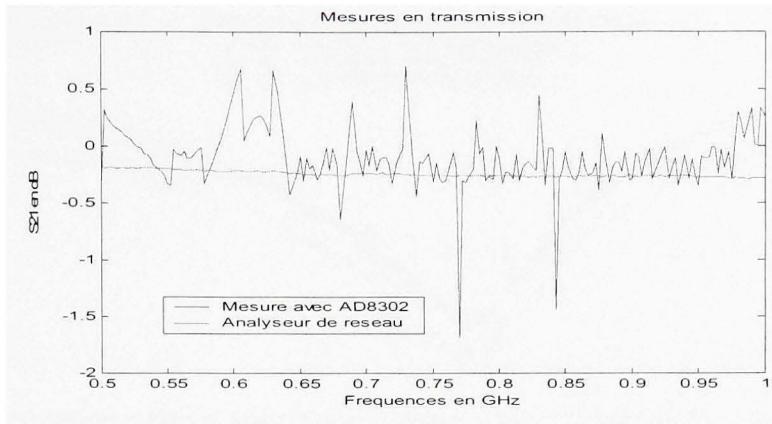

| Figure 3.31 Mesure de S21 pour un filtre sélectif.....              | 74 |

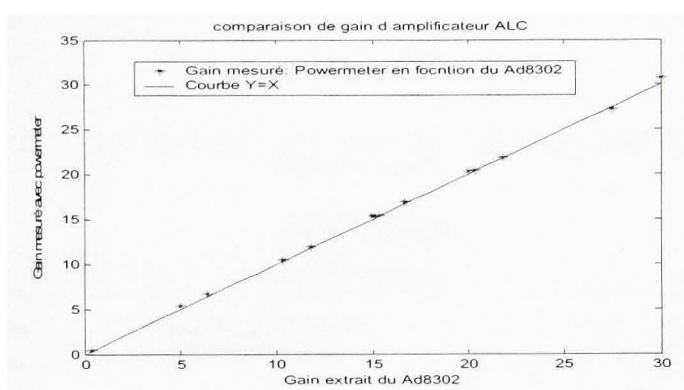

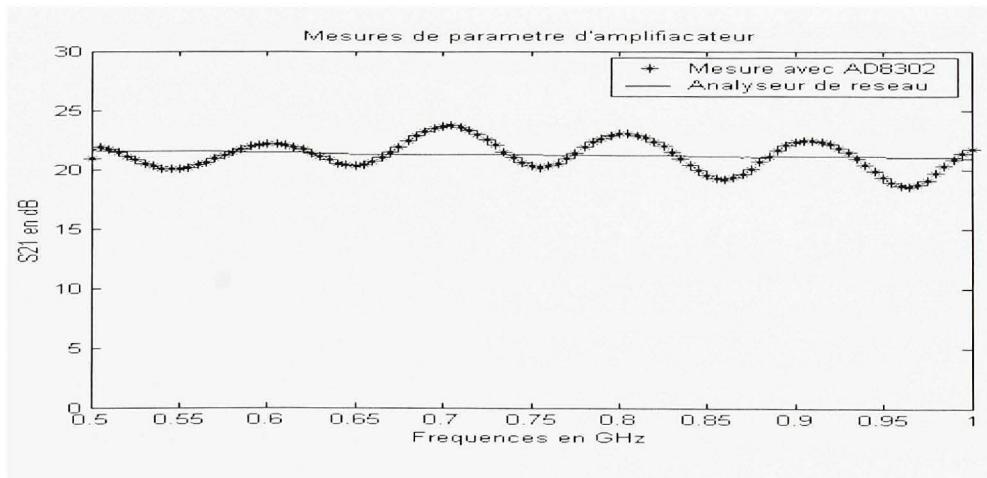

| Figure 3.32 Comparaison de gain d'amplificateur ALC .....           | 75 |

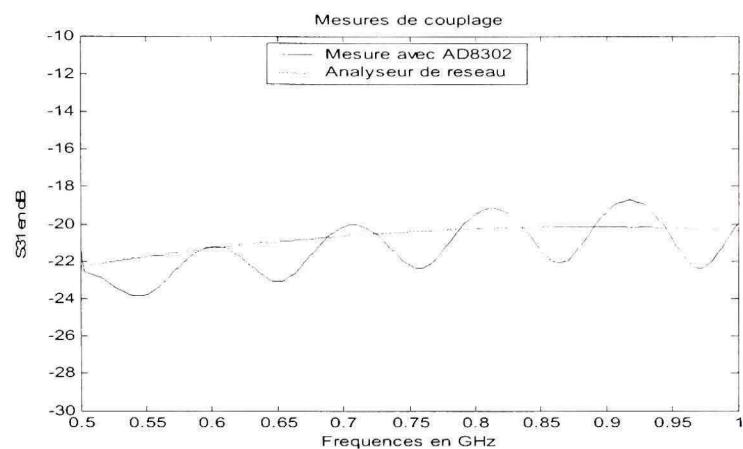

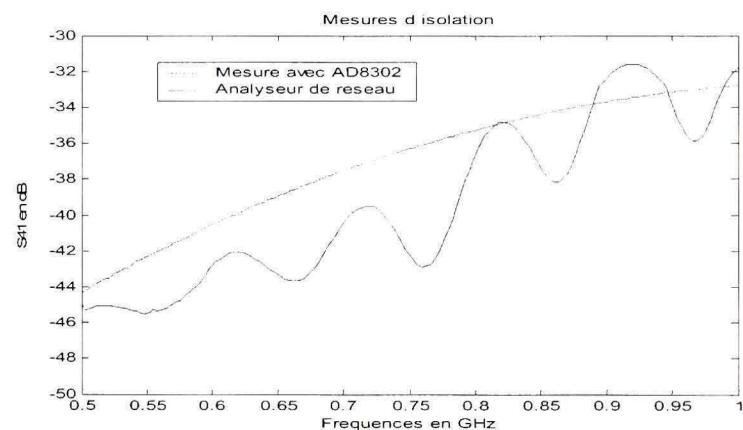

| Figure 3.33 Caractérisation d'un coupleur par le banc de test ..... | 76 |

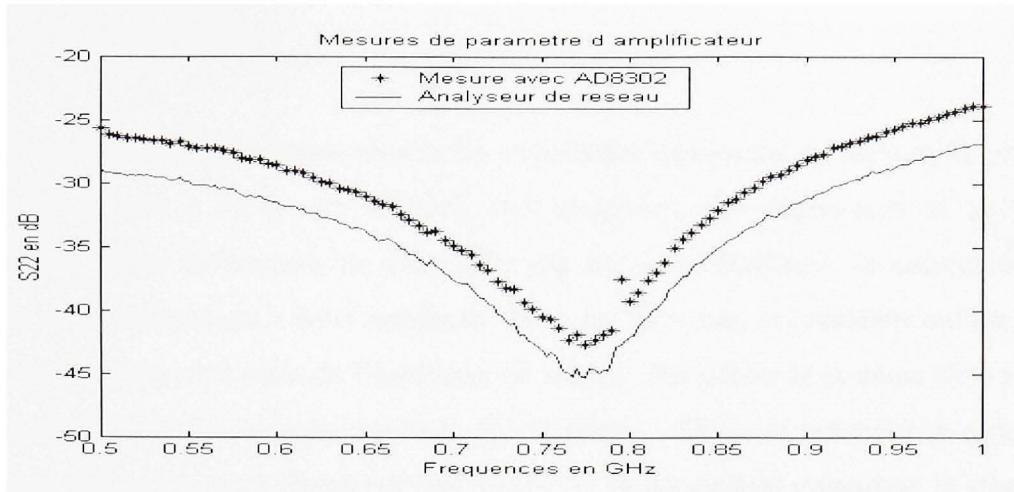

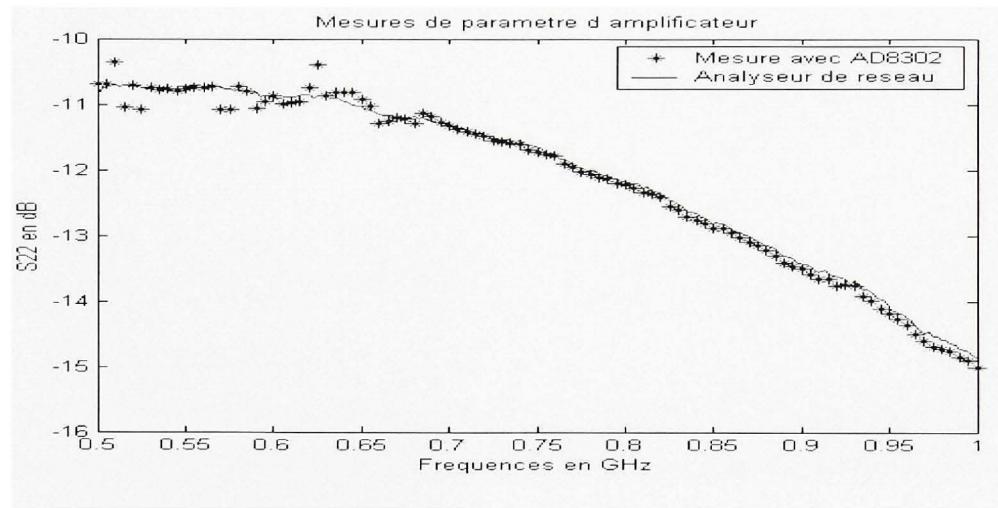

| Figure 3.34 Mesure de paramètres S d'amplificateur.....             | 78 |

| Figure 4.1 Architecture simplifiée des SRFI .....                   | 80 |

| Figure 4.2 Architecture désirée des SRFI .....                      | 82 |

| Figure 4.3 Intégration des DPG aux SRFI .....                       | 83 |

| Figure 4.4 Architecture n° 1 d'intégration des DPG aux SRFI.....    | 85 |

| Figure 4.5 Architecture n° 2 d'intégration des DPG aux SRFI.....    | 86 |

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|      |                                          |

|------|------------------------------------------|

| RF   | Radio Fréquence                          |

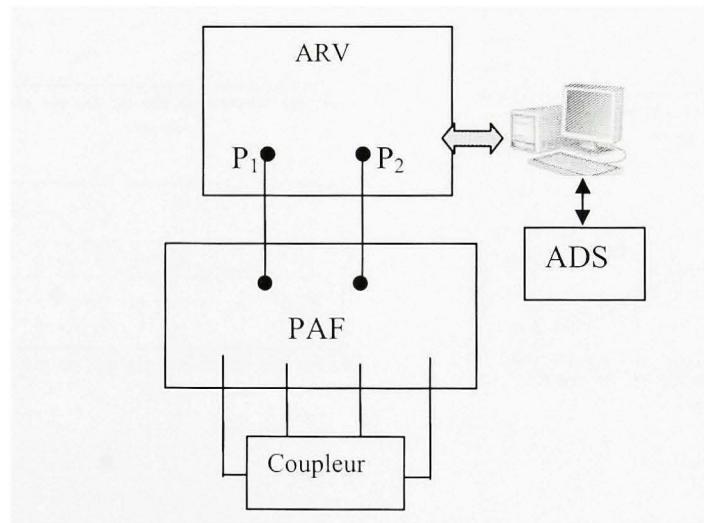

| ARV  | Analyseur de Réseau Vectoriel            |

| DST  | Dispositif Sous Test                     |

| DUT  | Dispositif Under Test                    |

| DPG  | Détecteur de Gain et de Phase            |

| PA   | Power Amplifier                          |

| ADS  | Advanced Design Systems                  |

| SRFI | Systèmes Radio Fréquences Intelligents   |

| PAF  | Progettazione ad Alta Frequenza          |

| ALC  | Automatic Level Controlled               |

| MMIC | Monolithic Microwave Integrate Circuit   |

| RAIV | Réseau d'Adaptation d'Impédance Variable |

| MEMS | Micro Electro – Mechanical Systems       |

| CAN  | Convertisseur Analogique Numérique       |

| CNA  | Convertisseur Numérique Analogique       |

| CMOS | Complementary Metal Oxyd Semiconductor   |

## INTRODUCTION

Au cours des années à venir, l'industrie des télécommunications devra faire face à de nombreuses modifications en raison de la prolifération des nouveaux produits et des exigences du marché.

Les défis qui émergent actuellement sont l'augmentation de la capacité des systèmes cellulaires, le développement des systèmes sans fil à large bande pouvant supporter les applications multimédias tout en intégrant la flexibilité et la reconfigurabilité. Afin de suivre ces nouvelles tendances, la section radio- fréquences (RF) se doit d'être plus agile et capable de s'auto caractériser en temps réel en tenant compte des critères dont le " faible coût ", l'intégration.

L'objectif de ce projet consiste donc à démontrer la faisabilité et la réalisation de tel dispositif de mesure à l'instar de l'analyseur de réseau vectoriel en ayant recours à des technologies intégrées de moindre coût. En d'autres termes, il s'agira de développer une technique de mesure en temps réel de circuits radio- fréquences à l'aide des composants facilement intégrables à ces circuits. Le dispositif permettra entre autre aux industriels de l'intégrer dans leurs produits afin de monitorer leur condition d'opération et d'apporter les modifications nécessaires pour en assurer une durée de vie meilleure.

Le présent mémoire est structuré en quatre chapitres. Le premier chapitre sera consacré à la description des systèmes actuels de caractérisation en RF. Nous y présenterons l'analyseur de réseau hétérodyne ainsi que la technique de mesure à six ports. Les avantages et inconvénients seront par la suite abordés pour démontrer leur manque de flexibilité dans les systèmes futurs de communication sans fil. En compromis, nous proposerons un dispositif de mesure capable d'effectuer des comparaisons d'amplitude et de phase. La compagnie Analog Devices offre un tel dispositif sous forme de puce AD8302 que nous avons choisie.

Le deuxième chapitre fera l'objet d'étude de la carte intégrant la puce AD8302.

Nous y décrirons la procédure d'étalonnage ainsi que les outils logiciels pour l'interfaçage. Nous établirons les estimateurs expérimentaux des fonctions de transfert régissant le fonctionnement de la carte en amplitude et en phase. Une étude de performance de la carte permettra de déterminer sa plage dynamique, son comportement en modulation AM ainsi que l'erreur commise en utilisant les fonctions de transfert expérimentales.

Dans le troisième chapitre, nous décrirons le banc de test réalisé. L'objectif étant de mesurer les paramètres S d'un dispositif sous test. Nous utiliserons différentes configurations du AD8302 via des coupleurs directionnels, des diviseurs de puissance et des déphasateurs pour mesurer les facteurs de réflexion et de transmission.

Enfin dans le dernier chapitre, nous ferons l'intégration du banc de test aux Systèmes RF Intelligents (SRFI) pour la mesure embarquée. Nous discuterons des architectures proposées ainsi que les technologies disponibles pour la réalisation de l'intégration aux SRFI.

## **CHAPITRE 1**

### **SYSTÈMES ACTUELS DE CARACTÉRISATION DES CIRCUITS MICRO -ONDES**

#### **1.1      Introduction**

L'analyseur de réseau est l'outil principal pour mesurer les performances des circuits linéaires actifs ou passifs aux hautes fréquences. Il permet entre autre de nous informer sur le comportement des circuits micro-ondes par rapport aux fréquences d'opération en mesurant les ondes transmises et réfléchies sur un dispositif sous test, donnant accès aux paramètres S. Deux grandes familles d'analyseurs de réseau existent sur le marché : le scalaire révélant le module des paramètres S et le vectoriel donnant accès à la forme complexe (module et phase) desdits paramètres [1]. Cette dernière catégorie, souvent convoitée, peut être hétérodyne ou homodyne. Les systèmes hétérodynes utilisent la technique de transposition fréquentielle tandis que les systèmes homodynes effectuent des mesures directes à la fréquence d'opération.

Qu'ils soient hétérodynes ou homodynes, les analyseurs de réseau vectoriels aussi complexes et coûteux soient-ils manquent de flexibilité pour certaines applications.

Dans ce chapitre, nous donnons un aperçu sur les techniques de mesures hétérodynes et homodynes pour mettre en exergue leurs avantages et inconvénients par rapport aux exigences actuelles du marché des télécommunications mobiles.

#### **1.2      Les analyseurs de réseau hétérodynes**

Apparus dans les années soixante [2], les analyseurs de réseau hétérodynes sont reconnus pour leur technique de transposition en fréquences. En effet, plus la fréquence devient considérable (à partir de 100 MHz), on ne peut mesurer le déphasage relatif des signaux. Une façon de s'affranchir est de faire la transposition en de fréquences plus basses (de l'ordre de

quelques KHz), ce qui permet d'augmenter la période facilitant ainsi l'utilisation de techniques de base dont l'échantillonnage.

### 1.2.1 Principe de fonctionnement

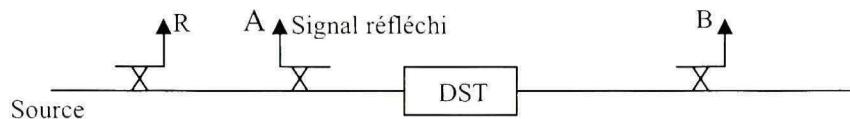

Le schéma suivant illustre le fonctionnement de l'analyseur :

*Figure 1.1 Fonctionnement de l'analyseur.*

À l'aide d'un diviseur de Wilkinson, on récupère des échantillons du signal en provenance de la source. Une fraction du signal émis par la source servira de référence (R) tandis que l'autre sera considérée comme l'onde incidente en direction du dispositif à tester. Deux coupleurs disposés respectivement en amont et en aval de celui-ci permettront d'échantillonner les ondes réfléchies (A) et transmises (B). Une fois les signaux séparés, leur module et phase sont mesurés les uns par rapport aux autres pour reconstituer la matrice des paramètres S. Un processeur intégré assure le traitement des données sur différentes échelles (linéaire, dB, dBm...) ainsi que dans les domaines temporel et fréquentiel.

Signalons toutefois que ce principe suppose que l'on opère dans des conditions idéales. D'un point de vue pratique, les mesures effectuées sont entachées d'erreurs corrigibles ou non. On peut corriger certaines de ces erreurs par étalonnage de l'analyseur. Il existe deux types de calibration : la calibration en normation qui permet de ne corriger que les erreurs fréquentielles et la calibration vectorielle qui corrige toutes les erreurs dites systématiques dues aux imperfections de l'analyseur et sont invariantes dans le temps. Dans les deux cas, l'étalonnage est d'une simplicité à réaliser car il est basé sur la mesure d'une série de standards sur chacun de ses ports.

### 1.2.2 Avantages et inconvénients reliés au système hétérodyne

Les avantages liés à l'utilisation d'analyseurs de réseau vectoriels hétérodynes sont multiples et multiformes. Outre leur fonctionnement à bande étroite leur conférant une dynamique assez considérable par simple élimination du bruit dont la puissance est proportionnelle à la bande passante du filtre, ils sont reconnus pour la rapidité de mesure et la simplicité à étalonner. Toutefois, ces systèmes présentent quelques inconvénients. En effet leur conception devient difficile à réaliser quand on s'approche des ondes millimétriques. De plus, les mesures manquent de précision quand il s'agit de circuits oscillants car les analyseurs présentent généralement des ports de mesure adaptés à 50 Ohms. D'un point de vue matériel, ces dispositifs sont constitués d'amplificateur sélectif, de détecteurs synchrones, d'oscillateurs locaux, de multiplicateurs de fréquence etc qui les rendent complexes, coûteux et sont destinés à un environnement physique particulier.

### 1.3 Les analyseurs de réseau homodynes

Contrairement au modèle précédent, les systèmes homodynes effectuent la mesure directe des paramètres S à une fréquence d'excitation donnée. La jonction à six- port est le modèle couramment rencontré sur le marché. Elle a été le fruit de l'initiative d'Engen du NBS vers 1972 [3]. Présentée au début comme une alternative, elle est devenue un instrument de mesures micro-ondes très précis et peut être utilisée pour des mesures à haute puissance et une large gamme de fréquences couvrant les micro-ondes et les ondes millimétriques. La jonction six- port, tout en éliminant la partie hétérodyne, permet de déterminer le facteur de réflexion d'un dispositif sous test (qui est directement lié à son impédance d'entrée) ou alternativement de trouver le rapport en module et phase entre différents signaux à partir des lectures de puissances.

### 1.3.1 Principe de la méthode six- port

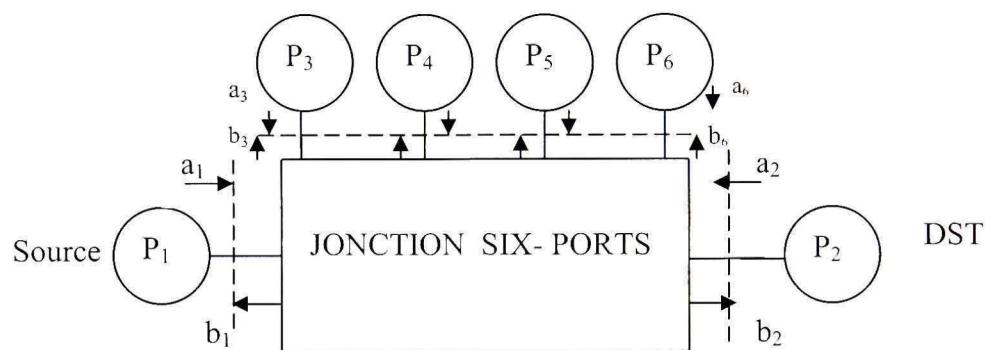

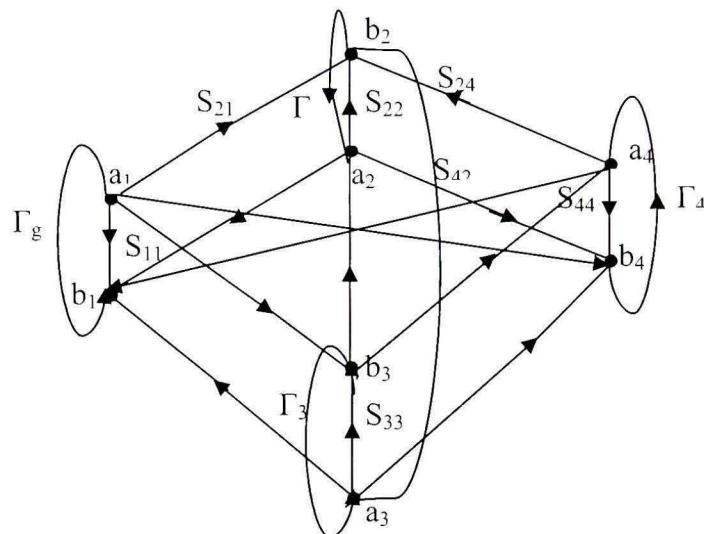

Le six- port doit son appellation à son circuit à six accès : un accès d'entrée noté  $P_1$ , un accès de sortie  $P_2$  et quatre ports de mesure ( $P_3, P_4, P_5$  et  $P_6$ ). La structure du six port est présentée à la figure 1.2.

*Figure 1.2 Structure de la jonction six- port.*

Le port  $P_3$  sera considéré comme référence et fournira un signal proportionnel à l'entrée. La mesure des puissances est assurée par des capteurs de puissance placés aux ports  $P_3, P_4, P_5$  et  $P_6$ . La topologie d'un six- port est faite d'éléments passifs comme des coupleurs, des déphasateurs et des diviseurs de puissance tel qu'illustré dans le circuit de la figure 1.3 :

*Figure 1.3 Circuit d'une jonction six- ports.*

Le signal émis par la source est d'entrée de jeu échantillonné par un coupleur avant d'être soumis au diviseur de puissance  $D_1$ . Généralement on utilise une jonction hybride ( $C_1$ ) à cet étage pour assurer l'échantillonnage de l'onde incidente. L'onde  $a_2$  réfléchie par la charge ou le circuit sous test au port 2 sera combinée à l'onde incidente  $a_1$  pour présenter quatre signaux de puissance aux ports  $P_3$ ,  $P_4$ ,  $P_5$  et  $P_6$ . Cette combinaison se fait de façon linéaire dans les conditions idéales. En pratique, on utilise le diagramme de fluence pour tenir compte de l'effet de mésadaptation du générateur et des défauts de directivités des coupleurs.

Le coefficient de réflexion s'extrait par la connaissance des rapports  $\frac{P_4}{P_3}$ ,  $\frac{P_5}{P_3}$ ,  $\frac{P_6}{P_3}$  ainsi que les constantes de calibration de la jonction six- port. Il est également possible de connaître la puissance absorbée par la charge à travers cette configuration. Celle-ci est directement liée au niveau de puissance à l'accès  $P_3$ , au coefficient de réflexion ainsi qu'aux paramètres d'étalonnage.

### 1.3.2 De la jonction six- port à l'analyseur de réseau six- port

La jonction six- port doit son essor dans le domaine de l'instrumentation et de la mesure à son faible coût et à la qualité des mesures due à la simplicité des circuits qui le constituent. A son utilisation comme réfléctomètre, s'ajoute son intérêt dans des applications comme les radars de sécurité pour les automobiles, les démodulateurs numériques, le contrôle d'antennes adaptatives ou même dans les boucles à verrouillage de phase et de récupération de porteuse.

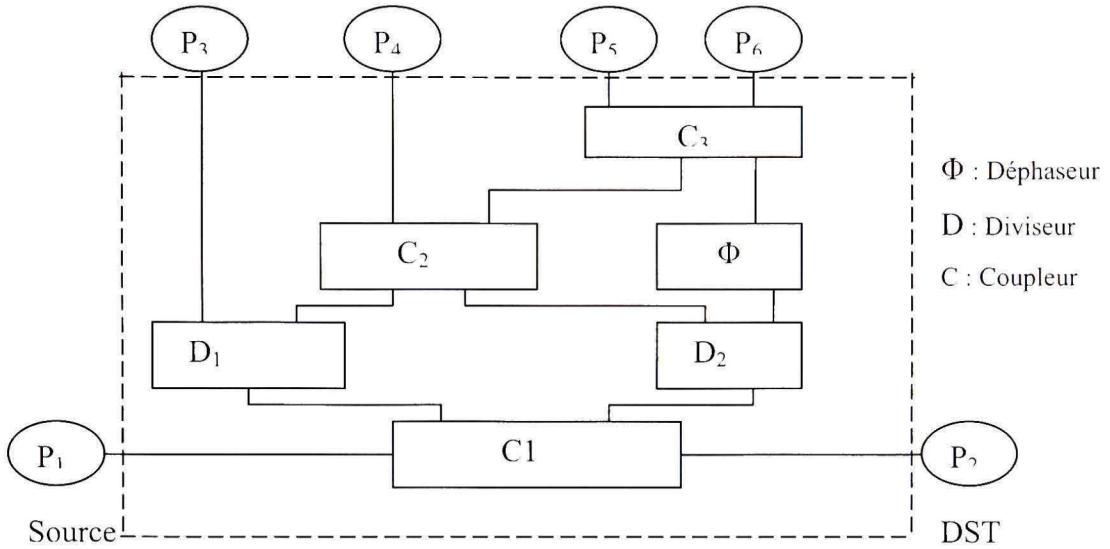

A partir de ce succès, il a été possible de développer un système de mesure pour les dispositifs micro-ondes : l'analyseur de réseau à six- port, communément appelé analyseur de réseau homodyne [3]. Il sera constitué de deux circuits six- port, d'un diviseur de puissance, de deux déphasateurs réglables ainsi que d'un atténuateur réglable comme le montre la figure 1.4 :

*Figure 1.4 Analyseur de réseau homodyne.*

On note à la figure 1.4 que le signal de la source RF est séparé en deux par un diviseur de puissance. Chaque partition attaque les circuits six- port auxquels est connecté le dispositif sous test. Les phases et les amplitudes des signaux incidents aux entrées des six- port sont

ajustés par des déphasateurs et atténuateurs réglables. En variant le déphasage de chaque six-port ainsi que l'atténuation, on mesure les coefficients de réflexion qui serviront à extraire les paramètres S du DST.

### 1.3.3 Équations régissant le fonctionnement de la jonction six- port

Considérons une jonction six- port linéaire avec des capteurs de puissance raccordés aux ports 3, 4, 5, et 6 tel qu'illustrée à la figure 1.3. Nous avons donc :

$$b_i = \sum_{j=1}^6 S_{ij} a_j \quad i=1..6 \quad (1.1)$$

$a_i$  et  $b_j$  représentent respectivement les pseudo ondes incidentes et émergentes de la jonction et  $S_{ij}$  sont les paramètres de dispersion.

Si  $\Gamma_j$  est le coefficient de réflexion au port  $j$ , alors nous pouvons écrire :

$$a_j = \Gamma_j b_j \quad j=3..6 \quad (1.2)$$

Somme toute, nous avons un système de 10 équations à 12 inconnues :  $a_i$  et  $b_j$

Nous pouvons également exprimer chacune des ondes émergentes sous forme de combinaison linéaire des ondes au port 2 :

$$b_i = A_i a_2 + B_i b_2 \quad i=3..6 \quad (1.3)$$

avec  $A_i$  et  $B_i$  des constantes déterminant les caractéristiques de la jonction six- port.

En termes de puissance, nous avons :

$$P_i = |b_i|^2 (1 - |\Gamma_i|^2) = |A_i a_2 + B_i b_2|^2 (1 - |\Gamma_i|^2) \quad i=3..6 \quad (1.4)$$

ou encore :

$$P_i = |A_i \Gamma_2 + B_i|^2 (1 - |\Gamma_i|^2) |b_2|^2 \quad i=3..6 \quad (1.5)$$

$$\text{Posons } \alpha_i = A_i \sqrt{1 - |\Gamma_i|^2} \quad (1.6)$$

$$\beta_i = B_i \sqrt{1 - |\Gamma_i|^2} \quad (1.7)$$

L'équation 1.5 s'écrit de la façon simplifiée comme suit :

$$P_i = |\alpha_i \Gamma_2 + \beta_i|^2 |b_2|^2 \quad i=3..6 \quad (1.8)$$

Généralement, on conçoit le réfléctomètre de façon à ce que la puissance mesurée par le détecteur 3 soit indépendante de la charge présentée au port de mesure. Ainsi avons-nous :

$$P_3 = |\alpha_3 \Gamma_2 + \beta_3|^2 |b_2|^2 \quad (1.9)$$

En faisant le rapport des équations 1.8 et 1.9, nous obtenons

$$\frac{P_i}{P_3} = \frac{|\alpha_i \Gamma_2 + \beta_i|^2}{|\alpha_3 \Gamma_2 + \beta_3|^2} = \frac{\left| \frac{\alpha_i}{\beta_3} \Gamma_2 + \frac{\beta_i}{\beta_3} \right|^2}{\left| \frac{\alpha_3}{\beta_3} \Gamma_2 + 1 \right|^2} \quad (1.10)$$

Définissons le rapport  $|W_k|^2 = \frac{P_i}{P_3}$  pour  $k=1,2,3$  et  $i=k+3$  (1.11)

Les équations 1.10 et 1.11 deviennent :  $|W_k|^2 = \frac{|d_k \Gamma_2 + e_k|^2}{c \Gamma_2 + 1}$  (1.12)

$$\text{avec } d_k = \frac{\alpha_i}{\beta_3}; \quad e_k = \frac{\beta_i}{\beta_3}; \quad c = \frac{\alpha_3}{\beta_3}$$

Ces équations définissent trois cercles dans le plan complexe. Leur point de concours détermine le coefficient de réflexion  $\Gamma_2$  au port de mesure. Pour expliciter les équations de cercles, il faudra connaître les paramètres  $c$ ,  $d$  et  $e$  de l'équation 1.12. C'est ce que vise la calibration du six- port.

### 1.3.4 Techniques de calibration de la jonction six- port

Il existe plusieurs méthodes de calibration d'un six- port [4]. Celles développées dans la littérature sont basées sur la résolution des équations générées par la réduction d'un six- port conventionnel à un quatre- port. Parmi les techniques d'étalonnage, citons :

- la méthode à sept standards (Woods)

- la méthode Shihe Li

- La méthode à standards et demi (Hodgetts)

- La méthode à charge coulissante (Ghannouchi)

- La méthode d'Engen [5]

La différence entre ces méthodes réside dans la façon de construire les équations en utilisant des étalons connus, des charges variables ou fixes [4]. Dans la suite du chapitre, nous présenterons la méthode Engen dont l'avantage est de rendre l'étalonnage facile de programmation.

Tout comme les autres méthodes, elle consiste à réduire le six- port en quatre- port et à rajouter une boîte d'erreur qui servira de correction par rapport au plan de mesure [5, 6, 7, 8]. La figure 1.5 présente sa procédure de calibration

*Figure 1.5 Procédure de calibration.*

En extrayant le coefficient de réflexion à partir de l'équation 1.12, nous obtenons :

$$\Gamma_2 = \frac{e_k - W_k}{cW_k - d_k} \quad (1.13)$$

En posant  $Q_k = |W_k|^2$ , nous définissons 3 équations par élimination de  $\Gamma_2$  : (1.14)

$$Q_1 = |W_1|^2 \quad (1.15)$$

$$A^2 Q_2 = |W_1 - m|^2 \quad (1.16)$$

$$B^2 Q_3 = |W_1 - n|^2 \quad (1.17)$$

A, B, m et n étant des paramètres liés à c, d et e.

Étant donné que les équations sont définies dans le plan complexe, nous généraliserons en utilisant la forme complexe des paramètres.

$$m = M \cos(\theta) + jM \sin(\theta) \quad (1.18)$$

$$n = N \cos(\phi) + jN \sin(\phi) \quad (1.19)$$

$$W_1 = u_1 + jv_1 \quad (1.20)$$

En faisant la différence entre les équations 1.15, 1.16 et 1.17, nous obtenons :

$$A^2 Q_2 - Q_1 = -2Mu_1 \cos(\theta) - 2Mv_1 \sin(\theta) + M^2 \quad (1.21)$$

$$B^2 Q_3 - Q_1 = -2Nu_1 \cos(\phi) - 2Nv_1 \sin(\phi) + N^2 \quad (1.22)$$

Ces 2 dernières équations peuvent s'exprimer sous forme matricielle :

$$\begin{pmatrix} u_1 \\ v_1 \end{pmatrix} = (\sin(\phi - \theta))^{-1} \begin{pmatrix} \sin \phi & -\sin \theta \\ -\cos \phi & \cos \theta \end{pmatrix} \begin{pmatrix} \frac{M^2 + Q_1 - A^2 Q_2}{2M} \\ \frac{N^2 + Q_1 - B^2 Q_3}{2N} \end{pmatrix} \quad (1.23)$$

Une façon de transformer les variables complexes en réelles est de déclarer d'autres variables qui seront associées à leur module. Posons donc :

$$p = |m - n|^2 \quad (1.24)$$

$$q = |n|^2 \quad (1.25)$$

$$r = |m|^2 \quad (1.26)$$

Nous pouvons simplifier l'équation 1.23 comme suit :

$$\begin{pmatrix} u_1 \\ v_1 \end{pmatrix} = (\sin(\phi - \theta))^{-1} \begin{pmatrix} \sin \phi & -\sin \theta \\ -\cos \phi & \cos \theta \end{pmatrix} \begin{pmatrix} \delta \\ \varepsilon \end{pmatrix} \quad (1.27)$$

avec  $\chi = \frac{p - q - r}{2\sqrt{qr}}$  (1.28)

$$\delta = \frac{M^2 + Q_1 - A^2 Q_2}{2M} = \frac{r + Q_1 - A^2 Q_2}{2\sqrt{r}} \quad (1.29)$$

$$\varepsilon = \frac{N^2 + Q_1 - B^2 Q_3}{2N} = \frac{q + Q_1 - B^2 Q_3}{2\sqrt{q}} \quad (1.30)$$

D'autre part, l'équation 1.15, pourrait s'écrire autrement :

$$Q_1 = \begin{pmatrix} u_1 \\ v_1 \end{pmatrix}^t \begin{pmatrix} u_1 \\ v_1 \end{pmatrix} \quad (1.31)$$

En remplaçant les équations 1.27 à 1.30 dans 1.31, on obtient une équation dont les seuls paramètres sont  $A^2$ ,  $B^2$ ,  $p$ ,  $q$  et  $r$  qui satisfont à l'équation suivante :

$$\begin{aligned} pQ_1^2 + qA^4Q_2^2 + rB^4Q_3^2 + (r-p-q)A^2Q_1Q_2 + (p-r-q)B^2Q_1Q_3 + \\ (p-r-q)A^2B^2Q_1Q_3 + p(p-r-q)Q_1 + q(q-r-p)A^2Q_2 + r(r-p-q)B^2Q_3 + pqr = 0 \end{aligned} \quad (1.32)$$

En linéarisant 1.32, nous avons :

$$X_1Q_1^2 + X_2Q_2^2 + X_3Q_3^2 + X_4Q_1Q_2 + X_5Q_1Q_3 + X_6Q_2Q_3 + X_7Q_1 + X_8Q_2 + X_9Q_3 + 1 = 0 \quad (1.33)$$

### 1.3.5 Étalonnage treize standards

Les paramètres  $A^2$ ,  $B^2$ ,  $p$ ,  $q$  et  $r$  peuvent être extraits en branchant successivement 9 charges différentes. En pratique, on utilise 13 charges réparties uniformément sur l'abaque de Smith. On peut utiliser à cet effet un circuit mobile et des atténuateurs pour obtenir les 13 charges pour lesquelles on lit les puissances de sortie du port 3 au port 6. La résolution du système nous fournit les paramètres de calibration :

$$\begin{aligned} A^2 &= \sqrt{prX_2} \\ B^2 &= \sqrt{pqX_3} \\ q &= \frac{2X_4 - X_7X_8}{2X_1X_8 - X_7X_4} \\ r &= \frac{2X_5 - X_7X_9}{2X_1X_9 - X_7X_5} \\ p &= r + q + \frac{X_7}{X_1} \end{aligned} \quad (1.34)$$

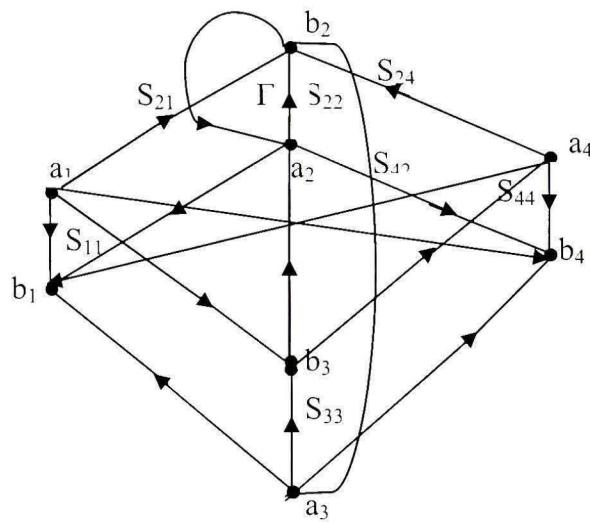

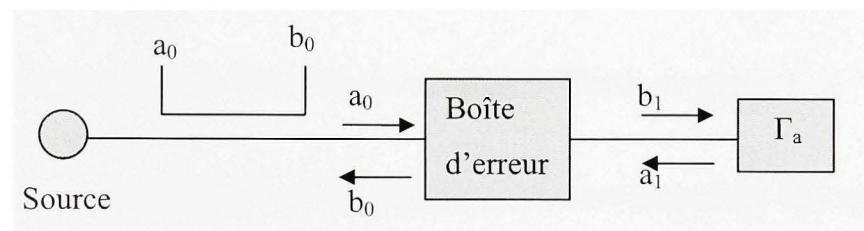

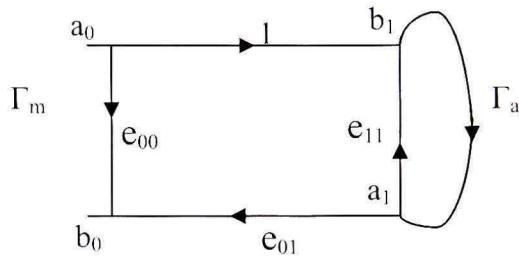

### 1.3.6 Boîte d'erreur

Après avoir calibré le six-port, c'est-à-dire trouvé  $W$ , il ne nous reste qu'à calculer le coefficient de réflexion de la charge sous test. On fait appel à la notion de boîte d'erreur par rapport à laquelle s'effectue le déplacement du plan de mesure. La boîte d'erreur est en d'autres termes la transformation qui permet de passer le plan de calcul  $W$  au plan physique  $\Gamma$  tel qu'illustré à la figure 1.6 :

*Figure 1.6 Boîte d'erreur.*

Elle peut être représentée par une matrice  $2 \times 2$  de paramètres de dispersion  $S$ . La relation de changement de plan de référence est donnée comme suit [9] :

$$W = S_{11} + \frac{S_{12}S_{21}\Gamma}{1 - S_{22}\Gamma} \quad (1.35)$$

Sous forme bilinéaire, cette relation s'écrit :

$$W = \frac{d\Gamma + e}{c\Gamma + 1} \quad (1.36)$$

L'équation 1.36 est en parfaite adéquation avec 1.12 que nous avons démontrée plus haut. Il suffit alors de déterminer les constantes  $c$ ,  $d$  et  $e$  à partir de trois étalons bien connus ainsi qu'une quatrième charge afin de supprimer l'ambiguïté de signe [4] : on parle de méthode trois standards et demi.

### **1.3.7 Mesure de performance du six- port**

Les performances du six- port dépendent principalement de la construction physique de son circuit ainsi que de la justesse de l'étalonnage. Les paramètres de calibration ( $A^2$ ,  $B^2$ ,  $p$ ,  $q$ ,  $r$ ,  $c$ ,  $d$  et  $e$ ) déterminent le positionnement des centres de cercles (notés  $q_i$ ) dont les rayons sont liés à la gamme dynamique des détecteurs de puissance. La simulation par ordinateur [6] révèle que l'étalonnage est moins fiable pour des  $|q_i|$  proches de 1 ou de  $\Gamma$ . Par contre les résultats sont concluants pour  $|q_i| \approx 1.5$ . Pour une jonction idéale,  $|q_1|=|q_2|=|q_3|$  avec une différence de phase de  $120^\circ$  entre eux [6].

### **1.3.8 Avantages et inconvénients des analyseurs de réseau homodynes**

Le principal avantage des systèmes homodynes réside dans la simplicité de sa conception faisant intervenir des circuits linéaires. De plus ils offrent la possibilité de mesurer le flux de puissance contrairement au système hétérodyne. Par contre, ils sont sensibles à la variation des fréquences. A cela s'ajoute l'effort de calcul de la procédure d'étalonnage.

Si l'agilité et la reconfigurabilité sont les principaux critères visés dans les prochains systèmes de communication, il importe avant tout de connaître l'état de fonctionnement des différents circuits intégrés pour pouvoir modifier leur caractéristique dans le temps. Les techniques actuelles de caractérisation s'avèrent alléchantes mais ne répondent pas toujours aux critères coût, simplicité et flexibilité. En effet, nous avons vu dans les sections précédentes que la technique hétérodyne nécessite l'utilisation des circuits complexes qui du coup affectent son coût. La méthode six- port quant à elle paraît attrayante de part sa simplicité de conception. Toutefois la difficulté réside dans la procédure d'étalonnage paraissant très laborieuse. Le tableau suivant résume les avantages et inconvénients des systèmes de caractérisation existant par rapport aux exigences du marché des télécommunications :

| Systèmes   | Agilité | Reconfigurabilité | Faible coût | Facilité |

|------------|---------|-------------------|-------------|----------|

| Hétérodyne | NON     | NON               | NON         | OUI      |

| Homodyne   | NON     | NON               | OUI         | NON      |

Nous proposons alors une nouvelle approche de caractérisation.

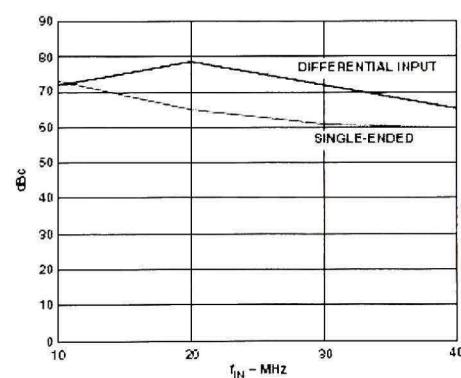

#### 1.4 Nouvelle approche de caractérisation

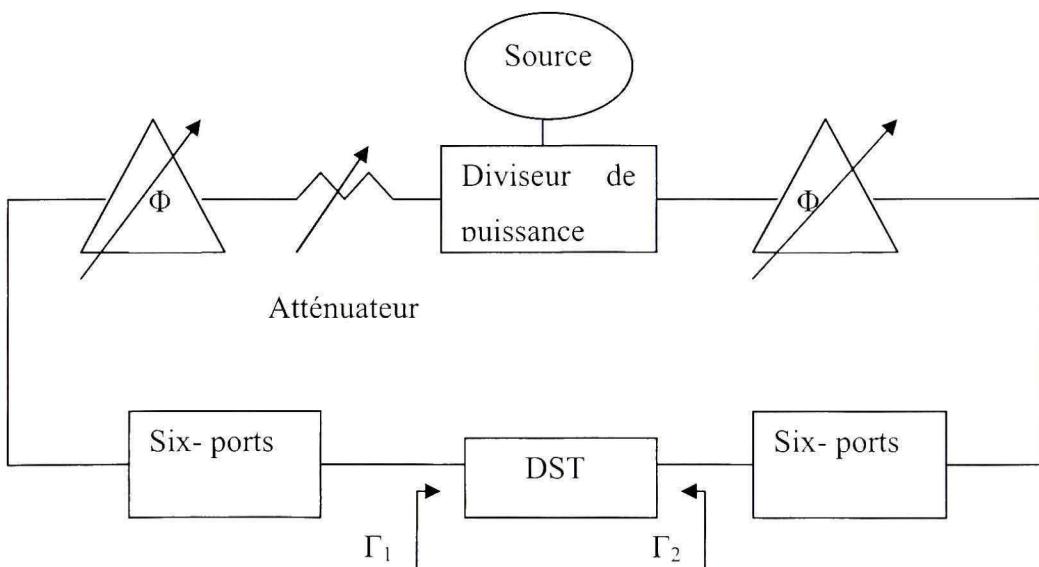

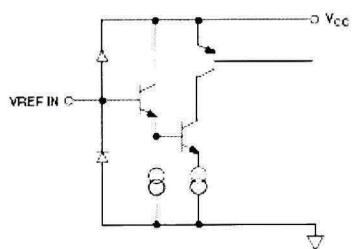

La nouvelle approche de caractérisation retenue en guise de compromis à ces différentes techniques consiste à utiliser un simple détecteur de gain et de phase. Nous avons opté pour le détecteur d'Analog Devices (AD8302) qui permet de connaître la différence d'amplitude et de phase entre deux signaux RF présentés à ses entrées. Des mesures de réflexion et en transmission peuvent être réalisées avec différentes configurations en utilisant des coupleurs bidirectionnels et au besoin des circulateurs ou isolateurs.

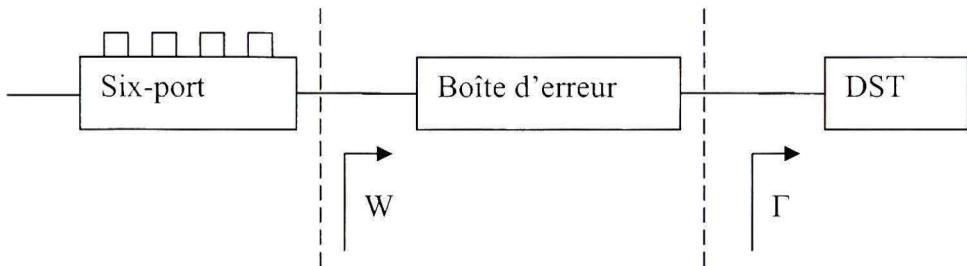

Cette technologie à coût faible permet donc de mesurer les paramètres S d'un DST tout comme un analyseur de réseau à six- port et ne nécessite pas une procédure fastidieuse de calibration. Une topologie de mesure se basant sur le détecteur choisi est illustrée à la figure 1.7 :

Figure 1.7 Exemple de topologie de mesure avec le AD8302.

## Méthodologie

La méthodologie d'utilisation du AD8302 consiste à se servir dans un premier temps de deux sources indépendantes pour valider les performances de la carte. Dans un second temps, nous utiliserons des coupleurs .Dans ce cas, les sources deviennent dépendantes ; il est donc nécessaire d'envisager des techniques de calibration.

### **1.5 Conclusion**

L'évaluation de la performance des circuits RF passifs ou actifs se fait par l'entremise d'instruments de mesure précis. L'analyseur de réseau est l'outil par excellence pour assurer la caractérisation de ces circuits. Dans ce chapitre, nous avons présenté les différents types d'analyseurs de réseau : homodyne et hétérodyne ainsi que leur principe de fonctionnement. L'analyseur de réseau hétérodyne est basé sur le principe de transposition de fréquences à partir des mélangeurs, des filtres, des multiplicateurs de fréquences qui le constituent. Ce qui le rend cher. L'analyseur de réseau homodyne quant à lui se fait distinguer par la simplicité de son circuit, mais en revanche s'avère laborieux à calibrer. Nous avons par conséquent investigué une nouvelle approche de mesure afin de répondre aux critères d'agilité, de flexibilité, de reconfigurabilité avec une technologie à faible coût : utilisation du détecteur d'Analog Devices AD8302 qui fera l'objet du chapitre suivant.

## CHAPITRE 2

### ÉTUDE ET CARACTÉRISATION DE LA CARTE AD8302 D'ANALOG DEVICES

#### 2.1 Introduction

Développé par la compagnie Analog Devices, l'AD8302 est un des premiers circuits intégrés permettant de mesurer le rapport complexe de deux signaux indépendants. Il serait l'aboutissement de plusieurs autres produits développés par la même compagnie pour pallier certaines difficultés reliées à la détection de puissance par les diodes (AD8309, AD8310, AD8313, AD8314...). En effet, la connaissance des niveaux de puissances est d'une grande utilité dans les systèmes de radiocommunication sans fil car elle permet d'ajuster les paramètres de l'"Automatic Gain Control " (AGC) dans une chaîne de transmission. Or les circuits de détections conventionnellement utilisés sont à base de diodes. Ces dernières exigent un effort de calibration, de linéarisation et sont souvent confrontés à un problème thermique. Pour venir à bout de ces problèmes, Analog Devices a développé plusieurs types d'amplificateurs logarithmiques démodulateurs permettant de mesurer le rapport de deux signaux en terme de puissance à partir des enveloppes des signaux. Toutefois dans plusieurs applications, il est nécessaire de connaître la différence relative en phase des signaux. Un détecteur de phase a été ajouté aux fonctions des amplificateurs logarithmiques démodulateurs. Le nouveau produit sera désigné sous le nom d'AD8302.

Utilisé à ses débuts comme un comparateur de signaux (détecteur de gain et de phase (DGP)), ce nouvel opus trouvera son utilité dans plusieurs autres applications. Il peut être entre autre utilisé comme un réfléctomètre pour effectuer l'ajustement d'une charge telle une antenne afin de minimiser le taux d'ondes stationnaire.

Dans ce chapitre, nous passerons en revue le principe de fonctionnement de la carte AD8302, ses modes et conditions d'opération et ferons un bref aperçu de ses applications. Nous ferons par la suite une étude détaillée pour mettre en relief ses performances.

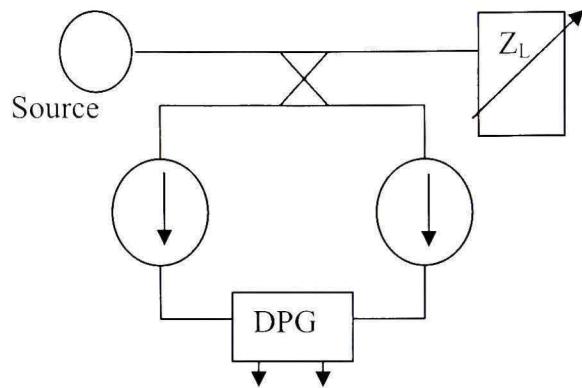

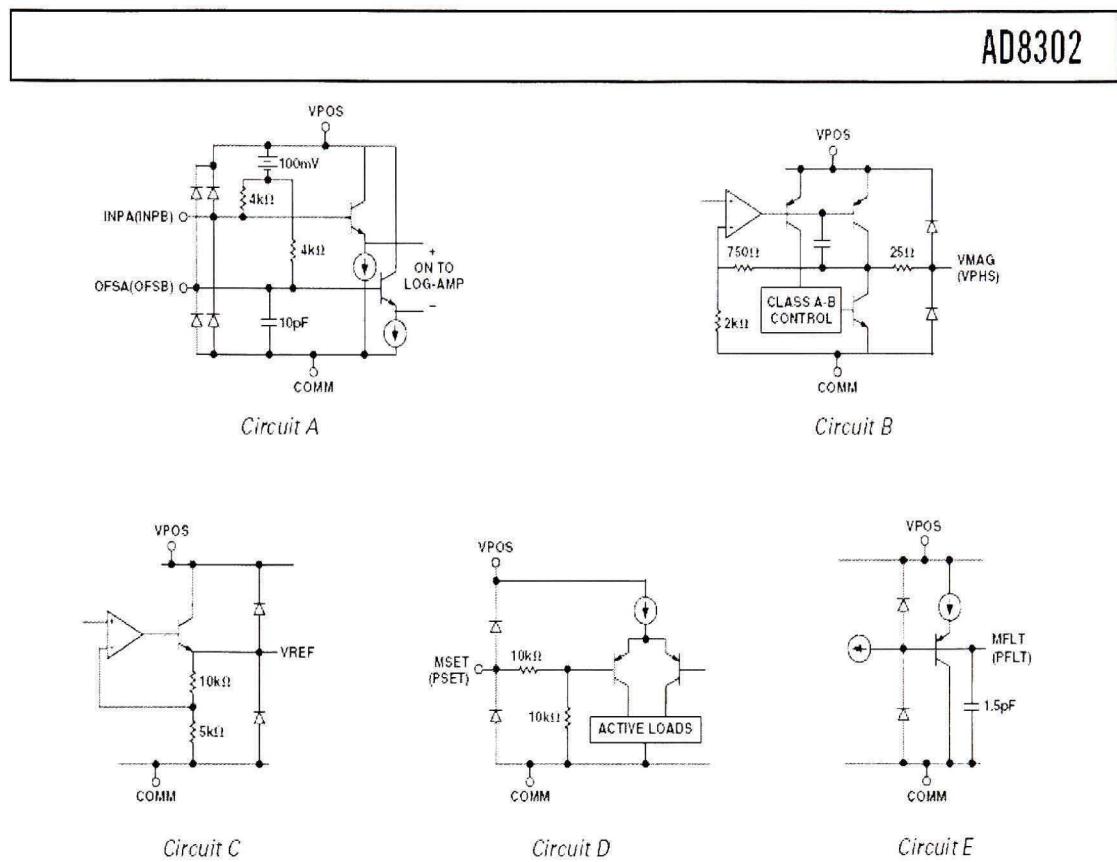

## 2.2 Description du système

### 2.2.1 Principe de fonctionnement

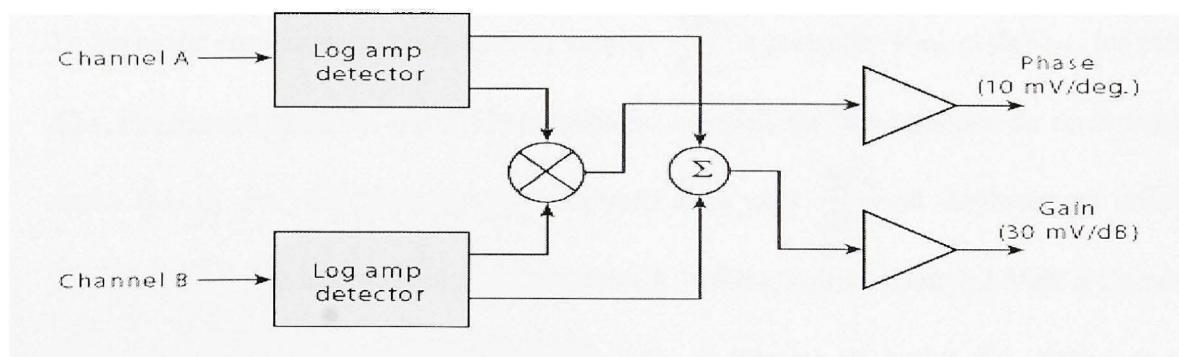

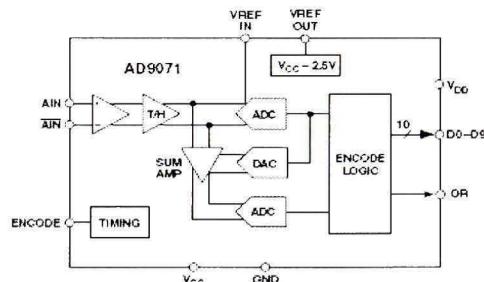

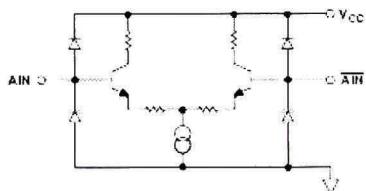

L'AD8302 permet de mesurer en dB le rapport de niveau de puissance et la différence de phase en degrés en produisant à la sortie deux tensions analogiques : une proportionnelle au rapport de puissance et l'autre relative au déphasage des signaux RF à ses deux entrées.

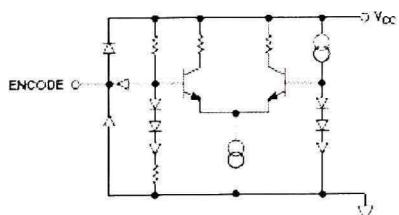

Son circuit simplifié est constitué de deux détecteurs logarithmiques identiques ayant chacun une plage dynamique de 60 dB, un détecteur numérique de phase et des amplificateurs de puissance. Le détecteur logarithmique produit deux signaux : un proportionnel au logarithme de l'enveloppe du signal d'entrée et le second représente le signal limité IF comportant l'information sur la phase et la fréquence. Les deux premières sorties des détecteurs sont envoyées dans un combinateur pour obtenir le rapport d'amplitude des signaux tandis que les signaux IF sont injectés dans un mélangeur pour assurer la détection de la différence de phase. La figure 2.1 tirée de la fiche technique du AD8302 montre de façon schématique le fonctionnement de la puce.

*Figure 2.1 Circuit simplifié du AD8302.*

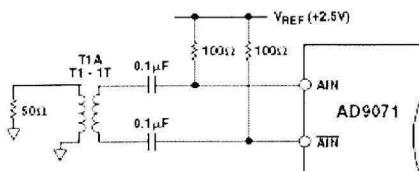

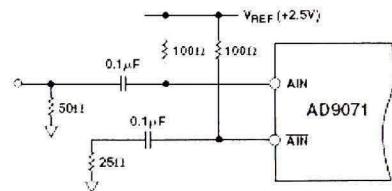

Les performances de la carte d'évaluation dépendent de plusieurs paramètres dont la différence d'amplitudes des signaux appliqués, leur bande passante ainsi que la température

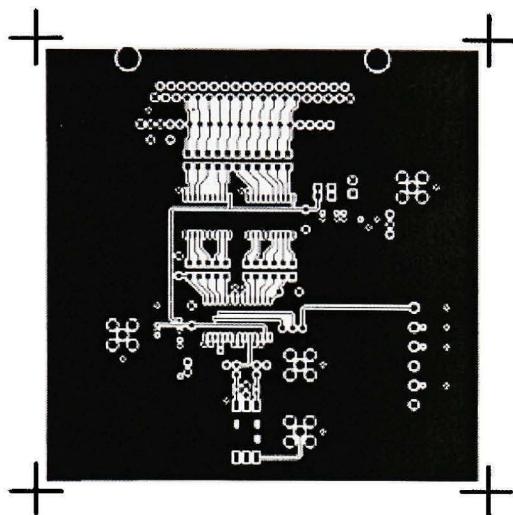

de fonctionnement du dispositif. Le circuit complet de la carte (détecteur de gain et de phase DPG) est montré à la figure 2.2 :

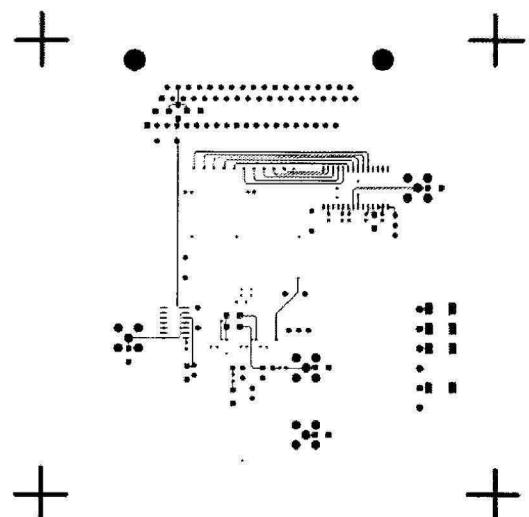

Figure 2.2 Carte d'évaluation AD8302 (DPG).

Elle peut être utilisée en mode comparateur ou en mode contrôleur à partir des switchs (1 et 2). En mode comparateur, on mesure le rapport  $\frac{RF_{in1}}{RF_{in2}}$  à partir de  $V_{Mag}$  et de  $V_{phs}$ , les pins  $V_{ref}$ ,

$G_{Set}$ ,  $P_{Set}$  restent flottants. En mode contrôleur, on applique des tensions de commande aux accès  $G_{Set}$  et  $P_{Set}$ . Par exemple pour indiquer si le gain  $\frac{RF_{in1}}{RF_{in2}}$  est supérieur ou inférieur à

10dB, on applique une tension correspondant à 10dBm, soit environ 1.2 Volt à l'accès  $G_{Set}$ .

Si le rapport  $\frac{RF_{in1}}{RF_{in2}}$  est supérieur à 10dB alors la tension de sortie  $V_{Mag}$  atteint sa valeur maximale qui avoisine 1.8V. Dans le cas échéant, la tension chute à sa valeur minimale proche de 0. On peut procéder de la même façon pour contrôler la phase en appliquant la tension de référence à l'accès  $P_{Set}$ .

Les fonctions de gain et de phase sont indépendantes l'une de l'autre. Il est donc possible d'utiliser simultanément une des fonctions en mode comparateur (ou mode de mesure) et l'autre en mode contrôleur.

### 2.2.2 Caractéristiques du DGP

Mathématiquement, la sortie du détecteur s'exprime comme suit [Annexe I]:

$$V_{out} = V_{slp} \log\left(\frac{V_{in}}{V_z}\right) \quad (2.1)$$

avec  $V_{in}$  la tension du signal d'entrée,  $V_z$  la tension de calibration pour laquelle  $V_{out}$  s'annule (0dB); cette tension est appelée "tension d'interception" et change en fonction de la forme du signal;  $V_{slp}$  est la pente exprimée en volt/Décade. Généralement, on utilise la forme  $V_{slp}/20$  qui représente le voltage par décibel (Volt/dB).

Pour deux signaux entrants de voltage  $V_{inA}$  et  $V_{inB}$ , la sortie de chaque amplificateur logarithmique s'écrira de la façon suivante (du fait de l'identité des deux détecteurs):

$$\begin{aligned} V_{outA} &= V_{slp} \log\left(\frac{V_{inA}}{V_z}\right) \\ V_{outB} &= V_{slp} \log\left(\frac{V_{inB}}{V_z}\right) \end{aligned} \quad (2.2)$$

En faisant la différence des équations (2.2), nous obtenons :

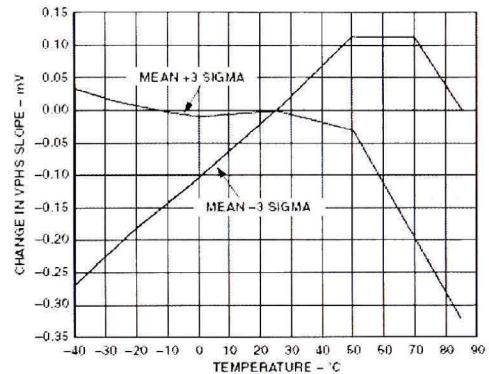

$$\begin{aligned} V_{Mag} &= V_{outA} - V_{outB} = V_{slp} \left( \log\left(\frac{V_{inA}}{V_z}\right) - \log\left(\frac{V_{inB}}{V_z}\right) \right) \\ &= V_{slp} \log\left(\frac{V_{inA}}{V_{inB}}\right) \end{aligned} \quad (2.3)$$

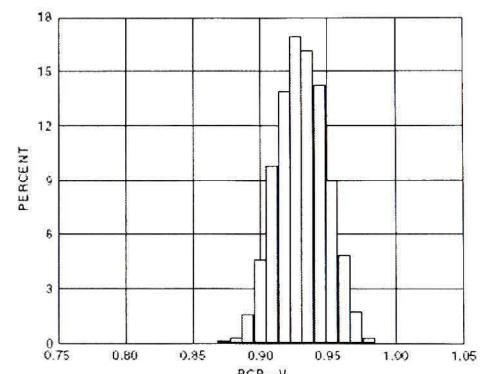

La pente  $V_{slp}$  peut être légèrement sensible à la température, à la fréquence d'opération ou à l'alimentation du circuit. Dans tous les cas, sa valeur moyenne est de 0.6 Volt/Décade ou 30mV/dB. La puissance des signaux d'entrées doit être comprise entre -60dBm et 0 dBm.

Pour éviter des voltages négatifs, un offset (tension de référence) a été introduit dans le circuit de façon à ce que la sortie minimale soit de 0 Volt. L'équation (2.3) devient alors :

$$V_{Mag} = V_{slp} \log\left(\frac{V_{inA}}{V_{inB}}\right) + V_{ref} \quad (2.4)$$

où  $V_{ref} = 0.9\text{ Volt}$ . Cette dernière représente la fonction de transfert du DPG en amplitude. La tension de sortie  $V_{Mag}$  peut varier alors de 0 à 1.8 Volt et la différence de puissances en décibel pouvant être détectée est de  $\pm 30\text{dB}$ .

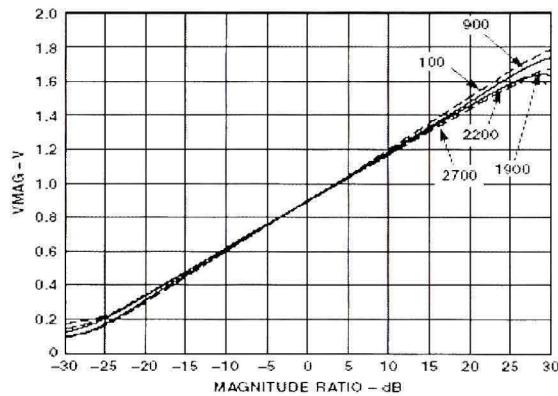

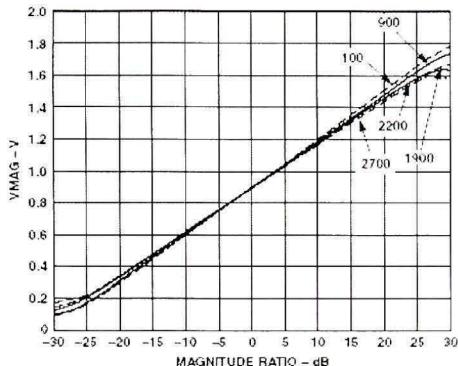

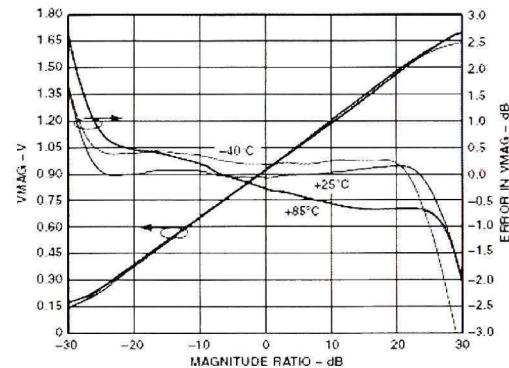

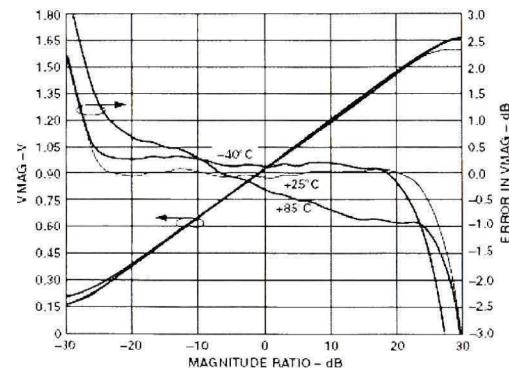

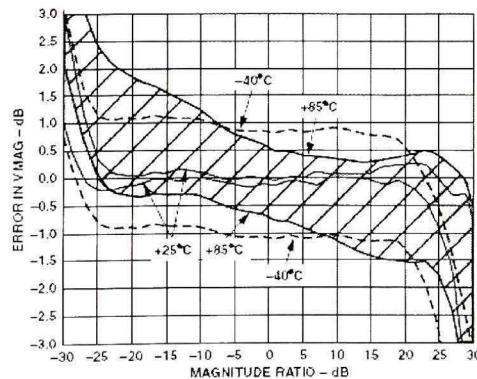

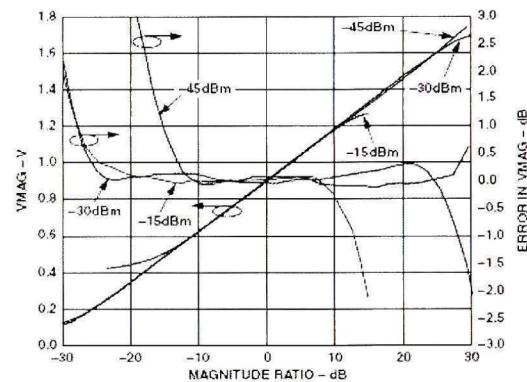

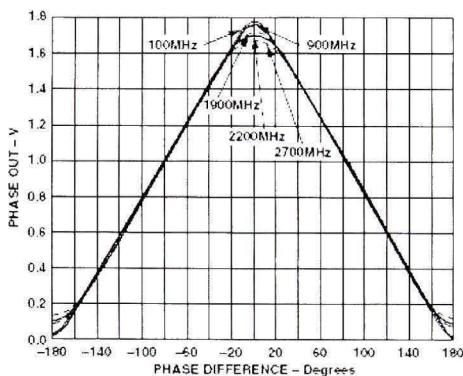

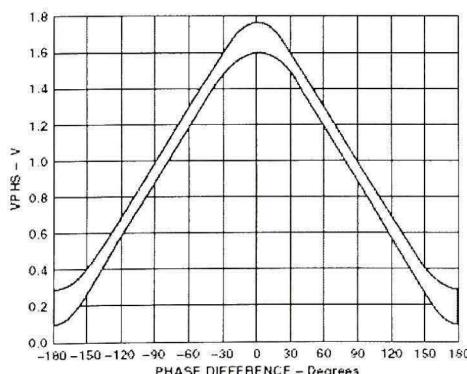

La figure 2.3 illustre la variation de la tension  $V_{Mag}$  en fonction des signaux d'entrée pour des fréquences radio cellulaires les plus connues [Annexe I]:

**Figure 2.3 Fonction de transfert en amplitude du DPG.**

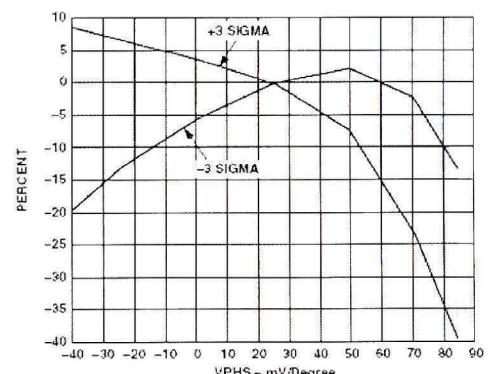

De façon analogue à la détection d'amplitude, l'équation régissant la détection de phase s'exprime en fonction de la différence de phase des signaux en suivant une pente :

$$V_{Phs} = V_\Phi (\Phi(V_{inA}) - \Phi(V_{inB})) \quad (2.5)$$

L'équation (2.5) est appelée fonction de transfert en phase du DPG.  $V_\Phi$  représente la pente en mV/degré. Idéalement sa valeur absolue est de 10mV/degré. La fonction  $\Phi(x)$  représente la phase relative des signaux d'entrée en degrés.

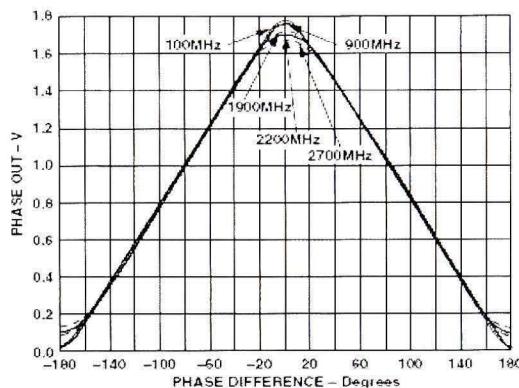

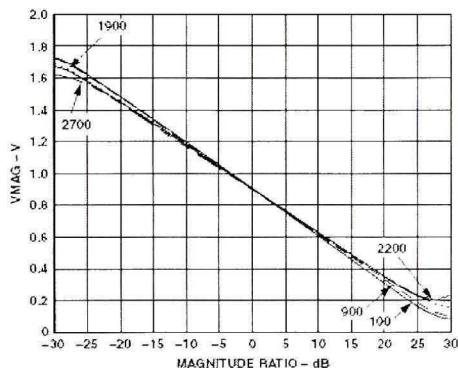

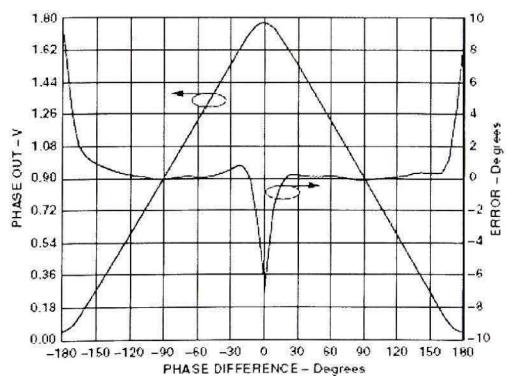

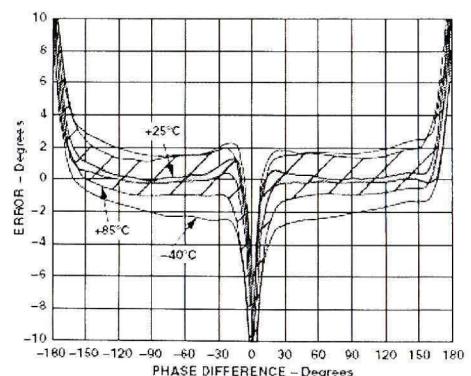

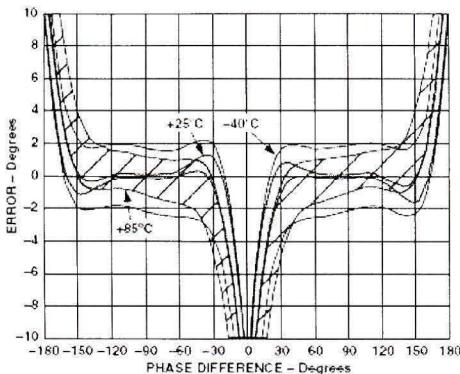

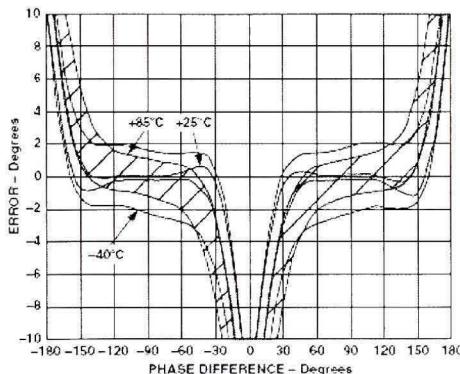

Le point central ( $V_{ref}$ ) est choisi à  $\pm 90^\circ$ . Ce qui correspond à une variation de la tension de sortie  $V_{Phs}$  de 0 à 1.8 Volt. La figure 2.4 tirée de la fiche technique du AD8302 [Annexe I] montre la réponse du circuit intégré en fonction de la différence de phase entre les deux signaux :

**Figure 2.4 Fonction de transfert en phase du DPG.**

La détection de phase se faisant de façon symétrique, il est impossible de savoir si la phase du signal A est en avance ou en retard sur la phase du signal B. Autrement dit, le DPG ne permet pas de connaître le signe associé à la différence de phase. Nous verrons plus loin comment lever cette ambiguïté de phase.

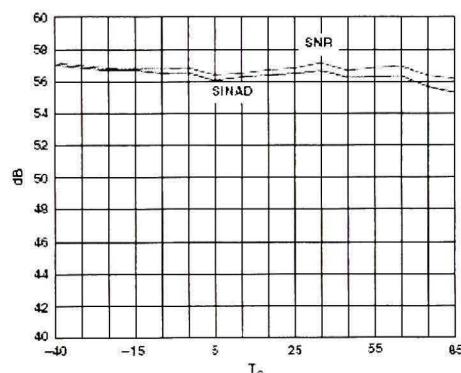

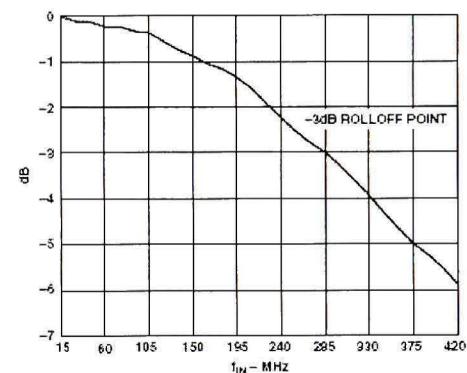

### 2.2.3 Spécifications

L'AD8302 peut opérer de 100MHz à 2.7 GHz. Il effectue toutefois des mesures précises en amplitude jusqu'à la fréquence de 3GHz. L'exactitude des mesures de phase se fait par contre sur une bande relativement réduite à 2.7 GHz. Il fonctionne particulièrement bien à de basses fréquences ; il est donc bien adapté pour les applications en bande de base, IF et RF.

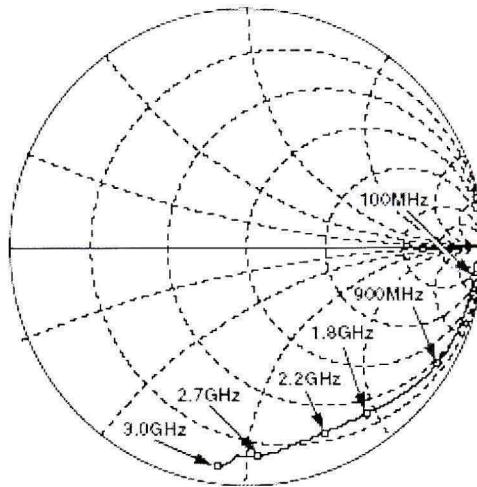

Par ailleurs, l'impédance d'entrée aux ports  $RF_{in1}$  et  $RF_{in2}$  est une fonction de la fréquence et des capacités parasites induites. Pour des fréquences modérées, elle peut équivaloir à une résistance de  $3K\Omega$  disposée en parallèle à une capacité de  $2pF$ . Aux hautes fréquences, cette

résistance peut décroître jusqu'à  $500\Omega$ . La variation de l'impédance d'entrée en fonction de la fréquence est illustrée comme suit [Annexe I] :

**Figure 2.5 Impédances d'entrée du DPG en fonction de la fréquence.**

D'après la fiche technique, le DPG est reconnu pour l'exactitude de ses mesures : 1dB d'erreur en amplitude et une plage dynamique de plus 55dB. En phase, l'erreur est de  $3^\circ$  pour une plage dynamique de  $180^\circ$ . La compilation des spécifications se tabule comme voici :

|                                          |                                                   |

|------------------------------------------|---------------------------------------------------|

| Fréquences                               | 100MHz - 2.7GHz                                   |

| Plage dynamique                          | 55dB en amplitude<br>$180^\circ$ en phase         |

| Précision                                | $\pm 1$ dB en amplitude<br>$\pm 3^\circ$ en phase |

| Impédance d'entrée aux basses fréquences | (R)3K $\Omega$ // 2pF (C)                         |

| Impédance d'entrée aux hautes fréquences | (R)3K $\Omega$ -500 $\Omega$ //2pF (C)            |

### 2.2.4 Applications

Qu'elle soit en mode de mesure ou de contrôleur, la carte peut être utilisée pour plusieurs applications. L'AD8302 offre la possibilité de mesurer continuellement la distribution de gain ou sa variation à travers une section de circuit. Il peut être configuré comme un circuit moniteur mesurant constamment la différence entre les signaux qui peut être par la suite numérisée ou être configuré comme un indicateur d'alarme s'il est utilisé en mode contrôleur. Une autre application majeure consiste à mesurer la perte ou le gain de conversion d'un mélangeur ou pour assurer le contrôle et la surveillance d'un "Power Amplifier" (PA).

D'autre part, il peut servir dans les boucles de poursuite pour réaliser les circuits de linéarisation. Son utilisation est adéquate pour toutes les architectures de linéarisation incluant la prédistorsion et le feedforward. Dans un système feedforward, il est employé pour surveiller l'annulation de la porteuse dans la première boucle du PA ainsi que l'annulation de la déformation dans la boucle "erreur-amplificateur".

## 2.3 Caractérisation du DPG

La caractérisation du DPG consiste à établir les fonctions de transfert aussi bien en phase qu'en amplitude afin d'extraire la différence en dB équivalant au rapport en amplitude des signaux et leur différence de phase. Pour ce faire, nous utiliserons deux sources indépendantes pour avoir des signaux complètement découplés. Le système est piloté par un logiciel de contrôle et d'acquisition de données : le HP VEE [12].

### 2.3.1 Présentation du logiciel HP VEE

Mis en œuvre par Agilent Technologies, HP VEE est un logiciel pour l'automatisation des instruments. Il permet d'effectuer la communication entre les équipements micro-ondes ayant un port HP-IB ou GPIB et un ordinateur. Le logiciel étant conçu sur une plateforme

graphique assez simple, l'implémentation d'un programme de contrôle consiste à relier des icônes fonctionnelles ou des objets en cascade pour former un schéma fonctionnel comme dans n'importe quel autre langage textuel. Ces blocs peuvent être de type I/O HP- IB, module de calcul, affichage, contrôle d'exécution etc. L'approche unique à la programmation visuelle du logiciel lui fournit la flexibilité, la facilité d'utilisation et la facilité d'exécution.

### 2.3.2 Description de l'appareillage

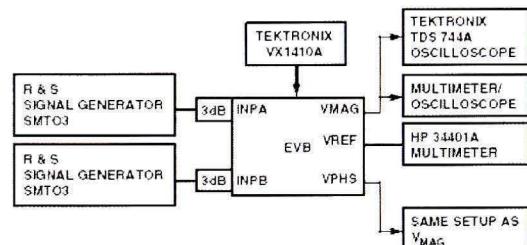

Les premiers tests ont été effectués à l'aide de deux générateurs de signaux RF synchronisés entre eux. Le DPG est alimenté par une source DC et les sorties sont relevées par des multimètres; le tout sous contrôle d'un programme VEE (confère figure 2.6) :

*Figure 2.6 Éléments de caractérisation du DPG.*

### 2.3.2.1 Générateurs de signaux RF

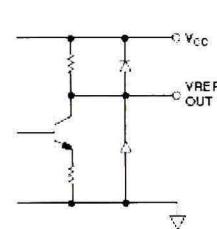

Nous avons configuré en mode “plug&play”, à partir de leur adresse, les deux générateurs de type E4433B d’Agilent. La fréquence des porteuses est initialement fixée à 900MHz. Les amplitude et phase du premier générateur sont prises comme état de référence alors que celles du second sont variables. Les deux générateurs sont verrouillés ensemble pour assurer la synchronisation. Dans un premier temps, ils seront configurés sans modulation afin de reproduire les fonctions de transfert. Nous ajouterons la modulation par la suite pour étudier son effet sur les performances du DPG.

### 2.3.2.2 Source d'alimentation

La carte peut être alimentée par une tension DC allant de 2.7 à 5.5 Volts et tire un courant équivalent de 17 à 25mA. Nous avons choisi sa valeur typique qui est de 5 Volts. Ceci correspond à un courant nominal de 19mA. Cette valeur sera maintenue durant tout le projet afin de rester dans les mêmes conditions d'opération. Nous avons utilisé lors des mesures la source E8244A syntonisée sur une échelle de 6V. Elle est branchée en série aux deux générateurs de signaux via le câble HP.

### 2.3.2.3 Multimètres

Deux multimètres E3631A sont utilisés en parallèle pour relever les tensions DC présentes aux sorties du DPG. Pour des fins de vérification, un troisième multimètre peut être branché au port  $V_{ref}$  pour s'assurer que la carte est bien calibrée. Dans le cas présent, cette tension devra correspondre à 0.9V.

Tous ces appareils étant installés et configurés sur HP VEE, l'acquisition des valeurs des multimètres se fait sous forme de fichier qui sera traité par des scripts MATLAB que nous avons intégrés au programme HP VEE pour faire une interface complète.

### 2.3.3 Fonctions de transfert expérimentales

Étant donné que l'impédance de sortie des générateurs qui est de  $50\Omega$  ne correspond pas à l'impédance d'entrée du DPG, nous avons à priori pensé à concevoir un circuit d'adaptation variable. Finalement cette idée a été négligée puis que la différence de puissances ne sera pas affectée par cette mésadaptation du fait que les deux entrées présentent la même impédance à la même fréquence d'excitation. Par contre, pour des mesures en phase, nous devons utiliser des câbles identiques puis que la phase reste sensible à la longueur des câbles utilisés.

#### 2.3.3.1 Fonctions de transfert en amplitude

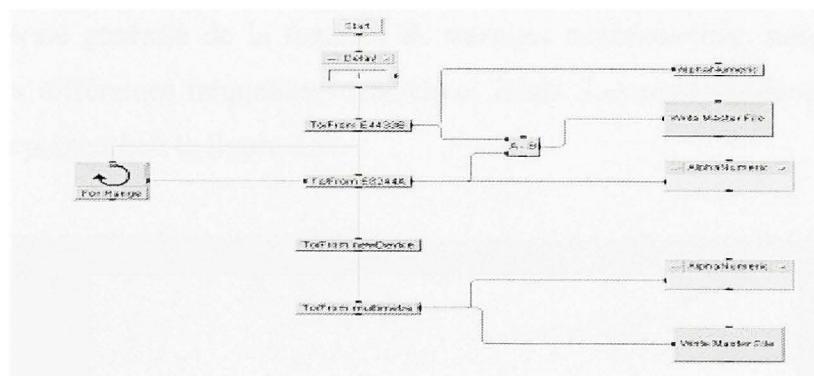

Pour obtenir la fonction de transfert en amplitude, nous avons programmé le banc de test tel que montré à la figure 2.7 à partir de HP VEE :

*Figure 2.7 Programme de fonction de transfert en amplitude.*

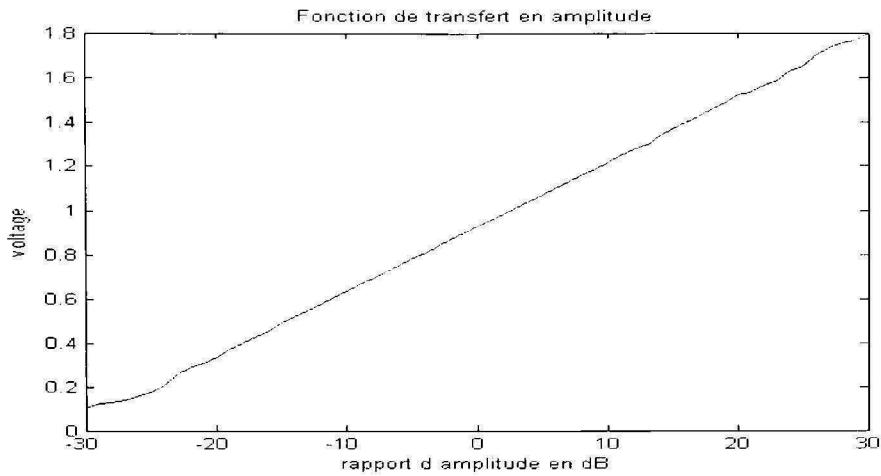

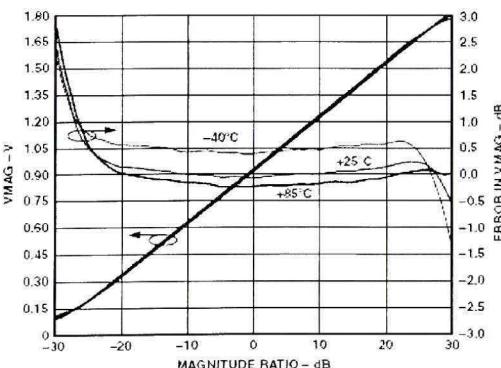

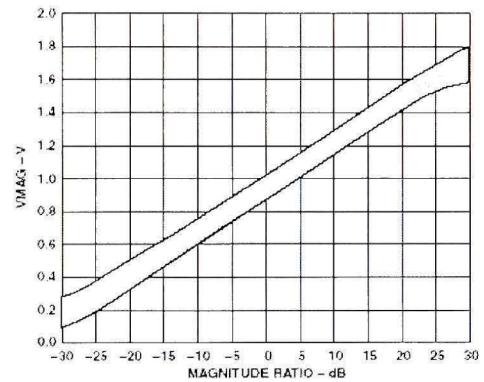

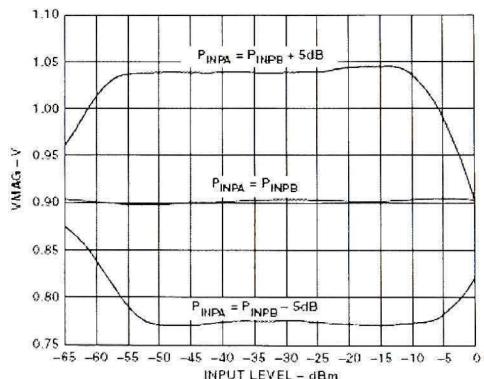

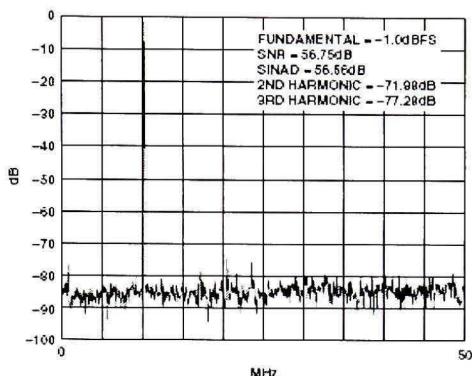

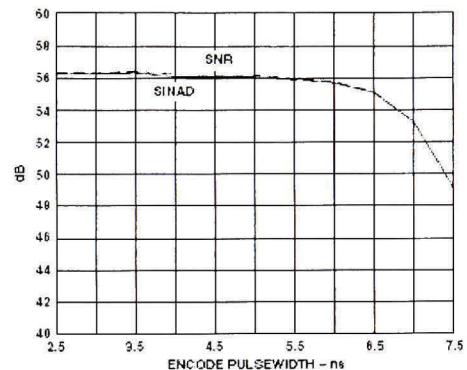

La puissance du générateur de référence est maintenue à -30dBm tandis que celle du second générateur varie de -60dBm à 0dBm. La réponse du DPG en fonction du rapport de puissances des signaux à la fréquence de 900MHz se présente à la figure 2.8 :

**Figure 2.8 Fonction de transfert expérimentale en amplitude à 900MHz.**

Nous avons une allure presque linéaire avec une pente moyenne de 28 mV/dB. Ce résultat est relativement proche de la valeur 30mV/dB prévue. Nous notons aussi une plage dynamique d'environ 60dB; preuve que la carte opère parfaitement bien à des fréquences modérées. La tension centrale équivalente à la tension référentielle ( $V_{ref}$ ) est d'environ 0.9V. Afin de valider la forme générale de la fonction de transfert expérimentale, nous avons répété les mesures pour différentes fréquentes : 1.6GHz et 2GHz. Les résultats dans ces deux cas sont identiques et présentés à la figure 2.9 :

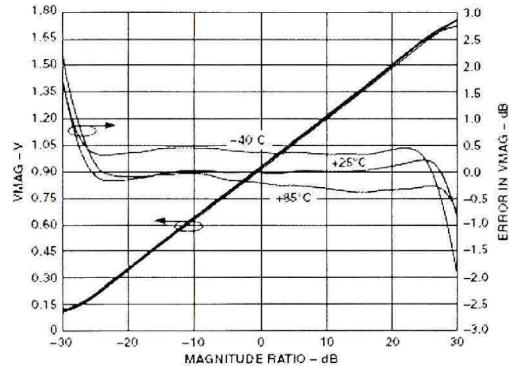

**Figure 2.9 Fonction de transfert expérimentale en amplitude à 1.6GHz et 2GHz.**

En comparant les figures 2.8 et 2.9, nous notons une similitude dans les allures des courbes. La pente dans les deux cas est de 28mV/dB et la tension centrale est très proche de 0.9V. Par contre la figure 2.9 présente une plage dynamique relativement réduite par rapport à celle de la figure 2.8. En effet la courbe devient quasi stationnaire lorsque la différence des niveaux de puissance devient supérieure à 20dB.

Au vu de ces résultats, nous pouvons déduire que le DPG a une fonction de transfert linéaire en amplitude et une plage dynamique d'au moins 50dB. Dans la suite du projet, nous utiliserons comme équation caractéristique expérimentale en amplitude, l'approximation :

$$V_{Mag} = 0.028 \Delta (\text{dB}) + 0.9 \quad (2.6)$$

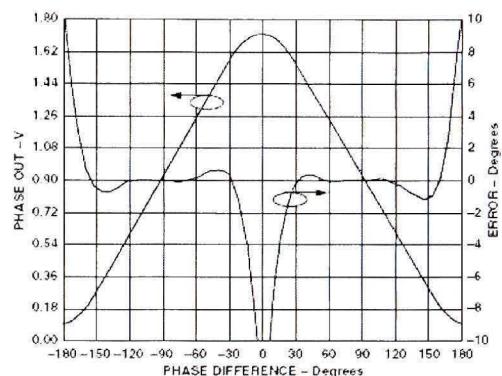

### 2.3.3.2 Fonctions de transfert en phase

Tout comme dans le cas précédent, un programme VEE a été conçu pour étudier la réponse du DPG en phase. La figure 2.10 présente en diagramme le programmé utilisé :

*Figure 2.10 Programme de fonction de transfert en phase.*

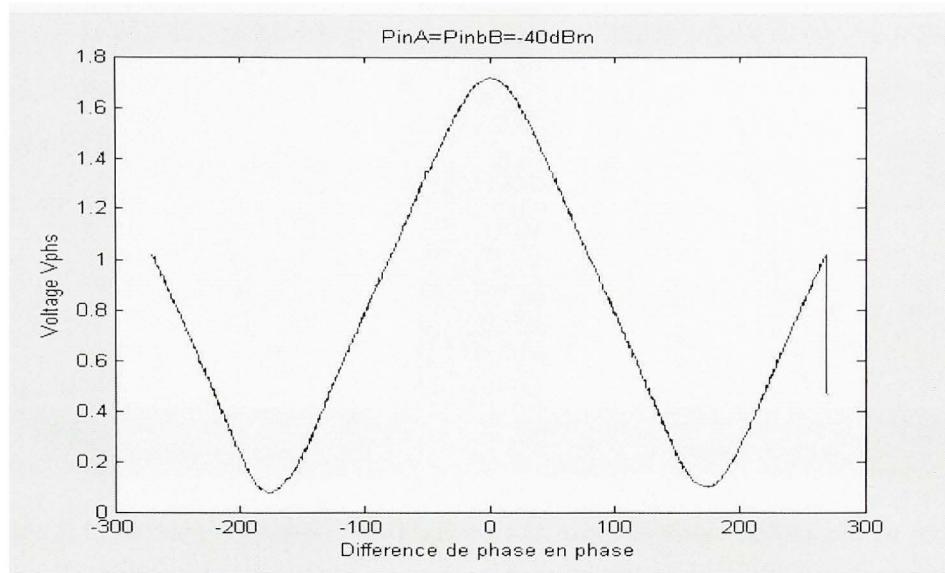

Les deux générateurs opèrent à la même fréquence initialement fixée à 900MHz et génèrent deux signaux de même niveau de puissance, à la différence que la phase du premier

générateur est nulle et celle du second varie de  $-180^\circ$  à  $180^\circ$ . La figure 2.11 illustre la réponse obtenue en phase :

*Figure 2.11 Fonction de transfert en phase.*

Les figures 2.4 et 2.11 prouvent de part leur similitude l'exactitude des mesures en phase. En effet nous retrouvons la tension référentielle  $V_{ref}$  à  $\pm 90^\circ$  telle que mentionnée plus haut. La courbe est symétrique et centrée sur  $0^\circ$  avec une pente de  $\pm 9\text{mV}/\text{degré}$ ; valeur assez proche des  $\pm 10\text{mV}/\text{degré}$  prévus en cas idéal dans la théorie du AD8302. L'équation caractéristique expérimentale en phase peut alors s'écrire de la façon suivante :

$$\begin{aligned} V_{Phs} &= 0.009\Delta_{Phs} + 1.75 && \text{Si } \Delta_{Phs} \leq 0 \\ V_{Phs} &= -0.009\Delta_{Phs} + 1.75 && \text{Si } \Delta_{Phs} \geq 0 \end{aligned} \quad (2.7)$$

Afin de mettre en évidence le déphasage provoqué par les câbles de raccordement, nous avons réalisé l'expérience qui consiste à utiliser des câbles de même type mais de longueurs différentes. Nous observons alors un décalage de la courbe par rapport à la référence comme le montre la figure 2.12.

**Figure 2.12** Mise en évidence de l'effet de la longueur des câbles sur la phase.

### 2.3.4 Mesure expérimentale de l'impédance d'entrée du DPG

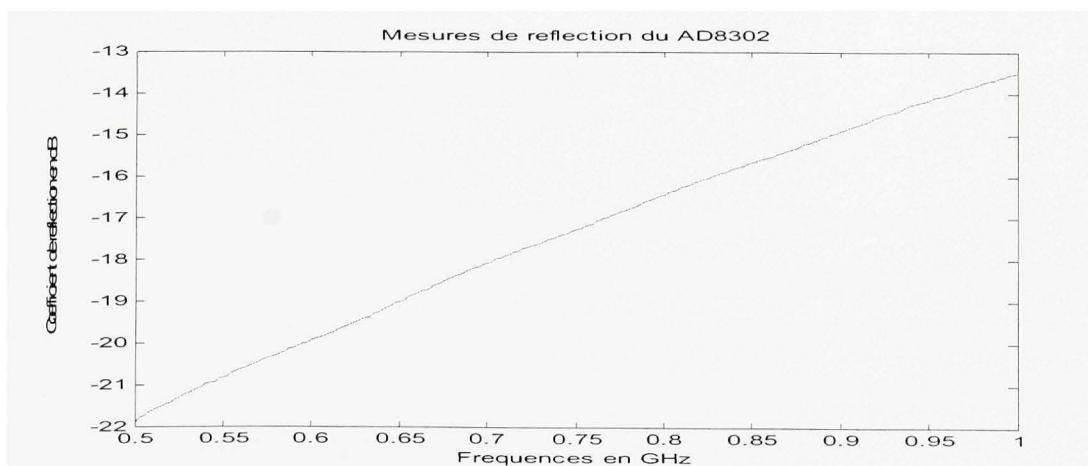

Afin de comparer l'impédance d'entrée réelle du DPG à celle indiquer sur la fiche technique, nous avons procédé à sa mesure présentée à la figure 2.13 :

**Figure 2.13** Mesure de  $S_{11}$  aux ports  $RFin1$  et  $RFin2$ .

Le coefficient de réflexion augmente en fonction de la fréquence. Ce qui laisse présager que le comportement du circuit aux basses fréquences sera meilleur qu'aux hautes fréquences.

Nous verrons plus loin que du fait de l'identité des impédances d'entrée du DPG, beaucoup de simplifications seront faites.

## 2.4 Extraction d'amplitude et de phase

Pour valider la performance de la carte, plusieurs tests ont été faits. Dans cette section nous présentons comment extraire à partir des caractéristiques du AD8302, les différences d'amplitude et de phase de signaux connus. Ceci nous permet de connaître l'erreur commise en généralisant le comportement de la carte par ses équations caractéristiques expérimentales décrites en (2.6) et (2.7).

### 2.4.1 Extraction d'amplitude

De l'équation (2.6), nous obtenons le rapport d'amplitude en dB en connaissant la tension de sortie  $V_{Mag}$  :

$$\Delta_{dB} = \frac{V_{Mag} - 0.9}{0.028} \quad (2.8)$$

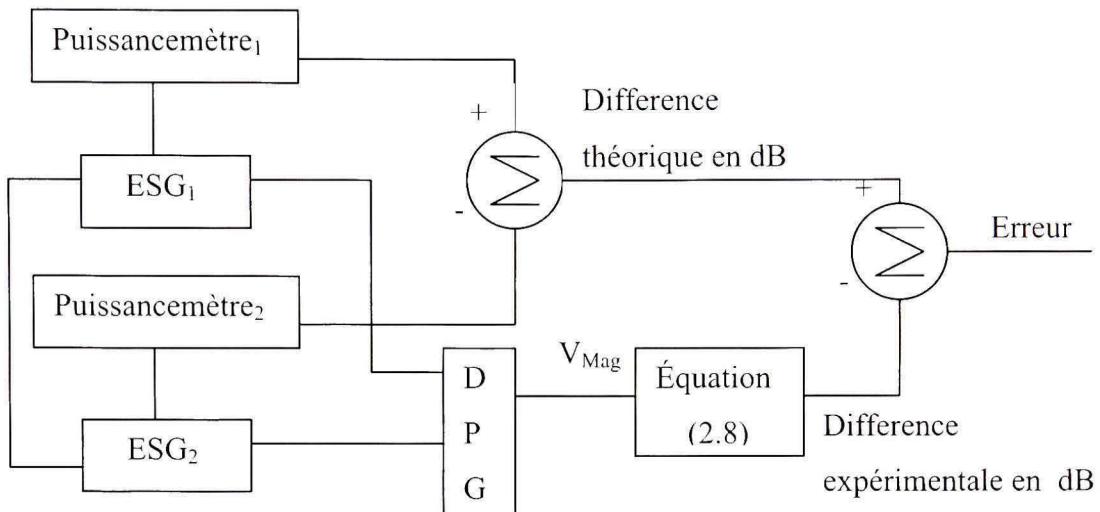

Deux signaux à amplitude connue sont générés à partir des sources RF. Leur niveau de puissance est relevé respectivement à partir de deux puissancemètres. La différence en dB des mesures des puissancemètres servira de référence théorique par rapport à laquelle nous évaluerons l'erreur commise en utilisant l'équation (2.8), une fois que le DPG est branché aux générateurs ( confère figure2.14).

*Figure 2.14 Procédure d'extraction d'amplitude.*

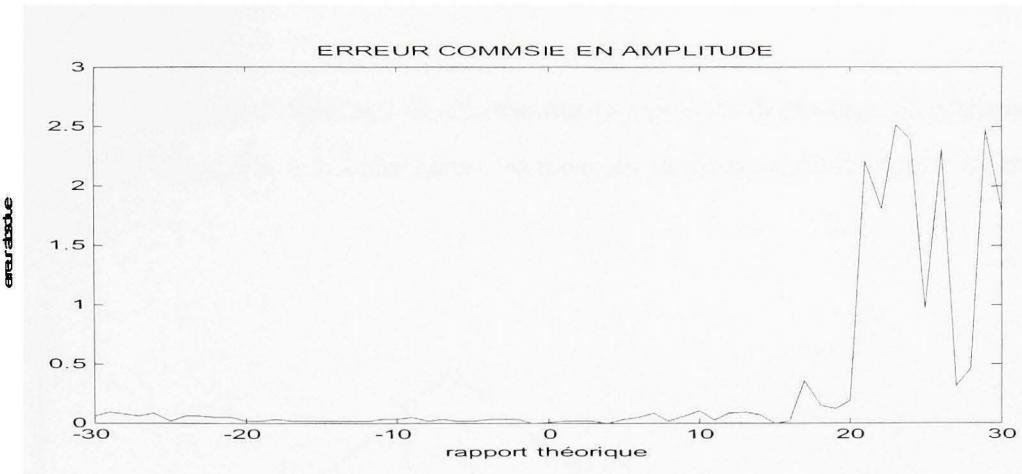

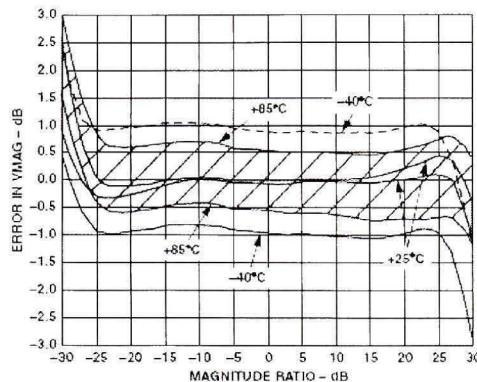

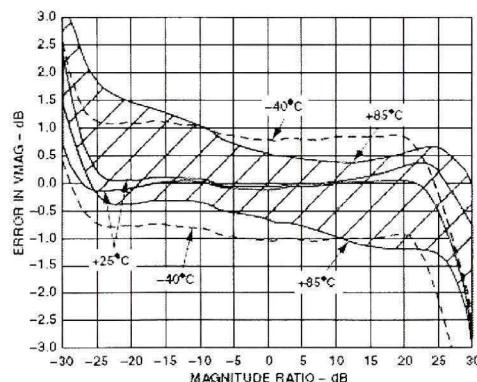

Les mesures ont été répétées plusieurs fois pour différentes fréquences : 900MHz, 1.6GHz, 2GHz. La compilation des résultats nous a permis d'obtenir la courbe d'erreur présentée à la figure 2.15.

L'extraction se fait avec une erreur de 0.2dB dans la plage dynamique (-30dB à 20 dB). Au delà de 20dB, l'erreur commise peut augmenter jusqu'à 2.5 dB. En effet dans cette zone la courbe caractérisant la fonction de transfert en amplitude a tendance à se saturer à sa valeur maximale de 1.8V.

*Figure 2.15 Erreur absolue commise en amplitude.*

## 2.4.2 Extraction de phase

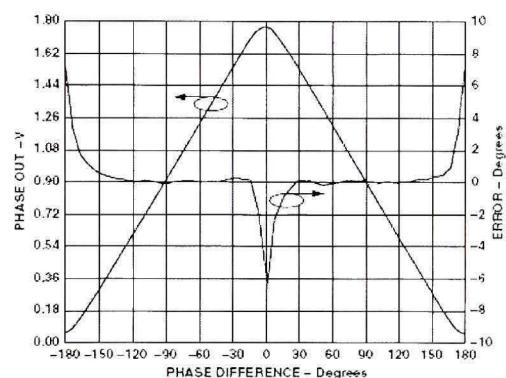

Le DPG présente une ambiguïté de signe du fait de la symétrie de la courbe caractéristique en phase. Pour lever cette ambiguïté, deux méthodes ont été investiguées.

### 2.4.2.1 Techniques de résolution d'ambiguïté de phase

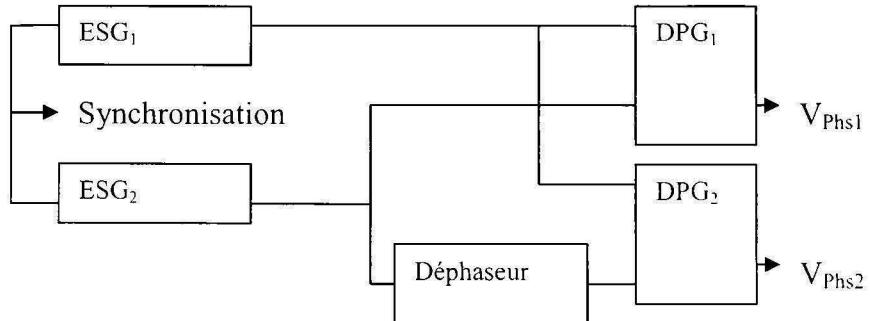

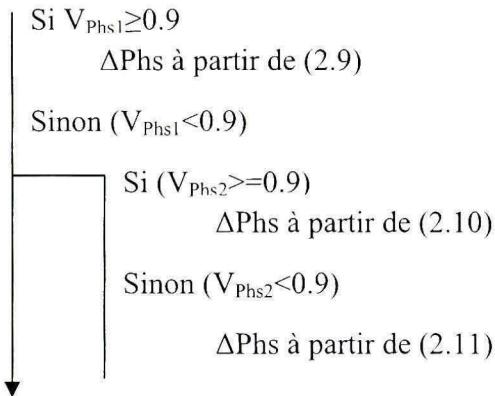

La première méthode consiste à dédoubler la prise de mesure en utilisant deux DPG ainsi qu'un déphasageur de  $90^\circ$ .

*Figure 2.16 Première méthode de résolution d'ambiguïté de phase.*

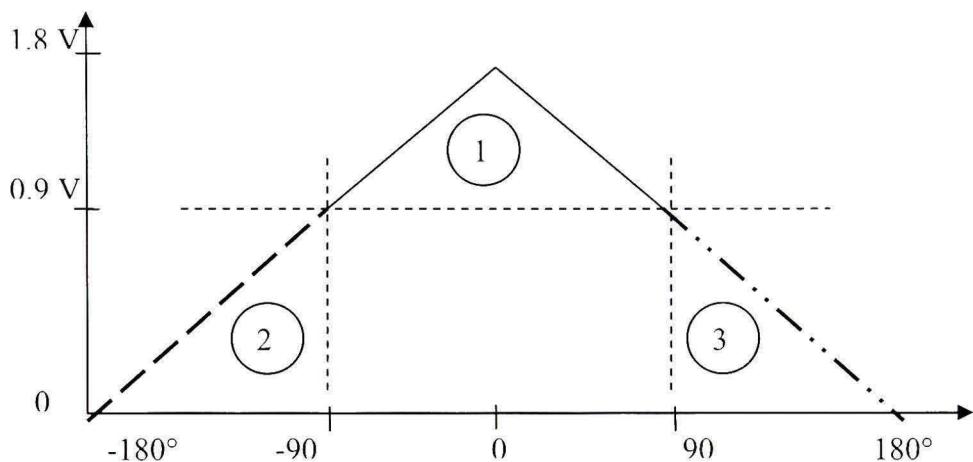

Cette méthode présente l'avantage de déterminer le signe du déphasage directement à partir de la lecture de  $V_{Phs1}$ ,  $V_{Phs2}$ . L'algorithme est basé sur la division de la courbe de transfert en trois zones :

**Figure 2.17 Répartition de la fonction de transfert en zones.**

- Si la sortie  $V_{Phs1}$  est comprise entre 0.9 V et 1.8 V alors on se situe dans la zone 1 et la différence de phase résultante est comprise entre  $-90^\circ$  et  $90^\circ$ . En utilisant le déphaseur de  $90^\circ$ , la différence réelle sera décalée et se situera entre 0 et  $180^\circ$ . Ce faisant on se retrouve sur la pente décroissante de la fonction de transfert. La sortie  $V_{Phs2}$  du second DPG variera alors de 0 à 1.8 V sans ambiguïté de signe car l'on opère dans la partie positive. En utilisant l'équation de cette droite (équation 2.7), nous pouvons extraire la différence de phase vue par le second DPG. Pour retrouver la différence réelle en phase, il suffira de retrancher le déphasage de  $90^\circ$  introduit par le déphaseur. L'expression finale de la différence de phase des deux signaux devient donc :

$$\Delta_{Phs} = \frac{V_{Phs2} - 1.75}{-0.009} - 90 \quad (2.9)$$

- Si la tension  $V_{Phs1}$  est inférieure à 0.9V alors nous avons deux possibilités :

Soit la différence réelle est comprise entre  $-180^\circ$  et  $-90^\circ$  (zone2) ou  $90^\circ$  et  $180^\circ$  (zone3). A partir de valeur  $V_{Phs2}$ , nous pouvons lever cette ambiguïté.

Dans le cas où elle se trouverait dans la zone 2, sous l'effet du déphaseur, la différence décalée se situerait entre  $-90^\circ$  et  $0^\circ$  et la sortie  $V_{Phs2}$  devrait être comprise entre 0.9 V et 1.8V.

$$\text{Ainsi } \Delta_{Phs} = \frac{V_{Phs1} - 1.75}{0.009} \quad (2.10)$$

Dans le cas échéant (zone3), la sortie  $V_{Phs2}$  varierait de 0V à 0.9V car la différence déphasée se retrouverait dans l'intervalle  $[180^\circ \ 270^\circ]$  équivalent à  $[-180^\circ \ -90^\circ]$ . Nous obtenons alors

$$\Delta_{Phs} = \frac{V_{Phs1} - 1.75}{-0.009} \quad (2.11)$$

Somme toute, l'algorithme de détection de signe a été implémenté sur HP VEE comme l'illustre la figure 2.18 :

**Figure 2.18 Algorithme de détection de signe.**

Rappelons qu'il existe plusieurs façons pour l'implémentation du déphaseur à  $90^\circ$ . Citons à titre d'exemple l'utilisation d'un déphaseur réglable conventionnel ou d'une jonction hybride à  $90^\circ$ . Cette méthode, bien qu'intéressante, est coûteuse en terme de matériel car elle nécessite l'utilisation de deux DPG.

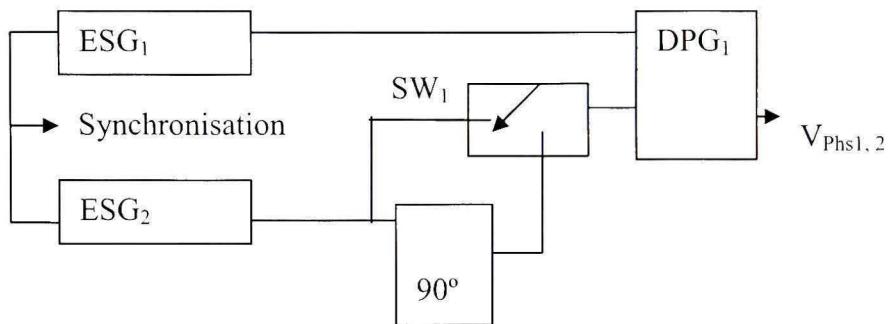

Nous avons initié une deuxième technique qui consiste à utiliser un switch pour faire la commutation lors de la prise de mesures. L'avantage réside dans l'emploi d'un seul DPG. Par contre les mesures seront prises en deux reprises. L'algorithme décrit à la figure 2.18 reste toujours valable pour cette deuxième proposition de solution (figure 2.19).

*Figure 2.19 Deuxième méthode de résolution d'ambiguïté de phase.*

Le commutateur permet de récupérer le signal directement à la sortie du générateur ou le signal déphasé. Les deux tensions de sortie seront notées respectivement  $V_{\text{Phs}1}$  et  $V_{\text{Phs}2}$  comme dans le cas précédent.

#### 2.4.2.2 Présentation de résultats

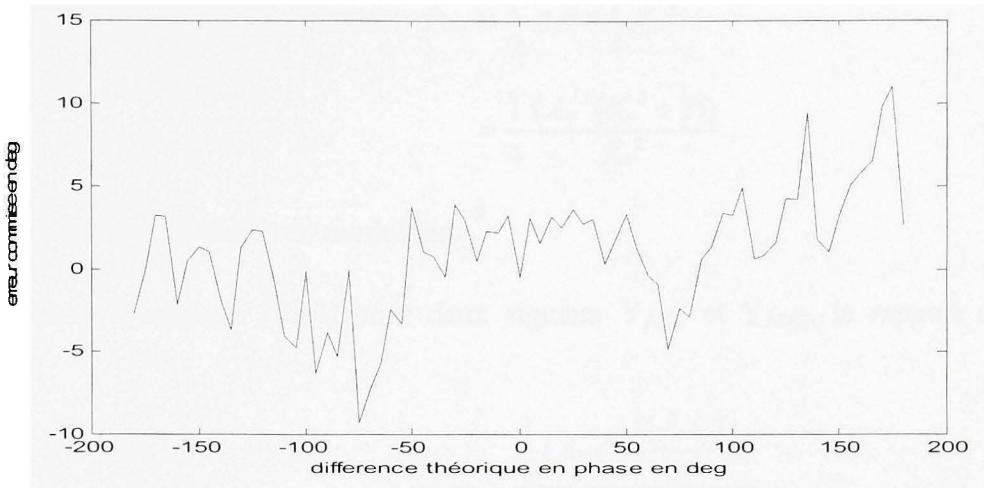

Le graphe 2.20 illustre l'erreur commise en phase. Nous remarquons que la plupart des valeurs sont extraites avec une tolérance de  $5^\circ$  même si nous notons par endroit des pics allant jusqu'à  $\pm 10^\circ$ . L'erreur moyenne prévue dans la fiche technique est de  $3^\circ$ .

**Figure 2.20 Erreur absolue commise en phase.**

## 2.5 Étude de performance de la carte en modulation AM

Une des applications reliées au dispositif que nous développons est la mesure embarquée de certains circuits RF en l'occurrence son intégration dans les systèmes RF intelligents (SRFI). Il doit permettre d'observer les signaux du système en mesurant les gains et les phases entre deux points. Généralement, ces signaux sont modulés, filtrés avant d'être amplifiés. Il serait donc intéressant d'étudier le comportement du DPG en présence de signaux modulés. Nous avons, pour des fins de mesure, utilisé la modulation AM.

### 2.5.1 Rappel théorique sur la modulation AM

Un signal modulé AM s'exprime mathématiquement comme suit :

$$Y_{AM}(t) = (A_p + A_m \cos(W_m t)) \cos(W_p t) \quad (2.12)$$

$Y_{AM}$  est le signal modulé,  $A_p$  l'amplitude de la porteuse,  $A_m$  l'amplitude du signal modulant,  $W_m$  la fréquence du signal modulant,  $W_p$  la fréquence de la porteuse et  $t$  la variable temporelle.

$$\text{En terme de puissance, nous avons : } P_{AM} = \frac{1}{2} A_p^2 + \frac{1}{4} A_m^2 \quad (2.13)$$

$$= \frac{1}{4} \frac{(A_m^2(K_a^2 + 2))}{K_a^2} \quad (2.14)$$

$K_a = \frac{A_m}{A_p}$  est appelé indice de modulation.

En utilisant l'équation (2.14) pour deux signaux  $Y_{AM1}$  et  $Y_{AM2}$ , le rapport de puissance devient :

$$\begin{aligned} \frac{P_{AM1}}{P_{AM2}} &= \frac{\frac{1}{4}(A_{m1}^2(\frac{K_a^2 + 2}{K_a^2}))}{\frac{1}{4}(A_{m2}^2(\frac{K_a^2 + 2}{K_a^2}))} \\ &= \frac{P_{AM1}}{P_{AM2}} = \frac{A_{m1}^2}{A_{m2}^2} \end{aligned} \quad (2.15)$$

Nous remarquons que ce rapport ne dépend que des amplitudes des signaux modulants si la même porteuse est appliquée.

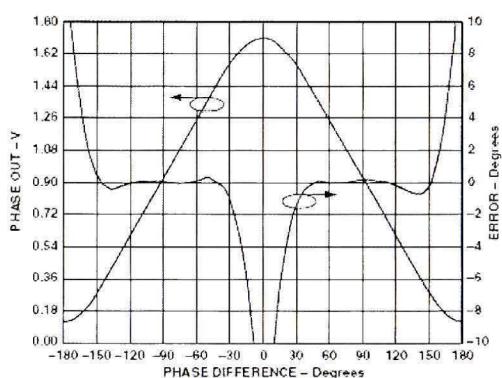

### 2.5.2 Résultats en modulation AM

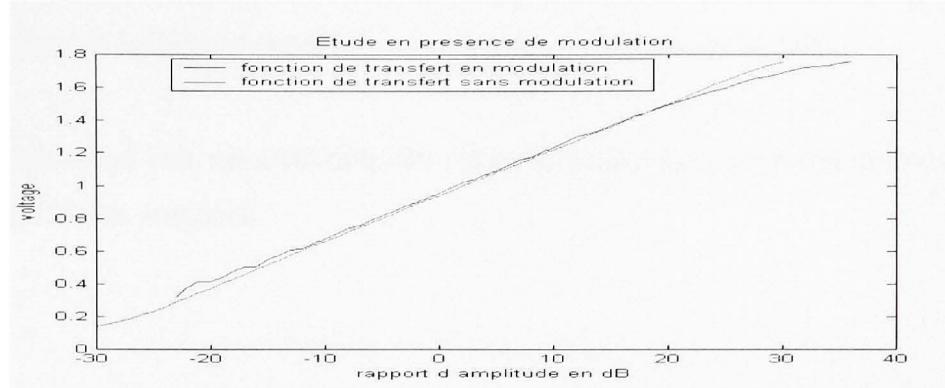

Nous avons repris les mêmes tests ayant servi à établir la fonction de transfert en amplitude (figure 2.7) en ajoutant la modulation AM. Les générateurs sont configurés en utilisant la même porteuse et le même indice de modulation.

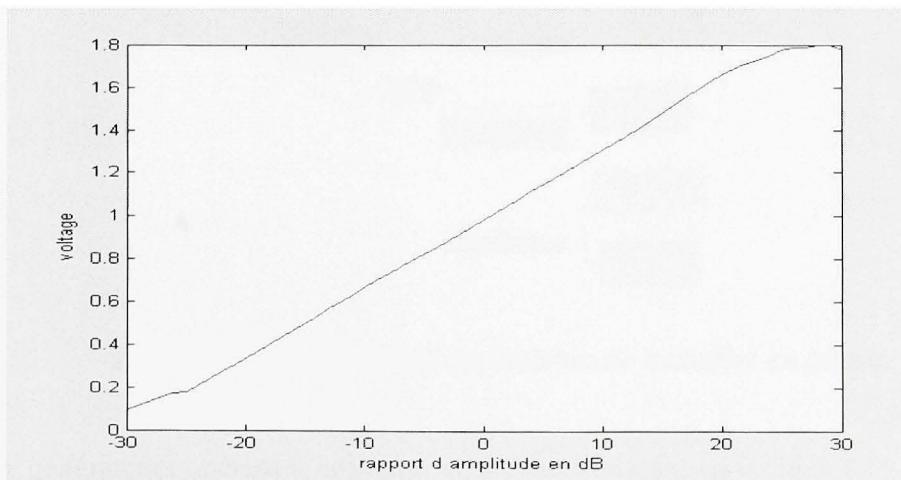

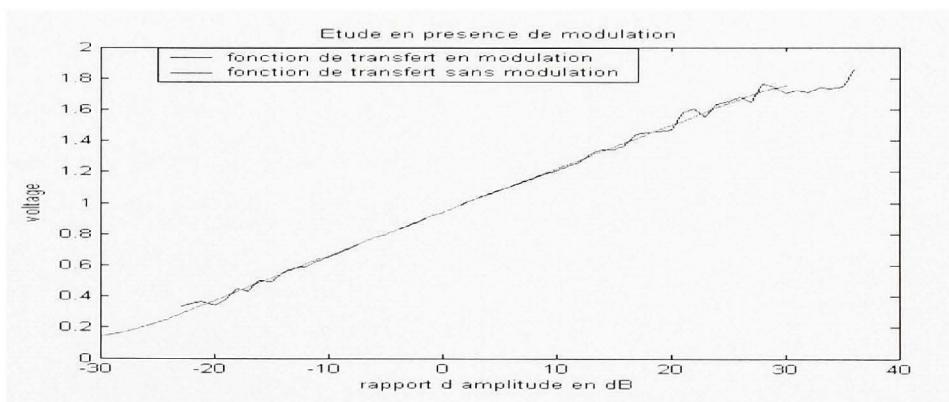

Les résultats obtenus sont en adéquation avec ceux escomptés. La fonction de transfert en amplitude dans les deux cas (sans et avec modulation) reste la même. De plus elle est invariante par rapport à l'indice de modulation comme en témoignent les graphes des figures 2.21 et 2.22 :

Ka=90%

*Figure 2.21 Comparaison de fonction de transfert avec et sans modulation (Ka=0.9).*

Ka=50%

*Figure 2.22 Comparaison de fonction de transfert avec et sans modulation (Ka=0.5).*

## 2.6 Conclusion

Dans ce chapitre, nous avons étudié et caractérisé la carte d'évaluation AD8302 d'Analog devices. Nous avons pu établir les fonctions de transfert expérimentales en amplitude et en phase. Les performances de la carte ont été étudiées afin de connaître l'erreur commise en utilisant les équations décrites en (2.6) et (2.7). Les résultats sont concluants et nous permettent de généraliser son comportement par ses expressions caractéristiques expérimentales dans sa plage de fréquences (100MHz- 2.7GHz); expressions que nous

utiliserons comme modélisation du AD8302 pour l'implémentation des programmes HP VEE. Nous avons également passé en revue quelques applications du DPG.

Dans le chapitre qui suit, nous étudions les différentes topologies pour son utilisation comme analyseur de réseau vectoriel.

## **CHAPITRE 3**

### **MESURE DE PARAMÈTRES S À L'AIDE DU DISPOSITIF DE MESURE INTÉGRANT L'AD8302**

#### **3.1      Introduction**

Dans le chapitre précédent, nous avons démontré qu'il est possible de mesurer le rapport complexe de deux signaux découplés à partir des caractéristiques de l'AD8302 en utilisant deux sources indépendantes. Outre cette possibilité de mesure, le DPG permet de caractériser un dispositif en mesurant ses paramètres S à travers différentes configurations. Le présent chapitre fera l'objet d'étude des différentes topologies de mesure. La réalisation du banc de test nécessitera l'utilisation des coupleurs directifs dont le rôle est de prélever des échantillons des signaux incidents et réfléchis. Les signaux à l'entrée du DPG se trouvent alors couplés. Par conséquent une procédure de correction s'impose. En d'autres termes, nous étudierons l'extraction des paramètres S d'un DST à partir des caractéristiques du AD8302 ainsi que de la caractérisation des coupleurs utilisés.

#### **3.2      Description du banc de test**

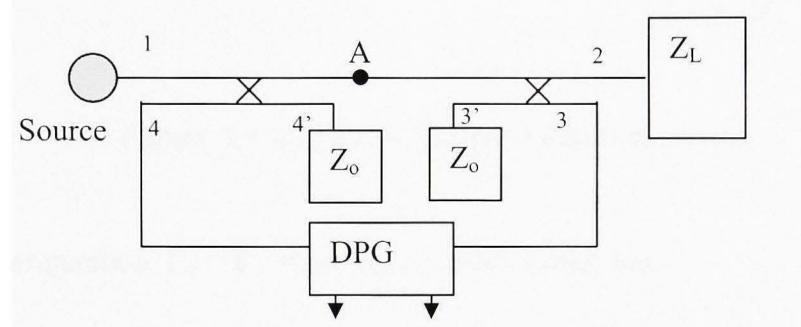

La figure 3.1 illustre le banc d'essai à réaliser et qui permettra dans le cas général d'obtenir les quatre paramètres S d'un DST. Pour son développement, nous utiliserons une source RF ou au besoin l'analyseur de réseau en mode source. Il doit répondre à certaines exigences dont :

- l'automatisation et le contrôle par ordinateur : une interface HP VEE sera développée pour assurer l'acquisition et le traitement de données.

- moins coûteux en terme de circuits RF

- flexibilité d'usage

- la justesse des mesures.

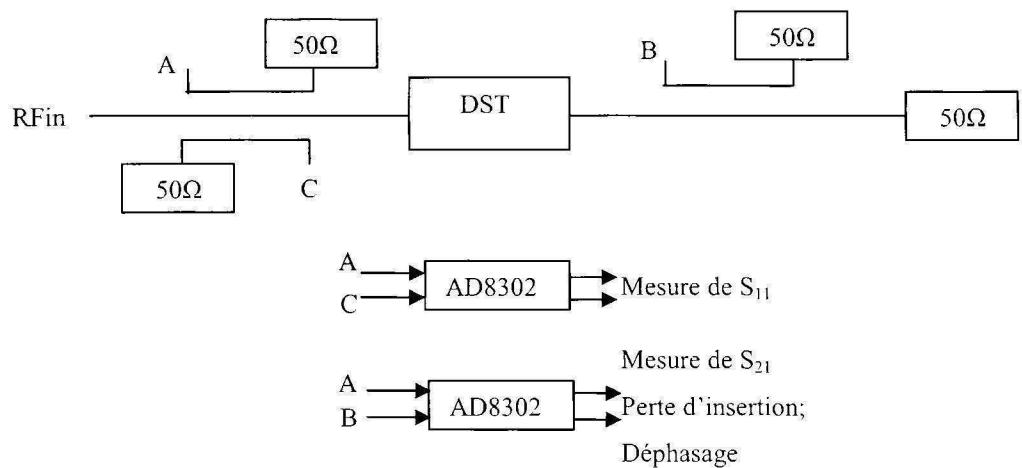

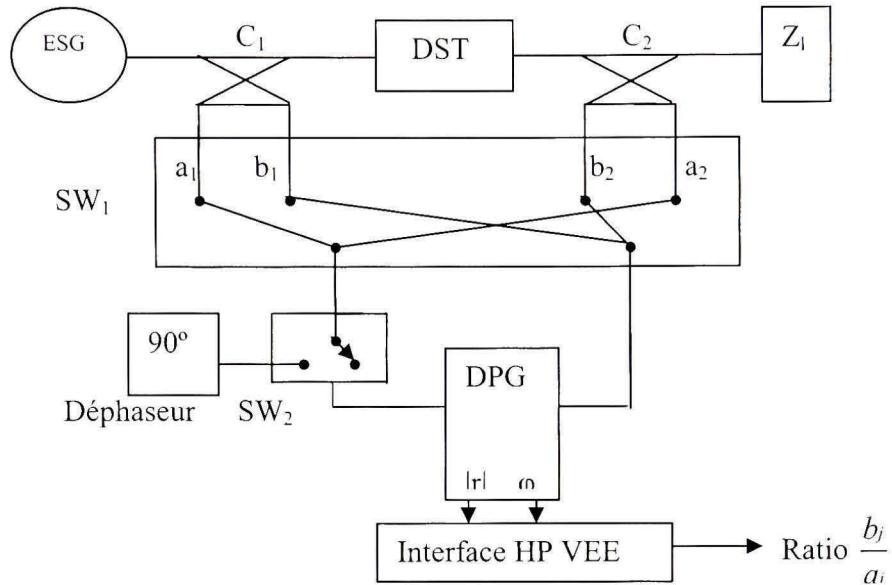

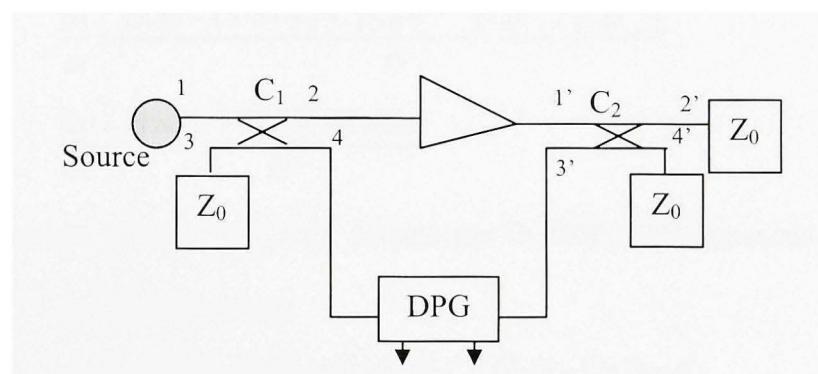

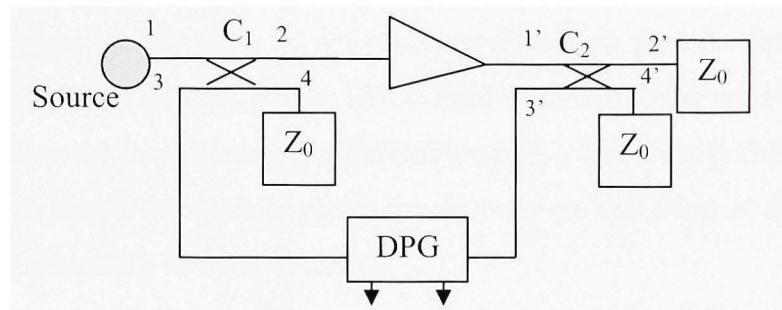

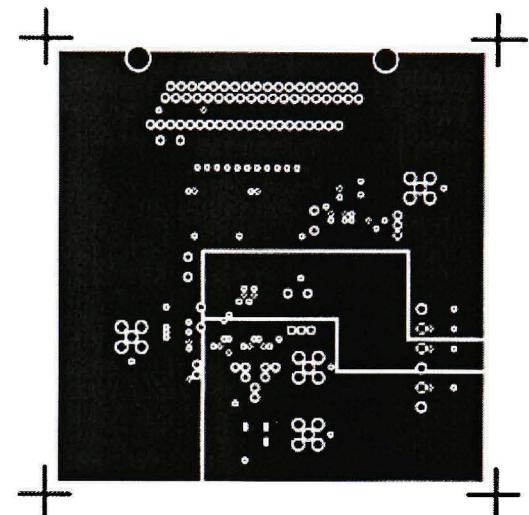

*Figure 3.1 Architecture simplifiée du banc de test.*

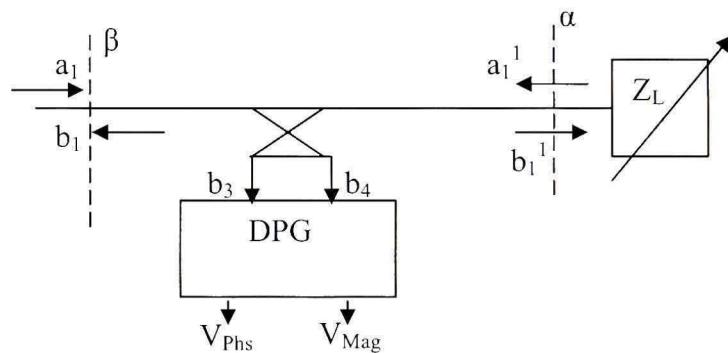

$C_1$  et  $C_2$  représentent des coupleurs directs ;  $SW_1$  et  $SW_2$  sont des commutateurs.

Le système de mesure dans sa forme simplifiée est composé de deux commutateurs de transfert, de deux coupleurs, d'un déphaseur et d'un DPG. Les coupleurs sont disposés en amont et en aval du dispositif à tester. Ils permettent d'échantillonner les pseudo-ondes émergentes et réfléchies  $a_1$ ,  $b_1$ ,  $a_2$  et  $b_2$ . Les échantillons seront acheminés au DPG par l'entremise du commutateur à quatre entrées et deux sorties ( $SW_1$ ) dont le rôle est de sélectionner des couples de pseudo-ondes :  $(a_1, b_1)$ ,  $(a_1, b_2)$ ,  $(a_2, b_1)$  et  $(a_2, b_2)$ .

L'onde réfléchie de la paire sélectionnée par  $SW_1$  est administrée directement à la première entrée du DPG alors que l'onde incidente peut être déphasée au besoin. Ce déphasage à  $90^\circ$  est assuré par un déphaseur manuellement réglable en basculant le commutateur  $SW_2$ . L'insertion du déphaseur permet de lever l'ambiguïté de phase associée à l'emploi du DPG. Une répétition des mesures sera de mise pour compléter la procédure de détection de signe telle que décrite dans le chapitre précédent.

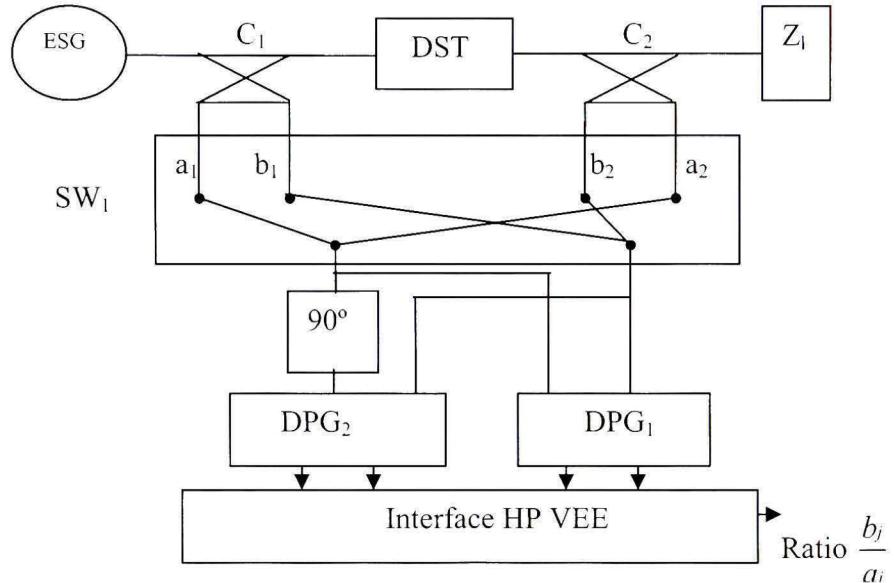

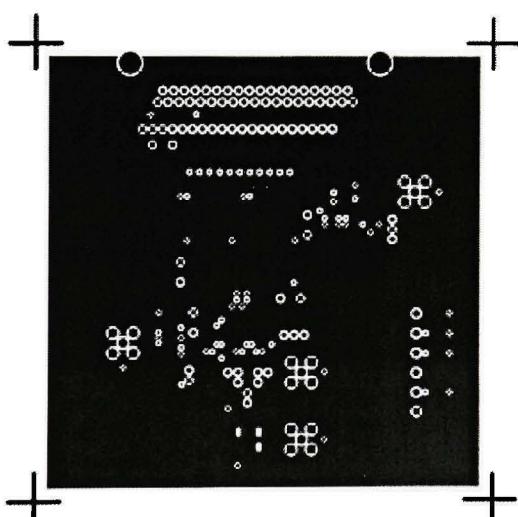

Une autre variante de cette architecture consiste à utiliser deux DPG et un seul commutateur. Cette configuration illustrée à la figure 3.2 permet de prendre instantanée les mesures contrairement à celle de la figure 3.1 dont les mesures se réalisent en deux temps.

*Figure 3.2 Architecture optimale du banc de test.*

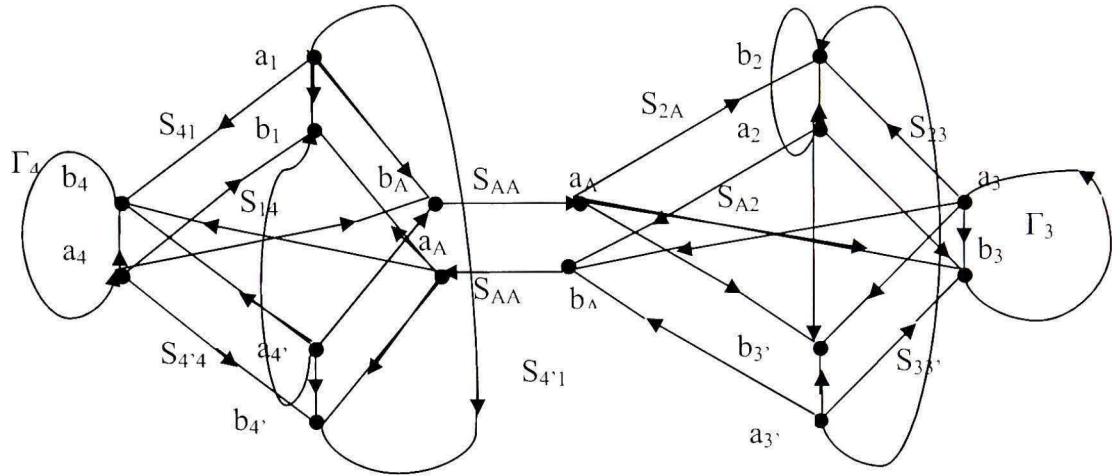

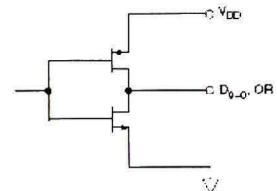

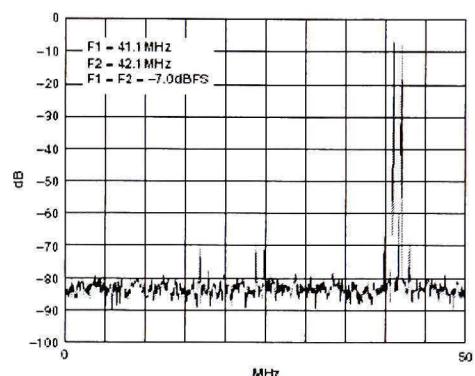

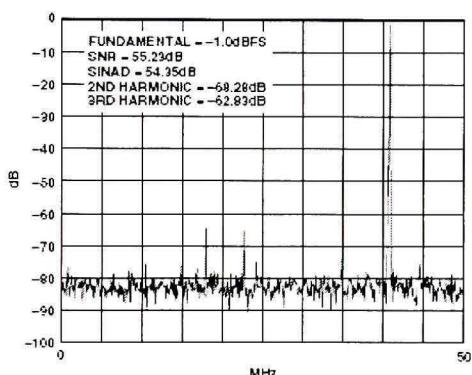

### 3.3 Technique de mesure de paramètres S