## Designing and developing nine-level Packed U-Cell (PUC9) inverter for high power applications

by

#### Kiavash ASKARI NOGHANI

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLEMENT FOR A MASTER'S DEGREE WITH THESIS IN ELECTRICAL ENGINEERING M.A.Sc.

MONTREAL, 23 DECEMBER, 2019

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

© Copyright 2019 reserved by Kiavash ASKARI NOGHANI

# © Copyright reserved It is forbidden to reproduce, save or share the content of this document either in whole or in parts. The reader who wishes to print or save this document on any media must first get the permission of the author.

# BOARD OF EXAMINERS (THESIS M.Sc.A.) THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Kamal Al-Haddad, Thesis Supervisor Department of Electrical Engineering, École de technologie supérieure

Mr. Louis A. Dessaint, President of the Board of Examiners Department of Electrical Engineering, École de technologie supérieure

Mr. Jean-Nicolas Paquin, External Evaluator OPAL-RT

THIS THESIS WAS PRENSENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS  $\text{ON DECEMBER } 19^{\text{TH}}, 2019$  AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGMENT

I would first like to thank my supervisor Prof. Kamal Al-Haddad who grabbed my hand when I was stuck in the middle of the river. Since then, he has guided and supported me unendingly and patiently until reaching the shore of success. Undoubtedly, without his help and support the fulfilment of this work would not be possible. Being his student is a brilliant point in my CV and I will be proud of it forever.

I would also like to acknowledge all of my colleagues in GREPCI group, especially Dr. Mostafa Abarzadeh, Dr. Hani Vahedi and Dr. Abdelhamid Hamadi, who were always welcoming to my questions. Thank you all.

I would also be grateful to the jury members for reviewing my thesis and giving comments on it and attending my thesis defense session. Thank you for giving me your precious time and accepting to be my jury members.

I would also like to appreciate my family: my mother who gave me assurance by her kind words; my father who encouraged me by using the electronic equipment that I have made since being a teenager; my parents-in-law who always believed and supported me; my brother who always calmed me down when I was in trouble, and finally my sister, my brothers-in-law, and my sister-in-law who have always encouraged me.

I would also like to thank my wife, who ignored her wants and postponed her wishes, so that I could peruse my dream. She worked hard from early morning to late evening without any complaints. She has always believed in me and encouraged me. She brought me energy and good luck by coming to my life. Thanks my love.

## Conception et développement d'un onduleur PUC9 (Packed U-Cell) à neuf niveaux pour les applications à forte puissance, THESIS M.Sc.A.

#### Kiavash ASKARI NOGHANI

#### **RÉSUMÉ**

Il est indéniable que la consommation d'énergie a tendance à augmenter et que, pour des raisons économiques et environnementales, l'utilisation des énergies renouvelables tels : éolienne et solaire a augmenté considérablement. A cet effet, des onduleurs sont nécessaires pour convertir l'énergie produite en énergie utilisable par les consommateurs. Bien que les onduleurs existants fonctionnent correctement, les efforts pour réduire les pertes d'énergie dans ces étages de conversion avec une réduction des coûts des composants utilisés constituent un objectif en soi. Compte tenu de ce qui précède, l'onduleur PUC9 pourrait être un choix approprié en raison de sa simplicité, de sa fiabilité et de son efficacité en comparaison avec d'autres onduleurs.

Les objectifs de ce projet sont de réduire la complexité du système de contrôle du PUC9, ce qui permet de produire un convertisseur orienté vers l'industrie et capable d'équilibrer les niveaux des tensions des condensateurs selon les besoins de la charge, aussi d'accroître son efficacité, et finalement de concevoir l'expérimentation nécessaire pour valider ce nouveau concept avec sa commande.

Afin d'atteindre les objectifs de recherche susmentionnés; tout d'abord, je effectué une revue de la littérature sur différents types d'onduleurs, en particulier des onduleurs à source continue, et vérifier la complexité de chaque type d'onduleur étudié en termes de fréquence de commutation, du nombre de composantes utilisées, et le THD. (Distorsion harmonique totale). Ensuite, j'ai passé en revue certaines techniques d'équilibrage des condensateurs. Par après, l'onduleur PUC9 est théoriquement analysé et étudié. Après cela, j'ai appliqué la commande prédictive sur le PUC9. J'ai proposé une technique de modulation adaptée. À cette occasion, j'ai obtenu un modèle mathématique du PUC9, et effectué la simulation utilisant SimPowerSystem et Matlab Simulink. Un prototype expérimental a été développé et a servi pour la validation expérimentale.

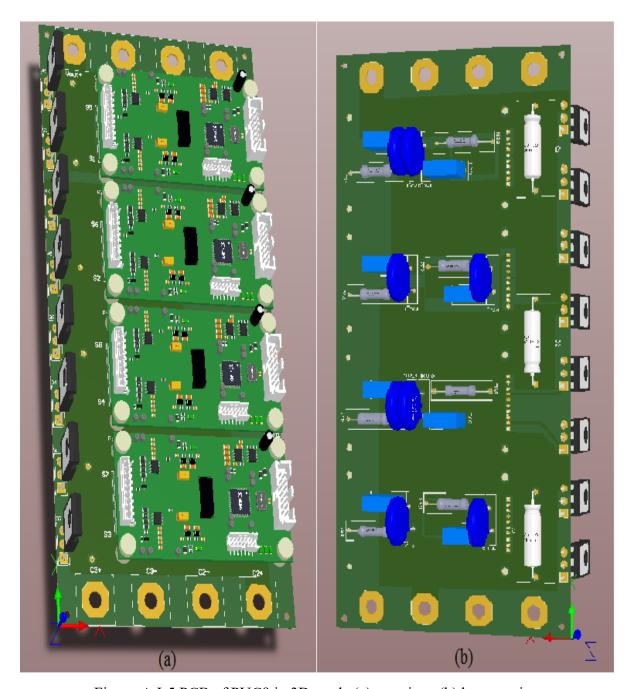

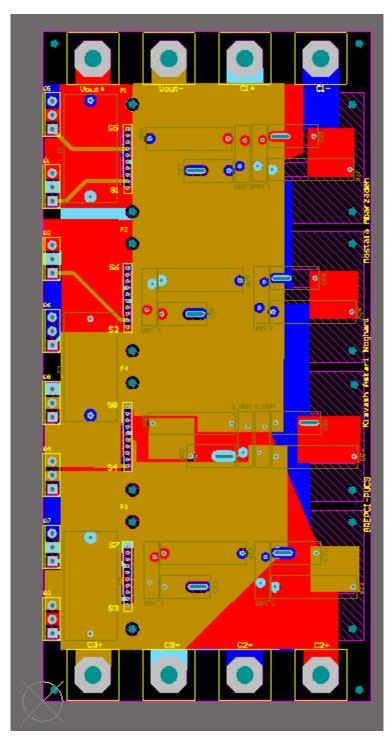

Enfin, une nouvelle topologie a été proposée nommée onduleur UX-Cell à neuf niveaux sur laquelle j'ai appliqué un contrôle prédictif et une technique de contrôle sans capteur. Cette nouvelle topologie a été simulée avec Matlab Simulink, et a été validée de manière expérimentale pour ainsi déterminer ses avantages et inconvénients par rapport à l'onduleur PUC9. À cette fin, le travail au laboratoire a permis la conception des circuits imprimés des onduleurs PUC9 et UX-Cell avec le logiciel Altium Design et de tester les deux brevets de manière expérimentale en mode autonome et en mode connecté au réseau électrique.

**Mots-clés:** PUC9, UX-Cell, Onduleur compact à neuf cellules en U, technique de commande MPC, équilibrage des tensions des condensateurs, états de commutation, onduleur à plusieurs niveaux de tension.

## Designing and developing nine-level Packed U-Cell (PUC9) inverter for high power applications, THESIS M.Sc.A

#### Kiavash ASKARI NOGHANI

#### **ABSTRACT**

It is a fact that energy consumption has had an increasing trend, and due to economic reasons and environmental concerns, the usage of renewable energies like wind and solar is increasing drastically. Inverters are needed in order to change the produced energy into usable energy for consumers. Although the existing inverters work properly, factories and countries always tend to decrease energy loss and the cost of the components used in producing and transferring energy. Considering the aforementioned issues, PUC9 inverter could be a suitable choice due to its simplicity, reliability and efficiency and also needing low weight transformers in comparison with other inverters.

The main objectives of this project are reducing the complexity of PUC9 control system, as a result producing an industry-oriented converter, which balances the dc capacitor level as desired, increasing the efficiency of PUC9 inverter, and designing an inverter compatible with adding series inverter together to decrease complexity.

In order to achieve the above mentioned research objectives; first, I do literature review on different types of inverters, especially single dc sources inverters, and check out the design the complexity of each type of reviewed inverter in terms of switching state possibility, the number of their components, advantages and disadvantages, and THD (Total Harmonic Distortion). Afterward, I review some modulation and voltage balancing techniques. Then, PUC9 inverter is theoretically analyzed. After that, I apply model predictive control on PUC9; in addition, I propose one modulation technique on it. On that occasion, I obtain mathematical model of PUC9, simulate it with SimPowerSystem and Matlab Simulink, and validate them experimentally. Finally, I offer nine-level UX-Cell inverter, apply model predictive control and sensorless control technique, simulate it with Matlab Simulink, validate it experimentally, and consider its pros and cons in comparison with PUC9 inverter. For this purpose, I design the PCB of PUC9 and UX-Cell inverter with Altium Design software and test both patents experimentally in stand-alone and grid-connected modes.

**Keywords:** Nine-Level Packed U-Cell Inverter, MPC Technique, Capacitors Voltage Balancing, Switching States Possibility, Multilevel Inverters, Total Harmonic Distortion, Power Quality, Renewable Energy Conversion.

#### **TABLE OF CONTENTS**

|       |          |                                                                    | Page   |

|-------|----------|--------------------------------------------------------------------|--------|

| INTRO | DUCTIO   | ON                                                                 | 1      |

| CHAP' | ΓER 1    | MULTILEVEL CONVERTER LITERATURE REVIEW                             | 3      |

| 1.1   | Introduc | etion                                                              |        |

| 1.2   |          | vel Cascaded Topologies                                            |        |

|       | 1.2.1    | Half-Bridge Inverter                                               |        |

|       | 1.2.2    | Full-Bridge Inverter                                               | 5      |

|       | 1.2.3    | Three-Phase Six Switches Voltage Source Inverter                   | 6      |

|       | 1.2.4    | Cascaded H-Bridge (CHB) Inverter                                   | 8      |

|       | 1.2.5    | Modular Multilevel Converter (MMC)                                 |        |

| 1.3   | Multilev | vel Diode Clamped Inverter Topologies                              |        |

|       | 1.3.1    | Three-level Neutral Point Clamped (NPC) Inverter                   |        |

|       | 1.3.2    | Five-level Diode Clamped Inverter                                  |        |

| 1.4   | Multilev | vel Flying Capacitor Topologies                                    | 18     |

|       | 1.4.1    | Flying Capacitor (FC) Single-phase three-level inverter            | 18     |

|       | 1.4.2    | Flying Capacitor (FC) Single-phase five-level inverter             | 19     |

| 1.5   | Asymm    | etric hybrid multilevel inverters (AH-MLI)                         | 21     |

| 1.6   | Modula   | tion Strategies to Control Switches of Inverters                   | 23     |

|       | 1.6.1    | Bipolar PWM                                                        |        |

|       | 1.6.2    | Level Shifted Modulation                                           | 24     |

|       | 1.6.3    | Phase Shifted Modulation                                           |        |

|       | 1.6.4    | Space Vector Modulation (SVM)                                      |        |

| 1.7   | Single-I | OC Source Multilevel Inverter Topologies                           |        |

|       | 1.7.1    | Single-DC Source CHB Inverter                                      |        |

|       | 1.7.2    | Single Phase Seven Level Cascaded H-Bridge Multilevel Inverter     |        |

|       | 1.7.3    | Step-Up Multilevel Inverter with a Single DC Source                |        |

|       | 1.7.4    | Seven-Level PWM Inverter Employing Series-Connected Capacitors     |        |

|       |          | Paralleled to a Single DC Voltage Source                           |        |

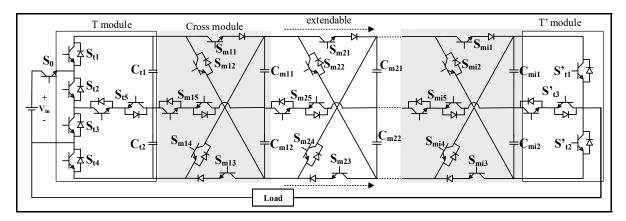

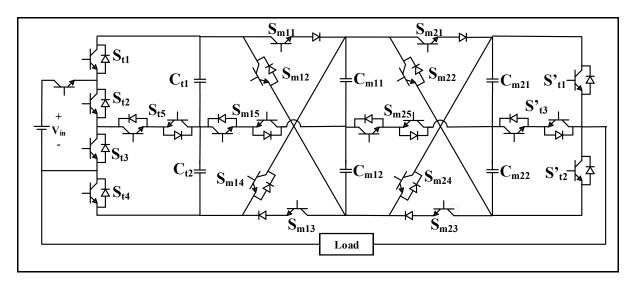

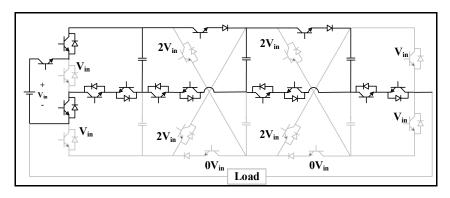

|       | 1.7.5    | Multilevel inverter with combined T-type and cross-connected modul | les 54 |

|       | 1.7.6    | Single-Phase Single-Source 7-Level Inverter with Triple Voltage    |        |

|       |          | Boosting Gain                                                      | 62     |

|       | 1.7.7    | A Novel Step-Up Single Source Multilevel Inverter: Topology,       |        |

|       |          | Operating Principle and Modulation                                 |        |

|       | 1.7.8    | Packed U-Cell (PUC) inverter                                       | 71     |

| CHAP' | ΓER 2    | CURRENT BASED MODEL PREDICTIVE CONTROL FOR DC                      |        |

|       |          | CAPACITOR OPTIMIZATION IN GRID-CONNECTED AND                       |        |

|       |          | STAND-ALONE NINE-LEVEL PACKED U-CELL INVERTER                      | 79     |

| 2.1   |          | etion                                                              |        |

| 2.2   | Nine-lev | vel Packed U-Cell Inverter operation and modeling                  | 79     |

| 2.3   | Model r  | oredictive control on PUC9                                         | 84     |

| 2.4   | Simulation Parameters                      | 86                               |

|-------|--------------------------------------------|----------------------------------|

| 2.5   | Simulation results in stand-alone mode     | 88                               |

| 2.6   | Simulation results in grid-connected mod   | le89                             |

| 2.7   |                                            | 90                               |

| 2.8   | •                                          | 94                               |

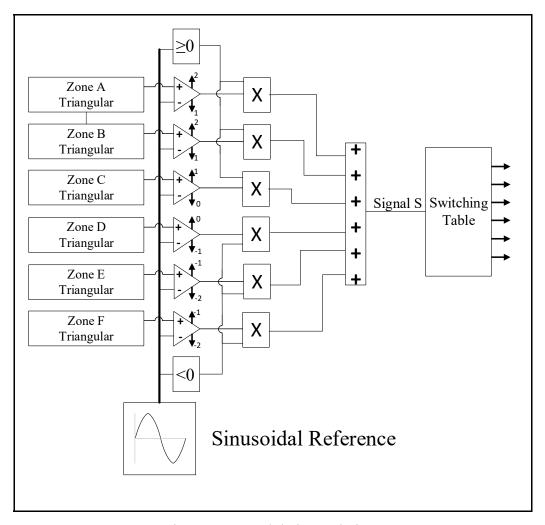

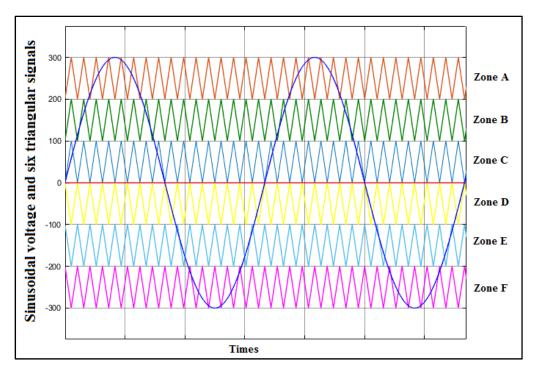

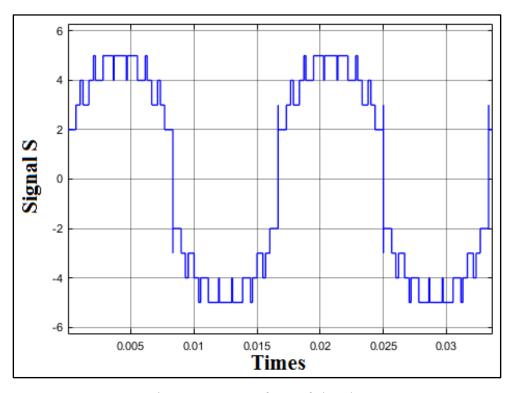

| CHAI  | PTER 3 A NEW MULTICARRIER LS               | S-PWM TECHNIQUE FOR              |

|       | VOLTAGE BALANCING OF                       | NINE-LEVEL PACKED U-CELL         |

|       | INVERTER'S CAPACITORS                      | 95                               |

| 3.1   | Introduction                               | 95                               |

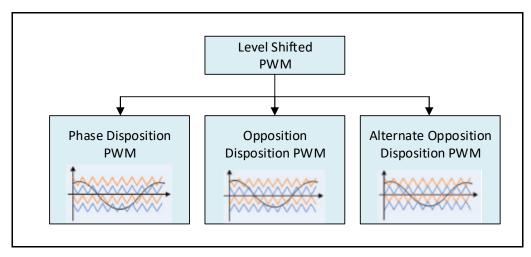

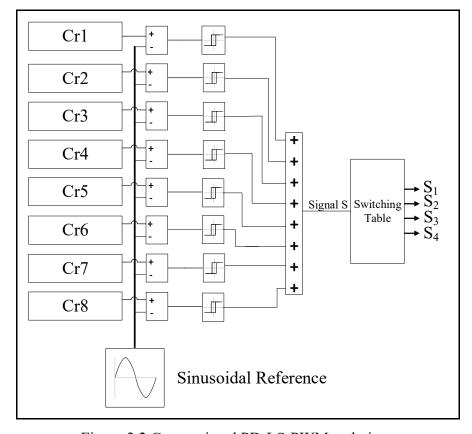

| 3.2   | Conventional multicarrier level shifted pu | alse width modulation (LS-PWM)95 |

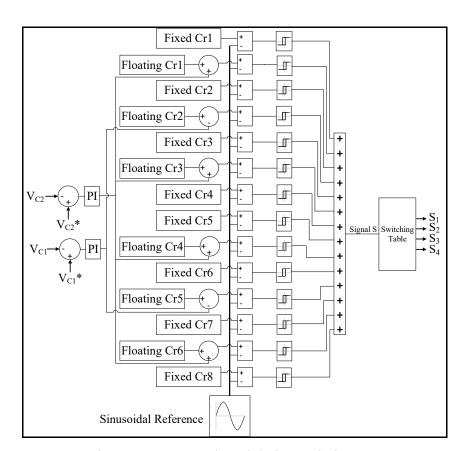

| 3.3   | Proposed voltage balancing technique       | 97                               |

| 3.4   |                                            | 99                               |

| 3.5   | Experimental Results                       | 103                              |

| 3.6   | •                                          | 107                              |

| CIIAI | DTED 4 NINE LEVEL LIV CELL IN              | VEDTED TODAL OCY, MODEL          |

| CHAI  |                                            | YERTER TOPOLOGY: MODEL           |

| 1 1   |                                            |                                  |

| 4.1   |                                            |                                  |

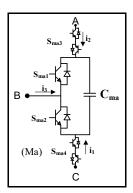

| 4.2   |                                            | nd modeling109                   |

| 4.3   | •                                          | 114                              |

| 4.4   | ±.                                         | 116                              |

| 4.5   |                                            | 117                              |

| 4.6   | •                                          | 124                              |

| 4.7   | Conclusion                                 | 128                              |

| CHAI  | PTER 5 SENSORLESS OPERATION                |                                  |

|       | INVERTER TOPOLOGY                          | 129                              |

| 5.1   | Introduction                               | 129                              |

| 5.2   | PWM Sensorless control technique on ni     | ne-level UX-Cell MLI129          |

| 5.3   | Simulation results                         | 131                              |

| 5.4   | Experimental results                       | 136                              |

| 5.5   | Conclusion                                 | 139                              |

| CON   | CLUSION                                    | 141                              |

| FUTU  | URE WORKS                                  | 143                              |

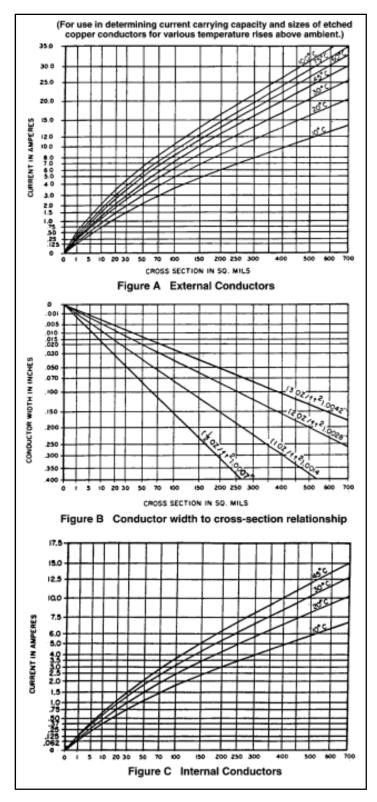

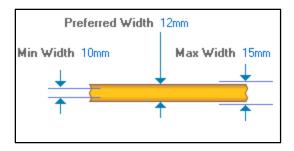

| APEN  | NDIX I DESIGN CONSIDERATION                | OF PUC9 MLI145                   |

| LIST  | OF BIBLIOGRAPHICAL REFERENCES.             | 155                              |

#### LIST OF TABLES

|            |                                                                                                     | Page |

|------------|-----------------------------------------------------------------------------------------------------|------|

| Table 1.1  | Switching state possibility of half-bridge inverter                                                 | 4    |

| Table 1.2  | Switching states of full-bridge inverter                                                            | 6    |

| Table 1.3  | Switching states of three-phase full-bridge inverter                                                | 7    |

| Table 1.4  | Switching states of single-phase five-level CHB MLI                                                 | 9    |

| Table 1.5  | Switching states of three level NPC inverter                                                        | 14   |

| Table 1.6  | Switching states of five-level NPC inverter                                                         | 16   |

| Table 1.7  | Switching states of three-level FC inverter                                                         | 19   |

| Table 1.8  | Switching states of FC inverter                                                                     | 20   |

| Table 1.9  | Switching states and Capacitor state of single-phase single-dc-source CHB cascaded 7-level inverter |      |

| Table 1.10 | Switching states                                                                                    | 32   |

| Table 1.11 | Switching states                                                                                    | 37   |

| Table 1.12 | Switching status for capacitor charging                                                             | 40   |

| Table 1.13 | Switching states for discharging capacitors                                                         | 41   |

| Table 1.14 | Switching states for automatic charging and discharging                                             | 44   |

| Table 1.15 | Switching states and output voltage levels                                                          | 51   |

| Table 1.16 | Switching angles                                                                                    | 52   |

| Table 1.17 | Switching states of thirteen-level proposed inverter                                                | 56   |

| Table 1.18 | Six switching angles for proposed 13-level inverter                                                 | 61   |

| Table 1.19 | Coefficients K1 and K2 for each voltage level                                                       | 61   |

| Table 1.20 | Switching states possibility of this model                                                          | 63   |

| Table 1.21 | Switching states possibility of this model and Charging / Discharging                               | 267  |

| Table 1.22 | Switching states possibility of this model                         | 71     |

|------------|--------------------------------------------------------------------|--------|

| Table 1.23 | DC voltages bus of the different converters of the PUC topology    | 73     |

| Table 1.24 | Switching states of PUC5 MLI                                       | 74     |

| Table 1.25 | Correspondence table                                               | 78     |

| Table 2.1  | Switching states of PUC9 MLI (↑=charging, ↓=discharging, - = no ef |        |

| Table 2.2  | PUC9 simulation parameters for Grid-Connected and Stand-alone Mo   |        |

| Table 2.3  | PUC9 experimentation parameters                                    | 91     |

| Table 3.1  | Main System Parameters                                             | 100    |

| Table 3.2  | System Parameters                                                  | 103    |

| Table 4.1  | Switching states of UX-Cell MLI                                    | 111    |

| Table 4.2  | Comparison between other nine-level inverter topologies and UX-Ce  | 11.113 |

| Table 4.3  | Main System Parameters                                             | 118    |

| Table 4.4  | Main System Parameters                                             | 125    |

| Table 5.1  | Main System Parameters                                             | 132    |

| Table 5.2  | Main System Parameters                                             | 136    |

#### LIST OF FIGURES

|             |                                                                                                     | Page |

|-------------|-----------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Half-bridge voltage source inverter                                                                 | 4    |

| Figure 1.2  | Equivalent circuit of half-bridge inverter in each switching state                                  | 4    |

| Figure 1.3  | Full-bridge voltage source inverter                                                                 | 5    |

| Figure 1.4  | Equivalent circuit of H-bridge inverter in each switching state                                     | 6    |

| Figure 1.5  | Three-phase full-bridge inverter                                                                    | 7    |

| Figure 1.6  | Single-phase five-level CHB MLI                                                                     | 8    |

| Figure 1.7  | General Structure of CHB MLI (a) single-phase (b) three-phase                                       | 9    |

| Figure 1.8  | General structure of single-phase MMC (a) with half-bridge submodule (b) with full-bridge submodule | 12   |

| Figure 1.9  | General structure of three-phase MMC                                                                | 13   |

| Figure 1.10 | Three-level NPC inverter                                                                            | 14   |

| Figure 1.11 | Equivalent circuit in each state of Table 1.5                                                       | 15   |

| Figure 1.12 | Five-level NPC inverter circuit                                                                     | 15   |

| Figure 1.13 | Five-level NPC inverter proposed by Yuan                                                            | 17   |

| Figure 1.14 | Circuit diagram of three level FC inverter                                                          | 18   |

| Figure 1.15 | Equivalent circuit for each state in Table 1.7                                                      | 19   |

| Figure 1.16 | Circuit diagram of five level FC inverter                                                           | 20   |

| Figure 1.17 | DC MLI and CHB MLI cascaded                                                                         | 22   |

| Figure 1.18 | FC MLI and CHB MLI cascaded                                                                         | 22   |

| Figure 1.19 | Conventional strategies for modulating the waveforms                                                | 23   |

| Figure 1.20 | Bipolar PWM                                                                                         | 24   |

| Figure 1 21 | I S-PWM for nine-level inverters                                                                    | 25   |

| Figure 1.22 | Phase shift PWM carrier wave forms                                                                                                      | 26 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.23 | Unipolar modulation signal                                                                                                              | 27 |

| Figure 1.24 | Space-vectors modulation to produce switching states of two level inverters                                                             | 28 |

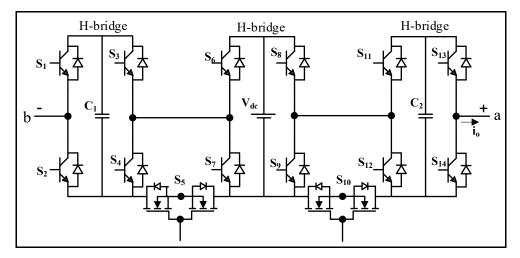

| Figure 1.25 | Single-phase Single DC source Cascade H-bridge (CHB) multilevel inverter                                                                | 29 |

| Figure 1.26 | Equivalent circuit in each state shown in Table 1.9                                                                                     | 31 |

| Figure 1.27 | Single Phase Seven Level Cascaded H-Bridge MLI circuit                                                                                  | 31 |

| Figure 1.28 | Current path in each switching state of Table 1.10                                                                                      | 33 |

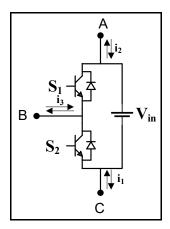

| Figure 1.29 | Half-bridge module                                                                                                                      | 34 |

| Figure 1.30 | Add two bidirectional switches to half bridge inverter                                                                                  | 34 |

| Figure 1.31 | (a), (b) unidirectional current control in two sides. (c), (d) unidirection current control in one side and bidirectional in other side |    |

| Figure 1.32 | Circuit of step-up multilevel inverter with single dc source                                                                            | 36 |

| Figure 1.33 | Three-stage step-up of this inverter                                                                                                    | 38 |

| Figure 1.34 | Charging different capacitors                                                                                                           | 40 |

| Figure 1.35 | Some selected equivalent circuits for discharging capacitors                                                                            | 43 |

| Figure 1.36 | Some selected equivalent circuits for charging and discharging capacitant                                                               |    |

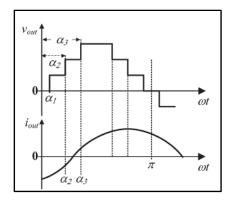

| Figure 1.37 | Output waveform                                                                                                                         | 46 |

| Figure 1.38 | Main circuit                                                                                                                            | 47 |

| Figure 1.39 | Equivalent circuit of each switching state for generating different output levels                                                       | 48 |

| Figure 1.40 | Switching pattern for generating 7-level PWM output voltage                                                                             | 50 |

| Figure 1.41 | Equivalent circuit of the proposed mode                                                                                                 | 52 |

| Figure 1.42 | Output voltage and lagging load current                                                                                                 | 53 |

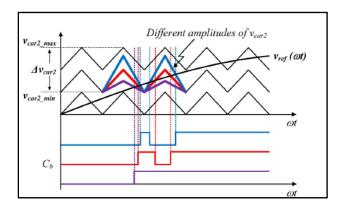

| Figure 1.43 | Modified control methods for regulating C2                                                                                              | 53 |

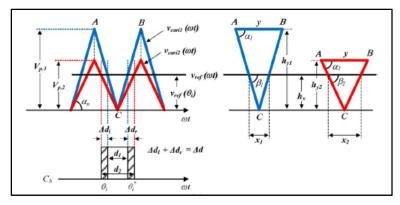

| Figure 1.44 | Relation between vcar1, vcar2 and Vref                                           | 54 |

|-------------|----------------------------------------------------------------------------------|----|

| Figure 1.45 | Circuit of combined T-type and cross-connected modules                           | 54 |

| Figure 1.46 | Equivalent circuit of thirteen-level proposed inverter                           | 55 |

| Figure 1.47 | Charging of top capacitors                                                       | 57 |

| Figure 1.48 | Charging of bottom capacitors                                                    | 58 |

| Figure 1.49 | Equivalent circuit for discharging capacitors in some selected switching states  | 58 |

| Figure 1.50 | Multi-level output waveform                                                      | 60 |

| Figure 1.51 | Discharging time of different capacitors                                         | 61 |

| Figure 1.52 | Single-Phase Single-Source 7-Level Inverter with Triple Voltage<br>Boosting Gain | 63 |

| Figure 1.53 | Equivalent circuit for each switching state                                      | 64 |

| Figure 1.54 | Output waveform                                                                  | 65 |

| Figure 1.55 | Circuit configuration of step-up single source MLI                               | 66 |

| Figure 1.56 | Charging paths of first SCC (b) charging path of second SCC                      | 67 |

| Figure 1.57 | Current path of output voltage levels                                            | 69 |

| Figure 1.58 | Modulation technique and output waveform of A Novel Step-Up Single Source MLI    | 70 |

| Figure 1.59 | U-shaped cell                                                                    | 72 |

| Figure 1.60 | Single-phase PUC-7 inverter                                                      | 72 |

| Figure 1.61 | Three-phase PUC7 inverter                                                        | 74 |

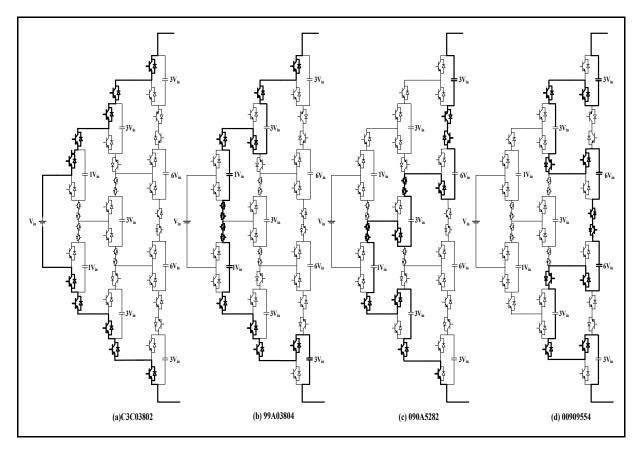

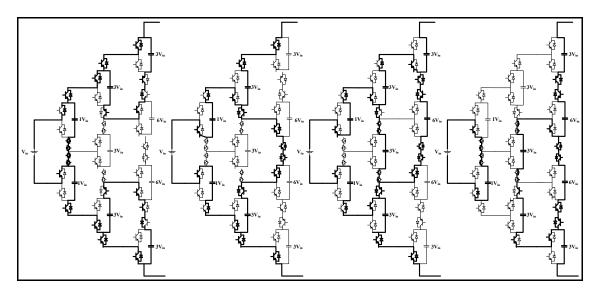

| Figure 1.62 | Thirty-one level transformerless PUC inverter                                    | 74 |

| Figure 1.63 | Equivalent circuit of each state in PUC7 or PUC5 inverter                        | 75 |

| Figure 1.64 | Modulation technique                                                             | 76 |

| Figure 1.65 | Seven-level sinusoidal PWM                                                       | 77 |

| Figure 1.66 | Waveform of signal S                                                             | 77 |

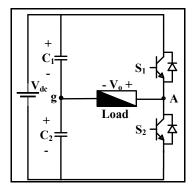

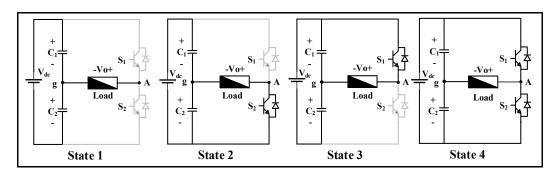

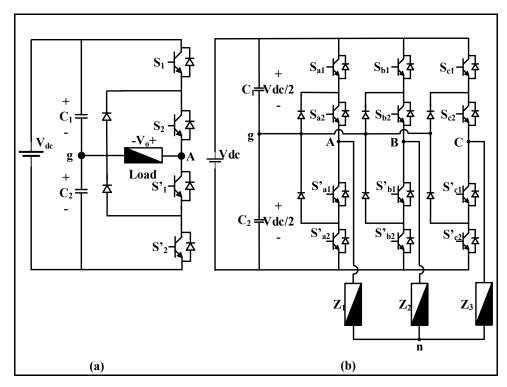

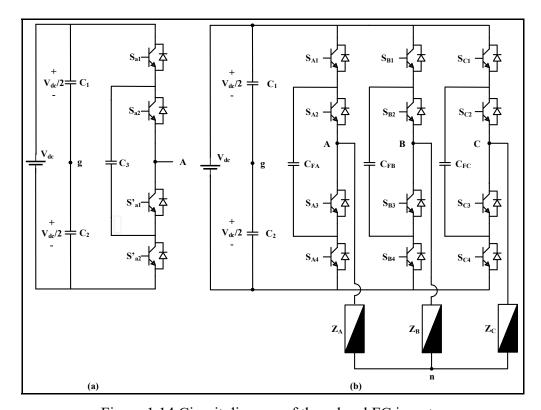

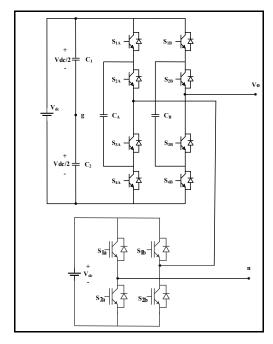

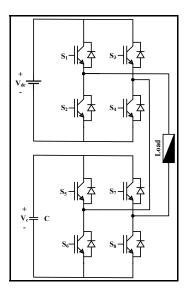

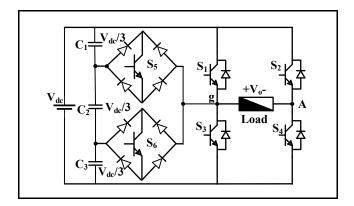

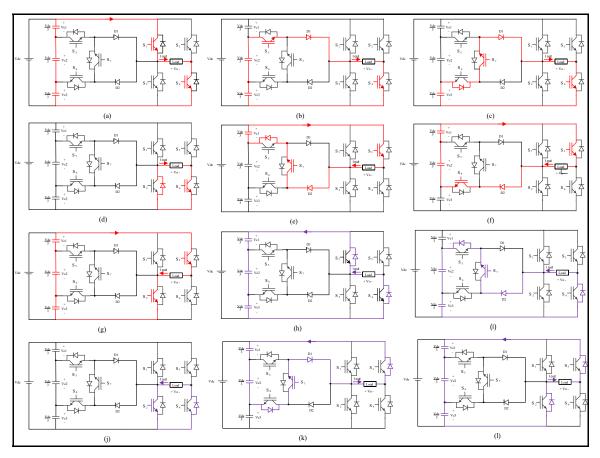

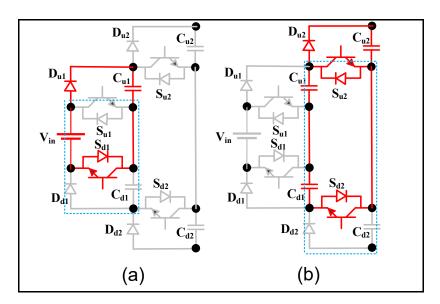

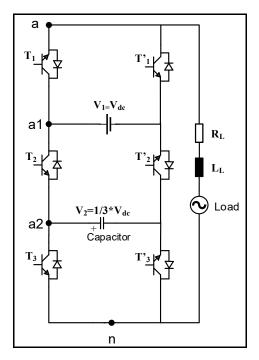

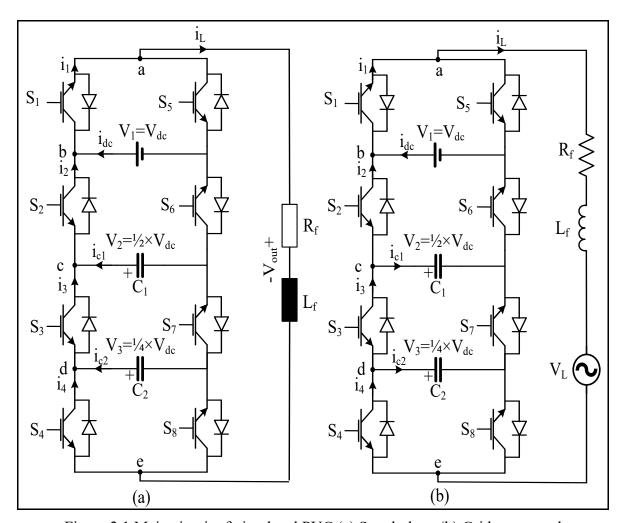

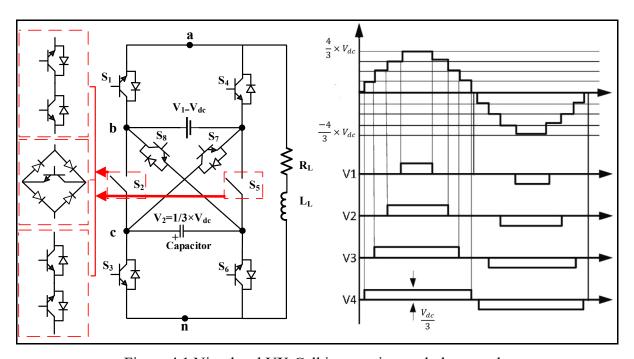

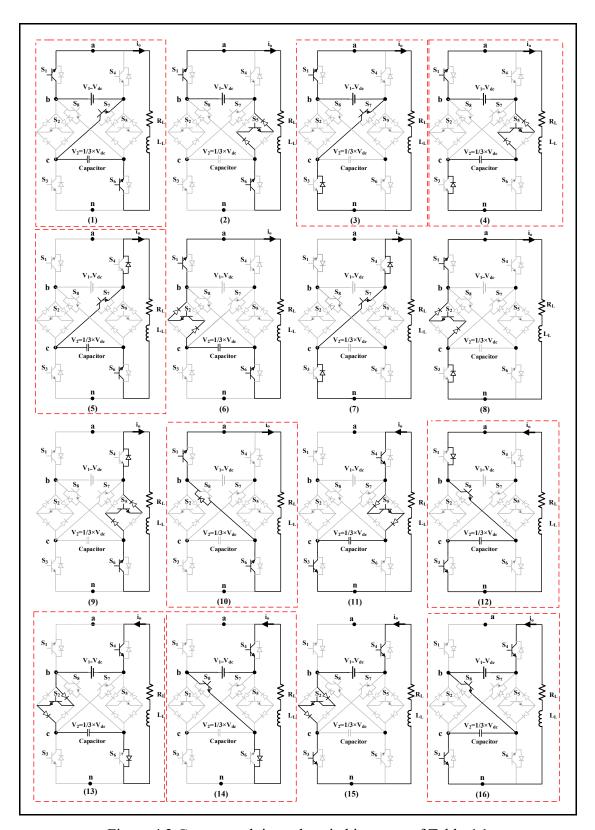

| Figure 2.1  | Main circuit of nine-level PUC (a) Stand-alone (b) Grid-connected                     | 80  |

|-------------|---------------------------------------------------------------------------------------|-----|

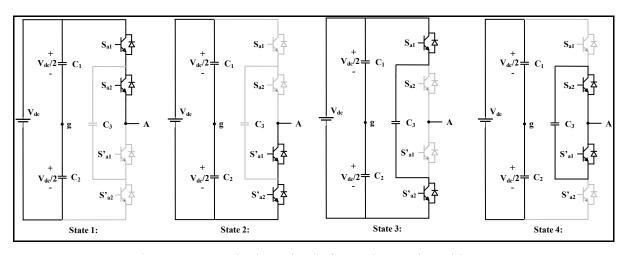

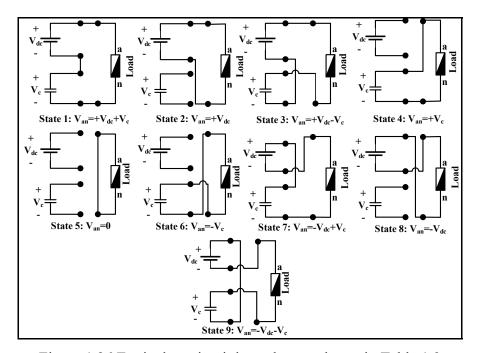

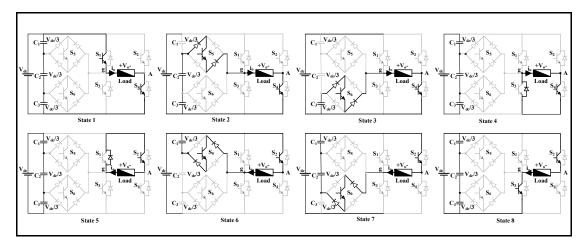

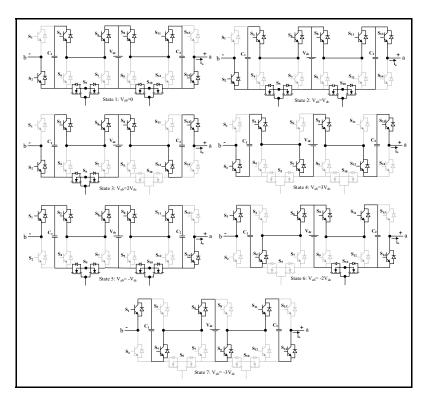

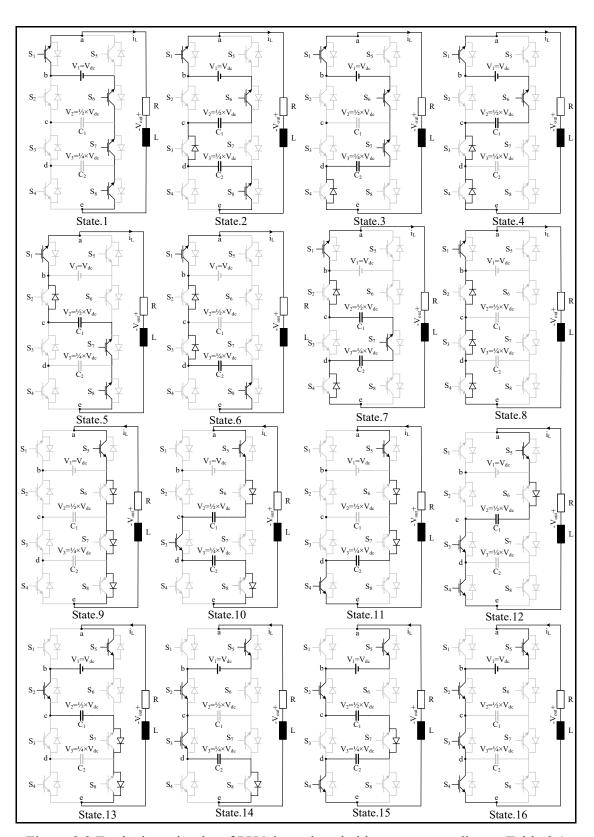

| Figure 2.2  | Equivalent circuits of PUC in each switching state according to Table 2.1             | 82  |

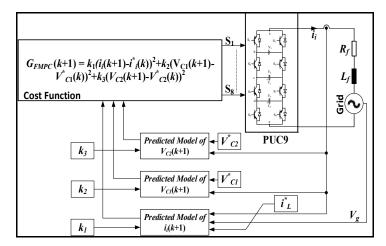

| Figure 2.3  | Block diagram of MPC for Grid-connected PUC9                                          | 86  |

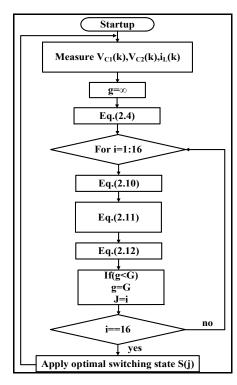

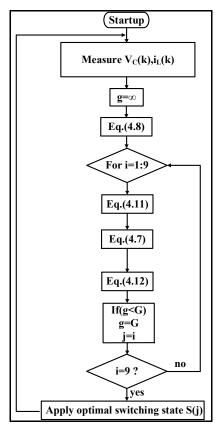

| Figure 2.4  | Flowchart of MPC for Grid-connected PUC9                                              | 87  |

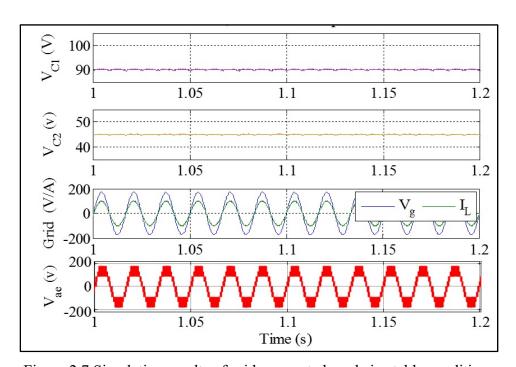

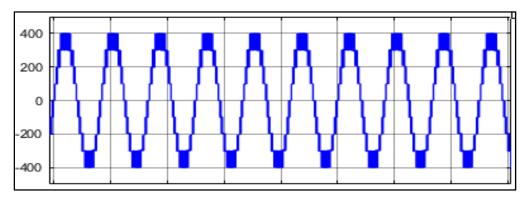

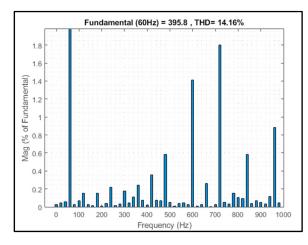

| Figure 2.5  | Simulation results of stand-alone mode in unstable conditions                         | 88  |

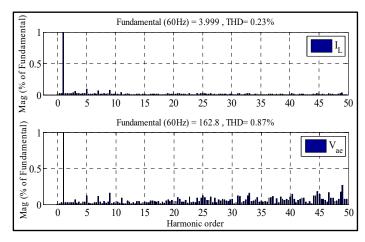

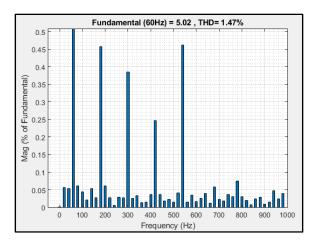

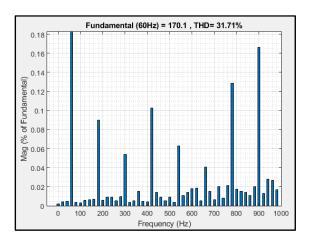

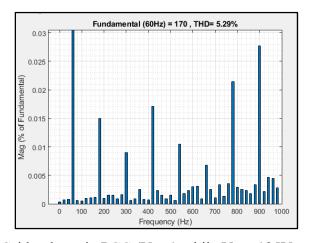

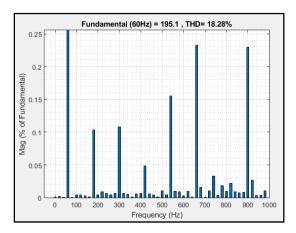

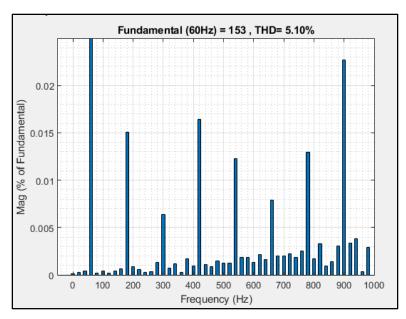

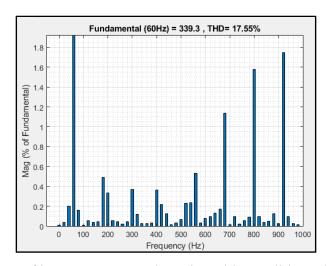

| Figure 2.6  | Harmonic content analysis for grid current and nine-level voltage in stand-alone mode | 88  |

| Figure 2.7  | Simulation results of grid-connected mode in stable conditions                        | 89  |

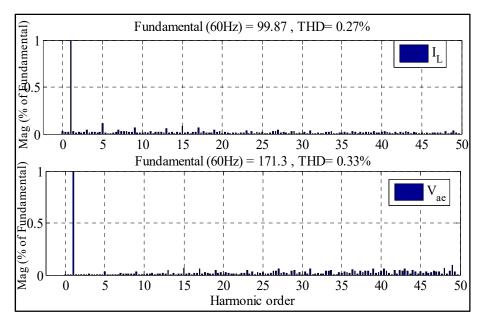

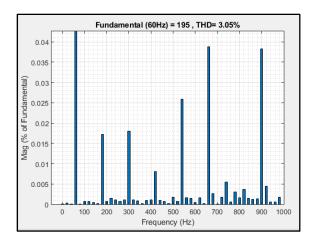

| Figure 2.8  | Harmonic content analysis for grid-current and nine-level voltage                     | 90  |

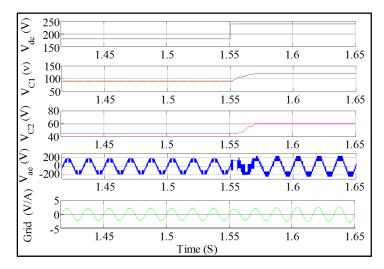

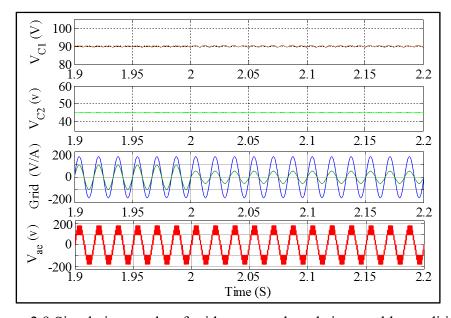

| Figure 2.9  | Simulation results of grid-connected mode in unstable conditions                      | 90  |

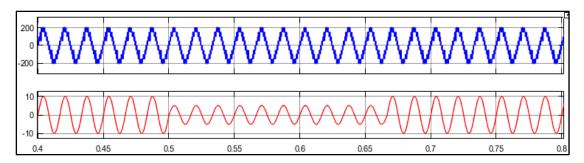

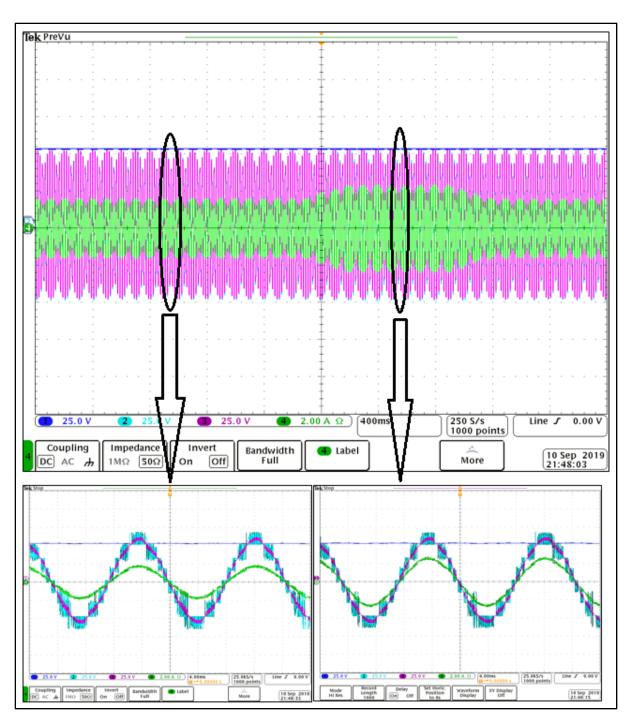

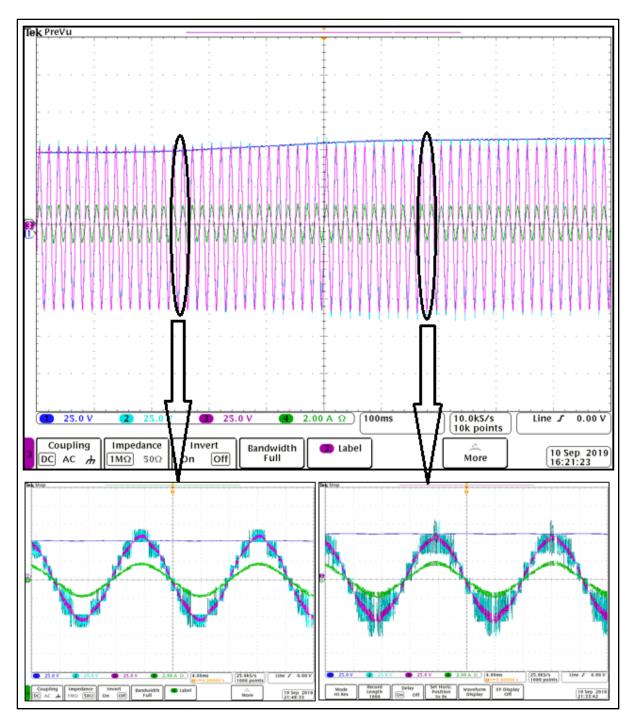

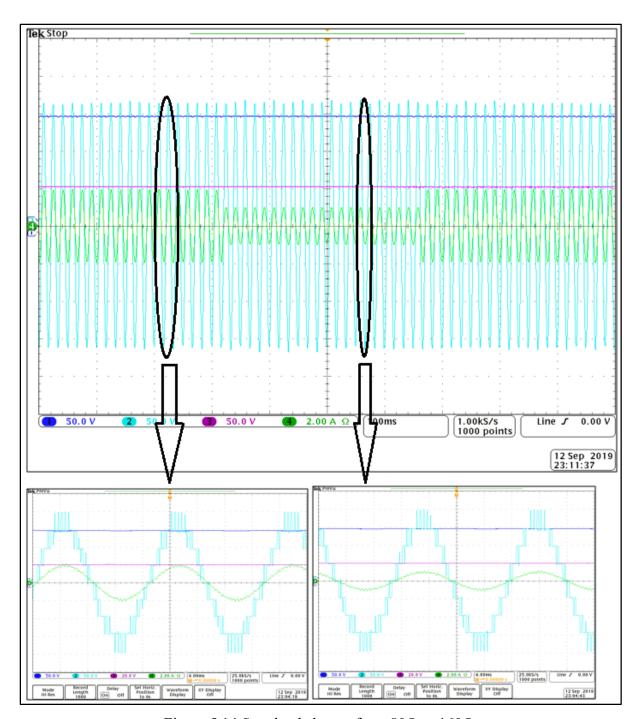

| Figure 2.10 | Stable condition reference current 2A                                                 | 91  |

| Figure 2.11 | Reference currenct changed from 4A to 2A                                              | 92  |

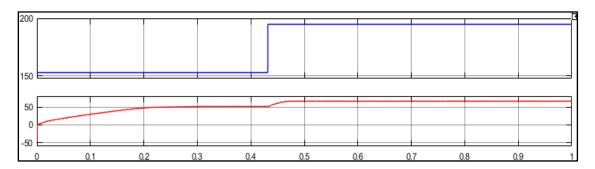

| Figure 2.12 | Vdc changed from 50V to 60V                                                           | 93  |

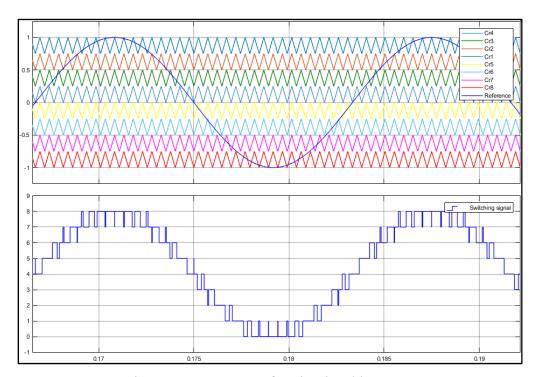

| Figure 3.1  | Three conventional LS-PWM                                                             | 96  |

| Figure 3.2  | Conventional PD-LS-PWM technique                                                      | 96  |

| Figure 3.3  | Input waveforms of conventional nine level PD-LS-PWM                                  | 97  |

| Figure 3.4  | Output Waveform of conventional nine level PD-LS-PWM                                  | 97  |

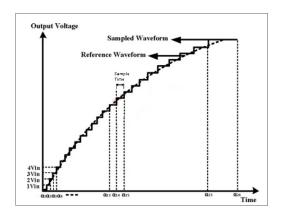

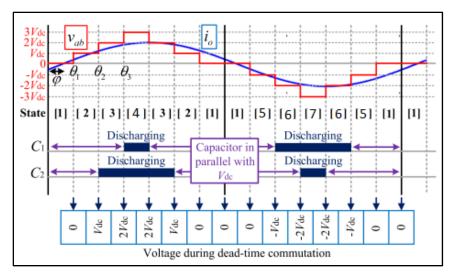

| Figure 3.5  | Proposed modulation technique                                                         | 98  |

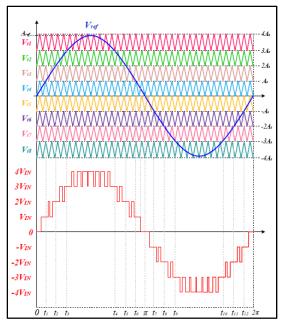

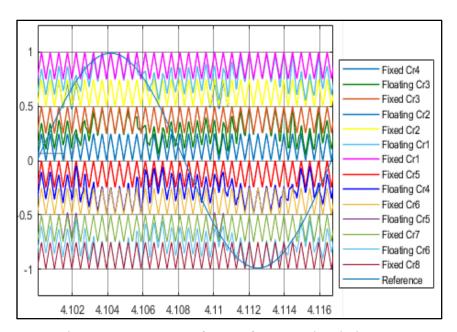

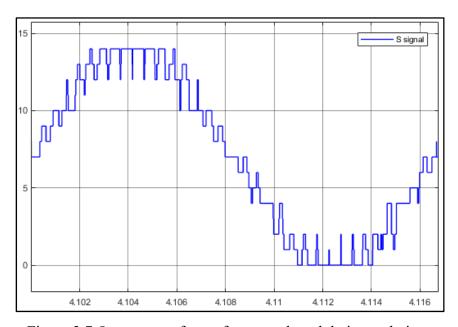

| Figure 3.6  | Input waveforms of proposed technique                                                 | 99  |

| Figure 3.7  | Output waveform of proposed modulation technique                                      | 99  |

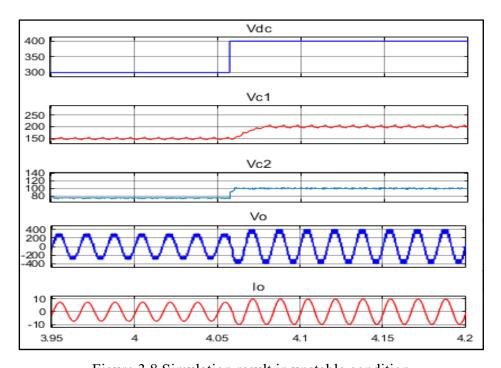

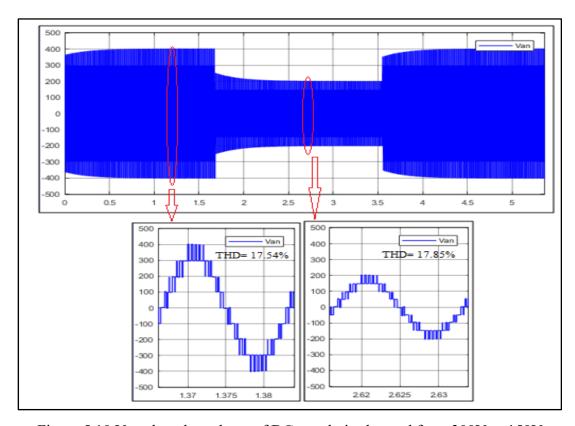

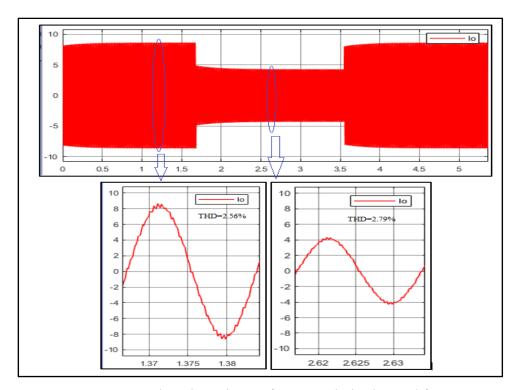

| Figure 3.8  | Simulation result in unstable condition                                               | 100 |

| Figure 3.9  | DC source and capacitors voltages in stable condition                                 | 101 |

| Figure 3.10 | Output voltage in stable condition                                                    | 101 |

| Figure 3.11 | Output voltage THD in stable condition                                                | 101 |

| Figure 3.12 | Output current in stable condition                                                                          | 102 |

|-------------|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.13 | Output current THD in stable condition                                                                      | 102 |

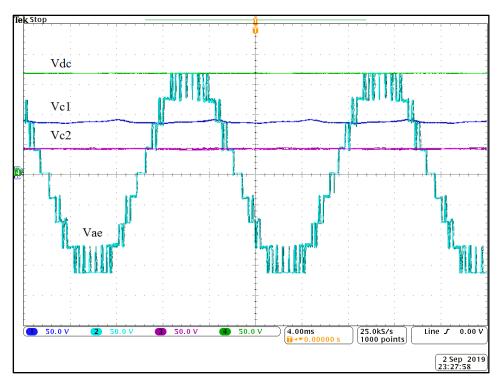

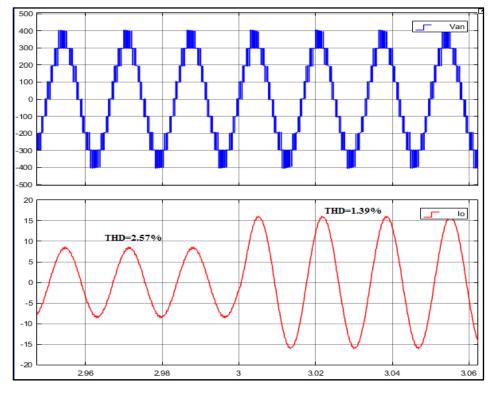

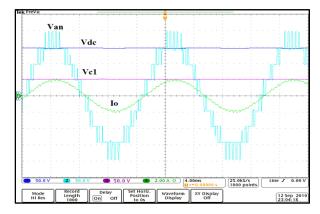

| Figure 3.14 | Voltages of V <sub>dc</sub> , V <sub>c1</sub> , V <sub>c2</sub> , and V <sub>ae</sub> in stable condition   | 104 |

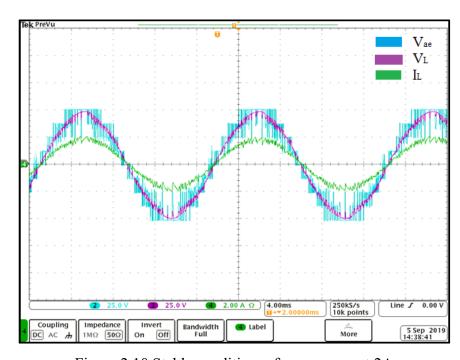

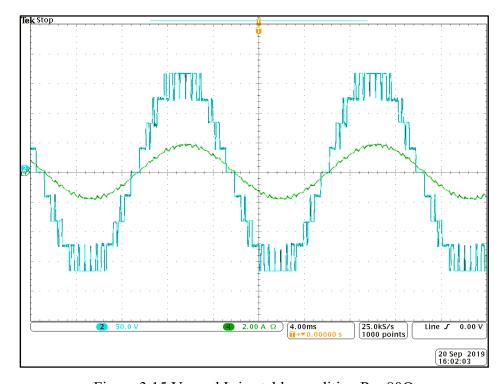

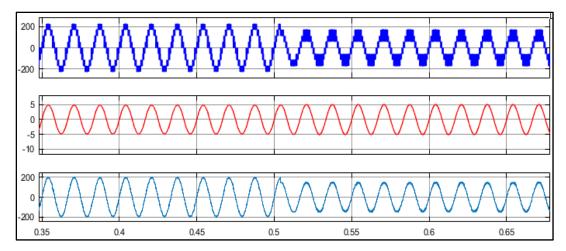

| Figure 3.15 | $V_{ae}$ and $I_o$ in stable condition $R_L$ =80 $\Omega$ .                                                 | 104 |

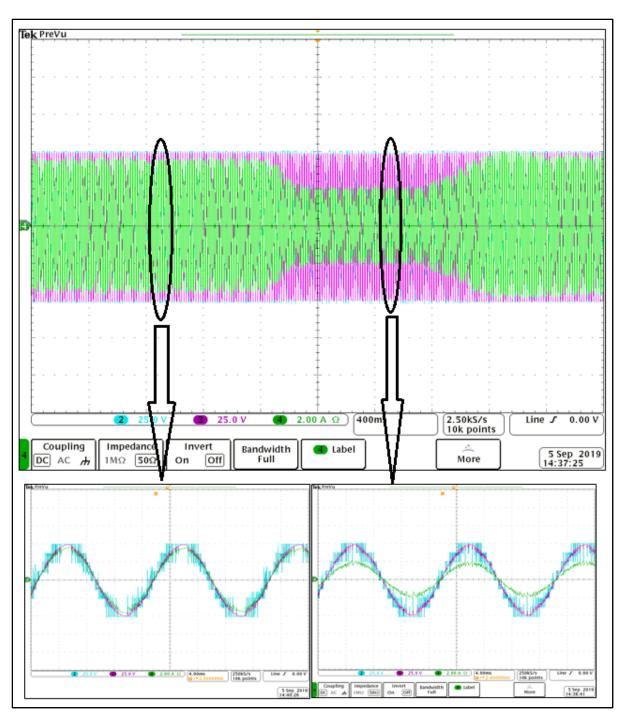

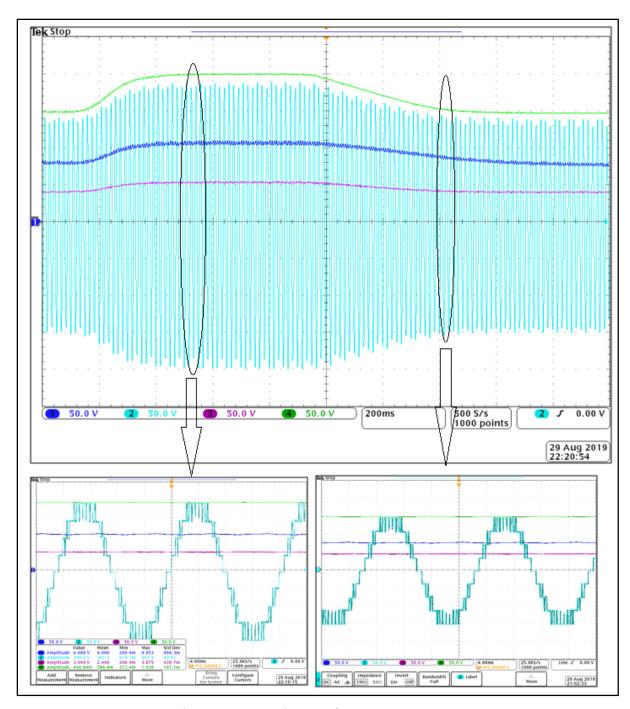

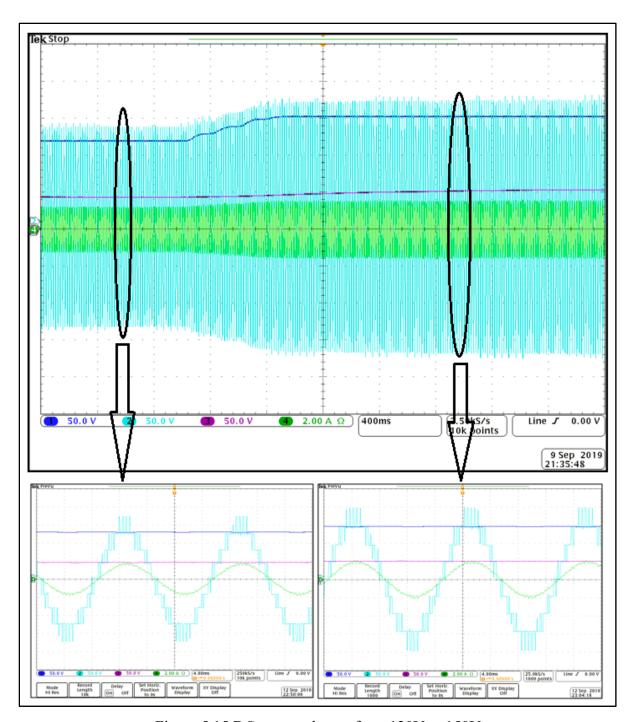

| Figure 3.16 | V <sub>dc</sub> changes from 153V to 195V                                                                   | 105 |

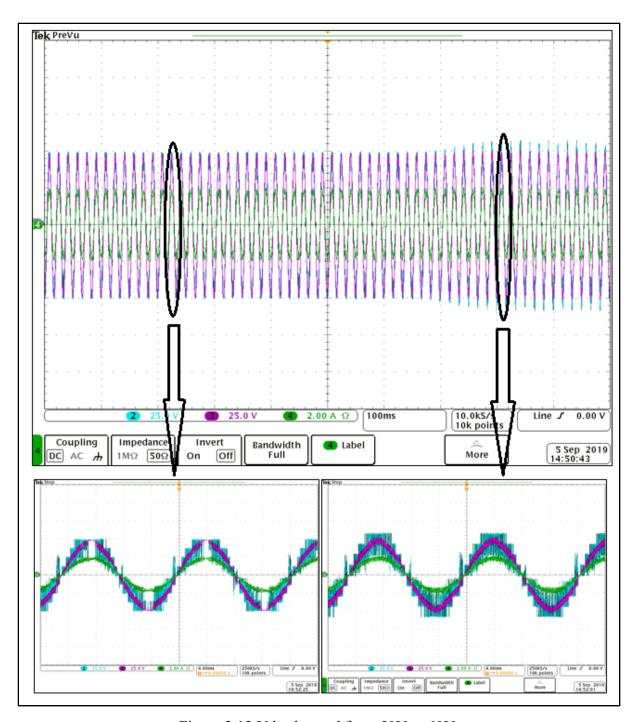

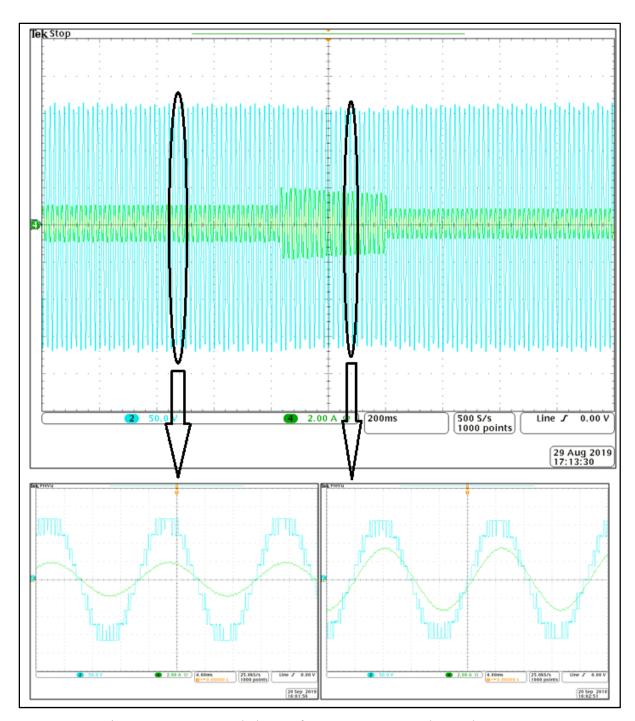

| Figure 3.17 | Step Load change from $80~\Omega$ to $40\Omega$ when Vdc= $170~V$                                           | 106 |

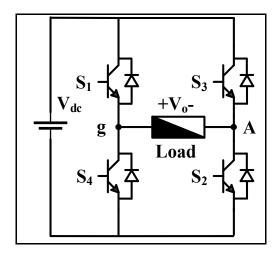

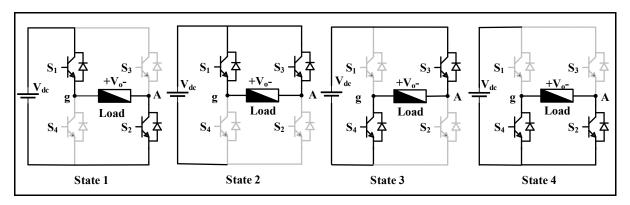

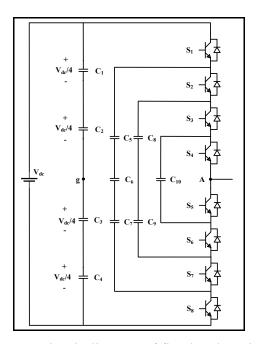

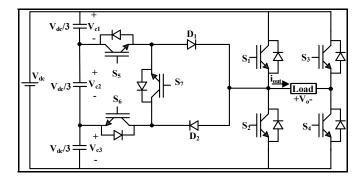

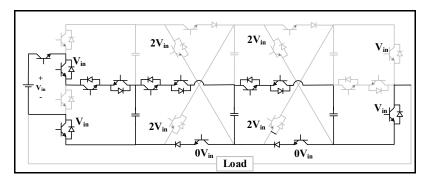

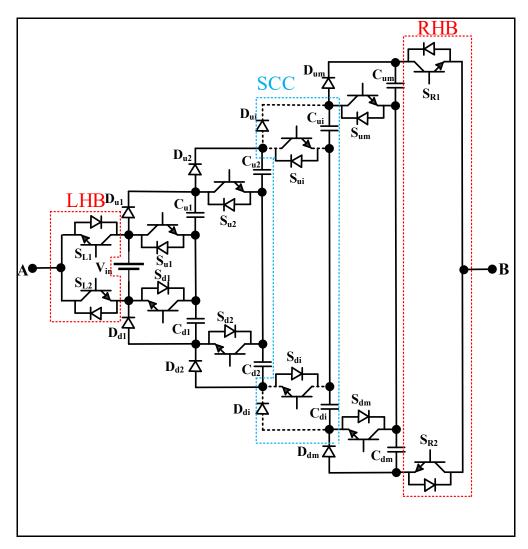

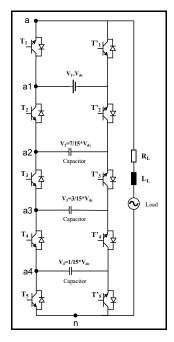

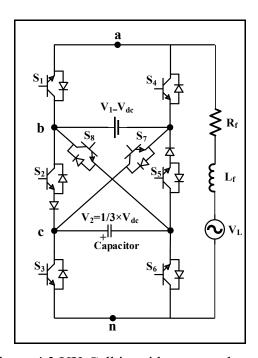

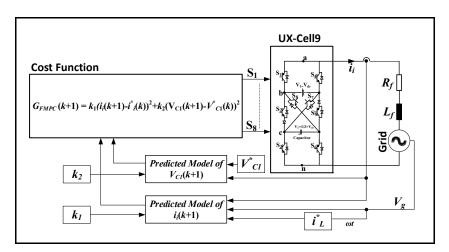

| Figure 4.1  | Nine-level UX-Cell inverter in stand-alone mode                                                             | 110 |

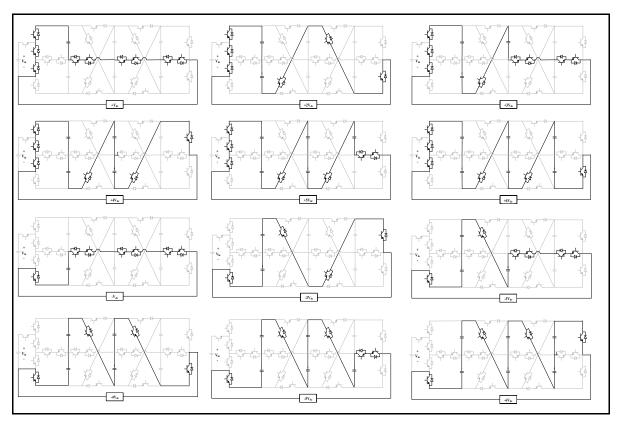

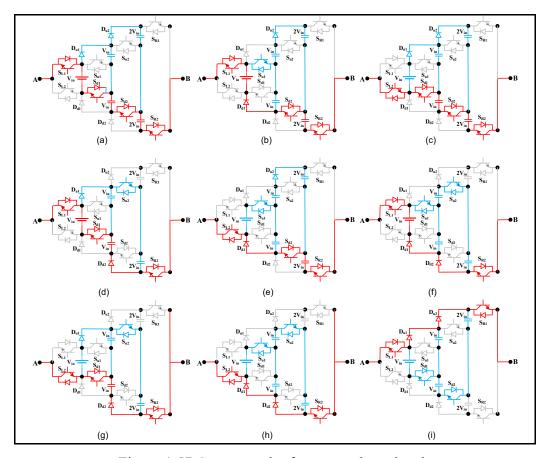

| Figure 4.2  | Current path in each switching state of Table 4.1                                                           | 112 |

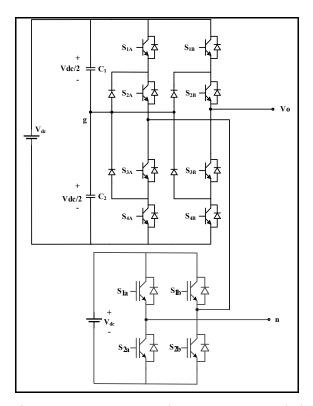

| Figure 4.3  | UX-Cell in grid-connected mode                                                                              | 113 |

| Figure 4.4  | Block diagram of MPC for Grid-connected UX-Cell MLI                                                         | 116 |

| Figure 4.5  | Flowchart of MPC for Grid-connected UX-Cell MLI                                                             | 118 |

| Figure 4.6  | Inverter voltage (Van) and Grid current (iL)                                                                | 119 |

| Figure 4.7  | Capacitors voltage (V <sub>dc</sub> , V <sub>c</sub> )                                                      | 119 |

| Figure 4.8  | Inverter voltage (Vae), Grid current (iL), Grid Voltage in PCC (Vpcc).                                      | 119 |

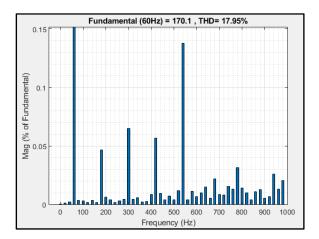

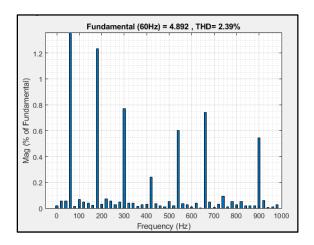

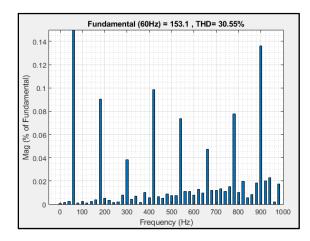

| Figure 4.9  | THD of grid current (i <sub>L</sub> ) while V <sub>DC</sub> =153V and V <sub>GRID</sub> =120V RMS           | 120 |

| Figure 4.10 | THD of inverter voltage (Vae) while VDC=153V and VGRID=120V RMS                                             |     |

| Figure 4.11 | THD of Grid voltage in PCC (V <sub>PCC</sub> ) while V <sub>DC</sub> =153V and V <sub>GRID</sub> =120V RMS. | 120 |

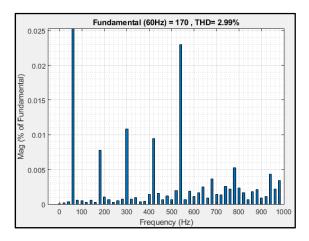

| Figure 4.12 | THD of grid current (i <sub>L</sub> ) while $V_{DC}$ =195V and $V_{GRID}$ =120V RMS                         | 121 |

| Figure 4.13 | THD of inverter voltage (Vae) while VDC=195V and VGRID=120V RMS                                             |     |

| Figure 4.14 | THD of Grid voltage in PCC (V <sub>PCC</sub> ) while V <sub>DC</sub> =195V and V <sub>GRID</sub> =120V RMS  | 121 |

| Figure 4.15 | Inverter voltage (Vae), Grid current (il), Grid Voltage in PCC (Vpcc)                                       | 122 |

| Figure 4.16 | THD of grid current (i <sub>L</sub> ) while V <sub>DC</sub> =170V and V <sub>GRID</sub> =138V RMS           | 122 |

| Figure 4.17 | THD of inverter voltage (V <sub>ae</sub> ) while V <sub>DC</sub> =170V and V <sub>GRID</sub> =138V RMS     |

|-------------|------------------------------------------------------------------------------------------------------------|

| Figure 4.18 | THD of Grid voltage in PCC (V <sub>PCC</sub> ) while V <sub>DC</sub> =170V and V <sub>GRID</sub> =138V RMS |

| Figure 4.19 | THD of grid current (i <sub>L</sub> ) while $V_{DC}$ =170V and $V_{GRID}$ =108V RMS123                     |

| Figure 4.20 | THD of inverter voltage (Vae) while VDC=170V and VGRID=108V RMS                                            |

| Figure 4.21 | THD of Grid voltage in PCC ( $V_{PCC}$ ) while $V_{DC}$ =170V and $V_{GRID}$ =108V RMS                     |

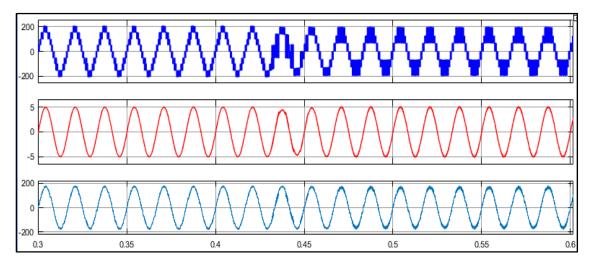

| Figure 4.22 | Grid voltage, output voltage, output current, and V <sub>dc</sub> in grid-connected mode                   |

| Figure 4.23 | Reference current is changed from 2A to 4A                                                                 |

| Figure 4.24 | DC voltage source is changed from 50V to 60V127                                                            |

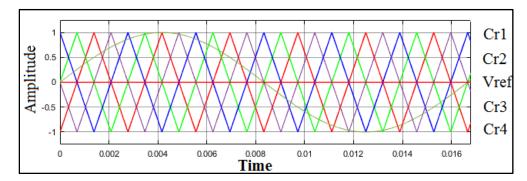

| Figure 5.1  | Carriers and sinusoidal reference waveforms in LS-PWM130                                                   |

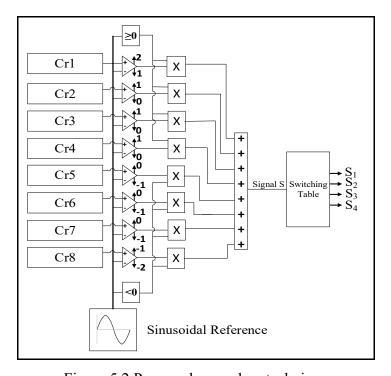

| Figure 5.2  | Proposed sensorless technique                                                                              |

| Figure 5.3  | Signal S                                                                                                   |

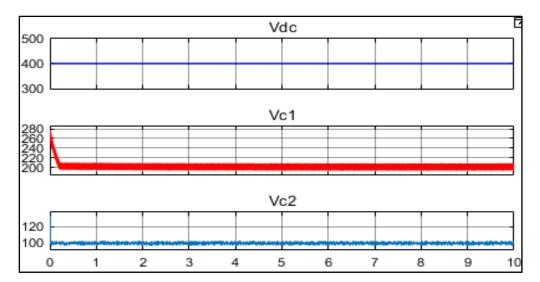

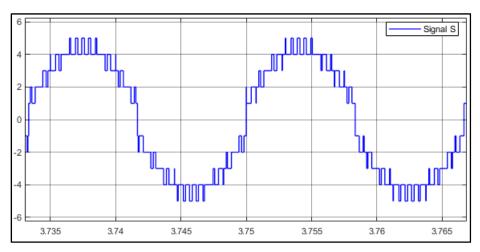

| Figure 5.4  | Capacitors voltage V <sub>dc</sub> , V <sub>c</sub> in stable condition                                    |

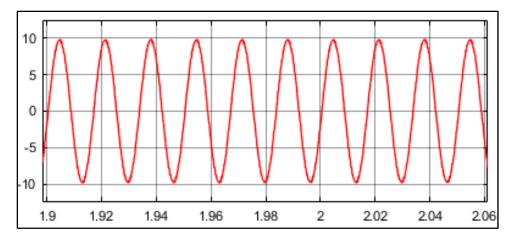

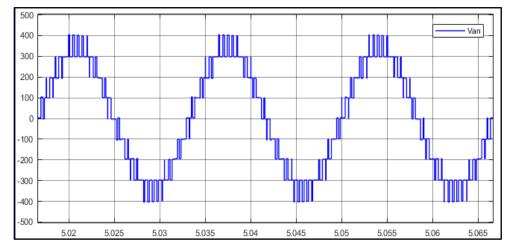

| Figure 5.5  | Inverter output voltage in stable condition when Vdc=300V132                                               |

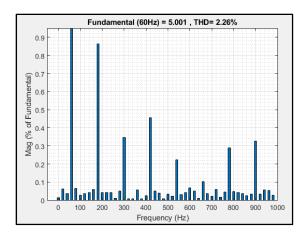

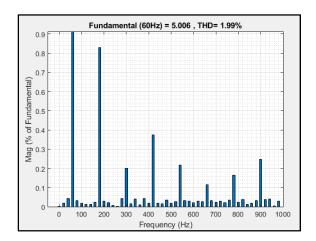

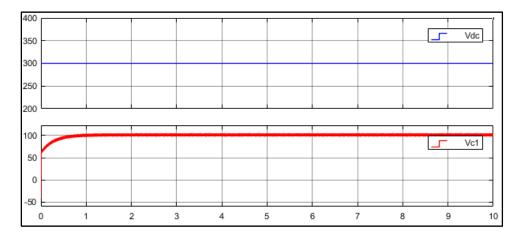

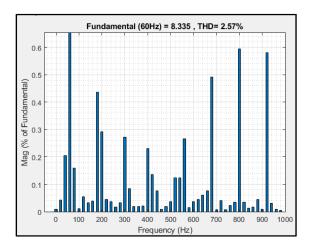

| Figure 5.6  | THD of inverter output voltage in stable condition when $V_{dc}$ =300V133                                  |

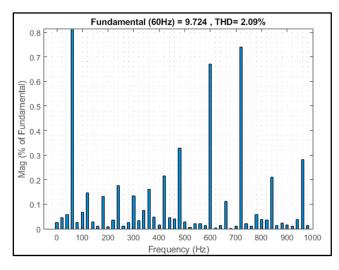

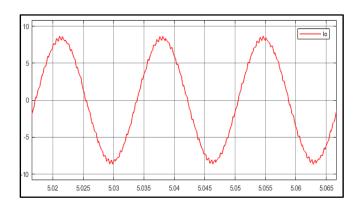

| Figure 5.7  | Output current when $R_L$ =40 $\Omega$ and $V_{dc}$ =300 $V$                                               |

| Figure 5.8  | THD of output current when $R_L$ =40 $\Omega$ and $V_{dc}$ =300 $V$ 133                                    |

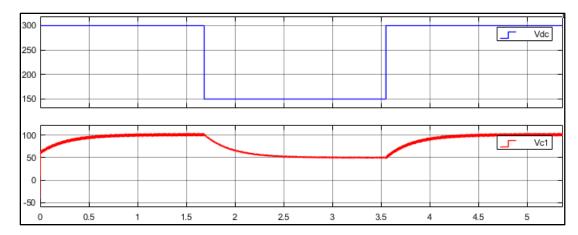

| Figure 5.9  | DC voltage source is changed from 300V to 150V134                                                          |

| Figure 5.10 | V <sub>an</sub> when the voltage of DC supply is changed from 300V to 150V134                              |

| Figure 5.11 | Output current when the voltage of DC supply is changed from 300V to 150V                                  |

| Figure 5.12 | Output voltage and output current when the load is changed from $40\Omega$ to $20\Omega$                   |

| Figure 5.13 | Stable condition (RL load 80Ω, 20mH, and Vdc=150)136                                                       |

| Figure 5.14 | Step load change from $80\Omega$ to $160\Omega$ | .137 |

|-------------|-------------------------------------------------|------|

| Figure 5.15 | DC source change from 120V to 150V              | .138 |

#### LIST OF ABREVIATIONS

AC Alternative Current

AF Active filter

AH-MLI Asymmetric hybrid multilevel inverters

AOD-LS-PWM Alternate Opposition-Disposition Level-Shifted Pulse Width Modulation

APF Active power filter

APOD Alternative Phase Opposite Disposition

CHB Cascaded H-Bridge

DC Direct Current

EV Electrical vehicle

FB Full Bridge

FC Flying Capacitor

HB Half Bridge

IEEE Institute of Electrical and Electronics Engineering

IGBT Insulated gate bipolar transistor

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

LS-PWM Level Shifted Pulse Width Modulation

MLI Multi-Level Inverter

NPC Neutral Point Clamped

OD-LS-PWM Opposition-Disposition Level-Shifted Pulse Width Modulation

PCC Point of common coupling

PD-LS-PWM Phase Disposition Level Shifted Pulse Width Modulation

PF Power Factor

PFC Power Factor Correction

PI Proportional Integral

PID Proportional Integral derivative

PLL Phase Locked Loop

PS-PWM Phase shifted Pulse Width Modulation

PUC5 5-Level Packed U-Cell

#### XXIV

PUC7 7-Level Packed U-Cell

PUC9 9-Level Packed U-Cell

PV Photovoltaic

PWM Pulse Width Modulation

RMS Root Mean Square

SPS SimPowerSystem

SVM Space Vector Modulation

THD Total Harmonic Distortion

UPS Uninterruptable power supplies

VSC Voltage source converter

VSI Voltage source inverter

#### INTRODUCTION

Due to rising concerns about the emission of greenhouse gases resulting from burning fossil fuels, which are expensive, air pollutant, and non-renewable sources, the usage of renewable energy sources is increasing in the world. As a result, countries invest more in such energy sources such as solar, wind, and hydroelectric power, etc. For injecting the generated electricity from solar panels, and new generation of wind and hydro turbines, we need inverters; however, conventional inverters, which are normally 2 or 3-levels converters, generate and inject negative harmonics into the grid. These adverse harmonics have negative effect on voltage and current of distributed networks and electric machines. Consequently, researchers focused more on reducing such harmful harmonics, especially after imposing harmonic restriction standards such as EN61000-3-2 and IEC 1000-3-2 recommended by IEEE (2004) and IEC (2005) in order (Grégoire, Al-Haddad, & Ounejjar, 2009; Ounejjar & Al-Haddad, 2008, 2009; Ounejjar, Al-Haddad, & Gregoire, 2011). Firstly, researches paid attention to developing active and passive filters in order to decrease negative harmonics that inverters produce. These days, researchers focus more on designing multilevel inverters, particularly single de source multilevel inverters for increasing the efficiency and decreasing the fabrication and installation costs. There are different multilevel topologies; each topology has its own pros and cons. Among these patents, Packed U-Cell (PUC), planned by Ounejjar and Al-Haddad in 2008, is a promising topology, known as a highly efficient and low-cost inverter with the least number of switches in comparison with other multilevel inverters. On the other hand, it has problems such as capacitors' voltage balancing, the current limitation drawn from the voltage source, requiring more DC sources in three-phase setup, etc. Reducing the complexity and weakness of high efficiency multilevel converters like PUC can convince industry to utilize them more. In this work, I tried to decrease the complexity of PUC9 and then prove these techniques with Matlab Simulink and validate them experimentally.

#### **CHAPTER 1**

#### MULTILEVEL CONVERTER LITERATURE REVIEW

#### 1.1 Introduction

The single dc source multilevel inverter topologies are dominant technologies in home and industrial applications due to high efficiency, high-power quality, and minimum manufacturing cost. They require many calculations for generating switching signals and more sensors compared to conventional inverters. Nowadays, by increasing the speed of microcontrollers, and decreasing the cost of high-speed microcontrollers and voltage/current sensors, the control of multilevel inverters is cheaper and easier. In this chapter, different topologies of single DC source multilevel inverters are reviewed. Some different structures of existing single DC source multilevel inverters are investigated in terms of switching state possibility, the number of their components, advantages and disadvantages, and THD (Total Harmonic Distortion). To this end, the conventional multilevel inverter topologies including NPC, FC and CHB are taken into consideration because they are the fundamental multilevel structures. Afterward, some recently introduced single dc source multilevel inverters' topologies are deeply surveyed. Then, PUC topology is considered. After that, some modulation and voltage balancing technique are briefly reviewed.

#### 1.2 Multi-level Cascaded Topologies

#### 1.2.1 Half-Bridge Inverter

Figure 1.1 shows half-bridge voltage-source inverter circuit, which consists of two identical capacitors: one ground between these capacitors, and one DC source (Batarseh & Harb, 2018; Koshti & Rao, 2017). These capacitors act as two identical DC sources with the value of  $\frac{V_{dc}}{2}$  to make the output positive and negative. Table 1.1 illustrates switching states' possibility of half-bridge voltage source inverter.

Figure 1.1 Half-bridge voltage source inverter

Table 1.1 Switching state possibility of half-bridge inverter

| States | $S_1$ | S <sub>2</sub> | Vo                  |

|--------|-------|----------------|---------------------|

| 1      | 0     | 0              | Open Circuit        |

| 2      | 0     | 1              | $\frac{-V_{dc}}{2}$ |

| 3      | 1     | 0              | $\frac{+V_{dc}}{2}$ |

| 4      | 1     | 1              | Short Circuit       |

Figure 1.2 Equivalent circuit of half-bridge inverter in each switching state

Due to having two switches, there are four possible switching states as shown in Table.1.1 In the first state, both switches are OFF, as seen in Figure 1.2; this state is not suitable for the operation of inverter because the current should keep going through the load. In the second state, switch one is OFF and switch two is ON, with a simple KVL in the lower loop, it is

obtained that  $V_o$  is equal to  $\frac{-V_{dc}}{2}$ . In the third state, switch one is ON and switch two is OFF and with KVL in upper loop; it is obtained that  $V_o$  is equal to  $\frac{+V_{dc}}{2}$ . In the final state, both switches are ON, in this state, the current is shot through voltage source, and again no current passes through the load; therefore, it is not the appropriate state for the operation of the inverter. As a result, only two operational states for this inverter exist (states 2 and 3). It can be clearly seen that the output of half-bridge inverter has only two levels  $(\frac{-V_{dc}}{2} \text{ and } \frac{+V_{dc}}{2})$ ; however, if the switches are controlled with PWM (Pulse Width Modulation), the output of the inverter looks like any voltages between  $\frac{-V_{dc}}{2}$  and  $\frac{+V_{dc}}{2}$ .

#### 1.2.2 Full-Bridge Inverter

Figure 1.3 shows full-bridge or H-bridge multilevel voltage-source inverter configuration (Batarseh & Harb, 2018; Koshti & Rao, 2017). Due to having four different switches in this topology, eight switching state possibilities exist, and yet in order to prevent KCL violation and shoot through, vertical switches are complimentary. It means that S<sub>1</sub> and S<sub>4</sub> cannot be ON or OFF at the same time; likewise, S<sub>3</sub> and S<sub>2</sub> cannot be ON or OFF at the same time, hence there are only four operational switching states, as shown in Table 1.2. Figure 1.4 indicates equivalent circuit for each state.

Figure 1.3 Full-bridge voltage source inverter

| States | $S_1$ | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | Vo               |

|--------|-------|----------------|----------------|----------------|------------------|

| 1      | 1     | 1              | 0              | 0              | $V_{dc}$         |

| 2      | 1     | 0              | 1              | 0              | 0                |

| 3      | 0     | 0              | 1              | 1              | -V <sub>dc</sub> |

| 4      | 0     | 1              | 0              | 1              | 0                |

Table 1.2 Switching states of full-bridge inverter

Figure 1.4 Equivalent circuit of H-bridge inverter in each switching state

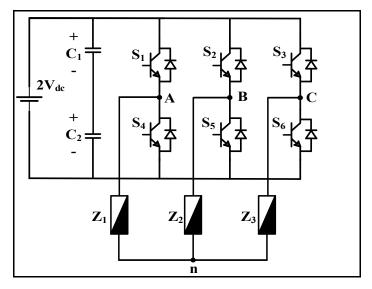

#### 1.2.3 Three-Phase Six Switches Voltage Source Inverter

Figure 1.5 shows three-phase full-bridge inverter with two capacitors as voltage sources and wye connected load (Batarseh & Harb, 2018; Koshti & Rao, 2017). As can be seen, this inverter is made by connecting three half-bridge inverters in parallel. The sequence of pulses summation at any time for  $S_1$ - $S_6$  should be zero in order to have balance line-to-line output voltage. In this regard, the conduction angle is equal to  $\frac{\pi}{2}$ .

Figure 1.5 Three-phase full-bridge inverter

Table 1.3 illustrates switching states of  $S_1$ - $S_6$  for a three-phase full bridge inverter. It should be mentioned that in order to avoid short circuit in power supply, vertical switches are complimentary. It means that  $S_1$ ,  $S_4$  and  $S_3$ ,  $S_6$  and  $S_5$ ,  $S_2$  switches cannot be ON or OFF at the same time. It can be seen that this inverter produces three levels of voltage in each phase. Due to having balanced output voltages, the switches must switch in a way that the voltages  $V_a$ ,  $V_b$ ,  $V_c$  have  $\frac{2\pi}{3}$  phase difference.

Table 1.3 Switching states of three-phase full-bridge inverter

| States | $S_1$ | S <sub>2</sub> | S <sub>3</sub> | Van              | V <sub>bn</sub>  | Vcn              | $V_{ab}$          | $V_{bc}$          | Vca               |

|--------|-------|----------------|----------------|------------------|------------------|------------------|-------------------|-------------------|-------------------|

| 1      | 0     | 0              | 0              | -V <sub>dc</sub> | -V <sub>dc</sub> | -V <sub>dc</sub> | 0                 | 0                 | 0                 |

| 2      | 0     | 0              | 1              | -V <sub>dc</sub> | -V <sub>dc</sub> | +V <sub>dc</sub> | 0                 | -2V <sub>dc</sub> | +2V <sub>dc</sub> |

| 3      | 0     | 1              | 0              | -V <sub>dc</sub> | $+V_{dc}$        | -V <sub>dc</sub> | -2V <sub>dc</sub> | $+2V_{dc}$        | 0                 |

| 4      | 0     | 1              | 1              | -V <sub>dc</sub> | $+V_{dc}$        | $+V_{dc}$        | -2V <sub>dc</sub> | 0                 | $+2V_{dc}$        |

| 5      | 1     | 0              | 0              | $+V_{dc}$        | -V <sub>dc</sub> | -V <sub>dc</sub> | +2V <sub>dc</sub> | 0                 | -2V <sub>dc</sub> |

| 6      | 1     | 0              | 1              | $+V_{dc}$        | -V <sub>dc</sub> | $+V_{dc}$        | $+2V_{dc}$        | -2V <sub>dc</sub> | 0                 |

| 7      | 1     | 1              | 0              | +V <sub>dc</sub> | +V <sub>dc</sub> | -V <sub>dc</sub> | 0                 | +2V <sub>dc</sub> | -2V <sub>dc</sub> |

| 8      | 1     | 1              | 1              | $+V_{dc}$        | $+V_{dc}$        | $+V_{dc}$        | 0                 | 0                 | 0                 |

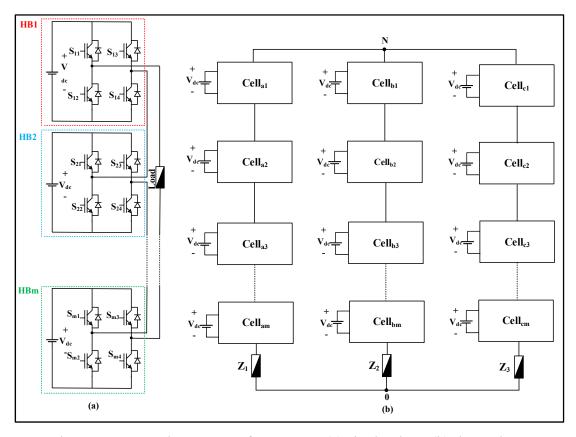

#### 1.2.4 Cascaded H-Bridge (CHB) Inverter

CHB is normally used for producing more than three levels of voltage at the inverter output (Gaikwad & Arbune, 2016; Koshti & Rao, 2017). This inverter, which is created by connecting a number of H-bridge inverters in series, is one of the popular inverters in industry due to its simplicity and basic technology. Each H-bridge has a separate DC source and produces two levels of voltage. Figure 1.6 shows the single phase five-level CHB MLI. The output voltage of this inverter is equal to the summation of output voltages of H-bridge cells together. Considering the 0-voltage, n number of H-bridge cells could produce (2n+1) levels of voltage at the output of this inverter and an n-level CHB inverter needs 2(n-1) switches.

Figure 1.6 Single-phase five-level CHB MLI

Figure 1.7 (a) illustrates the main circuit and Table 1.4 shows the switching states of single phase five-level CHB inverter. As known form H-bridge topology, in each H-bridge cell, vertical switches are complimentary. Besides, the output of each H-bridge cell could be  $V_{\rm dc}$ , 0, -V<sub>dc</sub>. Furthermore, single phase five-level CHB MLI has two H-bridge Cells. Considering the given information, it can be said that five voltage levels at the output of this inverter are ( $2V_{\rm dc}$ ,  $V_{\rm dc}$ ,  $V_{\rm dc}$ ,  $V_{\rm dc}$ ,  $V_{\rm dc}$ ). As can be seen in Table 1.4, there are six switching states; in addition, for feeding switches, four signal pairs have to be generated for single phase five-level CHB inverter.

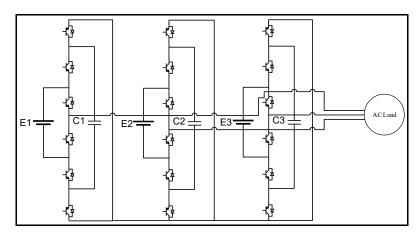

By connecting three single-phase CHB inverters in parallel, the three-phase CHB inverter would be produced. For generating three phases in this topology, 6-voltage sources and twelve pairs of switching signals for feeding 24 switches are needed. (See Figure 1.7 (b))

Figure 1.7 General Structure of CHB MLI (a) single-phase (b) three-phase

Table 1.4 Switching states of single-phase five-level CHB MLI

| States | $S_1$ | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | $V_{o}$    |

|--------|-------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|------------|

| 1      | 1     | 0              | 1              | 0              | 1              | 0              | 1                     | 0              | 0          |

| 2      | 1     | 0              | 1              | 0              | 1              | 0              | 0                     | 1              | $V_{dc}$   |

| 3      | 1     | 0              | 0              | 1              | 1              | 0              | 0                     | 1              | $2V_{dc}$  |

| 4      | 0     | 1              | 0              | 1              | 0              | 1              | 1                     | 0              | $-V_{dc}$  |

| 5      | 0     | 1              | 0              | 1              | 0              | 1              | 0                     | 1              | 0          |

| 6      | 0     | 1              | 1              | 0              | 0              | 1              | 1                     | 0              | $-2V_{dc}$ |

Advantages and disadvantages of five-level CHB Inverter are outlined as follows:

#### Advantages:

- It does not need any capacitor or diode for clamping.

- In comparison with NPC and FC inverter, it needs fewer components; therefore, its price is less than the two former types.

- By increasing the number of levels, its output is like sinusoidal waveform even without a filter.

- It is suitable for high-power, medium-power and low-power applications of renewable energies.

#### **Disadvantages:**

- It needs Isolated DC source for each stage.

- The number of PF levels is limited because of voltage unbalancing problems, packaging constraints and circuit layout.

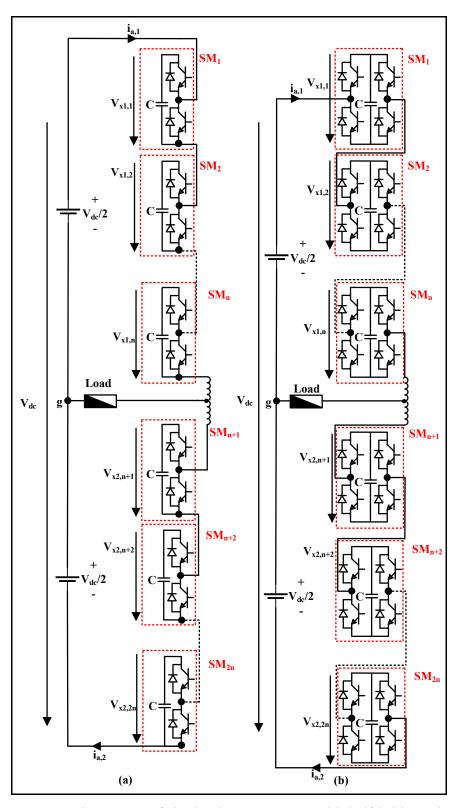

#### 1.2.5 Modular Multilevel Converter (MMC)

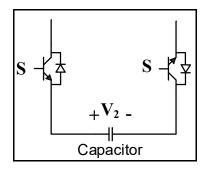

Lesnicar and Marquardt proposed Modular Multilevel Converter for HVDC applications in 2003 (Haridas, Khandelwal, & Das, 2016; Lesnicar & Marquardt, 2003). In this topology, a large number of identical submodules are connected in series for producing more voltage levels at the output of MMC MLI. Figure 1.8 (a) illustrates the main circuit of single phase MMC with half-bridge submodule and Figure 1.8 (b) indicates circuit of single phase MMC with full-bridge submodule. This topology consists of two arms and each arm consists of n submodules. Overall, one single phase MMC has 2n sub modules. In this topology, each submodule could be one of conventional voltage source inverters, such as half-bridge, full-bridge, etc. Half-bridge inverter can generate only +V<sub>c</sub> and 0 voltage level, so this topology with half-bridge submodules is appropriate for being connected to DC systems. Besides, full-bridge inverters generate -V<sub>c</sub>, 0, and +V<sub>c</sub>, hence this topology with full-bridge submodules is suitable for being connected to both DC and AC systems; however, it needs a high number of switches in

comparison with half-bridge submodules, which increases the cost of these inverters with full-bridge submodules. Figure 1.9 shows the general structure of three phase MMC.

Nowadays, this topology is used widely in industry and HVDC applications due to below pros.

#### **Advantages:**

- Different power and voltage levels are achieved.

- Developing is fast and easy.

- THD is decreased.

- Voltages are divided into power devices.

- Standard component are used.

- Approved devices are used.

- Failures are managed.

- It is modular.

#### Disadvantage:

• Capacitor voltage balancing is complicated.

Figure 1.8 General structure of single-phase MMC (a) with half-bridge submodule (b) with full-bridge submodule

Figure 1.9 General structure of three-phase MMC

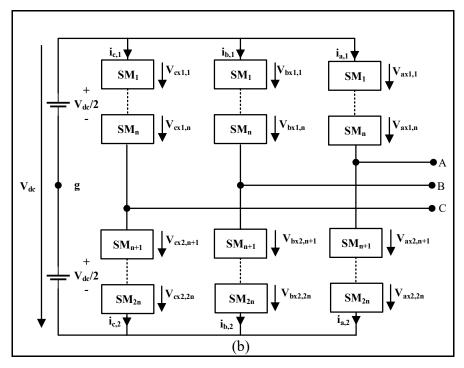

#### 1.3 Multilevel Diode Clamped Inverter Topologies

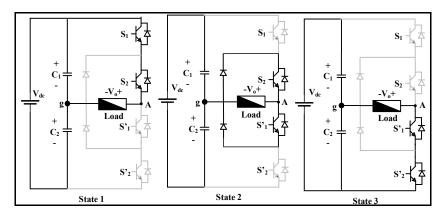

# 1.3.1 Three-level Neutral Point Clamped (NPC) Inverter

Nabae, Takashi and Akagiin invented NPC inverter in 1981. NPC is also known as diode clamped multilevel inverter (Koshti & Rao, 2017; Rodriguez, Bernet, Steimer, & Lizama, 2010). In this topology, clamped diodes are used in order to limit voltage stress of electric devices. Figure 1.10 (a) illustrates the main circuit of single phase three-level NPC inverter. This topology is similar to half-bridge inverter but with two switches instead of each switch in half-bridge inverter plus two clamping diodes, one between switch  $S_1$  and  $S_2$  and the other one between  $S'_1$  and  $S'_2$  connected to the neutral point, and two bulky capacitors.  $S_1$ ,  $S'_1$  and  $S_2$ ,  $S'_2$  are complimentary. Each capacitor acts as a voltage source with value of  $\frac{V_{dc}}{2}$  and the middle point of these capacitors is connected to the ground, thus three levels of voltage that the inverter produces in the output are  $(\frac{+V_{dc}}{2}, 0, \frac{-V_{dc}}{2})$ . By connecting three single-phase NPC inverters in parallel and managing the switching state in a way that each phase has 120-degree phase

difference with other phases, three-phase NPC inverter can be made, as seen in Figure 1.10 (b). Table 1.5 illustrates switching states of NPC three-level inverter and Figure 1.11 shows equivalent circuit of this topology in each state of Table 1.5.

Figure 1.10 Three-level NPC inverter

Table 1.5 Switching states of three level NPC inverter

| States | $S_1$ | S <sub>2</sub> | S' <sub>1</sub> | S'2 | Vo                  |

|--------|-------|----------------|-----------------|-----|---------------------|

| 1      | 1     | 1              | 0               | 0   | $\frac{+V_{dc}}{2}$ |

| 2      | 0     | 1              | 1               | 0   | 0                   |

| 3      | 0     | 0              | 1               | 1   | $\frac{-V_{dc}}{2}$ |

Figure 1.11 Equivalent circuit in each state of Table 1.5

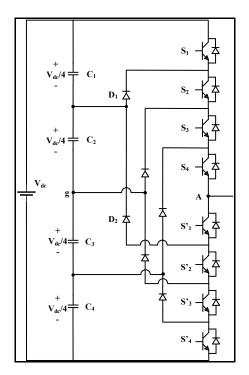

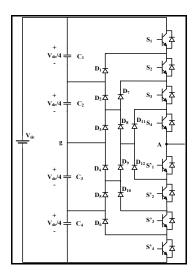

# 1.3.2 Five-level Diode Clamped Inverter

Among the most important problems of the NPC topology, the imbalance of voltage among voltage diodes is a significant one. Indeed, as soon as three levels are exceeded, this problem appears, because the diode  $D_2$  must support three times more voltage than diode  $D_1$  (see Figure 1.12) (Koshti & Rao, 2017; Rodriguez et al., 2010).

Figure 1.12 Five-level NPC inverter circuit

In general, the voltage that a diode must withstand depends on its position in the circuit, and is obtained by the following equation:

$$V_{diode} = \frac{N - 1 - k}{N - 1} V_{dc}$$

Where:

N is the number of levels.

k is the position of the diode in the converter, which can take the values of 1 up to N-2.  $V_{dc}$  is the voltage of the DC bus.

In order to overcome this problem, Lai and Peng (1996) suggested to use a topology similar to conventional NPC inverter, but with three series calibration diodes instead of one diode, which needs to support three times more voltage (instead of  $D_2$ ) in order to divide this voltage between these diodes.

An N-level NPC inverter needs  $\{2N-2\}$  switches,  $\{N-1\}$  voltage source, and  $\{(N-1), (N-2)\}$  diodes and each capacitor acts like a DC source with the value of  $\frac{V_{dc}}{(N-1)}$ . Table 1.6 indicates the switching states of five-level NPC inverter. It should be noted that switches  $S_1$ ,  $S'_1$  and  $S_2$ ,  $S'_2$  and  $S_3$ ,  $S'_3$  and  $S_4$ ,  $S'_4$  are complimentary.

Table 1.6 Switching states of five-level NPC inverter

| States | $S_1$ | S <sub>2</sub> | $S_3$ | S <sub>4</sub> | S'1 | S'2 | S'3 | S'4 | $V_{o}$             |

|--------|-------|----------------|-------|----------------|-----|-----|-----|-----|---------------------|

| 1      | 1     | 1              | 1     | 1              | 0   | 0   | 0   | 0   | $\frac{V_{dc}}{2}$  |

| 2      | 0     | 1              | 1     | 1              | 1   | 0   | 0   | 0   | $\frac{V_{dc}}{4}$  |

| 3      | 0     | 0              | 1     | 1              | 1   | 1   | 0   | 0   | 0                   |

| 4      | 0     | 0              | 0     | 1              | 1   | 1   | 1   | 0   | $\frac{-V_{dc}}{4}$ |

| 5      | 0     | 0              | 0     | 0              | 1   | 1   | 1   | 1   | $\frac{-V_{dc}}{2}$ |

# **Advantages:**

- Switches have to tolerate half of DC voltage source.

- Voltage harmonics placed at the center double the switching frequency.

- Capacitors are pre-charged and they have low capacitance.

- Inverted are used back to back.

- It has high efficiency at fundamental frequency.

## Disadvantages:

- By increasing a voltage level, the number of clamping diodes will increase.

- Precise monitoring and controlling of DC levels are needed.

Yuan and Barbi (1999, 2000) proposed a five-level converter characterized by diodes with the same voltage resistance  $\frac{V_{dc}}{4}$  (Figure 1.13). Take the example where the point A is connected to the point O through the switches S<sub>3</sub>, S<sub>4</sub>, S'<sub>1</sub> and S'<sub>2</sub>. In this case, the diodes D<sub>3</sub>, D<sub>4</sub>, D<sub>7</sub>, D<sub>8</sub>, D<sub>9</sub>, D<sub>10</sub>, D<sub>11</sub> and D<sub>12</sub> block zero volts, while D<sub>2</sub> and D<sub>5</sub> diodes block  $\frac{V_{dc}}{4}$ . Since S<sub>1</sub> and S'<sub>4</sub> are blocked, D<sub>1</sub> and D<sub>6</sub> diodes will block zero volts; however, a big problem of this topology is the imbalance of output voltages. This drawback limits the use of this topology in the industry for the three-level inverter.

Figure 1.13 Five-level NPC inverter proposed by Yuan

# 1.4 Multilevel Flying Capacitor Topologies

## 1.4.1 Flying Capacitor (FC) Single-phase three-level inverter

The capacitor clamped inverter or flying capacitor was invented by Meynard and Foch in 1992 (Koshti & Rao, 2017; Taleb, Helaimi, Benyoucef, & Boudjema, 2016). FC inverter is alike NPC inverter, but instead of clamping diodes, capacitors are used. In this structure, each capacitor acts as a different voltage source. Figure 1.14 (a) shows the main circuit of single phase three-level FC MLI. By connecting three single-phase inverters in parallel, a three-phase FC MLI is made as shown in Figure 1.14 (b). In addition, managing the switching states of switches in the way that each phase has 120-degree phase difference with other phases is necessary.

Figure 1.14 Circuit diagram of three level FC inverter

In the above-mentioned circuit, when  $S_{a1}$  and  $S_{a2}$  are ON,  $V_A$  is equal to  $+V_{C1}$ ; when  $S'_{a1}$  and  $S'_{a2}$  are ON,  $V_A$  is equal to  $-V_{C2}$ ; when  $S_{a1}$  and  $S'_{a1}$  are ON,  $C_3$  is charged and  $V_A$  is equal to zero; in addition, when  $S_{a2}$  and  $S'_{a2}$  are ON,  $C_3$  is discharged and also  $V_A$  is equal to zero( see Table 1.7 and Figure 1.15). An m-level FC inverter needs  $\{2m-2\}$  switches,  $\{m-1\}$  DC link capacitor, and  $\{\frac{(m-1)(m-2)}{2}\}$  auxiliary capacitor.

| States | Sal | S <sub>a2</sub> | S'a1 | S'a2 | Vo                  | Effect on capacitor(C <sub>3</sub> ) |

|--------|-----|-----------------|------|------|---------------------|--------------------------------------|

| 1      | 1   | 1               | 0    | 0    | $\frac{+V_{dc}}{2}$ | No effect                            |

| 2      | 0   | 0               | 1    | 1    | $\frac{-V_{dc}}{2}$ | No effect                            |

| 3      | 1   | 0               | 1    | 0    | 0                   | Charging                             |

| 4      | 0   | 1               | 0    | 1    | 0                   | Discharging                          |

Table 1.7 Switching states of three-level FC inverter

Figure 1.15 Equivalent circuit for each state in Table 1.7

## 1.4.2 Flying Capacitor (FC) Single-phase five-level inverter

Figure 1.16 shows the main circuit of FC single phase five-level inverter and Table 1.8 illustrates its switching states (Koshti & Rao, 2017; Taleb et al., 2016). In this topology, C<sub>1</sub>,

C<sub>2</sub>, C<sub>3</sub>, and C<sub>4</sub> are charged to the value of  $\frac{V_{dc}}{4}$ , hence they can be considered as four identical DC sources with the value of  $\frac{V_{dc}}{4}$ .

Figure 1.16 Circuit diagram of five level FC inverter

Table 1.8 Switching states of FC inverter

| States | $S_1$ | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | Vo                  |

|--------|-------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|---------------------|

| 1      | 1     | 1              | 1              | 1              | 0              | 0              | 0                     | 0              | $\frac{+V_{dc}}{2}$ |

| 2      | 1     | 1              | 1              | 0              | 1              | 0              | 0                     | 0              | $\frac{+V_{dc}}{4}$ |

| 3      | 1     | 1              | 0              | 1              | 1              | 1              | 0                     | 0              | 0                   |

| 4      | 1     | 0              | 0              | 1              | 1              | 1              | 1                     | 0              | $\frac{-V_{dc}}{4}$ |

| 5      | 0     | 0              | 0              | 0              | 1              | 1              | 1                     | 1              | $\frac{-V_{dc}}{2}$ |

## **Advantages:**

- No clamping diode is needed.

- One dc source is required.

- Without using transformer, the required number of voltage levels can be achieved.

- The capacitors are charged to different voltage levels instead of sharing the same voltage.

- Active and reactive power flow is controllable.

- Inverter can stay connected in short period outages and deep voltage sags.

#### Disadvantages:

- Complicated modulation process due to initial setup of capacitors.

- Controlling the voltage level of all capacitors is complicated.

- Pre-charging of all capacitors to the same voltage is complex.

- Switching utilization and efficiency for transmitting active power is poor.

- Design is complex when voltage across the capacitors has a large fraction of DC bus voltage.

- Capacitors are more expensive and bulky in comparison with diodes.

- Due to increasing the number of levels, packaging is more difficult.

#### 1.5 Asymmetric hybrid multilevel inverters (AH-MLI)

With combination of two conventional inverters, Asymmetric hybrid MLI has been proposed. Figure 1.17 and Figure 1.18 show two popular Asymmetric hybrid multilevel inverters(Malinowski, Gopakumar, Rodriguez, & Perez, 2010). Normally, for decreasing the number of separate DC sources, CHB MLI is combined with other topologies. These inverters produce more voltage levels. As a result, they have a positive effect on the THD and power quality; however, these topologies are not considered in this paper owing to the fact that most of them are not single dc source inverters. Nevertheless, one of these topologies, which is popular in industry and is also single dc source, is taken into consideration.

Figure 1.17 DC MLI and CHB MLI cascaded

Figure 1.18 FC MLI and CHB MLI cascaded

# Multilevel Modulation Space Vector Voltage Level Based Algorithms Based Algorithms Space Vector Hybrid Modulation Multicarrier PWM Selective Harmonic Modulation Control Level Shifted 3-D Algorithms High Switching Frequency Low Switching Frequency Mixed Switching Frequency Opposition Alternate Opposition

# 1.6 Modulation Strategies to Control Switches of Inverters

Figure 1.19 Conventional strategies for modulating the waveforms Taken from Franquelo et al (2008)

Figure 1.19 illustrates most strategies for modulating the waveforms. The popular techniques in industry include phase shift pulse width modulation (PS-PWM), level shift pulse width modulation (LS-PWM), space vector modulation (SVM) and selective harmonic elimination. In this section, three methods of common modulation control strategies; PS-PWM, LS-PWM and SVM, highly used in industry, will be explained. Before describing these methods, to compare the two level inverter with multilevel one, bipolar PWM for half-bridge inverters will be discussed. In addition, it should be noted that the number of carrier signals for generating multilevel voltages depends on the counts of voltage levels. The following equation shows the relation between voltage levels and number of carriers.

$$N=L-1$$

(1.1)

Where N is the number of carrier signals and L is the voltage levels. For instance, to generate 5 voltage levels, four carriers are needed.

# 1.6.1 Bipolar PWM

This modulation technique is called bipolar because in this method the output voltage of the inverter is varied between two values. Below equation shows the modulation index of bipolar PWM (Bin, 2006a, 2006b).

$$m = \frac{V_{ref}}{V_{cr}} \tag{1.2}$$

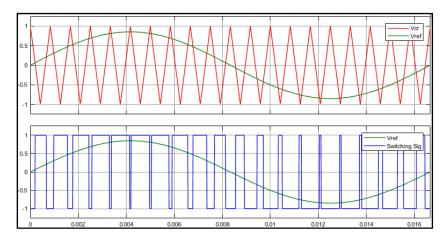

In this approach, generating bipolar voltage at the output needs one sinusoidal reference and one carrier signal. In this method, sinusoidal reference signal is compared to a carrier signal. When  $V_{ref} > V_{cr}$  the value of switching signal will be one otherwise the switching signal value will be -1. (See Figure 1.20)

Figure 1.20 Bipolar PWM

#### 1.6.2 Level Shifted Modulation

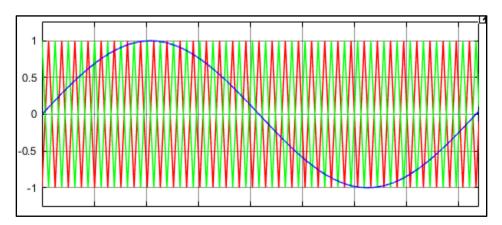

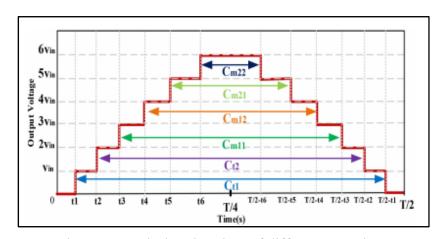

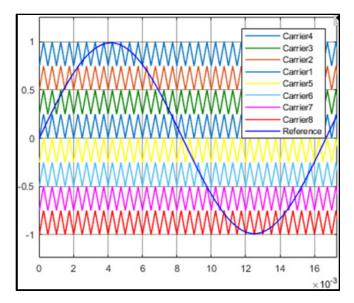

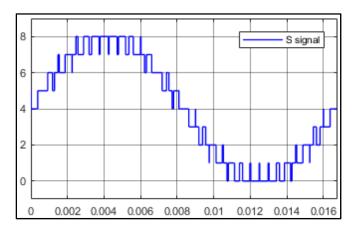

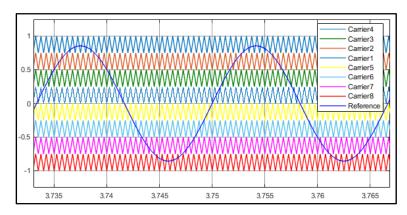

In this method, career signals are placed vertically between maximum and minimum value of sinusoidal reference signal (Bin, 2006a). In general, the sinusoidal reference signal is varied between 1 and -1. As a result, carriers are placed between 1 and -1. In this approach, an N level inverter needs N-1 carriers Equation (1.1). These carriers have the same frequency and peak-

to-peak amplitude. For example, for a nine level inverter like PUC9, eight carriers are needed. Assuming that sinusoidal reference signal fluctuates between 1 and -1, the amplitude of each carrier is equal to 0.25. In this method, triangular carriers' signals are compared to a sinusoidal reference signal. Equation (1.3) indicates the process of generating switching signal in this method and Figure 1.21 illustrates carriers' signals, sinusoidal reference signal and switching signal in this approach.

$$\begin{cases} \text{If } V_{\text{ref}} \geq \text{Cr}_1 & \rightarrow \text{Switching signal} = 8 \\ \text{If } \text{Cr}_2 \leq V_{\text{ref}} < \text{Cr}_1 & \rightarrow \text{Switching signal} = 7 \\ \text{If } \text{Cr}_3 \leq V_{\text{ref}} < \text{Cr}_2 & \rightarrow \text{Switching signal} = 6 \\ \text{If } \text{Cr}_4 \leq V_{\text{ref}} < \text{Cr}_3 & \rightarrow \text{Switching signal} = 5 \\ \text{If } \text{Cr}_5 \leq V_{\text{ref}} < \text{Cr}_4 & \rightarrow \text{Switching signal} = 4 \\ \text{If } \text{Cr}_6 \leq V_{\text{ref}} < \text{Cr}_5 & \rightarrow \text{Switching signal} = 3 \\ \text{If } \text{Cr}_7 \leq V_{\text{ref}} < \text{Cr}_6 & \rightarrow \text{Switching signal} = 2 \\ \text{If } \text{Cr}_8 \leq V_{\text{ref}} < \text{Cr}_7 & \rightarrow \text{Switching signal} = 1 \\ \text{If } \text{Cr}_8 > V_{\text{ref}} & \rightarrow \text{Switching signal} = 0 \end{cases}$$

Figure 1.21 LS-PWM for nine-level inverters

#### 1.6.3 Phase Shifted Modulation

In m voltage levels, MLI, m-1 carriers are required for PS-PWM(Bin, 2006a, 2006b). Equation (1.4) shows how by phase displacement these carriers should be placed between two adjacent carriers.

$$\Delta \emptyset = \frac{2\pi}{m-1} \tag{1.4}$$

For PS-PWM in five-level inverter, four triangular carriers are needed (see Figure 1.22) based on equation (1.4),  $\Delta \emptyset = \frac{\pi}{2}$ . It means that, Cr<sub>1</sub> with Cr<sub>4</sub> and Cr<sub>2</sub> with Cr<sub>3</sub> have 180° phase shift. Equation (1.5) shows Modulation index in PS-PWM.

$$m = \frac{V_{ref}}{Cr_i} \tag{1.5}$$

In this equation, Cr<sub>i</sub> are the carrier waveforms and i=1,2, 3,...,m. It should be mentioned that in this modulation technique all carriers have the same size, but the Cr<sub>i</sub> in LS-PWM for m voltage level inverter must be multiplied by m-1 because of the amplitude of carriers that are divided to m-1.

Figure 1.22 Phase shift PWM carrier wave forms

In order to shift the harmonic orders to next frequency, phase shift modulation technique is an industrial approach. Therefore, filters' size will be either low or neglected depending on the

switching frequency. Through PS-PWM, which is a modulation method, harmonic orders will be shifted to the multiples of (m-1) by switching frequency. The formula is as follows:

$$f_{sw-inverter} = \text{(m-1)} \ f_{cr}$$

(1.6)

If the modulation technique is PS-PWM, harmonic components are shifted due to the fact that carriers' frequency is multiplied by inverter's switching frequency. Inverter's frequency, however, is equal to carriers' frequency at level shift modulation.

Additionally, for modulating the reference voltage by the carrier signals, there is another technique, where two carrier signals are put at the phase shift of 180 and one reference voltage is compared to the signals. In this method, if  $V_{ref} > V_{cr1}$  switch 1 gate is turned on. Also, the gate of another switch is turned on when  $V_{ref} < V_{cr2}$ . The modulation signals are shown in Figure 1.23.

Figure 1.23 Unipolar modulation signal

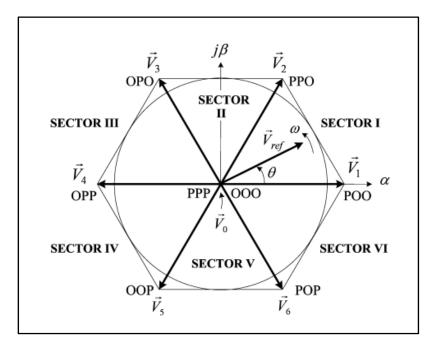

#### 1.6.4 Space Vector Modulation (SVM)

For generating pulses for switches, SVM is a method that uses vector concept, where the voltage vectors, which are produced by each switching state set, are calculated(Bin, 2006b). Next comes the instantaneous determining of magnitude and phase of the reference voltage vector. With respect to the location of reference voltage vector, the nearest voltage vectors'

combination is chosen and the corresponding switches for generating these voltage vectors are fired considering the time intervals which are specified. The calculation of the mentioned intervals is according to reference voltage vector. Figure 1.24 indicates the three-phase inverter H-bridge's concept of vectors. The equation mentioned below is used for modulation index if  $V_d$  is the DC voltage and  $V_{ref}$  is the reference voltage.

$$ma = \frac{\sqrt{3}V_{ref}}{V_d} \tag{1.7}$$

Figure 1.24 Space-vectors modulation to produce switching states of two level inverters Taken from Bin (2006b)

## 1.7 Single-DC Source Multilevel Inverter Topologies

#### 1.7.1 Single-DC Source CHB Inverter

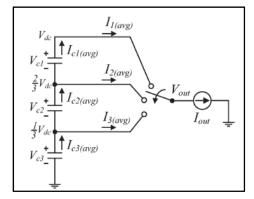

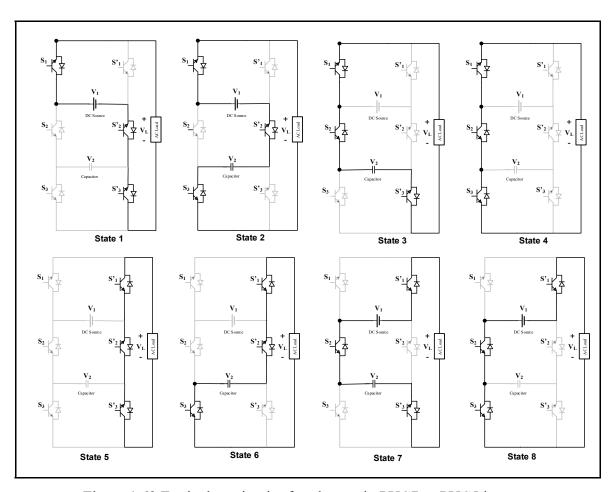

In the below five-level CHB inverter (Figure 1.6), if one of DC sources is replaced with one capacitor, it turns to single DC source CHB inverter as illustrated in Figure 1.25 (Vahedi, Sharifzadeh, Al-Haddad, & Wilamowski, 2015). It can be seen that the upper cell is connected

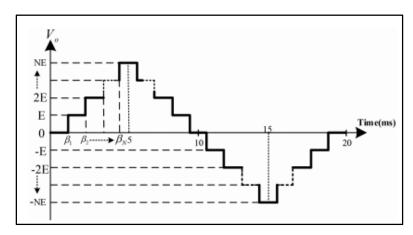

to voltage source and the lower cell is connected to the capacitor. Voltage source must charge the capacitor at the desired level, and for generating some voltage levels, capacitor is connected to the load. In this topology, for producing seven levels of voltage, capacitor must be controlled at  $V_{dc}/2$ . For clarification, we assume that the voltage source is equal to 2E; consequently, the voltage of the capacitor must be regulated at E. As a result, seven levels of output voltage are equal to +3E, +2E, +E, 0, -E,-2E,-3E. In this topology, in each cell (H-bridge cell), the switches which are in a vertical direction are complimentary; therefore,  $S_2 = \overline{S_1}$ ,  $S_4 = \overline{S_3}$ ,  $S_6 = \overline{S_5}$ , and  $S_8 = \overline{S_7}$ . To clarify, switch  $S_i = 0$  when the switch in off and  $S_i = 1$  when the switch is on and also  $V_c = V_{dc}/2$ .

Considering the above-mentioned information, it can be written that:

$$\begin{cases} V_1 = S_1 V_{dc} - S_3 V_{dc} \\ V_2 = S_5 V_{dc} - S_7 V_{dc} \end{cases} \qquad \qquad V_{an} = \left( S_1 - S_3 + \frac{S_5}{2} - \frac{S_7}{2} \right)$$

(1.8)

Figure 1.25 Single-phase Single DC source Cascade H-bridge (CHB) multilevel inverter

Table 1.9 illustrates the switching and capacitor state of CHB seven-level inverter. It can be seen that some redundant switching states exist in this table but these states are useful for balancing the capacitor voltage during charging and discharging. Figure 1.26 illustrates

equivalent of CHB seven-level inverter in each state, as shown in Table 1.9. It can be seen that states 2, 5, 8 do not affect capacitor since it is disconnected from voltage source and load. Moreover, States 3,4,6,7 play an important role for charging and discharging the capacitor. Furthermore, in States 1 and 9 the output is equal to the summation of  $V_c$  and  $V_{dc}$ . In these states, the capacitor is discharged firstly and then it is charged with reverse polarity, which is not desired. In this situation, larger capacitor is beneficial since it needs more time for discharging; as a result, it remains constant for a longer duration of time and in the next state, the capacitor will be charged again. In this topology, we can use PWM to manage these states easily.

Table 1.9 Switching states and Capacitor state of single-phase single-dc-source CHB cascaded 7-level inverter

| States | $S_1$ | <b>S</b> <sub>3</sub> | S <sub>5</sub> | <b>S</b> <sub>7</sub> | $V_1$     | $V_2$  | Van | Effect on capacitor(C) |

|--------|-------|-----------------------|----------------|-----------------------|-----------|--------|-----|------------------------|

| 1      | 1     | 0                     | 1              | 0                     | $+V_{dc}$ | $+V_c$ | +3E | Discharging            |

| 2      | 1     | 0                     | 1              | 1                     | $+V_{dc}$ | 0      | +2E | No effect              |

| 3      | 1     | 0                     | 0              | 1                     | $+V_{dc}$ | $-V_c$ | +E  | Charging               |

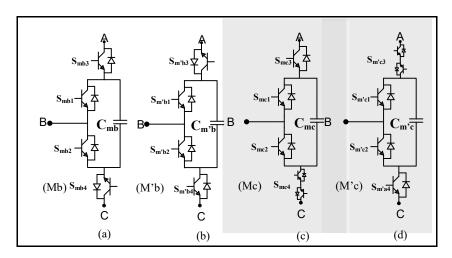

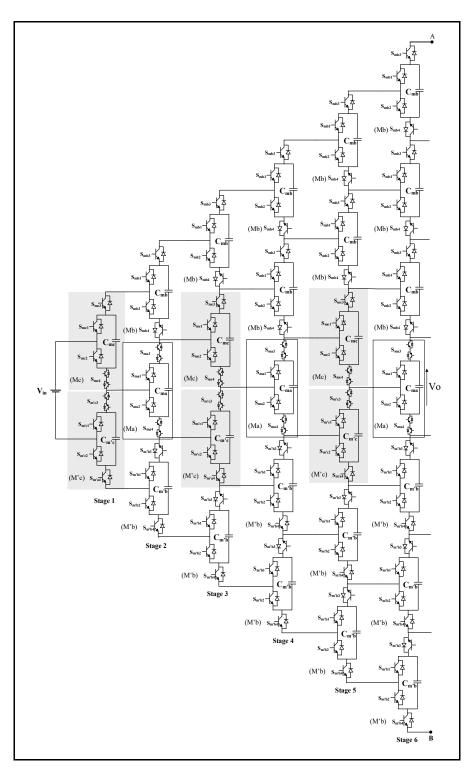

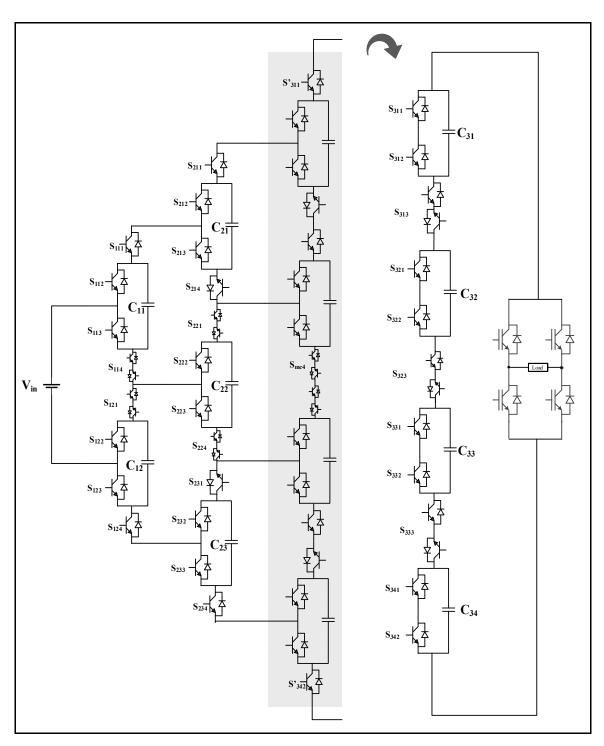

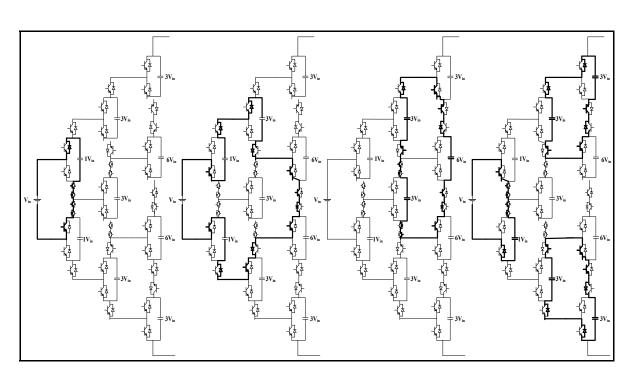

| 4      | 1     | 1                     | 1              | 0                     | 0         | $+V_c$ | +E  | Discharging            |