## A High-Voltage Multi-purpose On-the-fly Reconfigurable Half-bridge Gate Driver for GaN HEMTs in 0.18- $\mu$ m HV SOI CMOS Technology

by

#### Nam LY

THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT OF A MASTER'S DEGREE WITH THESIS IN ELECTRICAL ENGINEERING M.A.Sc.

MONTREAL, JUNE 22, 2020

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

## THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Nicolas Constantin, Thesis Supervisor Department of Electrical Engineering, École de Technologie Supérieure

Mr. Glenn Cowan, Co-supervisor Department of Electrical & Computer Engineering, Concordia University

Mr. Kamal Al-Haddad, President of the Board of Examiners Department of Electrical Engineering, École de Technologie Supérieure

Mr. Handy Fortin Blanchette, External Examiner Department of Electrical Engineering, École de Technologie Supérieure

# THIS THESIS WAS PRESENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC ON JUNE 19, 2020

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **ACKNOWLEDGEMENTS**

I would like to express the deepest appreciation to my supervisor, Professor Nicolas Constantin for his attitude and the substance of a genius. He continually and convincingly conveyed a spirit of adventure in regard to research and scholarship. Without his guidance and persistent help, this dissertation would not have been possible.

I am also grateful to Professor Glenn Cowan, my co-supervisor, for his useful comments, remarks and engagement through the learning process of this thesis. His questions throughout our weekly meetings were more than a guidance.

Professor Yves Blaquière's assistance with digital blocks of the project has been invaluable. His enthusiasm and generosity with his time as the project manager are greatly appreciated.

Thanks are owed to the CPIOS project team members. Nueraimaiti Aimaier's support on verification of one of the important digital blocks are appreciated. Special thanks are due to Abdul Hafiz Alameh and Ha Nguyen who have helped with layout trials of the chip and have been always available for any discussion.

My completion of this project could not have been accomplished without the support of the technicians and my fellow students of the Department of Electrical Engineering.

I am indebted to my wife for her love and support over the years. Her encouragement when the times got rough are much appreciated and duly noted. It was a great comfort and relief to know that she was willing to provide management of our household activities while I completed my work.

### Pilote de Grille pour Dispositifs GaN à Demi-pont Reconfigurable à Usages Multiples de Haute Tension en Technologie SOI CMOS HT 0.18- $\mu$ m

#### Nam LY

#### **RÉSUMÉ**

En raison de vitesses de commutation plus élevées, de faible résistance à l'état passant et de taille miniaturisée en comparaison avec des contreparties en silicium, l'utilisation de transistors de puissance à base de nitrure de gallium (GaN) est de plus en plus courante dans les circuits de puissances modernes. Avec des figures de mérite supérieures, les convertisseurs de puissance utilisant des dispositifs GaN peuvent fonctionner à des fréquences de commutation élevées. Cela se traduit par des dimensions plus petites, une efficacité supérieure et une réduction du coût du système. La redondance et la reconfigurabilité sont souhaitables dans les applications critiques pour la sécurité telles que les systèmes automobiles et aérospatiaux. Ces derniers fonctionnent dans des conditions difficiles nécessitant un niveau élevé de flexibilité et une grande fiabilité. Ce mémoire présente un circuit de pilotage de grille pour un tel système d'alimentation reconfigurable.

Destiné à être au coeur d'un système d'alimentation haute tension (HT) programmable et flexible, le pilote de grille présenté dans ce travail est capable de commander une large gamme de dispositifs GaN de différentes tailles. Cela est accompli en ayant un mécanisme configurable de vitesse de mis-à-on et mis-à-off. Cette fonctionnalité élimine le besoin de résistances de grille discrètes. Elle permet donc des conceptions de circuits plus denses, telles que l'intégration de système dans un boîtier (SiP - system-in-package). Dans un tel système les pilotes de grille, les dispositifs GaN et d'autres circuits intégrés de commande sont placés sur le même interposeur. La vitesse configurable de mis-à-on et de mis-à-off reconfigurable permet également de réduire les interférences électromagnétiques (EMI). Cela est important dans les applications critiques pour la sécurité. Une structure uniforme d'unités de commutation en demi-pont est proposée. Cette dernière permet une reconfigurabilité du fonctionnement du système avec une variété de topologies possibles à l'aide d'un grand nombre de cellules de commutation. Le pilote de grille exige un circuit de décalage de niveau de 200 V intégré. Ce circuit utilise une technique d'annulation de bruit en mode commun, ayant fait l'objet d'une étude approfondie. En utilisant cette technique dans une technologie HT SOI (silicium sur isolant), une immunité à une variation de bruit (CMTI) de 80 V/ns est obtenue. Le pilote de grille a un temps mort configurable allant de 5 ns à 60 ns. Ce temps mort configurable minimise les pertes dues à la conduction par mécanisme de «diode de corps» des transistors GaN pendant la période de conduction en roue libre pour différents profils de charge. Toutes les configurations sont programmées à travers un registre à décalage.

Le circuit de pilotage de grille a été fabriqué avec le procédé SOI de 200-V  $0.18-\mu m$  (XFAB XT018). Les résultats expérimentaux montrent que la puce peut piloter les transistors GaN ciblés de la plus petite à la plus grande taille aux vitesses de mis-à-on et mis-à-off souhaitées. Une vitesse de 1.46 / 1.18 ns de temps de montée / descente est atteinte. Le temps mort mesuré est de

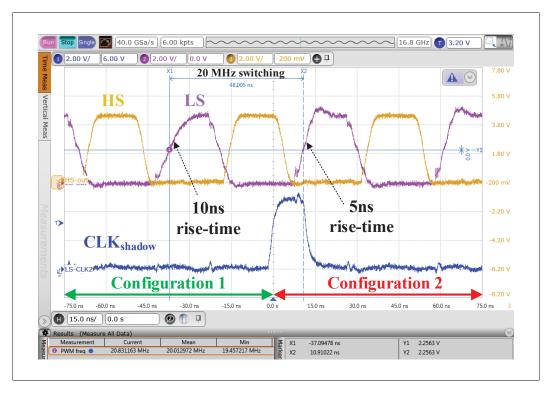

4,5 ns à 58 ns avec une tension d'entrée jusqu'à 86 V. Ces paramètres peuvent être reconfigurés à-chaud (on-the-fly) pendant que le circuit est en train de commuter à une fréquence jusqu'à 20 MHz. Ce travail contribue à l'avancement de la conception de pilotes de grille universels, en particulier pour les transistors GaN, et aux systèmes de puissance reconfigurables.

**Mots-clés:** Aérospatiale, CMOS, décalage de niveau, demi-pont, GaN, pilote de grille, reconfigurable

### A High-Voltage Multi-purpose On-the-fly Reconfigurable Half-bridge Gate Driver for GaN HEMTs in 0.18- $\mu$ m HV SOI CMOS Technology

#### Nam LY

#### **ABSTRACT**

Nowadays, the use of Gallium Nitride (GaN) power transistors in power electronics is common, due to higher switching speeds, lower on-resistance and smaller size compared to silicon counterparts. With superior figures of merit, power converters utilizing GaN devices can operate at high switching frequencies, which translates into smaller size, higher efficiency and lower system cost. Redundancy and reconfigurability are highly desirable for safety-critical applications such as automotive and aerospace systems that operate under harsh conditions and require a high degree of flexibility together with high reliability. This thesis presents a gate driver for such a reconfigurable power system.

Intended to be the core design of a programmable and flexible high-voltage (HV) power system, the gate driver in this work is capable of driving a wide range of GaN devices with different sizes by having independently configurable turn-on and turn-off resistance paths. This feature eliminates the need for discrete gate resistors and allows for higher density designs, such as System-in-Package integration (SiP) where the gate drivers, GaN devices and other control integrated circuits are placed on the same interposer. Reconfigurable driving strength also allows for electromagnetic interference (EMI) reduction, which is important in safetycritical applications. A uniform structure of half-bridge switching units is proposed, enabling reconfigurability in the operation of the system with a variety of possible topologies, out of a large array of switching cells. The gate driver requires a built-in 200-V level shifter, with common-mode noise cancellation technique, thoroughly investigated and migrated to HV SOI technology, which is immune against a 80-V/ns slew rate of fast switching GaN devices despite excessive parasitics in the process and the packaging technique employed. The gate driver has a configurable dead-time ranging from 5 ns to 60 ns that minimizes loss due to so-called "body diode" conduction of the GaN FETs during freewheeling for different load profiles. All the configurations are set via shift registers.

The gate driver has been fabricated in a 200-V  $0.18-\mu m$  silicon-on-insulator (SOI) process (XFAB XT018). Measurement results show that the chip can drive targeted GaN HEMTs from smallest to largest size at the desired turn-on and turn-off speeds, as fast as 1.46/1.18 ns of rise/fall-time. The measured dead-time is from 4.5 ns to 58 ns with an input voltage up to 86 V. The parameters can be reconfigured on-the-fly at a pulse width modulation switching frequency up to 20 MHz. This work contributes to the advancement of universal gate driver design, especially for GaN transistors, and toward reconfigurable power systems.

**Keywords:** Aerospace, CMOS, GaN, gate driver, half-bridge, level shifter, reconfigurable

#### TABLE OF CONTENTS

|       |         |                                           | Page |

|-------|---------|-------------------------------------------|------|

| INTRO | ODUCTI  | ION                                       | 1    |

| СНАР  | TER 1   | BACKGROUND                                | 4    |

| 1.1   |         | iction                                    |      |

| 1.1   |         | nentals of DC/DC converter                |      |

| 1.3   |         | rate Driver?                              |      |

| 1.4   | -       | Bandgap Semiconductor                     |      |

| 1.4   | 1.4.1   | Bandgap ( $E_g$ )                         |      |

|       | 1.4.2   | Critical field ( $E_{crit}$ )             |      |

|       | 1.4.3   | On-resistance $(R_{on})$                  |      |

|       | 1.4.4   | Commercial GaN HEMTs                      |      |

| 1.5   |         | ransistors - Attributes & Challenges      |      |

| 1.5   | 1.5.1   | Gate charge                               |      |

|       | 1.5.1   | Gate drive voltage                        |      |

|       | 1.5.2   | Reverse conduction                        |      |

|       | 1.5.4   | High-side driver supply                   |      |

|       | 1.5.4   |                                           |      |

|       | 1.5.5   | dV/dt immunity Ground bounce              |      |

| 1.6   |         | usion                                     |      |

| 1.0   | Conciu  | ISIOII                                    |      |

| CHAP  | TER 2   | GATE DRIVER FOR GAN - STATE-OF-THE-ART    | 23   |

| 2.1   | Introdu | iction                                    |      |

| 2.2   |         | ercial Gate Driver for GaN                |      |

| 2.3   |         | river for GaN in literature               |      |

| 2.4   | Conclu  | ision                                     | 29   |

|       |         |                                           |      |

| CHAP  | TER 3   | DESIGN OF THE GATE DRIVER                 | 31   |

| 3.1   | Introdu | action                                    | 31   |

| 3.2   | System  | Requirements                              | 31   |

| 3.3   | Techno  | ology Options                             | 34   |

| 3.4   | Block ( | Circuit Design                            | 35   |

|       | 3.4.1   | Output Driver Stage                       | 37   |

|       | 3.4.2   | Dead-time Controller                      | 45   |

|       | 3.4.3   | Level-shifter                             | 48   |

|       | 3.4.4   | Configuration registers                   | 52   |

| 3.5   | Chip la | yout & simulation                         | 57   |

|       | 3.5.1   | Gate driver layout                        |      |

|       | 3.5.2   | Post-layout simulation of the gate driver | 64   |

| 3.6   | Conclu  | sion                                      | 65   |

| CHAP  | TER 4     | CIRCUIT MEASUREMENTS | 69 |

|-------|-----------|----------------------|----|

| 4.1   | Introduc  | tion                 | 69 |

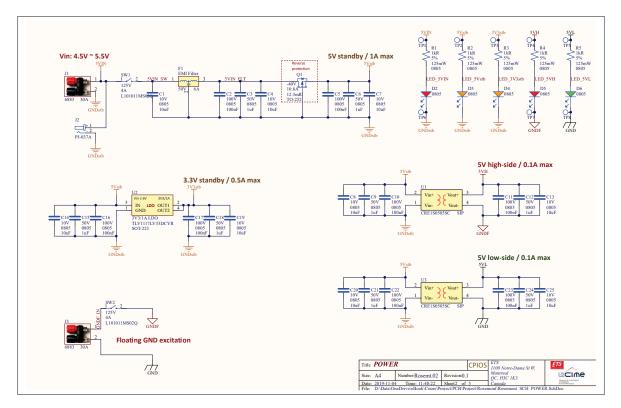

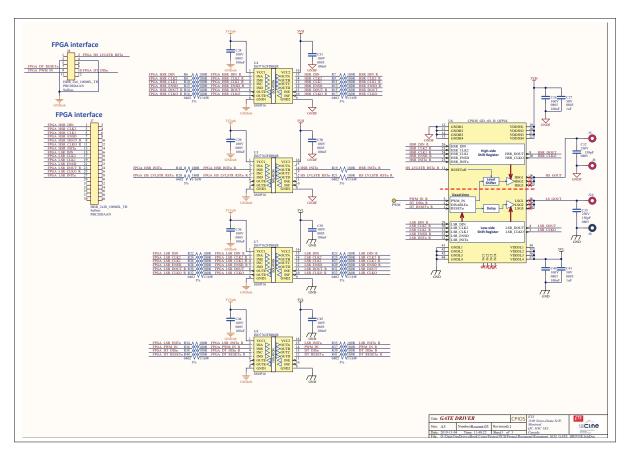

| 4.2   | Test Syst | tem Description      | 69 |

|       |           | ılts                 |    |

| 4.4   | Conclus   | ion                  | 71 |

| CONC  | LUSION    | AND RECOMMENDATIONS  | 75 |

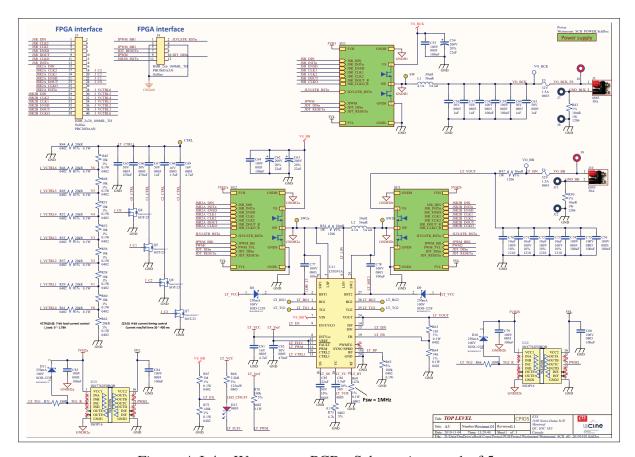

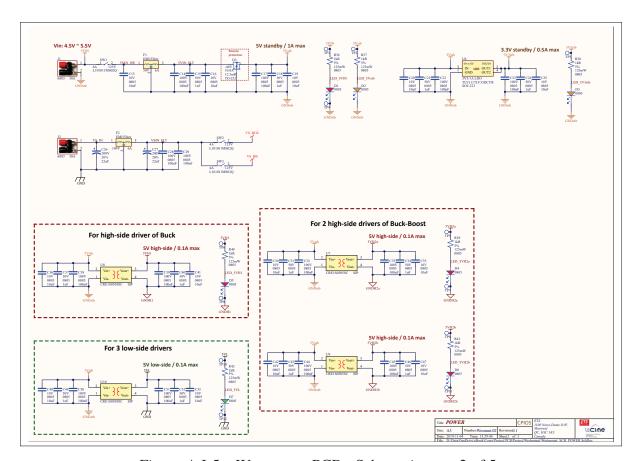

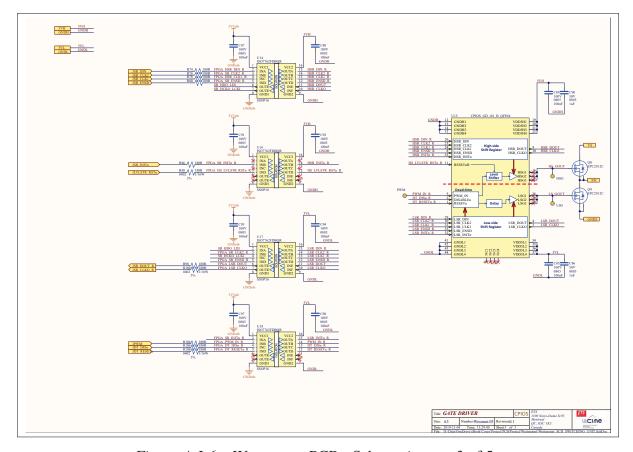

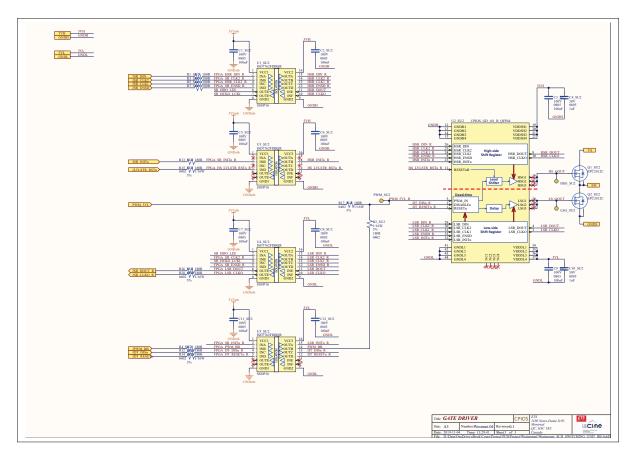

| APPEN | NDIX I    | PCB DESIGN           | 77 |

| REFER | RENCES    |                      | 85 |

#### LIST OF TABLES

|            | ]                                                               | Page |

|------------|-----------------------------------------------------------------|------|

| Table 1.1  | Non-isolated DC/DC converter topologies comparison              | 5    |

| Table 1.2  | Comparison of material properties                               | 10   |

| Table 1.3  | Commercial typical e-mode GaN discrete devices                  | 13   |

| Table 1.4  | Commercial typical e-mode GaN footprints                        | 14   |

| Table 1.5  | Gate charge components                                          | 15   |

| Table 2.1  | Typical commercial gate driver for GaN device in half-bridge    | 23   |

| Table 3.1  | CPIO-SiP power interfaces electrical specifications             | 33   |

| Table 3.2  | Targeted GaN FETs driven by the gate driver                     | 34   |

| Table 3.3  | Proposed Gate driver specifications                             | 34   |

| Table 3.4  | High voltage technologies                                       | 35   |

| Table 3.5  | Equivalent components of RLC tank for turn-on and turn-off path | 38   |

| Table 3.6  | Source current requirement across rise times and GaN FETs       | 41   |

| Table 3.7  | Chosen MP1 and MN1 sizes                                        | 43   |

| Table 3.8  | Drive strength configuration data                               | 44   |

| Table 3.9  | Dead-time configuration data                                    | 45   |

| Table 3.10 | Truth table of DT block                                         | 45   |

| Table 3.11 | $I_{diff}$ and $I_{com}$ of latch with different sizes          | 50   |

| Table 3.12 | Pin description of serial interface of the shift registers      | 55   |

| Table 3.13 | Data bit assignment of the shift registers                      | 55   |

| Table 3.14 | Pin description of the gate driver                              | 62   |

| Table 4.1  | Gate driver performance summary                                 | 72   |

#### LIST OF FIGURES

|             | Page                                                                                                                                          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

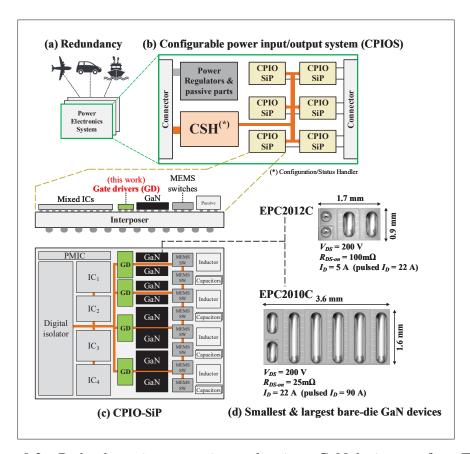

| Figure 0.1  | Power SiP in the literature                                                                                                                   |

| Figure 0.2  | Redundancy in automotive applications, GaN devices are from EPC 3                                                                             |

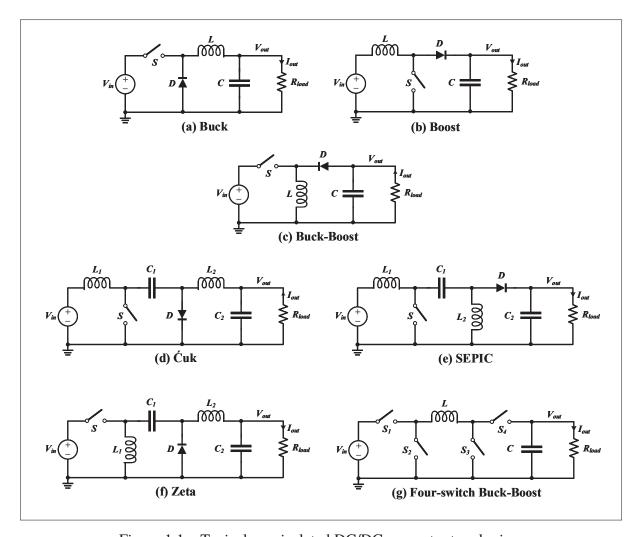

| Figure 1.1  | Typical non-isolated DC/DC converter topologies                                                                                               |

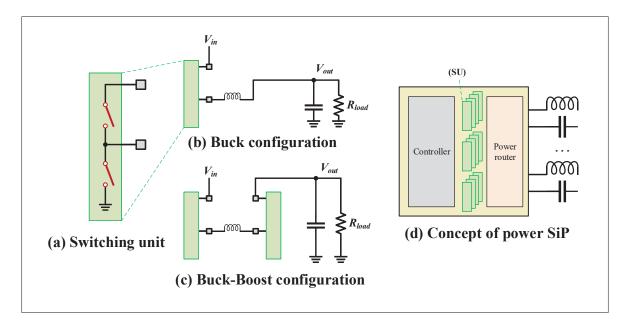

| Figure 1.2  | Switching unit and power SiP concept                                                                                                          |

| Figure 1.3  | Dead-time in half-bridge operation                                                                                                            |

| Figure 1.4  | The turn-on of a MOSFET driving a resistor                                                                                                    |

| Figure 1.5  | Theoretical $R_{on}$ vs. $V_{BD}$                                                                                                             |

| Figure 1.6  | An e-mode GaN FET driving an inductive load and different gate charge components of EPC2012C                                                  |

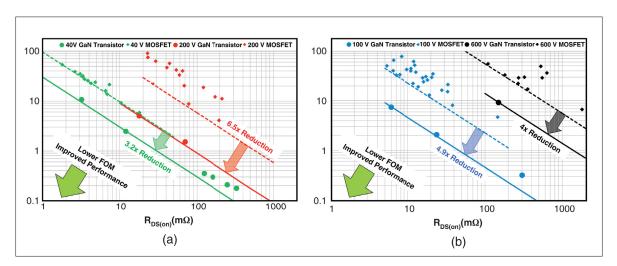

| Figure 1.7  | On-state resistance vs. total gate charge comparison for Si and GaN power devices showing (a) 40 V and 200 V, and (b) 100 V and 600 V devices |

| Figure 1.8  | $R_{on}$ vs. $V_{GS}$ of EPC2012C taken from its datasheet                                                                                    |

| Figure 1.9  | GaN reverse conduction                                                                                                                        |

| Figure 1.10 | Bootstrap circuit in half-bridge gate driver                                                                                                  |

| Figure 1.11 | Miller turn-on effect of dV/dt on a low-side transistor in off-state 20                                                                       |

| Figure 1.12 | Common source inductance causing ground bounce. (a) Gate drive impact and (b) simple solution for gate driver                                 |

| Figure 2.1  | Integrated GaN device with gate driver from EPC and Navitas Semiconductor                                                                     |

| Figure 2.2  | Half-bridge gate driver building blocks                                                                                                       |

| Figure 2.3  | $V_{SW}$ and dead-time                                                                                                                        |

| Figure 3.1  | CPIOS context of the gate driver                                                                                                              |

| Figure 3.2  | Configurable gate driver compatible with different GaN FET sizes 33                                                                           |

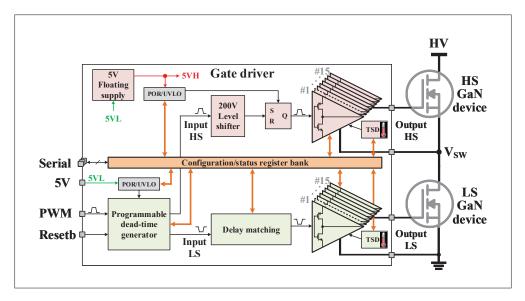

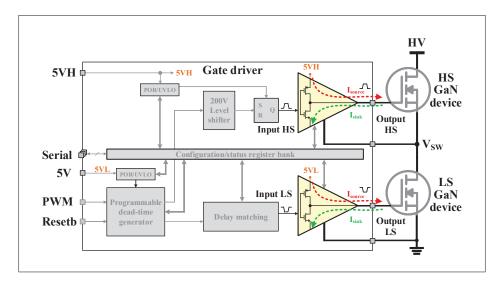

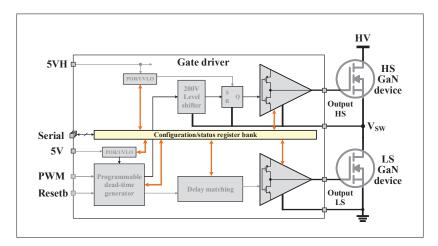

| Figure 3.3  | Proposed gate driver                                                                | 35 |

|-------------|-------------------------------------------------------------------------------------|----|

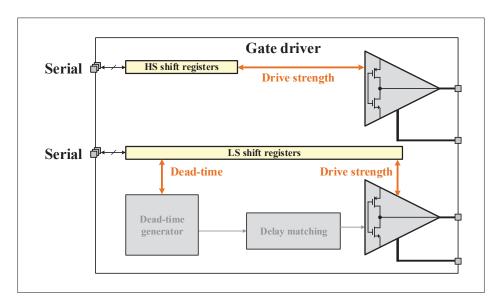

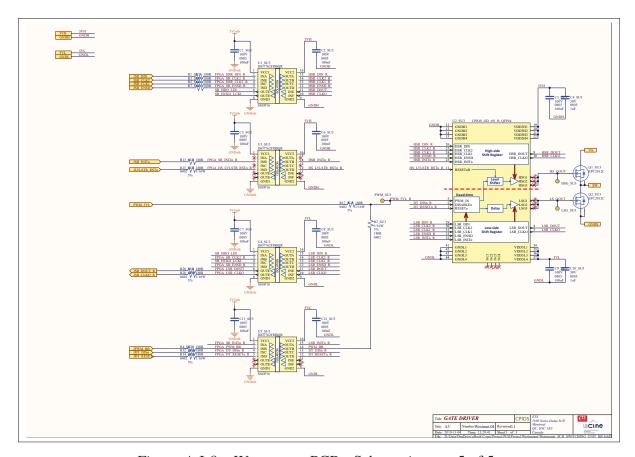

| Figure 3.4  | Half-bridge GaN gate driver block diagram                                           | 36 |

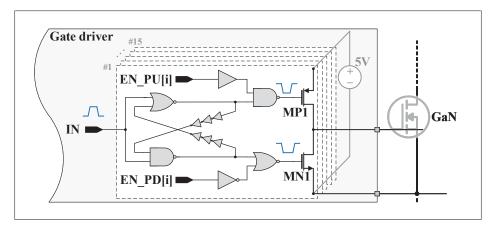

| Figure 3.5  | Output driver stage of the gate driver                                              | 37 |

| Figure 3.6  | Gate drive circuit with independent (a) turn-on and (b) turn-off path               | 37 |

| Figure 3.7  | Switching EPC2012C at (a) turn-on and (b) turn-off                                  | 39 |

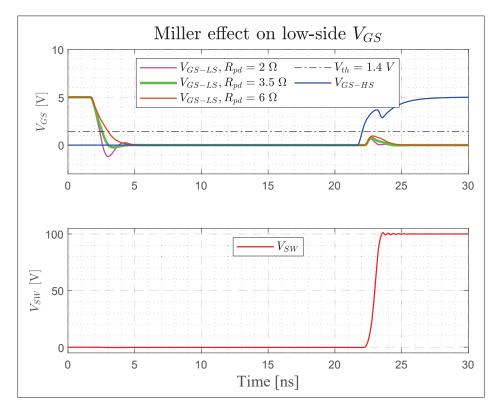

| Figure 3.8  | Miller effect on low-side GaN during off-state                                      | 39 |

| Figure 3.9  | Simulated waveforms under Miller effect                                             | 40 |

| Figure 3.10 | Zoomed waveforms of $V_{GS-LS}$ in Figure 3.9                                       | 40 |

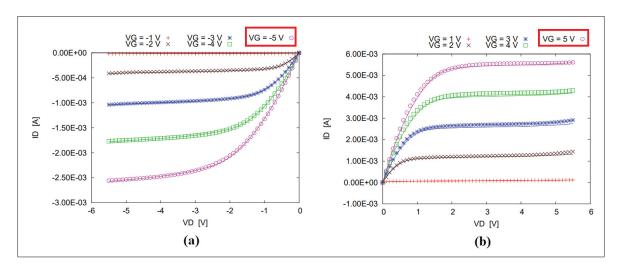

| Figure 3.11 | Gate charge, rise time and source current relationship                              | 42 |

| Figure 3.12 | Output stage of the gate driver                                                     | 42 |

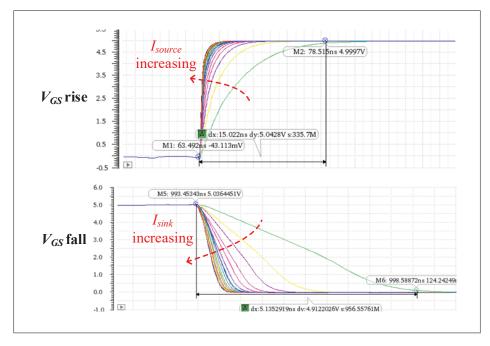

| Figure 3.13 | Characteristics curves of (a) pe5 and (b) ne5 at W/L = 10/0.5 um in XFAB XT018      | 43 |

| Figure 3.14 | Post-layout simulation of the buffer driving EPC2012C with 15 drive strength levels | 44 |

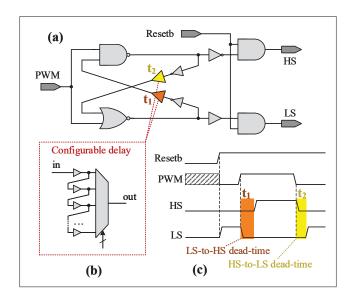

| Figure 3.15 | Dead-time generator of the gate driver                                              | 46 |

| Figure 3.16 | Dead-time generator design                                                          | 46 |

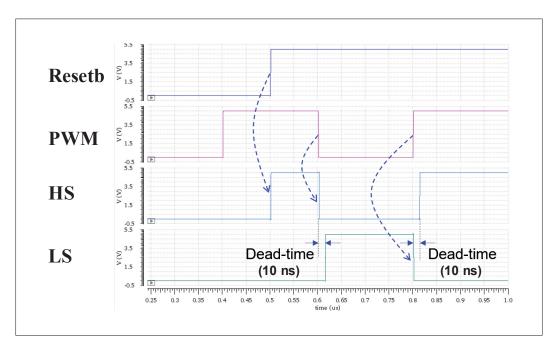

| Figure 3.17 | Dead-time behaviour simulation at DT = 10 ns                                        | 47 |

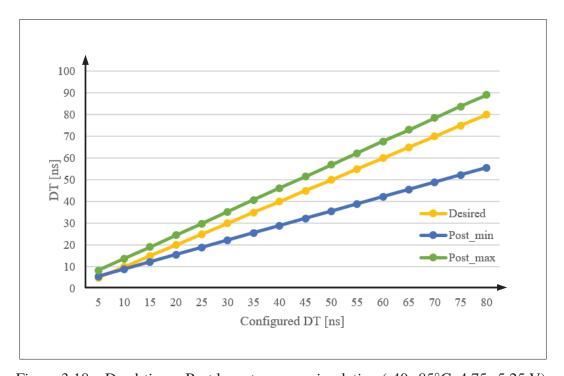

| Figure 3.18 | Dead-time - Post layout corners simulation (-40–85 $^{\circ}$ C, 4.75–5.25 V) .     | 47 |

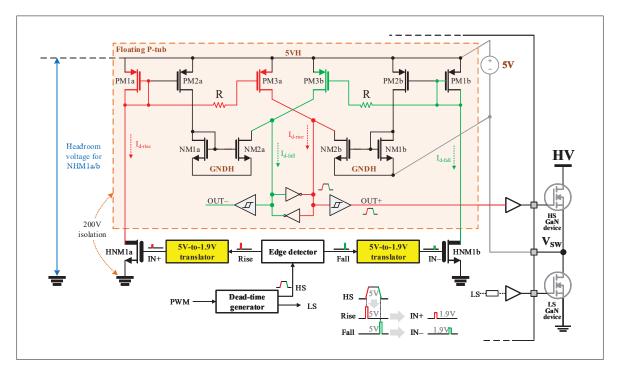

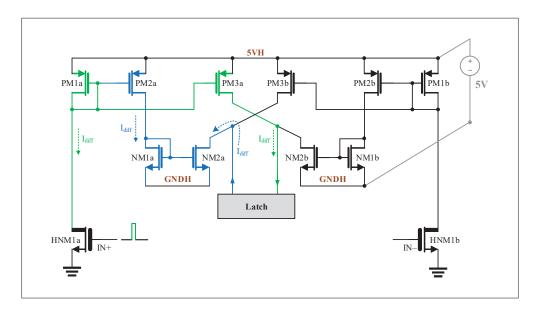

| Figure 3.19 | Level-shifter of the gate driver                                                    | 48 |

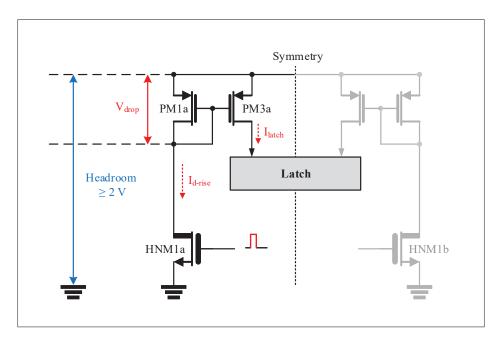

| Figure 3.20 | Level-shifter design                                                                | 49 |

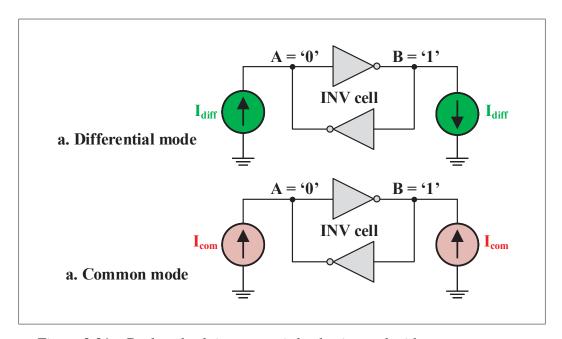

| Figure 3.21 | Back-to-back inverter pair latch triggered with current sources                     | 50 |

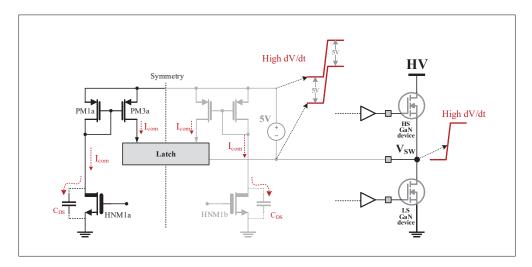

| Figure 3.22 | Mechanism of common-mode current                                                    | 51 |

| Figure 3.23 | Mechanism of differential-mode current                                              | 51 |

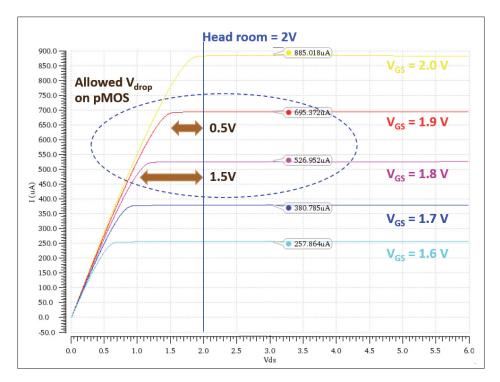

| Figure 3.24 | Sizing diode-connected pMOS                                                         | 52 |

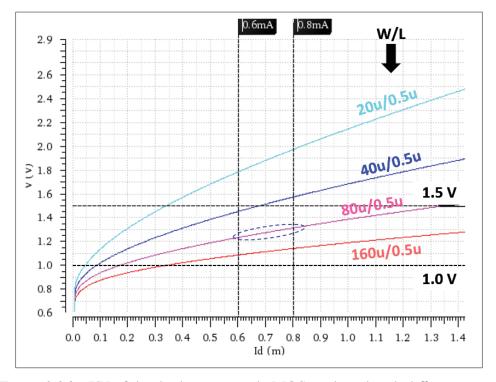

| Figure 3.25 | I/V characteristics of HV nMOS ( $50\mu$ m/ $1\mu$ m) is plotted with different $V_{GS}$                 | 53 |

|-------------|----------------------------------------------------------------------------------------------------------|----|

| Figure 3.26 | I/V of the diode-connected pMOS is plotted with different sizes                                          | 53 |

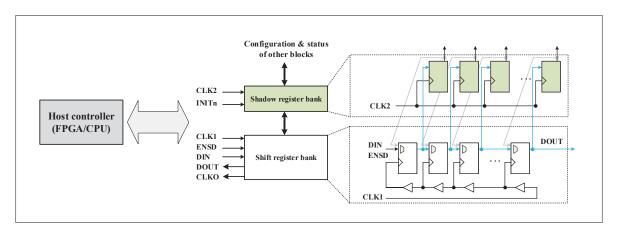

| Figure 3.27 | Configuration registers of the gate driver                                                               | 54 |

| Figure 3.28 | A configuration register set including a shift register and a shadow register                            | 54 |

| Figure 3.29 | Configuration registers distribution of the gate driver                                                  | 55 |

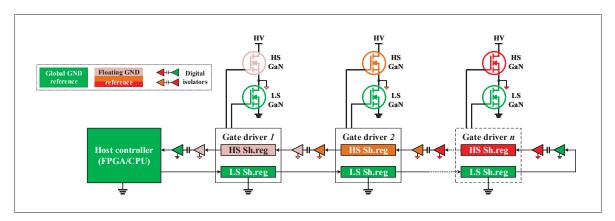

| Figure 3.30 | Daisy-chain of multiple shift registers in a system                                                      | 56 |

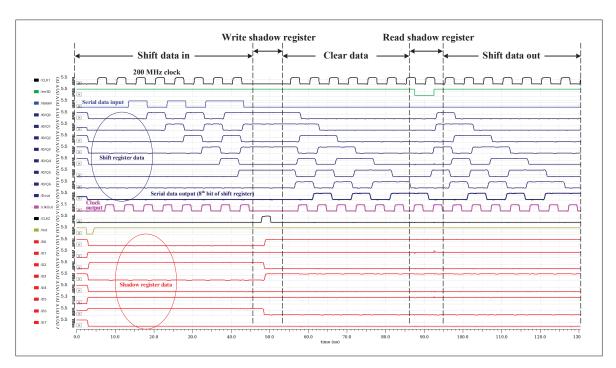

| Figure 3.31 | Four main operations of a shift/shadow register set                                                      | 57 |

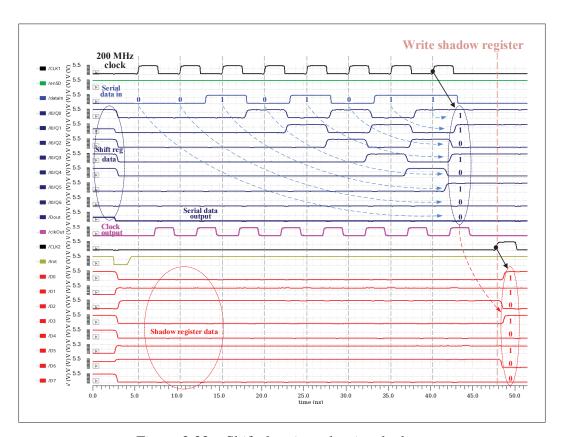

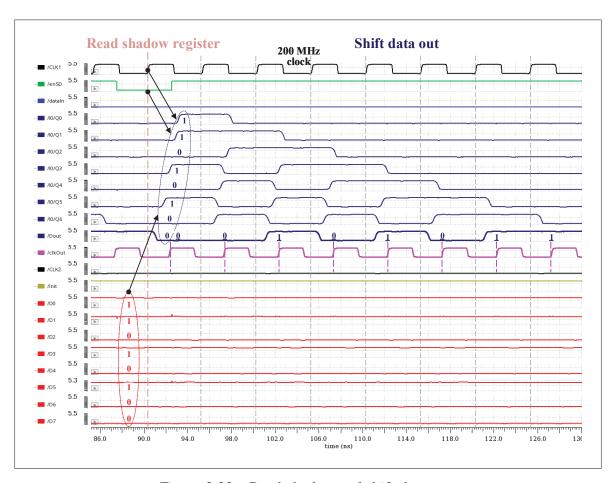

| Figure 3.32 | Shift-data-in and write-shadow                                                                           | 58 |

| Figure 3.33 | Read-shadow and shift-data-out                                                                           | 59 |

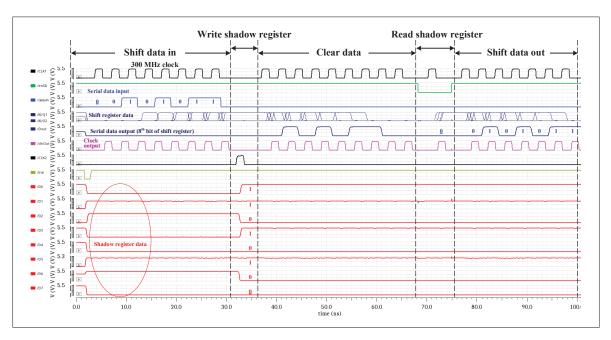

| Figure 3.34 | Post-layout simulation of 8-bit shift/shadow register at 300 MHz clock                                   | 60 |

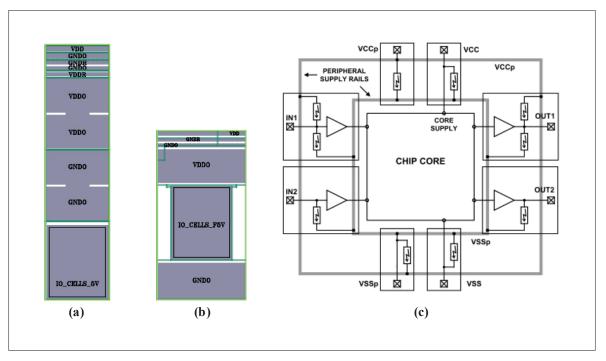

| Figure 3.35 | ESD pad cell for (a) pad-limited and (b) core-limited chip (c) General chip floorplan with ESD pad cells | 60 |

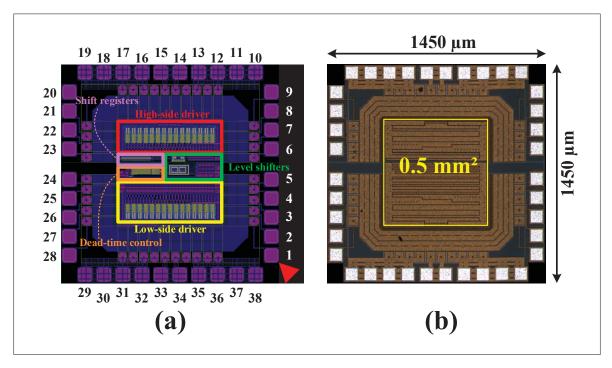

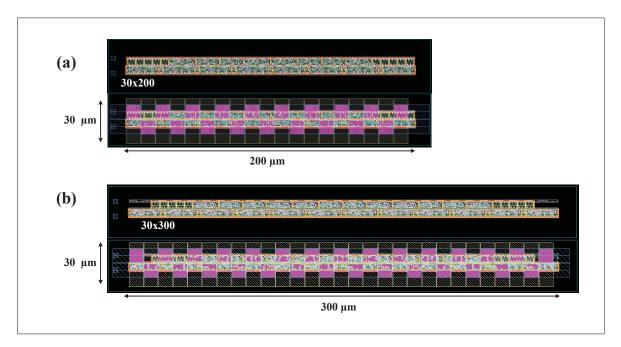

| Figure 3.36 | The gate driver (a) layout and (b) micrograph                                                            | 61 |

| Figure 3.37 | The layout of dead-time generator                                                                        | 61 |

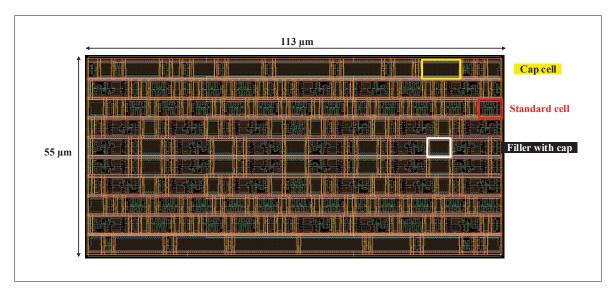

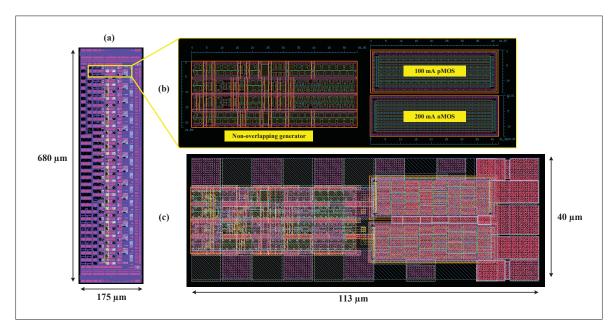

| Figure 3.38 | The layout of (a) output driver. One buffer slice (b) placement and (c) routing                          | 63 |

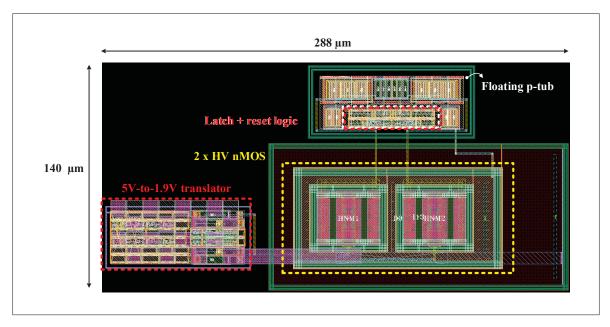

| Figure 3.39 | The layout of level-shifter group                                                                        | 63 |

| Figure 3.40 | The layout of configuration registers (a) 8-bit for HS and (b) 12-bit for LS                             | 64 |

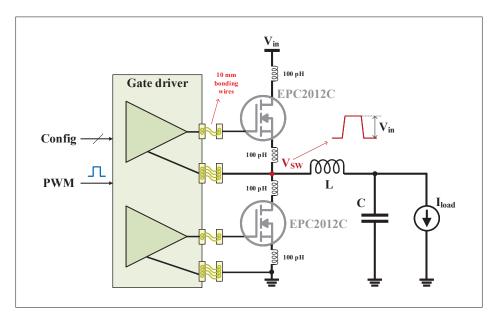

| Figure 3.41 | The test bench schematic of the gate driver                                                              | 65 |

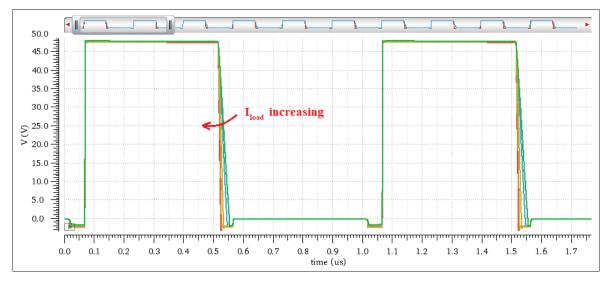

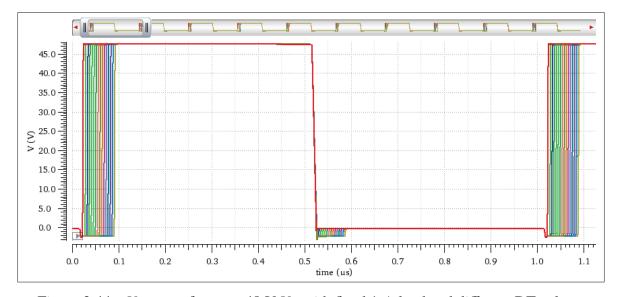

| Figure 3.42 | $V_{SW}$ waveforms at 48-V $V_{in}$ with fixed 50-ns DT and different load current values                | 65 |

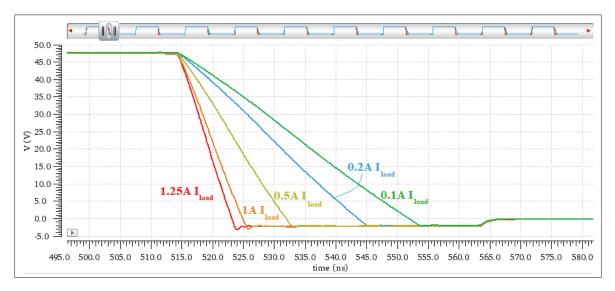

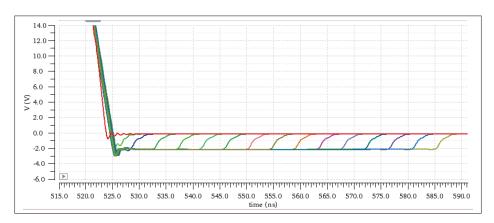

| Figure 3.43 | Zoomed falling edge of $V_{SW}$ in Figure 3.42                                                           | 66 |

| Figure 3.44 | $V_{SW}$ waveforms at 48-V $V_{in}$ with fixed 1-A load and different DT values                          | 66 |

|             |                                                                                                          |    |

#### XVIII

| Figure 3.45 | Zoomed falling edge of $V_{SW}$ in Figure 3.44                    | . 67 |

|-------------|-------------------------------------------------------------------|------|

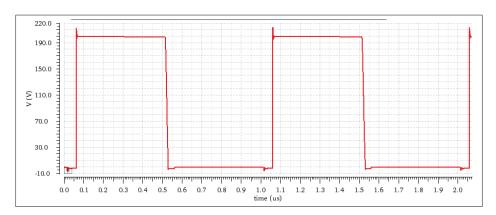

| Figure 3.46 | $V_{SW}$ waveforms at 200-V $V_{in}$ with 1-A load and 50-ns DT   | . 67 |

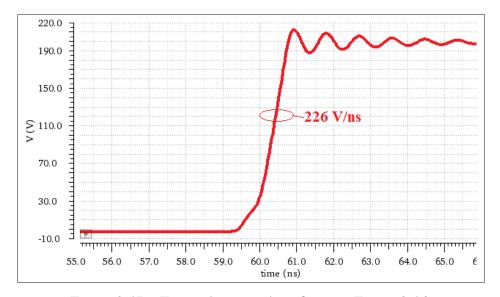

| Figure 3.47 | Zoomed rising edge of $V_{SW}$ in Figure 3.46                     | . 67 |

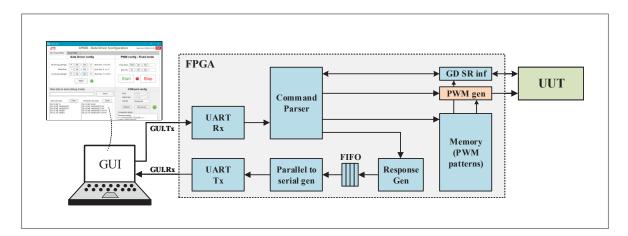

| Figure 4.1  | Test-bench diagram                                                | . 69 |

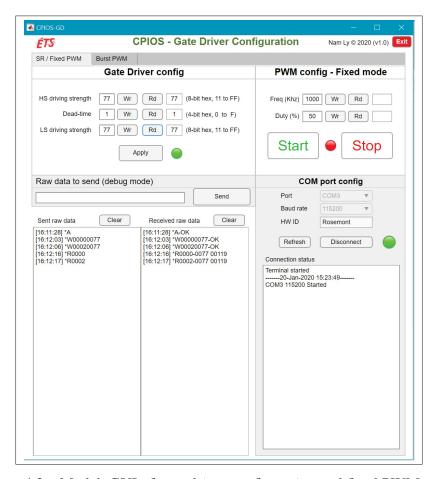

| Figure 4.2  | Matlab GUI of gate driver configuration and fixed PWM mode        | . 70 |

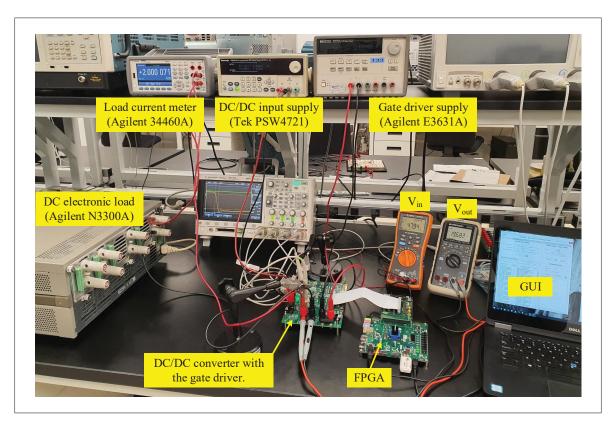

| Figure 4.3  | Test-bench of open-loop buck converter built with the gate driver | . 71 |

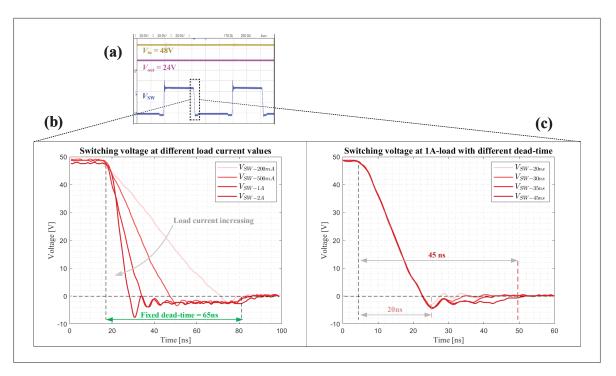

| Figure 4.4  | Switching node waveform with different dead-time values           | . 72 |

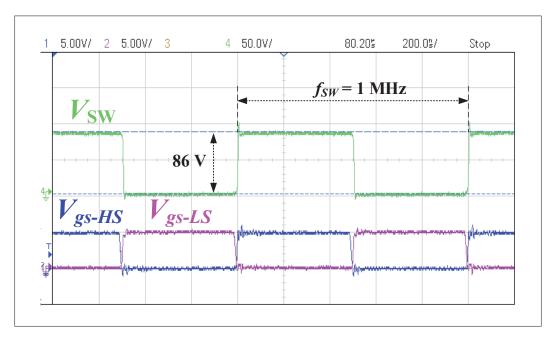

| Figure 4.5  | Switching at 1 MHz and 86 V input                                 | . 73 |

| Figure 4.6  | On-the-fly configuration of drive strength                        | . 73 |

#### LIST OF ABBREVIATIONS

BJT Bipolar Junction Transistor

CMOS Complementary Metal Oxide Semiconductor

CMTI Common-mode Transient Immunity

CPIOS Configurable integrated Power Input/Output System

CPU Central Processing Unit

DT Dead-time

ÉTS École de Technologie Supérieure

FET Field Effect Transistor

FPGA Field-Programmable Gate Array

GaN Gallium Nitride

HEMTs High Electron Mobility Transistors

HS High-side

HW Hardware

IC Integrated circuit

IGBT Insulated Gate Bipolar Transistor

LS Low-side

MCU Microcontroller Unit

nMOS N-channel Metal Oxide Semiconductor

PCB Printed Circuit Board

PD Pull-down

PMIC Power Management Integrated Circuit

pMOS P-channel Metal Oxide Semiconductor

PU Pull-up

PVT Process Voltage Temperature

SiC Silicon Carbide

SW Switching

WBG Wide Bandgap

#### LIST OF SYMBOLS AND UNITS OF MEASUREMENTS

A ampère

mA mili-ampère

$\mu$ A micro-ampère

nA nano-ampère

V volt

mV mili-volt

$\mu V$  micro-volt

nV nano-volt

W watt

mW mili-watt

$\mu W$  micro-watt

nW nano-watt

s second

ms mili-second

$\mu$ s micro-second

ns nano-second

#### INTRODUCTION

#### Motivation

In 72 years since the first transistor came to life (Riordan, 2004) and more than 60 years of integrated circuit (IC) history (Moore, 2006), the computer has transformed from house form-factor into palm size. That has been a fantastic time where all aspects of society have been impacted with the modernization thanks to these two moments in history. Processing and communication systems have become more and more sophisticated, especially in aerospace and automotive applications. In safety-critical applications, such as fly-by-wire and actuator control in aircraft, some parts are duplicated, triplicated or even quadrupled according to desired fault probability (Patton, 1991). The redundancy obviously increases system cost, size and weight. More functionalities and features implemented demand higher integration to diminish or at least retain system size.

Figure 0.1 Power SiP in the literature

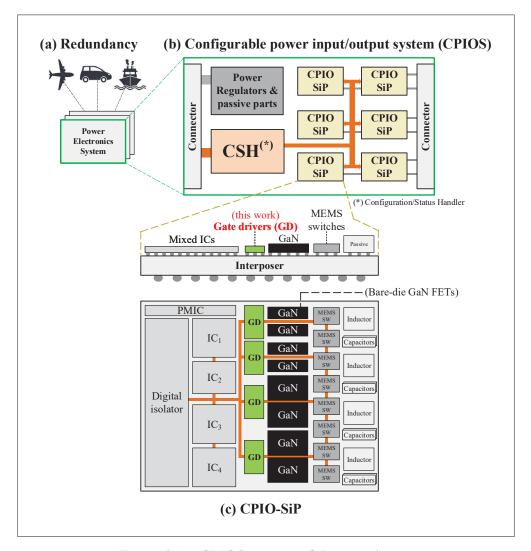

Power electronic circuits, occupying a large portion of the volume of a power supply, have been partially shrunk by introducing power semiconductor modules (Lee *et al.*, 2002). Other integrated components such as inductors, transformers, capacitors and control circuits require each a dedicated technology (Thomas *et al.*, 2018; Zhuo *et al.*, 2019; Jia & Gu, 2018; Wang *et al.*, 2018). The sub-system integration thus leads to a heterogeneous system or system-in-package (SiP) as illustrated in Figure 0.1.

Nowadays, wide bandgap (WBG) transistors are commonly used in power electronics due to superior figures of merit (FOM) which exceed the electrical boundary of silicon counterparts (Millán *et al.*, 2014). Furthermore, the reliability of silicon carbide (SiC) and gallium nitride (GaN) devices, the two mature WBG technologies, has been significantly improved over the last few years (Bindra, 2015b). GaN-based devices are suitable for 600-V range while SiC transistors are the candidates for kV range applications (Bindra, 2015a). These reasons make GaN high electron mobility transistor (HEMT) the best candidate as the power switch for a <200-V configurable power input/output system (CPIOS) (Figure 0.2b) for, but not limited to, aerospace applications. This CPIOS aims at shrinking overall system volume by replacing bulky power electronic parts with multiple configurable power SiPs (Figure 0.2c). Smaller system size relaxes the physical constraints associated with redundancy.

#### **Towards the Reconfigurable Power System**

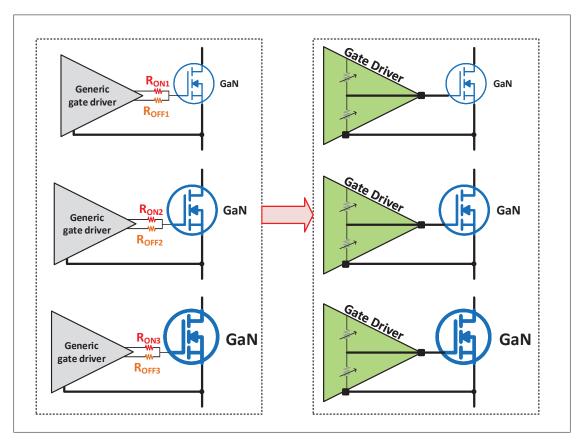

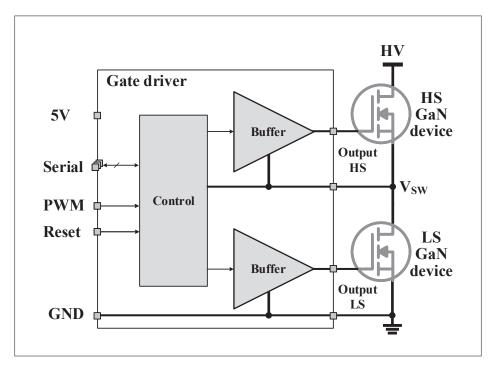

As an important part of the CPIO-SiP, the gate driver in this work is designed to be universal, i.e. capable of driving a range of commercial bare-die GaN devices of different sizes (Figure 0.2d) without the need of hardware change or external gate resistor. Thus, it can be used with appropriate GaN devices per output electrical specification for the optimum SiP size and efficiency. The gate driver only needs to be placed close to the GaN transistors that it drives and the settings are handled by the configuration/status handler (CSH). The gate driver can drive a single GaN device or two of them in half-bridge topology with a configurable dead-time (DT).

Figure 0.2 Redundancy in automotive applications, GaN devices are from EPC

In half-bridge configuration, the gate driver is robust against the high dV/dt slew rate of the switching (SW) node.

#### **Contributions to Research**

- The design, tape-out and testing of a versatile gate driver for GaN half-bridge (1–5.3 nC gate charge) with configurable speeds and dead-time with 226 V/ns CMTI.

- IEEE Publication:

- N. Ly, N. Aimaier, A. H. Alameh, Y. Blaquière, G. Cowan and N. G. Constantin (2020). A High Voltage Multi-Purpose On-the-fly Reconfigurable Half-Bridge Gate Driver for GaN HEMTs in 0.18-μm HV SOI CMOS Technology. 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS). (ACCEPTED)

#### **Overview of This Thesis**

This thesis consists of four chapters. Chapter 1 is an overview of gate driver concept, wide bandgap semiconductors and challenges of driving GaN transistors. A literature review of gate driver for GaN devices is discussed in Chapter 2. The design and simulation of the gate driver is outlined in Chapter 3 and its performance is examined and reported in Chapter 4.

#### **CHAPTER 1**

#### **BACKGROUND**

#### 1.1 Introduction

Before discussing the main topic, the gate driver design, it is important to have a relevant background. This chapter gives an overview of the concept of DC/DC converter, gate driver, wide bandgap semiconductors and the challenges of driving GaN transistors.

#### 1.2 Fundamentals of DC/DC converter

DC to DC converters are ubiquitous, from consumer electronics to electric vehicles. Such electronic devices often have multiple sub-circuits with their own supply level requirements different from the main input power which is either a built-in battery or an external supply. The supply of each sub-circuit can be either lower or higher than the main supply rail. Therefore, there are a lot of different types and topologies of DC/DC converter. They can be categorized into two main types: isolated and non-isolated.

Table 1.1 Non-isolated DC/DC converter topologies comparison

| Category                                                            | Topology               | Property                                          |

|---------------------------------------------------------------------|------------------------|---------------------------------------------------|

| Step-down                                                           | Buck                   | $ V_{out}  <  V_{in} $ , same polarity            |

| Step-up                                                             | Boost                  | $ V_{out}  >  V_{in} $ , same polarity            |

| Step-up/down ( $ V_{out} $ can be higher or lower than $ V_{in} $ ) | Buck-Boost             | $V_{out}$ < 0, simple structure & control         |

|                                                                     | Ćuk                    | $V_{out}$ < 0, low input current ripple           |

|                                                                     | SEPIC                  | $V_{out} > 0$ , low input current ripple          |

|                                                                     | Zeta                   | $V_{out} > 0$ , high input current ripple         |

|                                                                     | Four-switch buck-Boost | $V_{out} > 0$ , simple structure, complex control |

The isolated ones, as the name suggests, have their output isolated from the input with transformers. The benefits of this type are safety, noise isolation and floating output which are useful in some applications. However, the drawbacks of isolated DC/DC converters are big size, high cost and low efficiency. In the context of CPIO-SiP project, non-isolated type is preferable thanks to

its higher efficiency, lower cost due to low number of components, and especially smaller size that favours high density designs. Table 1.1 details the typical non-isolated DC/DC converter topologies which are depicted in Figure 1.1.

Figure 1.1 Typical non-isolated DC/DC converter topologies

In order to support the topology reconfigurability in CPIO-SiP, the half-bridge structure is chosen as the switching unit (SU). One SU can operate as either synchronous buck or synchronous boost typology. Two SUs can be combined to form a four-switch buck-boost as outlined in Figure 1.2. The power router can be realized using MEMS (Micro Electro-Mechanical System) switches. These MEMS switches do not need to switch fast but they must support high current in on-state and high voltage in off-state.

This solution has below advantages:

- 1. Uniform structure,

- 2. Scalable,

- 3. Covering both step-down and step-up with buck, boost and buck-boost topology.

Figure 1.2 Switching unit and power SiP concept

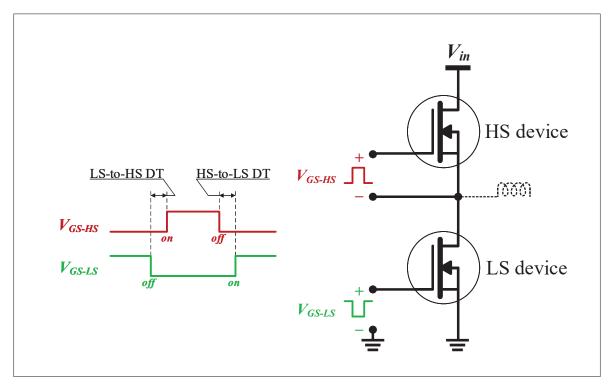

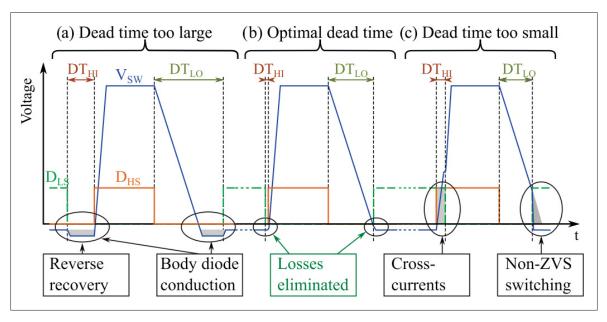

In half-bridge operation, if high-side (HS) and low-side (LS) transistors turn on at the same time, they will form a low impedance path which shorts out power rail to ground. This is called shoot-through or cross-conduction catastrophe which causes the power devices over heat resulting in reliability degradation or even permanent damage. Therefore, this incident must be avoided. To prevent this, there should be time margin from the moment one transistor is off to the moment the other transistor is ON. This time margin is called dead-time (DT) and described in Figure 1.3. Depending on applications and electrical specifications, DT can range from nanoseconds to milliseconds.

Figure 1.3 Dead-time in half-bridge operation

#### 1.3 Why Gate Driver?

Before the 1980s, the world of solid-state circuits witnessed the golden era of bipolar transistors (BJT) after they had replaced the vacuum tubes in radio and television. The power BJTs were robust but had a low current gain (beta) of <10 (White, 2018). Thus, a 10-A on-state requires at least 1-A continuous base current. Furthermore, the turn-off of BJTs demands a negative base current to remove all base-emitter charge. The fast turn-off hence needs a large negative current. There had been works addressing this issue such as Baker clamp and other feedback techniques.

Since the 1980s, the MOSFETs had become more mature to replace the BTJs in power supplies as they have fast switching speed and required voltage drive instead of "base drive" current. In contrast to BJTs, MOSFETs do not require power input to maintain an ON or OFF-state. The gate capacitor, formed by the gate terminal, oxide layer and the active region, must be charged or discharged to switch the MOSFETs. The gate capacitor has to be charged to a certain required voltage, so-called threshold voltage ( $V_{th}$ ), for the MOSFET to be ON. Similarly, this charge

must be depleted to turn the transistor off. When switching, MOSFETs do not instantly transit between the non-conducting and the conducting state. In fact, the transition time is inversely proportional to the charge and discharge speed of the gate capacitor, the typical range is from nanoseconds to milliseconds depending on power ratings and applications.

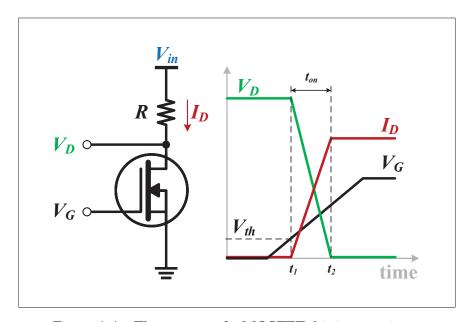

Let's examine an n-channel MOSFET driving a resistor in Figure 1.4. For simplicity, let's consider this an ideal MOSFET with zero on-state resistance. The applied voltage  $V_G$  to the gate rises from 0 V to surpass  $V_{th}$  to turn it ON. At  $t_1$ , when  $V_G$  equals  $V_{th}$ , the transistor starts to conduct and the drain current  $I_D$  starts to rise from 0 A while  $V_D$  starts to fall from  $V_{in}$ . At  $t_2$ , when  $V_D$  reaches 0 V,  $I_D$  reaches it max value. The period  $[t_1, t_2]$  is called turn-on time of the MOSFET. During this time interval, the MOSFET consumes an energy  $(E_{turn-on})$  as calculated in Equation 1.1. Since  $V_{in}$  and R are constant in the equation, the turn-on energy increases with  $t_{on}$ . Therefore, faster turn-on results in lower switching loss. During turn-off transition, the MOSFET also exhibits a similar switching loss that depends on  $t_{off}$ .

Figure 1.4 The turn-on of a MOSFET driving a resistor

$$E_{turn-on} = \int_{t_1}^{t_2} V_d(t) \cdot I_d(t) \cdot dt$$

$$= \frac{1}{6} \cdot V_{d(max)} \cdot I_{d(max)} \cdot (t_2 - t_1)$$

$$= \frac{1}{6} \cdot \frac{V_{in}^2}{R} \cdot t_{on}$$

$$(1.1)$$

In order to control the ON and OFF interval of MOSFETs, a new class of circuit was born: Gate driver. A gate driver usually refers to a power amplifier that gets a signal from a controller (e.g. MCU or FPGA) and accordingly drives the gate of a power MOSFET, IGBT, SiC or GaN transistor.

#### 1.4 Wide Bandgap Semiconductor

For over thirty years, innovations in power MOSFET technology and circuit topology have contributed to the improvement of power management efficiency and cost along with the increasing need for electrical power in human life. In the 21<sup>st</sup> century, the rate of improvement has slowed since the Si power MOSFET approaches its theoretical bounds. Hence, WBG power semiconductors have become gradually popular thanks to their superior characteristics versus Si counterparts.

Table 1.2 identifies the key electrical properties of three major semiconductor materials of the power electronics market.

Table 1.2 Comparison of material properties Taken from Lidow *et al.* (2015)

| Parameter                        |                      | Si   | GaN  | SiC  |

|----------------------------------|----------------------|------|------|------|

| Bandgap $(E_g)$                  | eV                   | 1.12 | 3.39 | 3.26 |

| Critical Field ( $E_{crit}$ )    | MV/cm                | 0.23 | 3.3  | 2.2  |

| Electron Mobility $(\mu_n)$      | cm <sup>2</sup> /V.s | 1400 | 1500 | 950  |

| Permittivity $(\epsilon_r)$      |                      | 11.8 | 9    | 9.7  |

| Thermal Conductivity $(\lambda)$ | W/cm.K               | 1.5  | 1.3  | 3.8  |

There are five key characteristics of a power device utilized in commercial power converters: conduction efficiency, switching efficiency, breakdown voltage, size and cost. The following sections will discuss the material characteristics and their relationship to the fore-mentioned power device characteristics in greater detail.

#### **1.4.1** Bandgap $(E_g)$

The semiconductor bandgap refers to the chemical bonds strength between the atoms in the lattice. It is more difficult for an electron to jump from an energy level to another in wider bandgap materials. Therefore, higher bandgap devices exhibit lower leakage currents, higher operating temperatures.

#### **1.4.2** Critical field $(E_{crit})$

Critical electric field is defined as the maximum field in one-sided junction at the onset of avalanche breakdown and is proportional to chemical bonds strength. Wider bandgap results in higher critical field and higher breakdown voltage  $(V_{BD})$ .

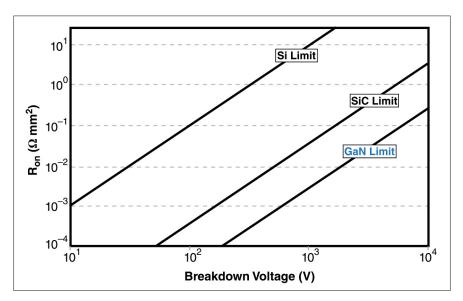

#### **1.4.3** On-resistance $(R_{on})$

The theoretical area-specific  $R_{on}$  of a field-effect transistor can be calculated as follow (Lidow *et al.*, 2015):

$$R_{on} = \frac{4 \cdot V_{BD}^2}{\mu_n \cdot \epsilon_0 \cdot \epsilon_r \cdot E_{crit}^3} \quad [\Omega \cdot mm^2]$$

(1.2)

Where  $\epsilon_0$  is the permittivity of a vacuum measured in farads per meter (8.854 ·  $10^{-12}$  F/m). Equation 1.2 can be plotted for the ideal semiconductor materials in Figure 1.5 for Si, SiC and GaN. GaN appears to yield the lowest  $R_{on}$  which translates into lowest conduction loss in power converters.

Figure 1.5 Theoretical  $R_{on}$  vs.  $V_{BD}$  Taken from Lidow *et al.* (2015)

Real devices do not have ideal structures, so they lie on the top part of their material limit line. It took more than thirty years in case of Si MOSFETs for the development, improvement and diminution of the gap from their theoretical limit (Lidow *et al.*, 2015).

#### 1.4.4 Commercial GaN HEMTs

There are two types of GaN HEMT: depletion-mode (d-mode) and enhancement-mode (e-mode). D-mode is normal-on and requires a negative  $V_{GS}$  to turn off. This requirement makes it ill-suited to DC/DC converters with the obvious risk of shoot-through current in half-bridges upon power up. In contrast, e-mode type is normally-off and has the same behaviour as n-channel MOSFETs, so this type is widely adopted. For this reason, e-mode GaN is in the scope of this thesis.

At the time this thesis is being written, there are many semiconductor companies showing their interest in GaN discrete components. Some of them have their products available on the market. The most emerging vendors are EPC, GaN systems, Infineon, Panasonic and VisIC. there are also various manufacturers doing research on GaN discrete device, such as HRL, Navitas, Exagan, Powdec, Sanken, etc.

| Vendor   | Part #     | $V_{DS-max}$ | $I_{D-max}$ | R <sub>on-max</sub> | $Q_{G-typ}$   | $Q_{OSS-typ}$ | Size mm            |

|----------|------------|--------------|-------------|---------------------|---------------|---------------|--------------------|

|          | EPC2036    | 100 V        | 1.7 A       | $73 m\Omega$        | 0.7 nC        | 3.9 nC        | $0.9 \times 0.9$   |

|          | EPC2052    | 100 V        | 8.2 A       | $13.5 m\Omega$      | 3.6 nC        | 13 <i>nC</i>  | $1.5 \times 1.5$   |

| EPC      | EPC2016C   | 100 V        | 18 A        | $16 m\Omega$        | 3.4 <i>nC</i> | 16 <i>nC</i>  | $2.1 \times 1.6$   |

|          | EPC2012C   | 200 V        | 5.0 A       | $100 m\Omega$       | 1.0 <i>nC</i> | 10 nC         | $1.7 \times 0.9$   |

|          | EPC2019    | 200 V        | 8.5 A       | $50 m\Omega$        | 1.8 <i>nC</i> | 18 <i>nC</i>  | $2.77 \times 0.95$ |

|          | EPC2010C   | 200 V        | 22 A        | $25 m\Omega$        | 3.7 nC        | 40 nC         | $3.6 \times 1.6$   |

| GaN      | GS-065-004 | 650 V        | 3.5 A       | $500 m\Omega$       | 0.7 nC        | 7.3 nC        | $5.0 \times 6.0$   |

| systems  | GS-065-011 | 650 V        | 11 A        | $150 m\Omega$       | 2.0 nC        | 20 nC         | $5.0 \times 6.0$   |

| Pana     | PGA26E34H  | 600 V        | 9.4 A       | $340 m\Omega$       | 1.0 nC        | 8.5 nC        | $4.0 \times 6.0$   |

| sonic    | PGA26E17B  | 600 V        | 15 A        | $175 m\Omega$       | 2.0 nC        | 17 <i>nC</i>  | $8.0 \times 8.0$   |

| Infineon | IGLD60R190 | 600 V        | 10 A        | $190 m\Omega$       | 3.2 nC        | 16 nC         | $8.0 \times 8.0$   |

| VisIC    | V22N65A    | 650 V        | 80 A        | $22 m\Omega$        | 41 nC         | 171 nC        | $18.6 \times 15.6$ |

Table 1.3 Commercial typical e-mode GaN discrete devices

Table 1.3 lists some GaN HEMTs that are available on the market. While most of the vendors make devices with the conventional package, Dual Flat No-lead (DFN), EPC and VisIC have their own unique footprint. VisIC parts support very high power whereas EPC ones favour lower power with higher density designs. Table 1.4 shows typical footprint options that are available on the market.

#### 1.5 GaN Transistors - Attributes & Challenges

Although e-mode GaN HEMTs have characteristics similar to n-channel MOSFETs, there are unique features of GaN HEMTs that circuit designers should understand to best control these fast switching transistors. The characteristics and associated challenges are discussed in the this section, focusing on the half-bridge topology which is the most commonly used topology in power electronics.

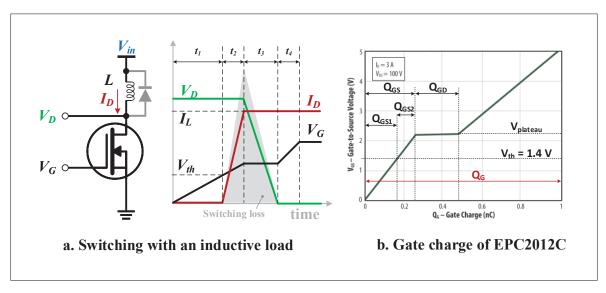

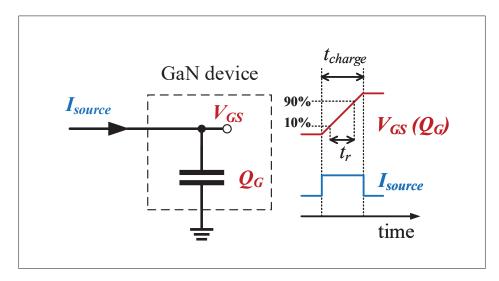

#### 1.5.1 Gate charge

Like nMOS, the e-mode GaN HEMTs are controlled by injecting or removing a required amount of charge from the gate. Figure 1.6a demonstrates a turn-on switching of a GaN transistor with an inductive load. This turn-on process consists of four intervals:  $(t_1)$  the charge needed to raise

Table 1.4 Commercial typical e-mode GaN footprints

| Vendor      | Footprint | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPC         | Bare-die  | 0.9x0.9 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GaN systems | DFN       | G506500 <sup>AL</sup><br>8ZCM (e <sup>3</sup> ) 5.0x6.0 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Panasonic   | DFN       | Perservice Company of Control of |

| Infineon    | DFN       | 8.0x8.0 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VisIC       | Custom    | V22N65AEF 061S 18.6x15.6 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

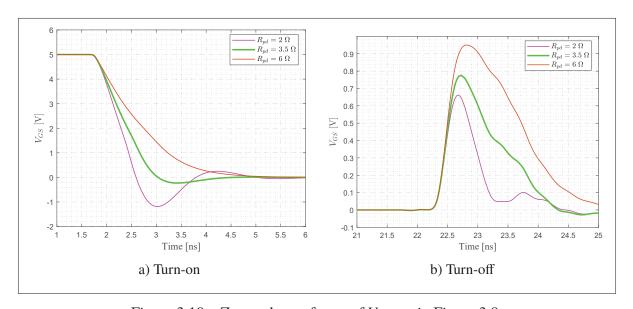

the gate to  $V_{th}$ ,  $(t_2)$  the charge required to complete the current rise time and for the gate to reach  $V_{plateau}$ ,  $(t_3)$  the charge required to complete the voltage fall time, and  $(t_4)$  the charge required to bring the gate to the desired steady-state voltage. Figure 1.6b depicts EPC2012C gate charge curve with various components that are defined in Table 1.5. These gate charge components correspond to above four time intervals  $(t_1, t_2, t_3 \text{ and } t_4)$ .

With the same gate driving circuit, a FET with smaller gate charge should have faster switching time compared to the one with higher gate charge, which means lower switching loss.

Figure 1.6 An e-mode GaN FET driving an inductive load and different gate charge components of EPC2012C

Table 1.5 Gate charge components

| Gate charge | Definition                                                                    |

|-------------|-------------------------------------------------------------------------------|

| component   |                                                                               |

| $Q_{GS1}$   | Charge required to increase gate voltage from zero to $V_{th}$ of the device. |

| $Q_{GS2}$   | Charge required to commute the device current.                                |

| $Q_{GS}$    | $Q_{GS1} + Q_{GS2}$                                                           |

| $Q_{GD}$    | Charge required to commute the device voltage, at which point the device      |

|             | enters the linear region                                                      |

| $Q_G$       | Total gate charge $(Q_G = Q_{GS} + Q_{GD})$ .                                 |

One of the FOMs commonly used to compare MOSFETs is the product  $R_{on} \times Q_G$ , smaller being better. This FOM can also be used to compare Si and GaN technologies, as plotted in Figure 1.7. First-generation GaN devices have at least 3x better FOM for the same  $V_{DS}$  rating, which makes them switch much faster. This, however can translate into severe ringings at switching nodes with parasitics. Therefore, higher level (PCB or SiP) design should have optimized parasitics.

Figure 1.7 On-state resistance vs. total gate charge comparison for Si and GaN power devices showing (a) 40 V and 200 V, and (b) 100 V and 600 V devices

Taken from Lidow *et al.* (2015)

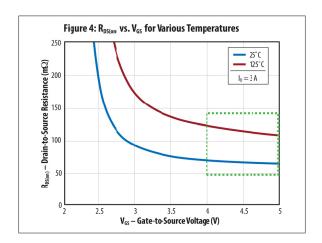

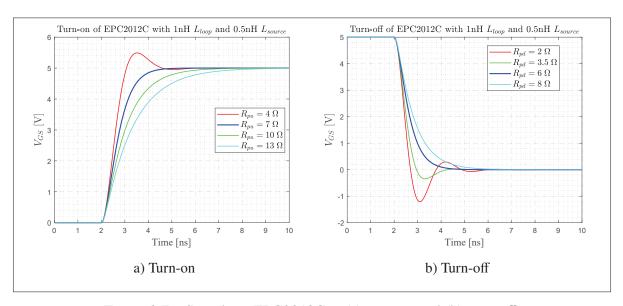

## 1.5.2 Gate drive voltage

Different technologies and different manufacturers have different maximum ratings. For e-mode GaN, such as the EPC2012C, the maximum  $V_{GS}$  is +6 V/-4 V. Exceeding this limit should be avoided, or the device will be damaged. For EPC2012C, the device  $R_{on}$  is specified in the datasheet at a recommended 5 V  $V_{GS}$ , which is 1 V below the absolute maximum rating. With very fast switching speed, care must be taken to prevent overshoot that may periodically bring  $V_{GS}$  above 6 V.

Figure 1.8 plots EPC2012C  $R_{on}$  across its  $V_{GS}$  at 3 A of drain current for the two temperature points: 25°C and 125°C. The rectangular dotted box in the figure marks the safe driving voltage range without significantly increasing its on-state resistance. This voltage range can be as low as 4 V. EPC also recommends keeping  $V_{GS-on}$  below 5.25 V to ensure a safe margin from 6 V. This requirement makes the gate driver design for GaN challenging due to tight  $V_{GS}$  tolerance in comparison with 6-10 V  $V_{GS-on}$  and  $\pm 20$  V  $V_{GS-max}$  of Si power transistors.

Figure 1.8  $R_{on}$  vs.  $V_{GS}$  of EPC2012C taken from its datasheet

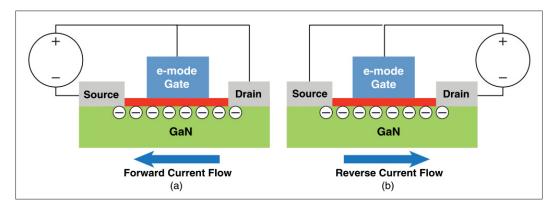

#### 1.5.3 Reverse conduction

In a transistor's physical structure, its body diode provides a path whenever reverse current is needed. However, in a HEMT's physical structure, there is no such p-n junction. The mechanism of reverse conduction is completely different. The drain and source are symmetrical as depicted in Figure 1.9. When the GaN device is in off-state (shorted gate-source as shown in Figure 1.9b), if the gate-drain voltage is higher than  $V_{th}$ , it will conduct current from source (virtual drain) to drain (virtual source) in a diode-connected fashion. The reverse voltage,  $V_{SD}$ , in this situation is higher than  $V_{th}$ , ranging from 1 to 2 V. This value is about double the one of MOSFET body diode.

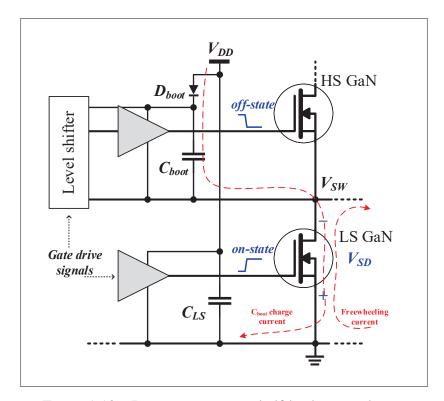

## 1.5.4 High-side driver supply

With half-bridge topology, the HS gate driver requires a floating supply. The simplest solution for this is using a bootstrap capacitor and a diode with a high reverse blocking voltage as illustrated in Figure 1.10. Decoupling capacitor  $C_{boot}$ , the bootstrap capacitor, acts as the energy storage for the HS logic circuitry supply.

At power-up,  $C_{boot}$  needs to be charged to  $V_{DD}$  value for the HS buffer to operate properly. This can only be done by turning on the LS GaN device to ground  $V_{SW}$ . The supply  $V_{DD}$  then charges

Figure 1.9 GaN reverse conduction Taken from Lidow *et al.* (2015)

Figure 1.10 Bootstrap circuit in half-bridge gate driver

$C_{boot}$  via  $D_{boot}$ . When HS buffer is turned on,  $C_{boot}$  is isolated from  $V_{DD}$  by  $D_{boot}$  and acts as the floating supply for the HS circuit.

Practically,  $C_{boot}$  is charged to  $V_{DD}$  minus the voltage drop across  $D_{boot}$ . This value is apparently lower than  $V_{DD}$ . However, when the half-bridge operates with a certain load current at the output,  $V_{SW}$  can swing negative during freewheeling current condition. The  $C_{boot}$ , in this situation, is charged up to  $V_{DD}$  minus forward voltage of  $D_{boot}$  and plus  $V_{SD}$ , the reverse conduction voltage of LS GaN device discussed in the previous section, which altogether could exceed 6 V. This overcharge issue can be avoided using the following common solutions:

- 1. Reduce dead-time resulting minimizing diode conduction time to nanoseconds range.

- 2. Reduce  $V_{SD}$  by adding an external Schottly diode across the LS GaN device.

- 3. Add a regulator (e.g. LDO) or a clamping circuit (e.g. Zener diode) after  $D_{boot}$ .

- 4. Replace bootstrap circuit with a charge pump, allowing the HS device to stay ON for a long time.

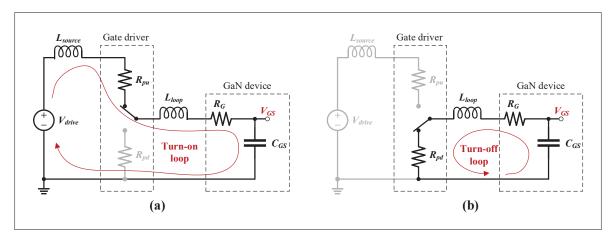

## 1.5.5 dV/dt immunity

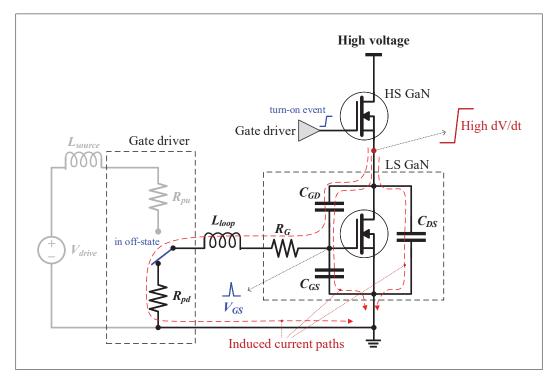

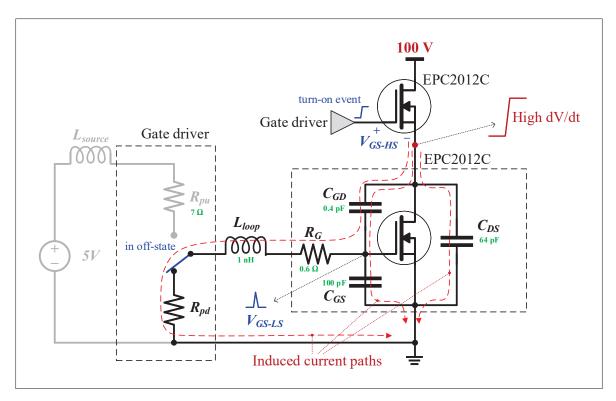

A high voltage slew rate (dV/dt) on the drain of an off-state GaN device is a phenomenon worth investigating. Let's examine the circuit depicted in Figure 1.11 where the LS GaN is in off-state and the HS GaN starts to turn on. The high switching speed of the HS GaN results in a high dV/dt on the drain of LS GaN. This high voltage slew rate charges up all parasitics seen by this node to ground including  $C_{DS}$ ,  $C_{GD}$  in series with a parallel circuit composed of  $C_{GS}$  and the turn-off path  $(R_G + L_{loop} + R_{pd})$ . The charge current though  $C_{GS}$  will result in a positive  $V_{GS}$  transient. If not well addressed, this induced  $V_{GS}$  could exceed  $V_{th}$  and accidentally turn on the LS GaN HEMT. This is known as the Miller turn-on effect and, if the duration is long enough, it may cause a catastrophic failure of the transistor and therefore must be prevented. The next chapter will discuss more about this as a criteria of the design.

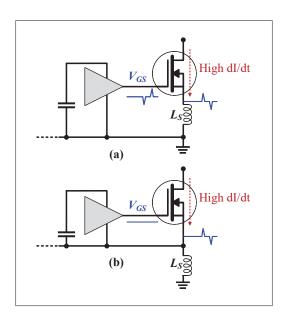

#### 1.5.6 Ground bounce

Ground bounce is a well-known phenomenon in power electronics, where parasitics inductance resonates with high dI/dt. As depicted in Figure 1.12a,  $L_S$  exhibits a high dI/dt switching and generates voltage spikes. The gate drive signal is then perturbed and could accidentally turn on

Figure 1.11 Miller turn-on effect of dV/dt on a low-side transistor in off-state

Figure 1.12 Common source inductance causing ground bounce.

(a) Gate drive impact and (b) simple solution for gate driver

or off the GaN device. One simple solution to this issue is to minimize the inductance within the loop comprising the Gate-Source terminals of the GaN device and the associated logic as in Figure 1.12b.

#### 1.6 Conclusion

In this CPIO-SiP project, the power interface has to drive a load up to 1.25 A and withstand 84 V transients for hundreds of milliseconds. It must also survive under 150 V transients induced by lightning strikes (the voltage after being filtered) during its off-state. Therefore the GaN device candidates should have the following characteristics:

- 1. Favourable to high density integration in the context of SiP.

- 2.  $I_D > 1.25$  A.

- 3.  $V_{DS} > 150 \text{ V}.$

The above requirements lead to the choice of EPC devices as the candidates of power switches used in CPIO-SiP. The SiP power stage is also scalable with the uniform SU of half-bridge. A light & low-voltage load can be driven by a buck converter with small GaN half-bridge while a current-controlled load with complex voltage profile can be supplied with a buck-boost stage. For this reason, a range of GaN device sizes are considered in this project.

With the background on the concept of gate driver, wide bandgap semiconductors and the challenges of driving GaN transistors, a review of state-of-the-art gate drivers will be given in the next chapter before entering into the detail of the proposed gate driver design.

### **CHAPTER 2**

### GATE DRIVER FOR GAN - STATE-OF-THE-ART

#### 2.1 Introduction

This chapter presents a literature review of commercial and state-of-the-art gate drivers for GaN devices, especially in half-bridge topology. This review helps converge towards a versatile and reconfigurable architecture in the proposed gate driver.

#### 2.2 Commercial Gate Driver for GaN

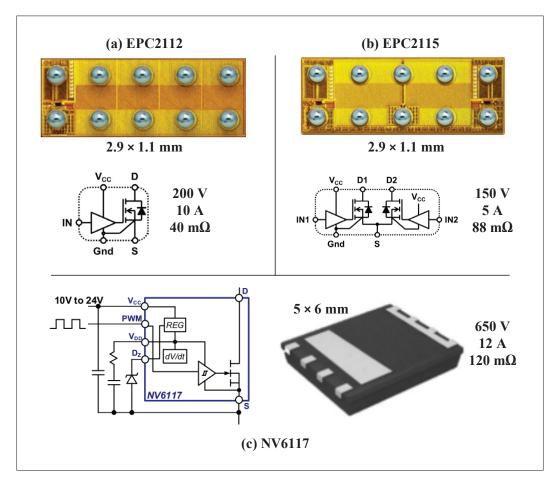

One of the key aspects of GaN power transistors is the capability of fast switching speed which copes with a minimum amount of parasitics. The ideal solution for power modules with GaN devices is monolithic integration of GaN switches, gate drivers and control ciruits on the same die. EPC and Navitas have commercialized e-mode GaN devices with built-in gate driver as detailed in Figure 2.1. However, these are with single power device or common source pair.

In the industry there are also commercial gate drivers for GaN device in half-bridge. Table 2.1 lists some of the typical parts.

Table 2.1 Typical commercial gate driver for GaN device in half-bridge

| Vendor            | Part Number | Description                                     |

|-------------------|-------------|-------------------------------------------------|

| Texas Instruments | LM5113      | 1.2/5 A, 100 V driver                           |

| Texas Instruments | LMG1210     | 1.5/3 A, 200 V driver with adjustable dead-time |

| Texas Instruments | LMG5200     | 80 V GaN half-bridge power stage                |

| On Semi           | NCP51820    | -3.5 to +650 V, adjustable dead time, dual LDOs |

| uPI Semiconductor | uP1966A     | $0.4/0.7\Omega$ pull-down/pull-up driver        |

| Peregrine         | PE29101     | 2/4 A, 80 V driver                              |

Figure 2.1 Integrated GaN device with gate driver from EPC and Navitas Semiconductor

### 2.3 Gate Driver for GaN in literature

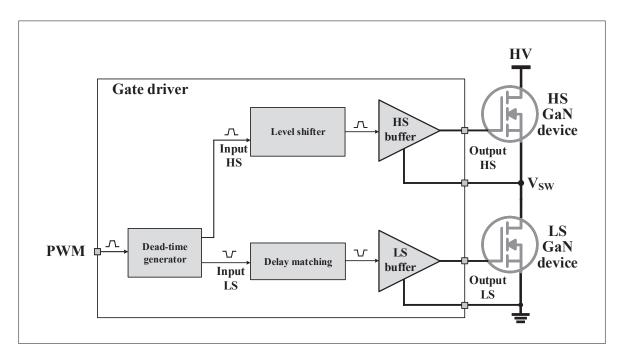

To highlight the key elements in GaN gate drivers, Figure 2.2 shows the main building blocks in a gate driver for half-bridge topology, the most popular and commonly used converter topology (Delaine *et al.*, 2012; Song *et al.*, 2015).

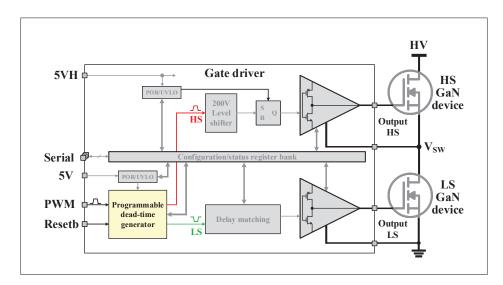

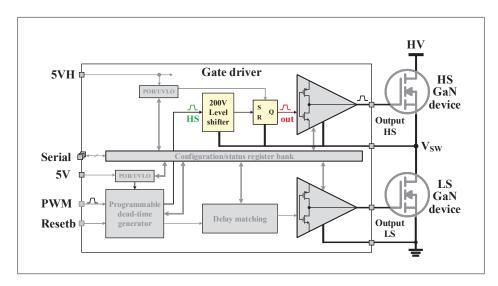

As depicted, there are two output stages controlling the two GaN devices, high-side (HS) and low-side (LS). Each of them has an independent power supply. The ground of HS logic is tied to  $V_{SW}$ . To prevent large shoot-through current, a dead-time (DT) is usually inserted between the conduction time of HS and LS devices. The level shifter serves as the interface between LS logic and HS power domains.

Figure 2.2 Half-bridge gate driver building blocks

In the literature, the majority of GaN power modules in half-bridge still opt for system-in-package, which integrates GaN power device with silicon gate driver on a surface-mount package (Luo *et al.*, 2014) or even PCB-level approaches. There are also works with discrete GaN devices in form of bare-die.

As power converter circuits are downsized, switching frequency increases to cope with miniature inductors and capacitors. At high  $f_{PWM}$ , timing mismatch between HS and LS becomes critical. Therefore, the performance bottleneck of high-speed gate drivers is the propagation delays of the level shifter and the DT generator. Such delays can be reduced with circuit techniques which leads to the classic power-speed compromise.

Conventional HV gate drivers often carry tens of ns of propagation delays in the level shifter, which becomes a critical problem as the  $f_{PWM}$  reaches the 10 MHz range. In (Kawai *et al.*, 2019), large delay of the level shifter and long DT in the driver limit its  $f_{PWM}$  to 1 MHz. To reduce the total delay, which is dominated by the HV level shifter, a sub-ns delay bootstrapped

gate driver with dynamic level shifter was reported (Song *et al.*, 2015). The speed gained at the cost of high power consumption that limits the peak power efficiency.

In a converter using half-bridge topology, the falling edge slope of  $V_{SW}$  is proportional to the output current (Roschatt *et al.*, 2016). A light load with a small DT leads to non-zero-switching of the GaN FETs whereas a heavy load with high DT results in reverse conduction in the GaN devices. Figure 2.3 illustrates the scenarios of optimal DT and two extremes. To overcome these challenges, digital control technique with generated adaptive DT is proposed. However, a high circuit complexity is involved (Wittmann *et al.*, 2016). A near-optimal DT control is reported (Lee *et al.*, 2011), however the long delay in sensing loop limits its use to low  $f_{PWM}$  applications. In (Ke *et al.*, 2016), a  $V_{SW}$  dual-edge DT modulator was designed, which senses load current and supply voltage and then generates modulated delays for  $V_{SW}$  rising and falling edges to adjust the instant DT, realizing zero-voltage switching for the GaN power switches. However, this method is too complicated for the CPIOS context of this project and the power consumption of the sub-ns comparator is high, leading to significant power loss.

Figure 2.3  $V_{SW}$  and dead-time Taken from Wittmann *et al.* (2016)

Concerning the reliability, there have been some works addressing the bootstrap capacitor overcharge issue discussed in chapter 1. A Zener diode clamping technique was used to protect the bootstrap rail by sinking excessive charge to ground (Kawai et al., 2019; Song et al., 2015). However, this technique limits  $f_{PWM}$  as the power loss is proportional to the switching frequency. In (Ke et al., 2016), an adaptive charging scheme called adaptive bootstrap balancing was proposed. To avoid overcharge, the charging time is initialized until the  $V_{SW}$  zero-crossing sensor determines that the charge voltage has enter the safe zone. This technique involves a high degree of circuit complexity. Another reliability issue is current collapse in the GaN devices. This phenomenon is due to hot electron injection and charge trapping, having been widely considered as one of the major causes of GaN device aging and premature failure (Bahl et al., 2016). It degrades channel conductivity and increases  $R_{on}$  leading to higher junction temperature  $(T_J)$ . As a consequence, the mean time to failure (MTTF) decreases exponentially (Paine et al., 2019). To monitor the device aging,  $R_{on}$  drift is highly desirable as the early warning, because its change is directly related to current collapse effect. A similar approach was reported in (Smet et al., 2011) using  $V_{CE}$  as the precursor for IGBTs. However, the monitoring can only be done when the system is off. An on-the-fly monitoring approach was reported (Dusmez et al., 2016) by using pole variation in loop gain for power MOSFETs which correlates to the  $R_{on}$  variation. However, this technique is limited in continuous conduction mode (CCM) and the implementation of pole location is very sophisticated. Another indirect  $R_{on}$  measurement technique is realized through an  $I_{GSS}$ -inspired  $T_J$  sensor, based on the fact that gate-leakage  $I_{GSS}$  of a GaN device is both  $T_J$ -sensitive and aging-independent (Chen & Ma, 2019a). With sensed  $T_J$ , the in-situ condition monitor removes the impact of  $T_J$  on  $R_{on}$  through the  $T_J$  dependence remover effectively. This technique allows to take more proactive measures to slow down the aging process whenever possible (Chen & Ma, 2019a).

Electro-magnetic inteference (EMI) is one of the critical problems in highly reliable electronic devices, such as aircrafts. When power switches operate at high switching frequency, short switching cycles lead to high dI/dt and dV/dt rates that favours EMI emission. An LC filter can reduce EMI at the cost of size. Several techniques are reported to mitigate EMI. One of

them is frequency hopping using discrete frequencies in (Tao & Fayed, 2011), but this technique cannot spread the frequency spectrum evenly to lower the peak EMI. Another approach is with a series resistor, which is typically added at the gate of the GaN FET to damp the transitions (Song *et al.*, 2015; Ke *et al.*, 2016). However, the drawback is high switching loss. To overcome this, adjustable driving strength is proposed in (Rose *et al.*, 2010). Unfortunately, the sensing and driver delays are complicated and limit its use to low switching frequency applications.

Currently, spread-spectrum modulation (SSM) techniques are regarded as the most effective methods for EMI suppression (Amin & Choi, 2019). Periodic SSM (PSSM) is straightforward and easy to implement (Tse *et al.*, 2002). However, its EMI suppression is the least effective. Randomized SSM (RSSM) can outperform PSSM, with lower peak EMI and near-uniform noise spreading, but its performance highly relies on the random clock design. In (Yang *et al.*, 2018), an N-bit digital random clock was reported to achieve discrete RSSM (D-RSSM). However, the bit number N has to be large in order to achieve satisfying EMI attenuation, significantly increasing circuit complexity, chip area and power consumption. (Chen & Ma, 2019b) proposed a Markov chain based random clock to achieve analog  $f_{SW}$  modulation. It conducts SSM continuously and spreads spurious noise at  $f_{SW0}$  and its harmonics uniformly, achieving the desirable C-RSSM.

Closed-Loop EMI regulation is another promising approach. To best compromise between EMI and switching loss, it is important to accurately identify the Miller Plateau (MP) start point of  $V_{GS}$ . In (Chen *et al.*, 2017), a closed-loop adaptive MP sensing technique is presented. The technique utilizes the reverse conduction behavior of low-side switch to identify the MP starting point of the high-side device. This relaxes the design stress on the closed-loop propagation delay. Once the MP starting point is detected, the driving strength is modulated with an adaptive closed-loop control to achieve low dI/dt before the MP (for low EMI generation) and high dI/dt after the MP (to reduce the switching noise), leading to an optimum between noise and efficiency.

### 2.4 Conclusion

Driving GaN FETs is quite challenging. Multiple aspects have been studied and addressed in the literature: driving for performance, for reliability and for EMI reduction. Every approach was elaborate and aimed at a specific improvement. There has been no universal and versatile gate driver. The universal and configurable gate driver for GaN half-bridges in the context of SiP is proposed in this work. It can control a range of GaN devices (1–5.3 nC gate charge) with configurable speeds and DT without extra components. The adjustable parameters make local efficiency optimization possible. This gate driver, as a standalone chip, can also serve as a platform for other works that need on-the-fly configuration of drive strength and DT.

### **CHAPTER 3**

#### DESIGN OF THE GATE DRIVER

#### 3.1 Introduction

This chapter outlines the gate driver design, starting with system requirements and the choice of technology. The internal blocks will then be discussed and simulated. Some blocks require special layout techniques which will also be detailed. Various post-layout simulations are performed to ensure the functionality of the chip.

## 3.2 System Requirements

Intended to be the core design of the CPIOS for aerospace applications, the gate driver in this work is capable of driving GaN devices of various sizes, in half-bridge configuration, with configurable driving strength and dead-time. The half-bridges, so-called switching unit, can be configured to operate in buck, boost or buck-boost topology. Figure 3.1 summarizes the context of this work.