## Contribution to the Design of the Closed-Loop Control of a Real-Time Power Simulator

by

#### Olivier TREMBLAY

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILISOPHY Ph.D.

MONTRÉAL, DECEMBER 15<sup>TH</sup>, 2020

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

This <u>Creative Commons</u> licence allows readers to download this work and share it with others as long as the author is credited. The content of this work can't be modified in any way or used commercially.

#### **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Handy Fortin Blanchette, Thesis Supervisor Department of Electrical Engineering at École de technologie supérieure

Mr. Richard Gagnon, Thesis Co-supervisor Hydro-Québec's research institute (IREQ)

Mr. Vincent Demers, President of the Board of Examiners Department of Mechanical Engineering at École de technologie supérieure

Mr. Kamal Al-Haddad, Member of the jury Department of Electrical Engineering at École de technologie supérieure

Mr Philippe Viarouge, External Independent Evaluator Department of Electrical Engineering at Université Laval

Mr Vahan Gevorgian, Independent Evaluator National Renewable Energy Laboratory (NREL)

THIS THESIS WAS PRESENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC ON DECEMBER  $8^{\mathrm{TH}}$ , 2020 AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### FOREWORD AND ACKNOWLEDGEMENTSS

Doctoral research with industrial applications is extremely stimulating and motivating, despite the significant pressure to complete it successfully. I would like to extend my most sincere thanks to my co-supervisor and colleague, Richard Gagnon, for suggesting this unique and thrilling project. I am deeply touched by the deep trust he put in me and the freedom of action he afforded me. His unfailing support, critical spirit, priceless advice/comments and relevant suggestions have contributed to my continued development as a scientist.

Completing this Ph.D. as part of my work as an IREQ researcher was an extremely rare opportunity. I openly thank my employer, Hydro-Québec, for its support over the last six years. I am extremely grateful for the opportunity to work in an outstanding environment.

I also wish to thank my supervisor, Handy-Fortin Blanchette, who enthusiastically agreed to direct this work. His unique experience in the areas of power electronics and power hardware-in-the-loop (PHIL) allowed this project to make giant steps forward. He offered me the perfect blend of supervision and autonomy. His informed advice, constructive criticism, passion for applied science and encouragement were essential to the success of this project.

This project could not have taken place without the support of a strong and united team that was willing to do anything to help. I am referring to my IREQ colleagues. First, I wish to thank my manager, Innocent Kamwa, who knows how to recognize scientific value when he sees it and who has always encouraged me. I also wish to thank my friend, Philippe, with whom I have shared an office for 12 years and counting. Our discussions of topics both scientific and personal have made my days richer. I also want to thank Dmitry "the new guy" with whom I have worked closely over the last three years to get the SimP project interface to work. For their help in overcoming various technical challenges, I thank the entire simulator team: Alain, Benoît, Éric, François, Gilbert, Jean, Léo, Manu, Omar, Patrice, Pierre and Sylvain. Special thanks to Karim and Réjean, who made it possible for this project to materialize in an original

way. Finally, I wish to salute two great departed spirits, Christian and Jean-Claude, to whom I am grateful for everything. I miss them greatly.

I also wish to thank Hydro-Québec Distribution/TransÉnergie, OPAL-RT Technologies and Natural Resources Canada for its financial support, which made possible the acquisition of state-of-the-art equipment.

To undertake a Ph.D. at 34 after building a family with three beautiful sons is a family decision, not just a personal one. Therefore, I thank the love of my life, Valérie, who not only gave me her support, but also encouraged me to take on this challenge. To my sons, Xavier, Alexis and Raphaël, who sometimes asked themselves why I was still going to school, I hope to have shown you the importance of finding a profession that you love. To my friends, in-laws and especially my parents, thank you for all the joy and happiness you have given me. Without you, my life would not be as balanced as it is!

# Contribution à la conception de la commande en boucle fermée d'un simulateur de puissance en temps réel

#### **OLIVIER TREMBLAY**

#### RÉSUMÉ

Le contexte de la transition énergétique amène l'Institut de recherche d'Hydro-Québec (IREQ) à se doter d'un simulateur de puissance de 7.5 MVA afin d'y raccorder des équipements de puissance à divers réseaux électriques simulés en temps réel sur Hypersim. Ce genre de système, appelé « power hardware-in-the-loop (PHIL) », est une technologie émergente dans le domaine des réseaux électriques et représente encore aujourd'hui un défi de réalisation de taille. Ce défi se situe au niveau de la maîrise des signaux échangés au point d'interface entre le simulateur et l'amplificateur, ce qui constitue la principale problématique à solutionner. En effet, des délais apparaissent au point d'interface et ces derniers peuvent compromettre la stabilité de fonctionnement et/ou détériorer les performances dynamiques du système.

Dans un premier temps, une nouvelle base est établie pour comprendre la stabilité des systèmes PHIL compte tenu de leur nature hybride (analogique / numérique). En effet, la méthode conventionnelle de détermination du critère de stabilité, qui considère le système PHIL comme un modèle continu, n'est pas appropriée. Une nouvelle méthode d'évaluation de la stabilité basée sur des réponses en fréquence de l'impédance discrète est ainsi présentée.

Dans un deuxième temps, cette thèse présente une implémentation stable, robuste et précise d'une interface pour un simulateur PHIL basée sur le modèle de ligne de transmission Bergeron (BTLM). Deux limites de cette interface sont identifiées et des stratégies correctives sont formulées afin de garantir sa compatibilité avec l'application PHIL. Des analyses de stabilité, de passivité et de précision sont ensuite réalisées pour vérifier ses performances. L'interface proposée est par la suite implantée dans un banc d'essai PHIL expérimentale de 3 kVA, conçu et réalisé à l'IREQ. Plusieurs tests sont effectués afin de démontrer la stabilité et la précision du système en boucle fermée dans un large éventail de conditions de fonctionnement et avec divers équipements testés.

Troisièmement, le banc d'essai PHIL est exploité pour caractériser des onduleurs photovoltaïques résidentiels connectés à un réseau de distribution typique. Une méthode d'agrégation est d'ailleurs développée pour obtenir des paramètres d'essais réalistes. Les essais en boucle fermée ont permis de révéler des anomalies de fonctionnement lorsque ces onduleurs sont connectés à des réseaux ayant certaines caractéristiques.

**Mots-clés:** Algorithme d'interface numérique, analyse de stabilité, conversion de l'énergie, FPGA, modélisation, modèle de ligne de transmission de Bergeron, simulateur de puissance, simulation numérique, simulation avec matériel de puissance dans la boucle, simulation en temps réel, systèmes discrets.

#### Contribution to the design of the closed-loop control of a real-time power simulator

#### **OLIVIER TREMBLAY**

#### **ABSTRACT**

The energy transition has spurred Hydro-Québec's research institute (IREQ) to acquire a 7.5-MVA power simulator that will allow for the connection of power equipment to various power systems simulated in real time on Hypersim. This kind of "power-hardware-in-the-loop" (PHIL) system is an emerging power grid technology whose implementation is still very challenging. The main challenge revolves around the control of the signals exchanged by the simulator and the amplifier at their point of interface. More specifically, delays that occur at the interface may compromise the operating stability or dynamic performance of the system.

First, a new basis has been established to understand the stability of PHIL systems in light of their hybrid (digital-analog) nature. The conventional method for determining stability criteria is not appropriate as it assumes a continuous model of PHIL systems. A new stability analysis method based on the discrete impedance frequency response is thus presented.

Second, this dissertation presents a stable, robust and accurate interface for PHIL simulator based on the Bergeron transmission line model (BTLM). Two limitations of this interface are identified, and corrective strategies are formulated to ensure its compatibility with the PHIL application. Stability, passivity and accuracy analyses are then performed to verify its performance. The proposed interface has been implemented in a 3-kVA experimental PHIL test bench designed and built at IREQ. Several tests have been performed to demonstrate the stability and accuracy of the closed-loop system for various pieces of equipment under a wide range of operating conditions.

Third, the PHIL test bench was used to identify the characteristics of residential photovoltaic inverters connected to a typical distribution system. An aggregation method was developed to develop realistic testing parameters. Close-loop testing revealed operating anomalies that occur when such inverters are connected to certain types of power systems.

**Keywords**: Bergeron transmission line model, digital simulation, discrete-time systems, energy conversion, FPGA, interface algorithm, modeling, power hardware-in-the-loop simulation, power simulator, real-time systems, stability analysis.

#### **TABLE OF CONTENTS**

Page

| INTR | ODUCTIO    | N                                                                | 1  |

|------|------------|------------------------------------------------------------------|----|

| СНАІ | PTER 1     | BACKGROUND AND LITERATURE REVIEW                                 | 11 |

| 1.1  |            | e simulator and CHIL/PHIL applications                           |    |

| 1.2  |            | ises of a PHIL system                                            |    |

| 1.3  |            | e review and assessment of existing digital interface algorithms |    |

| 1.0  | 1.3.1      | Ideal transformer method (ITM)                                   |    |

|      | 1.3.2      | Partial circuit duplication (PCD)                                |    |

|      | 1.3.3      | Damping impedance method (DIM)                                   |    |

|      | 1.3.4      | Time variant first-order approximation (TFA)                     |    |

|      | 1.3.5      | Transmission-line model (TLM)                                    |    |

|      | 1.3.6      | Park transform based method (DQ)                                 |    |

|      | 1.3.7      | Explicit discretization of series inductor or shunt capacitor    |    |

| 1.4  |            | of technologies used by major PHIL actors                        |    |

| 1.5  |            |                                                                  |    |

| 1.5  | Summary    |                                                                  |    |

| CHAI | PTER 2     | NEW PHIL SYSTEM STABILITY ANALYSIS METHOD                        | 27 |

| 2.1  | Introduct  | 10n                                                              | 27 |

| 2.2  | Decompo    | osition of system into two equivalent impedances                 | 30 |

|      | 2.2.1      | DUT impedance: effect of ZOH and sampling                        |    |

|      | 2.2.2      | ROS impedance: effect of numerical integration method            |    |

| 2.3  | Algorithn  | n to determine closed-loop system stability                      |    |

|      | 2.3.1      | DUT frequency response                                           |    |

|      | 2.3.2      | ROS frequency response                                           |    |

|      | 2.3.3      | Closed-loop system stability                                     |    |

|      | 2.3.4      | Marginal stability case                                          |    |

| 2.4  | Conclusio  | ons                                                              |    |

|      |            |                                                                  |    |

|      | PTER 3     | EXPLORING NEW INTERFACE METHODS                                  |    |

| 3.1  |            | ion                                                              |    |

| 3.2  | Mitigatio  | n methods for ITM-DIA                                            |    |

|      | 3.2.1      | Interface signal filtering                                       | 41 |

|      | 3.2.2      | Numerical methods                                                | 43 |

| 3.3  | Predictive | e control                                                        | 46 |

|      | 3.3.1      | Theory                                                           | 46 |

|      | 3.3.2      | Application to PHIL system: predictive control of ROS            | 49 |

|      | 3.3.3      | Discussion                                                       |    |

| 3.4  | Comparis   | son of digital interface algorithms for PHIL applications        |    |

| 3.5  | Conclusio  | ong                                                              | 53 |

| CHA | PTER 4    | DEVELOPMENT OF A NEW TRANSMISSION LINE-BASED            |         |

|-----|-----------|---------------------------------------------------------|---------|

|     |           | INTERFACE METHOD                                        |         |

| 4.1 |           | etion                                                   |         |

| 4.2 | Transm    | ission line model                                       |         |

|     | 4.2.1     | Solution for lossless line                              |         |

|     | 4.2.2     | Special lossy line case: distortionless line            |         |

| 4.3 | Bergero   | n model                                                 | 60      |

|     | 4.3.1     | Forward wave                                            | 61      |

|     | 4.3.2     | Backward wave                                           | 62      |

|     | 4.3.3     | Electrical model                                        | 63      |

|     | 4.3.4     | Intuitive implementation approach for PHIL systems      | 64      |

| 4.4 | New im    | plementation of Bergeron model for PHIL systems         | 66      |

|     | 4.4.1     | Output filter characteristic impedance emulator (OFCIE) | 67      |

|     | 4.4.2     | PA-VSC internal resistance compensator                  | 68      |

|     | 4.4.3     | Forward wave resampling                                 | 69      |

|     | 4.4.4     | Backward wave calculation                               | 70      |

| 4.5 | Validati  | on of new BTLM-PHIL interface                           | 70      |

|     | 4.5.1     | OFCIE validation                                        | 72      |

|     | 4.5.2     | Comparison with reference simulation                    | 72      |

| 4.6 | Stability | analysis of new BTLM-PHIL interface                     | 74      |

|     | 4.6.1     | OFCIE stability                                         | 75      |

|     | 4.6.2     | Passivity of multirate BTLM                             | 78      |

| 4.7 | Conclus   | sions                                                   | 81      |

| СНА | PTER 5    | EXPERIMENTAL PHIL TEST BENCH                            | 83      |

| 5.1 | Introduc  | etion                                                   | 83      |

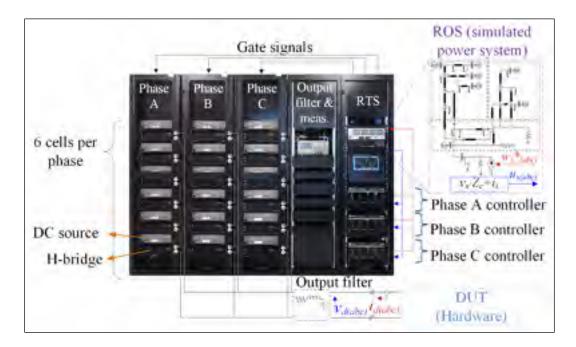

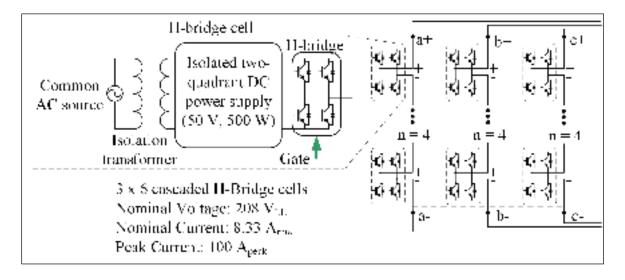

| 5.2 | Power a   | ımplifier                                               | 84      |

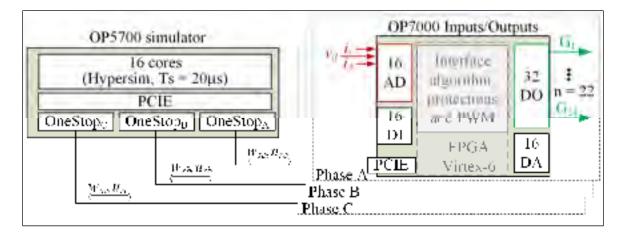

| 5.3 | Real-tin  | ne simulator and inputs/outputs                         | 85      |

| 5.4 |           | filter and measurement system                           |         |

|     | 5.4.1     | Output filter design                                    |         |

|     | 5.4.2     | Measuring system                                        | 88      |

| 5.5 | Implem    | entation of control system on FPGA                      | 90      |

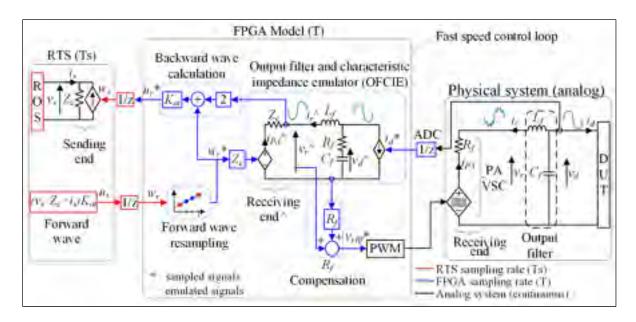

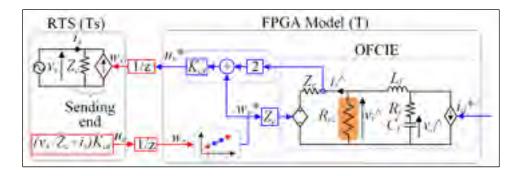

|     | 5.5.1     | Synchronization of FPGA with RTS                        | 91      |

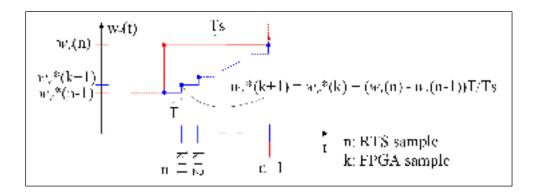

|     | 5.5.2     | Forward wave resampling                                 | 92      |

|     | 5.5.3     | Backward wave calculation                               | 92      |

|     | 5.5.4     | Analog inputs and signal conditioning                   | 92      |

|     | 5.5.5     | Output filter characteristic impedance emulator         |         |

|     | 5.5.6     | Internal resistance compensation                        |         |

|     | 5.5.7     | Phase-shifted PWM generator                             |         |

|     | 5.5.8     | FPGA control function summary                           | 97      |

| 5.6 | Conclus   | sions                                                   | 98      |

| СНА | PTER 6    | EXPERIMENTAL VALIDATION OF NEW BTLM-PHIL MET            | HOD.101 |

| 6.1 | Introduc  | etion                                                   |         |

| 6.2 | BTLM-     | PHIL parameterization and impact                        | 101     |

| 6.3  | Validati | on of delays – line short-circuit on receiving end   | 102 |

|------|----------|------------------------------------------------------|-----|

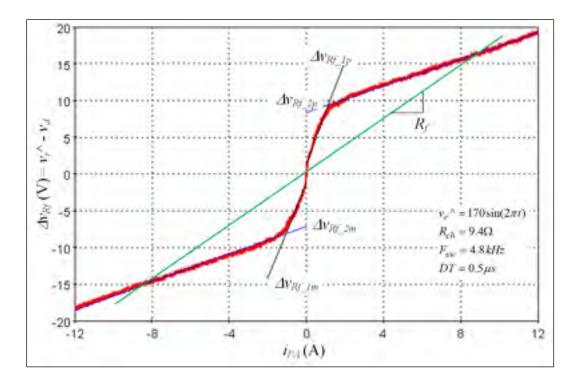

| 6.4  | Nonline  | arity characterization and compensation              | 104 |

| 6.5  |          | on of power grid emulation operating mode            |     |

|      | 6.5.1    | 1 0                                                  |     |

|      | 6.5.2    | Frequency response as seen by the grid emulator      | 110 |

| 6.6  | Validati | on of impedance emulation operating mode             | 113 |

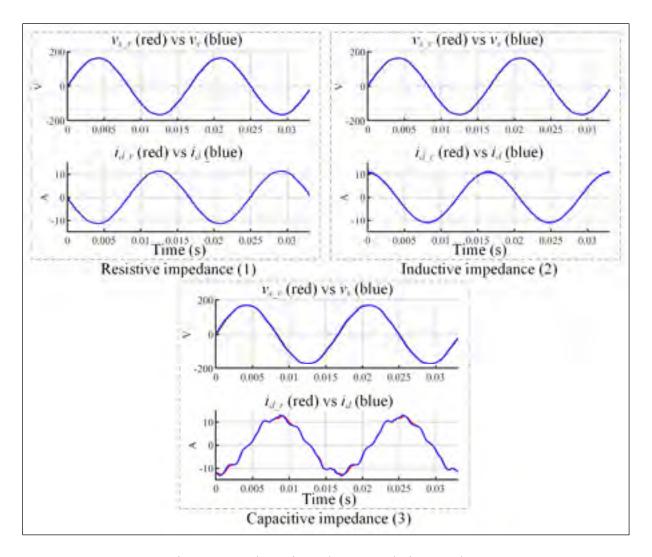

|      | 6.6.1    | Linear impedance emulator (R, L and C)               | 114 |

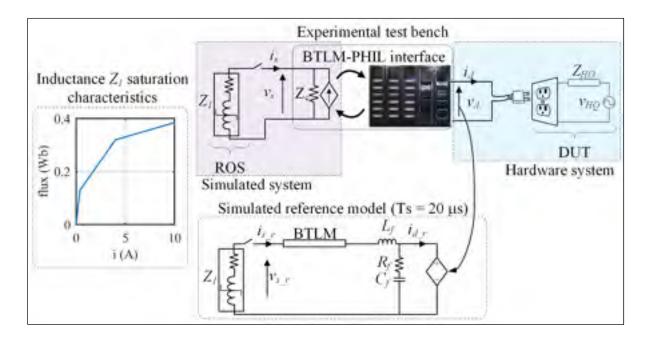

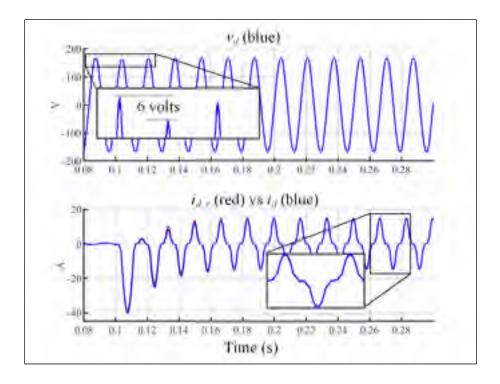

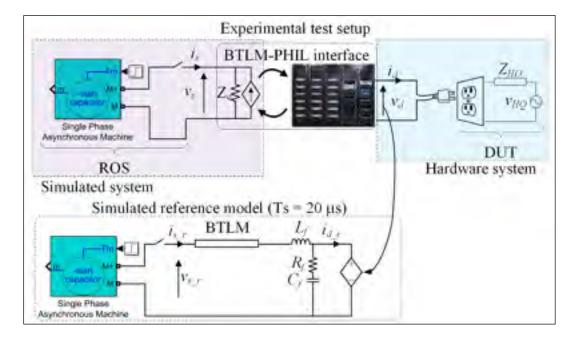

|      | 6.6.2    | Non-linear impedance emulator                        | 116 |

| 6.7  | Conclus  | sions                                                |     |

| СНА  | PTER 7   | PHIL TEST BENCH OPERATION                            | 123 |

| 7.1  | Introduc | etion                                                | 123 |

| 7.2  |          | cy response of Hydro-Québec's laboratory grid        |     |

| 7.3  |          | f the transient behavior of residential PV inverters |     |

|      | 7.3.1    | Parameters of system studied                         | 127 |

|      | 7.3.2    |                                                      |     |

|      | 7.3.3    | Residential inverter testing                         | 132 |

| 7.4  | Conclus  | sions                                                |     |

| CON  | CLUSION  | S AND CONTRIBUTIONS                                  | 141 |

| REC  | OMMEND   | DATIONS                                              | 145 |

| LIST | OF BIBL  | IOGRAPHIC REFERENCES                                 | 147 |

#### LIST OF TABLES

|           |                                                    | Page |

|-----------|----------------------------------------------------|------|

| Table 2.1 | Sets of parameters                                 | 28   |

| Table 2.2 | Stability truth table                              | 36   |

| Table 3.1 | Digital interface algorithm (DIA) comparison table | 52   |

| Table 4.1 | Set of parameters used for BTLM-PHIL validation    | 71   |

| Table 5.1 | Measurement system specifications                  | 90   |

| Table 5.2 | FPGA control system performance summary            | 98   |

| Table 5.3 | FPGA implementation results                        | 98   |

| Table 6.1 | Testing parameters                                 | 102  |

| Table 6.2 | Voltage drop parameters                            | 106  |

#### LIST OF FIGURES

Page

| Figure 1.1 | Sample simulation using controller hardware-in-the-loop (CH) |    |

|------------|--------------------------------------------------------------|----|

| Figure 1.2 | Partial circuit duplication                                  |    |

| Figure 1.3 | Damping impedance                                            | 16 |

| Figure 1.4 | First-order approximation                                    | 17 |

| Figure 1.5 | Short transmission line (stub line) model                    | 18 |

| Figure 1.6 | Park transform based interface                               |    |

| Figure 1.7 | Partitioning using an explicit integration method            | 21 |

| Figure 2.1 | Intuitive implementation of PHIL circuit separation          | 27 |

| Figure 2.2 | Hybrid model of a PHIL system                                | 28 |

| Figure 2.3 | Simulation results for hybrid PHIL system                    | 29 |

| Figure 2.4 | Impedance measurement for hybrid PHIL system                 | 31 |

| Figure 2.5 | Hybrid DUT frequency response                                |    |

| Figure 2.6 | Hybrid ROS frequency response                                |    |

| Figure 2.7 | DUT and ROS impedance frequency response                     | 37 |

| Figure 2.8 | Frequency response for marginally stable case                | 38 |

| Figure 2.9 | Simulation results around stability critical point           | 39 |

| Figure 3.1 | Block diagram for ITM with low-pass filter                   | 42 |

| Figure 3.2 | Results – ITM with low-pass filter                           | 43 |

| Figure 3.3 | Results – ITM with implicit Euler method                     | 44 |

| Figure 3.4 | Results – ITM with first-order hold (FOH)                    |    |

| Figure 3.5 | Predictive control block diagram                             |    |

| Figure 3.6  | Electrical circuit used to achieve predictive control                        | 49 |

|-------------|------------------------------------------------------------------------------|----|

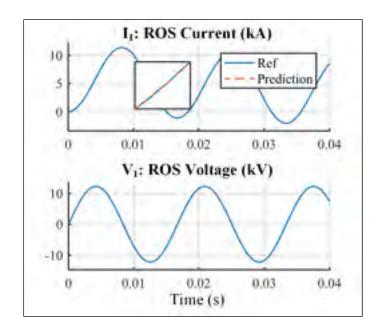

| Figure 3.7  | Predictive control of ROS                                                    | 50 |

| Figure 3.8  | Results – Predictive control                                                 | 51 |

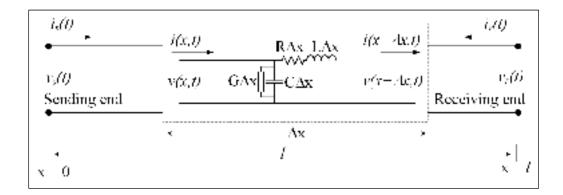

| Figure 4.1  | Distributed-parameter transmission line model                                | 56 |

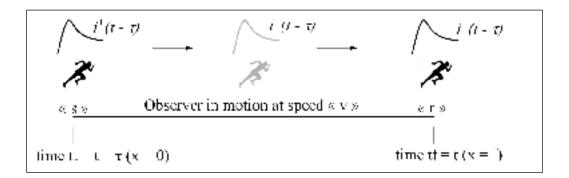

| Figure 4.2  | Forward wave observer                                                        | 61 |

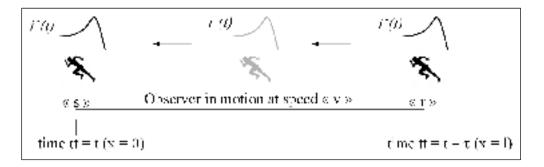

| Figure 4.3  | Backward wave observer                                                       | 62 |

| Figure 4.4  | Electrical diagram of Bergeron model for lossy line                          | 64 |

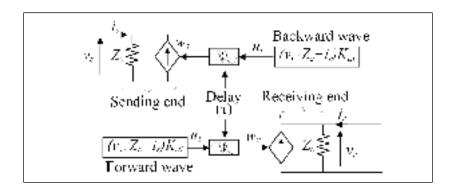

| Figure 4.5  | Electrical diagram of Bergeron model with losses (PHIL)                      | 65 |

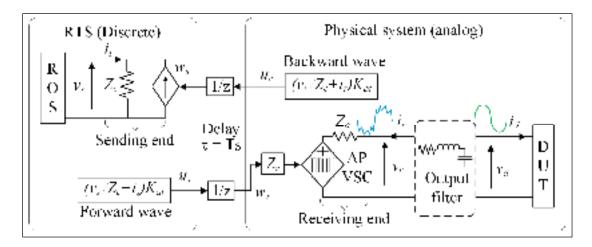

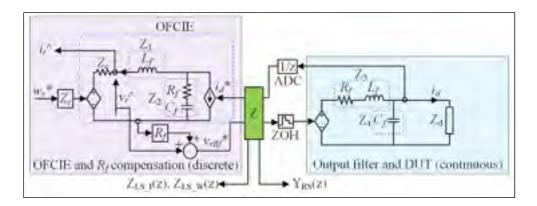

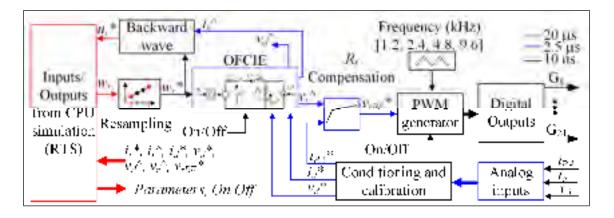

| Figure 4.6  | Implementation of the new BTLM-PHIL interface                                | 67 |

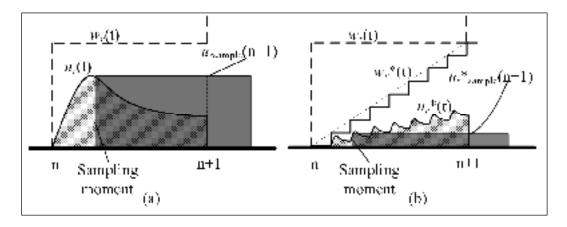

| Figure 4.7  | Resampling of forward wave originating from the RTS                          | 69 |

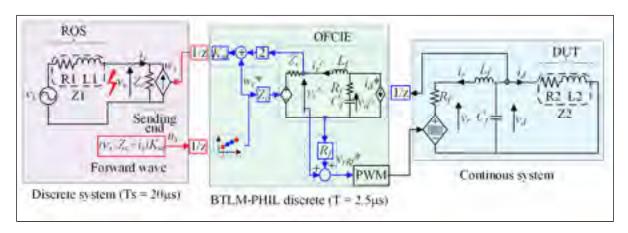

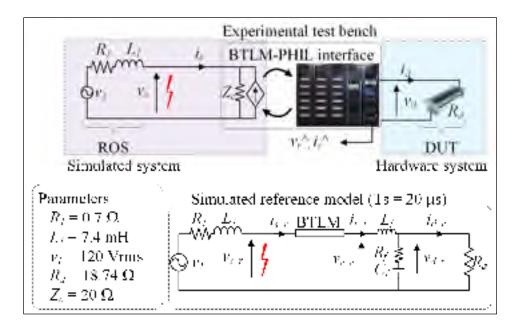

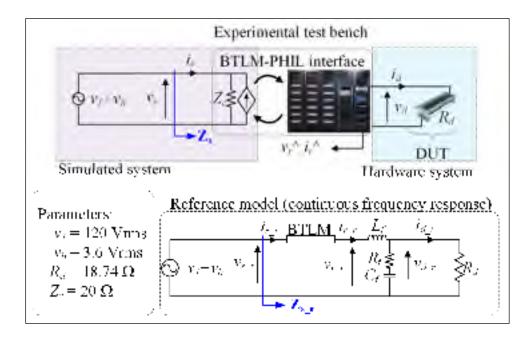

| Figure 4.8  | BTLM-PHIL simulation model                                                   | 71 |

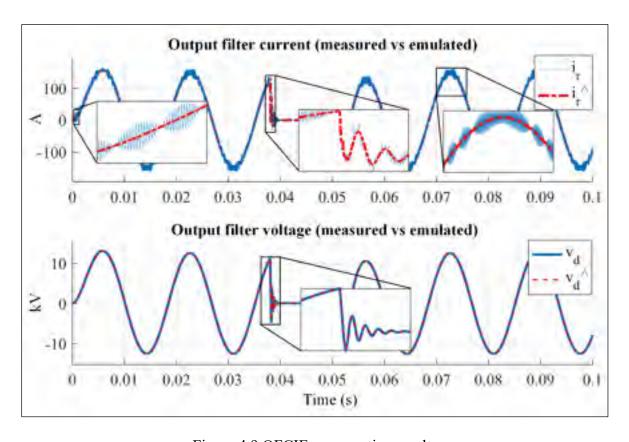

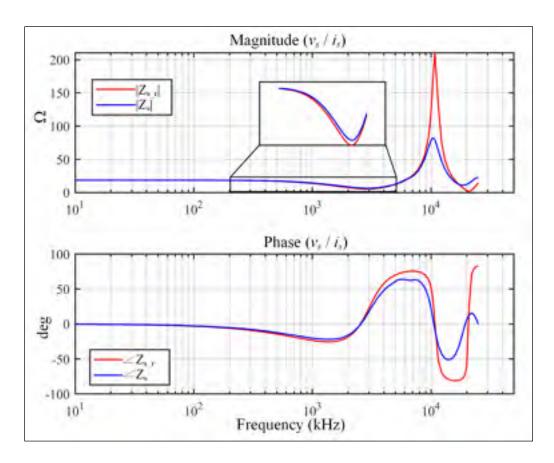

| Figure 4.9  | OFCIE comparative results                                                    | 72 |

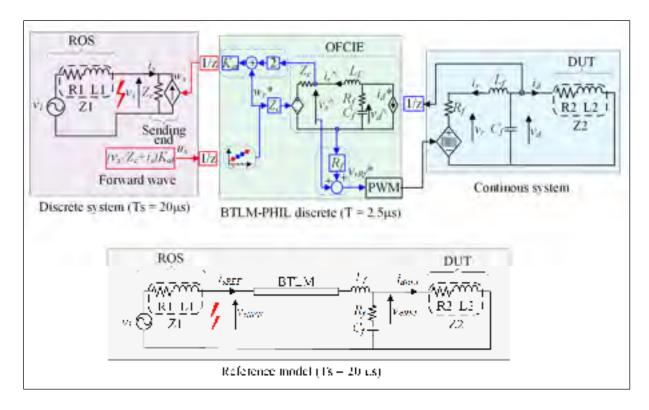

| Figure 4.10 | Reference case simulation model                                              | 73 |

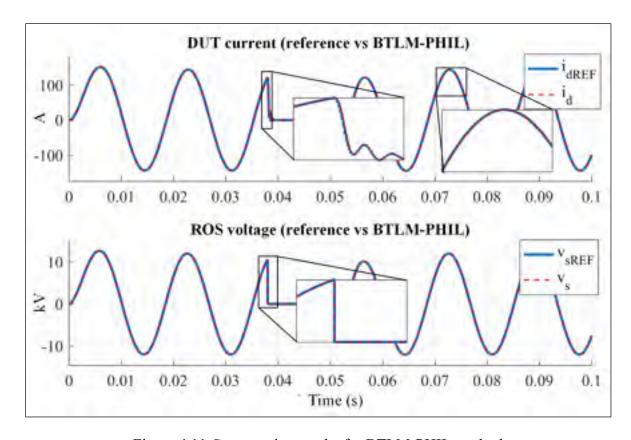

| Figure 4.11 | Comparative results for BTLM-PHIL method                                     | 74 |

| Figure 4.12 | Linear model of ITM interface (filter and emulator)                          | 76 |

| Figure 4.13 | Block diagram of linear model of OFCIE-ITM interface                         | 76 |

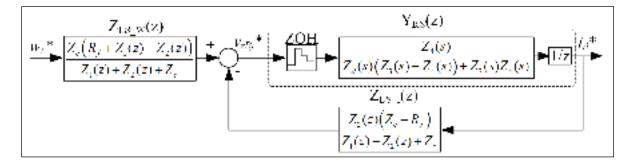

| Figure 4.14 | Instability regions for various values of $Zd(s)$ and (a) $R_f$ and (b) $Zc$ | 78 |

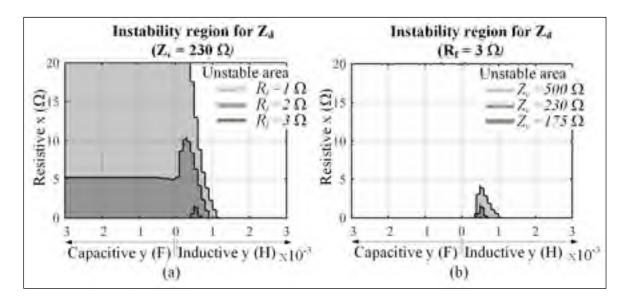

| Figure 4.15 | Illustration of ZOH effect on BTLM-PHIL passivity:                           | 80 |

| Figure 5.1  | Experimental PHIL test bench                                                 | 83 |

| Figure 5.2  | Experimental power amplifier topology                                        | 84 |

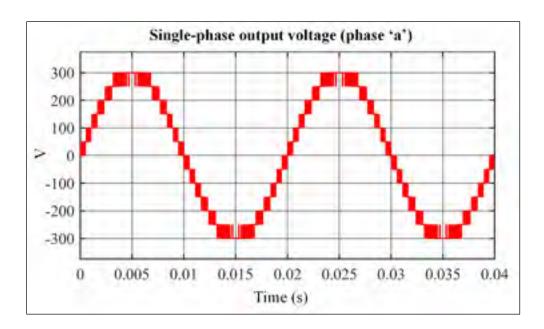

| Figure 5.3  | Theoretical amplifier output wave form                                       | 85 |

| Figure 5.4  | Simulator and I/O configuration                                              | 86 |

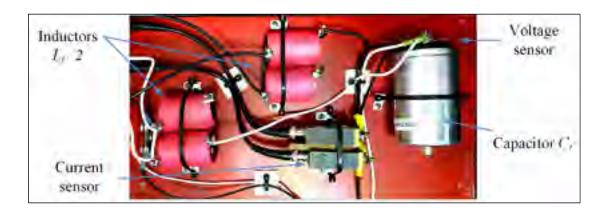

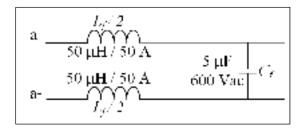

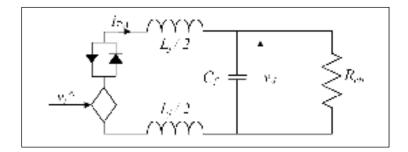

| Figure 5.5  | Experimental output filter configuration                                     | 86 |

| Figure 5.6  | Output filter                                                                | 87 |

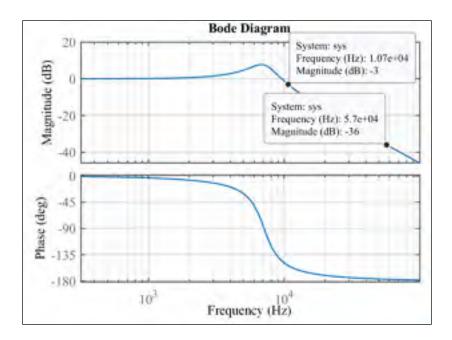

|             |                                                                              |    |

| Figure 5.7  | No-load frequency response of output filter      | 88  |

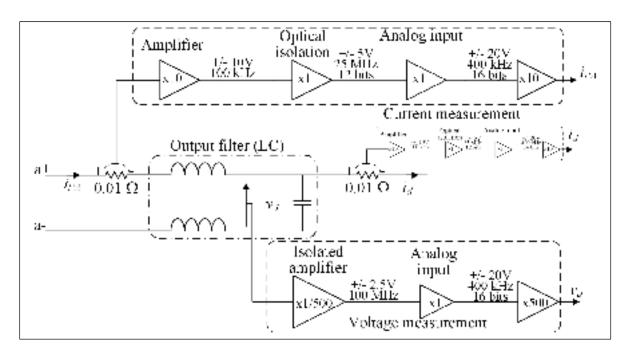

|-------------|--------------------------------------------------|-----|

| Figure 5.8  | Phase "a" measurement system                     | 89  |

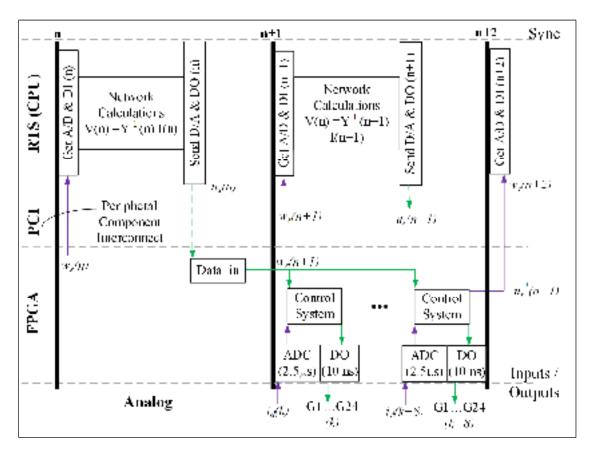

| Figure 5.9  | Implementation of control system on FPGA         | 90  |

| Figure 5.10 | Input/output synchronization                     | 91  |

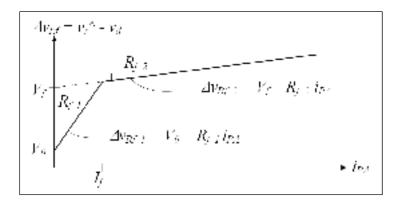

| Figure 5.11 | Non-linear amplifier resistance                  | 94  |

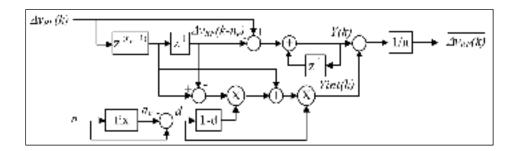

| Figure 5.12 | Moving average function with interpolation       | 95  |

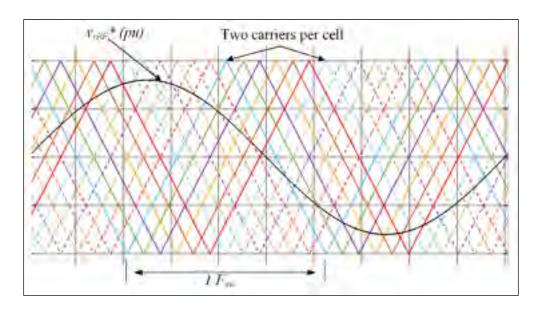

| Figure 5.13 | Phase-shifted PWM generator                      | 96  |

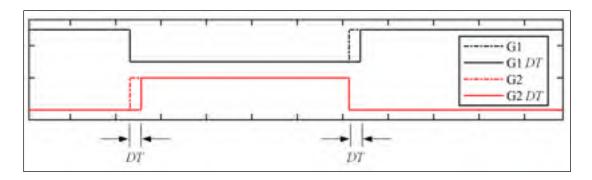

| Figure 5.14 | Waveform with dead time                          | 97  |

| Figure 6.1  | Short-circuit on receiving-end side of the line  | 103 |

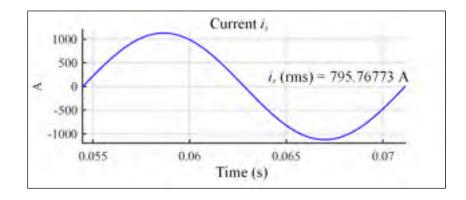

| Figure 6.2  | Short-circuit current test results               | 103 |

| Figure 6.3  | Power switch                                     | 104 |

| Figure 6.4  | Diode characteristics                            | 104 |

| Figure 6.5  | Nonlinearity characterization diagram            | 105 |

| Figure 6.6  | Voltage drop in amplifier phase "a"              | 106 |

| Figure 6.7  | Voltage drop after compensation                  | 107 |

| Figure 6.8  | Resistive load tests (grid emulation mode)       | 108 |

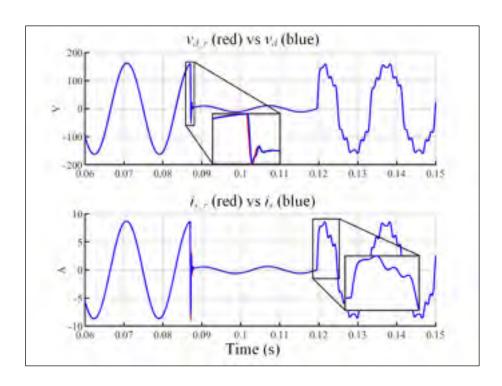

| Figure 6.9  | Transient results (grid emulator)                | 109 |

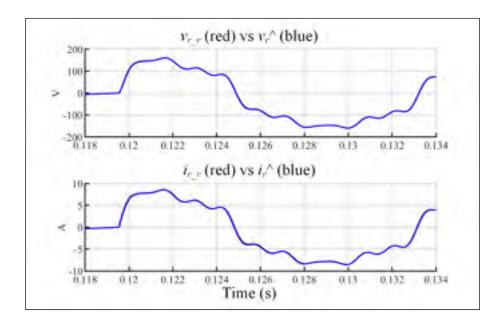

| Figure 6.10 | Experimental OFCIE validation                    | 110 |

| Figure 6.11 | Resistive load tests (frequency response)        | 111 |

| Figure 6.12 | Frequency response (resistive load)              | 112 |

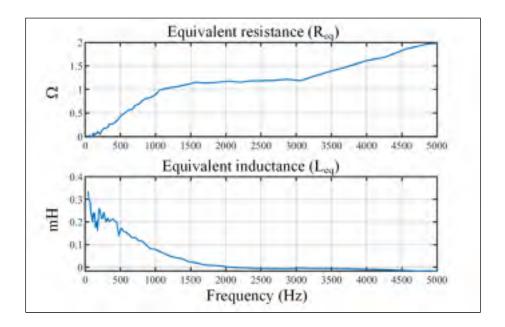

| Figure 6.13 | Equivalent impedance of test bench $(Z_{eq})$    | 113 |

| Figure 6.14 | Active DUT testing (impedance emulator)          | 114 |

| Figure 6.15 | Linear impedance emulation results               | 115 |

| Figure 6.16 | Active DUT testing (saturable inductor emulator) | 116 |

| Figure 6.17 | Saturable inductor emulation results                             | 117 |

|-------------|------------------------------------------------------------------|-----|

| Figure 6.18 | Active DUT testing (induction machine emulation)                 | 118 |

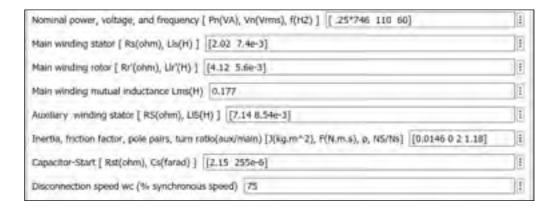

| Figure 6.19 | Single-phase induction machine model parameters                  | 118 |

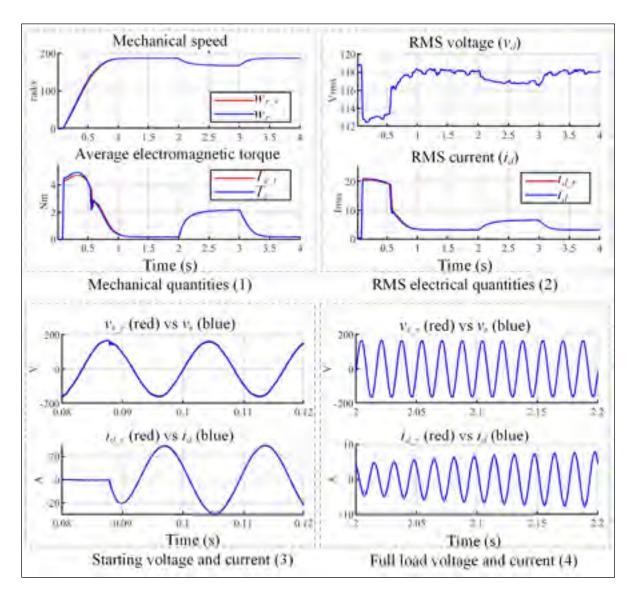

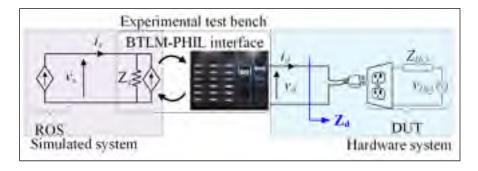

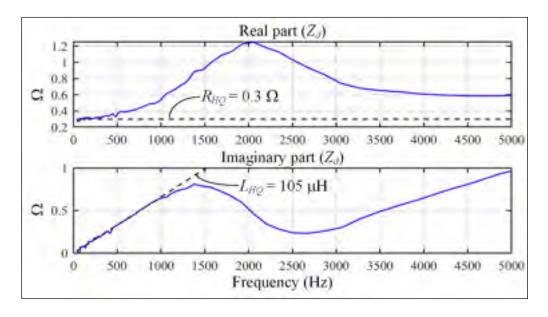

| Figure 6.20 | Induction machine emulation results                              | 119 |

| Figure 7.1  | HQ laboratory electrical outlet tests                            | 125 |

| Figure 7.2  | Frequency response of HQ's power system (laboratory outlet)      | 125 |

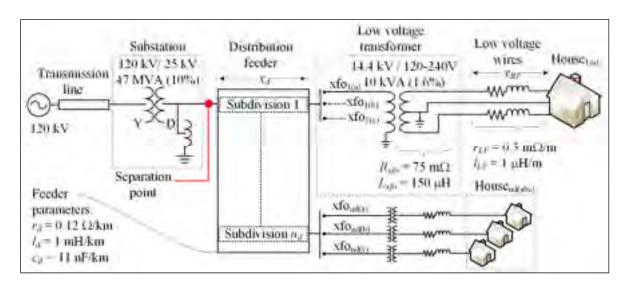

| Figure 7.3  | Typical feeder line connection                                   | 127 |

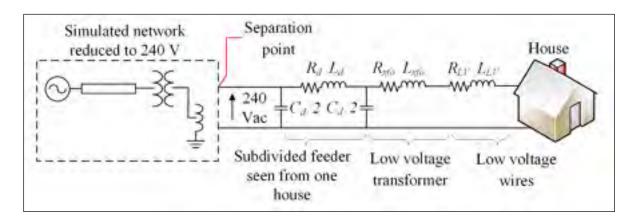

| Figure 7.4  | Equivalent impedances as seen from a home (aggregate model)      | 128 |

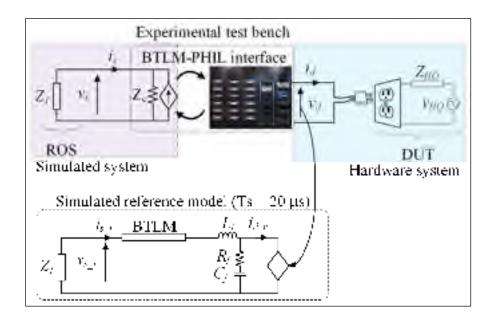

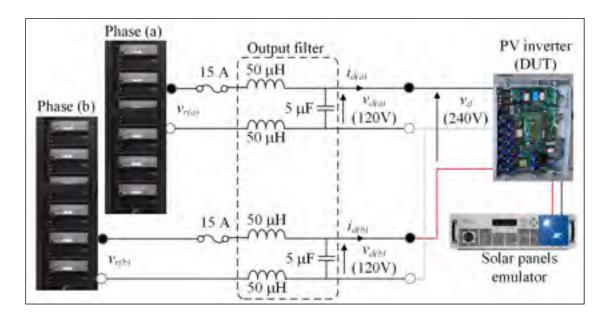

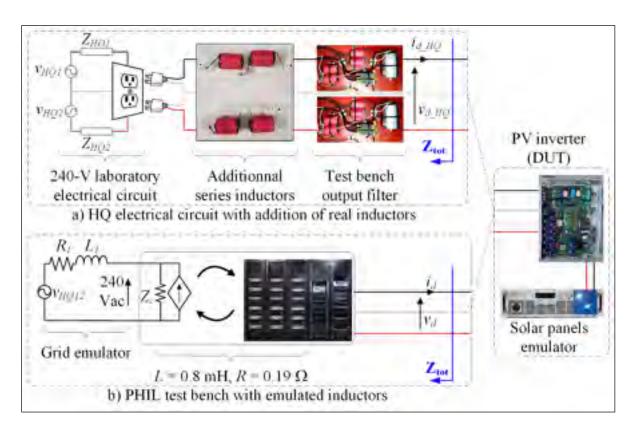

| Figure 7.5  | 240-V test bench configuration                                   | 129 |

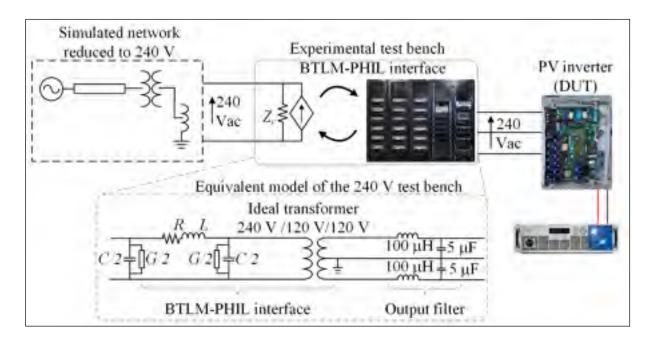

| Figure 7.6  | Equivalent diagram of 240-V PHIL test bench                      | 130 |

| Figure 7.7  | Comparative test setup: a) HQ outlet; b) PHIL test bench         | 133 |

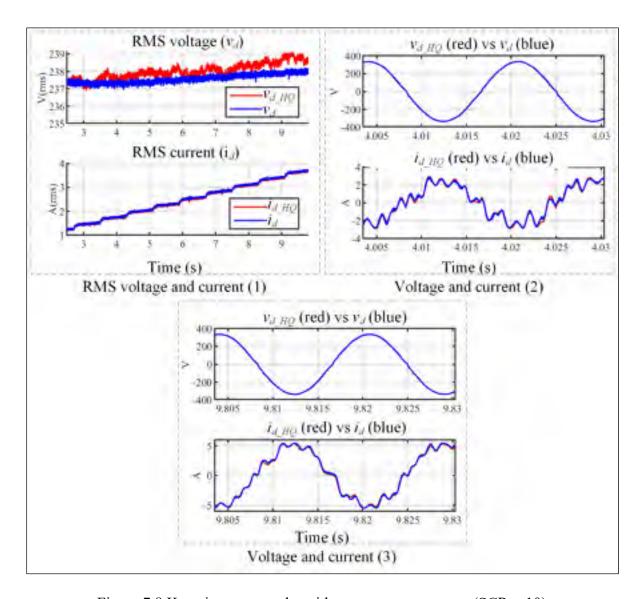

| Figure 7.8  | Kaco inverter results with strong power system (SCR = 10)        | 134 |

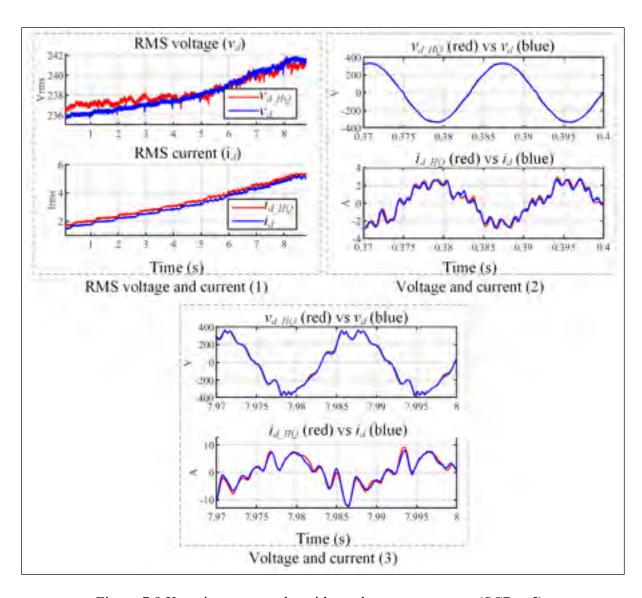

| Figure 7.9  | Kaco inverter results with weaker power system (SCR = 5)         | 136 |

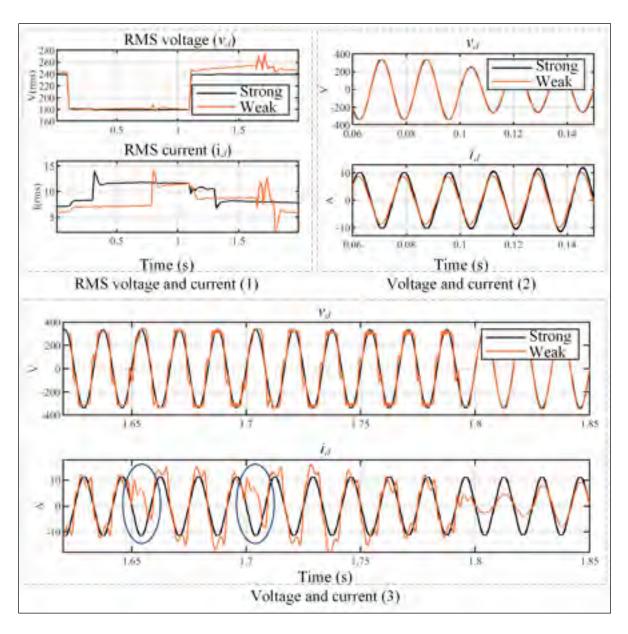

| Figure 7.10 | Voltage dips with strong/weak power system – SolarEdge inverter. | 138 |

#### LIST OF ABBREVIATIONS

AC Alternating current

ADC Analog-digital converter

BTLM Bergeron transmission line model

CEPRI China Electric Power Research Institute

CPU Central processing unit

CHIL Control hardware-in-the-loop

DAC Digital-analog converter

DC Direct current

DER Distributed energy resources

DIA Digital interface algorithm

DIM Damping impedance method

DT Dead time

DUT Device under test

EGRID Duke Energy Electrical Grid Research Innovation and Development

EMT Electromagnetic transient

FOH First-order hold

FPGA Field programmable gate array

FRT Frequency ride through

FSU-CAPS Florida State University Center for Advanced Power Systems

HIL Hardware in the loop

HVRT High voltage ride through

IREQ Institut de Recherche d'Hydro-Québec

ITM Ideal transformer method LVRT Low voltage ride through

NREL National Renewable Energy Laboratory

OFCIE Output filter characteristic impedance emulator

PA Power amplifier

PCD Partial circuit duplication

PHIL Power hardware in the loop

PLL Phase-locked loop

POC Point of connection

PV Photovoltaic

PWM Pulse-width modulation

RMS Root mean square

ROS Rest of system

RTE "Réseau de transport d'électricité" (power transmission system)

RTS Real-time simulator

SCC Short-circuit capacity

SCR Short circuit ratio

TFA Time-variant first-order approximation

TLM Transmission line model

VSC Voltage source converter

ZOH Zero-order hold

#### LIST OF SYMBOLS AND UNITS

#### **UNITS USED**

A Ampere

C Coulomb

Degree

dB Decibel

F Farad

H Henry

Hz Hertz

kA KiloamperekV KilovoltkW KilowattMW Megawatt

MVA Megavolt-voltampere (apparent power)

$\Omega$  Ohm rad Radian s Second V Volt

VA Voltampere (apparent power)

W Watt

#### SYMBOLS USED

C Transmission line capacitance

C<sub>f</sub> Output filter capacitance

$F_{sw}$  Switching frequency

$F_{swe}$  Effective switching frequency

G Transmission line conductance

I<sub>1</sub> Current left of separation point

I<sub>2</sub> Current right of separation point

### XXIV

| lPA                       | Power amplifier output current                                     |

|---------------------------|--------------------------------------------------------------------|

| is                        | Current on the emitting side of the transmission line              |

| $\mathbf{i}_{\mathbf{r}}$ | Current on the receiving side of the transmission line             |

| Kat                       | Wave attenuation factor                                            |

| 1                         | Length                                                             |

| L                         | Transmission line inductance                                       |

| L1                        | Power system side inductance                                       |

| L2                        | Equipment side inductance                                          |

| $L_{\mathrm{f}}$          | Output filter inductance                                           |

| Leq                       | Equivalent inductance of test bench                                |

| L <sub>HQ</sub>           | Equivalent inductance of Hydro-Québec laboratory electrical outlet |

| R                         | Transmission line resistance                                       |

| R1                        | Power system side resistance                                       |

| R2                        | Equipment side resistance                                          |

| $R_{\mathrm{f}}$          | Output filter resistance                                           |

| REQ                       | Equivalent resistance of test bench                                |

| $R_{HQ}$                  | Equivalent resistance of Hydro-Québec laboratory electrical outlet |

| S                         | Laplace variable                                                   |

| $V_1$                     | Voltage left of separation point                                   |

| $V_2$                     | Voltage right of separation point                                  |

| $V_{\mathrm{f}}$          | Voltage drop due to amplifier internal resistance                  |

| $V_{LL}$                  | Line-to-line RMS voltage                                           |

| $V_s$                     | Equivalent power system voltage                                    |

| Vd                        | Equipment (DUT) side voltage                                       |

| $\mathbf{V}_{\mathbf{S}}$ | Transmission line emitter side voltage                             |

| Vr                        | Transmission line receiver side voltage                            |

| τ                         | Time constant                                                      |

| t                         | time                                                               |

| Т                         | Sampling period                                                    |

RTS sampling period

Ts

us Forward wave

u<sub>r</sub> Backward wave

w<sub>s</sub> Backward wave (sending end)

w<sub>r</sub> Forward wave (receiver end)

x Distance

Y<sub>DUT</sub> ROS side admittance

z Discrete Laplace variable

Z<sub>C</sub> Characteristic impedance

Z<sub>EQ</sub> Equivalent impedance of test bench

Z<sub>DUT</sub> DUT side impedance

Z<sub>ROS</sub> ROS side impedance

Z1 Power system side equivalent impedance

Z2 Equipment side equivalent impedance

#### INTRODUCTION

Renewable energy integration, energy storage, emerging smart grids and ground transportation electrification are bringing new equipment onto power systems and new ways of operating it. Most of the new equipment includes power electronic converters and sophisticated control systems. Large-scale deployment of such new technologies on the transmission and distribution systems is presently limited by the ability of public utilities to validate their compliance with grid connection requirements, resilience, stability, compatibility and interoperability with other grid equipment.

To ensure a smooth integration of these new technologies and new future-grid operating modes, it no longer is sufficient to use the conventional approach, which consists in testing equipment and/or operating modes individually. A comprehensive approach is required whereby the system can be tested as a whole. The entire system means the actual physical equipment (e.g. microgrids, distributed generation equipment and storage), control systems (e.g., microgrid controllers), protection systems and the main power system. New means of testing must be developed, including cutting-edge simulation and testing techniques such as power hardware-in-the-loop (PHIL) and control hardware-in-the-loop (CHIL) (de Jong et al., 2012). Whereas CHIL simulation methods are well known and have been tested for a number of years, PHIL simulation techniques are the focus of ongoing research due to closed-loop operating stability issues.

#### **Drivers**

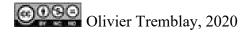

Hydro-Québec's research center (IREQ) already owns, continuously develops and operates a 25-kV (overhead and underground) distribution test line that includes energy storage, a diesel generator, various loads and a microgrid controller (Abbey, Brissette, Ouellet, & Zavoda, 2010; Awan, Abbey, Brissette, & Joós, 2014; Kleimaier, Brissette, Abbey, & Joós, 2013). IREQ also owns, develops and operates the Hypersim real-time power system simulator (Do, McCallum, Giroux, & De Kelper, 2001; Do et al., 1999; Paré, Turmel, Soumagne, & Casoria,

2003), marketed by Opal-RT Technologies Inc. The simulator is currently being used for CHIL testing (Sybille et al., 2010). The experimental test line and the Hypersim simulator are two separate facilities that are currently operated independently. Leveraging both of these large-scale facilities, Hydro-Québec is currently building a new PHIL/CHIL research and testing facility that will allow for the modeling of experimental transmission and distribution (T&D) systems. The new facility created by connecting the test line to the Hypersim simulator will greatly enhance IREQ's testing capacity. It will for example be used to develop and validate future grid technologies.

To create this new facility, it will be necessary to design a dedicated power amplifier and develop an algorithm to interface this amplifier with the Hypersim simulator. This dissertation focuses on this last point, i.e. the development of a high-performance control interface between the simulator and the power amplifier that fully leverages the capacities of both components.

#### Operating principle of IREQ's PHIL facility

To help readers, a simplified illustration of the new IREQ facility is shown in Figure 0.1. The new facility comprises the 25-kV distribution test line located on IREQ's campus, the Hypersim simulator and a 7.5-MVA amplifier with no output transformer. The interface between the test line and the simulator will be provided by the power amplifier, based on a multicellular converter, as well as the closed-loop control algorithm, which is the main topic of this dissertation. The closed-loop system comprised of the Hypersim simulator and the power amplifier is called a "power simulator" ("SimP"), whose operating principle is described below.

The simulator calculates in real time the instantaneous voltage (Vsim) to be applied to the line. The amplifier boosts the voltage to the desired value and applies it to the line. At the same time, the line current is measured (Imes) and injected into the simulator thus achieving closed-loop operation. In this operating mode, the test line is virtually connected to the simulated power grid.

Figure 0.1 Illustration of the SimP research and testing facility

Using SimP will greatly enhance the line's test capabilities. The use of a simulated power system rather than an actual one will allow for the simulation of a variety of system conditions. It will be possible, for instance, to produce voltage dips and surges, generate realistic grid transient voltages at frequencies ranging from 0 Hz (DC) to a several kHz, study the impact of the grid on equipment connected to the line and study the impact of that equipment on the simulated grid. Using SimP will also make it possible to connect the test line to any grid by implementing the grid's simulation model in Hypersim. For example, the test line with its distributed generation equipment could be connected to any power system in the world. Manufacturers will, for instance, be able to use the new facility to develop and test the operation of various devices through a virtual connection to this simulated grid. Lastly, the proposed world-class research/testing facility will be unique in Canada. It will support

unprecedented tests that will help develop and validate future grid technologies, thus promoting the integration of renewable energy sources into power systems and enhancing research into the decarbonization of power generation.

#### Problem to be addressed (CHIL vs. PHIL)

Real-time hardware-in-the-loop (HIL) simulation consists in interfacing the actual equipment with a power system simulation model. Delays occur when signals are exchanged by the systems, mainly due to the real-time simulator (RTS) and the conversion between the digital (simulator) and analog (actual equipment) worlds. HIL systems can be divided into two broad categories. First, there are CHIL (or controller HIL) systems, where the actual equipment is a control system. The delays applied to the CHIL system do not create any special problem as the two systems are naturally decoupled. The equations used to simulate the electrical system are not instantaneously coupled with the control system, thus facilitating the decoupling. In the case of PHIL (power HIL) systems, the physical system under study is divided in two parts: an actual, physical part and a simulated part. It is this division that gives rise to the delays that break the simultaneity needed for the system to operate properly since the simulated equations cannot be solved instantaneously based on the electrical measurements made on the equipment. This is the fundamental problem with PHIL systems.

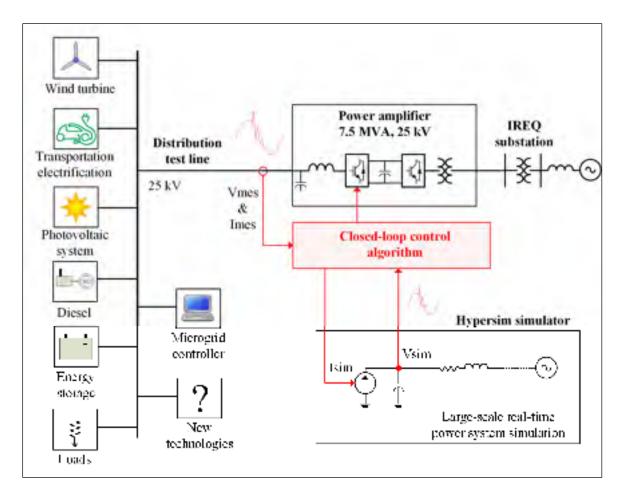

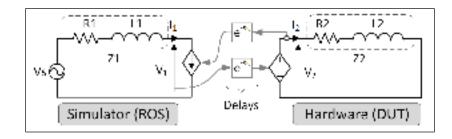

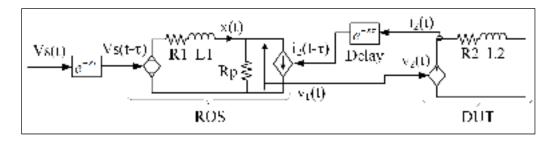

To illustrate the effect of these delays, consider the simplified electric circuit shown in Figure 0.2, comprising a source and two impedances. In this circuit, the current through impedance Z2 is the same as the current through impedance Z1.

Figure 0.2 Original simplified electric circuit

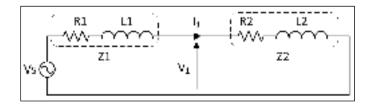

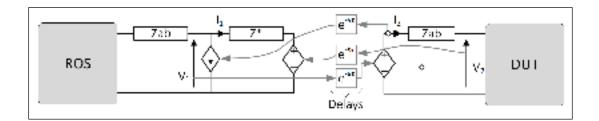

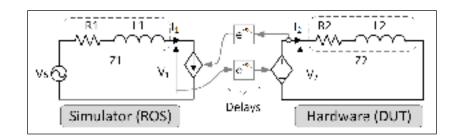

In a PHIL system, this electric circuit is deliberately divided in two: one part of the circuit (called "rest of system" or ROS) is modeled by a real-time simulator, while the other part of the circuit is the actual power equipment being tested (called "device under test" or DUT). One intuitive method for implementing this circuit separation is called the ideal transformer method; it consists in measuring the voltage and current on both sides of the separation point, then injecting these signals using controlled sources, as shown in Figure 0.3. If the signals were exchanged instantaneously,  $I_1$  would be strictly equal to  $I_2$ , and the same thing would hold for  $V_1$  and  $V_2$ . The PHIL circuit would then behave exactly like the original circuit (prior to separation).

Figure 0.3 Simplified PHIL system electric circuit

However, in practice, the exchange of signals between the two parts of the circuit cannot take place instantaneously, mainly due to communication, conversion and simulation delays as shown in Figure 0.4. These delays make it impossible for the currents and voltages on either side of the separation point to be equal, thus decoupling the system (which should normally remain coupled).

Figure 0.4 Practical implementation of a PHIL system

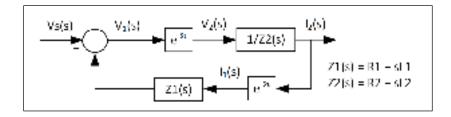

These delays alter currents and voltages, thus degrading the accuracy of results. They can also lead to system instability. Such instability could permanently damage the equipment under test and the power amplifier. To study the stability problem, it is possible to use the closed-loop block diagram in the Laplace domain, shown in Figure 0.5.

Figure 0.5 Closed-loop block diagram of PHIL system

An analysis of the stability of systems that include delays has demonstrated that this system becomes <u>unstable</u> for any delay ( $\tau$ ) greater than 0 when the magnitude of Z1(s) is greater than the magnitude of Z2(s) (M. H. Hong, S. Miura, Y. et al., 2009).

This potential instability due to interface delays is the main issue for PHIL systems as it considerably limits the operating range of such systems. For example, it is impossible to simulate power systems with low short-circuit capacities, islanded power systems or systems that contain supply disconnect switches. Furthermore, generating equipment under test generally includes an impedance that may be relatively low compared to the power system impedance. The development of higher performance digital interface algorithms (DIAs) is therefore necessary to achieve this high level of flexibility.

In the past, several DIAs were developed to mitigate the problems associated with the interface between the simulator and the power hardware. However, as the literature review will show, the range of validity of these digital interface algorithms is too limited to allow for the accurate modeling of complex and varied equipment as is the case for the SimP simulator.

#### Goal of thesis

The main goal of this thesis is to design a PHIL interface that is stable and accurate over a wide range of applications, independently of the equipment or power systems being simulated. The new digital interface algorithm (DIA) will need to be compatible with a 7.5-MVA @ 25-kV amplifier (i.e. high power electronics), with a large scale real-time simulation (based on the CPU technology) and with the connection of complex equipment. This DIA will also need to be implemented and validated experimentally on a reduced scale test bench.

The sub-goals of this thesis are:

- 1. Develop a new stability analysis method for PHIL systems that incorporates the notion of a hybrid system (analog-digital).

- 2. Design and build a reduced scale experimental test bench (3 kVA, 208 V<sub>LL</sub>) to replicate the behavior of the full-scale system (7.5 MVA @ 25 kV).

#### Contributions and spinoffs

The main contribution of this thesis is the full overall design of a PHIL system, including all constraints up to and including its implementation using industrial hardware and its use in power system studies. This includes the development of a method to better understand the mechanisms that lead to PHIL system instability and mitigation measures, the development of a DIA adapted to the typical, rigorous uses of such systems at IREQ, and the development and validation of an experimental PHIL test bench.

This work has been published in two peer-reviewed journals. Published in *IET Generation, Transmission and Distribution*, the first article deals with the analysis of the stability of PHIL systems (Tremblay, Fortin-Blanchette, Gagnon, & Brissette, 2017). Published in *IEEE Transactions on Energy Conversion*, the second article describes the development and experimental validation of a new method for interfacing PHIL systems (Tremblay, Rimorov, Gagnon, & Fortin-Blanchette, 2020). In addition, this work has been presented three times at

international conferences on PHIL systems (Tremblay, Gagnon, Giroux, & Slimani, 2015; Tremblay et al., 2018; Tremblay, Slimani, et al., 2017).

Finally, given the availability of the test bench developed through this work and the performance of the new DIA, the PHIL test bench was used to carry out a study on the transient response of residential photovoltaic inverters. This spinoff is a practical application of the method developed (Rimorov et al., 2020).

#### Methodology

The methodology used to complete this thesis work can be divided in four main stages:

- Modeling and simulation: A simulation environment capable of modeling complex systems

is essential to properly understand the phenomena under study and develop new DIAs.

Therefore, the environment provided by MATLAB/Simscape Electrical Specialized Power

Systems (SPS) has been used to model and simulate the PHIL electric circuits and digital

interface algorithms (DIAs) presented in this thesis.

- 2. Digital interface algorithm (DIA) development: The PHIL system stability analysis methods and the new DIAs can then be developed and improved in the simulation environment described in the first point.

- 3. Development and characterization of experimental test bench: Developing a test bench and mastering its operation are essential steps of the experimental validation process. It is therefore necessary to characterize the whole system, including its power amplifier, output filter, simulator, inputs-outputs, and field-programmable gate array (FPGA). This allows for the proper implementation of the DIA on the FPGA while taking into consideration all the system constraints.

- 4. Experimental validation: Experimental results (including tests on simple DUTs, such as passive loads, or more complex ones, such as a power system connected to photovoltaic inverters) will be compared with simulated cases to ensure the system is operating properly.

#### Thesis structure

To achieve the goals described above, this thesis is divided into seven chapters. The first chapter describes the typical environment in which a PHIL system is used, then reviews currently available DIAs. A new stability analysis method for PHIL systems that incorporates the notion of a hybrid system is then described in detail. The third chapter describes the exploratory attempts to develop a more performing DIA. Chapter four covers the development and validation of a new DIA suited to the IREQ environment. Chapter five describes in detail the experimental test bench specifically developed to implement a proof-of-concept version of the new DIA. Chapter six presents the experimental validation results obtained using the test bench and compares them with reference models. The seventh and last chapter describes how the PHIL system developed for this thesis was used by Hydro-Québec to study the transient response of residential photovoltaic inverters. Finally, concluding remarks and recommendations for future work are presented.

#### **CHAPTER 1**

#### BACKGROUND AND LITERATURE REVIEW

PHIL type simulations are increasingly being used in power system research due to the increased availability of real-time simulators and the growing capacity of amplifiers, on one hand, and the need to test increasingly complex equipment prior to their installation on the grid, on the other hand. The scientific community has yet to offer a general solution to the stability and accuracy problem that arises at the simulator-amplifier interface. It is therefore unsurprising to note the literature contains many articles on various interface methods and how they have been adapted to specific conditions. This chapter starts by defining the testing capabilities that a PHIL simulator should possess and assessing the ability of the main DIAs currently described in the literature to perform these tests. This chapter then reviews the technologies used by the main actors in the field of high-power PHIL systems (i.e. MW-order systems).

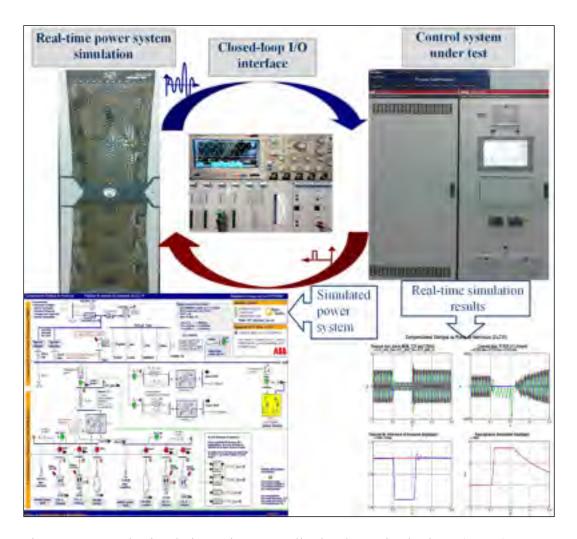

## 1.1 Real-time simulator and CHIL/PHIL applications

HIL (hardware-in-the-loop) simulation is widely used to validate the operation of hardware in a realistic simulated environment. Using this method, hardware can be tested under various scenarios that are generally not available under normal operating conditions. In power system research, HIL simulation allows for the testing of equipment under various grid contingencies. This enables the testing of equipment to ensure it operates properly prior to its commissioning, its testing under extreme operating conditions, the development of new functionalities, the training of future system operators and many more applications. There are two major families of HIL systems: those that only use the control module (controller HIL or "CHIL") and those that use a control system integrated with their electrical power system (power HIL or "PHIL").

The Hypersim simulator is mainly used to carry out CHIL type tests where the actual power equipment control system is connected to a simulated power system, as shown in Figure 1.1. The simulated model then includes the power circuitry of the equipment as well as the power

system to which the equipment is normally connected. This operating mode makes it possible to study the closed-loop dynamic performance of the actual control system of the equipment connected to its grid.

Typical applications include studies to validate the performance of protection relays, static VAR compensators and synchronous condensers control systems, as well as HVDC interconnections.

Figure 1.1 Sample simulation using controller hardware-in-the-loop (CHIL) system

The emergence of distributed energy resources (DERs) has changed the way equipment is tested. In these systems, electrical energy is generated using wind turbines and photovoltaic

panels, connected to energy storage systems, through power electric converters driven by advanced control systems. These converters can also provide ancillary services to the power grid, thus contributing to voltage and frequency regulation. In this kind of equipment, it is very difficult to dissociate the control system from its power circuitry, thus making CHIL testing especially difficult. In addition, it is sometimes impossible to develop the model required for CHIL testing as manufacturers (who often act as component assemblers) may not have detailed knowledge of the power circuitry.

To ensure the proper operation of these complex systems, it is necessary to carry out tests that consist in connecting the power equipment directly to a simulated grid in what is known as a PHIL system. The PHIL approach thus has the benefit of enabling the testing of equipment as a whole and not only its control system.

## 1.2 Typical uses of a PHIL system

Before developing or adapting a DIA for PHIL testing, it is necessary to define its typical uses, i.e. the types of tests that are to be performed and the hardware that may be tested. The DUT may be any electrical equipment, ranging from a simple passive load (e.g. resistive, inductive, capacitive or any combination of the three) to a more complex component (e.g. wind turbine, photovoltaic system or energy storage system, based on voltage-source converters). Furthermore, the DUT may consist in a combination of various interconnected components that form a complex distribution network.

The types of tests to be performed include tests that focus on the DUT's response to grid events, including low voltage ride through (LVRT), high voltage ride through (HVRT) and frequency ride through (FRT). These tests can be performed using any programmable voltage source, in an open-loop configuration where only the programmed voltage is applied to the equipment. However, under this kind of scenario, the interaction between the DUT and the power grid cannot be modeled, thus making it impossible to study phenomena such as voltage/VAR compensation or the effect of equipment inertial response on the grid frequency. Therefore, to

carry out more comprehensive studies, it is necessary to simulate a representative power grid and the DUT's response must be injected into the simulation through a closed-loop configuration. Examples of cases where closed-loop testing is required are provided below:

- DUT connected to a power grid with a low short-circuit ratio (SCR less than 10) 1.

- Testing in islanded mode, where the DUT only supplies power to local loads.

- Control tests of interactions between the DUT and the power grid to which it is connected.

- Ancillary service testing.

A digital interface algorithm (DIA) capable of handling all these tests is therefore essential. In addition, the selected DIA will need to ensure system stability without affecting the accuracy of results for all test cases.

### 1.3 Literature review and assessment of existing digital interface algorithms

This section provides an overview of the digital interface algorithms (DIAs) currently found in the literature. Each algorithm is assessed with respect to its ability to perform the tests listed in the previous section.

## 1.3.1 Ideal transformer method (ITM)

The ideal transformer method (ITM) described in the introduction is the most direct approach and the simplest one to implement (Brandl, 2017). On the other hand, two major constraints make its use difficult (M. Hong, Horie, Miura, Ise, & Dufour, 2009):

1. As mentioned above, to maintain stability, the equipment side inductance (L2) must always be greater than the sum of the simulator side series inductances, regardless of the interface delay.

\_\_\_

<sup>&</sup>lt;sup>1</sup> The short-circuit ratio (SCR) is defined as the ratio between the short-circuit capacity of the power system at the connection point and the rated capacity of the DUT.

2. A small delay (~1μs) promotes stability, while a large delay (~1ms) creates additional constraints on system impedance.

These constraints are incompatible with the PHIL approach since this DIA can become unstable, for example when an active DUT (i.e. one that supplies power) is connected to a power system that is islanded from the main system due to a switching operation. In this example, since the ROS impedance is greater than the DUT impedance, the system is unstable.

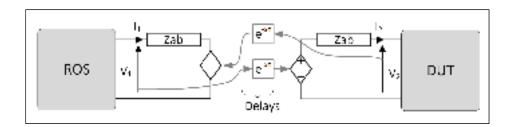

## 1.3.2 Partial circuit duplication (PCD)

Since the power grid is in general connected to the DUT through an impedance (Zab), it may be interesting to duplicate this impedance on both sides of the interface, as shown in Figure 1.2 (Paran, 2013). In this method, called partial circuit duplication (PCD), the voltages at each end of the impedance are exchanged with a delay of one simulator calculation step.

Figure 1.2 Partial circuit duplication

This technique has been used for over 30 years to decouple large calculation tasks in digital simulators. Off-line simulators, such as SPICE (Newton & Sangiovanni-Vincentelli, 1983), rely on this technique, which is based on relaxation, to separate the matrix of a large electrical system into several decoupled subsystems. Together with an iterative method, the solution obtained approaches the undecoupled system response (Dmitriev-Zdorov, 1996). For real-time simulators, it is very hard to achieve a sufficient accuracy due to the difficulty involved in iterating over calculation tasks (Kuffel et al., 1995). For PHIL systems, there are three problems:

- 1. If impedance Zab is located on the hardware side, it must be measured accurately to duplicate it on the simulator side. If impedance Zab is located on the simulator side, it must be physically inserted on the equipment side.

- 2. An error will be introduced since it is impossible to iterate between the two systems.

Although this DIA is stable for a wide range of operating conditions, the value of impedance Zab must be relatively large to ensure accurate results (Wei Ren, 2007), something that is not realistic for typical DUTs. In fact, the power grid is often connected to the DUT through a low impedance Zab, which is too limiting for our typical use cases.

## 1.3.3 Damping impedance method (DIM)

The damping impedance method (DIM) is a combination of the ideal transformer method (ITM) and the partial circuit duplication (PCD) method, with the addition of impedance Z\*, as shown in Figure 1.3 (Paran, 2013).

Figure 1.3 Damping impedance

For this configuration, it can be shown that if  $Z^*$  is strictly equal to the DUT impedance ( $Z_{\text{DUT}}$ ), the system will be absolutely stable, i.e. the error obtained at any given instant will not be cumulative (Wei Ren, 2007). In reality, measuring and "tracking" the value of  $Z_{\text{DUT}}$  can prove extremely difficult (Siegers & Santi, 2014). Although there are several methods for estimating the DUT impedance, they are difficult to use if the device is active, non-linear and/or complex (e.g. power converter).

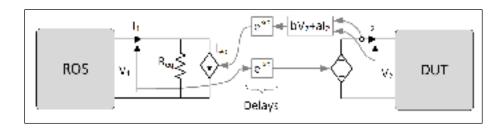

# 1.3.4 Time variant first-order approximation (TFA)

The time variant first-order approximation (TFA) method is based on the principle that the actual hardware can be modeled using a first-order linear system, i.e. a RL or RC circuit (Wu, Lentijo, & Monti, 2004). By estimating the DUT parameters and using a trapezoidal approximation, it is possible to obtain the values for a, b and  $R_{eq}$  that are needed to implement the impedance in nodal form. This method is illustrated in Figure 1.4.

Figure 1.4 First-order approximation

Although this method is interesting since it represents the equipment using simple RL model, it is subject to several constraints (Wei, Steurer, & Baldwin, 2008) that make its use difficult in our typical use case:

- 1. **Accuracy**: To achieve the desired accuracy, it is necessary to measure the R and L values of the equipment to estimate the values of R<sub>eq</sub>, b and a. This can be done through an online estimation using the recursive least-squares method, but the accuracy achieved will depend on the algorithm and the estimation noise.

- 2. **Instability**: The method is vulnerable to instabilities due to the inherently predictive nature of this method and the estimation algorithm. For example, an active DUT will be appear as a negative resistance, which could lead to instability.

- 3. Load type (RL or RC): The same approach can be used for a RC load. This will result in a voltage source on the simulator side and a current source on the equipment side. This will create an implementation problem since the power amplifier is in general a voltage source.

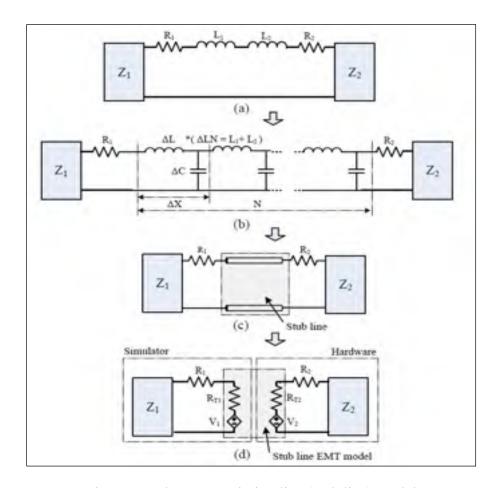

## 1.3.5 Transmission-line model (TLM)

The transmission-line model (TLM) is widely used in real-time power grid simulators to decouple calculation tasks since, by using the natural line propagation delay, it is possible to parallelize the calculations for both ends of the line without introducing any error provided the delay is greater than the simulator calculation step (Do et al., 1999; Gagnon et al., 2010).

For power simulators, it is possible to use a transmission line whose propagation delay is strictly equal to the delay between the simulator and the amplifier. The TLM equivalent circuit is shown in Figure 1.5 as it appears in (Yoo, 2013).

Figure 1.5 Short transmission line (stub line) model Taken from Yoo (2013)

This method has the benefit of always being numerically stable. However, it has several drawbacks that impede its use with PHIL systems:

- 1. Although necessary to model the characteristic impedance of the line, the addition of R<sub>T2</sub> on the equipment side causes Joule losses that may be significant. These losses should be compensated by oversizing the amplifier with respect to both power and voltage. To give the reader an order-of-magnitude estimate of the values involved, the SimP project amplifier has a rated capacity of 7.5 MVA at 25 kV, for a rated current of 173 A<sub>RMS</sub>. A current of this magnitude flowing through a typical 300 Ω, resistor would generate losses of 27 MW and a voltage drop of 52 kV, which is completely disproportionate relative to the amplifier ratings. In addition, the cooling system required for such a resistor would be disproportionately large compared with the rest of the system.

- 2. This method calls for the introduction of a shunt capacitor, whose capacitance is calculated to obtain the required propagation delay. Such a shunt capacitor may not exist, and its effect must be considered.

- 3. For a 50-µs calculation step, this would entail assuming the amplifier is connected to the simulator through a 15-km line. A realistic parametrization is therefore required to factor in this distance.

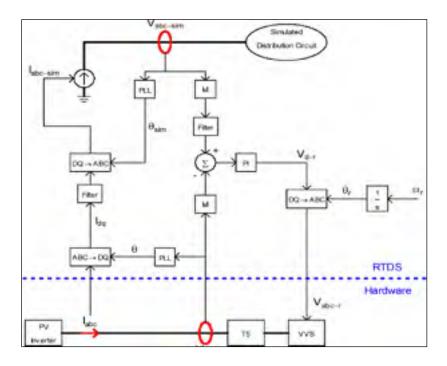

### 1.3.6 Park transform based method (DQ)

The Park transform can be used to model, through a change in reference frame, an alternating three-phase system as a two-phase system. When the three-phase system is balanced and has a negligible harmonic content, the two-phase system magnitudes are constant, thus greatly simplifying voltage-source inverter control algorithms. This technique is attractive for PHIL systems since it allows for the easy compensation of delays through rotating reference phase angle lead-lag adjustments (Langston et al., 2012). As shown in Figure 1.6, the amplitude of the simulator voltage (V<sub>abc-sim</sub>) becomes the reference signal for a voltage regulator whose output is the direct-axis voltage (V<sub>d-r</sub>). The DQ-ABC transform is then applied to allow the amplifier to generate the voltages. The equipment current I<sub>abc</sub> is then measured and converted into its rotating reference frame (ABC-DQ). This current is then injected into the simulation

using an inverse transform (DQ-ABC). Delays may then be compensated by adjusting the rotating reference frame phase-locked loop (PLL) lead-lag angle.

Figure 1.6 Park transform based interface Taken from Langston (2012)

The main drawback of this approach is its small bandwidth as voltage and current values are transmitted as phasors, i.e. the magnitude and angle at the fundamental system frequency (50/60 Hz), which makes it ill-suited to transient electromagnetic testing. For example, this method cannot model harmonic interactions between the simulated power grid and the DUT although these are common in power grid studies.

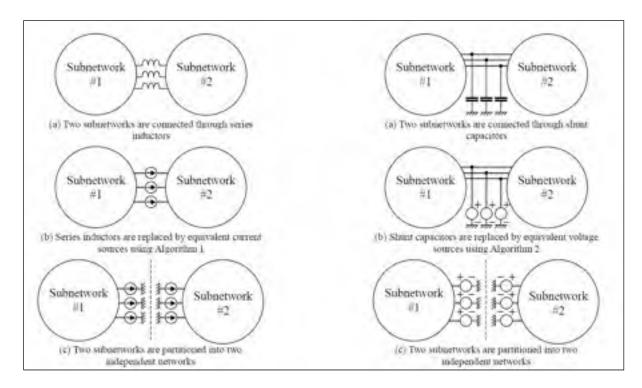

## 1.3.7 Explicit discretization of series inductor or shunt capacitor

The partitioning of subnetworks through the discretization of a series inductor or a shunt capacitor is described in (Noda, 2003) and shown in Figure 1.7. This method consists mainly in using an explicit numerical integration method to discretize the differential equation (where

the inductor is modeled as a historical current source while the capacitor becomes a historical voltage source).

Figure 1.7 Partitioning using an explicit integration method Taken from Noda (2003)

In general, inductor discretization is achieved using the trapezoidal method:

$$v_1(t) - v_2(t) = L \frac{d}{dt}i(t) \implies \frac{2(1 - z^{-1})}{T(1 + z^{-1})}I(z) = \frac{1}{L} \cdot (V_1(z) - V_2(z))$$

(1.1)

$$i(k) = i(k-1) + \frac{T}{2L} \left( v_1(k) - v_2(k) + v_1(k-1) - v_2(k-1) \right)$$

(1.2)

Implicit since i depends on  $v_{12}$  at same instant.

This method has the advantage of being A-stable, thus ensuring the stability of the system regardless of the calculation step used by the simulator. However, this absolute stability has a significant drawback: the method is implicit since current i(k) is instantaneously dependent on voltages  $v_1(k)$  and  $v_2(k)$ , as shown by equation (1.2). It is therefore to solve the equations for the whole system simultaneously. Hence, this method cannot be used for a PHIL system since the voltage at one of the two ends is in fact obtained with a delay of one calculation step.

To overcome this problem, (Noda, 2003) suggests using a linear extrapolation for the voltage that is not instantaneously available. This amounts to replacing the trapezoidal integrator with a two-step explicit linear method (second-order Adam-Basforth method):

$$v_1(t) - v_2(t) = L \frac{d}{dt} i(t) \implies \frac{2(1 - z^{-1})}{T(3 - z^{-1})} I(z) = \frac{1}{L} \cdot (V_1(z) - V_2(z))$$

(1.3)

$$i(k) = i(k-1) + \frac{T}{2L} \left( 3v_1(k-1) - 3v_2(k-1) - v_1(k-2) + v_2(k-2) \right)$$

(1.4)

Although its reliance on an explicit model allows for the exact expression of the inductor current, this method has some drawbacks that hinder its use with PHIL systems:

- The second-order Adam-Basforth (AB) method is not A-stable (Ashourloo, Mirzahosseini,

& Iravani, 2018), i.e. it may become unstable depending on system poles.

- 2. It is necessary to inject current on the amplifier side, but this amplifier is generally a voltage-source inverter.

- 3. The voltage extrapolation at both ends quickly becomes inaccurate during discontinuities or transient phenomena with a significant harmonic content, which is generally the case when transient events occur on the power grid.

## 1.4 Review of technologies used by major PHIL actors

Emerging at the start of the 2000s (Ayasun et al., 2003; Woodruff, Steurer, & Sloderbeck, 2004; Wu et al., 2004), the field of PHIL simulation has evolved steadily. Several major actors

currently operate MW-scale PHIL systems, including Florida State University Center for Advanced Power Systems (FSU-CAPS), Duke Energy Electrical Grid Research Innovation and Development (eGRID) (Clemson University, North Charleston, SC, USA) and National Renewable Energy Laboratory (NREL) Flatirons Campus (Boulder, CO, USA).

The FSU-CAPS system—commonly referred to as the "Advanced Prototype Power Test Bed"—consists of a set of AC and DC amplifiers connected to a digital simulator (Schoder, Langston, & Steurer, 2013). The bandwidth of these amplifiers is about 1 kHz; a transformer raises the output AC voltage from 416 V to 4.16 kV. At the simulator-amplifier interface, the ideal transformer method (ITM) (Steurer, Edrington, Sloderbeck, Ren, & Langston, 2010) and the damping impedance method (DIM) (Langston et al., 2015) have been used with several limitations with regards to their accuracy and stability. In fact, delays of the order of 350 µs have been observed between the reference and measured voltages (Steurer et al., 2010). Stability issues are avoided by using a more conservative DIA, based only on the fundamental frequency (Langston et al., 2012).

The Clemson University system—called "15-MW Grid Simulator"—consists in an amplifier designed by TECO-Westinghouse Motor Company (Ledezma et al., 2013) connected to a digital simulator. This amplifier has a 800-Hz bandwidth; a transformer raises the output AC voltage from 4.16 kV to 23.9 kV (Fox & Gislason, 2014). The ideal transformer method (ITM) is used; open-loop delays of 83 µs have been observed (McKinney, Fox, Collins, Bulgakov, & Salem, 2016).

Finally the NREL *Controllable Grid Interface* (GCI) is based on ABB's ACS6000 drive (converter) (Koralewicz, Gevorgian, Wallen, Merwe, & Jörg, 2016). The output voltage of the 7-MVA amplifier is obtained through magnetic addition using a transformer expressly designed for this application. The amplifier receives reference voltage magnitude and angle setpoints (at the fundamental frequency); a method is used to compensate for delays, which can be of the order of 2 ms (Koralewicz, Gevorgian, & Wallen, 2017). Although the system is

designed to operate at frequencies near 60 Hz, the amplifier has a 1-kHz bandwidth. The use of an interface method based on the fundamental frequency helps avoid stability issues.

Several lessons can be drawn from the experiences of these pioneers in the field of high-power PHIL simulation. First, it is worth noting that the results obtained by them are generally acceptable for tests the focus exclusively on DUT behavior. To assure DIA stability, low-impedance systems are used, which is tantamount to performing open-loop tests since the DUT has little or no impact on the simulated grid.

Second, the presence of a transformer at the output of the amplifier is a major drawback since it can easily saturate under the conditions below:

- Subsynchronous voltage oscillations (e.g. during an event on a series-compensated grid).

- Voltage with DC component.

- Voltage recovery after fault.

Saturation will decrease and distort the output voltage. In addition, the amplifier must be oversized since it must supply the saturation current. The fault could be cleared at a specific time to avoid saturating the transformer, but this would not be realistic since the exact fault clearance time is not usually known. Another solution would be to design a transformer with an appropriately sized magnetic circuit, but such a device would be extremely large and expensive.

Third, the observed delays between the simulator and the amplifier must be minimized to reduce uncertainty and stability issues. Finally, the selected DIA must be capable of replicating complex phenomena for any DUT connected to any ROS, including low short-circuit capacity power grids.

#### 1.5 Summary

In short, existing digital interface algorithms (DIAs) found in the literature do not allow for the implementation of a general PHIL system, i.e. one that remains stable and accurate regardless

of its operating conditions. The methods developed until now perform in general well, but only for special cases, thus making them ill-suited to our application.

Although major laboratories currently operate high power PHIL systems similar to the system under development at IREQ, their performance does not meet our specifications. Commercially available products are unfortunately not designed for this type of application and do not have the required performance.

To efficiently integrate its various components, a comprehensive approach is being taken to design IREQ's PHIL system. This comprehensive approach considers all the components of the system: power amplifier, digital simulator and interface methods. Since stability is the main issue to be addressed for PHIL systems, the next chapter will describe a new stability analysis method that takes into consideration their technological particularities.

#### **CHAPTER 2**

#### NEW PHIL SYSTEM STABILITY ANALYSIS METHOD

#### 2.1 Introduction

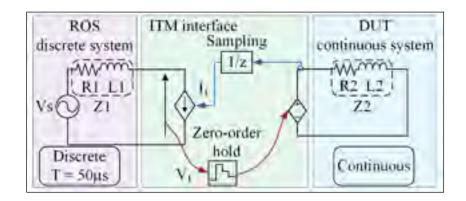

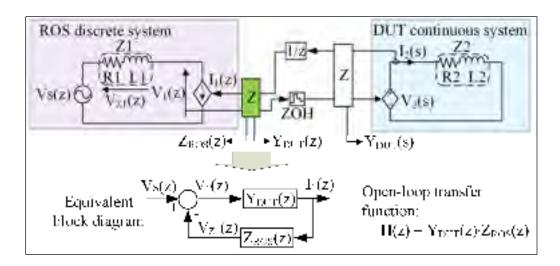

The simplified circuit shown in Figure 0.4 (reproduced below for the reader's convenience) is often used to investigate the stability of PHIL systems.

Figure 2.1 Intuitive implementation of PHIL circuit separation<sup>2</sup>

As demonstrated repeatedly (Guillo-Sansano, Roscoe, Jones, & Burt, 2014; M. H. Hong, S. Miura, Y. et al., 2009; Kotsampopoulos, Lehfuss, Lauss, Bletterie, & Hatziargyriou, 2015; G. Lauss, Lehfuss, Viehweider, & Strasser, 2011; G. F. Lauss et al., 2016; W. Ren et al., 2011; Alexander Viehweider, Lauss, & Felix, 2011; A. Viehweider, Lehfuss, & Lauss, 2012; Wei et al., 2008), the closed-loop stability of such systems can be maintained if the value of the ROS impedance (Z1) is less than the value of the DUT impedance (Z2) at all frequencies. This stability relation is valid if both the ROS and the DUT are analog (i.e. continuous) systems. However, in an actual PHIL system such the system shown in Figure 2.2, the ROS is a discrete system since the governing equations are solved using the simulator's numerical integration method and the DUT is a continuous system since the behavior of the power equipment is driven by the laws of physics. The system is therefore hybrid (discrete-continuous) and the

<sup>&</sup>lt;sup>2</sup> A large resistor, not shown in this figure, is inserted in parallel with the current source to avoid a series connection with inductor L1. The effect of this resistor is neglected.

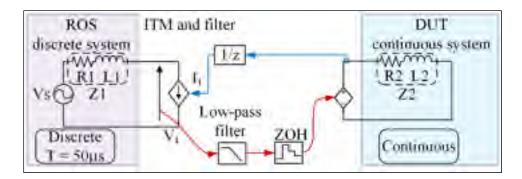

interface is implemented using a sampler (unit delay 1/z), which models the analog-digital conversion (ADC), and a zero-order hold (ZOH) block, which models the digital-analog conversion (DAC).

Figure 2.2 Hybrid model of a PHIL system

This system was simulated in the MATLAB/SPS environment, which can be used to model continuous systems (simulated using variable step algorithms) and discrete ones in the same simulation environment. The system is discretized using a 50-µs sampling period (T), which is a typical value for power grid simulations (Gagnon et al., 2010). Two sets of parameters were used for this simulation (see Table 2.1). In both cases, the ROS has a short-circuit capacity (SCC) of 150 MVA, with a X/R³ ratio of 30 and a rated voltage of 14.4 kV, which are typical single-phase values at the output of a 47-MVA distribution substation transformer.

Table 2.1 Sets of parameters

| Parameter                                      | Case 1 $(Z1/Z2 = 0.1)$                                                           | Case 2 $(Z1/Z2 = 0.67)$                                                     |

|------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| $\begin{bmatrix} R1 \\ L1 \end{bmatrix}$ $-Z1$ | $\begin{array}{c c} 0.0460 \Omega \\ 0.0036 \text{ H} \end{array}$ SCC = 150 MVA | $\begin{bmatrix} 0.0460 \ \Omega \\ 0.0036 \ H \end{bmatrix}$ SCC = 150 MVA |

| R2<br>L2 Z2                                    | $\begin{array}{c} 0.4600 \ \Omega \\ 0.0360 \ H \end{array}$ SCC = 15 MVA        | $0.0690 \Omega$<br>0.0054  H SCC = 100 MVA                                  |

$<sup>^{3}</sup>$  The X/R ratio is the ratio between the inductive and resistive components of the impedance at the fundamental frequency.

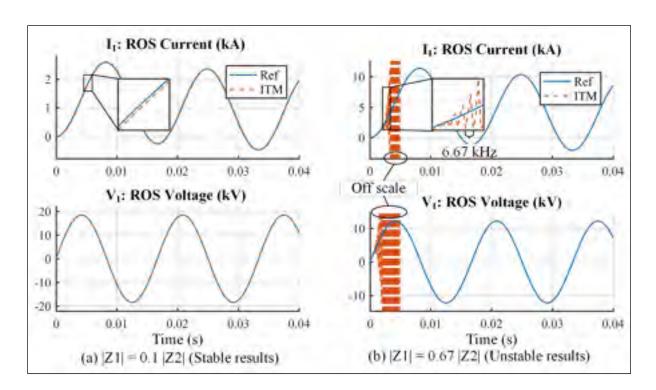

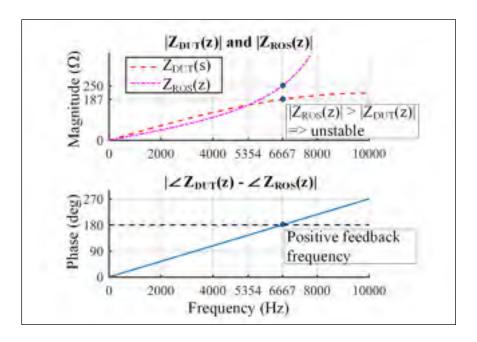

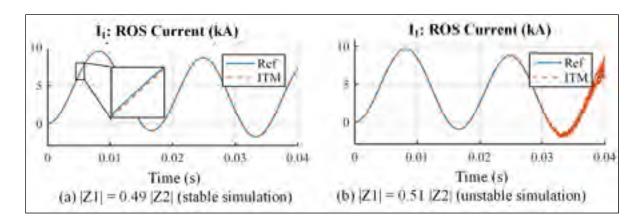

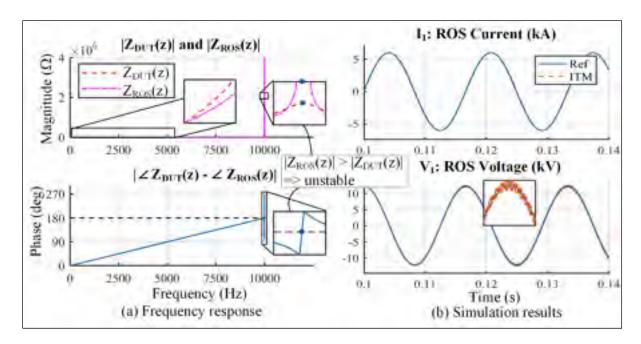

Let us start with Case No. 1, where impedance Z1 is a tenth of impedance Z2. The simulation results presented in Figure 2.3 (a) show the current and voltage at the interface point, on the simulator side, relative to an undecoupled reference system (such as the system shown in Figure 0.4). The PHIL system simulation results are stable and properly match the reference case. Case 2 should also be stable since impedance Z1 is 1.5 times less than impedance Z2 (|Z1| / |Z2| = 0.67). However, the simulation results shown in Figure 2.3(b) indicate that the PHIL system is in fact unstable, with an oscillation frequency of 6,667 Hz.

Figure 2.3 Simulation results for hybrid PHIL system

Unexpected according to existing analysis methods, this behavior will be analyzed in detail in this chapter using a new stability analysis method designed for closed-loop hybrid systems (Tremblay, Fortin-Blanchette, et al., 2017). It has been found that the development of a stability analysis method must take into consideration sampling effects at the analog-digital interface. In addition, the development of a method that allows for the independent analysis of both systems (ROS and DUT) will simplify the development of instability mitigation techniques.

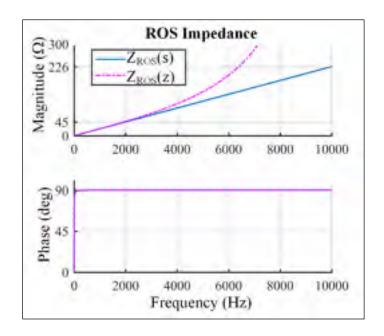

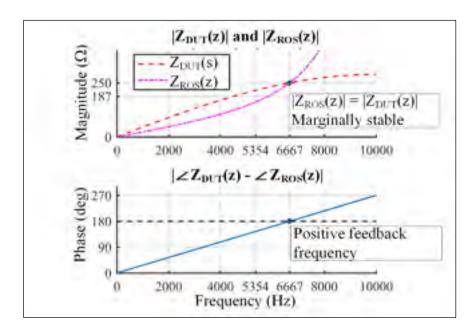

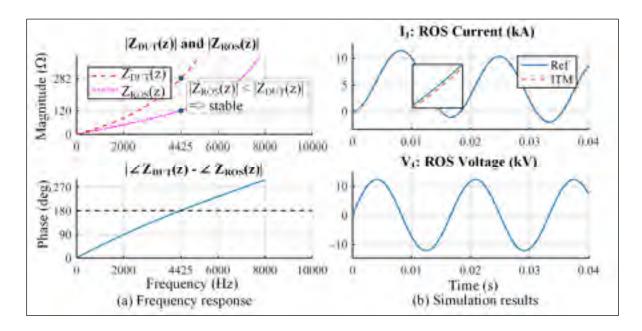

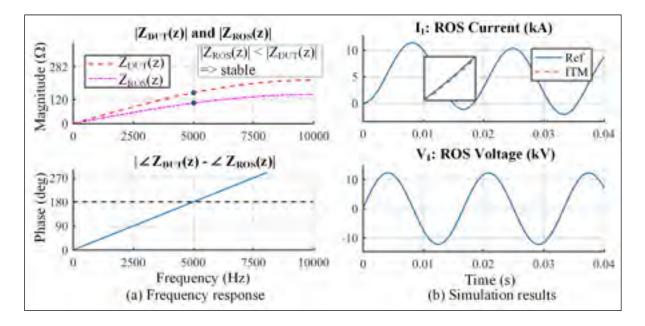

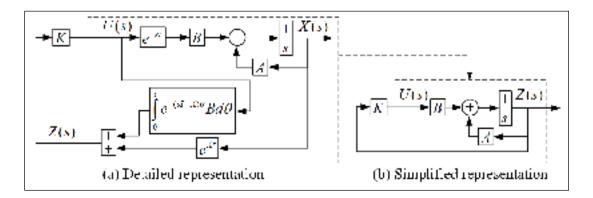

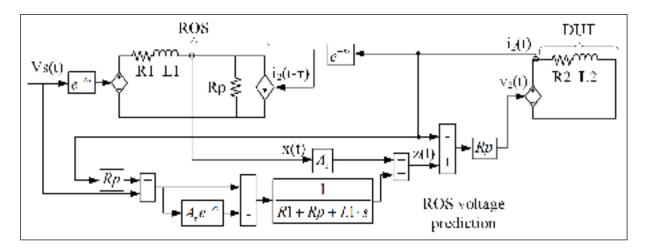

## 2.2 Decomposition of system into two equivalent impedances

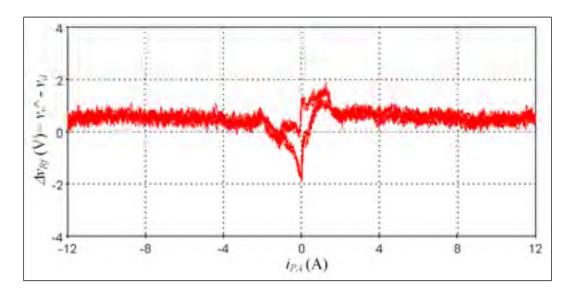

Used to assess the stability of continuous closed-loop systems, the Nyquist diagram is in general the approach used by researchers to study the stability of PHIL systems (G. Lauss et al., 2011; Lentijo, D'Arco, & Monti, 2010; A. Viehweider et al., 2012). However, as mentioned above, stability analysis cannot assume a fully continuous system since several significant aspects of system implementation would otherwise be ignored, including sampling and numerical integration effects. In addition, it is difficult to assess the impact of the various factors that affect the stability of PHIL systems using Nyquist diagrams since the ROS and the DUT are treated as a whole system. To overcome this challenge, a new stability analysis method is proposed to take into consideration the discrete modeling of the impedance on both sides of the separation point (by factoring in DUT sampler-hold block effects and the approximate numerical integration used for the ROS). By independently obtaining the frequency response of the two discrete systems, it will be possible the evaluation the stability of the system and identify proper mitigation measures to ensure closed-loop stability.