# Optimized Multilevel Inverters and Modulation Techniques for Power Electronics Applications

by

# Mohammad SHARIFZADEH

# MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT OF THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, APRIL 21ST, 2021

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

It is forbidden to reproduce, save or share the content of this document either in whole or in parts. The reader who wishes to print or save this document on any media must first get the permission of the author.

#### **BOARD OF EXAMINERS**

#### THIS THESIS HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Kamal Al-Haddad, Thesis Supervisor Department of electrical engineering, École de Technologie Supérieure

Mr. Gabriel J. Assaf, Chair, Board of Examiners Department of electrical engineering, École de Technologie Supérieure

Mr. Ambrish Chandra, Examiner Department of electrical engineering, École de Technologie Supérieure

Mr. Handy Fortin Blanchette, Examiner Department of electrical engineering, École de Technologie Supérieure

Mr. Sheldon Williamson, External Examiner Department of Electrical, Computer and Software Engineering, Ontario Tech University

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENTED OF A BOARD OF EXAMINERS AND THE PUBLIC

APRIL 1ST, 2021

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **ACKNOWLEDGMENT**

"The man can have nothing but what he tries for"

I would like to say my gratitude and appreciation to all people who have accompanied me during my doctorate study and during the writing of my dissertation with their great deal of support and assistance.

Firstly; from the bottom of my heart, I would like to express big and a special thanks to my PhD supervisor Professor Kamal Al-Haddad, for his continued support and patience, for his friendly manner, for his advice and guidance, for his thoughtful comments and recommendations, throughout this research project. I want to greatly appreciate him for all of the opportunities that you gave me for my future professional life. I hope that I could stratify him by doing my researches and studies.

I greatly appreciate my honorable and respectful member of my PhD committee who patiently reviewed my thesis. I would also like to thank all of my friends and colleagues who helped me in my studies and in my life. I could not have completed this dissertation without their sincere and friendly support and help. I never forget it.

Finally, I am very grateful to my family especially to my parents for their wise counsel and sympathetic ear. You are always there for me.

### Onduleurs Multiniveaux Optimisés et Techniques De Modulation Pour Les Applications D'Électronique De Puissance

#### Mohammad SHARIFZADEH

#### **RÉSUMÉ**

L'objectif principal de cette thèse est d'optimiser les techniques de modulation et les topologies d'onduleurs multiniveaux pour atteindre une efficacité plus élevée dans les applications d'électronique de puissance. Parmi les onduleurs conventionnels multiniveaux, les technologies compactes comme la cellule-U compacte est particulièrement intéressante pour les applications monophasées en raison de la structure continue de source CC. La cellule-U compacte apparaissait comme une topologie prometteuse qui pouvait trouver son chemin vers l'industrie, mais, elle se heurte à quelques inconvénients lorsqu'elle est étendue pour générer plus de niveaux. Le principal inconvénient est le problème de l'équilibrage de la tension des condensateurs qui nécessite une optimisation profonde pour atteindre une topologie d'onduleurs multiniveaux compacts innovantes et fiables. De même que l'optimisation de la topologie des onduleurs, les techniques de modulation doivent être optimisées pour améliorer l'efficacité des onduleurs dans les applications ciblées. Bien que les techniques populaires comme : « la Méthode du Vecteur Spatial et MLI Sinusoïdale » peuvent montrer leurs performances fiables, elles ont une fréquence de commutation élevée ce qui augmente les pertes de puissance. D'autre part, l'Élimination Sélective d'Harmoniques-MLI et l'Atténuation Sélective d'Harmoniques-MLI ont été introduites comme techniques prometteuses à basse fréquence de commutation où, elles peuvent être les candidats appropriés pour l'optimisation et l'utilisation dans les applications de haute puissance des onduleurs à multiniveaux. Comme principal effort d'optimisation de l'Élimination Sélective d'Harmoniques et de l'Atténuation Sélective d'Harmoniques, un nouvel angle de commutation a été obtenu pour une forme d'onde de tension à basse fréquence de commutation grâce à l'analyse mathématique précise sur les harmoniques triples pour auto-éliminer toutes les harmoniques triples sans faire de calculs supplémentaires. Ensuite, les harmoniques non triples déterminées sont éliminées ou atténuées par le fonctionnement normal de l'Élimination Sélective d'Harmoniques ou de l'Atténuation Sélective d'Harmoniques. Par conséquent, les amplitudes d'harmoniques maximales sont contrôlées tandis que la fréquence de commutation est au minimum.

Dans le prochain travail, l'Élimination Sélective d'Harmoniques est conçue de manière optimale pour les onduleurs triphasés 4 fils afin de fournir à la fois des charges symétriques et asymétriques en fonctionnement à basse fréquence de commutation. L'Élimination Sélective d'Harmoniques a été conçue de manière adaptable à la fois pour les deux configurations à 4 fils de l'onduleur à Point Neutre Fixe 3 phases, 4 branches 4 fils et 3 branches 4 fils. Il a été démontré que l'Élimination Sélective d'Harmoniques est plus compatible avec la configuration 3 branches 4 fils sur 4 branches 4 fils en termes de distorsion harmonique de la tension de phase de sortie, des calculs des angles de commutation et de la complexité de conception ainsi que des pertes de puissance. Le travail suivant présente une stratégie hybride de la technique de modulation l'Atténuation Sélective

d'Harmoniques pour contrôler la Tension en Mode Commun dans les onduleurs triphasés. Dans tous les travaux précédents où une solution logicielle basée sur les techniques de modulation était utilisée pour contrôler la Tension en Mode Commun, la technique appliquée a été conçue sur la base d'une sélection appropriée du vecteur de commutation. Toutefois, le travail proposé dans cette thèse, la Tension en Mode Commun est contrôlée sur la base de l'analyse harmonique afin de formuler la Tension en Mode Commun dans la technique hybride de l'Atténuation Sélective d'Harmoniques. Il a été montré que la Tension en Mode Commun a notablement été réduite par l'élimination des harmoniques triples tandis que le rapport de fréquence de commutation est maintenu sous 1 kHz. Enfin, les derniers travaux présentent un nouvel onduleur multiniveaux compact, appelé topologie Cellule-E compacte. La Cellule-E compacte est une optimisation en profondeur de la génération précédente d'onduleurs multiniveaux compacts; la Cellule-U compacte va atteindre d'autres niveaux de tension de sortie, réduire le nombre de composants et simplifier l'équilibrage de la tension des condensateurs. La Cellule-E compacte a été créé sur la base de l'idée d'étendre les condensateurs de manière horizontale contrairement à la manière verticale, ce qui se traduit par une structure plus optimisée par rapport à la Cellule-U compacte. Il a été démontré que la Cellule-E compacte peut être une topologie alternative appropriée et fiable pour remplacer la Cellule-U compacte.

Tous les travaux sont entièrement étayés par des analyses et des discussions théoriques, des simulations et des expérimentations.

**Mots-clés :** Onduleurs Multiniveaux, Techniques de Modulation à Faible Fréquence de Commutation, Élimination Sélective d'Harmoniques, Atténuation Sélective d'Harmoniques, Cellule-U Compacte, Cellule-E Compacte.

# Optimized Multilevel Inverters and Modulation Techniques for Power Electronics Applications

#### Mohammad SHARIFZADEH

#### **ABSTRACT**

The main goal of this thesis is to optimize the modulation techniques and multilevel inverter topologies to reach a higher efficiency in power electronics applications. Among conventional multilevel inverters, compact topologies like Packed U-Cell is interesting particularly for single phase applications because of single dc source structure. Five-level Packed U-Cell appeared as a promising topology that could find its way to industry; but, it confronts some drawbacks when it is extended to generate more levels. The main drawback is the capacitor voltage balancing issue which demands a deep optimization to reach a novel and reliable compact multilevel inverter topology. Along with optimization of the inverter topology, modulation techniques need to be optimized to enhance the inverters efficiency in the targeted applications. Although popular techniques like SVM and SPWM could show their reliable performance, they have high switching frequency which increases power losses. On the other hand, SHE-PWM and SHM-PWM were introduced as a promising low switching frequency techniques where, they can be the appropriate candidates for optimization and utilization in high power applications of multilevel inverters. As the primary effort for optimization of the SHE and SHM, a new switching angles has been obtained for a low switching frequency voltage waveform through the precise mathematic analysis on the triplen harmonics to self-eliminate all triplen harmonics without doing any extra calculations. Then, the determined non-triplen harmonics are eliminated or mitigated by the normal operation of the SHE or SHM. Therefore, maximum harmonics amplitudes are controlled while the switching frequency is at minimum.

In the next work, SHE is optimally designed for 3phase 4wire inverters as to supply both symmetrical and asymmetrical loads under low switching frequency operation. SHE has been adaptably designed for both 4wire configurations of 3phase NPC inverter; 4leg 4wire and 3leg 4wire. It has been shown that SHE is more compatible with 3leg 4wire configuration over 4leg 4wire one in terms of harmonic distortion of output phase voltage, switching angles calculations and design complexity as well as power losses. Next work presents a hybrid strategy of SHM modulation technique for controlling CMV in 3phase inverters. In all previous works where software solution based on the modulation techniques was used to control CMV, the applied technique was deigned based on the proper selection of the switching vector. However, it the proposed work in this thesis, the CMV is controlled based on the harmonic analysis in order to formulize CMV in the hybrid SHM technique. It was shown that CMV is notably reduced by elimination of triplen harmonics while the switching frequency ratio is kept under 1KHz. Finally, last work introduces a novel compact multilevel inverter so-called as Packed E-Cell topology. Packed E-Cell is a deep optimization of previous generation of compact multilevel inverter; Packed U-Cell to reach further output voltage levels, reduced components counts and simplicity in capacitor voltage balancing. Packed E-Cell has been established based on the idea of extending the capacitors in

horizontal way unlike vertical way which results in more optimized structure compared to Packed U-Cell. It was shown that the Packed E-Cell can be a suitable and reliable alternative topology to replace Packed U-Cell.

All works are fully supported by theoretical, simulation and experimental analyses and discussion.

Keywords: Multilevel Inverters, Low Switching Frequency Modulation Techniques,

Selective Harmonic Elimination, Selective Harmonic Mitigation, Packed U-

Cell, Packed E-Cell.

# TABLE OF CONTENTS

|            |          |                                                       | Page |

|------------|----------|-------------------------------------------------------|------|

| INTRO      | DUCTIO   | ON                                                    | 1    |

| CHADT      | CCD 1    | A CUDATEN ON CONVENTIONAL MULTIPLEMEL VOLTACE         |      |

| CHAP       | IEK I    | A SURVEY ON CONVENTIONAL MULTILEVEL VOLTAGE           |      |

|            |          | SOURCE INVERTERS TOPOLOGIES AND MODULATION            | C    |

| 1 1        | Interedu | TECHNIQUES                                            |      |

| 1.1<br>1.2 |          | ction                                                 |      |

| 1.2        | 1.2.1    | vel Voltage Source Inverters Topologies               |      |

|            | 1.2.1    | Diode Clamped Inverter                                |      |

|            | 1.2.2    | Flying Capacitor Inverter                             |      |

|            | 1.2.3    | Cascaded H-Bridge Inverter                            |      |

| 1.2        |          | Packed U-Cell Inverter                                |      |

| 1.3        |          | vel Voltage Source Inverters Topologies               |      |

|            | 1.3.1    | High Switching Frequency Modulation Techniques        |      |

|            | 1.3.2    | Sinusoidal Pulse Width Modulation (SPWM) Technique    |      |

|            | 1.3.3    | Space Vector Modulation (SVM) Technique               |      |

|            | 1.3.4    | Hysteresis Current Control                            |      |

|            | 1.3.5    | Low Switching Frequency Modulation Techniques         |      |

|            | 1.3.6    | SHE-PWM Technique                                     |      |

|            | 1.3.7    | Fourier Series Expression                             | 21   |

|            | 1.3.8    | Fourier Decomposition for Different Voltage Waveforms |      |

|            | 1.3.9    | Bipolar Voltage Waveform                              |      |

|            | 1.3.10   | Unipolar Voltage Waveform                             |      |

|            | 1.3.11   | Multilevel Voltage Waveform                           |      |

|            | 1.3.12   | SHE Equations for 1/3-Phase Inverters                 |      |

|            | 1.3.13   | SHE Equations Solving Strategies                      |      |

|            | 1.3.14   | Repetition Methods                                    |      |

|            | 1.3.15   | Walsh Functions                                       |      |

|            | 1.3.16   | Resultant Theory                                      |      |

|            | 1.3.17   | Polynomial Homotopy Method                            |      |

|            | 1.3.18   | Optimization Techniques                               |      |

|            | 1.3.19   | SHM-PWM Technique                                     |      |

|            | 1.3.20   | SHM versus SHE Technique                              |      |

| 1.4        | State of | the Art and Originality of the research               | 40   |

| CHAPT      | ΓER 2    | SELECTIVE HARMONIC MITIGATION BASED SELF-             |      |

|            |          | ELIMINATION OF TRIPLEN HARMONICS FOR SINGLE-PHAS      | SE   |

|            |          | FIVE-LEVEL INVERTERS                                  |      |

| 2.1        | Introdu  | ction                                                 |      |

| 2.2        |          | tional Single-Phase SHM-PAM Technique                 |      |

|            | 2.2.1    | 5-Level Inverter and Associated Waveform              |      |

|            | 2.2.2    | Single-Phase SHM-PAM principle                        |      |

| 2.3  | Self-Eli | mination of All Triplen Harmonics                                      | 51  |

|------|----------|------------------------------------------------------------------------|-----|

|      | 2.3.1    | Proposed Condition for Two Switching Angles ( $\alpha_1 \& \alpha_2$ ) |     |

|      | 2.3.2    | A General Solution for Self-Elimination of Triplen Orders in Other     |     |

|      |          | Multilevel Voltage Waveforms                                           | 55  |

|      | 2.3.3    | Comparative Study among Conventional SHM-PWM/PAM and                   |     |

|      |          | Modified SHM-PAM Techniques                                            | 57  |

| 2.4  | Mathem   | natical Analysis of Proposed Conditional for Two Switching Angles      |     |

|      | 2.4.1    | Harmonic Amplitude                                                     |     |

|      | 2.4.2    | Voltage THD                                                            | 61  |

| 2.5  | Results  | Discussion                                                             | 63  |

|      | 2.5.1    | Analytical Comparison of Harmonic Amplitudes                           | 64  |

|      | 2.5.2    | Experimental Evaluation of Single-Phase CHB Performance under          |     |

|      |          | Linear/Nonlinear Loads                                                 | 66  |

| 2.6  | Conclus  | sions                                                                  | 70  |

|      |          |                                                                        |     |

| CHAP | TER 3    | NEW CONSTRAINT IN SHE-PWM FOR SINGLE PHASE                             |     |

|      |          | INVERTER APPLICATIONS                                                  |     |

| 3.1  |          | ction                                                                  |     |

| 3.2  | -        | d SHE-PWM for Single-Phase Systems                                     |     |

|      | 3.2.1    | Modified PUC (MPUC) Inverter                                           |     |

|      | 3.2.2    | Conventional Single-Phase SHE Technique                                |     |

|      | 3.2.3    | Proposed Single-Phase SHE Technique                                    |     |

| 3.3  |          | THD Analysis for Switching Angles Calculations in Five-level Voltage   |     |

| 3.4  |          | Harmonic Cancellation for Higher Level Voltage Waveforms               |     |

| 3.5  |          | Discussion                                                             |     |

| 3.6  | Conclus  | sions                                                                  | 93  |

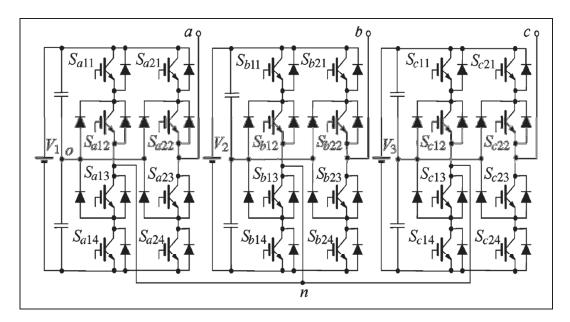

| CHAP | TER 4    | COMPATIBLE SELECTIVE HARMONIC ELIMINATION FOR                          |     |

|      |          | THREE-PHASE FOUR-WIRE NPC INVERTER WITH DC-LINK                        |     |

|      |          | CAPACITOR VOLTAGE BALANCING                                            | 95  |

| 4.1  |          | ction                                                                  |     |

| 4.2  | SHE-PV   | VM for 4L/4W and 3L/4W NPC Topologies                                  | 99  |

|      | 4.2.1    | SHE-PWM for 4L/4W NPC Inverter                                         | 99  |

|      | 4.2.2    | Proposed CSHE-PWM for 3L/4W NPC Inverter                               | 102 |

|      | 4.2.3    | Regulation of Capacitor Voltage Ripple and Importance of Triplen       |     |

|      |          | and Non-Triplen Elimination in 3L/4W NPC Inverter                      | 105 |

| 4.3  | Harmon   | ic Content and Power Losses Analysis                                   | 108 |

|      | 4.3.1    | Phase Voltage Harmonic Content Quality                                 |     |

|      | 4.3.2    | Switching Frequency and Power Losses Concerns                          | 113 |

| 4.4  |          | ion and Experimental Results Analysis of the Proposed CSHE for         |     |

|      | 3L/4W 1  | NPC Inverter                                                           | 115 |

| 4.5  | Conclus  | sions                                                                  | 122 |

| СНА  | PTER 5   | HYBRID SHM-PWM FOR COMMON MODE VOLTAGE<br>REDUTION IN THREE-PHASE THREE-LEVEL<br>NPC INVERTER | 125 |

|------|----------|-----------------------------------------------------------------------------------------------|-----|

| 5.1  | Introdu  | ction                                                                                         |     |

| 5.2  |          | Harmonic Modeling of 3Phase 3Level NPC                                                        |     |

| 3.2  | 5.2.1    | 3Level 3Phase Configuration of NPC Inverter Topology                                          |     |

|      | 5.2.2    | Mathematical Formulation of CMV Harmonic Content                                              |     |

| 5.3  |          | SHM-PWM for CMV Reduction                                                                     |     |

| 3.3  | 5.3.1    | Conventional SHE-PWM and SHM-PWM Techniques                                                   |     |

|      | 5.3.2    | Hybridizing SHM-PWM Based on SHE-PWM                                                          |     |

|      | 5.3.3    | Switching Angles Calculations Using ABC Algorithm                                             |     |

| 5.4  |          | nic Spectrum and CMV Reduction Analyses                                                       |     |

| J. 1 | 5.4.1    | Harmonic Amplitudes and Voltage THD Analysis                                                  |     |

|      | 5.4.2    | Root Mean Square (RMS) Analysis of CMV Reduction                                              |     |

|      | 5.4.3    | Hybrid SHM-PWM versus SHM-PWM and SHE-PWM                                                     |     |

| 5.5  |          | nental Results Discussion and Analysis                                                        |     |

| 5.6  |          | ions                                                                                          |     |

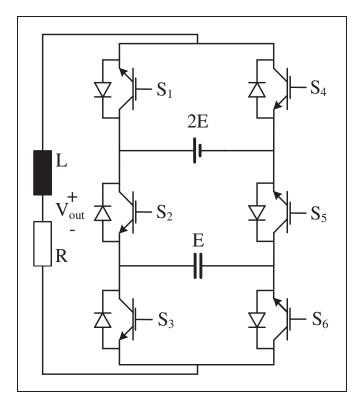

| СНА  | PTER 6   | PACKED E-CELL (PEC) CONVERTER TOPOLOGY OPERATION AND EXPERIMENTAL VALIDATION                  |     |

| 6.1  |          | ction                                                                                         |     |

| 6.2  |          | ed Nine-Level Packed E-Cell (PEC9)                                                            |     |

|      | 6.2.1    | PEC9 Circuit Topology                                                                         |     |

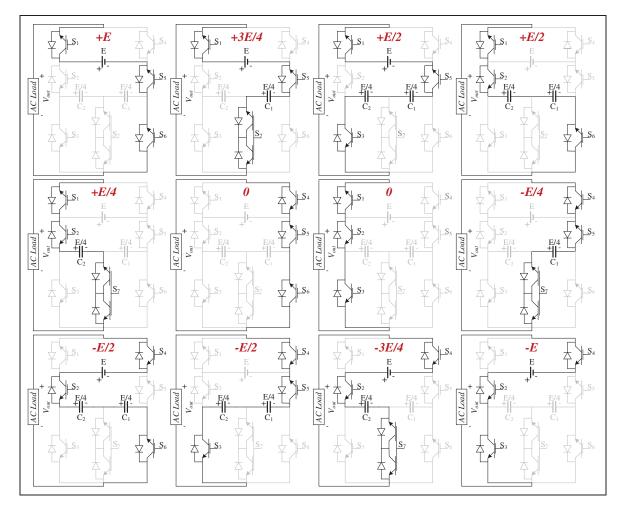

|      | 6.2.2    | PEC9 Switching States                                                                         |     |

|      | 6.2.3    | Multi-Level Terminal Capability of PEC9 Topology                                              |     |

| 6.3  |          | ed PWM Active Voltage Balancing                                                               |     |

|      | 6.3.1    | E-Cell Capacitors Voltages Equations                                                          | 163 |

|      | 6.3.2    | Proposed Active Capacitor Voltage Balancing PWM Technique                                     |     |

|      |          | Using Single Voltage Sensor for Auxiliary DC-Link                                             |     |

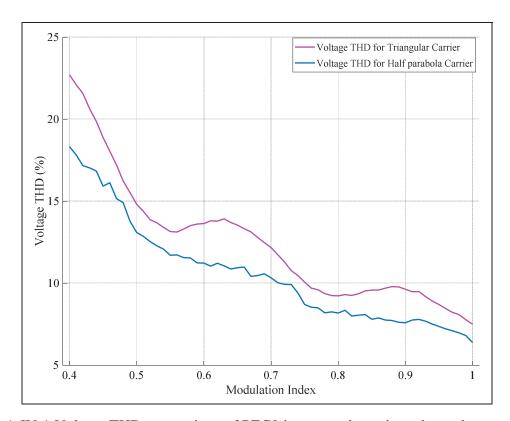

|      | 6.3.3    | PWM Technique Using Half-Parabola Carrier                                                     | 169 |

| 6.4  |          | rsus Other Recently Presented Multilevel Inverters; Components                                |     |

|      |          | ison                                                                                          |     |

| 6.5  |          | nental Validation and Analysis of PEC9                                                        |     |

|      | 6.5.1    | Test1: Multilevel Voltage Operation                                                           |     |

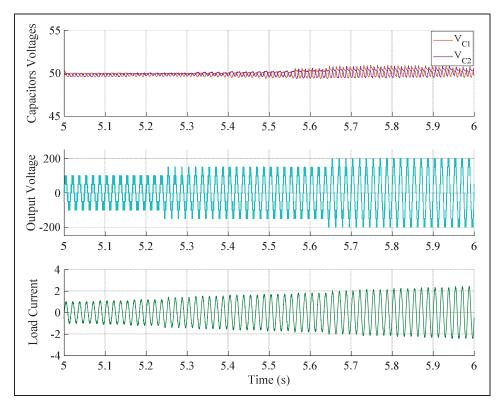

|      | 6.5.2    | Test2: Modulation Index and DC Input Voltage Variations                                       |     |

|      | 6.5.3    | Test3: Output Load Changes                                                                    |     |

| 6.6  | Conclusi | ions                                                                                          | 182 |

| CON  | CLUSION  |                                                                                               | 183 |

| ANN  | EX I     | DEADTIMES AFFECTS ON SWITCHING ANGLES                                                         | 189 |

| ANNEX II       | PROPOSED SELECTIVE HARMONIC MITIGATION FOR 3L/4W INVERTERS                                             | .192 |

|----------------|--------------------------------------------------------------------------------------------------------|------|

| ANNEX III      | CAPACITORS SELF-VOTAGE BALANCING AND ELECTRICAL MOTOR CONTROL IN THE PROPOSED HYBRID SHM-PWM TECHNIQUE | .196 |

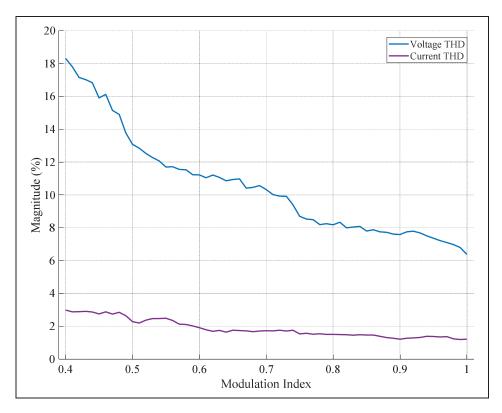

| ANNEX IV       | VOLTAGE/CURRENT THD AND CAPACITORS RIPPLES<br>ANALYSES OF PEC9                                         | .200 |

| LIST OF REFERI | ENCES                                                                                                  | 204  |

# LIST OF TABLES

|           |                                                                                         | Page |

|-----------|-----------------------------------------------------------------------------------------|------|

| Table 1.1 | Switching States of Three-Level Diode Clamped (NPC) Inverter                            | 11   |

| Table 1.2 | Switching States of Five-Level Diode Clamped Inverter                                   | 11   |

| Table 1.3 | Switching States of Three-Level Flying Capacitor Inverter                               | 14   |

| Table 1.4 | Switching States of Five-Level Flying Capacitor Inverter                                | 14   |

| Table 1.5 | Switching States of Five-Level Packed U-Cell Inverter                                   | 18   |

| Table 1.6 | Switching States for Three-Phase Two-Level Inverter                                     | 22   |

| Table 1.7 | EN50160 and CIGRE WG 36-05 Requirements for Non-triplen and Triplen Harmonics Amplitude | 37   |

| Table 2.1 | Non-Triplen and Triplen Harmonics Amplitude Standard                                    | 49   |

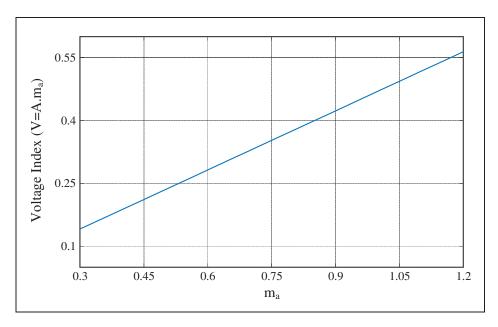

| Table 2.2 | Computed Values for Switching Angles (Radian) and Parameter A                           | 54   |

| Table 2.3 | A Comparison among Conventional SHM-PWM/PAM and Modified SHM-PAM                        | 58   |

| Table 3.1 | Switching States of MPUC Inverters                                                      | 78   |

| Table 3.2 | Utilized Parameters Characteristics for Single-Phase MPUC                               | 91   |

| Table 4.1 | Tested NPC Inverter System Parameters                                                   | 116  |

| Table 5.1 | Switching States of Each Leg in 3Phase NPC Inverter                                     | 130  |

| Table 5.2 | Standard Limitation for Non-Triplen/Triplen Amplitude                                   | 134  |

| Table 5.3 | Initialization of ABC Algorithm                                                         | 138  |

| Table 5.4 | Parameters Values Utilized in Experimental tests of 3Phase NPC                          | 147  |

| Table 6.1 | PEC9 Switching States (†: Charging, ↓: Discharging, -: No Effect)                       | 162  |

| Table 6.2 | Component Comparison Among 9Level Converters and PEC9                                   | 171  |

| Table 6.3 | PEC9 Parameters Used for Experimental Tests                                             | 173  |

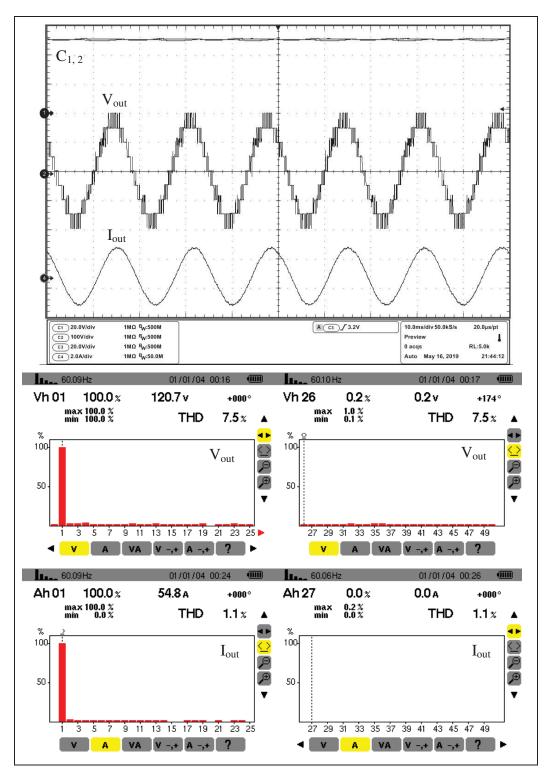

| Table 6.4 | The Amplitude of Harmonic Spectrum of Nine-Level Output | 156 |

|-----------|---------------------------------------------------------|-----|

|           | Voltage and Load Current of Figure 6.11                 | 176 |

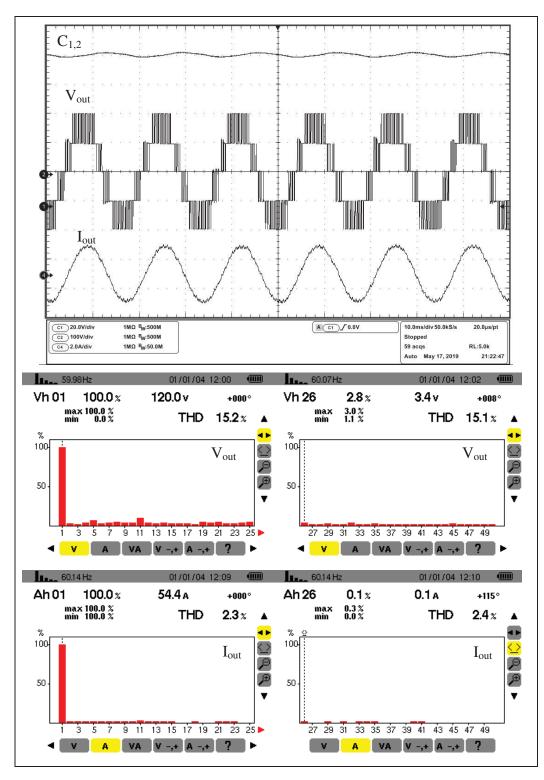

| Table 6.5 | The Amplitude of Harmonic Spectrum of Five-Level Output |     |

|           | Voltage and Load Current of Figure 6.13                 | 179 |

### LIST OF FIGURES

|             |                                                                                                                                                                      | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

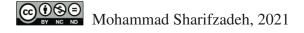

| Figure 1.1  | Conventional two-level inverter configuration                                                                                                                        | 11   |

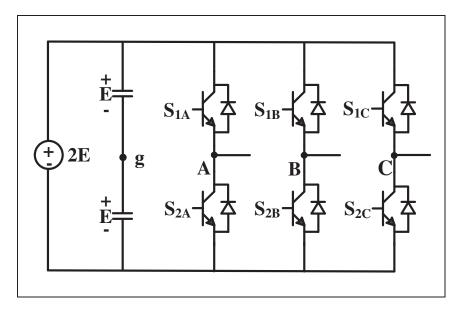

| Figure 1.2  | Single-phase three-level and five-level diode clamped (NPC) inverter configuration, (a) three-level NPC inverter, (b) five-level NPC inverter                        | 12   |

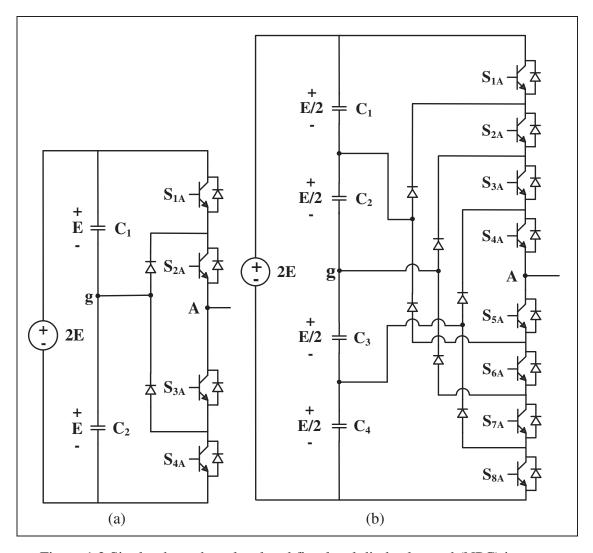

| Figure 1.3  | Single-phase three-level and five-level flying capacitor inverter configuration, (a) three-level flying capacitor inverter, (b) five-level flying capacitor inverter | 15   |

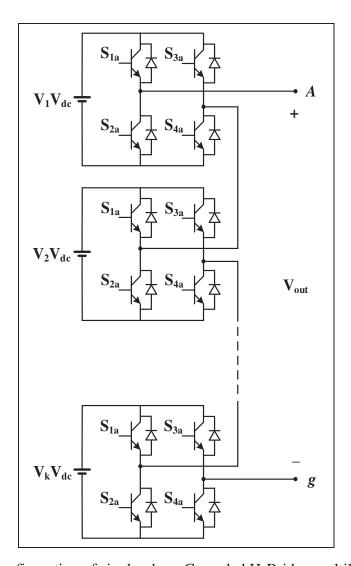

| Figure 1.4  | Configuration of single-phase Cascaded H-Bridge multilevel inverte                                                                                                   | r16  |

| Figure 1.5  | Five-level cascaded NPC inverter                                                                                                                                     | 17   |

| Figure 1.6  | Configuration of Packed U-Cell inverter                                                                                                                              | 18   |

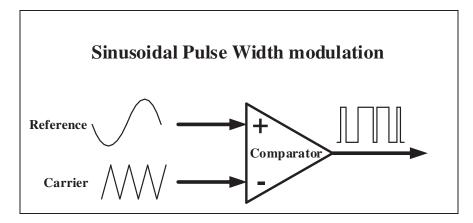

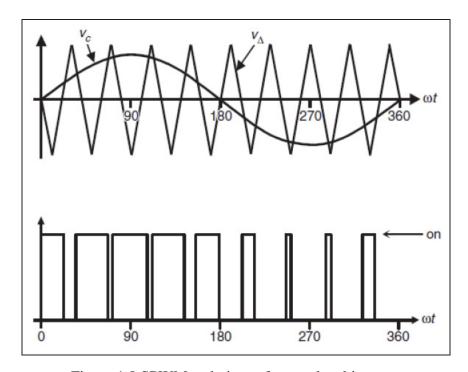

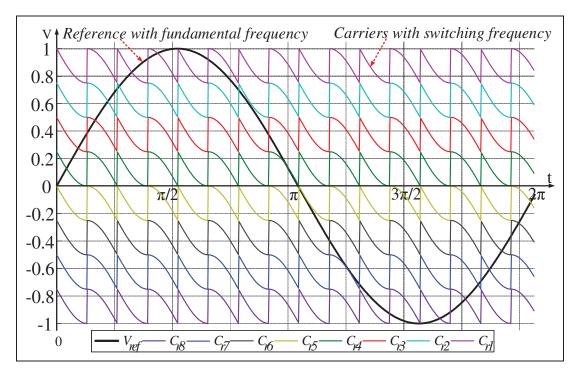

| Figure 1.7  | General diagram of SPWM method                                                                                                                                       | 20   |

| Figure 1.8  | SPWM technique for two-level inverter                                                                                                                                | 20   |

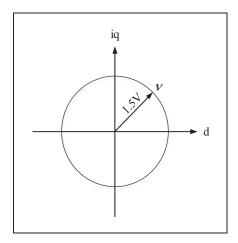

| Figure 1.9  | Locus of vector V                                                                                                                                                    | 23   |

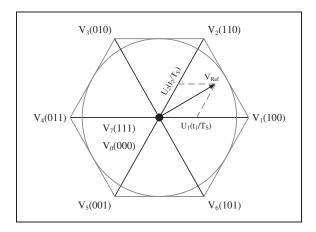

| Figure 1.10 | Space vector of three-phase two-level inverter                                                                                                                       | 23   |

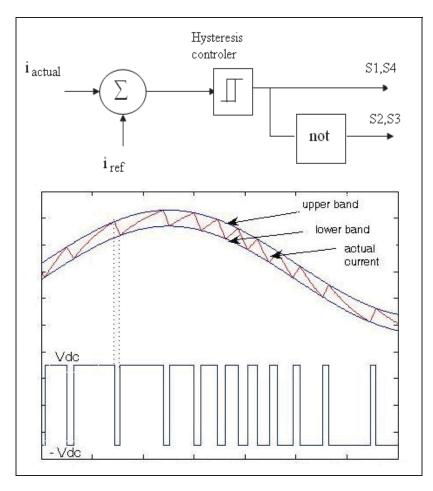

| Figure 1.11 | Hysteresis current controls for conventional two-level inverter                                                                                                      | 24   |

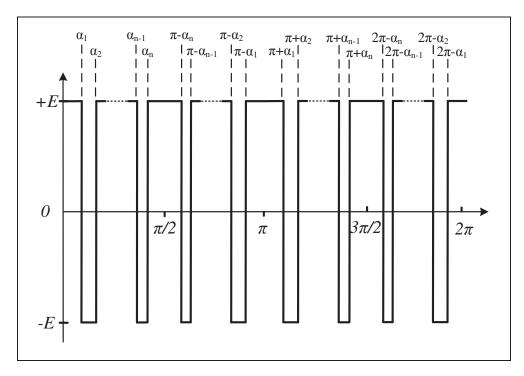

| Figure 1.12 | Bipolar voltage waveform                                                                                                                                             | 28   |

| Figure 1.13 | Unipolar voltage waveform                                                                                                                                            | 29   |

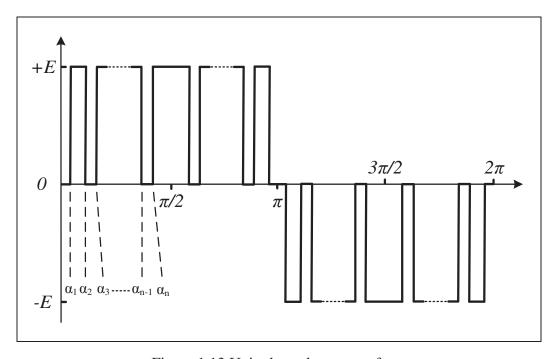

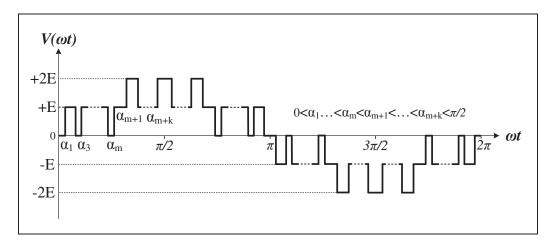

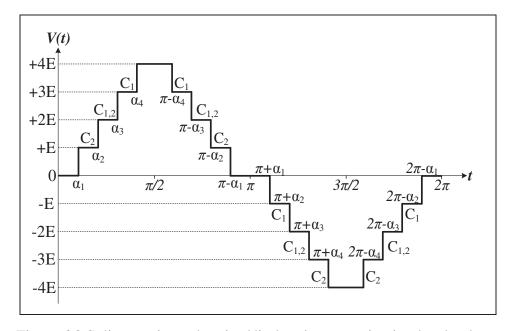

| Figure 1.14 | Multilevel voltage waveform                                                                                                                                          | 30   |

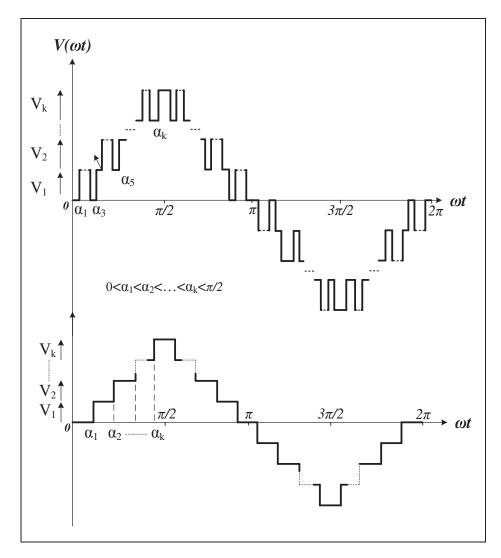

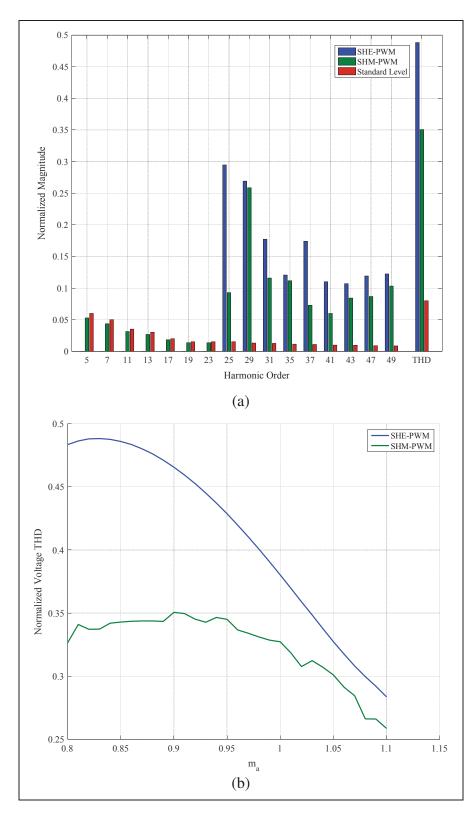

| Figure 1.15 | Harmonic amplitude and voltage THD comparison between SHM and SHE (a) worst case scenario for harmonic amplitudes (b) voltage THD                                    | 39   |

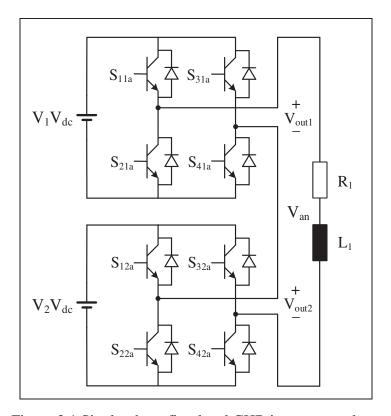

| Figure 2.1  | Single-phase five-level CHB inverter topology                                                                                                                        | 47   |

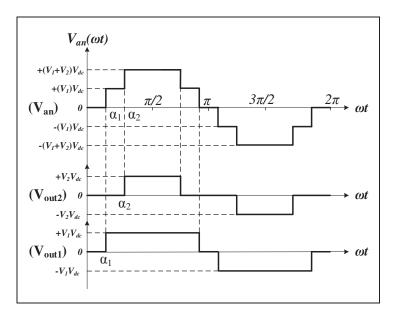

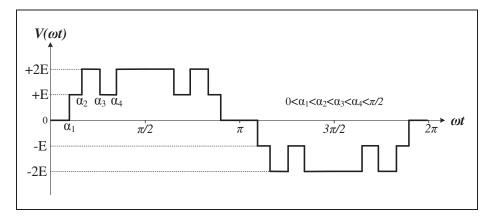

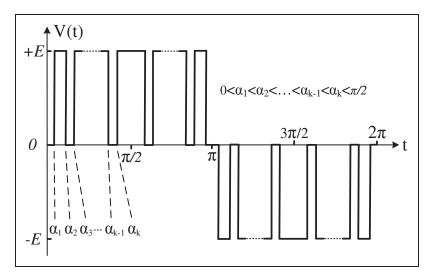

| Figure 2.2  | Five-level low switching frequency voltage waveform                                                                                                                  | 47   |

| Figure 2.3  | five-level CHB inverter                                                                                                                                                                   | 55 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

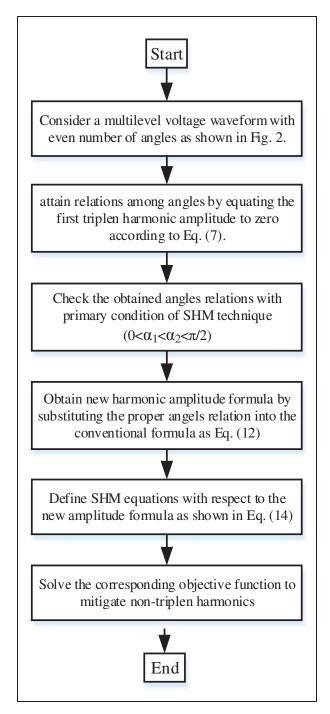

| Figure 2.4  | The flow chart of proposed procedure for elimination of all triplen harmonics                                                                                                             | 56 |

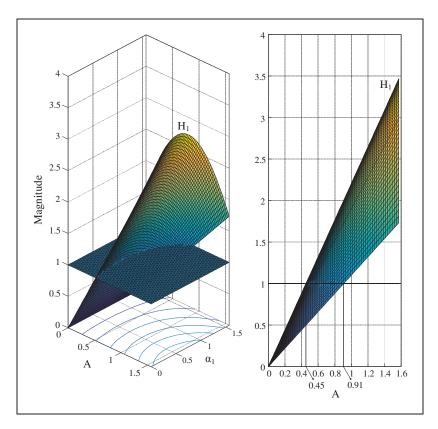

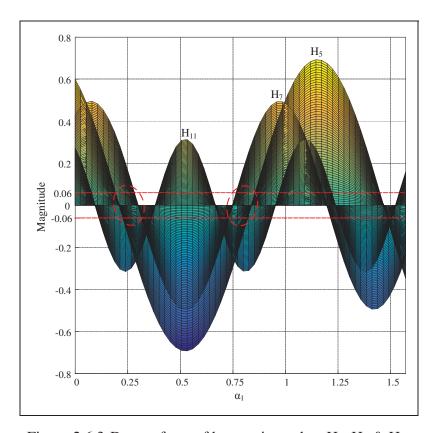

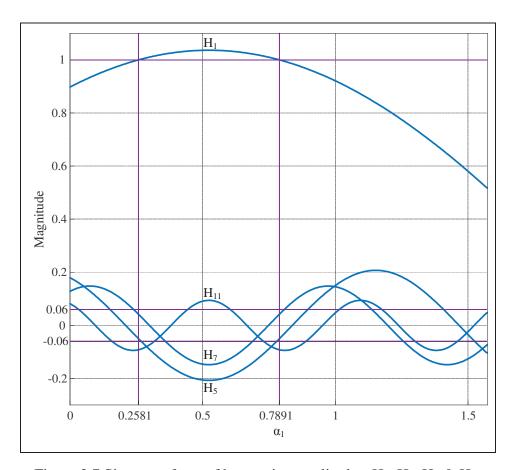

| Figure 2.5  | 3-D waveform of first harmonic (H <sub>1</sub> )                                                                                                                                          | 59 |

| Figure 2.6  | 3-D waveform of harmonics orders H <sub>5</sub> , H <sub>7</sub> & H <sub>11</sub>                                                                                                        | 60 |

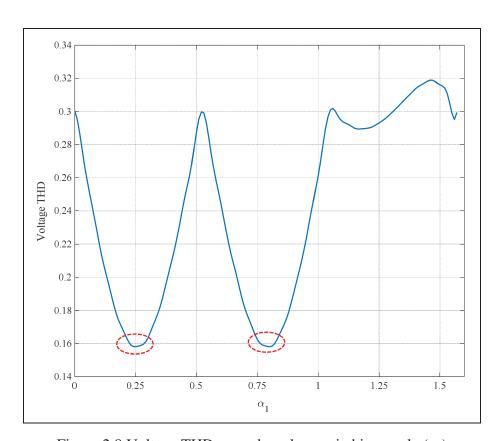

| Figure 2.7  | Sine waveform of harmonics amplitudes; H <sub>1</sub> , H <sub>5</sub> , H <sub>7</sub> & H <sub>11</sub>                                                                                 | 61 |

| Figure 2.8  | Voltage THD curve based on switching angle $(\alpha_1)$                                                                                                                                   | 62 |

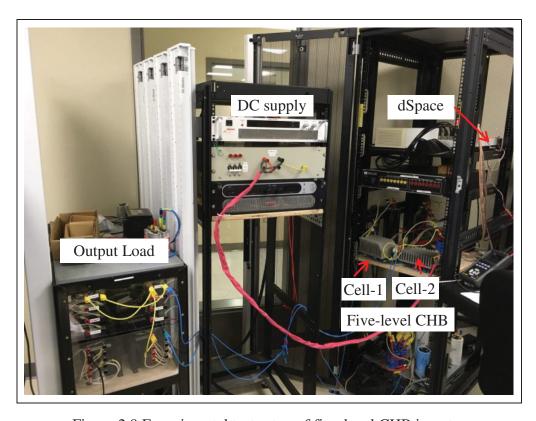

| Figure 2.9  | Experimental test setup of five-level CHB inverter                                                                                                                                        | 63 |

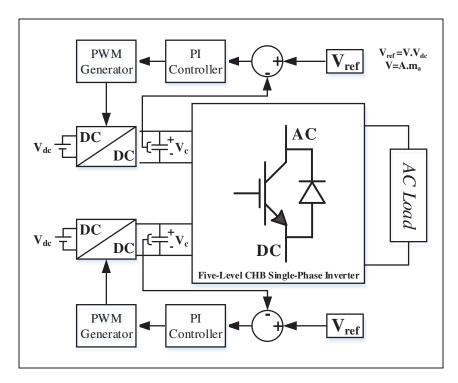

| Figure 2.10 | Close loop controller for implementation of PAM                                                                                                                                           | 64 |

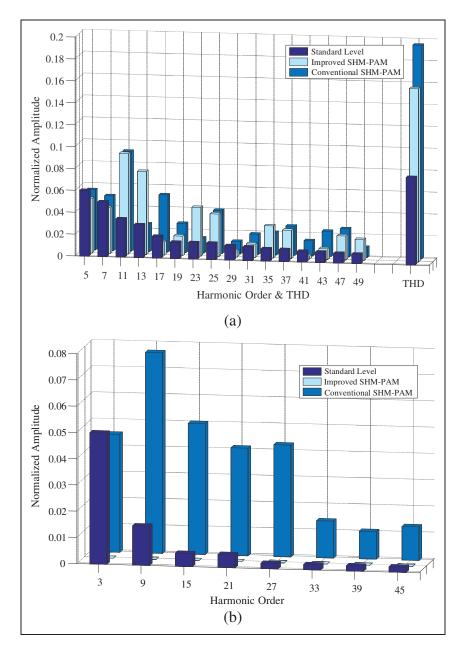

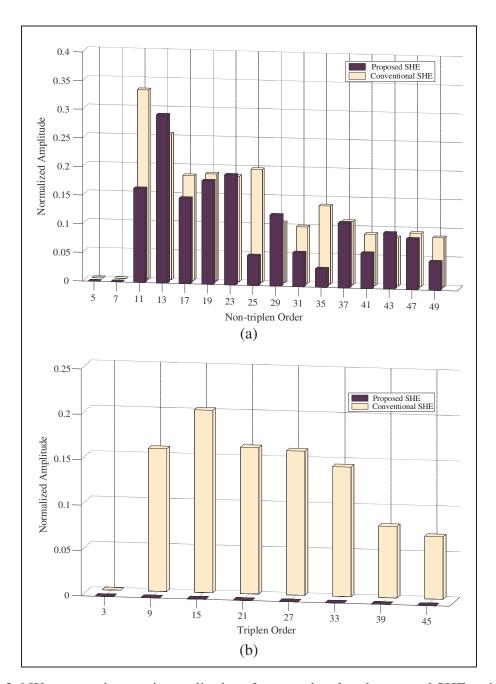

| Figure 2.11 | Non-triplen and triplen amplitudes in both conventional and improved single-phase SHM-PAM techniques,  (a) non-triplen, (b) triplen                                                       | 65 |

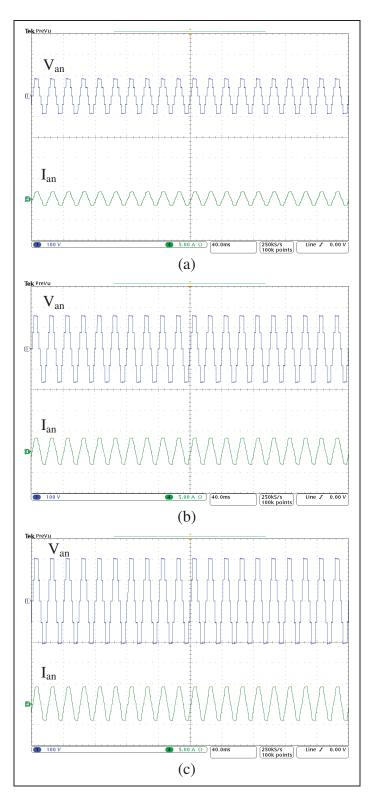

| Figure 2.12 | Output Voltage and current waveforms of five-level single-phase CHB inverter under linear R-L load for different the modulation indices, (a) $m_a$ =0.45, (b) $m_a$ =0.85, (c) $m_a$ =1.1 | 67 |

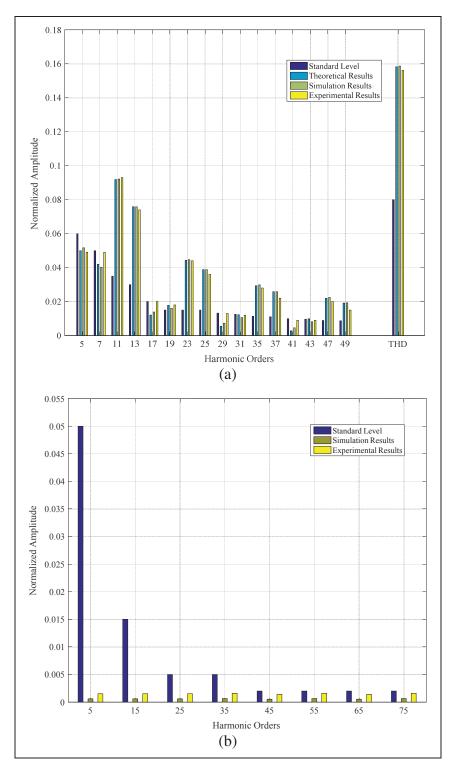

| Figure 2.13 | Harmonic amplitudes and voltage THD for theoretical, simulation and experimental results,  (a) Triplen orders, (b) Non-triplen orders                                                     | 68 |

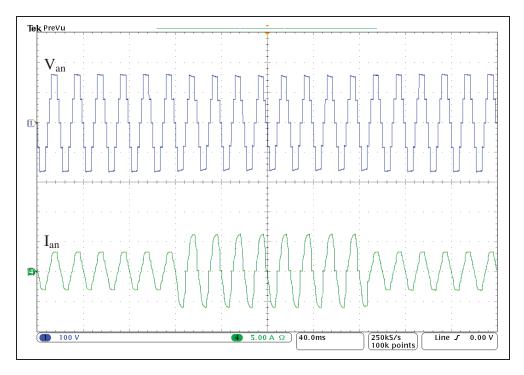

| Figure 2.14 | Voltage and current waveforms when five-level CHB inverter supplies both linear and harmonic loads                                                                                        | 69 |

| Figure 3.1  | Five-level Modified PUC (MPUC) inverter topology                                                                                                                                          | 77 |

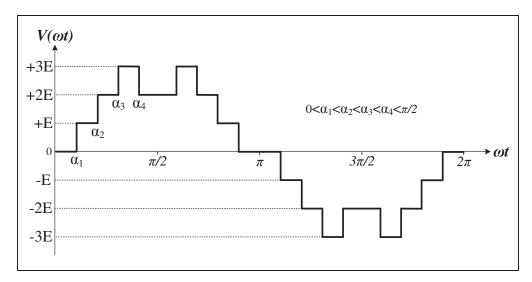

| Figure 3.2  | Typical predetermined five-level voltage waveform                                                                                                                                         | 79 |

| Figure 3.3  | Proposed five-level voltage waveform for single-phase inverter                                                                                                                            | 80 |

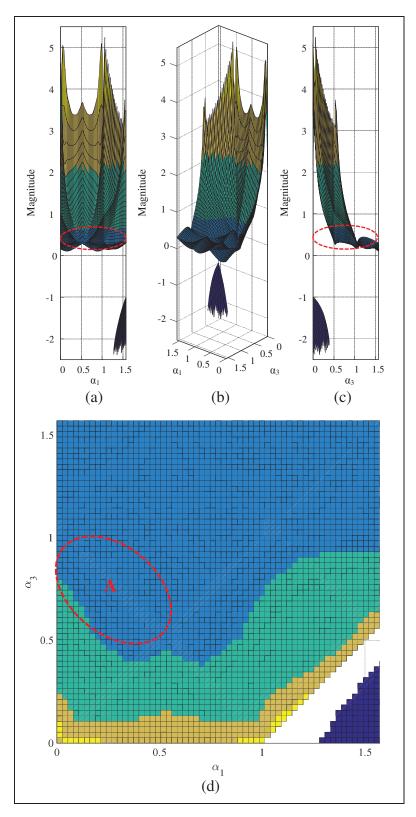

| Figure 3.4  | 3D waveform of THD, (a) X-Z view, (b) Original view, (c) Y-Z view, (d) X-Y view                                                                                                           | 85 |

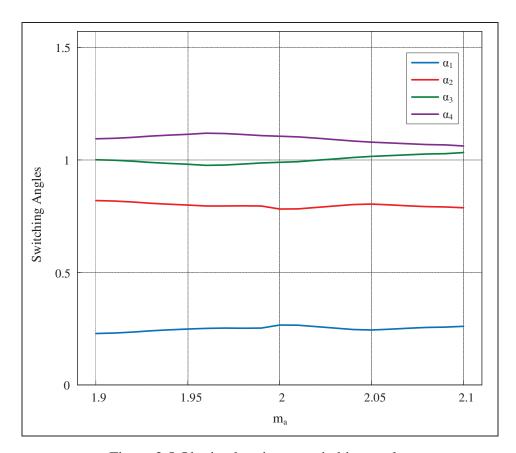

| Figure 3.5  | Obtained optimum switching angles                                                                                                                                                         | 86 |

| Figure 3.6    | Worst case harmonic amplitudes of conventional and proposed SHE techniques (a) Non-triplen orders, (b) Triplen orders87                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

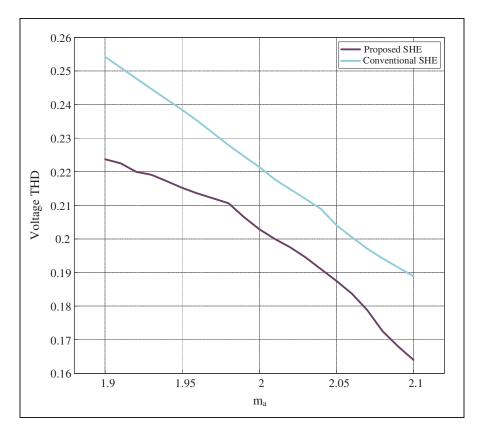

| Figure 3.7    | Voltage THD of single-phase conventional and proposed SHE techniques                                                                                                                                          |

| Figure 3.8    | Proposed seven-level voltage waveform for single-phase inverter90                                                                                                                                             |

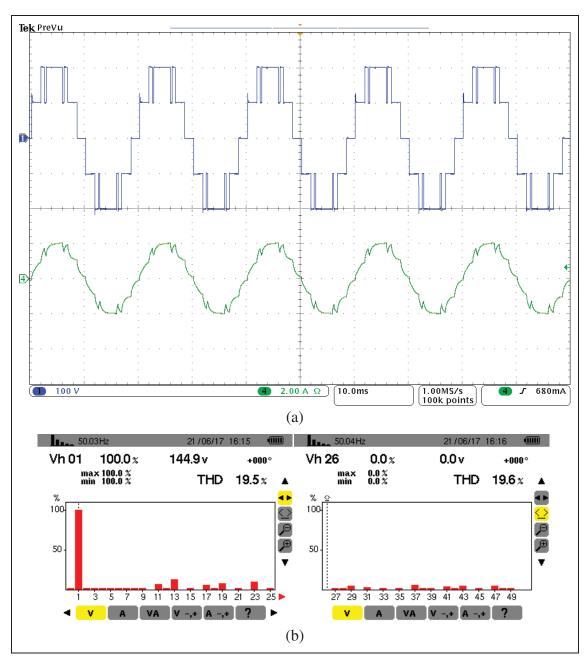

| Figure 3.9    | Experimental results of five-level voltage and current waveforms with voltage harmonic content of single-phase MPUC inverter, (a) voltage and current waveforms (b) voltage harmonic spectrum92               |

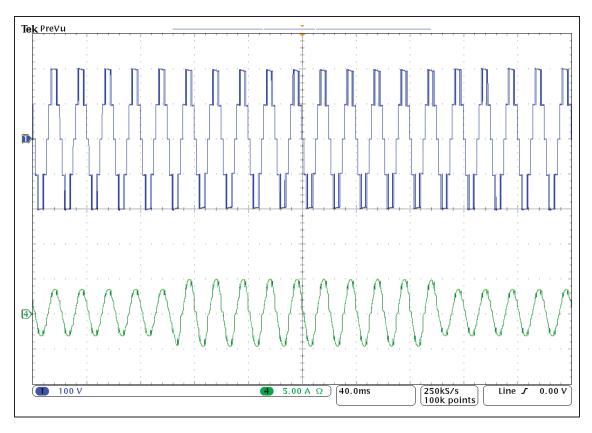

| Figure 3.10   | Experimental results of voltage and current of single-phase MPUC inverter when it is supplying linear and nonlinear loads93                                                                                   |

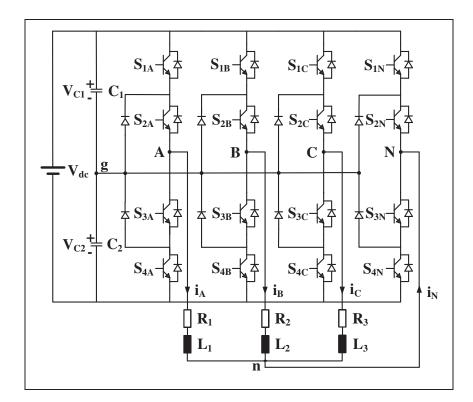

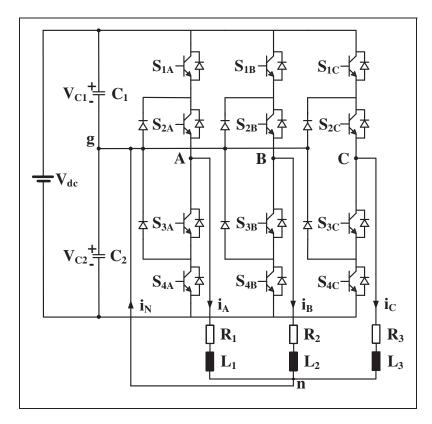

| Figure 4.1    | 4L/4W NPC inverter configuration                                                                                                                                                                              |

| Figure 4.2    | A typical three level of predefined branch voltage waveform101                                                                                                                                                |

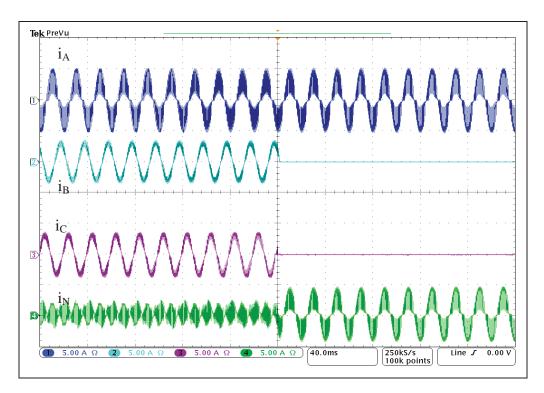

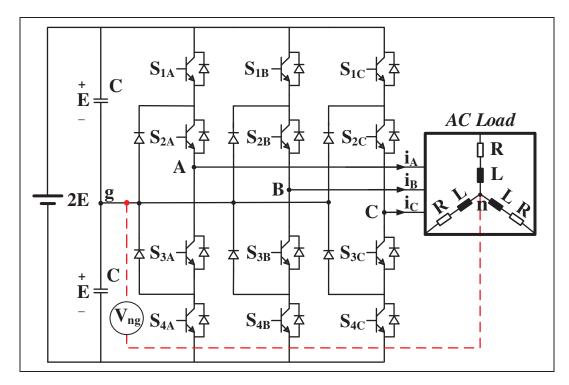

| Figure 4.3    | 3L/4W NPC inverter configuration                                                                                                                                                                              |

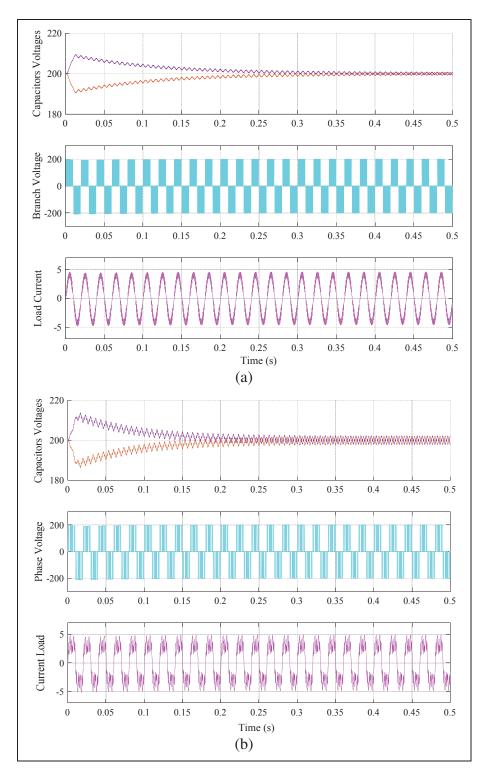

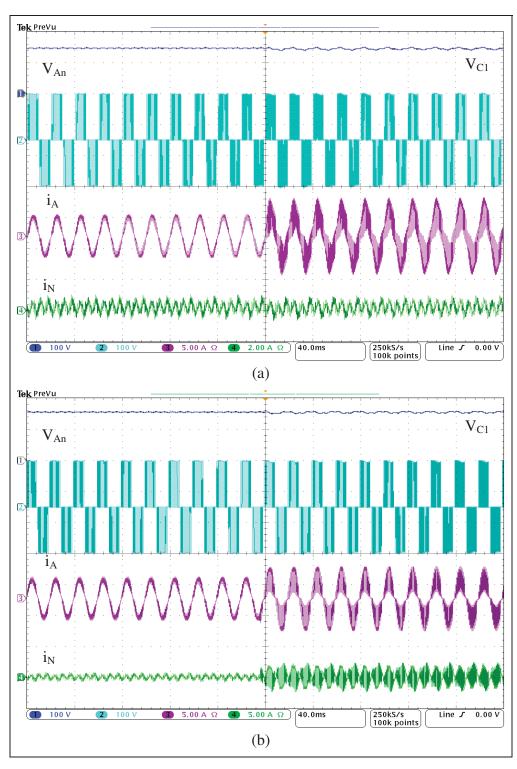

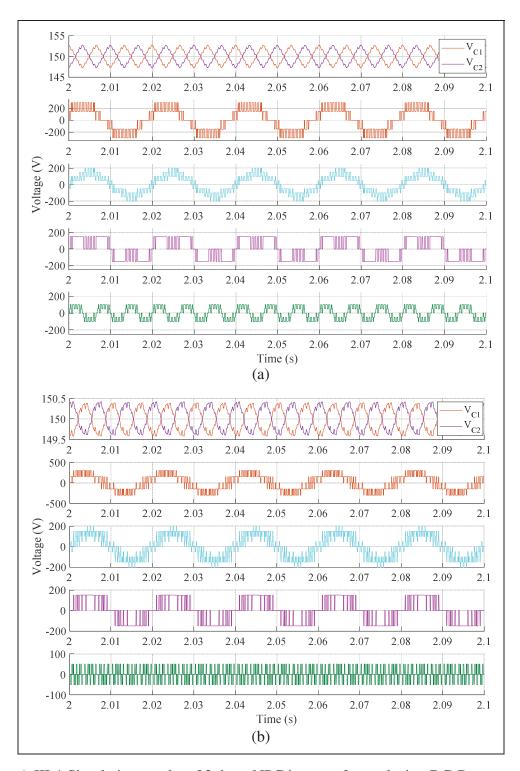

| Figure 4.4    | The effects of triplen harmonics on the capacitors voltages and load current in SHE for 3L/4W NPC inverter,  (a) SHE with elimination of triplen harmonics,  (b) SHE without elimination of triplen harmonics |

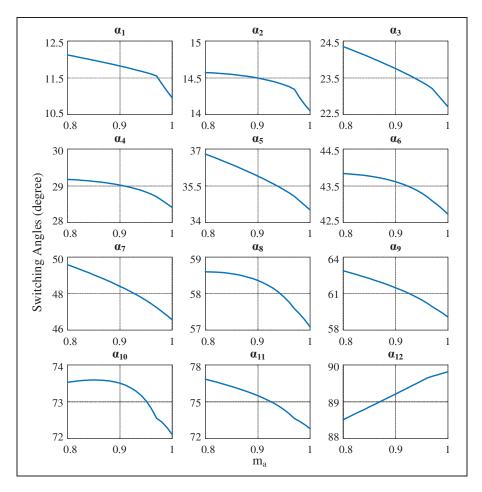

| Figure 4.5    | Obtained values for 12 switching angles of CSHE for 3L/4W NPC109                                                                                                                                              |

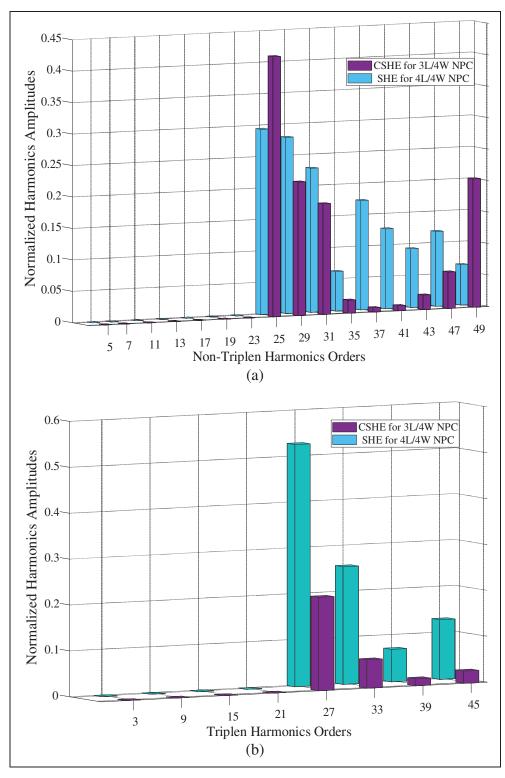

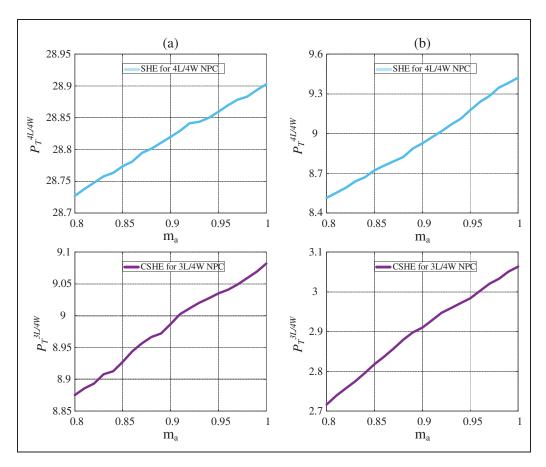

| Figure 4.6    | Worst case amplitudes of non-triplen and triplen orders of both SHE techniques for 4wire NPC inverters,  (a) non-triplen orders (b) triplen orders                                                            |

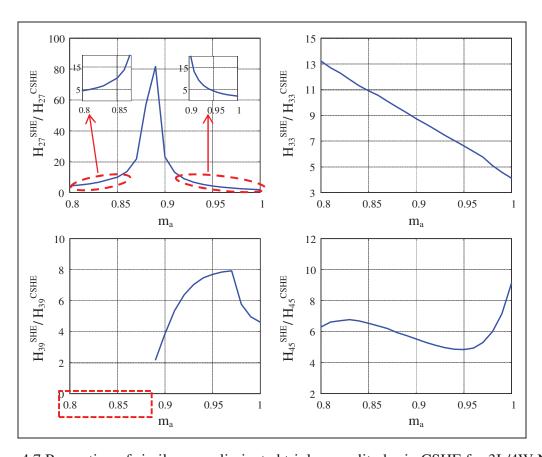

| Figure 4.7    | Proportion of similar non-eliminated triplen amplitudes in CSHE for 3L/4W NPC and SHE for 4L/4W NPC                                                                                                           |

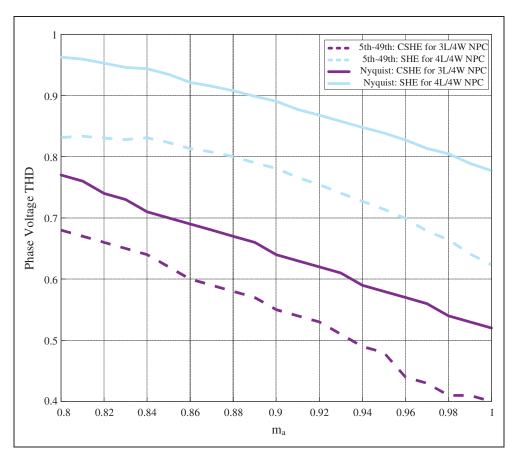

| Figure 4.8    | Phase voltage THD of CSHE-PWM and normal SHE-PWM for harmonic orders up to 49th and Nyquist frequency113                                                                                                      |

| Figure 4.9    | Switching power losses in CSHE for 3L/4W and SHE for 4L/4W NPC, (a) balanced three-phase load, (b) unbalanced single phase load                                                                               |

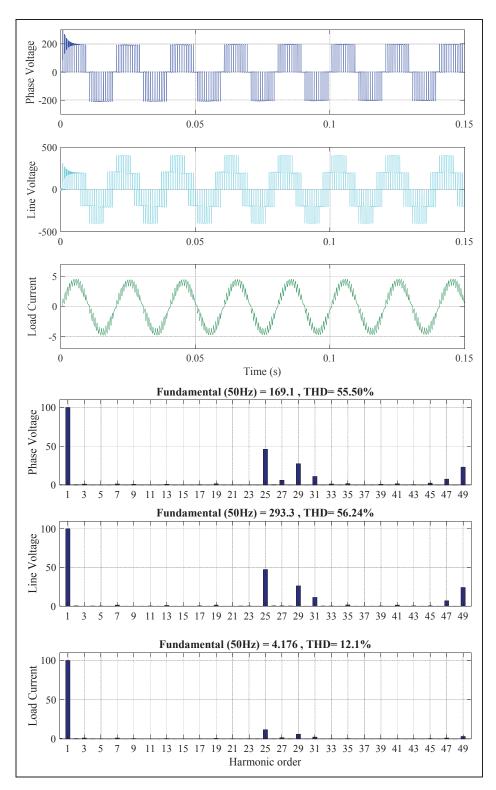

| Figure 4.10-a | Simulation results of phase, line voltages and load current along with their harmonic spectrum results when 3L/4W NPC connected to linear/balance load                                                        |

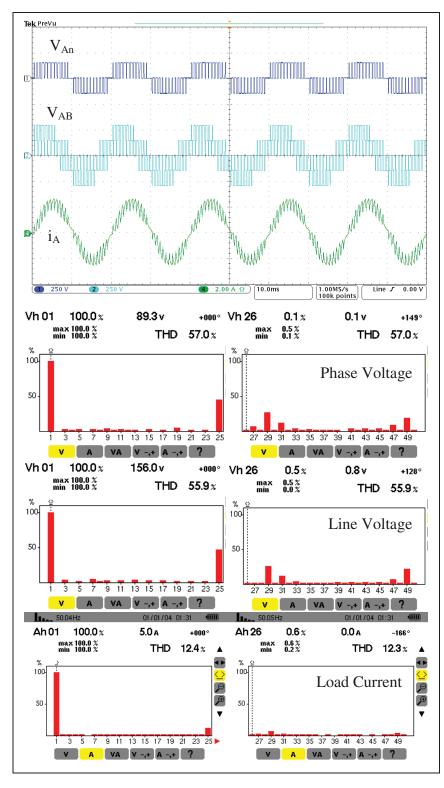

| Figure 4.10-b | Experimental result of phase, line voltages and load current and experimental analysis of harmonic spectrum of phase, line voltages and load current when 3L/4W NPC connected to linear/balance load                                           |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

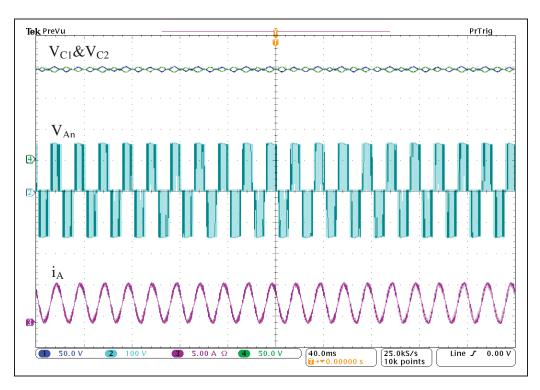

| Figure 4.11   | Experimental results of DC-link capacitors voltages and phase voltage and load current when 3L/4W NPC connected to linear/balance load                                                                                                         |

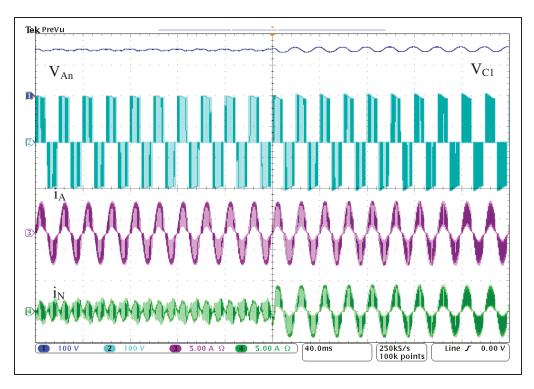

| Figure 4.12   | Experimental results of phase voltage and current when nonlinear load is connected to 3L/4W NPC,  (a) nonlinear load is between leg A and B,  (b) nonlinear load is between leg A and neutral wire                                             |

| Figure 4.13   | Experimental results of phase voltage and current when 3L/4W NPC supply single phase linear and nonlinear loads121                                                                                                                             |

| Figure 4.14   | 3phase and neutral currents related to experimental results of Figure 4.12                                                                                                                                                                     |

| Figure 5.1    | 3phase configuration of 3level NPC inverter                                                                                                                                                                                                    |

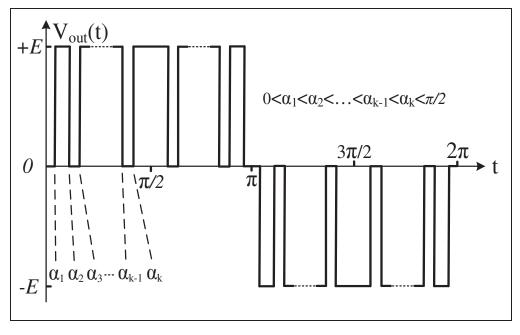

| Figure 5.2    | Generalized odd quarter wave symmetry of three-level voltage131                                                                                                                                                                                |

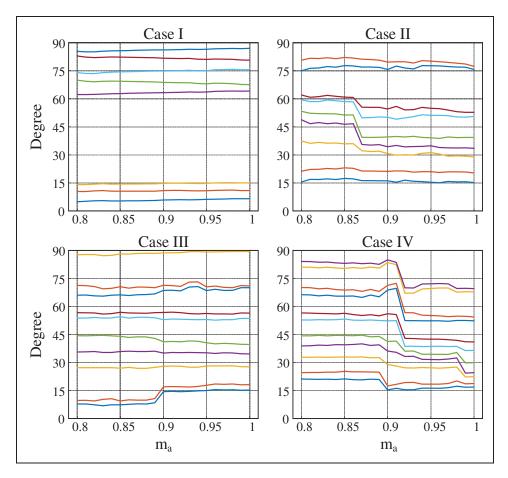

| Figure 5.3    | Obtained switching angles for four scenarios in Hybrid SHM-PWM; case I, II, III & IV: 8, 9, 10 & 11 angles, respectively138                                                                                                                    |

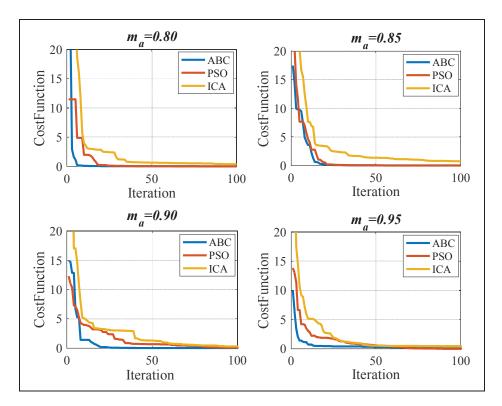

| Figure 5.4    | Comparison results of implementing ABC, PSO and ICA to calculate the switching angles for different values of modulation index including $m_a$ =0.80, $m_a$ =0.85, $m_a$ =0.90 and $m_a$ =0.95                                                 |

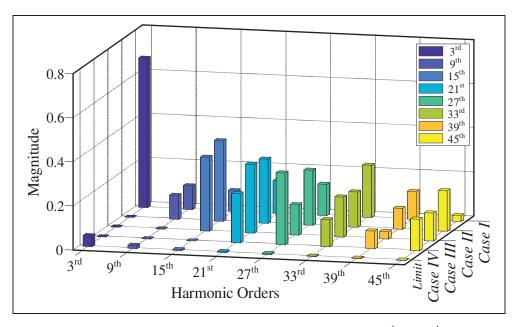

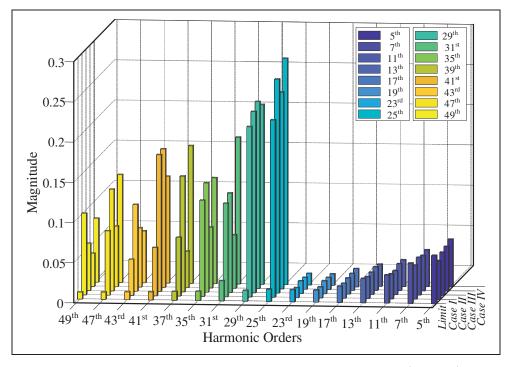

| Figure 5.5    | Worst case triplen harmonics between 3rd-to-45th in four angle scenarios of Hybrid SHM-PWM compared to Table 5.2141                                                                                                                            |

| Figure 5.6    | Worst case non-triplen harmonics between 5th-to-49th in four angle scenarios of Hybrid SHM-PWM compared to Table 5.2141                                                                                                                        |

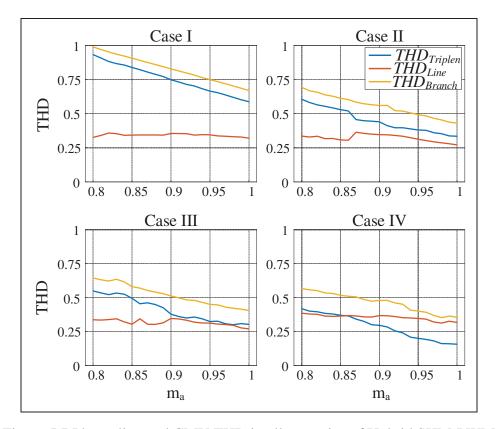

| Figure 5.7    | Phase, line and CMV THD in all scenarios of Hybrid SHM-PWM142                                                                                                                                                                                  |

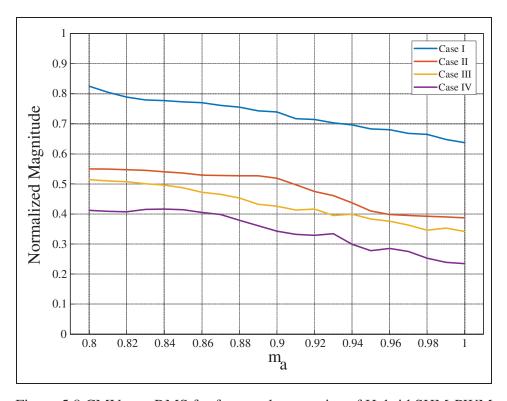

| Figure 5.8    | CMV true RMS for four angle scenarios of Hybrid SHM-PWM143                                                                                                                                                                                     |

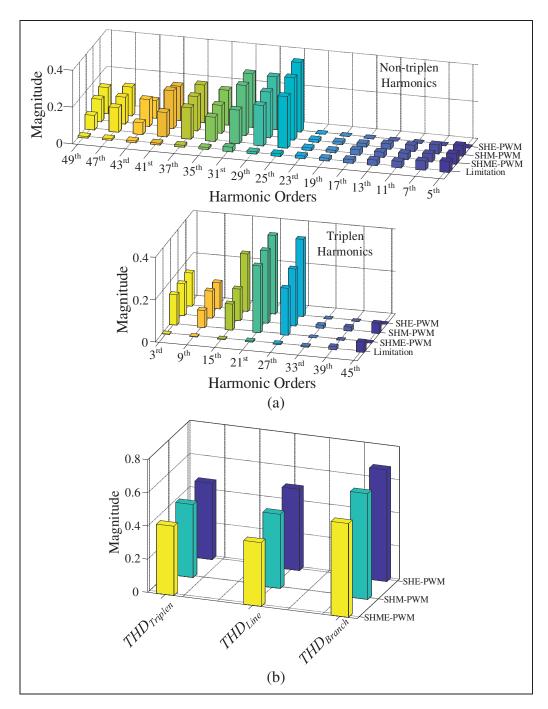

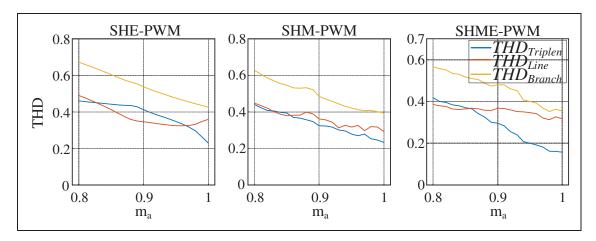

| Figure 5.9    | Worst case triplens and non-triplens and THD of SHE, SHM and Hybrid SHM designed according to case IV,  (a) worst case of triplens and non-triplens,  (b) worst case of THD <sub>Branch</sub> , THD <sub>Line</sub> and THD <sub>Triplen</sub> |

| Figure 5.10   | Phase, line and CMV THD of SHM-PWM, SHM-PWM and Hybrid SHM-PWM designed according to case IV                                                                                            |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

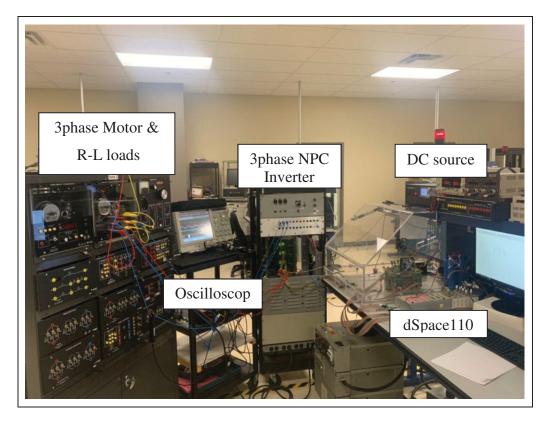

| Figure 5.11   | The experimental setup of the 3phase 3level prototype of NPC inverter tested under Hybrid SHM-PWM                                                                                       |

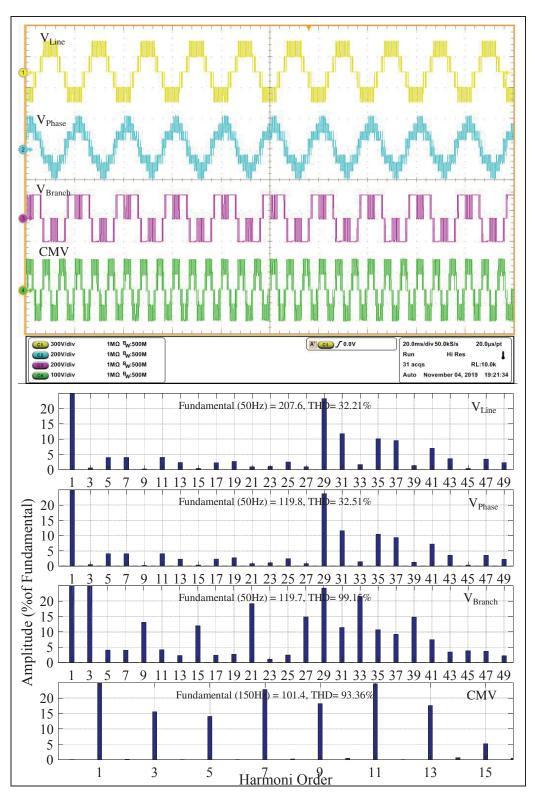

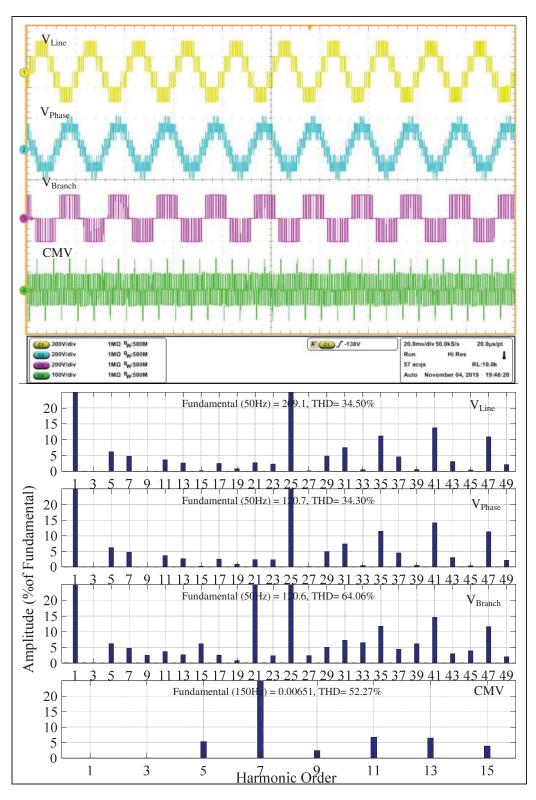

| Figure 5.12-a | Experimental results of line, phase, branch voltages and CMV and the harmonic contents (from up to down) in all scenarios of Hybrid SHM, Case I                                         |

| Figure 5.12-b | Experimental results of line, phase, branch voltages and CMV and the harmonic contents (from up to down) in all scenarios of Hybrid SHM, Case II                                        |

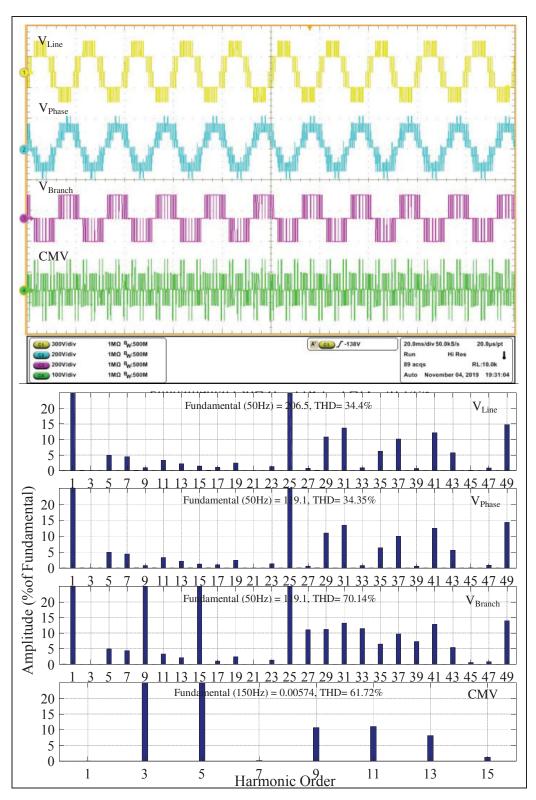

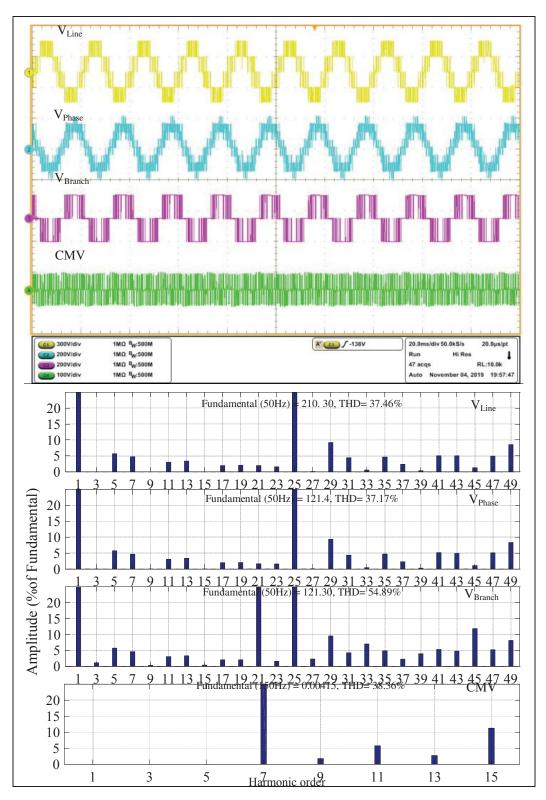

| Figure 5.12-c | Experimental results of line, phase, branch voltages and CMV and the harmonic contents (from up to down) in all scenarios of Hybrid SHM, Case III                                       |

| Figure 5.12-d | Experimental results of line, phase, branch voltages and CMV and the harmonic contents (from up to down) in all scenarios of Hybrid SHM, Case IV                                        |

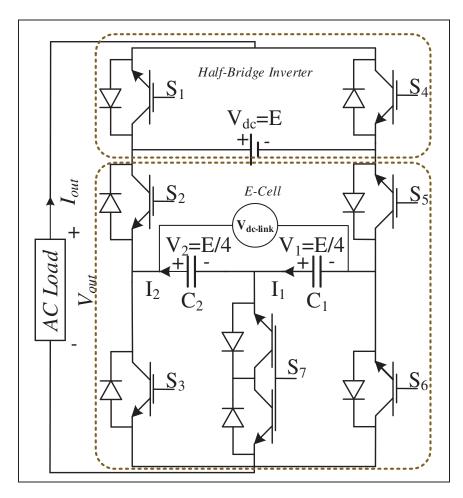

| Figure 6.1    | Proposed nine-level Packed E-Cell (PEC9) inverter topology160                                                                                                                           |

| Figure 6.2    | Operating sequences of PEC9 inverter showing devices, shunted capacitors and DC link connection during the 12 operating sequences forming according to the switching states possibility |

| Figure 6.3    | Split capacitors charging/discharging states in nine-level voltage166                                                                                                                   |

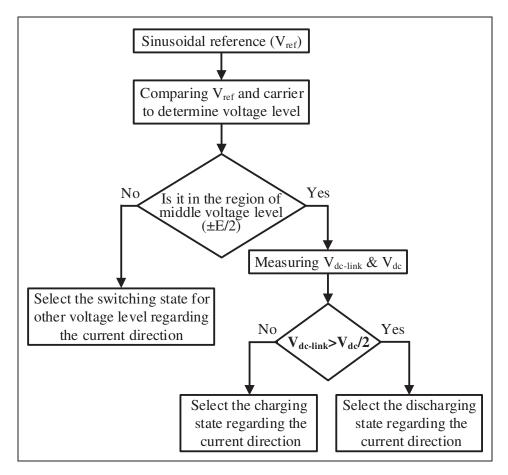

| Figure 6.4    | The designed flowchart for the active capacitor voltage balancing of PEC9 inverter                                                                                                      |

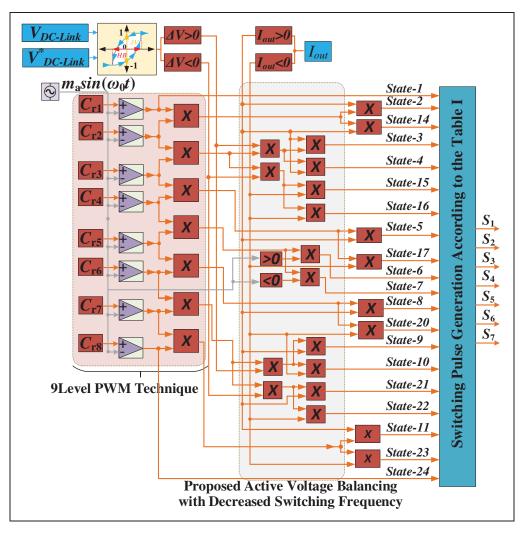

| Figure 6.5    | The block diagram of the proposed single sensor active voltage balancing method                                                                                                         |

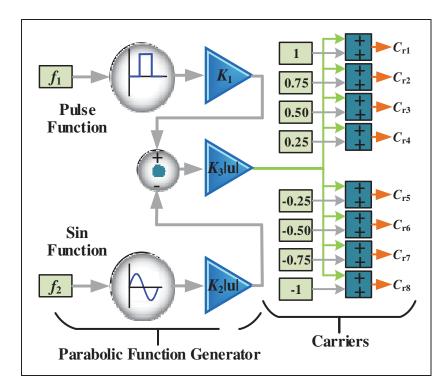

| Figure 6.6    | Parabolic waveforms generator using sinusoidal and pulse functions170                                                                                                                   |

| Figure 6.7    | 9level hybrid PWM with half-parabola vertically shifted carriers170                                                                                                                     |

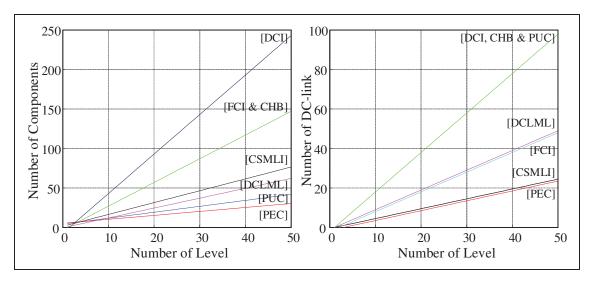

| Figure 6.8    | Component comparisons among multilevel topologies and PEC, (a) number of active devices and gate driver circuits (b) number of DC-link                                                  |

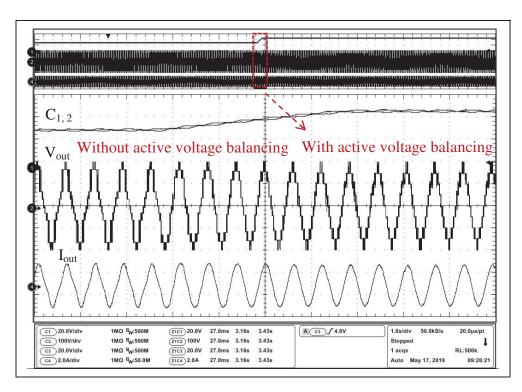

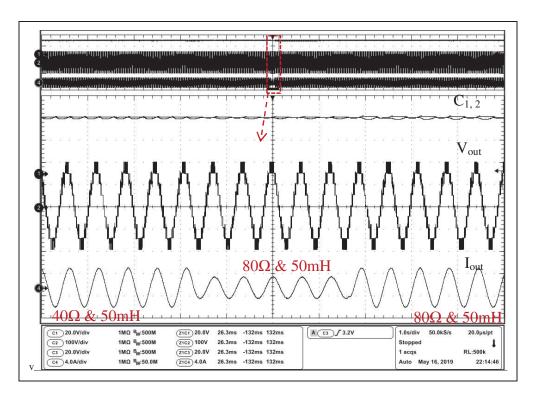

| Figure 6.9  | Experimental results of PEC9 operations with and without designed active voltage balancing PWM technique                                                                                        | 174 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

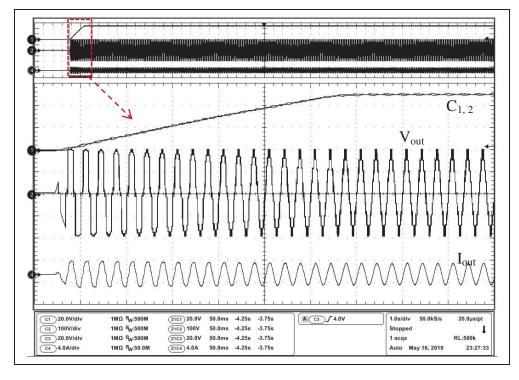

| Figure 6.10 | Experimental results of start-up mode of PEC9 operation controlled by the proposed active voltage balancing PWM technique                                                                       | 174 |

| Figure 6.11 | Steady state nine-level voltage waveform along with harmonic spectrum of nine- level output voltage and load current                                                                            | 175 |

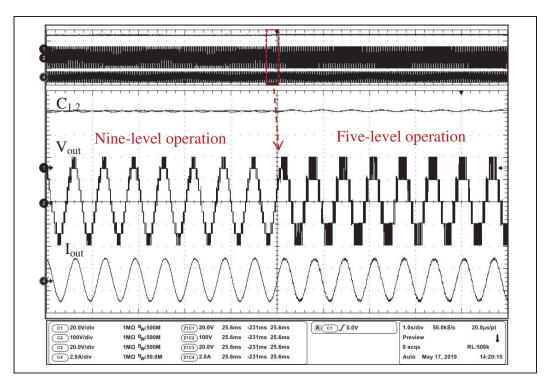

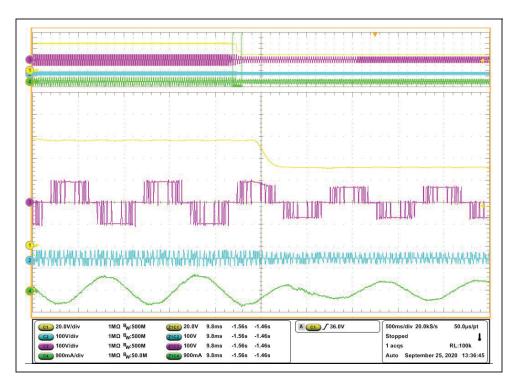

| Figure 6.12 | Experimental results of dynamic changes from nine- to five-level voltages of PEC9 inverter under faulty four-quadrant switch condition                                                          | 176 |

| Figure 6.13 | Steady state five-level voltage operation of PEC inverter along with output voltage and load current harmonic spectrum                                                                          | 177 |

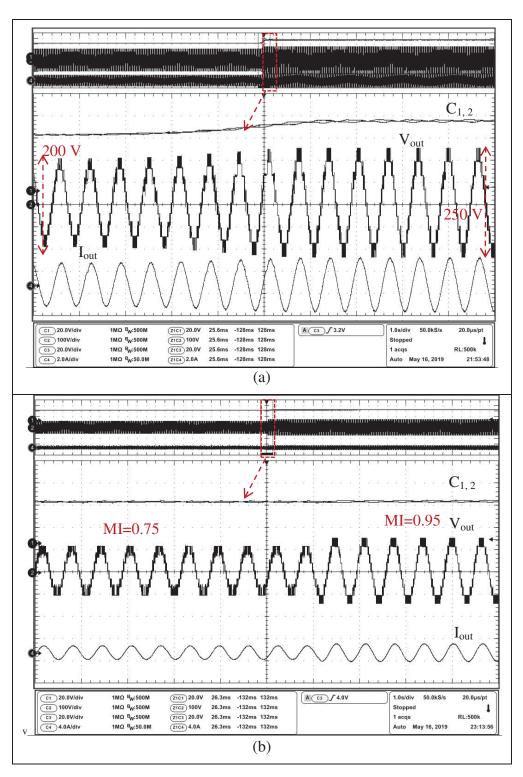

| Figure 6.14 | Experimental results of nine-level voltage (Vout), load current (Iout) and split DC capacitors voltages (C <sub>1,2</sub> ) of PEC9, (a) modulation index changes, (b) DC input variations      | 180 |

| Figure 6.15 | Experimental results of nine-level voltage (Vout), load current (Iout) and split DC capacitors voltages (C1,2) of PEC9 for load changes from $40\Omega$ to- $80\Omega$ and back to $40\Omega$ . | 181 |

#### LIST OF ABREVIATIONS

CHB Cascaded H-Bridge

DC Direct Current

FC Flying Capacitor

NPC Neutral Point Clamped

PUC Packed U-Cell

PEC Packed E-Cell

SVM Space Vector Modulation

SPWM Sinusoidal Pulse Width Modulation

SHE-PWM Selective Harmonic Elimination-Pulse Width Modulation

SHE-PWM Selective Harmonic Mitigation-Pulse Width Modulation

#### INTRODUCTION

The DC-AC converters which are well-known as inverters can produce AC staircase voltage waveform using a combination of power semiconductor elements as well as DC sources and capacitors. The first generation of inverter was consist of two switches per phase forming a simple circuit structure and could produce two voltage levels, but it was not optimized in terms of the quality of output voltage and number of semiconductor devises. In order to reach further optimization, multilevel inverters with various topologies were emerged where they are capable of producing multilevel step voltage suitable for high voltage and power applications (Choudhury, Pillay et Williamson, at al., 2014; Masisi et al., 2016). The conventional topologies suffered from a non-optimized circuit design as numerous dc source and dc capacitors as well as semiconductor devices are used. During to the last decade, many modifications on classical multilevel structures as well as new topologies have been presented in literatures (Chattopadhyay et Chakraborty, 2014; Babaei, Alilu et Laali, 2014; Samadaei, et al., 2016; Taghvaie, Adabi et Rezanejad, 2017; Taghvaie, Adabi et Rezanejad, 2018). The main purpose was to reduce the number of active and passive components and achieve more voltage levels in AC terminal in order to design an optimized inverter topology. Beside the aforementioned point, inverter switches like all kind of power electronics converters must be optimally controlled to achieve further efficiency. There are several switching methods that have been presented and deeply researched to generate proper firing pulses for inverter switches (Ahmed et al., 2016; Leon et al., 2016). Although multilevel inverter topologies improved the quality of output voltage and current in comparison to the conventional two-level inverter, switching techniques still play a significant role to provide an excellent performance. They have significant influence on the designing of an optimized inverter particularly in two aspects, the switching power losses and output voltage harmonic distortion.

Continuous development of semiconductor devices as well as optimization of inverter topology and their switching techniques have led to the widespread utilization of inverter in various power electronics applications. Depending on the range of output power, inverters

applications include battery chargers, AC/DC motor derives, FACTS and HVDC system, interconnecting renewable energy sources to the grid, uninterruptible power supplies (UPS), etc. However, the inverter requirements must be provided to be adjusted for each specific application. For instance, the inverter should be designed and controlled for motor derives to produce lower common mode voltage or they must be equipped to neutral wire if they are used in four wire applications such as UPS. For grid connected applications, the inverter must be switched to inject the current with high quality and unity power factor. Moreover, conventional electrical AC equipment such as transformer is being replaced by power inverters. This can remove the bulky transformers that can result in manufacturing expenses reduction.

#### **Consideration of High Power Applications of Multilevel Inverters (Problem Statement)**

The proper selection as well as number of semiconductor devices can enhance the inverters efficiency and lead to the optimized design in terms of power losses. However, the switching technique has also a significant impact on the minimization of power losses of the inverter. The switching technique can be optimally designed as the efficiency of the inverter improved remarkably. In this case, switching frequency of modulation technique must be taken into account in designing process of inverter control method which needs to be optimized. The switching frequency in PWM converters is defined based on the number of turn of ON and OFF state for semiconductor switches in one complete cycle which its period is T. Each turn of ON and OFF state is considered as one switched auction. So, the switching frequency (for each power switch) with respect to the provided definition can be achieved multiplying number of switched action and output voltage fundamental frequency (f=1/T). The switching frequency leads to the switching losses and can affect the inverter's efficiency. So, it is one of the crucial issues that must be assumed in the optimization of the switching technique. In (Gupta, et Ghosh, et. Joshi, 2008), the switching losses are formulated as following equation:

$$P_{S} = \frac{f_{s} \cdot E \cdot I_{S} \cdot (T_{on} + T_{off})}{2\pi} & P_{D} = 0.125 \cdot (V_{D} \cdot I_{D} \cdot T_{D} \cdot f_{s})$$

(0.1)

Where,  $I_S$ , E,  $T_{on}$  and  $T_{off}$  are the peak current, maximum voltage cross the switch, the rise and fall time of switch, respectively. Also,  $V_D$ ,  $I_D$  and  $T_D$  are diode peak voltage, peak reverse current and reverse time, respectively. According to the switching losses formulation, in high power application where the voltage and current are in the range of kV and kA, the switching losses must be considered as one of the inverter's efficiency factors. In this case, the high ratio of switching frequency can significantly increase switching and conduction losses and decrease inverter's efficiency. Moreover, the other key factor in optimization of the modulation technique is its capability in dealing with harmonic distortion of the output voltage. The modulation technique can be optimally designed according to the multilevel inverter application as to fulfill the required harmonic distortion quality for the targeted applications. In spite of excellent performance of the conventional modulation techniques in controlling the harmonic distortion of the output voltage, they require high switching frequency to obtain such achievement. So, the trend is to use methods with low switching frequency in high power application. Among all switching techniques, Selective Harmonic Elimination (SHE) and Selective Harmonic Mitigation (SHM) have the lowest switching frequency arbitrary can be reduced. According to SHE or SHM, selected harmonic amplitudes can be also precisely controlled while switching frequency is less than 1 kHz. But, these two techniques can be still optimized a long with multilevel inverter topology to enhance the efficiency for targeted power electronics applications.

#### **Research Objectives**

Multilevel inverters topologies benefits of more semiconductor switches, dc sources and capacitors for generation of more voltage level in AC output terminal which can create a waveform similar to sine wave, so less harmonic distortion is produced. Despite this, the modulation techniques that are used to control inverter switches plays an important role to enhance the power quality in terms of voltage and current THD. They can enhance the inverters' efficiency though decreasing switching frequency providing voltage balancing across DC capacitor with standard ripple and lower capacitance. This research concentrates on the optimization of multilevel inverter topology and low switching frequency modulation

techniques to achieve further efficiency in the targeted applications. For optimization of the multilevel topologies, this research focuses on developing compact multilevel inverter structure like Packed U-Cell topology in order to reach further optimized converter in terms of number of components, number of output voltage and simplicity in capacitor voltage balancing. For optimization of the modulation technique, SHE and SHM as the successful low switching frequency modulation techniques which they can reduce power losses and control low harmonic orders precisely have been accordingly chosen to be optimized for the targeted applications. Since these two modulation techniques are based on strong mathematic theory, they can be fully investigated to be optimized in dealing with more harmonic orders in lower switching frequency ratio so as they operate with higher efficiency in the existing or new applications. Consequently, the research objectives are summarized as below in order to optimize both modulation techniques and multilevel inverter topologies for power electronics applications:

- Optimizing SHE and SHM techniques to control more harmonics with lower switching frequency.

- Utilizing SHE and SHM for three-phase four-wire inverters applications.

- Reducing common mode voltage through the optimized SHE or SHM technique.

- Developing Packed U-Cell topology to achieve a further optimized compact multilevel inverter.

#### **Research Methodology**

This research needs to be accomplished according to the following steps: Mathematical analysis, simulation and experimental implementation.

Step I: a literature review is required to be done on the modulation techniques specially SHE and SHM as well as multilevel voltage source inverters particularly compact inverters topologies to fully perceive their drawback in order to propose some solution for developing them. The study should consider issues such as inverter's application, capacitor self-voltage

balancing and developed procedure for multilevel inverters and modulation techniques This step can be completed by some simulation of previous model or propose some improvement in order to find a way to optimize inverter topologies and their switching methods.

Step II: the thorough mathematic analysis must be done to modify conventional or even recent compact inverter topology and modulation technique. In this case, SHE and SHM technique due to the fact that they are established based on mathematic theory (Fourier series decomposition of voltage waveform) can be completely investigated to be improved in terms of having same switching frequency while more harmonic amplitude are controlled. This investigation must be extended to the compact multilevel inverter topology to find new solution for some existed drawbacks and in addition to develop compact inverter structure.

Step III: The developed compact inverter topology and modulation technique which were finalized in the step II will be evaluated though simulation analysis in MATLAB/Simulink environment first. After completing simulation results successfully, the improved switching technique and inverter structure will be experimentally tested in the laboratory.

#### **Thesis Contribution**

The main contributions and novelties of this thesis research are as below:

# **Maximum Harmonic Mitigation and Elimination with Minimum Switching Frequency Ratio**

The conventional SHE or SHM is established as number of harmonic that can be eliminated or mitigated are equivalent to the number of variables in the trigonometric equations which are switching angles and/or the index of input voltages. This means that if more harmonics are required to be controlled, more variables specifically more switching angles are required. More switching angles also increase the switching frequency and complexity of solving the trigonometric equations. In this work, a new switching angles constraint is introduced for both SHE and SHM technique of a low switching frequency voltage waveform which results

in self-elimination of all triplen harmonics while the non-triplen harmonic are controlled (eliminated or mitigated) through normal operation of the SHE or SHM technique. Therefore, maximum number of harmonic is controlled while minimum switching frequency is used.

#### SHE or SHM Application for 3phase 4wire Inverter

3phase 4wire inverter topologies are used to supply different load character including 3phase, single phase, balanced and unbalanced as well as linear and nonlinear loads. In previous works, high switching frequency modulation techniques have been employed to control 3phase 4wire inverters. Although they have an excellent performance in dealing with such mentioned load, their main drawback is the high switching frequency which causes high power losses. In this work, SHE has been designed for two configurations of 4wire inverter including 3leg 4wire inverter and 4leg 4wire inverter. It is shown that SHE on both 4wire configurations has suitable performance in dealing with both symmetrical and asymmetrical loads, but SHE is more compatible with 3leg 4wire inverter compared to 4leg 4wire inverter in terms of harmonic content of output voltage, design complexity and power losses.

#### SHE or SHM Application for Common Mode Voltage Control In 3phase Inverter

Common Mode Voltage (CMV) is a voltage in 3phase inverters which is measured between the neutral points of load and inverter. CMV is main reason for some adverse effects such as bearing failure, shaft voltage stress on electrical drives and EMI noises which indicates that CMV must be properly controlled in 3phase inverters. There are two general solutions for CMV control which are based on hardware and software modifications. In hardware solutions, the CMV is controlled by the help of an external circuit such as filter that makes some extra expenses. On the contrary, the software modifications like modulation techniques do not make extra cost and they are further economical solution for controlling CMV in 3phase inverters. In general, modulation techniques are designed to control CMV through proper switching vector selection as lower CMV it is generated. The high switching frequency modulation techniques have acceptable performance on controlling CMV, but they cause some disadvantages such as high power losses, imprecise control on lower harmonic

amplitude as well as capacitor voltage balancing problem. Unlike the previous methods, SHM and SHE are hybridized in this work to reduce CMV based on harmonic analysis in a low switching frequency while low order harmonics are precisely controlled and capacitors voltages are balanced with acceptable voltage ripple.

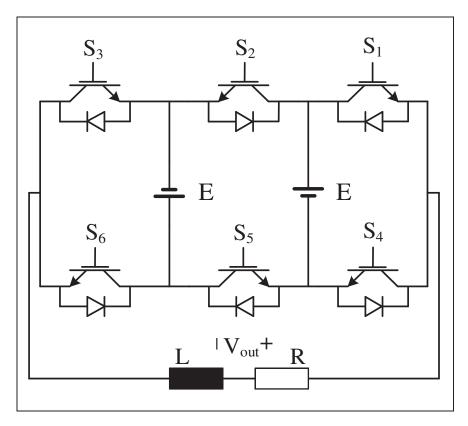

#### Design an Optimized Compact Multilevel Inverter Topology

The compact multilevel inverter structures are interesting topology for single phase configuration. Although the well-known compact topology; Packed U-Cell, has several advantages like reduced components counts, self-voltage balancing in its five-level configuration and so on, it has other disadvantages like difficulty in capacitor voltage balancing in the extension version. Also, Packed U-Cell can be further optimized like other multilevel inverters topologies. In previous works, different control strategies were mainly investigated on Packed U-Cell for various applications and a few works were done to modify this structure. In this work, Packed U-Cell has been deeply optimized and a new compact multilevel inverter structure has been emerged which is so-called as Packed E-Cell topology. Unlike Packed U-Cell where the auxiliary capacitors are extended in a vertical way, Packed E-Cell horizontally develops the auxiliary capacitors which results in further components counts and simplicity in capacitor voltage balancing.

#### **Thesis Outline**

This thesis is written in six chapters which include a survey on multilevel inverters topologies and modulation techniques and the proposed optimization techniques for SHE and SHM on single phase and 3phase inverters applications as well as the novel compact multilevel inverter.

CHAPTER 1 includes a thorough investigation on conventional multilevel inverters topologies, their advantages and disadvantages as well as conventional switching technique. This chapter is completed by a comprehensive survey on the SHE and SHM as the targeted low switching frequency modulation techniques. CHAPTER 2 introduces a new switching

angles constraint which optimizes SHM technique for single phase inverter application to have self-elimination of all triplen harmonics as well as mitigation of selected non-triplen harmonics in a fundamental switching frequency operation. A new switching angles condition is also presented in CHAPTER 3 to optimize SHE technique for single phase inverter application in order to eliminate all triplen harmonics and remove selected nontriplen harmonics in low switching frequency operation. CHAPTER 4 design SHE technique for both 4wire inverters configurations including 3leg 4wire inverter and 4leg 4wire inverter in order to deal with both symmetrical and asymmetrical loads under low switching frequency operation. It is shown through precise analysis that SHE is more compatible with 3leg 4wire inverter over 4leg 4wire inverter in terms of the design complexity, harmonic content and power losses. CHAPTER 5 also presents a hybrid SHM technique for CMV control in 3phase inverter which is done based on the harmonic analysis of the CMV in order to include it in the hybrid SHM cost function. CHAPTER 6 introduces a novel compact multilevel inverter based on the optimization of the previous generation; Packed U-Cell to reach further components counts and more voltage levels as well as simplicity in capacitor voltage balancing. Finally, CHAPTER 7 summarizes the thesis conclusions and presents some novel ideas for the future works.

#### **CHAPTER 1**

# A SURVEY ON CONVENTIONAL MULTILEVEL VOLTAGE SOURCE INVERTERS TOPOLOGIES AND MODULATION TECHNIQUES

#### 1.1 Introduction

During last decade, power electronics converters particularly DC-AC and AC-DC types of converters could find their way into the power industrial market and nowadays they are being employed in various applications such renewable energy system, electrical drives, electrical vehicles, HVDC, UPS and so on. Due to this high attention of industry to the power electronics converter, many researches have comprehensibly investigated different aspects of them, including topology, control and applications. Starting from two level structure, multilevel topologies where emerged to overcome the drawbacks and restrictions which prevents utilization of power converters in higher voltage and current applications. Various topologies of multilevel converters were introduced where each of them possess a prominent advantage that makes them further suitable for particular applications. While the primary multilevel topologies concentrates on using numerous semiconductor devices and main dc sources, later many endeavor were conducted to optimize the conventional multilevel structures or to design an optimized novel structure. The optimization was a trade-off among number of output voltage, number of active and passive devices and dc sources. So, the trend was to produce more voltage levels with reduced components counts while other key parameters are considered.

A long with development of the converter topologies, their switching techniques have been taken into consideration to be optimized as they have a remarkable impact on the performance of the multilevel converters. One of the key points in optimization of the designing the modulation technique is the matter of the switching frequency operation. In general, the switching techniques of the multilevel converters are categorized into the high and low switching frequency methods. Since multilevel converter includes considerable number of semiconductor devices, they can generate notable power losses particularly in

high power applications if the high switching frequency modulation techniques are employed. On the other hand, the low frequency modulation technique must be adaptably optimized according to the targeted application so as they can enhance the efficiency of the converter performance. In this chapter a survey on the conventional multilevel inverters topologies and modulation techniques particularly on low switching frequency switching methods is done to have better understanding of their advantages and disadvantages.

#### 1.2 Multilevel Voltage Source Inverters Topologies

During the last century, researchers focused on amplification of inverter output power. Some tried to increase the current level and some investigated on possibility of voltage level increment in order to achieve the aim. In 1981, Nabae *et al.* the output power by introducing new PWM inverter topology (Nabae, Takahashi et Akagi, 1981). The new inverter called NPC could generate three voltage levels. Presenting NPC topology led to emerging multilevel inverter topologies. Afterwards, different multilevel inverter topologies were emerged and employed in various applications. Some multilevel inverter structures have been surveyed in the following.

### **1.2.1 Diode Clamped Inverter**

As it was mentioned, the three-level NPC inverter was the first attempt to introduce the multilevel inverter structure. The idea of designing NPC inverter is based on the modification of conventional two-level inverter with two switches in each leg as shown in Figure 1.1. In two-level inverter, each capacitor voltage is dropped on one of semiconductor power switches when it is OFF. Then, the switch must be selected in such way to stand with high voltage ratio if it is utilized in high power applications. On the contrary, the NPC topology consists of four power switches in each inverter's leg. Therefore, each capacitor voltage is divided between two switches. Moreover, a diode loop clamped two middle switches has been used in NPC structure to guarantee the proper voltage division between two OFF switches. Due to this fact, NPC inverter is more suitable for high power applications compared to conventional two-level inverter with similar semiconductor switch.

Figure 1.1 Conventional two-level inverter configuration

Table 1.1 Switching States of Three-Level Diode Clamped (NPC) Inverter

| <b>Switching States</b> | S <sub>1A</sub> | S <sub>2A</sub> | S <sub>3A</sub> | S <sub>4A</sub> | Vout |

|-------------------------|-----------------|-----------------|-----------------|-----------------|------|

| 1                       | 1               | 1               | 0               | 0               | +E   |

| 2                       | 0               | 1               | 1               | 0               | 0    |

| 3                       | 0               | 0               | 1               | 1               | -E   |

Table 1.2 Switching States of Five-level Diode Clamped Inverter

| <b>Switching States</b> | S <sub>1A</sub> | S <sub>2A</sub> | S <sub>3A</sub> | S <sub>4A</sub> | S <sub>5A</sub> | S <sub>6A</sub> | S <sub>7A</sub> | S <sub>8A</sub> | V <sub>out</sub> |

|-------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| 1                       | 1               | 1               | 1               | 1               | 0               | 0               | 0               | 0               | +E               |

| 2                       | 0               | 1               | 1               | 1               | 1               | 0               | 0               | 0               | +E/2             |

| 3                       | 0               | 0               | 1               | 1               | 1               | 1               | 0               | 0               | 0                |

| 4                       | 0               | 0               | 0               | 1               | 1               | 1               | 1               | 0               | -E/2             |

| 5                       | 0               | 0               | 0               | 0               | 1               | 1               | 1               | 1               | -E               |

Figure 1.2-a depicts single-phase three-level NPC inverter topology. According to Figure 1.2-a, NPC inverter includes four switches and two diodes for each leg that can produce three voltage levels in output.

Figure 1.2 Single-phase three-level and five-level diode clamped (NPC) inverter configuration, (a) three-level NPC inverter, (b) five-level NPC inverter

In order to generate these three voltage levels (+E, 0, -E), there are three switching states. Considering the fact that ( $S_{IA}$ ,  $S_{3A}$ ) and ( $S_{2A}$ ,  $S_{4A}$ ) are complimentary switches, if two upper switches ( $S_{IA}$ ,  $S_{2A}$ ) are ON state, the output voltage will be +E and if two lower switches ( $S_{3A}$ ,  $S_{4A}$ ) are ON state the voltage –E will be appeared in output terminal. The output voltage zero will be produced when two middle switches ( $S_{2A}$ ,  $S_{3A}$ ) turn on. It must be mentioned that the fourth switching state in NPC will result in DC-link short circuit. The three switching state possibility have been listed in Table 1.1.

Three-level NPC inverter was developed and generalized as Diode Clamped multilevel inverter to have arbitrary multilevel voltage in output terminal using diode loops. Indeed, the three-level diode clamped inverter is known as NPC inverter. The single-phase five-level diode clamped inverter topology has been illustrated in Figure 1.2-b. According to Figure 1.2-b, five-level diode clamped includes eight power switches and six diodes as well as four DC capacitors in DC-link. Also, the corresponding switching state for five-level diode clamped inverter is shown in Table 1.2. In general, (K-I) DC-link capacitors, (K-I)(K-2) clamping diodes and 2(k-I) semiconductor power switches are required to produce K voltage level with diode clamped inverter topology. Furthermore, the diode clamped multilevel inverter advantages and disadvantages are briefly listed in below:

The advantages are summarized as: (I) less DC capacitors and sources are used in diode clamped compared to other multilevel structures. (II) the utilization of DC-link voltage is improved in diode clamped topology. (III) it is not required to employ isolated transformer in diode clamped inverter. The disadvantages are summarized as: (I) the complexity of DC-Link capacitor voltage balancing. (II) the problem of clamping diode selection in higher voltage range. (III) The limitation of its application to medium voltage one.

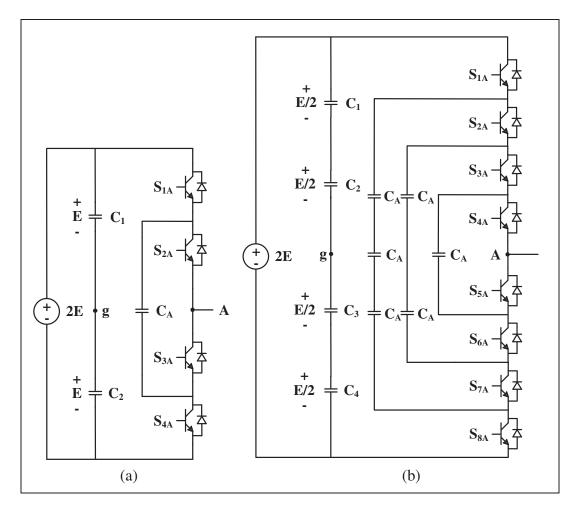

#### **1.2.2 Flying Capacitor Inverter**

Another multilevel inverter structure is Flying Capacitor inverter topology. The idea of designing flying capacitor inverter is to use capacitive loops instead of clamping diode to produce different voltage levels. Figure 1.3-a demonstrates three-level flying capacitor inverter. According to Figure 1.3-a, if the capacitor voltage ( $C_A$ ) is equal to E (which is equivalent to each DC-link capacitor voltage), there would be four switching states possibility for three-level flying capacitor inverter. In this case, the output level +E is caused by turning on two upper switches and -E is produced by ON state of two lower switches. Also, there are two possible states for zero voltage level, turning on the switches ( $S_{1A}$ ,  $S_{3A}$ ) or the switches ( $S_{2A}$ ,  $S_{4A}$ ). These four switching states are listed in Table 1.3. As can be seen from Table 1.3, switches ( $S_{1A}$ ,  $S_{4A}$ ) and ( $S_{2A}$ ,  $S_{3A}$ ) are complementary. The five-level flying

capacitor inverter structure has been also shown in Figure 1.3-b that has eight power switches and six capacitors for capacitive loop as well as four capacitors used DC-link. Table 1.4 contains the corresponding switching states for five-level flying capacitor inverter. In order to produce K voltage level with flying capacitor inverter, 2(K-1) power switches, (K-1)(K-2)/2 balancing capacitors as well as (K-1) capacitors in DC-link are needed. Moreover, the advantages and disadvantages of flying capacitor inverter can be shortly expressed as follows:

The advantages are summarized as: (I) flying capacitor inverter topology requires only one DC-link. (II) it provides more switching states possibility compared to other multilevel inverter structures which can increase the chance of voltage balancing for DC-link capacitor. The disadvantages are summarized as: (I) more capacitor is used in flying capacitor structure which increases the total manufacturing cost. (II) The problem of voltage balancing for capacitor installed in capacitive loop.

Table 1.3 Switching States of Three-Level Flying Capacitor Inverter

| <b>Switching States</b> | $S_{1A}$ | S <sub>2A</sub> | $S_{3A}$ | S <sub>4A</sub> | V <sub>out</sub> |

|-------------------------|----------|-----------------|----------|-----------------|------------------|

| 1                       | 1        | 1               | 0        | 0               | +E               |

| 2                       | 1        | 0               | 1        | 0               | 0                |

| 3                       | 0        | 1               | 0        | 1               | 0                |

| 4                       | 0        | 0               | 1        | 1               | -E               |

Table 1.4 Switching States of Five-Level Flying Capacitor Inverter

| <b>Switching States</b> | S <sub>1A</sub> | S <sub>2A</sub> | S <sub>3A</sub> | S <sub>4A</sub> | S <sub>5A</sub> | S <sub>6A</sub> | S <sub>7A</sub> | S <sub>8A</sub> | Vout |

|-------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------|

| 1                       | 1               | 1               | 1               | 1               | 0               | 0               | 0               | 0               | +E   |

| 2                       | 1               | 1               | 1               | 0               | 1               | 0               | 0               | 0               | +E/2 |

| 3                       | 1               | 1               | 0               | 0               | 1               | 1               | 0               | 0               | 0    |

| 4                       | 1               | 0               | 0               | 0               | 1               | 1               | 1               | 0               | -E/2 |

| 5                       | 0               | 0               | 0               | 0               | 1               | 1               | 1               | 1               | -E   |

Figure 1.3 Single-phase three-level and five-level flying capacitor inverter configuration, (a) three-level flying capacitor inverter, (b) five-level flying capacitor inverter

## 1.2.3 Cascaded H-Bridge Inverter