### Study, Modelling and Control of Bidirectional Battery Chargers for Real-Time Simulation Applications

by

#### Kevin-Rafael SORTO-VENTURA

MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT OF A MASTER'S DEGREE WITH THESIS IN ELECTRICAL ENGINEERING M.A.Sc.

MONTREAL, JULY 20, 2021

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

## THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Kamal Al-Haddad, Thesis Supervisor Department of electrical engineering, École de technologie supérieure

Mrs. Lyne Woodward, President of the Board of Examiners Department of electrical engineering, École de technologie supérieure

Mr. Jean-Nicolas Paquin, External Examiner Application Expertise and Electric Simulation, OPAL-RT Technologies

Mr. Rawad Zgheib, External Examiner IREQ, Hydro-Québec

# THIS THESIS WAS PRESENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC ON JULY 6, 2021

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGEMENTS

I would like to start by acknowledging that, just as it did for everyone else, the Covid-19 pandemic brought about sudden and considerable changes to the work I would do with regards to my thesis. We all had to learn how to efficiently work remotely and the lack of human interaction made it difficult to find motivation at times. This is why the support of the people mentioned below was all the more invaluable especially during the last year and a half of my Master.

First and foremost, I would like to express my thanks to my parents. They are the ones who had initially encouraged me to pursue graduate studies, and despite the fact that they never fully understood the scope of my work, they always believed in me and supported me in any way that they could.

Then, I would also like to thank my research supervisor Professor Kamal Al-Haddad. Of course, he was the person who guided me throughout my research work, but more importantly, his innovative ideas and genuine enthusiasm towards my work are ultimately what gave me the inspiration and motivation to work hard and to produce the best results I could. I also particularly appreciate how despite the restrictions of remote work, he was always readily available to meet with me and answer my questions. I am also giving special thanks to the NSERC for their financial support of my project.

Finally, I would like to thank the people of Opal-RT who also helped with my thesis. First, I am thanking Jean-Nicolas Paquin, who while I was working at the company, proposed to me the Master's project I ended up working on with Professor Kamal Al-Haddad.

Then, I also give my thanks to Wei Li, who was somewhat of a mentor for me during my Master. His technical expertise and support were invaluable to me as I was able to learn much about the field of real-time simulation thanks to him. Furthermore, I am certain that the quality of my thesis greatly benefited from my interactions with him.

Once again, thank you to all who have supported me throughout these two years and made this a memorable experience for me.

## Étude, modélisation et commande de chargeurs de batterie bidirectionnels pour applications en simulation en temps-réel

#### Kevin-Rafael SORTO-VENTURA

#### RÉSUMÉ

Le travail réalisé dans ce projet a pour but de proposer une topologie de convertisseur AC-DC et une commande appropriées pour des chargeurs de batterie bidirectionnels à haute puissance. D'autre part, l'objectif est aussi de concevoir des modèles équivalents de ces convertisseurs afin de les implémenter en simulation en temps-réel. Cette recherche est motivée par la présence croissante des véhicules électriques sur les routes ainsi que par la demande accrue pour des stations de charge rapides et bidirectionnelles. En plus d'offrir une densité énergétique élevée et un écoulement de puissance bidirectionnel, les convertisseurs employés dans les chargeurs de batterie devraient assurer une bonne qualité de l'énergie. Par conséquent, ce mémoire étudie deux topologies de convertisseurs multiniveaux qui sont capables de minimiser la distorsion harmonique sur le réseau électrique grâce à leur nombre élevé de niveaux de tension. Donc, le convertisseur monophasé H-PUC à 23 niveaux est proposé avec une commande de type model predictive control. Ce convertisseur est implémenté en simulation en temps-réel avec le logiciel RT-LAB sur le simulateur OP4510 et il est démontré que cette topologie réduit considérablement les exigences de filtrage du courant AC lorsque comparé à des convertisseurs conventionnels. Ensuite, une commande de type deadbeat predictive control pour un écoulement bidirectionnel de la puissance est développé pour le convertisseur triphasé à 13 niveaux PM-ANPC. Des résultats de simulation obtenus dans Simulink confirment que la méthode de commande proposée peut efficacement réguler le courant AC et la tension du lien DC autant lorsque le convertisseur est en mode charge que lorsqu'il est en mode décharge. Finalement, un modèle équivalent du PM-ANPC est présenté et validé à l'aide d'un modèle référence qui utilise des blocs de SimPowerSystems dans Simulink. Puis, un simulateur en temps-réel OP4510 est utilisé afin d'illustrer la performance de simulation supérieure du modèle équivalent proposé par rapport au modèle référence.

**Mots-clés:** chargeur de batterie, véhicule électrique, convertisseur multiniveaux, qualité de l'énergie, simulation en temps-réel

## Study, Modelling and Control of Bidirectional Battery Chargers for Real-Time Simulation Applications

#### Kevin-Rafael SORTO-VENTURA

#### **ABSTRACT**

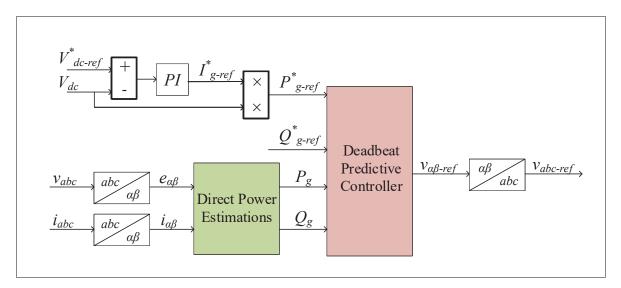

The work done in this project aims to propose a suitable AC-DC converter topology and control method for high power, bidirectional battery chargers. Moreover, another objective is to design equivalent converter models suitable for real-time simulation applications. This research is motivated by the growing presence of electric vehicles and the increasing demand for faster and bidirectional battery chargers. In addition to high power density and bidirectional power flow capability, the converter used in the battery charger should offer good power quality. Therefore, this thesis studies two multilevel converter topologies, which are able to minimize harmonic distortion on the grid due to their high number of output voltage levels. Thus, the single-phase 23-level H-PUC is proposed with a model predictive controller. By implementing this converter in real-time simulation using the RT-LAB software and OP4510 simulator, it is shown that the topology greatly reduces the AC current filtering requirements when compared to conventional converter topologies. Then, a deadbeat predictive controller for bidirectional power flow is developed for the three-phase PM-ANPC 13-level converter. Simulation results obtained in Simulink demonstrate that the proposed controller can effectively regulate the AC current and DC link voltage during both charging and discharging modes of operation. Finally, an equivalent model of the PM-ANPC converter is presented and validated against a reference model that uses blocks from the SimPowerSystems library in Simulink. Then, an OP4510 real-time simulator is used to illustrate the improved simulation performance of the equivalent model with respect to the reference model.

**Keywords:** battery charger, electric vehicle, multilevel converter, power quality, real-time simulation

#### TABLE OF CONTENTS

|      |         |                                                                                                                                                           | Page |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| INTR | ODUCTI  | ON                                                                                                                                                        | 1    |

| CHAI | PTER 1  | LITERATURE REVIEW OF ELECTRIC VEHICLE BATTERY CHARGERS, MULTILEVEL CONVERTERS AND REAL-TIME                                                               |      |

|      |         | SIMULATION                                                                                                                                                |      |

| 1.1  |         | ction                                                                                                                                                     |      |

| 1.2  |         | ters Commonly Used for Battery Chargers                                                                                                                   |      |

|      | 1.2.1   | The Three-phase Full Bridge Converter                                                                                                                     |      |

|      | 1.2.2   | The Neutral-point-clamped Converter                                                                                                                       |      |

| 1.3  |         | vel Converters and Their Advantages                                                                                                                       |      |

|      | 1.3.1   | The Cascaded H-bridge Converter                                                                                                                           |      |

|      | 1.3.2   | The Active-neutral-point-clamped Multilevel Converter                                                                                                     |      |

|      | 1.3.3   | The Packed U-cell Family of Multilevel Converters                                                                                                         |      |

| 1.4  |         | me Simulation and Equivalent Converter Models                                                                                                             |      |

|      | 1.4.1   | The Importance of Real-time Simulation                                                                                                                    | 14   |

|      | 1.4.2   | Performance Considerations and Equivalent Converter Models for                                                                                            |      |

|      |         | Real-time Simulation                                                                                                                                      | 15   |

| 1.5  | Conclu  | sion                                                                                                                                                      | 16   |

| CHAI | PTER 2  | 23-LEVEL SINGLE DC SOURCE HYBRID PUC (H-PUC) CONVERTER TOPOLOGY WITH REDUCED NUMBER OF COMPONENTS: REAL-TIME IMPLEMENTATION WITH MODEL PREDICTIVE CONTROL | 19   |

| 2.1  | Introdu | ction                                                                                                                                                     |      |

| 2.2  |         | PUC (H-PUC) Inverter Topology                                                                                                                             |      |

|      | 2.2.1   | Presentation of the Circuit Topology                                                                                                                      |      |

|      | 2.2.2   | Determination of Capacitor Values                                                                                                                         |      |

|      | 2.2.3   | Comparison of the H-PUC with Other MLI topologies                                                                                                         |      |

| 2.3  |         | oposed Finite Control Set Model Predictive Controller (FCS-MPC)                                                                                           |      |

|      | 2.3.1   | Mathematical Modelling of the Inverter                                                                                                                    |      |

|      | 2.3.2   | Control Objectives and Implementation of the MPC                                                                                                          |      |

|      | 2.3.3   | Reference Values for 23 Output Voltage Levels                                                                                                             |      |

| 2.4  | Conver  | ter Modeling for Real-Time Simulation on the OPAL-RT Platform                                                                                             |      |

|      | 2.4.1   | Software-in-the-Loop Simulation                                                                                                                           |      |

|      | 2.4.2   | Real-Time Model of the H-PUC Inverter                                                                                                                     |      |

|      | 2.4.3   | Validation of the Equivalent Real-Time Model of the H-PUC                                                                                                 |      |

|      |         | Inverter                                                                                                                                                  | 36   |

| 2.5  | Real-Ti | me Simulation Results                                                                                                                                     |      |

| 2.6  | Conclu  |                                                                                                                                                           | 46   |

| CHAP   | TER 3   | THE PARALLELED MODULAR ANPC CONVERTER AS A         |    |  |  |  |

|--------|---------|----------------------------------------------------|----|--|--|--|

|        |         | BIDIRECTIONAL BATTERY CHARGER WITH DEADBEAT        |    |  |  |  |

|        |         | PREDICTIVE CONTROL                                 | 49 |  |  |  |

| 3.1    | Introdu | ction                                              | 49 |  |  |  |

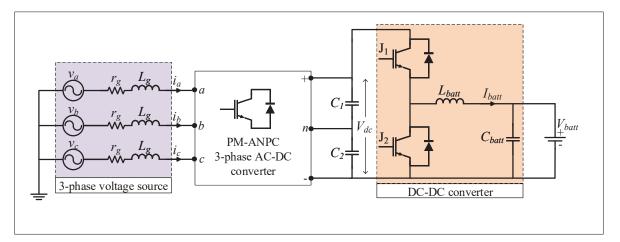

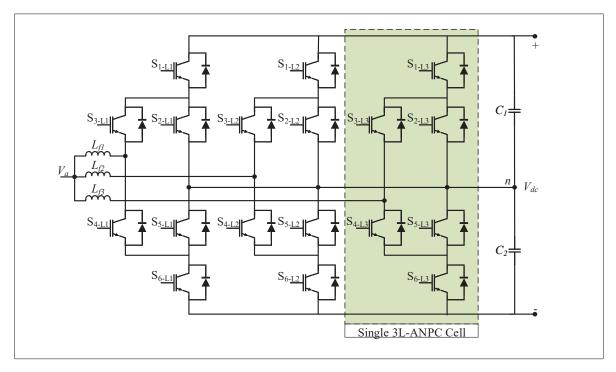

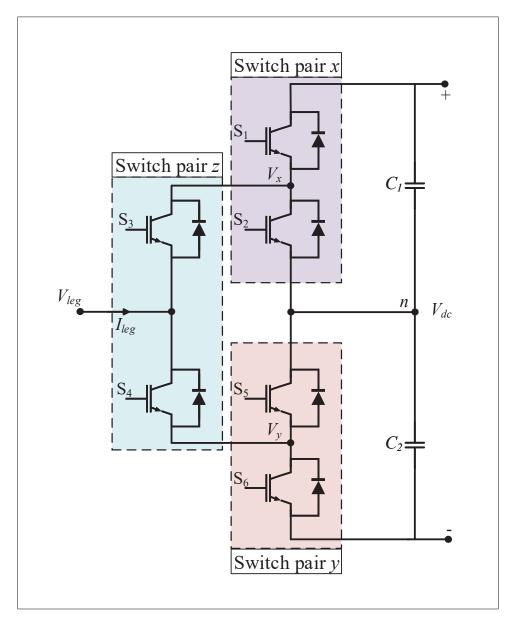

| 3.2    | Present | tation of the PM-ANPC Converter Topology           | 50 |  |  |  |

| 3.3    |         | erview of the Modulation Method                    |    |  |  |  |

| 3.4    | Implen  | nentation of the Deadbeat Predictive Controller    | 54 |  |  |  |

|        | 3.4.1   | The Deadbeat Predictive Controller for the PM-ANPC | 54 |  |  |  |

| 3.5    | Simula  | tion Results and Validation                        | 57 |  |  |  |

|        | 3.5.1   | System Under Test                                  | 57 |  |  |  |

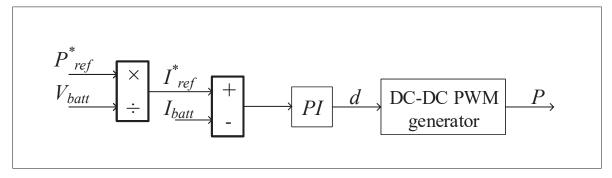

|        | 3.5.2   | Pulse Generation for the DC-DC Converter           | 58 |  |  |  |

|        | 3.5.3   | Simulation Setup                                   | 59 |  |  |  |

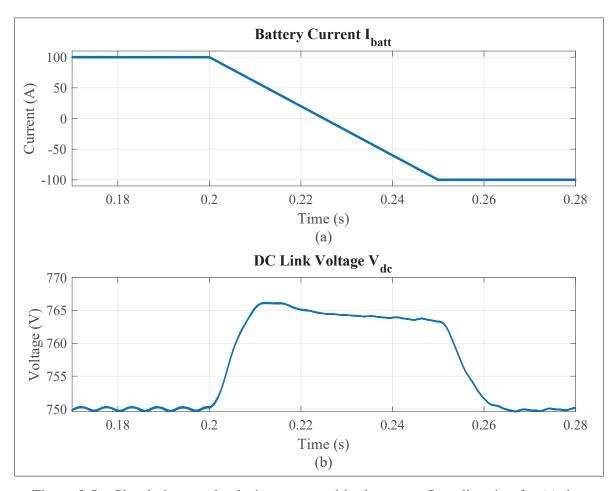

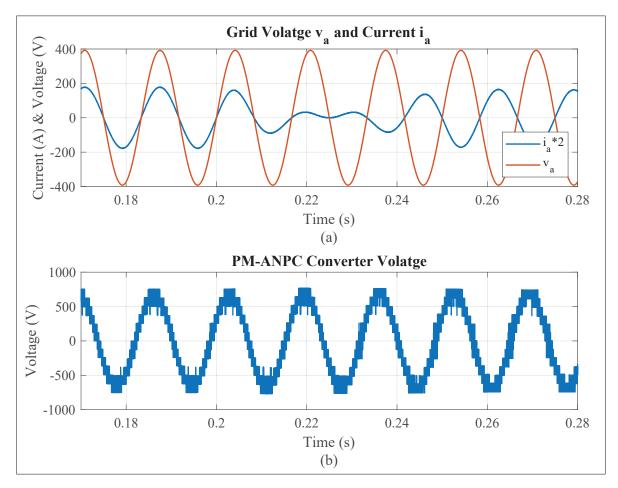

|        | 3.5.4   | Bidirectional Power Flow Results                   | 60 |  |  |  |

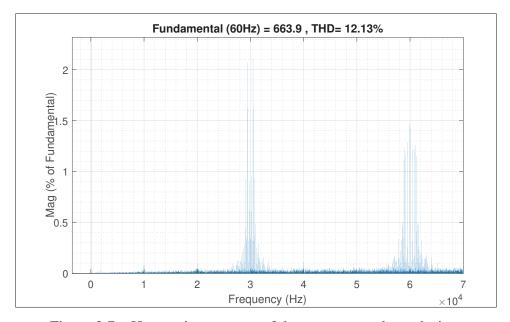

|        | 3.5.5   | Analysis of the Harmonic Spectra                   | 63 |  |  |  |

| 3.6    | Conclu  | sion                                               | 65 |  |  |  |

| СНАР   | TER 4   | AN EQUIVALENT MODEL OF THE PARALLELED              |    |  |  |  |

|        |         | MODULAR ANPC CONVERTER WITH A DECOUPLED DC         |    |  |  |  |

|        |         | LINK FOR REAL-TIME SIMULATION                      | 67 |  |  |  |

| 4.1    | Introdu | ection                                             |    |  |  |  |

| 4.2    |         | lent Model of a PM-ANPC Cell                       |    |  |  |  |

|        | 4.2.1   | The 3L-ANPC Cell                                   |    |  |  |  |

|        | 4.2.2   |                                                    |    |  |  |  |

|        | 4.2.3   | Full 3L-ANPC Cell Model and Voltage Calculations   |    |  |  |  |

| 4.3    | Modell  | ing of the Decoupled DC Link Capacitors            |    |  |  |  |

|        | 4.3.1   |                                                    |    |  |  |  |

|        | 4.3.2   | Further Simplification of the DC Link Model        |    |  |  |  |

| 4.4    | Compa   | rison of Offline and Real-Time Simulation Results  |    |  |  |  |

| 4.5    |         | sion                                               |    |  |  |  |

| CONC   | CLUSION | N AND RECOMMENDATIONS                              | 83 |  |  |  |

| LIST ( | OF REFI | ERENCES                                            | 86 |  |  |  |

|        |         |                                                    |    |  |  |  |

#### LIST OF TABLES

|           | Page                                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 | Possible Switching States and Capacitor Charging States of 1st and 2nd PUC                                                            |

| Table 2.2 | Comparison of the Proposed 23L H-PUC Converter with other Presented Converters in the Literature in Terms of the Number of Components |

| Table 2.3 | Simplified Switching States and Capacitor Charging States of 1st and 2nd PUC for MPC                                                  |

| Table 2.4 | Simulation Parameters                                                                                                                 |

| Table 3.1 | Switching States of a 3L-ANPC Cell                                                                                                    |

| Table 3.2 | Circuit and simulation parameters                                                                                                     |

| Table 4.1 | Positive and negative path voltages with respect to the switching pulses 7                                                            |

| Table 4.2 | Circuit and simulation parameters                                                                                                     |

| Table 4.3 | Comparison of execution times and RT performance between the reference and equivalent models                                          |

#### LIST OF FIGURES

| Page                                                                                                                    |            |

|-------------------------------------------------------------------------------------------------------------------------|------------|

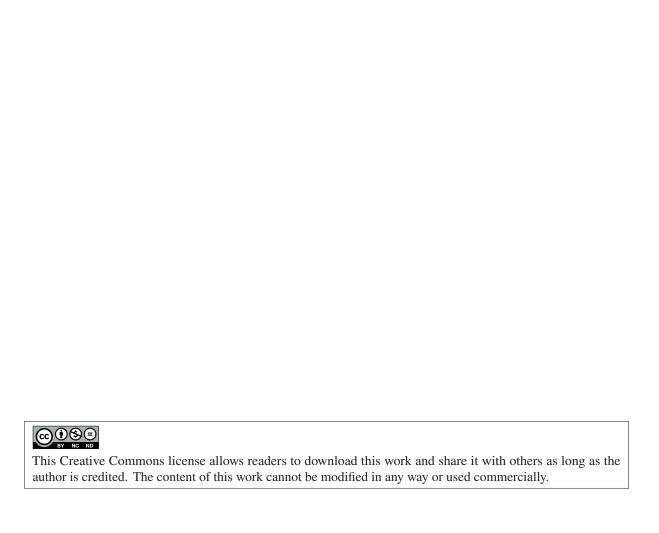

| gure 1.1 Circuit diagram of the three-phase full-bridge converter                                                       | Figure 1.1 |

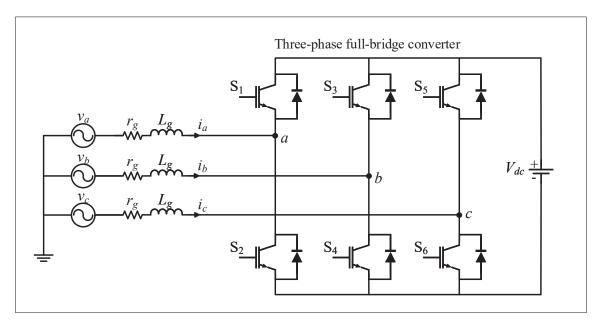

| gure 1.2 Circuit diagram of the three-phase NPC converter                                                               | Figure 1.2 |

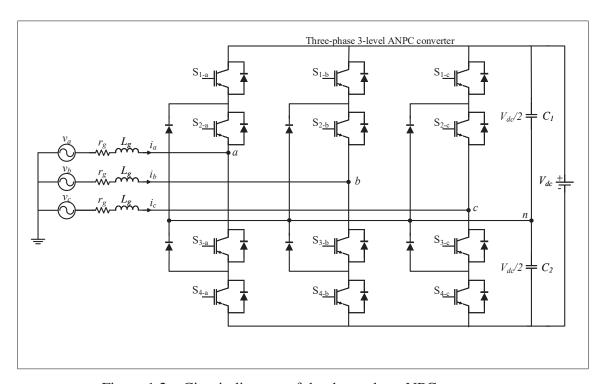

| gure 1.3 Waveform comparison of a perfect sine wave with (a) a three-level voltage and (b) a 7-level voltage            | Figure 1.3 |

| gure 1.4 Voltage THD with respect to the number of voltage levels                                                       | Figure 1.4 |

| gure 1.5 Circuit diagram of a single-phase cascaded H-bridge converter                                                  | Figure 1.5 |

| gure 1.6 Circuit diagram of the three-phase 3L-ANPC converter                                                           | Figure 1.6 |

| gure 1.7 Circuit diagram of the single-phase 5L-ANPC converter                                                          | Figure 1.7 |

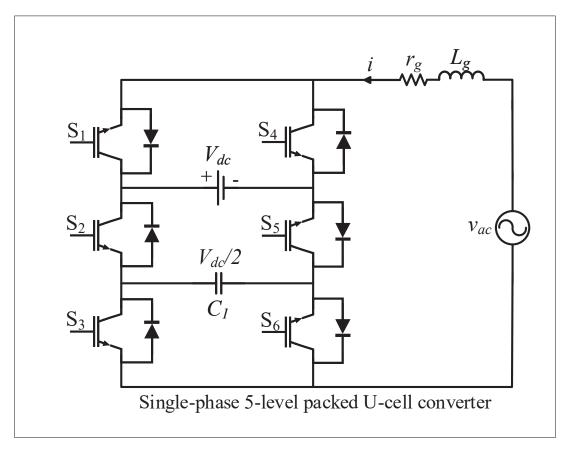

| gure 1.8 Circuit diagram of the single-phase PUC5 converter                                                             | Figure 1.8 |

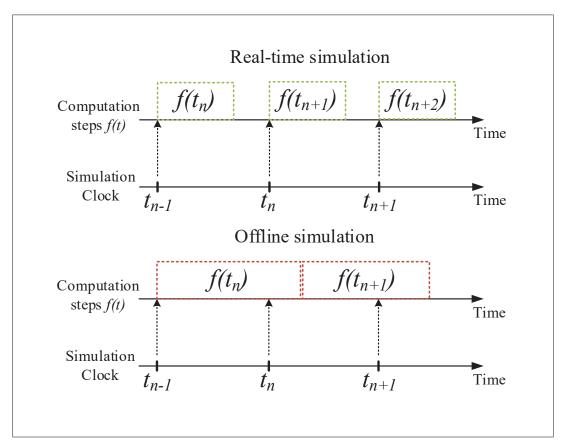

| gure 1.9 Diagram of the computational differences between offline and real-time simulation                              | Figure 1.9 |

| gure 2.1 The Proposed Hybrid PUC (H-PUC) Inverter Topology with Single DC Source                                        | Figure 2.1 |

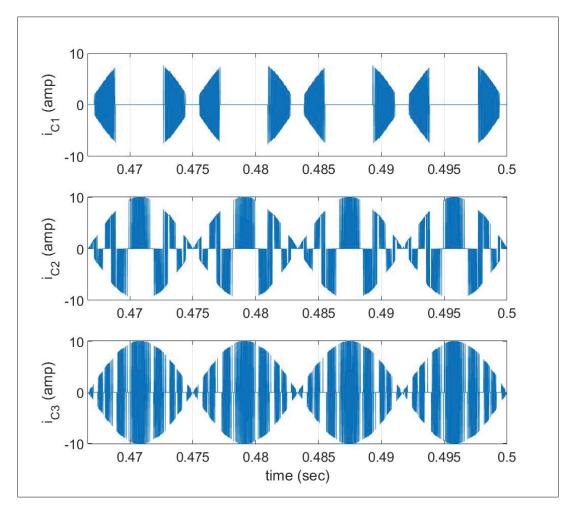

| gure 2.2 Charging and discharging currents of all three capacitors of the H-PUC converter during two fundamental cycles | Figure 2.2 |

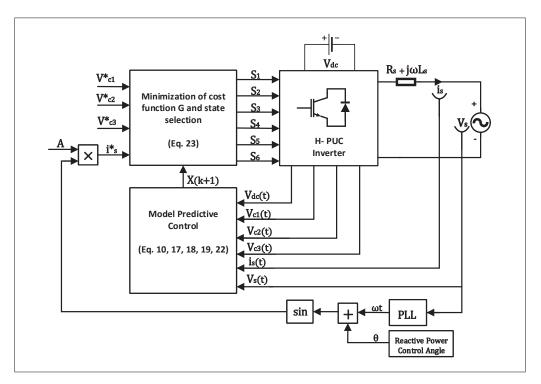

| gure 2.3 The Schematic Diagram of the Proposed FCS-MPC for the H-PUC Inverter                                           | Figure 2.3 |

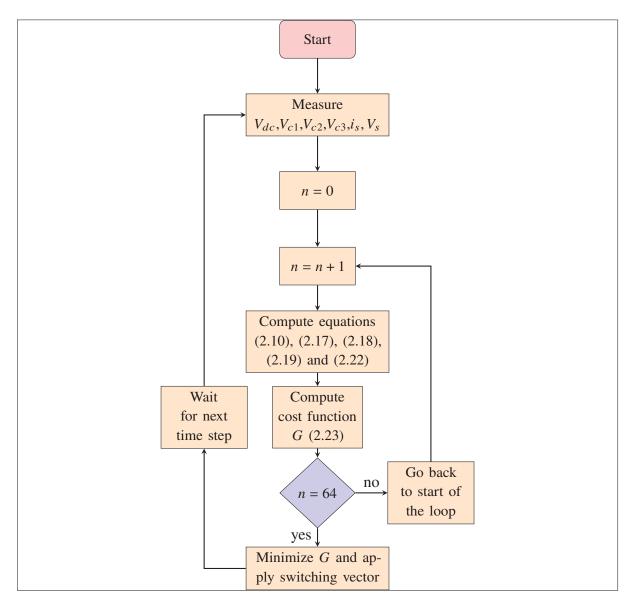

| gure 2.4 Flowchart of the Proposed FCS-MPC Process                                                                      | Figure 2.4 |

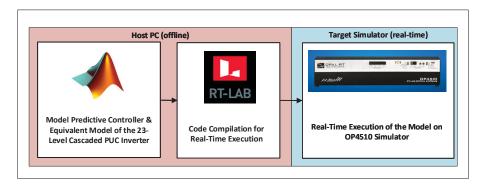

| gure 2.5 Schematic of the Simulation Process with OP4510                                                                | Figure 2.5 |

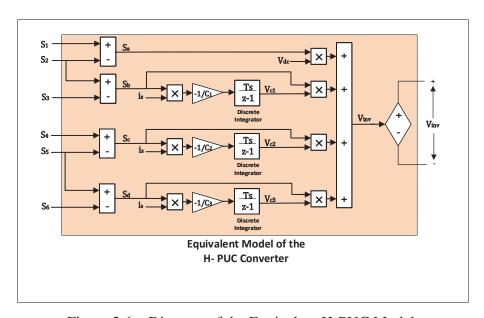

| gure 2.6 Diagram of the Equivalent H-PUC Model                                                                          | Figure 2.6 |

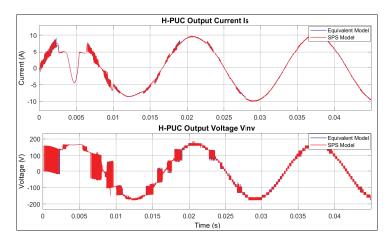

| gure 2.7 Output voltage and grid current transient response: comparison of SPS and equivalent model                     | Figure 2.7 |

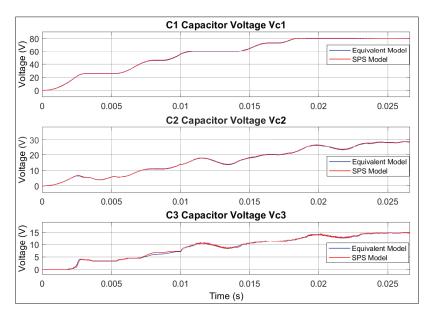

| gure 2.8 Capacitor voltages transient response: comparison of SPS and equivalent model                                  | Figure 2.8 |

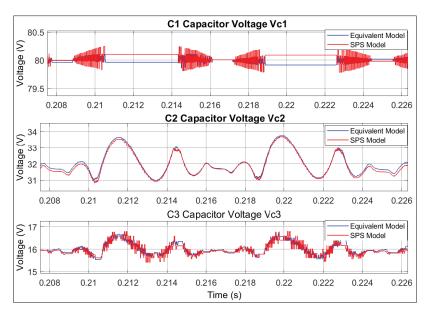

| gure 2.9 Capacitor voltages ripple: comparison of SPS and equivalent model 37                                           | Figure 2.9 |

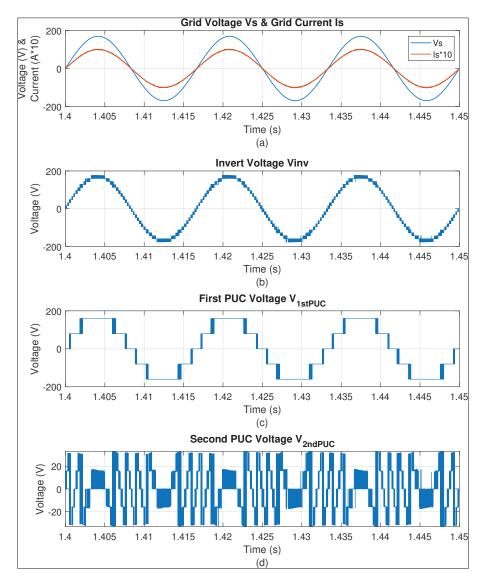

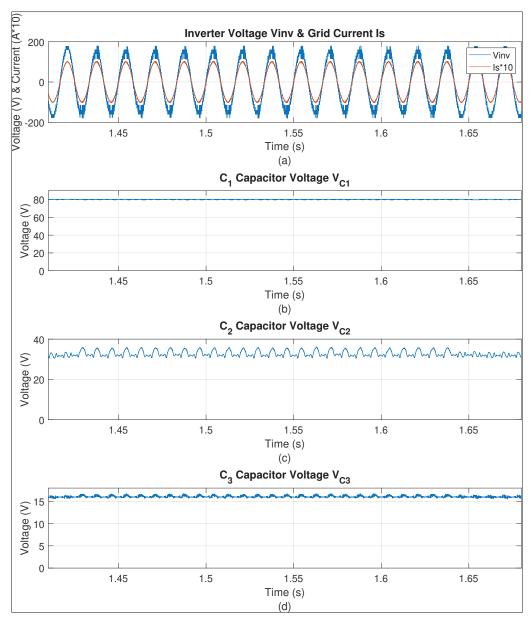

| Figure 2.10 | Real-time simulation results of the proposed H-PUC converter. (a) Grid voltage and current. (b) The output voltage of the proposed 23- level H-PUC inverter (c) The first PUC sub-module output voltage.  (d) The second PUC sub-module output voltage |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

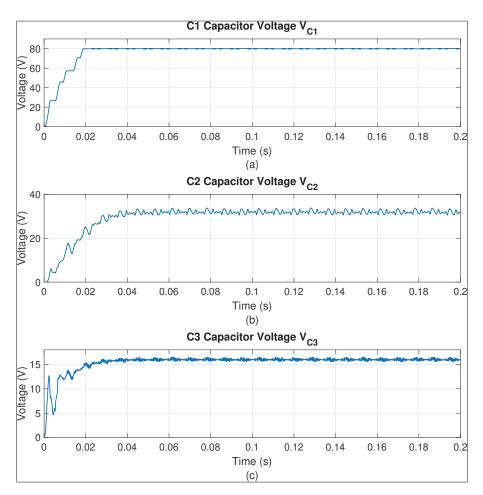

| Figure 2.11 | Transient response of (a) C1 capacitor voltage. (b) C2 capacitor voltage. (c) C3 capacitor voltage                                                                                                                                                     |

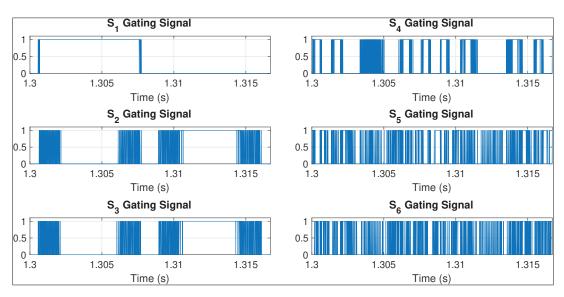

| Figure 2.12 | Gating Signals for Switches S1 to S6 Over a Steady-State 60Hz Cycle 41                                                                                                                                                                                 |

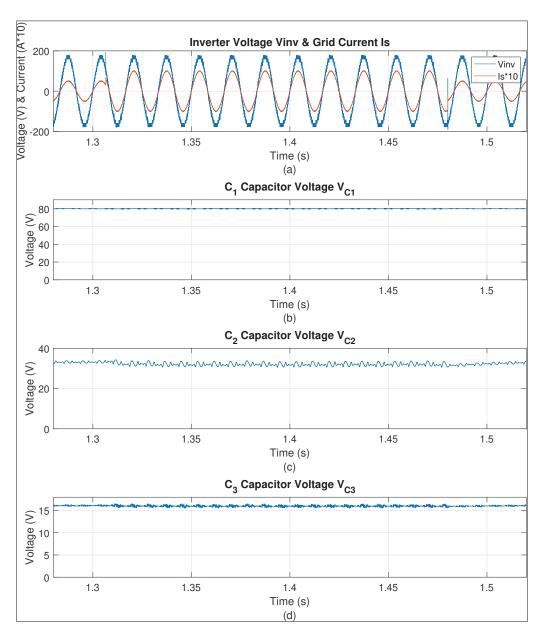

| Figure 2.13 | Response for the (a) inverter voltage and grid current, (b) C1 voltage, (c) C2 voltage and (d) C3 voltage during a step current change                                                                                                                 |

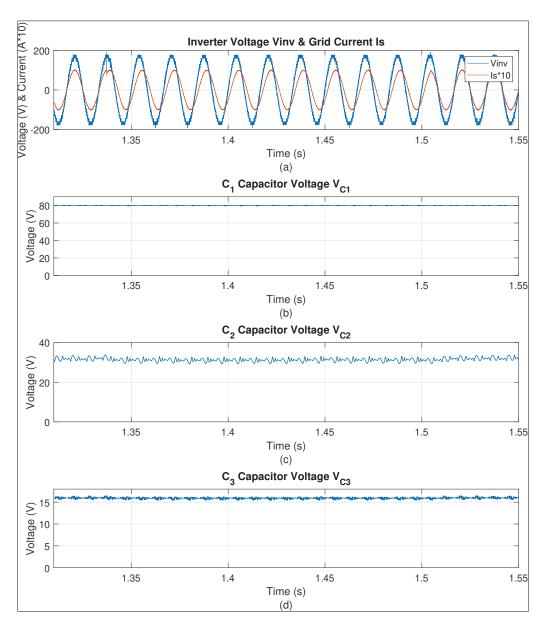

| Figure 2.14 | Response for the (a) inverter voltage and grid current, (b) C1 voltage, (c) C2 voltage and (d) C3 voltage during a current phase change                                                                                                                |

| Figure 2.15 | Response for the (a) inverter voltage and grid current, (b) C1 voltage, (c) C2 voltage and (d) C3 voltage during a voltage sag test                                                                                                                    |

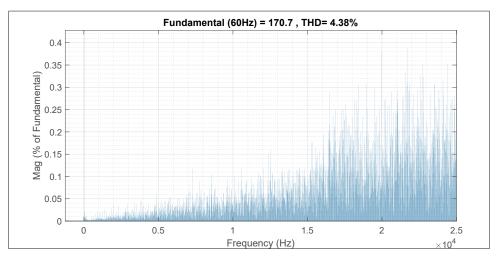

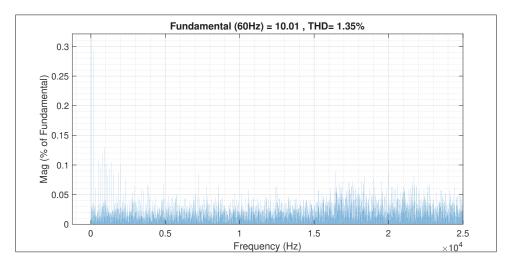

| Figure 2.16 | Inverter Voltage (Vinv) FFT Analysis                                                                                                                                                                                                                   |

| Figure 2.17 | Grid Current (Is) FFT Analysis                                                                                                                                                                                                                         |

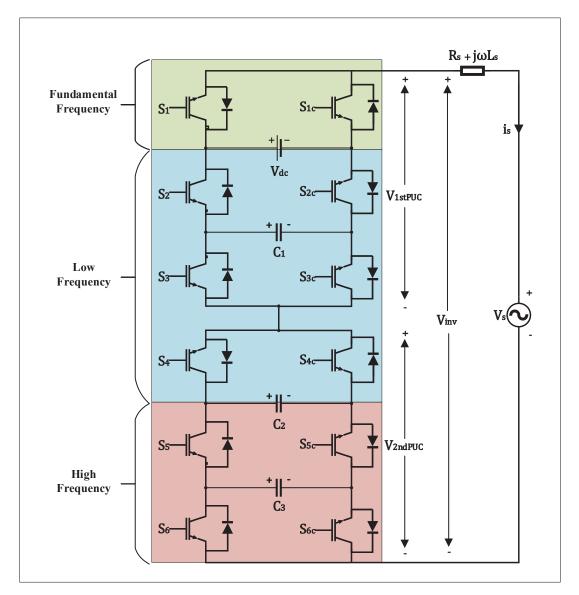

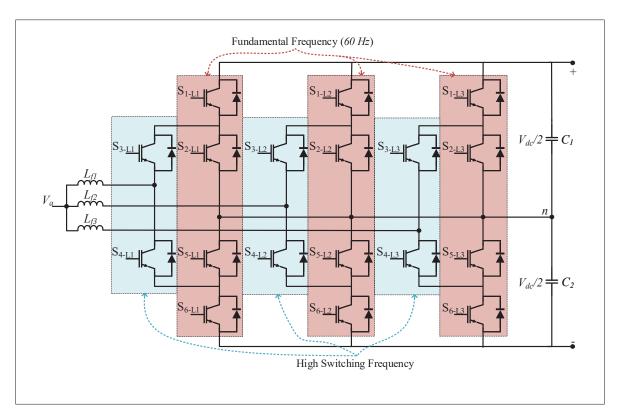

| Figure 3.1  | Per phase circuit diagram of the PM-ANPC converter                                                                                                                                                                                                     |

| Figure 3.2  | Diagram of the deadbeat predictive control system                                                                                                                                                                                                      |

| Figure 3.3  | Diagram of the system under test                                                                                                                                                                                                                       |

| Figure 3.4  | Diagram of DC-DC converter pulse generation                                                                                                                                                                                                            |

| Figure 3.5  | Simulation results during a reversal in the power flow direction for (a) the battery current and (b) the DC link voltage                                                                                                                               |

| Figure 3.6  | Simulation results during a reversal in the power flow direction for (a) the grid current & voltage and (b) the PM-ANPC converter voltage                                                                                                              |

| Figure 3.7  | Harmonic spectrum of the converter voltage during charging mode 63                                                                                                                                                                                     |

| Figure 3.8  | Harmonic spectrum of the converter voltage during discharging mode 64                                                                                                                                                                                  |

| Figure 4.1  | Per phase circuit diagram of the PM-ANPC converter highlighting a 3L-ANPC cell                                                                                                                                                                         |

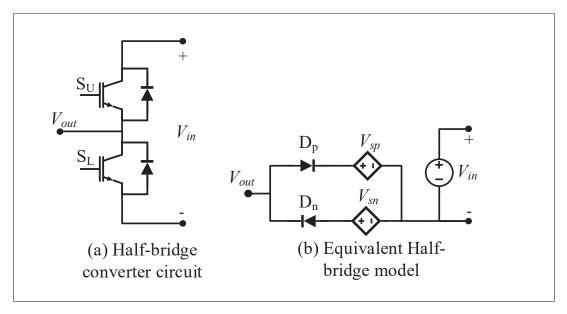

| Figure 4.2 | (a) Half-bridge converter and (b) equivalent model with controlled voltage sources                                                                        | 70 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.3 | Circuit diagram of a 3L-ANPC cell highlighting the half-bridge submodules                                                                                 | 72 |

| Figure 4.4 | Equivalent 3L-ANPC cell model                                                                                                                             | 73 |

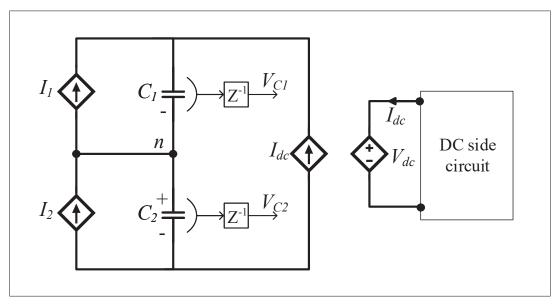

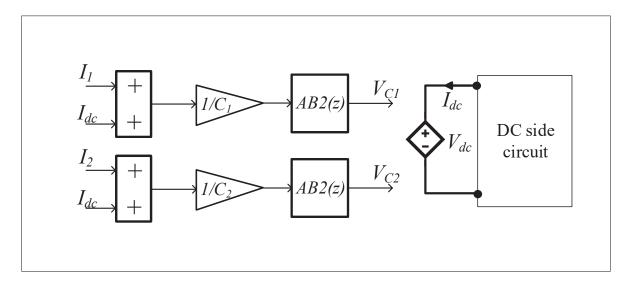

| Figure 4.5 | Circuit diagram of the decoupled DC link                                                                                                                  | 75 |

| Figure 4.6 | Diagram of the simplified decoupled DC link                                                                                                               | 76 |

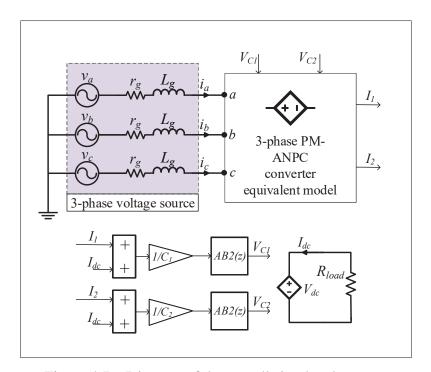

| Figure 4.7 | Diagram of the overall simulated system                                                                                                                   | 78 |

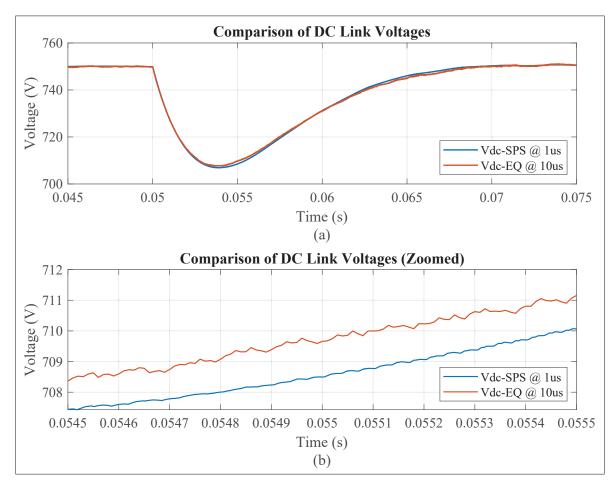

| Figure 4.8 | Comparison of DC voltages: (a) during transient response and (b) zoomed in                                                                                | 80 |

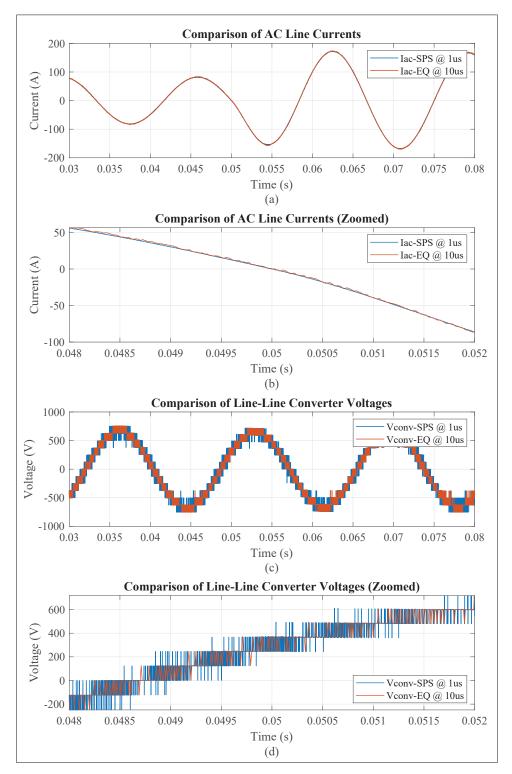

| Figure 4.9 | Comparison of AC measurements: (a) AC line current, (b) zoomed in AC line current, (c) line-to-line converter voltage and (d) zoomed in converter voltage | 81 |

#### LIST OF ABBREVIATIONS

AB2 Adams-Bashforth 2

AC Alternating current

ANPC Active-neutral-point-clamped

CHB Cascaded H-Bridge

CPU Central processing unit

DC Direct current

DPC Deadbeat predictive control

EMI Electromagnetic interference

EV Electric vehicle

FCS-MPC Finite control set model predictive control

FE Forward Euler

FFT Fast Fourier transform

HB Half-bridge

HF High frequency

HIL Hardware-in-the-loop

HNPC Hybrid neutral-point-clamped

H-PUC Hybrid Packed U-cell

IGBT Insulated-gate bipolar transistor

KVL Kirchoff voltage loop

LF Low frequency

MLC Multilevel converter

MLI Multilevel inverter

MOSFET Metal oxide semiconductor field-effect transistor

MPC Model predictive control

NPC Neutral-point-clamped

PCC Point of common coupling

PFC Power factor corrector

PLL Phase-locked-loop

PM-ANPC Paralleled modular active-neutral-point-clamped

PUC Packed U-cell

RCP Rapid control prototyping

RTS Real-time simulation

SIL Software-in-the-loop

SPS SimPowerSystems

SPWM Sine pulse width modulation

SVM Space vector modulation

THD Total harmonic distortion

VSC Voltage source converter

VSI Voltage source inverter

#### INTRODUCTION

The presence of electric vehicles (EVs) is steadily increasing on the roads worldwide. This increase is prompting the implementation of a higher number of battery charging stations due to the higher demand. In addition, EVs are themselves becoming more power hungry and are starting to carry batteries with larger capacities. As a result, even more high power, fast DC battery chargers need to be installed (Burnham et al., 2017; Khaligh & Antonio, 2019). Indeed, manufacturers are constantly pushing the limits of their peak charging rates with Tesla, for example, achieving up to 250kW of power delivery from the third version of their supercharger (Tesla, 2019). However, high peak power delivery is not the only feature that is desirable in battery chargers. In fact, manufacturers and researchers have also been developing battery chargers with bidirectional power flow capabilities (Restrepo, Morris, Kazerani & Cañizares, 2018). Bidirectional battery chargers have the ability to use the connected EV batteries as storage devices and thus, can send the battery power back to the grid. Another consideration when designing these chargers is the control of the power quality at the point of interconnection with the grid. Since charging stations are typically composed of multiple high power chargers all on the same grid connection, and if we consider that these are bidirectional chargers, then ensuring good power quality becomes even more important.

#### **Objectives**

Therefore, one of the objectives of this thesis is to propose an AC-DC converter topology and control method that will satisfy the high power density, bidirectional power flow and good power quality requirements for battery charger applications. Then, in an effort to facilitate the study of large systems containing multiple units of the proposed battery charger, this thesis also aims to develop an equivalent model of the proposed converter topology. This model is to be tested and validated for real-time simulation applications.

#### **Thesis Outline**

The first chapter of this thesis is a literature review that goes over conventional AC-DC converter topologies, such as the full-bridge and neutral-point-clamped (NPC) converters, that are commonly used in battery chargers. Then, an overview of some multilevel converter topologies is done with an emphasis on their advantages over the conventional topologies. Next, the literature review gives a brief overview of real-time simulation, its main features and the importance of equivalent converter models used in real-time simulation. In chapter 2, the single-phase Hybrid-PUC 23-level converter topology and its associated model predictive controller (MPC) are proposed. A simple equivalent model is also developed for the Hybrid-PUC and real-time simulation results are provided to validate the design. Chapter 3 studies the three-phase paralleled modular active-neutral-point clamped (PM-ANPC) 13-level converter and proposes a deadbeat predictive control method for it that allows for bidirectional power flow. The proposed system is tested and offline simulation results are given. Next, chapter 4 proposes a detailed equivalent model with a decoupled DC link for the PM-ANPC. The equivalent model is compared to a reference model in order to confirm its validity. Then, a comparison of their performance is done for both offline and real-time simulation to highlight the improved performance of the proposed equivalent model. Finally, the conclusion of this thesis regroups the main takeaways of the research done and gives recommendations for potential future works.

#### **CHAPTER 1**

#### LITERATURE REVIEW OF ELECTRIC VEHICLE BATTERY CHARGERS, MULTILEVEL CONVERTERS AND REAL-TIME SIMULATION

#### 1.1 Introduction

The increasing rate of the electrification of transportation combined with larger battery capacities are prompting more research to be done in the field of fast DC battery chargers. Since this thesis aims to contribute to the field of battery charger topologies and equivalent converter models, an appropriate literature review needs to be done. Indeed, it is relevant to assess the current state-of-the-art in terms of the power electronic converters that are commonly used in battery chargers currently. This assessment can provide information as to what are the important features that a converter needs in order to properly operate as a battery charger. Then, in an effort to iterate upon conventional battery charger topologies, a study of the main multilevel converter topologies is done to show their inherent advantages. Moreover, it is relevant to define the importance of real-time simulation and how it can benefit the testing and prototyping of large and complex circuits such as those containing multilevel converters.

Therefore, this literature review begins by reviewing the main power electronic converter topologies used currently in fast DC battery chargers. Next, an overview of the main multilevel converter topology families is done with an emphasis on their advantages when compared to conventional two or three-level converters. Finally, a brief review of real-time simulation and equivalent converter models is presented so as to highlight their importance in the field of prototyping and testing of large electrical systems.

#### 1.2 Converters Commonly Used for Battery Chargers

There exist different types of EV battery chargers, which are classified by their power levels ranging from levels 1 to 3. Levels 1 and 2 are lower power on-board chargers that are integrated within the vehicle's own power electronics, and are typically fed by single-phase grid connections.

In comparison, level 3 charging stations output much higher peak power (50kW +) and usually perform the three-phase AC to DC conversion through a dedicated power electronic converter in the station itself (Tran, Sutanto & Muttaqi, 2017). The latter type, also known as fast DC charging, is the focus of this thesis. As such, the full bridge and the neutral-point-clamped converters, two of the more common three-phase AC-DC converters used in battery chargers (Yilmaz & Krein, 2013), are reviewed in this section.

#### 1.2.1 The Three-phase Full Bridge Converter

Probably the most common three-phase converter is the full bridge converter pictured in Fig. 1.1. It is used in many different applications as a power factor corrector (PFC) and has multiple interesting advantages.

Figure 1.1 Circuit diagram of the three-phase full-bridge converter

Firstly, it is composed of relatively few power electronic switches with only six of them across all three phases. The full bridge converter's simple topology also makes designing control systems for it an easy task. All this can be achieved while still maintaining relatively good power efficiency and near unit power factor (Kolar & Friedli, 2013).

However, there are some drawbacks with this converter. Indeed, since this is only a three-level voltage converter, the input AC side requires large and bulky inductors in order to filter the current and achieve acceptable total harmonic distortion (THD) levels. Furthermore, the maximum voltage stress experience by the semiconductor switches is equal to the full value of the DC link voltage, which means that their reliability is reduced in the long term (Yilmaz & Krein, 2013).

#### 1.2.2 The Neutral-point-clamped Converter

Some of the disadvantages mentioned above are mitigated in battery chargers using the neutral-point-clamped (NPC) converter. The general topology of this converter is illustrated in Fig. 1.2. Unlike the full-bridge converter, the NPC converter uses a combination of active semiconductor switches, passive diodes and capacitors (Rodriguez, Bernet, Steimer & Lizama, 2010).

Figure 1.2 Circuit diagram of the three-phase NPC converter

More precisely, the three-phase converter has a total of 12 switches, 6 diodes and 4 capacitors. It is also relatively simple to control and can achieve good efficiency and power factor.

In addition, the configuration of the NPC makes it so that the semiconductor switches only need to support the stress of half of the DC link voltage, meaning that it is possible to use devices rated for smaller voltages which can achieve higher frequencies. The NPC converter also produces three phase-to-ground or five line-to-line output voltage levels, making its output naturally more sinusoidal that the full-bridge. These features combine to result in higher power density and a reasonable current THD value while using smaller filtering inductances (Yilmaz & Krein, 2013; Rivera, Wu, Kouro, Yaramasu & Wang, 2015).

#### 1.3 Multilevel Converters and Their Advantages

Many of the limitations that exist in the conventional AC-DC converters can be remedied with multilevel converters (MLC). These advantages are important when considering that battery chargers must satisfy grid interconnection standards such as the IEEE 1547 (Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces), which requires the current THD to be less than 5% at the point of interconnection (IEEE, 2018). In fact, these converters, when coupled with appropriate modulation techniques and control methods, can generate a high number of output voltage levels, which results in a staircase shaped voltage waveform that is much closer to a sinusoidal wave than a two or three-level converter (Rodriguez, Jih-Sheng & Fang Zheng, 2002; Akagi, 2017). This comparison is further illustrated in Fig. 1.3 with examples of a 3-level waveform and a 7-level waveform.

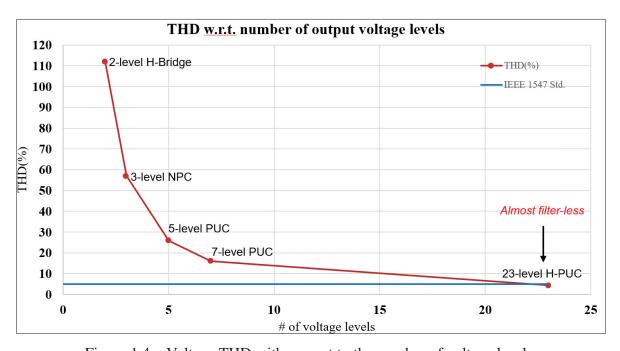

In fact, the improvement of MLCs in terms of THD are well illustrated in the graph in Fig. 1.4. In the plot, it becomes clear that by increasing the number of output voltage levels, the value of the voltage THD significantly decreases. Moreover, once a high enough number of voltage levels is reached, such as the 23-level seen in the graph, an almost filter-less implementation becomes possible since the THD obtained there is already less than the maximum 5% mandated by the IEEE 1547 standard.

Figure 1.3 Waveform comparison of a perfect sine wave with (a) a three-level voltage and (b) a 7-level voltage

Figure 1.4 Voltage THD with respect to the number of voltage levels

Hence, MLCs can help in greatly reducing the harmonic content of the AC current and voltage, as well as decreasing the dv/dt and electromagnetic interference. Ultimately, MLCs generate nearly sinusoidal voltages with lower THD, which considerably reduces the filtering requirements on the input AC current and more easily respect the interconnection standards (Rodriguez *et al.*, 2009; Abu-Rub, Holtz, Rodriguez & Baoming, 2010; Kouro *et al.*, 2010). Therefore, a review of three major types of MLCs is done in this section.

#### 1.3.1 The Cascaded H-bridge Converter

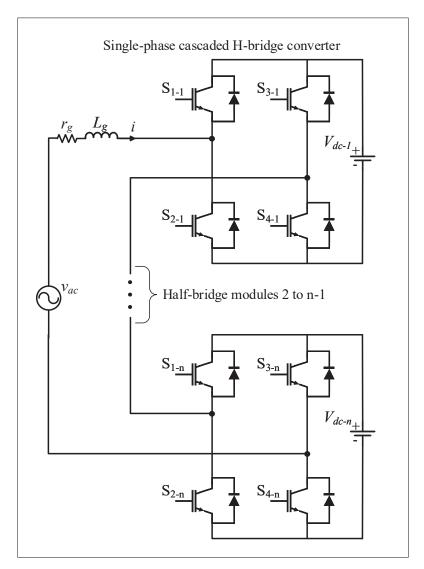

The first type of MLC that is being studied in this thesis is the cascaded H-bridge (CHB). As its name suggests, this converter is composed of a cascade of multiple half-bridge converters. Indeed, the cascading of multiple half-bridge modules has the effect of augmenting the total number of output voltage levels produced by the CHB converter (Malinowski, Gopakumar, Rodriguez & Pérez, 2010; Zhang & Gao, 2019). An example of a single-phase CHB converter is displayed in Fig. 1.5.

The circuit diagram reveals the modularity of the CHB topology. In fact, any number of half-bridge modules can be added as illustrated by the ellipses between the connection of modules 1 and n. Naturally, the number of modules n will determine the number of output voltage levels  $N_L$  as defined by:

$$N_L = 2n + 1. (1.1)$$

Therefore, if we take for example the case with two half-bridge modules, then it would produce 5 phase-to-ground voltage levels and this would become 9 line-to-line voltage levels in a three-phase configuration. For the latter case, the three-phase circuit would contain a total of 24 semiconductor switches, which is considerably more than either the three-phase full bridge or NPC converters and hence increases the overall cost. Another drawback is that each of the half-bridge modules requires its own DC voltage source. This configuration is not ideal in the context of a battery charger for which it is more desirable to have a single DC link through which all of the converter's power is transferred. For the CHB, this means that each of the DC voltage links could supply power to separate loads but only at a fraction of the rated converter power. For a high power battery charger, the objective is to supply as much power as the converter can support to a single battery load. In that case, there would have to be an additional conversion stage that would consolidate all the DC sources into a single DC link, and this would further increase the cost and complexity of the device.

Figure 1.5 Circuit diagram of a single-phase cascaded H-bridge converter

In conclusion, the CHB converter offers the same advantages as the full-bridge converter: easy control, good efficiency and near unity power factor. Additionally, it also benefits from the high number of voltage levels, which considerably reduce the THD of the input AC current and voltage (Villanueva, Correa, Rodriguez & Pacas, 2009). However, the high number of semiconductor switches and the need for multiple DC sources keep the CHB topology from being the ideal choice for a battery charger.

#### 1.3.2 The Active-neutral-point-clamped Multilevel Converter

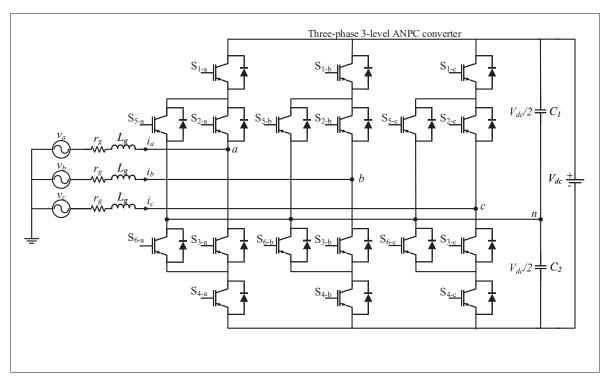

The next type of multilevel converter topology is the active-neutral-point-clamped (ANPC) converter. There are multiple variations of this topology, but the basic circuit is essentially the same as the NPC converter, except that the passive diodes are replaced with active semiconductor switches (Rodriguez *et al.*, 2010). The corresponding circuit diagram is reproduced in Fig. 1.6 for the three-level ANPC (3L-ANPC) converter.

Figure 1.6 Circuit diagram of the three-phase 3L-ANPC converter

The main advantage of the ANPC over the NPC is that the active control of the switches allows to mitigate the unequal loss distribution caused by the diodes in the NPC (Rodriguez *et al.*, 2010). However, this implementation of the ANPC does not increase the number of output voltage levels when compared to the NPC. Hence, more advanced, modular implementations of the ANPC have been developed that increase the number of voltage levels (Abarzadeh, Kojabadi & Chang,

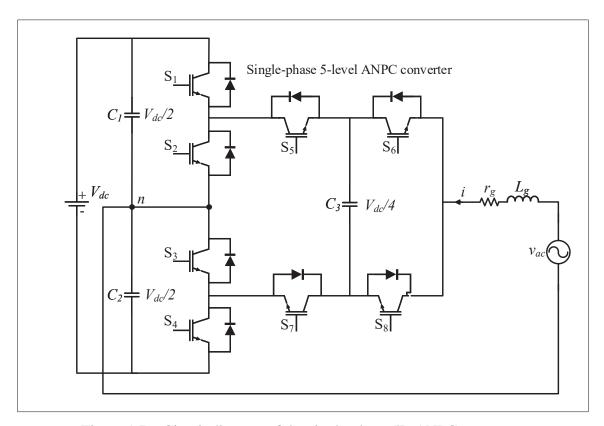

2016). An example of these, the five-level ANPC (5L-ANPC), in single-phase form is shown in Fig. 1.7.

Figure 1.7 Circuit diagram of the single-phase 5L-ANPC converter

The diagram demonstrates that by adding a cell to the converter like the one shown in the diagram, it is possible to increase the number of output voltage levels by two. The added cell results in two additional switches and one capacitor per phase when compared to the 3L-ANPC. By regulating the voltage of the added capacitor to 1/4 of the DC link voltage and by employing the appropriate switching patterns, the five voltage levels are achieved. Besides, this approach is also modular, which means that by adding more cells, it is possible to further multiply the number of output voltage levels (Dargahi *et al.*, 2019; Li, Bhattacharya & Huang, 2011).

As such, for the three-phase 5L-ANPC, the converter is composed of 24 active power switches, which is equal to the 5-level CHB described previously. However, it should be noted that

the 5L-ANPC also adds a total of 9 capacitors when compared to the CHB topology. These capacitors increase the cost and the control complexity as they need to be actively regulated at specific values in order to achieve the 5 voltage levels. Despite these limitations, the ANPC might still be more attractive than the CHB for a battery charger since the former requires only a single DC voltage source. Furthermore, like for the NPC, the semiconductor devices do not need to be rated for the full values of the DC link voltage. In fact, for one phase of the 5L-ANPC, four of the switches are rated for half of the DC link voltage, and the other four are rated for a quarter of that, thus giving this converter a considerably higher power density than the CHB topology.

#### 1.3.3 The Packed U-cell Family of Multilevel Converters

A newer family of multilevel converters is one called the packed U-Cell (PUC) family. They are capable producing a high number of voltage levels while using fewer active components than either the CHB or ANPC topologies (Ounejjar, Al-Haddad & Gregoire, 2011). A circuit diagram of the single-phase five-level PUC (PUC5) is given in Fig. 1.8.

The circuit is composed of 6 semiconductor switches, one DC voltage source and one capacitor. These numbers are of course multiplied by three when considering the three-phase implementation of this converter. It is through proper regulation of the capacitor voltage at one half of the DC source's value that the five voltage levels are achieved. Moreover, it has also been shown that the same topology can generate seven voltage levels when the capacitor is instead regulated at a third of the DC source voltage and an appropriate modulation method is used (Ounejjar, Al-Haddad & Dessaint, 2012). Also, like for the ANPC topology, the number of voltage levels of the PUC can be augmented even more by adding cells composed of one capacitor and two switches. Indeed, there exist implementations of the PUC converter that achieve 9 voltage levels (Abdelbasset, Refaat & Trabelsi, 2019) as well many other PUC derivatives that can generate even higher numbers of voltage levels (Sharifzadeh & Al-Haddad, 2019; Arazm & Al-Haddad, 2020).

Figure 1.8 Circuit diagram of the single-phase PUC5 converter

Once again, if the three-phase 5-level PUC5 is considered, the circuit would contain a total of 18 semiconductor switches, 3 capacitors and 3 voltage sources. As it was discussed previously with the CHB converter, the multiple DC sources in the three-phase PUC are not desirable for battery charger applications. However, it is important to note that the PUC5 still requires six fewer active switches than both the CHB and ANPC variants for the same number of voltage levels. Furthermore, it also requires 6 fewer capacitors than the corresponding ANPC topology, making the PUC the option with the best number of voltage levels to component number ratio. Consequently, the PUC family of multilevel converters is determined to be one of the more promising options for designing a high power density battery charger.

#### 1.4 Real-time Simulation and Equivalent Converter Models

This thesis aims to study bidirectional battery chargers based on multilevel converter topologies that are large and complex. Such systems are not always easily implemented as hardware prototypes and therefore, simulation is often employed when trying to design and validate these systems. However, normal or offline simulation is not always sufficient to properly validate complex electrical systems like those that contain power electronic converters.

#### 1.4.1 The Importance of Real-time Simulation

Indeed, it is often important to be able to test power converters with real hardware controllers. This kind of setup is known as hardware-in-the-loop (HIL) simulation, where a real hardware controller is physically connected to a simulator that is emulating the electrical system under test (Javadi, Abarzadeh, Grégoire & Al-Haddad, 2019). Because the simulated system is connected to a real device, the simulation needs to be performed in real-time, hence the importance of real-time simulation (RTS). Indeed, RTS makes use of high performance simulators, such as the OP4510 from Opal-RT, in order to perfectly match every simulation second with every real-time second (Yamane *et al.*, 2019; Bouzid, Sicard, Paquin & Yamane, 2016). In other words, for a given fixed time step, every necessary computation of the simulated model needs to be completed within that time step. This way, the hardware controller and the simulated system can communicate properly and an HIL test can be performed. A visual representation of the differences between offline simulation that is slower than real-time and true real-time simulation is depicted in Fig. 1.9.

As can be seen in the diagram, a real-time simulation can complete all necessary operations f(t) within each fixed time step. These computations include the calculations of the simulated system but also other overhead operations such as operating system calls and interrupt handling (Parizad, Baghaee, Iranian, Gharehpetian & Guerrero, 2020; Lauss, Faruque, Schoder, Dufour, Viehweider & Langston, 2016). In comparison, offline simulations will not always complete all

Figure 1.9 Diagram of the computational differences between offline and real-time simulation

calculations within a fixed time step, especially since the time step needs to be quite small in order for the simulated system to yield accurate and precise results.

## 1.4.2 Performance Considerations and Equivalent Converter Models for Real-time Simulation

However, there are some performance limitations with RTS that exist when dealing with both small computation time steps and systems composed of large numbers of semiconductor switches, such as the MLCs that are studied in this thesis. Additionally, those switches are typically operated at high frequencies, which further increases the already considerable computational burden in simulating MLCs. This burden is a result of the different circuit solving methods that are employed by discrete time step simulation software such as Matlab/Simulink. These

solving methods essentially store and solve large sets of matrices at every computation time step depending on the number of possible switching states of the converters under test. Furthermore, the sizes of these matrices increase either when the number of switches increases, when the switching frequency is increased or when the fixed time step is decreased. All of these factors contribute to adding more computations at every time step, thus making the real-time simulation of MLCs at reasonably low time steps difficult (Dommel, 1969; Dufour, Mahseredjian, Bélanger & Naredo, 2010). Therefore, researchers have proposed some interesting workarounds that would allow to overcome these limitations and achieve true real-time simulation of MLCs.

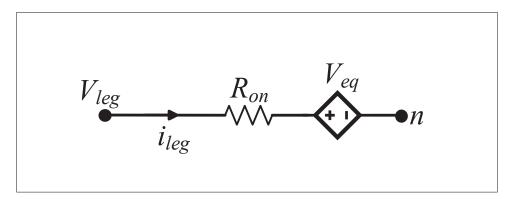

One of the potential solutions to these limitations is to replace the converters that are usually modelled with non-linear, diode-based semiconductor models, with equivalent models based on controlled voltage sources and switching functions. Indeed, some of these equivalent models that use controlled voltage sources and switching functions are already detailed in the literature (Zhang & Li, 2019; Li & Zhang, 2019) for topologies that are based on the half-bridge converter. Such equivalent models that do not contain detailed switches are advantageous since their logic is more similar to a simple look-up table and thus, it is no longer required to recalculate the matrices of every possible switching state at every time step. As a result, it becomes possible to decrease the time step to acceptable levels while maintaining good accuracy. Hence, true real-time simulation of a MLC could be achieved by developing an appropriate equivalent model of the MLC that is being studied.

#### 1.5 Conclusion

Fast electric vehicle battery chargers are becoming an increasingly popular commodity. As the demand grows and the number of charging stations increases with it, maintaining acceptable power quality on the grid will become a greater challenge, especially for bidirectional chargers. The more popular AC-DC converters used in the present for fast DC battery chargers are attractive due to their simplicity in both their configurations and control. However, they typically only generate up to three output voltage levels and thus require considerably large and costly filtering inductances to smooth out the input AC current and maintain acceptable THD levels. In

comparison, multilevel converters have more complex topologies, but they offer higher power density and improved power quality thanks to their high number of output voltage levels. Finally, the complexity of MLCs highlights the usefulness of real-time simulation when it comes to studying and validating large systems that would be composed of multiple MLC-based battery chargers. Hence, by developing robust and accurate equivalent models of MLCs, it becomes possible to perform large system studies of bidirectional battery chargers by using real-time simulators.

#### **CHAPTER 2**

# 23-LEVEL SINGLE DC SOURCE HYBRID PUC (H-PUC) CONVERTER TOPOLOGY WITH REDUCED NUMBER OF COMPONENTS: REAL-TIME IMPLEMENTATION WITH MODEL PREDICTIVE CONTROL

Kevin-Rafael Sorto-Ventura<sup>a</sup>, Mostafa Abarzadeh<sup>b</sup>, Kamal Al-Haddad<sup>a</sup>, Louis A. Dessaint<sup>a</sup>

a Department of Electrical Engineering, École de Technologie Supérieure,

1100 Notre-Dame St W, Montréal, Québec, Canada H3C 1K3

b Department of Electrical and Computer Engineering, Marquette University,

1250 W Wisconsin Ave, Milwaukee, WI 53233, United States

This chapter has been published in IEEE Open Journal of the Industrial Electronics Society, vol. 1, pp. 127-137, 2020.

#### Abstract

In this paper, a new configuration of single DC source hybrid packed U-cell (H-PUC) converter with reduced number of components is proposed. The proposed H-PUC only requires one dc source, twelve power switches, and three capacitors to provide 23-level output voltage. It is comprised of two high voltage low frequency (LF) and low voltage high frequency (HF) sub-modules which leads to less power losses and higher efficiency of the proposed H-PUC converter. Moreover, a finite control set model predictive control (FCS-MPC) method is proposed to generate 23-level staircase output voltage with low THD and to regulate voltages of three capacitors to their desired values simultaneously. A real-time model of the proposed 23-level H-PUC converter and its suggested FCS-MPC are developed and implemented in OPAL-RT OP4510 platform to evaluate and validate the feasibility of the proposed H-PUC in grid-connected operation mode. The provided real-time implementation results verify and demonstrate the performance and viability of the proposed 23-level H-PUC and its associated FCS-MPC to provide low THD 23-level output voltage and all three capacitors voltages balancing.

#### 2.1 Introduction

The global adoption rate of renewable energy sources has been increasing significantly in the past years and shows no sign of slowing down. More specifically, solar energy is becoming increasingly popular in many parts of the world. As such, proper power electronic devices need to be developed in order to meet the appropriate grid power quality requirements (Carrasco *et al.*, 2006). Indeed, the main requirement for a photovoltaic system is a suitable voltage source inverter (VSI), which converts the DC voltage generated by the photovoltaic arrays to AC voltage that can be injected to the grid (Akbari, Poloei & Bakhshai, 2019).

Furthermore, the injected current to the grid must meet requirements compelled by stringent standards in terms of harmonic content reduction, identified as total harmonic distortion (THD). One method of reducing this harmonic pollution on the grid is to use passive, active or hybrid filters as interfacing components connected between the inverter circuit and the grid at the point of common coupling (PCC) (Javadi *et al.*, 2019).

Nonetheless, it is possible to considerably reduce the harmonic content of the injected power without the use of additional filters by using multilevel types of inverters. The latter offer a better solution than conventional inverters as they are capable of providing low THD staircase multilevel output voltage, low electromagnetic interference (EMI), low dv/dt (responsible for unintentional semiconductor turn-on), and low switching frequency. This results in overall cleaner waveforms with less harmonic distortion, which in turn reduces or even eliminates the requirement for bulky passive or hybrid filters (Rodriguez *et al.*, 2002, 2009; Abu-Rub *et al.*, 2010; Kouro *et al.*, 2010; Akagi, 2017). Some popular multilevel inverter topologies include the cascaded H-bridge (CHB), the neutral-point-clamped (NPC) and the active neutral-point-clamped (ANPC) inverters. However, these topologies are only feasible to provide lower number of output voltage levels and the number of required DC sources, power switches, diodes, and capacitors are significantly increased at higher number of output voltage levels (Zhang & Gao, 2019; Rodriguez *et al.*, 2010; Abarzadeh *et al.*, 2016; Dargahi *et al.*, 2019; Li *et al.*, 2011; Abarzadeh & Kojabadi, 2016).

A new breed of multilevel inverters, known as the packed U-Cell, is able to overcome the limitations previously mentioned. These inverters can generate a high number of voltage levels while using a smaller number of active switches and passive components (Arazm & Al-Haddad, 2020; Sharifzadeh & Al-Haddad, 2019; Babadi, Salari, Mojibian & Bina, 2018; Ounejjar *et al.*, 2011). In fact, some specific applications of the PUC converters have shown the ability to generate 7, 9 and even 15 voltage levels with a single DC source, isolated or generated by photovoltaic arrays (Sahli, Krim, Laib & Talbi, 2019; Makhamreh, Trabelsi, Kükrer & Abu-Rub, 2020; Abdelbasset *et al.*, 2019). These higher number of output voltage levels are attained by using more complex control methods that usually employ some form of sine pulse width modulation (SPWM) or space vector modulation (SVM) (Biricik & Komurcugil, 2018; Grigoletto, Schuetz, Junior, Carnielutti & Pinheiro, 2018).

Recently, hybrid multilevel inverters formed by cascade connection of two or more sub-modules are introduced in the literature. Applying asymmetrical ratio of isolated DC links to the sub-modules results in higher number of output voltage levels by employing reduced number of components in hybrid multilevel inverters (Lezana & Aceiton, 2011; Malinowski *et al.*, 2010). However, hybrid multilevel inverters require two or more isolated DC sources or high frequency links to provide multiple isolated DC links. Hence, the complexity and cost of hybrid multilevel inverters are increased (Xia & Li, 2013).

To overcome the above mentioned frailties, this paper proposes the single DC source hybrid PUC (H-PUC) inverter and its suggested FCS-MPC to provide 23-level output voltage with less number of components. The 23-level output voltage with low THD and voltage balancing of all capacitors are obtained by employing the proposed FCS-MPC in the proposed H-PUC. Hence, the proposed H-PUC only needs one isolated DC source and the high frequency link is eliminated from this configuration. This paper is organized as follows. The general topology and its mathematical model are developed and presented in Section 2.2. Then, in Section 2.3, the model predictive controller is designed for 23 output voltage levels and tested in grid-connected mode. Subsequently, in Section 2.4, the real-time equivalent model of the proposed converter is

discussed. Finally, the designed converter-controller is simulated in real-time and validated in Section 2.5.

# 2.2 Hybrid PUC (H-PUC) Inverter Topology

# 2.2.1 Presentation of the Circuit Topology

The proposed H-PUC configuration is comprised of two sub-modules that are based on the PUC topology. This PUC converter was first introduced in (Ounejjar *et al.*, 2011). It is composed of 6 active switches, one DC voltage source and one DC capacitor. This topology can be used in single-phase system configuration, operating in either inverter or rectifier modes. In single-phase inverter mode, the basic form of the converter, called PUC5, can generate five voltage output levels and has the ability to self-balance the DC capacitor voltage to one half of the main DC source without the use of voltage sensors thanks to appropriate modulation techniques (Abarzadeh, Vahedi & Al-Haddad, 2019). In addition, the same converter topology is capable of generating 7 voltage output levels (PUC7) when paired to an appropriate control technique that regulates the DC capacitor voltage to one third of the main DC source (Ounejjar *et al.*, 2012). The proposed single DC source H-PUC inverter is formed by cascade connection of two PUC5 sub-modules with quinary ratio.

In (Meraj *et al.*, 2019) and (Lodi *et al.*, 2020), multilevel converter composed of two cascaded PUC7 converters have been introduced, but they require two or more DC sources to achieve a high number of voltage output levels. Similarly in (Abarzadeh & Al-Haddad, 2019), the Q-HNPC is proposed as a modular approach to cascaded multilevel inverters based on HNPC and PUC5 converters has been presented, but again multiple DC sources are necessary for proper operation. In this paper, the proposed topology, shown in Fig. 2.1, is based on a cascade connection of two PUC5 inverters where the DC source of the second converter is replaced by a voltage regulated DC capacitor, which reduces the burden of using multiple isolated bidirectional DC sources. Additionally, as shown in Fig. 2.1, only 4 of the 12 switches operate at high switching frequency, whereas 6 switches operate at lower frequencies, and the first 2 complementary switches operate

at fundamental frequency. This results in overall higher efficiency since higher voltages like  $V_{dc}$  are switched at lower frequencies.

Figure 2.1 The Proposed Hybrid PUC (H-PUC) Inverter Topology with Single DC Source

The use of a model predictive controller requires prior knowledge of all possible switching states of the converter (Kouro, Cortes, Vargas, Ammann & Rodriguez, 2009; Metri, Vahedi, Kanaan & Al-Haddad, 2016; Trabelsi, Bayhan, Ghazi, Abu-Rub & Ben-Brahim, 2016). Since

the proposed converter is composed of 6 pairs of complementary switches ( $S_1$  to  $S_6$  and  $S_{1c}$  to  $S_{6c}$ ), there are in total  $2^6 = 64$  possible switching states for this topology. However, individually each of the two PUC5 converters has  $2^3 = 8$  possible switching states. Thus, for the sake of conciseness, only the states of each individual PUC5s (1st PUC and 2nd PUC) are shown in Table 2.1.

Table 2.1 Possible Switching States and Capacitor Charging States of 1st and 2nd PUC

| 1st PUC States   |                  |                       |                       |                            |                   |                                                                                                            |  |  |

|------------------|------------------|-----------------------|-----------------------|----------------------------|-------------------|------------------------------------------------------------------------------------------------------------|--|--|

| State            | S1               | S2                    | <b>S3</b>             | C1                         | $V_{1stPUC}$      |                                                                                                            |  |  |

| 1                | 0                | 0                     | 0                     | _                          | 0                 |                                                                                                            |  |  |

| 2                | 0                | 0                     | 1                     | $\downarrow$               | $-V_{c1}$         |                                                                                                            |  |  |

| 3                | 0                | 1                     | 0                     | 1                          | V                 | $c_{c1} - V_{dc}$                                                                                          |  |  |

| 4                | 0                | 1                     | 1                     | _                          |                   | $-V_{dc}$                                                                                                  |  |  |

| 5                | 1                | 0                     | 0                     | _                          |                   | $V_{dc}$                                                                                                   |  |  |

| 6                | 1                | 0                     | 1                     | 1                          | $V_{dc} - V_{c1}$ |                                                                                                            |  |  |

| 7                | 1                | 1                     | 0                     | $\downarrow$               | $V_{c1}$          |                                                                                                            |  |  |

| 8                | 1                | 1                     | 1                     | _                          | 0                 |                                                                                                            |  |  |

|                  |                  | 2nc                   | l PU                  | C Sta                      | tes               |                                                                                                            |  |  |

| State            | <b>S4</b>        | <b>S5</b>             | <b>S6</b>             | <b>C2</b>                  | $C3 V_{2ndPUC}$   |                                                                                                            |  |  |

| 1                | D <b>T</b>       | 00                    | 30                    |                            | CJ                | V 2ndPUC                                                                                                   |  |  |

| 1                | 0                | 0                     | 0                     | -                          | -                 | 0 V 2ndPUC                                                                                                 |  |  |

| 1 2              |                  |                       |                       | -<br>-                     | -<br>↓            | $0$ $-V_{c3}$                                                                                              |  |  |

|                  | 0                | 0                     | 0                     | -<br>-<br>-                | _                 | $ \begin{array}{c c} 0 \\ -V_{c3} \\ \hline V_{c3} - V_{c2} \end{array} $                                  |  |  |

| 2                | 0                | 0                     | 0                     | -<br>-<br>-<br>-           | _                 | 0                                                                                                          |  |  |

| 2 3              | 0 0 0            | 0 0 1                 | 0<br>1<br>0           | -<br>-<br>-<br>↓<br>↑      | _                 | $ \begin{array}{c c} 0 \\ -V_{c3} \\ \hline V_{c3} - V_{c2} \end{array} $                                  |  |  |

| 2<br>3<br>4      | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1      | 0<br>1<br>0<br>1      | -<br>-<br>-<br>-<br>-<br>- | _                 | $ \begin{array}{c c} 0 \\ -V_{c3} \\ V_{c3} - V_{c2} \\ -V_{c2} \\ V_{c2} \\ V_{c2} - V_{c3} \end{array} $ |  |  |

| 2<br>3<br>4<br>5 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0 | -<br>-<br>-<br>↑<br>↑<br>- | _<br>↓<br>↑<br>_  | $0$ $-V_{c3}$ $V_{c3} - V_{c2}$ $-V_{c2}$ $V_{c2}$                                                         |  |  |

The overall 64 switching states can then be obtained by listing every combination of the two individual converters' states. The following definitions should be observed:

$$S_{i} = \bar{S}_{ic} = \begin{cases} 1 & \text{if } S_{i} \text{ is ON} \\ 0 & \text{if } S_{i} \text{ is OFF} \end{cases}$$

$i = 1, 2, 3, 4, 5, 6$  (2.1)

where  $S_i$  ans  $S_{ic}$  are pairs of complementary switches that are never ON simultaneously in order to avoid short-circuiting the DC source.

# 2.2.2 Determination of Capacitor Values

The selection of capacitor values is influenced by their peak current, their charging and discharging period, and their voltage ripple as expressed in the following equation:

$$C_i = \frac{I_{peak} \times \Delta t_{ci}}{V_{ripple}}, \qquad i = 1, 2, 3$$

(2.2)

where  $I_{peak}$  is load current peak value,  $V_{ripple}$  is desired capacitor voltage ripple and  $\Delta t_{ci}$  is the duration of charge and discharge of i-th capacitor. The values of  $I_{peak}$  and  $V_{ripple}$  are imposed by the user, but they still depend on  $\Delta t_{ci}$ . Thus, in Fig. 2.2 the charging and discharging currents of all three capacitors  $C_1$ ,  $C_2$  and  $C_3$  are depicted over two fundamental cycles.

It is observed that the charging and discharging periods of  $C_1$  and  $C_3$  are balanced with about sampling frequency ( $f_s$ ), whereas the charging and discharging period of  $C_2$  is balanced with about 5 times of fundamental frequency ( $5 \times f_0$ ). In other words, the currents in  $C_1$  and  $C_3$  complete their charging and discharging cycles (balancing) a lot faster than  $C_2$ . As such, the values of  $\Delta t_c$  of  $C_1$  and  $C_3$  are much smaller than that of  $C_2$  and consequently, considering (2.2), the selected values of  $C_1$  and  $C_3$  can be considerably smaller than the value of  $C_2$ . With this knowledge, and by considering a peak current of 10A as seen in Fig. 2.2 and voltage ripple of 5V, one can find approximate ranges for the optimal capacitor values. Since the MPC method does not use a fixed switching frequency, the precise value of  $\Delta t_{ci}$  is unknown. So, based on the previous discussion and some iterative tests, some capacitor values are selected in an effort minimize their sizes. More specifically, the capacitor values utilized in this work are  $C_1 = 500\mu F$ ,  $C_2 = 1500\mu F$  and  $C_3 = 500\mu F$ .

Figure 2.2 Charging and discharging currents of all three capacitors of the H-PUC converter during two fundamental cycles

# 2.2.3 Comparison of the H-PUC with Other MLI topologies

The proposed 23-level H-PUC converter is compared to other MLI converters in Table 2.2. The table lists the number of DC sources, capacitors, diodes, high frequency (HF) switches and low frequency (LF) switches for the CHB, Q-HNPC, PUC, ANPC and H-ANPC converters with similar numbers of voltage output levels. As such, Table 2.2 demonstrates that the proposed H-PUC is able to considerably reduce the number of HF and LF switches when compared to other topologies, even decreasing the number of LF switches by two with respect to the 25-level H-ANPC (Abarzadeh & Kojabadi, 2016) and by four with respect to the 21-level Q-HNPC

Table 2.2 Comparison of the Proposed 23L H-PUC Converter with other Presented Converters in the Literature in Terms of the Number of Components

| MLI       | HF       | LF       | Diodes | Caps. | DC      |

|-----------|----------|----------|--------|-------|---------|

| Type      | Switches | Switches |        |       | Sources |

| 23L-CHB   | 44       | -        | -      | -     | 11      |

| 21L       | 4        | 10       | 4      | 3     | 2       |

| Q-HNPC    |          |          |        |       |         |

| 23L-PUC   | 22       | 2        | -      | 10    | 1       |

| 23L-ANPC  | 22       | 4        | -      | 12    | 1       |

| 25L       | 8        | 6        | -      | 3     | 3       |

| H-ANPC    |          |          |        |       |         |

| Proposed  | 8        | 4        | _      | 3     | 1       |

| 23L-H-PUC |          |          |        |       |         |

(Abarzadeh & Al-Haddad, 2019). In addition, the H-PUC requires only one DC source, three capacitors and no clamped diodes. Hence, the H-PUC inverter is capable of attaining a high number of output voltage levels with a reduced number of components.

# 2.3 The Proposed Finite Control Set Model Predictive Controller (FCS-MPC)

#### **2.3.1** Mathematical Modelling of the Inverter

It is necessary to define a mathematical model of the converter in order to use a model predictive controller effectively. This is because the basis of MPC is the prediction of the future state of the converter model (Metri *et al.*, 2016). Hence, a simple and discretized converter model based on the Forward Euler approximation is developed and presented in this section.

The first equation that can be defined is the overall inverter AC output voltage in the time domain as:

$$V_{inv}(t) = V_{1stPUC}(t) + V_{2ndPUC}(t). (2.3)$$

Because the objective of the model predictive controller is to select an appropriate switching state, it is more useful to express  $V_{inv}$  as a function of the individual switches' states ( $S_1$  to  $S_6$ ).

This approach was used in (Metri *et al.*, 2016) and is reproduced here. Indeed, by examining the relationships between the states of the switches  $S_i$  and the converter output voltage, which is defined by the sum of  $V_{1stPUC}$  and  $V_{2ndPUC}$ , two switching functions can then be defined:

$$V_{1stPUC}(t) = (S_1 - S_2)V_{dc}(t) + (S_2 - S_3)V_{c1}(t)$$

(2.4)

$$V_{2ndPUC}(t) = (S_4 - S_5)V_{c2}(t) + (S_5 - S_6)V_{c3}(t).$$

(2.5)

These equations can be further simplified by introducing four new switching variables constructed by combining each two consecutive switching functions, namely:

$$S_a = S_1 - S_2 (2.6)$$

$$S_b = S_2 - S_3 \tag{2.7}$$

$$S_c = S_4 - S_5 \tag{2.8}$$

$$S_d = S_5 - S_6. (2.9)$$

Therefore, new simplified switching states are obtained based on the newly introduced intermediate switching states, as can be shown in Table 2.3. These new switching variables are used in the MPC to generate the appropriate output voltage level of the converter.

With the new variables defined in (2.6) to (2.9), it is then possible to combine equations (2.3) to (2.9) to write the following discrete expression

$$V_{inv}(k) = S_a V_{dc}(k) + S_b V_{c1}(k) + S_c V_{c2}(k) + S_d V_{c3}(k)$$

(2.10)

for the inverter output voltage, where k = 0, 1, 2, 3... is the discrete index chosen to denote the value of a variable at a given computation time step. One can observe that the output voltage is a combination of the switching variables that multiply each of the  $V_{dc}$  and the three capacitor voltages  $V_{c1}$ ,  $V_{c2}$  and  $V_{c3}$ . Subsequently, the equations of the  $C_1$ ,  $C_2$ , and  $C_3$  capacitors currents

Table 2.3 Simplified Switching States and Capacitor Charging States of 1st and 2nd PUC for MPC

| 1st PUC States |    |      |              |                              |                   |  |  |

|----------------|----|------|--------------|------------------------------|-------------------|--|--|

| State          | Sa | Sb   | C1           | $V_{1stPUC}$                 |                   |  |  |

| 1              | 0  | 0    | _            | 0                            |                   |  |  |

| 2              | 0  | -1   | $\downarrow$ |                              | $-V_{c1}$         |  |  |

| 3              | -1 | 1    | 1            | V                            | $V_{c1} - V_{dc}$ |  |  |

| 4              | -1 | 0    | _            |                              | $-V_{dc}$         |  |  |

| 5              | 1  | 0    | _            |                              | $V_{dc}$          |  |  |

| 6              | 1  | -1   | 1            | $V_{dc} - V_{c1}$            |                   |  |  |

| 7              | 0  | 1    | <b>1</b>     | $V_{c1}$                     |                   |  |  |

| 8              | 0  | 0    | _            | 0                            |                   |  |  |

|                | 2  | nd P | UC S         | tates                        |                   |  |  |

| State          | Sc | Sd   | <b>C2</b>    | C3                           | $V_{2ndPUC}$      |  |  |

| 1              | 0  | 0    | _            | _                            | 0                 |  |  |

| 2              | 0  | -1   | _            | $\downarrow$ $-V_{c3}$       |                   |  |  |

| 3              | -1 | 1    | $\downarrow$ | $\uparrow$ $V_{c3} - V_{c2}$ |                   |  |  |

| 4              | -1 | 0    | 1            | $ -V_{c2}$                   |                   |  |  |

| 5              | 1  | 0    | 1            | $ V_{c2}$                    |                   |  |  |

| 6              | 1  | -1   | <b>1</b>     | $\uparrow$ $V_{c2} - V_{c3}$ |                   |  |  |

| 7              | 0  | 1    | _            | $\downarrow$ $V_{c3}$        |                   |  |  |

| 8              | 0  | 0    | _            | _                            | 0                 |  |  |

as functions of the new switching variables along with the grid current  $i_s(t)$  can be written as

$$i_1(t) = C_1 \frac{dV_{c1}(t)}{dt} = -S_b i_s(t)$$

(2.11)

$$i_2(t) = C_2 \frac{dV_{c2}(t)}{dt} = -S_c i_s(t)$$

(2.12)

$$i_3(t) = C_3 \frac{dV_{c3}(t)}{dt} = -S_d i_s(t).$$

(2.13)