## Measurement techniques to characterize SiC, GaN, and Si power MOSFETs for transportation applications

by

#### Yan Bérubé

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT OF A MASTER'S DEGREE WITH THESIS IN ELECTRICAL ENGINEERING M.A.Sc.

MONTREAL, SEPTEMBER 15, 2021

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

#### THIS THESIS HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Handy Fortin Blanchette, Thesis Supervisor Department of Electrical Engineering, École de technologie supérieure

Mr. Amin Ghazanfari, Thesis Co-supervisor Center of Excellence in Transportation Electrification and Energy Storage, Hydro-Québec

Mr. Vincent Duchaine, President of the Board of Examiners Department of Electrical Engineering, École de technologie supérieure

Mr. Kamal Al-Haddad, Member of the jury Department of Electrical Engineering, École de technologie supérieure

Mr. Sheldon Williamson, External Independent Examiner Department of Electrical Engineering, Ontario Tech university

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON "AUGUST 31, 2021"

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **FOREWORD**

This document presents the work that I carried out as part of my master's studies at École de technologie supérieure between May 2019 and April 2021. The main objective of this research work is to conduct a comparative study on emerging Wide Bandgap (WBG) MOSFETs technologies in energy conversion applications. Although the guideline has been retained, the multiple challenges of reproducing simulation results by experimentation led to paying particular attention to methods of extracting experimental data. Most of the time not enough attention is given to establishing an experimental data extraction methodology which lead to unexpected perturbations, false observations, and inaccurate conclusions.

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my thesis director, Professor Handy Fortin Blanchette from the Department of Electrical Engineering at École de technologie supérieure. It is the passion of Professor Fortin Blanchette that made me want to pursue graduate studies. His dedication, both personally and professionally, is a real source of inspiration for me. I would also like to thank my co-supervisor, Professor Amin Ghazanfari from Hydro-Québec's Center of Excellence in Transportation Electrification and Energy Storage (CETEES). Dr. Ghazanfari has always been altruistic, providing technical support as well as personal support. His dedication to science, to sharing knowledge, and his involvement in making energies cleaner are exemplary behaviors to adopt. I would like to thank them both for their support, advice and confidence in carrying out this project.

Thanks go to Mr. Christian Perreault, Head of Expertise and Systems at CETEES. Without his confidence and financial support to carry out this project, none of this would have been possible. The initiative of the Mitacs organization also deserves thanks and mention for supporting innovation by granting research partnerships, advice and funding.

Moreover, I would like to take a moment to thank friends, family and colleagues from Hydro-Québec and École de technologie supérieure. Your support, your encouragement, your passion and your friendship have allowed me to take one more step in the right direction every day. Finally, I must thank my girlfriend Émie for the great understanding and support given to this whole work.

## Simulation et expérimentation des caractéristiques des semi-conducteurs de puissance Si, SiC et GaN dans les applications de conversion de l'énergie

#### Yan Bérubé

#### **RÉSUMÉ**

Les semiconducteurs à large bande (WBG) ont le potentiel de franchir les barrières qui limitent l'adoption à grande échelle des véhicules électriques (VE). Les WBG améliorent la densité de puissance et permettent aux circuits électroniques de puissance (PE) d'atteindre des points de fonctionnement et une efficacité au-delà de ce que le Silicium (Si) standard peut offrir. Actuellement, les semiconducteurs WBG à base de Carbure de Silicium (SiC) et Nitrure de Gallium (GaN) sont les candidats les plus viables pour remplacer les semiconducteurs Si. Pour l'instant, la littérature apporte encore de la confusion lorsqu'il s'agit de choisir entre les SiCs et les GaNs pour tirer le meilleur parti des applications des convertisseurs d'énergie. Afin de faire pencher la balance face à ce débat, cette thèse présente une analyse comparative par simulation et expérimentation entre les MOSFETs Si, SiC et GaN dans les applications de conversion d'énergie.

Une revue des équations de simulation basées sur les paramètres intrinsèques du modèle mathématique équivalent du MOSFET expose les hypothèses, limites et possibilités d'améliorations du modèle de calcul. Ensuite, la simulation de multiples conditions expérimentales révèle des résultats de commutations favorables envers les SiCs tout en mettant en évidence les avantages marqués de cette technologie à haute température. Bien que les résultats de simulation soient prometteurs, la validation expérimentale reste nécessaire pour tirer des conclusions finales sur les observations. Dans cette optique, la conformité des hypothèses théoriques est satisfaite à des fins de comparaison entre les résultats de simulation et d'expérimentation. L'analyse des méthodologies d'extraction de données expérimentales met en évidence l'importance des perturbations des inductances parasites, capacités parasites, du couplage mutuel et des interférences électromagnétiques (EMI) sur le processus de commutation et de prise de mesures. De cela, une méthodologie d'extraction de tension et de courant est proposée pour minimiser les perturbations sur les mesures expérimentales et processus de commutation. Enfin, la comparaison relative des résultats expérimentaux montre les grandes tendances de chaque technologie par le biais de l'analyse statistique. Leur interprétation fait le pont avec les paramètres intrinsèques des MOSFETs.

**Mots-clés:** Wide Bandgap (WBG), semiconducteur de puissance, Carbure de silicium (SiC), Nitrure de gallium (GaN), électronique de puissance (PE), véhicules électriques (VE), modélisation, mesures expérimentales

## Measurement techniques to characterize SiC, GaN, and Si power MOSFETs for transportation applications

Yan Bérubé

#### **ABSTRACT**

Wide Bandgap (WBG) semiconductors have the potential to cross the barriers that limit the widespread adoption of power electronics (PE) circuits in various energy conversion applications. The WBG devices improve power density and allow PE circuits to reach operating points and efficiency beyond what standard Silicon (Si) can offer. Currently, Silicon Carbide (SiC) and Gallium Nitride (GaN) are the most viable WBG semiconductor candidates to replace Si-based devices. For now, the state-of-the-art technologies still bring confusion when it comes to choosing between SiCs and GaNs to get the most benefits of them for power converter applications. To tilt the balance in the face of this debate, this thesis presents a comprehensive comparative computation and experimental analysis among Si, SiC, and GaN MOSFETs in energy conversion applications.

A presentation of simulation equations based on intrinsic parameters of MOSFET's equivalent mathematical model highlights the assumptions, limitations, and opportunities for improvement of the computational model. Then, simulation of multiple experimental conditions reveals favorable switching results towards SiCs while highlighting the marked advantages of this technology at high temperature. Although the simulation results are promising, the experimental validation remains necessary to make the concluding remarks. Analysis of experimental data extraction methodologies highlights the perturbation from parasitic inductances, parasitic capacitances, mutual coupling, and electromagnetic interference (EMI) on the switching process and measurements. Based on the detailed assessment of parasitic perturbations, this work proposes a voltage and current extraction methodology to remarkably minimize disturbances on measurements and the switching process. Finally, interpretation of experimental results through statistical analysis of relative comparison presents major trends from each technology while providing an interpretation of observations based on intrinsic parameters.

**Keywords:** Wide Bandgap (WBG), power semiconductor, Silicon Carbide (SiC), Gallium Nitride (GaN), power electronic (PE), electric vehicles (EVs), modelization, experimental measurements

#### TABLE OF CONTENTS

|      |          |                                                  | Pag                | 56       |

|------|----------|--------------------------------------------------|--------------------|----------|

| INTR | ODUCT1   | ON                                               |                    | . ]      |

| CHA  | PTER 1   | RECENT ADVANCES IN WIDE BA                       |                    |          |

|      |          | AUTOMOTIVE INDUSTRY                              |                    | 3        |

| 1.1  | Overvi   | w                                                |                    | 4        |

|      | 1.1.1    | Introduction                                     |                    | 5        |

|      | 1.1.2    | Why WBGs?                                        |                    | 7        |

|      | 1.1.3    | Benefits of WBG semiconductors                   |                    |          |

|      | 1.1.4    | SiC as an Enabler of Transportation Ele          | ectrification1     | . 2      |

|      | 1.1.5    | Challenges of WBGs integration                   |                    | 5        |

| 1.2  | Advanc   | ements and Future prospects of WBG ser           | miconductors1      | 8        |

| 1.3  |          | ent of the Problem and Research Objective        |                    |          |

| 1.4  | Thesis   | Outline and Methodology                          | 2                  | :2       |

| CHA  | PTER 2   | UNDERSTANDING CHARACTERIS                        | TICS AND SWITCHING |          |

|      |          | PERFORMANCE OF MOSFETS                           |                    | 13       |

| 2.1  | MOSF     | ET Modeling Technique and Parasitic Cor          | mponents2          | 13       |

|      | 2.1.1    | Resistance, Parasitic JFET                       |                    |          |

|      | 2.1.2    | Internal Parasitic Capacitances                  |                    | 15       |

|      | 2.1.3    | Bipolar Junction Transistor and Body-D           |                    |          |

|      | 2.1.4    | An Introduction to the Temperature Effe          | ect2               | 29       |

| 2.2  | MOSF     | ET Transient Behavior                            |                    | 29       |

| 2.3  | Hypoth   | eses of MOSFET's Simulation Model                |                    | <u>ا</u> |

| 2.4  | MOSF     | ET's Simulation Modeling                         |                    | 5        |

|      | 2.4.1    | Mathematical and Simulation Modeling             | g's Nomenclature 3 | 37       |

|      | 2.4.2    | Turn-On Intervals                                |                    | 8        |

|      |          | 2.4.2.1 Turn-On 1 <sup>st</sup> Interval: The De | elay Time3         | 39       |

|      |          | 2.4.2.2 Turn-On 2 <sup>nd</sup> Interval: Main   | Transition Period4 | .5       |

|      |          | 2.4.2.3 Turn-On 3 <sup>rd</sup> Interval: Con    | ±                  |          |

|      |          |                                                  | 6                  |          |

|      | 2.4.2    |                                                  | Gate Charging6     |          |

|      | 2.4.3    | Turn-Off Intervals                               |                    |          |

|      |          |                                                  | elay Time6         |          |

|      |          |                                                  | oltage Rise6       |          |

|      |          |                                                  | urrent Fall6       |          |

| 2.5  | G 1      |                                                  | esonance           |          |

| 2.5  | Conclu   | sions and remarks                                |                    |          |

| CHA  | PTER 3   | SIMULATION RESULTS                               |                    |          |

| 3.1  | Criterio | n for Choosing MOSFETs and Final Cho             | ice 7              | 15       |

| 3.2  | Simulat  | ion Metho     | dology and Results                                   | 78  |

|------|----------|---------------|------------------------------------------------------|-----|

|      | 3.2.1    | Turn-On       | Switching Performances                               | 80  |

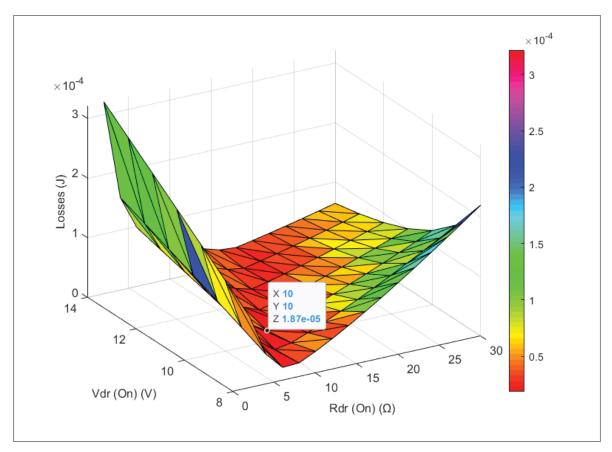

|      |          | 3.2.1.1       | Silicon (Si) MOSFET: Optimal Operating Point to      |     |

|      |          |               | Minimize Turn-On Losses                              | 80  |

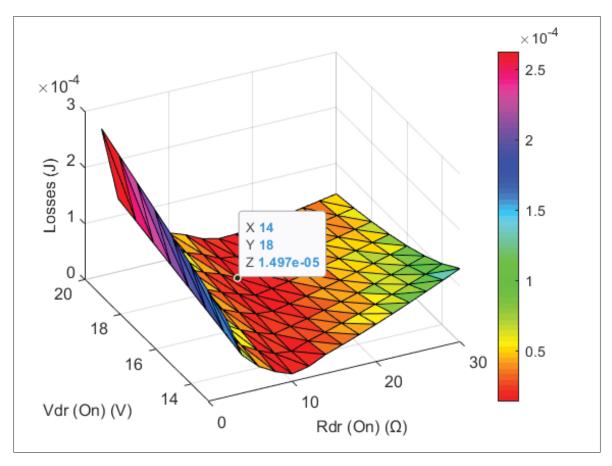

|      |          | 3.2.1.2       | Silicon Carbide (SiC) MOSFET: Optimal Operating      |     |

|      |          |               | Point to Minimize Turn-On Losses                     | 82  |

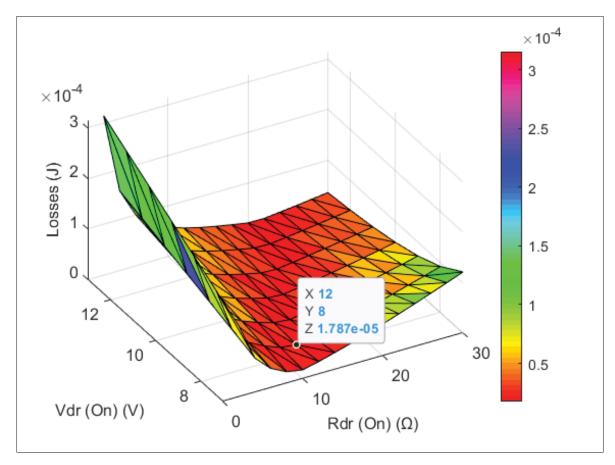

|      |          | 3.2.1.3       | Gallium Nitride (GaN) MOSFET: Optimal Operating      |     |

|      |          |               | Point to Minimize Turn-On Losses                     | 83  |

|      | 3.2.2    | Conducti      | on Losses and Dependency of Si, SiC and GaN MOSFET's |     |

|      |          |               | Parameters on Temperature                            | 85  |

|      | 3.2.3    |               | Losses                                               |     |

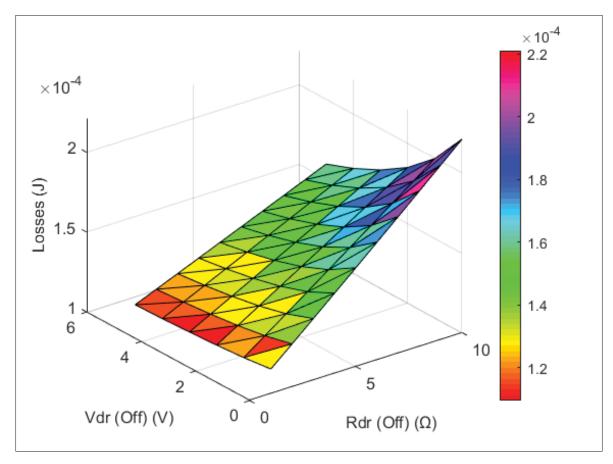

|      |          | 3.2.3.1       | Silicon (Si) MOSFET: Optimal Operating Point to      |     |

|      |          |               | Minimize Turn-Off Losses                             | 87  |

|      |          | 3.2.3.2       | Silicon Carbide (SiC) MOSFET: Optimal Operating      |     |

|      |          |               | Point to Minimize Turn-Off Losses                    | 90  |

|      |          | 3.2.3.3       | Gallium Nitride (GaN) MOSFET: Optimal Operating      |     |

|      |          |               | Point to Minimize Turn-Off Losses                    | 91  |

| 3.3  | Compai   | rison of Sv   | vitching Losses of Simulation Results                |     |

|      | 3.3.1    |               | ational Observations at Reduced Operating Point      |     |

| 3.4  | Observa  | _             | commendations and Drawback of Simulation Results     |     |

|      |          |               |                                                      |     |

| CHAF | PTER 4   |               | REMENT METHODOLOGIES                                 |     |

| 4.1  | Presenta | ation of the  | e Experimental Configuration                         | 99  |

| 4.2  | Experin  | nental Mea    | asurement Technique and Recommendations              | 102 |

|      | 4.2.1    | The Basi      | c Early Essentials                                   | 103 |

|      | 4.2.2    | The Prox      | imity Magnetic Field                                 | 105 |

|      | 4.2.3    | Introduct     | tion to the Lead Wire Current Measurement Technique  | 110 |

|      |          | 4.2.3.1       | Comparison between the Added Lead Wire and the       |     |

|      |          |               | Proximity Magnetic Field                             | 113 |

| 4.3  | Compai   | rative Meth   | nodology of Experimental Waveforms Between MOSFETs   | 115 |

|      | 4.3.1    |               | Turn-On and Mitigation Techniques                    |     |

|      | 4.3.2    | Adaptation    | on of Voltage and Current Measurement Techniques     | 125 |

|      | 4.3.3    |               | ental Configuration for Waveform Extraction          |     |

|      |          | 4.3.3.1       | Losses Computation Methodology                       |     |

|      |          | 4.3.3.2       | Comparison Between the Drain and Source Lead Wire    |     |

|      |          |               | Current Measurement Technique                        | 144 |

| 4.4  | Review   | of Final E    | Experimental Comparative Methodology, Measurement    |     |

|      |          |               | omputation Methods                                   | 149 |

|      | ,        | L             | •                                                    |     |

| CHAF | PTER 5   | <b>EXPERI</b> | MENTS AND INTERPRETATION OF RESULTS                  | 151 |

| 5.1  | Measur   | ements to     | Compare MOSFET's Switching Performances              | 152 |

|      | 5.1.1    | Turn-On       | Losses and Duration                                  | 152 |

|      | 5.1.2    | High Sic      | de Estimated Current (HS-EC) and Reverse Recovery    |     |

|      |          | Process.      |                                                      | 157 |

|       | 5.1.3     | Low Side Drain-Source Voltage (LS-VDS)                       | 167 |

|-------|-----------|--------------------------------------------------------------|-----|

|       | 5.1.4     | Turn-Off losses, Duration and Maximum Turn-off High Side     |     |

|       |           | Estimated Current (HS-EC) Slope                              | 169 |

|       | 5.1.5     | Conduction Losses (10 µs)                                    |     |

| 5.2   | Compar    | ison of Experimental Results                                 |     |

|       | 5.2.1     | Comparative Experimental Results between Si MOSFETs          |     |

|       |           | (IPW65R080CFDA) and SiC MOSFETs (SCT3060ALHR) in             |     |

|       |           | pu                                                           | 173 |

|       | 5.2.2     | Comparative Experimental Results between GaN MOSFETs         |     |

|       |           | (TPH3205WSBQA) and SiC MOSFETs (SCT3060ALHR) in pu           | 180 |

| 5.3   | Recomn    | nendations Based On Relative Experimental Comparison Between |     |

|       | Si, SiC a | and GaN MOSFETs                                              | 190 |

|       |           |                                                              |     |

| CON   | CLUSION   | AND RECOMMENDATIONS                                          | 191 |

| A DDI |           | THEN ON INTERNAL 1. COMPLETE MATHEMATICAL                    |     |

| APPI  | ENDIX I   |                                                              | 107 |

|       |           | ANALYSIS                                                     | 195 |

| Δ ΡΡΙ | ENDIX II  | MOSFET'S TEMPERATURE DEPENDENCY                              | 201 |

| 71111 |           | MOSTEL STEWNER TORE DELEVOEIVET                              | 201 |

| APPI  | ENDIX III | RAW DATA OF EXPERIMENTAL RESULTS                             | 205 |

|       |           |                                                              |     |

| APPI  | ENDIX IV  | RELATIVE EXPERIMENTAL COMPARISON BETWEEN                     |     |

|       |           | THE SOURCE CURRENT MEASUREMENT AND DRAIN                     |     |

|       |           | CURRENT MEASUREMENT METHODOLOGIES                            | 209 |

|       |           |                                                              |     |

| RIRI  | JOGR API  | 4Y                                                           | 212 |

#### LIST OF TABLES

|            | Page                                                                                                                                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

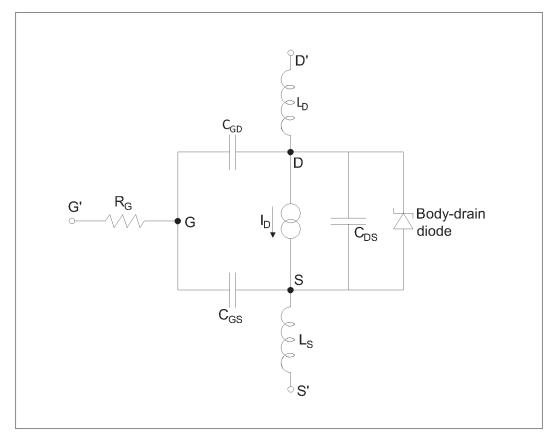

| Table 2.1  | Inclusion from the Main Passive and Active Components of the Equivalent MOSFET Electrical Schematic with Parasitic Components 27                                                                                 |

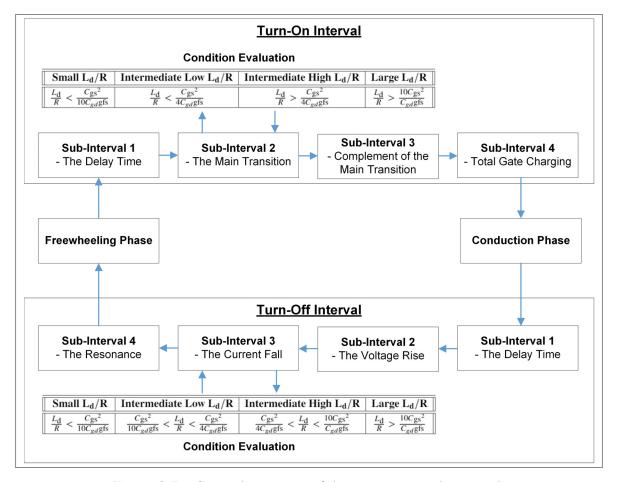

| Table 2.2  | Condition Evaluation's Equations of 2 <sup>nd</sup> Turn-On Switching Interval 53                                                                                                                                |

| Table 2.3  | Condition Evaluation's Equations of 3 <sup>rd</sup> Turn-Off Switching Interval 70                                                                                                                               |

| Table 3.1  | Main Characteristics of Si IPW65R080CFDA, SiC SCT3060ALHR and GaN TPH3205WSBQA MOSFETs                                                                                                                           |

| Table 3.2  | Main Computation Conditions and Characteristics of Si IPW65R080CFDA, SiC SCT3060ALHR and GaN TPH3205WSBQA MOSFETs                                                                                                |

| Table 3.3  | Best Computational Suited Configurations for Minimal Turn-on Losses and Duration of the Si MOSFET IPW65R080CFDA                                                                                                  |

| Table 3.4  | Best Computational Suited Configurations for Minimal Turn-On Losses and Duration of the SiC MOSFET SCT3060ALHR                                                                                                   |

| Table 3.5  | Best Computational Suited Configurations for Minimal Turn-On Losses and Duration of GaN MOSFET TPH3205WSBQA                                                                                                      |

| Table 3.6  | Average Influence of Increasing the Temperature from $25^{\circ}\text{C}$ to $75^{\circ}\text{C}$ on MOSFET's $R_{ds(on)}$ and $V_{gs(th)}$ Depending on Voltage and Current Rating, Package Type and Technology |

| Table 3.7  | Suited Computational Configurations for Minimal Turn-Off Losses without Voltage Clamping of the Si MOSFET (IPW65R080CFDA)                                                                                        |

| Table 3.8  | Suited Computational Configurations for Minimal Turn-Off Losses without Voltage Clamping of the SiC MOSFET (SCT3060ALHR)                                                                                         |

| Table 3.9  | Suited Computational Configurations for Minimal Turn-Off Losses without Voltage Clamping of the GaN MOSFET (TPH3205WSBQA) 91                                                                                     |

| Table 3.10 | Summary of Optimal Computed Configuration and Corresponding Minimal Switching Losses of Si, SiC and GaN MOSFETs under study for an Operating Point of 400V & 20A, without Clamping                               |

| Table 3.11 | Summary of Optimal Computed Configuration and Corresponding Minimal Switching Losses of Si, SiC and GaN MOSFETs under study for an Operating Point of 325V & 10A, without Clamping | 96  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.1  | Average Current Value and Deviation as a Function of the Load Configuration from Simulink                                                                                          | 100 |

| Table 4.2  | Film Capacitor's Properties of the External Capacitor Bank                                                                                                                         | 101 |

| Table 4.3  | Comparison between the Low Side MOSFET's Drain Lead and Source Lead Current Extraction Methodology                                                                                 | 148 |

| Table 5.1  | Relative Comparison of Si MOSFET (IPW65R080FDA) to SiC MOSFET (SCR3060ALHR) (pu)                                                                                                   | 174 |

| Table 5.2  | Cummulative Statistical Relative Comparison of Si MOSFETs (IPW65R080FDA) to SiC MOSFETs (SCR3060ALHR) under all Experimental Configurations (pu)                                   | 175 |

| Table 5.3  | Relative Comparison of GaN MOSFETs (TPH3205WSBQA) to SiC MOSFETs (SCR3060ALHR) (pu)                                                                                                | 181 |

| Table 5.4  | Cummulative Statistical Relative Comparison of GaN MOSFETs (TPH3205WSBQA) to SiC MOSFETs (SCR3060ALHR) under all Experimental Configurations (pu)                                  | 182 |

| Table 5.5  | Relative Comparison of GaN's Experimental Results with Drain Methodology to its relative Source Methodology Referenced on the Source Methodology's Results (pu)                    | 183 |

| Table 5.6  | Relative Comparison of GaN MOSFETs (TPH3205WSBQA) to SiC MOSFETs (SCR3060ALHR) (pu) Long-Term Turn-on relative observations with the drain methodology excluded                    | 185 |

| Table 5.7  | Cummulative Statistical Relative Comparison of GaN MOSFETs (TPH3205WSBQA) to SiC MOSFETs (SCR3060ALHR) under all Configurations (pu) Long-Term Turn-on relative observations with  | 10/ |

|            | the drain methodology excluded                                                                                                                                                     | 180 |

#### LIST OF FIGURES

|            | Page                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1 | Global annual energy consumption by source (TWh) and average annual energy use per capita (kWh)                                                                                                                                                              |

| Figure 1.2 | Percentage of global CO <sub>2</sub> emissions from fuel combustion by sectors from 1990 to 2017 and annual CO <sub>2</sub> emissions from 1990 to 2017                                                                                                      |

| Figure 1.3 | Theoretical on-state resistance versus blocking voltage capabilities of Si, SiC and GaN                                                                                                                                                                      |

| Figure 1.4 | Summary of typical ratings of commercially available Si and WBG semiconductors                                                                                                                                                                               |

| Figure 1.5 | Ratings of commercially available SiC and GaN devices for middle voltage and current range (>100V to $\leq$ 900V & >3A to $\leq$ 90A) and normalized maximum power (p.u.) based on the highest power capability of the SiC device in the middle range (1 pu) |

| Figure 1.6 | Main advantages of SiCs in APE systems                                                                                                                                                                                                                       |

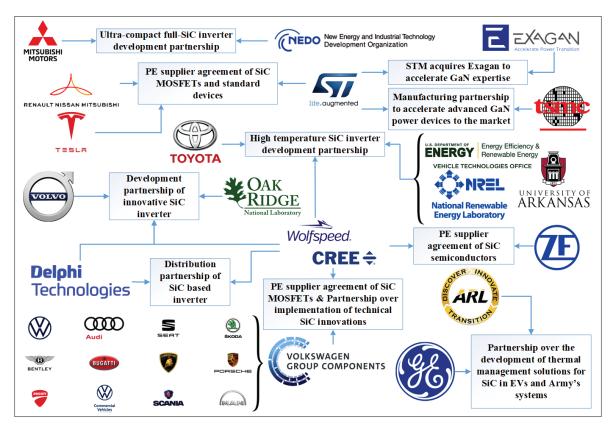

| Figure 1.7 | An overview of industrial partnerships between EV manufacturers and PE WBG suppliers                                                                                                                                                                         |

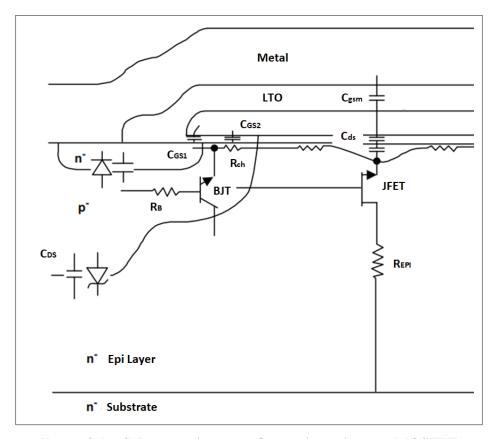

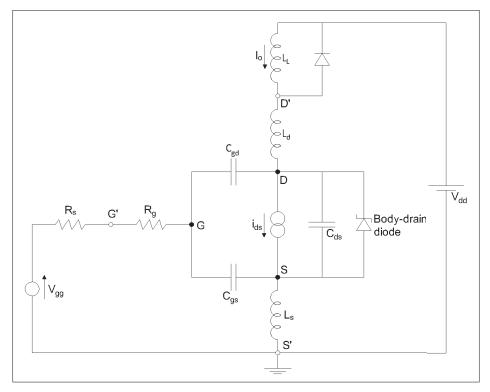

| Figure 2.1 | Schematic diagram of an n-channel power MOSFET with its parasitic components                                                                                                                                                                                 |

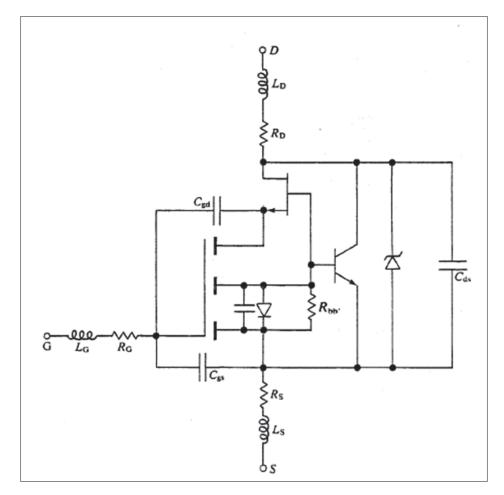

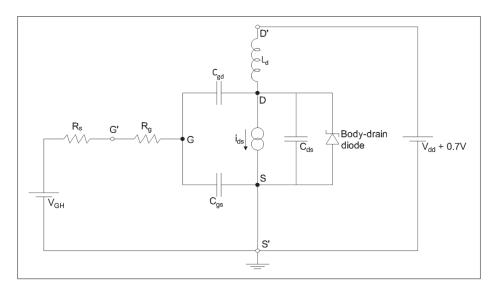

| Figure 2.2 | MOSFET equivalent electrical circuit with parasitic components 26                                                                                                                                                                                            |

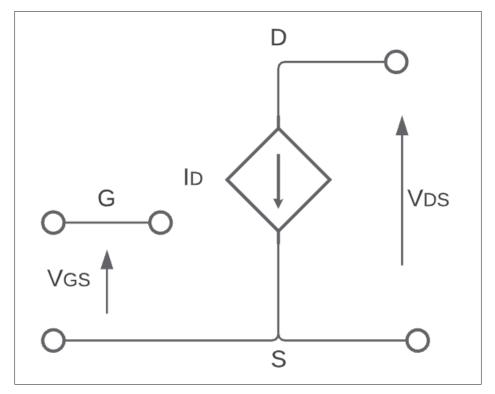

| Figure 2.3 | Simple MOSFET model for transient analysis                                                                                                                                                                                                                   |

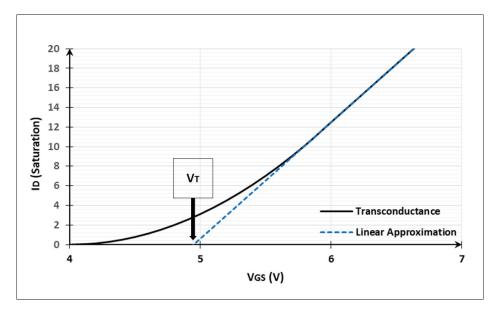

| Figure 2.4 | Example of linear approximation of the transfer characteristic of a MOSFET                                                                                                                                                                                   |

| Figure 2.5 | Equivalent MOSFET model with its most important parasitic components                                                                                                                                                                                         |

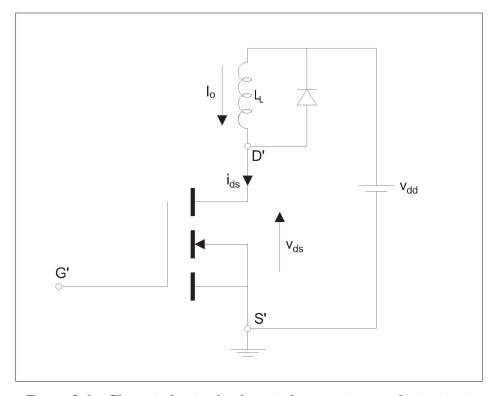

| Figure 2.6 | Clamp inductive load equivalent transient analysis circuit                                                                                                                                                                                                   |

| Figure 2.7 | General overview of the computational approach                                                                                                                                                                                                               |

| Figure 2.8 | Reference simulation model of clamp inductive MOSFET's transient                                                                                                                                                                                             |

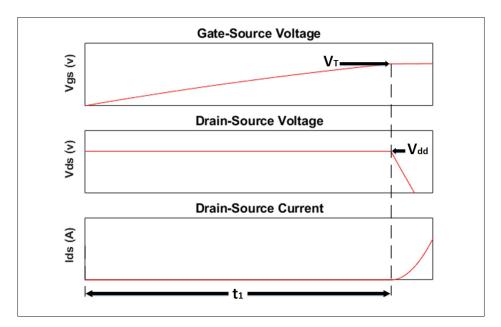

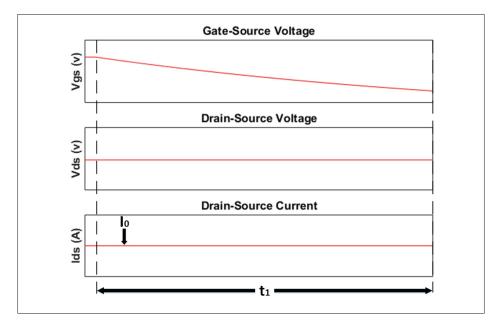

| Figure 2.9  | Expected waveforms of MOSFET's Transient Analysis for the 1 <sup>st</sup> turn-on interval                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

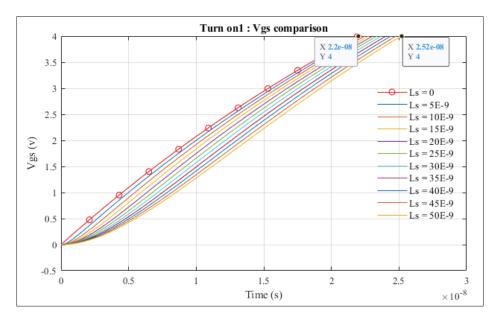

| Figure 2.10 | Comparison between Vgs computed with the abbreviated equation 2.14 and the complete equation 2.15 for $L_s$ between 5nH and 50nH 45                |

| Figure 2.11 | Reference model of MOSFET's transient analysis circuit for the 2 <sup>nd</sup> interval of turn-on                                                 |

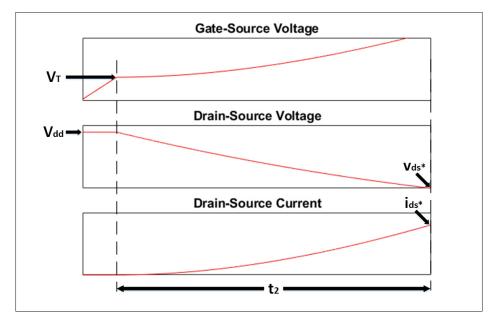

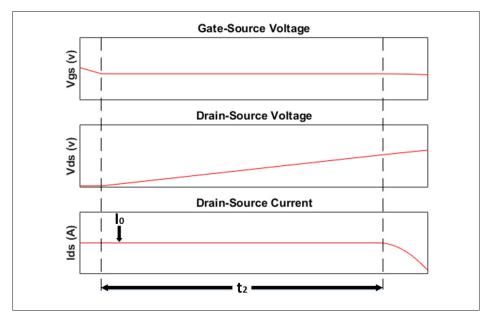

| Figure 2.12 | Expected waveforms of MOSFET's transient analysis for the 2 <sup>nd</sup> turn-on interval                                                         |

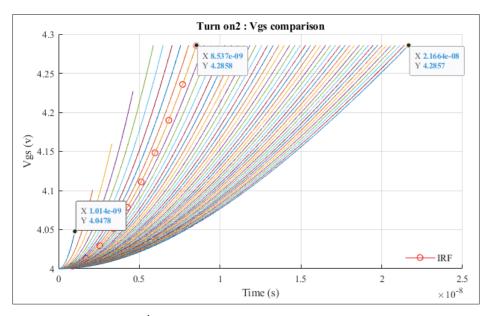

| Figure 2.13 | $2^{nd}$ Turn-on interval: $v_{gs}$ comparison for total gate resistance from $1\Omega$ to $50\Omega$ by increments of $1\Omega$ with $L_d=100 nH$ |

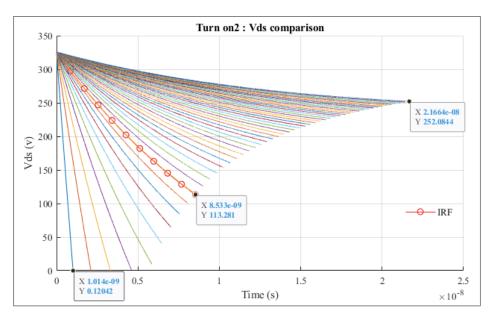

| Figure 2.14 | $2^{nd}$ Turn-on interval: $v_{ds}$ comparison for total gate resistance from $1\Omega$ to $50\Omega$ by increments of $1\Omega$ with $L_d=100 nH$ |

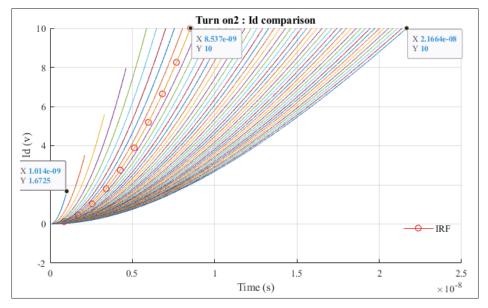

| Figure 2.15 | $2^{nd}$ Turn-on interval: $i_{ds}$ comparison for total gate resistance from $1\Omega$ to $50\Omega$ by increments of $1\Omega$ with $L_d=100 nH$ |

| Figure 2.16 | $2^{nd}$ Turn-on interval: energy comparison for total gate resistance from $1\Omega$ to $50\Omega$ by increments of $1\Omega$ with $L_d=100nH$    |

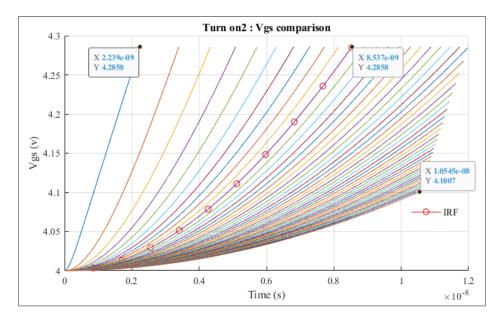

| Figure 2.17 | $2^{nd}$ Turn-on interval: $v_{gs}$ comparison for total unclamped inductance from 1nH to 500nH by increments of 10nH with R = $10~\Omega$         |

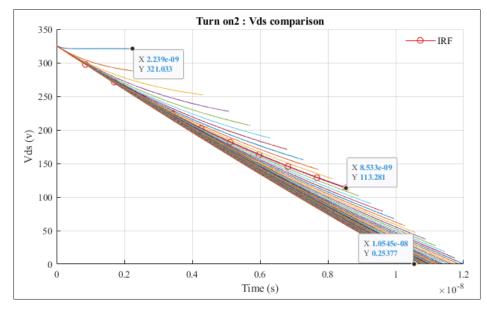

| Figure 2.18 | $2^{nd}$ Turn-on interval: $v_{ds}$ comparison for total unclamped inductance from 1nH to 500nH by increments of 10nH with $R=10~\Omega$           |

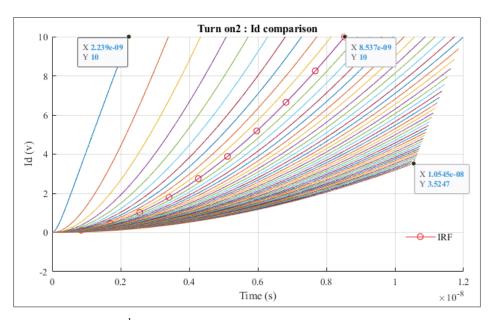

| Figure 2.19 | $2^{nd}$ Turn-on interval: $i_{ds}$ comparison for total unclamped inductance from 1nH to 500nH by increments of 10nH with R = 10 $\Omega$         |

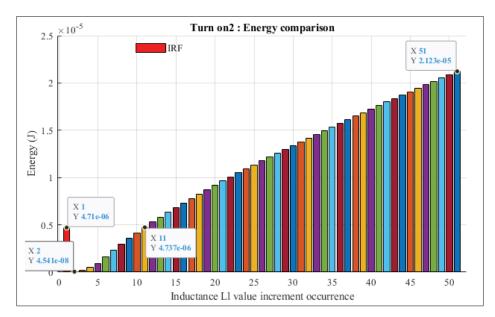

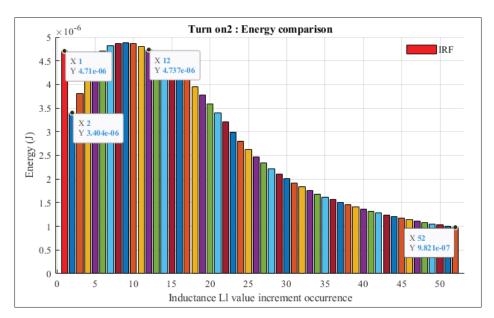

| Figure 2.20 | $2^{nd}$ Turn-on interval: Energy comparison for total unclamped inductance from 1nH to 500nH by increments of 10nH with R = $10~\Omega$ 61        |

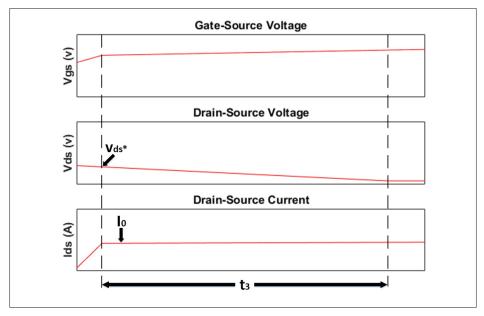

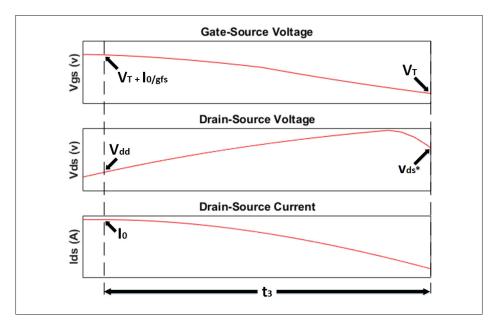

| Figure 2.21 | Expected waveforms of MOSFET's transient analysis for the 3 <sup>rd</sup> turn-on interval: The Drain-Source Voltage Fall                          |

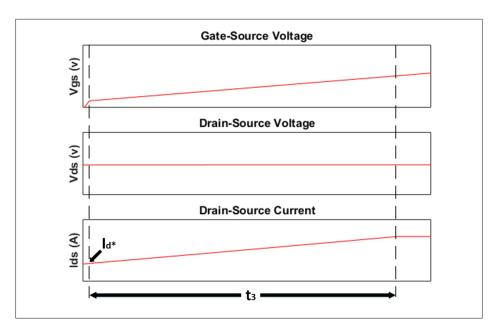

| Figure 2.22 | Expected waveforms of MOSFET's transient analysis for the 3 <sup>rd</sup> turn-on interval: The Rise of the Drain Current                          |

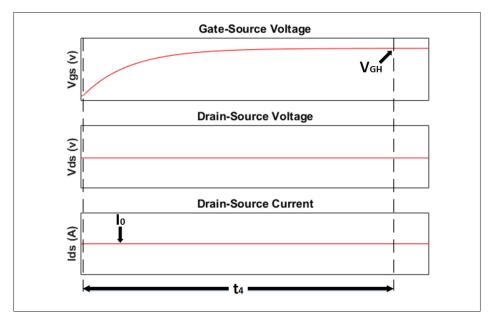

| Figure 2.23 | Expected waveforms of MOSFET's transient analysis for the 4 <sup>th</sup> turn-on interval                                                         |

| Figure 2.24 | Expected waveforms of MOSFET's transient analysis for the 1 <sup>st</sup> turn-off interval: The Delay Time                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.25 | Approximated waveforms of MOSFET's transient analysis for the 2 <sup>nd</sup> turn-off interval : The Voltage Rise                                                                                              |

| Figure 2.26 | Approximated waveforms of MOSFET's transient analysis for the 3 <sup>rd</sup> turn-off interval : The Current Fall                                                                                              |

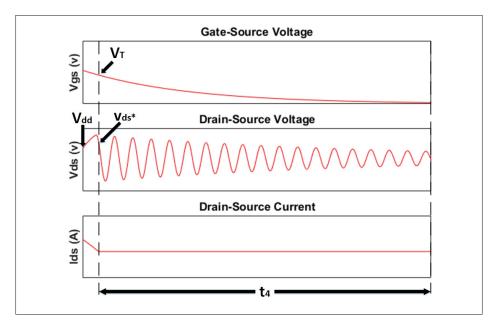

| Figure 2.27 | Approximated waveforms of MOSFET's transient analysis for the 4 <sup>th</sup> turn-off interval : The Resonance                                                                                                 |

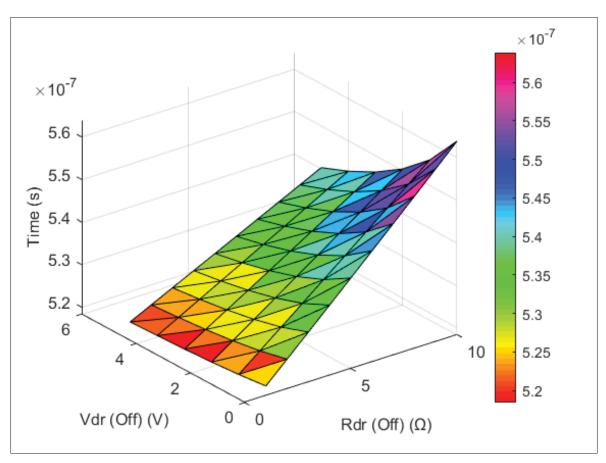

| Figure 3.1  | Si MOSFET: impact of the turn-on driving voltage and resistance on total turn-on energy                                                                                                                         |

| Figure 3.2  | Impact of the turn-on driving voltage and resistance on total turn-on energy for SiC MOSFET SCT3060ALHR                                                                                                         |

| Figure 3.3  | Impact of the turn-on driving voltage and resistance on total turn-on energy for GaN MOSFET TPH3205WSBQA                                                                                                        |

| Figure 3.4  | Si MOSFET: impact of the turn-off driving voltage and resistance on total turn-off energy                                                                                                                       |

| Figure 3.5  | Si MOSFET: impact of the turn-off driving voltage and resistance on total turn-off time duration                                                                                                                |

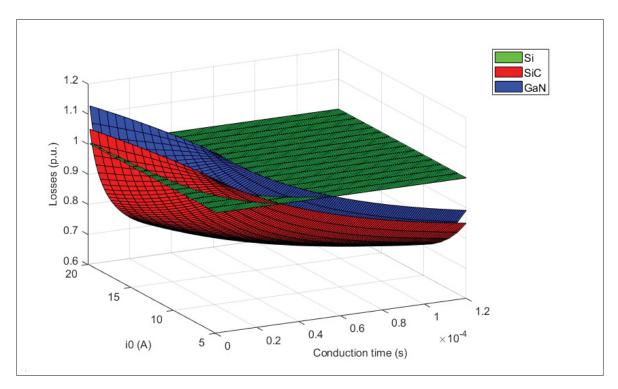

| Figure 3.6  | Relative comparison of total losses per cycle of SiC and GaN MOSFET compared to the Si MOSFET at 400V with a nominal current between 5A and 20A, and conduction time between 1 $\mu$ s and 120 $\mu$ s at 75 °C |

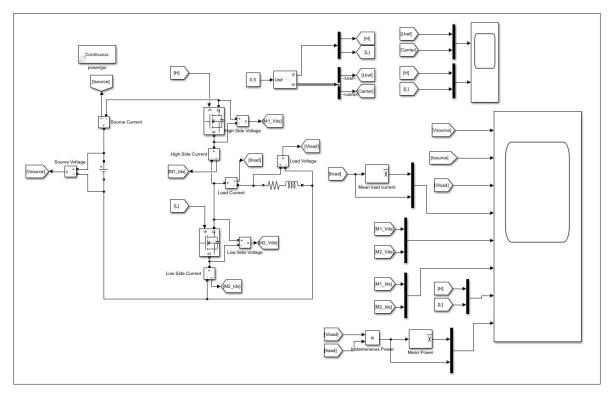

| Figure 4.1  | Simulink model of the experimental configuration of the Half-Bridge board                                                                                                                                       |

| Figure 4.2  | Capacitor bank assembly on the Half-Bridge board                                                                                                                                                                |

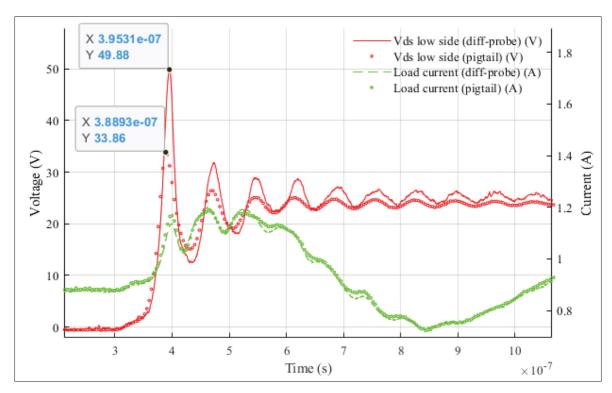

| Figure 4.3  | General comparison between differential probe ADP305 and passive pigtail probe PP0006A on low side drain-source surge voltage                                                                                   |

| Figure 4.4  | Magnetic field probe built from a coaxial cable covered with Kapton tape                                                                                                                                        |

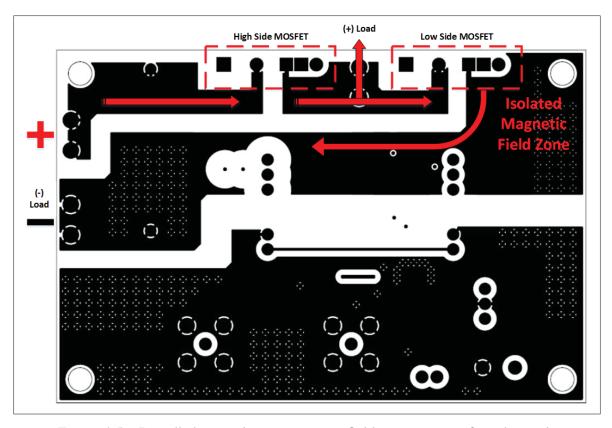

| Figure 4.5  | Board's bottom layout magnetic field measurement from low side MOSFET's reverse recovery current                                                                                                                |

| Figure 4.6  | measurements of the proximity magnetic field                                                                                                                              | 108 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

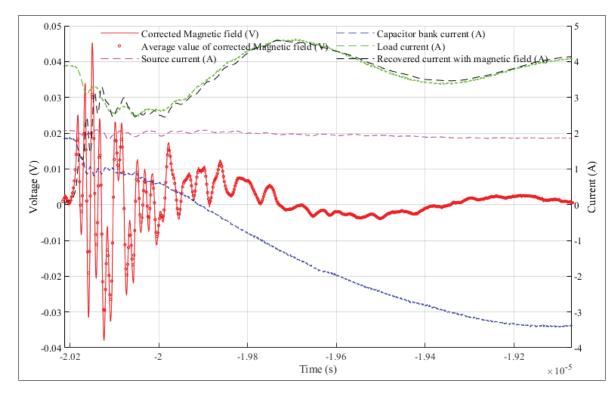

| Figure 4.7  | Integration of the magnetic field measurement to adjust the magnetic coupling factor during turn-off waveform                                                             | 109 |

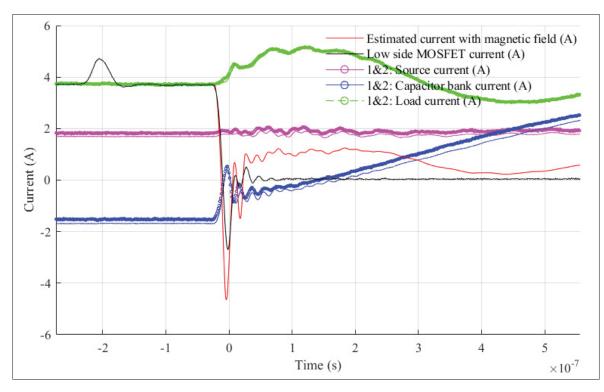

| Figure 4.8  | Approximation of the reverse recovery current through integration of the magnetic field during turn-on waveform                                                           | 110 |

| Figure 4.9  | Additional current measurement wire on the source lead of the low side MOSFET partially covered with Kapton tape                                                          | 111 |

| Figure 4.10 | Impact of the source lead wire on turn-off waveforms (rounded results with added source lead wire)                                                                        | 112 |

| Figure 4.11 | Impact of the source lead wire on turn-on waveforms (rounded results with added source lead wire)                                                                         | 113 |

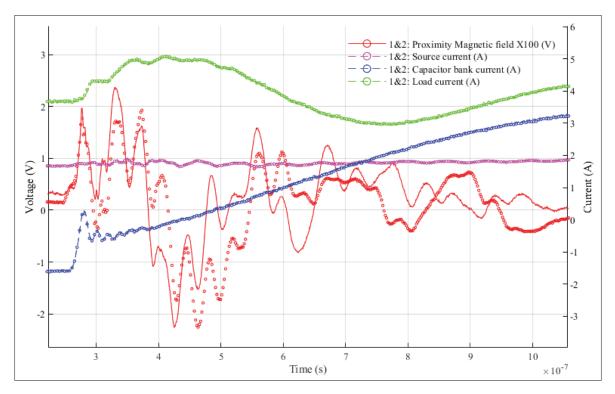

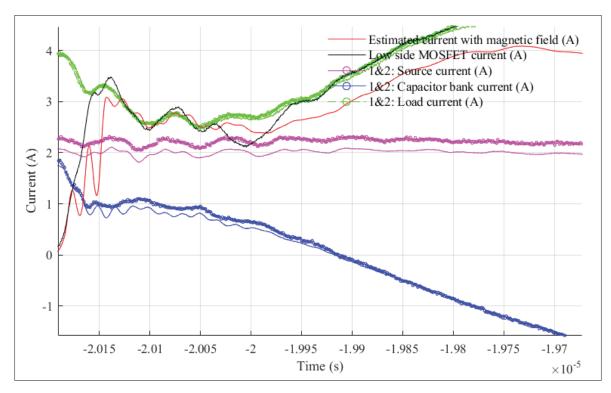

| Figure 4.12 | Comparison between the proximity field and source lead wire methodologies to extract the low side MOSFET's current on turn-off waveforms                                  | 114 |

| Figure 4.13 | Comparison between the proximity field and source lead wire methodologies to extract the low side MOSFET's current on turn-on waveforms                                   | 115 |

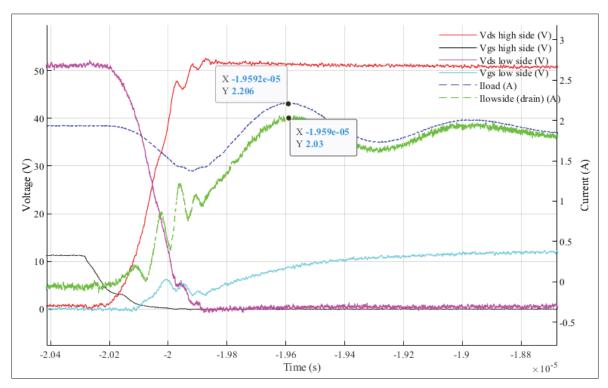

| Figure 4.14 | Si MOSFET: equivalent total gate resistance (22 $\Omega$ On & 15 $\Omega$ Off) turn-on waveform gate overlap (with source lead wire)                                      | 116 |

| Figure 4.15 | SiC MOSFET: equivalent total gate resistance (12 $\Omega$ On & 12 $\Omega$ Off) turn-on waveform gate overshoot (without source lead wire)                                | 117 |

| Figure 4.16 | Si MOSFET: turn-on waveforms at 100 V without the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                                    | 119 |

| Figure 4.17 | Si MOSFET: turn-on waveforms at $100V$ without the added source lead wire ( $22\Omega$ On & $3.3\Omega$ Off & DT $80\%$ )                                                 | 120 |

| Figure 4.18 | Si MOSFET: turn-on waveforms at 100V with the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                                        | 121 |

| Figure 4.19 | Si MOSFET: turn-on waveforms at 50 V with the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 % with multiple simultaneous differential voltage probes) | 124 |

| Figure 4.20 | Si MOSFET: turn-on waveforms at 50 V with the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 % with a single passive probe)125                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

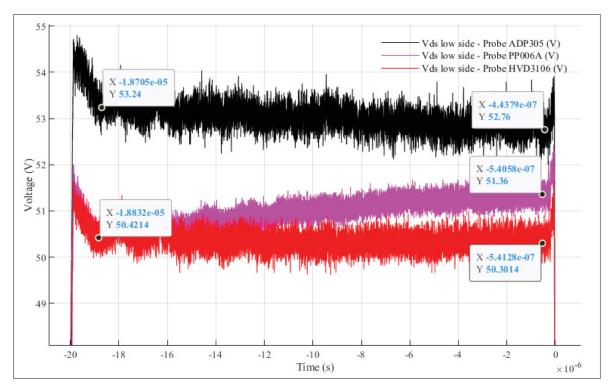

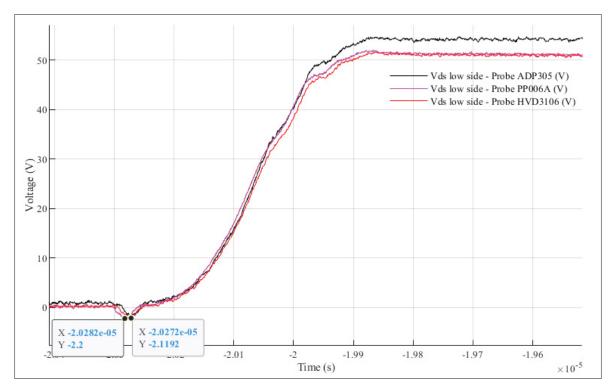

| Figure 4.21 | Si MOSFET: comparison of low side voltage measurements on turn-off steady state waveforms at 50V with the added source lead wire on low side switching MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)       |

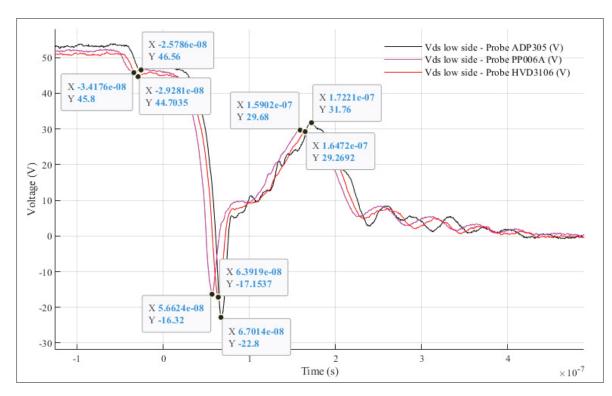

| Figure 4.22 | Si MOSFET: comparison of low side voltage measurements on turn-on transient waveforms at 50 V with the added source lead wire on low side switching MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)129       |

| Figure 4.23 | Si MOSFET: comparison of low side voltage measurements on turn-off transient waveforms at 50 V with the added source lead wire on low side switching MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)         |

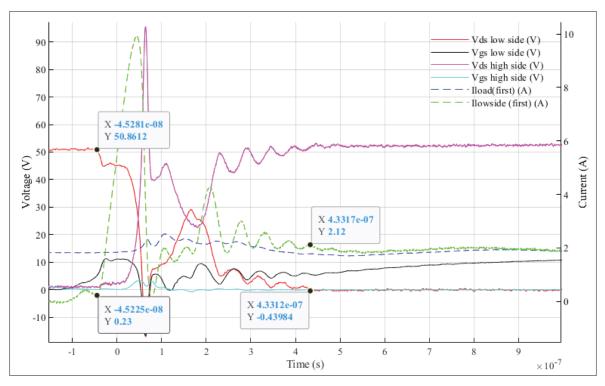

| Figure 4.24 | Si MOSFET: comparison between first and last CP031 current measurements on transient waveforms at 50 V with the added source lead wire on low side switching MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %) |

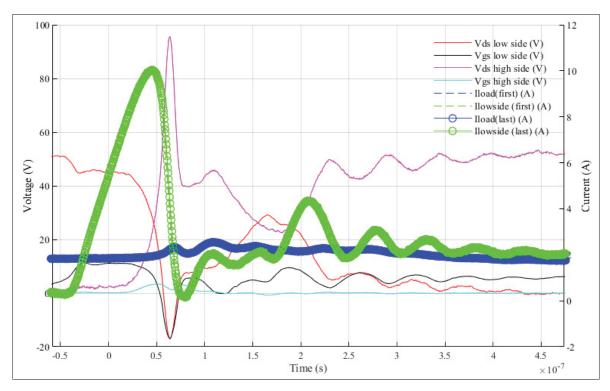

| Figure 4.25 | Si MOSFET: turn-on waveforms of low side switching MOSFET at 50 V with the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                                                   |

| Figure 4.26 | Si MOSFET: turn-off waveforms of low side switching MOSFET at 50 V with the added source lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                                                  |

| Figure 4.27 | Si MOSFET: turn-off waveforms of low side switching MOSFET at 50 V with the added drain lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %) .134                                                              |

| Figure 4.28 | Si MOSFET: turn-on waveforms of low side switching MOSFET at 50 V with the added drain lead wire (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %) .135                                                               |

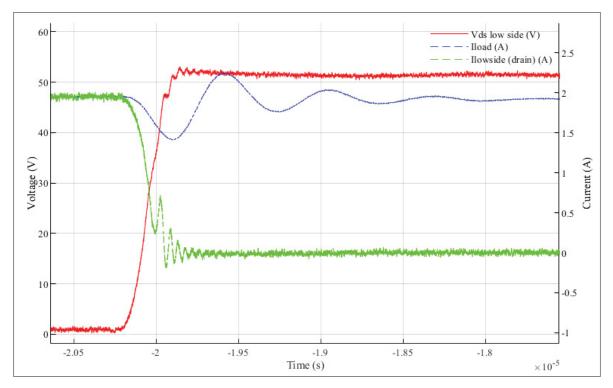

| Figure 4.29 | Si MOSFET: turn-on waveforms of high side switching MOSFET at 50 V with the added drain lead wire on low side MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                                |

| Figure 4.30 | Si MOSFET: turn-off waveforms of high side switching MOSFET at 50 V with the added drain lead wire on low side MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                                               |

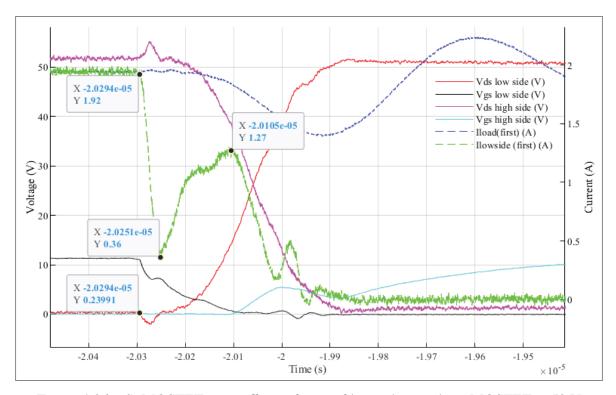

| Figure 4.31 | Si MOSFET: turn-on waveforms of high side switching MOSFET at 50 V with the added source lead wire on low side MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)                | 138 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.32 | Si MOSFET: turn-off waveforms of high side switching MOSFET at 50 V with the added source lead wire on low side MOSFET (22 $\Omega$ On & 3.3 $\Omega$ Off & DT 50 %)               | 139 |

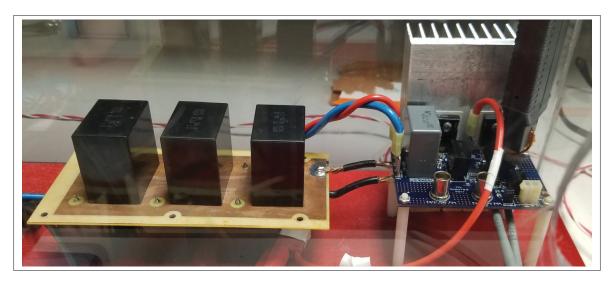

| Figure 4.33 | Si MOSFET: experimental board ready for measurement extraction under a high side switching MOSFET configuration with the added source lead wire on low side MOSFET                 | 141 |

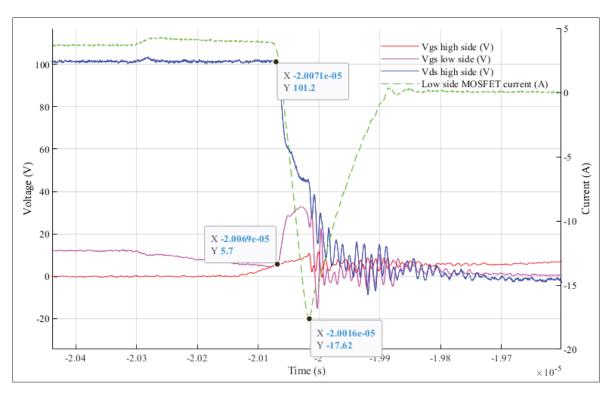

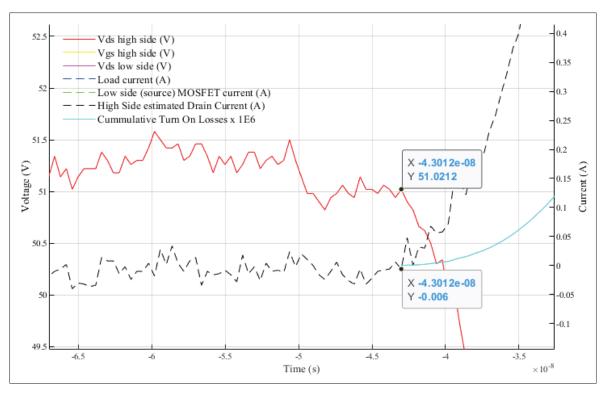

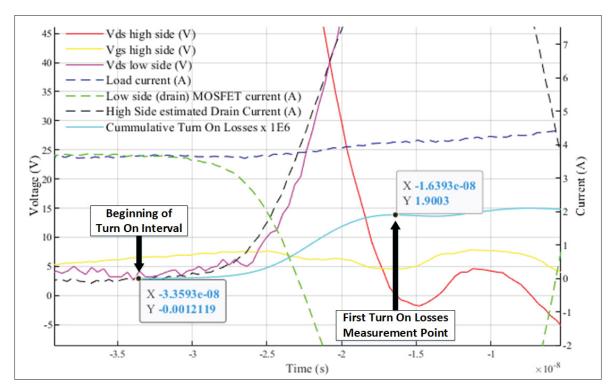

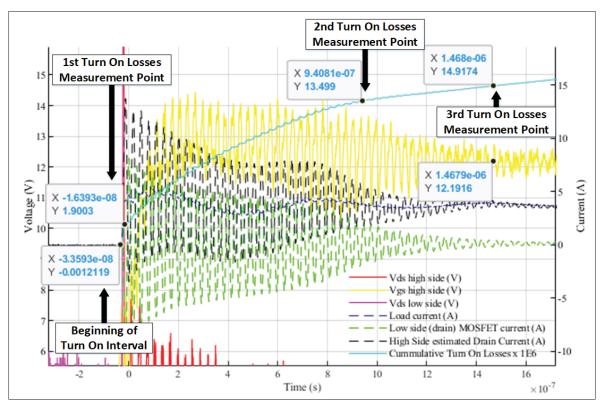

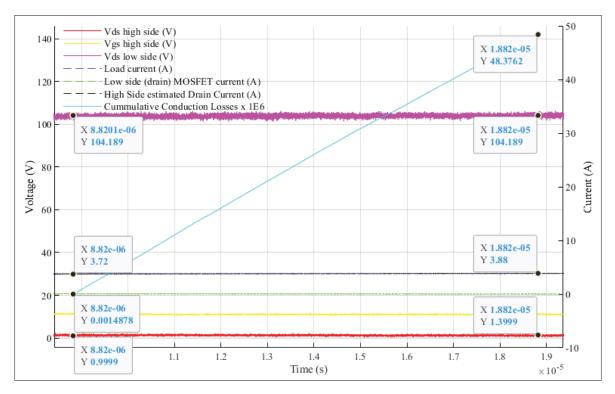

| Figure 4.34 | High side switching MOSFET: fine adjustment of current waveforms for turn-on losses computation                                                                                    | 142 |

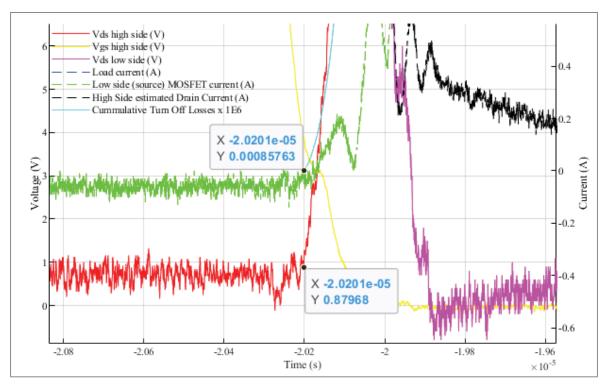

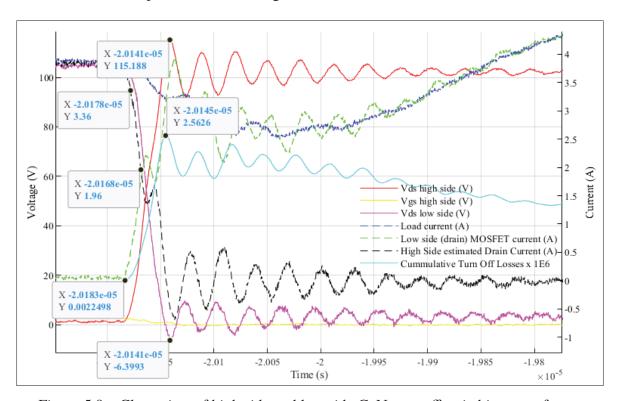

| Figure 4.35 | High side switching MOSFET: starting point for turn-off losses computation                                                                                                         | 143 |

| Figure 4.36 | High side switching Si MOSFET: turn-on losses computation with the source lead methodology                                                                                         | 144 |

| Figure 4.37 | High side switching Si MOSFET: turn-on losses computation with the drain lead methodology                                                                                          | 145 |

| Figure 4.38 | High side switching Si MOSFET: turn-off losses computation with the source lead methodology                                                                                        | 146 |

| Figure 4.39 | High side switching Si MOSFET: turn-off losses computation with the drain lead methodology                                                                                         | 147 |

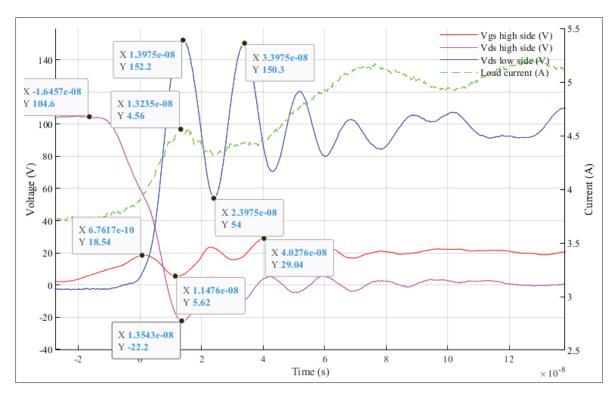

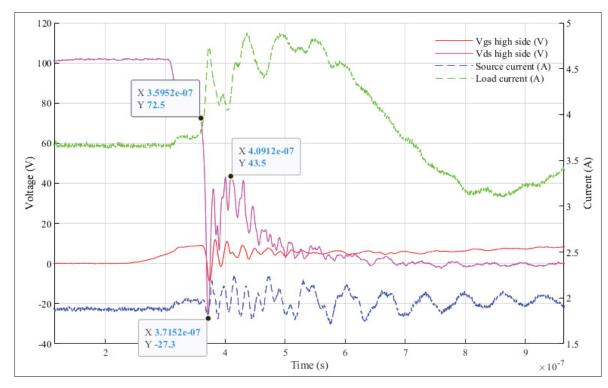

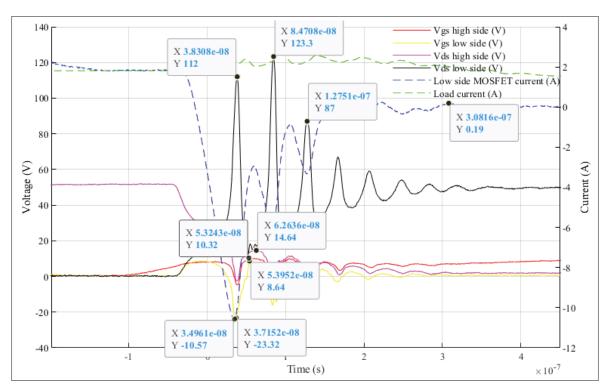

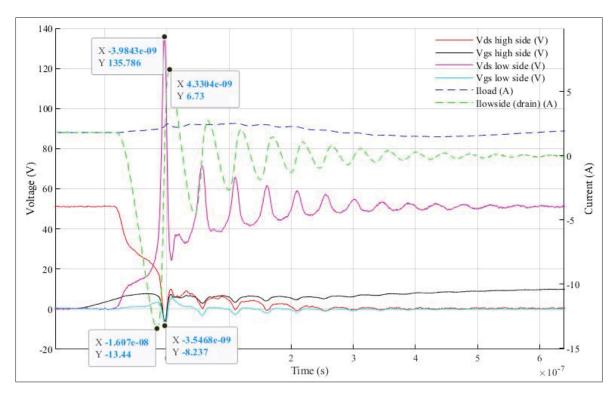

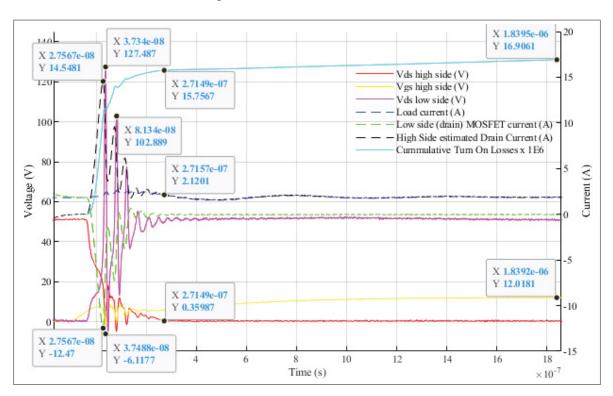

| Figure 5.1  | Close view of high side GaN turn-on switching waveforms and losses at 100 V with low side drain lead (both high and low side $R_{on}$ = 10 $\Omega$ & $R_{off}$ = 3.3 $\Omega$ )   | 154 |

| Figure 5.2  | General view of high side GaN turn-on switching waveforms and losses at 100 V with low side drain lead (both high and low side $R_{on}$ = 10 $\Omega$ & $R_{off}$ = 3.3 $\Omega$ ) | 155 |

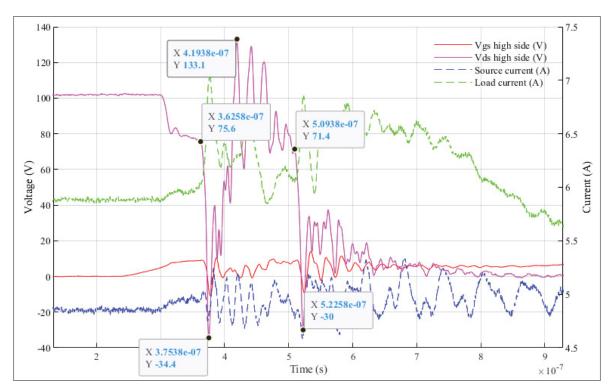

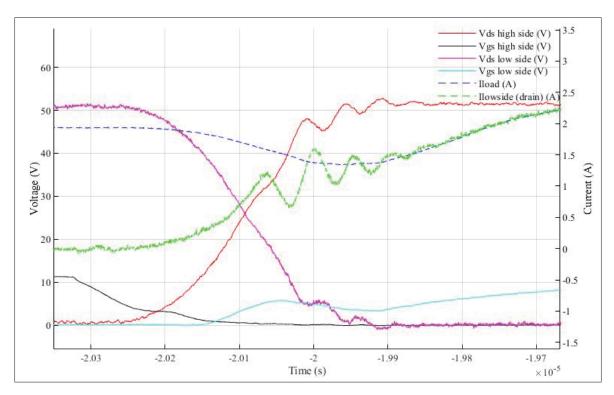

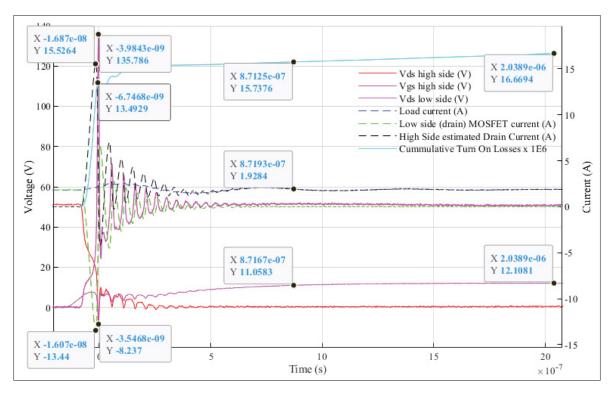

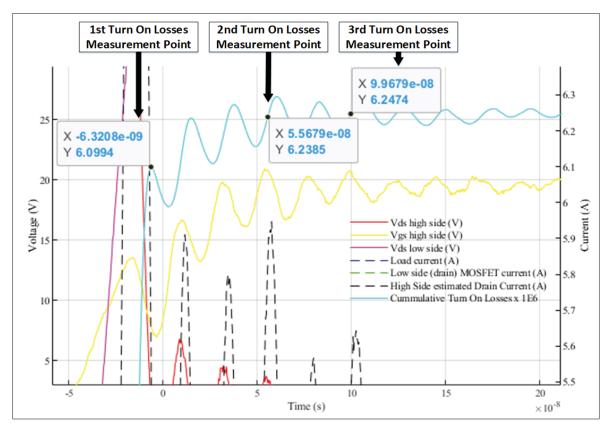

| Figure 5.3  | Close view of high side SiC turn-on switching waveforms and losses at 100V with low side drain lead (both high and low side $R_{on}$ = $10\Omega$ & $R_{off}$ = $3.3\Omega$ )      | 156 |

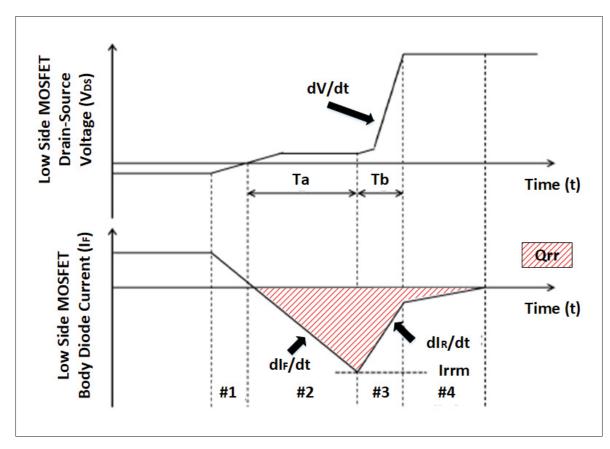

| Figure 5.4  | Overview of MOSFET reverse recovery process divided into four sub-intervals                                                                                                        | 159 |

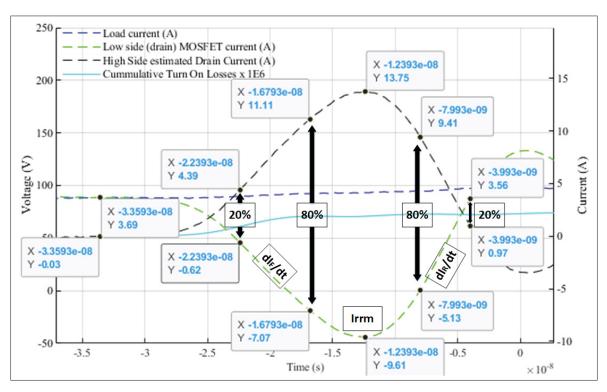

| Figure 5.5  | Close view of high side GaN turn-on switching waveforms: HS-EC maximum value ( $I_{rrm}$ ), positive ( $dI_F/dt$ ) and negative maximum slope ( $-dI_R/dt$ ) at 100V with low side drain lead (both high and low side $R_{on} = 10\Omega$ & $R_{off} = 3.3\Omega$ )                         | .162 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.6  | Cascode schematic symbol and internal cascode device structure of GaN MOSFETs under TO-247-3 package                                                                                                                                                                                        | .165 |

| Figure 5.7  | Simplified GaN behavior and turn-on conditions in the first and third quadrant                                                                                                                                                                                                              | .166 |

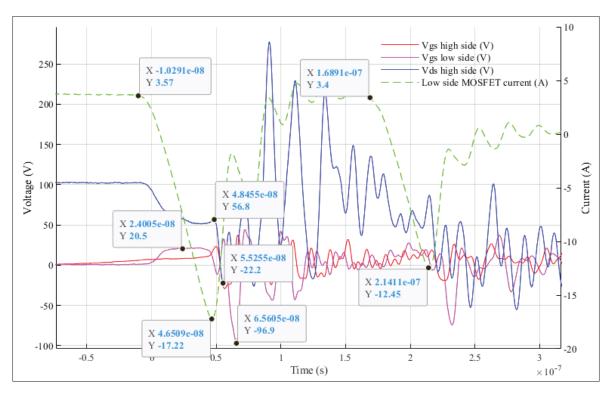

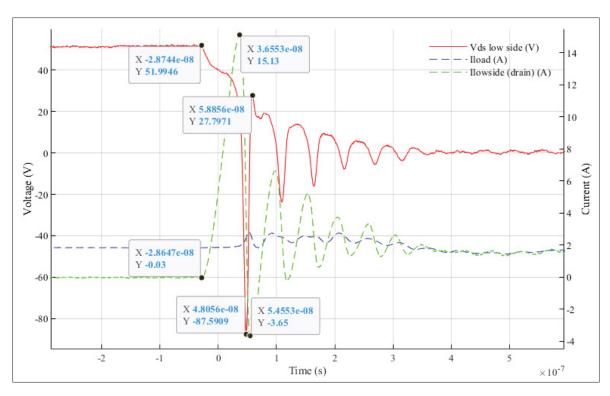

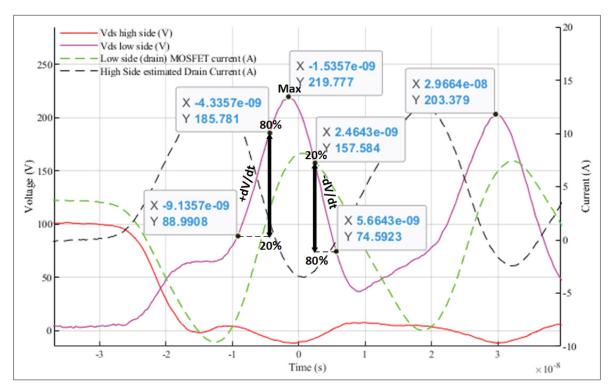

| Figure 5.8  | Close view of high side and low side GaN turn-on switching waveforms: LS- $v_{ds}$ maximum positive slope $(+dv_{ds}/dt)$ , maximum value and maximum negative slope $(-dv_{ds}/dt)$ at 100V with low side drain lead (both high and low side $R_{on} = 10\Omega$ & $R_{off} = 3.3\Omega$ ) | .168 |

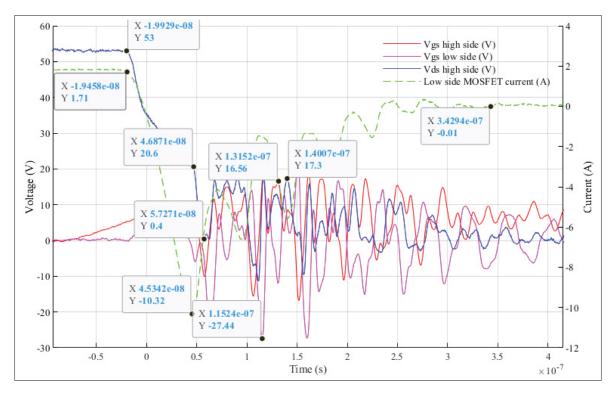

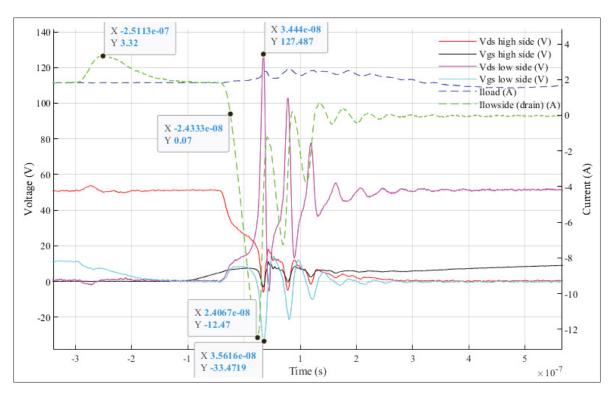

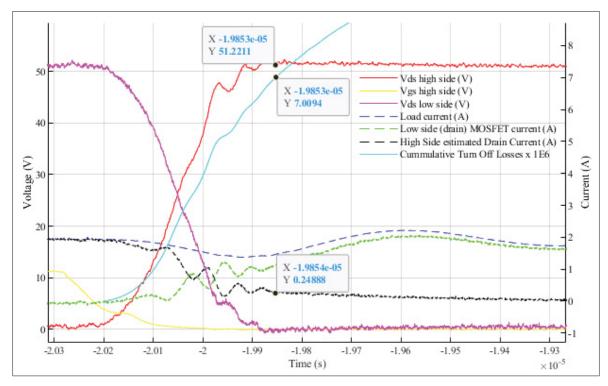

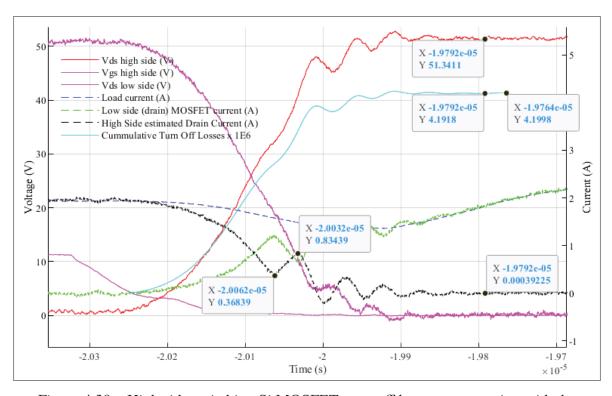

| Figure 5.9  | Close view of high side and low side GaN turn-off switching waveforms: turn-off losses, duration and maximum value of decreasing slope at 100V with low side drain lead (both high and low side $R_{on}$ = 10 $\Omega$ & $R_{off}$ = 3.3 $\Omega$ )                                         | .170 |

| Figure 5.10 | Close view of GaN conduction waveforms: computation of conduction losses at 100V with low side drain lead (both high and low side $R_{on} = 10\Omega$ & $R_{off} = 3.3\Omega$ )                                                                                                             | .172 |

#### LIST OF ABBREVIATIONS

2DEG Two-Dimensional Electron Gas

APE Automotive Power Electronic

APEEM Advanced Power Electronics and Electric Motors

ARPA-E Advanced Research Projects Agency-Energy

BJT Bipolar Junction Transistor

BNC Bayonet Neill-Concelman

CETEES Center of Excellence in Transportation Electrification and Energy Storage

CMRR Common-Mode Rejection Ratio

DC Direct Current

DOD Department of Defense

DOE Department of Energy

EDV Electric Drive Vehicle

EMI Electromagnetic Interference

EV Electric Vehicle

FE Field-Effect

FET Field-Effect Transistor

GaN Gallium Nitride

GPI GaNPower International

HEMT High Electron Mobility Transistor

HEV Hybrid Electric Vehicle

HS-EC High Side Estimated Current

HV High Voltage

IAPG Interagency Advanced Power Group

ICE Internal Combustion Engine

IECON Industrial Electronics, Control, and Instrumentation Conference

IEEE Institute of Electrical and Electronics Engineers

IGBT Insulated-Gate Bipolar Transistor

JEDEC Joint Electron Device Engineering Council

JFET Junction-Gate Field-Effect Transistor

LS-VDS Low Side Drain-Source Voltage

LV Low Voltage

MKP Metallized Polypropylene

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NEDO New Energy and Industrial Technology Development Organization

NMI National Network for Manufacturing Innovation

OBC On-Board Charger

OEM Original Equipment Manufacturer

ORNL Oak Ridge National Laboratory

PCB Printed Circuit Board

PE Power Electronic

PHEV Plug-In Hybrid Electric Vehicle

PWM Pulse-Width Modulation

RMS Root Mean Square

Si Silicon

SiC Silicon Carbide

SMA SubMiniature A

SNR Signal-To-Noise-Ratio

TSMC Taiwan Semiconductor Manufacturing Company

TTL Transistor-Transistor Logic

UCS Union of Concerned Scientists

VDMOS Vertical Double-Diffused MOS

VE Véhicule Électrique

VTO Vehicle Technologies Office

VVMOS Vertical V-groove MOSFET

WBG Wide Bandgap

#### LIST OF SYMBOLS AND UNITS OF MEASUREMENTS

A Ampere

°C Degree Celsius

Hz Hertz

J Joule

$\Omega \hspace{1cm} Ohm$

pu Per-unit

V Volt

W Watt

Wh Watt-Hour

#### INTRODUCTION

New emerging Wide Bandgap (WBG) MOSFETs technologies are increasingly analyzed using experimental and simulation studies. Although the simulation remains generally well defined to compare MOSFET's semiconductors, the experiments generally show much less rigor in terms of methodology which can lead to large disparities in conclusions and raise a global debate for choosing among WBG semiconductors. Choosing an appropriate experimental measurement technique can be a challenging topic, and depending on the applied technique, the experimental results may significantly defer from simulation results. Tiny details such as mutual coupling can generate great influences on the results, which is why it is necessary to develop a rigorous experimental measurement methodology. This condition can be even more crucial when comparing semiconductors with different internal characteristics because experimental measurements are very sensitive to parasitic elements in power converter applications. To settle this unprecedented debate between WBG and Si MOSFETs in power converter applications, a detailed analysis by simulation and experimentation is required. Particular attention is paid to analyze the best practices in the industry and propose new effective measurement technique to minimize perturbations on the switching behavior. This thesis is organized as follows:

Chapter 1 highlights the great importance of introducing the WBG MOSFETs for power converter applications, particularly on electric mobility. This literature review presents the current state of Si, SiC, and GaN MOSFET's semiconductor on the market, the need to orient future development towards more efficient technologies, and the benefits of each technology. This also highlight the great debate between GaN, SiC, and standard Si MOSFET under PE applications.

Chapter 2 presents the chosen modeling approach based on intrinsic characteristics of MOSFET's structure as defined in the literature. Partial development of computational equations highlights the assumptions and limitations of the modeling approach while improving the modeling accuracy.

Chapter 3 defines the experimental configuration and selected Si, SiC and GaN MOSFET of similar characteristics for comparison purpose. Then, computational results based on the modeling approach of Chapter 2 gives early remarks on Si, SiC, and GaN MOSFETs in a half-bridge power converter application.

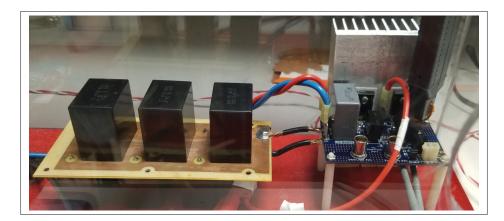

In Chapter 4, the disturbances of taking measurements in energy conversion applications is presented, outlining the importance to develop a method of carefully extracting experimental data. Then, a comparison method between MOSFETs is defined due to difference in internal characteristics between technologies. In addition, several switching current extraction methodologies are developed and analyzed. In the end, a comparative measurement methodology is defined to take experimental results between Si, SiC, and GaN MOSFETs while minimizing disturbances on measurements and the switching process.

Finally, Chapter 5 presents the interdependency of established measurements points with internal characteristics of MOSFETs. In total, experimental switching waveforms of MOSFETs are analyzed under four distinct configurations in a half-bridge hard commutation test circuit. Statistical analysis and interpretation of relative comparison highlight major trend in the switching process for Si, SiC, and GaN MOSFETs.

#### **CHAPTER 1**

### RECENT ADVANCES IN WIDE BANDGAP DEVICES FOR AUTOMOTIVE INDUSTRY

Yan Bérubé $^a$ , Amin Ghazanfari $^b$ , Handy Fortin Blanchette $^c$ , Christian Perreault $^d$ , Karim Zaghib $^e$

a, c Department of Electrical Engineering, École de Technologie Supérieure,

1100 Notre-Dame Ouest, Montréal, Québec, Canada H3C 1K3

b, d, e Center of Excellence in Transportation Electrification and Energy Storage, Hydro-Québec,

1806 Boulevard Lionel-Boulet, Varennes, Québec, Canada J3X 1S1

Paper published in *IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society*, October 2020

©2021 IEEE. Reprinted, with permission, from Y. Bérubé, A. Ghazanfari, H. F. Blanchette, C. Perreault and K. Zaghib, "Recent Advances in Wide Bandgap Devices for Automotive Industry," IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, 2020, pp. 2557-2564, doi: 10.1109/IECON43393.2020.9254478.

Currently, there is a big debate to know which Wide Bandgap (WBG) technology will dominate the power semiconductor market for power converters and electric vehicle applications. It is necessary to start with an in-depth literature review to take the pulse of this question. Also, it is essential to shed the light on the reasons for the appearance of WBG devices on the market. This paper presented in the 46<sup>th</sup> Annual Conference of the IEEE Industrial Electronics Society contains main remarks to draw a basic understanding of the state-of-the-art of WBG semiconductors, particularly for the automotive industry. A presentation of the benefits for each WBG technology, as well as an overview of the current availability of these technologies makes it possible to demonstrate the current state of the art of WBGs. Finally, challenges in design integration, actual innovations, and development partnerships on WBGs open the door to future applications and possibilities.

#### 1.1 Overview

The main barriers in the widespread adoption of electric vehicles (EVs) include limited autonomy, high upfront cost, low availability of charging infrastructure, and long charging time. Wide Bandgap (WBG) semiconductors are key industry players in the electronics circuit design because they are advantageous in terms of high operating temperature, high efficiency, low volume and weight. The WBG devices improve power density and allow power electronics (PE) circuits to reach operating points and temperatures that have not been considered before. Currently, SiC and GaN are the most viable WBG semiconductor candidates to replace Si-based devices. However, cost, packaging limitations, reliability, safety, low manufacturing, and demand level of WBGs are issues that should be addressed; the integration of these devices into the automotive power electronic (APE) systems can then successfully be realized. This paper presents an industrial oriented overview of WBG power semiconductors including their advantages, recent progress, challenges, and development partnerships.

#### 1.1.1 Introduction

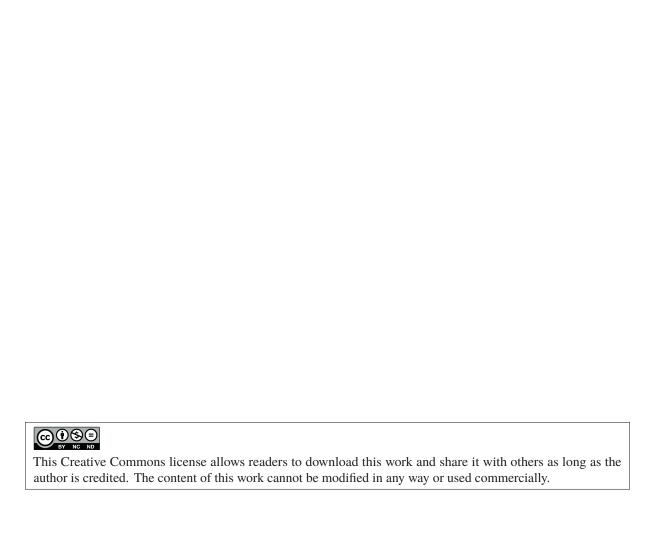

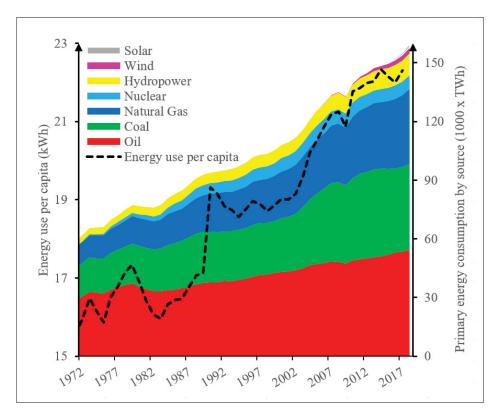

The global demand for energy continues to grow due to the economic and population growth. The worldwide primary energy consumption by sources and energy use per capita is demonstrated in Fig 1.1. The increase in GHG emissions is one of the main challenges of the growing global energy demand (Das, Marlino & Armstrong, 2018). Most governments have been actively engaged in the fight against climate change by reducing GHG emissions and oil dependence (Natural Resources Canada, 2016). Because a large proportion of GHG emissions is released by the transportation sector, transportation electrification can significantly contribute in mitigating climate change (STMicroelectronics, 2019b; Transports Québec, 2020). In 2017, the transportation sector accounted for over 29% of GHG emissions in the United States (United States Environmental Protection Agency, 2020) and 24% of the total CO<sub>2</sub> emissions globally (International Energy Agency, 2019a). Fig. 1.2 presents the percentage of CO<sub>2</sub> emissions from fuel combustion by different sectors and evolution of worldwide CO<sub>2</sub> emissions from 1990 to 2017.

Even in coal-intensive electricity generation, electric vehicles (EVs) are cleaner than the most efficient conventional internal combustion engine (ICE) vehicles (Hausfather, 2019; Hodges, 2019; Reichmuth, 2020). Moreover, because grid decarbonization occurs globally, the footprints of EVs will continue to decrease (Hausfather, 2019; Hodges, 2019; Reichmuth, 2020). According to the Union of Concerned Scientists (UCS), consumers can further decrease their footprints by opting for the most efficient EV in the market (Reichmuth, 2020). Given its benefits for the environment and energy consumption, efforts in technological designs translate into higher power density and efficiency requirements (Bartolomeo, Abbatelli, Macauda, Giovanni, Catalisano, Ryzek & Kohout, 2016). For manufacturers, these benefits can result in the use of more energy-efficient components, topologies, and energy management techniques (Bartolomeo *et al.*, 2016).

According to Bloomberg New Energy Finance (Shankleman, 2017), sales of EVs would exceed those of ICE vehicles by 2038. The limited autonomy, high cost, low availability of charging

Figure 1.1 Global annual energy consumption by source (TWh) and average annual energy use per capita (kWh)

Adapted from Ritchie & Roser (2014); International Energy Agency (2019b)

infrastructure, and long charging time are barriers in the widespread adoption of EVs, and these limitations compel car manufacturers to invest in R&D (Szymkowski, 2019). Wide Bandgap (WBG) semiconductors can improve the electrification of the transport sector because they are advantageous in terms of their operating temperatures, voltages, and maximum powers. These semiconductors can significantly increase the efficiency of electrical power systems by reducing the losses, dimensions, and weights of vehicles (Das *et al.*, 2018; Bartolomeo *et al.*, 2016; Matthews, 2019).

The objective of this study was to clarify the effect of WBG semiconductors on the automotive industry, specifically Silicon Carbide (SiC) and Gallium Nitride (GaN). This study also aimed to determine the state of WBG in the transport sector. The remainder of this paper is organized as follows. Section 1.1.2 discussed the reasons that led to the development of WBG technologies.

Figure 1.2 Percentage of global CO<sub>2</sub> emissions from fuel combustion by sectors from 1990 to 2017 (%) and annual CO<sub>2</sub> emissions from 1990 to 2017 (Giga tonnes per year)

Adapted from International Energy Agency (2019a); Ritchie & Roser (2017)

In section 1.1.3, the benefits and classification of WBG semiconductors based on intrinsic characteristics of commercially available devices, respectively, were discussed. Then, the advantages and challenges of the integration of WBG semiconductors into the automotive industry are presented in sections 1.1.4 and 1.1.5. Section 1.2 presents the industrial partnerships and prospects of WBG semiconductors. Finally, section 1.3 concludes the main remarks.

# **1.1.2** Why WBGs?

Investing in new power semiconductors is required to achieve higher efficiency. Power MOSFETs appeared approximately 30 years ago on the market. Overtime, many improvements have been achieved, and the fabrication of silicon (Si) MOSFETs is currently close to its theoretical limits

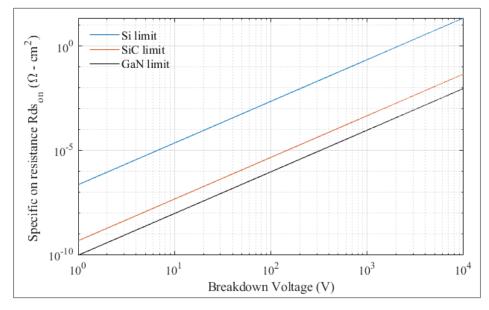

(Baliga, 2008; Lidow, Strydom, de Rooij & Reusch, 2015). The theoretical specific on-resistance of Si MOSFETs is almost attained, and the performance improvement of the Si-based IGBTs is approaching its limit. The theoretical on-resistance versus blocking voltage capability of Si and WBGs are shown in Fig 1.3 The Si semiconductors lack the capability to efficiently operate in high temperatures and high range of voltage and power. These limitations are pushing manufacturers to look for new solutions such as WBG materials (Baliga, 2008; Lidow, 2011; Lidow *et al.*, 2015; NIKKEI XTECH, 2012). Specifically, WBG semiconductors are great sources of investigation in the automotive sector to support electric mobility.

Figure 1.3 Theoretical on-state resistance versus blocking voltage capabilities of Si, SiC and GaN

Adapted from Baliga (2008); Lidow *et al.* (2015)

#### 1.1.3 Benefits of WBG semiconductors

The introduction of WBG semiconductors into the power electronics conversion topologies can significantly reduce power losses (Das *et al.*, 2018; Ghazanfari, Perreault & Zaghib, 2019). SiC and GaN are two of the most popular WBGs that offer different advantages compared to that of the standard Si technology. These advantages allow manufacturers to achieve a performance level that cannot be achieved by the Si technology. From a general overview, WBGs allow operations

at higher voltage and current while reliably withstanding high temperatures (Ghazanfari *et al.*, 2019; Charged EVs, 2017). The higher capabilities of WBG semiconductors helps to track key efficiency objectives.

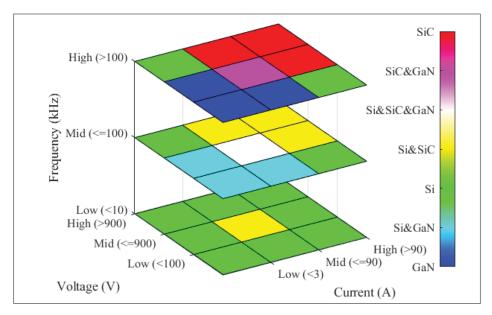

There are different expectations regarding the improved performance, reliability, efficiency, and cost of the WBG materials in all switching applications. However, the introduction of WBGs to the market does not mean the end of well-established Si semiconductors. Although WBGs are necessary to improve efficiency, each semiconductor technology has its own advantages depending on the application. A summary of typical ratings of commercially available Si and WBG semiconductors is shown in Fig. 1.4.

Figure 1.4 Summary of typical ratings of commercially available Si and WBG semiconductors

GaN has similar features with SiC such as low conduction losses, low switching losses, and high voltage carrying capacity. Similar to SiC, GaN also offers some advantages in system and design levels (Di Paolo Emilio, 2019; STMicroelectronics, 2019a). However, GaN is rarely used by manufacturers in energy conversion applications because of its lack of maturity (Matthews, 2019). Specifically, most GaNs are lateral devices on Si substrates because of their low cost and availability. Thus, large current capabilities require large area devices and result in low-voltage

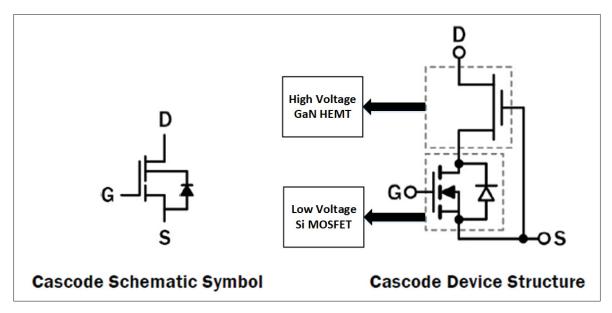

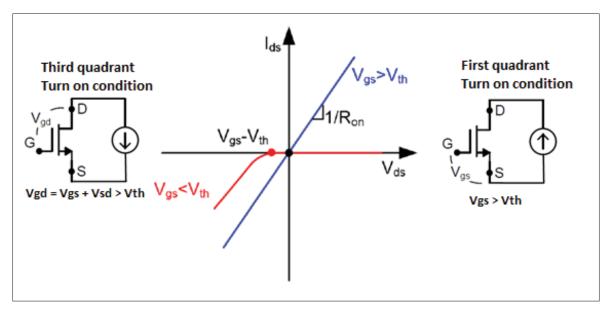

capabilities and poor thermal handling (Das et al., 2018). The vertical GaN has a theoretical potential for higher breakdown voltages, but it requires a GaN substrate which is less mature than the standard Si or SiC and is expensive (Das et al., 2018). To avoid the high cost of the GaN substrate, there has been a global effort to grow vertical GaN on Si substrates (Hu, Zhang, Sun, Piedra, Chowdhury & Palacios, 2018). However, because of the lattice constant and thermal expansion mismatches between GaN and Si, the process of vertical high-voltage GaN devices is a challenge (Hu et al., 2018). Currently, GaN is not mature enough for high-power applications because of its limited thermal and voltage handling capabilities. Nonetheless, GaN has a higher value of electron saturation velocity which gives it favorable characteristics for fast switching applications such as audio amplifiers and miniaturized switched-mode power supplies (Bartolomeo et al., 2016). The poor thermal capability and limited power of GaN make it suited for low to mid power applications at mid to high frequency. According to Wolfspeed, although GaN may not be a great fit for EV powertrain inverter applications, it is most appropriate in applications starting at approximately 40 to 600 V. The limitation comes from the way the technology was built, and it requires bigger chips to support high current, which results in a higher cost and larger package size. Accordingly, GaNs are barely available at 900 V as cascode devices (Das et al., 2018; Charged EVs, 2017).

On the other hand, the presence of SiC in the low voltage and power market is limited and does not offer competitive properties compared to that of Si and GaN devices. However, SiC have excellent thermal, voltage, power, and speed capabilities, which makes it suited for mid to high voltage, power, and frequency applications. SiC is currently more mature, which makes it the preferred WBG semiconductor for power electronic applications (Das *et al.*, 2018). According to Wolfspeed, SiC provides more efficient power conversion, and there is a growing market for it in the form of legislation, consumer demand, and energy cost (Charged EVs, 2017).

Finally, Si devices offer competitive proprieties for low frequencies, mid voltages, and power applications. Moreover, specific application requirements such as high voltage and low current or low voltage and high current are not covered by WBG semiconductors, giving exclusivity to the standard Si devices.

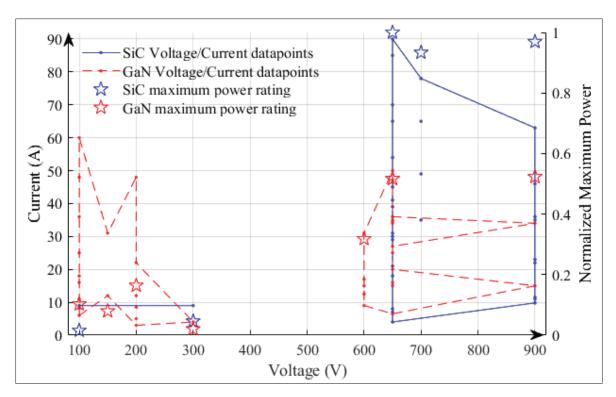

It is evident that high frequency and power applications and high frequency and low-power applications are favored by SiC and GaN devices, respectively. However, in the middle range of voltage, current, power, and frequency, the most suited technology depends on the specific requirements of the application. The ratings of the SiC and GaN devices for middle voltage and current range obtained from most distributors are shown in Fig. 1.5 (>100V to  $\leq$ 900V & >3A to  $\leq$ 90A). Because there were no WBG field-effect transistors (FETs) between 300 and 600 V, the middle range was divided into two subsections: the lower and higher voltage devices. For the lower voltage, the SiC devices have poor power and speed capabilities, making GaN dominant for that part in the middle range. However, for the 600 to 900 V, SiC offer higher voltage and twice the power capability of the GaN devices. Thus, it is evident that SiC dominates the market of the middle to high voltage, power, and frequency applications.

Figure 1.5 Ratings of commercially available SiC and GaN devices for middle voltage and current range (>100V to  $\leq$ 900V & >3A to  $\leq$ 90A) and normalized maximum power (p.u.) based on the highest power capability of the SiC device in the middle range (1 pu)

In comparison to the ratings of Si technologies, SiCs can operate at 10 times higher frequency and voltage (Das et al., 2018; STMicroelectronics, 2019b; Bartolomeo et al., 2016; STMicroelectronics, 2018; Bosch Media Service, 2019; NIKKEI XTECH, 2012; Charged EVs, 2017; Garrou, 2019; Hamblen, 2019; Huntley, 2019). This advantage reduces the size, weight, and cost of all the magnetic elements of converters, resulting in an overall reduction in the space, weight, and cost of designs (Das et al., 2018; Bartolomeo et al., 2016; NIKKEI XTECH, 2012; Charged EVs, 2017; Garrou, 2019; Huntley, 2019). Moreover, higher operating temperature (Das et al., 2018; STMicroelectronics, 2019b, 2018; NIKKEI XTECH, 2012; Ghazanfari et al., 2019; Garrou, 2019; Hamblen, 2019) (of up to 200 °C) (STMicroelectronics, 2018; NIKKEI XTECH, 2012) and better thermal conductivity (Bartolomeo et al., 2016; Huntley, 2019) can reduce the complexity of cooling systems (Das et al., 2018; NIKKEI XTECH, 2012; Garrou, 2019). This feature reduces the cost and increases durability and reliability of the systems (Els, 2018). Moreover, the smaller form factor (STMicroelectronics, 2019b, 2018; Els, 2018; Hamblen, 2019) and lower on-resistance per area (Bartolomeo et al., 2016; STMicroelectronics, 2018; Els, 2018; Bosch Media Service, 2019; Huntley, 2019; ROHM CO., LTD., 2020a) of SiC respectively reduces PCB form factor (Els, 2018) and thermal losses by up to 90% (STMicroelectronics, 2018; Bosch Media Service, 2019). These advantages result in lower conduction and switching losses by a factor of 100 (Els, 2018; Huntley, 2019). According to STMicroelectronics, the variation of the on-resistance and switching losses are approximately independent of the junction temperature (Els, 2018).

## 1.1.4 SiC as an Enabler of Transportation Electrification

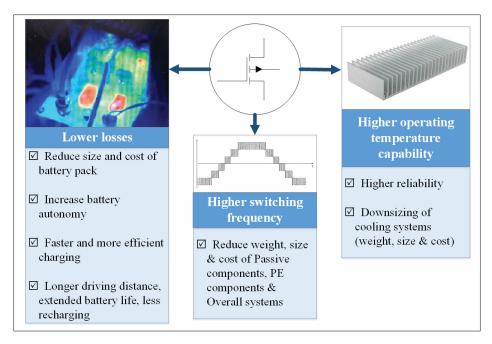

According to the Oak Ridge National Laboratory, the transportation sector can significantly benefit from the advantages of WBG; however, this potential is dependent on the future production of WBGs and its adoption by hybrid EVs (HEVs) and EV manufacturers (Das *et al.*, 2018). The innovations in EV manufacturing are strongly motivated by the need to increase autonomy and reduce energy consumption, but restrained by issues on cost and safety. SiCs can be used in the development of battery-dependent vehicles in several aspects, including the reduction of energy

losses in the conversion stages (Das *et al.*, 2018; Bartolomeo *et al.*, 2016). A summary of the main advantages of SiCs in APE systems is described in Fig. 1.6.

Figure 1.6 Main advantages of SiCs in APE systems

Practically, losses associated with EV traction inverter correspond to a small part of the total losses in the system. According to Wolfspeed, the associated loss accounts for approximately 7% of total losses (Charged EVs, 2017). The increase in the energy efficiency of SiC makes it possible to considerably reduce these losses to 2% of total losses (Charged EVs, 2017). Hence, it is possible to reduce the size and cost of the battery pack to achieve the same autonomy or increase it by up to 6% (Bosch Media Service, 2019) for the same battery pack (Bartolomeo *et al.*, 2016; STMicroelectronics, 2018; Cree, Inc., 2019a; Bosch Media Service, 2019; Charged EVs, 2017; Delphi Technologies, 2019; Chin, 2019; ROHM CO., LTD., 2020b). The lower losses mean longer driving ranges and less recharging, which allow the battery life to be extended (STMicroelectronics, 2018; Els, 2018; Charged EVs, 2017; Infineon Technologies AG, 2020). In addition to efficiency, SiCs contribute to other characteristics including favorable weight, size, reliability, and total system cost (Das *et al.*, 2018). Increasing the switching frequency, voltage, and operating temperature of converters are major factors in reducing the weight, dimension,

cost of passive and power electronics components, and overall systems of EVs (Das *et al.*, 2018; Els, 2018; The National Renewable Energy Laboratory, 2020; Charged EVs, 2017; ROHM CO., LTD., 2020a; Delphi Technologies, 2019; Chin, 2019; Council, 2015). Moreover, the higher voltage of EVs can significantly extend the vehicle range and reduce the charging time (ROHM CO., LTD., 2020a; Delphi Technologies, 2019; Infineon Technologies AG, 2020). Although a high switching frequency may negatively affect the efficiency of the converter, the operating point should be optimized to get the best compromise between the efficiency, weight, space, reliability, and total cost. These perspectives provide different design options and flexibility in EV layouts and battery sizes (Das *et al.*, 2018; Els, 2018; Delphi Technologies, 2019; Chin, 2019).

SiC material can operate at higher temperatures while keeping high reliability. This feature results in the reduction in size, weight, and cost of cooling systems, particularly through design simplification (Das *et al.*, 2018; Bartolomeo *et al.*, 2016; Els, 2018; Charged EVs, 2017; Council, 2015). This advantage could be beneficial to EVs through systems combination. For example, (Das *et al.*, 2018) and (Council, 2015) explained that it is possible in HEV and plug-in hybrid electric vehicle (PHEV) applications to combine the inverter and ICE cooling systems. Thus, the higher operating temperature of SiCs can reduce the traction system size and weight; however, this is not ready to be implemented because other power electronics components should also be accommodated to the higher temperature (Das *et al.*, 2018).

Altogether, the performance characteristics of SiCs is favorable for designing compact, high-power, fast, and efficient power converters such as battery chargers and inverters (STMicroelectronics, 2018; Cree, Inc., 2019a; Charged EVs, 2017; Huntley, 2019; Delphi Technologies, 2019; Chin, 2019; Infineon Technologies AG, 2020). The commercialization of SiC with enhanced performance, robustness, and reliability accelerates the transportation electrification (STMicroelectronics, 2018; Els, 2018; Cree, Inc., 2019a).

# 1.1.5 Challenges of WBGs integration

The main challenges of the automotive industry are reflected in the power electronics manufacturing industry. The original equipment manufacturers (OEMs) have been trying to meet the needs of the consumers and be as competitive as possible on the market. This competitiveness refers to the demand for higher efficiency and reduction in weight and volume of EV systems to increase the mileage range (Bartolomeo *et al.*, 2016). There are major changes in the design of the automotive industry to meet objectives and expectations of the consumers. Increasing the design voltages up to 1200 V, targeting the power to hundreds of kilowatts, opting for a high-temperature environment as well as enormous thermal cycling constraints, integrating complex mechatronic systems, and designing new cooling techniques and functional safety boundaries are some of the recent changes in the industry (Bartolomeo *et al.*, 2016). More importantly, it is essential to maintain an affordable cost. To keep up with all these developments, WBG power semiconductors have been investigated.

Although energy losses are lower for WBGs, using the higher form factor of SiC to increase power density with a smaller die size at a lower cost results in greater heat fluxes, higher temperatures, and higher thermal gradients in PE systems (Moreno, 2017). Thus, other components such as passive elements and soldering can potentially exceed their limits because they are exposed to a higher temperature. Therefore, there are some challenges in the thermal management and cooling systems to maintain a high level of reliability (Moreno, 2017). Excessive temperature degrades performance, lifetime, and reliability of power electronic components (MIL-217, 1991). Thus, advanced thermal management technologies are required to keep the temperature below acceptable limits, while maintaining increased power density and reduced costs related to materials, configurations, and systems. On a larger scale, advanced thermal techniques ensure reliability, increase lifespan, and can be used to develop predictive lifespan models (Narumanchi, 2017).

The high cost of WBG semiconductors is a challenge for APE manufacturers (Das *et al.*, 2018; STMicroelectronics, 2018; Charged EVs, 2017; Council, 2015; National Renewable Energy

Laboratory, 2019). In the following years, SiCs will remain more expensive than the traditional Si technology, which will slow down its adoption on a larger scale (Charged EVs, 2017; National Renewable Energy Laboratory, 2019). This is partly due to the higher cost of raw materials and difficulty of manufacturing substrates (STMicroelectronics, 2018; Charged EVs, 2017). Some new manufacturing methods result in cost reduction and consequently promote the production of WBG devices. This trend creates numerous transformations in industries that rely on high-voltage systems such as power converters (STMicroelectronics, 2018). Different power applications could benefit from the increase in efficiency from WBGs to achieve reduced costs at the system (Charged EVs, 2017). However, this cost reduction at the system level may not always be enough to address the high cost of WBG semiconductors (Das *et al.*, 2018).

The availability of WBGs is another issue caused by the low manufacturing and increased demand levels (Das *et al.*, 2018). The higher demand of SiC semiconductors resulted in the global shortage of wafers supply, which is a major challenge for both the APE and PE industries (Shao, 2019).

Reliability and safety are the major concerns of APE manufacturers. The failure of the PE systems of a vehicle could have a major impact on the safety and performance of EVs (Das et al., 2018). WBGs have not yet been proved to be reliable at the level demanded by the industry (Das et al., 2018). The lack of maturity of WBGs evidently impacts their reliability. Moreover, their cost limits their market penetration (Das et al., 2018; Els, 2018). Although some WBGs have passed automotive reliability testing for semiconductors, it is known by automotive manufacturers that WBGs can fail differently from conventional Si devices (Das et al., 2018). Thus, the reliability tests of standard Si may not be suitable for WBGs. Specifically, JEDEC, a leading developer of microelectronic standards, is currently working on developing WBG standards for Power Electronic Conversion under the JC-70 Committee (Das et al., 2018; Els, 2018; JEDEC, 2020a). Currently, only the dynamic on-resistance test method guidelines and switching reliability evaluation procedures for GaN is available on the JEDEC website. In the automotive industry, tests are rigorous and undergo a long design cycle, but the validation of the final reliability is based on hours of reliable operation (Charged EVs, 2017). Hence, quality

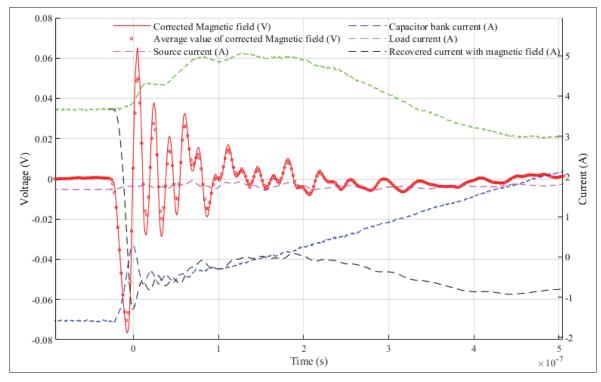

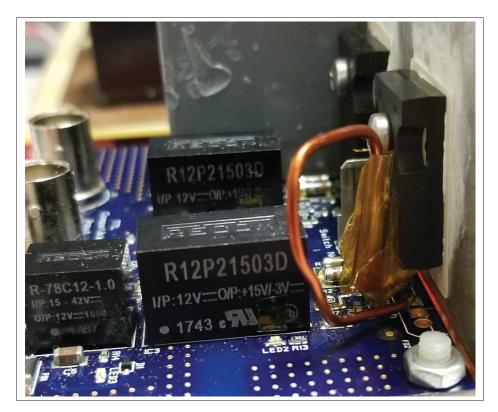

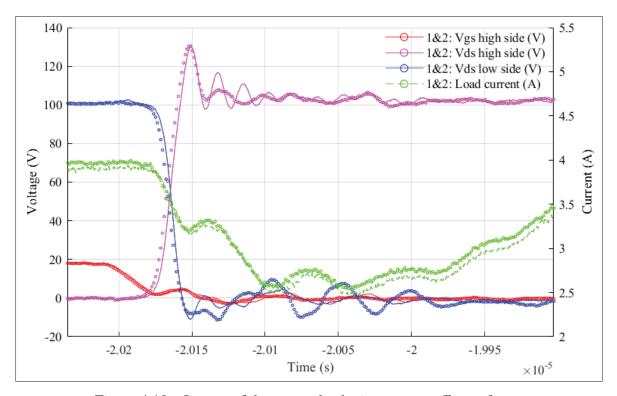

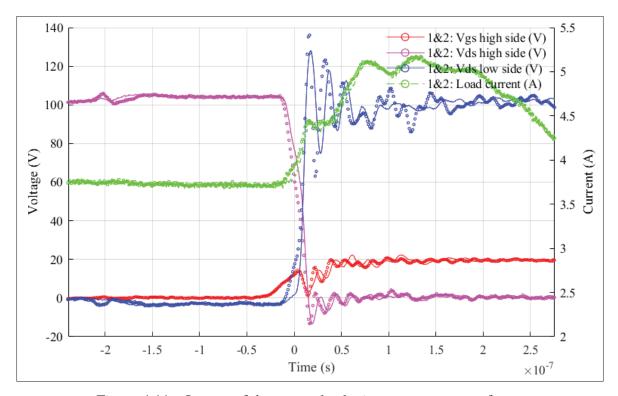

and reliability must be impeccable to meet the needs of the automotive industry (Charged EVs, 2017).