# Design and Implementation of Chaos-based Random Number Generators for IoT Platforms

by

## Ngoc NGUYEN THI THU

MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, 03 FEBRUARY 2022

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

#### THIS THESIS HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS

M. Georges Kaddoum, Thesis Supervisor Departement of Electrical Engineering, École de technologie supérieure

M. Pascal Giard, Thesis Co-Supervisor Departement of Electrical Engineering, École de technologie supérieure

M. Chamseddine Talhi, Chair, Board of Examiners Department of Software Engineering and Information Technologies, École de technologie supérieure

M. Ghyslain Gagnon, Member of the Jury Departement of Electrical Engineering, École de technologie supérieure

M. Christophe Guyeux, External Examiner Femto-ST Institute, Université de Bourgogne Franche-Comté, France

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON 20 JANUARY 2022

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **FOREWORD**

This dissertation is mainly based on research outcomes, which have been accomplished under the supervision of Dr. Georges Kaddoum and Dr. Pascal Giard between May 2017 and May 2021. This work has been partly supported by the FRQNT and NSERC Ph.D. fellowships, and the Schlumberger Foundation for the Faculty for the Future (FFTF). This dissertation is subjective to address the hardware design of random number generator for multiple platforms. Resultantly, my Ph.D. study successfully ended with 3 journal papers published, and 1 journal paper submitted as the first author, and 2 conference papers. Apart from the first two chapters, where the background of random number generators is intensively introduced, the remaining chapters are based on my journal papers. For those chapters, I did a comprehensive literature review, proposed a chaotic system design, mathematically analyzed and simulated the dynamical and chaotic characteristics. Then, the hardware design for the proposed system was provided. After the presentation of those chapters, chapter 7 concludes the thesis and lists several future research directions.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to gratefully acknowledge and express my sincere thanks to my supervisor Dr. Georges Kaddoum for his considerate guidance, valuable inspiration, constructive suggestions, and consistent encouragement throughout my four years research study. This thesis would not have come to the completion without his dedicated mentorship and scholarly inputs.

Besides my supervisor, I am also appreciative to Dr. Pascal Giard, who is my co-supervisor, for his immense knowledge, technical meetings and discussions. Similar profound gratitude also goes to Dr. François Gagnon, who is my formal co-supervisor, for his encouragement and guidance from the beginning of my Ph.D. journey. I also gratefully thank Professor Chamsedine Talhi, Professor Ghyslain Gagnon, and Professor Christophe Guyeux, for their agreement to serve as my jury members. Each of the members of my Dissertation Committee has provided me extensive personal and professional guidance and taught me a great deal about both scientific research and life in general. Also, a special mention and thanks goes to the Schlumberger Foundation for their financial support during my Ph.D. study.

I am grateful to all of those with whom I have had the pleasure to work during this and other related projects. Many thanks also goes to my friends for their help and encouragement to embrace my research problems with high enthusiasm. I do hereby acknowledge all my colleagues from LACIME group, including Vu, Dat, Khaled, Bassant, Victor, Dawa, Zeeshan, Elli, Hamza, Long, Jung, Michael, Marwan, etc., and my ETS friends including Sahar, Nakisha, Benaf She, Nam, Ha, Dung, Dai.

Nobody has been more patient in the pursuit of this journey than the members of my family. I would like to thank my loving and supportive husband, Toan Bui who always provides me encouragement, unconditional support, and love, and my two beautiful daughters Thao Nguyen and Alyssa, who sacrificed a lot and provided unending inspiration.

Last but not the least, I would like to wholeheartedly thank my mother and my mother-in-law for their continued patience, unconditional support, and warm love. They are sacrifying their freedom and giving up the life of ease to take care of my daughters. I owe them an appology since I gave them a burden instead of being beside and taking care of them during the hardest time of life. I feel sorry for my departed father and father-in-law who cannot share this moment with us, although I believe they would have been proud of me and given me their total support. Also, my special thanks and appreciation goes to my brothers and sisters for their spiritually invaluable love and support to my studies and life.

# Conception et mise en œuvre de générateurs de nombres aléatoires basés sur le chaos pour plates-formes IoT

## Ngoc NGUYEN THI THU

## **RÉSUMÉ**

Pour les communications futures, la sécurité est l'un des principaux défis. Dans ce contexte, le générateur de nombres aléatoires, qui est chargé de générer des clés publiques, des clés privées et d'autres types de nombres aléatoires, est un moteur essentiel des algorithmes cryptographiques et du secret des données. Les algorithmes cryptographiques nécessitent des capacités de calcul élevées et une puissance élevée, ce qui est un défi dans les appareils limité en ressources. Par conséquent, le générateur de nombres aléatoires matériel, qui fournit un débit élevé à faible puissance, est un composant essentiel pour les futurs appareils. De nombreuses approches ont été développées pour améliorer le caractère aléatoire et la sécurité des générateurs de nombres aléatoires utilisés sur des dispositifs limité en ressources. Cependant, les générateurs de nombres aléatoires matériel actuels ont été confrontés à des défis de conception, tels que l'efficacité énergétique (qui est l'énergie consommée pour générer un seul bit aléatoire), la sécurité et la flexibilité. Pour relever ces défis, des générateurs de nombres aléatoires basés sur le chaos sont apparus dans lesquels les systèmes chaotiques non linéaires jouent un rôle clé.

Pour les générateurs de nombres aléatoires basés sur le chaos, les caractéristiques chaotiques et dynamiques sont cruciales. Plus la complexité et la dynamique du système chaotique sont élevées, plus le caractère aléatoire des bits de sortie est élevé; cependant, le caractère aléatoire des bits de sortie dépend également d'autres facteurs, tels que l'implémentation et le post-traitement des données. Récemment, la communauté des chercheurs s'est particulièrement intéressée aux systèmes chaotiques continus. Par conséquent, cette recherche se concentre sur le développement de nouveaux systèmes chaotiques continus, hautement dynamiques et hautement dimensionnels des données, afin d'améliorer la sécurité et le débit des générateurs de nombres aléatoires proposés.

Les contributions de cette thèse sont quadruples: (i) le développement de systèmes chaotiques robustes et l'analyse des caractéristiques dynamiques pour trouver les meilleurs paramètres (ii) l'implémentation matérielle en tenant compte des applications cibles et des plates-formes d'appareils; (iii) la proposition d'applications techniques utilisant les générateurs de nombres aléatoires proposés; (iv) la conception et la fabrication de véritables générateurs de nombres aléatoires et de générateurs de nombres pseudo-aléatoires pour fournir des dispositifs de sécurité prêts à l'emploi pouvant être utilisés comme produits commerciaux.

Tout d'abord, nous développons plusieurs systèmes chaotiques qui se concentrent sur l'extension des dimensions (ce qui peut améliorer le débit global des générateurs de nombres aléatoires), et sur l'amélioration du niveau de sensibilité du système en masquant les informations des points d'équilibre et en faisant dépendre les caractéristiques du système des conditions initiales difficiles à prévoir. L'analyse mathématique montre les avantages des systèmes chaotiques proposés par rapport aux systèmes précédents. Dans la mise en œuvre matérielle, la consommation d'énergie,

les ressources de l'appareil et le niveau de sécurité sont des compromis. Par conséquent, les systèmes chaotiques avec une conception matérielle peu complexe sont prioritaires.

En ce qui concerne la mise en œuvre matérielle, nous présentons deux stratégies différentes pour les véritables générateurs de nombres aléatoires et les générateurs de nombres pseudo-aléatoires. La conception de circuits analogiques est utilisée pour mettre en œuvre un véritable générateur de nombres aléatoires, dans lequel le bruit du circuit et l'imperfection du circuit affectent les caractéristiques chaotiques. Les générateurs de nombres pseudo-aléatoires sont implémentés dans des dispositifs FPGA qui peuvent être intégrés dans plusieurs plates-formes matérielles.

Avec les plates-formes IoT, les développeurs peuvent créer une large gamme d'applications spécifiquement à des fins IoT, telles que la surveillance et la surveillance en temps réel, dans lesquelles le secret des données est important. Pour prouver les avantages de l'utilisation des générateurs de nombres aléatoires désignés dans les applications, nous fournissons un cryptage / décryptage d'image à l'aide d'un encodage de données de pad à usage unique. Par conséquent, un cryptosystème de pas à usage unique basé sur le chaos est développé, les données (images) sont codées à l'aide du générateur de nombres aléatoires basé sur le chaos proposé. Le récepteur et l'émetteur partagent des informations sur l'état initial du système chaotique pour récupérer la clé et décoder les données.

Enfin, après près de quatre ans de recherche sur les générateurs de nombres aléatoires avec les réalisations que nous avons obtenues jusqu'à présent, il est possible de commencer à commercialiser notre projet de recherche. Reconnaissant la demande croissante de sécurité personnelle, notre produit vise à donner aux utilisateurs le contrôle le plus élevé sur leurs données en leur fournissant le générateur de clés. Par conséquent, les données stockées ne peuvent pas être décodées même si l'hôte (où les données sont stockées / réservées) est attaqué. De plus, notre produit vise à fournir des solutions d'encodage / décodage de données à haute vitesse pour des applications en temps réel telles que la diffusion en continu de vidéo, en particulier pendant la quarantaine de la pandémie mondiale COVID-19.

**Mots-clés:** générateur de nombres aléatoires, système chaotique, carte chaotique, hyperchaos, système chaotique continu, sécurité, cryptographie, prochaine génération de réseau.

## Design and Implementation of Chaos-based Random Number Generators for IoT Platforms

## Ngoc NGUYEN THI THU

#### **ABSTRACT**

For future network communication, security is one of the main challenges. In this context, the random number generator, which is responsible for generating public keys, private keys, and other kinds of random numbers, is a critical engine in cryptographic algorithms and data secrecy. Cryptographic algorithms require high computational capabilities and high power, which can be challenging in hardware-constrained devices. Therefore, the hardware-based random number generator, which provides high throughput at low power, is an essential component for future devices. Many approaches have been developed to enhance the randomness and security of random number generators used in constrained devices. However, current hardware-based random number generators have been facing design challenges, such as energy efficiency (which is the energy consumed to generate one single random bit), security, and flexibility. To address these challenges, chaos-based random number generators, in which non-linear chaotic systems are playing a key role, have emerged.

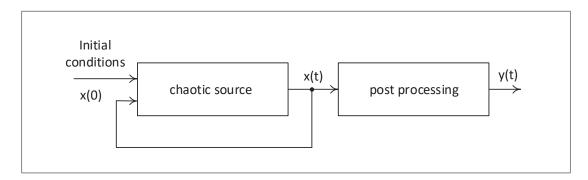

For chaos-based random number generators, the chaotic and dynamical characteristics are crucial. The higher the complexity and dynamics of the chaotic system, the higher the randomness of the output bits; however, the randomness of the output bits also depends on other factors, such as the implementation and data post-processing. Recently, considerable attention has been drawn by the research community to continuous chaotic systems. Therefore, this research focuses on developing novel continuous chaotic systems, which are highly dynamic and highly data dimensional, to improve the security and throughput of the proposed random number generators.

The contributions of this dissertation are fourfold: (i) development of robust chaotic systems and dynamic characteristics analysis to find the best parameter set (ii) hardware implementation in consideration of the target applications and device platforms; (iii) proposition of engineering applications using the proposed random number generators; and (iv) design and fabrication of true random number generators and pseudo-random number generators to provide ready-to-use security devices that can be used as commercial products.

First of all, we develop several chaotic systems which focus on extending dimensions (which can improve the overall throughput of random number generators), improving system sensitivity level by hiding information of equilibrium points and making the system's characteristics depend on the initial conditions which are difficult to predict. Mathematical analysis shows the advantages of the proposed chaotic systems compared to previous systems. In hardware implementation, the power consumption, device resources, and security level are tradeoffs. In chaotic system, non-linear function is the main component. Therefore, the non-linear functions, which have low complexity hardware design, are prioritized.

Regarding hardware implementation, we present two different strategies for true random number generators and pseudo-random number generators. Analog circuit design is employed to implement true random number generator, in which the circuit noise and circuit imperfection affect the chaotic characteristics. The pseudo-random number generators are implemented in FPGA devices which can be integrated into multiple hardware platforms.

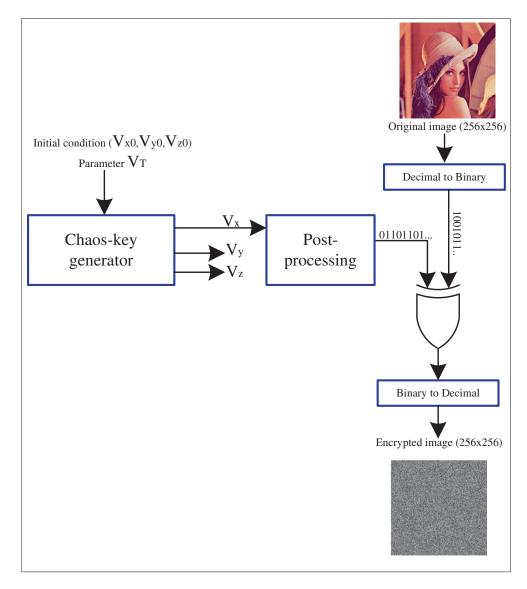

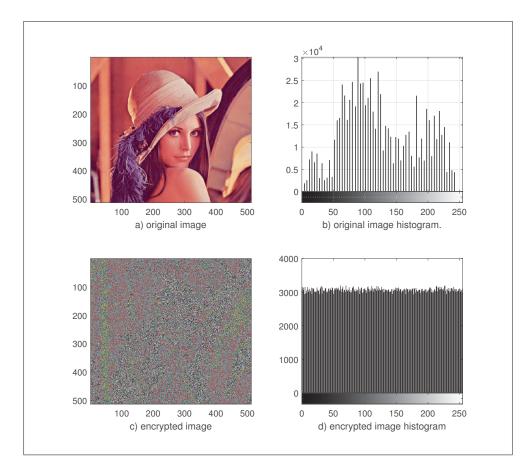

With IoT platforms, developers can build a wide range of applications, such as real-time monitoring, surveillance, in which data secrecy matters. To prove the benefits of using the designated random number generators in these applications, we provide image encryption/decryption using one-time pad data encoding. Therefore, a chaos-based one-time pad cryptosystem is developed, the data (images) is encoded using the proposed chaos-based random number generator. The receiver and transmitter share information on the initial condition of the chaotic system to recover the key and decode the data.

Finally, after nearly four years of research on random number generators with the achievements we have been getting so far, it is possible to start commercializing our research project. Acknowledging the increasing demand for personal security, our product aims to give users the highest control over their data by providing them with the key generator. Therefore, stored data cannot be decoded even if the host (where the data is stored/reserved) is attacked. Moreover, our product aims to provide high-speed data encoding/decoding solutions for real-time applications such as video streaming, especially during the quarantine of the worldwide pandemic COVID-19.

**Keywords:** random number generator, chaotic system, chaotic map, hyperchaos, continuous chaotic system, security, cryptography, next generation network.

## **TABLE OF CONTENTS**

|      |        |             |                                          | Page |

|------|--------|-------------|------------------------------------------|------|

| INTR | ODUCTI | ON          |                                          | 1    |

| CHAI | PTER 1 | BACKGI      | ROUND AND LITERATURE REVIEW              | 15   |

| 1.1  |        |             | NGs                                      |      |

|      | 1.1.1  |             | ture of conventional RNGs                |      |

|      |        | 1.1.1.1     | Physical entropy source                  |      |

|      |        | 1.1.1.2     | Harvester                                |      |

|      |        | 1.1.1.3     | Data post-processing                     |      |

|      | 1.1.2  | Architec    | ture of chaos-based RNG                  |      |

|      |        | 1.1.2.1     | Random chaotic source                    | 23   |

|      |        | 1.1.2.2     | Data post-processing                     | 23   |

| 1.2  | Backgr | ound on dy  | namical system                           |      |

|      | 1.2.1  |             | ation of dynamical systems               |      |

|      |        | 1.2.1.1     | Iterated maps                            |      |

|      |        | 1.2.1.2     | Differential equations                   |      |

|      | 1.2.2  | Equilibri   | um points and system stability           | 25   |

|      | 1.2.3  |             | v exponents and dynamic characteristics  |      |

|      | 1.2.4  |             | ace orbits                               |      |

|      |        | 1.2.4.1     | Periodic orbits                          | 27   |

|      |        | 1.2.4.2     | Chaotic orbits                           | 27   |

|      | 1.2.5  | Bifurcati   | on diagram                               | 28   |

|      | 1.2.6  | Poincare    | map                                      | 28   |

|      | 1.2.7  | Solving of  | differential equations on computer       | 28   |

|      |        | 1.2.7.1     | Euler method                             | 29   |

|      |        | 1.2.7.2     | Fourth-order Runge Kutta algorithm       |      |

| 1.3  | Chaos- | based RNC   | Ss in the literature                     | 30   |

|      | 1.3.1  | RNGs ba     | ased on chaotic maps                     | 30   |

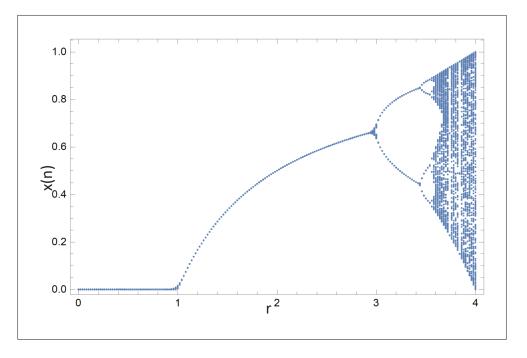

|      |        | 1.3.1.1     | Logistic map                             | 31   |

|      |        | 1.3.1.2     | N-Bernouli map                           | 32   |

|      |        | 1.3.1.3     | Tent and zigzag maps                     | 35   |

|      |        | 1.3.1.4     | Recent research in extended chaotic maps | 36   |

|      | 1.3.2  | RNG bas     | sed on continuous chaotic systems        | 37   |

|      |        | 1.3.2.1     | 3D chaotic systems                       | 37   |

|      |        | 1.3.2.2     | Recent research on 3D chaotic systems    | 39   |

|      |        | 1.3.2.3     | Hyperchaotic-based RNG                   | 40   |

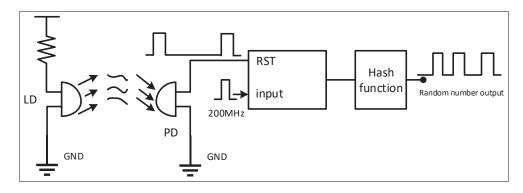

|      | 1.3.3  | RNG bas     | sed on chaos laser semiconductor         | 40   |

|      | 1.3.4  | Discussion  | on                                       | 43   |

| 1.4  | Randor | nness evalı | nation                                   | 45   |

|      | 1.4.1  | Entropy     |                                          | 45   |

|      | 1 / 2  | Correlati   | on                                       | 16   |

|            | 1.4.3   | Histogram and d    | listribution                         | 46 |

|------------|---------|--------------------|--------------------------------------|----|

|            | 1.4.4   | Randomness tes     | t suites                             | 47 |

|            |         | 1.4.4.1 NIST       | tests                                | 47 |

|            |         | 1.4.4.2 TestU      | 01 tests                             | 47 |

| СНА        | PTER 2  | RESEARCH AF        | PPROACH METHODOLOGY                  | 49 |

| 2.1        | Hierarc | ny of research met | thodology                            | 49 |

| 2.2        |         |                    |                                      |    |

| 2.3        | •       | · ·                |                                      |    |

|            | 2.3.1   |                    |                                      |    |

|            | 2.3.2   | Xilinx Design S    | uite                                 | 52 |

|            |         | 2.3.2.1 Xilinx     | x System Generator                   | 52 |

|            |         |                    | x Vivado Design Suite                |    |

| 2.4        | Fabrica |                    |                                      |    |

| 2.5        |         |                    |                                      |    |

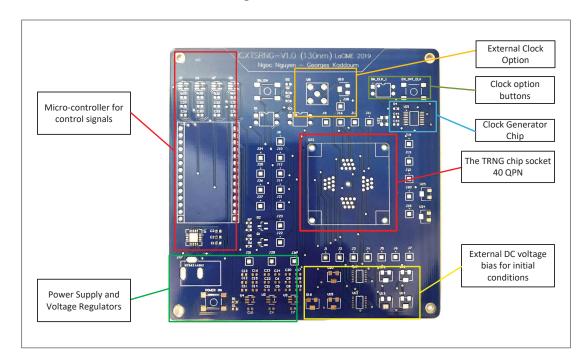

|            | 2.5.1   | Testboard for TR   | RNG chip                             | 54 |

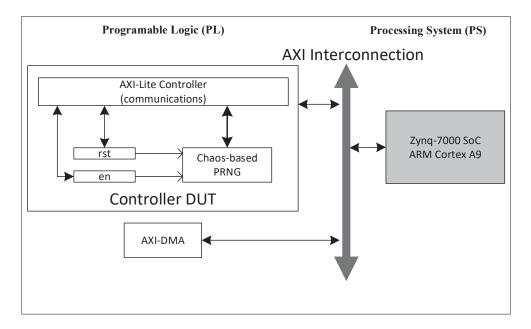

|            | 2.5.2   |                    | eation for chaos-based PRNG          |    |

| СНА        | PTER 3  | A LOW POWER        | R CIRCUIT DESIGN FOR CHAOS-KEY BASED |    |

|            |         |                    | PTION                                | 57 |

| 3.1        | Abstrac |                    |                                      |    |

| 3.2        |         |                    |                                      |    |

| 3.3        |         |                    | chaotic system                       |    |

|            | 3.3.1   |                    | otic system                          |    |

|            | 3.3.2   |                    | nalysis                              |    |

|            | 3.3.3   |                    | libium points                        |    |

| 3.4        |         | • 1                |                                      |    |

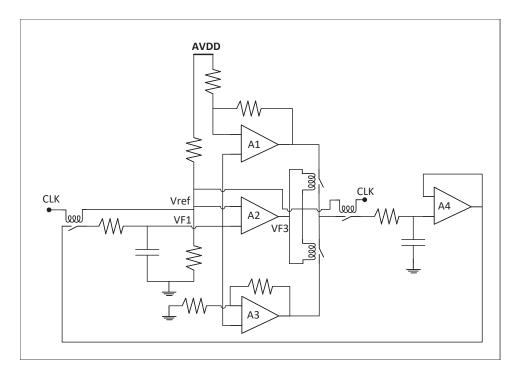

|            | 3.4.1   | -                  | lesign                               |    |

|            | 3.4.2   |                    | circuit design                       |    |

|            |         | 1 0                | parator                              |    |

|            |         |                    | T-XOR based post-processing circuit  |    |

| 3.5        | Randor  |                    |                                      |    |

| 3.6        |         |                    | Pad Cryptosystem                     |    |

|            | 3.6.1   |                    | sis                                  |    |

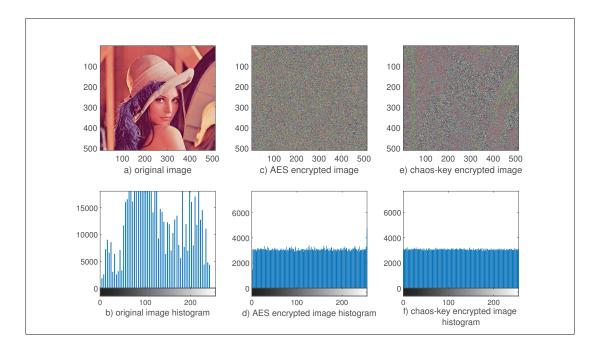

|            |         |                    | gram analysis                        |    |

|            |         |                    | e entropy, UACI and NPCR evaluation  |    |

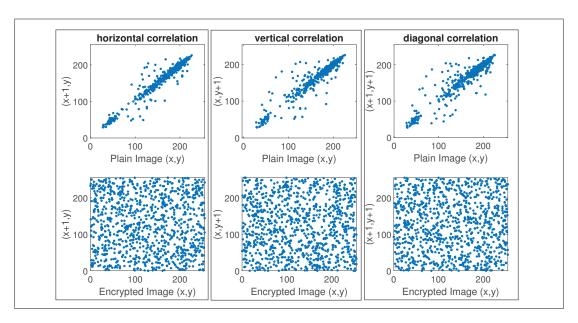

|            |         |                    | elation test                         |    |

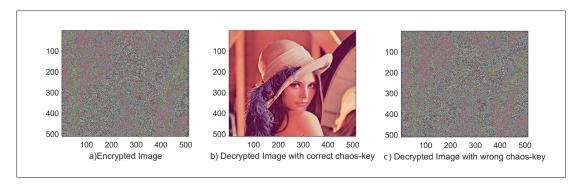

|            | 3.6.2   |                    |                                      |    |

|            | 3.6.3   | • •                |                                      |    |

| 3.7        |         | •                  |                                      |    |

| СНА        | PTER 4  | A FULLY CMC        | OS TRUE RANDOM NUMBER GENERATOR      |    |

|            |         |                    | DDEN ATTRACTOR HYPERCHAOTIC SYSTEM.  | 85 |

| <i>4</i> 1 | Abstrac |                    |                                      | 85 |

| 4.2  | Introdu  | ction                                        | 86  |

|------|----------|----------------------------------------------|-----|

|      | 4.2.1    | Motivations and contributions                | 88  |

| 4.3  | System   | design and mathematical analysis             | 90  |

|      | 4.3.1    | The proposed hyper-chaotic system            | 90  |

|      | 4.3.2    | Stability analysis of line equilibria        | 93  |

| 4.4  | Circuit  | implementation                               | 96  |

|      | 4.4.1    | Hyperchaotic circuit design                  |     |

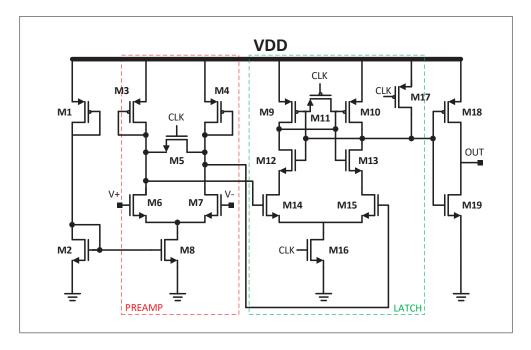

|      | 4.4.2    | Comparator                                   | 105 |

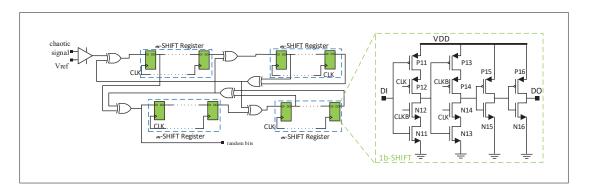

|      | 4.4.3    | SHIFT-XOR based post-processing              |     |

| 4.5  | Perforn  | nance evaluation                             |     |

|      | 4.5.1    | Power consumption                            |     |

|      | 4.5.2    | Randomness evaluation                        |     |

|      |          | 4.5.2.1 Min-entropy estimation               | 109 |

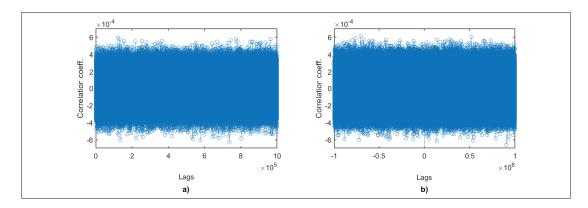

|      |          | 4.5.2.2 Correlation tests                    |     |

|      |          | 4.5.2.3 NIST's test results                  | 111 |

| 4.6  | Conclu   | sion                                         | 113 |

|      |          |                                              |     |

| CHAI | PTER 5   | PSEUDO-RANDOM BIT GENERATOR BASED ON A NOVEL |     |

|      |          | 5D-HYPERCHAOTIC SYSTEM                       | 115 |

| 5.1  | Abstrac  | t                                            | 115 |

| 5.2  | Introdu  | ction                                        | 116 |

| 5.3  | Related  | works                                        | 117 |

| 5.4  | 5D diffe | erential chaotic system model                | 119 |

|      | 5.4.1    | Mathematical analysis                        | 119 |

|      | 5.4.2    | Stability of equilibria                      |     |

|      | 5.4.3    | Transitions to chaotic region                | 122 |

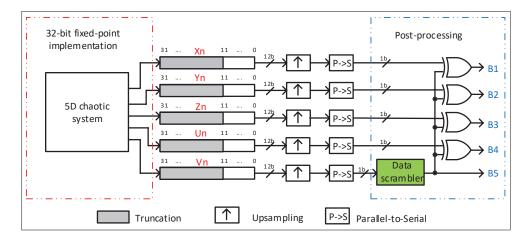

| 5.5  | Pseudo   | -random number generator scheme              | 124 |

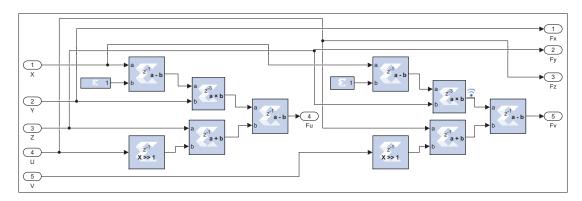

|      | 5.5.1    | Implementation of the 5D hyperchaotic system | 125 |

|      | 5.5.2    | Data post-processing implementation          |     |

| 5.6  | Experir  | mental results                               |     |

|      | 5.6.1    | Experimental setup                           | 129 |

|      | 5.6.2    | Comparison and discussion                    |     |

| 5.7  |          | nness performance evaluation                 |     |

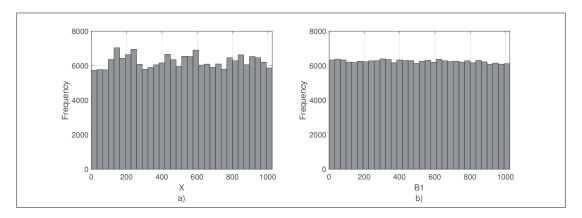

|      | 5.7.1    | Histogram                                    | 133 |

|      | 5.7.2    | Standard statistical random testsuites       |     |

|      | 5.7.3    | TestU01 test                                 |     |

| 5.8  | Conclu   | sion                                         |     |

|      |          |                                              |     |

| CHAI | PTER 6   | CONTINUOUS-CHAOS-BASED PSEUDO RANDOM NUMBER  |     |

|      |          | GENERATOR FOR HARDWARE CONSTRAINED DEVICES   | 139 |

| 6.1  | Abstrac  | et                                           | 139 |

| 6.2  | Introdu  | ction                                        | 139 |

| 6.3  | Related  | works                                        | 14  |

| 6.4  | Four-di  | mensional hyperchaotic system                | 143 |

|      | 6.4.1  | Bifurcation diagram               | 144 |

|------|--------|-----------------------------------|-----|

|      | 6.4.2  | Dynamic characteristics           |     |

|      | 6.4.3  | Transitions to chaotic region     | 148 |

| 6.5  | Hardw  | are implementation                |     |

|      | 6.5.1  | Four-dimensional chaotic system   | 149 |

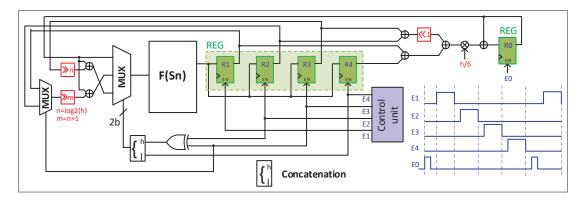

|      | 6.5.2  | Data post-processing              |     |

|      | 6.5.3  | Implementation Results            | 153 |

| 6.6  | Rando  | mness performance evaluation      | 154 |

|      | 6.6.1  | Distribution                      | 155 |

|      | 6.6.2  | Correlation test                  | 157 |

|      |        | 6.6.2.1 NIST SP800-22 test        | 158 |

|      | 6.6.3  | TestU01 test                      | 158 |

|      | 6.6.4  | Image encryption test             | 159 |

| 6.7  | Conclu | ision                             | 160 |

| CON  | CLUSIO | N AND RECOMMENDATIONS             | 163 |

| 7.1  | Conclu | ısion                             | 163 |

| 7.2  | Future | works                             | 165 |

|      | 7.2.1  | Fractional-order chaotic systems  | 165 |

|      | 7.2.2  | Development of IoT secure devices | 166 |

| BIBL | JOGRAP | PHY                               | 168 |

## LIST OF TABLES

| Page |                                                                                           |           |

|------|-------------------------------------------------------------------------------------------|-----------|

| 5    | List of existing network protocols                                                        | Table 0.1 |

| 18   | List of existing physical entropy true random number generators                           | Table 1.1 |

| 62   | Lyapunov exponents comparison                                                             | Table 3.1 |

| 74   | Summary of comparison with previous designs                                               | Table 3.2 |

| 78   | NIST test result of final output bit stream                                               | Table 3.3 |

| 82   | Image entropy, NPCR, and UACI test results for image encryption                           | Table 3.4 |

| 82   | Correlation coefficients of two adjacent pixels in two images                             | Table 3.5 |

| 92   | Lyapunov exponents comparison                                                             | Table 4.1 |

| 94   | Stability of equilibria with different initial conditions                                 | Table 4.2 |

| 109  | Power consumption summary                                                                 | Table 4.3 |

| 110  | Entropy per bit estimation of the raw binary sequences                                    | Table 4.4 |

| 112  | Statistical test results of the output bitstreams after post-processing                   | Table 4.5 |

| 113  | Comparison of modern TRNGs implemented in various entropy sources                         | Table 4.6 |

| 133  | FPGA resource comparison for various implementations of continuous chaos-based PRNGs      | Table 5.1 |

| 136  | Results of NIST SP800-22 for the proposed PRNG, $N = 10^3$ sequences of the length of 1Mb | Table 5.2 |

| 136  | Diehard tests for the proposed PRNG, sequence of 5M bits                                  | Table 5.3 |

| 137  | Battery test results for 2 <sup>25</sup> output binary bits                               | Table 5.4 |

| 147  | Comparison of different 4D hyperchaotic systems                                           | Table 6.1 |

| 155  | Comparison in device utilization of existing chaos-based PRNGs and the proposed PRNG      | Table 6.2 |

| Table 6.3 | Results of NIST SP800-22 for the proposed PRNG for streams of 10Mb                      | 159 |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Table 6.4 | TestU01 statistical test results on the sample of 2 <sup>25</sup> generated random bits | 159 |

| Table 6.5 | Image entropy, NPCR, and UACI test results for image encryption                         | 161 |

## LIST OF FIGURES

|             | Page                                                                                           |

|-------------|------------------------------------------------------------------------------------------------|

| Figure 0.1  | Cellular IoT use cases                                                                         |

| Figure 0.2  | Elements of IoT security architecture                                                          |

| Figure 0.3  | Block diagram of secure element for secured transactions                                       |

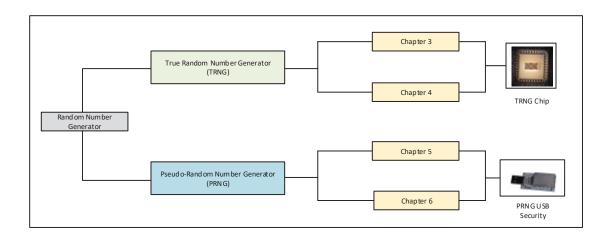

| Figure 0.4  | Paradigm of the thesis's contributions                                                         |

| Figure 1.1  | Conventional architecture for the hardware implementation of a) PRNG and b) TRNG               |

| Figure 1.2  | Jitter noise harvesting circuit implementation                                                 |

| Figure 1.3  | Simulation results of the thermal noise circuit                                                |

| Figure 1.4  | Thermal noise harvesting circuit                                                               |

| Figure 1.5  | Metastability to generating random bits                                                        |

| Figure 1.6  | Conceptual architecture of chaos-based RNG                                                     |

| Figure 1.7  | Logistic bifurcation diagram with $r \rightarrow [0, 4]$                                       |

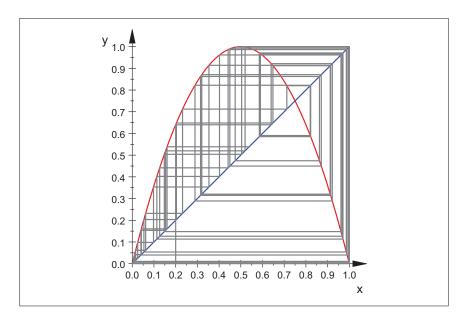

| Figure 1.8  | Chaotic behavior of logistic map for $r = 4$                                                   |

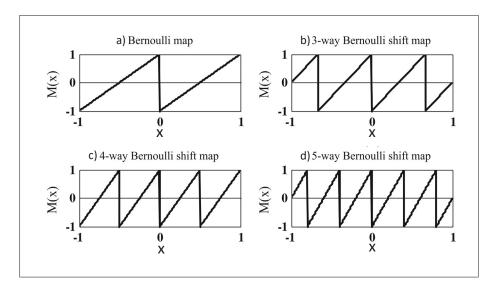

| Figure 1.9  | N-Bernoulli shift map for different values of N                                                |

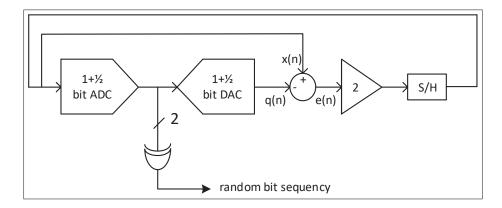

| Figure 1.10 | Basic block diagram of 1.5-bit ADC using as true random source. (S/H is sample and hold block) |

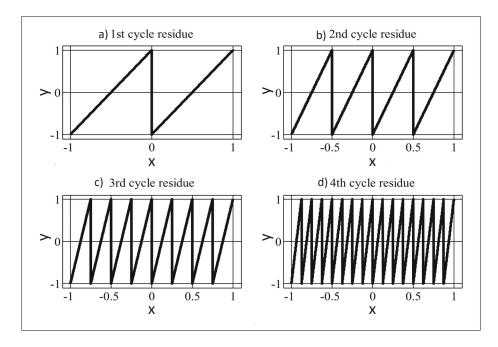

| Figure 1.11 | The different cycle residue of 1-bit ADC                                                       |

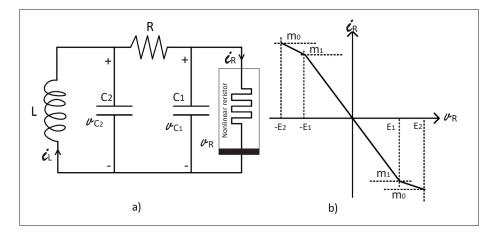

| Figure 1.12 | a) Chua's circuit b) Chua's diode                                                              |

| Figure 1.13 | Stroboscopic map chaos-based Oscillator                                                        |

| Figure 1.14 | Quantum true random number generator                                                           |

| Figure 2.1  | Hierarchy of research methodology for a) TRNG and b) PRNG                                      |

| Figure 2.2  | Testboard PCB design of the TRNG chip                                                          |

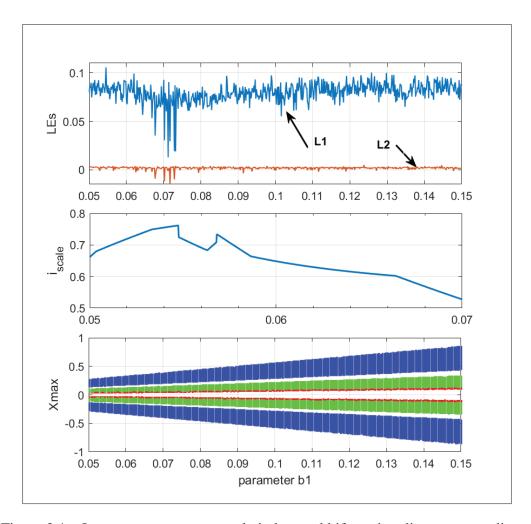

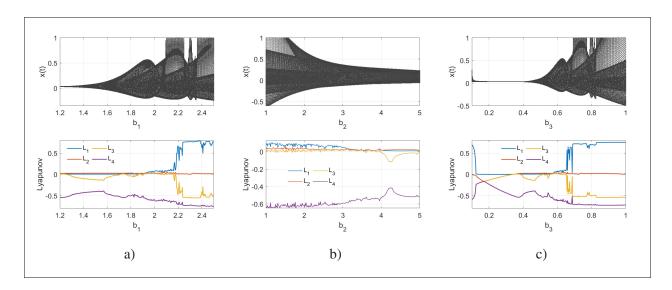

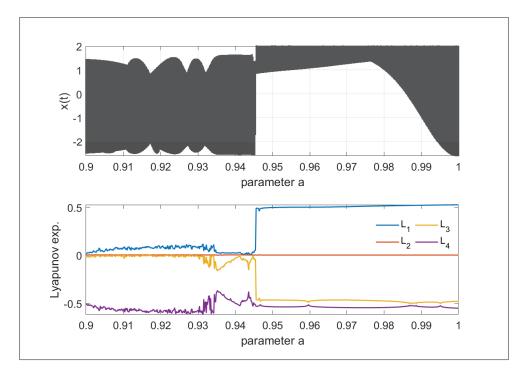

| Figure 3.1  | Lyapunov spectrums, scale index, and bifurcation diagram according to parameter $b_1$                                                                                                                        | 64 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

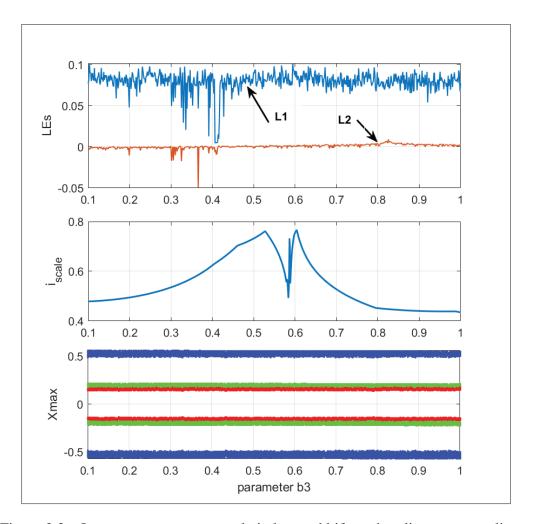

| Figure 3.2  | Lyapunov spectrums, scale index, and bifurcation diagram according to parameter $b_3$                                                                                                                        | 65 |

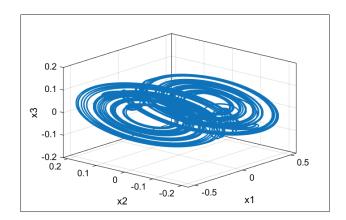

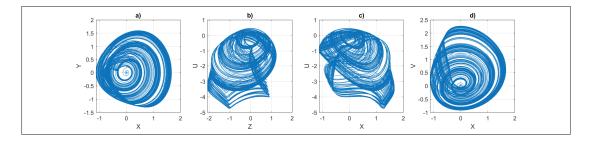

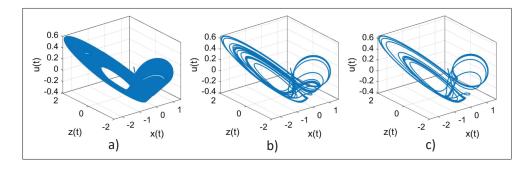

| Figure 3.3  | 3D trajectories of chaotic signals simulated in MATLAB                                                                                                                                                       | 66 |

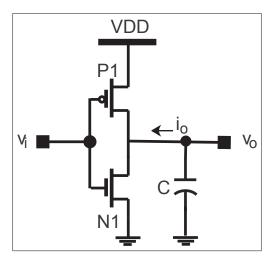

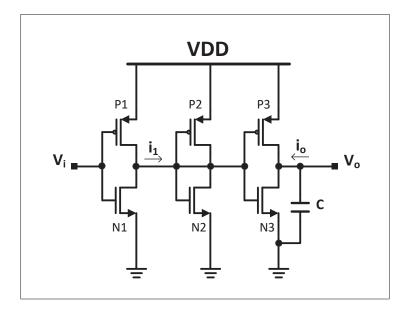

| Figure 3.4  | Inverted-based Gm-C integrator                                                                                                                                                                               | 67 |

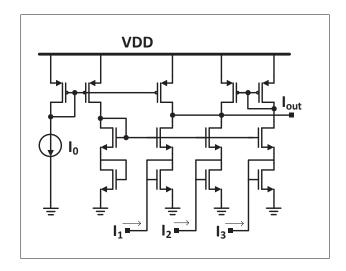

| Figure 3.5  | Hyperbolic function implementation                                                                                                                                                                           | 68 |

| Figure 3.6  | Fully CMOS cicuit design of the proposed continuous chaotic system                                                                                                                                           | 70 |

| Figure 3.7  | 2D trajectories with initial state of $V = [0.62, 0.61, 0.6]$                                                                                                                                                | 71 |

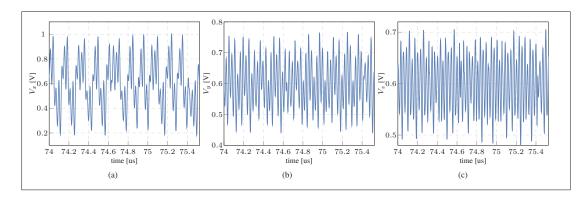

| Figure 3.8  | Chaotic signal waveform outputs                                                                                                                                                                              | 71 |

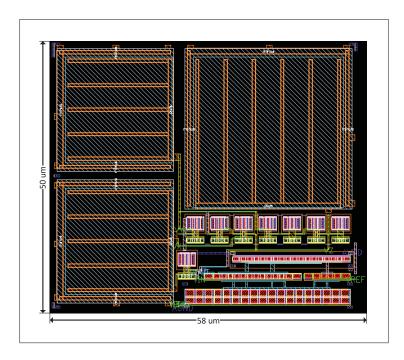

| Figure 3.9  | Layout diagram of the chaotic circuit design without padding                                                                                                                                                 | 72 |

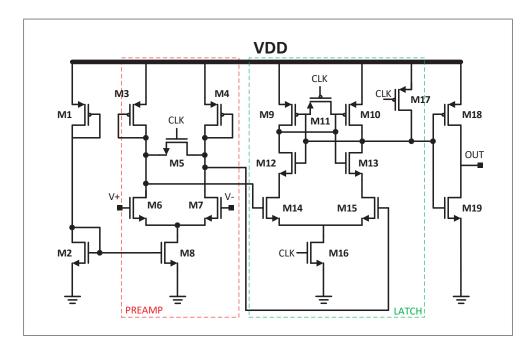

| Figure 3.10 | Comparator circuit design                                                                                                                                                                                    | 72 |

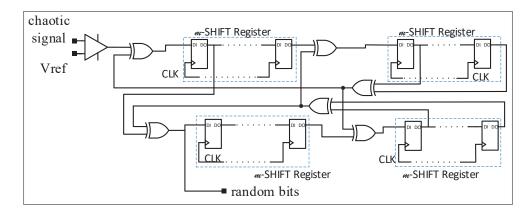

| Figure 3.11 | SHIFT-XOR based post processing circuit                                                                                                                                                                      | 73 |

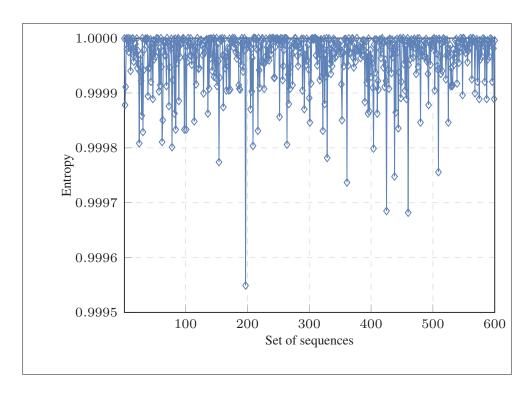

| Figure 3.12 | Entropy test result of the chaotic circuit design                                                                                                                                                            | 74 |

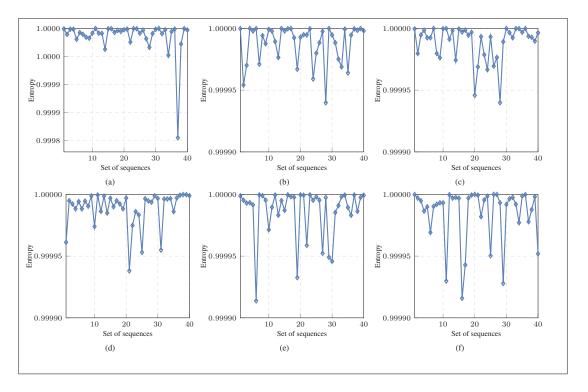

| Figure 3.13 | Average entropy with multiple corners in Monte Carlo simulations: (a) TT(-20°C,VDD=1.2 V) (b) TT(60°C,VDD=1.3 V) (c) TT(60°C,VDD=1.1 V) (d) SS(60°C,VDD=1.2 V) (e) SF(60°C,VDD=1.2 V) (f) FS(60°C,VDD=1.2 V) | 75 |

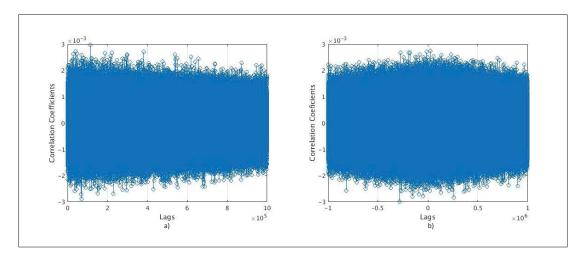

| Figure 3.14 | Correlation measurement of two different time series a) auto-correlation and b) cross-correlation                                                                                                            | 75 |

| Figure 3.15 | Chaos-key generator based image encryption algorithm scheme                                                                                                                                                  | 79 |

| Figure 3.16 | Comparison between AES and Chaos-key based image encryption                                                                                                                                                  | 80 |

| Figure 3.17 | Correlation tests of two adjacent pixels in the plain image and chaos-based encrypted image                                                                                                                  | 82 |

| Figure 3.18 | Comparison of image decryption with correct key $k_1$ and a wrong chaos-key $k_2$                                                                                                                            | 83 |

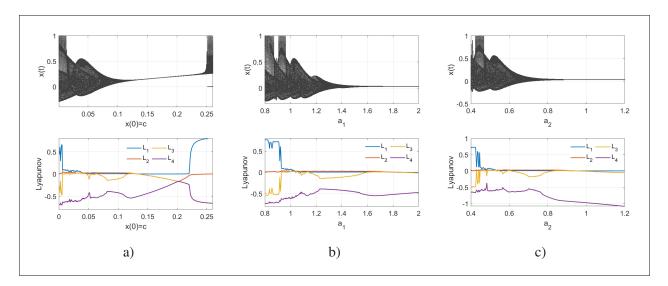

| Figure 4.1  | Bifurcation diagram and Lyapunov spectrum of signal $x_1$ according to parameters (a) initial condition $x(0) = c$ (b) $a_1$ and (c) $a_2$                                                                   | 95 |

| Figure 4.2  | Bifurcation diagram and Lyapunov spectrum of the signal $x_1$ according to parameters (a) $b_1$ , (b) $b_2$ , and (c) $b_3$                                                                                                                                        | 95    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4.3  | Integrator circuit design                                                                                                                                                                                                                                          | 97    |

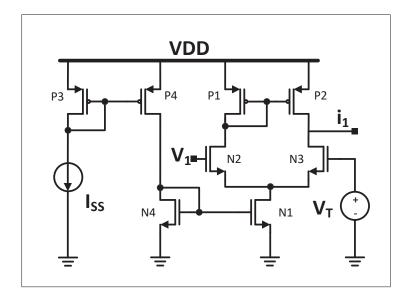

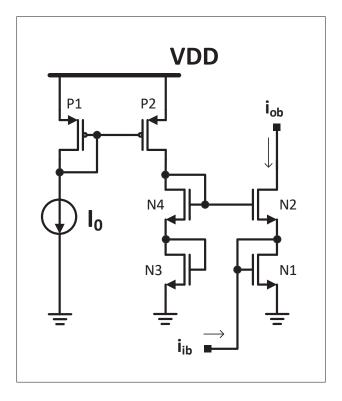

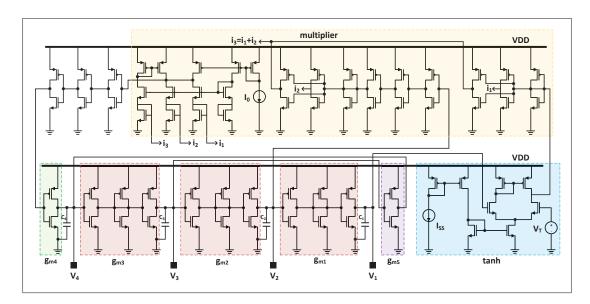

| Figure 4.4  | Circuit design of current square                                                                                                                                                                                                                                   | 98    |

| Figure 4.5  | Hyperbolic function implementation                                                                                                                                                                                                                                 | . 101 |

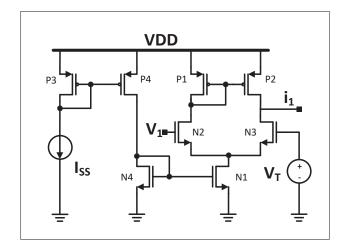

| Figure 4.6  | Multiplier circuit design                                                                                                                                                                                                                                          | . 101 |

| Figure 4.7  | Circuit design of the proposed 4D hyperchaotic system                                                                                                                                                                                                              | . 102 |

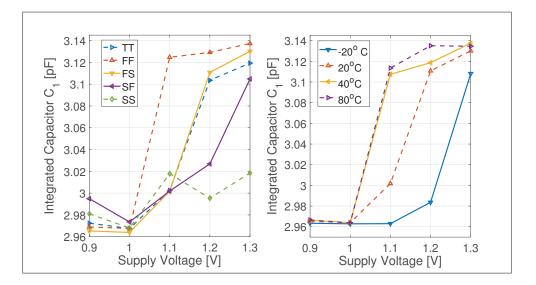

| Figure 4.8  | Integrated capacitor $C_1$ according to PVT variations                                                                                                                                                                                                             | .103  |

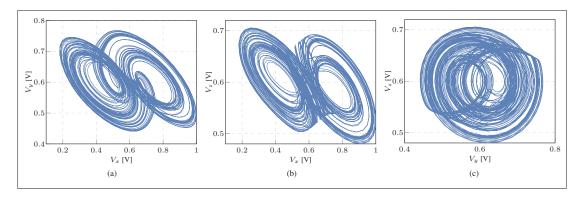

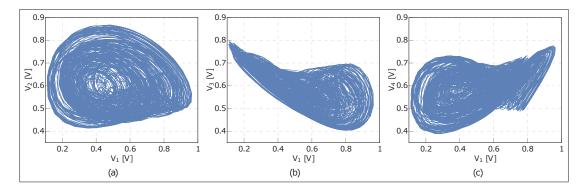

| Figure 4.9  | Trajectories of the chaotic outputs (a) $V_1-V_2$ , (b) $V_1-V_3$ , and (c) $V_1-V_4$                                                                                                                                                                              | . 104 |

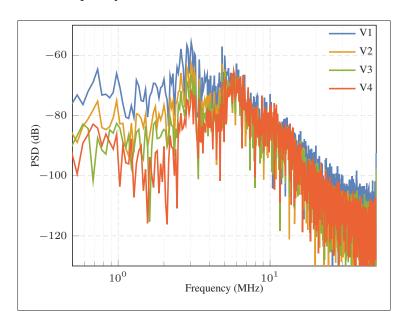

| Figure 4.10 | Chaotic signal output frequency spectrum                                                                                                                                                                                                                           | . 105 |

| Figure 4.11 | Comparator circuit design                                                                                                                                                                                                                                          | .106  |

| Figure 4.12 | Circuit design for post-processing based on dynamic D Flip-Flop                                                                                                                                                                                                    | . 107 |

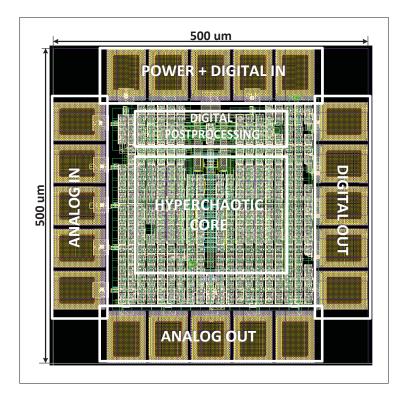

| Figure 4.13 | Layout diagram of the chip                                                                                                                                                                                                                                         | .108  |

| Figure 4.14 | Cross-correlation measurement of random bitstreams generated from different chaotic signals $V_1$ and $V_2$ at the same time                                                                                                                                       | 111   |

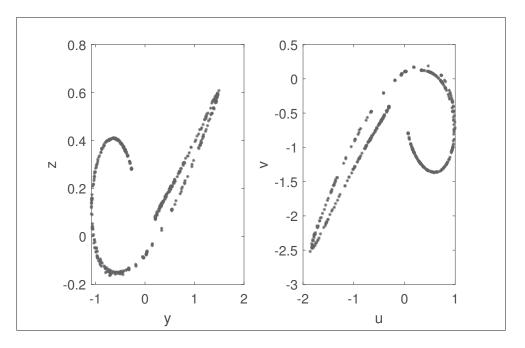

| Figure 5.1  | Poincaré section of the phase-space in the plain $(x = 1)$                                                                                                                                                                                                         | 121   |

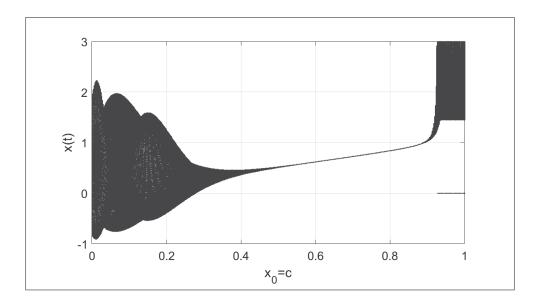

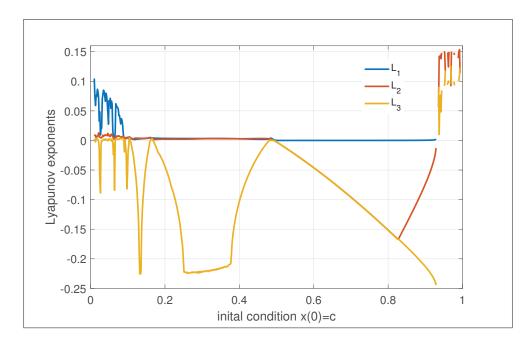

| Figure 5.2  | Bifurcation diagram according the initial condition                                                                                                                                                                                                                | 122   |

| Figure 5.3  | Lyapunov spectrum according to initial condition $x(0)=c$                                                                                                                                                                                                          | 123   |

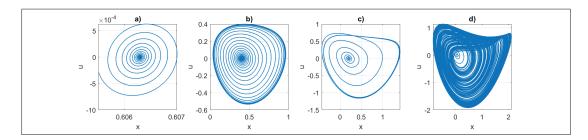

| Figure 5.4  | Transition to chaos regions depending to initial condition $x(0) = c$ :<br>a) stable region for $c = 0.6$ , b) limited dynamic region for $c = 0.4$ , c) chaotic region with limited periods for $c = 0.2$ , and d) rich dynamic and chaotic region for $c = 0.05$ | 123   |

| Figure 5.5  | The proposed pseudo-random number generator scheme                                                                                                                                                                                                                 | 124   |

| Figure 5.6  | Hyperchaos function $F(S_k)$ implementation in XSG                                                                                                                                                                                                                 | 125   |

| Figure 5.7  | Block diagram of the proposed fourth-folding Runge-Kutta algorithm                                                                                                                                                                                                 | 125   |

| Figure 5.8  | Trajectories of the chaotic outputs                                                                                                                                                                                                                                | 126   |

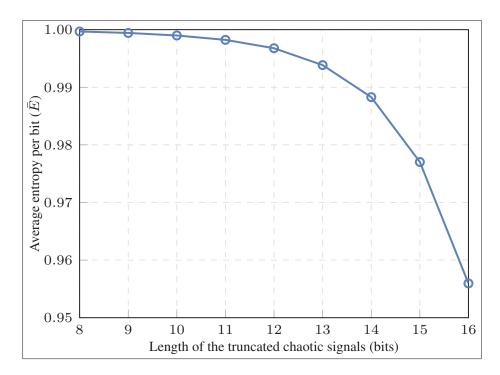

| Figure 5.9  | Average entropy per bit with different length of truncated chaotic signals                                                                                           | 129 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

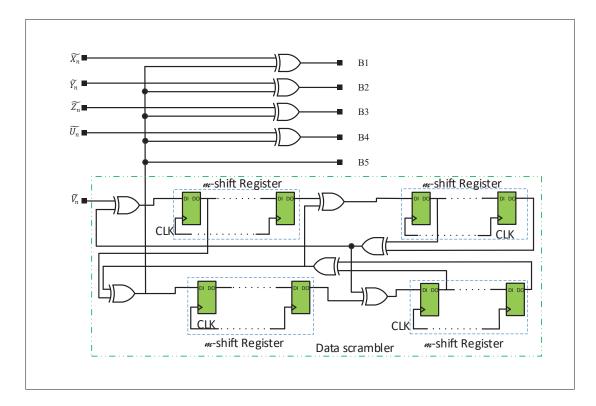

| Figure 5.10 | Post-processing design                                                                                                                                               | 130 |

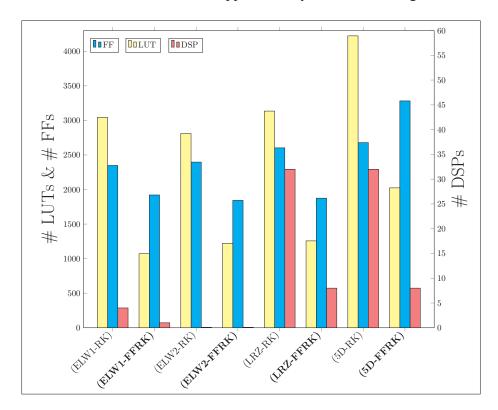

| Figure 5.11 | Amount of FPGA resources in terms of LUT, FF, and DSPs required by various continuous chaotic systems, using the traditional RK implementation and the proposed FFRK | 131 |

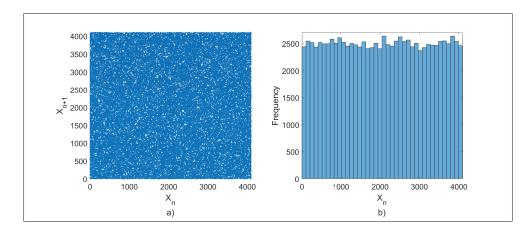

| Figure 5.12 | 12b-truncated chaotic signals in a) X-Y distribution points and b) Histogram diagram. (before post-processing)                                                       | 133 |

| Figure 5.13 | Histogram of output bitstreams.(after post-processing)                                                                                                               | 134 |

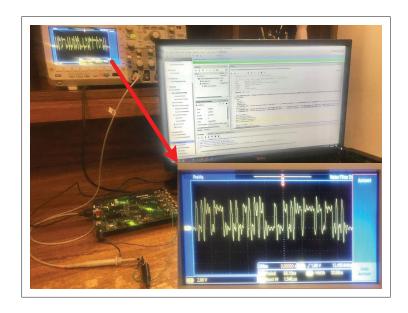

| Figure 5.14 | The experimental setup for the proposed chaos-based PRNG                                                                                                             | 134 |

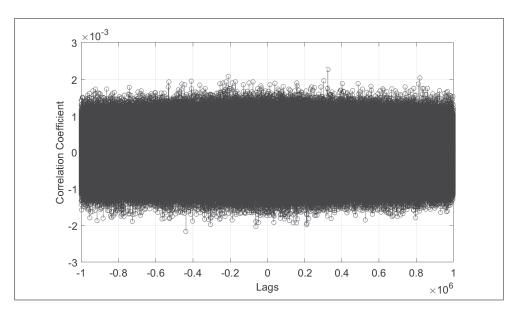

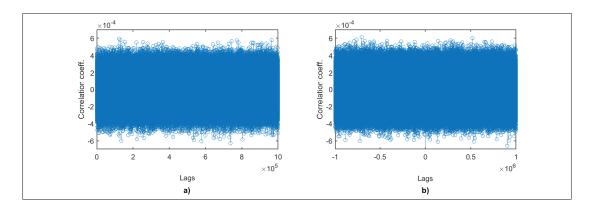

| Figure 5.15 | a) autocorrelation of intra-signal random bitstream $B_1$ and b) crosscorrelation of inter-signal random bitstreams $B_1$ vs. $B_2$                                  | 135 |

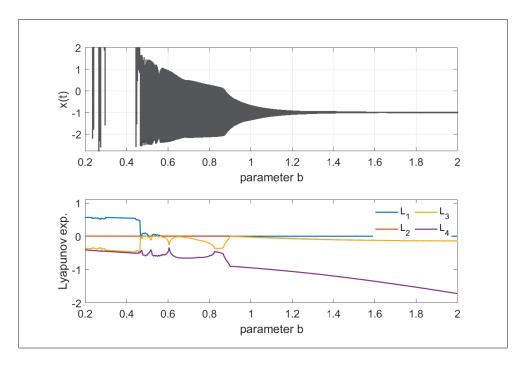

| Figure 6.1  | Bifurcation diagram of $x(t)$ according to parameter $a$                                                                                                             | 145 |

| Figure 6.2  | Bifurcation diagram of $x(t)$ according to parameter $b$                                                                                                             | 146 |

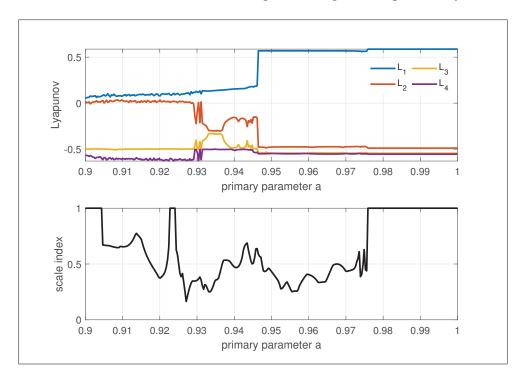

| Figure 6.3  | Lyapunov spectrum according to the parameter a                                                                                                                       | 148 |

| Figure 6.4  | Transition from chaotic region to periodic region with parameter $a$ - a) $a = 0.91$ , b) $b = 0.93$ , and c) $a = 0.94$ .                                           | 148 |

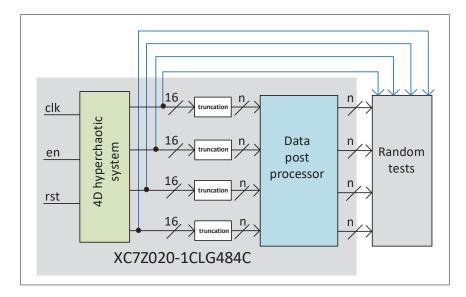

| Figure 6.5  | System overview of the proposed PRNG with hardware implementation in FPGA. The width of data in post-processing block ( <i>n</i> ) is defined at synthesis           | 150 |

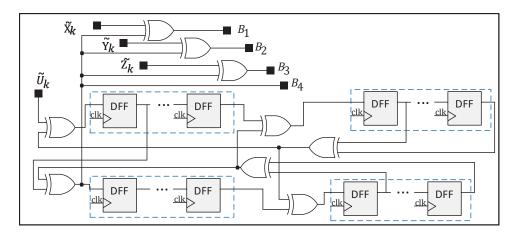

| Figure 6.6  | The post-processing design in the Xilinx System Generator                                                                                                            | 151 |

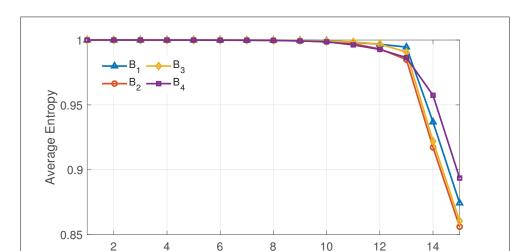

| Figure 6.7  | The variation of average entropy of random data depending on the truncated position                                                                                  | 152 |

| Figure 6.8  | Hardware validation of the proposed PRNG. Only the LSB of the random data $B_1$ is observed in oscilloscope. The system is running at 50 MHz                         | 153 |

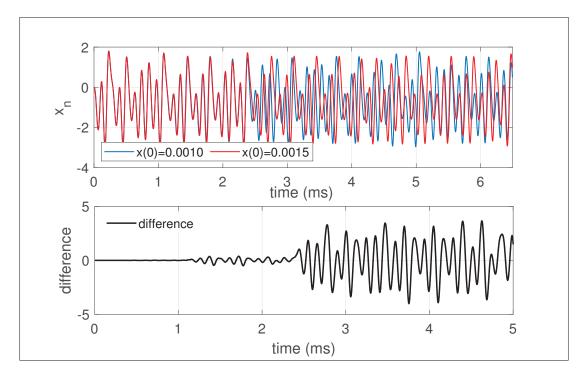

| Figure 6.9  | The system's senitivity to the initial condition                                                                                                                     | 156 |

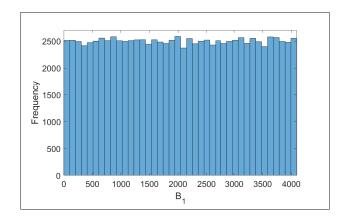

| Figure 6.10 | Histogram of a) the 10-bit raw truncated chaotic signal $X$ - before post-processing, and b) the 10-bit random signal $B_1$ - after post-processing                  | 156 |

| Figure 6.11 | a) auto-correlation of intra-signal random bitstream $B_1$ and b) crosscorrelation of inter-signal random bitstreams $B_1$ vs. $B_2$ |     |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Figure 6.12 | Hardware architecture of data encryption based on the chaos-based PRNG                                                               | 160 |  |  |

| Figure 6.13 | Comparison between original image and encrypted image                                                                                | 162 |  |  |

## LIST OF ABBREVIATIONS

GSM Global System for Mobile communications

SIM Subscriber Identification Module

RNG Random Number Generator

TRNG True-Random Number Generator

PRNG Pseudo-Random Number Generator

FFRK Fourth-Folding Runge-Kutta

LPWA Low-Power Wide Area

IoT Internet-of-Thing

PMOD Peripherial module interface

JTAG the Joint Test Action Group

DSP Digital Signal Processing

LFSR Linear-Feedback Shift Register

DRC Design Rule Checks

LVS Layout Versus Schematic

ESD Electrostatic discharge

I<sup>2</sup>C Inter-Integrated Circuit Protocol

USB Universal Serial Bus

UART Universal asynchronous receiver-transmitter

TSMC Taiwan Semiconductor Manufacturing Company

PDK Process Design Kit

PCB Printed-Circuit Board

LUT Look-up Table

FF Flip-flop

TP Throughput

#### INTRODUCTION

The downscale of semiconductor technology has been opening an era of the Internet of Things (IoT), causing an unprecedented impact on society. IoT services are likely to be a key driver for future growth in cellular networks. According to the report of Machina Research in May 2015, 30 billion devices are expected to be deployed by 2025, of which cellular IoT and Low-Power Wide-Area (LPWA) modules are forecasted to account for 7 billion units (Nokia (2017a)). IoT networks, which allow people to connect with multiple devices, where some of them contain private information, such as heartbeat records and credit card information, are subjects to continuous attacks. Therefore, among several significant obstacles remaining to fulfill the IoT vision, security is the chief. Although \$550M have been spent on IoT security, it was reported that more than 30% attacks involve IoT devices by March 2020(Bonvarlet (2017)). Researcher from Unit 42, a threat intelligence team at Palo Alto Networks, also discovered 98% of IoT devices are unencrypted, exposing personal and confidential data on the network, which are vulnerable to cybersecurity attacks UNIT42 (2020).

25 years ago, when GSM was developed and standardized, the first security functions were introduced partly because of emerging threats. The invention of a tamper-resistant subscriber identification module (SIM) provided strong authentication of the subscriber and strong binding to fraud (Nokia (2017b)). Moving to 3G and 4G standards, additional improvements were made including mutual authentication and data encryption at the base station. Moreover, true key management was employed to protect against potential physical attacks.

Reflecting on the development of 2G-4G security, it can be said that security was developed to protect a basic connectivity service (voice and packet data) (Roman, Najera & Lopez (2011)). The drivers for next generation networks are continuously being developed to provide trustworthy basic connectivity services. However, additional key driving factors will be considered because

the upcoming 5G networks are not only designed to serve mobile users but also connecting industries such as manufacturing, transport, smart grids, healthcare, etc.

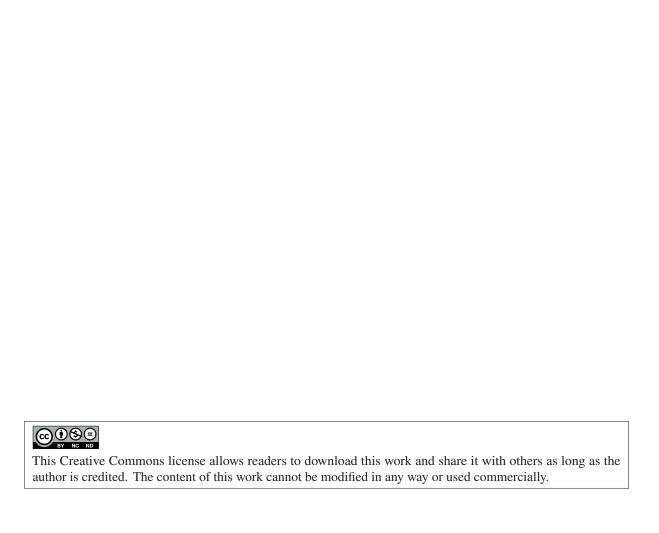

Figure 0.1 Cellular IoT use cases

Figure 0.1 shows multiple applications and IoT connections that will be required in future networks. IoT applications and services vary widely based on their service requirements, data throughput, latency, connectivity, and reliability. Security is required at many levels in communications, from the physical layers to cloud services; data needs to be protected for safe operations. Most of the existing security mechanisms are based on software implementation, which has limitations when it comes to providing high-level security in cryptographic applications deployed in low-power consumption devices (Bae, Kim, Park & Kim (2017)). Software-based cryptographic applications require high device resources which make them not applicable to embedded systems in low power consumption devices.

In software implementations, linear methods have been used to generate pseudo-random bits such as LFSRs, which are very popular due to their efficiency, easy embedding, and programming. However, being deterministic and periodic, their key streams are predictable and reproducible.

In this context, hardware-based RNGs using non-linear methods have been emerging as a natural choice for high-security applications.

#### **Research motivation**

In this section, we address two main factors motivating our research toward designing new RNGs. First, the high security requirement of IoT devices is presented. Second, we demonstrate that a hardware implementation of RNGs is required for future networks.

## Information security

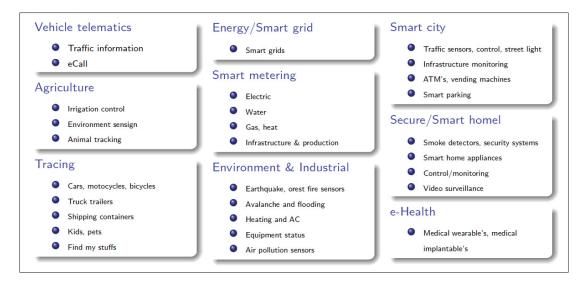

Figure 0.2 shows the data flow from IoT devices to the central cloud which allows devices to connect to the Internet. The IoT security framework is composed of three elements: the IoT secure device, the IoT cloud service providing device and security management, and the IoT central cloud. In ubiquitous network environments, every physical device has its device identification, which is locatable, addressable, and readable/writable, on the Internet. This device identification produces and consumes services and collaborates with each other toward a common goal.

Figure 0.2 Elements of IoT security architecture

The first element, IoT secure device is a microprocessor that includes a secure element and a high-level application platform within an integrated circuit. This device operates in real-time and supports standard IoT protocols enabling it to be connected to the IoT cloud service (IoT

CS). The IoT device's ID in the IoT network is a feature that distinguishes the IoT devices within the Internet. The IoT devices collect data and monitor the system state through the sensors. Then, the data travels through IoT network protocols to the IoT CS. Some of the existing protocols that are used and developed currently by different companies or groups are listed in Table 0.1. In data cryptography, random number generator provides random keys such as private key, public key, authenticate key for any kind of cryptographic operations. The random number generators in the IoT secure devices should provide random key bitstreams at proper throughputs to be compatible with the network protocols they are serving. The designs for the RNG at the device side have to satisfy the limited power consumption and device size requirements. The second element is the IoT CS which provides device and security management. In secured communications, devices need the provision the device's IDs and the activation keys. The device manager manages the device's ID and enables the IoT CS to recognize authorized devices and prevent unauthorized devices from attacking its services. The security management module provides an activation key to establish a secure channel between devices and services. Finally, the IoT CS connects to the central cloud which provides many applications for users. The IoT CS employs trusted key management providing high-security keys and high throughput to support a large number of devices. The throughput and security requirements of the random number generators at the IoT CS are more critical than that of the IoT devices. The last element is the IoT cloud center (IoT CC) which provides multiple services for users. The connection between the IoT CS and IoT CC is standardized. It is out of the scope of this report.

There are many attacks that can occur during the data transfer process, such as interference, shielding, theft, and side-channel attacks, which cause data leakage and other security issues if insufficient data protection is adopted. As such, any IoT design that places a high priority on security needs a secure element to encrypt or decrypt data and provide an integrity checking mechanism to ensure information security.

Table 0.1 List of existing network protocols

| Protocol  | Standard        | Frequency (Hz)       | Range    | Data rate (bps) |

|-----------|-----------------|----------------------|----------|-----------------|

| Bluetooth | Bluetooth 4.2   | 2.4 G                | 50-100 m | 1 M             |

| ZigBee    | ZigBee 3.0      | 2.4 G                | 10-100 m | 250 k           |

| Z-wave    | Z-wave Alliance | 900 M                | 30 m     | < 10-100 k      |

| 6LowLan   | RFC6282         | 2.4G / <1G           | N/A      | N/A             |

| Thread    | Thread          | 2.4 G                | N/A      | N/A             |

| Wifi      | 802.11n         | 2.4 G / 5 G          | 50 m     | 600 M-1 G       |

| Cellular  | 2G,3G,4G,LTE    | 900/1800/8900/2100 M | 35 Km    | 10 M            |

| NFC       | IOS/IEC         | 13.56 M              | 10 cm    | 100-420 k       |

| Neul      | Neul            | 900,458,470-490 M    | 10 Km    | < 100 k         |

| SigFox    | SigFox          | 900 M                | < 50 Km  | 10 bps-1 k      |

| LoRaWan   | LoRaWan         | Various              | 10 Km    | 0.3-50 k        |

## Hardware design requirement

As the key engine of the secure element, the random number generator plays an important role in information security applications. With the development of network information technologies, especially the booming of IoT devices, the random number generator's requirements are no longer limited to soft computing. The traditional random number generator in a secure element is implemented in the instruction set architecture processor (ISAP) that uses a software implementation mode, for example 32-bit ARM Cortex-M4F processors in the Tiva<sup>TM</sup> C Series from Texas Instrument (TI). However, the generic form of the instructions facilitates the modeling of physical attacks. As a result, ISAP-based RNGs' resistance to attacks is generally lower than hardware-based RNGs. Hence, ISAP-based devices are not applicable to scenarios where high security is required.

Physical attacks can be divided into invasive, semi-invasive, and non-invasive attacks according to the way the attacker acts on the circuits. Invasive attacks damage the package and remove the passivation layer of the chip. Here, attackers obtain the circuit function

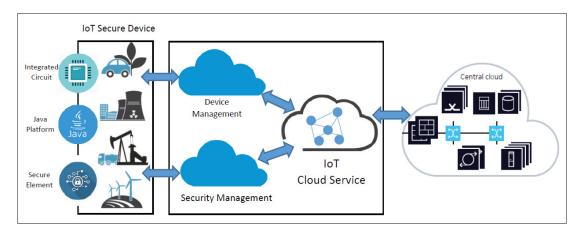

or the key information by imaging the circuit structure. These attacks are very powerful and cause permanent and irreversible damage to the targets. However, they require a long time and high cost. Semi-invasive attacks need to only remove the package of the chip only. Non-invasive attacks do not damage the original circuit or its package. They usually attack by analyzing information such as power consumption and electromagnetic radiation which are leaked during the chip's operation (Liu, Wang & Wei (2018)). The software-based random generator, which is a deterministic process in software implementation, such as xorshift, linear congruential generator, is non-cryptographically generator. Additionally, some cryptographically software-based PRNGs, such as SHA256PRNG, Fortuna, consume high power (for example  $0.5\mu J$  for each integer). Compared to hardware implementation; they have drawback of either low security level or high power consumption. Therefore, the hardware-based RNGs are in demand for IoT devices. Figure 0.3 shows the typical architecture of an IoT secure device that performs several cryptographic algorithms for secured transactions. The true random number generator, which is implemented in hardware design, is a core engine of the secure element.

## • Challenges of random number generator design

There has been numerous approaches to design random number generators in hardware. The random number generator in a secure element should be designed considering a trade-off between four factors: energy efficiency, security, reliability, and flexibility. We need to consider the balance between these factors in the design of a random number generator.

## - Energy efficiency

The power consumed to generate a single random bit is denoted as energy efficiency, which is evaluated by dividing the power consumption by the throughput. It is one of the most important design metrics to evaluate the system design. Specific applications and IoT communication protocols require different throughputs of random bit generators. For example, applications using real-time secure transmission through Zigbee protocol

Figure 0.3 Block diagram of secure element for secured transactions Taken from Liu et al. (2018, p.5)

require random bits at a throughput of at least 100 kbps, while the throughput requirement for 5G cellular communications is 100 Mbps. In stream cipher, which provides higher security of data encryption than the block cipher, requires high security, unpredictable random bitstream at the same speed as the plaintext stream. Therefore, the random number generators in the cipher stream need to meet the network's requirements in terms of data rate or throughput. Software implementations of RNGs are associated with a low energy efficiency due to their highly computational requirements and the fact that they are not optimized for specific applications. Hardware designs are necessary to provide high speed and high efficiency.

## - Security

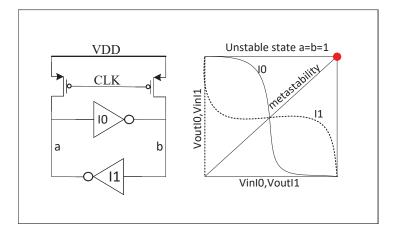

Random number generators for high-security communications should provide high resistance to physical attacks. Most of the existing works on RNG designs do not analyze their security ability. The invasive attack resistance could be improved by masking the circuit with many layers of metal shields and sensors on top of the chip. Non-invasive attacks should be considered while designing TRNG circuits. Thermal noise-based TRNGs are affected by supply noise injection. Attackers can use the side-channel information to change the ground potential. As a result, the randomness of the signal generated from this circuit could be destroyed. Multiple ring oscillator-frequencies were added to supply noise, which locked the oscillation with smaller jitter and greatly reduced the entropy harvested (Yang *et al.* (2014)). The metastability-based method using cross-coupled inverters provides excellent operating frequency and power efficiency. However, this approach is sensitive to environmental variations that degrade the robustness against attacks. The resistance to physical attacks is a key element for RNG designs in IoT devices due to two main reasons.

- The environment conditions vary during the chip's operations; the circuit should be verified in a wide range of working conditions. All the circuit components are affected by the voltage supply variation. TRNGs, which are based on the circuit noise and metastability, are highly affected by voltage variations, device mismatches and working temperature.

- Recently, many powerful non-invasive attacks have emerged. A low-frequency attack method that is based on sound or electromagnetic wave has been successful in jeopardizing many secure chips. This method uses specific MHz or kHz signals leaked by the attack target, even if the circuit works at the GHz range Liu *et al.* (2018). Therefore, using high sampling operations to resist the low-frequency noise attacks is

no longer valid Bae *et al.* (2017). Therefore, the secure devices have to be designed considering novel attack methodologies and potential future attacks.

Therefore, the designated RNGs have to pass the randomness tests for cryptography purposes such as standard statistical tests.

## - Reliability

There are many RNG designs that rely on physical entropy sources which can be based on different effects. Some researchers proposed to harvest thermal noise of a resistor in an analog circuit. Jitter noise in a ring oscillator can be added as a random source to fully digital circuits. Entropy sources, such as metastability state or jitter measurement, can be implemented in digital primitives or digital standard cells. Due to the high speed and adaptability to different technology processes, they were recently widely developed. However, these solutions are highly sensitive to systematic noises. Additionally, these entropy sources are assumed to have a Gaussian distribution, but in reality, they experienced unknown statistical distributions due to their limited dynamic range. This is caused by external factors, such as supply and temperature variations. To make them suitable for high-security applications, more reliable designs are necessary.

#### - Flexibility

There are many IoT communication protocols for multiple purposes, but designing an RNG compatible with all these applications is neither practical nor reliable. The current RNG methods are optimized for a specific application. However, an IoT secure device is mainly used to process various tasks as encrypt/decrypt data or real-time authentication which have different requirements to RNGs. It is better to integrate multiple operation modes in a processor.

#### Research objectives

RNGs are required in many applications, such as wireless networking, gaming, military communications, online payments, etc. RNGs are used to generate keys, initialize vectors, and

other random numbers used in many security standards and applications. As an example, the IoT is a fast-growing market where data can easily be intercepted and devices can be hacked, especially if weak RNGs are selected. Our main long-term objective is to design robust low-cost RNGs based on chaos systems for secure communication applications. Thus, we aim to achieve the following specific objectives:

- Robust RNG designs: Based on our investigation, the physical entropy sources like thermal noise, jitter noise, and metastability have low reliability. Therefore, we aim to design robust RNGs using chaotic systems. Chaos-based RNGs have been developed in many works. However, the existing chaos-based solutions are limited by their large occupation areas, high power consumption, or their use of 1D piecewise chaotic maps which degrade the dynamic properties. Our robust chaos-based RNG designs are expected to overcome these limitations.

- To deploy the designated RNGs in different IoT platforms, we will optimize the proposed approaches to meet the requirements in data rate, operating frequency, power consumption, etc. Different optimization strategies are investigated and performed. For example, the device resource optimization would be applied for constrained devices, with less consideration of data throughput. We can also optimize the proposed RNGs in which security and data rate are priorities.

## **Contributions and Outline**

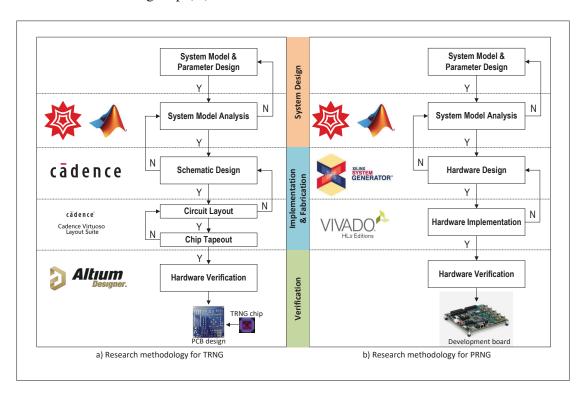

The organization of this dissertation, which includes 6 chapters, is structured and detailed as follows. Chapter 1 presents the background knowledge in chaos theory and random number generators, and the comprehensive literature review of conventional RNGs and chaos-based RNGs. In this vein, a discussion on the trends of future research in RNGs is presented.

Chapter 2 presents the research methodology for both the TRNG and PRNG designs, which are used in this project from system development to design. Although this is a research-based project, the methodology adopted the scheme and processes of high-tech commercial product

development. However, for industrial products, more product constrains could be applied during design and verification process. For example, industrial products should be verified in a wider range of temperature, voltage variations.

Chapter 3 presents the first article on designing a TRNG based on a novel 3D continuous chaotic system and an application of the designated chaos-based RNG in data encryption. In this chapter, a novel 3D continuous chaotic system is presented and analyzed mathematically in terms of dynamic characteristics, stability, and chaotic trajectories. The chaotic system and data post-processing circuit are implemented in a 130 nm CMOS technology with a low voltage supply of 1.2 V. The system design enables the utilization of multiple chaotic signals to generate random bits. The core of the chaotic circuit consumes  $630\mu W$  in static mode and a maximum of  $660\mu W$  in running mode which is lower than previous continuous chaos-based TRNGs. Moreover, the random bits are successfully tested by the NIST test suite and other kinds of randomness tests, such as entropy and correlation tests. Then, the generated random bits are used for image encryption.

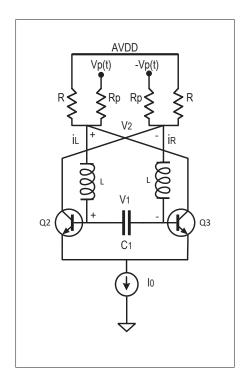

Chapter 4 presents the second article discussing another TRNG based on a hyperchaotic system. The novel hyperchaotic system has four dimensions that provide higher throughputs for the RNG. The advantages of the proposed hyperchaotic system in generating random bits are discussed and compared to the state-of-the-art. The analog circuit design of the proposed 4D hyperchaotic system and the data post-processing provides truly random bits. Due to analog circuit imperfections and circuit noises at the initial conditions, the unpredictable trajectories of chaotics signals provide high randomness for the output bits. The circuit is implemented and fabricated using 130 nm CMOS technology. The proposed novel system design and its circuit implementation provide the best energy efficiency of 4.37 pJ/b at a maximum sampling frequency of 100 MHz which is much better than previous chaos-based TRNGs.

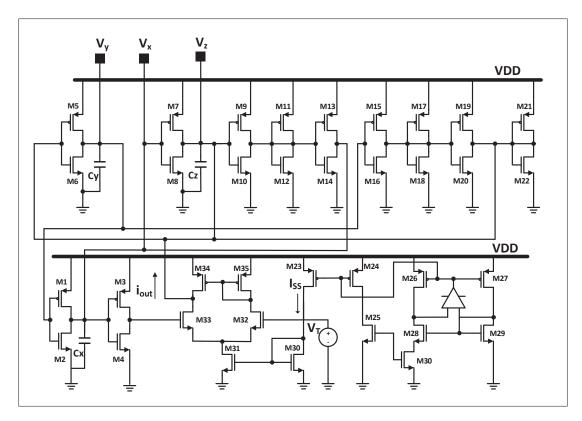

Chapter 5 presents the third article proposing a novel 5D hyperchaotic system that provides improved dynamic characteristics. Moreover, a digital implementation of the proposed 5D chaotic system and data post-processing provides a high throughput PRNG. A novel method to implement the fourth-order Runge-Kutta algorithm for chaotic systems in FPGAs which reduces the implementation cost compared to traditional implementations, is provided. The generated random bits are tested with the NIST test suite and the excessive random test TestU01. The proposed random bit generator can achieve a maximum throughput of 6.78 Gbps which is higher in compared to state-of-the-art designs.

Chapter 6 presents the fourth article proposing a novel 4D hyperchaotic system that provides high dynamic characteristics. Digital implementations of the chaotic system and data post-processing are performed using the Xilinx System Generator, which reduces the time-to-market. The advantage of the proposed 4D hyperchaotic system is that the non-linear function is implemented in a simple manner without multiplexers. Thus, the implementation cost is reduced while the high dimensional output signal provides a high throughput bitstream at a maximum of 8.56 Gbps which is higher than previous continous-based PRNGs's.

Chapter 7 provides the conclusion of the dissertation and recommendations for future works.

For convenience, a big picture of the thesis is provided in Figure 0.4.

Figure 0.4 Paradigm of the thesis's contributions

### **CHAPTER 1**

#### BACKGROUND AND LITERATURE REVIEW

As mentioned in the Introduction, security is required at many layers of a communication system: device, network, and cloud to ensure efficient and safe operations by protecting data in motion and at rest. In this manner, the RNG is the key engine of any security method. In this chapter, a review of conventional RNGs is presented. Recent research on chaos-based RNGs and the prerequisite background in chaos theory are provided. Lastly, randomness evaluation metrics are presented.

### 1.1 Architecture of RNGs

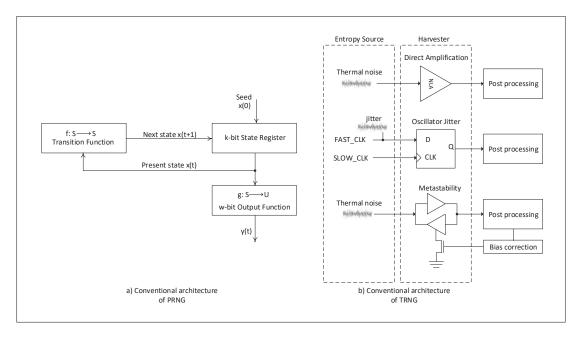

### 1.1.1 Architecture of conventional RNGs

As previously stated, this research focuses on the hardware implementation of RNGs. The conceptual architectures of conventional hardware PRNG and TRNG are presented in Figure 1.1. The conventional hardware PRNG architecture is similar to that of software-based PRNG; however, it is implemented in a hardware device such as FPGA Addabbo *et al.* (2007). The periodicity and deterministic algorithms used in the transition functions are the main engines of PRNGs Hazwani *et al.* (2014). The initial state x(0) is the seed. The next state is determined by applying the transition function x(t + 1) = f(x(t)). The function f is an arithmetic linear or non-linear function in PRNGs and a physical phenomenon in TRNG Kim, Ha & Lee (2017b). Then, the output function g(x(t)) is applied to the current state. This process, presented in Figure 1.1-b), is considered as the data post-processing in TRNG.

### 1.1.1.1 Physical entropy source

In the last few decades, various RNGs that can employ physical sources, such as thermal noise, jitter noise, telegraph noise, and metastability, have been proposed.

Figure 1.1 Conventional architecture for the hardware implementation of a) PRNG and b)

TRNG

Taken from Kim et al. (2017, p.2)

• Thermal noise: Thermal circuit noise, which is very easy to harvest, is utilized in some TRNGs. However, the Flicker noise (1/f noise) affects the quality of the randomness at low frequency operation. Moreover, the relative low noise power available needs to be amplified before harvesting, which increases the circuit bias. The thermal noise power harvested from a resistor R at absolute temperature T is extracted as:

$$P_{AN} = kT\Delta f \to (\frac{v_n^2}{2})\frac{1}{R} = kT\Delta f, \tag{1.1}$$

$$\rightarrow \overline{v_n^2} = 4kTR\Delta f. \tag{1.2}$$

The voltage spectral density derived from the above equations is:

$$S_{\nu}(f) = \frac{\overline{\nu_n^2}}{\Delta f} = 4kTR \quad (V^2/Hz), \tag{1.3}$$

where  $\Delta f$  is the bandwidth of the signal. It is noticed that the power of the noise extracted from a resistor fabricated in CMOS technology is insufficient for direct use, it should be amplified

before post-processing. However, amplifiers suffer from other deterministic noise sources, such as power variations and process variations, that degrade the randomness by varying the bias points. Some researchers utilized external metal layers which are high-temperature sensitive materials, such as SiN embedded in Metal-X layers used in CMOS technologies, resulting in much higher noise powers, without amplifiers Matsumoto *et al.* (2008).

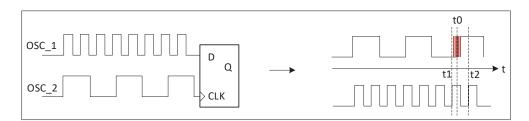

- **Jitter noise:** Jitter noise, which has random distribution as the white noise, is a common noise in any clock signal. Therefore, in recent research, it has been used as an entropy source for generating random bits. Jitter-noise-based RNGs use two clock sources with one being faster than the other. The jitter noise that occurs in the faster clock signal is sampled by the slower clock. The output bit is random according to the level of jitter noise. Kim, Lee & Kim (2017a) accumulated jitter noise from differential ring oscillators. The chip fabricated in 65 nm CMOS technology showed attractive performances: up to approximately 10Mbps throughput with low power consumption (<0.5 mW). The researchers from the University of Michigan (Yang *et al.* (2014)) also proposed a TRNG based on jitter noise, which was implemented in both 28 nm and 65 nm CMOS technologies. The results showed the highest throughput was 23.16 Mbps while consuming 0.54 mW. Mathew *et al.* (2016) presented an all-digital TRNG based on the collapse time of two racing edges in even-stage ring oscillators.

- **Metastability:** Metastability takes advantage of the uncertainty of either a logical state or its resolve time. The main drawback of these methods is that they require very specific and stable initial and/or operating conditions. Therefore, the entire system is extremely sensitive to deterministic system noise sources, such as power variations, bias voltage variations, and device mismatches Kim *et al.* (2017a); Yang *et al.* (2014); Bae *et al.* (2017); Petrie & Connelly (2000); Chen *et al.* (2009); Yang, Blaauw & Sylvester (2016); Chen, Li, Wang, Liu & Yang (2016).

#### 1.1.1.2 Harvester

Each kind of physical entropy source requires a specific harvesting circuit. Due to the low power characteristic of thermal noise, a low-noise amplifier is needed in the harvester circuit. Figure 1.4

| Design                    | Entropy      | Technology         | TP(bps)       | Power(W)       |

|---------------------------|--------------|--------------------|---------------|----------------|

| Petrie & Connelly (2000)  | Thermal      | $2 \mu \mathrm{m}$ | 1 M           | 3.9m           |

| Mathew et al. (2012)      | Meta.        | 45 nm              | 2.4 G         | 7 m            |

| Yang et al. (2014)        | Jitter       | 28 nm/65 nm        | 23.16 M/2.8 M | 0.54 m         |

| Laurenciu C. (2015)       | Thermal      | 65 nm              | 1 G           | _              |

| Liu, Liu, Li & Zou (2016) | Jitter       | 130 nm             | 0.1 M         | $40\mu$        |

| Mathew et al. (2016)      | Jitter       | 40 nm/180 nm       | 2 M/1 M       | $46\mu/109\mu$ |

| Bae et al. (2017)         | Meta.&Jitter | 65 nm              | 3 G           | 5 m            |

| Kim et al. (2017a)        | Jitter       | 65 nm              | 8.2 M         | 0.289 m        |

Table 1.1 List of existing physical entropy true random number generators

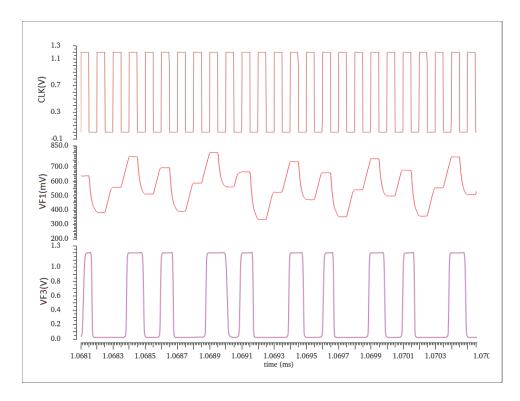

shows a simple implementation of a thermal noise harvesting circuit and the simulation results. The circuit is implemented in 65 nm CMOS technology. Laurenciu C. (2015) compared two identity resistor noise sources to generate the random sequence. Using comparison eliminates the common-mode and power supply interferences. The circuit, implemented in 65 nm CMOS technology, can provide bit samples at 1GHz. The work of Bae *et al.* (2017) proposed a combination of thermal noise and metastability, which allows to use a high sampling frequency to dominate the Flicker noise. The implementation using 65 nm CMOS technology presented high throughputs (3 Gbps) with a relatively low power consumption of 5 mW.

Figure 1.2 Jitter noise harvesting circuit implementation