ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA

MAÎTRISE EN GÉNIE ÉLECTRIQUE

M.Ing.

PAR

Rami LOUKIL

CONCEPTION ET MISE EN ŒUVRE DE MODULE DE CONTRÔLE DE PUISSANCE

ET DE GÉNÉRATION DE BRUIT POUR CONDITIONNER LES SIGNAUX RF D'UN

SIMULATEUR DE CONSTELLATION GPS ET GALILEO

MONTRÉAL, LE 4 MAI 2010

© Rami Loukil, 2010

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE :

M. Ammar Kouki, directeur de mémoire

Département de Génie électrique à l'École de technologie supérieure

M. René Jr. Landry, président du jury

Département de Génie électrique à l'École de technologie supérieure

Jocelyn Dore, examinateur externe

AGENCE SPATIALE CANADIENNE

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 9 AVRIL 2010

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# **CONCEPTION ET MISE EN ŒUVRE DE MODULE DE CONTRÔLE DE PUISSEANCE ET DE GÉNÉRATION DE BRUIT POUR CONDITIONNER LES SIGNAUX RF D'UN SIMULATEUR DE CONSTELLATION GPS ET GALILEO**

Rami LOUKIL

## **RÉSUMÉ**

La radionavigation par satellite a reçu beaucoup d'intérêt pendant le 21<sup>e</sup> siècle. Les avènements les plus importants dans ce secteur sont le nouveau système de positionnement par satellite de l'Union européenne baptisé Galileo et la modernisation du système américain GPS (*Global Positionning System*). Le regroupement de ces différents systèmes sous l'acronyme GNSS (*Global Navigation Satellite System*) permettrait une fiabilité et un positionnement d'une très grande précision. Cette tendance pousse les industries à concevoir des récepteurs capables de gérer ce nombre croissant de signaux. Ces nouveaux produits nécessitent des procédures de validation avant même que le système européen Galileo ne soit opérationnel.

Dans ce contexte, le laboratoire LACIME développe un simulateur de signaux GPS et Galileo. Le présent mémoire traitera les différentes parties de ce simulateur ainsi qu'une étude détaillée la conception d'un système de contrôle de puissance des signaux piloté par logiciel ainsi qu'un système de contrôle du ratio C/N<sub>0</sub> (*Carrier to Noise Ratio*).

Le système de contrôle de puissance a été développé afin d'offrir une précision de l'ordre de 0.1 dB sur une plage de 40 dB pour les signaux « GPS L1, Galileo E1 » à la fréquence de 1575.42 MHz, « GPS L5, Galileo E5a » à la fréquence 1176.45 MHz et le signal Galileo E5b à la fréquence 1207.14 MHz. Le système de contrôle de puissance a été mis en œuvre par l'élaboration d'une carte à circuit imprimé et d'une communication bidirectionnelle avec le logiciel qui permet une gérance totale du système. L'architecture implémentée a été judicieusement étudiée afin de permettre une flexibilité et une extensibilité du système. Elle permet d'exécuter plusieurs modes de contrôle à savoir « contrôle de gain », « contrôle automatique de puissance », « calibration de puissance » et « variation de la puissance dans le temps ». Le système de contrôle de puissance a été testé et validé pour donner une précision inférieure à 0.1 dB sur 40 dB pour les deux modes de fonctionnement de base (contrôle de gain et contrôle automatique de puissance). Les deux autres modes découlent de ces derniers pour donner plus d'options à l'utilisateur du simulateur GPS et Galileo.

Afin de donner à l'utilisateur une maîtrise totale de la qualité des signaux, un générateur de bruit blanc gaussien a été mis en œuvre. Il permet, en combinaison avec le système de contrôle de puissance, de contrôler le ratio C/N<sub>0</sub>. Une étude sur les méthodes de génération d'un tel bruit blanc a été faite. Le choix s'est établit sur une implémentation numérique au sein du FPGA qui présente une flexibilité et une complexité moindre par rapport à une approche analogique. Le générateur de bruit blanc a été développé par la méthode Box-Muller qui présente beaucoup d'avantages dans le cas d'une implémentation numérique. Son architecture a été optimisée pour rejoindre les contraintes des ressources matérielles du

FPGA. Le bruit blanc gaussien est combiné aux signaux en analogique et sa puissance est contrôlable par le biais de la partie logicielle. Il a été testé et validé par un récepteur commercial et un récepteur développé au sein de l'école. L'augmentation linéaire du niveau du bruit dégrade la qualité des signaux et le rapport C/N<sub>0</sub> diminue linéairement dans les deux récepteurs de test.

**Mots clés :** GNSS, contrôle de puissance, bruit blanc gaussien, FPGA.

# **DESIGN AND IMPLEMENTATION OF A POWER CONTROL MODULE AND NOISE GENERATOION FOR RF SIGNALS CONDITIONNING IN A GPS AND GALILEO CONSTELLATION SIMULATOR**

LOUKIL, Rami

## **ABSTRACT**

Satellite radio navigation has received considerable interest during the 21st century. The most important advents in this sector are the new satellite positioning system of the European Union called Galileo and the modernization of the United States' Global Positioning System GPS. The combination of these different systems under the acronym GNSS (Global Navigation Satellite System) would allow reliable positioning and a high accuracy. This trend pushes the industry to design receivers able to handle the growing number of signals. These new products require validation procedures before the European system, Galileo becomes operational.

In this context, the laboratory LACIME is developing a GPS and Galileo signals simulator. This master's thesis presents the different parts of the simulator and a detailed design study of a power control system driven by software for GPS and Galileo signals and a C/N<sub>0</sub> ratio control system.

The power control system has been developed to provide an accuracy of about 0.1 dB over a range of 40 dB for signals "L1 GPS, Galileo E1" at a frequency of 1575.42 MHz, "GPS L5, Galileo E5a" at 1176.45 MHz and the Galileo signal E5b at 1207.14 MHz. The power control system has been implemented by developing a printed circuit board and a two-way communication with the software that allows complete system management. The architecture has been carefully studied and implemented to allow flexibility and scalability. It allows the user to run multiple control modes namely "gain control", "automatic power control", "power calibration" and "time varying power control". The power control system has been tested and validated to give an accuracy of less than 0.1 dB over 40 dB for both basic modes of operation (gain control and automatic power control). The other two modes resulting from the latter give more features to the user of the simulator.

To give the user a total control of signal quality, a white Gaussian noise generator has been implemented. It allows, in addition to the power control system, the ratio C/N<sub>0</sub> control. A study on methods for generating such a white noise was made. The choice was a digital implementation in the FPGA which provides a flexibility and lower complexity compared to an analog approach. The white noise generator was developed with the Box-Muller method which has many advantages in the case of digital implementation. Its architecture has been optimized to reach the hardware resources constraints of FPGA. The white Gaussian noise is combined with the signals in the RF part and its power can be controlled by software. It has been tested and validated by a commercial receiver and receiver built within the school. The linear increase in the noise level degrades the signal quality and the C/N<sub>0</sub> ratio decreases linearly in both test receivers.

**Key words:** GNSS, power control, white Gaussian noise, FPGA.

## TABLE DES MATIÈRES

|                                                                                           | Page |

|-------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                        | 1    |

| <br>                                                                                      |      |

| CHAPITRE 1 LE SIMULATEUR DE SIGNAUX GNSS .....                                            | 3    |

| 1.1 Principe du positionnement par satellite .....                                        | 3    |

| 1.1.1 Principe de la trilateration .....                                                  | 3    |

| 1.1.2 Le positionnement par satellites .....                                              | 6    |

| 1.2 Spécifications des systèmes GPS et Galileo .....                                      | 8    |

| 1.2.1 Spécification du système GPS .....                                                  | 8    |

| 1.2.2 Spécifications du système Galileo .....                                             | 11   |

| 1.3 Présentation globale du simulateur de signaux GNSS .....                              | 14   |

| 1.4 Architecture du simulateur .....                                                      | 15   |

| 1.4.1 Partie logicielle .....                                                             | 16   |

| 1.4.2 Partie IF .....                                                                     | 18   |

| 1.4.3 Partie RF .....                                                                     | 18   |

| 1.5 Description de la partie RF du simulateur .....                                       | 18   |

| 1.6 Défauts reliés au design RF final .....                                               | 24   |

| 1.6.1 Défauts reliés au dessin du circuit imprimé .....                                   | 24   |

| 1.6.2 Défauts reliés aux choix des composants .....                                       | 26   |

| 1.7 Conclusion .....                                                                      | 28   |

| <br>                                                                                      |      |

| CHAPITRE 2 SYSTÈME DE CONTRÔLE DE PUISSANCE RF .....                                      | 29   |

| 2.1 Description du système de contrôle de puissance .....                                 | 29   |

| 2.2 Architecture et fonctionnement du système de contrôle de puissance .....              | 30   |

| 2.2.1 Calibration de la puissance .....                                                   | 33   |

| 2.2.2 Contrôle de gain .....                                                              | 35   |

| 2.2.3 Contrôle automatique de puissance .....                                             | 35   |

| 2.2.4 Contrôle de puissance dans le temps .....                                           | 37   |

| 2.3 Choix des composants pour la réalisation du système de contrôle de puissance .....    | 38   |

| 2.3.1 Les coupleurs .....                                                                 | 39   |

| 2.3.2 Le détecteur de puissance .....                                                     | 42   |

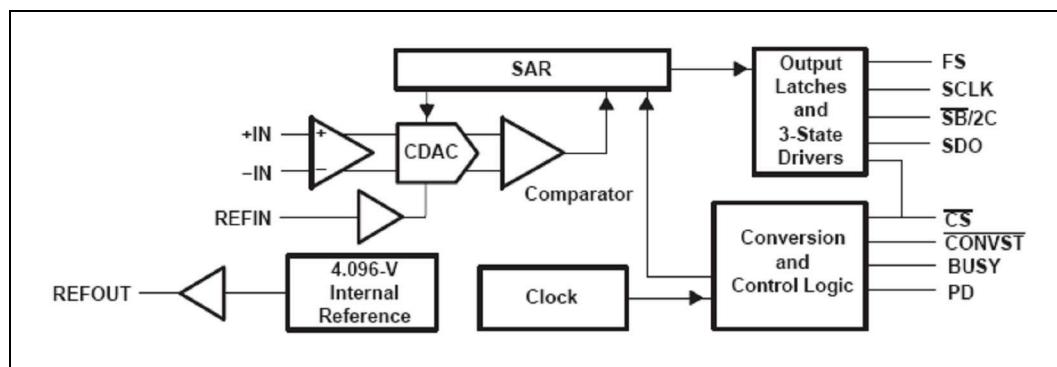

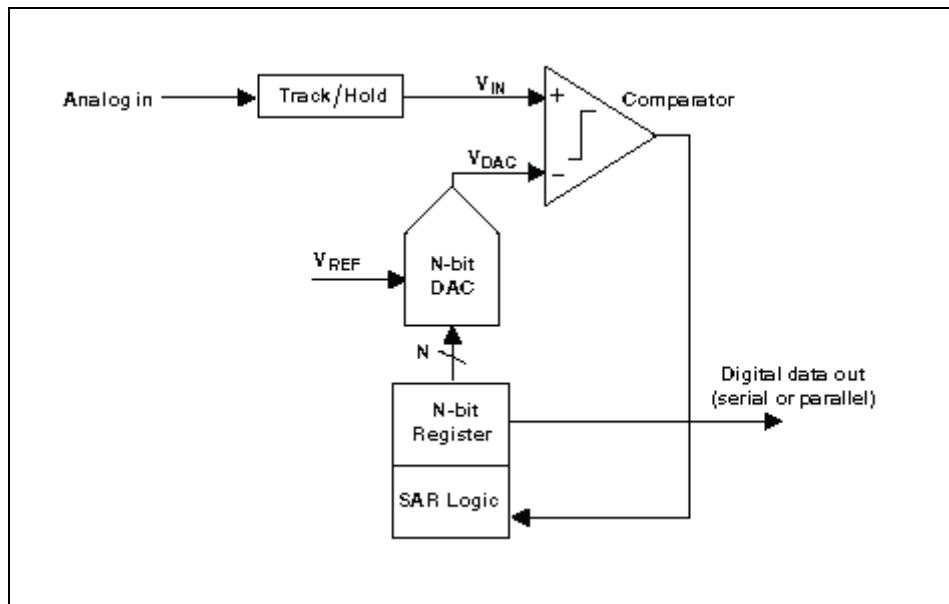

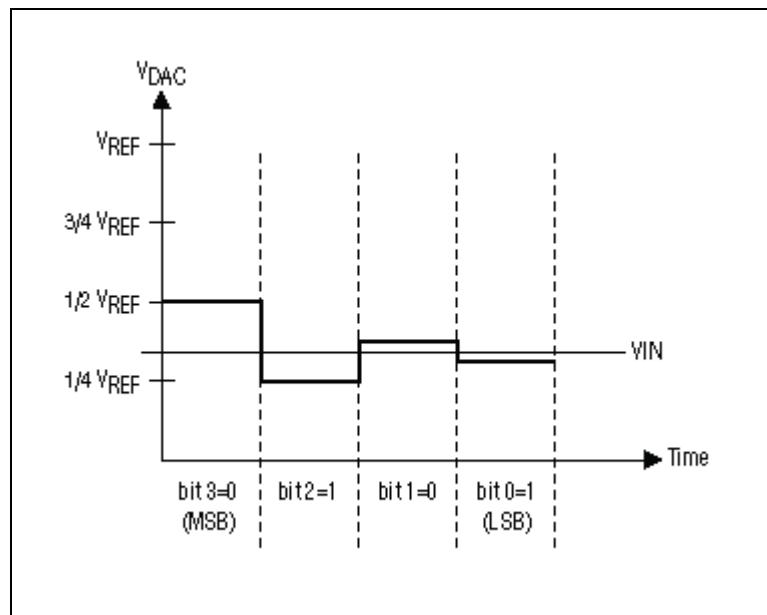

| 2.3.3 Le convertisseur analogique numérique .....                                         | 44   |

| 2.3.4 Le convertisseur numérique analogique .....                                         | 44   |

| 2.3.5 Le CPLD .....                                                                       | 45   |

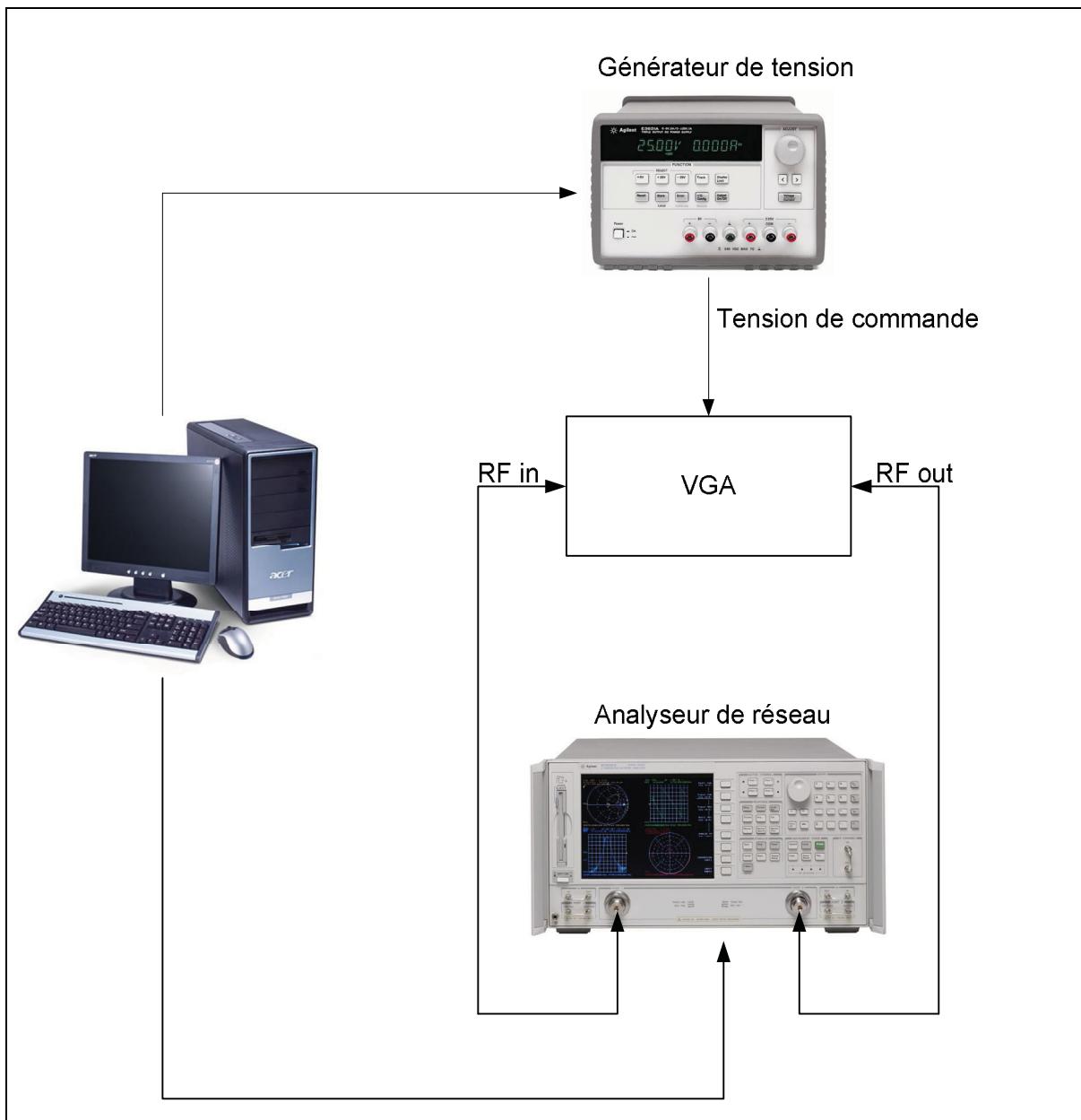

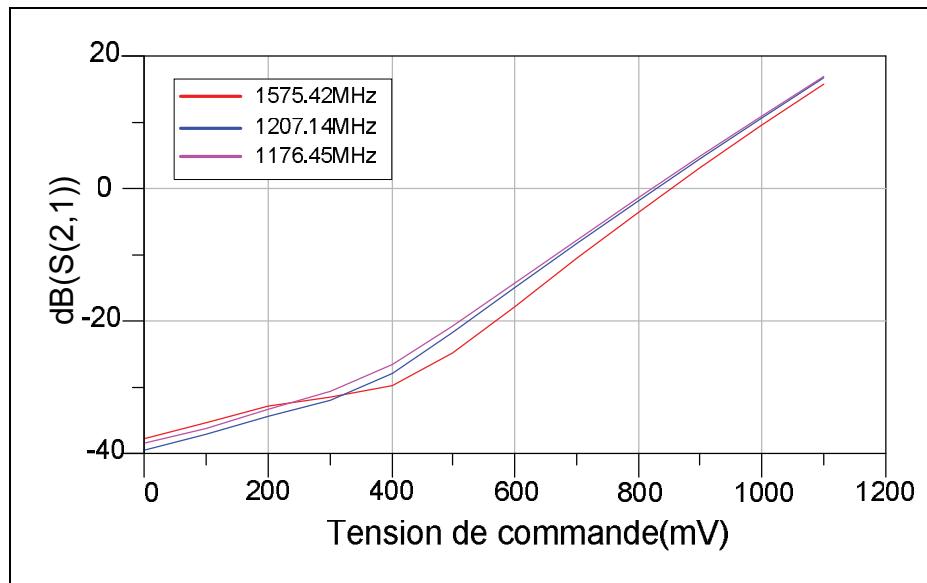

| 2.3.6 Le VGA .....                                                                        | 45   |

| 2.4 Algorithmes de contrôle de puissance .....                                            | 48   |

| 2.4.1 Algorithme N° 1 .....                                                               | 48   |

| 2.4.2 Algorithme N° 2 .....                                                               | 50   |

| 2.5 Communication entre la partie logicielle et le système de contrôle de puissance ..... | 52   |

| 2.5.1 Protocole de communication du système de contrôle de puissance .....                | 52   |

| 2.5.2 Communication entre la partie logicielle et la partie IF .....                      | 56   |

| 2.5.3 Communication entre la partie IF et la partie RF .....                              | 57   |

|                                                                                      |                                                                                |            |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------|

| 2.6                                                                                  | Interface d'utilisation du système de contrôle de puissance .....              | 58         |

| 2.7                                                                                  | Validation du système de contrôle de puissance .....                           | 61         |

| 2.7.1                                                                                | Validation des composants du système de contrôle de puissance.....             | 61         |

| 2.7.2                                                                                | Validation de la communication entre la partie logicielle et la partie RF .... | 62         |

| 2.7.3                                                                                | Validation du fonctionnement du système de contrôle de puissance .....         | 63         |

| 2.8                                                                                  | Conclusion.....                                                                | 71         |

| <b>CHAPITRE 3 SYSTÈME DE CONTRÔLE DU RAPPORT C/N<sub>0</sub> .....</b>               |                                                                                | <b>72</b>  |

| 3.1                                                                                  | Principe du contrôle du rapport C/N <sub>0</sub> .....                         | 72         |

| 3.1.1                                                                                | Définition du rapport C/N <sub>0</sub> .....                                   | 72         |

| 3.1.2                                                                                | Fonctionnement du système de contrôle du rapport C/N <sub>0</sub> .....        | 73         |

| 3.1.3                                                                                | Interface graphique de l'usager .....                                          | 75         |

| 3.2                                                                                  | Survol de notions sur le bruit.....                                            | 75         |

| 3.2.1                                                                                | Fonction d'autocorrélation.....                                                | 76         |

| 3.2.2                                                                                | Processus stationnaire au sens large .....                                     | 77         |

| 3.2.3                                                                                | Densité spectrale de puissance .....                                           | 77         |

| 3.2.4                                                                                | Le bruit blanc .....                                                           | 77         |

| 3.3                                                                                  | Solutions d'implémentation d'un bruit banc .....                               | 78         |

| 3.3.1                                                                                | Implémentation analogique.....                                                 | 79         |

| 3.3.2                                                                                | Implémentation numérique .....                                                 | 80         |

| 3.4                                                                                  | Génération d'un bruit blanc gaussien.....                                      | 81         |

| 3.4.1                                                                                | Variable aléatoire gaussienne.....                                             | 81         |

| 3.4.2                                                                                | Algorithmes de génération de variables aléatoires gaussiennes .....            | 84         |

| 3.5                                                                                  | Implémentation du générateur de bruit blanc gaussien.....                      | 98         |

| 3.5.1                                                                                | Quantification des fonctions $f$ et $g$ .....                                  | 99         |

| 3.5.2                                                                                | Génération des variables aléatoires uniformes.....                             | 101        |

| 3.5.3                                                                                | Architecture du générateur de bruit blanc gaussien .....                       | 105        |

| 3.5.4                                                                                | Optimisation de l'architecture du générateur de bruit blanc gaussien.....      | 110        |

| 3.6                                                                                  | Validation du système de contrôle du ratio C/N <sub>0</sub> .....              | 113        |

| 3.6.1                                                                                | Le spectre du bruit généré .....                                               | 113        |

| 3.6.2                                                                                | Plage de contrôle de la densité du bruit .....                                 | 116        |

| 3.6.3                                                                                | Validation du contrôle de bruit avec les récepteurs.....                       | 116        |

| 3.7                                                                                  | Conclusion.....                                                                | 121        |

| <b>CONCLUSION</b>                                                                    |                                                                                | <b>122</b> |

| <b>ANNEXE I Détails sur les composants du système de contrôle de puissance .....</b> |                                                                                | <b>124</b> |

| <b>ANNEXE II Les ADC de type SAR .....</b>                                           |                                                                                | <b>136</b> |

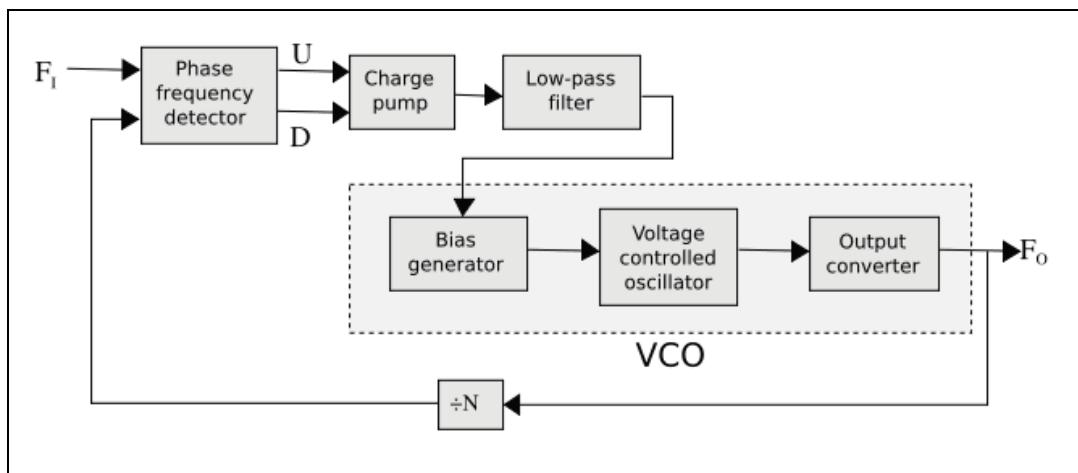

| <b>ANNEXE III Boucle à verrouillage de phase .....</b>                               |                                                                                | <b>138</b> |

| <b>ANNEXE IV Matrice de transition du LP-LFSR .....</b>                              |                                                                                | <b>141</b> |

| <b>ANNEXE V Registres utilisés .....</b>                                             |                                                                                | <b>142</b> |

|                                                                                    |     |

|------------------------------------------------------------------------------------|-----|

| ANNEXE VI Schémas électriques des cartes du système de contrôle de puissance ..... | 143 |

| ANNEXE VII Procédure de test du CAN .....                                          | 147 |

| BIBLIOGRAPHIE .....                                                                | 149 |

## LISTE DES TABLEAUX

|             | Page                                                                                                                                   |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 1.1 | Caractéristiques physiques des signaux GPS .....                                                                                       | 10  |

| Tableau 1.2 | Fréquences porteuses des signaux Galileo.....                                                                                          | 13  |

| Tableau 1.3 | Bande de réception et polarisation des signaux Galileo .....                                                                           | 14  |

| Tableau 2.1 | Niveaux de puissance des signaux GPS et Galileo à la réception.....                                                                    | 30  |

| Tableau 2.2 | Caractéristiques du substrat RO3006.....                                                                                               | 40  |

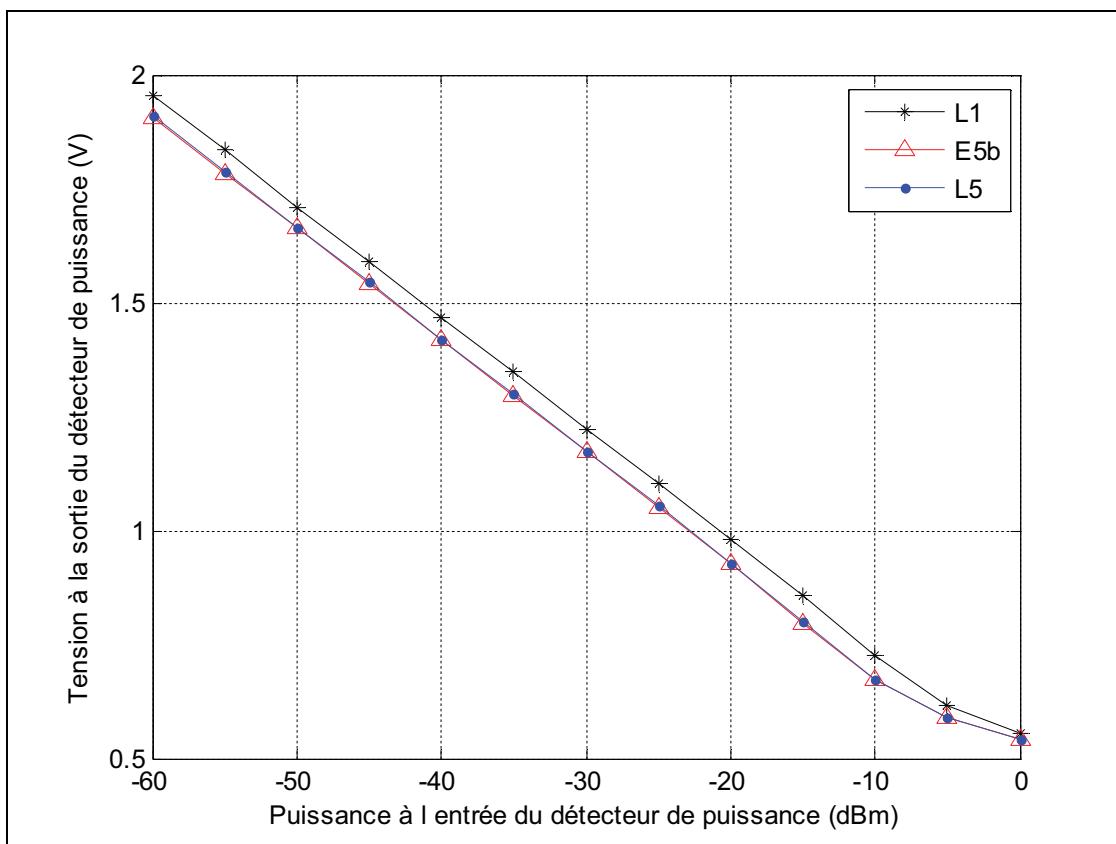

| Tableau 2.3 | Les pentes et les points d'intersectioins avec l'axe des abscisses de la réponse du détecteur de puissance pour les trois signaux..... | 43  |

| Tableau 2.4 | Table de vérité des bits de commande .....                                                                                             | 53  |

| Tableau 2.5 | Table de vérité des bits de choix des signaux .....                                                                                    | 54  |

| Tableau 3.1 | Propriétés d'un bruit blanc .....                                                                                                      | 78  |

| Tableau 3.2 | Fonctions utilisées dans les algorithmes Ziggurat et Box-Muller .....                                                                  | 95  |

| Tableau 3.3 | Probabilité d'apparition des valeurs au-delà de $4\sigma$ pour la loi normale centrée réduite .....                                    | 97  |

| Tableau 3.4 | Paramètres optimaux pour la génération des tables de la méthode Box-Muller .....                                                       | 105 |

## LISTE DES FIGURES

|             | Page                                                              |    |

|-------------|-------------------------------------------------------------------|----|

| Figure 1.1  | Principe de la trilateration en 2D.....                           | 4  |

| Figure 1.2  | Principe de la trilateration en 3D.....                           | 5  |

| Figure 1.3  | L'effet des erreurs sur la trilateration.....                     | 6  |

| Figure 1.4  | Constellation des satellites du système GPS.....                  | 9  |

| Figure 1.5  | Le plan de fréquence des signaux GPS.....                         | 11 |

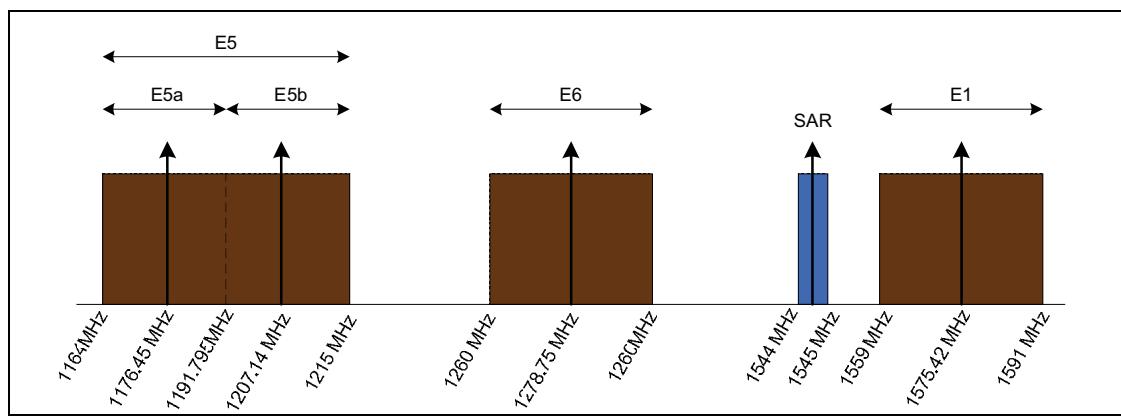

| Figure 1.6  | Plan de fréquence Galileo.....                                    | 13 |

| Figure 1.7  | Structure du simulateur GNSS.....                                 | 15 |

| Figure 1.8  | Le simulateur GNSS du LACIME.....                                 | 16 |

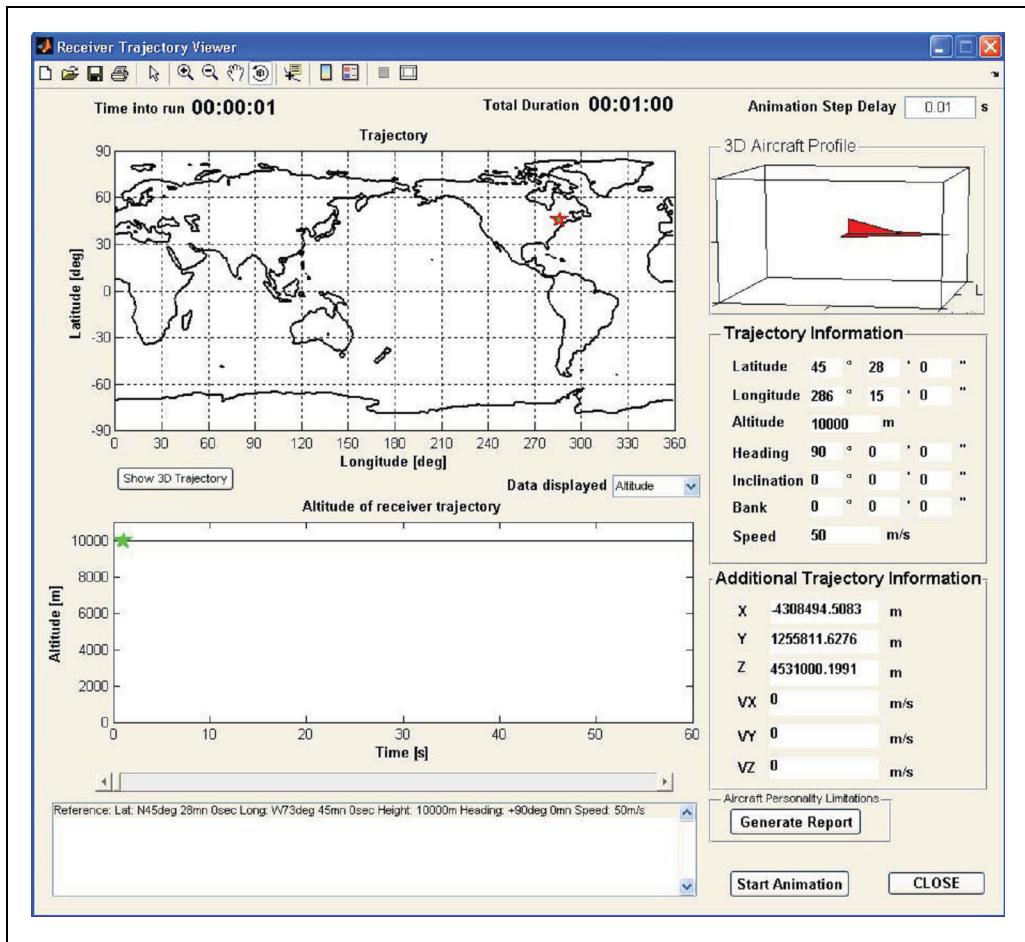

| Figure 1.9  | Interface principale du simulateur.....                           | 17 |

| Figure 1.10 | Interface du simulateur de trajectoire.....                       | 17 |

| Figure 1.11 | Architecture de la partie RF du simulateur.....                   | 20 |

| Figure 1.12 | Plateforme RF modulaire.....                                      | 23 |

| Figure 1.13 | Carte RF finale.....                                              | 24 |

| Figure 1.14 | Défauts de dessin du circuit imprimé.....                         | 26 |

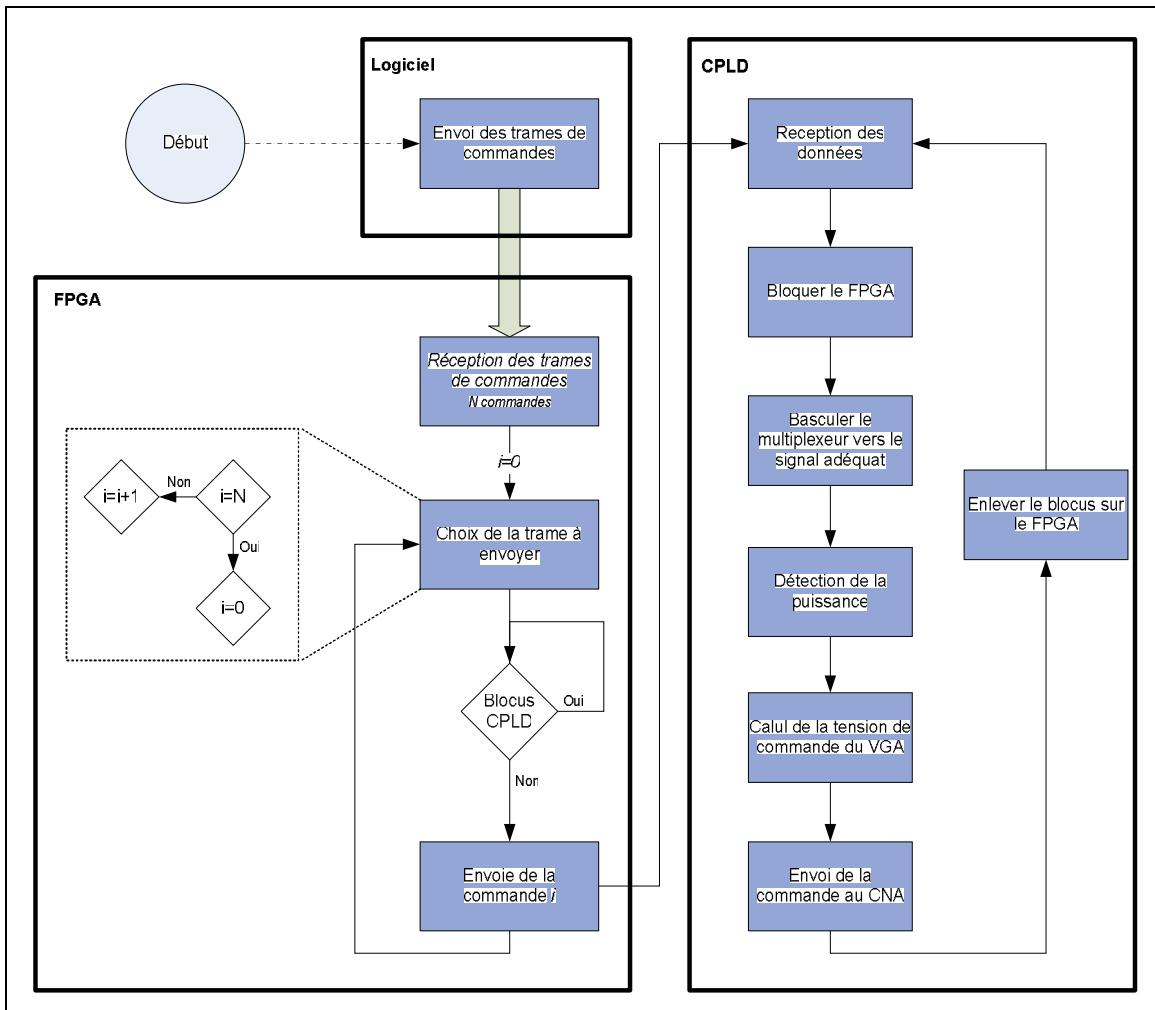

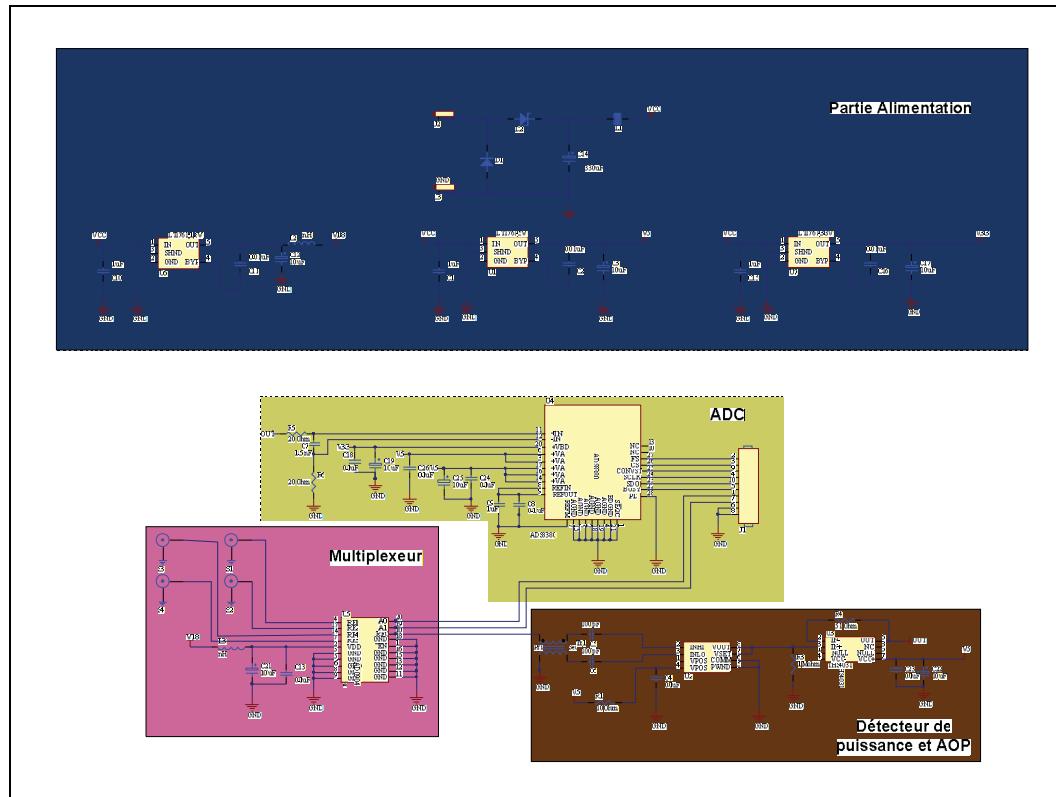

| Figure 2.1  | Architecture du système de contrôle de gain.....                  | 32 |

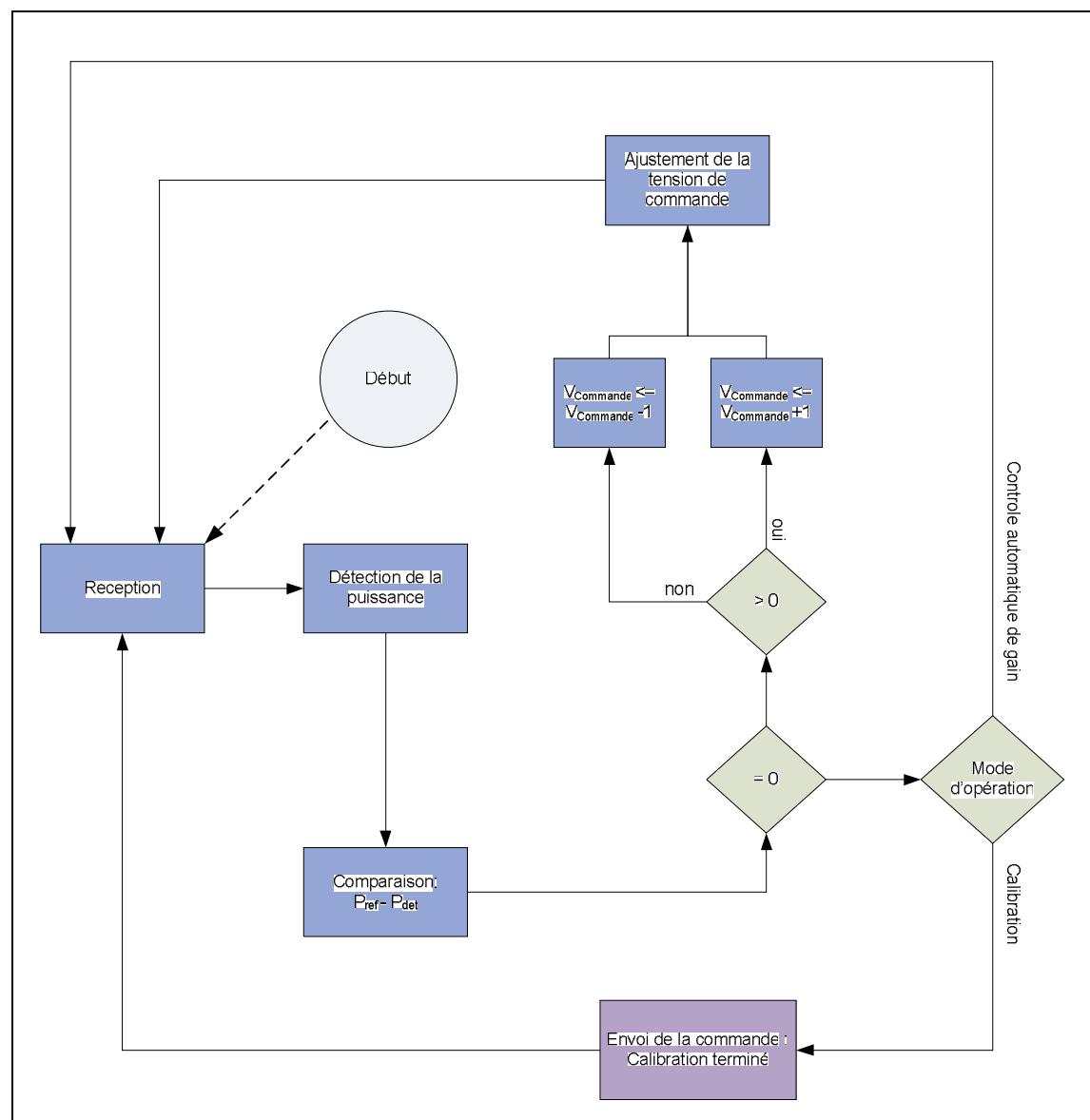

| Figure 2.2  | Fonctionnement du mode « Calibration ».....                       | 34 |

| Figure 2.3  | Fonctionnement du mode « contrôle de gain ».....                  | 35 |

| Figure 2.4  | Fonctionnement du mode « contrôle automatique de puissance »..... | 37 |

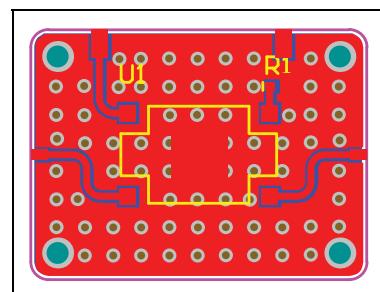

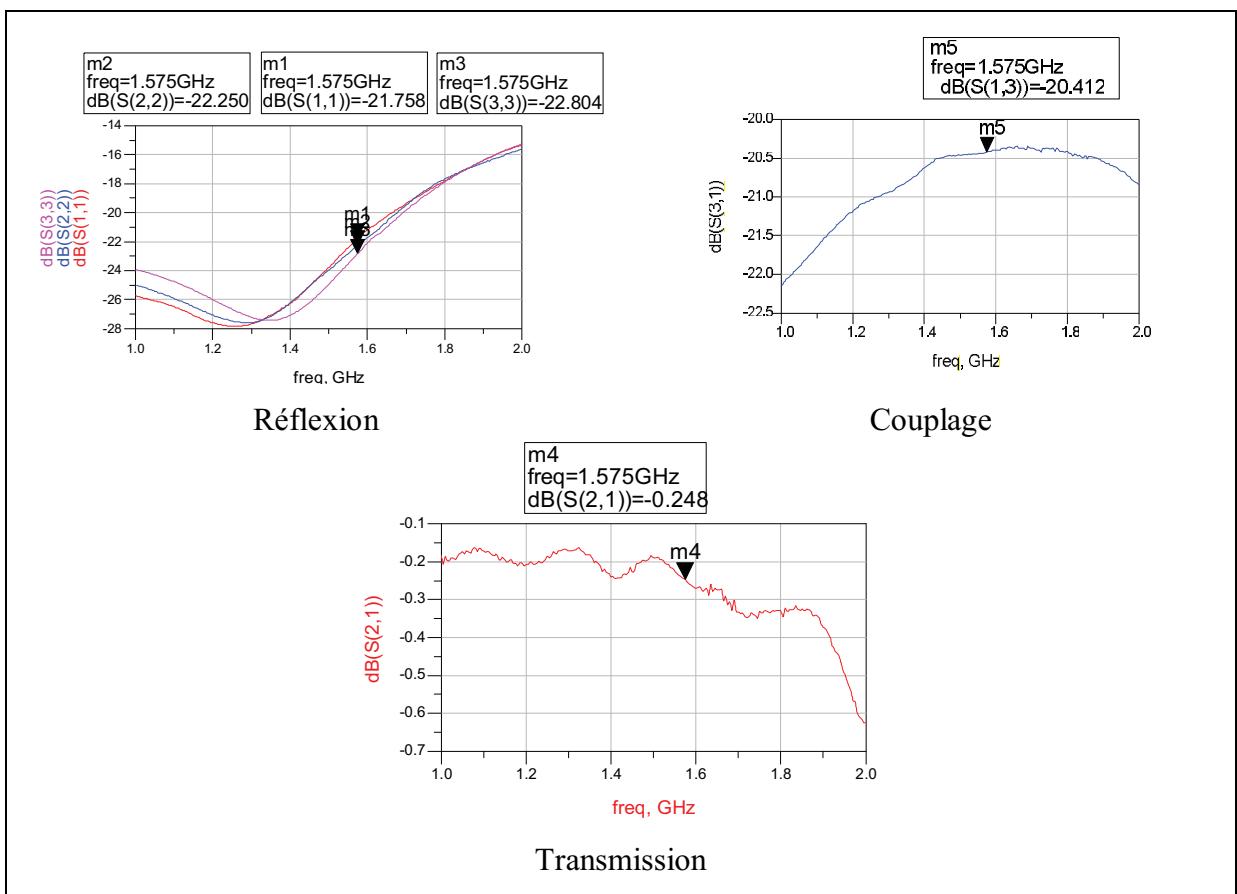

| Figure 2.5  | PCB de test des coupleurs.....                                    | 39 |

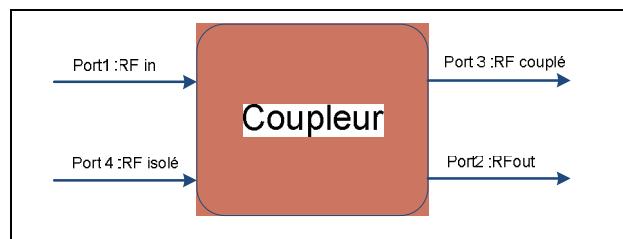

| Figure 2.6  | Schéma bloc des coupleurs.....                                    | 40 |

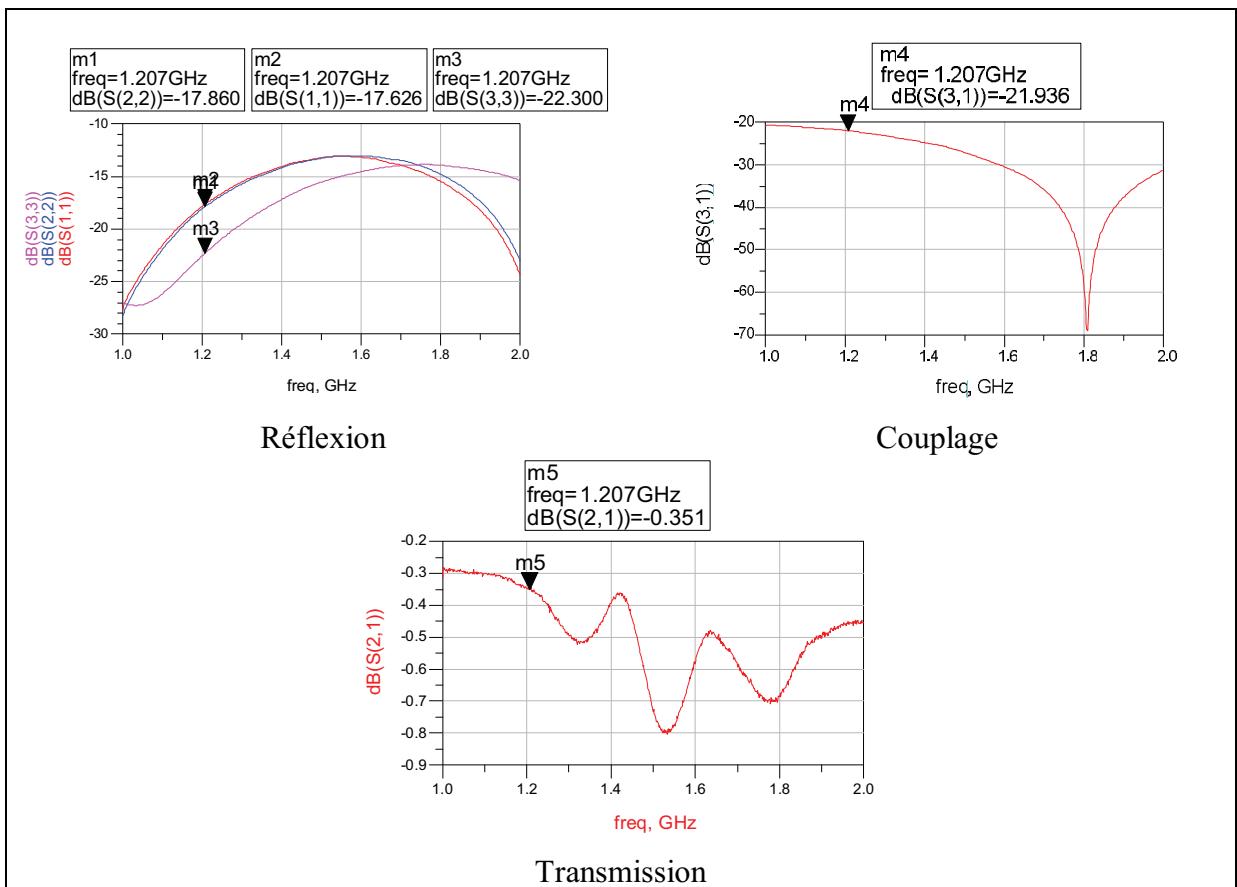

| Figure 2.7  | Paramètres « S » du coupleur XC0900A-20S.....                     | 41 |

| Figure 2.8  | Paramètres « S » du coupleur XC1900A-20S.....                     | 42 |

|             |                                                                                                 |    |

|-------------|-------------------------------------------------------------------------------------------------|----|

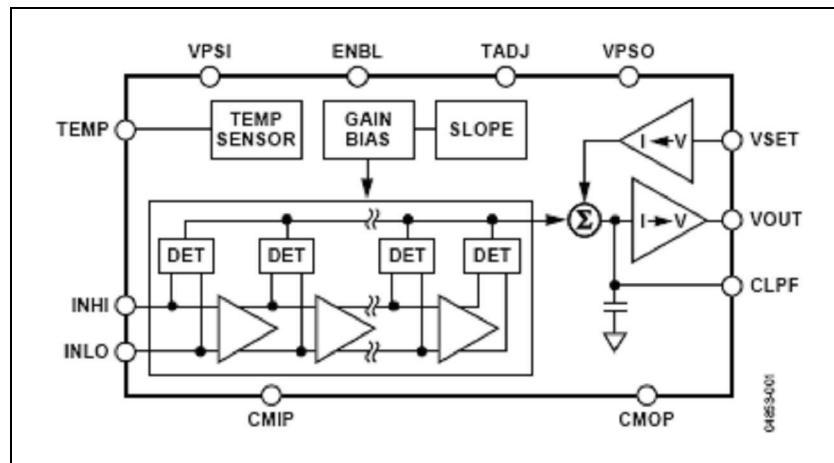

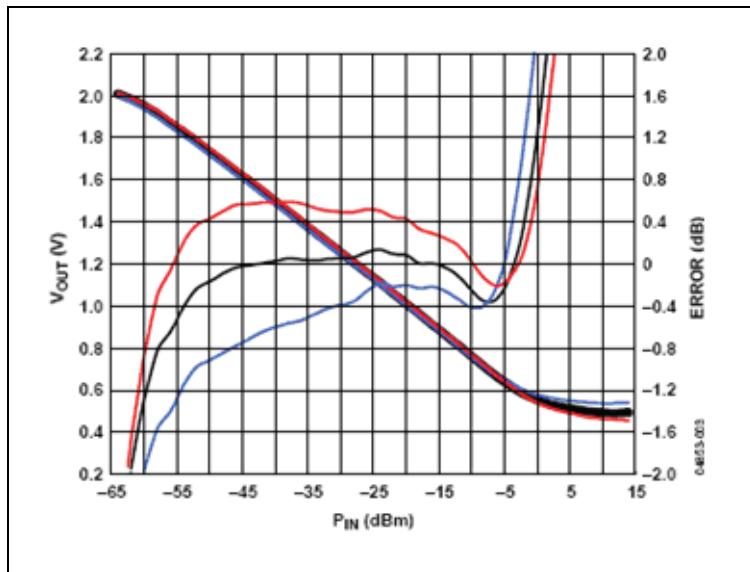

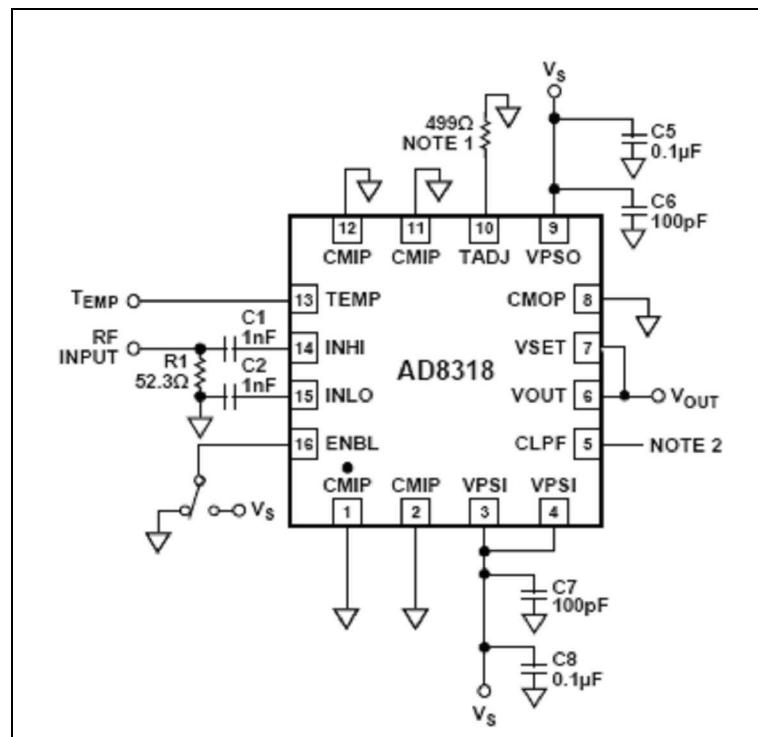

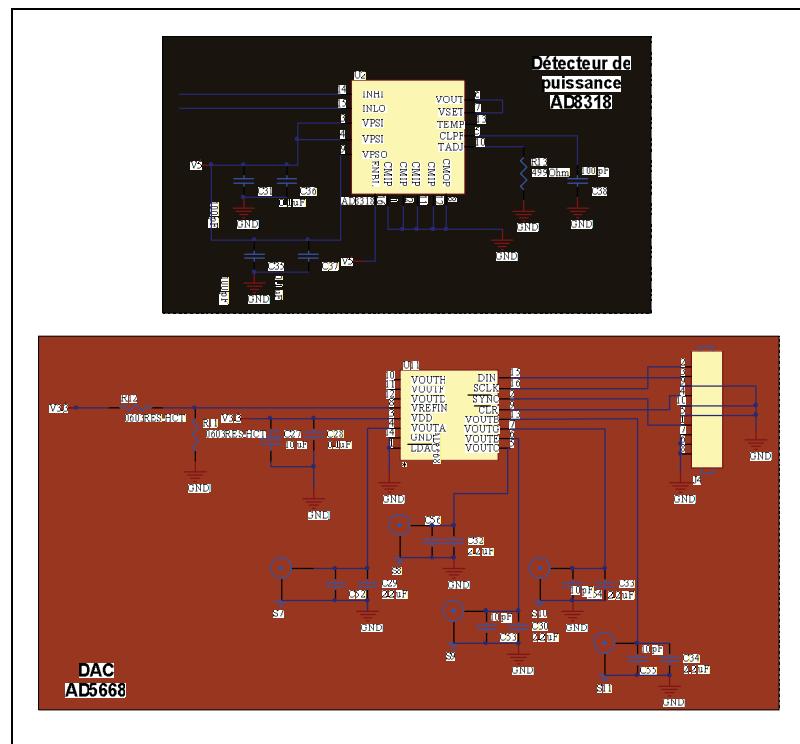

| Figure 2.9  | Réponse du détecteur de puissance AD8318. ....                                                  | 43 |

| Figure 2.10 | Montage de test du VGA. ....                                                                    | 46 |

| Figure 2.11 | Réponse du VGA pour les fréquences GPS et Galileo. ....                                         | 47 |

| Figure 2.12 | Mode de fonctionnement du deuxième algorithme. ....                                             | 51 |

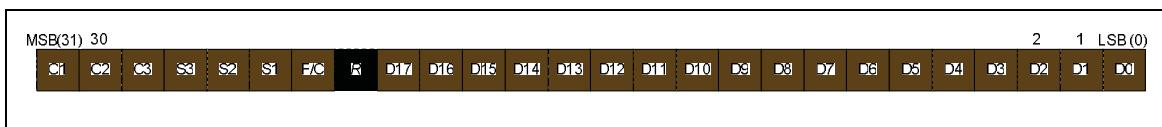

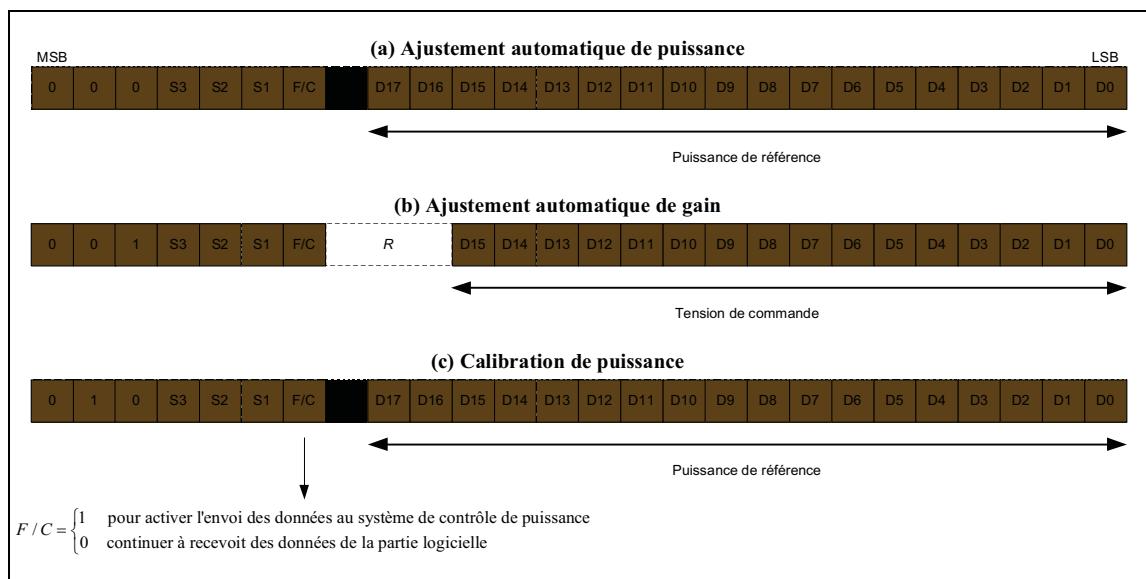

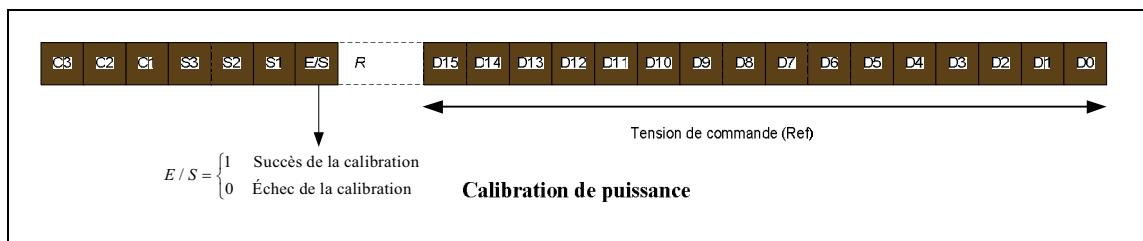

| Figure 2.13 | Trame de communication générique entre le FPGA et la partie RF. ....                            | 53 |

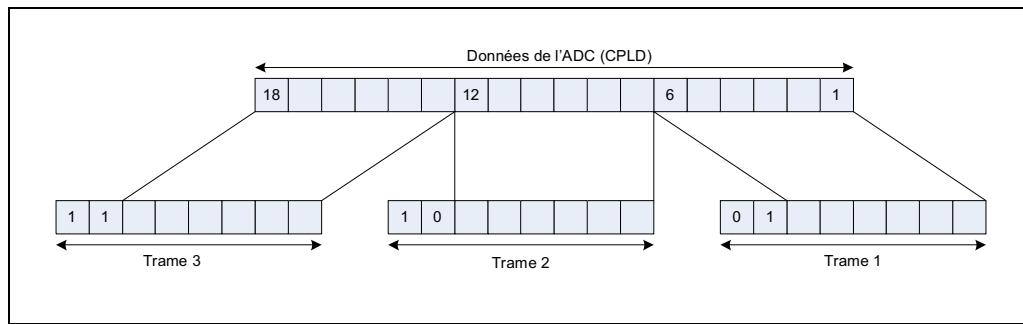

| Figure 2.14 | Trame de communication du FPGA vers le CPLD. ....                                               | 55 |

| Figure 2.15 | Trame de communication du FPGA vers le CPLD. ....                                               | 56 |

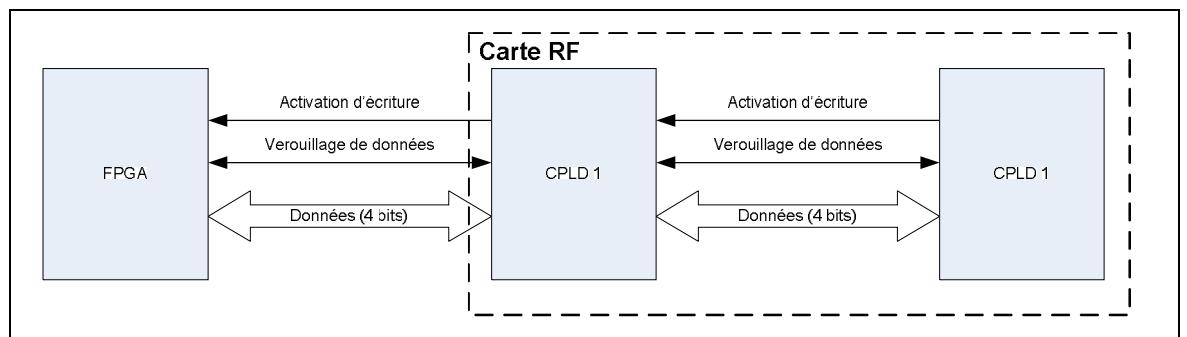

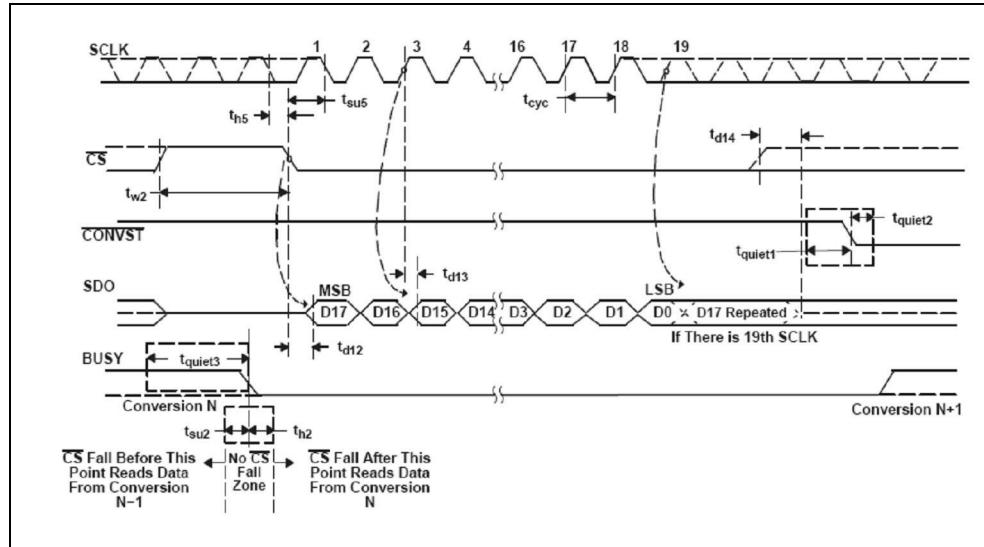

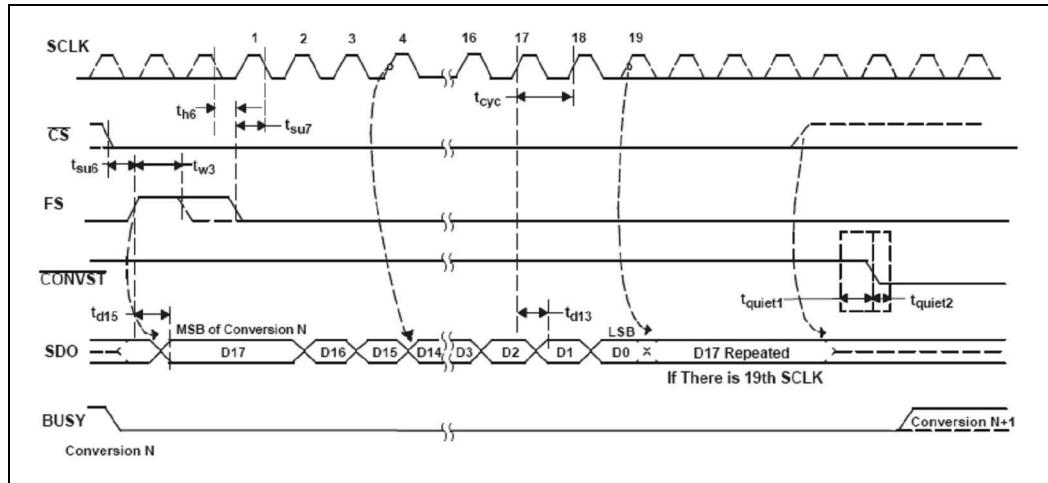

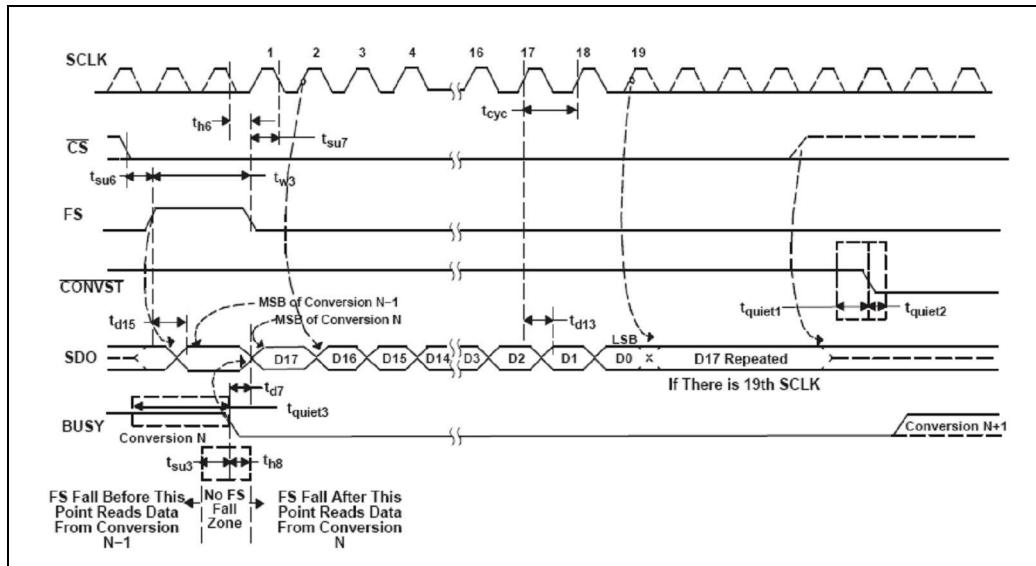

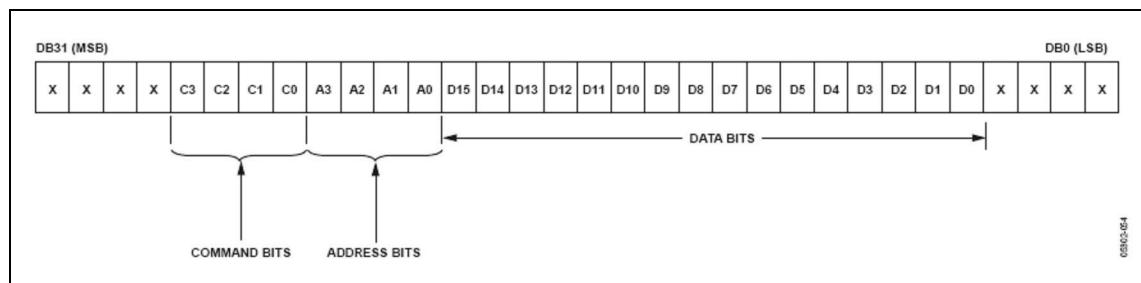

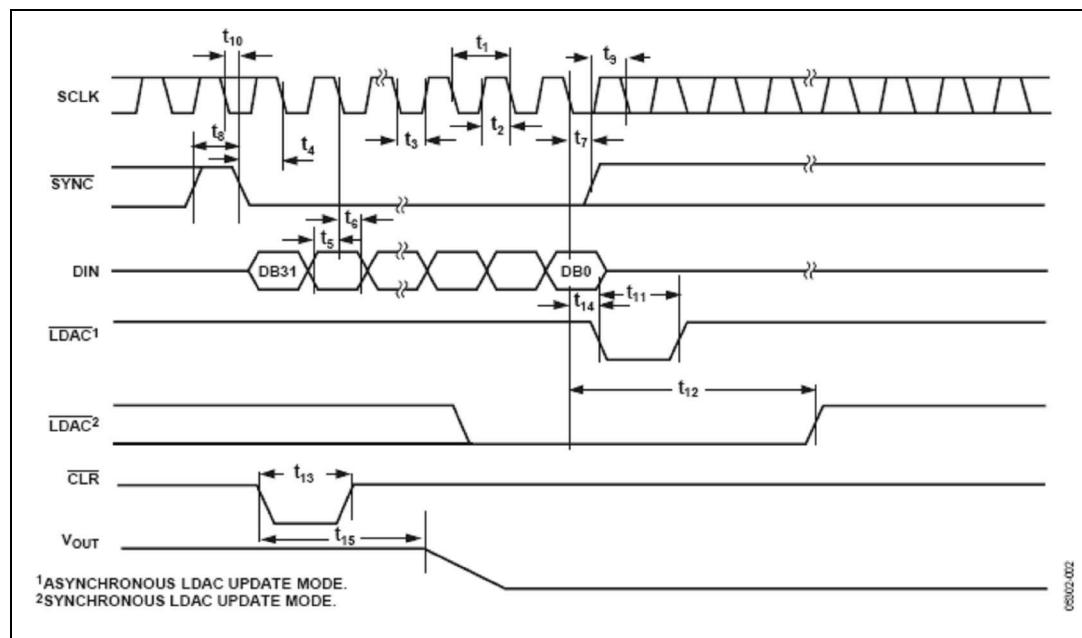

| Figure 2.16 | Signaux de communication entre la partie IF et la partie RF. ....                               | 58 |

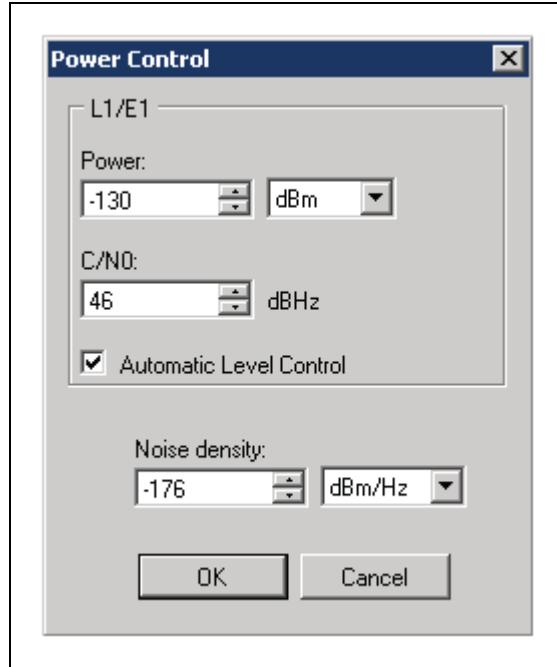

| Figure 2.17 | Interface de contrôle de puissance. ....                                                        | 59 |

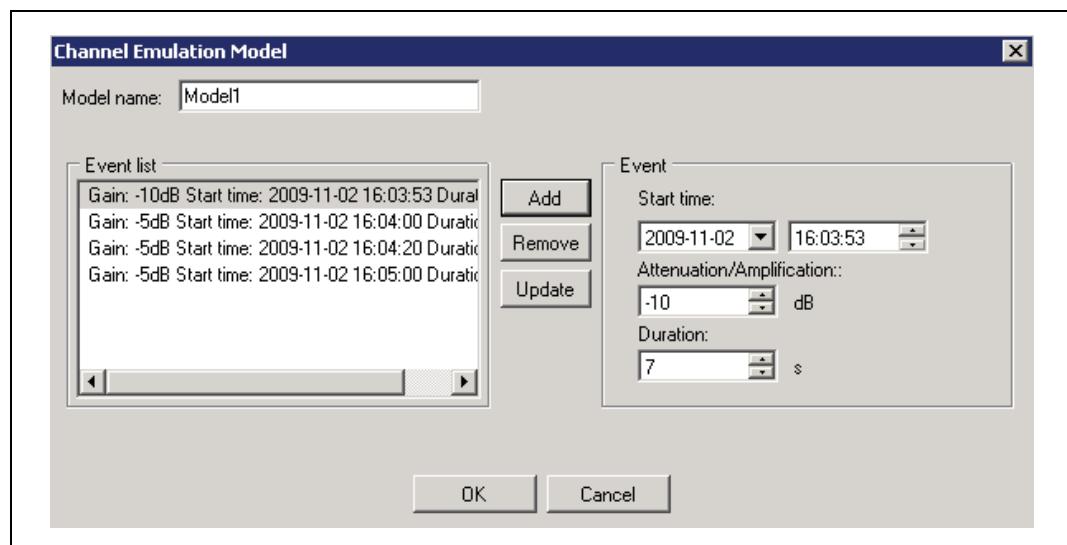

| Figure 2.18 | Interface de création d'un mode de contrôle de puissance dans le temps.                         | 60 |

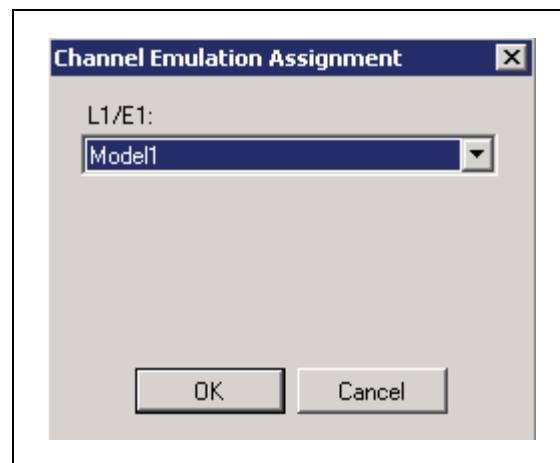

| Figure 2.19 | Interface d'assignation d'un modèle à un signal. ....                                           | 60 |

| Figure 2.20 | Transfert des données du CPLD au PC. ....                                                       | 62 |

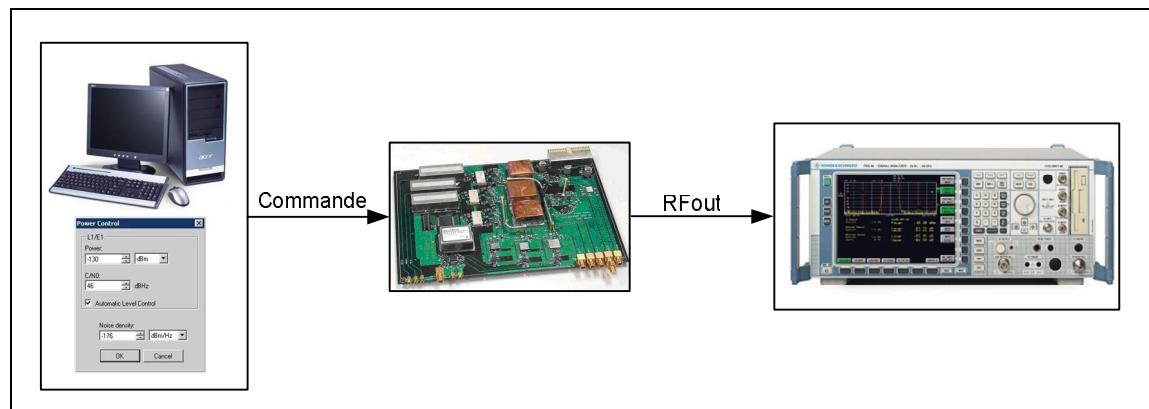

| Figure 2.21 | Montage de validation du système de contrôle de puissance. ....                                 | 63 |

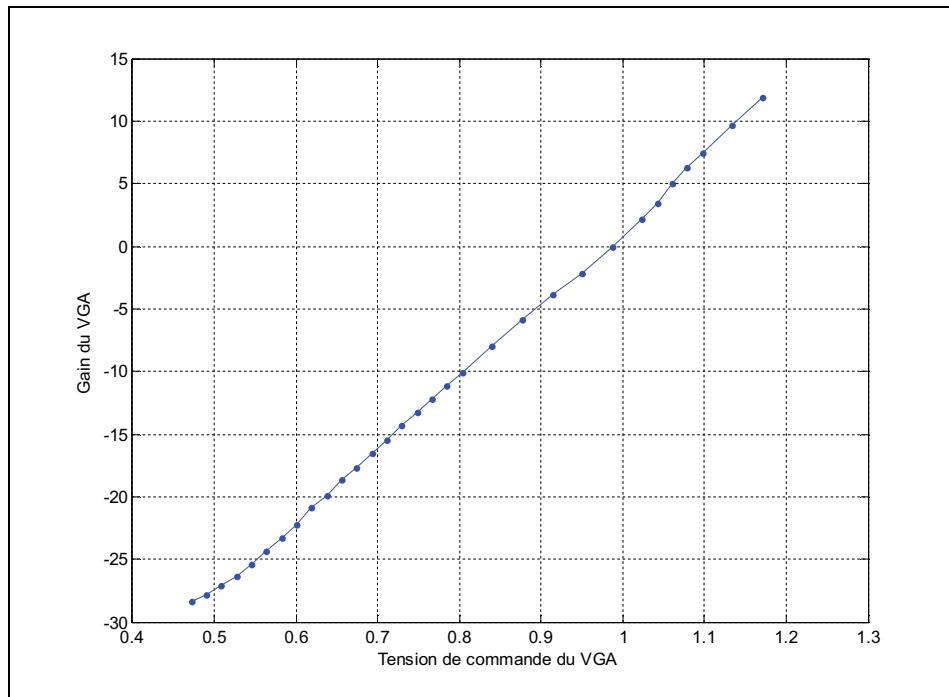

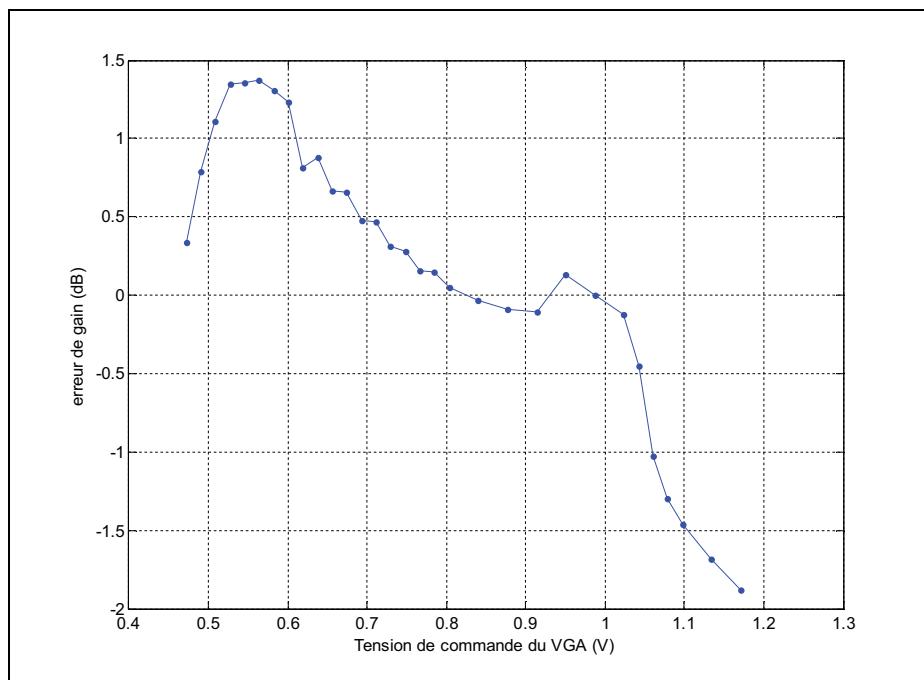

| Figure 2.22 | Réponse du VGA pour le signal L1/E1. ....                                                       | 64 |

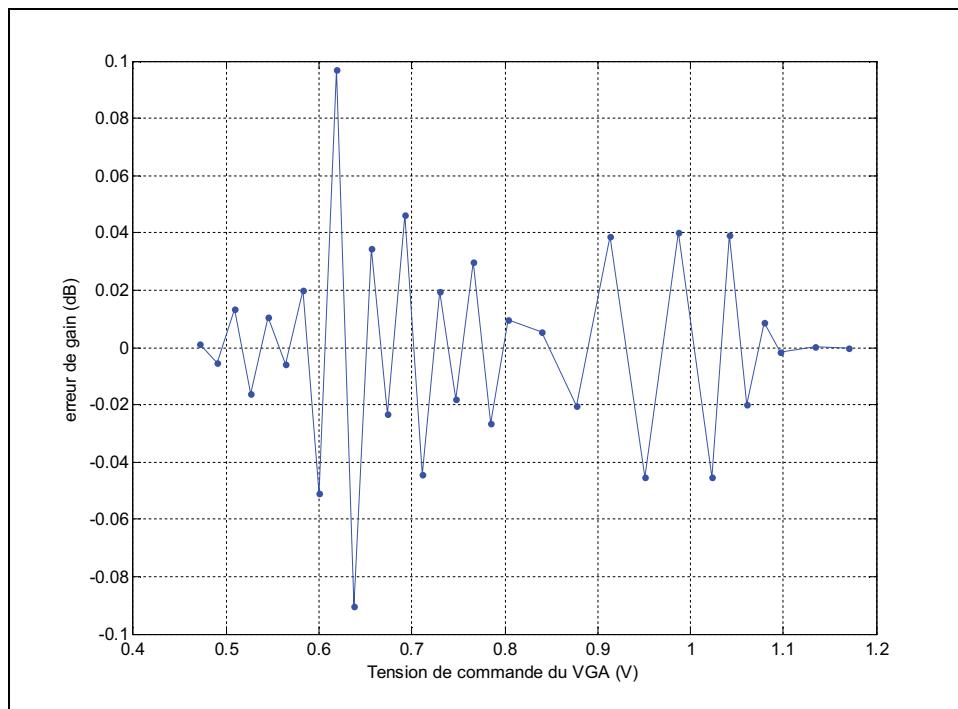

| Figure 2.23 | Erreur de gain du VGA avant correction. ....                                                    | 65 |

| Figure 2.24 | Erreur de gain du VGA après correction. ....                                                    | 65 |

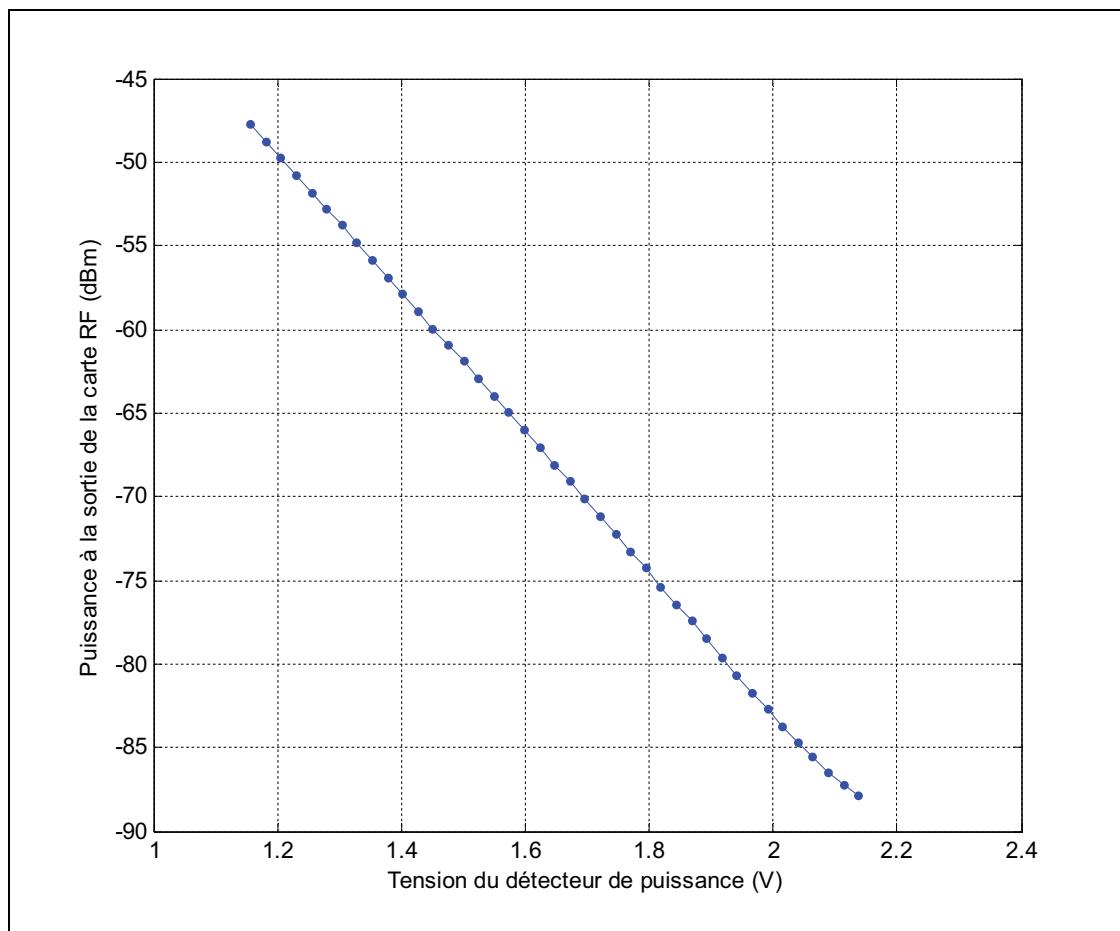

| Figure 2.25 | Réponse du système de contrôle de puissance en mode « contrôle automatique de puissance ». .... | 66 |

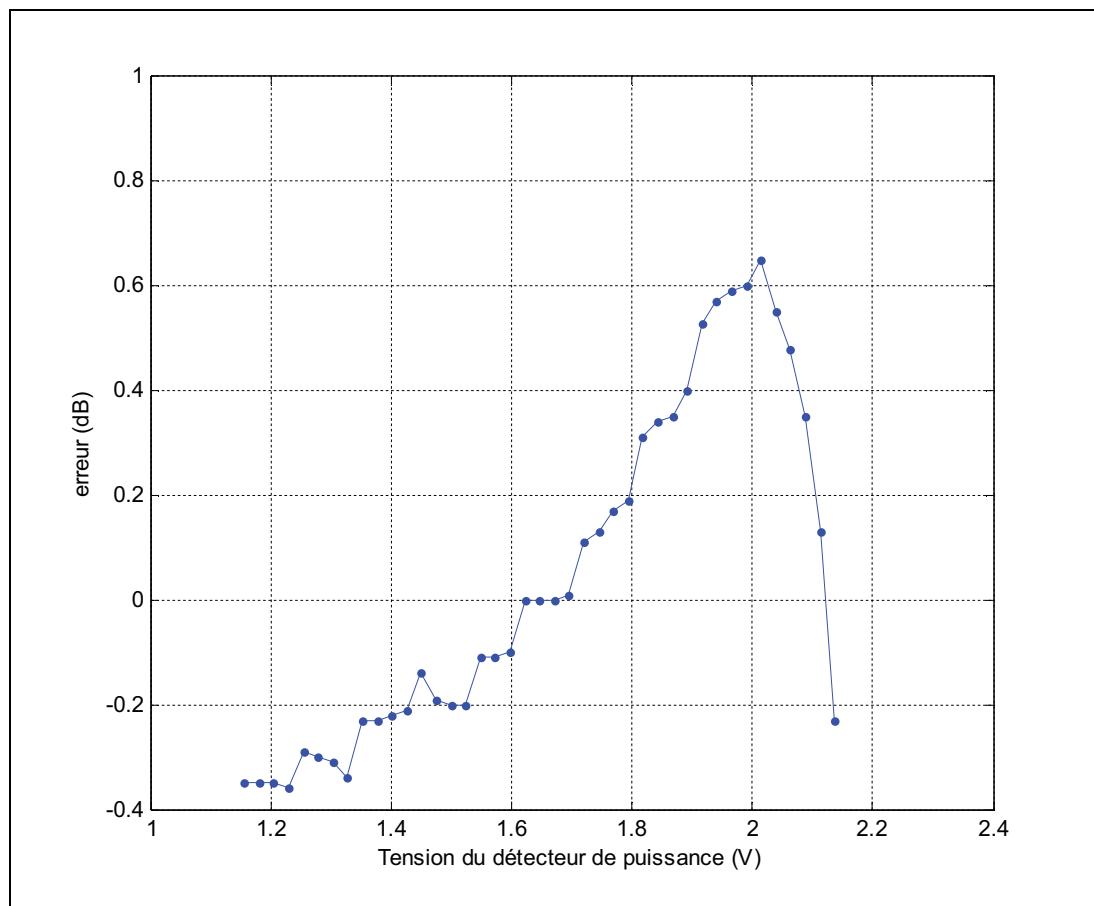

| Figure 2.26 | Erreur entre la puissance mesurée et la puissance théorique. ....                               | 67 |

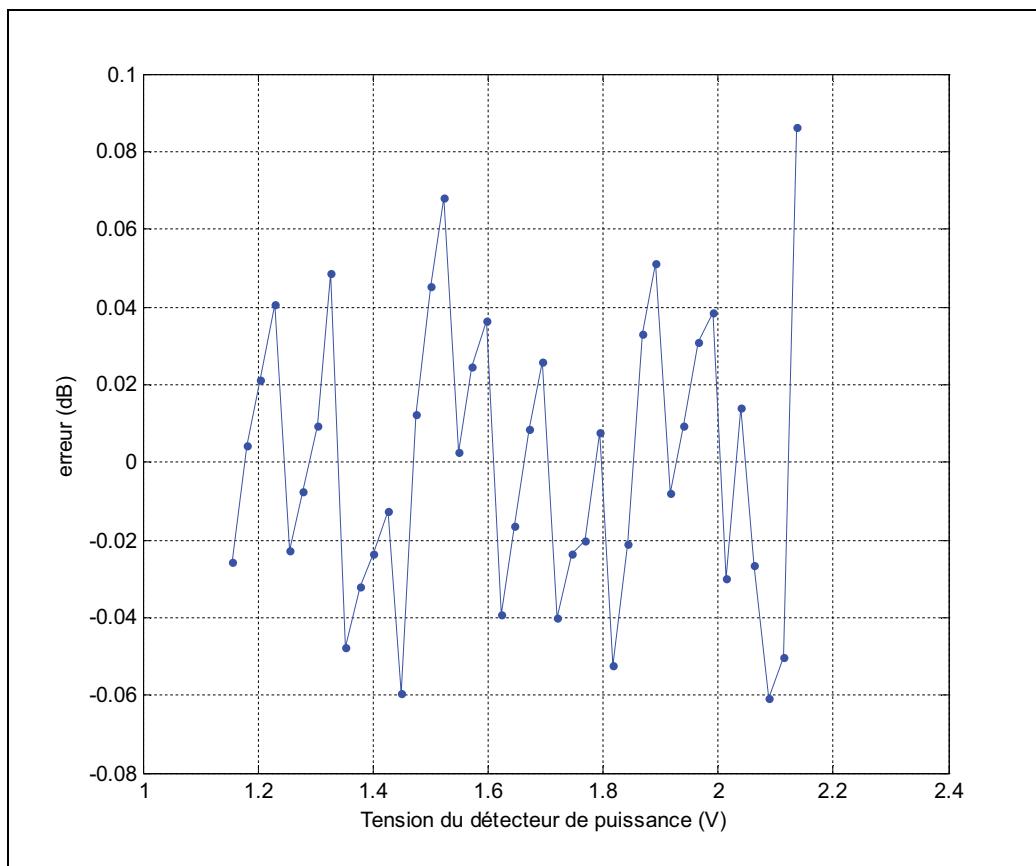

| Figure 2.27 | Erreur de puissance entre les valeurs corrigées et théoriques. ....                             | 68 |

| Figure 2.28 | Réponse du système de contrôle de puissance avec un récepteur GPS commercial. ....              | 70 |

| Figure 2.29 | Erreur entre les valeurs du ratio C/N <sub>0</sub> observées et les valeurs théoriques. ....    | 70 |

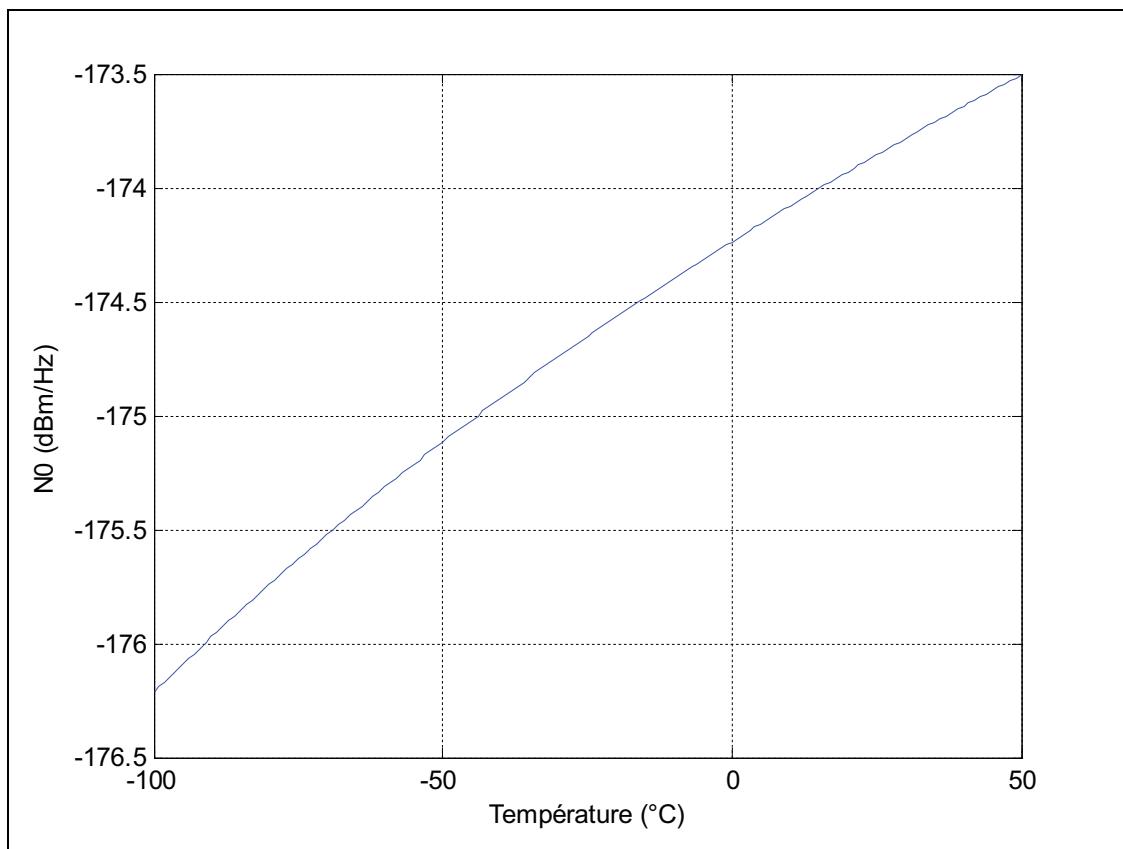

| Figure 3.1  | Effet de la température sur la densité du bruit thermique. ....                                 | 74 |

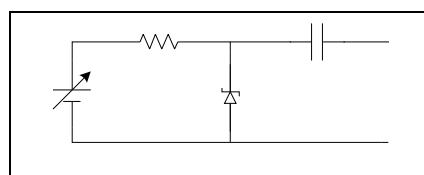

| Figure 3.2  | Générateur d'un bruit analogique simple. ....                                                   | 79 |

|             |                                                                                                                                                                                                                                      |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

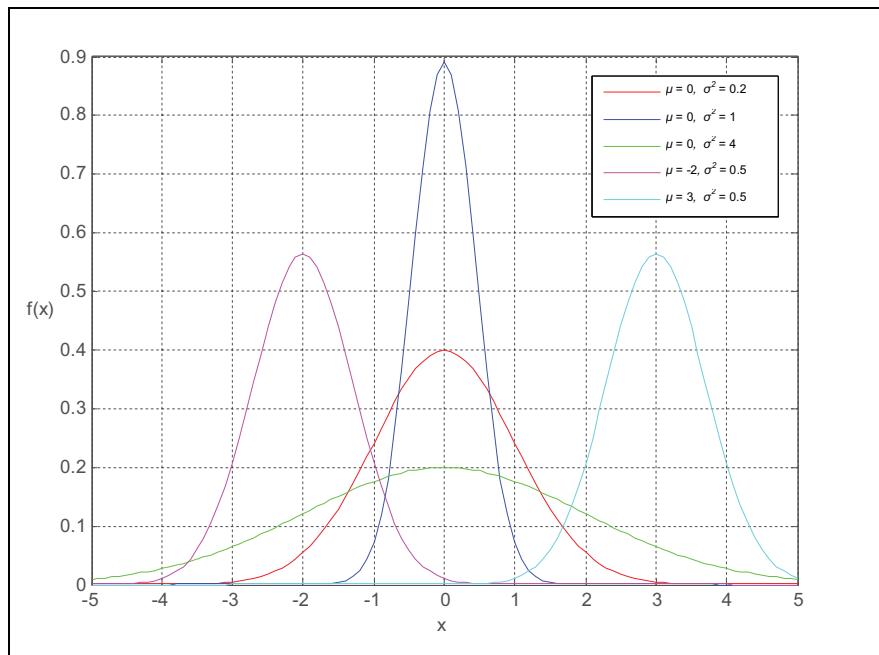

| Figure 3.3  | Densité de probabilité de la loi normale. ....                                                                                                                                                                                       | 82  |

| Figure 3.4  | Exemple d'illustration du théorème de la limite centrale. ....                                                                                                                                                                       | 84  |

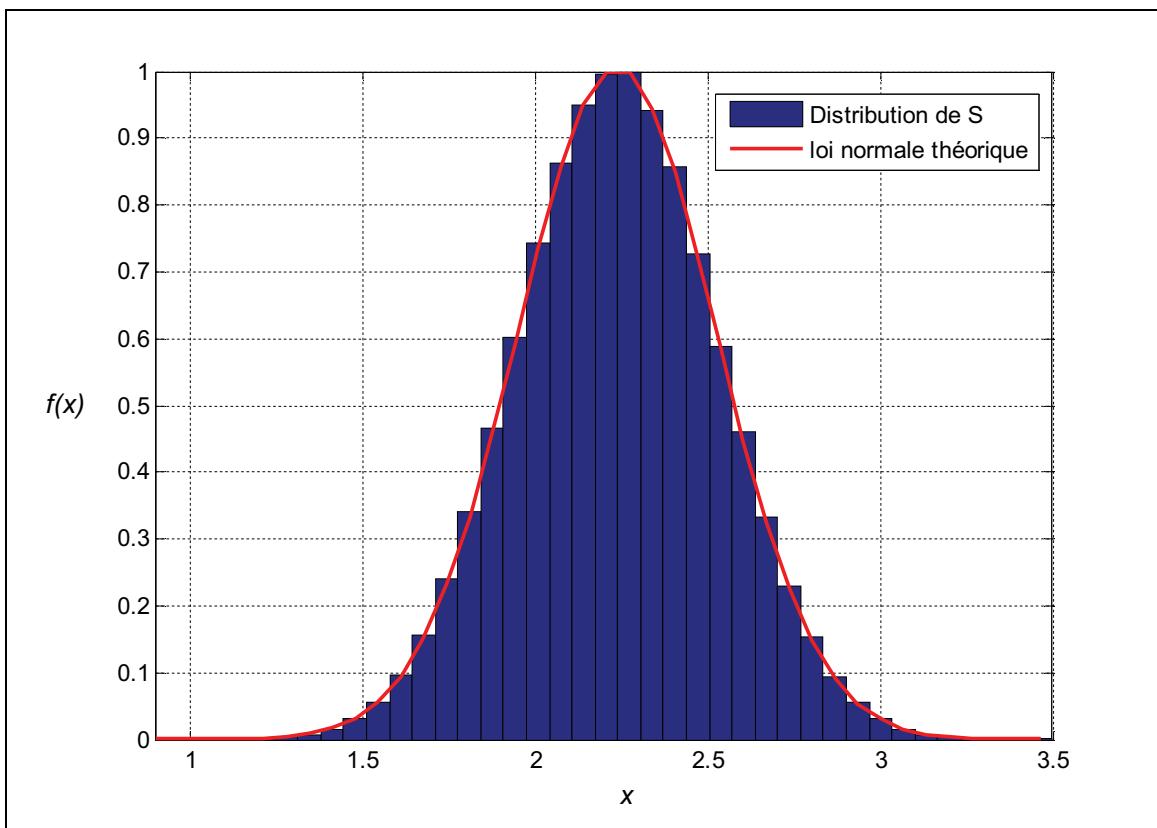

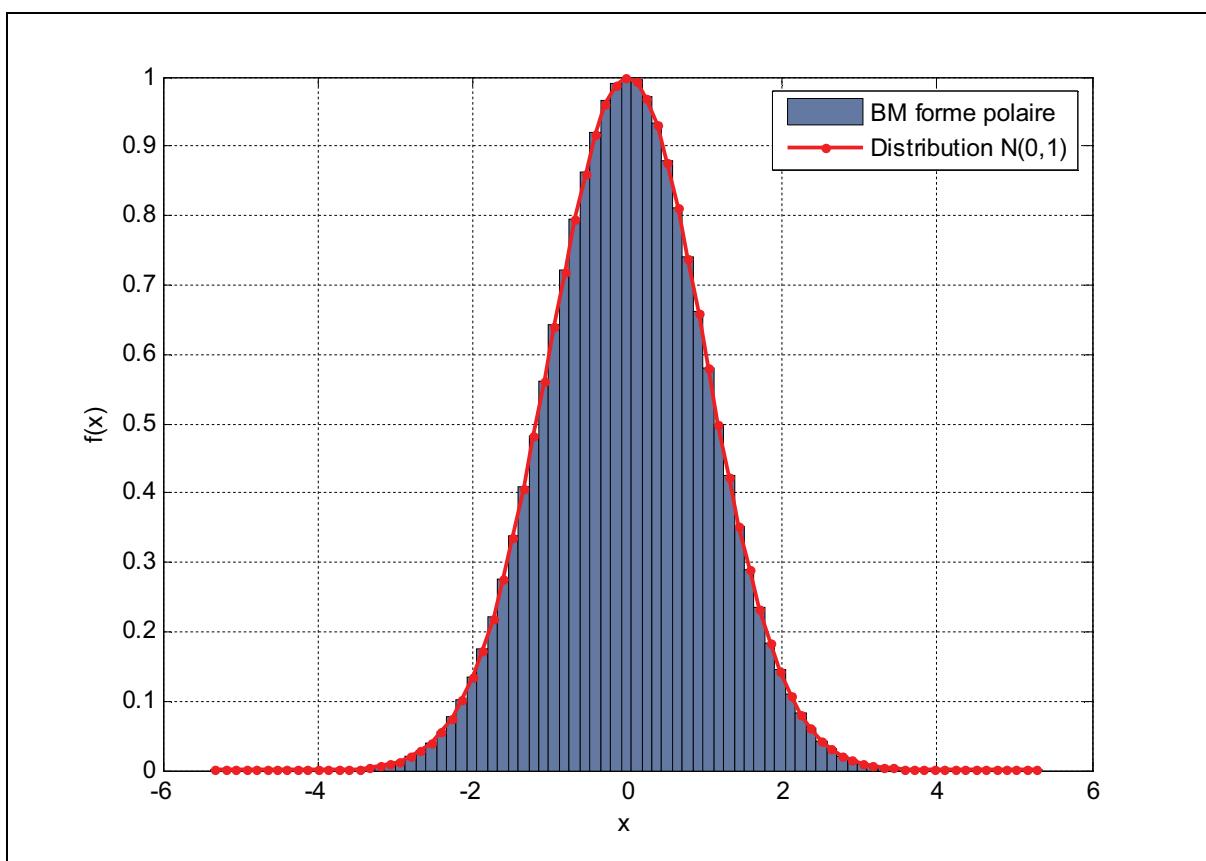

| Figure 3.5  | Distribution d'une v.a gaussienne générée par la forme de base de la méthode Box-Muller. ....                                                                                                                                        | 86  |

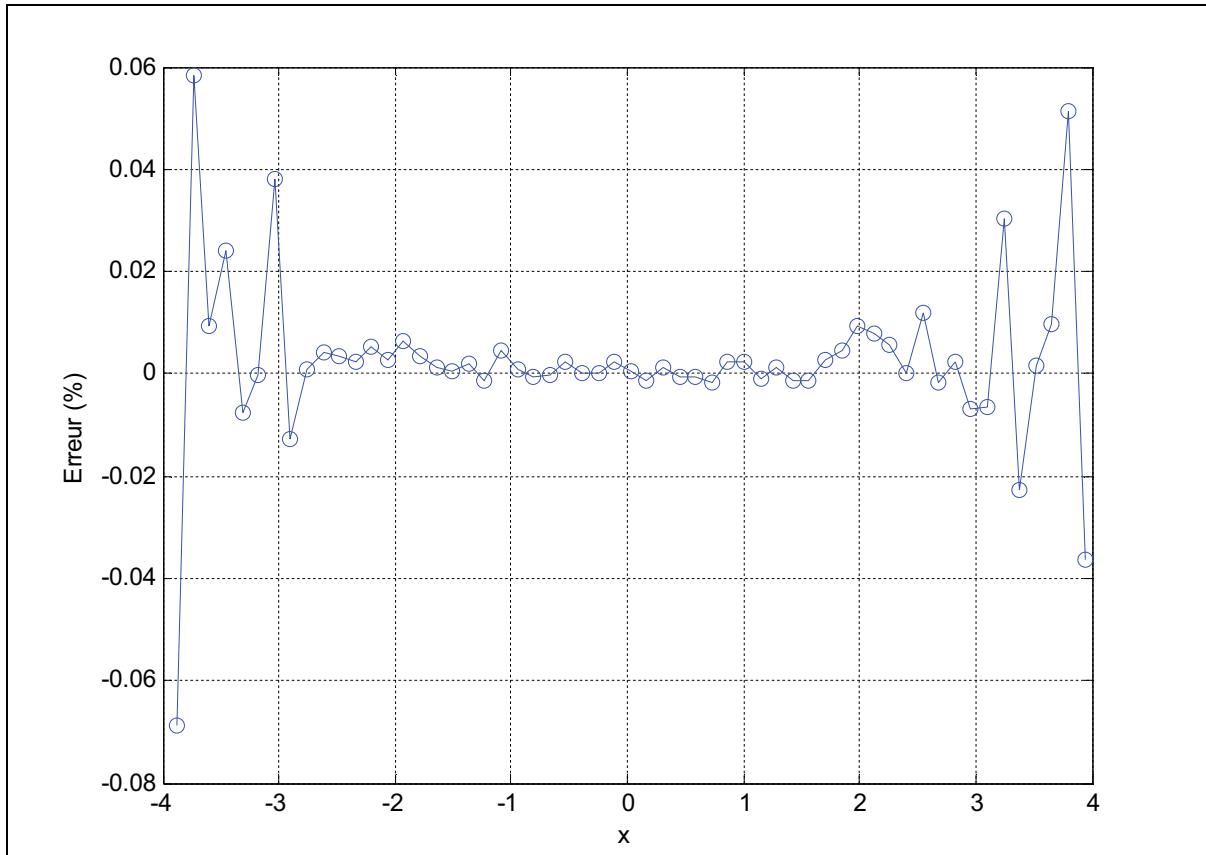

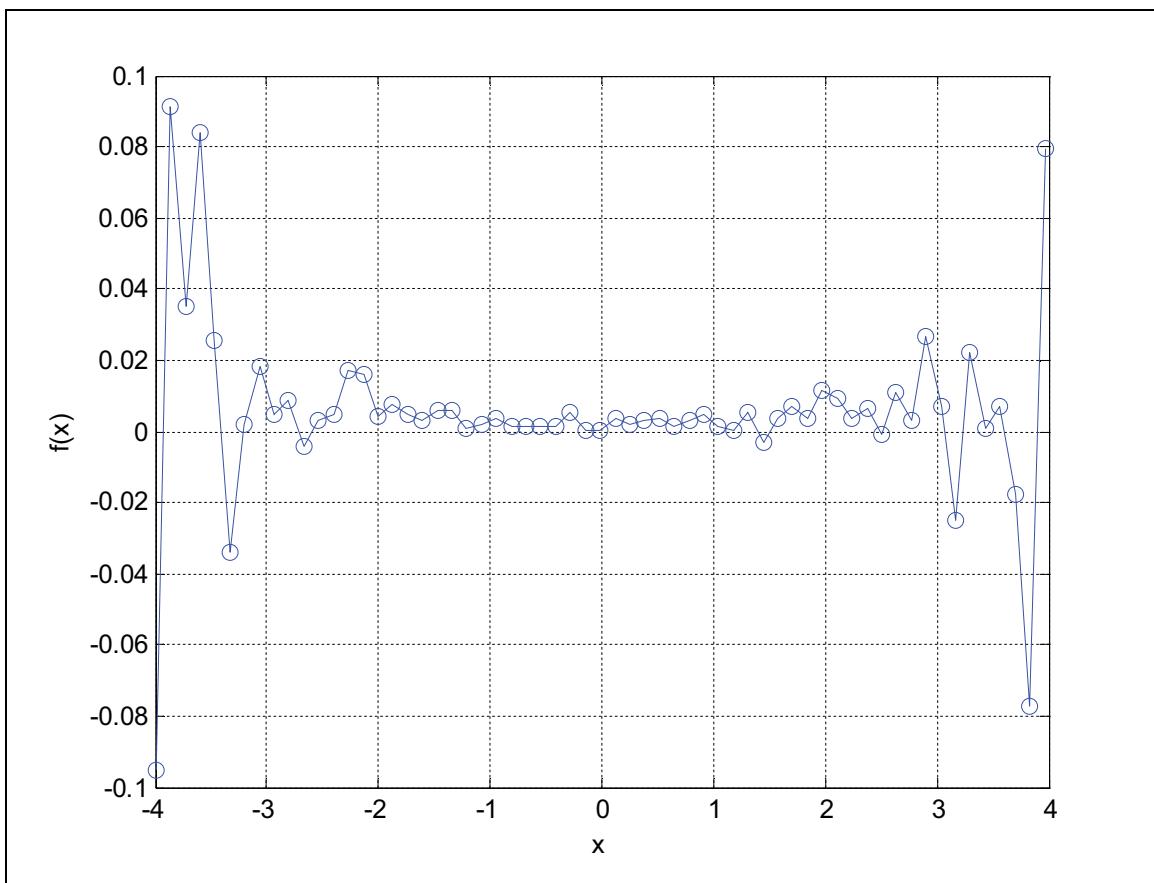

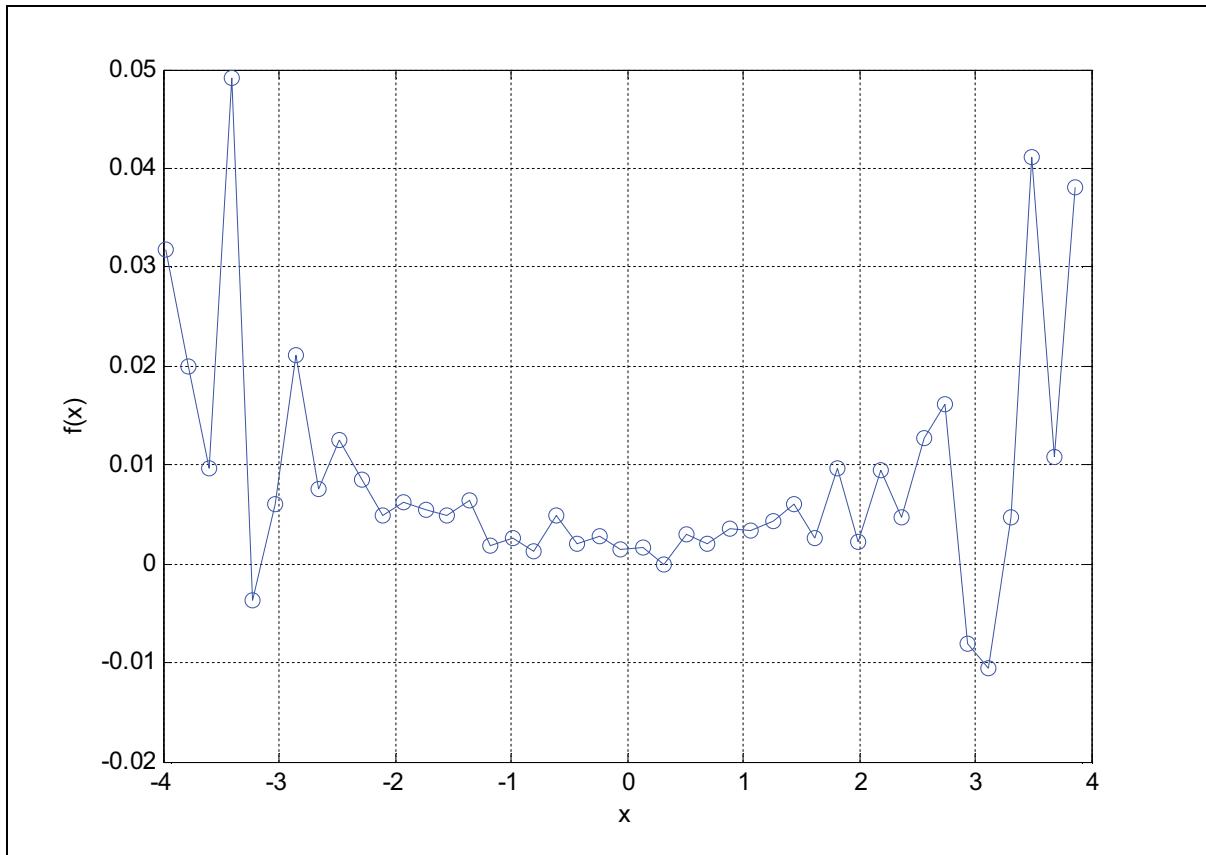

| Figure 3.6  | Erreur relative entre la distribution de la v.a générée par la forme de base de la méthode Box-Muller et la fonction de distribution de la loi normale $N(0,1)$ . ....                                                               | 87  |

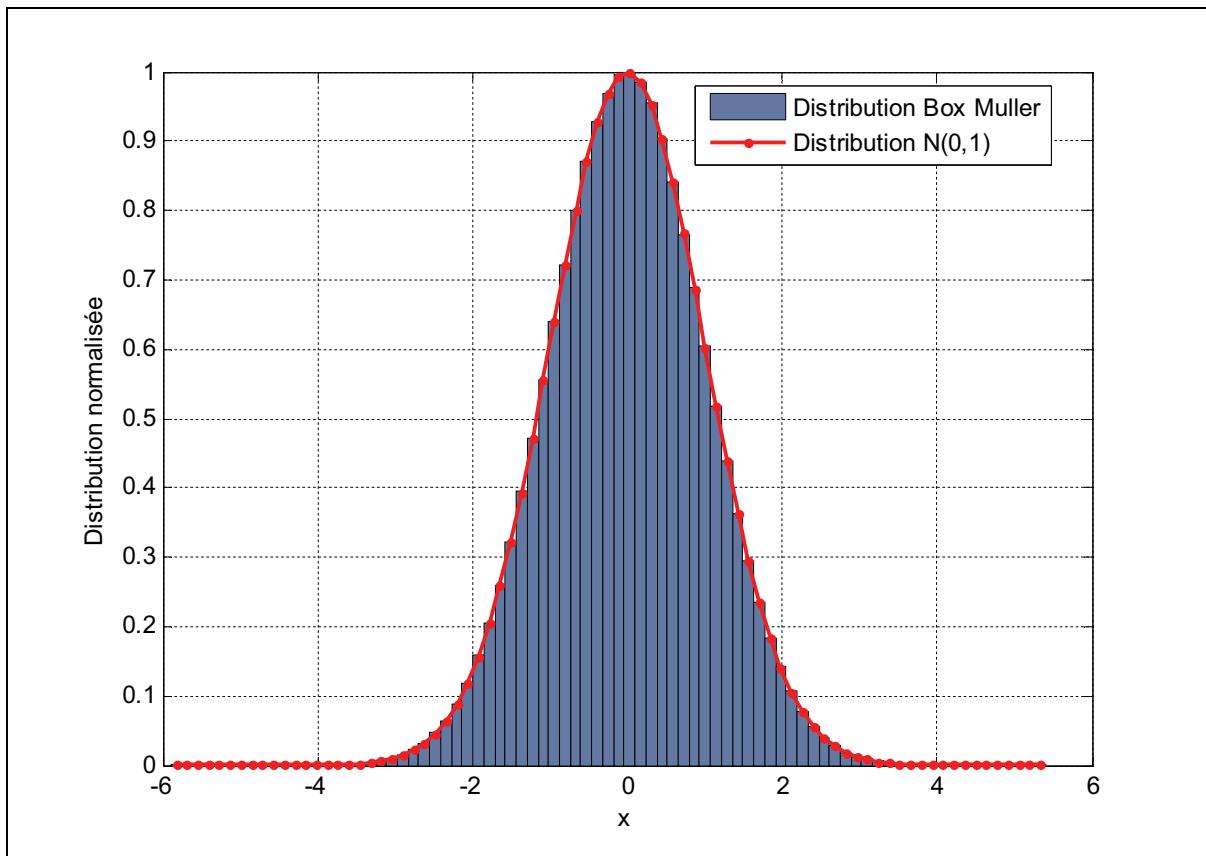

| Figure 3.7  | Distribution d'une v.a gaussienne générée par forme polaire de la méthode Box-Muller. ....                                                                                                                                           | 88  |

| Figure 3.8  | Erreur relative entre la distribution de la v.a générée par la forme polaire de la méthode Box-Muller et la fonction de distribution de la loi normale $N(0,1)$ ....                                                                 | 89  |

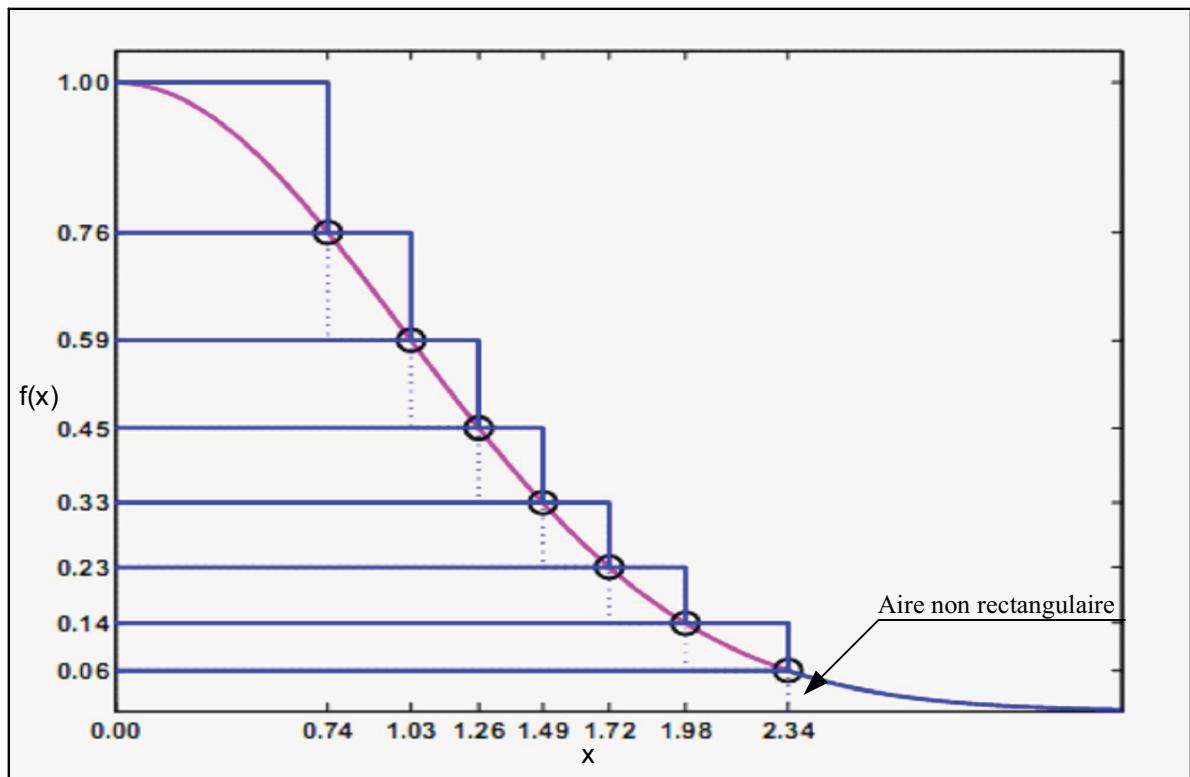

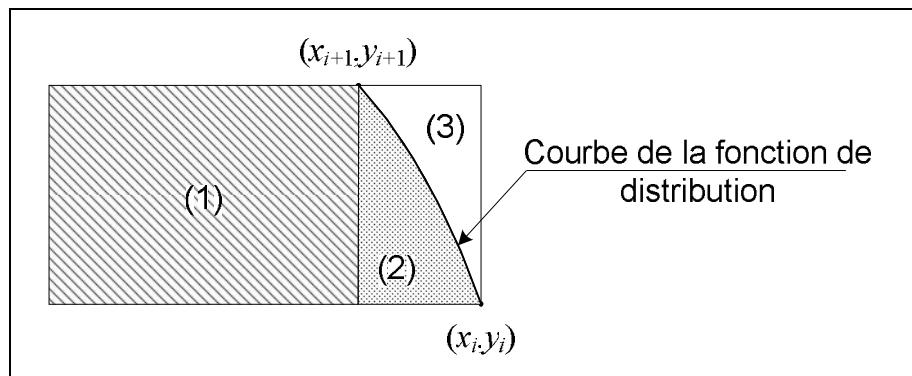

| Figure 3.9  | Construction d'une ziggurat pour la loi normale. ....                                                                                                                                                                                | 90  |

| Figure 3.10 | Déroulement de l'algorithme Ziggurat. ....                                                                                                                                                                                           | 92  |

| Figure 3.11 | Erreur relative entre la distribution de la v.a générée par l'algorithme Ziggurat et la fonction de distribution de la loi normale $N(0,1)$ ....                                                                                     | 94  |

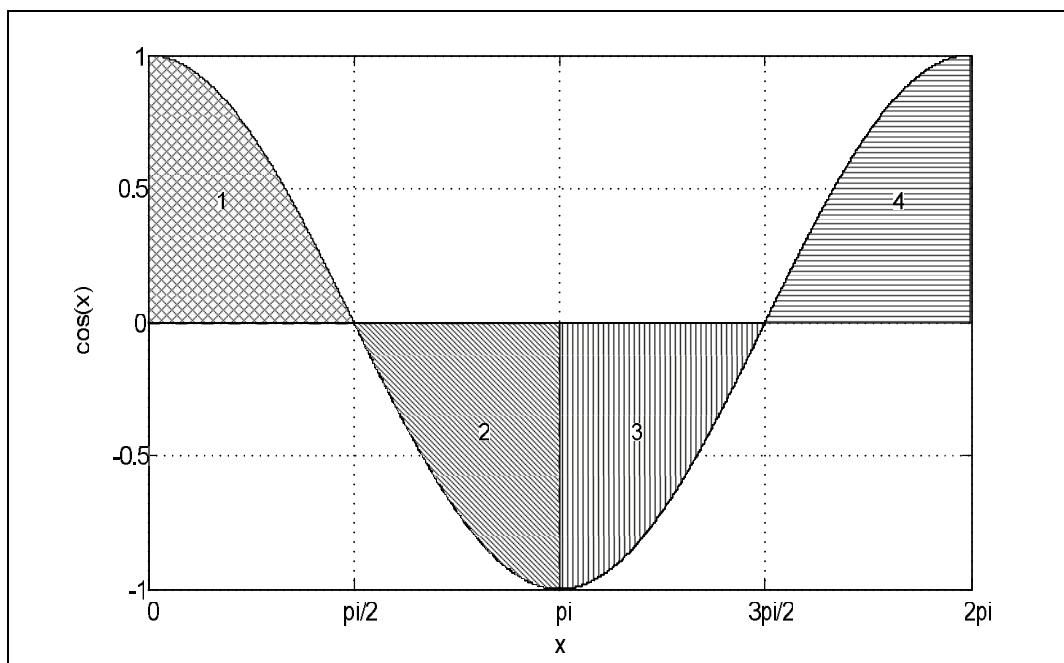

| Figure 3.12 | Fonction cosinus. ....                                                                                                                                                                                                               | 98  |

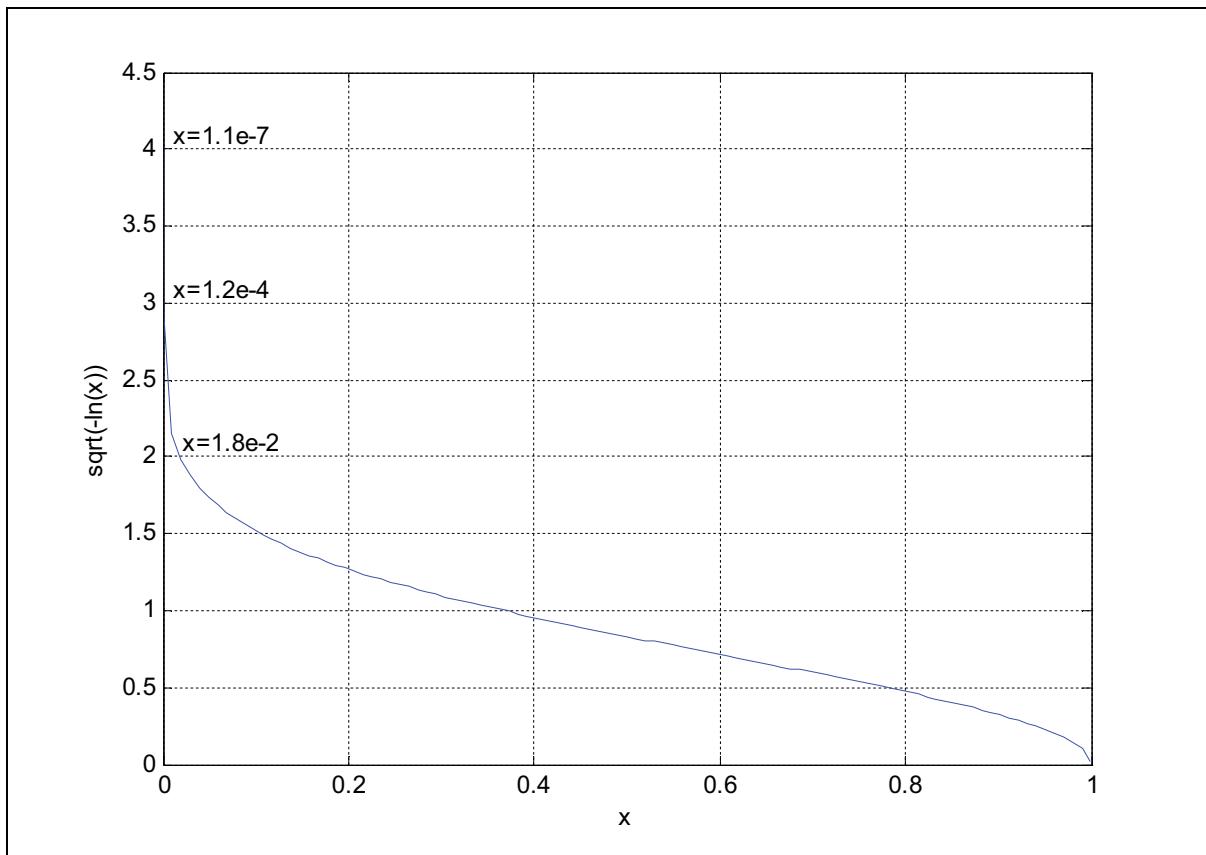

| Figure 3.13 | Fonction logarithme combinée avec la racine carrée. ....                                                                                                                                                                             | 99  |

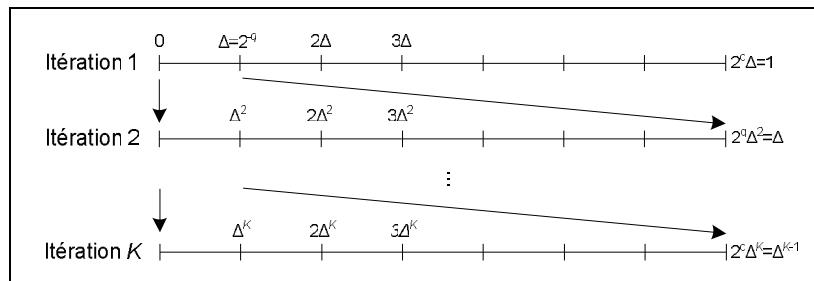

| Figure 3.14 | Quantification non uniforme récursive de la fonction $f$ . ....                                                                                                                                                                      | 100 |

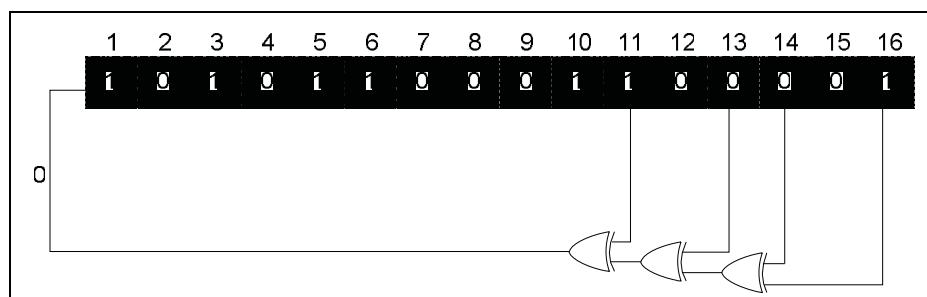

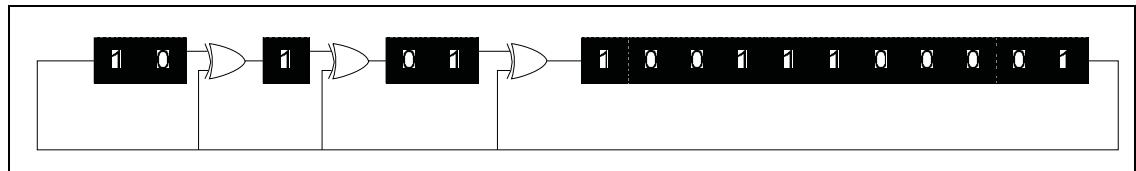

| Figure 3.15 | Exemple d'un LFSR de type Fibonacci. ....                                                                                                                                                                                            | 102 |

| Figure 3.16 | Exemple d'un LFSR de type Galois. ....                                                                                                                                                                                               | 103 |

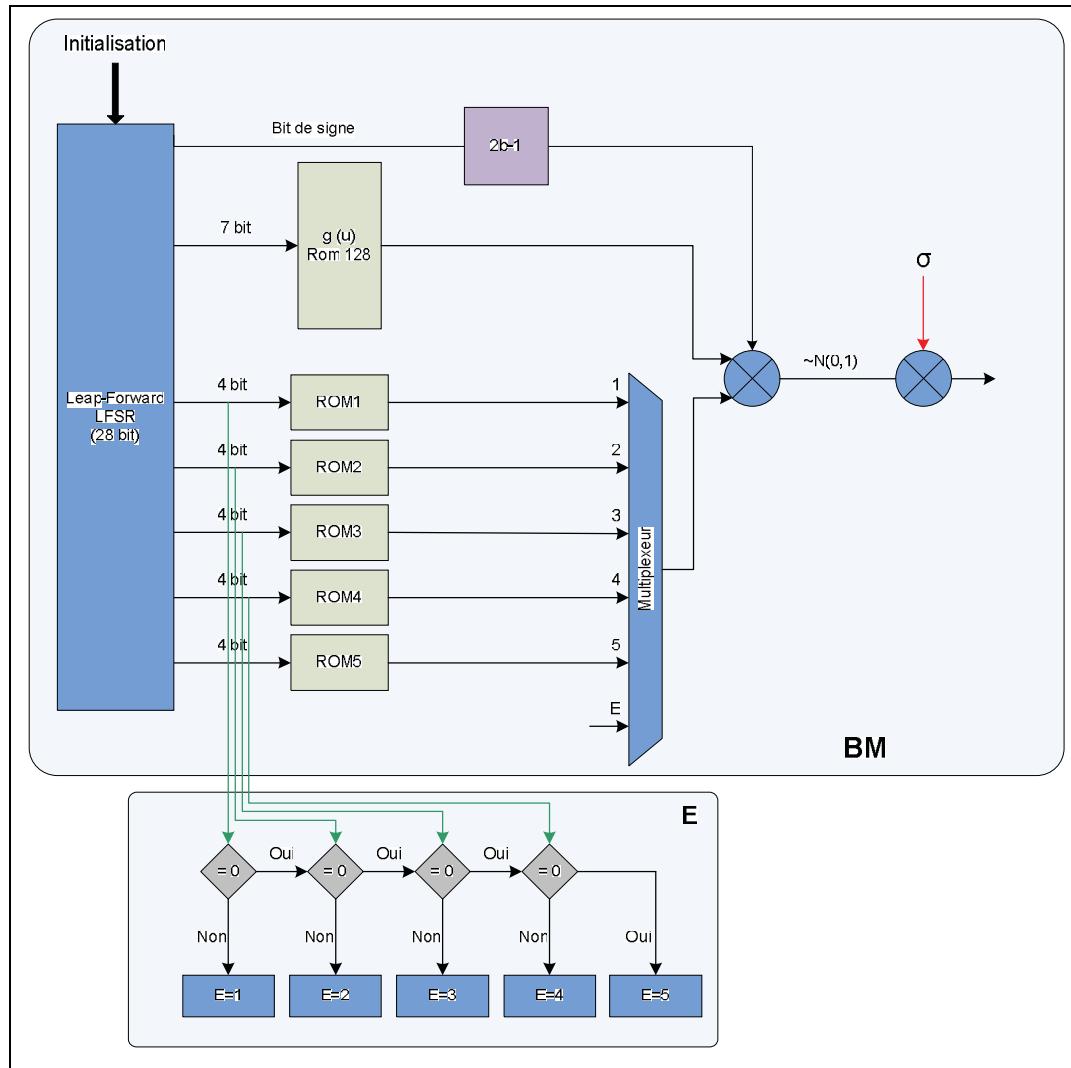

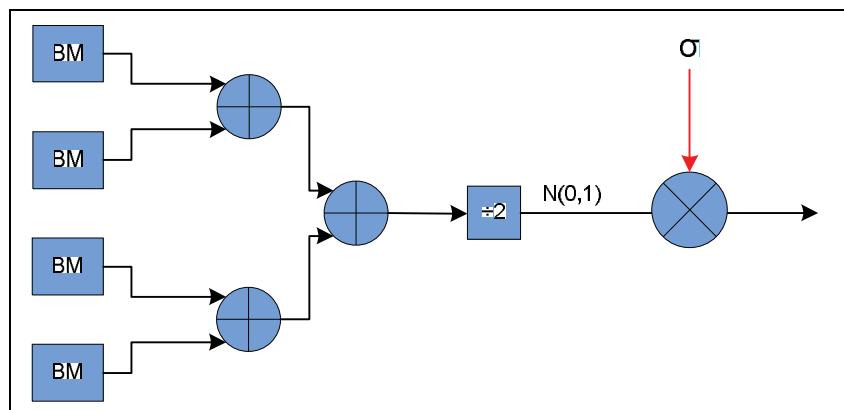

| Figure 3.17 | Architecture de base du générateur Box-Muller. ....                                                                                                                                                                                  | 107 |

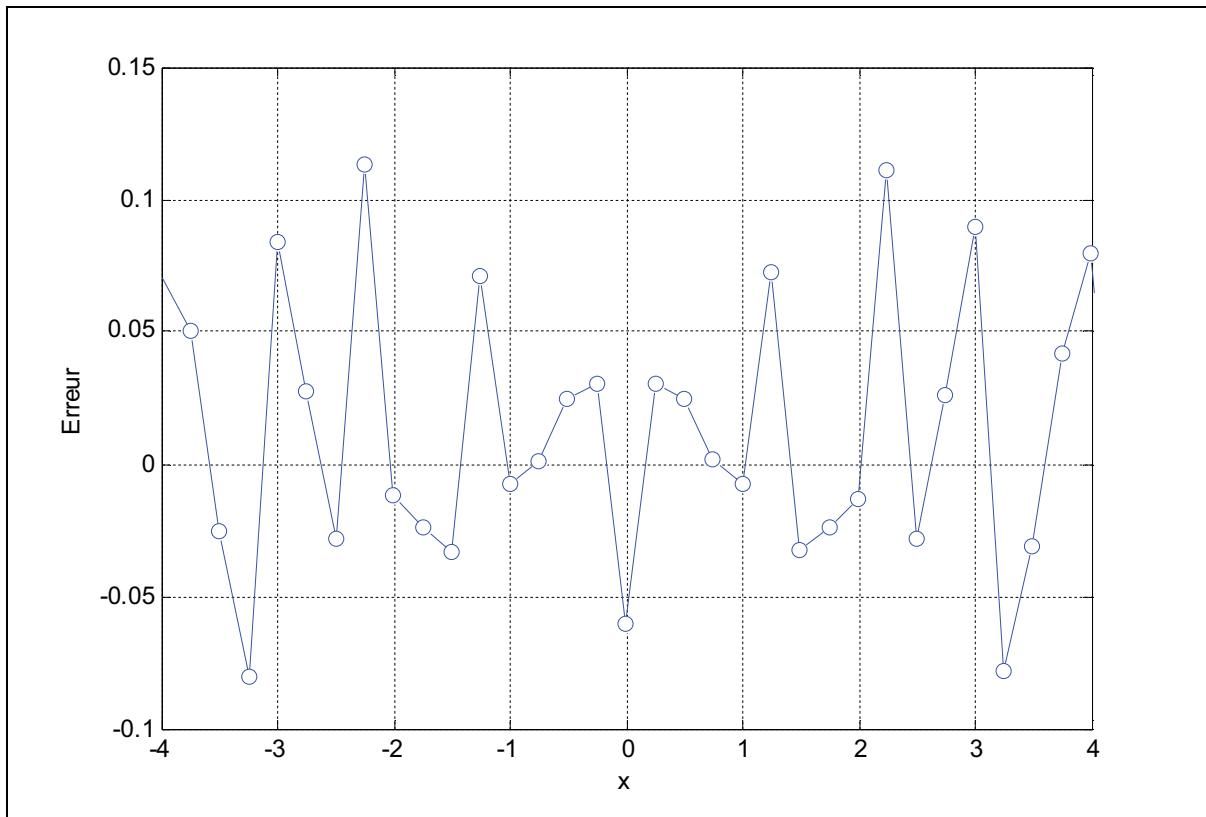

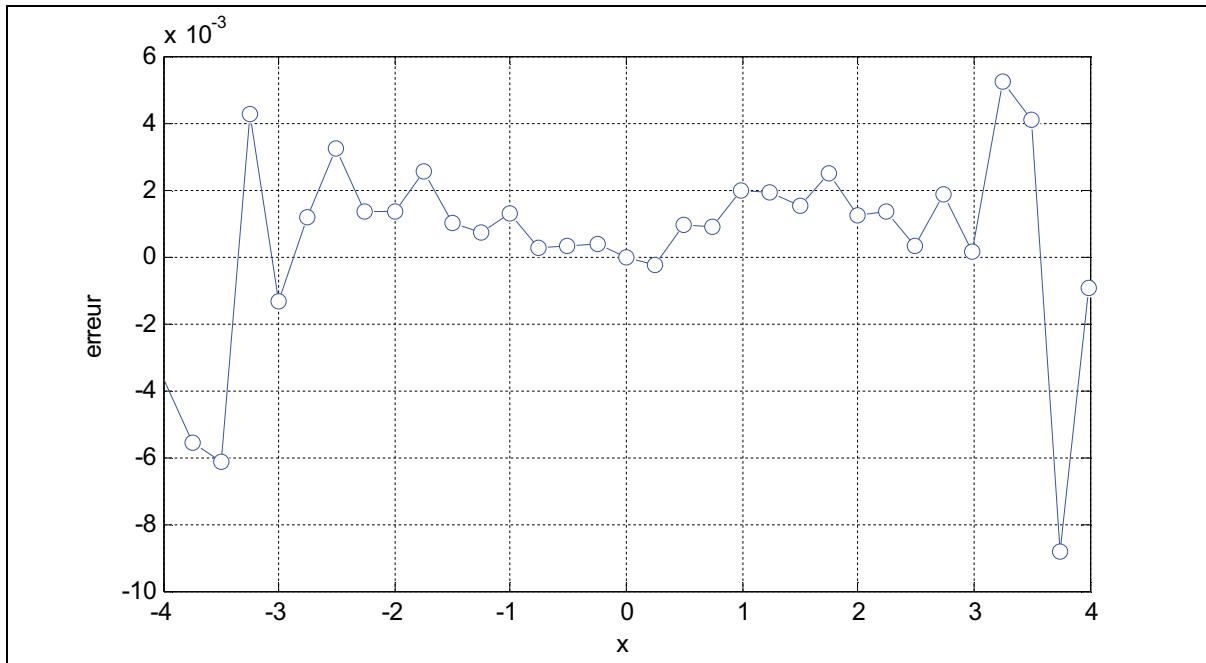

| Figure 3.18 | Erreur relative de la distribution de la v.a générée par l'architecture de base de la méthode Box-Muller sur FPGA. ....                                                                                                              | 108 |

| Figure 3.19 | Architecture du générateur Box-Muller utilisant le théorème de la limite centrale. ....                                                                                                                                              | 109 |

| Figure 3.20 | Erreur relative entre la distribution de la v.a générée par la combinaison de l'architecture de base de la méthode Box-Muller avec la méthode de la limite centrale et la fonction de distribution de la loi normale $N(0,1)$ . .... | 110 |

|             |                                                                                                                                                                                |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

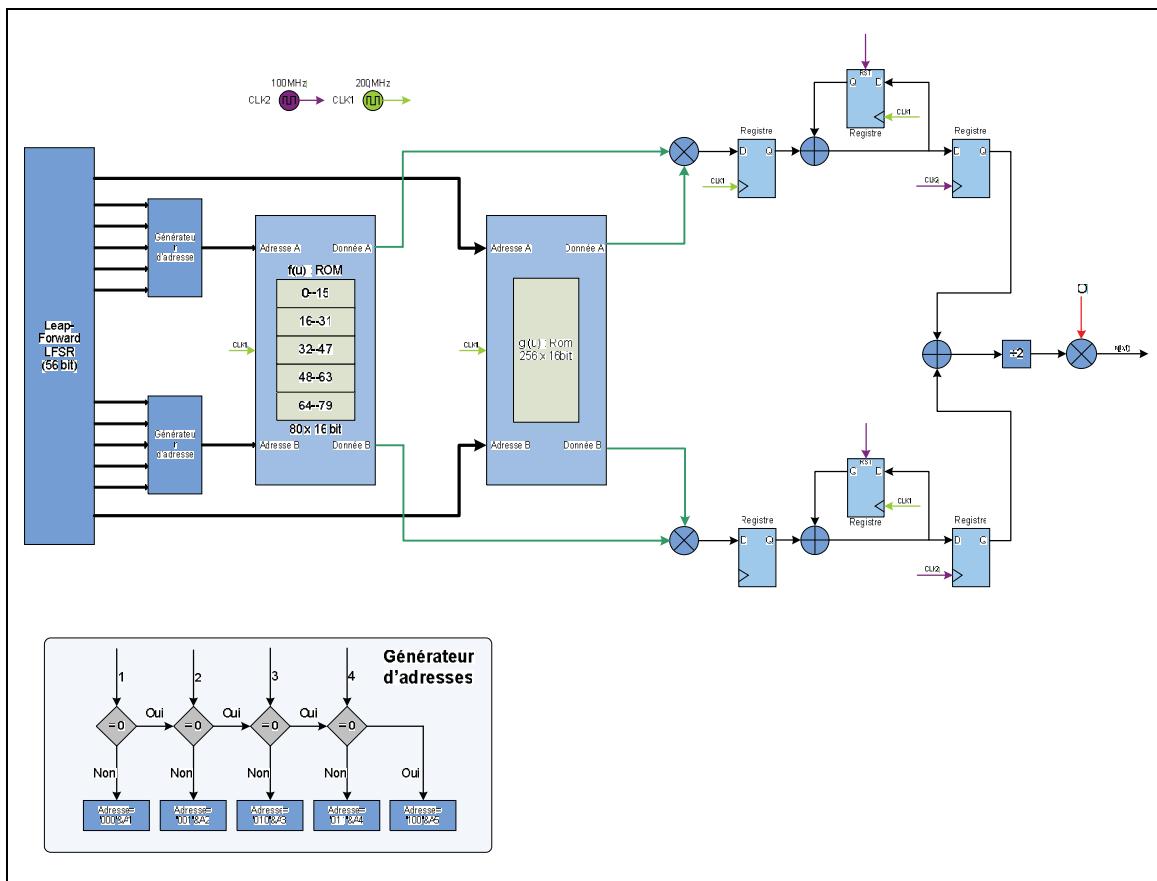

| Figure 3.21 | Architecture finale du générateur Box-Muller. ....                                                                                                                             | 111 |

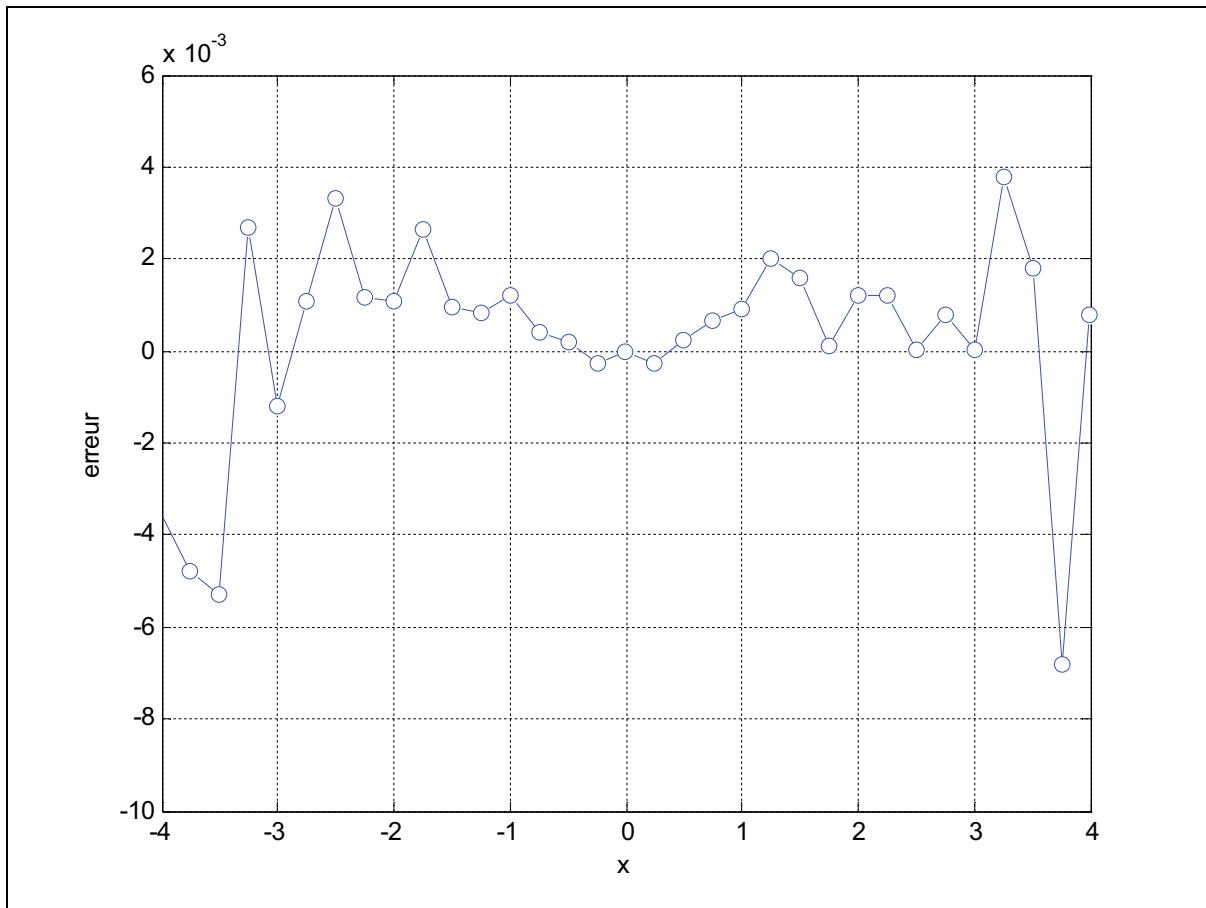

| Figure 3.22 | Erreur relative entre la distribution de la v.a générée par l'architecture optimisée de la méthode Box-Muller et la fonction de distribution de la loi normale $N(0,1)$ . .... | 113 |

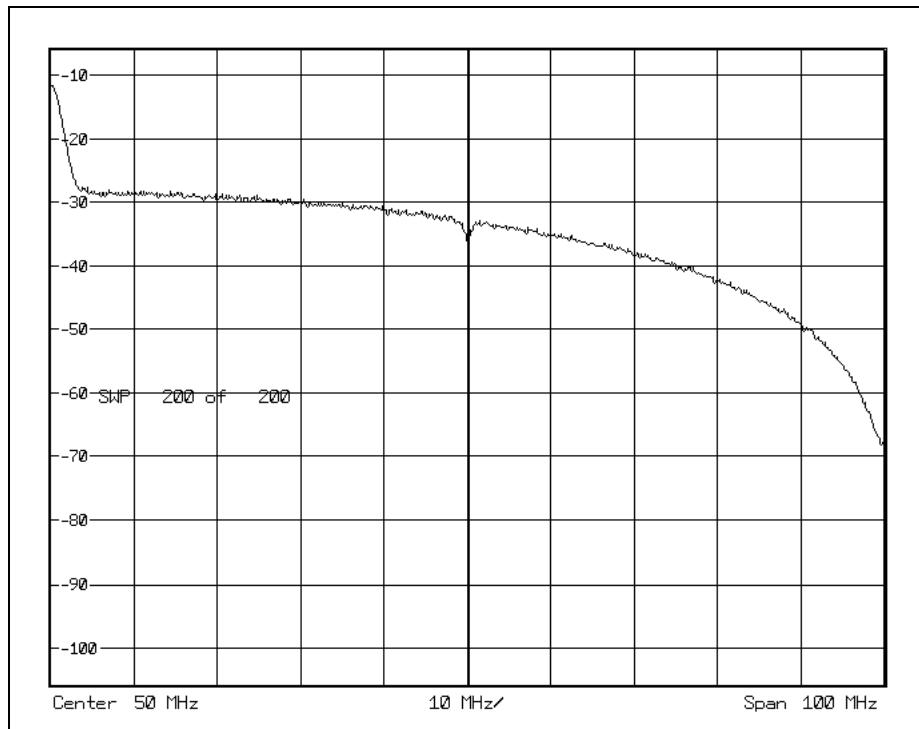

| Figure 3.23 | Spectre du bruit sur une largeur de 100 MHz. ....                                                                                                                              | 114 |

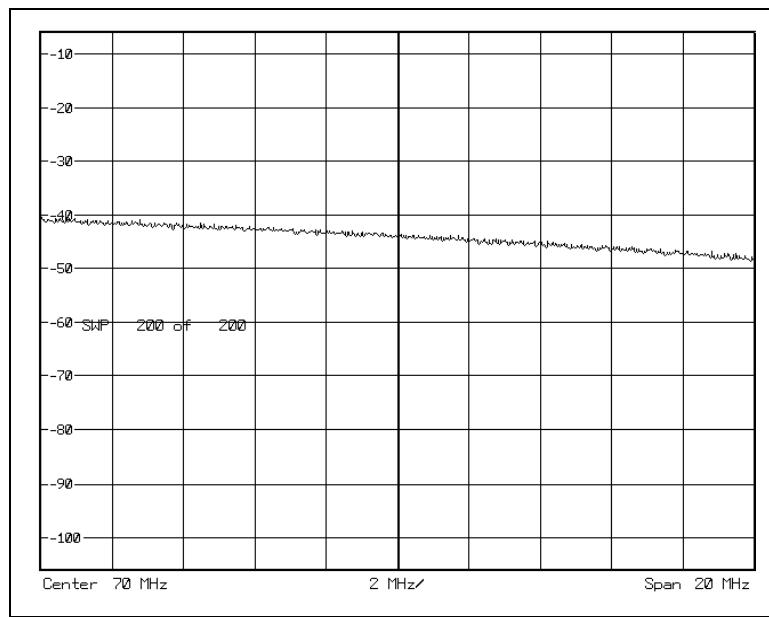

| Figure 3.24 | Spectre du bruit sur une bande allant de 60 à 80 MHz. ....                                                                                                                     | 115 |

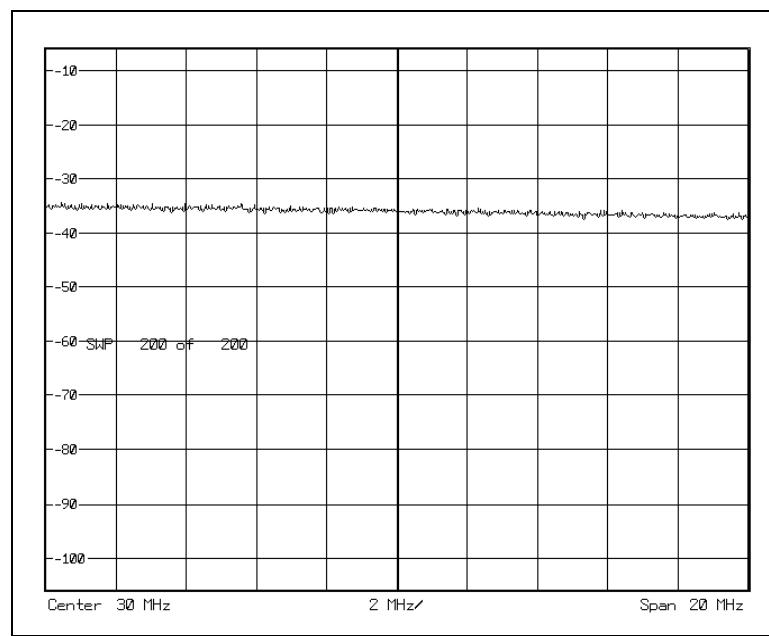

| Figure 3.25 | Spectre du bruit sur une bande allant de 20 à 30 MHz. ....                                                                                                                     | 115 |

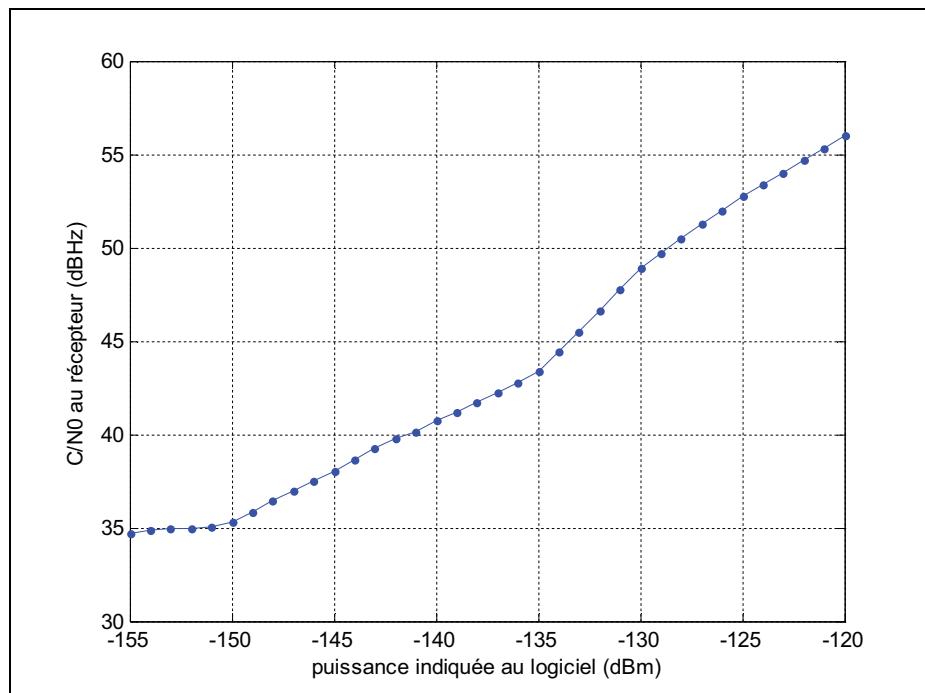

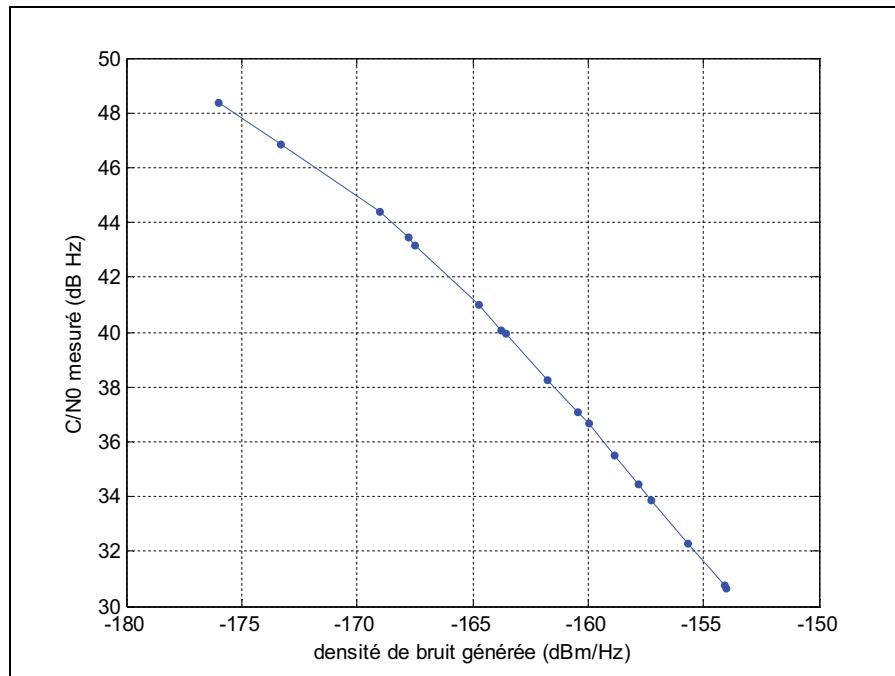

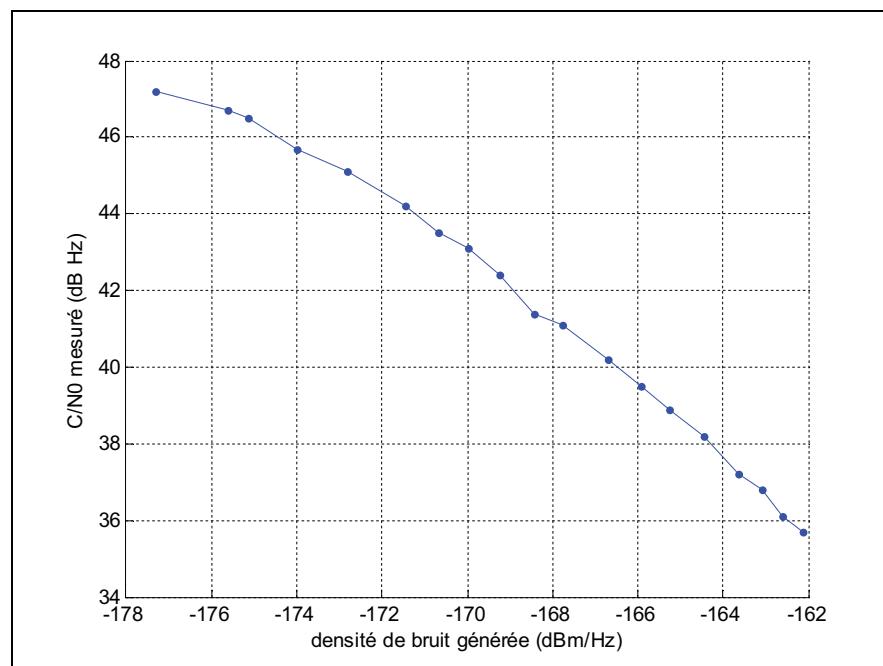

| Figure 3.26 | $C/N_0$ mesuré à l'aide du récepteur commercial. ....                                                                                                                          | 117 |

| Figure 3.27 | $C/N_0$ mesuré à l'aide du récepteur de l'ÉTS. ....                                                                                                                            | 118 |

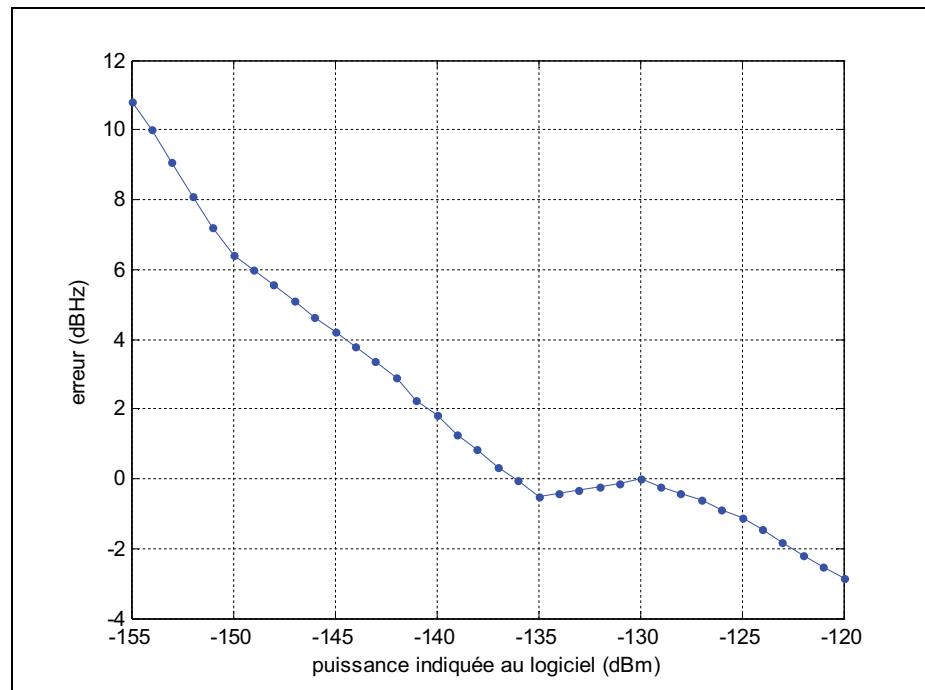

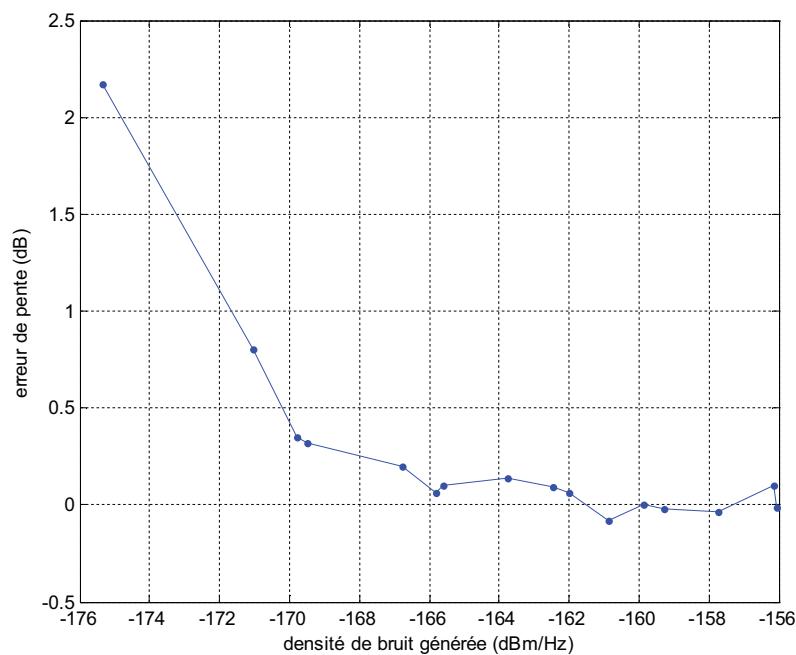

| Figure 3.28 | Erreur de la pente du récepteur commercial. ....                                                                                                                               | 118 |

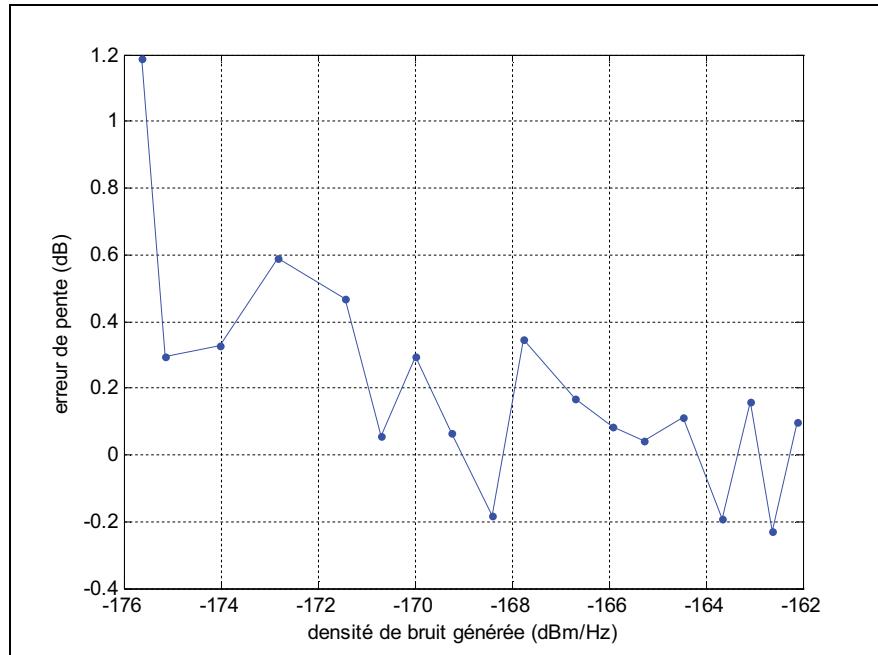

| Figure 3.29 | Erreur de la pente du récepteur de l'ÉTS. ....                                                                                                                                 | 119 |

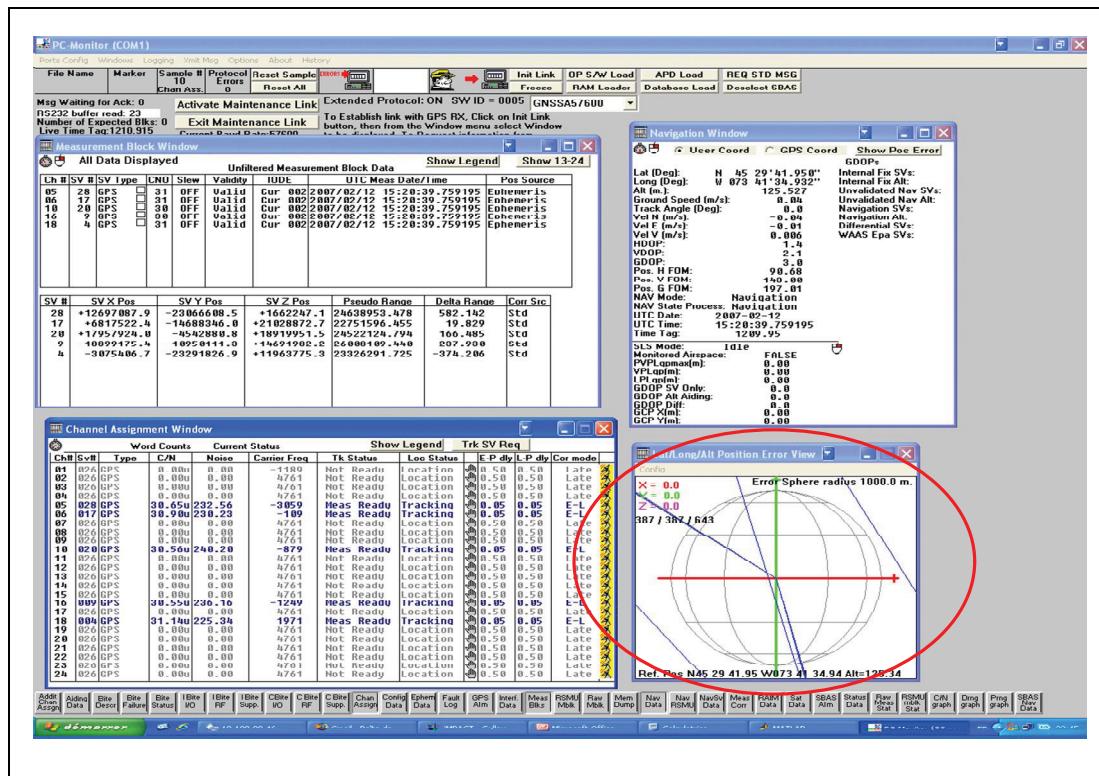

| Figure 3.30 | Décrochage du récepteur commercial. ....                                                                                                                                       | 120 |

| Figure 3.31 | Pic de corrélation dans le récepteur de l'ÉTS sans injection de bruit. ...                                                                                                     | 120 |

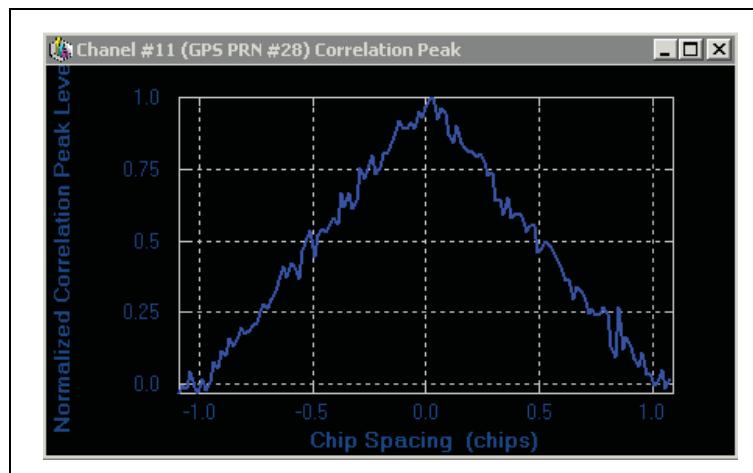

| Figure 3.32 | Décrochage du récepteur de l'ÉTS en présence de bruit. ....                                                                                                                    | 121 |

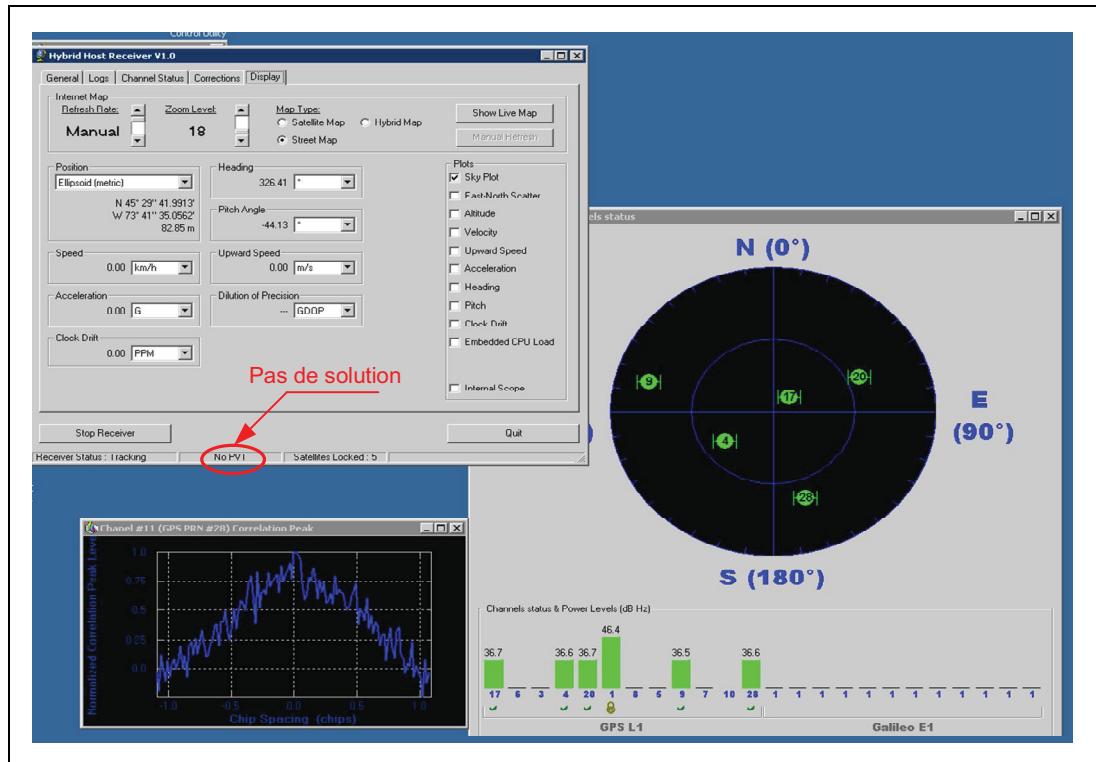

## **LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|                  |                                    |

|------------------|------------------------------------|

| ADC              | Analog to Digital Converter        |

| ADS              | Advanced Design System             |

| ALC              | Automatic Level Control            |

| BER              | Bit Error Rate                     |

| BM               | Box Muller                         |

| C/N <sub>0</sub> | Carrier to Noise Density Ratio     |

| CAN              | Convertisseur Analogique Numérique |

| CDMA             | Code Division Multiple Access      |

| CAN              | Convertisseur Numérique Analogique |

| CPLD             | Complex Programmable Logic Device  |

| DAC              | Digital to Analog Converter        |

| DS-CDMA          | Direct Sequence-CDMA               |

| DSP              | Digital Signal Processing          |

| ÉTS              | École de Technologie Supérieure    |

| FPGA             | Field Programmable Grid Array      |

| FSB              | Fast Synchronous Bus               |

| GNSS             | Global Navigation Satellite System |

| GPIO             | General Purpose Input Output       |

| GPS              | Global Positioning System          |

| IF               | Intermediary Frequency             |

| JTAG             | Joint Test Action Group            |

|         |                                                                        |

|---------|------------------------------------------------------------------------|

| LACIME  | Laboratoire de Communication et d'Intégration de la Micro Électronique |

| LFSR    | Linear Feedback Shift Register                                         |

| LP-LFSR | Leap forward Linear Feedback Shift Register                            |

| LUT     | Look Up Table                                                          |

| OCXO    | Oven Controlled Crystal Oscillator                                     |

| PC      | Personal Computer                                                      |

| PCB     | Printed Circuit Board                                                  |

| PCI     | Peripheral Component Interconnect                                      |

| PLL     | Phase Locked Loop                                                      |

| RF      | Radio Frequency                                                        |

| SNR     | Signal to Noise Ratio                                                  |

| SSBM    | Single SideBand Mixer                                                  |

| TEB     | taux d'Erreurs Binaire                                                 |

| v.a     | variable aléatoire                                                     |

| VCO     | Voltage Controlled Oscillator                                          |

| VGA     | Variable Gain Amplifier/Attenuator                                     |

| VHDL    | VHSIC Hardware Description Language                                    |

| VHSIC   | Very High Speed Integrated Circuit                                     |

## INTRODUCTION

Depuis une vingtaine d'années, les États-Unis étaient le seul pays à fournir un système pleinement opérationnel de radionavigation avec le GPS (*Global Positionning System*). Le 21<sup>e</sup> siècle s'annonce prometteur en matière de positionnement par satellites. Le système le plus attendu est celui de l'Union européenne « Galileo » qui fournira une multitude de nouveaux services aux utilisateurs ainsi qu'une meilleure précision de positionnement.

La tendance industrielle du moment tourne autour du développement des récepteurs hybrides et spécialement GPS et Galileo. Ces industries doivent tester leurs équipements avant la mise sur le marché. Une première solution consiste à placer une antenne sur le toit d'un bâtiment et la relier au laboratoire de test. Les longueurs de câbles peuvent atteindre des centaines de mètres et donc engendrer de grandes pertes en puissance ce qui est très contraignant vu que les signaux reçus des satellites sont déjà très faibles. En plus, on ne peut simuler qu'une seule position (celle du bâtiment) avec GPS. Le système Galileo est encore en cours de déploiement, il n'y a pas donc assez de satellites en orbite pour le calcul des positions. La deuxième solution consiste à embarquer tout l'équipement de test (récepteur, ordinateur, logiciel d'analyse) dans un véhicule et de circuler dans les rues afin de tester les capacités des récepteurs. Cette solution est encombrante et est couteuse en temps et en effort. Un simulateur de constellations GPS et Galileo permet, donc, de s'affranchir de tous ces problèmes, car on peut créer tous les scénarios de déplacement et tester les récepteurs en laboratoire.

Dans ce cadre, le LACIME (Laboratoire de Communication et d'Intégration de la Micro Électronique) développe un simulateur de signaux GPS/Galileo qui lui permettra de tester des récepteurs hybrides. Ce simulateur doit reproduire les signaux des constellations de satellites de chacun des deux systèmes. Il doit être capable de générer des signaux identiques (codage, modulation, bandes de fréquences...) pour recréer des conditions similaires à celles des deux systèmes.

Le simulateur est composé de trois parties. Une partie logicielle qui fait tous les calculs nécessaires à la génération des signaux des constellations. Elle permet aussi de piloter la deuxième partie du simulateur, la partie du traitement numérique des signaux (partie IF) qui a pour tâche de mettre en forme les signaux en se basant sur les données reçues de la partie logicielle. Trois signaux analogiques sont générés par la partie IF (à 70 MHz) et sont injecté dans une carte RF, le troisième et dernier maillon du simulateur. La partie RF permet de transposer les signaux IF à leurs fréquences réelles (celles des signaux GPS et Galileo). Elle a aussi le rôle de mettre ces signaux à la puissance adéquate et de les combiner pour les injecter dans le récepteur de tests.

Ce projet de maîtrise est composé de deux parties. La première consiste à développer un système de contrôle de puissance pour les trois signaux GPS et Galileo. Le contrôle doit être établit sur une plage de 40 dB avec un pas de 0.1 dB. La deuxième partie du travail comprend la mise en œuvre d'un système de contrôle du ratio  $C/N_0$  et plus précisément, développer un générateur de bruit blanc qui sera injecté aux signaux GPS et Galileo pour dégrader leurs qualités et par conséquent évaluer la robustesse des récepteurs.

Le présent mémoire est divisé en trois chapitres. Le premier présente un survol des systèmes de positionnements GPS et Galileo ainsi qu'une présentation du simulateur GPS et Galileo. Il se focalisera sur la partie RF du simulateur. Le deuxième chapitre traitera en détail la conception et la réalisation du système de contrôle de puissance en commençant par l'architecture du module pour passer ensuite aux composants et les modes d'ajustements ainsi que la communication entre la partie logicielle et la partie RF et enfin, être conclu par la validation du système. Le troisième et dernier chapitre aborde le deuxième volet de ce projet à savoir le système de contrôle du ratio  $C/N_0$ . Il traitera, les différents types d'implémentation d'un générateur de bruit blanc et les étapes de conception d'un tel générateur. Ce chapitre est conclu par la validation du générateur de bruit par le biais d'un récepteur commercial et d'un récepteur développé au sein de l'ÉTS.

## Equation Chapter 1 Section 1

## CHAPITRE 1

### LE SIMULATEUR DE SIGNAUX GNSS

Le positionnement par satellites a reçu beaucoup d'intérêt depuis leurs créations dans la fin des années cinquante. Plusieurs systèmes ont été développés pour satisfaire ce besoin, uniquement militaire à l'époque. Actuellement, on compte quelques systèmes pleinement et partiellement opérationnels à savoir :

- GPS (*Global Positionning System*) pour les États-Unis (opérationnel) ;

- Galileo pour l'Europe (en cours de déploiement) ;

- GLONASS (*GLObal'naya NAVigatsionnaya Sputnikovaya Sistema*) pour la Russie (n'est pas pleinement opérationnel) (NovAtel, 2007);

- Compass/Beidou pour la Chine (opérationnel uniquement en asie) (UNOOSA, 2008).

Ce chapitre présente en premier lieu le principe du positionnement par satellites et décrit les systèmes GPS et Galileo. Ensuite, il introduit le projet GNSS (*Global Navigation Satellite System*) en détaillant la partie RF sur laquelle nous allons travailler.

#### 1.1 Principe du positionnement par satellite

Le principe de positionnement est simple. Si les distances séparant un récepteur de quatre satellites sont connues, on peut alors, déterminer la position de ce récepteur.

##### 1.1.1 Principe de la trilateration

La trilateration est un concept géométrique qui permet de calculer les coordonnées d'un point dans un plan à l'aide de trois points de références (Sauriol B, 2008). Elle se base uniquement sur les coordonnées de ces points ainsi que les distances les séparant du point dont on veut calculer la position. En connaissant la distance entre un point de référence et le point désiré (le point M dans la Figure 1.1), on affirme que ce dernier se trouve sur un cercle de centre le

point de référence et de rayon la distance les séparant. De cette manière, et en obtenant les deux distances restantes, le point M n'est que l'intersection des trois cercles. La Figure 1.1 illustre le principe de la trilateration dans un espace à deux dimensions.

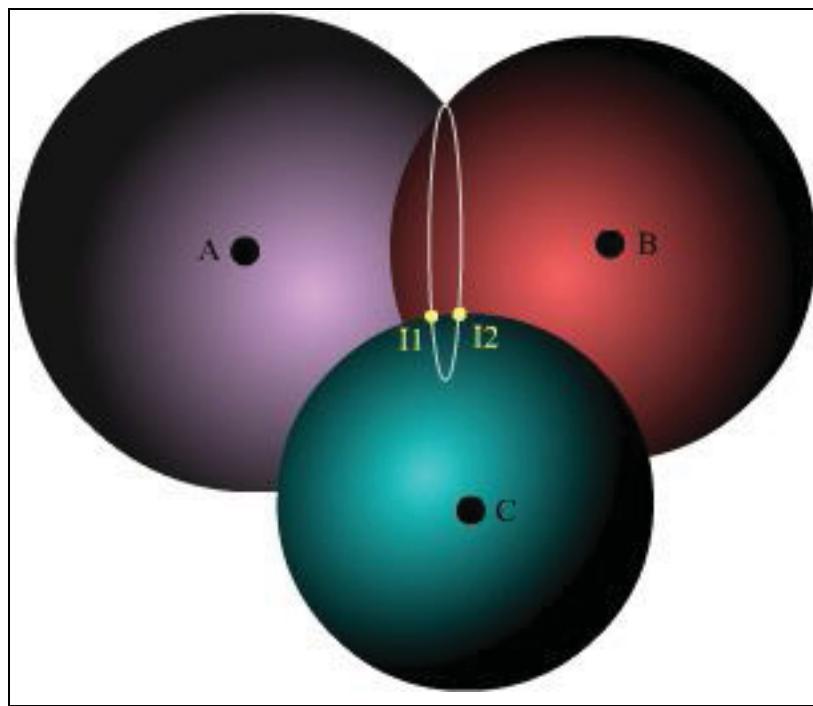

**Figure 1.1    Principe de la trilateration en 2D.**

La trilateration peut s'appliquer aussi pour un espace tridimensionnel. Les cercles de la Figure 1.1 se transforment, alors, en sphères centrées en les points de références et de rayon les distances  $d_1$ ,  $d_2$  et  $d_3$ . La Figure 1.2 illustre le résultat de la trilateration en trois dimensions. En effet, l'intersection de deux sphères donne naissance à un cercle qui intercepte la troisième sphère en deux points. La position ne peut encore être déterminée avec précision d'où le besoin d'un quatrième point de référence qui permettra de lever l'ambigüité sur la décision.

**Figure 1.2    Principe de la trilateration en 3D.**

Si on connaît les coordonnées  $(x_i, y_i, z_i)$  des quatre points de références et les distances  $d_i$ , on peut déterminer, en résolvant le système d'équations (1.1), les coordonnées  $(x_M, y_M, z_M)$  du point désiré.

$$\begin{cases} d_1 = \sqrt{(x_1 - x_M)^2 + (y_1 - y_M)^2 + (z_1 - z_M)^2} \\ d_2 = \sqrt{(x_2 - x_M)^2 + (y_2 - y_M)^2 + (z_2 - z_M)^2} \\ d_3 = \sqrt{(x_3 - x_M)^2 + (y_3 - y_M)^2 + (z_3 - z_M)^2} \\ d_4 = \sqrt{(x_4 - x_M)^2 + (y_4 - y_M)^2 + (z_4 - z_M)^2} \end{cases} \quad (1.1)$$

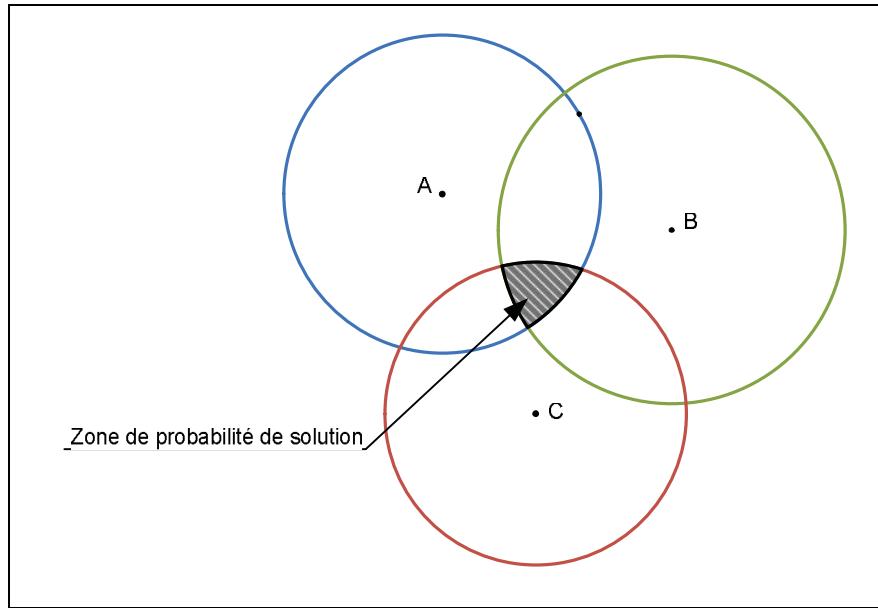

Dans un cas idéal, la résolution de ce système donne une solution unique. Toutefois, dans la pratique, des erreurs surviennent au niveau des positions des points de référence et des distances. L'intersection des sphères n'étant plus un point dans l'espace, on obtient une région de probabilité qui est représentée par la Figure 1.3 pour un espace à deux dimensions.

**Figure 1.3 L'effet des erreurs sur la trilateration.**

### 1.1.2 Le positionnement par satellites

Les systèmes de positionnement par satellites utilisent la méthode de la trilateration afin de calculer la position d'un récepteur. Les points de références dans ces systèmes constituent la constellation des satellites gravitant autour de la terre. Il faudrait donc connaître leurs positions de façon précise. Ensuite, il suffit de mesurer la distance séparant le satellite du récepteur avec une précision compatible avec la précision de navigation qu'on veut obtenir.

Les satellites émettent continuellement des signaux radio qui contiennent leurs positions et l'instant d'envoi  $t_e$ . Le récepteur a la tâche de calculer le temps de réception de ces signaux  $t_r$ . Connaissant leur vitesse de propagation ( $c$  : vitesse de la lumière), on en déduit la distance séparant le récepteur du satellite :

$$d = c(t_r - t_e) \quad (1.2)$$

Le calcul du temps de propagation doit être extrêmement précis, car une erreur d'une microseconde dans le temps provoque une erreur de 300 m en position. Le temps d'envoi des

signaux est déterminé par les horloges atomiques embarquées à bord des satellites. Ce sont des horloges atomiques extrêmement coûteuses, mais aussi extrêmement fiables et stables. Le temps d'arrivée est donné par le récepteur qui possède une horloge de moindre qualité. Au niveau du temps d'arrivée, il y a donc une erreur provoquée par le récepteur (Sauriol B, 2008). La différence entre le temps d'envoi et le temps de réception est calculé par le récepteur, ensuite il en déduit la distance qui le sépare du satellite. Cette distance est biaisée principalement à cause des imperfections de l'horloge du récepteur, elle est appelée pseudo-distance (Sauriol B, 2008).

Dans la section précédente, nous avons conclu qu'il faudrait quatre points de références pour arriver à calculer une position. Dans le fait, il est facile de lever l'ambigüité sur la position, car une des solutions se trouve sur la surface de la terre alors que la deuxième se situe dans l'espace. Par conséquent, trois satellites suffiraient pour déterminer la position d'un récepteur. Cependant, ce n'est pas le cas en pratique. En effet, en plus des erreurs d'horloges des satellites dont la correction est envoyée dans le message de navigation, les erreurs causées par l'horloge du récepteur engendrent une imprécision au niveau du calcul de la pseudo-distance. On suppose, donc, qu'il y a un biais entre le véritable temps de réception des signaux et le temps déterminé par le récepteur. Pour éliminer ce biais, un quatrième satellite est requis et ainsi, le récepteur doit résoudre le système d'équations (1.3) pour déterminer sa position (Sauriol B, 2008).

$$\left\{ \begin{array}{l} \Delta t_1 = \frac{1}{c} \sqrt{\left[ (x_M - x_1)^2 + (y_M - y_1)^2 + (z_M - z_1)^2 \right]} + \Delta H_m \\ \Delta t_2 = \frac{1}{c} \sqrt{\left[ (x_M - x_2)^2 + (y_M - y_2)^2 + (z_M - z_2)^2 \right]} + \Delta H_m \\ \Delta t_3 = \frac{1}{c} \sqrt{\left[ (x_M - x_3)^2 + (y_M - y_3)^2 + (z_M - z_3)^2 \right]} + \Delta H_m \\ \Delta t_4 = \frac{1}{c} \sqrt{\left[ (x_M - x_4)^2 + (y_M - y_4)^2 + (z_M - z_4)^2 \right]} + \Delta H_m \end{array} \right. \quad (1.3)$$

Où  $\Delta t_i$  représente le temps de propagation calculé par le récepteur,  $(x_m, y_m, z_m)$  sont les coordonnées du mobile,  $(x_i, y_i, z_i)$  sont les coordonnées du satellite  $i$  et  $\Delta H_m$  est le biais inconnu de l'horloge du récepteur.

## 1.2 Spécifications des systèmes GPS et Galileo

### 1.2.1 Spécification du système GPS

Le GPS est un système de positionnement par satellite qui a été développé vers la fin des années soixante-dix par le département de la défense américain (Ublox, 2007). Il a été conçu, initialement, pour un usage militaire. Ce n'est que plus tard qu'il a été accessible pour les civils. Le GPS offre une capacité de positionnement n'importe où sur la planète et dans toutes les conditions météorologiques. Il peut desservir un nombre illimité d'usagers vu que le système est unidirectionnel (les utilisateurs ne font que recevoir les signaux et calculer leurs positions).

#### Structure du système GPS

Le système GPS est composé de trois segments : spatial, contrôle et utilisateur.

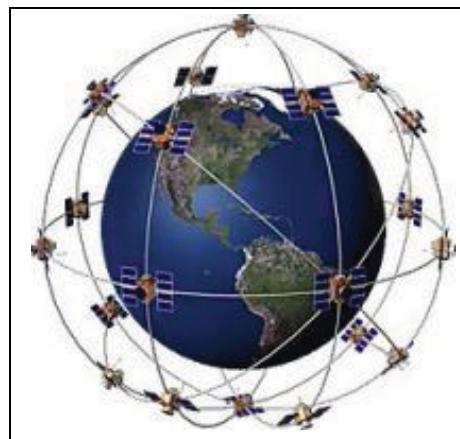

- Segment spatial : il est constitué de 30 à 32 satellites opérationnels qui sont placés sur six orbites quasi circulaires inclinées de  $55^\circ$ . La Figure 1.4 illustre l'organisation des satellites sur les orbites;

- Segment de contrôle : comme son nom l'indique, le segment de contrôle permet de piloter le système GPS. Il est composé d'un réseau mondial de stations de contrôle. Sa première tâche est de suivre les satellites de la constellation, déterminer leurs positions, vérifier l'intégrité du système, les horloges atomiques, l'état des satellites et les erreurs de positionnement (Ublox, 2007). Ces informations sont ensuite envoyées vers les satellites sur la bande S (2 à 4 GHz);

- Segment utilisateur : il inclut tous les utilisateurs civils et militaires. Avec un récepteur GPS, ils peuvent capter les signaux et déterminer leurs positions. Le GPS est accessible partout dans le monde sauf où la puissance est affaiblie (ex : environnement *Indoor*, environnement urbain, etc) sans frais (Ublox, 2007);

**Figure 1.4 Constellation des satellites du système GPS.**

Tiré de (Cole-Parmer, 2009)

### Spécifications des signaux GPS

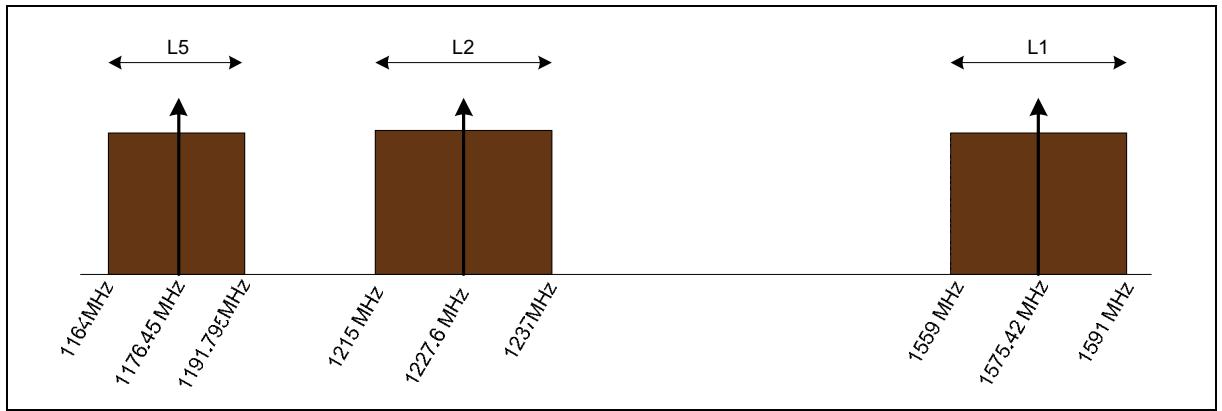

Les satellites GPS émettent actuellement trois signaux L1, L2 et L5. Ces signaux transportent les messages de navigation permettant aux récepteurs de calculer leurs positions (ARINC research corporation, 2000).

- Signal L1 : ce signal transporte les messages de navigation avec l'utilisation de deux codes d'étalement de spectre. L'un pour l'usage public et l'autre pour l'usage militaire;

- Signal L2C : ce signal est une modernisation du système GPS. Il a été ajouté pour accroître la précision de navigation. Il y a actuellement huit satellites en orbite qui transmettent le signal L2C. Les récepteurs auront le choix entre les différents signaux selon leurs niveaux de puissances, la nature de l'application utilisée, etc;

- Signal L5 : ce signal sera destiné pour le grand public (SoL : *Safety of Life*). Il est une amélioration du système GPS et il servira à améliorer les applications en aviation. Il y a maintenant un seul satellite en orbite à titre de démonstration.

Les signaux GPS sont basés sur la technique DS-CDMA (*Direct Sequence – Code Division Multiple Access*). Cette solution se révèle la plus adéquate à une telle application vu qu'il n'y a pas de communication ascendante entre le segment utilisateur et le segment spatial (du récepteur au satellite). De cette façon, les satellites émettent sur les mêmes fréquences L1, L2 et L5 et ils sont différenciés selon des codes. En plus, cette technique assure le cryptage des données pour les applications militaires ou commerciales et permet la réception des signaux de très faibles puissances (noyés dans le bruit).

Les caractéristiques des signaux GPS sont listées dans le Tableau 1.1. La largeur de bande des signaux est grande, car le système utilise l'étalement de spectre comme technique.

Tableau 1.1 Caractéristiques physiques des signaux GPS

Tiré de (ARINC research corporation, 2000) (ARINC Incorporated, 2001)

| <b>Signal</b> | <b>Fréquence porteuse</b> | <b>Bande</b> | <b>Polarisation</b> |

|---------------|---------------------------|--------------|---------------------|

| L1            | 1575.42 MHz               | 20.46 MHz    | Circulaire droite   |

| L2            | 1227.6 MHz                | 20.46 MHz    | Circulaire droite   |

| L5            | 1176.45 MHz               | 24 MHz       | Circulaire droite   |

La Figure 1.5 illustre le plan de fréquence des signaux GPS. Les fréquences L1, L2 et L5 doivent dériver d'une même source de fréquence,  $f_0=10.23$  MHz, commune sur les satellites (ARINC research corporation, 2000). De cette façon, on obtient  $f_{L1}=154 \cdot f_0$ ,  $f_{L2}=120 \cdot f_0$  et  $f_{L5}=115 \cdot f_0$ .

**Figure 1.5 Le plan de fréquence des signaux GPS.**

### 1.2.2 Spécifications du système Galileo

Le système de positionnement Galileo a été conçu principalement pour enlever la dépendance de l'Europe vis-à-vis des Etats-Unis.

#### Structure du système Galileo

Le système Galileo est composé de quatre segments indépendants (European Space Agency, 2006) : spatial, sol de contrôle, sol de mission et test des utilisateurs :

- Segment spatial : il est constitué de 30 satellites placés sur trois orbites circulaires à une altitude de 23,616 km. Chaque satellite comprend plusieurs horloges atomiques pour calculer le temps d'émission des signaux;

- Segment sol de contrôle : ce segment a pour tâche de surveiller et de contrôler les satellites, il est composé de deux centres localisés en Europe et de cinq autres stations qui ont la charge de maintenir les liaisons de télécommande et de téléméasures avec les satellites;

- Segment sol de mission : ce segment est chargé de créer les messages de navigation diffusés par le satellite. Il permet aussi de localiser les éventuelles anomalies du système et prévenir les récepteurs via des messages envoyés par les satellites;

- Segment de test des utilisateurs : comme c'est le cas pour le GPS, cette partie est constituée par les récepteurs qui ne font que recevoir les signaux provenant des satellites.

### **Spécifications des signaux Galileo**

Chaque satellite Galileo transmet des messages dans les signaux E1, E6, E5a et E5b (European Space Agency, 2006) :

- Signal E1 : ce signal est transmis sur la bande L1 comprenant deux canaux (E1-B et E1-C). Il inclut des données de navigation accessibles au grand public. Le canal E1-B transmet des données et le canal E1-C transmet des signaux pilotes. Les signaux pilotes permettent, comme indiquent leurs noms, de guider le récepteur pour l'acquisition du signal E1-B;

- Signal E6 : ce signal transporte des informations pour un but commercial. Il comprend deux canaux (E6-B et E6-C). Le premier étant un canal de données et le deuxième transmet des signaux pilotes;

- Signal E5a : ce signal est transmis sur la bande E5 et comprend deux canaux (données, pilote). Il transporte des données de navigation accessible pour le grand public;

- Signal E5b : ce signal est aussi transmis sur la bande E5 et comprend aussi deux canaux, un pour les données de navigation et un pour les signaux pilotes. Ce signal comporte des données non cryptées accessibles par tous les utilisateurs et des données cryptées réservées pour un usage commercial.

**Figure 1.6 Plan de fréquence Galileo.**

Comme c'est le cas pour les signaux GPS, le système Galileo utilise la technique DS-CDMA et par conséquent, les satellites émettent chaque type de signal dans une même bande de fréquence. Chaque satellite possède son propre code pour être différencié lors de la réception. La Figure 1.6 illustre les fréquences centrales et les bandes de fréquences des différents signaux Galileo. Ces informations sont résumées dans le Tableau 1.2 et 1.3.

Tableau 1.2 Fréquences porteuses des signaux Galileo

Tiré de (Galileo Open Service, 2006)

| Signal       | Fréquence porteuse |

|--------------|--------------------|

| E5a          | 1176.45 MHz        |

| E5b          | 1207.14 MHz        |

| E5 (E5a+E5b) | 1191.795 MHz       |

| E6           | 1278.75 MHz        |

| E1           | 1575.42 MHz        |

Tableau 1.3 Bande de réception et polarisation des signaux Galileo

Tiré de (Galileo Open Service, 2006)

| Signal | Bandé de réception | Polarisation      |

|--------|--------------------|-------------------|

| E5     | 51.150 MHz         | Circulaire droite |

| E6     | 40.92 MHz          | Circulaire droite |

| E1     | 24.552 MHz         | Circulaire droite |

La composition des deux signaux E5a et E5b est considérée en un seul signal E5 de fréquence centrale  $\frac{f_{E5a} + f_{E5b}}{2}$ . Les deux fréquences étant proches l'une de l'autre, ils peuvent être traités comme une seule bande large avec une implémentation spécifique au niveau des récepteurs. E5 n'est pas un signal à part entière, il est juste la composition des deux signaux E5a et E5b (European Space Agency, 2006).

### 1.3 Présentation globale du simulateur de signaux GNSS

Au lancement du projet, il n'existait pas de simulateur de signaux Galileo sur le marché. C'était une bonne initiative de démarrer le projet d'un simulateur hybride GPS/Galileo. Dernièrement, un tel simulateur a été mis sur le marché, mais il est encore trop coûteux (autour de 800,000 \$) ce qui est stimulant pour notre projet en cours, présentant un coût nettement inférieur.

Le projet est très riche en matière de développement. Il inclut plusieurs sections qui opèrent ensemble. L'architecture est centrée autour d'une plateforme de développement à base de FPGA (*Field Programmable Gate Array*) qui offre une très grande flexibilité au niveau du développement vu que le système de positionnement Galileo était encore en phase de développement et était susceptible à des changements majeurs. Cette plateforme est reliée à un logiciel qui gère la nature de la simulation et effectue tous les calculs nécessaires au bon

déroulement du scénario. Enfin, une partie analogique RF (Radio Fréquence) complète le tout en générant les signaux désirés.

#### 1.4 Architecture du simulateur

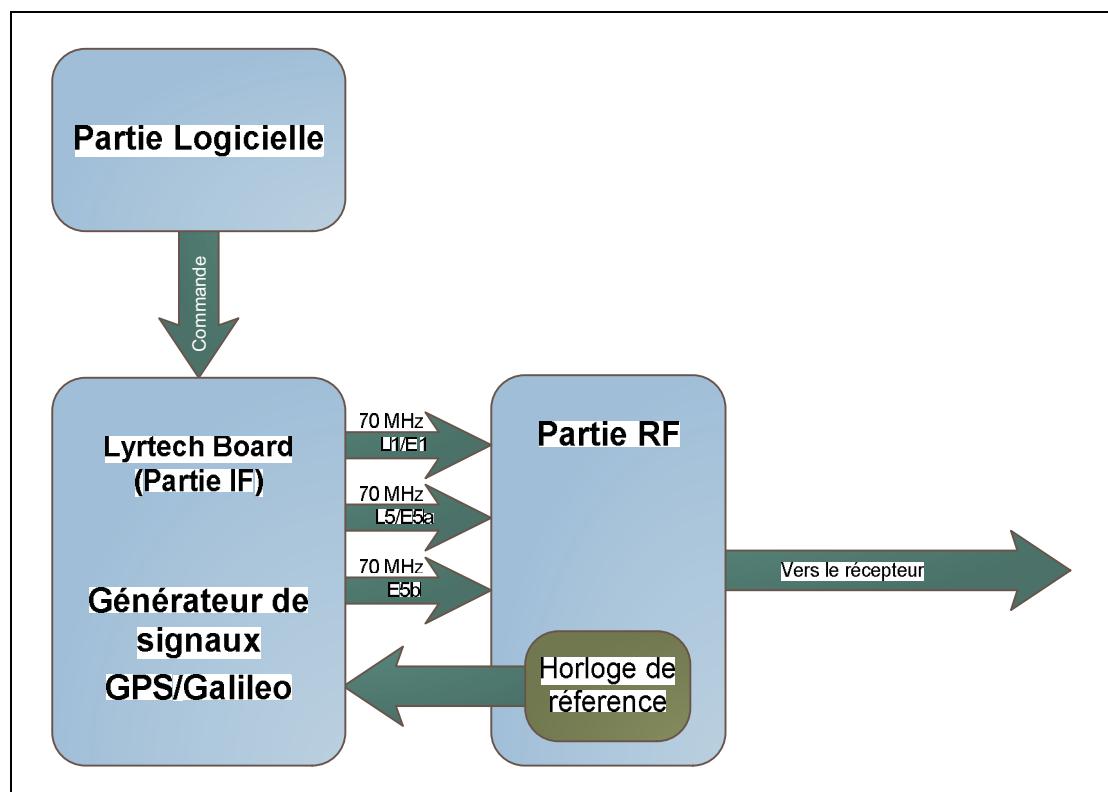

Comme décrit dans l'introduction, le simulateur comporte trois parties fondamentales : la partie logicielle, la partie de traitement des signaux (partie IF) et la partie RF. La Figure 1.7 illustre globalement l'architecture du simulateur GNSS.

**Figure 1.7 Structure du simulateur GNSS.**

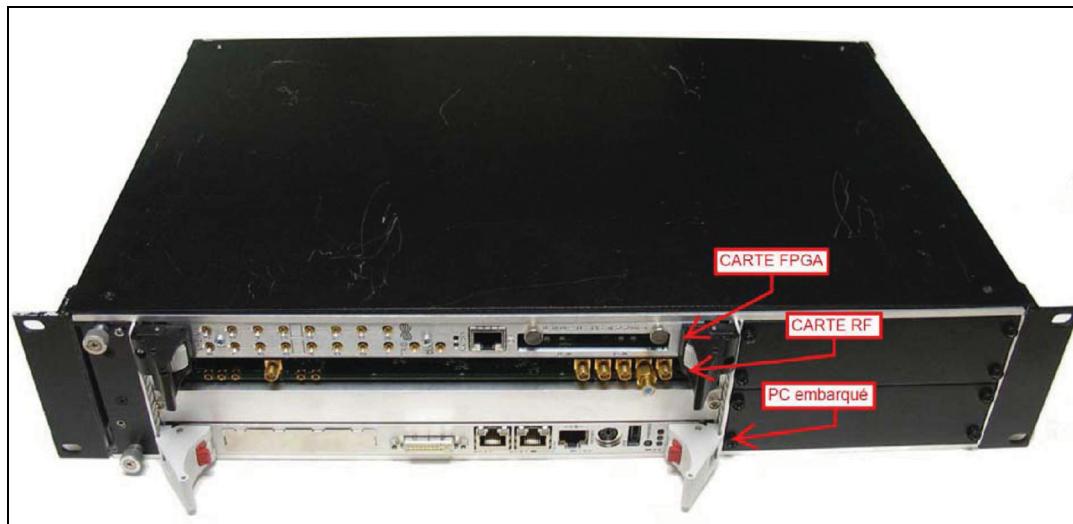

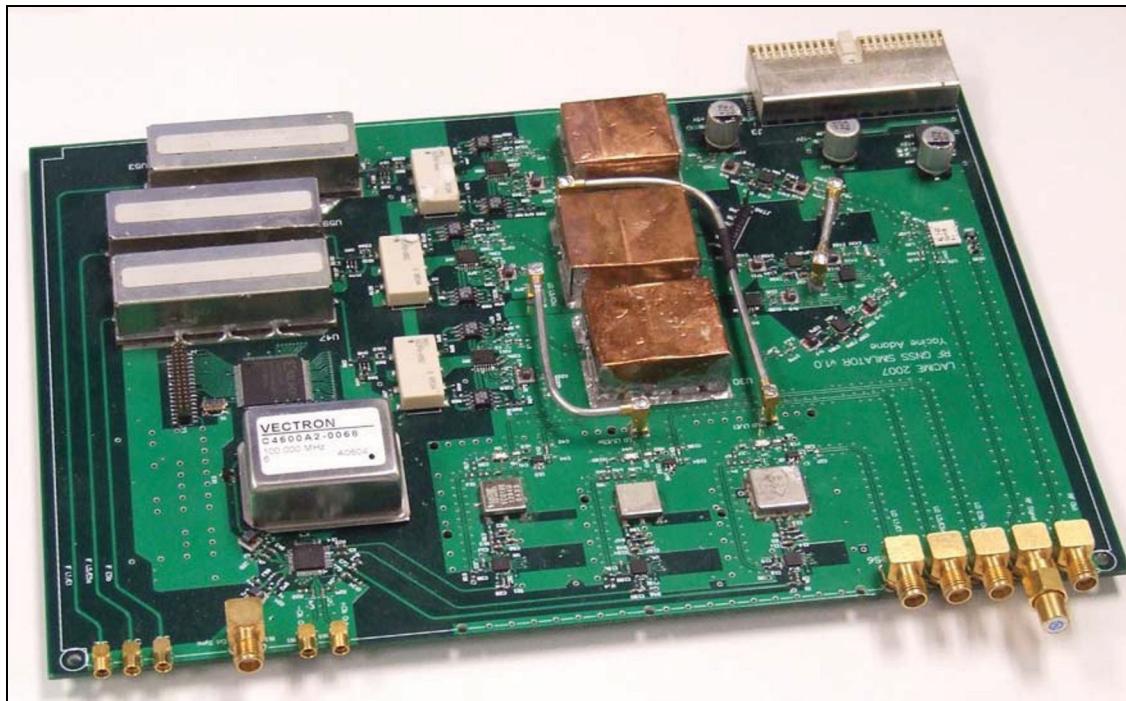

La totalité du simulateur est intégrée dans un boîtier compact PCI (*Peripheral Component Interconnect*), qui comporte une carte mère compacte d'un PC embarqué, une carte à base de FPGA de la compagnie Lyrtech pour le traitement en temps réel des signaux ainsi qu'une carte RF développée au sein du LACIME. Les signaux E1, L5, E5a et E5b ne sont pas

implémentés dans la partie logicielle du simulateur. La Figure 1.8 présente une photo du simulateur actuel.

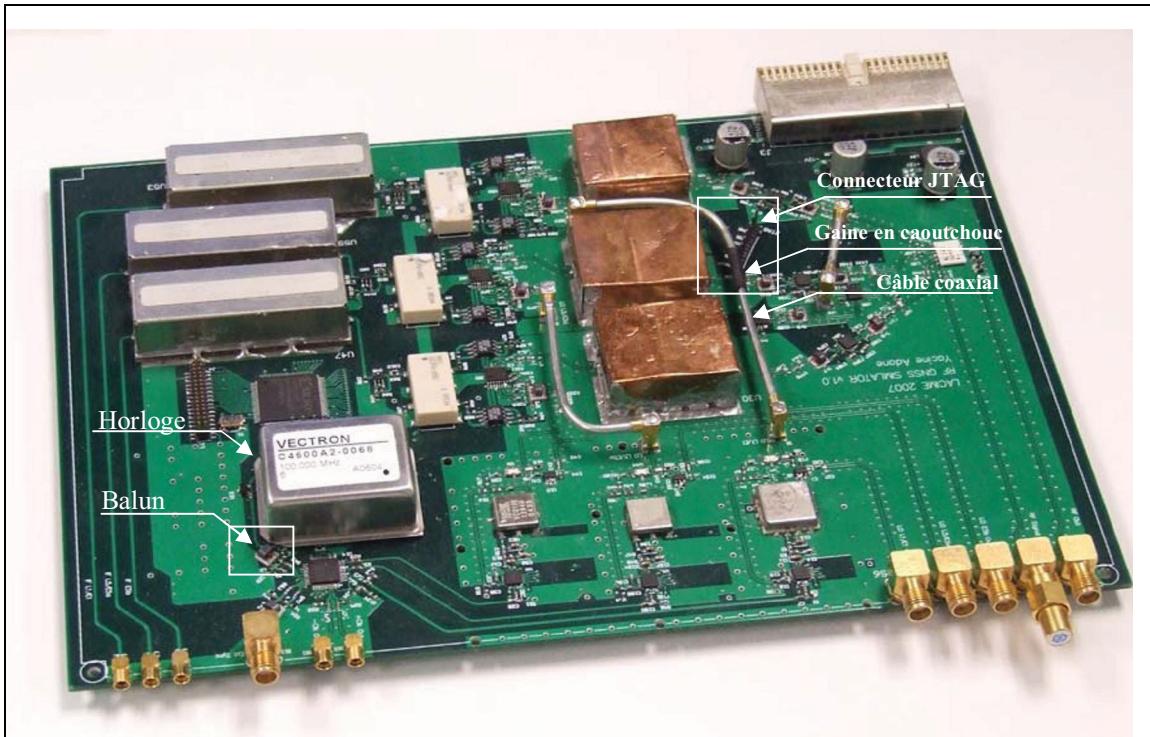

**Figure 1.8 Le simulateur GNSS du LACIME.**

#### 1.4.1 Partie logicielle

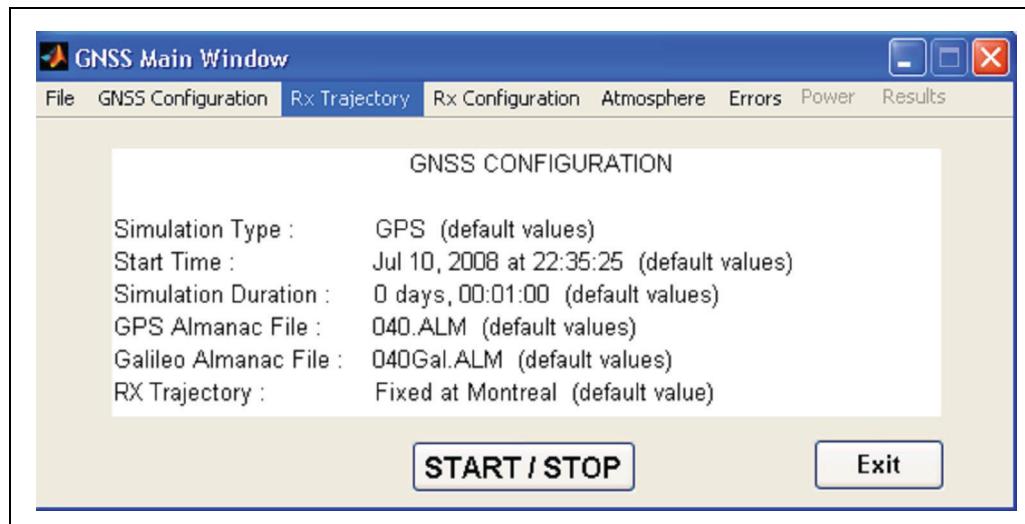

La partie logicielle est responsable de la configuration du scénario de navigation et du calcul des paramètres nécessaires pour la simulation. Elle est composée d'un cœur de base en MATLAB et d'une partie C++. La partie MATLAB sert à exécuter tous les calculs nécessaires ainsi qu'à configurer la simulation. Elle intègre des interfaces d'utilisation (voir Figure 1.9 et Figure 1.10) permettant de définir le scénario de navigation et les paramètres primaires nécessaires à l'élaboration de la simulation. La section C++ du simulateur a pour rôle de mettre en forme les données calculées par MATLAB et les envoyer à la carte de traitement des signaux en temps réel via le port *PCI Express*. Une mise à jour de la partie logicielle est en cours de développement par un collaborateur afin de migrer tout le code en C++.

**Figure 1.9 Interface principale du simulateur.**

**Figure 1.10 Interface du simulateur de trajectoire.**

La partie logicielle permet aussi de piloter la partie RF du simulateur. En effet, l'utilisateur peut définir plusieurs paramètres se rapportant au fonctionnement de la partie analogique du simulateur à savoir, choisir l'horloge de référence du système (interne ou externe) et fixer la puissance des signaux GPS et Galileo. Le contrôle de puissance n'est pas implémentée dans l'ancienne version de la partie logicielle. Elle l'est dans la nouvelle version entièrement développée en C++ et sera traité dans le chapitre suivant.

#### 1.4.2 Partie IF

La partie IF (*Intermediate Frequency*) est celle responsable du traitement numérique des signaux en temps réel. C'est une carte électronique à base de FPGA. Elle sert à mettre en forme les signaux GPS et Galileo (codage, modulation...) à partir des informations reçues de la partie logicielle. Les signaux sont donc générés à une fréquence intermédiaire de 70 MHz pour être, ensuite, convertis en analogique par un CNA (Convertisseur Analogique Numérique) ou DAC en anglais (*Digital to Analog Converter*). Ces signaux sont envoyés vers la carte RF, dernier maillon du simulateur. La partie IF sert aussi de relais de communication entre la partie logicielle et la partie RF du simulateur pour des fins de contrôle (ex : puissance des signaux).

#### 1.4.3 Partie RF

La partie RF du simulateur a pour rôle de translater la fréquence des signaux (70 MHz) aux fréquences désirées GPS et Galileo. Cette partie est au cœur de nos travaux. Elle est étudiée plus en détail dans la section suivante de ce chapitre.

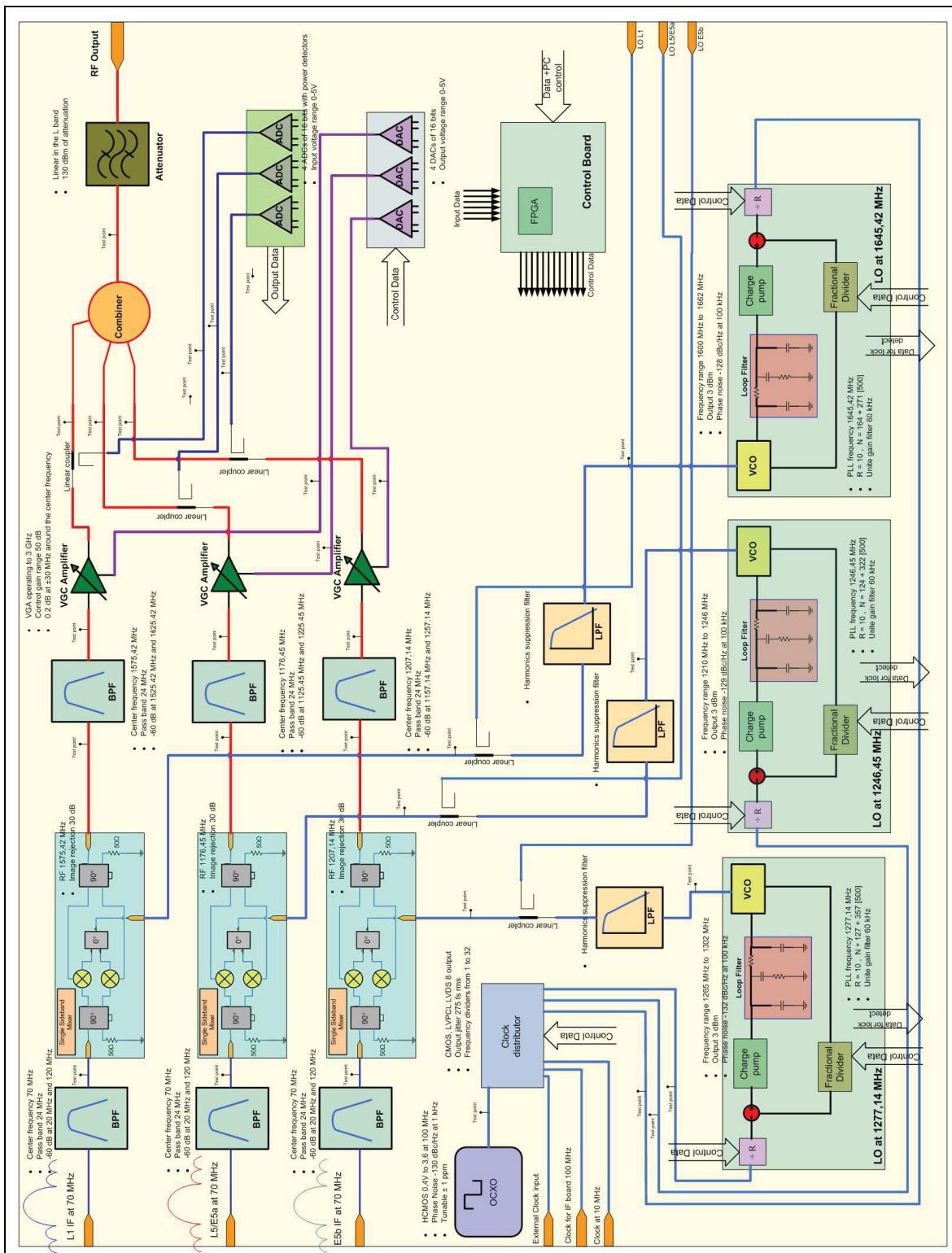

### 1.5 Description de la partie RF du simulateur

La partie RF consiste en trois transmetteurs RF qui permettent de translater les signaux reçus de la partie IF aux fréquences des signaux transmis par les satellites GPS et Galileo à savoir L1, L5, E1, E5a et E5b. Elle permet aussi de contrôler la puissance de ces signaux à sa sortie de façon à ce qu'ils arrivent au récepteur de test comme s'ils étaient reçus par leurs antennes

(c'est-à-dire très affaiblis). Cette section du simulateur a été en grande partie développée par un collaborateur qui a travaillé longuement sur le projet. J'ai principalement travaillé sur la partie de contrôle et d'ajustement de la puissance des signaux ainsi que sur le débogage de la carte RF finale.

La partie RF du simulateur est composée de trois sous chaines qui partagent des ressources communes. Chacune de ces chaines est assignée à un des signaux issus de la partie IF et les transpose aux fréquences suivantes :

- $f=1575.42$  MHz pour le signal GPS L1 et Galileo E1;

- $f=1176.45$  MHz pour les signaux GPS L5 et Galileo E5a;

- $f=1207.14$  MHz pour le signal E5b.

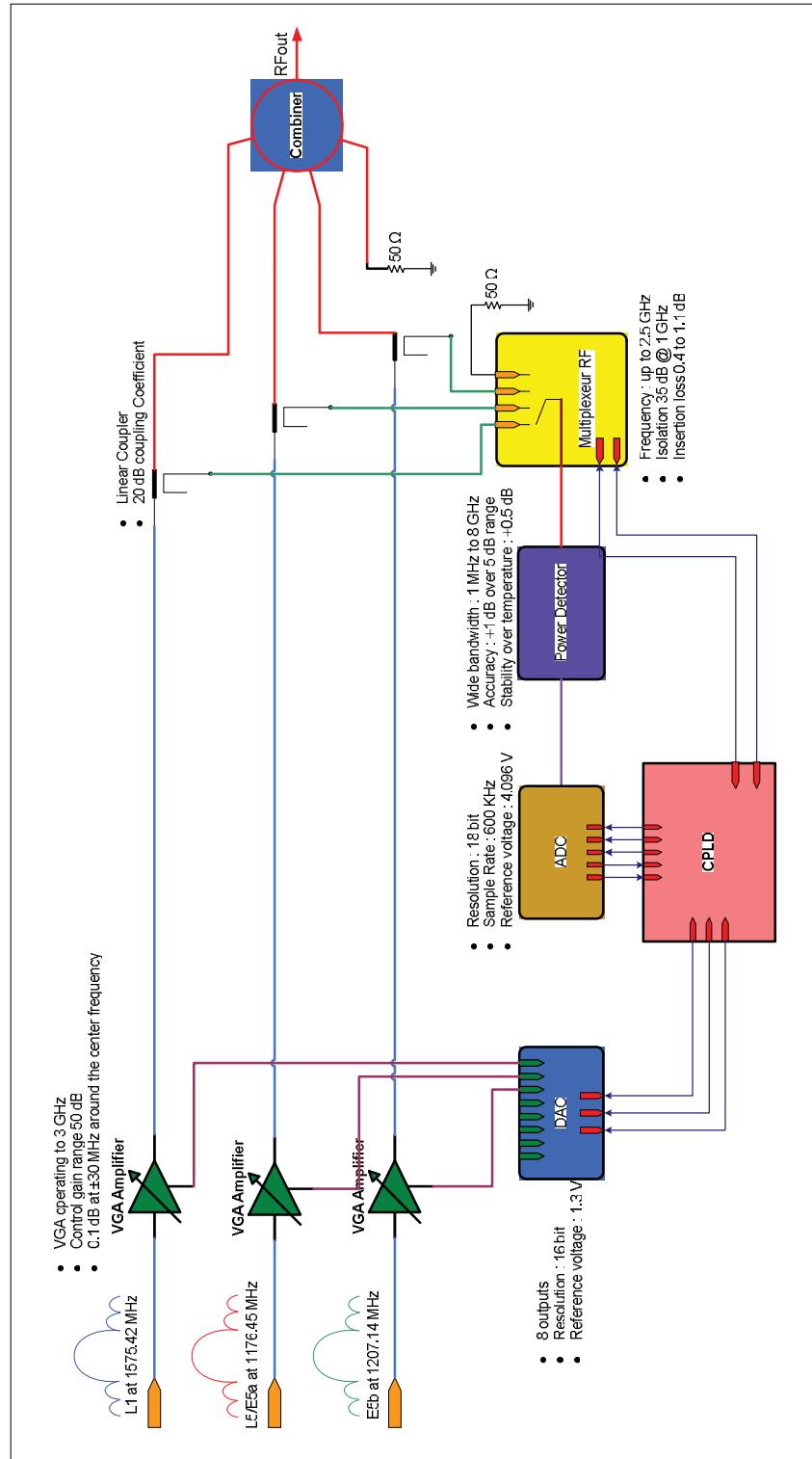

L'architecture détaillée de la partie RF est illustrée par la Figure 1.11.

Figure 1.11 Architecture de la partie RF du simulateur.

Les composants communs aux chaines d'émissions sont les suivants :

- Horloge de référence : c'est une horloge OCXO (*Oven Controlled X-tal (Crystal) Oscillator*) de 100 MHz de haute qualité avec un faible bruit de phase et une très faible variation au cours du temps ce qui permet de s'approcher un peu de la qualité des horloges embarquées dans les satellites. Une tension de raffinement de la précision de la fréquence centrale de l'OCXO est disponible dans le composant et fixée expérimentalement, au niveau matériel, en fonction du design;

- Distributeur d'horloge : il permet de distribuer l'horloge vers différents points du simulateur en préservant sa qualité et son niveau de puissance. Ce composant est configurable et peut, donc, soit distribuer l'horloge interne de la carte, soit, pour plus de précision, une horloge externe fournie par l'utilisateur. L'horloge est transmise vers la partie IF du simulateur et elle est utilisée comme horloge de référence. Elle est transmise aussi vers les boucles à verrouillage de phase ou PLL en anglais (*Phase Locked Loop*) pour chacune de chaines d'émissions;

- Calibration et ajustement de la puissance : ce système comporte plusieurs composants qui permettent de calibrer le niveau de puissance des signaux RF ainsi que leurs niveaux à la sortie de la partie RF. Ce système présente une grande partie de nos travaux et sera détaillé dans le chapitre 2;

- Combineur : il permet de combiner les signaux issus des trois chaines d'émissions sur une seule ligne de transmission;

- Atténuateurs fixes : ce sont deux atténuateurs de 20 dB chacun. Ils sont placés après le combineur afin d'atténuer le signal final pour que sa puissance soit conforme à la réalité;

- CPLD (*Complex Programmable Logic Device*): il en existe deux sur la carte. Le premier a pour tâche de commander la tension de précision de l'horloge de référence, de configurer le distributeur d'horloge (horloge interne ou externe) et de programmer les trois PLL pour qu'ils verrouillent aux bonnes fréquences. Le deuxième CPLD est utilisé pour piloter le système de contrôle des puissances des signaux.

Les trois chaines d'émissions sont identiques sauf qu'ils sont adaptées à chacun des signaux GPS et Galileo. Les composants de ces chaines sont les suivants :

- Filtre IF : c'est un filtre passe-bande de fréquence centrale 70 MHz et d'une largeur de bande de 24 MHz. Il a une haute rejection hors bande qui filtre les harmoniques générés par le CNA;

- Boucle à verrouillage de phase : c'est un synthétiseur de fréquence qui génère l'Oscillateur local ou, en anglais, LO (*Local Oscillator*) requis pour chaque chaîne d'émission. Les fréquences générées sont 1645,42 MHz pour le signal L1, 1246,45 MHz pour les signaux L5 et E5a et enfin 1277,14 MHz pour le signal E5b. Chaque PLL comporte (voir annexe III) :

- Un synthétiseur de fréquence fractionnel qui, à partir d'un signal de référence (100 MHz dans notre cas), génère la fréquence désirée,

- Un filtre de boucle conçu pour une minimisation du bruit de phase, et

- Un VCO (*Voltage Controlled Oscillator*) : chaque chaîne a son propre VCO à bande étroite qui permet d'obtenir de bonnes performances au niveau de la précision et du bruit de phase;

- Mélangeur à bande latérale unique ou en anglais SSBM (*Single Side Band Mixer*) : ce composant permet de transposer les signaux IF à la fréquence désirée. Son constituant de base est un modulateur quadratique (Modulateur IQ) qui, combiné à un coupleur 3 dB hybride 90°, permet d'atténuer un des deux signaux générés par le mélangeur (NorthWood Labs LL, 2003);

- Filtre RF : les signaux GPS et Galileo étant centrés sur des fréquences différentes, les filtres RF sont par conséquent différents. Ces filtres sont à base de quatre résonateurs (*Stepped impedance hairpin resonator*) qui sont couplés entre eux. Une multitude de paramètres sont contrôlés pour obtenir la bonne fréquence centrale et la largeur de bande requise. Ils ont été conçus et fabriqués au sein du laboratoire en technologie micro-ruban ou *micro-strip* en anglais (Yacine Adane, 2007); et

- Amplificateur/Atténuateur contrôlé par tension : ou en anglais VGA (*Voltage Controlled Amplifier/Attenuator*). Il assure l'ajustement du niveau de la puissance à la sortie de la

chaine RF. Ce composant est contrôlé par une tension continue (0 à 1.3 V) qui fixe le niveau du gain de l'amplificateur soit en atténuant le signal, soit en l'amplifiant.

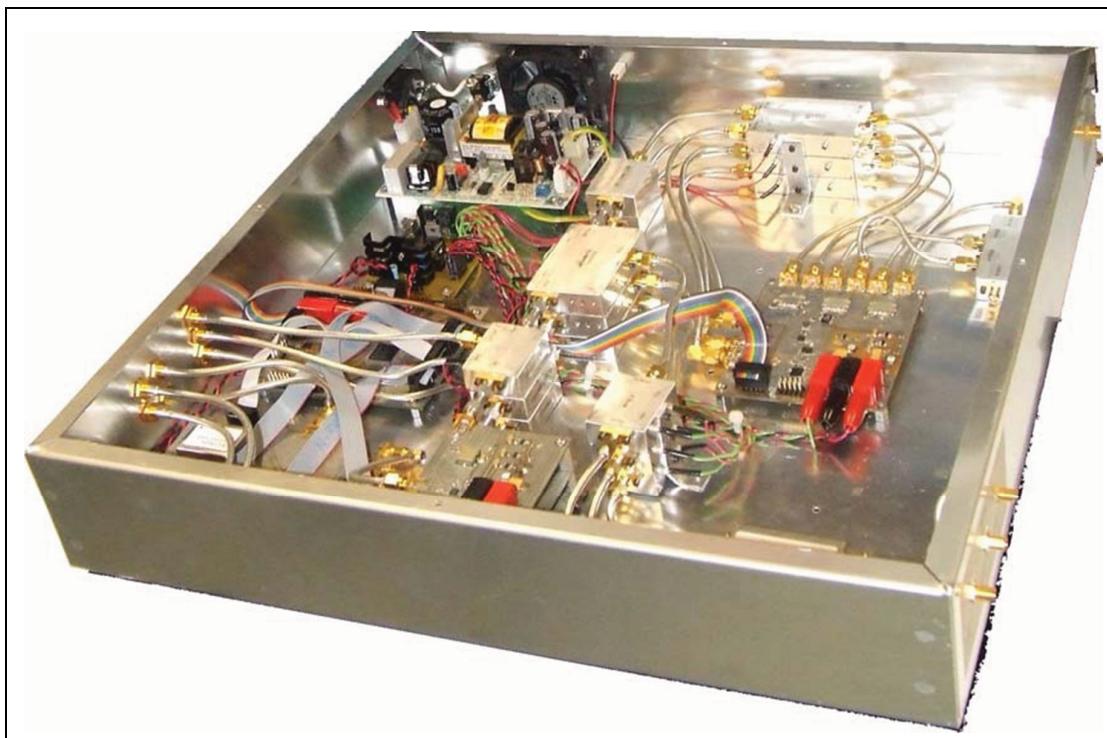

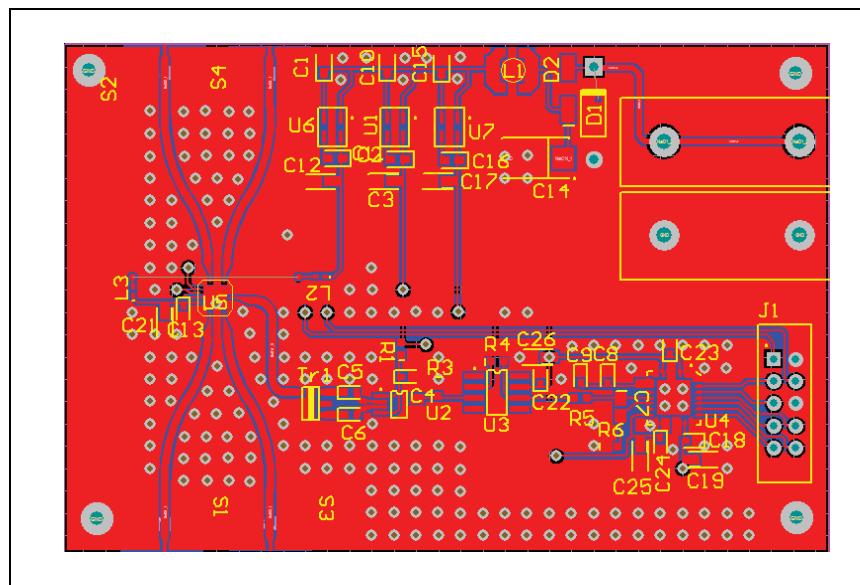

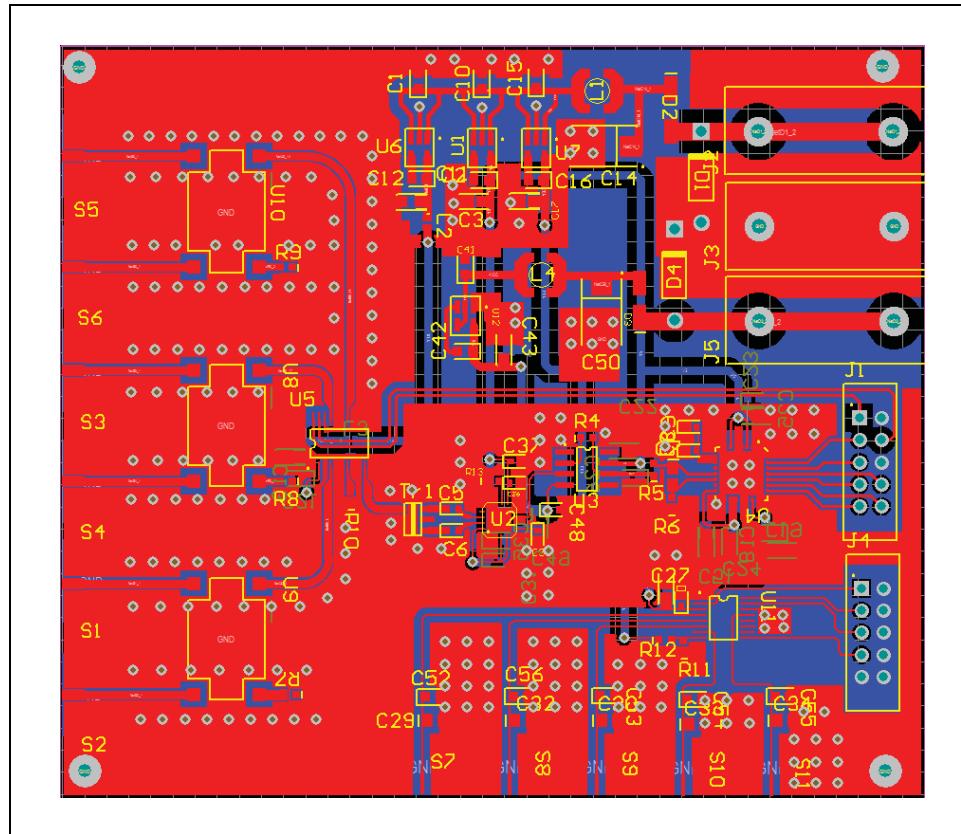

Afin de réaliser une telle architecture, la partie RF a été développée en deux étapes. La première consistait à développer chaque sous-système à part et ensuite connecter le tout ensemble. Cette étape s'est avérée très importante, car elle a permis de tester chaque sous-système et de corriger les problèmes sans pour autant nuire à la totalité du système (réglages, adaptation d'impédance, déverminage des signaux numériques). Le prototype modulaire de la partie RF est présenté dans la Figure 1.12. La deuxième étape de développement consiste en l'intégration de tous les modules sur une seule et unique carte compacte et adaptée au boîtier compact PCI du simulateur. La carte RF complète ainsi réalisée est illustrée par la Figure 1.13.

**Figure 1.12 Plateforme RF modulaire.**

**Figure 1.13 Carte RF finale.**

## 1.6 Défauts reliés au design RF final

Après la conception de la carte RF finale du simulateur, nous nous sommes rendu compte de quelques défauts au niveau du dessin du circuit imprimé et du choix de quelques composants.

### 1.6.1 Défauts reliés au dessin du circuit imprimé

La taille de certains composants n'a pas été prise totalement en compte lors du dessin du circuit imprimé de la carte RF ce qui a conduit à une difficulté lors de l'assemblage et de la soudure des composants sur la carte. Les problèmes que nous avons remarqués sont les suivants :

- L'horloge de référence touche le transformateur RF (*Balun*) sur la couche supérieure du circuit imprimé de la carte RF (encadré en blanc sur la Figure 1.14). Nous avons remédié à ce problème en enlevant une petite partie métallique de la coquille de l'horloge de référence;

- Un connecteur JTAG (*Joint Test Action Group*), dédié pour un des deux CPLD de la carte, a été placé près du câble coaxial reliant la sortie de la PLL du signal L1 au modulateur. Lors de l'assemblage de la carte, nous nous sommes aperçus que le connecteur JTAG touchait le câble coaxial (Conducteur externe à la masse) et nous nous sommes rendu compte, lors du débogage de la carte, qu'il causait un court-circuit vu qu'une patte du connecteur JTAG est connectée à  $V_{DD}$ . Nous avons, alors, résolu ce problème en plaçant une gaine en caoutchouc sur le câble coaxial et nous avons incliné les pattes du connecteur JTAG pour qu'il soit accessible pour la reprogrammation du CPLD sans recourir au détachement du câble coaxial. La partie encadrée de la Figure 1.14 illustre le défaut et la correction réalisée;

- L'empreinte, ou en anglais *footprint*, du connecteur PCI express avec lequel la carte est connectée à la plate-forme a été mal dessiné. Lors de la soudure de ce connecteur, il s'est avéré que les trous, dans la carte RF, étaient plus petits que les pattes du connecteur. Nous avons, alors, aplati ces pattes par une pince pour qu'ils puissent se placer correctement sur la carte.

Ces problèmes ne causent pas une dégradation des performances de la carte RF du simulateur, elles sont juste des défauts mineurs à éviter lors d'une deuxième itération. Les solutions sont simples à réaliser. Pour le premier problème, il suffit de décaler un peu le transformateur RF et ajuster les connexions. De même pour le deuxième problème, il suffit de décaler un peu le connecteur JTAG ou de modifier son orientation. En ce qui concerne le dernier problème, il suffit d'augmenter le diamètre des trous dans l'empreinte du connecteur.

**Figure 1.14 Défauts de dessin du circuit imprimé.**

### 1.6.2 Défauts reliés aux choix des composants

Certains aspects de la carte ont été mal dimensionnés ce qui a causé quelques problèmes au niveau de la validation. Ces erreurs ont été contournées pour pouvoir accéder à des tests en RF. Elles sont au nombre de deux et sont les suivantes :

- Le régulateur de tension qui permet d'alimenter l'horloge de référence de la carte RF ne fournit pas assez de courant. Les spécifications données par le constructeur de l'horloge confirment que ce composant ne consomme pas plus que 500 mA, ce qui s'est révélé faux. Lors de la conception de cette carte, un régulateur de tension qui fournit un maximum de 500 mA a été utilisé ce qui est juste le nécessaire pour faire fonctionner ce composant. Avec la constatation qu'il consommait plus que 500 mA, nous avons, en premier lieu, décidé de mettre deux régulateurs de tension en parallèle (l'un au-dessus de l'autre). Cette solution permettait un fonctionnement normal de la carte, mais c'était juste une solution de dépannage. Après, nous avons cherché d'autres régulateurs de tension qui

pourraient remplacer le précédent et nous avons trouvé un seul et unique composant qui correspondait à tous les critères (*package, pin out*) et qui fournissait un courant de 700 mA au maximum, ce qui a permis de résoudre totalement le problème;

- Lors de sa réception, le signal GPS est très affaibli et se situe au-dessous du plancher de bruit. Dans le cas du simulateur, les signaux doivent sortir à un niveau très bas pour les injecter directement dans le récepteur de test. Pour arriver à cette fin, deux atténuateurs RF, d'une valeur de 20 dB chacun, ont été placé juste avant le connecteur de sortie de la carte RF. Avec ces conditions, les niveaux de puissance des signaux sont encore hauts et n'atteignent pas les niveaux nominaux des signaux GPS et Galileo qui se situent autour de -130 dBm. En effet, le niveau de puissance à la sortie est autour de -70 dBm. En utilisant le VGA qui permet de fournir une atténuation supplémentaire de 30 dB, nous arrivons à un seuil de -100 dBm ce qui est loin des spécifications. Le choix de ces composants n'est pas une erreur en tant que telle, car augmenter les valeurs d'atténuations conduirait à la difficulté de visualiser les signaux sur un analyseur de spectre. Le problème ici, est qu'un espace pour ajouter plus d'atténuateurs n'a pas été prévu. Pour pallier ce problème, nous avons utilisé un atténuateur externe contrôlable qui permet d'ajouter les 60 ou 70 dB d'atténuations. Cette solution est seulement temporaire, car le produit final doit s'affranchir d'un tel atténuateur. Nous avons effectué une recherche de composants chez le même fournisseur d'atténuateur et nous en avons trouvé un, d'une valeur de 30 dB d'atténuation, susceptible de remplacer l'ancien. Nous obtenons alors, sans utiliser l'atténuation supplémentaire du VGA, un niveau de puissance de -90 dBm. Il faut donc, ajouter encore 40 dB d'atténuation sans recourir au VGA, car sa fonction principale est de contrôler la puissance des signaux sur une plage aux alentours de 40 dB. La solution était donc de rechercher d'autres atténuateurs qu'on pourrait insérer dans la carte. Le même fournisseur de composants offre une gamme d'atténuateurs qui peuvent se connecter à une trace linéaire. Il faudrait alors, gratter le cuivre sur la carte, couper la trace et insérer un dernier atténuateur pour atteindre les spécifications. Cette approche permet de régler le problème tout en conservant la carte actuelle. Ces modifications n'ont pas été effectuées sur la carte pour des fins de tests. Néanmoins, les composants ont été choisis et il ne reste qu'à les placer.

Au moment de la rédaction de ce mémoire, la carte est fonctionnelle et permet d'effectuer les tests requis, mais un design final s'impose pour éliminer, d'une façon définitive, les problèmes cités ci-dessus. Il faut aussi penser à changer le CPLD responsable du contrôle de puissance car le design actuel est inséré de justesse. Dans cette partie, ma tâche était d'aider à déboguer la carte RF, aider à trouver des solutions à court terme et trouver les solutions à long terme pour faire un design final sans erreurs.

## 1.7 Conclusion

Ce chapitre a donné un aperçu sur les systèmes GPS et Galileo du point de vue de la structure globale et spécifications des signaux. Nous avons aussi décrit le projet GNSS en cours de développement. Nous avons mis l'accent sur la partie RF. Elle a été développée en deux étapes. Une modulaire qui consiste en la mise en œuvre de chaque sous-système à part et de combiner le tout à la fin. La deuxième s'est effectuée après le débogage du premier prototype et se présente comme l'intégration de tous les sous-systèmes sur une seule carte s'insérant dans un boîtier compact PCI. Le simulateur doit permettre à l'utilisateur de créer le scénario adéquat afin de réaliser ses tests. Il doit être en mesure de reproduire le niveau des puissances des satellites ainsi que le niveau du bruit à la réception. Ceci donnera un control sur la qualité des signaux. Le chapitre suivant traitera le système de contrôle des puissances des signaux issues du simulateur GNSS.

Equation Chapter 2 Section 1

## CHAPITRE 2

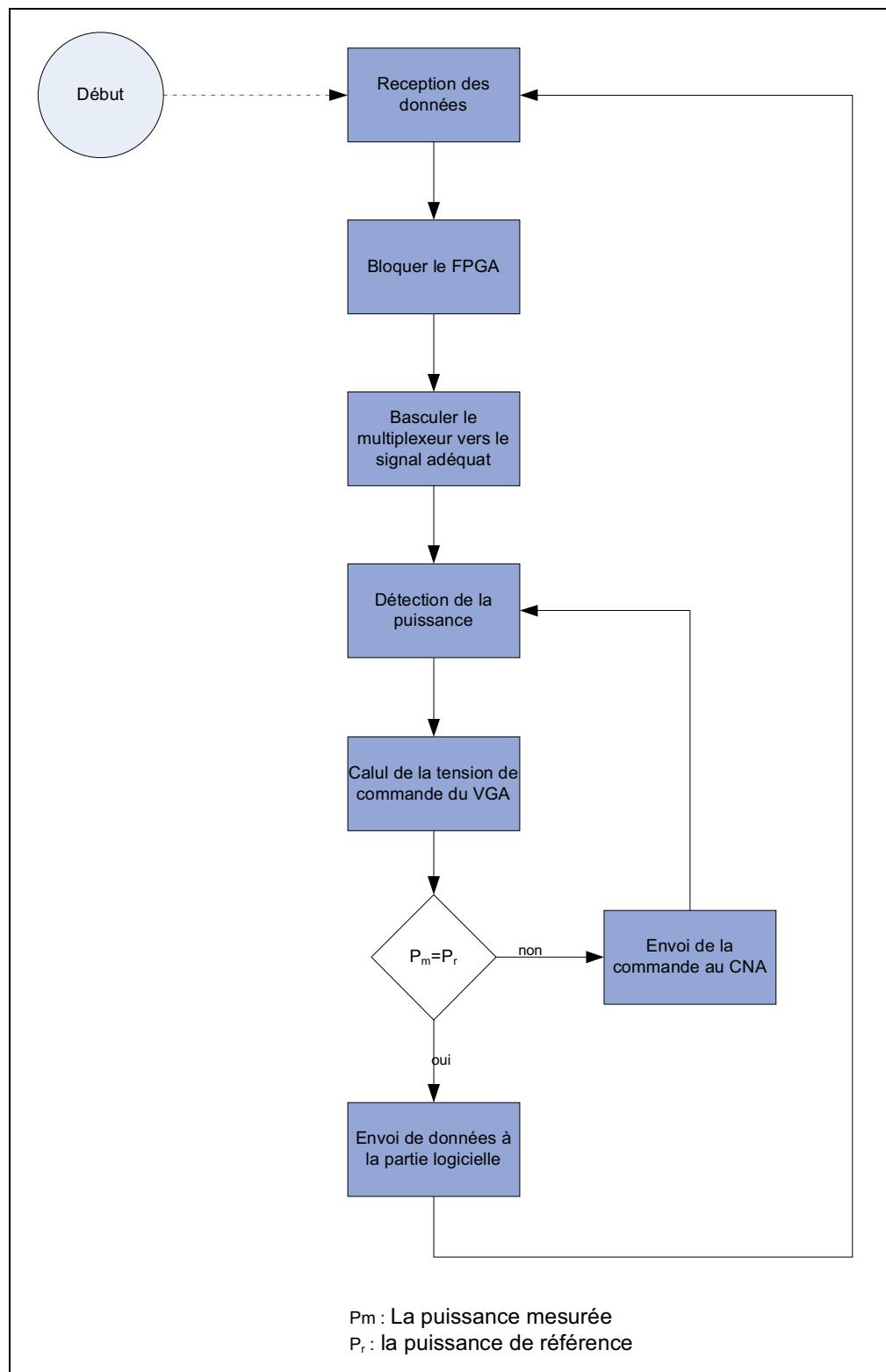

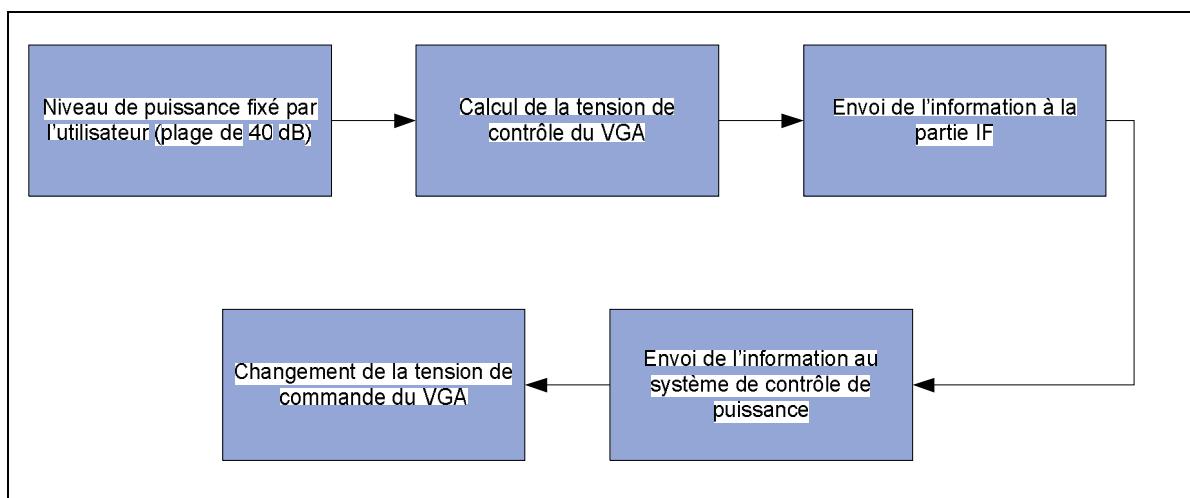

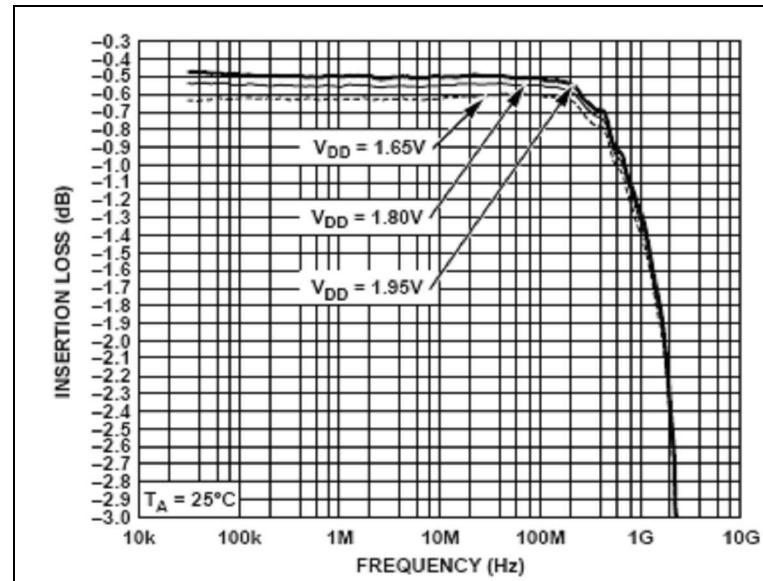

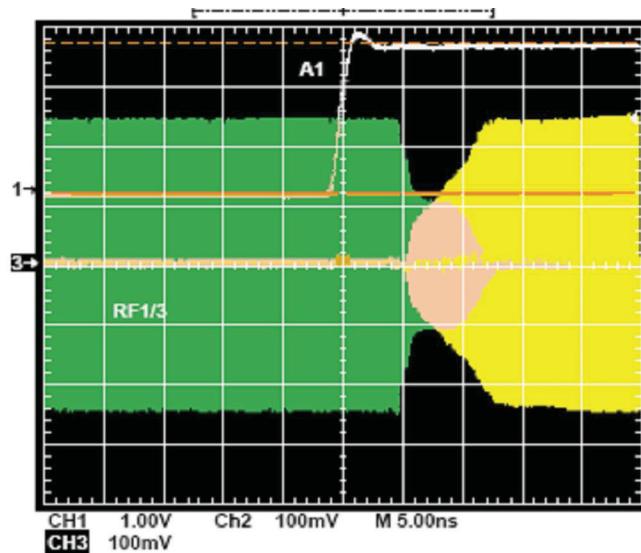

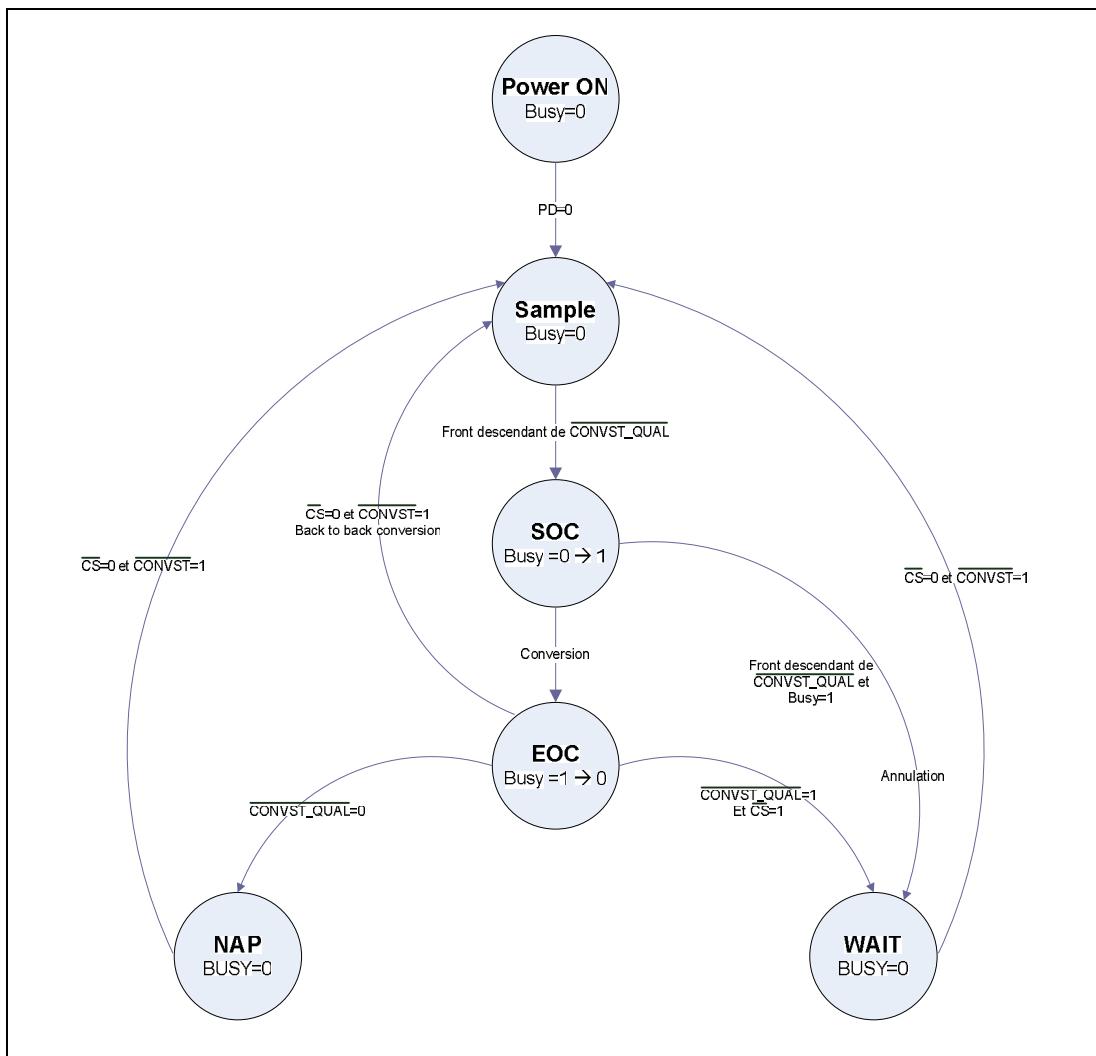

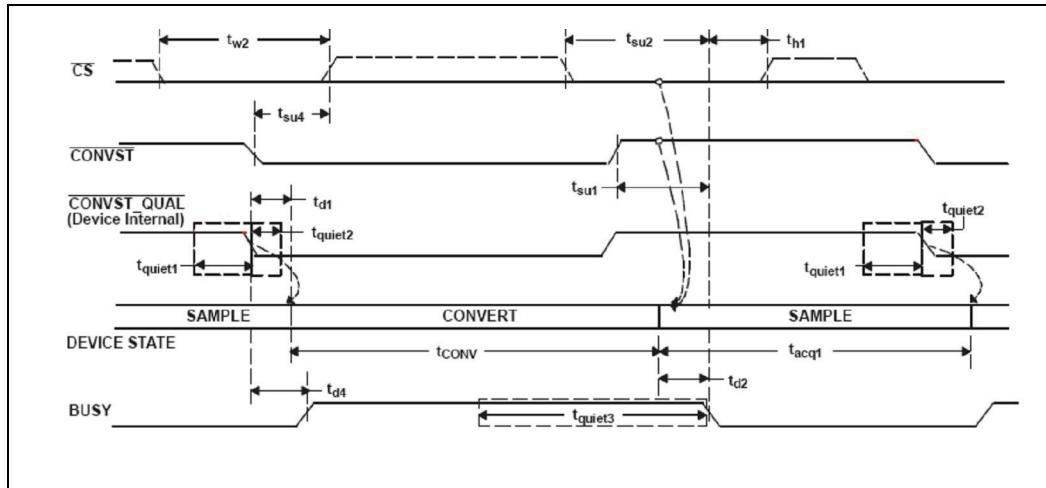

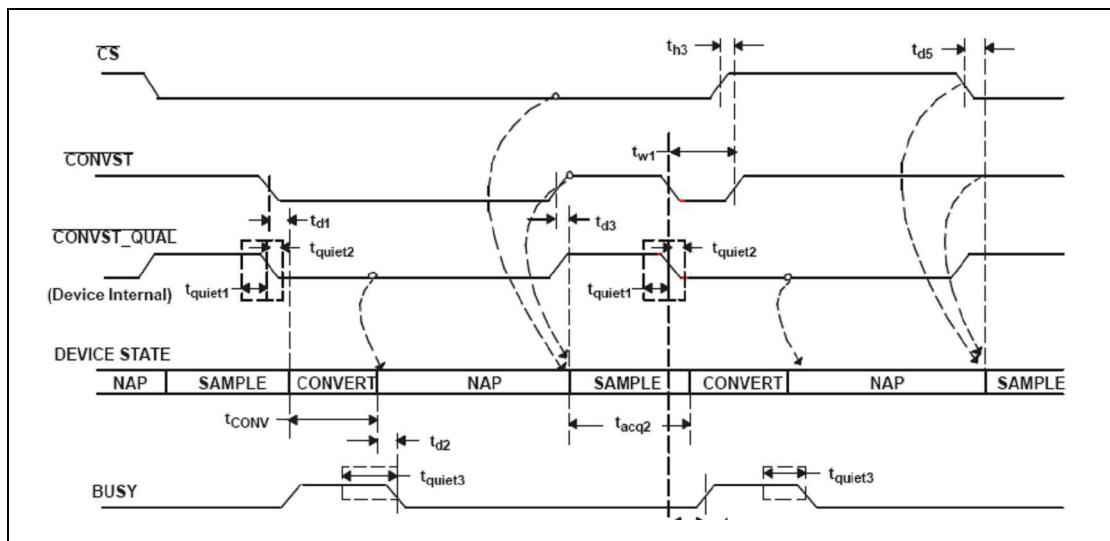

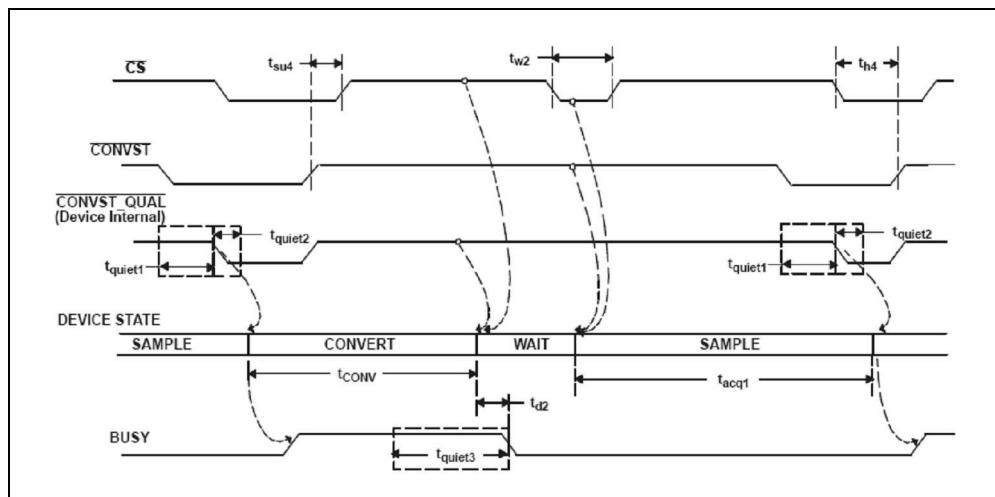

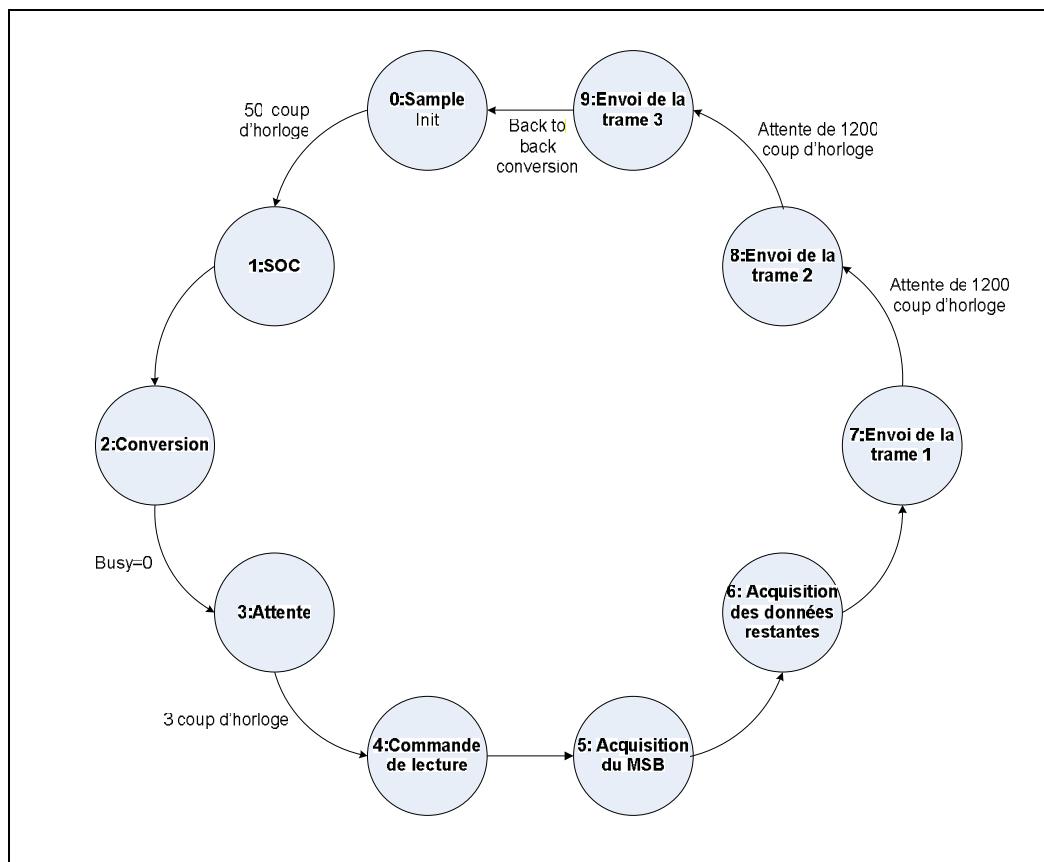

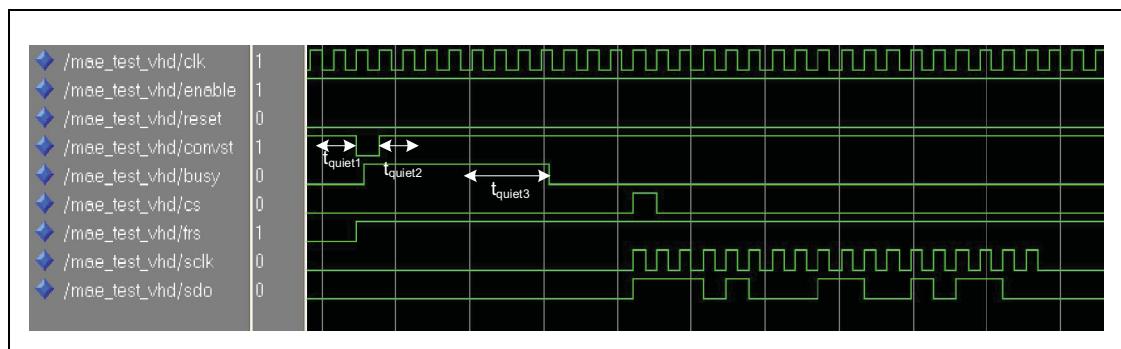

### SYSTÈME DE CONTRÔLE DE PUISSANCE RF