## Low-Power Wideband Receiver Front-End Design for Short-Range IoT Applications

by

#### Arash ABBASI

MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, DECEMBER 9, 2022

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

## THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

M. Frederic Nabki, Thesis supervisor Department of Electrical Engineering, École de technologie supérieure

M. DAVID ST-ONGE, Chair, Board of Examiners Department of Mechanical Engineering, École de technologie supérieure

M. DOMINIC DESLANDES, Member of the Jury Department of Electrical Engineering, École de technologie supérieure

M. YVES AUDET, External Examiner Department of Electrical Engineering, Polytechnique Montréal

# THIS THESIS WAS PRESENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC ON "NOVEMBER 25, 2022"

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### **ACKNOWLEDGEMENTS**

First of all, I would like to express my sincere gratitude to my thesis supervisor, Professor Frédéric Nabki. I would particularly like to thank him for the freedom he gave me in choosing the direction to give to my research project, his advice and ideas which made this doctorate what it is today and lots of kind supports during the hard time of COVID-19 pandemic.

I would like to thank Norm, Jackson, Mark, Lorenzo, Eric, Matthew, Thomas, Peter, Ali, Miranda... at Sequans communications for their enthusiasm to the project, technical supports and encouragements. Special Thanks to Luke Parker for his kind support for PCB modifications.

I would also like to thank all those who contributed to this thesis. I must mention here in particular the company CMC Microsystems, which provided the design tools and allowed the manufacture of chips designed during this doctorate.

Thank to my lovely friends, Anousha, Mehran, Bahador, Ehsan, Ali and Amir to strike a balance with life outside the dark depths of the lab and office. Special thanks to Mathieu for IT supports and logistics.

And finally, I would also like to thank my parents, my sister and my brother for their support throughout my life and my studies. Dad, Mom, Golnaz and Amir thank you! Without you, none of this would have been possible.

### Conception de récepteur RF large bande à basse consommation pour les applications IoT à courte portée

#### Arash ABBASI

#### **RÉSUMÉ**

La croissance rapide de l'internet des objets (IoT) promet la mise en place d'un environnement intelligent, y compris la domotique. Des milliards d'appareils IoT sont nécessaires pour atteindre cet objectif. En conséquence, la réduction d'une fraction de la consommation d'énergie de chaque appareil IoT peut entraîner une importante réduction globale de la consommation d'énergie à l'échelle mondiale. Sans aucun doute, l'émetteur-récepteur RF joue un rôle important pour définir la consommation électrique globale des modules IoT.

L'objectif de ce travail est de développer un récepteur RF à faible consommation d'énergie et à large bande pour les applications IoT. Pour ce faire, dans un premier temps, une revue de la littérature est présentée. Elle se concentre sur les techniques de conception de récepteurs à faible puissance et examine les circuits en détail.

À la suite de la revue de littérature, un tutoriel de conception détaillé comprenant la procédure de conception et la caractérisation est présenté pour fournir une approche de conception systématique du récepteur RF à réutilisation du courant proposé.

Un récepteur RF à faible puissance et à réutilisation de courant utilisant une inductance active et des techniques d'annulation de bruit 1/f pour les applications en bande L est présenté. L'inductance active améliore le facteur de bruit du récepteur à des fréquences plus élevées et les techniques d'annulation de bruit suppriment le bruit à basses fréquences.

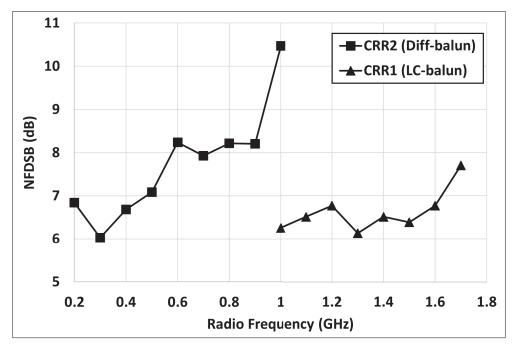

Une comparaison d'un balun différentiel hors puce et d'un balun LC utilisant le même récepteur RF à réutilisation de courant avec et sans inductance sur puce est présentée pour évaluer les performances en utilisant différents réseaux d'adaptation et bandes de fréquences.

En somme, cette thèse décrit l'étude, la conception et la caractérisation d'un récepteur RF à faible puissance et à large bande à réutilisation du courant qui peut être conçu dans plusieurs bandes fréquentielles pour utilisation dans différentes applications IoT.

**Mots-clés:** IoT, current-reuse receiver, low noise amplifier, wideband, low-power

#### Low-Power Wideband Receiver Front-End Design for Short-Range IoT Applications

#### Arash ABBASI

#### **ABSTRACT**

The fast growth of the internet-of-things (IoT) promises the establishment of a smart environment including home automation, health monitoring, location tracking etc. Billions of IoT devices are needed to achieve this goal and connect the objects around us. This introduces a need to develop low-power IoT devices. Accordingly, reducing by a fraction of the power consumption in each IoT device can lead to an important overall energy use reduction globally. undoubtedly, the RF transceiver plays a significant role to define the overall power consumption of the IoT module.

The aim of this work is to develop a low-power and wideband current-reuse receiver front-end for IoT applications. The wideband feature covers several frequency bands to reduce the number of receivers required. To do this, first, a literature review is presented. It focuses on the low-power receiver design techniques and discusses the circuits in detail.

Following the literature review, A detailed design tutorial including the design procedures and characterization results is presented to provide a systematic design approach of the current-reuse receiver front-end to breakdown the circuit to sub-blocks and perform the design as a conventional receiver architecture.

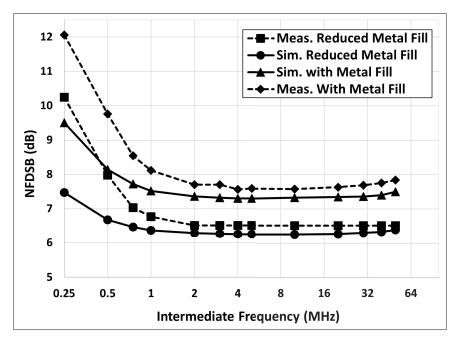

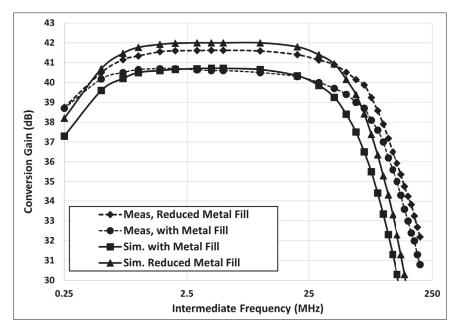

A low-power RF-to-BB current-reuse receiver front-end using an active-inductor and 1/f noise-cancellation techniques for L-band applications is presented. The active-inductor improves the receiver noise-figure at higher frequencies and the noise-cancellation technique suppresses the low frequency noise. Both active-inductor and 1/f noise-cancellation techniques help enhance the receiver noise figure. The effect of the metal fill on the performance is studied in measurements that shows the notable improvement in the noise figure performance.

A comparison of an off-chip differential and an LC Balun employing the same current-reuse receiver front-end with and without an on-chip inductor is presented to evaluate the performance using different matching networks and frequencies. This demonstrates that the receiver can be tuned to any frequency band by adjusting the matching network.

Overall, this thesis describes the study, design and characterization of low-power and wideband current-reuse receiver front-ends that can be tuned for any frequency band to be used for different IoT applications. The active-inductor and 1/f noise-cancellation techniques introduced in this work improve the performance of the receiver and allow it to maintain its performance at higher frequencies even in a relatively large 130 nm CMOS process.

**Keywords:** IoT, current-reuse receiver, low noise amplifier, wideband, low-power

#### **TABLE OF CONTENTS**

|      |         |                                                              | Page |

|------|---------|--------------------------------------------------------------|------|

| INTR | ODUCTI  | ON                                                           | 1    |

| CHAF | PTER 1  | LITERATURE REVIEW                                            | 7    |

| 1.1  |         | reuse receiver                                               |      |

|      | 1.1.1   | Current-Reuse Receiver with Stacked LNTA, Mixer and VCO      | 7    |

|      | 1.1.2   | Current-Reuse Receiver with Balun-LNA                        |      |

|      | 1.1.3   | Current-Reuse Receiver with an N-path Configuration          |      |

|      | 1.1.4   | Current-Reuse Receiver with Stacked I/Q Paths                |      |

|      | 1.1.5   | Source-Degenerated Current-Reuse Receiver with 1/f Reduction |      |

|      | 1.1.6   | Quadrature RF-to-Baseband-Current-Reuse Architecture         |      |

| 1.2  | Functio | n-Reuse Architecture                                         |      |

| 1.3  |         | ow Power Receivers                                           |      |

|      | 1.3.1   | ULP Receiver for MedRadio Standard using a New Mixing        |      |

|      |         | Technique                                                    | 20   |

|      | 1.3.2   | ULP Receiver using Novel $g_m$ -Boosted Common-Gate LNA      |      |

|      | 1.3.3   | Receiver Employing an LNTA and Current-Reuse Image Rejection |      |

|      |         | Filter                                                       | 23   |

| 1.4  | Conclus | sion                                                         | 25   |

|      |         |                                                              |      |

| CHAF | PTER 2  | A DESIGN METHODOLOGY FOR WIDEBAND CURRENT-                   |      |

|      |         | REUSE RECEIVER FRONT-ENDS AIMED AT LOW-POWER                 |      |

|      |         | APPLICATIONS                                                 |      |

| 2.1  |         | ction                                                        |      |

| 2.2  | RF-to-E | BB Current-Reuse Receiver Front-End Circuit Level Design     |      |

|      | 2.2.1   | Low Noise Transconductance Amplifier                         |      |

|      | 2.2.2   | Down-Conversion Mixer                                        |      |

|      | 2.2.3   | Active Inductor and Noise Cancellation                       |      |

|      | 2.2.4   | Transimpedance Amplifier                                     |      |

| 2.3  | 2       | Integration                                                  |      |

| 2.4  | 2       | Considerations                                               |      |

|      | 2.4.1   | LNTA Layout                                                  |      |

|      | 2.4.2   | Mixer Layout                                                 |      |

|      | 2.4.3   | Baseband Circuits                                            |      |

|      | 2.4.4   | Floor Plan                                                   |      |

| 2.5  |         | yout Simulation Results and Discussion                       |      |

| 2.6  | Conclu  | sions                                                        | 49   |

| СНАЕ | PTER 3  | A WIDEBAND LOW-POWER RF-TO-BB CURRENT-REUSE                  |      |

|      |         | RECEIVER USING AN ACTIVE INDUCTOR AND 1/F NOISE-             |      |

|      |         | CANCELLATION FOR L-BAND APPLICATIONS                         | 51   |

| 3.1    | Introduc | ction                                                                                                                                 | 52  |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2    | Receive  | r Overview                                                                                                                            | 55  |

| 3.3    | Circuit  | Design                                                                                                                                | 57  |

|        | 3.3.1    | LNTA with LC-Balun Matching Network                                                                                                   |     |

|        | 3.3.2    | Active Inductor and $1/f$ Noise-Cancellation Technique                                                                                | 59  |

|        | 3.3.3    | Passive Down-conversion Mixer                                                                                                         |     |

|        | 3.3.4    | Transimpedance Amplifier                                                                                                              | 64  |

|        | 3.3.5    | Output Buffer                                                                                                                         |     |

| 3.4    | Experin  | nental Results and Discussion                                                                                                         |     |

| 3.5    | -        | sion                                                                                                                                  |     |

| CHAP'  | TER 4    | A COMPARISON OF OFF-CHIP DIFFERENTIAL AND LC INPUT MATCHING BALUNS IN A WIDEBAND AND LOW-POWER RF-TO-BB CURRENT-REUSE RECEIVER FRONT- |     |

|        |          | END                                                                                                                                   | 77  |

| 4.1    | Introduc | ction                                                                                                                                 |     |

| 4.2    | RF-to-E  | BB-Current-Reuse Receiver Front-End Circuit-Level Considerations .                                                                    |     |

|        | 4.2.1    | LNTA Design with Differential Balun and LC Balun Input Matching                                                                       | 92  |

|        | 4.2.2    | Network                                                                                                                               |     |

|        | 4.2.3    | · •                                                                                                                                   |     |

|        | 4.2.3    | Passive Mixer                                                                                                                         |     |

| 4.3    |          | Transimpedance Amplifier                                                                                                              |     |

| 4.3    | _        | nental Results and Discussions                                                                                                        |     |

| 4.4    | Conclus  | sion                                                                                                                                  | 97  |

| CONC   | LUSION   | NAND RECOMMENDATIONS                                                                                                                  | 101 |

| LIST ( | F REFE   | RENCES                                                                                                                                | 107 |

#### LIST OF TABLES

|           |                                                   | Page |

|-----------|---------------------------------------------------|------|

| Table 2.1 | Performance Summary and Comparison.               | 49   |

| Table 3.1 | Performance Summary and Comparison                | 74   |

| Table 4.1 | Performance Summary and Comparison to Other Works | 97   |

| Table 4.2 | Performance Summary and Comparison                | 100  |

#### LIST OF FIGURES

|             | Page                                                                                                       |

|-------------|------------------------------------------------------------------------------------------------------------|

| Figure 0.1  | Applications of IoT.                                                                                       |

| Figure 0.2  | Receiver using Wideband and narrow-band RF front-end.                                                      |

| Figure 1.1  | LMV circuit diagram.                                                                                       |

| Figure 1.2  | LNTA circuit using quadrature generation through capacitor                                                 |

| Figure 1.3  | System overview of single-input current-reuse architecture.                                                |

| Figure 1.4  | Single input Balun-LNA.                                                                                    |

| Figure 1.5  | Proposed IF-noise-shaping Biquad                                                                           |

| Figure 1.6  | (a) Proposed complex-pole load and (b) its small-signal equivalent circuit                                 |

| Figure 1.7  | Current-reuse receiver with an N-path configuration                                                        |

| Figure 1.8  | An 8-path combiner circuit.                                                                                |

| Figure 1.9  | Block diagram of the current-reuse receiver                                                                |

| Figure 1.10 | (a) Cross-coupled common-gate LNTA. (b) Single to differential transformer.                                |

| Figure 1.11 | Receiver I path circuit.                                                                                   |

| Figure 1.12 | Front-end with conventional AI (left) and adopted solution (right) 16                                      |

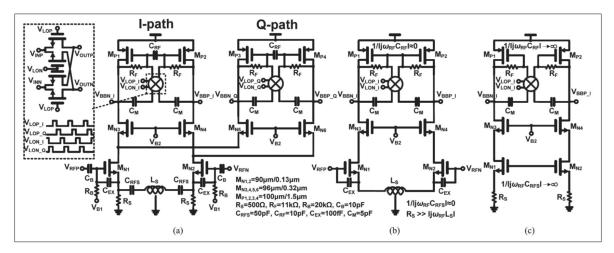

| Figure 1.13 | (a) Proposed current-reuse structure; (b) I path model in the RF domain; (c) I path model in the BB domain |

| Figure 1.14 | Quadrature RF-to-BB-CR receiver architecture.                                                              |

| Figure 1.15 | Function-reuse receiver with highlighted RF path                                                           |

| Figure 1.16 | Baseband signal path.                                                                                      |

| Figure 1.17 | Ultra-low power receiver for MedRadio application                                                          |

| Figure 1 18 | Mixer functionality diagram                                                                                |

| Figure 1.19 | Common-gate doubly balanced I/Q receiver front-end                                                                                      | 22 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.20 | RF receiver front-end architecture.                                                                                                     | 23 |

| Figure 1.21 | (a) Conventional input matching; (b) Simulated bonding effect on $S_{11}$ ; (c) LNTA circuit diagram.                                   | 24 |

| Figure 1.22 | I/Q image rejection circuit.                                                                                                            | 24 |

| Figure 2.1  | Block diagram of the proposed current-reuse receiver.                                                                                   | 31 |

| Figure 2.2  | (a) Test bench to optimize and characterize $g_m$ and $f_T$ , (b) resulting $g_m$ plots, and (c) resulting $f_T$ plots.                 | 33 |

| Figure 2.3  | Test bench to design and optimize the down-conversion mixer switches.                                                                   | 34 |

| Figure 2.4  | (a) The noise figure and (b) the 1 dB compression point versus the W/L ratio for different gate voltages of the input transistors       | 35 |

| Figure 2.5  | (a) Test bench to design the active inductor and (b) its impedance magnitude over frequency with and without $R_S$ considered           | 36 |

| Figure 2.6  | Magnitude of $Z_{AI}$ for different values of $C_{AI}$ .                                                                                | 37 |

| Figure 2.7  | Magnitude of $Z_{AI}$ for different W/L ratio multipliers of transistor $M_{AI}$ . The unit W/L ratio is $10\mu\text{m}/260\text{nm}$ . | 38 |

| Figure 2.8  | The NF and conversion gain versus the gate bias voltage of the LNTA                                                                     | 40 |

| Figure 2.9  | The input matching $(S_{11})$ versus frequency for several gate bias voltages of LNTA.                                                  | 40 |

| Figure 2.10 | The NF and conversion gain versus the gate bias voltage of the mixer                                                                    | 41 |

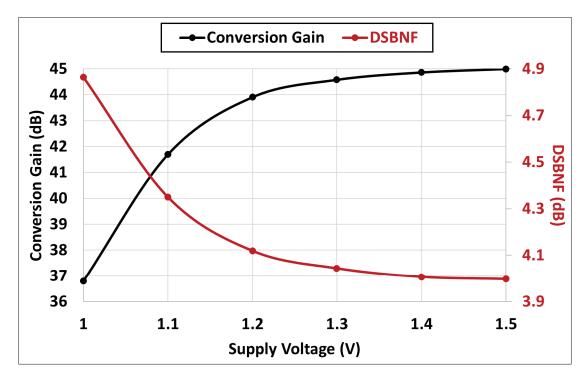

| Figure 2.11 | The NF and conversion gain versus supply variations                                                                                     | 42 |

| Figure 2.12 | The NF and conversion gain versus the LO frequency.                                                                                     | 42 |

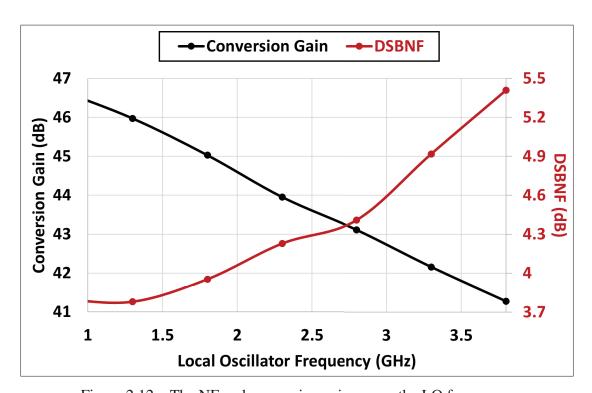

| Figure 2.13 | The layout of CRR front-end                                                                                                             | 45 |

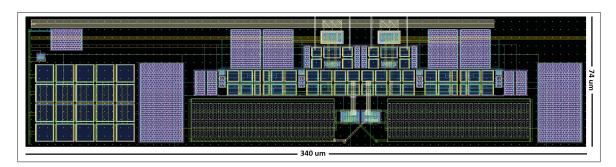

| Figure 2.14 | The post-layout simulated NF versus the IF.                                                                                             | 46 |

| Figure 2.15 | The post-layout simulated fundamental and third-order intermodulation products versus the input power.                                  | 47 |

| Figure 2.16 | Receiver post-layout simulated performance versus the RF signal                                                                         | 48 |

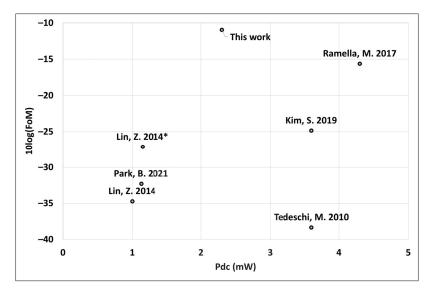

| Figure 2.17 | Comparison of the FoM to prior works versus the power consumption                                                                                                                                                                  | 48 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

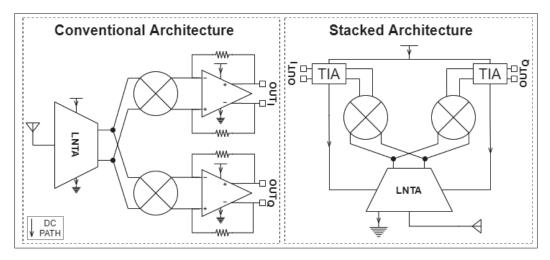

| Figure 3.1  | Conventional and stacked receiver front-end architectures                                                                                                                                                                          | 53 |

| Figure 3.2  | Block diagram of the proposed CRR front-end.                                                                                                                                                                                       | 56 |

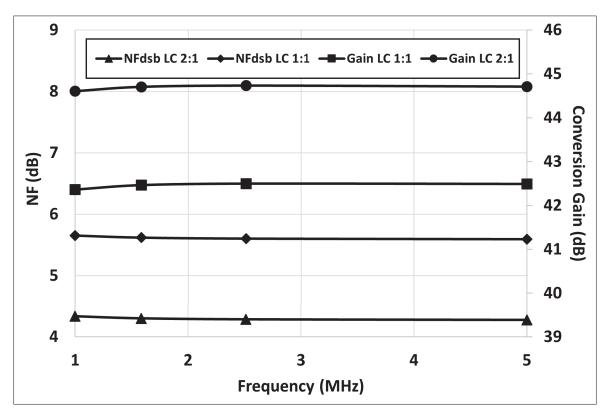

| Figure 3.3  | Simulated conversion-gain and DSB NF of the CRR using a 1:1 LC-balun or a 2:1 LC-balun.                                                                                                                                            | 58 |

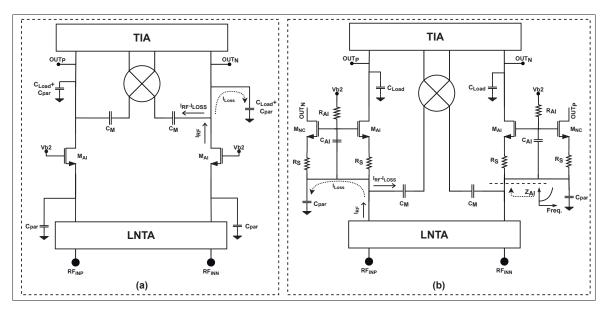

| Figure 3.4  | (a) Convectional CRR with cascoded transistor. (b) Proposed architecture introducing an AI and $1/f$ NC technique                                                                                                                  | 60 |

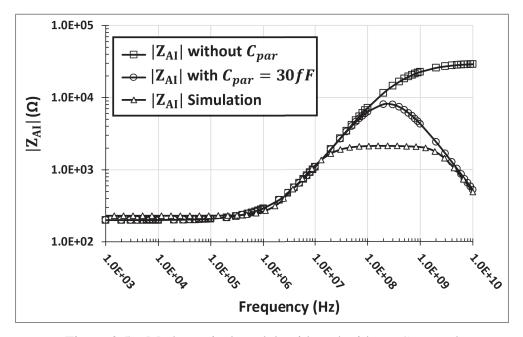

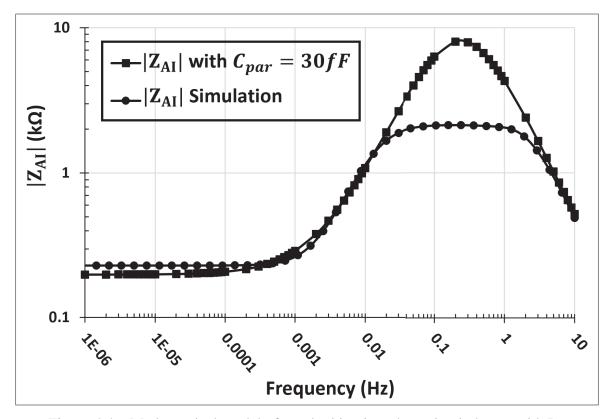

| Figure 3.5  | Mathematical model, with and without $C_{par}$ , and simulation of the magnitude of $Z_{AI}$ versus frequency.                                                                                                                     | 61 |

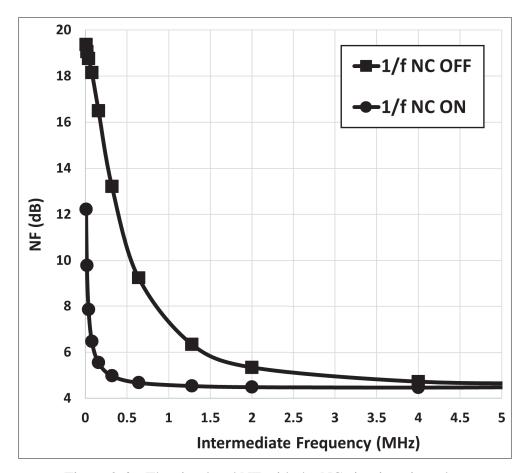

| Figure 3.6  | The simulated NF with the NC circuit activated or deactivated                                                                                                                                                                      | 62 |

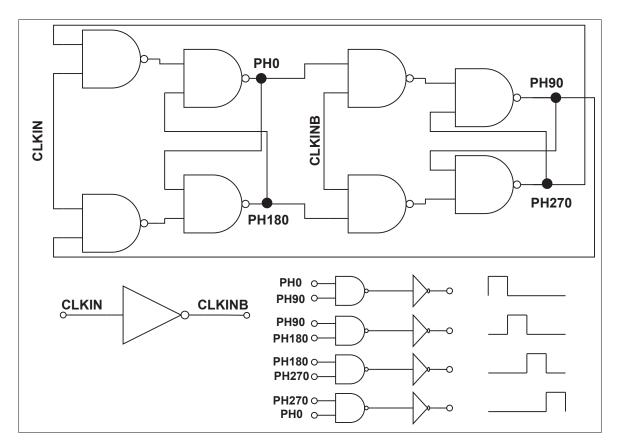

| Figure 3.7  | Schematic of the clock generation circuit generating 25% duty cycle phases.                                                                                                                                                        | 63 |

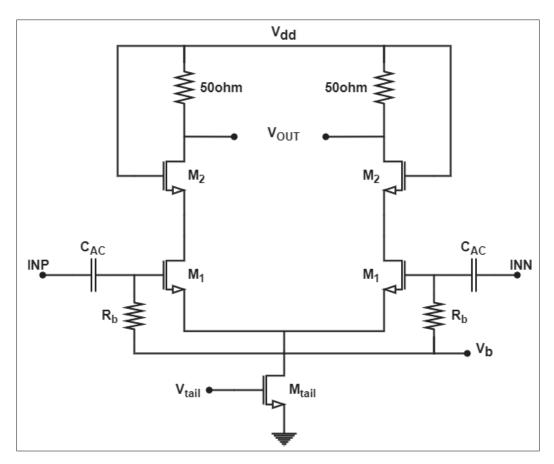

| Figure 3.8  | Output buffer circuit used in the measurements.                                                                                                                                                                                    | 65 |

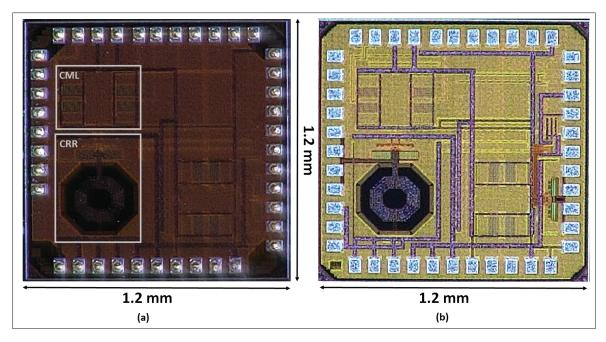

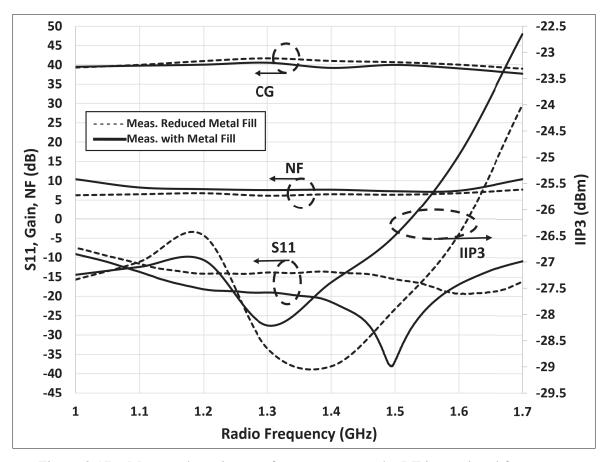

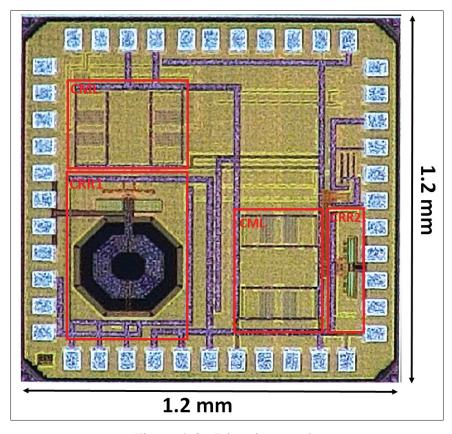

| Figure 3.9  | Die micrograph of the fabricated die (a) fully covered with metal fill (Chip1), and (b) with reduced metal fill on the sensitive nodes (Chip2). Note that the circuitry on the right half of the dies is not related to this work. | 66 |

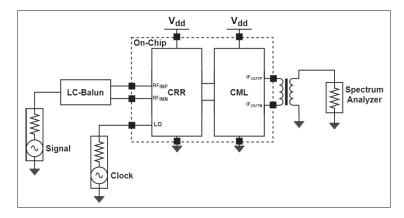

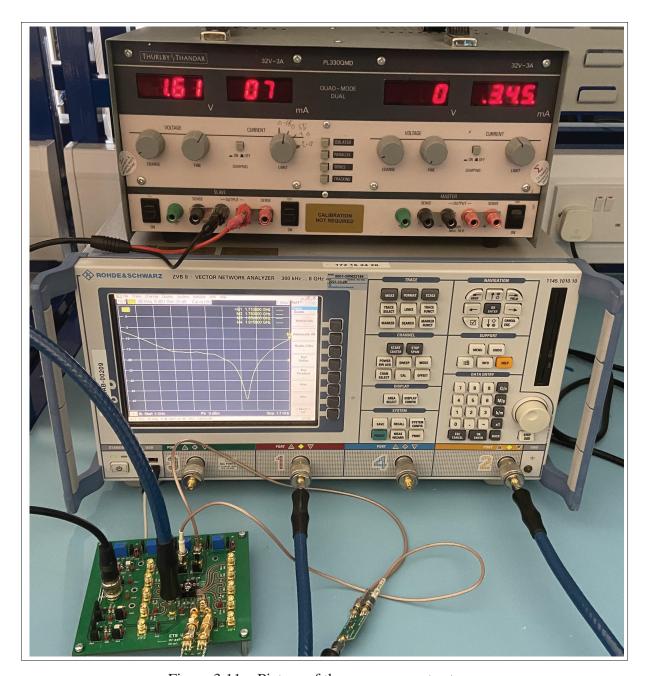

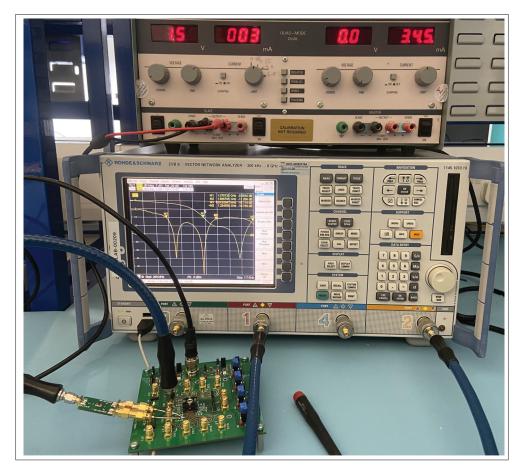

| Figure 3.10 | Diagram of the measurement setup.                                                                                                                                                                                                  | 66 |

| Figure 3.11 | Picture of the measurement setup.                                                                                                                                                                                                  | 67 |

| Figure 3.12 | The simulated and measured NF versus the IF.                                                                                                                                                                                       | 68 |

| Figure 3.13 | The simulated and measured conversion gain versus the IF                                                                                                                                                                           | 69 |

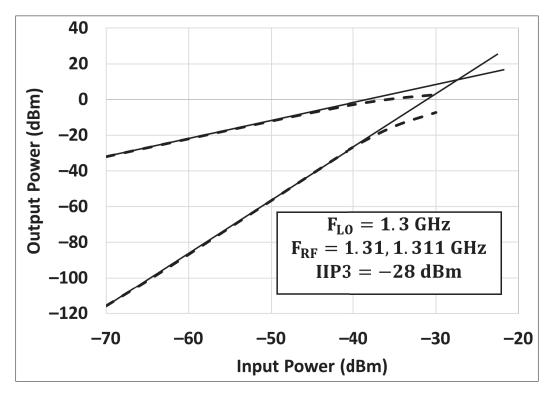

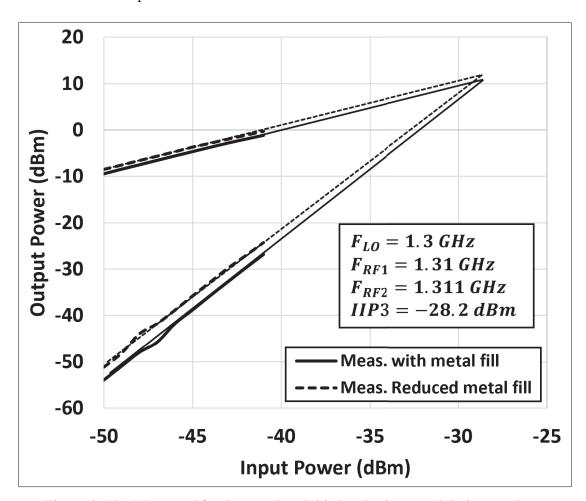

| Figure 3.14 | Measured fundamental and third-order intermodulation products versus the input power sweep. The resulting in-band IIP3 is shown                                                                                                    | 70 |

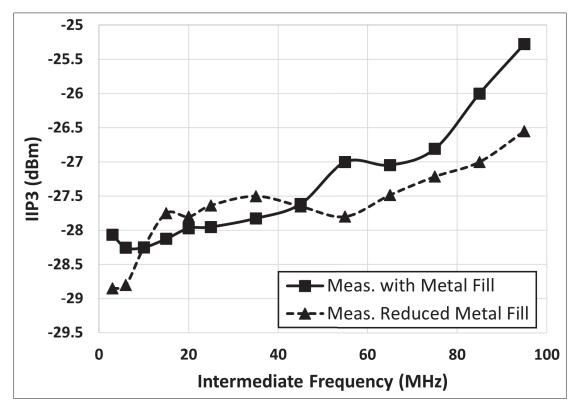

| Figure 3.15 | Measured in-band IIP3 performance versus the IF                                                                                                                                                                                    | 71 |

| Figure 3.16 | Measured OOB IIP3 performance versus the IF.                                                                                                                                                                                       | 72 |

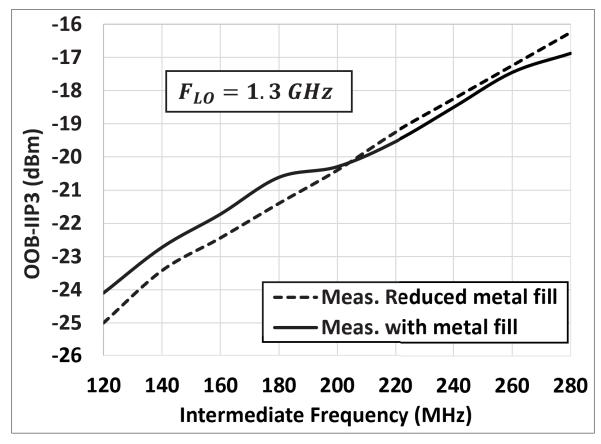

| Figure 3.17 | Measured receiver performance versus the RF input signal frequency                                                                                                                                                                 | 73 |

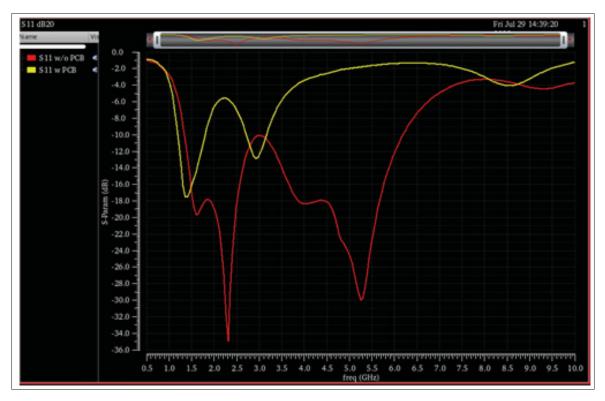

| Figure 3.18 | Effect of PCB model on S11 performance.                                                                                                                                                                                            | 76 |

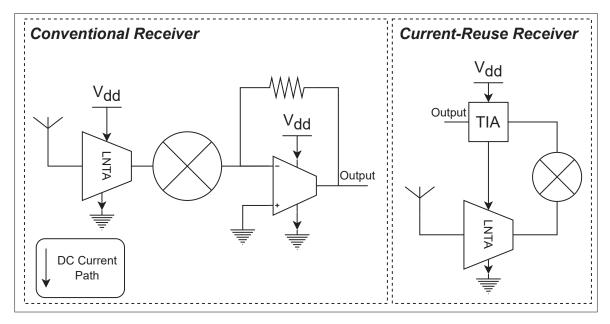

| Figure 4.1  | Conventional (left) and current-reuse (right) receiver architectures                                                                                                                                                               | 79 |

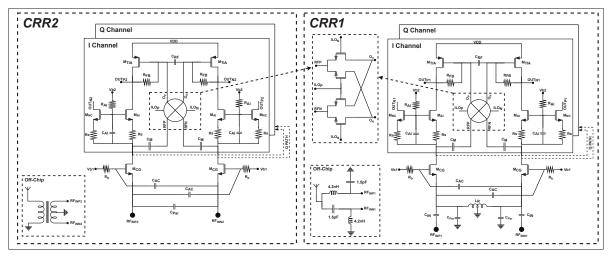

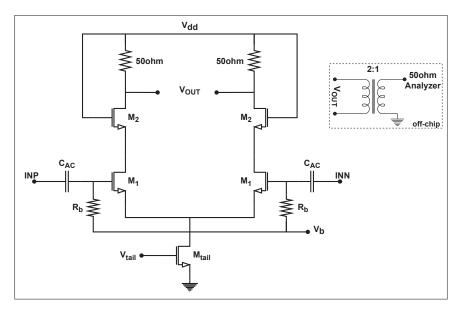

| Figure 4.2  | CRR1 proposed in our earlier work (right), CRR2 proposed in this work (left).                                                                    | 82 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

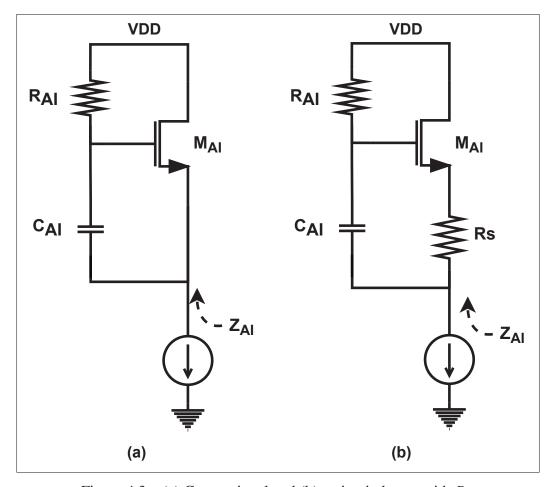

| Figure 4.3  | (a) Conventional and (b) active-inductor with $R_s$                                                                                              | 85 |

| Figure 4.4  | Mathematical model of $Z_{AI}$ looking into the active-inductor with $R_S$ included and $C_{par}$ of 30 fF along with circuit simulation results | 86 |

| Figure 4.5  | The CML buffer circuit used to drive the measurement equipment in matched state.                                                                 | 89 |

| Figure 4.6  | Die micrograph.                                                                                                                                  | 89 |

| Figure 4.7  | Measurement setup using a VNA to evaluate the $S_{11}$ performance of CRR1 and CRR2.                                                             | 90 |

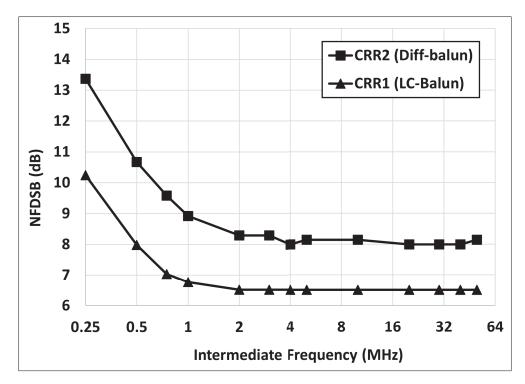

| Figure 4.8  | The NF performance CRR1 and CRR2 versus the RF input                                                                                             | 92 |

| Figure 4.9  | The NF performance of CRR1 and CRR2 versus the IF                                                                                                | 92 |

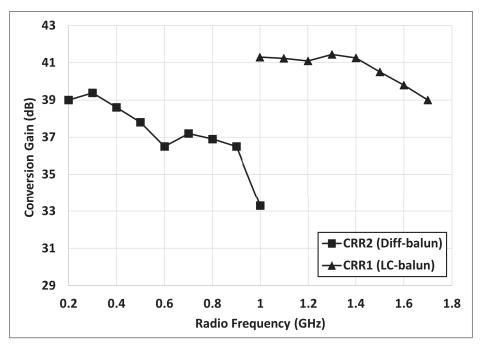

| Figure 4.10 | The conversion-gain performance of CRR1 and CRR2 versus the RF input.                                                                            | 93 |

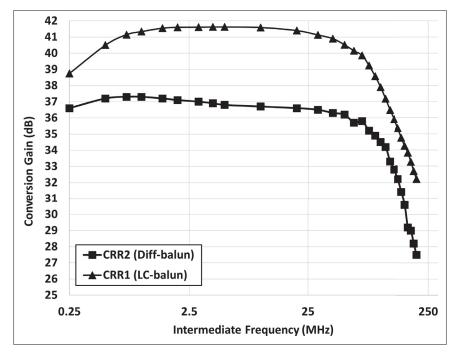

| Figure 4.11 | The conversion-gain performance of CRR1 and CRR2 versus the IF                                                                                   | 93 |

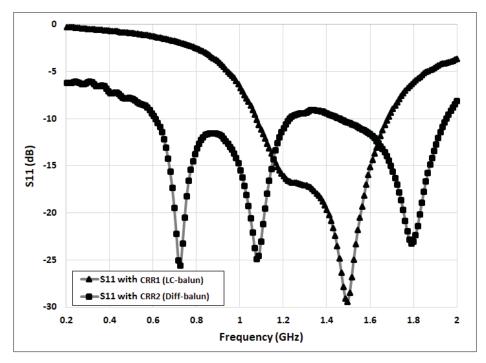

| Figure 4.12 | The S11 performance of CRR1 and CRR2 versus the RF input                                                                                         | 94 |

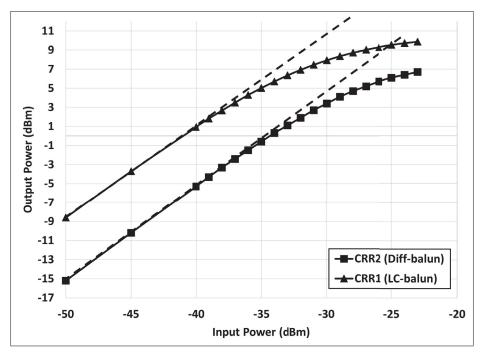

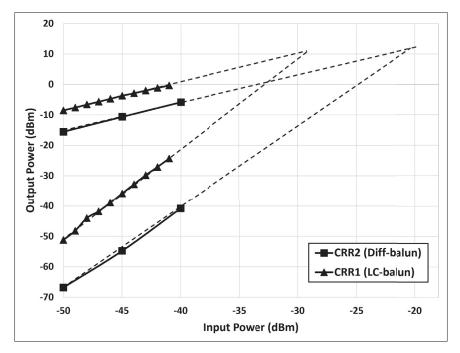

| Figure 4.13 | The measured output signal power of CRR1 and CRR2 versus a single-tone input power sweep.                                                        | 95 |

| Figure 4.14 | The measured third-order intercept points of CRR1 and CRR2 versus a two-tone input power sweep.                                                  | 95 |

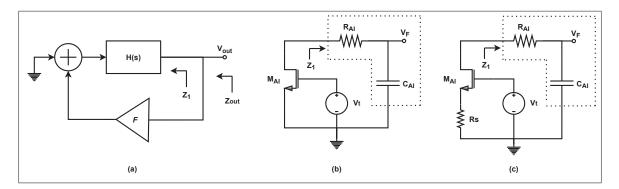

| Figure 4.15 | (a) Output impedance of a negative-feedback system. The open-loop circuit of (b) Figure 4.3(a) and (c) Figure 4.3(b).                            | 98 |

#### LIST OF ABBREVIATIONS

ADC Analog to Digital Converter

ETS Ecole de Technologie Superieure

FFT Fast Fourrier Transform

FOM Figure Of Merit

IC Integrated Circuit

IoT Internet of things

IEEE Institute of Electrical and Electronics

TCAS Transaction on Circuit and System

MDPI Multidisciplinary Digital Publishing Institute

VCO Voltage Controlled Oscillator

VNA Vectorial Network Analyzer

LNTA Low Noise Transconductance Amplifier

LNA Low Noise Amplifier

TIA Transimpedance Amplifier

AI Active-Inductor

NC Noise-Cancellation

CRR Current-Reuse Receiver

BB Baseband

GPS Global Positioning System

GNSS Global Navigation Satellite System

NF Noise Figure

DSB Double Side-band

IIP3 Third-order Input Intercept Point

IM3 Third-order Intermodulation Product

CG Conversion-Gain

LO Local-oscillator

RF Radio Frequency

IF Intermediate Frequency

CMOS Complementary metal—oxide—semiconductor

DC Direct Current

AC Alternating Current

PCB Printed Circuit Board

CML Current-mode Logic

LDO Low-dropout Regulator

EDA Electronic Design Automation

VCCS Voltage Controlled Current Source

V<sub>TH</sub> Voltage-Threshold

PDK Process Design Kit

CS Common-source

CG Common-gate

P1dB 1-dB compression point

#### LIST OF SYMBOLS AND UNITS OF MEASUREMENTS

$\Omega$  Ohm

F Farad

Hz Hertz

m Meter

Q Quality Factor

s Seconde

V Volt

W Watt

$\lambda$  Lambda

dB Decibel

dBm Decibel Milliwatt

*g<sub>m</sub>* Transconductance

#### INTRODUCTION

#### **Context of the Study and Problems**

As the proliferation of the internet of things (IoT) occurs, many are expecting the gradual establishment of a ubiquitous smart environment, including home automation, health monitoring, traffic control, transportation, etc, as shown in figure 0.1, an improvement in the wireless connectivity is a top priority Liu & Niknejad (2019); Kim *et al.* (2019); Karim (2018).

Figure 0.1 Applications of IoT. Taken from plopdo.com.

The smart city is one of the most important applications of the IoT, in which a broad number of ultra-low power sensors connect wirelessly to monitor the environment and provide monolithic communication between humans and things. In healthcare, the IoT enables continuous monitoring of patients by professionals and doctors to reduce the risk of any incidents. IoT devices are also utilized widely for location tracking and positioning in different applications such as vehicles for navigation, health for patient tracking, military for soldier localization, shipping to track goods,

etc. For instance, car insurance companies provide special discount for costumers willing to install tracking devices that provide useful information such as millage and speed to the insurer; Pascual Pelayo (2018); Petäjäjärvi (2018).

In recent years, there has been a significant change in wireless communications. At the beginning of the history of communication, a radio or television station employed a very high power transmitter for video and audio broadcasting to several receivers. A few decades ago, a dramatic change was observed and today the number of cordless and wireless devices, like wireless internet and cellular telephones, are growing everyday with vastly proliferating wireless links. As wireless applications have been increasing in all sectors, there will be a new opportunity for more use cases requiring devices to be wirelessly connected and networked together. There has been a wide range of research and development on IoT applications, where every objects such as our home appliances are to be connected to a network to enhance monitoring and control. It is undeniable, today, that a great number of human beings are carrying a laptop, smartwatch or smartphone in everyday life which are powerful computing platforms. Thus, this is a unique chance to increase the number of sensors to connect and monitor the world around us (and us) through mobile devices married to wireless technology. These sensors can be used for wide range of purposes like continuous life signs monitoring or dynamically locating patients in hospitals.

As a part of any wireless application, the wireless transceiver plays a key role to determine a wireless system's specifications such as performance and power. In a transceiver, a radio frequency (RF) front-end consumes most of the power. Moreover, it determines the key specifications of the receiver and transmitter performance, such as linearity and noise figure (NF), which has led to a broad number of research works on RF front-end circuit design (Jeong, Lee, Lee & Kim (2016); Liu *et al.* (2018); Niitsu *et al.* (2018); Ture, Devos, Maloberti & Dehollain (2018)). The transceiver includes the receiver and the transmitter blocks. The receiver, which is

the main interest of this work, receive a low-power wanted signal that needs to be amplified and differentiated from interference and noise. Thus, it need to have very low NF with sufficient linearity while consuming minimum power. Therefore, careful consideration and effort should be taken in designing an RF front-end to achieve the highest performance with the minimum power consumption, requiring specific circuit design techniques and architectures. We can think of a few major requirements for transceivers such as NF, gain, linearity and power Tam (2016); Ali Niknejad (2019).

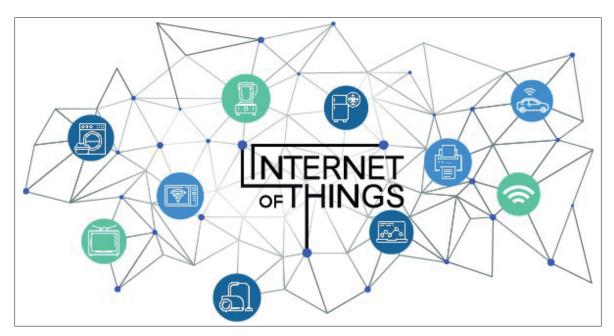

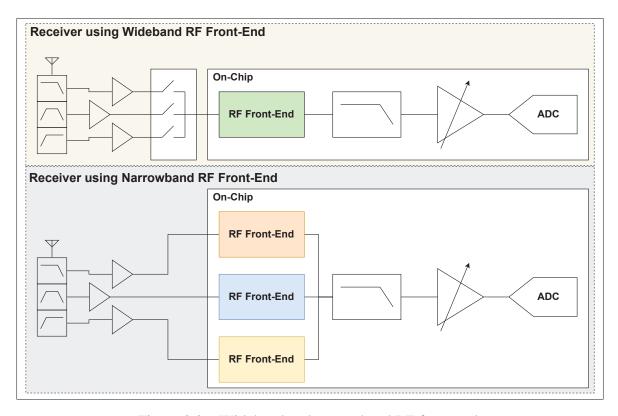

Figure 0.2 Wideband and narrowband RF front-end.

As the number of wireless devices for IoT is expected to increase to the tens of billions by 2025, saving even a fraction of the power on every wireless device is crucial to save significant amounts of aggregate power. As mentioned earlier, most of the power in wireless applications is consumed by the RF transceiver to process the RF signals. There has been a wide range

of research and articles in both academia and industry that propose circuit design techniques and receiver architectures to reduce the power consumption of the RF transceiver front-end while maintaining the other performance metrics such as gain, noise and linearity Thijssen, Klumperink, Quinlan & Nauta (2020); Elsayed *et al.* (2019); Neeraja, Moganti & Md (2021); Chen *et al.* (2019); Vijayalakshmi & Nagarajan (2019); Forno, Moio, Schenatti, Macii & Urgese (2020). However, they still need improvement that need to be taken into account and will be discussed in this work. In addition, it is crucial to maintain the performances of transceiver over a wide frequency range to meet the requirements of several wireless standards. In this way, a single transceiver to meet the requirements of several wireless standards becomes possible and cost and power consumption of the RF subsystem can be substantially reduced. Figure 0.2 shows receiver front-ends using a narrowband and a wideband RF front-end. It shows that the wideband RF front-end can cover several wireless standards using external switches that switch different frequency bands. In this way, a low power, low cost and agile RF receiver can be achieved to support several wireless protocols without requiring multiple font-ends.

#### **Research Objectives**

Low power and high performance receivers have attracted great interest in the research community, as they provide a potential to extend the battery life of wireless devices. In recent years, attempts have been made to reduce power consumption of the RF receiver front-end as it is consuming most of the power in the receiver circuits. In low-power receivers, attaining the low noise figure (NF) and the high blocker tolerability is of the great importance, though very challenging in wideband implementations which are sought after, as they reduce the number of RF front-ends required in a given wireless device that needs to support multiple wireless standards.

The selection process of the wideband RF front-end structure is a difficult, challenging and time-consuming task that directly affects the performance of the entire receiver. It is important

to manage the challenges and properties related to each building blocks. To this end, a number of parameters need to be taken into account.

A conventional receiver architectures contain a low noise amplifier (LNA) or a low noise transconductance amplifier (LNTA), a down-conversion mixer, an local oscillator (LO) and integrated analog filters. However, the low-power design requires the new receiver design techniques to reduce the power consumption while the overall performances are not affected, notably over a wide frequency range. After architecture selection, performance enhancing and low-power techniques are required to design each of the sub-blocks.

The goal of this work is to:

- 1. propose a wideband low-power receiver front-end using current-reuse architecture to reduce static power consumption

- 2. propose an active-inductor technique to enhance the performance of the current-reuse receiver at high radio frequencies

- 3. propose a 1/f noise-cancellation technique to enhance the noise performance at a low intermediate-frequency

- 4. fabricate and test the proposed current-reuse circuits with different matching circuits to outline circuit reliability and input matching options

The main contributions of the research work are as follows:

- 1. It gives a unique perspective on low-power and wideband RF-to-Baseband currentreuse receivers (CRRs) including the related architectural choices, characterization and analysis that are involved in the design methodology.

- 2. It presents the design and fabrication of a wideband low-power RF-to-BB current-reuse receiver using an active inductor and 1/f noise-cancellation for L-band applications in order to validate the proposed methodology and architecture

3. It provides a comparison of the impact of an off-chip differential balun and an LC Balun with or without using an on-chip inductor in a wideband low-power RF-to-BB CRR front-end to provide design insights into the impact of the input matching strategy of such a front-end structure

#### **Structure of the Thesis**

- The CHAPITRE 1 presents the state-of-the-art. Its main objective is to give an overview of the low-power receiver architectures. It also discuss the weakness of the prior art and potential future developments.

- The CHAPITRE 2 is a paper published in the special issue "Design of Mixed Analog/Digital Circuits", section "Circuit and Signal Processing", Electronics, MDPI. It presents the design procedure and characterization of ideband current-reuse receiver front-ends for low-power applications.

- The CHAPITRE 3 is a paper published in the IEEE Access journal. It presents the

design and measurement results of a CRR front-end employing an active-inductor and 1/f

noise-cancellation techniques. It also shows the effect of a metal fill in the measurement

results.

- The CHAPITRE 4 is an article submitted to the special issue "Design of Mixed Analog/Digital

Circuits, Volume 2", section "Circuit and Signal Processing", Electronics, MDPI. It presents

the design and measurement comparison of an off-chip differential balun and an LC balun in

a low-power RF-to-BB current-reuse receiver front-end.

#### **CHAPTER 1**

#### LITERATURE REVIEW

#### Overview

In wireless communications, a very weak wanted signal arrives at the receiver input. This received wanted signal need to be amplified with minimum added noise. The RF signal should be down-converted to a low intermediate-frequency (IF) or base-band (BB) signal by local oscillator (LO) and then filtered before analog to digital conversion (ADC) and digital signal processing (DSP) to remove interference and noise. This chapter studies and analyses the recent published works on low-power receiver architectures and a critical analysis of the drawbacks and benefits of each work is given.

#### 1.1 Current reuse receiver

It is challenging to reduce the power consumption of the RF front-end while maintaining performance metrics such as linearity and NF. Various methods and techniques have been studied to address these challenges. Among them, a widespread method to reduce the power consumption is current-reuse. Usually, current-reuse has been employed within individual blocks such as a low noise transconductance amplifier (LNTA), Shams, Abbasi & Nabki (2020). By scaling down the CMOS technology, one may increase the operating frequency and reduce the threshold voltage such that new transceiver design techniques have emerged. The idea of current-reuse focused on stacking different circuits and sharing the same supply. Several recent published current-reuse receivers are discussed in this section.

#### 1.1.1 Current-Reuse Receiver with Stacked LNTA, Mixer and VCO

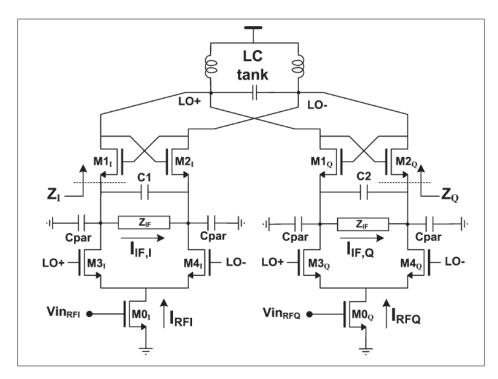

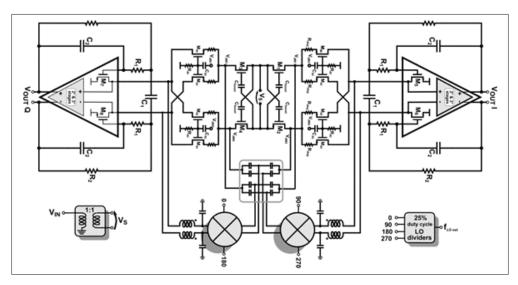

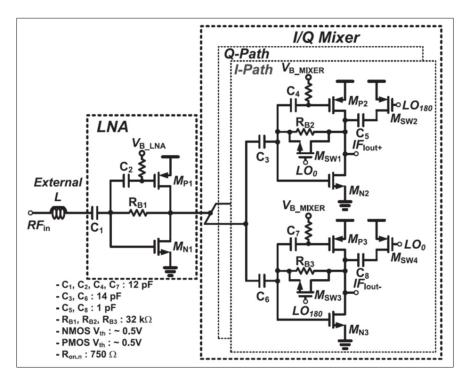

A stacked LNTA, Mixer and Voltage controlled oscillator (VCO) (LMV) is proposed by Tedeschi, Liscidini & Castello (2010) to reduce power consumption by sharing a single supply and biasing current shown in Figure 1.1. Transistor M<sub>0</sub> defines the VCO current while at the same time

performs as LNTA to amplify and convert the RF signal to RF current. Stacking the VCO may cause injection locking issue of the VCO due to the large blocker. Moreover, it reported very high NF of 10 dB.

Figure 1.1 LMV circuit diagram. Taken from Tedeschi *et al.* (2010)

Figure 1.2 LNTA circuit using quadrature generation through capacitor.

Taken from Tedeschi et al. (2010)

The I and Q generation can be achieved through LNTA using capacitive generation, shown in Figure 1.2. This may cause unbalance output of LNTA which is only suitable for narrowband applications such as ZigBee standard. In addition, the LNTA may suffer stability issue where certain criteria need to be met to avoid instability.

Although very low-power consumption is achieved by Tedeschi *et al.* (2010), It still suffers from several issues like high NF and instability that makes this work not suitable to many applications. Next, a current-reuse receiver is proposed where the VCO is not stacked to avoid the problems related to the injection locking of the VCO.

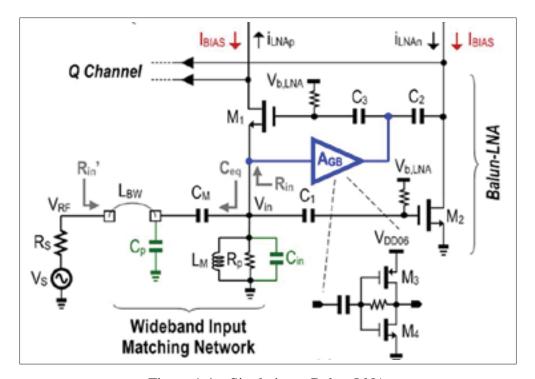

#### 1.1.2 Current-Reuse Receiver with Balun-LNA

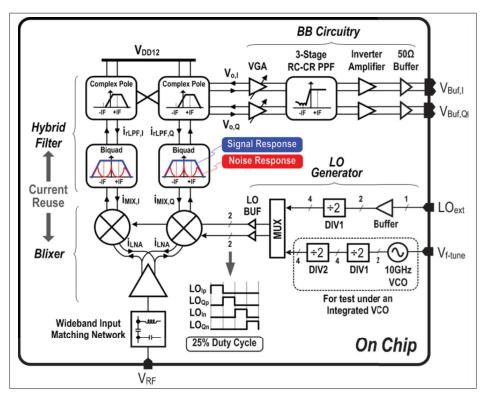

Figure 1.3 shows the current-reuse receiver front-end proposed by Lin, Mak & Martins (2014b).

Figure 1.3 System overview of single-input current-reuse architecture.

Taken from Lin *et al.* (2014b)

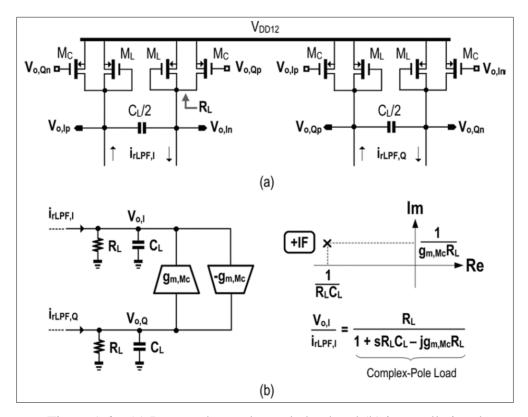

The receiver cascodes Balun-LNA, mixer, biquad filter and a complex filter to enhance image rejection in the initial stage. The current-reuse receiver followed by VGA and RC-CR complex filter offers additional gain programmability and extra image rejection. The proposed Balun-LNA illustrates in Figure 1.4. It converts the single-ended signal to a differential current through a common-source and common-gate noise-cancelling LNTA topology. Although the  $A_{GB}$  inverter based amplifier reduces the imbalance, such a design is always susceptible to mismatch. Moreover, extra components at the input increase NF and power consumption. Figure 1.5 shows the biquad filter that helps for channel selection and filtering.

The active inductor shapes the noise at the IF frequency; however, the NF is reduced only by 0.5 dB at the cost of the oscillation risk due to the positive feedback.

The proposed complex filter circuit shown in Figure 1.6 obtains the real part from diode connected transistor  $M_L$  and the imaginary part from I/Q cross connected  $M_C$ . In this way, the image is slightly rejected, 5 dB, while NF is degraded.

Figure 1.4 Single input Balun-LNA. Taken from Lin *et al.* (2014b)

Figure 1.5 Proposed IF-noise-shaping Biquad. Taken from Lin *et al.* (2014b)

Figure 1.6 (a) Proposed complex-pole load and (b) its small-signal equivalent circuit.

Taken from Lin et al. (2014b)

Lin *et al.* (2014b) proposed a receiver front-end for the ZigBee wireless standard. There are both advantages and disadvantages in this approach. The complex pole attenuates the image signal by 5 dB; however, it is not sufficient, which led to the use of an additional complex filter at the cost of higher NF and supply voltage that increases power consumption. The better solution here is to use a programmable gain complex filter instead of VGA, RC-CR filter and complex pole as a current reuse architecture separately. Moreover, an additional active-inductor to reduce NF by 0.5 dB from 9 dB to 8.5 dB is not efficient where it increases the risk of oscillation due to the positive feedback. In addition, cascoding several blocks requires a higher supply voltage that increases power consumption. In the next section, another approach is introduced with an N-path configuration.

#### 1.1.3 Current-Reuse Receiver with an N-path Configuration

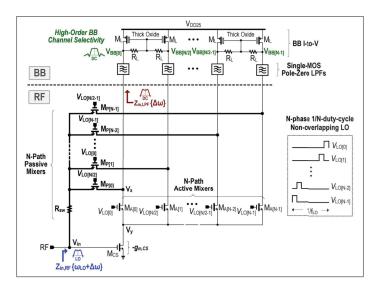

Figure 1.7 shows the current-reuse receiver proposed by Lin, Mak & Martins (2014a) where the structure takes advantage of the N-path configuration to enhance the overall performance. The receiver is proposed for TV-band (0.15 to 0.85 GHz) applications.

The receiver uses a single input common-source configuration without any extra components for external matching. An 8-path passive mixer feedback realizes input impedance matching, RF filtering and noise cancelling. It also takes advantage of harmonic recombination; 8-phase BB signals can combine in a way to remove the 3rd and 5th order harmonics at the output.

The current-reuse technique combined with an N-path down-conversion mixer could enhance the performance as reported by Lin *et al.* (2014a) while consuming a lot of current 16 mW. The feedback N-path passive mixer is not recommended due to the risk of oscillation. Another drawback is additional circuits to combine the N-path at the output that is power consuming, shown in Figure 1.8. To reduce the voltage headroom requirement, an active mixer can be replaced with a current driven passive mixer. Next, a current-reuse receiver using a passive mixer is shown where the I and Q path are stacked.

Figure 1.7 Current-reuse receiver with N-path configuration.

Taken from Lin *et al.* (2014a)

Figure 1.8 8-path combiner circuit. Taken from Lin *et al.* (2014a)

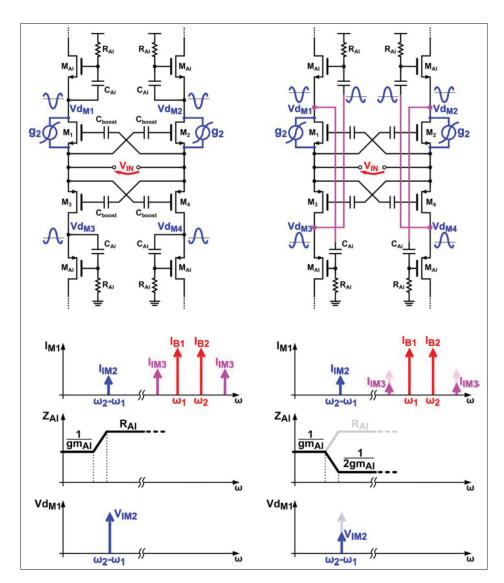

# 1.1.4 Current-Reuse Receiver with Stacked I/Q Paths

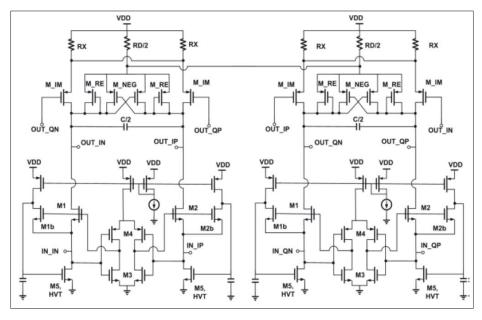

Figure 1.9 shows a current-reuse receiver circuit proposed by Ramella, Fabiano, Manstretta & Castello (2017). In this architecture, both I and Q paths are cascoded and share the same supply voltage. A single to differential transformer followed by common-gate amplifier to convert voltage to current employed at the input illustrated in Figure 1.10. The cross-coupled technique at the input boosts the transconductance where it reduces NF and enhances gain.

Figure 1.9 Block diagram of the current-reuse receiver. Taken from Ramella *et al.* (2017)

Figure 1.10 (a) Cross-coupled common-gate LNTA. (b) Single to differential transformer.

Taken from Ramella *et al.* (2017)

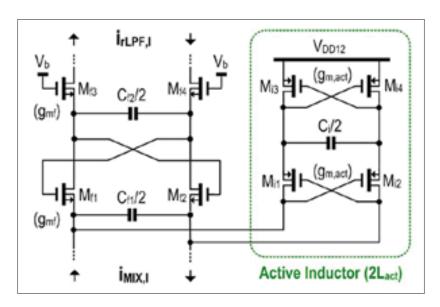

A schematic of the I path is shown in Figure 1.11. The active-inductor boosts the  $Z_{RF}$  at high frequency. In this way, the RF current is routed towards the mixer input. However, it shows low impedance at low frequency where  $M_{AI}$  acts like a cascode stage for the baseband (BB) output stage to boost the output impedance. However, this degrades the linearity that limits the IIP3 and curtails the circuit's applicability to a wide range of use cases.

Figure 1.11 Receiver I path circuit. Taken from Ramella *et al.* (2017)

The solution to improve the linearity is shown in Figure 1.12. Cross-coupling reduces the common mode impedance to  $\frac{1}{2g_{m,AI}}$  at higher frequencies, thus improving linearity.

Although the reported circuit by Ramella *et al.* (2017) shows good linearity and NF results, high power is consumed in this architecture. By stacking the I and Q paths, a high voltage headroom is required. Moreover, keeping all transistors in saturation across process, voltage and temperature corners is complex and potentially non-viable. The circuit proposed by Ramella *et al.* (2017) has the advantage of featuring a parallel passive mixer over the circuit in Lin *et al.* (2014b) and Lin *et al.* (2014a) where significant voltage headroom is saved.

Figure 1.12 Front-end with conventional AI (left) and adopted solution (right).

Taken from Ramella *et al.* (2017)

# 1.1.5 Source-Degenerated Current-Reuse Receiver with 1/f Reduction

Figure 1.13 shows current-reuse architecture proposed by Kim & Kwon (2019). It offers better performance in terms of NF in comparison to earlier mentioned architectures while consuming  $3.6 \,\mathrm{mW}$  power. A common-source input stage with a source-degeneration inductor is used for input matching.  $R_S$  employed to minimize the 1/f noise. Cascode transistors provide better

isolation between input and output. Moreover, it boosts the output impedance that increases the gain and current driving to the next stage. The passive mixer is followed by transimpedance amplifier (TIA) that converts the RF current to a BB voltage at the output. By increasing the feedback resistor, R<sub>F</sub>, the conversion gain increases.

Figure 1.13 (a) Proposed current-reuse. (b) I path model in RF domain. (c) I path model in BB domain.

Taken from Kim & Kwon (2019)

The circuit proposed by Kim & Kwon (2019) shows interesting NF and linearity results while input matching is degraded after fabrication due to the susceptible behaviour of the common-source configuration, which is very sensitive to bond-wires and parasitics. To enhance the input matching result, a common-gate amplifier using a cross-coupled technique can be used by slightly sacrificing NF, which is acceptable for several wireless standards. Moreover, a programmable R<sub>F</sub> resistor to be employed to program the receiver gain and increase circuit reliability when the input RF is high.

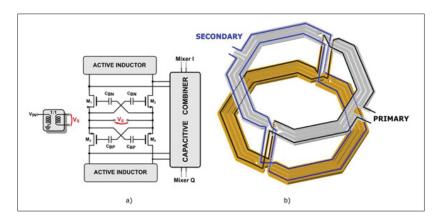

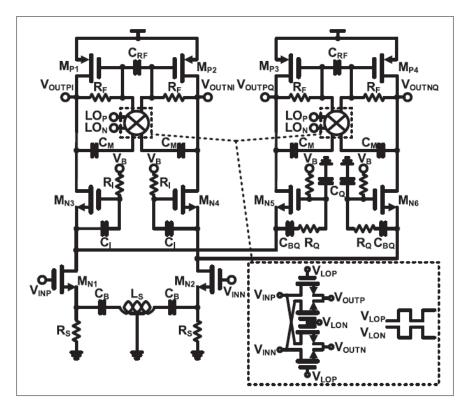

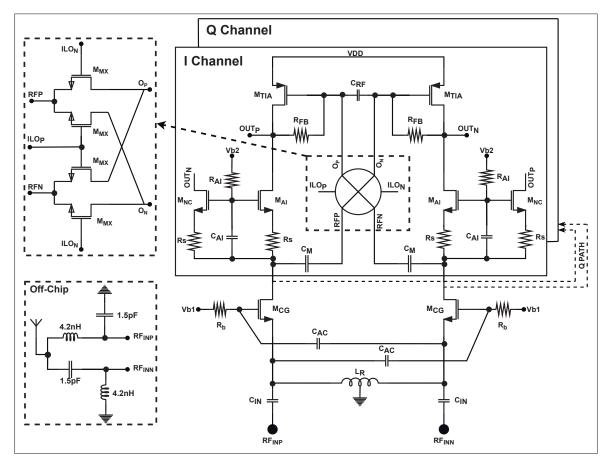

## 1.1.6 Quadrature RF-to-Baseband-Current-Reuse Architecture

Park & Kwon (2021) extended the work proposed by Kim & Kwon (2019) which employed simultaneous input matching and 1/f noise cancellation technique, but modified the cascode circuit to perform as an I/Q generator, shown in Figure 1.14.

Figure 1.14 Quadrature RF-to-BB-CR receiver architecture. Taken from Park & Kwon (2021)

Although power consumption of 1.13 mW is very low, this approach is only suitable for the applications where receiver sensitivity is not important since it reported a high NF of 13.2 dB. The high NF is due to the active-inductor that blocks the RF signal in the I path to achieve the quadrature signal at the output. In addition, the performance of the quadrature generation is very sensitive to the parasitic capacitances and resistances of the transistors ( $M_{N3}$ - $M_{N6}$ ), increasing circuit variability .

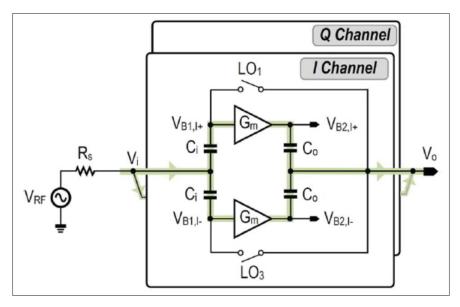

#### **1.2** Function-Reuse Architecture

One of the low-power receiver design techniques is function-reuse of the current consuming blocks. The circuit shown in Figure 1.15 is proposed by Lin, Mak & Martins (2014c). The green colour shows the RF path where the RF signal is amplified and converted to a current through the  $G_m$  stage.

Figure 1.15 Function-reuse receiver with highlighted RF path.

Taken from Lin *et al.* (2014c)

Figure 1.16 Baseband signal path. Taken from Lin *et al.* (2014c)

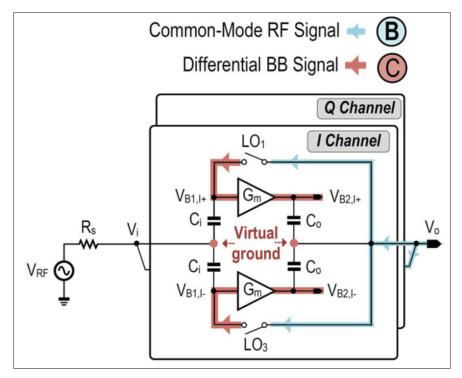

The RF current is down-converted to a BB signal through LO switches and amplified with the  $G_m$  stage that is shown with a red colour in Figure 1.16. In this way, the  $G_m$  stage is employed for both RF and BB signal amplification. The output BB signal is separated from the RF signal with  $C_o$ .

Although this architecture consumes very low power, it still has several drawbacks. A feedback loop in the RF path increases the risk of oscillation. Moreover, the design suffers from limited bandwidth and it is only suitable for narrowband designs, and it is susceptible to clock jitter. In addition, reported results show poor linearity. Like the current-reuse technique, the function-reuse technique is also not suitable for a zero-IF receiver. A low IF is recommended by utilizing an image rejection filter.

Next, ultra-low power techniques are discussed and their issues are mentioned.

#### 1.3 Ultra-Low Power Receivers

Recently several ultra-low power (ULP) receiver topologies have been published and proposed circuits with less than 1 mW of power consumtion. In this section, we detail and analyse the drawbacks and benefits of each one.

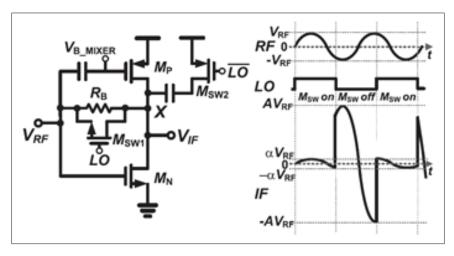

#### 1.3.1 ULP Receiver for MedRadio Standard using a New Mixing Technique

The circuit shown in Figure 1.17 is proposed for MedRadio applications in the 400 MHz band. The inverter based LNA is used at the input with external inductor for the matching purpose.

A novel active current-reuse inverter based down-conversion mixer enhances gain and reduces NF. When the local oscillator (LO) is ON, the input shorts to the output and attenuates the BB signal. On the other hand, when the LO is off, amplification takes place. In this way, a higher gain and lower NF are achieved in the mixer compared with the conventional passive mixer. The mixer functionality is shown in Figure 1.18. Due to the single balanced configuration of the mixer, linearity degrades to the certain extent. The circuit performance over frequency is

relative to the current consumption. Thus, to work at higher frequencies, a higher current needs to be consumed to achieve sufficient operating bandwidth.

Figure 1.17 Ultra-low power receiver for MedRadio application.

Taken from Choi *et al.* (2015)

Figure 1.18 Mixer functionality diagram. Taken from Choi *et al.* (2015)

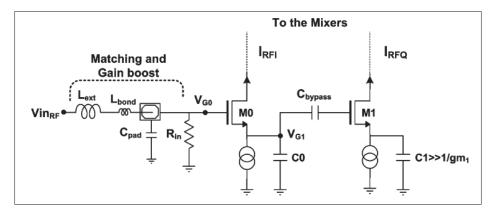

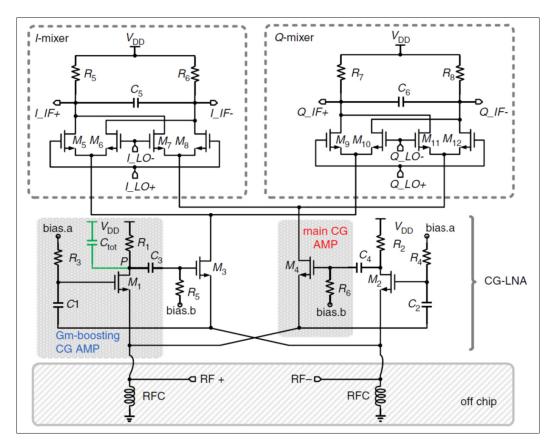

# 1.3.2 ULP Receiver using Novel $g_m$ -Boosted Common-Gate LNA

The ircuit proposed in Wang, Li, Cheng, Luo & Gao (2016) employed a common-gate configuration amplifier with an additional novel  $G_m$ -boosting technique that is shown in Figure 1.19.  $G_m$ -boosting is achieved through a feedforward amplifier. The input voltage is converted to a current and down-converted to BB through double balanced switches. Finally, the current is converted to a voltage through the output resistor.

The proposed circuit consumes very low-power of  $0.8 \, \text{mW}$  in sub-GHz applications. The NF performance is degraded due to the additional components at the input. To reduce NF and increase gain bandwidth at higher frequencies, higher power needs to be consumed. The circuit performance with a conventional cross-coupling capacitor technique is still preferred over the proposed architecture to boost the  $g_m$  which enhances the gain and reduces NF.

Figure 1.19 Common-gate doubly balanced I/Q receiver front-end. Taken from Wang *et al.* (2016)

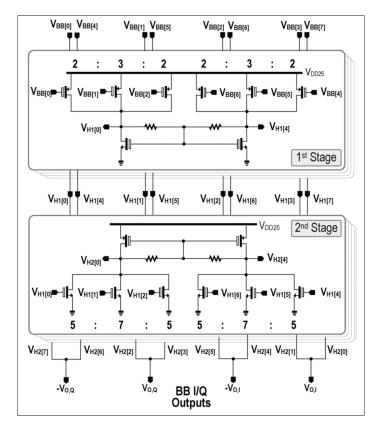

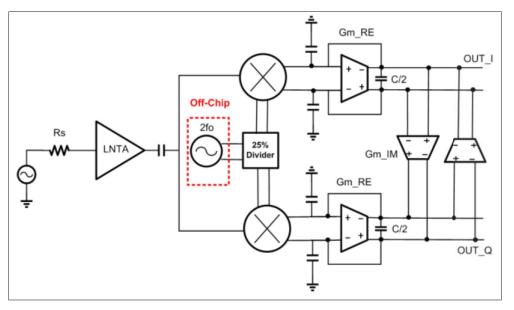

# 1.3.3 Receiver Employing an LNTA and Current-Reuse Image Rejection Filter

Another ultra-low power approach was proposed by Kargaran, Guo, Manstretta & Castello (2019). The front-end architecture including LNTA and current driven passive mixer is followed by a novel image rejection filter, as shown in Figure 1.20.

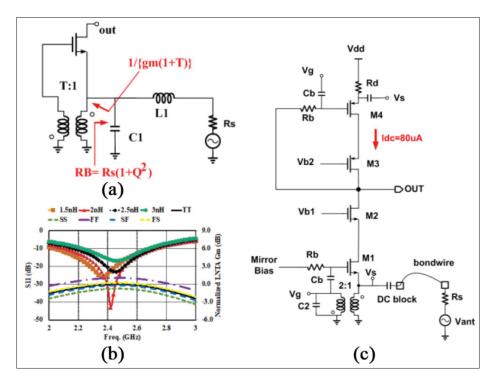

The conventional LNTA circuit is shown in Figure 1.21(a) that uses an external LC network matching and on-chip transformer to boost the  $g_m$  to improve input matching for low-power designs. The proposed LNTA circuit by Kargaran *et al.* (2019) is shown in Figure 1.21(c) that utilizes the bondwire and additional  $C_2$  without using an extra inductor to improve matching and reduce chip area. The effect of the bondwire variation is shown in Figure 1.21(b) that is acceptable thanks to the reliable common-gate topology which is relative to the effective  $g_m$ .

Figure 1.20 RF receiver front-end architecture. Taken from Kargaran *et al.* (2019)

The circuit shown in Figure 1.22 uses a  $g_m$ -boosted input stage to enhance the NF result and complex pole load to improve image rejection for a low-IF receiver. A complex pole is achieved by cross connecting the  $M_{IM}$  transistors. To minimize the mismatch effect of the passive mixer, the  $M_5$  transistor with negative feedback is used.

Figure 1.21 (a) Conventional input matching; (b) Simulated bonding effect on  $S_{11}$ ; (c) LNTA circuit diagram. Taken from Kargaran *et al.* (2019)

Figure 1.22 I/Q image rejection circuit. Taken from Kargaran *et al.* (2019)

The mentioned circuit is designed at  $2.4\,\mathrm{GHz}$  and shows good linearity performance while consuming very low power below  $500\,\mu\mathrm{W}$ . An image rejection of  $15\,\mathrm{dB}$  at  $2\,\mathrm{MHz}$  IF is reported which required an additional image rejection filter that increases the power consumption. Moreover, Monte-Carlo simulation needs to be performed to make sure image rejection is sufficient when considering process-induced mismatches.

Notably, most of the current-reuse image rejection techniques proposed in the previous sections does not generally provide enough image rejection. It is preferred to include image rejection circuitry separately to achieve better overall performance in the RF front-end.

#### 1.4 Conclusion

Among various receiver architectures studied in this section, the current-reuse architecture is a promising candidate for low-power applications. However, this technique suffers several problems that need to be improved. It suffers from direct leakage of the low frequency noise into the BB that should be improved to make it suitable for a Zero-IF receiver architecture. Better isolation of the RF signal to improve the NF at higher RF needs to be taken into account to make it suitable for large technology nodes such as 130 nm CMOS process and enable low cost implementations that are amenable to IoT-driven applications.

### **CHAPTER 2**

# A DESIGN METHODOLOGY FOR WIDEBAND CURRENT-REUSE RECEIVER FRONT-ENDS AIMED AT LOW-POWER APPLICATIONS

Arash Abbasi, Frederic Nabki

Department of Electrical Engineering, École de Technologie Supérieure, 1100 Rue Notre-Dame Ouest, Montréal, Québec, H3C 1K3, Canada

Article published in *MDPI Electronics*, August 2022. https://doi.org/10.3390/electronics11091493

**Abstract:** This work gives a design perspective on low-power and wideband RF-to-Baseband current-reuse receivers (CRR). The proposed CRR architecture design shares a single supply and biasing current among both LNTA and baseband circuits to reduce power consumption. The work discusses topology selection and a suitable design procedure of the low noise transconductance amplifier (LNTA), down-conversion passive-mixer, active-inductor (AI) and TIA circuits. Layout considerations are also discussed. The receiver was simulated in 130 nm CMOS technology and occupies an active area of 0.025 mm<sup>2</sup>. It achieves a wideband input matching of less than  $-10 \, \mathrm{dB}$  from 0.8 GHz to 3.4 GHz. A conversion-gain of 39.5 dB, IIP3 of  $-28 \, \mathrm{dBm}$  and a double-sideband (DSB) NF of 5.6 dB is simulated at a local-oscillator (LO) frequency of 2.4 GHz and an intermediate frequency (IF) of 10 MHz, while consuming 1.92 mA from a 1.2 V supply.

**Keywords:** current-reuse receiver; common gate; common source; low power; current sharing; low noise.

# 2.1 Introduction

The fast growing Internet of Things (IoT) is creating smart environments that have the potential to significantly improve our quality of life. This includes IoT systems used in location tracking and positioning, such as vehicles or drones for navigation, home automation, in the health industry to monitor patients and in agriculture to optimize and control watering systems, etc. This requires IoT devices with low power consumption, which will translate into billions of IoT devices that will require significant aggregate power consumption to operate. Accordingly, reducing the power consumption in each IoT device by a fraction can lead to an important overall energy use reduction globally.

Notably, in a typical IoT module, the RF transceiver plays a significant role in defining the overall power consumption of a given system. This work thus aims at giving insights regarding how to reduce the power consumption of RF transceivers. There are several techniques to reduce the power consumption of RF transceivers, including current sharing of the baseband and RF front-end by stacking a transimpedance amplifier (TIA) on top of the low transconductance amplifier (LNTA) and mixer, which is very effective compared to the conventional technique that cascades the LNTA, mixer and TIA.

There have been a wide range of studies into current-reuse techniques for RF receivers, leading to the introduction of the current-reuse receiver (CRR) architecture. Conventionally, in such receivers, current-reuse is employed in the LNTA design to boost the transconductance by stacking both PMOS and NMOS transistors and sharing their current bias through a single supply (Shams *et al.* (2020)). Recently, the current-reuse technique has been applied to receiver design by stacking several blocks such as the LNTA, mixer and TIA and sharing the biasing current among all of these circuits. In this fashion, power consumption can be reduced significantly. In Tedeschi *et al.* (2010), a voltage-controlled oscillator (VCO), mixer and LNTA are stacked to share the biasing current from a single supply. This reduces the overall power consumption significantly, but the design suffers from a high noise figure (NF) and VCO injection locking. Similarly, in Cai, Shi, Hu & Wang (2020), VCO and LNA are stacked, thus reducing the

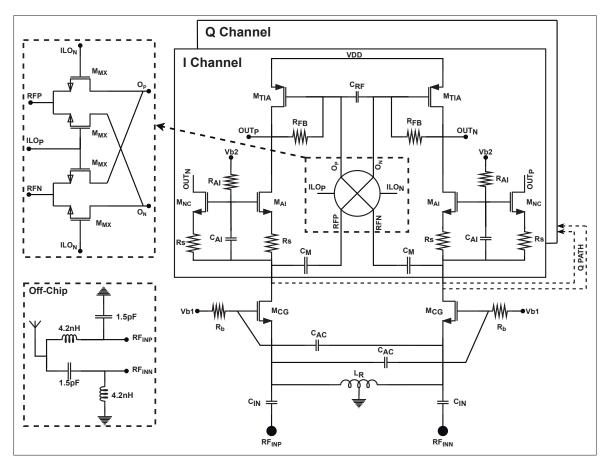

power consumption at the price of narrowing the bandwidth, potentially becoming prone to VCO injection locking as in Tedeschi et al. (2010). A balun LNA, active mixer and hybrid baseband filter are stacked in Lin et al. (2014b) to form a current-reuse topology to reduce power consumption. However, the active-mixer consumes voltage headroom, which reduces linearity. Another approach is the function-reuse technique employed in Lin et al. (2014c), where a push–pull amplifier is used to function as both the LNTA and TIA. However, a poor linearity of  $-50 \, dBm$  due to the low supply voltage is reported. Moreover, this approach is suitable for sub-GHz applications only. In Lin et al. (2014a), a current-reuse receiver using an N-path passive mixer for input matching and an active mixer for down-conversion is used. This topology needs additional voltage headroom for its active mixer, increasing its supply voltage requirement. Moreover, it requires an additional circuit to combine the N paths, consuming additional power. Another approach introduces the 1/f noise-cancellation (NC) technique. However, it consume a high power of 8 mW Ghosh & Gharpurey (2011). Another alternative in Kim & Kwon (2019) utilizes both input matching and a 1/f NC technique and reports a low NF of 1.94 dB at the cost of very narrow bandwidth. The same current-reuse receiver architecture is employed in Abbasi, Shams, Kakhki & Nabki (2020a) but utilizes a cross-coupled common-gate (CCCG) LNTA topology to enhance the operating bandwidth. However, both Kim & Kwon (2019); Abbasi et al. (2020a) suffer from the loading effect on the RF signal due to the sharing of the passive mixer input and receiver output nodes. A quadrature RF-to-BB current-reuse receiver is proposed in Park & Kwon (2021), which comprises the architecture from Kim & Kwon (2019). It reports a very high NF of 13.2 dB despite using a common-source LNTA topology with a low noise contribution and narrow bandwidth. In Ramella et al. (2017), the concept of an active-inductor (AI) was introduced, and this was used in our earlier works Abbasi, Shams & Nabki (2020b) to overcome the issues mentioned above.

In order to provide design insights into low-power CRR circuits, this work provides a design procedure, characterization and more depth into the design methodology behind the circuit proposed in our earlier work Abbasi *et al.* (2020b). It includes the topology selection and design of the LNTA, down-conversion mixer and active-inductor (AI). The concept and design of the

TIA is described as well. The paper provides all of the design steps and test benches required, along with the mathematical calculations necessary for the design. The paper is structured as follows. Section 2.2 overviews the design steps and test benches of the circuit implementation, Section 2.3 presents system integration considerations, Section 2.4 discusses circuit layout aspects, and Section 2.5 presents the post-layout simulation results of the resulting design and discusses them.

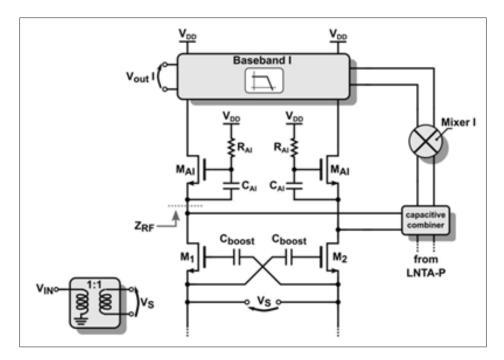

# 2.2 RF-to-BB Current-Reuse Receiver Front-End Circuit Level Design

Thanks to the CMOS scaling, which reduces the threshold voltage of the transistors,  $V_{TH}$ , and increases their frequency of operation (i.e., transition frequency  $\omega_T$  or  $f_T$ ), the stacking of several circuits sharing a single supply is possible. However, this introduces design challenges, which are discussed in Abbasi *et al.* (2020b). The current-reuse receiver (CRR) block diagram proposed in Abbasi *et al.* (2020b) is shown in Figure 2.1. In this section, the detailed design steps, test benches and topology selections are discussed.

## 2.2.1 Low Noise Transconductance Amplifier

In CRR front-ends, the LNTA plays a significant role in defining the overall performance of the CRR, such as its sensitivity, input matching and power consumption. There are two well-known LNTA topologies that can be employed: common-source (CS) and common-gate (CG). The common-source topology is suitable for very low-noise applications, where the noise-figure (NF) is given by Razavi (2013)

$$NF_{CS} = 1 + g_m R_S \gamma \left(\frac{\omega_o}{\omega_T}\right)^2, \qquad (2.1)$$

where  $g_m$  is the transconductance,  $R_S$  is the source impedance,  $\gamma$  is the channel effect,  $\omega_o$  is the operating frequency, and  $\omega_T$  is related to the maximum frequency at which that transistor can operate effectively (i.e. transition frequency). Equation (2.1) shows that a higher  $\omega_T$  results in a very low NF in the CS LNTA topology. The NF in CG topology is given by

$$NF_{CG} = 1 + \frac{\gamma}{g_m R_s}. (2.2)$$

Figure 2.1 Block diagram of the proposed current-reuse receiver. Taken from Abbasi *et al.* (2020b)

It is undeniable that the CG topology achieves much higher NF (>3 dB) than the CS topology since the second term in Equation (2.1) is suppressed by  $\omega_T$  when  $\omega_T \gg \omega_o$ . On the other hand, the CG topology is more suitable for wideband applications, while the CS topology results in narrow-band input impedance matching. The input impedance considering the CS LNTA is given by

$$Z_{CS} = s \left( L_g + L_s \right) + \frac{1}{s(C_{gs} \parallel C_{par})} + \omega_T L_s, \tag{2.3}$$

where  $L_g$  is a series gate inductor,  $L_s$  is an source-degeneration inductor,  $C_{gs}$  is the gate to source capacitance, and  $C_{par}$  is the parasitic capacitance considering the input of the LNTA, such as the pad and ESD cell capacitance. Equation (2.3) shows that the CS topology is suitable for narrow-band applications. On the other hand, the input impedance considering the CG LNTA is calculated by  $1/g_m$  which is a real impedance. Hence, the CG LNTA topology is very suitable for wideband applications as it can be readily matched to the antenna (e.g.,  $50\,\Omega$ ). Thus, topology selection for the LNTA depends on the application requirements. The receiver in Abbasi *et al.* (2020b) requires a wideband operation to cover a wide range of frequencies for several wireless standards; hence, the CG topology is suitable for this goal at the cost of a higher NF compared with the CS topology.

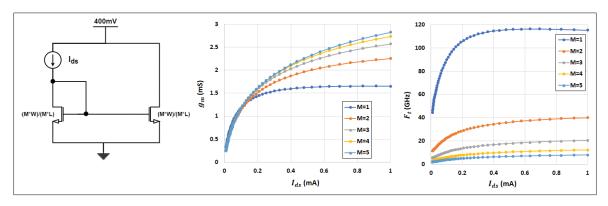

The LNTA design begins with an optimization of  $g_{m}$  and  $f_{T}$ . Figure 2.2a shows a test bench utilized to optimize and characterize  $g_m$  and  $f_T$ . Less than half of the supply voltage is applied to the drain terminal, which is close to the voltage that is expected after the receiver integration. The simulation is performed by sweeping the biasing current (I<sub>ds</sub>) while the width over length ratio (W/L) is maintained at constant value. To observe the channel-length effect, W and L are increased with a scaling coefficient from W/L to 5W/5L, resulting in the plots shown in Figure 2.2b,c. This shows that, by increasing the current for a given W/L, both g<sub>m</sub> and f<sub>T</sub> increase to a certain value until they flatten. The short channel effect can be reduced by increasing L. Thus, by increasing both W and L by the same scaling factor, g<sub>m</sub> improves. However, f<sub>T</sub> reduces due to the increase in gate-source and gate-drain capacitance. In the CG topology, f<sub>T</sub> is not the main contributor in the NF equation, but it is preferred to maintain it to be at least 10 times higher than the operating frequency to avoid any non-idealities such as oscillations. In this case, a scaling factor of 2 (i.e., 2W/2L) is selected. To achieve the required g<sub>m</sub> for input matching, both the width and the current need to increase. This can lead the circuit to consume high power. One approach to reduce the power consumption is to use the capacitive cross-coupling technique to boost the transconductance by a factor of 2. In this way, half of the current is required to achieve

the required  $g_m$ . The LNTA requires a current path to ground, and this can be achieved using either a resistor or inductor. In Abbasi *et al.* (2020b), an inductor is used to reduce the voltage headroom requirement and the RF signal loss by resonating with the parasitic capacitance. Note that further device optimization will need to be performed after receiver integration.

Figure 2.2 (a) Test bench to optimize and characterize  $g_m$  and  $f_T$ , (b) resulting  $g_m$  plots, and (c) resulting  $f_T$  plots.

A single-ended antenna input needs to be converted to a differential signal at the input of the receiver. Both single to differential and LC baluns can be used. An LC-balun achieves a lower NF than a differential balun at the cost of a narrower bandwidth, but its combination with a CG LNTA topology provides wide bandwidth. Moreover, an LC-balun is able to convert the antenna impedance to any impedance considering the LNTA by adjusting the L and C values. This gives more flexibility to the design and allows it to operate at higher  $g_m$ .

#### 2.2.2 Down-Conversion Mixer

There are two choices of down-conversion mixers: active and passive. A passive mixer is preferred over an active mixer since active mixers require voltage headroom, which is not desirable due to the resulting poor linearity performance. Moreover, low-frequency noise can be filtered out using an AC-coupling capacitor at the input of the passive mixer. Thus, in Abbasi *et al.* (2020b), a passive mixer is used to down-convert the RF signal to the IF. A double-balanced passive mixer, as shown in Figure 2.1, is used. To design the mixer switches and optimize the

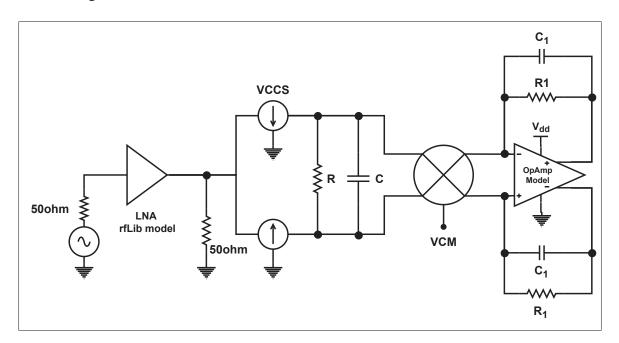

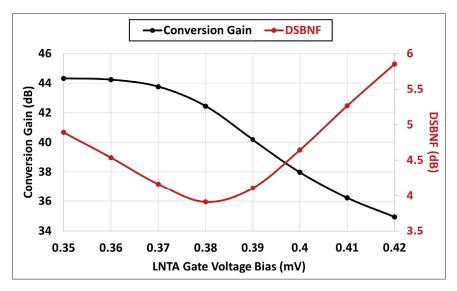

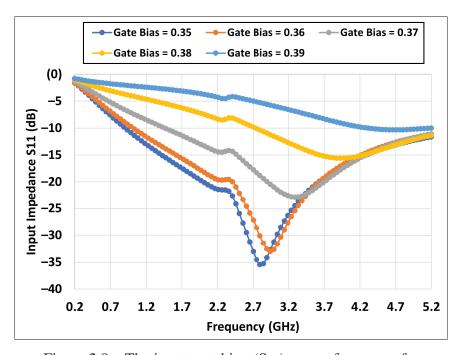

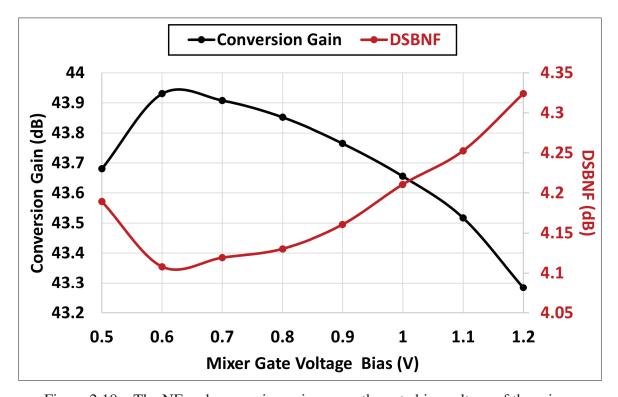

W/L ratio, where L is minimum, a test bench that models the receiver front-end is employed as shown in Figure 2.3. In this test bench, the LNA and TIA are ideal macro-models. A voltage controlled current source (VCCS) is used to convert the RF voltage to the RF current to perform as an LNTA. The LNTA output impedance is modeled by R and C. R<sub>1</sub>, C<sub>1</sub> and an OpAmp model define the TIA macromodel. The design of the mixer switches is performed by sweeping the value of the W/L ratio and the gate voltage of the mixer switches concurrently in order to achieve the best NF and linearity. Figure 2.4 shows the NF and 1 dB compression point (P1dB) performance versus the W/L ratio and the gate voltage of the switches, VCM. The best integrated double side band noise figure (DSBNF), from 1 MHz to 10 MHz, is achieved at a VCM of 800 mV, while the P1dB at 600 mV is 1.4 dB higher than at a VCM of 800 mV. Very large mixer switches need to be avoided to minimize large parasitic capacitors at the input of the mixer that attenuate the RF signal and cause LO to RF leakage. Thus, a W/L ratio of 35 µm/130 nm is selected as a suitable trade-off value. Moreover, the gate voltage should be below the breakdown of the transistors when the LO signal switches high or low. Final optimization is needed after receiver integration.

Figure 2.3 Test bench to design and optimize the down-conversion mixer switches.

Figure 2.4 (a) The noise figure and (b) the 1 dB compression point versus the W/L ratio for different gate voltages of the input transistors.

#### 2.2.3 Active Inductor and Noise Cancellation

In Kim & Kwon (2019), the mixer input and receiver output share the same node, which causes RF signal losses. As a result, the design is not able to operate at very high frequency and is more suitable to sub-GHz applications. In our earlier works Abbasi *et al.* (2020b), the concept of an AI was introduced. In this design, cascoded devices are used to boost the output impedance, as shown in Figure 2.1 ( $M_{AI}$ ). The impedance considering the AI circuit,  $Z_{AI}$ , by ignoring  $M_{NC}$  since it is in parallel, is summarized and given by

$$Z_{AI}(s) \cong \frac{g_{m,AI}R_S(R_{AI}C_{AI}s+1) + R_{AI}C_{AI}s}{g_{m,AI}R_SC_{AI}s + g_{m,AI} + C_{AI}s} || \frac{1}{sC_{nar}},$$

(2.4)

where  $C_{par}$  is the parasitic capacitance at the mixer input and is related to the technology node.

The impedance from the LNTA to the AI is very small at lower frequencies and increases at higher frequencies. This helps to isolate the RF signal from the output node. In this case, the mixer input connects to the LNTA output directly, where the majority of the RF signal flows through the mixer input due to the lower input impedance compared to that of the AI.

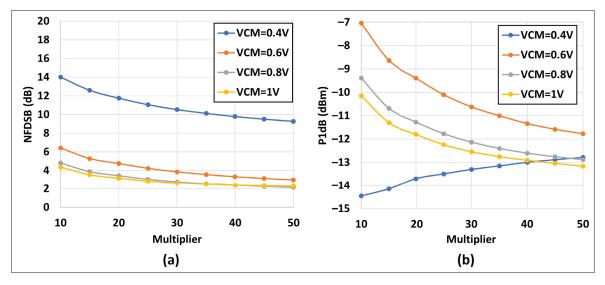

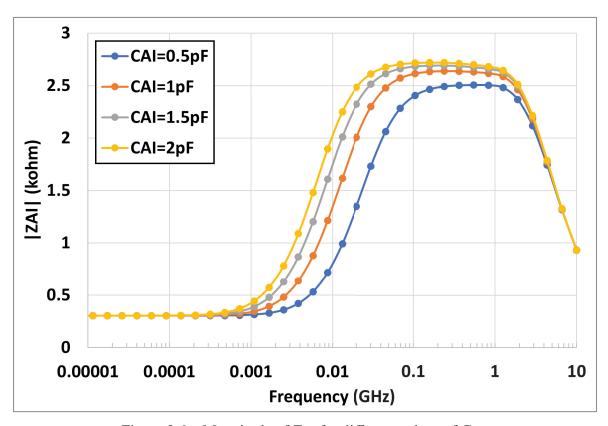

Figure 2.5a shows the test bench to design the AI circuit. The AI circuit includes  $M_{AI}$ ,  $R_{AI}$  and  $C_{AI}$ .  $R_S$  is used to boost the impedance at higher frequencies. A small value is considered to avoid excessive voltage headroom usage.  $M_{TIA}$  and  $R_{FB}$  are used to model the TIA circuit.  $R_{AI}$  and  $C_{AI}$  should be optimized to define the cut-off frequency. The transconductance of  $M_{AI}$  defines the impedance of the AI at DC and low frequencies. A small signal,  $I_{AC}$ , is applied to the input of the AI circuit, and  $V_{AC}/I_{AC}$  is calculated to extract the input impedance of the AI circuit,  $Z_{AI}$ . Figure 2.5b illustrates the magnitude of  $Z_{AI}$  versus the frequency with and without  $R_S$  being considered. It is obvious that  $R_S$  helps to boost the AI input impedance at the cost of voltage headroom. Thus, there is a trade-off between the NF and linearity when the value of  $R_S$  is defined. The gate terminal of  $M_{AI}$  needs to be biased with a voltage,  $V_b$ , of 800 mV to keep it in saturation.

Figure 2.5 (a) Test bench to design the active inductor and (b) its impedance magnitude over frequency with and without  $R_S$  considered.

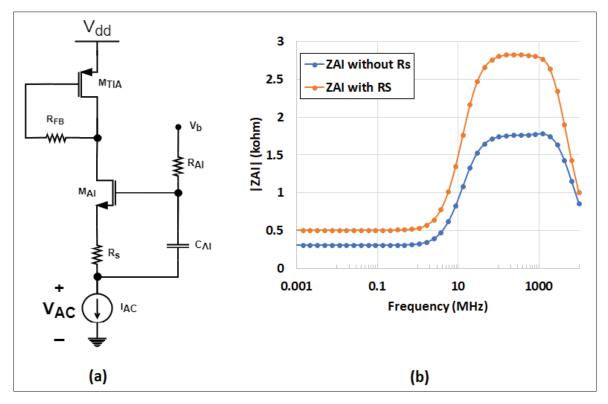

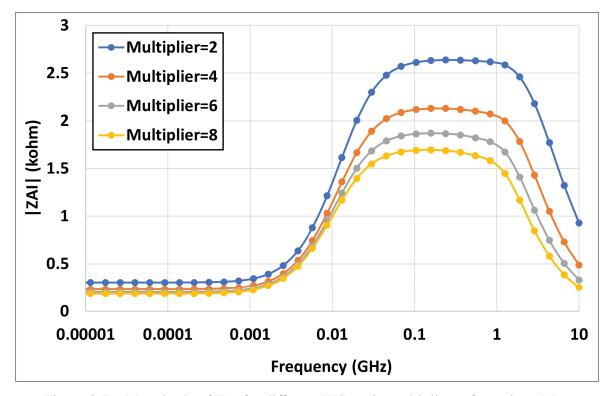

The magnitude of  $Z_{AI}$  is shown for different  $C_{AI}$  values in Figure 2.6. This illustrates that a higher  $C_{AI}$  value pushes the cutoff frequency of  $Z_{AI}$  to a lower frequency and increases its magnitude at high frequency, while it remains constant at lower frequencies. A value for  $C_{AI}$  of 1 pF shows a good trade-off value between the frequency cutoff and maximal impedance magnitude. Another step in the design of the AI circuit is to select the best W/L ratio of  $M_{AI}$ . Figure 2.7 shows that increasing the W/L ratio of  $M_{AI}$  with the multiplier from 2 to 8 leads to a higher  $g_m$  and a lower  $Z_{AI}$  magnitude at lower frequencies. A W/L ratio of  $M\times10\,\mu\text{m}/260\,\text{nm}$ , where M is equal to 4, is selected as a good trade-off between low-frequency and high-frequency impedance behavior.

Final component value fine tuning can be performed after receiver integration.

Figure 2.6 Magnitude of Z<sub>AI</sub> for different values of C<sub>AI</sub>.

Figure 2.7 Magnitude of  $Z_{AI}$  for different W/L ratio multipliers of transistor  $M_{AI}$ . The unit W/L ratio is  $10\,\mu\text{m}/260\,\text{nm}$ .

# 2.2.4 Transimpedance Amplifier

The final step is to design the baseband (BB) circuit in the CRR front-end where the BB current needs to be converted to a BB voltage at the output. In Kim & Kwon (2019); Abbasi *et al.* (2020b), a TIA is designed using a single transistor with a feedback resistor,  $R_{FB}$ , shown in Figure 2.1. A large channel-length value should be used to enhance the TIA output impedance. The impedance considering the TIA is defined by  $1/g_m$  of  $M_{TIA}$ . The conversion gain is approximately calculated through the following relation:

$$Conv.Gain \cong \frac{2\sqrt{2}}{\pi} g_{m,eff} R_{FB}.$$

(2.5)