## Low Power Agile Wideband RF CMOS Front-Ends for 5G, Wi-Fi 6E and Impulse Radio Applications

by

#### Nakisa SHAMS

#### MANUSCRIPT-BASED THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, 12, DECEMBER, 2022

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#### **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED BY THE FOLLOWING BOARD OF EXAMINERS

M. Frédéric Nabki, thesis supervisor Département de génie électrique à l'École de Technologie Supérieure

M. Jérémie Voix, president of the board of examiners Département de génie mécanique à l'École de Technologie Supérieure

M. Ammar B. Kouki, member of the jury Département de génie électrique à l'École de Technologie Supérieure

M. Réjean Fontaine, external examiner Département de génie électrique et informatique à l'Université de Sherbrooke

# THIS THESIS WAS PRESENTED AND DEFENDED IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC ON 28, NOVEMBER, 2022

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGEMENTS

First of all, I would like to express my sincere thanks to my thesis supervisor, Professor Frédéric Nabki. I would particularly like to thank him both for the freedom he gave me in choosing the direction to give to my research project, as well as for his advice and ideas which made this doctorate what it is today.

I would also like to thank my colleagues and friends within the Laboratory of Communications and Integration of the Micro Électronique (LaCIME) and the École de Technologie Supérieure.

I would also like to thank everyone who contributed to this thesis. I must mention here in particular CMC Microsystems, which provided the design tools and allowed the manufacture of the various chips designed during this doctorate.

My deepest gratitude goes to all of my family members. It would not be possible to write this thesis without the support from them. I would like to thank my parents, my sisters for their support throughout my life and my studies. Dad, Mom, and my sisters thank you! Without you, none of this would have been possible.

## Circuits CMOS RF large bande agiles à faible consommation pour les applications de la 5G, du Wi-Fi 6E et de la radio impulsionnelle.

#### Nakisa SHAMS

#### **RÉSUMÉ**

Les années 2020 appartiennent à la cinquième génération, la 5G, c'est-à-dire une nouvelle norme radio (NR), qui est considérée comme une évolution remarquable par rapport aux systèmes de communication actuels et qui peut être configurée de manière flexible pour divers scénarios d'application. Ainsi, nos vies seront affectées par la 5G de manière plus spectaculaire que tout autre changement technologique, car elle nous mène vers un monde entièrement connecté. La 5G, qui utilise la bande de fréquences sub-6 GHz et le spectre des ondes millimétriques (mm-Wave) avec d'autres technologies RF comme les radios à bande ultra-large (UWB), fournira de multiples services.

Alors que la 5G NR est passée de l'état de concept à celui de réalité, la norme Wi-Fi s'est développée en parallèle pour rester au niveau de la norme cellulaire et offrir de meilleures performances et un débit plus élevé. Récemment, l'organisation IEEE a créé un nouveau groupe de travail, le Wi-Fi 6E ou IEEE 802.11ax, pour étudier et réaliser les technologies Wi-Fi de nouvelle génération. Wi-Fi 6E fait référence à l'ensemble des dispositifs Wi-Fi, fournit des débits gigabit avec des performances plus élevées, des débits de données plus rapides et une latence plus faible, et complète le déploiement des réseaux 5G pour fournir une connectivité à l'intérieur, où la 5G NR est beaucoup moins efficace. Le Wi-Fi 6E a été étendu à la bande 6 GHz, offrant une augmentation considérable de la bande passante disponible. Cependant, sa dissipation d'énergie relativement élevée pose des problèmes à l'adoption du Wi-Fi pour les plateformes à faible consommation, telles que les dispositifs de l'Internet des objets (IoT) et les nœuds de capteurs sans fil. Les prévisions d'un grand nombre d'appareils connectés d'ici 2030 et la réalisation de la 5G et de la Wi-Fi 6E entraînent le besoin de techniques au niveau des circuits pour atténuer les interférences croissantes liées à ce nombre croissant d'appareils.

À cette fin, ce travail se concentre sur les techniques de conception pour fournir des architectures frontales de récepteur RF hautement résistantes aux interférences, de manière économe en énergie et fonctionnant dans une large gamme de fréquences RF d'entrée. Tout d'abord, une revue de la littérature est présentée. Elle se concentre sur les circuits frontaux des récepteurs RF, leurs circuits au niveau des transistors et leurs spécifications. Dans la deuxième partie de cette thèse, nous démontrons trois récepteurs RF utilisant une configuration de commutation à 4, 8 et 16 chemins qui permettent la sélection de la troisième harmonique de la fréquence de l'oscillateur local (LO), et qui suppriment efficacement les autres harmoniques afin de réduire la fréquence d'entrée et la consommation d'énergie du générateur d'horloge multiphase dans des bandes de fréquences RF plus élevées.

En considérant les défis de conception liés au filtre de commutation à N chemins, y compris le nombre de commutateurs, la consommation énergétique du circuit de génération des phases du LO et la performance de bruit, il est démontré qu'un système de filtre de commutation à 8

chemins est préférable pour fournir un compromis approprié entre les effets de repli harmonique, la mesuresbruit, la surface du circuit et la consommation d'énergie. Ainsi, la troisième partie de cette thèse démontre un récepteur RF à sélection d'harmoniques tolérant aux bloqueurs qui peut être reconfiguré pour sélectionner les premières et troisièmes harmoniques de la fréquence de commutation dans les bandes de fréquences basses et hautes, respectivement. Nous présentons un circuit intégré de preuve de concept en technologie CMOS 130 nm. Nous présentons un circuit intégré de preuve de concept dans un processus de technologie CMOS et nous présentons les résultats de mesures.

De fortes interférences hors bande (OOB) ou des bloqueurs indésirables peuvent désensibiliser un récepteur. Pour améliorer la résilience aux bloqueurs, le circuit frontal RF doit éviter l'amplification aux fréquences des bloqueurs au niveau du nœud d'entrée du récepteur. Pour ce faire, deux architectures différentes de récepteurs RF à large bande et antibruit sont présentées. Elles sont capables de tolérer les bloqueurs d'harmoniques LO sans sacrifier les performances en matière de bruit et en éliminant les pré-filtres SAW tout en consommant peu d'énergie d'horloge. Les résultats de mesure des prototypes de circuits intégrés en CMOS 65 nm confirment les avantages de nos techniques.

La dissipation d'énergie étant toujours importante pour les dispositifs de communication à large bande, il est possible d'économiser davantage d'énergie en exploitant une architecture IR-UWB à conversion directe auto-démodulante. À cette fin, cette thèse décrit l'étude, la conception, la fabrication et la caractérisation d'une électronique frontale IR-UWB non cohérent à double bande reconfigurable. Le récepteur IR-UWB multi-bandes proposé peut être reconfiguré numériquement dans différents modes de fréquence de fonctionnement, et est capable de supporter des données modulées en modulation par déplacement de fréquence binaire (FSK) en plus de la modulation tout-ou-rien (OOK), et permet de tirer parti de la signalisation ternaire en combinant les modulations OOK et FSK. Enfin, une méthodologie de conception détaillée est proposée, les résultats de mesure du récepteur fabriqué en technologie CMOS TSMC 130 nm et des discussions sont présentées.

Les techniques présentées permettront sans aucun doute le développement de nouvelles applications et contribueront ainsi à l'avancement des connaissances scientifiques sur les récepteurs frontaux à large bande RF.

**Mots-clés:** Récepteur, sélection des harmoniques, suppression du bruit, IR-UWB, reconfigurable.

## Low Power Agile Wideband RF CMOS Front-Ends for 5G, Wi-Fi 6E and Impulse Radio Applications

#### Nakisa SHAMS

#### **ABSTRACT**

The 2020s belong to the fifth generation, 5G, that is a new radio (NR) standard, which is considered an outstanding evolution over the current communication systems and can be flexibly configured for various application scenarios. Thus, our lives will be affected by 5G more dramatically than any other technology shift since it will lead us to a fully connected world. 5G using sub-6 GHz frequency band and millimeter wave (mm-Wave) spectrum together with other RF technologies like ultra-wideband (UWB) will provide multiple services.

As 5G NR transitioned from concept to reality, Wi-Fi has been the developing standard in parallel to keep it at par with the cellular standard providing better performance and higher throughput. Recently, the IEEE introduced a new task group, i.e., the Wi-Fi 6E or IEEE 802.11ax, to investigate and realize next-generation Wi-Fi technologies. Wi-Fi 6E refers to the set of Wi-Fi devices, provides gigabit throughputs with higher performance, faster data rates, and lower latency, and complements the deployment of 5G networks to provide connectivity indoors, where 5G NR is far less effective. Wi-Fi 6E was extended into the 6 GHz band, offering considerable increases in available bandwidth. However, its relatively high power dissipation poses challenges for Wi-Fi being adopted for low power platforms, such as Internet-of-Things (IoT) devices and wireless sensor nodes. Forecasts of numerous connected devices by 2030 and the realization of 5G and Wi-Fi 6E drive the need for circuit-level techniques to alleviate the increasing interference coming with this growing number of devices.

To this end, this work focuses on design techniques to provide highly interference resilient RF receiver front-end architectures in a power efficient manner and operating in a wide range of input RF frequencies. First, a literature review is presented. It focuses on the RF receiver front-ends, their transistor-level circuit, and their specifications. In the second part of this dissertation, we demonstrate three wideband RF receivers using a 4-, 8-, and 16-path switching configuration that allows for the selection of the third harmonic of the local oscillator (LO) frequency, and that effectively suppresses other harmonics to reduce the input frequency and power consumption of the multi-phase clock generator at higher RF frequency bands of operation.

When considering the design challenges related to the N-path switching filter, including the number of switches, power consumption of the LO phases generation circuitry, and noise performance, it is shown that an 8-path switching filter system is preferred to provide a suitable trade-off between the harmonic fold back effects, noise figure, circuit area, and power consumption. Thus, the third part of this dissertation demonstrates a blocker-tolerant harmonic selection wideband RF receiver that can be reconfigured to select the first and third harmonics of the switching frequency at the low and high frequency bands, respectively. We present a proof of concept integrated circuit in 130 nm CMOS technology process and present the measurement results.

Strong out-of-band (OOB) interference or undesired blockers can desensitize a receiver. To enhance resilience to the blockers, the RF front-end must avoid amplification at blocker frequencies at the input node of the receiver. To do this, two different wideband noise-cancelling wideband RF receiver architectures are then presented that have the capability of tolerating the LO harmonic blockers without sacrificing noise performance and alleviating the SAW pre-filters requirement while consuming low clocking power consumption. Measurement results from the integrated circuit prototypes in 65 nm CMOS confirm our techniques' benefits.

Since power dissipation is always important for wideband communication devices, more power can be saved by exploiting a self-demodulating direct conversion impulse radio UWB (IR-UWB) architecture. To this end, this dissertation describes the study, design, fabrication, and characterization of a reconfigurable dual-band non-coherent wideband IR-UWB front-end. The proposed multi-band IR-UWB receiver can be digitally reconfigured in different operating frequency modes, and is able to support data modulated in binary frequency shift keying (FSK) in addition to on-off keying (OOK), and allows for the leveraging of ternary signaling by combining both OOK and FSK modulations. Ultimately, a detailed design methodology and measurement results of the fabricated receiver in TSMC 130 nm CMOS technology are presented.

The presented techniques will undoubtedly allow the development of new applications, and will thus contribute to the scientific knowledge advancement on RF wideband receiver front-ends.

**Keywords:** Wideband, Wireless, Receiver, Harmonic Selection, Noise-Cancelling, Ultra wideband, Impulse radio, Reconfigurable.

#### TABLE OF CONTENTS

|        |         |                                                                  | Page |

|--------|---------|------------------------------------------------------------------|------|

| INTR   | ODUCTI  | ON                                                               | 1    |

| CHA    | PTER 1  | LITERATURE REVIEW                                                | 13   |

| 1.1    | Wideba  | and RF Receiver Front-End Architectures                          |      |

|        | 1.1.1   | Wideband RF receiver using discrete-time analog filtering        | 11   |

|        | 1.1.2   | Wideband RF receiver using switching mixers                      |      |

|        | 1.1.3   | Wideband RF receivers using N-path filtering                     | 15   |

|        |         | 1.1.3.1 Mixer-first receivers using N-path filtering             |      |

| 1.2    | Ultra-V | Videband Impulse Radio Receiver Architectures                    |      |

|        | 1.2.1   | Coherent receivers                                               | 19   |

|        | 1.2.2   | Non-coherent receivers                                           | 21   |

|        |         | 1.2.2.1 Energy detection receiver                                | 21   |

|        |         | 1.2.2.2 Peak detection receiver                                  | 22   |

|        |         | 1.2.2.3 Super regenerative receiver (SRR)                        | 23   |

| 1.3    | Compa   | rison of the state-of-the-art                                    | 25   |

| 1.4    | Conclu  | sion                                                             | 25   |

| CHA    | PTER 2  | ANALYSIS AND COMPARISON OF LOW-POWER 6 GHZ N-                    |      |

| OIII I | 121(2   | PATH FILTER-BASED HARMONIC SELECTION RF RECEIVER                 |      |

|        |         | FRONT-END ARCHITECTURES                                          | 27   |

| 2.1    | Introdu | ection                                                           |      |

| 2.2    |         | rt in Harmonic Rejection RF Receivers                            |      |

| 2.3    |         | is of the Frequency Down-conversion Properties of the N-Path     |      |

|        |         | ing Filter and its Harmonic Selection Properties                 | 32   |

| 2.4    |         | ed Harmonic Selection RF Front-end Architectures                 |      |

|        | 2.4.1   | Comparison of the RF front-ends using 4-path, 8-path and 16-path |      |

|        |         | mixing                                                           | 40   |

| 2.5    | Circuit | Implementation                                                   | 42   |

|        | 2.5.1   | Differential wideband low noise amplifier                        | 43   |

|        | 2.5.2   | N-path switching filter                                          | 46   |

|        | 2.5.3   | Baseband harmonic recombination transconductors                  |      |

|        | 2.5.4   | N-phase non-overlapping clock generation                         | 48   |

| 2.6    | Post-la | yout Simulations Results                                         | 49   |

|        | 2.6.1   | LO performance                                                   | 51   |

|        | 2.6.2   | Performance comparison of the conventional and the proposed HR   |      |

|        |         | receivers                                                        | 53   |

|        | 2.6.3   | 8-path HR receiver performance in two CMOS technologies          | 57   |

|        | 2.6.4   | Linearity                                                        |      |

|        | 2.6.5   | Blocker Tolerability                                             |      |

|        | 2.6.6   | 8-path HR receiver robustness to process variations              | 61   |

| 2.7        |         | sion                                                                                               |     |

|------------|---------|----------------------------------------------------------------------------------------------------|-----|

| 2.8        | Conclu  | sion                                                                                               | 62  |

| CHA        | PTER 3  | BLOCKER-TOLERANT INDUCTOR-LESS HARMONIC SELECTI<br>WIDEBAND RECEIVER FRONT-END FOR 5G APPLICATIONS | ON  |

|            |         |                                                                                                    | 65  |

| 3.1        | Introdu | ection                                                                                             |     |

| 3.2        | Propos  | ed Harmonic Selection Receiver Architecture                                                        | 72  |

| 3.3        | Circuit | Design                                                                                             | 74  |

|            | 3.3.1   | Differential Wideband LNA                                                                          | 77  |

|            | 3.3.2   | 8-Path Switching Filter                                                                            | 79  |

|            | 3.3.3   | First and Third Harmonic Recombination Paths                                                       | 80  |

|            | 3.3.4   | Variable Gain BB Amplifier and LO Clock Generator                                                  | 84  |

| 3.4        | Measu   | rement Results                                                                                     | 86  |

|            | 3.4.1   | Receiver Characterization in the LB Frequency Range                                                | 88  |

|            | 3.4.2   | Receiver Characterization in the HB Frequency Range                                                | 91  |

|            | 3.4.3   | Summary and Comparison to the State-of-the-Art                                                     | 95  |

| 3.5        | Conclu  | sion                                                                                               | 96  |

| 3.6        | Append  | dix A                                                                                              | 97  |

| 3.7        | Append  | dix B                                                                                              | 98  |

| СНА        | PTER 4  | A BLOCKER TOLERANT HARMONIC SELECTION NOISE-                                                       |     |

| CIII       | ILICT   | CANCELLING RF RECEIVER FOR 5G AND WI-FI 6E                                                         |     |

|            |         | APPLICATIONS                                                                                       | 103 |

| 4.1        | Introdu | action                                                                                             |     |

| 4.2        |         | nic Selection Noise-Cancelling Architecture of RX1 and RX2                                         |     |

| 4.3        |         | nic Selection Switching Filter Based on Resistive Coefficients                                     |     |

| 4.4        |         | Implementation                                                                                     |     |

|            | 4.4.1   | Differential wideband LNA                                                                          |     |

|            | 4.4.2   | Differential down-conversion paths                                                                 |     |

|            | 4.4.3   | Analog baseband circuits                                                                           |     |

|            | 4.4.4   | Multi-phase LO generator                                                                           |     |

| 4.5        |         | rement Results                                                                                     |     |

|            | 4.5.1   | Performance of RX1                                                                                 |     |

|            | 4.5.2   | Performance of RX2                                                                                 |     |

|            | 4.5.3   | Performance Summary                                                                                |     |

| 4.6        |         | sion                                                                                               |     |

| 4.7        |         | dix A                                                                                              |     |

| СПУ        | PTER 5  | AN OOK AND BINARY FSK RECONFIGURABLE DUAL-                                                         |     |

| СПА        | FIEK J  |                                                                                                    |     |

|            |         | BAND NON-COHERENT IR-UWB RECEIVER SUPPORTING                                                       | 120 |

| 5 1        | Into de | TERNARY SIGNALING                                                                                  |     |

| 5.1<br>5.2 |         | action                                                                                             |     |

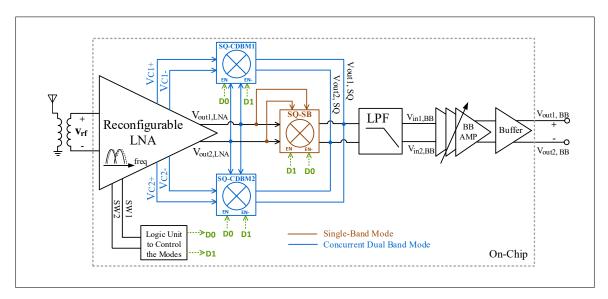

| 3.2        | Kece1V  | er Architecture                                                                                    | 144 |

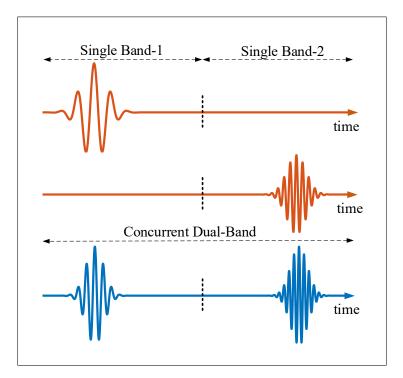

|      | 5.2.1  | Single-E    | Band Mode                                 | 145 |

|------|--------|-------------|-------------------------------------------|-----|

|      | 5.2.2  | Concurr     | ent Dual-band Mode                        | 147 |

| 5.3  | RF Fro | ont-end Cir | cuit Design                               | 148 |

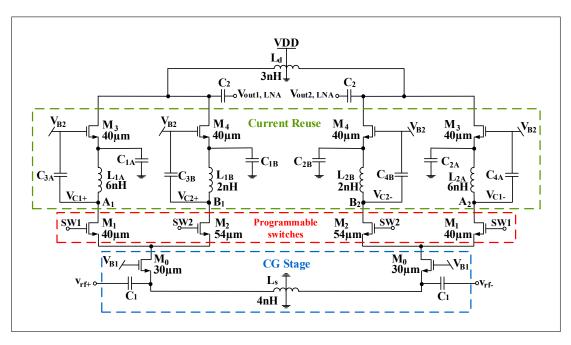

|      | 5.3.1  | Reconfig    | gurable Multi-band Fully-Differential LNA | 149 |

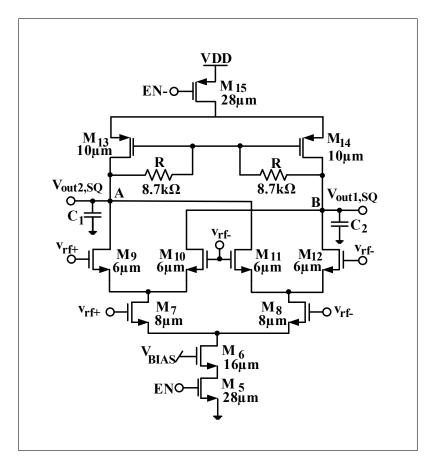

|      | 5.3.2  | Fully Di    | ifferential Squarer                       | 153 |

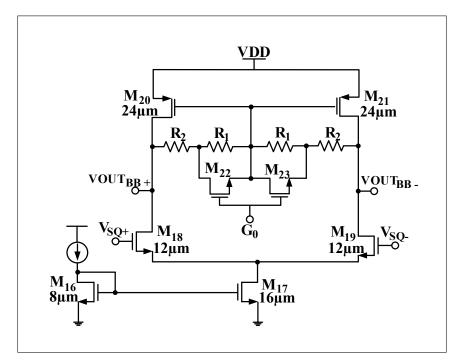

|      | 5.3.3  | Differen    | tial Variable Gain Baseband Amplifier     | 156 |

| 5.4  | Measu  | rement Res  | sults                                     | 157 |

|      | 5.4.1  | IR-UWI      | B Receiver Characterization               | 160 |

|      |        | 5.4.1.1     | Single-Band Modes                         | 161 |

|      |        | 5.4.1.2     | Concurrent Dual-band Mode                 | 162 |

|      |        | 5.4.1.3     | Linearity                                 | 164 |

|      |        | 5.4.1.4     | Performance and Comparisons               | 166 |

| 5.5  | Conclu | ision       |                                           | 167 |

| 5.6  | Appen  | dix A       |                                           | 168 |

|      | 5.6.1  | LNA Ga      | ain Analysis                              | 168 |

|      | 5.6.2  | LNA No      | oise Analysis                             | 169 |

| 5.7  | Appen  | dix B       |                                           | 173 |

|      | 5.7.1  | Squarer     | Conversion Gain Analysis                  | 173 |

| CON  | CLUSIO | N AND RE    | ECOMMENDATIONS                            | 177 |

| LIST | OF REF | ERENCES     | 3                                         | 185 |

#### LIST OF TABLES

|           |                                                                                                                                                                                                                                                         | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1.1 | Comparison of the state-of-the-art                                                                                                                                                                                                                      | 25   |

| Table 2.1 | Post-layout simulation results overview for the conventional and the three proposed receivers (65 nm CMOS)                                                                                                                                              | 55   |

| Table 2.2 | Post-layout simulation performance summary and comparison to recently published RF receivers, illustrating the potential of the proposed architecture to achieve high frequency operation and low power consumption, including in larger geometry nodes | 60   |

| Table 3.1 | Performance summary and comparison to the state-of-the-art                                                                                                                                                                                              | 101  |

| Table 4.1 | Measurement performance summary and comparison to recently published RF receivers                                                                                                                                                                       | 137  |

| Table 5.1 | Operation modes supported using the current-mode switches                                                                                                                                                                                               | 146  |

| Table 5.2 | Summary of the LNA performance and comparison to other works                                                                                                                                                                                            | 160  |

| Table 5.3 | Summary of the IR-UWB receiver performance and comparison to other works                                                                                                                                                                                | 167  |

#### LIST OF FIGURES

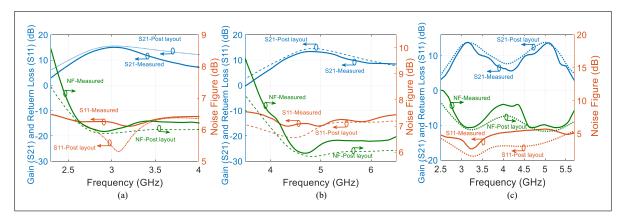

|            | Pag                                                                                                                                                                                                                                                         | e |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 0.1 | Evolution of communication systems                                                                                                                                                                                                                          | 1 |

| Figure 0.2 | The evolution of Wi-Fi Standards                                                                                                                                                                                                                            | 3 |

| Figure 1.1 | Prior art in wideband RF receiver front-ends (a) Discrete-time (DT) RF signal processing, (b) receiver based on the N-path band path filters, (c) receiver based on the notch filters, (d) Mixer-first architectures, and (e) Noise cancellation structures | 2 |

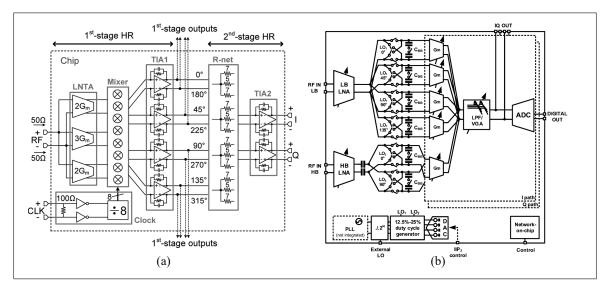

| Figure 1.2 | (a) Wideband receiver architecture using the two-stage polyphase HR and the low-pass blocker filtering, and (b) harmonic recombination receiver architecture                                                                                                | 4 |

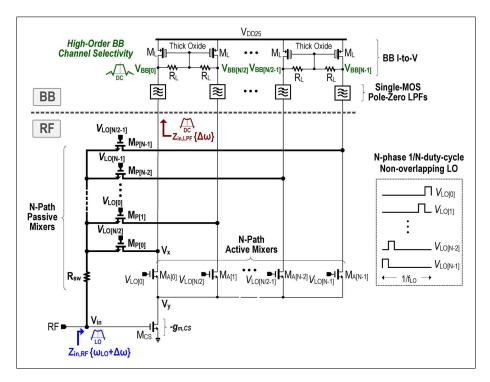

| Figure 1.3 | Stacked RF-to-BB receiver with parallel N-Path active/passive mixers                                                                                                                                                                                        | 7 |

| Figure 1.4 | Operating principle of a coherent receiver                                                                                                                                                                                                                  | 9 |

| Figure 1.5 | Quadrature analog correlating architectures                                                                                                                                                                                                                 | 0 |

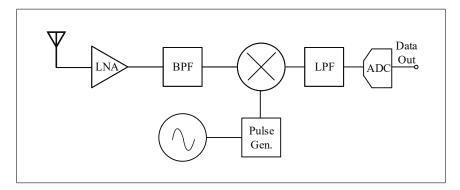

| Figure 1.6 | Block diagram of an energy detection receiver                                                                                                                                                                                                               | 1 |

| Figure 1.7 | Energy detection non-coherent receiver                                                                                                                                                                                                                      | 2 |

| Figure 1.8 | An IR-UWB peak detection non-coherent receiver                                                                                                                                                                                                              | 3 |

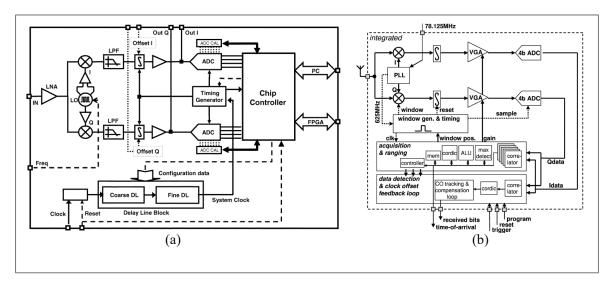

| Figure 1.9 | (a) Simplified block diagram of the SRR, and (b) SRR system level architecture using a statistics-based time averaging technique                                                                                                                            | 4 |

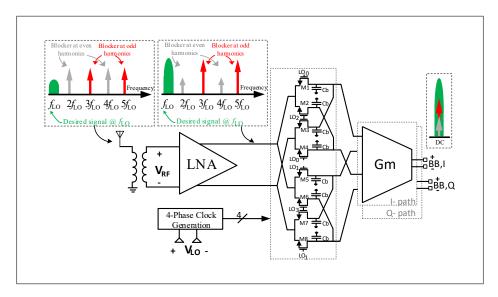

| Figure 2.1 | Conventional wideband receiver using a 4-phase passive mixer                                                                                                                                                                                                | 9 |

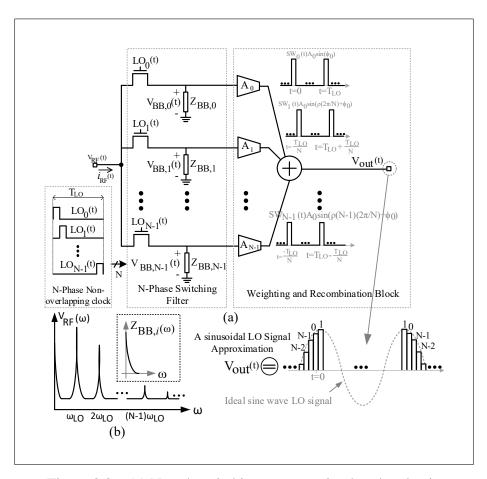

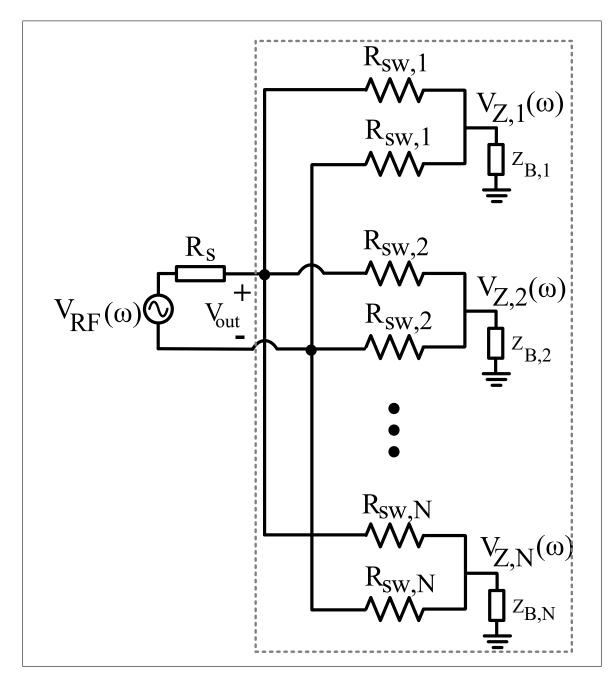

| Figure 2.2 | (a) N-path switching system using baseband gain coefficients, and (b) RF input voltage of $V_{RF}(\omega)$                                                                                                                                                  | 2 |

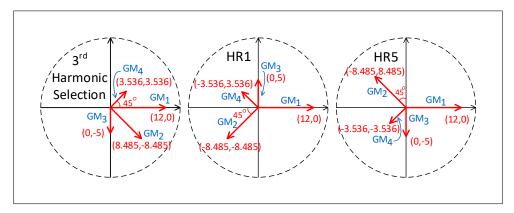

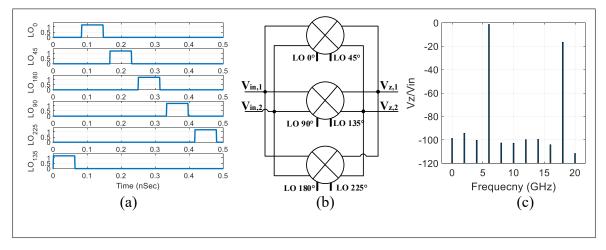

| Figure 2.3 | Operating principle of the proposed harmonic recombination RF receiver                                                                                                                                                                                      | 9 |

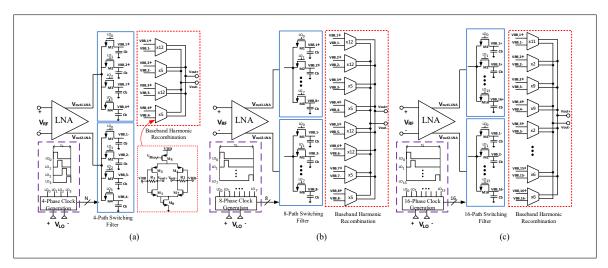

| Figure 2.4 | Architecture of the harmonic recombination RF receiver front-end using a (a) 4-path switching system, (b) 8-path switching system, and (c) 16-path switching system                                                                                         | 0 |

| Figure 2.5  | and $5^{th}$ harmonic rejection for the 8-path HR receiver                                                                                                                                                                                                                            | 41 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

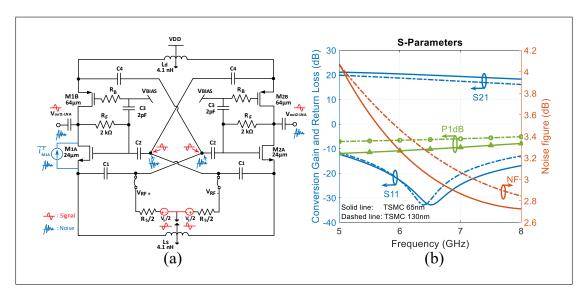

| Figure 2.6  | (a) Differential wideband LNA, and (b) its Gain (S21), return loss (S11), NF and 1-dB compression point (P1dB)                                                                                                                                                                        | 43 |

| Figure 2.7  | 4-phase clock generation circuit, (b) 8-phase clock generation circuit, (c) 16-phase clock generation circuit                                                                                                                                                                         | 48 |

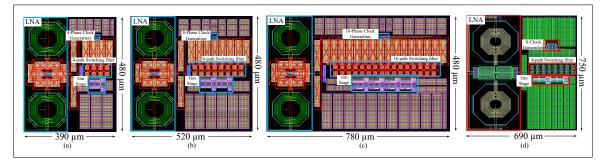

| Figure 2.8  | Layout of the proposed harmonic recombination receivers                                                                                                                                                                                                                               | 50 |

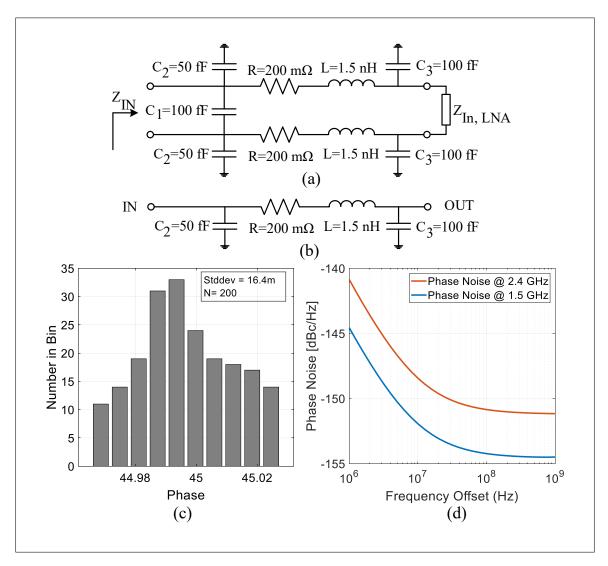

| Figure 2.9  | Bond-wire packaging model for (a) differential LNA input, and (b) single-ended pins, (c) post-layout simulated histogram of the phase deviation from 45° between two adjacent 2.4 GHz LO clocks and (d) the output phase noise of the 8-phase LO clock generator vs. frequency offset | 51 |

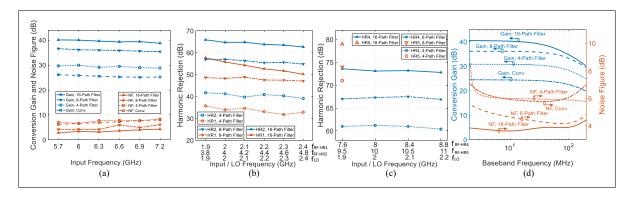

| Figure 2.10 | Post-layout simulation performance of the conventional receiver along with that of the proposed RF receivers using 4-, 8- and 16-path switching systems                                                                                                                               | 53 |

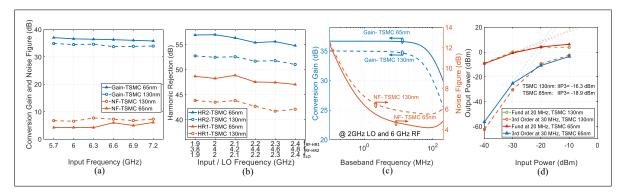

| Figure 2.11 | Post-layout simulation performance of the proposed 8-path HR receiver implemented in 65 nm and 130 nm CMOS                                                                                                                                                                            | 57 |

| Figure 2.12 | Post-layout simulated                                                                                                                                                                                                                                                                 | 58 |

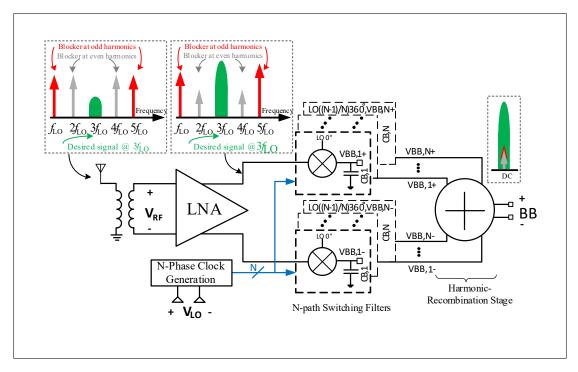

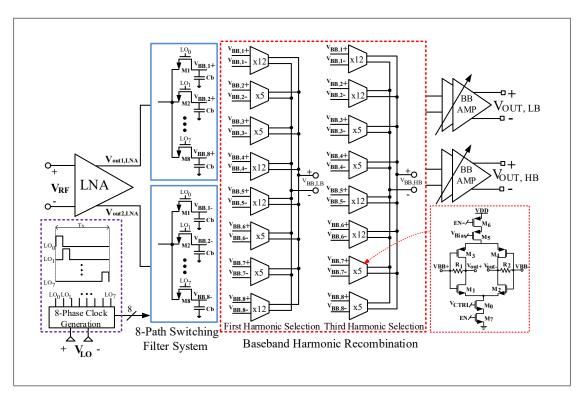

| Figure 3.1  | Diagram of the proposed harmonic recombination RF receiver                                                                                                                                                                                                                            | 72 |

| Figure 3.2  | Architecture of the 1 <sup>st</sup> and 3 <sup>rd</sup> harmonic selection receiver frontend                                                                                                                                                                                          | 73 |

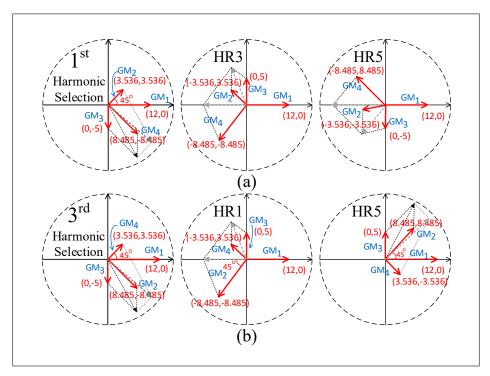

| Figure 3.3  | Phasor diagrams of (a) the $1^{st}$ harmonic selection, along with the $3^{rd}$ and $5^{th}$ harmonic rejection, and (b) the 3rd harmonic selection, along with the $1^{st}$ harmonic rejection for the 8-path HR receiver                                                            | 76 |

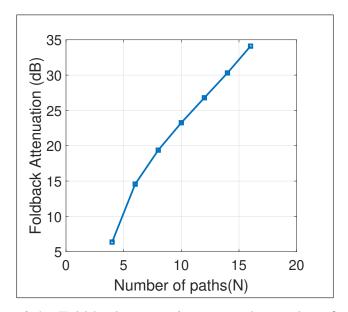

| Figure 3.4  | Fold-back attenuation versus the number of paths                                                                                                                                                                                                                                      | 77 |

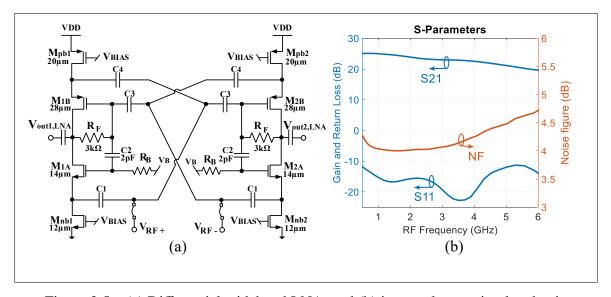

| Figure 3.5  | (a) Differential wideband LNA, and (b) its post-layout simulated gain (S21), return loss (S11) and NF.                                                                                                                                                                                | 78 |

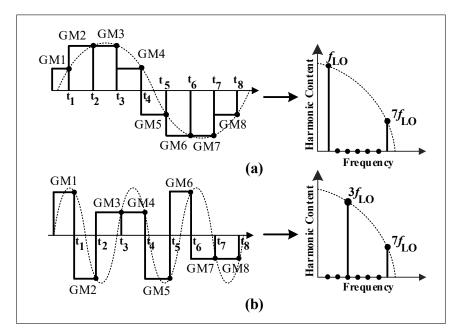

| Figure 3.6  | Effective LO waveform and harmonic content from the Fourier analysis at (a) the $V_{BB,LB}$ output, and at (b) the $V_{BB,HB}$ output                                                                                                                                                 | 82 |

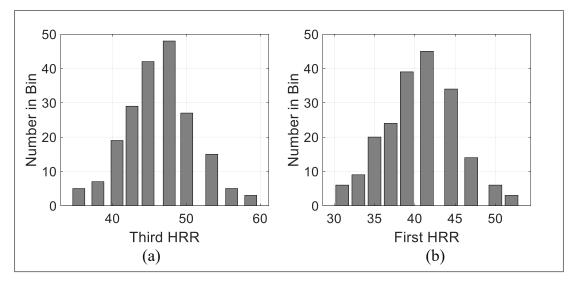

| Figure 3.7  | Post-layout Monte Carlo simulation histograms of the HRR for a 1 GHz LO with 200 runs: (a) 3 <sup>rd</sup> HRR for the LB frequency range and (b) 1 <sup>st</sup> HRR for the HB frequency range                                                                                      | 83 |

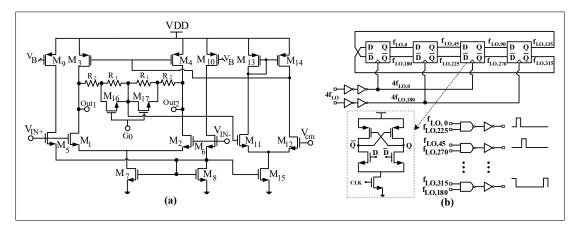

| Figure 3.8  | (a) Variable gain BB amplifier, and (b) 8-phase non-overlapping LO clock generator                                                                                                                                                                                                                                                                                                                                                        | 85  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

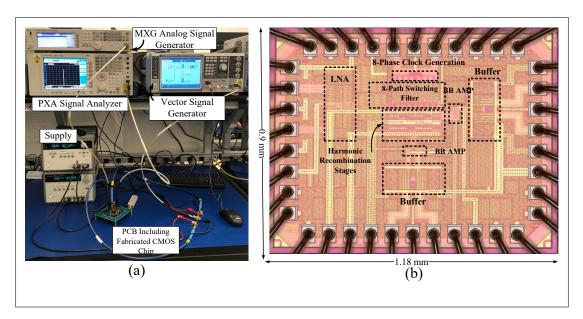

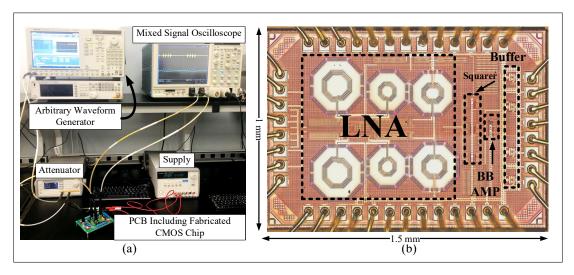

| Figure 3.9  | (a) Micrograph of the harmonic selection receiver occupying an active area of $0.76\mathrm{mm}\times0.64\mathrm{mm}$ in $130\mathrm{nm}$ CMOS, and (b) the measurement setup.                                                                                                                                                                                                                                                             | 86  |

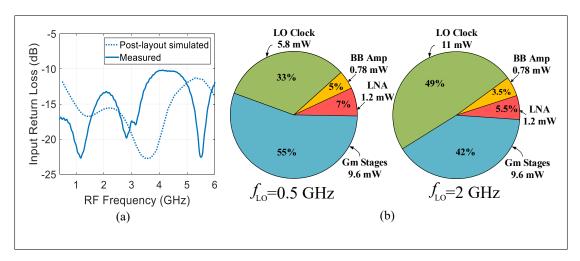

| Figure 3.10 | a) The post-layout simulated and measured input return loss, and (b) the power consumption breakdown at a 0.5 GHz and 2 GHz switching frequency                                                                                                                                                                                                                                                                                           | 87  |

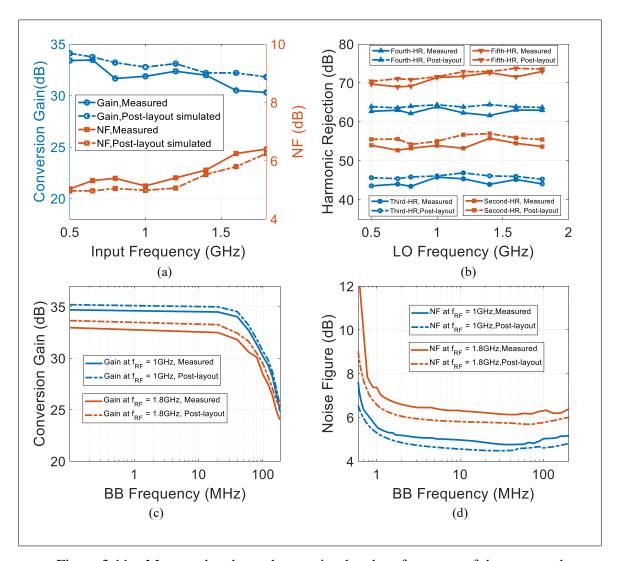

| Figure 3.11 | Measured performance of the proposed receiver operating in the LB frequency range (1 <sup>st</sup> harmonic selection)                                                                                                                                                                                                                                                                                                                    | 89  |

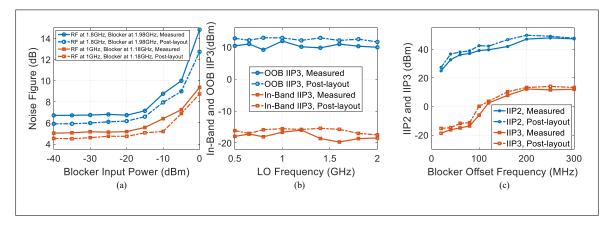

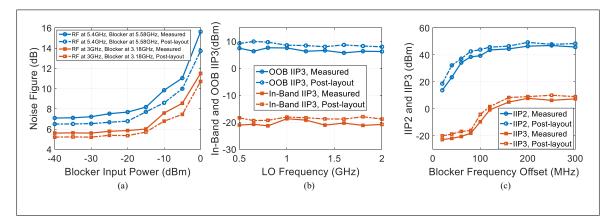

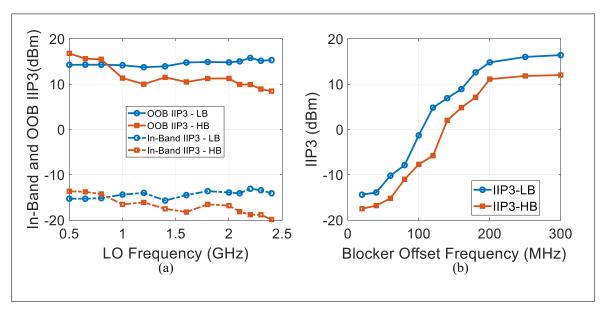

| Figure 3.12 | Measured and post-layout simulated performance of the proposed receiver operating in the LB frequency range (1 <sup>st</sup> harmonic selection): (a) NF versus blocker power at a blocker offset frequency of 180 MHz for $f_{RF} = 1$ GHz and $f_{RF} = 1.8$ GHz, (b) in-band and OOB IIP3 vs. LO frequency and (c) IIP2 and IIP3 vs. blocker offset frequency for a 1 GHz LO frequency                                                 | 90  |

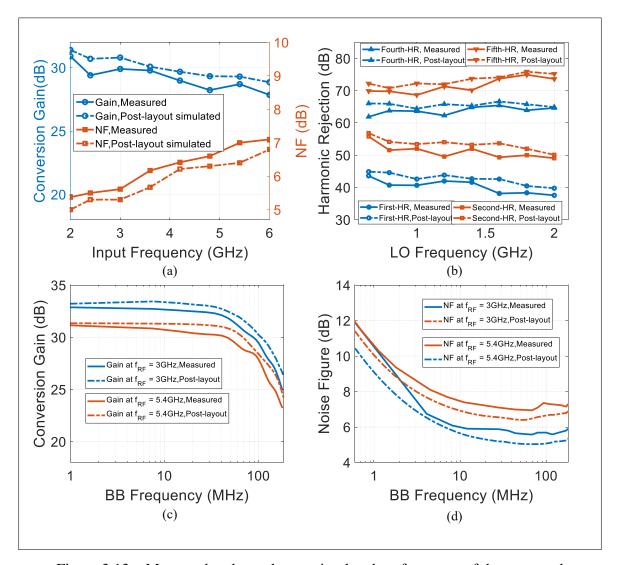

| Figure 3.13 | Measured and post-layout simulated performance of the proposed receiver operating in the HB frequency range (3 <sup>rd</sup> harmonic selection)                                                                                                                                                                                                                                                                                          | 93  |

| Figure 3.14 | Measured and post-layout simulated performance of the proposed receiver operating in the HB frequency range ( $3^{rd}$ harmonic selection):(a) NF versus blocker power at a blocker offset frequency of 180 MHz for $f_{RF}=3$ GHz and $f_{RF}=5.4$ GHz, (b) in-band and OOB IIP3 vs. LO frequency at a frequency offset of 40 MHz and 200 MHz, respectively, and (c) IIP2 and IIP3 vs. blocker offset frequency for a 1 GHz LO frequency | 94  |

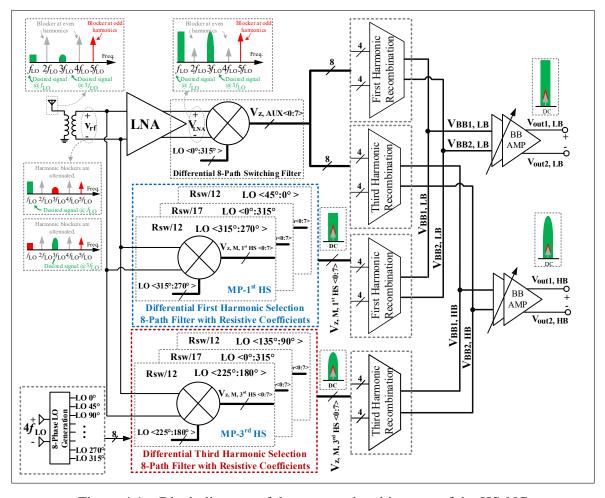

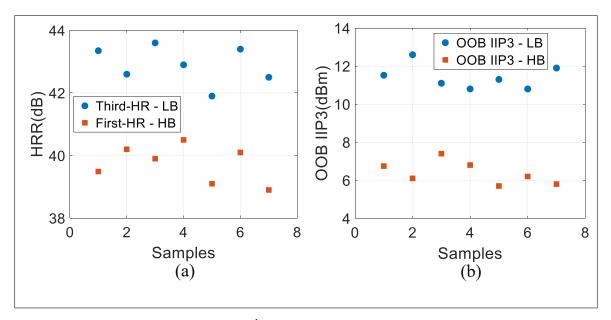

| Figure 4.1  | Block diagram of the proposed architecture of the HS-NC front-end RX1                                                                                                                                                                                                                                                                                                                                                                     | 111 |

| Figure 4.2  | Block diagram of the proposed architecture of the HS-NC front-end RX2                                                                                                                                                                                                                                                                                                                                                                     | 114 |

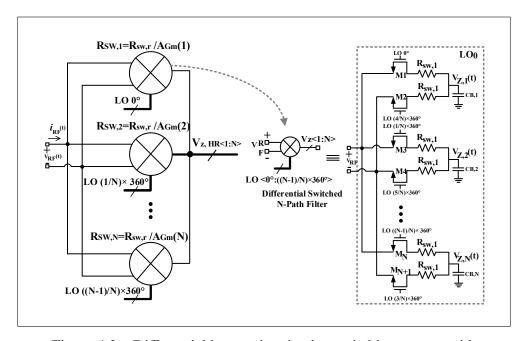

| Figure 4.3  | Differential harmonic rejection switching system with resistive coefficients                                                                                                                                                                                                                                                                                                                                                              | 116 |

| Figure 4.4  | The equivalent input impedance seen from the input port of the resistive HS-NPF at any specific time                                                                                                                                                                                                                                                                                                                                      | 119 |

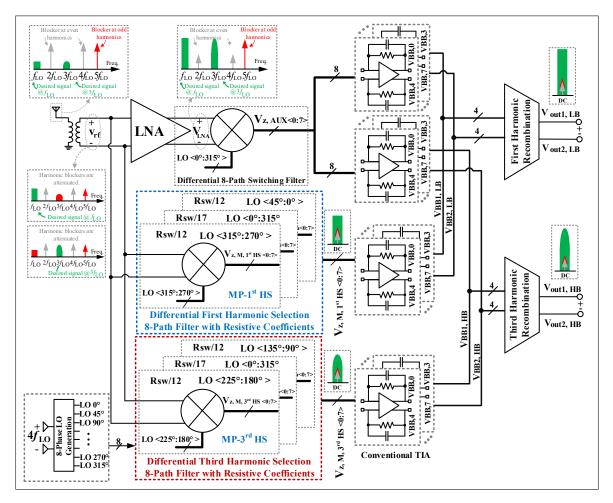

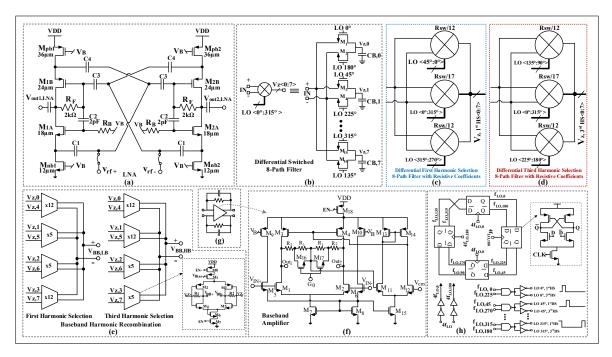

| Figure 4.5  | Transistor level implementation of the proposed receiver: (a) differential wideband LNA, (b) Differential switched 8-path filter, (c) differential first harmonic selection 8-path filter with resistive coefficients, (d) differential third harmonic selection 8-path filter with resistive coefficients, (e) first and third harmonic selection circuits for BB harmonic recombination, (f) BB amplifier, and (g) multi-phase LO generator |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

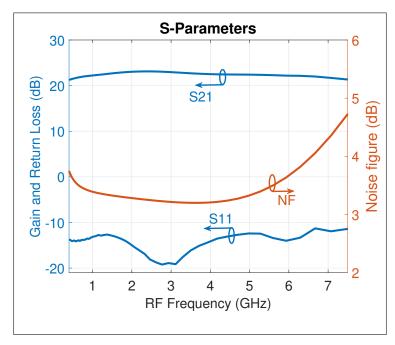

| Figure 4.6  | The LNA post-layout simulated gain (S21), return loss (S11) and NF                                                                                                                                                                                                                                                                                                                                                                            |

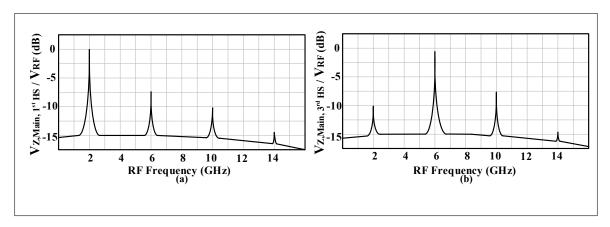

| Figure 4.7  | Frequency response of the (a) differential 1 <sup>st</sup> harmonic selection 8-path filter, and (b) differential 3 <sup>rd</sup> harmonic selection 8-path filter at a 2 GHz LO frequency                                                                                                                                                                                                                                                    |

| Figure 4.8  | The post-layout simulation of the output phase noise of the 8-phase LO signal generator as a function of the frequency offset                                                                                                                                                                                                                                                                                                                 |

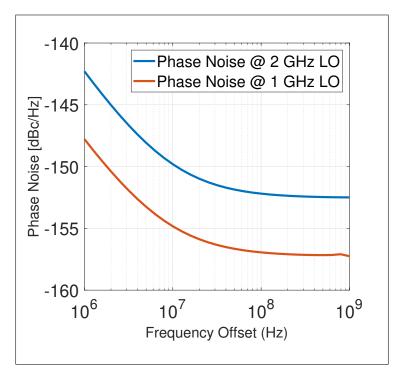

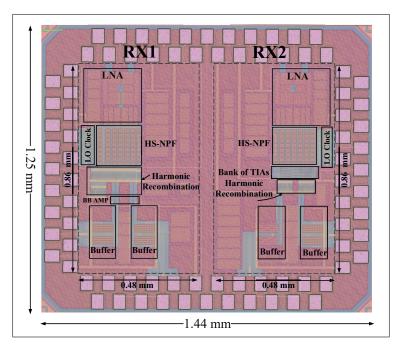

| Figure 4.9  | Chip micrograph of RX1 and RX2, occupying an active area of 0.88 mm × 1.085 mm in 65 nm CMOS                                                                                                                                                                                                                                                                                                                                                  |

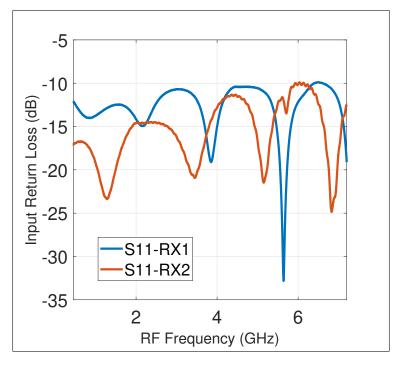

| Figure 4.10 | Measured input return loss (S11) of RX1 and RX2                                                                                                                                                                                                                                                                                                                                                                                               |

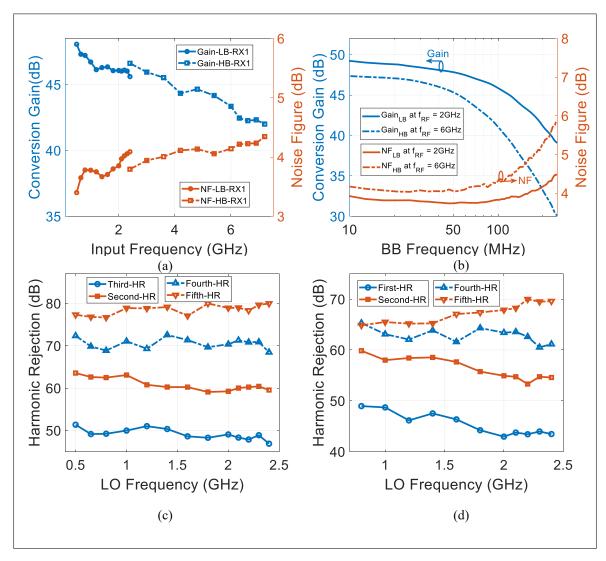

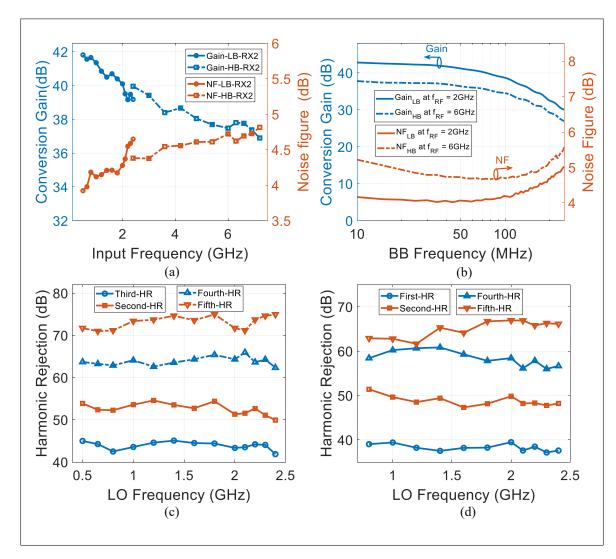

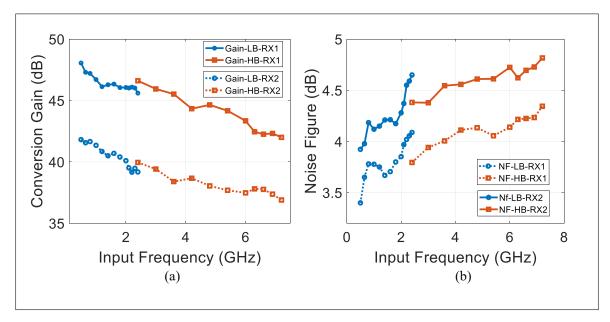

| Figure 4.11 | Measured performance of RX1 implemented in 65 nm CMOS                                                                                                                                                                                                                                                                                                                                                                                         |

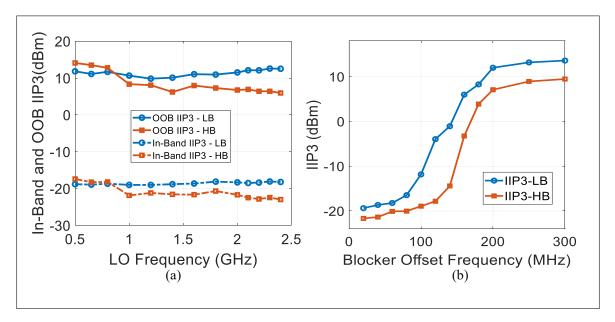

| Figure 4.12 | Measured RX1 (a) OOB and in-band IIP3 vs. LO frequency, and (b) IIP3 vs. blocker offset frequency                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.13 | Measured performance of RX2 implemented in 65 nm CMOS                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.14 | Measured RX2 (a) OOB and in-band IIP3 vs. LO frequency, and (b) IIP3 vs. blocker offset frequency                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.15 | Measured (a) conversion gain and (b) NF of RX1 and RX2 over both supported RF ranges                                                                                                                                                                                                                                                                                                                                                          |

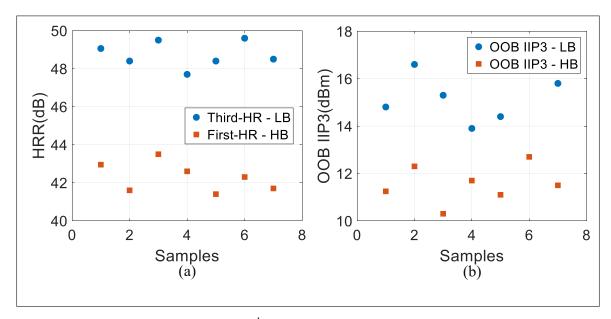

| Figure 4.16 | Measured (a) 3 <sup>rd</sup> and 1 <sup>st</sup> HRRs and (b) OOB IIP3 at the 2 GHz LO frequency over seven samples for the RX1                                                                                                                                                                                                                                                                                                               |

| Figure 4.17 | Measured (a) $3^{rd}$ and $1^{st}$ HRRs and (b) OOB IIP3 at the 2 GHz LO frequency over seven samples for the RX2                                                                                                                                                                                                                                                                                                                             |

| Figure 5.1  | Proposed reconfigurable multi-mode non-coherent IR-UWB receiver. Blocks used by each of the modes are outlined in different colors                                                                                                                                                                                                                                                                                                            |

| Figure 5.2  | Different operation bands of the reconfigurable IR-UWB receiver                                                                                                                                                              | 146 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

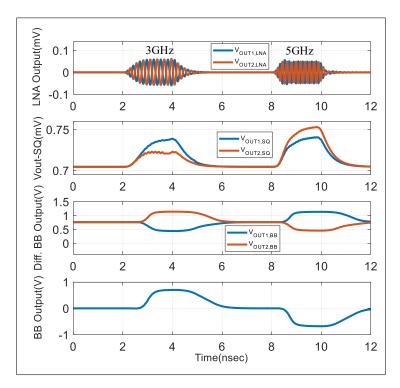

| Figure 5.3  | Transient post-layout simulation of the proposed receiver in the concurrent dual-band mode                                                                                                                                   | 149 |

| Figure 5.4  | Schematic of the reconfigurable fully-differential LNA                                                                                                                                                                       | 151 |

| Figure 5.5  | Schematic of the squarer circuit integrated with a LPF load                                                                                                                                                                  | 154 |

| Figure 5.6  | Schematic of the variable gain BB amplifier circuit                                                                                                                                                                          | 156 |

| Figure 5.7  | (a) Measurement setup used to characterize the proposed design, and (b) micrograph of the reconfigurable IR-UWB receiver frontend, occupying an active area of $1.2\mathrm{mm}\times0.8\mathrm{mm}$ in $130\mathrm{nm}$ CMOS | 158 |

| Figure 5.8  | Measured and post-layout simulation results of the LNA gain (S21), input return loss (S11) and NF                                                                                                                            | 158 |

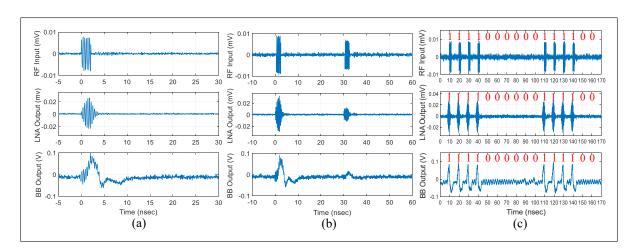

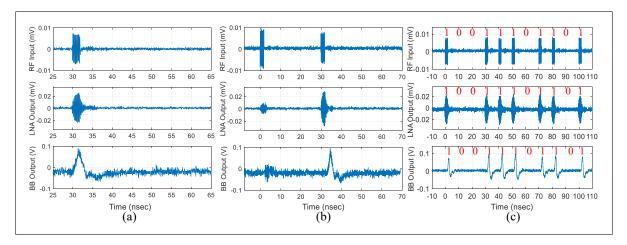

| Figure 5.9  | Measured operation of the IR-receiver operating in band-1 mode                                                                                                                                                               | 161 |

| Figure 5.10 | Measured operation of the IR-receiver operating in band-2 mode                                                                                                                                                               | 162 |

| Figure 5.11 | Measured waveforms of the IR-UWB receiver operating in the concurrent dual-band mode                                                                                                                                         | 163 |

| Figure 5.12 | The measured BER performance vs receiver input power in the concurrent dual-band mode                                                                                                                                        | 165 |

| Figure 5.13 | Power consumption breakdown in the (a) single-band modes and (b) concurrent dual-band mode                                                                                                                                   | 166 |

| Figure 5.14 | (a) Equivalent half-circuit of the proposed LNA, (b) the noise equivalent circuit of the first stage, and (c) the noise equivalent circuit of the second and third stages                                                    | 170 |

| Figure 6.1  | (a) 6-phase clock with $PW = T_s/8$ and $T_{delay} = T_s/6$ , and (b) LO harmonic of the 6-phase clocks                                                                                                                      | 180 |

#### LIST OF ABREVIATIONS

ADC Analog to Digital Converter

AWG Arbitrary Waveform Generator

BB Baseband

BER Bit Error Rate

BPF Band-Pass Filter

CCC Capacitive Cross Coupling

CCD Critical Current Detection

CG Common Gate

CS Common source

D-MPPM Digitalized Multi-pulse Position Modulation

FCC Federal Communications Commission

FSK Frequency Shift Keying

IIP3 Input Third Order Intercept Point

IM3 Third Order Intermodulation

IR Image Rejection

IoT Internet of Things

IR-UWB Impulse Radio Ultra Wide Band

HRM Harmonic-Rejection Mixer

HRR Harmonic Rejection Ratio

LNA Low Noise Amplifier

LO Local Oscillator

LVDS Low Voltage Differential Signaling

LPF Low Pass Filter

NF Noise Figure

OOB Out-Of-Band

OOK On-Off Keying

PCB Printed-Circuit-Board

PLL Phase-Locked Loop

PVD Peak Voltage Detector

PHY Physical Layer

PGA Programmable Gain Amplifier

PPM Pulse Position Modulation

PVT Process-Voltage-Temperature

RF AMP Radio Frequency Amplifier

SAW Surface-Acoustic-Wave

SRO Super Regenerative Oscillator

SRR Super Regenerative Receiver

TCA Transconductance Amplifier

TDC Time-to-Digital Converter

TIA Transimpedance Amplifier

VCO Voltage Controlled Oscillator

VNA Vector Network Analyzer

#### LIST OF SYMBOLS AND UNITS OF MEASUREMENTS

$\Omega \hspace{1cm} Ohm$

F Farad

Hz Hertz

m meter

Q Quality factor

s second

V Volt

W Watt

#### INTRODUCTION

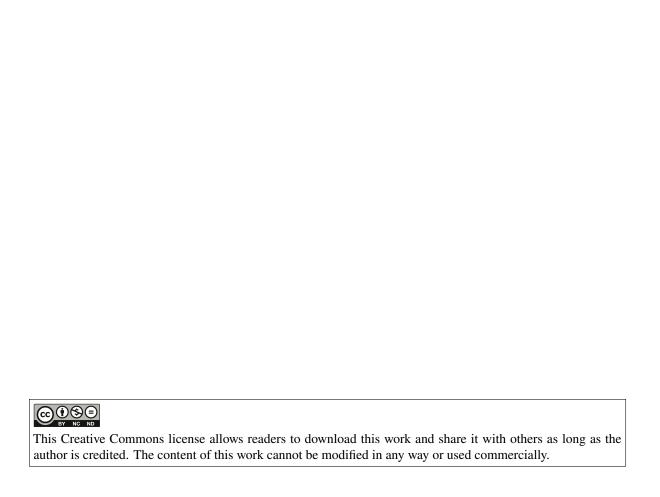

The 2020s belong to 5G radio, the fifth generation cellular radio standard, according to the ongoing trend of wireless mobile telecommunications technology that has evolved since the 1980s. It is expected that 5G will provide a various range of services from enhanced mobile broadband at multi-Gb/s, to the massive Internet of Things (IoT) revolution. That is why the new radio (NR) term was coined for 5G as it employs denser modulation schemes and pairs with current technologies to meet the ever-increasing demand for communication networks. A 5G system can support large bandwidth, wide connectivity, low latency, and support the IoT paradigm that has expended in recent years. The transition to 5G from LTE is much faster than the transition to 4G from 3G as technologies have rapidly advanced, (Fig. 0.1 illustrates this). All generations up to 4G are used below the 3 GHz frequency spectrum, while 5G is expected to support a wide spectrum range, ranging from low-bands from 0.45 –6 GHz and millimeter wave (mm-Wave) bands greater than 24 GHz.

Figure 0.1 Evolution of communication systems Extracted from Lin & Lee (2021); Sheikh & Babul (2020)

The sub-6 GHz and millimeter wave (mm-Wave) bands aim in part to solve spectrum congestion in 5G wireless systems that are low in cost, highly reliable, and compact (Lee, Han, Lee, Kang, Bae, Jang, Oh, Chang, Kang, Son et al. (2019b)). As the sub-6 GHz frequency band allows for power efficient and simpler designs to implement 5G systems, as opposed to the mm-Wave band, this puts a strain on developing the RF front-end designs that leverage new architectures to meet the 5G specifications within a wide band.

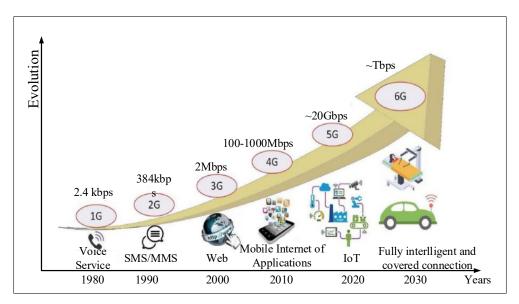

In addition to mobile telecommunications technology, Wi-Fi (IEEE 802.11 a/g/n/ac/ax) is the most common Internet access technology and has had considerable success in deploying IoT networks in outdoor and indoor environments during the last decade. This evolution has led to many different standards depicted in Fig. 0.2. Wi-Fi can operate on an unlicensed spectrum, as opposed to 5G. Despite achieving great success in mobile, business, research, daily usage, etc, the existing Wi-Fi standard does not provide enough network access performance for all IoT devices with different service requirements. Thus recently, the IEEE introduced a new task group, i.e., Wi-Fi 6 or IEEE 802.11ax, to investigate and realize next-generation Wi-Fi technologies for dense IoT networks' scenarios with large data traffic (Chen, Li, Balasubramaniam, Wu, Zhang & Wan (2020); López-Pérez, Garcia-Rodriguez, Galati-Giordano, Kasslin & Doppler (2019); Maldonado, Karstensen, Pocovi, Esswie, Rosa, Alanen, Kasslin & Kolding (2021)). In addition for the first time in several years, the FCC proposed several rules to provide more spectrum available for unlicensed usage in the 5.925 –7.125 GHz band (a.k.a. 6 GHz band). This spectrum was deemed suitable for Wi-Fi expansion because of its proximity to the existing Wi-Fi bands (2.4 GHz and 5 GHz). Moreover, this new opportunity offers wider channels that enable higher throught and latency properties for new Wi-Fi 6 (802.11ax standard). Moreover, it ensures that licensed services and devices operating in the band continue on thriving.

The introduction of the 5G NR standard has imposed several challenges in the sub-6GHz receivers' design. The maximum channel bandwidth increases to 100 MHz, while a -15 dBm

Figure 0.2 The evolution of Wi-Fi Standards Taken from Chauhan *et al.* (2021); Sun *et al.* (2014)

continuous-wave blocker can only be placed  $\Delta f = 85$  MHz away from the desired band edge. A small  $\frac{\Delta f}{BW}$  places a stringent linearity requirement on a receiver, thus demanding higher-order filtering. Moreover, a low noise figure is required to achieve the highest possible sensitivity and link budget, allowing to maximize data rates and range, along with spectral efficiency. In addition, since the desired band may contain many signals resulting from the digital beam-forming operation and carrier aggregation, in-band (IB) linearity also becomes critical.

Moreover, the demand for highly integrated receivers has driven the development of blocker-tolerant systems based on widely tunable filters. The recent CMOS receivers employ bulk acoustic wave (BAW) filters and high-Q surface acoustic wave (SAW) to suppress large out-of-band (OOB) blockers in a conventional narrow-band receiver design (Hasan, Gu & Liu (2016)). To cover different frequency bands, multiple BAW/SAW filters are necessary, which increases the form factor and cost. The RF filtering elimination is challenging because of the reciprocal mixing and gain compression. To reduce the size and cost of the transceiver, multiple narrow-band receivers can be replaced by a widely tunable receiver or wideband receiver. On the other

hand, a wideband receiver passes the desired signal and undesired blockers/OOB interference since it has no selectivity. The blockers might be placed very close to the desired frequency channels, thus it is difficult to maintain a high dynamic range in the presence of large blockers (Bu, Hameed & Pamarti (2020); Han & Kinget (2021); Murphy, Darabi & Xu (2015); Wu, Mikhemar, Murphy, Darabi & Chang (2015)). In addition, a 0-dBm blocker can clip the low noise amplifier (LNA) due to the low supply voltage in the modern CMOS process (e.g., 1 V). As a result, the wideband receiver, while sought after to simplify the radio system architecture, experiences high noise and distortion, leading to deteriorated performance. Therefore, the challenge lies in designing a wideband receiver architecture to improve its blocker-tolerance without sacrificing area and power consumption.

Accordingly, this dissertation attempts to provide some solutions for several of the problems described thus far by exploiting N-path switching filter based blocker tolerant wideband RF receiver front-ends to enhance resilience to undesired blockers and out of band (OOB) interference. The three different receiver front-end integrated circuits (ICs) demonstrated in this dissertation target sub-6 GHz applications that cover 5G, Wi-Fi and IR-UWB. The implemented RF wideband receivers employ fully-differential architectures that are able to tolerate harmonic local oscillator (LO) blockers without sacrificing noise performance and to alleviate the SAW pre-filters requirement while allowing for low-power LO clock generation.

Note that N-path switching filters used in the proposed RF wideband receivers are driven by an N-phase LO clock generator. As the number of paths, N, in the N-path switching filter and/or the operating frequency increases, the dynamic power consumption of the LO clock generation increases in a linear fashion. Since driving the switches of the 8-phase mixer beyond 3 GHz significantly increases the dynamic power consumption, even in smaller CMOS technologies, there is a need to design a receiver architecture to save the dynamic power by relaxing the requirements of the clock generator, phase-locked loop (PLL) and oscillator. Thus, this dissertation

also presents a more agile design through a differential reconfigurable multi-band non-coherent impulse radio ultra-wideband (IR-UWB) receiver. Since the proposed IR-UWB architecture employs a self-demodulating direct conversion RF front-end structure, it avoids using frequency translation blocks like a down-conversion mixer, a PLL and an oscillator. Among all techniques and architectures employed for multi-standard wireless systems, IR-UWB has gained much attention because of its potential for low power implementations. The use of IR-UWB technology in designing and implementing energy efficient RF receiver front-end for short range communications is another main subject of this dissertation.

#### Research objectives

This doctoral thesis aims to present the work carried out over the past five years. This work focuses on the design and characterization of wideband RF receiver structures for next generation radio, 6 GHz Wi-Fi and IR-UWB. This research will enable future RF and analog designers to have a better understanding of these RF receivers, and therefore to improve the performance of tomorrow's wideband RF front-ends. To achieve this objective and with the aim of building a complete receiver front-end, different sub-objectives have been identified, which are:

- establish clear and simple receiver design methods at the system and transistor levels,

- propose design methods or structures for wideband RF receivers supporting higher frequency RF inputs beyond 3 GHz, while consuming low LO power compared to the conventional architectures,

- propose design methods or structures that increase the performance of wideband receivers over the entire frequency band of operation,

- design an IR-UWB architecture supporting data modulated in binary frequency shift keying (FSK) in addition to on-off keying (OOK) modulation scheme, for enhanced robustness, and

propose design methods or structures providing robustness to process variations and mismatches.

The main contributions of the research work are as follows:

- 1. A new architecture for wideband RF receiver operating at third order harmonic of the switching frequency rather than the fundamental to reduce the input frequency and power consumption of the multi-phase clock generator by a factor of three

- A harmonic selective RF receiver to select a first and third harmonic of switching frequency and to efficiently suppress blockers at LO harmonics together with suppressing near-band blockers

- 3. A new filtering characteristic at the RF input node of the front-end by using differential first and third harmonic selection N-path filters (HS-NPF) to prevent the blockers from experiencing significant voltage gain

- 4. A new RF receiver structure exploiting a noise-canceling technique and  $1^{st}$  and  $3^{rd}$ order LO harmonic selection at low and high frequency bands, respectively

- 5. A multi-band IR-UWB non-coherent receiver that can be digitally reconfigured in different operating frequency modes. This receiver includes a self-demodulating direct conversion front-end architecture supporting an on-off keying (OOK) modulation scheme, in addition to data modulated in binary frequency shift keying (FSK) for enhanced robustness, and supporting ternary signaling

While the four different RF receiver front-ends presented in this thesis contribute key innovations towards greater front-end integration, they obviously provide only a small portion of the possible research areas in the broader space of wideband receivers.

#### **Thesis Organization**

This dissertation attempts to provide some solutions to several of the problems described, by building a reconfigurable dual-band non-coherent IR-UWB receiver, in addition to N-path filter based blocker tolerant inductor-less harmonic selection RF receiver front-ends. The four different RF receiver front-end ICs demonstrated in this dissertation target three different application thrusts: one front-end targeting sub-6 GHz 5G applications, two front-ends for sub-6 GHz 5G and 6 GHz Wi-Fi applications, and one targeting IR-UWB systems.

Chapter 1 presents a literature review of wideband receiver architectures. Its main objective is to give an overview of what a wideband RF receiver front-end is and to describe some of the recent reported structures: a wideband RF receiver using discrete-time analog filtering, a receiver using switching mixers, receivers based on N-path filtering, and IR-UWB receiver architectures including coherent and non-coherent architectures.

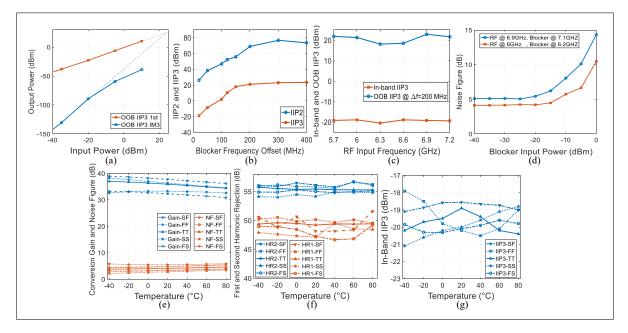

Chapter 2 presents the proposed RF front-end receiver configuration that allows for the selection of the third harmonic of the LO frequency, and that effectively suppresses other harmonics to reduce clocking power consumption at higher RF frequency bands of operation. Notably, the use of an N-path switching filter is mathematically analyzed to demonstrate how the harmonic recombination stage is reconfigured at the baseband to select the third harmonic of the LO switching frequency rather than the fundamental to reduce the input frequency and power consumption of the multi-phase clock generator by a factor of three. Moreover, the chapter further expands on three RF receiver front-ends using a 4-, 8-, and 16-path switching configuration and harmonic recombination at the baseband. Post-layout simulation results of these front-ends in TSMC 65 nm CMOS technology are used to fully expose the trade-offs of the proposed architecture. In addition, the simulated post-layout performance of the 4-, 8-, and 16-path third harmonic selection receivers is compared to a conventional architecture to provide a fair comparison to the performance metrics of the proposed architecture.

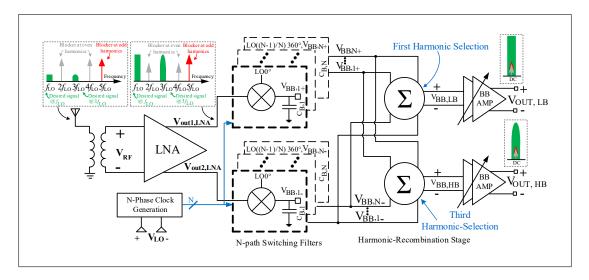

Chapter 3 presents the fabricated harmonic selection receiver front-end to support the 5G sub-6 GHz band. A 0.5-6 GHz harmonic selective RF receiver front-end exploiting wideband inductor-less LNA, 8-path switching filter and BB  $1^{st}$  and  $3^{rd}$  harmonic recombination blocks has been designed and verified in 130 nm TSMC CMOS technology. It is demonstrated how the baseband harmonic recombination stage can be reconfigured to select the first harmonic of the switching frequency at the low frequency band  $(0.5-1.9\,\text{GHz})$  and the third LO harmonic at the high frequency band  $(1.95-6\,\text{GHz})$ . Based on harmonic selectivity, the proposed wideband receiver achieves blocker tolerance and harmonic rejection while consuming substantially less power, compared to the existing architectures operating at such high frequencies.

Chapter 4 extends the work on the harmonic selection receiver of Chapter 3 by demonstrating two wideband harmonic selection noise-canceling (HS-NC) RF receiver front-ends for 5G and Wi-Fi 6. Two proposed RF receiver architectures employ two harmonic rejection N-path filters with resistive coefficients and frequency translational noise cancellation (FTNC) technique to enhance resilience to the harmonic LO blockers and to achieve low noise. Since driving the switches of the N-path switching system beyond 3 GHz increases the power consumption significantly, the proposed HS-NC architectures are configured to select the 1<sup>st</sup> and 3<sup>rd</sup>-order LO harmonic at the low frequency band (0.5 –2.4 GHz) and high frequency band (2.4 –7.2 GHz), respectively. An IC prototype of both front-ends is fabricated in TSMC 65 nm CMOS as a proof-of-concept and it is characterized. The front-ends, capable of operation from 0.5 –7.2 GHz, show a minimum in-band NF of 3.4 dB at a 80 MHz BB frequency.

Finally, Chapter 5 focuses on building an OOK and binary FSK reconfigurable dual-band non-coherent IR-UWB receiver supporting ternary signaling. It can be digitally reconfigured in different operating frequency modes, including two single-band modes and one concurrent dual-band mode. The proposed receiver employs a self-demodulating direct conversion RF front-end architecture with OOK modulation scheme. Moreover, the proposed reconfigurable receiver

architecture supports data modulated in binary FSK in addition to OOK for enhanced robustness. It also uniquely supports ternary signaling by combining both OOK and FSK modulations. The receiver was fabricated in TSMC 130 nm CMOS technology and is characterized. The proposed receiver has the capability of decoding the frequency information of the received pulse at a 100 Mbps data rate in OOK or binary FSK, or 150 Mbps by leveraging ternary signaling in the concurrent dual-band mode, hence improving power efficiency.

Finally, this manuscript ends with a conclusion covering the whole of this thesis and summarizes the key contributions of this dissertation. It also presents different avenues for future research to build on the work done in the course of this doctorate.

## **CHAPTER 1**

## LITERATURE REVIEW

This chapter presents a brief review of the work done by various researchers on wideband RF front-end architectures. The receivers have been analysed based on their performances, as well as the benefits and the drawbacks of using these receivers.

#### 1.1 Wideband RF Receiver Front-End Architectures

The narrow-band receiver front-ends invariably use external RF filtering to prevent the large OOB signals from corrupting the desired signal. Since RF filters are almost fixed, multiple receivers are required to support the large number of frequency bands serviced by a modern wireless devices. Compared to narrow-band receivers, wideband receivers that are tunable over the entire frequency band of interest can be employed. Wideband receivers offer great reconfigurability and flexibility. However, since there is no off-chip surface-acoustic-wave (SAW) filtering available, any blocker and interferer along with the desired signal can corrupt the reception. Thus, it has prevented the commercial adoption and wideband structures. To enable a wideband front-end into commercialization, one must improve its tolerance in the presence of blocker signals in order to be competitive with narrow-band receivers. Accordingly, there has been a growing interest in blocker-tolerant wideband receiver architectures without resulting in a significant increase in power consumption or occupied chip area (Murphy, Darabi, Abidi, Hafez, Mirzaei, Mikhemar & Chang (2012); Wu et al. (2015)).

# 1.1.1 Wideband RF receiver using discrete-time analog filtering

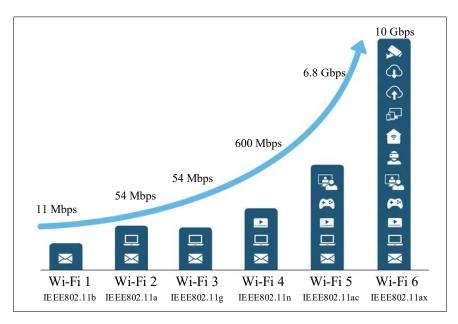

Typically, the RF signal can be down-converted to the IF or baseband by using either sampling or mixing. Based on sampling theory, down-conversion can be realized by sampling of an RF signal on a capacitor, as utilized in discrete-time approaches that employ switched-capacitor techniques (Fig. 1.1(a)) (Chen & Hashemi; Tohidian, Madadi & Staszewski (2014)). Down-conversion by using discrete-time mixers provides programmability in the center frequency of

the receiver, while the order of the filters and the bandwidth are controlled by selecting the number of charge sharing phases and proper down-sampling rate, respectively. In addition, there is a need for digital filtering and oversampling to reduce the gain at the harmonics. In the digital domain, high harmonic rejection is achieved by using a high sampling rate (Tohidian *et al.* (2014)). However, discrete-time approaches suffers from the limited linearity caused by the first sampling stage that usually is composed of an LNA.

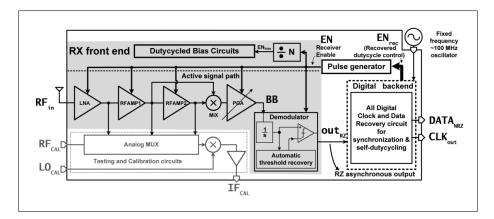

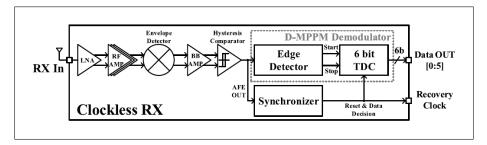

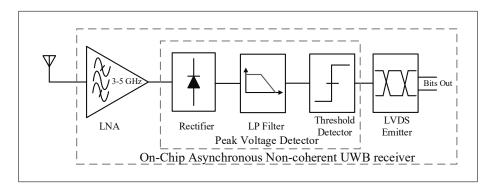

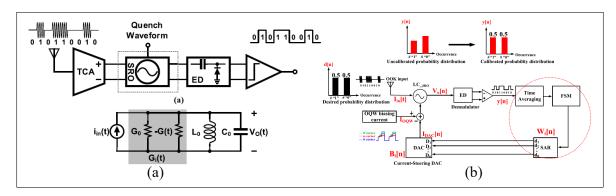

Figure 1.1 Prior art in receivers. (a) Discrete-time (DT) RF signal processing (taken from Chen & Hashemi), (b) receiver based on the N-path band path filters (taken from Darvishi *et al.* (2013a); Luo *et al.* (2016)), (c)receiver based on the notch filters, (d) Mixer-first architectures (taken from Andrews & Molnar (2010); Lin *et al.* (2014)), and (e) Noise cancellation structures (taken from Murphy *et al.* (2012))

## 1.1.2 Wideband RF receiver using switching mixers

RF signal down-conversion can also be realized by switching mixers (sampling mixers) that multiply the RF signal and a square-wave LO waveform. Since the LO waveform is not a pure sine-wave and contains undesired harmonics, mixing the RF signal with a square wave down-converts both the desired signal located around the LO frequency and the signals located around the LO harmonics. An RF band-selection filter mitigates this harmonic mixing in narrow-band receivers. An alternative approach is to employ harmonic-rejection mixers (HRM) in order

to cancel the need for a discrete IF filter and to limit spurious mixing in receivers. By providing frequency-synthesis, HRMs can be employed in broadband receivers such as proposed in Ho, Singh, Forbes & Gharpurey (2014); Singh, Forbes, Ho, Ko & Gharpurey (2014); Wu, Murphy & Darabi (2019).

The first harmonic-rejection principle proposed in Weldon, Narayanaswami, Rudell, Lin, Otsuka, Dedieu, Tee, Tsai, Lee & Gray (2001) used the gain coefficients at the RF part of the circuit, while the use of the harmonic-rejection coefficients at the baseband analog-domain was described in Molnar, Lu, Lanzisera, Cook & Pister (2004). The proposed HRM in Weldon *et al.* (2001) includes three parallel mixing paths with gain ratios of  $1:\sqrt{2}:1$ . Three weighted current outputs are summed to approximate a sine-wave LO that includes only the  $8m \pm 1$  harmonics of the fundamental frequency of  $f_{LO}$ , where m is an integer. In this fashion, the  $3^{rd}$  and  $5^{th}$  harmonics can be rejected. Higher harmonic rejection can be achieved by accurately implementing the desired weighting ratio  $1:\sqrt{2}$  on chip. Realizing an accurate ratio and handling the random variations because of circuit mismatches are two challenges of this approach.

To address these issues, an analog two-stage poly-phase harmonic rejection (HR) filter can be implemented on chip (Ru, Moseley, Klumperink & Nauta (2009)). Figure 1.2 shows wide-band receiver architecture proposed in Ru *et al.* (2009). For the differential transconductance LNA section, the receiver entails two off-chip inductors and one off-chip transformer. An 8-path passive mixer in current-driven mode is used for down-conversion (Figure 1.2(a)). The 8-phase 12.5 % duty cycle clock generation with a high phase accuracy (<0.07° at 0.8 GHz) is generated by using a divide-by-8 circuit. Transimpedance amplifiers (TIAs) realize the baseband (BB) low-pass filters (LPFs). This structure acts as a frequency-translated RF-to-BB LNA, with the frequency-translated BB-to-RF virtual ground, which absorbs both the out-band signal and in-of-band interferers. The channel selection and signal amplification are done at BB, thus resulting in high linearity. Although it offers higher HR, well above 60 dB, good out-of-band linearity (16 dBm) and robustness to mismatches, it features a moderate 1-dB compression point and higher power consumption (60 mW from 1.2 V at 0.9 GHz) due to the use of a 7 unit low noise transconductance amplifier in 3 parallel groups and two TIA stages.

Figure 1.2 (a) The proposed wideband receiver architecture using the two-stage poly-phase HR and the low-pass blocker filtering, and (b) harmonic recombination receiver architecture

Taken from Ru et al. (2009) and van Liempd et al. (2014), respectively

Another wideband receiver architecture is proposed in van Liempd *et al.* (2014), shown in Figure 1.2(b). This wideband RF receiver operates at up to 6 GHz. The receiver architecture is split into a low-band RF path (0.4 - 3 GHz) and a high-band RF path (3 - 6 GHz) using 8- and 4-phase passive mixers, respectively. It employs two differential LNAs followed by a 4-path and 8-path passive mixers and a set of BB gain stages  $(G_m)$  before applying the LPF and gain control. A low-pass RC input impedance is realized by using the power-efficient Gm-C circuitry instead of a virtual ground. A band-pass response at the output of the LNA is frequency translated to a low-pass response at BB. Thus, it suppresses the OBB blockers at RF. Since driving the switches of the 8-phase mixer beyond 3 GHz escalates power consumption significantly, even in 28 nm CMOS technology, conventional 4-phase passive mixers are used for high-band RF signals, precluding from many advantages. Noise figure and the OBB IIP3 of this topology are lower than 3 dB and +3 dBm, respectively, while consuming 35 mW from 0.9 V supply voltage.

# 1.1.3 Wideband RF receivers using N-path filtering

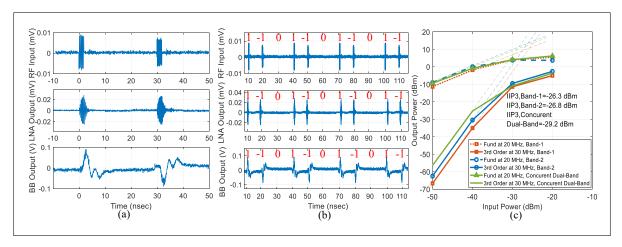

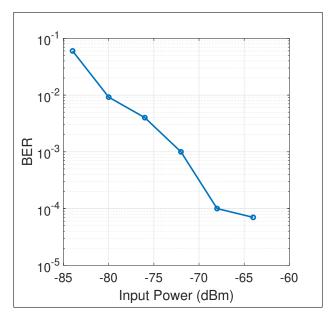

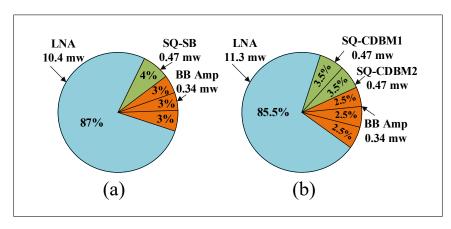

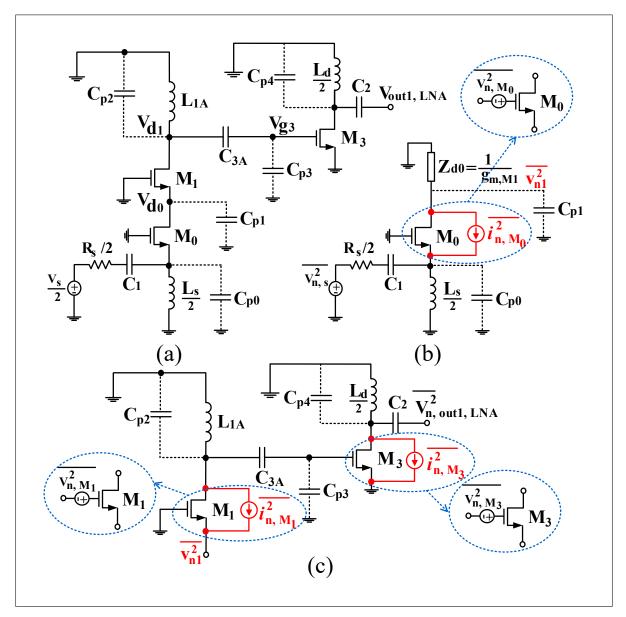

A promising solution is the impedance transformation that is realized in N-path switching systems that act as passive mixers, as these have no reverse isolation, unlike active mixers. The impedance transformation of a passive mixer can be used to synthesize on-chip high-Q bandpass filtering (BPF) by frequency-translating low-Q baseband impedances to the RF (see Fig. 1.1(b) and Fig. 1.1(c)) (Forbes, Ho & Gharpurey (2013); Lin *et al.* (2014); Xu, Zhu & Kinget (2017)). The center frequencies of the BPF impedances are tuned by the clock frequency, making them very attractive for tunable multi-standard receivers. As these switching systems are only composed of switches and capacitors, the resulting high-Q BPFs provide a high linearity. Moreover, there is no flicker noise issue since the BPF switches are not biased with a DC current (Mirzaei, Darabi & Murphy (2012)).