# GHz-range Characterization and Modeling of Power Integrity in SiP for an Array of Switch-Mode Converters

by

Gabriel NOBERT

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

# MONTREAL, APRIL 10TH, 2024

# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

#

This Creative Commons license allows readers to download this work and share it with others as long as the author is credited. The content of this work cannot be modified in any way or used commercially.

# **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED

# BY THE FOLLOWING BOARD OF EXAMINERS

M. Yves Blaquière, Thesis Supervisor Department of Electrical Engineering, ÉTS

M. Nicolas Constantin, Thesis Co-Supervisor Department of Electrical Engineering, ÉTS

M. Christian Belleau, Chair, Board of Examiners Department of Mechanical Engineering, ÉTS

M. Handy Fortin-Blanchette, Member of the Jury Department of Electrical Engineering, ÉTS

M. Boris Vaisband, External Independent Examiner Department of Electrical and Computer Engineering, McGill University

#### THIS THESIS WAS PRESENTED AND DEFENDED

#### IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

# ON MARCH 19TH, 2024

# AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

#### ACKNOWLEDGEMENTS

I want to thank my colleagues from the CPIOS project, without whom there wouldn't have been such a success within the entire team. Thank you to everyone who have contributed to that success: Abdul-Hafiz Alameh, Abdurrashid Shuaibu, Allan Riboullet, Hamid Sadrimanesh, Nam Ly, Nurahmed Omar, Reyhaneh Taherpour, Sudabeh Fotoohi, Tan Pham and Van-Ha Nguyen. I also want to thank the professors involved in the CPIOS project for their kind words and occasional support. You have made this project a success and we, the students, wouldn't have been as successful without you. Aside from my advisor and co-advisor, I would like to specifically thank professors Frédéric Nabki and Glenn Cowan.

J'aimerais remercier chaque personne ayant rendu la rédaction de cette thèse possible. Il y a une quantité inombrable de gens qui ont eu un impact de près ou de loin sur mes travaux et je vous dis tous sincèrement: merci. Plus spécifiquement, merci au laboratoire LACIME et à Normand Gravel, qui a su m'aiguiller dans l'utilisation des équipements nécessaires et me donner de précieux conseils techniques qui m'ont permis de mener à bien mes mesures. Merci également à Mathieu Gratuze: non seulement pour son support immense d'un point de vue technique et en design de banc de mesures, mais également pour avoir été un ami durant toute la durée de mon doctorat. Merci pour toutes les discussions, techniques ou non. Merci à mes anciens et présents collègues du LACIME que j'appelle aujourd'hui mes amis: David Berthiaume, Smarjeet Sharma, Ilshat Shagitov, et encore une fois, Tan Pham et Mathieu Gratuze. Vous avez rendu mon temps à l'ÉTS plus agréable et pour cela, je vous en remercie. Merci aux techniciens du département de Génie Électrique. Plus spécifiquement merci à André Zalzal, Rigoberto Avelar, Jorge Rojas Abad et Youssef Bekbouti pour leur support et leur aide dans mes différentes fabrications et assemblages qui étaient nécessaires à ma recherche. Finalement, je dois remercier mon directeur ainsi que co-directeur: les professeurs Yves Blaquière et Nicolas Constantin. Vos précieux conseils, techniques et en matière de recherche, ont fait de moi un meilleur chercheur et un meilleur concepteur. Je vous serai toujours reconnaissant pour la chance que vous m'avez donnée de compléter un doctorat sous votre supervision.

# Caractérisation et modélisation à plusieurs GHz de l'intégrité de la puissance dans un SiP pour une matrice de convertisseurs à commutation

# Gabriel NOBERT

# RÉSUMÉ

La tendance à la miniaturisation s'est répandue dans une grande variété de circuits. Dans cette perspective, il est nécessaire d'intégrer de manière plus compacte des circuits électroniques de puissance et des convertisseurs à commutation (switch-mode converter). Conséquemment, le concept de Configurable Power Input and Output System (CPIOS) fut introduit dans le cadre de cette recherche. Ce système intègre sur un même substrat une matrice de convertisseurs à commutation, des circuits analogiques sensibles pour la commande et des capteurs. De nouveaux défis en intégrité de la puissance surgissent alors. En effet, l'activité de commutation du convertisseur génère du bruit sur les rails d'alimentation du CPIOS, affectant du même coup les performances des circuits sensibles. Il est nécessaire de prédire les fluctuations de tension générées par la commutation simultannée des convertisseurs, en termes d'amplitude crête, de forme temporelle et de densité spectrale de puissance, sur ces circuits plus sensibles afin d'évaluer la dégradation des performances. Il y a également un besoin de modèle d'intégrité de la puissance (power integrity) qui prédit la forme des fluctuations de tension sur les circuits sensibles dans une matrice de convertisseurs commutant simultanément. De plus, plusieurs convertisseurs peuvent commuter simultanément dans le CPIOS, augmentant la complexité de la prédiction de ce bruit. La caractérisation du courant est également importante pour évaluer l'intégrité de la puissance, car c'est le principal mécanisme de génération de bruit. Par conséquent, il existe également un besoin pour une technique de mesure de courant intégrée avec des provisions minimales pour les mesures et une bande passa4nte supérieure comparativement aux techniques proposées dans la litérature.

L'objectif principal de cette recherche est de modéliser les contraintes d'intégrité de la puissance dans le CPIOS en fonction des différentes conditions de fonctionnement et d'une caractérisation du système. Le premier objectif spécifique est de caractériser le courant de commutation dans les convertisseurs de puissance pour le CPIOS, qui est crucial pour prédire l'intégrité de l'énergie avec une large bande passante. Pour ce faire, une technique de mesure de courant basée sur une ligne de transmission au secondaire d'une structure inductive est proposée. Une analyse du comportement de la structure montre que sa distorsion de mesure (measurement distortion) peut être prédite jusqu'à plusieurs GHz et que le point de mesure peut être placé à n'importe quel endroit pratique sur le substrat sans affecter la distorsion de mesure. Les mesures avec la structure proposée, validées avec la technique connue de résistance série, montrent que le courant dans un convertisseur à commutation peut être caractérisé jusqu'à 1,95 GHz avec une distorsion de mesure inférieure à 3 dB. Ces résultats représentent une amélioration par rapport à l'état de l'art en termes de fréquence et de facilité d'intégration de la technique de mesure de courant. Le deuxième objectif spécifique est de prédire les fluctuations sur les rails d'alimentation des circuits sensibles, en termes de forme temporelle et de densité spectrale de puissance. Ainsi, un modèle pour l'intégrité de la puissance et pour prédire les fluctuations de tension pendant

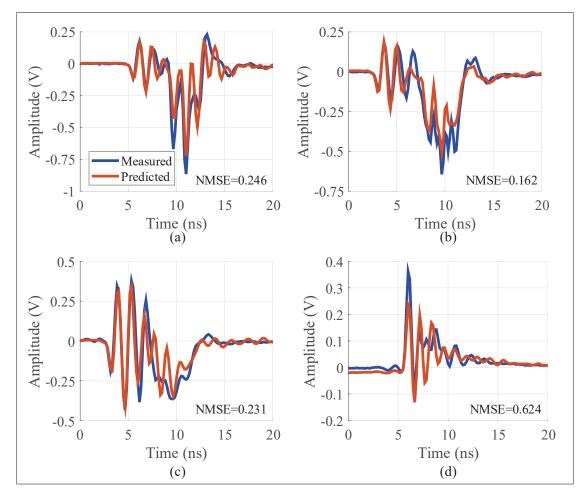

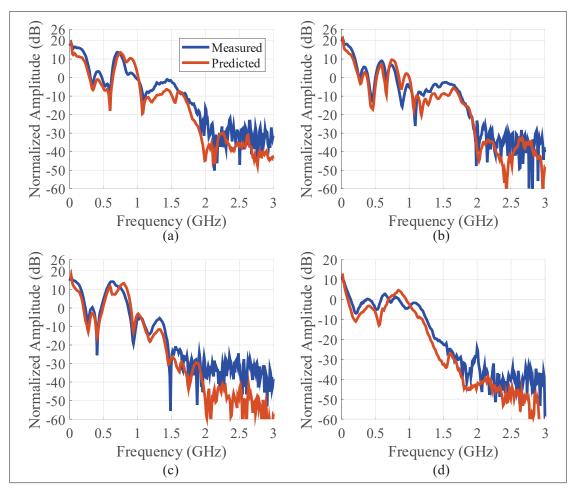

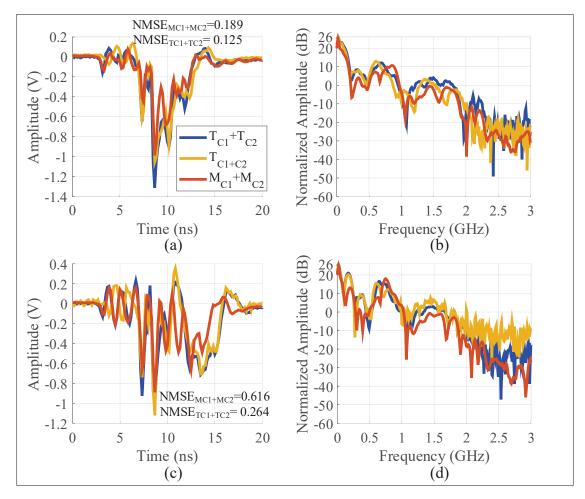

la commutation simultanée des convertisseurs sur les rails d'alimentation est présenté. Pour chaque condition mesurée, une précision meilleure que 10 dB est obtenue entre 0 et 2 GHz, en comparant un signal de référence mesuré et les prédictions, lorsque les fluctuations causées par un ou plusieurs convertisseurs sont mesurées. En termes de forme temporelle, l'erreur quadratique moyenne normalisée par la variance (NMSE) est dans le pire des cas de 0,624 et, dans de nombreuses conditions, meilleure que 0,25. Ce modèle est le premier en son genre à prédire jusqu'à plusieurs GHz l'intégrité de la puissance dans le contexte des convertisseurs de puissance.

**Mots-clés:** Convertisseur à Commutation, Intégrité de la Puissance, SiP, Système-dans-unboîtier

# GHz-range Characterization and Modeling of Power Integrity in SiP for an Array of Switch-Mode Converters

#### Gabriel NOBERT

#### ABSTRACT

The trend of miniaturization has been spread to a vast variety of circuits. Among those, there is a need to integrate in a more compact way power electronic circuits and switch-mode converters. Accordingly, the concept of Configurable Power Input and Output System (CPIOS) is introduced. Such a system integrates into the same compact substrate switch-mode converters, sensitive analog circuits for control and readback together. That type of system brings new challenges in terms of power integrity. Indeed, the switching activity from the switch-mode converters generate noise onto the power rails of the CPIOS, thereby impeding the performances of the more sensitive circuits. There is a need to predict voltage fluctuations generated by the switching activity of one or multiple converters switching simultaneously onto those more sensitive circuits, in terms of shape, peak amplitude and power spectral density, in order to assess the degradation of the performances. Moreover, multiple converters may switch simultaneously in CPIOS, increasing the complexity of predicting that noise. Furthermore, the characterization of the current is equally important in order to assess power integrity due to it being the main noise generation mechanism. Therefore, there is also a need for embedded current measurement technique with minimal required on-board provisions and a bandwidth better than available from the state-of-the-art techniques.

The main objective of this research is to model power integrity constraints in CPIOS based on the different operating conditions and a thorough characterization of the system. The first specific objective is to characterize the switching currents in power converters for the CPIOS, which are critical for predicting power integrity with high bandwidth. Accordingly, a transmission-linebased current measurement technique is proposed. A thorough analytical formulation of the behavior of the structure shows that its measurement distortion can be predicted at up to multiple GHz and that the probing pad can be placed at any convenient location on the substrate without affecting measurement distortion. Measurements with the transmission-line-based structure validated with the well-known resistive shunt technique show that the current in a switch-mode converter can be characterized at up to 1.95 GHz with less than 3 dB measurement distortion. Such results are an improvement over the state of the art in terms of frequency, compactness and ease of implementation of the embedded technique. The second specific objective is to predict fluctuations onto the power rails of sensitive circuits, in terms of shape and energy spectrum. For that purpose, a model for power integrity and voltage fluctuations during simultaneous switching of the converters on power rails is presented. For every condition validated, accuracy better than 10 dB is obtained between 0 and 2 GHz by comparing a measured reference signal and predictions when the fluctuations caused by a single or multiple converters are measured. In terms of overall shape, the variance-normalized mean squared error (NMSE) in the worst case is of 0.624 and under numerous conditions better than 0.25. This model is the first of its kind to predict power integrity in the context of power converters at up to multiple GHz.

Keywords: Switch-Mode Converter, Power Integrity, SiP, System-in-Package

# TABLE OF CONTENTS

| INTRODUCTION                                       |                                                                       |                                                                |  |

|----------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|--|

| 0.1                                                | Context and motivation for this work: Configurable Power Input/Output |                                                                |  |

|                                                    | System (CPIOS)                                                        |                                                                |  |

| 0.2                                                | The cha                                                               | Ilenge of Power Integrity in CPIOS    3                        |  |

|                                                    | 0.2.1                                                                 | Modeling Power Integrity in CPIOS 3                            |  |

|                                                    | 0.2.2                                                                 | GHz-range Current Measurement technique for CPIOS              |  |

| 0.3                                                | Researc                                                               | h Objectives                                                   |  |

| 0.4                                                | Key Co                                                                | ntributions to State-of-the-Art 7                              |  |

| 0.5                                                | Organiz                                                               | ation of the Thesis                                            |  |

| CHAPTER 1 LITERATURE REVIEW: GHZ-RANGE FREQUENCIES |                                                                       |                                                                |  |

| 01111                                              |                                                                       | POWER INTEGRITY ASSESSMENT AND CURRENT MEA-                    |  |

|                                                    |                                                                       | SUREMENT TECHNIQUES                                            |  |

| 1.1                                                | Hioh-Fr                                                               | equency Current Measurement Techniques                         |  |

|                                                    | 1.1.1                                                                 | Resistive Shunt Sensing and its Limitations                    |  |

|                                                    | 1.1.1                                                                 | 1.1.1.1SMD Shunt Resistors10                                   |  |

|                                                    |                                                                       | 1.1.1.2Coaxial Shunt Resistors12                               |  |

|                                                    | 1.1.2                                                                 | Inductor-Based Techniques                                      |  |

|                                                    | 1.1.2                                                                 | 1.1.2.1       Current Transformers       14                    |  |

|                                                    |                                                                       | 1.1.2.2         Rogowski Coils         15                      |  |

|                                                    |                                                                       | 1.1.2.3         Pickup Coils         15                        |  |

|                                                    |                                                                       | 1.1.2.4Current Surface Probe Sensing16                         |  |

|                                                    | 1.1.3                                                                 | Limitations in Hall-Effect Sensors                             |  |

|                                                    | 1.1.4                                                                 | Conclusion on Current Measurement Techniques                   |  |

| 1.2                                                |                                                                       | ues for Power Integrity Assessment in System-in-Package        |  |

|                                                    |                                                                       | Simultaneous Switching Noise and Power Distribution Network in |  |

|                                                    |                                                                       | Digital Systems                                                |  |

|                                                    |                                                                       | 1.2.1.1 Similarities of SSN in Digital Systems With Switch-    |  |

|                                                    |                                                                       | Mode Converters                                                |  |

|                                                    |                                                                       | 1.2.1.2 SSN Port-Based Models                                  |  |

|                                                    |                                                                       | 1.2.1.3 IBIS Models and Other Macromodels for Power Integrity  |  |

|                                                    |                                                                       | Predictions                                                    |  |

|                                                    | 1.2.2                                                                 | Conducted EMI in Switch-Mode Converters                        |  |

|                                                    |                                                                       | 1.2.2.1 General Terminal Modeling                              |  |

|                                                    | 1.2.3                                                                 | Conclusion on Power Integrity Assessment Techniques            |  |

| CHAP                                               | TED 2                                                                 | POWER INTEGRITY CONSTRAINTS IN CPIOS                           |  |

| СПАР<br>2.1                                        |                                                                       | Level Summary of CPIOS                                         |  |

| 2.1                                                |                                                                       |                                                                |  |

| 2.2                                                | 0                                                                     |                                                                |  |

| 2.3 Power Integrity Constraints in CPIOS           |                                                                       |                                                                |  |

|           | 2.3.1    | GaN HEMT Devices for CPIOS                                           | 38 |  |  |

|-----------|----------|----------------------------------------------------------------------|----|--|--|

|           | 2.3.2    | GHz-range DM current and noise in switch-mode converters for         |    |  |  |

|           |          | SiP integration                                                      | 38 |  |  |

|           | 2.3.3    | The problem of simultaneous switching in an array of switch-mode     |    |  |  |

|           |          | converters for SiP integration                                       | 41 |  |  |

| 2.4       | Detaile  | d objectives                                                         | 44 |  |  |

| CILA      |          |                                                                      |    |  |  |

| CHAPTER 3 |          | A COUPLED TRANSMISSION-LINE-BASED MEASURE-                           |    |  |  |

|           |          | MENT TECHNIQUE FOR CURRENTS IN SWITCH-MODE                           | 47 |  |  |

| 2 1       |          | CONVERTERS                                                           |    |  |  |

| 3.1       |          |                                                                      |    |  |  |

|           | 3.1.1    | Case Example: Resistive Shunt Sensing                                |    |  |  |

| 2.2       | The Dee  | 3.1.1.1 Another Case Example: Inductive Sensing                      |    |  |  |

| 3.2       |          | posed Transmission-Line-Based Technique                              | 51 |  |  |

|           | 3.2.1    | Distributed-Circuit Analysis of the Transmission-Line-Based Tech-    | 50 |  |  |

|           | 2 2 2 2  | nique                                                                |    |  |  |

|           | 3.2.2    | Main Takeaways of the Analysis                                       | 56 |  |  |

|           | 3.2.3    | Electromagnetic Simulations of the Transmission-Line-Based Tech-     | 50 |  |  |

| 2.2       | Europein | nique                                                                |    |  |  |

| 3.3       | 1        | Experimental Apparatus for Current Measurement Techniques in Switch- |    |  |  |

|           |          | Converters<br>Dimensions of the Transmission-Line-Based Technique    |    |  |  |

|           | 3.3.1    | -                                                                    |    |  |  |

|           | 3.3.2    | Use of a Damping Resistor for Increased Accuracy                     |    |  |  |

|           | 3.3.3    | Ferrite Bead for Ideal Current Source Behavior                       |    |  |  |

|           | 3.3.4    | Resistive Shunt Sensing for Validation                               | 65 |  |  |

|           | 3.3.5    | Measurement Setups for the Characterization of the Current Mea-      |    |  |  |

|           |          | surement Structures                                                  | 66 |  |  |

|           |          | 3.3.5.1 Measurement Distortion Characterization and Z-               |    |  |  |

|           | 226      | Parameters Transformation                                            |    |  |  |

| 2.4       | 3.3.6    | Time-Domain Current Measurement Setup                                |    |  |  |

| 3.4       |          | rement Results for the Transmission-Line-Based Technique             |    |  |  |

|           | 3.4.1    | Characterization of Measurement Distortion and Self-Impedance        |    |  |  |

|           | 3.4.2    | Measurement of Currents in a Switch-Mode Converter                   |    |  |  |

|           | 3.4.3    | Limitations and Drawbacks                                            |    |  |  |

|           |          | 3.4.3.1 Imprecision of Measurements in Narrow Bandwidths             |    |  |  |

|           |          | 3.4.3.2 Simulation of Added Parasitics in the Structure              |    |  |  |

|           |          | 3.4.3.3 Layout Limitations                                           |    |  |  |

| ~ -       | 3.4.4    | Comparison With the State-of-the-Art                                 |    |  |  |

| 3.5       | Conclu   | sion                                                                 | 80 |  |  |

| СНА       | PTER 4   | GHZ-RANGE MODELING OF POWER INTEGRITY IN AN                          |    |  |  |

|           |          | ARRAY OF SIMULTANEOUSLY SWITCHING POWER CON-                         |    |  |  |

|           |          | VERTERS                                                              | 83 |  |  |

| 4.1       | Concer   | ot of the Proposed Model for Power Integrity Assessment              |    |  |  |

| 4.1       | Concer   | n of the I toposed whotel for I ower fillegilty Assessificilit       | 03 |  |  |

XIII

|        | 4.1.1   | Mathematical Formulation of the proposed Model                |     |

|--------|---------|---------------------------------------------------------------|-----|

|        | 4.1.2   | The Hypothesis of an LTI System                               | 88  |

|        |         | 4.1.2.1 Linearity of Switch-Mode Converters                   |     |

|        | 4.1.3   | The One-Port Assumption Under Simultaneous Switching Condi-   |     |

|        |         | tions                                                         |     |

|        | 4.1.4   | General Methodology for the Characterization of the Model     |     |

| 4.2    | Experim | ental Apparatus for the Validation of the Model               |     |

|        | 4.2.1   | Experimental Design                                           |     |

|        | 4.2.2   | Frequency-Domain Measurement Setup                            |     |

|        | 4.2.3   | Design of the Current Measurement Setup                       |     |

|        |         | 4.2.3.1 Windowing Function                                    |     |

|        |         | 4.2.3.2 Sampling Rate                                         |     |

|        | 4.2.4   | Time-Domain Switching Fluctuations for Model Validation Setup |     |

|        | 4.2.5   | Simultaneous Switching Characterization Setup                 | 101 |

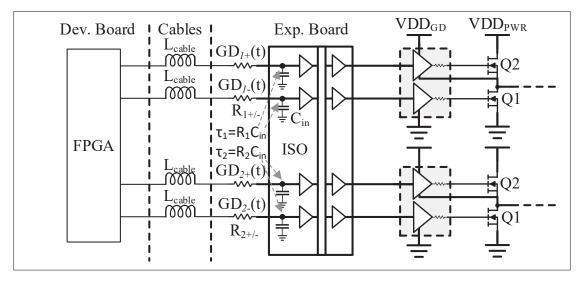

|        |         | 4.2.5.1 Quasi-Simultaneous Switching Delays Generation and    |     |

|        |         | Characterization                                              | 101 |

| 4.3    | Measure | ement Results for Predictions of Voltage Fluctuations         |     |

|        | 4.3.1   | Metric for the Prediction of Voltage Fluctuations: NMSE       | 103 |

|        | 4.3.2   | Conditions for Fluctuation Predictions                        | 104 |

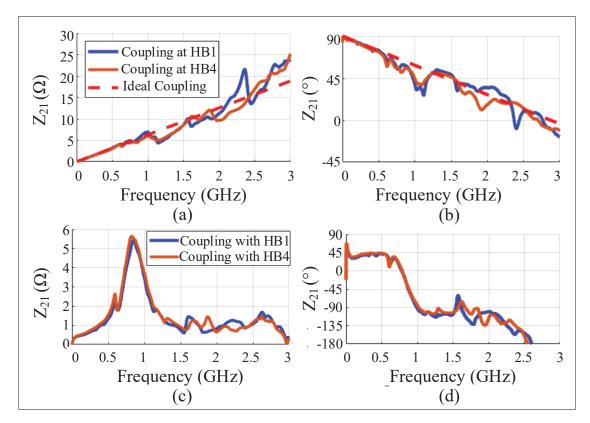

|        | 4.3.3   | Coupling Characterization of the System                       | 105 |

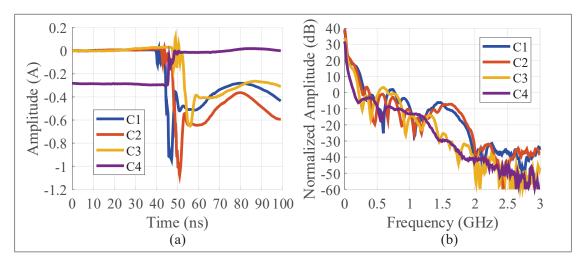

|        | 4.3.4   | Characterized Currents for Different Conditions               | 106 |

|        | 4.3.5   | Single Transient Fluctuation Predictions                      | 106 |

|        | 4.3.6   | Simultaneous Switching and LTI Hypothesis Revisited           |     |

|        |         | 4.3.6.1 Characterization of Delays for Simultaneous Switching | 109 |

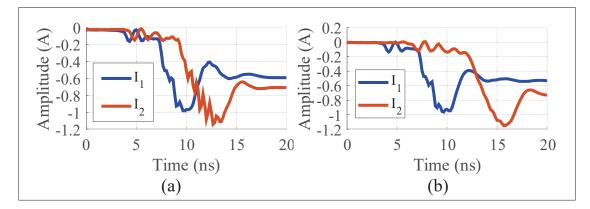

|        |         | 4.3.6.2 Measurement Results for Simultaneous Switching        | 110 |

| 4.4    | Conclus | ion                                                           | 110 |

| ~~~~   |         |                                                               |     |

| CONC   | LUSION  | AND RECOMMENDATIONS                                           | 115 |

| APPE   | NDIX I  | TEST BOARD DESIGN FOR GHZ-RANGE CHARACTERIZA-                 |     |

|        |         | TION OF CURRENT AND VOLTAGE FLUCTUATIONS                      | 123 |

|        |         |                                                               |     |

| LIST ( | OF REFE | RENCES                                                        | 143 |

# LIST OF TABLES

Page

| Table 1.1 | Summary of techniques for switching current measurement                                                        | 19  |

|-----------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 1.2 | Summary of models for power integrity assessment                                                               | 31  |

| Table 3.1 | Design parameters used for electromagnetic (EM) simulations of the current measurement structure in Figure 3.3 | 60  |

| Table 3.2 | Comparison with Previous Works                                                                                 | 80  |

| Table 4.1 | Testing configurations for single transient fluctuation predictions                                            | 104 |

| Table 5.1 | List of publications1                                                                                          | 120 |

# LIST OF FIGURES

|             | Page                                                                                             | e |

|-------------|--------------------------------------------------------------------------------------------------|---|

| Figure 0.1  | System-Level depiction of a safety-critical system                                               | 1 |

| Figure 0.2  | Problem of Power Integrity in CPIOS                                                              | 3 |

| Figure 1.1  | Two-Port Model of shunt resistor and pickup coil                                                 | С |

| Figure 1.2  | Shunt resistor network viewed from side, top and bottom                                          | 1 |

| Figure 1.3  | LR Compensation network for high bandwidth current shunt sensing 12                              | 2 |

| Figure 1.4  | Classical structure of coaxial shunt resistors                                                   | 3 |

| Figure 1.5  | Structure of the integrated Rogowski coil on PCB                                                 | 5 |

| Figure 1.6  | Simultaneous Switching Noise in Digital Systems                                                  | 1 |

| Figure 1.7  | SSN in Digital Systems                                                                           | 2 |

| Figure 1.8  | Switching Current in converters                                                                  | 3 |

| Figure 1.9  | Physics-based modeling                                                                           | 4 |

| Figure 1.10 | Improved model with PDN for IBIS                                                                 | 8 |

| Figure 1.11 | Conducted EMI in Power Electronics vs. PI in digital systems and CPIOS                           | 9 |

| Figure 2.1  | System-Level depiction of the CPIOS system                                                       | 4 |

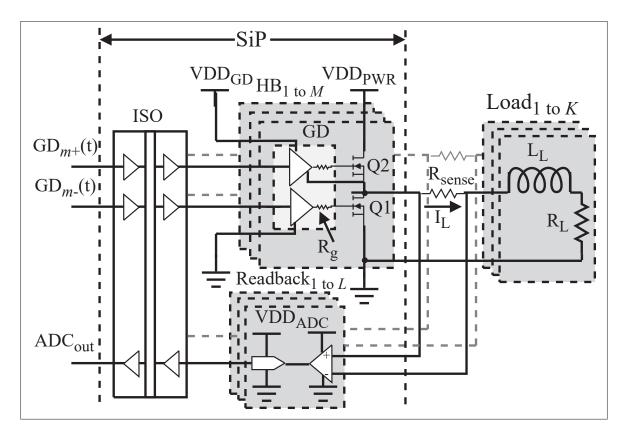

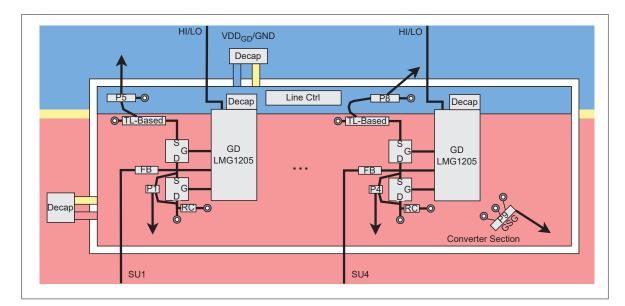

| Figure 2.2  | Array of <i>M</i> independent half-bridges (HB) in an SiP of configurable switch-mode converters | 5 |

| Figure 2.3  | 3D integration of the CPIOS                                                                      | 7 |

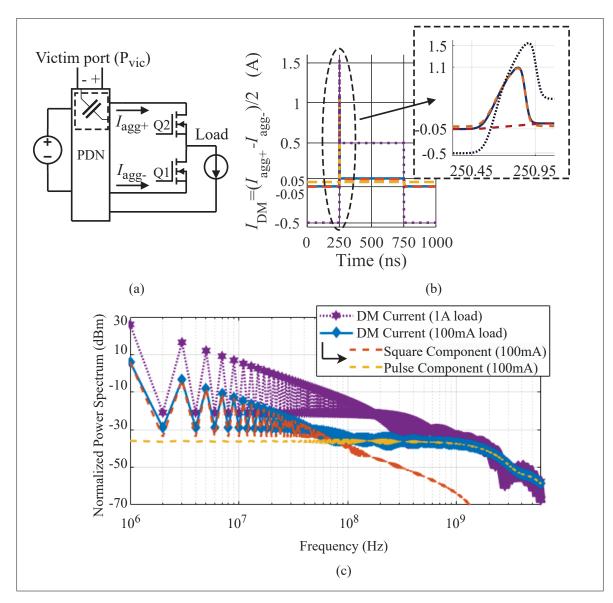

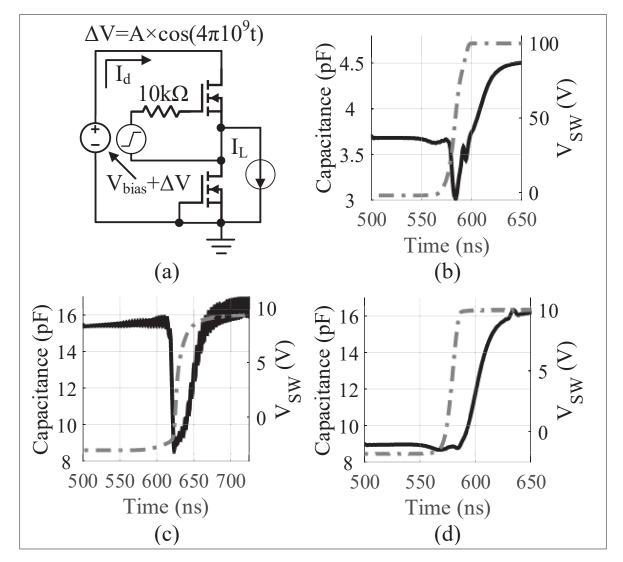

| Figure 2.4  | DM currents at GHz range in a GaN HEMT-based switch-mode converter                               | 0 |

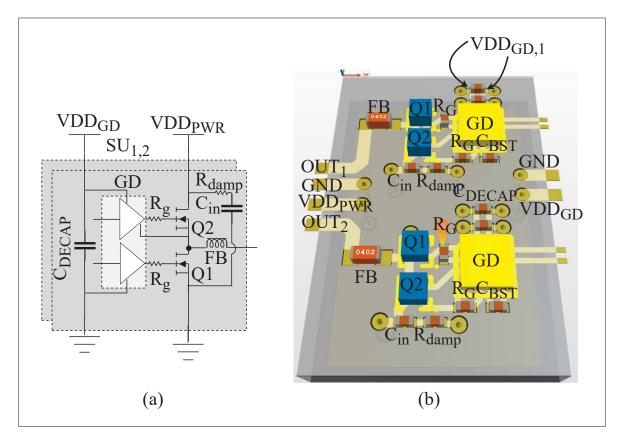

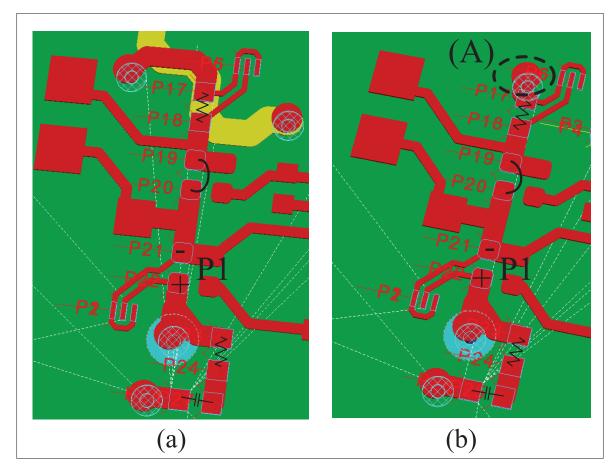

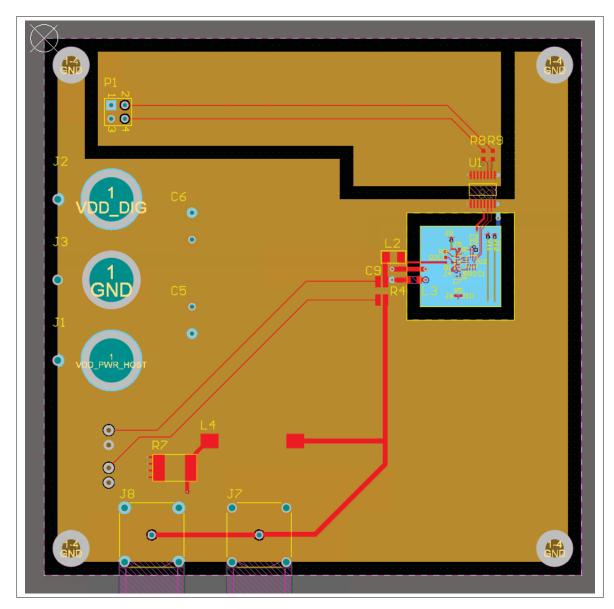

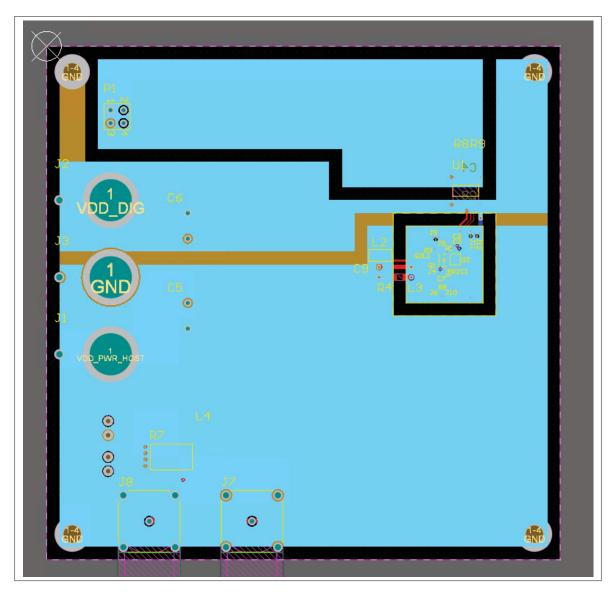

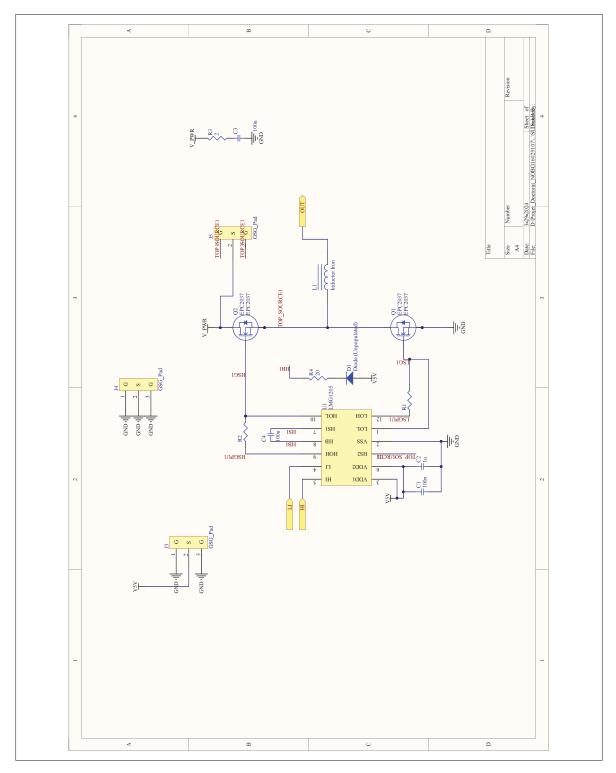

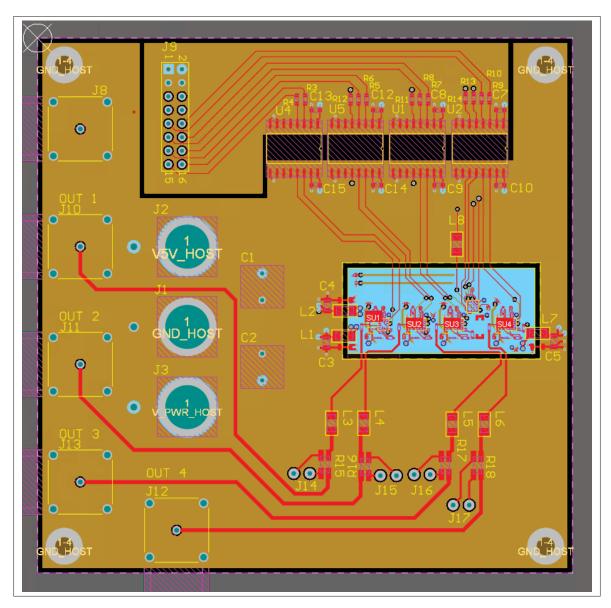

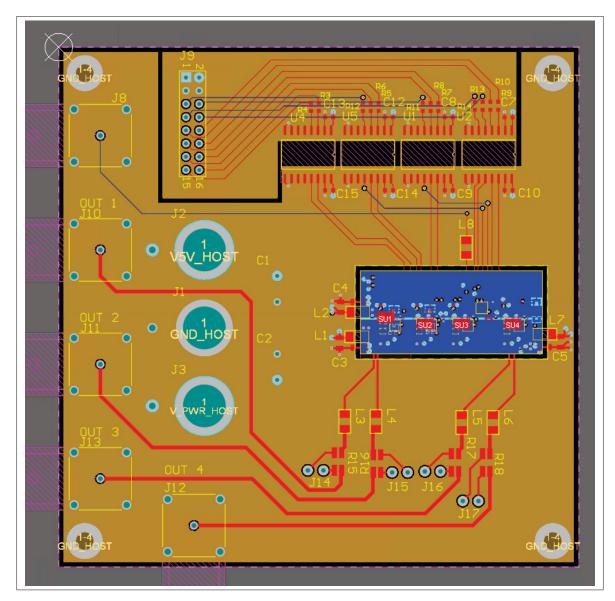

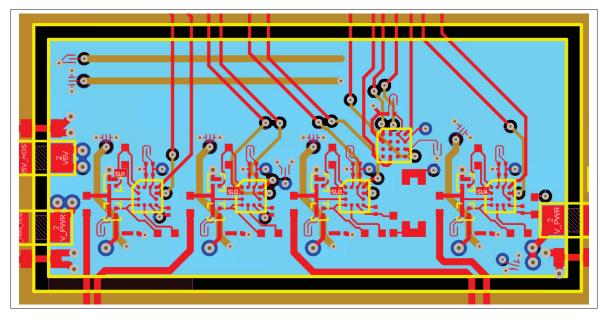

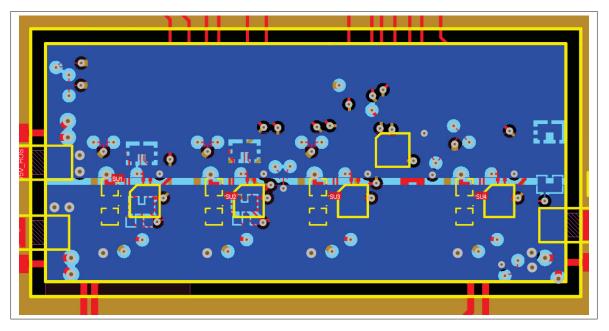

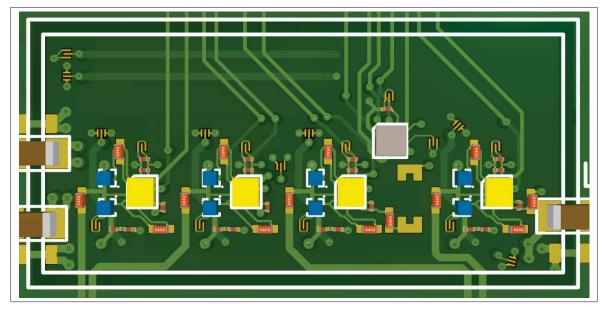

| Figure 2.5  | Board layout of an array of two switching units and its schematic                                | 2 |

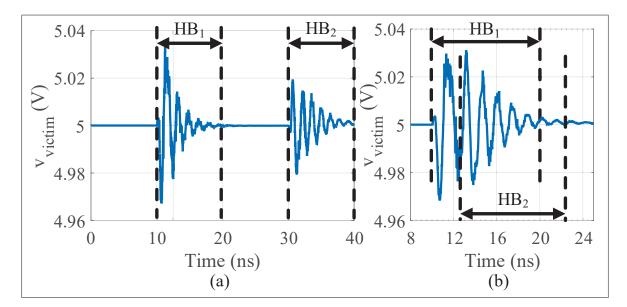

| Figure 2.6  | Simulated noise on the gate driver supply rails when two units are switching                     | 3 |

| Figure 3.1  | Need for current Measurement                                                                     | 7 |

# XVIII

| Figure 3.2  | Two-Port Model of shunt resistor and pickup coil                                                                             |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

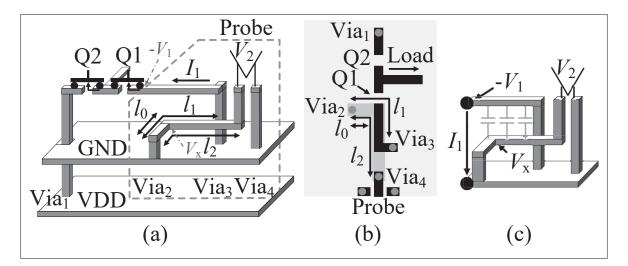

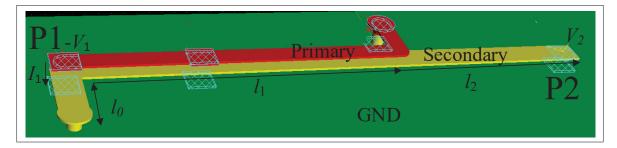

| Figure 3.3  | Simplified views of the transmission-line-based structure in a switch-<br>mode converter                                     |

| Figure 3.4  | Equivalent circuit of the structure in Figure 3.3(c)                                                                         |

| Figure 3.5  | Simulated structure for the validation of the analysis                                                                       |

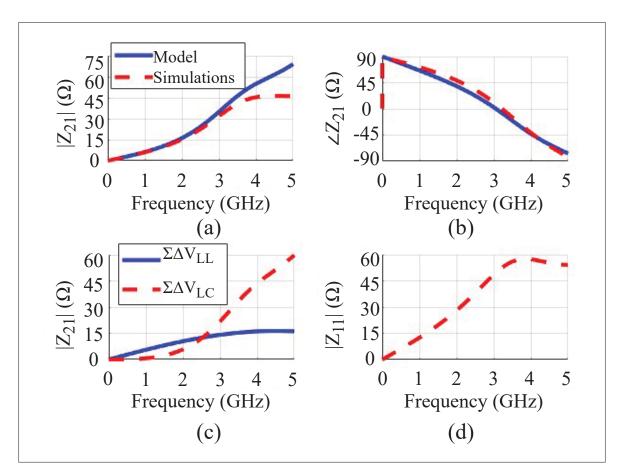

| Figure 3.6  | EM simulation results compared with the analytical                                                                           |

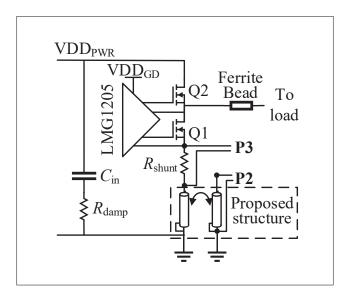

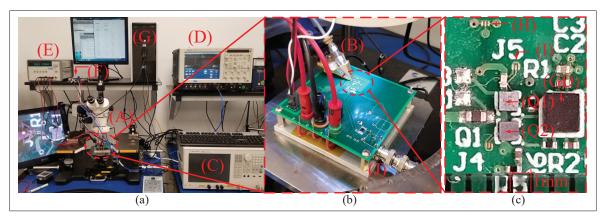

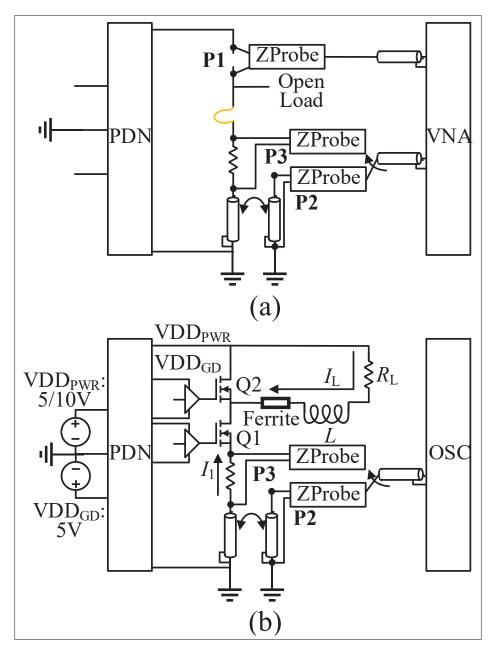

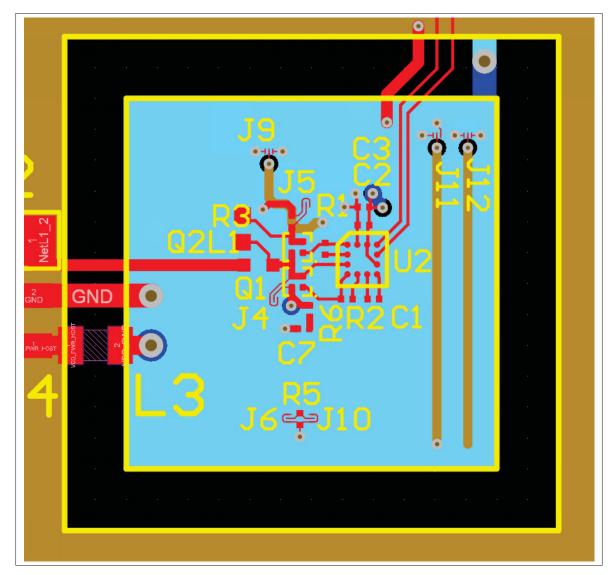

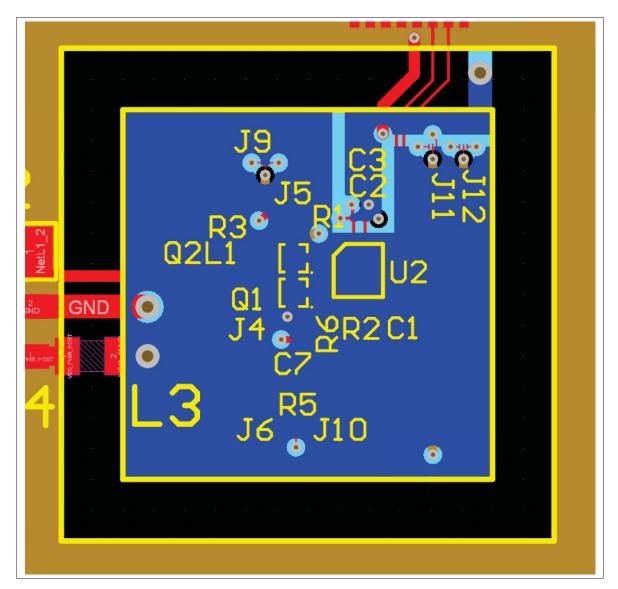

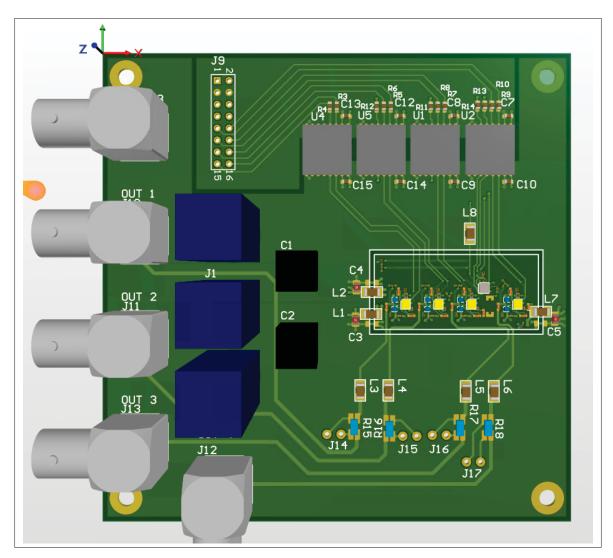

| Figure 3.7  | Switch-mode converter circuit and transmission-line-based structure implemented on the printed circuit board (PCB) prototype |

| Figure 3.8  | Measurement apparatus for time-domain measurements                                                                           |

| Figure 3.9  | Effect of Damping Resistor on Power Loop Self-Impedance                                                                      |

| Figure 3.10 | Block diagrams of measurement apparatus on the circuit in Figure 3.7 67                                                      |

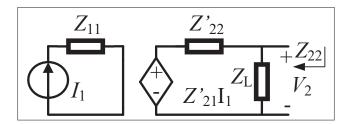

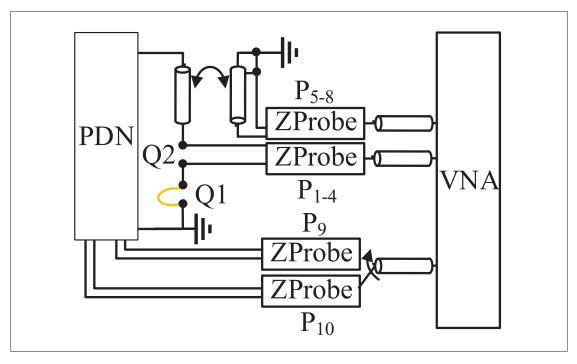

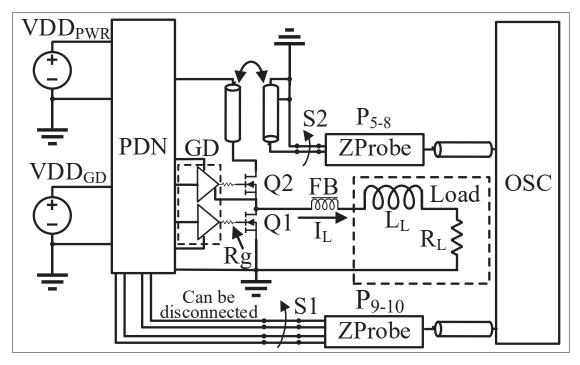

| Figure 3.11 | Equivalent loaded circuit from the computed two-port Z-parameters 69                                                         |

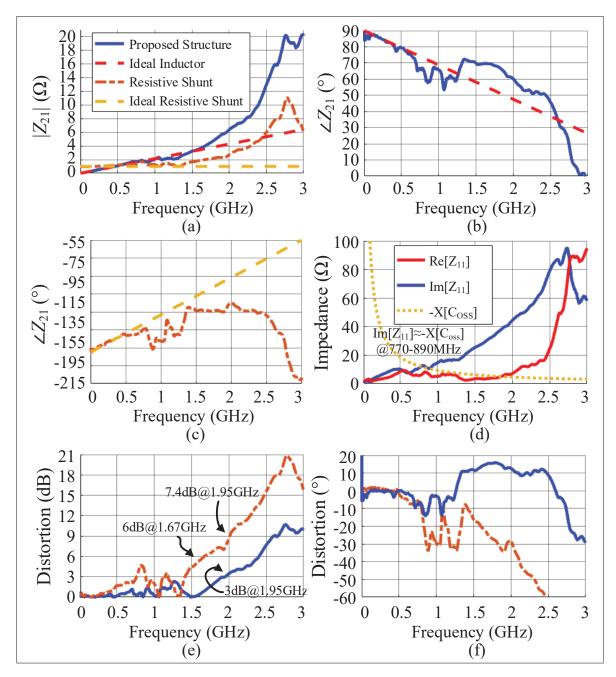

| Figure 3.12 | Transimpedance $Z_{21}$ measurement results for the shunt resistor and transmission-line-based structures                    |

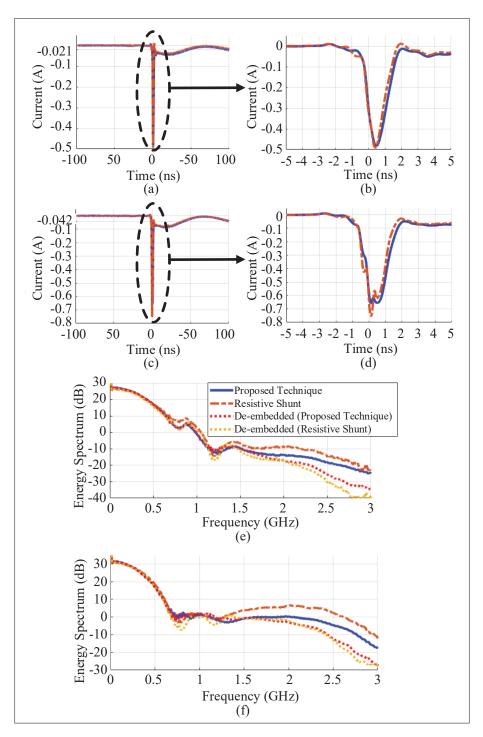

| Figure 3.13 | Switching currents in time along with their energy spectra                                                                   |

| Figure 3.14 | Simulation setup for insertion inductance                                                                                    |

| Figure 4.1  | Array of <i>M</i> independent half-bridges (HB) in an SiP of configurable switch-mode converters                             |

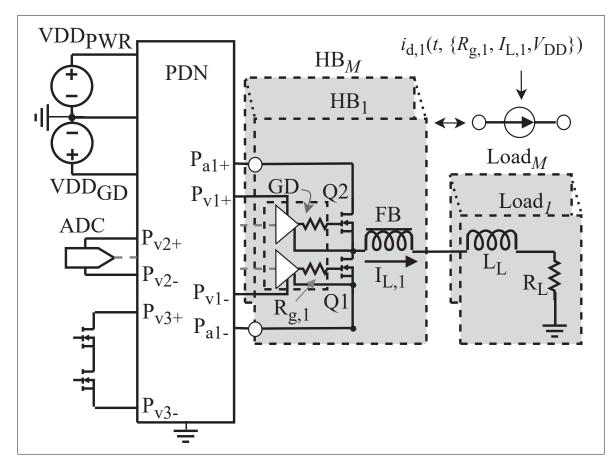

| Figure 4.2  | Physical representation of the model                                                                                         |

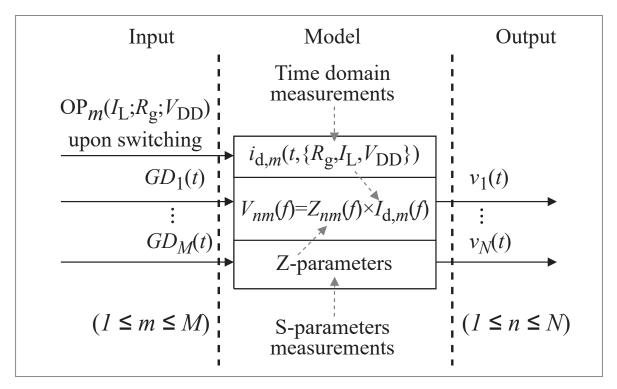

| Figure 4.3  | High-level diagram of the model                                                                                              |

| Figure 4.4  | Simulation of the capacitance seen from the power rails in a converter 91                                                    |

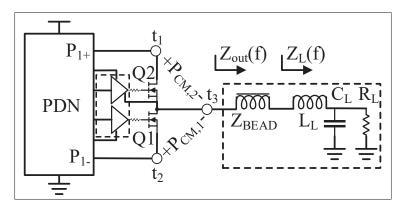

| Figure 4.5  | Three-port representation of a half-bridge with an LC filter as the load 93                                                  |

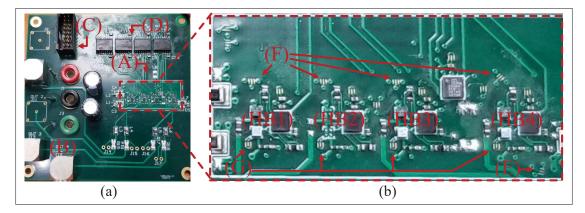

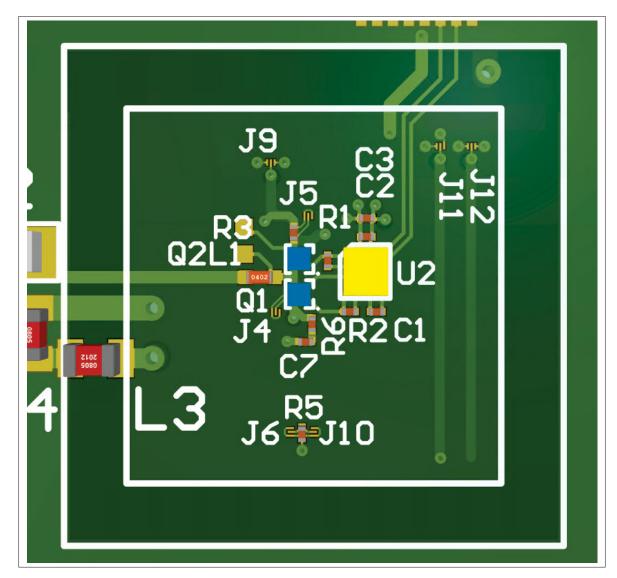

| Figure 4.6  | Board prototype used for model validation                                                                                    |

| Figure 4.7  | Measurement setup for frequency-domain characterization                                                                      |

| Figure 4.8  | Frequency-domain characterization setup for each individual switching half-bridge                                            |

| Figure 4.9  | Current and noise measurement setup for each individual switching half-bridge                        | 99    |

|-------------|------------------------------------------------------------------------------------------------------|-------|

| Figure 4.10 | Setup for simultaneous and quasi-simultaneous switching                                              | .102  |

| Figure 4.11 | Coupling onto current measurement structure and victim node                                          | .105  |

| Figure 4.12 | Measured switching currents for configurations C1 to C4                                              | .106  |

| Figure 4.13 | Prediction of fluctuations caused by switching under configurations<br>C1 to C4                      | . 107 |

| Figure 4.14 | Energy spectra of fluctuations caused by switching under configurations C1 to C4                     | .108  |

| Figure 4.15 | Characterized delays between quasi-simultaneous switching events                                     | .109  |

| Figure 4.16 | Predictions of fluctuations on the power rails under simultaneous switching and their energy spectra | .111  |

# LIST OF ABBREVIATIONS

| AC    | Alternating Current                     |

|-------|-----------------------------------------|

| ADC   | Analog-to-Digital Converters            |

| BNC   | Bayonet Neill-Concelman                 |

| BTL   | Bridge-Tied Load                        |

| ССМ   | Continuous Conduction Mode              |

| CGD   | Configurable Gate Driver                |

| СМ    | Common-Mode                             |

| CMOS  | Complementary Metal-Oxide-Semiconductor |

| CPIOS | Configurable Power Input/Output System  |

| CSP   | Current Surface Probes                  |

| CSR   | Coaxial Shunt Resistors                 |

| DC    | Direct Current                          |

| DM    | Differential-Mode                       |

| DFT   | Discrete Fourier Transform              |

| DPT   | Double-Pulse Test                       |

| DUT   | Device Under Test                       |

| EM    | ElectroMagnetic                         |

| EMC   | ElectroMagnetic Compatibility           |

| EMI   | ElectroMagnetic Interference            |

# XXII

| ENOB     | Effective Number Of Bits                          |

|----------|---------------------------------------------------|

| ÉTS      | École de Technologie Supérieure                   |

| FET      | Field-Effect Transistor                           |

| FPGA     | Field-Programmable Gate Array                     |

| GaN HEMT | Gallium Nitride High-Electron Mobility Transistor |

| GTM      | General Terminal Modeling                         |

| GSG      | Ground-Signal-Ground                              |

| IBIS     | Input/output Buffer Information Specification     |

| IC       | Integrated Circuits                               |

| LTCC     | Low-Temperature Co-fired Ceramics                 |

| LISN     | Line Impedance Stabilization Network              |

| LTI      | Linear Time-Invariant                             |

| MEMS     | MicroElectroMechanical Switch                     |

| MOSFET   | Metal Oxide Silicon Field-Effect Transistor       |

| NMOS     | N-type Metal-Oxide-Semiconductor                  |

| NMSE     | Variance-Normalized Mean-Squared Error            |

| PCB      | Printed Circuit Board                             |

| PDN      | Power Distribution Network                        |

| PEEC     | Partial Element Equivalent Circuit                |

| PI       | Power Integrity                                   |

- PMOS P-type Metal-Oxide-Semiconductor

- PPP Plane-Pair PEEC

- PWM Pulse-Width Modulation

- RF RadioFrequency

- RMS Root Mean Square

- SI Signal Integrity

- SiC Silicon Carbide

- SiP System-in-Package

- SMD Surface-Mount Device

- SOIC Small-Outline Integrated Circuit

- SOLT Short-Open-Load-Through

- SPICE Simulation Program with Integrated Circuit Emphasis

- SSN Simultaneous Switching Noise

- THD Total Harmonic Distortion

- TLM Transmission-line-matrix

- VNA Vector Network Analyzer

- WBG Wide-Band-Gap

# LIST OF SYMBOLS AND UNITS OF MEASUREMENTS

| А   | Ampere                 |

|-----|------------------------|

| dec | Decade (of frequency)  |

| dB  | Decibel                |

| 0   | Degree                 |

| F   | Farad                  |

| Н   | Henry                  |

| Hz  | Hertz                  |

| m   | Meter                  |

| %   | Percent                |

| Ω   | Ohm                    |

| rad | Radian                 |

| S   | Second                 |

| mil | Thousandths of an inch |

| V   | Volt                   |

#### **INTRODUCTION**

# 0.1 Context and motivation for this work: Configurable Power Input/Output System (CPIOS)

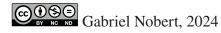

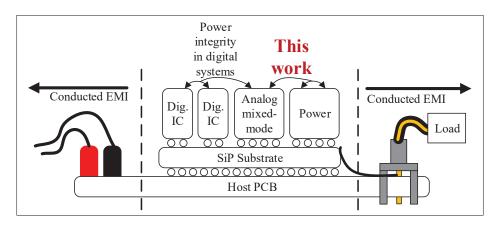

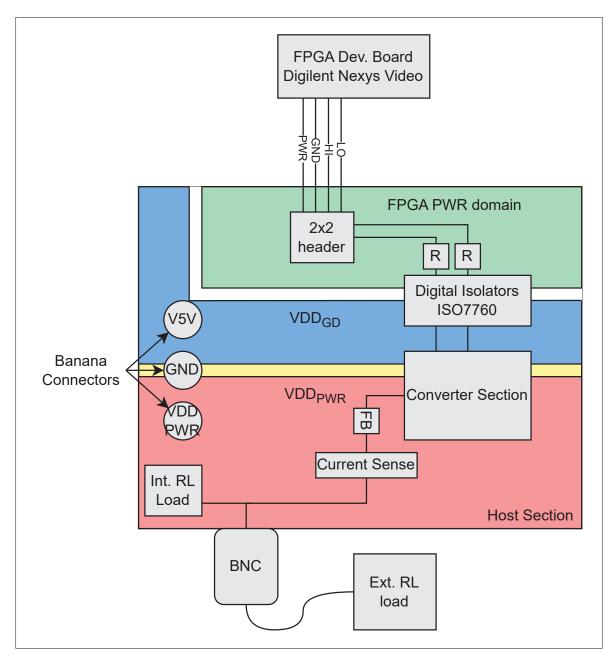

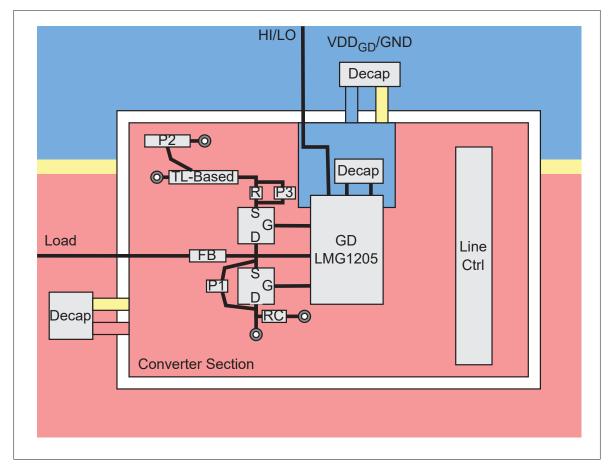

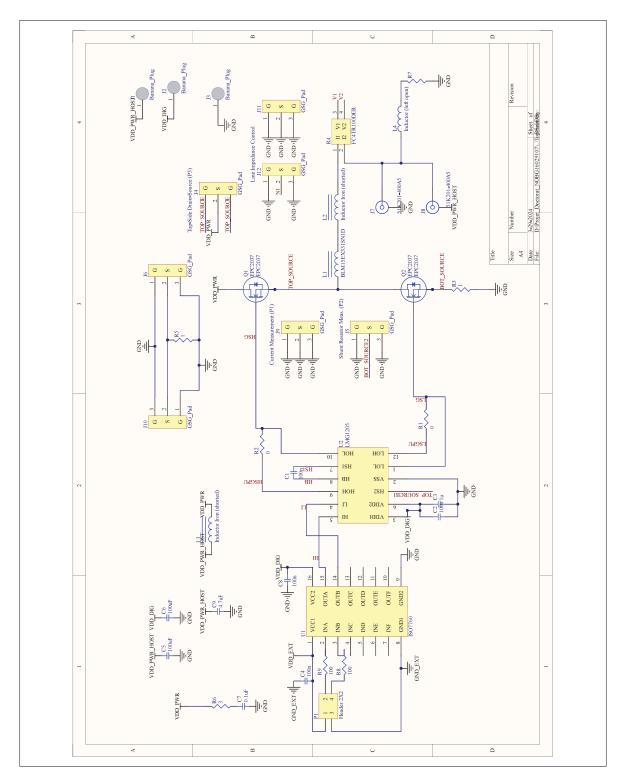

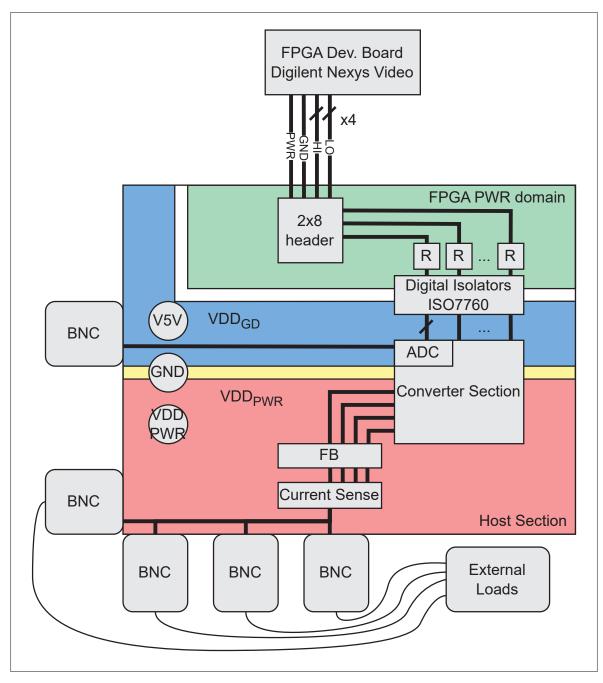

In safety-critical automotive, avionic and even in industrial applications, highly reliable electronic systems are used in the control of independent and critical loads, such as high- and low-voltage sensors and actuators. Those sensors and actuators have several requirements in terms of functionality, reliability, configurability and redundancy. For the control of sensors and actuators, not only is the power stage important, but also the read-out circuits. It is important to integrate flexible and accurate read-out in the form of analog-to-digital converters (ADC) and signal conditioning circuits for, as an example, either closed-loop operations of the actuators or conversion of analog signals from the sensors to digital signals in decision-making processes. Those control and decision-making processes are typically taken care of by a digital system such as a field-programmable gate array (FPGA) or microcontroller. That digital system needs to be protected from the high-power domain of the different loads and sensors typically through digital isolators. Such a safety-critical system, with the main blocks described above, is depicted in Figure 0.1.

Figure 0.1 System-Level depiction of a safety-critical system

In those applications, reliability is of the utmost importance because human safety is at play. In addition, there is a need to control a variety of loads that range from servo-electric motors and electromechanical systems to driving and reading active sensors, among others. It is therefore practical, in such systems, to have a level of configurability that allows the independent switching converters and amplifiers to be used in a wide range of applications. Finally, due to the need for reliability, redundancy is also important. In addition, adding more converters within a small area helps reduce the size and weight of the overall system. These systems commonly employ electronic modules that are assembled on PCBs for the implementation of switching converter-based power stages with discrete power devices and readback stages using ADC.

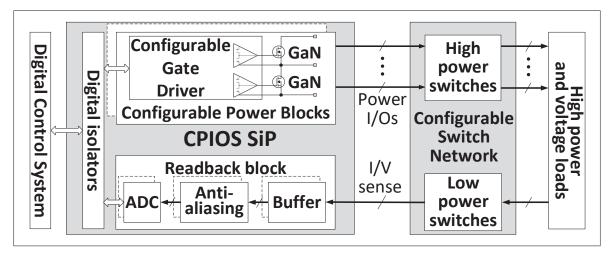

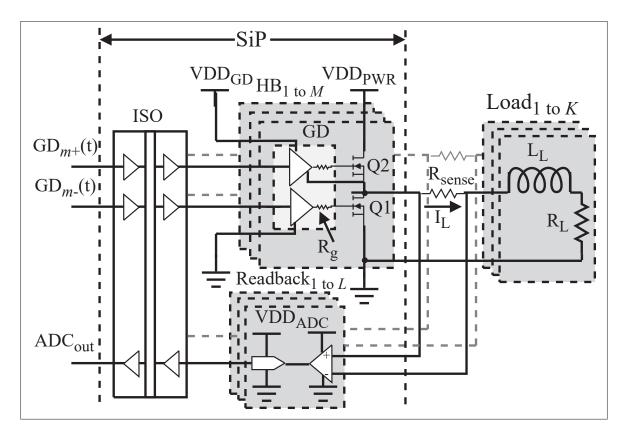

There is a need to reduce the size and weight of those subsystems. One of the ways this can be done is through system-in-package (SiP) integration. Accordingly, a configurable power SiP with read-out and power circuits, i.e., a configurable power input and output system (CPIOS), is presented in this thesis.

The power circuits are switch-mode converters with configurable dead times and gate driver strength, where multiple types of power transistors can be used due to a flexible board footprint. A read-out block allows sensing and conversion of analog voltages or currents in loads to the digital domain. The system therefore supports multiple digital control loops for power converter circuits. The digital isolators protect external control circuits against common-mode transients and faulty signal lines between the digital control system and the power domain.

That CPIOS system is the main application in this work and motivates the need for the GHz-range linear modeling of power integrity and the current measurement technique presented in this thesis.

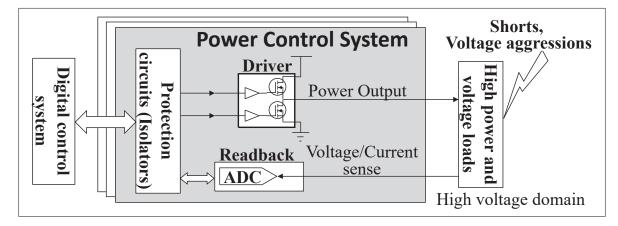

# 0.2 The challenge of Power Integrity in CPIOS

As mentioned previously, the CPIOS features an array of switch-mode converters integrated alongside more sensitive circuits such as ADC and operational amplifiers for signal conditioning (Figure 0.2). As noise-generating circuits such as those switch-mode converters, are integrated closer to sensitive analog and mixed-mode circuits, the power supply noise coupled to those analog devices increases in magnitude, which in turn affects their performance (Bae *et al.*, 2013). In the literature, power integrity is typically defined as the study of the quality of the supply rails in terms of voltage level and noise on the supply rails. More specifically with CPIOS, the main concern is that the noise generated by the switch-mode converter will either affect other converters, or the sensitive circuits in the form of voltage fluctuations on the power rails. The research question studied in this thesis is the following: *what is an accurate way to assess power integrity in systems that integrate power converters with more sensitive analog and mixed-mode circuits, e.g., CPIOS?*

Figure 0.2 Problem of Power Integrity in CPIOS

# 0.2.1 Modeling Power Integrity in CPIOS

In CPIOS, there is an array of switch-mode converters operating independently. However, integrating multiple switching converters together will exacerbate that switching noise onto

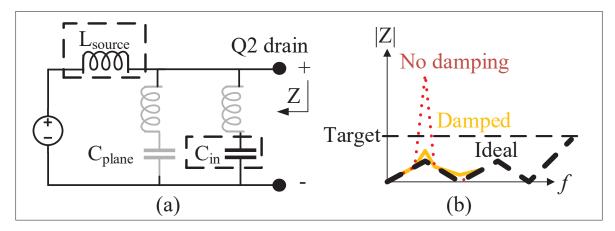

the sensitive analog and mixed-mode circuits. In specific systems that integrate an array of independent switching converters, such as in CPIOS, simultaneous switching of those converters may lead to increased peak voltage fluctuations onto the power rails of sensitive devices. Those switching converters may switch simultaneously or at relative times (referred to as *timing conditions*) short enough that the effect of the current pulled by two independent converters on a victim node overlap each other (simultaneous switching). They may also be switching with different strengths (gate driving conditions), and load currents (loading conditions). All those factors affect the fluctuations generated onto the different power domains of the SiP when the array of converter switches. Predicting those fluctuations both in time and frequency domains under this variety of conditions is of importance in order to assess power integrity (PI) constraints and take appropriate design decisions. Indeed, due to the plurality of conditions, a system-level designer that uses the CPIOS with given timing, gate driving and loading conditions needs to be able to predict by how much it will affect the behavior of, for instance, the control or the noise on the power output of the converters. By being able to predict those fluctuations, it becomes possible to avoid situations where the noise levels exceed the acceptable thresholds in terms of peak level and spectral density.

Those fluctuations could be predicted, in a more generic way, through a mix of circuit-level and electromagnetic simulations. However, for various reasons, it is not an ideal solution in configurable systems. The power transistors, which are simulated through time-domain analysis, are non-linear devices that operate in various operating regions in a converter during switching: cut-off (*off state*), saturation and triode (*on state*). Furthermore, electromagnetic simulations are done in order to accurately model the behavior of the power distribution network (PDN). The result of those electromagnetic simulations can either be an equivalent RLCG network such as with ANSYS Q3D Extractor (ANSYS, 2022) or an S-parameter network, with most tools for EM modeling. In either case, the simulations of the non-linear power transistors need to be augmented with those PDN models and be simulated through, for instance, SPICE-like

simulations (for RLCG network PDN models) or transient and convolution simulations (Keysight, 2022b) for PDN defined as a function of frequency such as with S-parameter network PDN models. It is known in the state-of-the-art that power electronic circuit simulations are prone to convergence problems during switching events and are time-consuming (Tan, 2017). Therefore, augmenting the simulation of multiple switching power devices with complex PDN, having it converge, and be of short duration is challenging even to the seasoned designer. With a large variety of conditions to simulate it becomes a time-consuming task that needs to be repeated even for small design changes if the simulations even converge. For those reasons, a behavioral-model-based approach that requires a one-time characterization with no convergence issue is preferable. Therefore, *there is a need for a model that predicts the voltage fluctuations onto sensitive nodes, specifically for power converters operating under a range of conditions and switching simultaneously.*

## 0.2.2 GHz-range Current Measurement technique for CPIOS

It is the current transients (di/dt) drawn by the power converters that generates the noise on the power rails. For that reason, in order to assess power integrity in the CPIOS, it is critical that the current is properly measured when switching of the converter occurs. Furthermore, for power applications operating at high-voltage levels, transistors that offer a better trade-off between gate charge, i.e.,  $Q_G$  in typical power field-effect transistor (FET) data sheets, dimensions and power handling capabilities are required. For that purpose, devices such as gallium nitride high-electron mobility transistors (GaN HEMT) and silicon carbide (SiC) metal oxide silicon field-effect transistor (MOSFET) are preferred. On such devices, the gate charge is significantly reduced, hence switching times are reduced compared to a silicon device of similar power handling capabilities (Saito *et al.*, 2007). In a specific case, a switching time of less than a nanosecond was reached (Simonaitis *et al.*, 2021). On the other hand, the shorter switching times and smaller output capacitance increase the bandwidth of the switching current transient

to a point where characterizing switching noise in the GHz range may be required. In this context, the measurements of currents at GHz range in switching converters are key to allow the characterization of PI in SiP power electronics systems that combine switching converters and sensitive analog and mixed-mode circuits.

Aside from the bandwidth requirements, it is also critical that the technique is suited for compact power electronics SiP implementations with minimal on-board overhead for probing provisions and low losses in order to assess PI constraints. Indeed, as will be explained in the literature review, while there exist current measurement techniques with high bandwidth, those are based on a resistive shunt, which significantly affect either circuit dimensions or losses and current-handling capabilities. Therefore, *there is a need for a current measurement technique in the GHz range that is suitable for high current levels and specifically for power integrity application in highly integrated systems.*

#### 0.3 Research Objectives

In light of the previous sections, the following main research objective is pursued: *To model power integrity constraints in CPIOS based on diverse operating conditions and a thorough characterization of the system*. More specifically, the following objectives are pursued:

- (O1) To characterize the switching current in power converters for the CPIOS, which are critical for power integrity with high bandwidth.

- (O2) To predict fluctuations onto the power rails of sensitive circuits, in terms of shape and energy spectrum.

The state-of-the-art is reviewed in the following sections and sub-specific objectives are also derived to assess if each of those objectives are met.

#### 0.4 Key Contributions to State-of-the-Art

This thesis is based on two major contributions, which both have been submitted to scientific journals as well as a conference paper, presented at the International Symposium on Circuits and Systems (ISCAS 2021). The first journal paper, which was accepted, introduces a GHz-range current measurement technique suited for high-density integration.

Nobert, G., Constantin, N. G. & Blaquière, Y. (2023). A Coupled Transmission-Line-Based Measurement Technique for Currents in Switch-Mode Converters. IEEE Transactions on Electromagnetic Compatibility, 65(5), 1535-1547. doi: 10.1109/TEMC.2023.3300988.

The second contribution, which was submitted for publication in October 2023, is a model for the prediction of supply rail voltage fluctuations under a range of operating conditions in an array of simultaneously switching power converters.

Nobert, G., Constantin, N. G. & Blaquière, Y. (submitted for publication in IEEE Transactions on Electromagnetic Compatiblity, October 2023). GHz-range Linear Modeling of Power Integrity in an Array of Simultaneously Switching Power Converters.

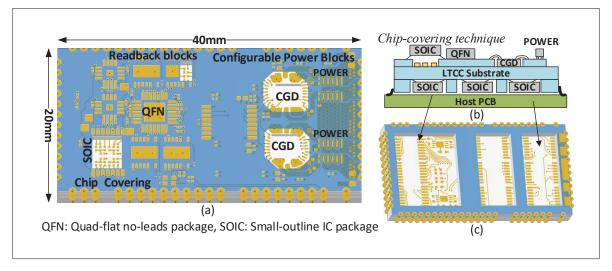

In the conference paper, the general idea of the CPIOS system is presented along with the analysis of integration technologies and early design constraints: density, self-heating, losses and signal integrity.

Nobert, G., Alameh, A.-H., Ly, N., Constantin, N. G. & Blaquière, Y. (2021). *Towards an LTCC SiP for Control System in Safety-Critical Applications*. 2021 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5. doi:10.1109/ISCAS51556.2021.9401066.

The following contributions were made for that paper:

- a novel system-level architecture for a CPIOS;

- a comparison between integration technologies is presented for different aspects: density, self-heating, losses and signal integrity for CPIOS;

• three techniques to take advantage of LTCC capabilities: a multi-layer routing technique to circumvent the issue of thin conductors with limited thermal and electrical conductivity.

### 0.5 Organization of the Thesis

Chapter 1 of this thesis is a review of the state-of-the-art regarding the challenges discussed in the introduction. The different techniques for current sensing in power converters, both based on shunt resistors and mutual inductance are presented along with their main drawbacks. A review of the different methods in the state-of-the-art for the prediction of voltage fluctuations are then presented. The techniques in digital systems for power integrity assessment are first presented, followed by electromagnetic interference (EMI) prediction techniques in power converters.

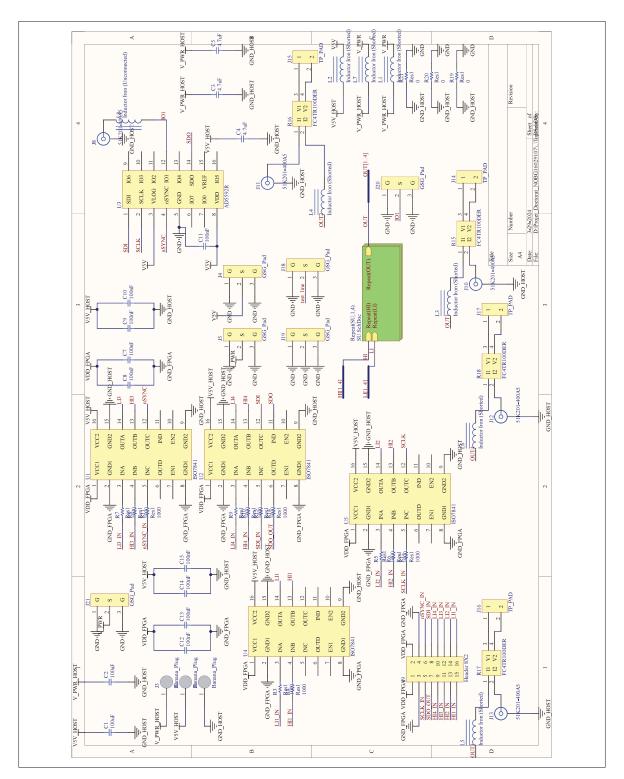

Chapter 2 of this thesis further introduces the challenges of current measurement techniques as well as power integrity in CPIOS. Simulations and numerical applications are presented in order to motivate the need for power integrity assessment and current measurement in the GHz range.

Chapter 3 presents a GHz-range, high-current measurement technique suited for high-density SiP integration. The technique is first introduced and analyzed. Then the experimental measurement apparatus is described and experimental results as well as the main findings are presented.

Chapter 4 presents a model for the prediction of supply rail voltage fluctuations under a range of operating conditions in an array of simultaneously switching power converters. The model is first presented and analyzed. A system with multiple power converters switching simultaneously is then presented, together with the necessary setup to measure one of the sensitive nodes. The predictions made by the model are compared with experimental measurements and conclusions are drawn. The conclusion chapter explores the different outlooks for the research presented in this thesis.

#### **CHAPTER 1**

# LITERATURE REVIEW: GHZ-RANGE FREQUENCIES POWER INTEGRITY ASSESSMENT AND CURRENT MEASUREMENT TECHNIQUES

This chapter presents the different state-of-the-art techniques for the measurement of the current in switch-mode converters. Then, the techniques used for the assessment of power integrity in SiP are introduced. The section is based on, with extracts from, the first two sections of (Nobert, Constantin & Blaquière, 2023) and (Nobert, Constantin & Blaquière, submitted for publication) as well as the conference paper (Nobert *et al.*, 2021).

# 1.1 High-Frequency Current Measurement Techniques

As presented in the introduction, there is a need for a GHz-range current measurement technique applicable to switch-mode converters for power integrity applications in converters based on the use of fast-switching devices such as GaN HEMT and SiC transistors, which allow more compact power systems as needed in SiP. The power integrity characterization at GHz range in SiP of such components leads to some specific requirements in terms of bandwidth, level of integration and current limitations, which are not addressed in state-of-the-art techniques.

The techniques proposed so far in the literature are divided into three different categories in this review:

- Resistive shunt sensing: this category includes the use of surface-mount device (SMD) shunt resistors and coaxial shunt resistors;

- Inductor-based: this category includes mutual-inductance techniques such as pickup coils. It also includes Rogowski coils, which can be integrated on PCB, commercial current transformers and current-surface probes;

- Hall effect sensors: this category includes techniques based on the sensing of magnetic fields through the Hall effect.

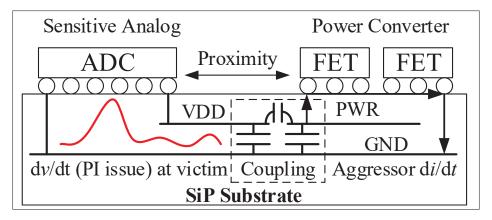

## **1.1.1** Resistive Shunt Sensing and its Limitations

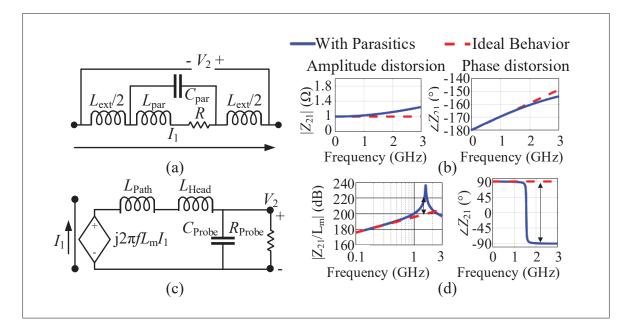

Small shunt resistors can address the problem of characterizing the switching current in power converters for the CPIOS, which are critical for power integrity with high bandwidth. When using shunt-resistor-based techniques, a resistor is placed in series with the current flow  $(I_1)$  to measure this current as a voltage  $(V_2)$  through the IR drop of the shunt resistor. It can be represented by the equivalent circuit of Figure 1.1(a). There are two main types of resistors that are used for such a purpose: SMD resistors and coaxial shunt resistors.

Figure 1.1 Two-port model of two current measurement techniques: (a) resistive shunt technique and (b) mutual inductance-based technique Taken and adapted from Wang *et al.* (2018, p. 6203)

## 1.1.1.1 SMD Shunt Resistors

The SMD resistors are, for current sensing applications, either based on a thin metal film or a thin resistive film. In either case, the film is printed on top of a ceramic substrate and terminations on both sides of the resistor allow the connection to a PCB through soldering. The SMD shunt resistor has the advantage of being low-cost. However, a trade-off has to be made between size, bandwidth and current-handling capabilities. Indeed, the larger the SMD resistor package, the greater its equivalent lead inductances ( $L_{ext}$  and  $L_{par}$ ). Consequently, the bandwidth of the current measurement decreases (Vishay Intertechnology, Inc., 2009). Smaller packages have fewer parasitics, which results in a larger bandwidth, but at the expense of lower power-handling capabilities, leading to current limitations in the converter.

In order to circumvent that problem of trade-off between parasitics and current-handling capabilities, multiple SMD shunt resistors can be put in a parallel configuration (Shillaber, Jiang, Ran & Long, 2022), reducing the parasitic inductance of the resistor network while increasing current-handling capability due to having less current in each individual SMD resistor. However, as depicted in Figure 1.2, which shows the implementation in (Shillaber *et al.*, 2022), the area on a substrate for this technique is larger than that of a single shunt resistor.

Figure 1.2 Depiction of parallel shunt resistor network: (a) cross-section across a single parallel shunt resistor, (b) top and (c) bottom views Taken from Shillaber *et al.* (2022)

Another solution to the parasitic inductance of the SMD shunt resistor is to add an LR compensation network in order to mitigate the impact of the parasitic inductances in the SMD resistor (Figure 1.3). However, that LR network requires a large value of series inductance (compensation inductor) in order to properly compensate the parasitic inductance in the shunt resistor. Moreover, larger compensation inductor leads to lower series resonant frequency and thus, bandwidth in those compensation networks is limited. The authors achieve a bandwidth of 85 MHz with such a compensation network (Yang *et al.*, 2020).

Figure 1.3 LR Compensation network for high bandwidth current shunt sensing Taken from Yang *et al.* (2020)

# 1.1.1.2 Coaxial Shunt Resistors

Coaxial shunt resistors (CSR) improve the current-handling capabilities and bandwidth trade-off with SMD shunt resistors. They are resistors that are integrated within a coaxial structure where the inner material is typically a resistive film, while the outer material is a conductive material such as copper. A classical structure of CSR is depicted in Figure 1.4. The coaxial structure has the advantage of canceling magnetic fields and thus not adding significant series inductance when measuring the voltage across the resistive material (Ferreira, Cronje & Relihan, 1992). Therefore, bandwidths reached for CSR are typically higher than their SMD counterparts for similar current-handling capabilities. However, they suffer from disadvantages in terms of size and added inductance to power loop. Indeed, CSR are bulky for SiP applications and are therefore not ideal for integration into smaller systems. They are rather practical in the

characterization of large-area power transistor applications. Those CSR are connected through leads that add significant inductance to the power loop (referred to as *insertion inductance*). In (Liu, Huang, Lee & Li, 2014), the authors used commercial CSR in order to characterize the current in a switch-mode converter in double-pulse test (DPT) configuration. The CSR lead, however, adds a 2 nH insertion inductance, which may affect the behavior of the converter. More recently, leadless surface-mount CSR were implemented in an effort to have lower footprints and insertion inductance. Taking into account the required footprint of the shunt, an inductance of 0.53 nH was obtained (Zhang *et al.*, 2021). While significant insertion inductance reduction was achieved, the size of the CSR is still significant with its diameter being 8.9 mm.

Figure 1.4 Classical structure of coaxial shunt resistors Taken from Ferreira *et al.* (1992)

It can be concluded for resistive shunt sensing techniques that resistor networks are either too bulky, such as the case in CSR or SMD resistor network, or have limited bandwidth, such as is the case in compensated sense SMD resistors. If a small resistor network or a single small resistor is selected, these limitations are improved at the expense of smaller current-handling.

## 1.1.2 Inductor-Based Techniques

In inductor-based techniques, the current is measured by capturing its generated magnetic flux. Indeed, in Figure 1.1(b),  $I_1$  is measured, leading to voltage  $V_2$  across the inductor structure. That voltage  $V_2$  is then integrated in order to extract the current  $I_1$ . Although still present, the problem of current-handling capabilities observed in resistor-based techniques is significantly reduced due to the absence of the inherent loss mechanism of shunt resistors, which is proportional to the square of the current. One of the main drawbacks of inductor-based techniques compared to shunt resistor techniques is its inability to measure DC or very low-frequency currents.

#### **1.1.2.1** Current Transformers

In applications where integration level is not critical, current transformers in the form of clamps are commonly used. Those current transformers are typically based on an inductor coil around a toroidal magnetic core. The magnetic flux generated by a current passing through the center of the toroid (*primary*) is coupled into the coil (*secondary*) from which the current can be sensed with a sense resistor. In some cases, the primary may itself be wound onto the core (wound current transformers). Commercial probes such as (Pearson Electronics Inc., 2022) have a bandwidth of up to 250 MHz and a maximum root mean square (RMS) current of 10 A. In the case of the Keysight N2783B, a 100 MHz bandwidth is reached with a maximum RMS current of 30 A (Keysight, 2022a). However, current transformers with higher current-handling capabilities typically have bandwidths in the order of tens of kHz to a few MHz. Those bandwidth limitations are typically due to the large leakage inductance and stray capacitance (Kondrath & Kazimierczuk, 2009). In either case, aside from bandwidth limitations, another problem in such current clamps is that they require to pass an electrical cable through the transformer in order to measure the current. Adding a cable passing through the center of the toroid, or a primary winding in the case of wound current transformers, to the power loop increases the insertion inductance by a significant amount, leading to a change to the behavior of the converter when measuring it. In addition, those clamps are not practical, because of their size and the hard-to-integrate magnetic core in the context of SiP. Finally, the magnetic core of current transformers is an issue when magnetic fields become stronger and the core reaches saturation: non-linearity and hysteretic effects occur.

#### 1.1.2.2 Rogowski Coils

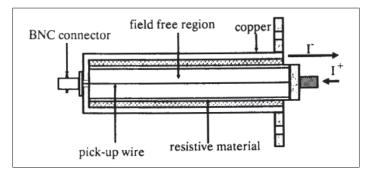

Rogowski coils are similar to current transformers, but do not suffer the drawbacks from having a magnetic core. Therefore, they are not subjected to saturation non-linearity and can be integrated on PCB or SiP due to not requiring a magnetic core. Although classically made on a machined circular skeleton (Ramboz, 1996), more modern implementations exist directly on PCB using conductor traces and vias (Shi, Xin, Loh & Blaabjerg, 2020) followed by an integrator circuit. In those implementations, the helical shape of the coil is printed around a via or slot for a cable in the PCB by having traces and vias to alternate between two layers, hence creating a coil shape on PCB, such as depicted in Figure 1.5. According to the coil model of Shi et al. (2020), the bandwidth is, however, limited by the self-inductance of the coil and its inductance between the different windings and the current return from the coil. In high-bandwidth Rogowski coils made specifically for wide-band-gap (WBG) transistor characterization (Fritz, Neeb & Doncker, 2015), a bandwidth of 110 MHz and a mutual inductance of 3.89 nH was reached for a 64 mm<sup>2</sup> coil. In (Fritz et al., 2015), the current from the low-side FET located on the bottom layer, to the high-side FET on the top layer is captured with a Rogowski coil around the via. That technique, however, requires a specific layout and the use of a via on the switching node, which increases the power loop inductance in addition to have non-negligible dimensions. In other works, one of the layers of the coil is used as a screen return (Ming et al., 2019) in order to improve the bandwidth of the design and noise immunity. The obtained bandwidth is, however, not reported in the paper.

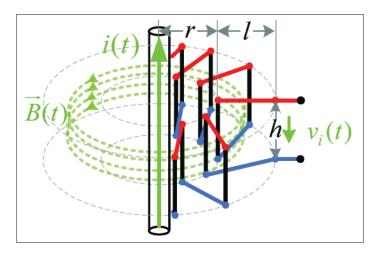

## 1.1.2.3 Pickup Coils

As mentioned, the bandwidth of Rogowski coils is mainly limited by the inductive nature of the coil and its stray capacitance. Therefore, shorter coils exhibit superior bandwidths. In (Wang *et al.*, 2018), the authors use a single-winding coil, referred to as a *pickup coil*. Using those pickup coils, superior bandwidth is reached thanks to having negligible stray capacitance and minimal coil self-inductance. In the case of pickup coils, bandwidth is limited by the resonant frequency between the coil self-inductance and the probe capacitance at the output of the coil.

Figure 1.5 Structure of the integrated Rogowski coil on PCB Taken from Ming *et al.* (2019)

Based on the equivalent circuit for their pickup coil (Figure 1.1(b)) and the data provided in the paper, the bandwidth of their circuit can be estimated to approximately 840 MHz, although that bandwidth is not directly reported, but rather represents a 3 dB deviation from ideal behavior as defined in section 3.1 of this thesis. The pickup coil, however, has several issues. First, the bandwidth of the pickup coil is limited by the probe capacitance and the inductive effects in the probe and the coil. In a context of sub-ns switching times, a GHz-range bandwidth is preferable. In addition, in order to properly probe the coil, the probe must be placed as close as possible to the coil and therefore the converter. A more convenient probing apparatus where the probe could be placed in a safe probing location, meaning where there is no risk of short-circuiting due to mishandling of the probe, is preferable.

# 1.1.2.4 Current Surface Probe Sensing

One of the main issues with discrete current transformers in the form of clamps and Rogowski coils is that the current carrying trace has to go through a cable and then into the transformer. One of the solutions is to build a current transformer or coil that lies flat on board and would measure the magnetic field generated by a trace: current surface probes (CSP). The CSP would

then be laid flat on the trace that needs to be measured. Using such a probe helps reduce the insertion inductance compared with discrete current transformers and Rogowski coils. However, the probe still has to be laid flat on a componentless area. In the case of SiP or a tightly integrated system, leaving an area without any component may increase the dimensions of the system. In addition, it increases the length of the power loop where the current needs to be characterized. Nevertheless, commercial products such as the Fischer CC F-97-1 have an upper bandwidth of up to 1.5 GHz, while supporting a current of 10 A. In (Li, Videt & Idir, 2015a), the authors use a CSP and a coaxial shunt resistor in order to measure the switching current in a GaN HEMT-based converter. In terms of insertion inductance, they obtain significantly less insertion inductance (4.5 nH) with the CSP compared with a commercial coaxial shunt resistor (14 nH).

In conclusion, with mutual-inductance-based sensing, while it is possible to reach higher bandwidth with minimal losses, there is still an issue of high insertion inductance leading to altered behavior of the converter, because of the overhead required, such as loose cables into a transformer or componentless area for current surface probe sensing. For those same reasons, making measurements of the current often requires a special board design that requires a significant PCB area (e.g., Rogowski coils). While pickup coils partially solve those problems, they are still limited in terms of probing convenience and bandwidth.

## **1.1.3** Limitations in Hall-Effect Sensors

Hall effect is commonly described as the current flow being deviated when a magnetic field is perpendicular to a conductor plate, hence creating a potential difference across the conductor's cross-section. Hall-effect sensors use that effect in order to measure magnetic fields crossing the conductor, which is the sensor in that case. In current measurement applications, the goal is to measure the magnetic field generated by a direct current (DC), in order to obtain that current. Unlike inductor-based techniques, Hall-effect sensors have the advantage of being able to measure DC. They also do not suffer from the main limitation of shunt resistors, which inherently dissipate power proportional to the current squared. More recently, hall-effect sensors have been integrated in a package (Motz *et al.*, 2012) along with the readout circuit. The authors

manage to achieve a 10 kHz measurement bandwidth and 50 A current-handling capability. In other works, the sensor is integrated directly on an integrated circuits (IC) (Heidari, Bonizzoni, Gatti & Maloberti, 2015) and integrate the sensor and the readout circuit in a 1.16 mm<sup>2</sup> area. However, the main issue of hall-effect sensors is their bandwidth limitation. Indeed, even in integrated applications, a 10 kHz bandwidth is highly insufficient for the CPIOS application. Therefore, while hall-effect sensors allow compact measurement of high currents along with their DC component, they are severely limited in terms of bandwidth and unusable as a current measurement technique in the case of CPIOS.

## 1.1.4 Conclusion on Current Measurement Techniques

The initial objective for current measurement was to characterize the switching current in power converters for the CPIOS, which are critical for power integrity with high bandwidth. Among the high-frequency current measurement techniques, the ones based on a resistive current shunt present a trade-off between current-handling capabilities, bandwidth and size that is insufficient for the CPIOS application. To solve that problem, an inductance-based solution, such as a current transformer, Rogowski coil, pickup coil or current surface probe sensing could be considered. However, the combination of the probe and inductive secondaries in the case of pickup coils, Rogowski coils and current transformers are limiting the bandwidth of the current measurement structure. Finally, Rogowski coils and current surface probe sensors require significant dimensions either for probing overhead or physical implementation of the coil, which is unfit for the SiP integration of CPIOS. It is therefore necessary to develop a current measurement technique, which doesn't have the limited current-handling capabilities or excessive size of current-shunt resistor. It also needs an improved bandwidth and dimensions compared to inductance-based solutions. Those problems in the literature are summarized in Table 1.1.

| Technique                   | Description                                                                               | Drawback                                                                                                                                                       |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                             | Resitive Shunt Sensing                                                                    | -<br>                                                                                                                                                          |  |  |

| SMD Shunt Resistor          | Use an SMD shunt resistor alone                                                           | Trade-off between bandwidth<br>and current-handling<br>capabilities                                                                                            |  |  |

|                             | Multiple shunt resistor put in parallel                                                   | Requires multiple components<br>Limited Bandwidth                                                                                                              |  |  |

|                             | Use an LR compensation network to improve bandwidth                                       |                                                                                                                                                                |  |  |

| Coaxial Shunt<br>Resistor   | Coaxial resistor structure to<br>contain magnetic field and limit<br>parasitic inductance | Bulky structure unfit for SiP integration                                                                                                                      |  |  |

| Inductance-based techniques |                                                                                           |                                                                                                                                                                |  |  |

| Current Transformers        | Capture magnetic flux through<br>a toroidal-shaped inductor coil<br>around magnetic core  | Magnetic Core cannot be<br>integrated<br>Limited Bandwidth                                                                                                     |  |  |

| Rogowski Coils              | Integrated on-board current transformer with no core                                      | Significant Dimensions<br>Limited Bandwidth                                                                                                                    |  |  |

| Pickup coil                 | Single-winding Rogowski coil                                                              | Limited Bandwidth<br>Probing location must be<br>placed next to the coil itself,<br>and therefore the converter,<br>leading to a complex probing<br>apparatus. |  |  |

| Current-Surface<br>Probe    | Current Transformer probe<br>with no core and that lies flat<br>on the board              | Requires special layout and<br>large area without components<br>or traces on the substrate,<br>which is unfit for SiP<br>integration                           |  |  |

| Other Techniques            |                                                                                           |                                                                                                                                                                |  |  |

| Hall-effect sensors         | Use the Hall Effect to measure<br>current both at DC and higher<br>frequencies.           | Limited bandwidth;                                                                                                                                             |  |  |

| Table 1.1 | Summary of techniques for switching current measurement |

|-----------|---------------------------------------------------------|

|-----------|---------------------------------------------------------|

# **1.2** Techniques for Power Integrity Assessment in System-in-Package

Power integrity PI assessment is of critical importance in SiP. More specifically, there is a need for a model that predicts the voltage fluctuations onto sensitive nodes for a range of conditions under which a converter switches. There are two separate fields of study that are of interest for that challenge: PI in digital systems and electromagnetic compatibility in power systems.

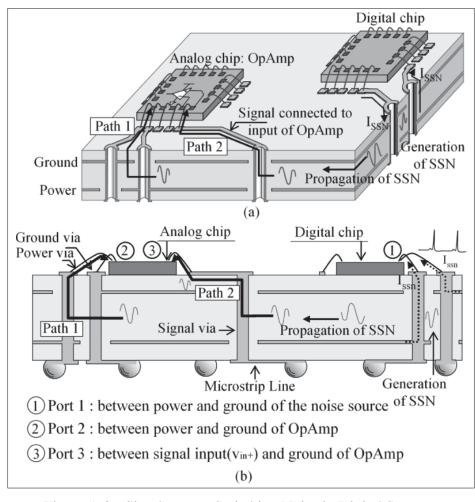

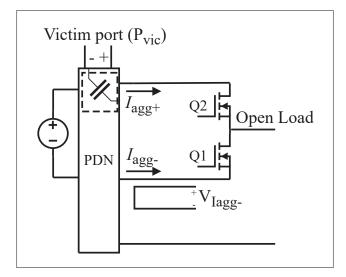

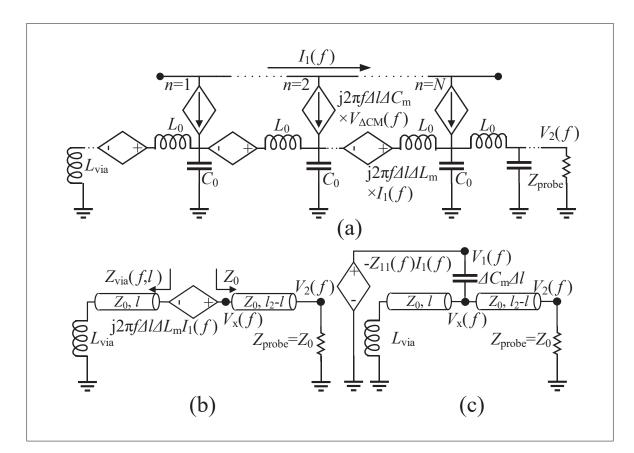

# 1.2.1 Simultaneous Switching Noise and Power Distribution Network in Digital Systems

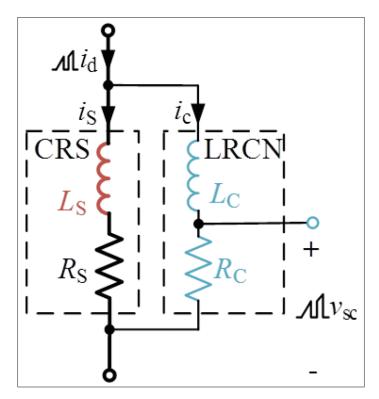

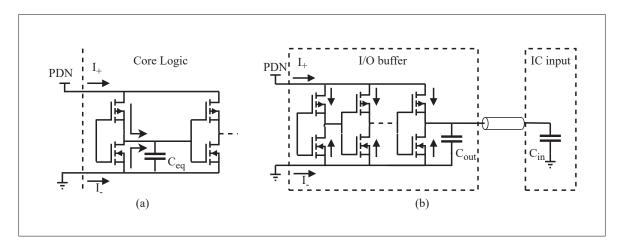

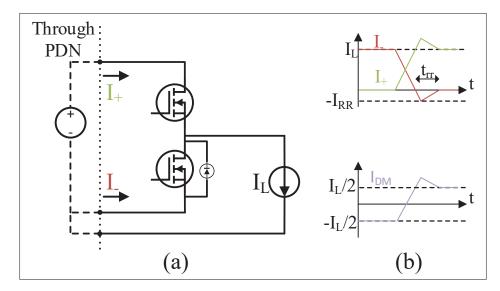

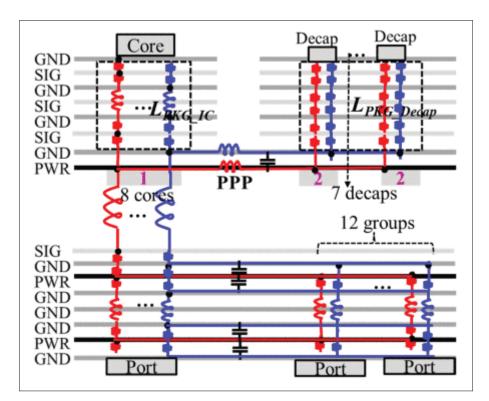

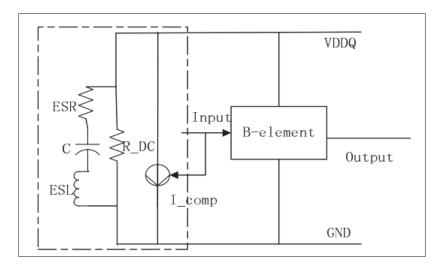

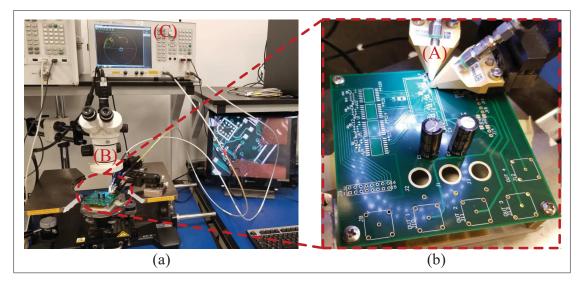

In the field of PI in digital systems, so-called simultaneous switching noise (SSN) is the main mechanism that generates voltage fluctuations on the power rails of more sensitive IC such as operational amplifiers, ADC and even other digital circuits. The voltage fluctuations generated by SSN propagate through the different coupling mechanisms and power planes in the PDN, such as depicted in Figure 1.6. Those voltage fluctuations can affect the behavior of operational amplifiers (Shim *et al.*, 2009), the effective number of bits (ENOB) of ADC (Bae *et al.*, 2013) and even the clock jitter (Tripathi *et al.*, 2016) among other metrics (Wen, Cai & Zhuo, 2021) in digital circuits. Although the aggressor source in the CPIOS is not a digital IC, but rather the current transient generated by the switching of different power converters, the switching characteristics of power converters still share similarities with digital IO buffers of digital circuits and core logic.