# **Energy-Proportional Polar Decoders**

by

# **Ilshat SAGITOV**

# THESIS PRESENTED TO ÉCOLE DE TECHNOLOGIE SUPÉRIEURE IN PARTIAL FULFILLMENT FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Ph.D.

MONTREAL, NOVEMBER 29, 2024

ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

# **BOARD OF EXAMINERS**

# THIS THESIS HAS BEEN EVALUATED

# BY THE FOLLOWING BOARD OF EXAMINERS

Mr. Pascal Giard, thesis supervisor Département de génie électrique à l'École de technologie supérieure

Mr. Kaiwen Zhang, president of the board of examiners Département de génie électrique à l'École de technologie supérieure

Mr. Georges Kaddoum, member of the jury Département de génie électrique à l'École de technologie supérieure

Ms. Elsa Dupraz, external independent examiner Lab-STICC à IMT Atlantique

THIS THESIS WAS PRESENTED AND DEFENDED

IN THE PRESENCE OF A BOARD OF EXAMINERS AND THE PUBLIC

ON 21, NOVEMBER, 2024

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my research director Professor Pascal Giard for his guidance, support, and motivation throughout my PhD journey. I would like to thank Dr. Charles Pillet for his great friendship and assistance. I would like to express my gratitude to Professor Alexios Balatsoukas-Stimming for his support and expertise. I further extend my thanks to my dear colleagues at the LaCIME – communications and microelectronics laboratory, for their friendship and support. Finally, I express my heartfelt thanks to both my dearest mother as well as my beloved wife for their countless prayers, love, and support in helping me achieve my goals.

#### Décodeurs polaires proportionnels à l'énergie

#### Ilshat SAGITOV

#### RÉSUMÉ

Les codes polaires sont une classe de codes correcteur d'erreurs ayant reçus beaucoup d'attention depuis leur découverte. Cela s'explique en partie par le fait qu'il a été prouvé que les codes polaires atteignent asymptotiquement la capacité d'un canal binaire symmétrique sans mémoire (binary discrete memoryless channel (B-DMC)) via un algorithme de décodage à faible complexité nommé annulation successive (successive-cancellation (SC)). Cependant, les performances de correction d'erreurs restent limitées pour SC pour des longueurs de codes finis. Ainsi, un algorithme plus performant, le décodeur à annulation successive par liste (successive-cancellation list (SCL)) est considéré comme l'algorithme de référence dans de nombreuses applications pratiques, comme lors de la standardisation de la 5G. Le décodeur SCL génère une liste de candidats pour décoder la représentation bruitée d'un message transmis. En conséquence, les performances de correction d'erreurs de SCL sont considérablement améliorées par rapport à SC. Par contre, l'implémentation matérielle d'un décodeur SCL consomme plus d'énergie et requiert une plus grande surface en comparaison à SC.

Le décodage SC à inversion (successive-cancellation flip (SCF)) a été proposé pour améliorer les performances de correction d'erreurs de SC en générant les candidats à travers plusieurs essais de décodage, c'est-à-dire de manière séquentielle. À chaque essai supplémentaire, le bit de décision estimé comme le moins fiable est inversé. Le décodeur à annulation successive par liste à inversion (successive-cancellation list flip (SCLF)) a été proposé avec l'idée de combiner les stratégies de décodage SCL et SCF. Les variantes dynamiques de ces décodeurs, SCF dynamique (dynamic successive-cancellation flip (DSCF)) et SCLF dynamique (dynamic successive-cancellation list flip (DSCLF)), améliorent les performances de correction d'erreurs. Cette stratégie de décodage à inversion fait que SCF et SCLF présentent des temps d'exécution variables, rendant le temps d'exécution moyen et la latence potentiellement très élevés. Néanmoins, les architectures existantes montrent que les décodeurs à inversion sont plus efficaces en termes de surface et de consommation énergétique en comparaison au décodeur SCL.

Les contributions de ce doctorat s'articulent autour de la conception de décodeurs de codes polaires à faible consommation d'énergie. Les algorithmes de décodage par inversion basés sur SCF et leurs variations peuvent atteindre les performances de correction d'erreurs des décodeurs SCL tout en ayant des implémentations matérielles plus efficaces. Cependant, le temps d'exécution variable pose un problème pour la réalisation des récepteurs. Les mécanismes proposés dans cette étude doctorale améliorent le temps d'exécution des décodeurs à inversion avec un impact minimal ou nul sur les performances de correction d'erreurs et les ressources matérielles. Concernant l'implémentation matérielle, l'accent est mis sur la mémoire requise, majoritaire à la surface du décodeur.

La première contribution de ce mémoire est le mécanisme de redémarrage généralisé (generalized restart mechanism (GRM)) pour le décodeur par inversion basé sur SCF. Lors de l'application du GRM à chaque essai supplémentaire, la partie de l'arbre de décodage précédant l'inversion du bit non fiable est évitée. Le chemin de redémarrage parcourt l'arbre de décodage depuis la racine jusqu'au bit de redémarrage afin de pouvoir l'estimer tout en évitant l'estimation des bits précédents. Le GRM réduit le temps d'exécution moyen du décodeur DSCF-3 de 26% à 60% sans aucun effet négatif sur les performances de correction d'erreurs. Le GRM requiert environ 4% de mémoire supplémentaire pour ce décodeur.

La deuxième contribution est l'ajout d'un GRM modifié pour des décodeurs à inversion possédant des techniques de décodage rapide. Ces techniques de décodage rapide améliorent le temps d'exécution des décodeurs à inversion. Notre proposition GRM est conçue pour être adaptable à ces techniques de décodage rapide. Grâce à cela, le temps d'exécution moyen des décodeurs à inversion est encore plus réduit.

La troisième contribution est le mécanisme de redémarrage à localisation limitée (limited-locations restart mechanism (LLRM)) pour le décodeur SCLF. L'ajout du GRM aux décodeurs à inversion par liste requiert une quantité trop importante de mémoire. Pour résoudre ce problème, nous proposons le LLRM, une modification du

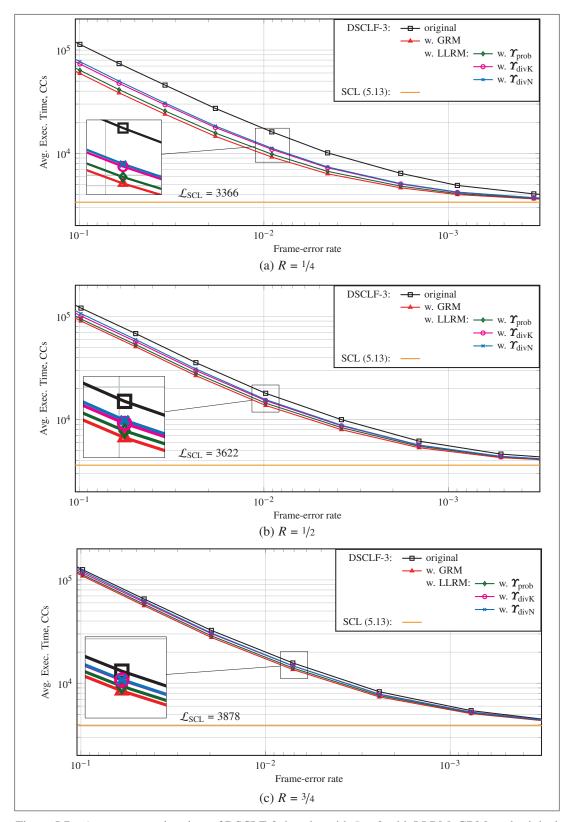

GRM. Une méthode basée sur les probabilités pour sélectionner les emplacements de redémarrage est proposée. Elle vise à maximiser la réduction du temps d'exécution tout en minimisant la mémoire requise. Le LLRM réduit le temps d'exécution moyen de 10% à 40% lorsqu'il est appliqué au décodeur DSCLF-3. Le LLRM nécessite environ 2% de mémoire supplémentaire.

La quatrième contribution est le mécanisme de terminaison anticipée pour les décodeurs à inversion. Cette contribution consiste en deux mécanismes distincts. Tout d'abord, un mécanisme d'arrêt précoce est introduit pour différencier les mots de code indécodables des mots de code décodables en utilisant notre métrique. Si la métrique suggère qu'un mot codé est probablement indécodable, le décodeur tente un nombre maximal réduit d'essais. Le mécanisme d'arrêt précoce réduit le temps d'exécution moyen du décodeur DSCF-1 de 22% au prix d'une perte de correction d'erreur mineure de 0,05 dB. Deuxièmement, le mécanisme à seuils multiples proposé limite la latence d'un décodeur à inversion en fonction de l'état du buffer afin d'éviter toute perte de données. Ce mécanisme est mis en œuvre dans un système où le canal produit des données à un taux fixe. Appliqué au décodeur DSCF-1, le mécanisme à seuils multiples permet d'opérer dans un système avec un taux de production de canaux fixe 1,13 fois inférieur au taux associé à un seul essai de décodage. Il en résulte une perte de correction d'erreurs mineure de 0,06 dB.

**Mots-clés:** Codes polaires, Codes correcteur d'erreurs, Décodage, Gestion de la mémoire, Temps d'exécution, Complexité, Efficacité énergétique

#### **Energy-Proportional Polar Decoders**

#### Ilshat SAGITOV

#### **ABSTRACT**

Polar codes are a class of linear error-correction codes that have received a lot of attention due to their ability to achieve channel capacity in an arbitrary binary discrete memoryless channel (B-DMC) with low-complexity successive-cancellation (SC) decoding. However, practical implementations often require better error-correction performance than what SC decoding provides, particularly at shorter code lengths. As a result, the successive-cancellation list (SCL) decoder has become the reference algorithm for many practical applications, such as 3GPP's next-generation mobile-communication standard (5G). The SCL decoder improves error-correction performance by generating a list of candidate codewords from the noisy received message. However, the hardware implementation of SCL decoder tends to be less energy- and area-efficient than that of a SC decoder.

Successive-cancellation flip (SCF) decoder involves multiple decoding trials, where at each additional trial, the decision bit estimated as the least reliable is flipped before resuming the standard SC decoding. The successive-cancellation list flip (SCLF) decoder combines the SCL and SCF decoding strategies. Variations of these decoders, such as dynamic successive-cancellation flip (DSCF) and dynamic successive-cancellation list flip (DSCLF), further improve the error-correction performance. Despite their advantages in error correction, the flip decoders (SCF and SCLF) have variable execution times, which can lead to high average execution time and latency. Nevertheless, existing architectural designs demonstrate that flip decoders are more efficient in area and energy requirements compared to the SCL decoder.

The contributions of this doctoral study are focused on the design of energy-efficient decoders for polar codes. The flip decoding algorithms based on SCF and their variations can achieve the error-correction performance of the state-of-the-art SCL decoders while resulting in more efficient hardware implementations. However, variable execution time poses a challenge for realization in receivers. This doctoral study proposes mechanisms to improve the execution-time characteristics of flip decoders while minimizing the impact on error-correction performance and hardware resources. Among hardware resources, the primary focus is on the decoder memory, which occupies the largest part of the decoder area.

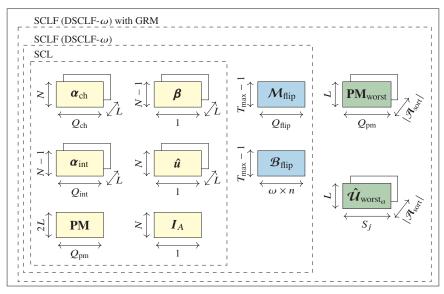

The first contribution of this thesis is the generalized restart mechanism (GRM) for the flip decoder based on SCF. By applying the GRM, a portion of the decoding tree can be skipped. This portion corresponds to parts of the tree to estimate the bit-flipping candidate and all the previous bits in each additional decoding trial. The GRM reduces the average execution time of the DSCF-3 decoder by 26% to 60% without any negative effect on the error-correction performance. The GRM results in approximately 4% of additional memory for this decoder.

The second contribution is the modified GRM for flip decoders with fast decoding techniques. Existing fast decoding techniques improve the execution-time characteristics of the flip decoders. Our proposed GRM is designed to be adaptable to these fast decoders. As a result of this combination, the average execution time of the flip decoders is further reduced while maintaining the original error-correction performance.

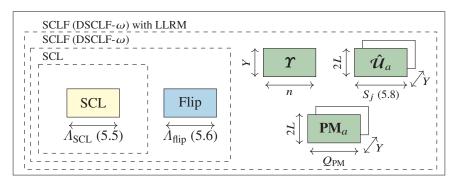

The third contribution is the limited-locations restart mechanism (LLRM) for the list-flip decoder (SCLF and its variations). Applying our proposed GRM to list-flip decoders results in enormous memory overhead. To overcome this issue, the LLRM, a modification of the GRM, is proposed. The probability-based method for selecting restart locations is proposed, which aims to maximize the execution-time reduction while minimizing the memory overhead. The LLRM reduces the average execution time by 10% to 40% when applied to DSCLF-3 decoder. For this decoder, the LLRM requires approximately 2% of additional memory. The LLRM does not modify original error-correction performance.

The fourth contribution is the early-termination mechanism for flip decoders. This contribution consists of two mechanisms. First, the early-stopping mechanism is introduced to differentiate undecodable codewords from

decodable ones by using our proposed early-stopping metric. If the metric suggests that a codeword is likely undecodable, the decoder attempts a reduced maximum number of trials, much smaller than the initial maximum number of trials. The early-stopping mechanism reduces the average execution time of the DSCF-1 decoder by 22% at the cost of minor error-correction loss of 0.05 dB. Second, the multi-threshold mechanism is proposed. This mechanism restrains the delay of a flip decoder depending on the state of the buffer to prevent overflow. This mechanism is implemented in the system where the channel produces data with a fixed rate. When applied to the DSCF-1 decoder, the multi-threshold mechanism allows to operate in a system with a fixed channel-production rate 1.13 times lower than the rate associated with a single decoding trial. This results in a minor in a minor error-correction loss of 0.06 dB.

**Keywords:** Polar Codes, Error-correction Codes, Decoding, Memory Management, Execution Time, Complexity, Energy Efficiency

# TABLE OF CONTENTS

|       |         |                                                        | Page |

|-------|---------|--------------------------------------------------------|------|

| INTRO | DDUCTI  | ION                                                    | 1    |

| CHAP  | TER 1   | LITERATURE REVIEW                                      | g    |

| 1.1   |         | Communication System                                   |      |

| 1.2   |         | uction and Encoding of Polar Codes                     |      |

| 1.2   | 1.2.1   | Code Construction                                      |      |

|       | 1.2.2   | Encoding                                               |      |

| 1.3   | Success | sive-Cancellation (SC) Decoding                        |      |

| 1.4   |         | g Fast Decoding Techniques                             |      |

|       | 1.4.1   | Decoding of Special Nodes                              |      |

|       | 1.4.2   | Latency-Reducing Technique (LRT)                       | 19   |

| 1.5   | Success | sive-Cancellation List (SCL) Decoding                  | 19   |

| 1.6   | Hardwa  | are Implementations of SC and SCL Decoders             |      |

| 1.7   | Conclus | sion                                                   | 24   |

| СНАР  | TER 2   | BACKGROUND AND BASIS OF FLIP DECODING ALGORITHMS       | 25   |

| 2.1   | Success | sive-Cancellation Flip (SCF) Decoding                  | 25   |

| 2.2   |         | ic Successive-Cancellation Flip (DSCF) Decoding        |      |

|       | 2.2.1   | Error-Correction Performance Analysis                  |      |

| 2.3   | Success | sive-Cancellation List-Flip (SCLF) Decoding            |      |

| 2.4   |         | iic Successive-Cancellation List-Flip (DSCLF) Decoding |      |

|       | 2.4.1   | Error-Correction Performance Analysis                  |      |

| 2.5   | Executi | ion-Time Model                                         |      |

| 2.6   | Hardwa  | are Implementations of SCF Decoders                    | 36   |

| 2.7   | Conclus | sion                                                   | 39   |

| CHAP  | TER 3   | EXECUTION-TIME REDUCTION MECHANISMS FOR FLIP DECODERS  | 41   |

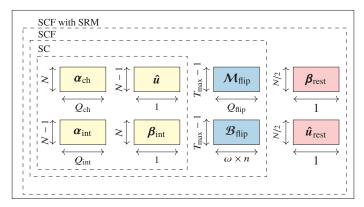

| 3.1   |         | fied Restart Mechanisms (SRM) For Flip Decoder         |      |

|       | 3.1.1   | Introduction                                           |      |

|       | 3.1.2   | Description of the SRM                                 |      |

|       | 3.1.3   | Time and Resource Analysis                             |      |

|       |         | 3.1.3.1 Memory Structure                               |      |

|       |         | 3.1.3.2 Execution-Time Estimations                     |      |

|       | 3.1.4   | Simulation Results                                     | 47   |

|       |         | 3.1.4.1 Error-Correction Performance                   | 48   |

|       |         | 3.1.4.2 Memory Estimates                               | 48   |

|       |         | 3.1.4.3 Execution-Time Characteristics                 | 49   |

|       | 3.1.5   | Conclusion on Simplified Restart Mechanism             | 51   |

| 3.2   | General | lized Restart Mechanism (GRM) For Flip Decoders        | 52   |

|       | 3.2.1   | Introduction                                           |      |

|       | 3.2.2   | Distribution of the Bit-Flipping Candidates            | 53   |

|       | 3.2.3   | Description of the GRM                                 |      |

|       | 3.2.4   | Time and Resource Analysis of the GRM                  | 57   |

|       |         | 3.2.4.1 Execution-Time Reduction Capability            | 58   |

|       |         | 3.2.4.2 Memory Structure                               |      |

|       |         | 3.2.4.3 Partial-Sum Restoration                        | 61   |

|       | 3.2.5   | Simulation Results                                     |      |

|       |         | 3.2.5.1 Error-Correction Performance                   |      |

|       |         | 2.2.5.2 Mamory Estimations                             | 62   |

|      |           | 3.2.5.3    |                                                                  |     |

|------|-----------|------------|------------------------------------------------------------------|-----|

|      | 3.2.6     |            | on on Generalized Restart Mechanism                              |     |

| 3.3  | Conclus   | ion        |                                                                  | 66  |

| CHAP | TER 4     | MODIFI     | ED GRM FOR FAST DECODING TECHNIQUES                              | 67  |

| 4.1  | Fast Dec  | coding Tec | chniques                                                         | 67  |

|      | 4.1.1     | Fast-Sim   | plified SC (SSC) Decoding                                        | 67  |

|      | 4.1.2     | SC with    | LRT Decoding                                                     | 68  |

| 4.2  | Applyin   | g GRM w    | ith Fast Decoding Techniques                                     | 69  |

| 4.3  | Time an   | d Resourc  | e Analysis                                                       | 70  |

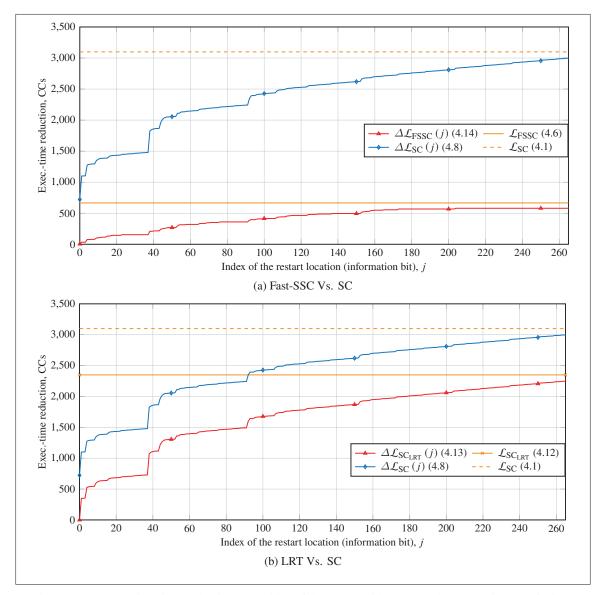

|      | 4.3.1     | Execution  | n-Time Reduction Capability of the GRM                           | 72  |

|      | 4.3.2     | Execution  | n-Time Reduction of Combined GRM with SC <sub>LRT</sub> and FSSC | 74  |

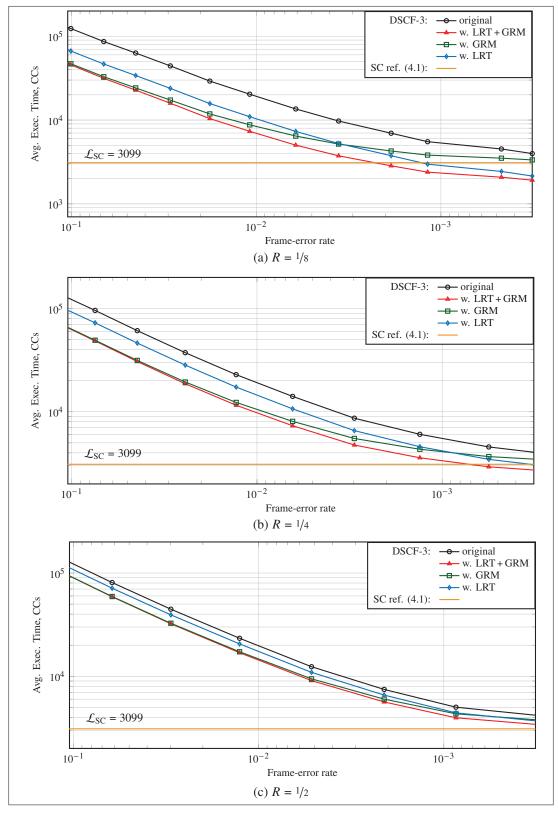

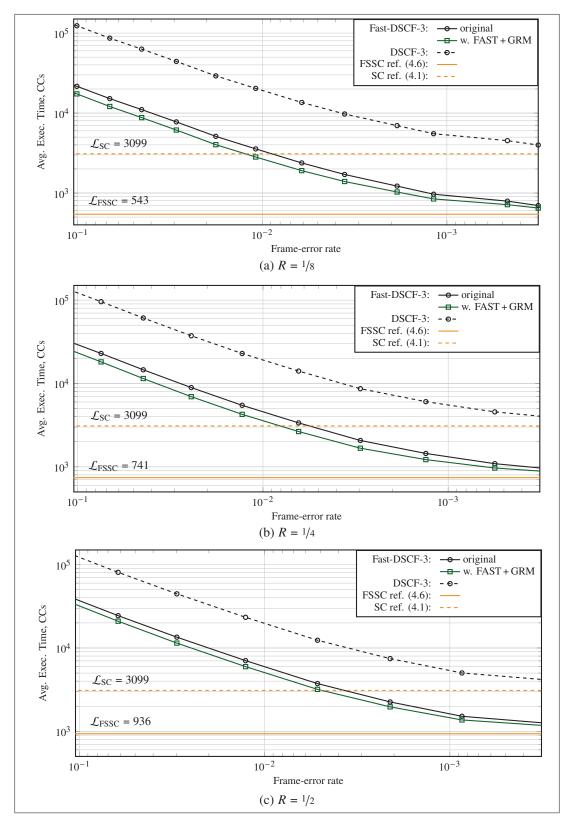

| 4.4  | Simulati  | on Results | s                                                                | 76  |

|      | 4.4.1     | Average 1  | Execution Time                                                   | 76  |

| 4.5  | Conclus   |            |                                                                  |     |

| CHAP | TER 5     | RESTAR     | RT MECHANISMS FOR LIST-FLIP DECODERS                             | 83  |

| 5.1  | Summar    |            | Flip Decoders                                                    |     |

| 5.2  |           |            | lying GRM to List-Flip Decoder                                   |     |

|      | 5.2.1     |            | Path Requirements in SCLF with GRM                               |     |

|      | 5.2.2     |            | Estimates                                                        |     |

| 5.3  | List-Flir |            | with LLRM                                                        |     |

|      | 5.3.1     |            | on of Restart Path in LLRM                                       |     |

|      | 5.3.2     |            | Estimates                                                        |     |

| 5.4  | Selection |            | rt Locations in LLRM                                             |     |

|      | 5.4.1     |            | Based on Code Construction                                       |     |

|      | 5.4.2     |            | ity-based Design                                                 |     |

| 5.5  |           |            | e Analysis                                                       |     |

| 5.6  |           |            | S                                                                |     |

|      | 5.6.1     |            | rrection Performance                                             |     |

|      | 5.6.2     |            | Estimates                                                        |     |

|      | 5.6.3     | •          | Execution Time                                                   |     |

| 5.7  |           | _          |                                                                  |     |

| CHAP | TER 6     | EARLY-     | TERMINATION MECHANISMS FOR FLIP DECODERS                         | 105 |

| 6.1  |           |            | echanism For Flip Decoder                                        |     |

|      | 6.1.1     |            | tion                                                             |     |

|      | 6.1.2     |            | ecoder with Early-Stopping Mechanism                             |     |

|      |           | 6.1.2.1    | Summary of DSCF Decoding                                         |     |

|      |           | 6.1.2.2    | Early-Stopping Metric                                            |     |

|      |           | 6.1.2.3    | Early-Stopping Algorithm                                         |     |

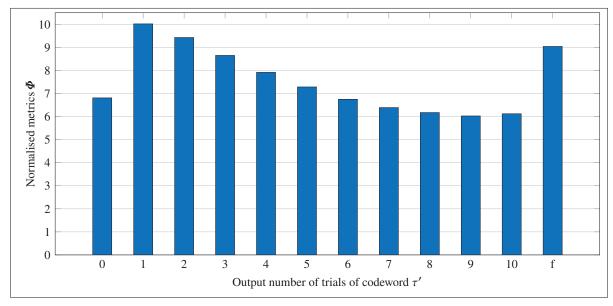

|      | 6.1.3     |            | g the Threshold from the Metric Distribution                     |     |

|      | 0.1.0     | 6.1.3.1    | Average Early-Stopping Metric Distribution                       |     |

|      |           | 6.1.3.2    | Defining the Threshold Metric and the Reduced Number of Maximum  |     |

|      |           |            | Trials                                                           | 109 |

|      | 6.1.4     | Simulation | on Results                                                       | 110 |

|      |           | 6.1.4.1    | Average Execution Time and Variance                              |     |

|      |           | 6.1.4.2    | Error-Correction Performance                                     |     |

|      | 6.1.5     | Conclusi   | on on Early-Stopping Mechanism for Flip Decoder                  |     |

| 6.2  | Flip Dec  |            | er Fixed Channel-Production Rate                                 |     |

|      | 6.2.1     |            | tion                                                             |     |

|      | 6.2.2     |            | Model with Fixed Channel Production Rate                         |     |

|      |           | 6.2.2.1    | Channel Block                                                    |     |

|         |         | 6.2.2.2    | Buffer Block                                                    | 115 |

|---------|---------|------------|-----------------------------------------------------------------|-----|

|         |         | 6.2.2.3    | Decoder Block                                                   | 115 |

|         | 6.2.3   | Control N  | Mechanisms                                                      | 115 |

|         |         | 6.2.3.1    | Codeword-Dropping Mechanism                                     | 116 |

|         |         | 6.2.3.2    | Multi-Threshold Mechanism                                       | 117 |

|         | 6.2.4   | Threshol   | d-Selection Methodology                                         | 117 |

|         | 6.2.5   | Simulation | on Results                                                      | 118 |

|         |         | 6.2.5.1    | Simulation Setup                                                | 119 |

|         |         | 6.2.5.2    | Simulation Algorithm                                            | 120 |

|         |         | 6.2.5.3    | State of the Buffer Over the Course of Simulation               | 121 |

|         |         | 6.2.5.4    | Error-correction performance                                    | 121 |

|         |         | 6.2.5.5    | Conclusion on Flip Decoding Under Fixed Channel-Production Rate | 122 |

| 6.3     | Conclus | ion        |                                                                 | 123 |

| CONC    | LUSION  | AND RE     | COMMENDATIONS                                                   | 125 |

| APPE    | NDIX I  |            | ONAL ANALYSIS FOR LIST-FLIP DECODERS WITH PROPOSED NISMS        | 131 |

| I ICT ( | TE DEEE | RENCES     |                                                                 | 135 |

# LIST OF TABLES

|           |                                                                                                                                                                                                                                                                    | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1.1 | Summary of implementations and scaling parameters to the target 65 nm technology                                                                                                                                                                                   | 22   |

| Table 1.2 | Hardware comparisons of state-of-the-art SC, Fast-SSC, and SCL decoders                                                                                                                                                                                            | 22   |

| Table 1.3 | Area breakdown for the SC and SCL decoder implementations for $N = 1024$ polar code                                                                                                                                                                                | 23   |

| Table 2.1 | Hardware comparisons of state-of-the-art SC, SCF, and SCL decoders for a (1024, 512) code                                                                                                                                                                          | 37   |

| Table 2.2 | Hardware comparisons of state-of-the-art DSCF and SCL decoders for a (1024, 512) code                                                                                                                                                                              | 38   |

| Table 3.1 | Memory estimates and overhead for decoders with and without the simplified restart mechanism (SRM)                                                                                                                                                                 | 49   |

| Table 3.2 | Reductions of the execution-time characteristics by applying the SRM to flip decoders compared to original decoders at the frame-error rate (FER) of $10^{-2}$                                                                                                     | 51   |

| Table 3.3 | Memory estimates and overhead for flip decoders with and without the GRM for a (1024, 512 + 11) code                                                                                                                                                               | 63   |

| Table 3.4 | Reduction $\Delta \overline{\mathcal{L}}_{flip}$ (3.13) by applying the GRM to flip decoders at the FER of $10^{-2}$                                                                                                                                               | 65   |

| Table 3.5 | Reduction $\Delta\overline{\mathcal{L}}_{\rm flip}$ (3.13) by applying the GRM and SRM to DSCF-3 decoder at the FER $10^{-2}$ .                                                                                                                                    | 65   |

| Table 4.1 | Summary of the key differences between execution-time reduction mechanisms for flip decoders based on SCF.                                                                                                                                                         | 70   |

| Table 4.2 | Upper bounds on the length $N_v$ of special nodes in FSSC for the Fast-SCF and Fast-DSCF- $\omega$ decoders with $\omega = \{1, 2, 3\}$                                                                                                                            | 71   |

| Table 4.3 | Execution time (in clock cycles (CCs)) of SC, SC <sub>LRT</sub> and Fast-SSC decoders for the 3GPP's next-generation mobile-communication standard (5G) polar codes. The limits on length $N_{\nu}$ in Fast-SSC are applied according to $\omega = 1$ in Table 4.2 | 74   |

| Table 4.4 | Reduction $\Delta \overline{\mathcal{L}}_{\text{flip}}$ (4.17) by applying the GRM to flip decoders with different baseline algorithms at the FER $10^{-2}$                                                                                                        | 80   |

| Table 4.5 | Reduction $\Delta \overline{\mathcal{L}}_{\text{flip}}$ (4.17) by applying the GRM, SRM and latency-reducing technique (LRT) to DSCF-3 decoder at the FER $10^{-2}$                                                                                                | 80   |

| Table 5.1 | Memory estimates and overhead by applying GRM for DSCLF-2 and DSCLF-3 decoders in two considered scenarios.                                                                                                                                                        | 89   |

| Table 5.2 | Memory estimates and overhead for list-flip decoders with $L = 2$ with LLRM, with GRM and the original decoders                                                                                                                                                    | 100  |

| Table 5.3 | Reduction $\Delta \overline{\mathcal{L}}_{\text{lflip}}$ (5.24) in % by applying the LLRM and GRM to list-flip decoders with $L=2$ at FER $10^{-2}$                                                                                                                | 103  |

# LIST OF FIGURES

|             |                                                                                                                                                                      | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

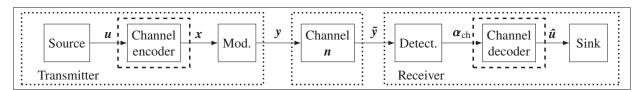

| Figure 1.1  | Simplified block diagram of the digital communication system                                                                                                         | 9    |

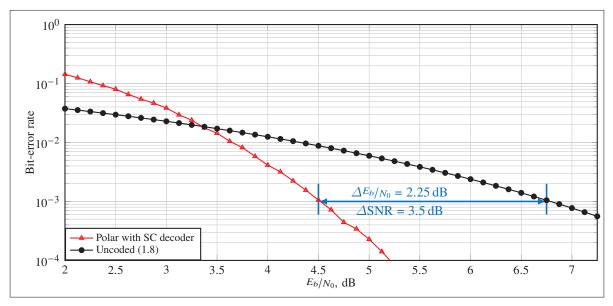

| Figure 1.2  | Error-correction performance of uncoded vs polar-encoded messages, both of length $N = 128$ . Polar codes of rate $R = \frac{3}{4}$ are decoded by the SC decoder    | 12   |

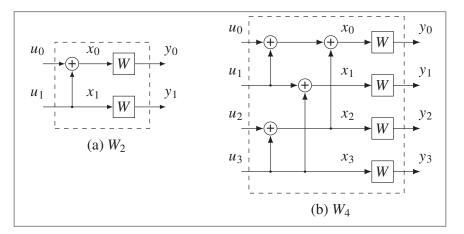

| Figure 1.3  | Construction of the channels $W_N$ with $N = 2$ and $N = 4$                                                                                                          | 13   |

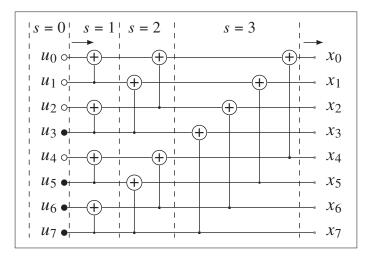

| Figure 1.4  | Encoder graph for an (8, 4) polar code                                                                                                                               | 15   |

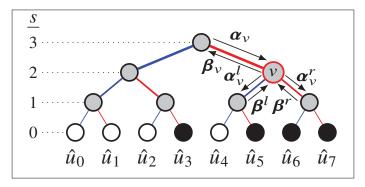

| Figure 1.5  | SC decoding tree for an $(8, 4)$ polar code with a focus on a node $v$ of length $N_v = 4$                                                                           | 16   |

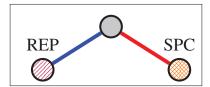

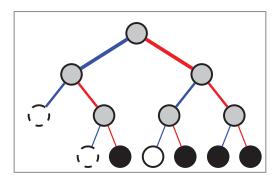

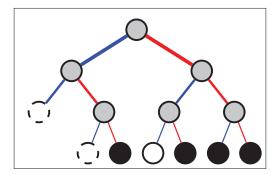

| Figure 1.6  | Fast-SSC decoding tree for an (8,4) polar code                                                                                                                       | 19   |

| Figure 1.7  | SC <sub>LRT</sub> decoding tree for an (8, 4) polar code                                                                                                             | 19   |

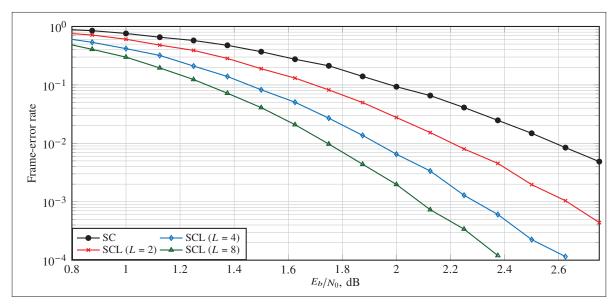

| Figure 1.8  | Error-correction performance of SC vs SCL decoders for a (1024, 512) polar code.  An 11-bit cyclic-redundancy check (CRC) is applied by SCL decoder                  | 21   |

| Figure 2.1  | Block-diagram of SCF decoding algorithm                                                                                                                              | 25   |

| Figure 2.2  | Block-diagram of DSCF decoding algorithm                                                                                                                             | 26   |

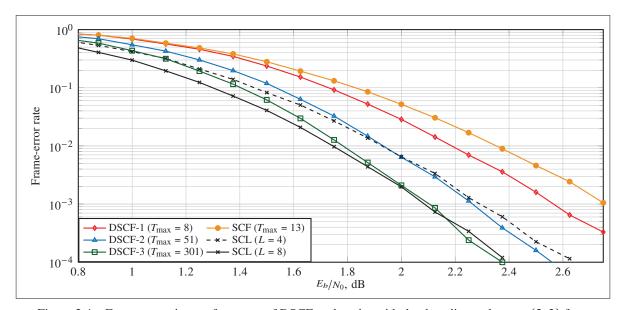

| Figure 2.3  | Error-correction performance of SCF and DSCF-1 decoders for a (1024, 512 + 11) polar code                                                                            | 28   |

| Figure 2.4  | Error-correction performance of DSCF- $\omega$ decoder with the decoding order $\omega \in \{2,3\}$ for a (1024, 512 + 11) polar code                                | 28   |

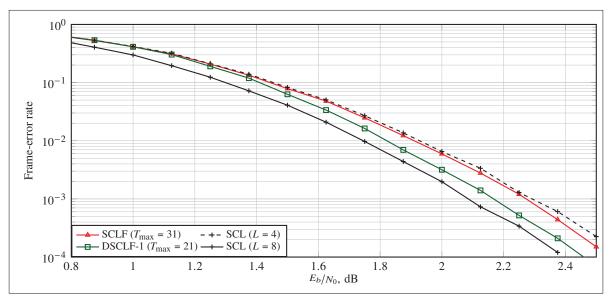

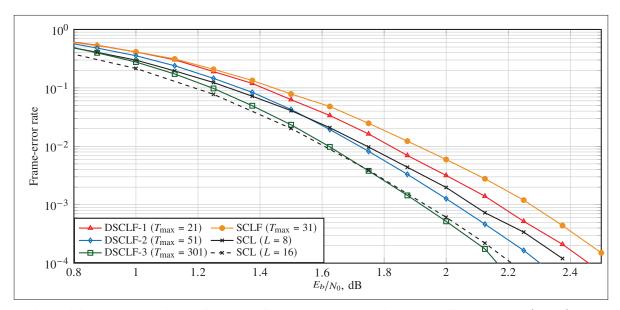

| Figure 2.5  | Error-correction performance of SCLF and DSCLF-1 decoders with $L=2$ for a (1024, 512 + 11) polar code                                                               | 32   |

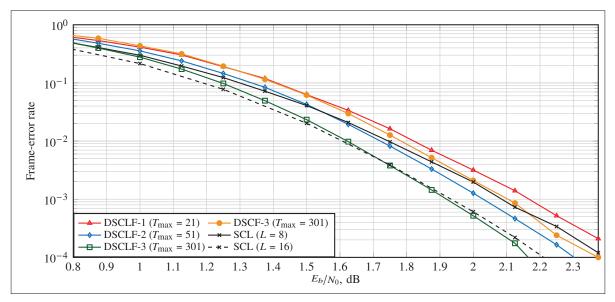

| Figure 2.6  | Error-correction performance of DSCLF- $\omega$ decoder with the decoding order $\omega \in \{2,3\}$ and $L=2$ for a (1024, 512 + 11) polar code                     | 32   |

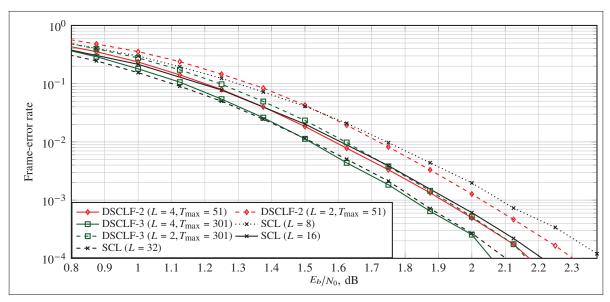

| Figure 2.7  | Error-correction performance of DSCLF- $\omega$ decoder with $\omega \in \{2,3\}$ and $L = \{2,4\}$ for a (1024, 512 + 11) polar code                                | 33   |

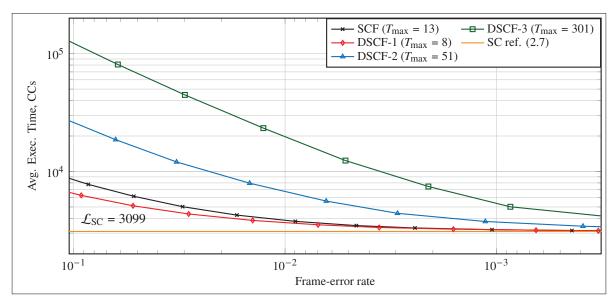

| Figure 2.8  | Average execution time of flip SCF and DSCF- $\omega$ decoders with the decoding order $\omega \in \{1, 2, 3\}$ for a (1024, 512 + 11) polar code                    | 35   |

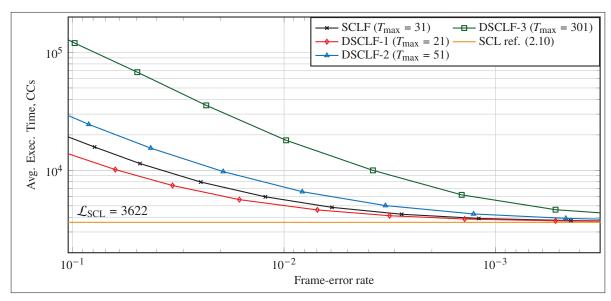

| Figure 2.9  | Average execution time of list-flip SCLF and DSCLF- $\omega$ decoders with the decoding order $\omega \in \{1, 2, 3\}$ and $L = 2$ for a (1024, 512 + 11) polar code | 36   |

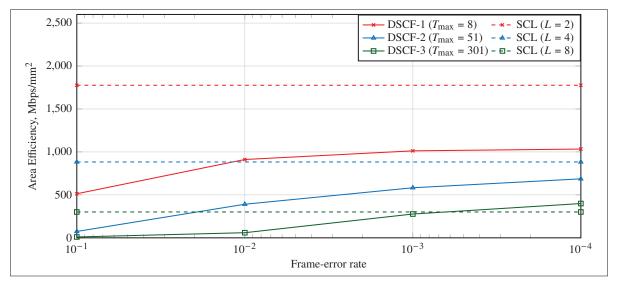

| Figure 2.10 | Area efficiency of Fast-DSCF- $\omega$ and SCL decoders at various FER points for a (1024, 512) polar code                                                           | 38   |

| Figure 3.1  | The modified SC trial SC $(\psi_{t'}, \boldsymbol{\varepsilon}_{t'})$ with the bit-flipping index $i_1 = 5$ in SCF with the SRM for an $(8,4)$ polar code            | 43   |

| Figure 3.2  | Memory sketch of SC, SCF and SCF with SRM                                                                                                                            | 45   |

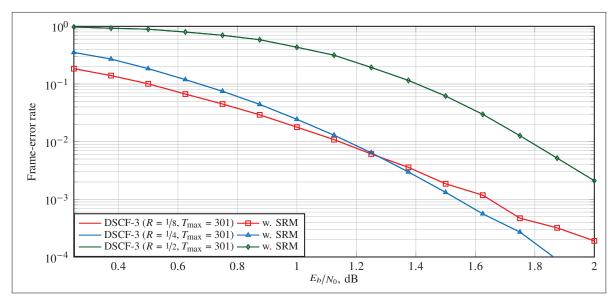

| Figure 3.3  | Error-correction performance of DSCF-3 decoder for a (1024, 128 + 11) polar code                                                                                     | 48   |

| Figure 3.4  | Error-correction performance of DSCF-3 decoder with and without the SRM for polar code with $N=1024$ and $R=\{1/8,1/4,1/2\}$                                                                                                                                                                              | 49 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

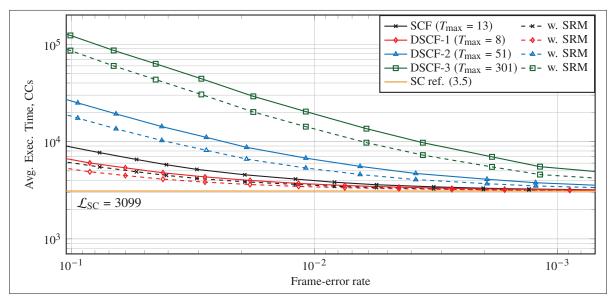

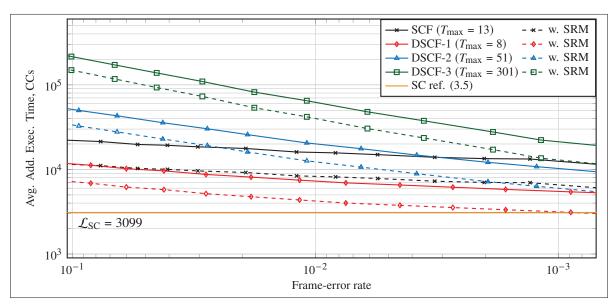

| Figure 3.5  | Average execution time of SCF and DSCF- $\omega$ decoders with and without the SRM for a (1024, 128 + 11) polar code                                                                                                                                                                                      | 50 |

| Figure 3.6  | Average additional execution time of SCF and DSCF- $\omega$ decoders with and without the SRM for a (1024, 128 + 11) polar code                                                                                                                                                                           | 51 |

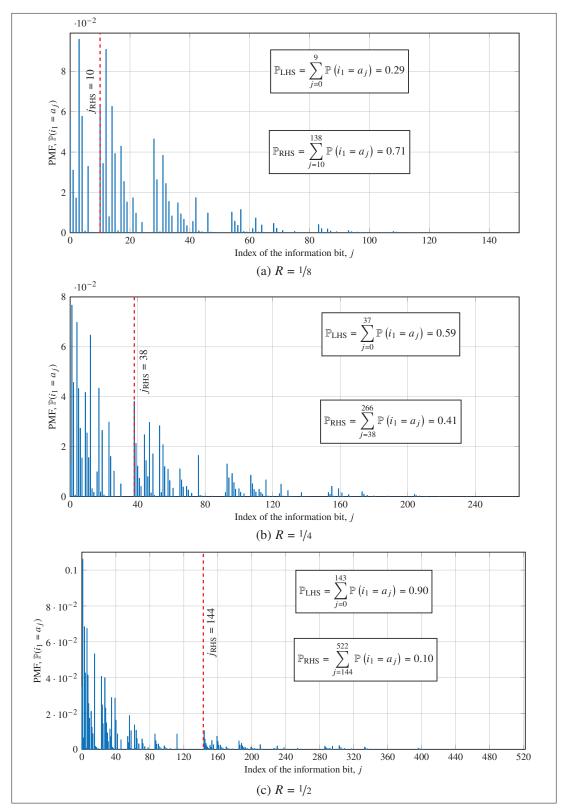

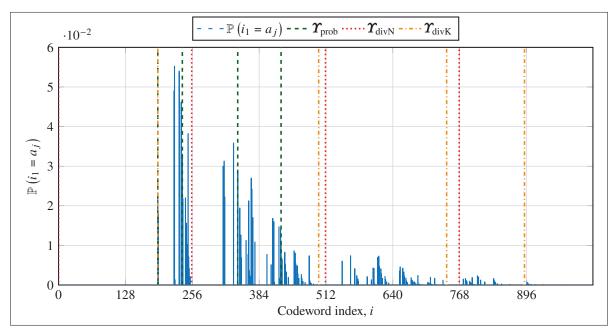

| Figure 3.7  | Probability-mass function (PMF) of the information-bit location $a_j \in \mathcal{A}$ being the first bit-flipping candidate $i_1 = \varepsilon_{t'}$ (0) under DSCF-3 decoding for the code rates $R = \{1/8, 1/4, 1/2\}$ . Probabilities $\mathbb{P}_{LHS}$ and $\mathbb{P}_{RHS}$ are inside each plot | 54 |

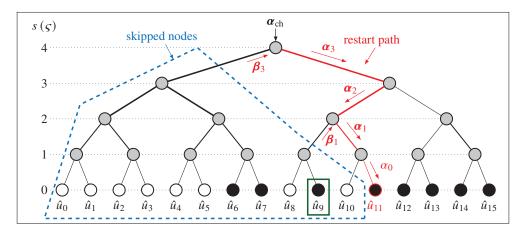

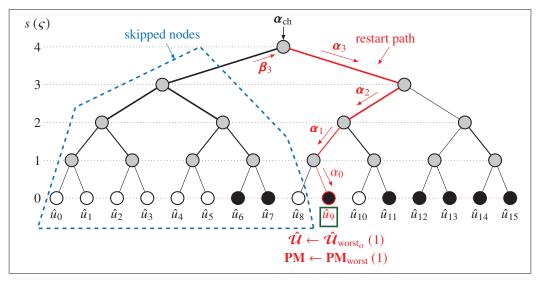

| Figure 3.8  | The modified SC trial SC $(\psi_{t'}, \boldsymbol{\varepsilon}_{t'})$ with the bit-flipping index $i_1 = 9$ and the restart location $\psi_{t'} = 11$ , in SCF with the GRM for a $(16, 8)$ polar code                                                                                                    | 57 |

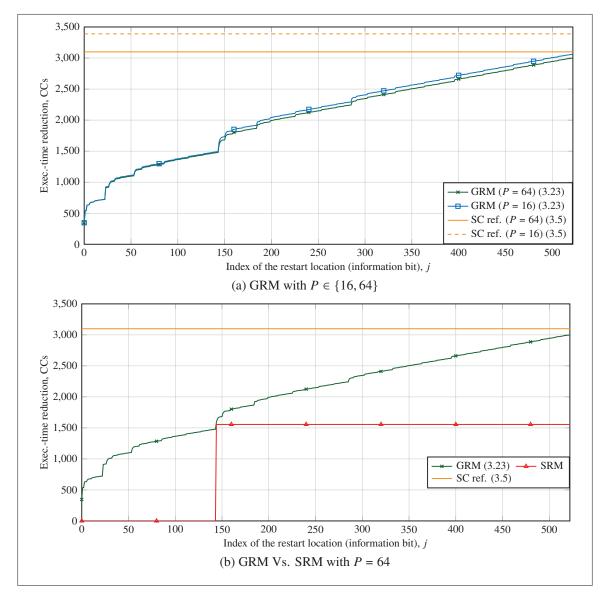

| Figure 3.9  | Execution-time reduction of SC $(\psi_{t'}, \boldsymbol{\varepsilon}_{t'})$ in the GRM estimated by (3.23) for a (1024, 512 + 11) code with $\psi_{t'} = a_j \in \mathcal{A}$                                                                                                                             | 59 |

| Figure 3.10 | Memory sketch of SC, SCF and SCF decoders with the GRM                                                                                                                                                                                                                                                    | 60 |

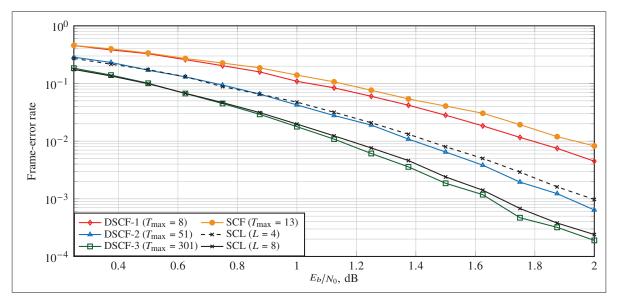

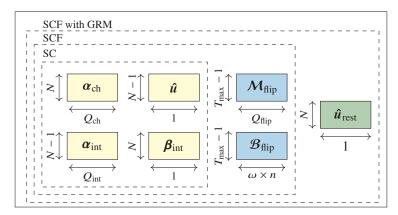

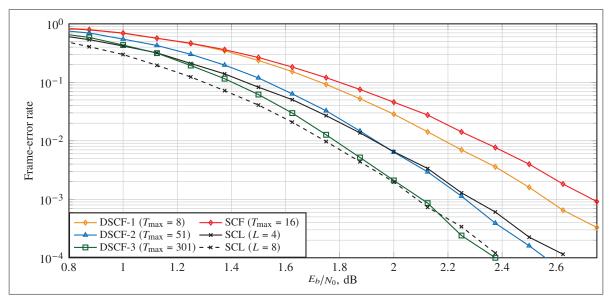

| Figure 3.11 | Error-correction performance for a $(1024, 512 + 11)$ code of SCF and DSCF- $\omega$ decoders with decoding order $\omega \in \{2, 3\}$ , and of SCL decoder with $L = 4$ and $L = 8$                                                                                                                     | 62 |

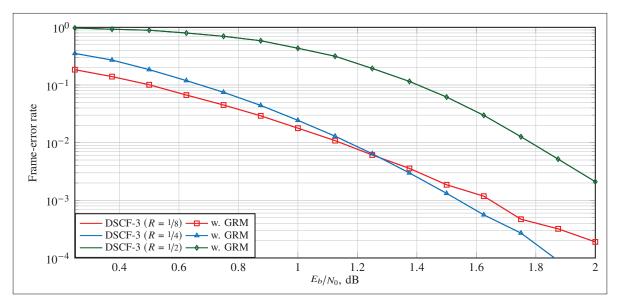

| Figure 3.12 | Error-correction performance for a $N = 1024$ polar code with $R = \{1/8, 1/4, 1/2\}$ of DSCF-3 decoder with and without the GRM                                                                                                                                                                          | 63 |

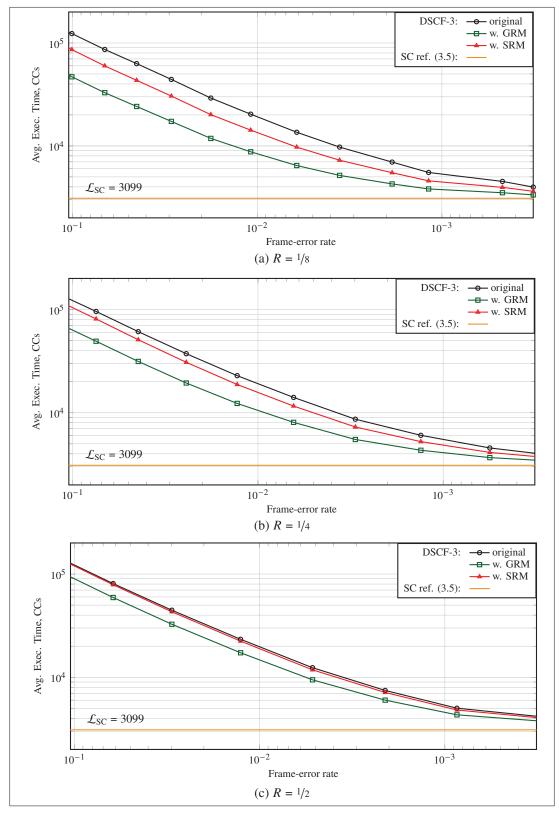

| Figure 3.13 | Average execution time of DSCF-3 decoder with the GRM, SRM and original decoder for $R \in \{1/8, 1/4, 1/2\}$ .                                                                                                                                                                                           | 64 |

| Figure 4.1  | Fast-SSC decoding tree for an (8,4) polar code                                                                                                                                                                                                                                                            | 68 |

| Figure 4.2  | SC <sub>LRT</sub> decoding tree for an (8, 4) polar code                                                                                                                                                                                                                                                  | 69 |

| Figure 4.3  | Execution-time reduction capability of the GRM with FSSC and SC <sub>LRT</sub> with $P=64$ for a (1024, 256 + 11) polar code with $\psi_{t'}=a_j\in\mathcal{A}$                                                                                                                                           | 75 |

| Figure 4.4  | Average execution time of DSCF-3 decoder with and without the proposed GRM for $\text{dec} \in \{\text{SC}, \text{SC}_{\text{LRT}}\}\ $ and for $R \in \{1/8, 1/4, 1/2\}$                                                                                                                                 | 78 |

| Figure 4.5  | Average execution time of DSCF-3 decoder with and without the proposed GRM for $\text{dec} \in \{\text{SC,FSSC}\}\ $ and for $R \in \{1/8,1/4,1/2\}$                                                                                                                                                      | 79 |

| Figure 5.1  | The modified SCL trial SCL $(\psi_{t'}, \boldsymbol{\varepsilon}_{t'})$ with the path-flipping index $i_1 = 9$ and the restart location $\psi_{t'} = 9$ , in SCLF with the GRM for a $(16, 8)$ polar code                                                                                                 | 86 |

| Figure 5.2  | Memory sketch of SCL, SCLF and SCLF with GRM                                                                                                                                                                                                                                                              | 87 |

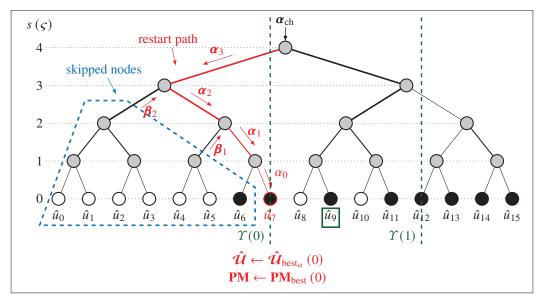

| Figure 5.3  | The modified SCL trial SCL $(\psi_{t'}, \mathbf{\varepsilon}_{t'})$ with the path-flipping index $i_1 = 9$ and the restart location $\psi_{t'} = \Upsilon(0) = 7$ , in SCLF with the LLRM for a (16, 8) polar code                                                                                        | 91 |

| Figure 5.4  | Memory sketch of SCL, SCLF and SCLF with LLRM                                                                                                                                                                                                                                                             | 92 |

| Figure 5.5  | PMF of the bits <i>i</i> being the first path-flipping candidate $i_1 = \varepsilon_{t'}$ (0) of the DSCLF-3 decoder for a (1024, 512 + 11) code. Restart locations $\Upsilon$ are represented by the vertical lines                                                                                      | 95 |

| Figure 5.6 | Error-correction performance of DSCLF- $\omega$ decoder with the decoding order $\omega \in \{1, 2, 3\}$ and $L = 2$ for a (1024, 512 + 11) polar code                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.7 | Average execution time of DSCLF-3 decoder with $L=2$ with LLRM, GRM, and original decoder for $R \in \{1/4, 1/2, 3/4\}$                                                                           |

| Figure 6.1 | Distribution of early-stopping metrics depending on the number of trials required by the original DSCF-1 decoder at the FER of $10^{-2}$ for a (1024, 512 + 16) polar code 110                    |

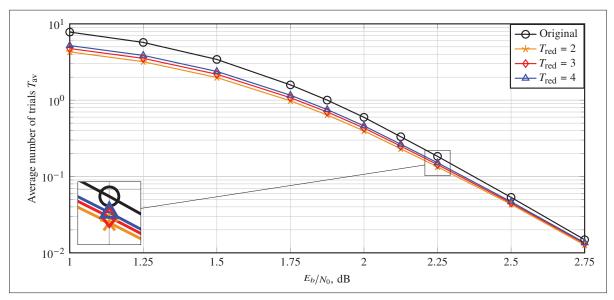

| Figure 6.2 | Average number of trials beyond the first SC decoding pass for various $E_b/N_0$ points of the DSCF-1 decoder for a (1024, 512 + 16) code, with and without the proposed early-stopping mechanism |

| Figure 6.3 | Variance of the number of trials for various $E_b/N_0$ points for a DSCF-1 decoder for a (1024, 512 + 16) code, with and without the proposed early-stopping mechanism                            |

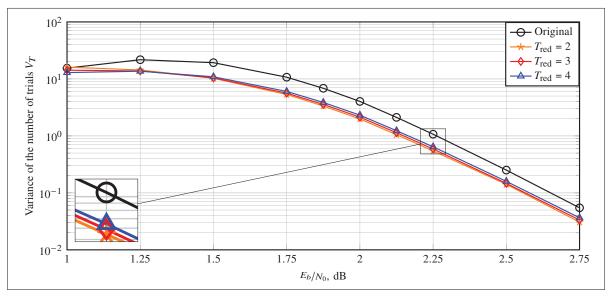

| Figure 6.4 | FER of the DSCF-1 decoder for a (1024, 512 + 16) with and without the proposed early-stopping mechanism                                                                                           |

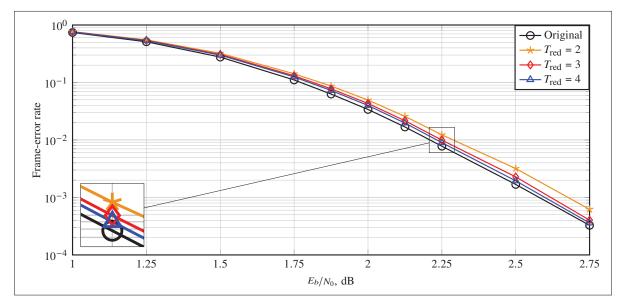

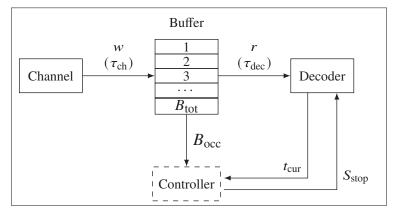

| Figure 6.5 | System model containing simplified blocks of the channel, buffer, controller, and flip decoder. Arrows indicate the data flow between the blocks                                                  |

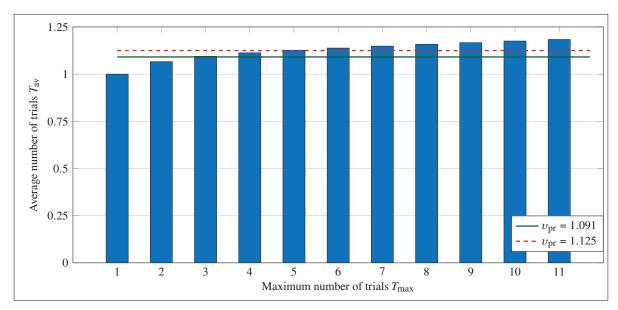

| Figure 6.6 | Average execution time of a DSCF-1 decoder with various maximum number of trials $T_{\text{max}}$ . Two examples of production coefficients $v_{\text{pr}}$ are shown as horizontal lines 118     |

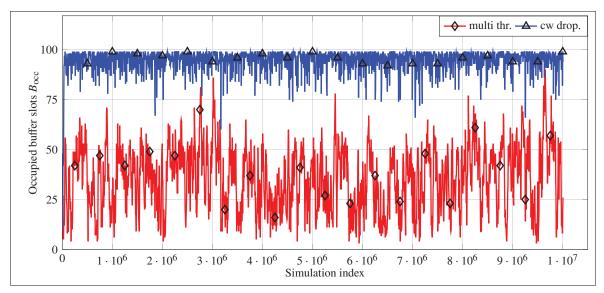

| Figure 6.7 | Number of occupied buffer slots over the course of a simulation of the codeword-dropping and the multi-threshold mechanisms for $^{E_b/N_0}$ point of 2.25 dB and $\upsilon_{\rm pr} = 1.125$     |

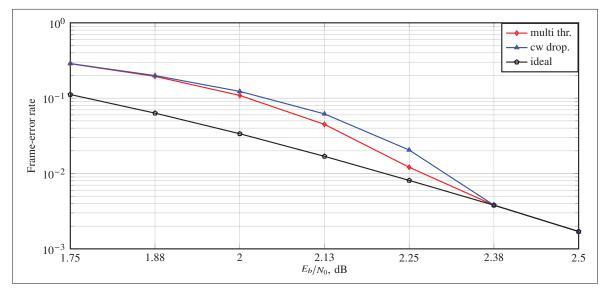

| Figure 6.8 | FER of the codeword-dropping and the multi-threshold mechanisms for the range of $E_b/N_0$ and $\upsilon_{pr} = 1.125$                                                                            |

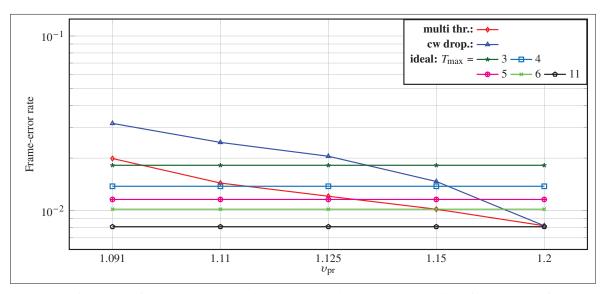

| Figure 6.9 | FER of the codeword-dropping and the multi-threshold mechanisms for the range of the production coefficient $v_{pr}$ and $E_b/N_0$ of 2.25 dB                                                     |

# LIST OF ALGORITHMS

| 1 | Flip (SCF or DSCF) decoding with the SRM                                                                        | 44  |

|---|-----------------------------------------------------------------------------------------------------------------|-----|

| 2 | Obtaining the PMF of the path-flipping locations $i_1 = a_j$ for an SCLF decoder by simulations                 | 94  |

| 3 | Design of restart locations $m{\varUpsilon}_{prob}$ based on PMF of path-flipping locations for an SCLF decoder | 94  |

| 4 | DSCF decoding algorithm with early stopping                                                                     | 107 |

| 5 | Obtaining the metric distribution by simulation                                                                 | 109 |

| 6 | Generating the controller signals according to the states of the buffer and decoder                             | 116 |

| 7 | Simulation algorithm of the system model with the fixed channel production data rate                            | 120 |

# LIST OF GLOSSARIES

ASIC application-specific integrated circuit. AWGN additive white Gaussian noise. **B-DMC** binary discrete memoryless channel. BER bit-error rate. BPSK binary phase-shift keying. CC clock cycle. CRC cyclic-redundancy check. **DSCF** dynamic successive-cancellation flip. **DSCLF** dynamic successive-cancellation list flip. eMBB enhanced mobile broadband. **FER** frame-error rate. **GRM** generalized restart mechanism. **IoT** Internet of things. LDPC low-density parity check. **LHS** left-hand side. **LLR** log-likelihood ratio. LLRM limited-locations restart mechanism. **LRT** latency-reducing technique. LSB least significant bit. mMTC massive machine-type communications.

**5G** 3GPP's next-generation mobile-communication standard.

| PMF probability-mass function.                 |  |  |  |  |  |  |

|------------------------------------------------|--|--|--|--|--|--|

| PS partial-sum.                                |  |  |  |  |  |  |

| <b>PSCF</b> partitioned SCF.                   |  |  |  |  |  |  |

| <b>PSCLF</b> partitioned SCLF.                 |  |  |  |  |  |  |

| <b>R0</b> rate-0.                              |  |  |  |  |  |  |

| R1 rate-1.                                     |  |  |  |  |  |  |

| REP repetition.                                |  |  |  |  |  |  |

| RHS right-hand side.                           |  |  |  |  |  |  |

| SC successive-cancellation.                    |  |  |  |  |  |  |

| <b>SCF</b> successive-cancellation flip.       |  |  |  |  |  |  |

| SCL successive-cancellation list.              |  |  |  |  |  |  |

| <b>SCLF</b> successive-cancellation list flip. |  |  |  |  |  |  |

| <b>SNR</b> signal-to-noise ratio.              |  |  |  |  |  |  |

| SPC single-parity-check.                       |  |  |  |  |  |  |

| <b>SRM</b> simplified restart mechanism.       |  |  |  |  |  |  |

| SSC Simplified SC.                             |  |  |  |  |  |  |

|                                                |  |  |  |  |  |  |

|                                                |  |  |  |  |  |  |

#### INTRODUCTION

Digital communication systems are integrated into many areas of modern technology. Networks such as the Internet of things (IoT) require low-power transmitters and receivers to provide service for networks with strict requirements on production cost and battery life. The 5G networks have gained solid ground and are being actively implemented in modern digital systems. The massive machine-type communications (mMTC) service of 5G fits the requirements of Internet of things (IoT) networks, and it will be expanded and further improved in the 5G advanced 3GPP (2018).

The transmitted information can often get corrupted due to noises and disturbances present in the communication channel. A straightforward retransmission can solve the problem to a certain extent. However, it increases communication delay, which restrains communication capabilities. Error detection and correction algorithms on the receiver's side are crucial for reliable and sustainable communication systems, such as satellite and 5G networks. Nevertheless, blocks implementing error detection and correction, particularly decoding, are typically among the most resource-intensive blocks of the entire communication system. Therefore, developing efficient error-correction decoding algorithms is crucial, especially for systems with strict resource requirements, such as IoT networks.

Polar codes are linear block codes that asymptotically achieve the channel capacity under the low-complexity SC decoding as the code length approaches infinity (Arıkan, 2009). Polar codes have explicit construction and the low-complexity SC decoding algorithm. Unfortunately, as shown in the study by Balatsoukas-Stimming, Giard & Burg (2017), polar codes with the SC decoder provide mediocre error-correction performance at short-to-moderate code lengths compared to other modern channel codes like low-density parity check (LDPC). Nevertheless, low-complexity encoding and decoding algorithms make polar codes suitable for mMTC service of 5G, as stated in the work of Zhou, Miao, Liu & Liu (2021).

#### **Problem Statement**

Tal & Vardy (2011) have proposed the SCL decoding algorithm to improve the error-correction performance of the SC decoder for polar codes. This algorithm decodes a codeword by generating a list of L parallel candidates throughout decoding. In their following work, Tal & Vardy (2015) have concatenated the information block with the CRC code before passing it through a polar encoder. This allows the SCL decoder to select the most likely transmitted word from the final list of candidates if the initial selection strategy fails. The resulting CRC-aided SCL decoder significantly improves error-correction performance to the extent that polar codes are selected to protect the control channel of the enhanced mobile broadband (eMBB) service in 5G (3GPP, 2018). However, the SCL decoder implementations require more resources compared to the SC decoder because of their parallel decoding schedule.

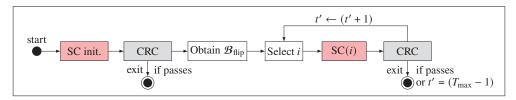

Afisiadis, Balatsoukas-Stimming & Burg (2014) have proposed the SCF decoding to improve the error-correction performance of the SC decoding. Unlike the SCL, which decodes a codeword with L parallel candidates, SCF generates the candidates across multiple decoding trials, i.e., decoding attempts. A list of bit-flipping candidates is constructed at the end of an initial unsuccessful SC decoding trial. This list contains the bit locations estimated as the least reliable ones. At each additional trial, a decision bit from the list is flipped during the course of the SC decoding before normal decoding is resumed. A block of information bits is concatenated with the CRC code before passing it through a polar encoder. This allows the SCF decoder to validate an estimated information word and exit decoding when the CRC passes. In their study, Afisiadis *et al.* (2014) have presented that the SCF decoder achieves the same error-correction performance as the SCL with a small list size L.

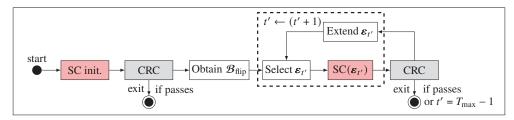

The DSCF algorithm was proposed by Chandesris, Savin & Declercq (2018) with two major contributions: (a) a more accurate metric to construct the list of the bit-flipping candidates, and (b) algorithmic modifications where multiple bits can be simultaneously flipped per decoding trial and where the list of candidates is dynamically updated. As a result of these modifications, the DSCF decoding achieves the same performance as the SCL with a medium list size L.

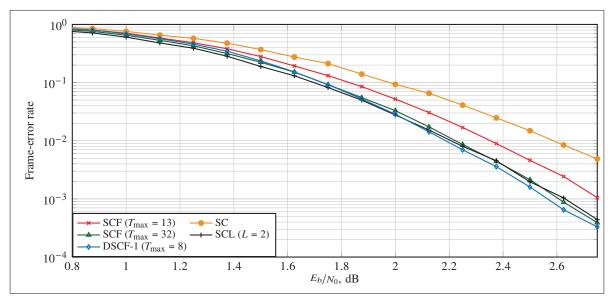

The SCLF decoding is proposed by Yongrun, Zhiwen, Nan & Xiaohu (2018) with the idea of combining the SCL and SCF decoding strategies. The standard SCL decoding is performed at the initial trial. If none of the L paths pass the CRC at the end of this trial, a list of path-flipping candidates is constructed. The path-flipping strategy for the SCLF decoding was first introduced by Cheng, Liu, Zhang & Ren (2019). The additional decoding trial follows the standard SCL algorithm until the path-flip location, where all initially discarded paths are selected as opposed to the original selection criteria. The standard SCL decoding is then resumed to decode the remaining bits in a codeword. The SCLF decoder has the  $T_{\rm max}$  trials to decode a codeword, and if failed, the codeword is deemed undecodable. Then, the DSCLF decoding was proposed by Shen, Balatsoukas-Stimming, You, Zhang & Burg (2022), where the DSCF algorithm strategy was adapted to SCLF. This adaptation has allowed the authors to perform multi-path flipping during an additional decoding trial. The SCLF decoders allow for a balance between SCL and SCF decoders to achieve the target error-correction performance.

Despite improved error-correction performance, the SCF and SCLF decoding algorithms and their variations introduce variability in execution time. This variability poses challenges in implementing receivers with fixed-time operations. Giard, Balatsoukas-Stimming, Müller, Bonetti, Thibeault, Gross, Flatresse & Burg (2017) and Ercan, Tonnellier, Doan & Gross (2020a) have proposed architectural designs. These designs demonstrate that the SCF and DSCF decoders are more efficient in hardware resources and energy requirements compared to the SCL decoder.

However, the average execution time of SCF and DSCF decoders is higher than the latency of the SCL decoder. Therefore, mechanisms that can reduce this average execution time are needed.

#### **Research Objectives**

The main objective of this doctoral study is to design energy-efficient flip decoders of polar codes, based on the SCF algorithm. In particular, the goal is to develop mechanisms to improve the execution-time characteristics of flip decoders with minimal to no impact on the error-correction performance and hardware resources. The analysis of hardware resources focuses on decoder memory.

To achieve the main objective, the following sub-objectives are identified:

- 1. Design universal restart mechanisms that skip computationally intensive operations in flip decoders.

- Derive a methodology for analyzing resource requirements and execution-time characteristics for realistic hardware implementations.

- 3. Modify the mechanisms to integrate with existing fast decoding techniques to further improve the execution-time characteristics of flip decoders.

- 4. Design efficient early-termination mechanisms for flip decoders that are adapted to specific channel or latency conditions.

This study proposes the following mechanisms for flip decoders of polar codes:

#### 1. Generalized Restart Mechanism (GRM) for Flip Decoders.

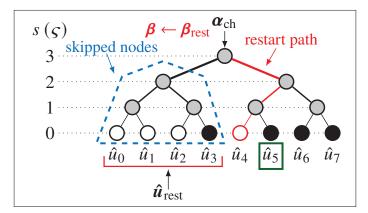

The flip decoders can achieve the error-correction performance of the state-of-the-art SCL decoders. However, they can only achieve this with a high maximum number of trials, resulting in increased average and worst-case execution times. In our proposed GRM, the parts of the tree to estimate a bit-flipping candidate and all of the prior bits of each additional decoding trial are skipped. The decoding tree is traversed from the root along the restart path to directly estimate the restart bit. To perform such a restart, the bit estimates must be stored in memory at the end of the initial unsuccessful decoding trial. The GRM reduces the average execution time of the DSCF-3 decoder by 26% to 60% without any negative effect on the error-correction performance. This decoder achieves the error-correction performance of the state-of-the-art SCL decoder. The GRM results in approximately 4% of additional memory.

#### 2. Modified Generalized Restart Mechanism for Fast Decoding Techniques.

Existing fast decoding techniques improve the execution-time characteristics of the flip decoders. The GRM proposed in this study is designed to be adaptable to these fast decoding techniques. The modified GRM reduces the average execution time by 15% to 22% when applied to Fast-DSCF-3 decoder. This reduction is in addition to the reduction already attained by fast decoding. Compared to the original decoding, the modified GRM requires approximately 4% of additional memory.

#### 3. LLRM for List-Flip Decoders.

List-flip decoders based on SCLF allow for a balance between the SCL and SCF decoders to achieve the desired error-correction performance. Similar to flip decoders, they also exhibit high average and worst-case execution times. Applying the GRM to list-flip decoders highly improves the execution-time characteristics. However, this improvement results in enormous memory overhead. To overcome the issue of memory overhead, the LLRM, a modification of the GRM, is proposed. Alongside this, the probability-based method for selecting restart locations is developed. This method aims to maximize the execution-time reduction while minimizing the memory overhead. The LLRM reduces the average execution time by 10% to 40% when applied to DSCLF-3 decoder. This decoder provides the strongest error-correction performance compared to other list-flip decoders. The LLRM results in approximately 2% memory overhead, whereas the GRM incurred 170% to 1500% memory overhead. According to the results, the proposed LLRM is the more appropriate algorithm for hardware implementations of the list-flip decoders.

# 4. Early-termination Mechanisms for Flip Decoders.

Two early-termination mechanisms, namely the early-stopping mechanism and the multi-threshold mechanism, are proposed to improve the execution time characteristics of flip decoders. The early-stopping mechanism attempts to differentiate undecodable codewords from decodable ones. It uses the proposed early-stopping metric and a predefined threshold. If the metric suggests a codeword is likely undecodable, the decoder attempts a reduced maximum number of trials. This number is much smaller than the initial maximum trials. The early-stopping mechanism reduces the average execution time of the DSCF-1 decoder by approximately 22% and execution-time variance by approximately 45%. This mechanism results in a minor error-correction loss of approximately  $0.05 \, \text{dB}$  at the target FER of  $10^{-2}$ . The proposed multi-threshold mechanism restrains the delay of a flip decoder depending on the state of the buffer to prevent overflow. This mechanism is implemented in the system where the channel produces data with a fixed rate, which closely approaches that of a single decoding trial. When applied to DSCF-1 decoder, our proposed multi-threshold mechanism allows to operate in a system with a fixed channel-production rate approximately 1.13 times lower than the rate associated with

a single decoding trial. This adjustment helps prevent buffer overflow. Compared to the ideal scenario, the proposed mechanism has a minor error-correction loss of approximately  $0.06 \, dB$  at the target FER of  $10^{-2}$ . The ideal scenario, where the decoder operates without constraints, leads to an unsustainable situation due to the rapid overflow of the buffer.

#### **Related Publications**

The following publications resulted throughout the course of the doctoral study:

- <u>I. Sagitov</u> and P. Giard, "An Early-Stopping Mechanism for DSCF Decoding of Polar Codes", *IEEE Workshop on Signal Processing Systems (SiPS)*, 2020, Coimbra, Portugal.

- I. Sagitov, C. Pillet, A. Balatsoukas-Stimming, and P. Giard, "Successive-Cancellation Flip Decoding of Polar Codes with a Simplified Restart Mechanism." *IEEE Wireless Communications and Networking Conference (WCNC)*, 2023, Glasgow, United Kingdom.

- C. Pillet, <u>I. Sagitov</u>, G. Domer, and P. Giard, "Partitioned Successive-Cancellation List Flip Decoding of Polar Codes." *IEEE Workshop on Signal Processing Systems (SiPS)*, 2024, Cambridge, USA.

- <u>I. Sagitov</u>, C. Pillet, and P. Giard, "Successive-Cancellation Flip Decoding of Polar Codes Under Fixed Channel-Production Rate." *arXiv preprint arXiv:2409.03051*, 2024.

- C. Pillet, <u>I. Sagitov</u>, D. Deslandes, and P. Giard, "Successive-Cancellation Flip and Perturbation Decoder of Polar Codes." *IEEE Wireless Communications and Networking Conference (WCNC)*, 2025, Milan, Italy (under review).

- <u>I. Sagitov</u>, C. Pillet, A. Balatsoukas-Stimming, and P. Giard, "Generalized Restart Mechanism for Successive-Cancellation Flip Decoding of Polar Codes." *J. Signal Process. Syst.*, 2024 (*under review*).

- <u>I. Sagitov</u>, C. Pillet, A. Balatsoukas-Stimming, and P. Giard, "Restart Mechanisms for the Successive-Cancellation List-Flip Decoding of Polar Codes." *J. Signal Process. Syst.*, 2024 (*under review*).

# **Thesis Organization**

The thesis is structured as follows to provide a comprehensive overview of the research problem, progress, and results.

- CHAPTER 1: Literature review describes the background of digital communication, channel coding, polar code construction, and polar encoding. This chapter also describes the SC, fast and simplified SC, and SCL decoding algorithms, along with a comparison of their error-correction performance. At the end of the chapter, the implementation results of the state-of-the-art decoders are summarized and compared.

- CHAPTER 2: This chapter discusses the background on flip decoding algorithms while describing the SCF and DSCF decoding algorithms, along with the SCLF and DSCLF list-flip decoding algorithms. This chapter provides detailed comparisons in terms of the error-correction performance for all flip decoders. Then, it describes the time model that aligns with the architectural design. Following this, a comparison of the average execution time for the flip decoders is provided. Then, the implementation results of the state-of-the-art flip decoders are summarized and compared.

- CHAPTER 3: This chapter describes two proposed mechanisms for flip decoders, namely, the SRM and the generalized restart mechanism (GRM). The SRM is presented with a detailed description of the algorithm, followed by methodologies for resource and execution-time analysis. The simulation results are presented, focusing on error-correction performance and average execution time. Following this, the effectiveness and drawbacks of the SRM are identified. This chapter also presents the GRM, an extension of the SRM. The algorithm of the GRM and methodologies for resource and execution-time analysis are presented. At the end of the chapter, the simulation results are provided to highlight the effectiveness of the proposed GRM to SCF and DSCF decoders.

- CHAPTER 4: This chapter describes our proposed modified GRM for flip decoders with fast decoding techniques. The algorithm and the assumptions for applying the proposed GRM in conjunction with fast decoding techniques are provided. Then, methodologies for resource and execution-time analysis are presented. At the end of the chapter, simulation results are presented, highlighting the effectiveness of the proposed GRM when combined with existing fast decoding techniques for flip decoders, such as Fast-SCF and Fast-DSCF decoders.

- CHAPTER 5: This chapter introduces the proposed limited-locations restart mechanism (LLRM) for list-flip decoders and explores the challenges associated with applying the previously proposed GRM to these decoders. It provides a detailed description of the LLRM algorithm and memory estimates. Following this, the chapter presents the proposed probability-based method to determine the restart locations in the LLRM. Then, the methodologies for resource and execution-time analysis are provided. At the end of the chapter, the simulation results are presented, demonstrating the effectiveness of the proposed LLRM to SCLF and DSCLF decoders.

- CHAPTER 6: This chapter discusses two early-termination mechanisms for flip decoders: the early-stopping mechanism and the multi-threshold mechanism. It begins with a comprehensive description of the proposed early-stopping mechanism, followed by simulation results that demonstrate its effectiveness for the DSCF decoder. This chapter then discusses flip decoding under a fixed channel-production rate, starting with a description of the system model. The core of the model is the control mechanism that regulates the decoder based on the state of the buffer. It introduces the straightforward codeword-dropping mechanism and then presents the proposed multi-threshold mechanism. The simulation results are provided, highlighting the effectiveness of the multi-threshold mechanism for the DSCF decoder under a fixed channel-production rate.

The thesis concludes with a summary of the work. It provides academic achievements and discusses the limitations of the proposed modifications. Additionally, it outlines potential future research directions.

# **CHAPTER 1**

#### LITERATURE REVIEW

Throughout the thesis, we use bold notations for vectors and matrices, while normal notations are used for single values (for example, a single element of the vector).

#### 1.1 Digital Communication System

Figure 1.1 Simplified block diagram of the digital communication system

A digital communication system is often represented by three main blocks: the transmitter, the channel, and the receiver. The block diagram of this system is depicted in Figure 1.1, with these three blocks surrounded by the dotted line. In the transmitter block, the source delivers the information bit vector  $\mathbf{u}$ , which has the length of k. The channel encoder applies the encoding algorithm, creating a codeword  $\mathbf{x} = \{x_0, \dots, x_i, \dots, x_{N-1}\}$ , which has the length of N. The code rate R is defined as R = k/N, and R < 1 is required to enable error-correction coding. Next, modulation is applied, converting the resulting bit stream into a signal vector  $\mathbf{y}$  that is transmitted over the channel. The channel affects the signal by adding noise vector  $\mathbf{n}$  to the signal, and the resulting signal  $\tilde{\mathbf{y}} = \mathbf{y} + \mathbf{n}$  is observed at the receiver. In the receiver, detection is made, where either soft or hard channel information is first observed. In the scope of this doctoral study, the soft channel information  $\alpha_{\rm ch} = \{\alpha_{\rm ch}(0), \dots, \alpha_{\rm ch}(i), \dots, \alpha_{\rm ch}(N-1)\}$  is considered. Next,  $\alpha_{\rm ch}$  is delivered to the channel decoder, where the error-correction decoding algorithm is executed. Together, the channel encoder and decoder protect the transmitted information. Finally, the estimated information is received (forwarded to the sink).

Despite their important role in protecting transmitted information, the channel coding blocks, especially the decoder, are one of the most resource-consuming parts of the entire communication system. Therefore, the design of the decoder is the focus of this doctoral study. The channel encoder and decoder blocks are highlighted in the dashed line in Figure 1.1, and these blocks are where the polar codes are implemented. Additionally, a block of information bits is commonly concatenated with the cyclic-redundancy check (CRC) code, which is applied by the state-of-the-art polar codes to enhance the overall error-correction capability.

The choice of the channel model depends on the application environment. In this doctoral study, we consider wireless communication scenarios, thus the additive white Gaussian noise (AWGN) channel is used. The noise

follows a normal distribution  $n \sim \mathcal{N}(\mu, \sigma_n^2)$ , where the mean is  $\mu = 0$  and the variance is  $\sigma_n^2$ . Furthermore, we use the binary phase-shift keying (BPSK) modulation scheme, where each bit in the transmitted codeword  $x_i \in \mathbf{x}$  is mapped to a digital signal as:

$$y_i = \begin{cases} 1.0, & \text{when } x_i = 0, \\ -1.0, & \text{otherwise.} \end{cases}$$

(1.1)

Each bit of the signal is affected by the noise before it arrives at the receiver, as  $\tilde{y}_i = y_i + n_i$ . To decode a polar code, the demodulator performs a log-likelihood estimation of the input signal to obtain the soft estimated vector  $\alpha_{\rm ch}$ , also called the channel log-likelihood ratios (LLRs). In BPSK modulation, for each bit of the transmitted codeword,  $\alpha_{\rm ch}$  (i) is calculated as follows:

$$\alpha_{\rm ch}(i) = \ln \left( \frac{p(\tilde{y}_i|y_i = 0)}{p(\tilde{y}_i|y_i = 1)} \right),\tag{1.2}$$

where "ln" denotes the natural logarithm and  $p(\tilde{y}_i|y_i)$  represents the probabilities of transmitting each bit of the digital signal  $y_i \in \{1, -1\}$ . Those probabilities can be calculated by the probability density function as follows:

$$p\left(\tilde{y}_{i}|y_{i}\right) = \frac{1}{\sqrt{2\pi\sigma_{n}^{2}}} \cdot \exp\left(-\frac{\left(\tilde{y}_{i} - y_{i}\right)}{2\sigma_{n}^{2}}\right). \tag{1.3}$$

Finally, applying (1.3) to (1.2), calculation of the channel LLRs for BPSK modulation can be simplified as:

$$\alpha_{\rm ch}(i) = \frac{2\tilde{y}_i}{\sigma_n^2},\tag{1.4}$$

The noise spectral density in the AWGN channel is estimated as  $N_0 = 2\sigma_n^2$ . The channel signal-to-noise ratio (SNR) is a common measure used to characterize the channel quality, which is computed as:

$$SNR = \frac{E_s}{N_0} = \frac{1}{2\sigma_n^2},\tag{1.5}$$

where  $E_s$  denotes the signal energy, which is set to  $E_s = 1$  to simplify the analysis.

Another common measure characterizing the channel is the ratio of the energy per information bit to the noise spectral density, denoted by  $E_b/N_0$ . It differs from the SNR by taking into account the code rate and the modulation applied to the transmitted message. It is calculated as follows:

$$E_b/N_0 = \frac{\text{SNR}}{R \cdot \log_2 M},\tag{1.6}$$

where M is the size of the constellation, R = k/N is the code rate, and the SNR is calculated by (1.5). For the BPSK, M = 2 is set. Note that both SNR and  $E_b/N_0$  are typically expressed in dB.

Similarly to (1.6), the measures  $E_b/N_0$  and SNR are related to each other in the logarithmic domain as follows:

$$E_b/N_0|_{dB} = SNR|_{dB} - 10\log_{10}(R \cdot \log_2 M)$$

(1.7)

Note that since M = 2 applied in this work and  $R \le 1$ , the relation  $E_b/N_0 \ge SNR$  in (1.7) holds.

#### **Uncoded Versus Coded Communication**

To demonstrate the advantages of using error-correction codes, we performed simulations to analyze the error-correction performance in terms of the bit errors of a message encoded with polar code transmitted over the channel. This performance is compared to the analytical expression of an uncoded message. The analysis is made only for demonstration purposes, while the details on polar code construction and encoding will be provided in the following sections of this chapter.

For the polar-encoded message, the block with the length N=128 bits and with the rate R=3/4 is used. It contains k=96 information bits, and the remaining (N-k)=32 bits are used for error correction. These 32 bits, also known as parity bits, are formed as a combination of the 96 bits according to the encoding scheme. Simulations are made with the BPSK modulation over the AWGN channel, expressed through the  $E_b/N_0$  with values  $\{2.0, 2.125, \ldots, 7.25\}$  dB. The polar codes are decoded by the successive-cancellation (SC) decoder, the original decoding algorithm proposed in the seminal paper by Arıkan (2009). Simulations are performed with a minimum of  $C=2\cdot 10^5$  messages and continue until at least 2000 message errors are observed for each  $E_b/N_0$  point. The error-correction performance is analyzed using the bit-error rate (BER), i.e., the ratio of incorrectly received bits in messages to the total transmitted message bits. The BER is evaluated for each  $E_b/N_0$  point.

For the uncoded message, the analytical expression for a bit-error probability, denoted by  $P_e$ , can be analytically estimated as:

$$P_e = Q\left(\sqrt{2\frac{E_b}{N_0}}\right),\tag{1.8}$$

where Q-function is calculated for a given value of  $E_b/N_0$  expressed in the linear domain. Note that (1.8) is valid for the BPSK modulation under the AWGN channel.

Figure 1.2 depicts the error-correction performance for uncoded and polar-encoded messages. The x axis represents  $E_b/N_0$ , where moving left indicates deterioration in the channel condition while moving right indicates improvement. The y axis, displayed on a logarithmic scale, corresponds to the BER. The top of the y axis indicates the high BER,

Figure 1.2 Error-correction performance of uncoded vs polar-encoded messages, both of length N = 128. Polar codes of rate  $R = \frac{3}{4}$  are decoded by the SC decoder

with the maximum value of  $10^0 = 1$ , indicating that 100% of the transmitted bits result in errors. As we descend the y axis, the BER decreases. The minimum displayed point is  $10^{-4} = 0.0001$ , indicating 0.01% of the bit errors.

The results of Figure 1.2 show that at low  $E_b/N_0$ , polar codes with SC decoder have worse performance than the uncoded messages. The region corresponding to BER of  $10^{-1}$  is considered unreliable, while BER of  $10^{-4}$  is the point of reference in many practical communication systems. In the BER region of  $10^{-3}$  to  $10^{-4}$ , the encoded messages highly surpass the performance of uncoded messages. At the BER of  $10^{-3}$ , polar codes achieve a gain of  $\Delta E_b/N_0 = 2.25$  dB and of  $\Delta SNR = 3.5$  dB. Therefore, to achieve the same error-correction performance as polar codes, the transmitter needs to send the signal of the uncoded messages with significantly more energy to compensate for the loss due to the channel noise.

Note that analyzing the error-correction performance using  $E_b/N_0$  instead of SNR favors the uncoded messages over the polar-encoded messages. As shown in Figure 1.2, at the BER of  $10^{-3}$ , the coding gain  $\Delta E_b/N_0 = 2.25$  dB, while the coding gain in terms of SNR is  $\Delta$ SNR = 3.5 dB. The difference occurs because the code rate R used for polar codes shifts the BER curve to the right along the  $E_b/N_0$  axis relative to the SNR axis, according to (1.7). Thus, the gain achieved by polar codes in the BER region of  $10^{-3}$  to  $10^{-4}$  is significant.

#### 1.2 Construction and Encoding of Polar Codes

Polar codes are the first linear block codes proven to asymptotically achieve the channel capacity over the binary-input discrete memoryless channel (B-DMC) (Arıkan, 2009). Polar codes have explicit construction, which is based on

the concept of channel polarization. This allows the assignment of k information bits among N total bits in the input vector. After constructing the code, encoding is performed, resulting in the creation of a codeword. These two operations are summarized below.

### 1.2.1 Code Construction

To understand the concept of channel polarisation, a simple example of a polarizing construction with N=2 is shown in Figure 1.3 (a). Two bits,  $u_0$  and  $u_1$  are transformed into  $x_0=u_0\oplus u_1$  and  $x_1=u_1$ , where  $\oplus$  is a bitwise XOR operation. Then,  $x_0$  and  $x_1$  each are sent over the combined channel  $W_2$ , whereas W is the original channel. On the receiver side, given that the channel noise affected the signal, the probability of correctly estimating the bit  $u_1$  increases compared to the scenario without any transformation. Meanwhile, the probability of correctly estimating bit  $u_0$  decreases. Thus, the effect of channel polarization is observed.

Figure 1.3 Construction of the channels  $W_N$  with N = 2 and N = 4

Such polarizing transformation can be combined recursively to create channels with longer codes, as shown in Figure 1.3 (b), for channel  $W_N$  with N=4. As  $N\to\infty$ , the probability of successfully estimating each bit  $u_i$  approaches either 1 or 0.5, indicating perfectly reliable and completely unreliable bit-channels. The proportion of reliable bits approaches the symmetric capacity of  $W_N$ , as was shown by Arıkan (2009).

To construct an (N, k) polar code, the k most reliable positions are assigned to information bits, while the remaining (N-k) bits, called frozen bits, are set to predefined values. These frozen bits, known by the decoder, are typically set to zero. The vector  $\mathbf{u}$  contains the k information bits in their predefined locations and (N-k) frozen bits. The set of information-bit indices is denoted by  $\mathcal{A}$ , and  $\mathcal{A} = \{a_0, \dots, a_j, \dots, a_{k-1}\}$ , with  $a_0 < \dots < a_j < \dots < a_{k-1}$ . Similarly, the set of frozen-bit indices is denoted by  $\mathcal{A}^C$ , and  $\mathcal{A}^C = \{a_0^c, \dots, a_j^c, \dots, a_{N-k-1}^c\}$ , with  $a_0^c < \dots < a_j^c < \dots < a_{N-k-1}^c\}$ .

In the finite-length regime, not all bit-channel reliabilities correspond to 1 and 0.5, meaning they are not fully polarized. Therefore, an accurate ranking algorithm for reliabilities is required to select k most reliable channels, ensuring strong error-correction performance. The state-of-the-art works include the density evolution and the Gaussian approximation of density evolution methods, proposed by Tal & Vardy (2013) and Trifonov (2012). In these methods, the reliability ranking is determined for specific channel conditions.

Recent works on the partial reliability order, such as Mondelli, Hassani & Urbanke (2017) and Condo, Hashemi & Gross (2017), created an opportunity to derive a universal construction of polar codes independent of the channel conditions. Based on the results of these works, the 3GPP has derived a reliability sequence of 1024 bits, which is used as a basis to extract individual reliabilities. These reliabilities are then used to construct polar codes with  $N \le 1024$ , as used in 3GPP's next-generation mobile-communication standard (5G) according to 3GPP (2018).

In the scope of this doctoral study, the proposed modifications to flip decoders demonstrated efficiency for any construction of the polar code, with negligible differences. Therefore, we selected the 5G code construction (3GPP, 2018) and presented all the results accordingly.

#### 1.2.2 Encoding