ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DE LA

MAÎTRISE EN GÉNIE ÉLECTRIQUE

M.Ing.

PAR

BOUCHARD, Tommy

ÉTUDE D'APPLICATION D'UN CONVERTISSEUR ANALOGIQUE À NUMÉRIQUE À

LA RÉCEPTION DIRECTE DES RADIOFRÉQUENCES

MONTRÉAL, LE 25 MAI 2009

© Tommy Bouchard, 2009

**PRÉSENTATION DU JURY**

CE MÉMOIRE A ÉTÉ ÉVALUÉ

PAR UN JURY COMPOSÉ DE

M. François Gagnon, directeur de mémoire

Département de génie électrique à l'École de technologie supérieure

M. Ammar B. Kouki, président du jury

Département de génie électrique à l'École de technologie supérieure

M. Ghyslain Gagnon, membre du jury

Département de génie électrique à l'École de technologie supérieure

IL A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 12 MAI 2009

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

J'aimerais remercier mon directeur de recherche, Prof. François Gagnon, qui m'a permis de joindre à une équipe formidable.

Je désire aussi souligner les judicieux conseils de Prof. Ghyslain Gagnon qui m'ont éclairé à des moments importants.

Finalement, merci à ma femme, Marie-Luce, pour son soutien inconditionnel et ses encouragements, sans lesquels j'aurais terminé mes études depuis bien longtemps.

# ÉTUDE D'APPLICATION D'UN CONVERTISSEUR ANALOGIQUE À NUMÉRIQUE À LA RÉCEPTION DIRECTE DES RADIOFRÉQUENCES

Tommy BOUCHARD

## RÉSUMÉ

La prochaine génération de radios logicielles, les radios cognitives, imposent une flexibilité que la plupart des radios logicielles actuelles ne possèdent pas. Ce travail a pour objectif l'amélioration de cette flexibilité en établissant dans quelle mesure et de quelle façon les convertisseurs analogiques à numériques peuvent être utilisés dans la réalisation d'un récepteur direct des radiofréquences.

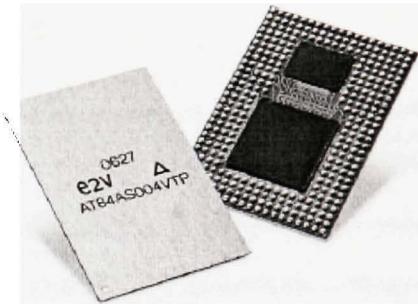

Une revue des techniques de conversion de signal proposées dans la littérature permet de constater que la numérisation directe est le meilleur choix pour la présente application. Le convertisseur analogique à numérique AT84AS004 d'*e2v* est identifié comme celui disponible sur le marché répondant le mieux aux exigences de ce travail.

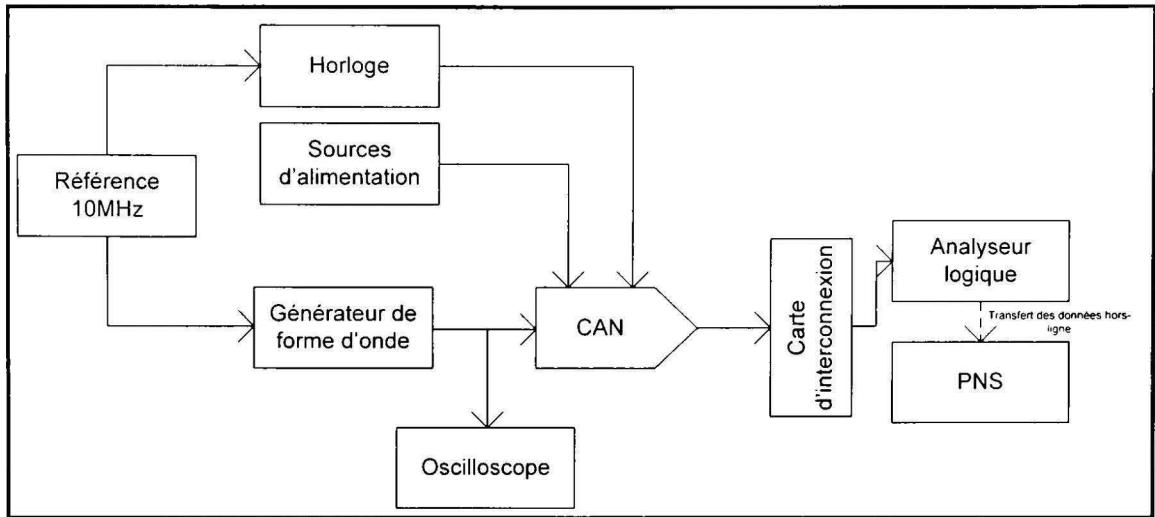

Un récepteur logiciel, formé d'une carte d'interconnexion entre le convertisseur et un analyseur logique et d'une unité de traitement de signal *Matlab*, est conçu. L'intégrité du signal sur la carte et la fonctionnalité du logiciel sont ensuite vérifiées.

Le convertisseur sélectionné est ensuite caractérisé. Les résultats sont comparés aux données fournies par le manufacturier. On constate alors que les spécifications mesurées collent aux attentes, sauf pour la vitesse d'opération maximale. Cette dernière est bien en deçà des attentes.

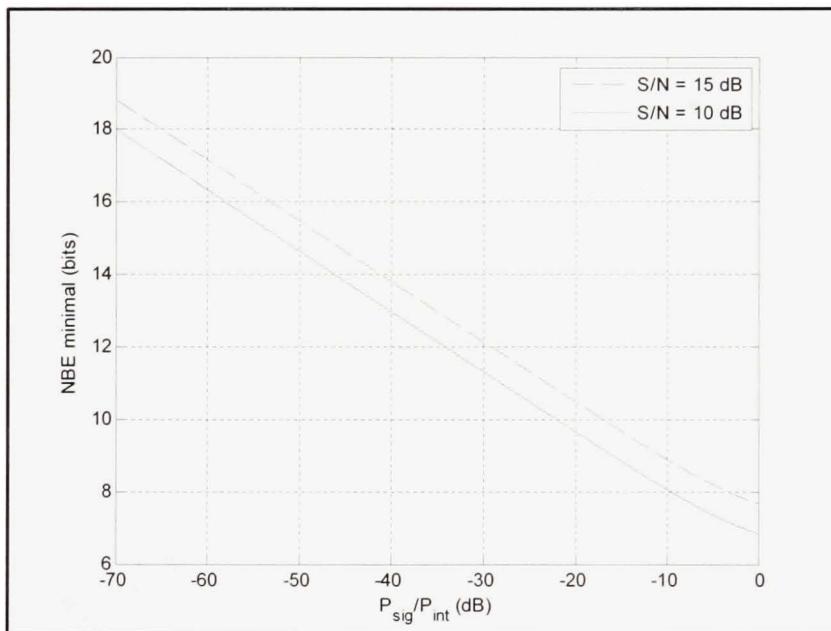

À la lumière de ces mesures, le convertisseur est évalué en termes de récepteur direct des radiofréquences. Les résultats démontrent que les détériorations occasionnées lors de la conversion du signal n'empêchent pas la réception correcte du signal. Cependant, un facteur limitatif important est mis en évidence : la plage dynamique allouée au signal d'intérêt. Comme une grande largeur de bande est numérisée instantanément, la plage dynamique est divisée entre plusieurs signaux du spectre. La puissance de ces signaux influence le rapport signal à bruit à la réception.

**Mots-clés :** Conversion analogique à numérique, radio cognitive, radio logicielle, récepteur direct des radiofréquences.

# DIRECT RADIOFREQUENCY RECEIVER APPLICATION STUDY

Tommy BOUCHARD

## ABSTRACT

The next generation of software radios, cognitive radios, needs a flexibility that current software radios do not possess. This work's objective is to improve this flexibility by establishing how an analog-to-digital converter can be used as a direct radiofrequency receiver.

A review of conversion techniques proposed in the literature shows that direct conversion is the best way to achieve such a receiver. The analog to digital converter AT84AS004, made by e2v, is identified as the best suited, commercially available converter, for the present application.

A software receiver, composed of an interconnection board between the converter and a logic analyzer and a *Matlab* signal processing unit, is designed. Signal integrity on the board and software unit's functionality are then confirmed.

The selected converter is then characterized. Results are compared to manufacturer's data. Except for maximum operating frequency, which is way below expectations, the measurements are similar to those anticipated.

The converter is finally used in a direct radiofrequency receiver. Results show that conversion deteriorations are not important enough to prevent the demodulation of the received signal. However, a more important limitative factor is highlighted: dynamic range allocated to the main signal. Since a large bandwidth is instantly digitalized, the dynamic range is divided between all signals in this bandwidth. The power of those signals alters the signal to noise ratio at reception.

**Keywords:** Analog-to-digital conversion, cognitive radio, direct radiofrequency receiver, software defined radio.

## TABLE DES MATIÈRES

|                                                                                                                                        | Page |

|----------------------------------------------------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                                                                     | 1    |

| <br>                                                                                                                                   |      |

| CHAPITRE 1 TECHNOLOGIES DE CONVERSION DE HAUT DÉBIT .....                                                                              | 3    |

| 1.1    Revue des techniques et des méthodes de conversion d'un signal analogique à un<br>signal numérique .....                        | 3    |

| 1.1.1    Méthodes peu répandues de conversion d'un signal analogique<br>à numérique.....                                               | 3    |

| 1.1.2    Méthodes traditionnelles de conversion d'un signal analogique<br>à numérique.....                                             | 5    |

| 1.2    Choix de la technique retenue.....                                                                                              | 7    |

| 1.2.1    Avantages et inconvénients des méthodes exotiques et traditionnelles de<br>conversion d'un signal analogique à numérique..... | 8    |

| 1.2.2    Sélection préalable de la technique de conversion .....                                                                       | 9    |

| 1.3    Revue des convertisseurs analogique-numérique disponibles sur le marché .....                                                   | 10   |

| 1.3.1    Caractéristiques souhaitables pour un CAN utilisé dans un étage de<br>conversion directe des radiofréquences .....            | 11   |

| 1.3.2    Comparaison et choix d'un convertisseur.....                                                                                  | 13   |

| 1.4    Modèles de simulation de convertisseurs analogique à numérique.....                                                             | 15   |

| 1.4.1    Modèle comportemental .....                                                                                                   | 15   |

| 1.4.2    Modèle par table de conversion .....                                                                                          | 17   |

| 1.4.3    Modèle électrique.....                                                                                                        | 18   |

| 1.5    Conclusion .....                                                                                                                | 18   |

| <br>                                                                                                                                   |      |

| CHAPITRE 2 CONCEPTION DU RÉCEPTEUR NUMÉRIQUE .....                                                                                     | 20   |

| 2.1    Introduction.....                                                                                                               | 20   |

| 2.2    Conception du circuit imprimé .....                                                                                             | 21   |

| 2.2.1    Détails théoriques.....                                                                                                       | 22   |

| 2.2.2    Calcul de l'impédance des câbles .....                                                                                        | 24   |

| 2.2.3    Calcul de l'impédance des lignes microbandes .....                                                                            | 24   |

| 2.2.4    Création du circuit imprimé .....                                                                                             | 27   |

| 2.3    Vérification de l'intégrité du signal .....                                                                                     | 30   |

| 2.3.1    Simulations électriques .....                                                                                                 | 31   |

| 2.3.2    Mesures sur le circuit .....                                                                                                  | 35   |

| 2.4    Conception du récepteur logiciel .....                                                                                          | 38   |

| 2.4.1    Conception du récepteur QPSK .....                                                                                            | 38   |

| 2.4.2    Conception du récepteur QAM .....                                                                                             | 41   |

| 2.4.3    Calcul de l'amplitude du vecteur d'erreur .....                                                                               | 42   |

| <br>                                                                                                                                   |      |

| CHAPITRE 3 ÉVALUATION DU CONVERTISSEUR ANALOGIQUE À NUMÉRIQUE<br>SÉLECTIONNÉ .....                                                     | 44   |

|                                                                                             |                                                                                         |         |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------|

| 3.1                                                                                         | Introduction.....                                                                       | 44      |

| 3.2                                                                                         | Montage expérimental .....                                                              | 44      |

| 3.3                                                                                         | Évaluation de la vitesse maximale de fonctionnement du convertisseur.....               | 46      |

| 3.3.1                                                                                       | Description de l'expérimentation.....                                                   | 46      |

| 3.3.2                                                                                       | Résultats et analyses .....                                                             | 47      |

| 3.4                                                                                         | Évaluation du bruit de quantification.....                                              | 50      |

| 3.4.1                                                                                       | Description de l'expérimentation.....                                                   | 50      |

| 3.4.2                                                                                       | Résultats et analyse .....                                                              | 51      |

| 3.5                                                                                         | Évaluation de la plage dynamique sans parasites .....                                   | 54      |

| 3.5.1                                                                                       | Description de l'expérimentation.....                                                   | 55      |

| 3.5.2                                                                                       | Résultats et analyse .....                                                              | 55      |

| 3.6                                                                                         | Évaluation du bruit de phase.....                                                       | 56      |

| 3.6.1                                                                                       | Description des expérimentations.....                                                   | 57      |

| 3.6.2                                                                                       | Résultats et analyses du bruit de phase de l'horloge.....                               | 58      |

| 3.6.3                                                                                       | Résultats et analyse du bruit de phase du convertisseur analogique à<br>numérique ..... | 59      |

| 3.7                                                                                         | Comparaison des résultats avec les spécifications du manufacturier et discussion.....   | 61      |

| <br><b>CHAPITRE 4 ÉVALUATION DU CONVERTISSEUR EN TERMES DE RÉCEPTEUR<br/>NUMÉRIQUE.....</b> |                                                                                         | <br>62  |

| 4.1                                                                                         | Introduction.....                                                                       | 62      |

| 4.2                                                                                         | Théorie des communications QPSK et QAM .....                                            | 62      |

| 4.3                                                                                         | Évaluation de l'effet du bruit de quantification sur la réception .....                 | 65      |

| 4.3.1                                                                                       | Description de l'expérimentation.....                                                   | 65      |

| 4.3.2                                                                                       | Résultats et analyse .....                                                              | 66      |

| 4.4                                                                                         | Évaluation de l'effet de la plage dynamique sans parasites sur la réception .....       | 71      |

| 4.4.1                                                                                       | Description de l'expérimentation.....                                                   | 71      |

| 4.4.2                                                                                       | Résultats et analyse .....                                                              | 73      |

| 4.5                                                                                         | Évaluation de l'effet du bruit de phase sur la réception.....                           | 74      |

| 4.5.1                                                                                       | Description de l'expérimentation.....                                                   | 75      |

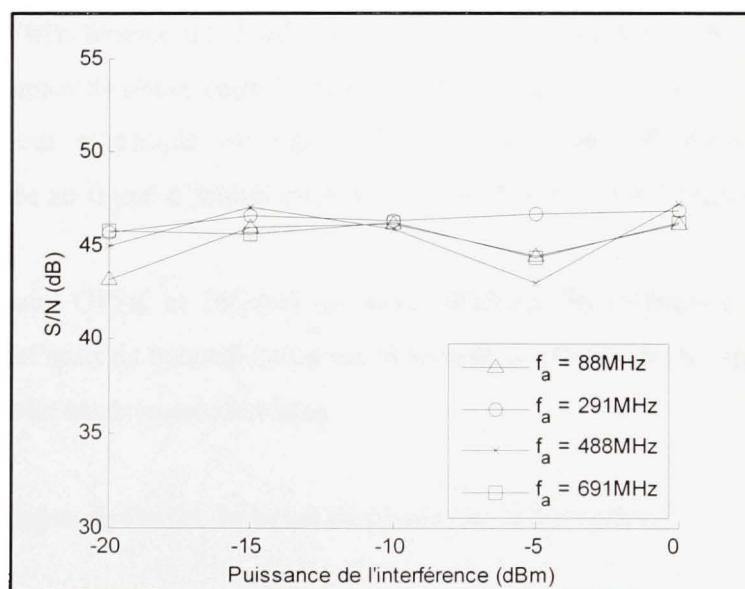

| 4.5.2                                                                                       | Résultats et analyse .....                                                              | 75      |

| 4.6                                                                                         | Analyse et discussion des résultats .....                                               | 77      |

| <br><b>CONCLUSION.....</b>                                                                  |                                                                                         | <br>81  |

| <br><b>ANNEXE I</b>                                                                         | <br><b>SPÉCIFICATIONS DU CONVERTISSEUR ANALOGIQUE À<br/>NUMÉRIQUE RETENU.....</b>       | <br>83  |

| <br><b>ANNEXE II</b>                                                                        | <br><b>RAPPORTS SUR LA CONCEPTION DES CIRCUITS IMPRIMÉS<br/>D'ALTIUM DESIGNER .....</b> | <br>104 |

| <br><b>ANNEXE III</b>                                                                       | <br><b>CODE MATLAB POUR LE CALCUL DU TAUX D'ERREURS ET DE<br/>CODES SAUTÉS .....</b>    | <br>109 |

|                           |                                                                                     |     |

|---------------------------|-------------------------------------------------------------------------------------|-----|

| ANNEXE IV                 | CODE MATLAB DU RÉCEPTEUR LOGICIEL.....                                              | 111 |

| ANNEXE V                  | CODE MATLAB DU CALCULE DE L'AVE .....                                               | 113 |

| ANNEXE VI                 | RÉSULTATS COMPLETS DE L'EXPÉRIMENTATION SUR LA<br>VITESSE MAXIMALE D'OPÉRATION..... | 114 |

| ANNEXE VII                | CODE MATLAB POUR CALCULER LE S/N D'UN SIGNAL<br>PRÉ-ENREGISTRÉ .....                | 121 |

| LISTE DE RÉFÉRENCES ..... |                                                                                     | 122 |

| BIBLIOGRAPHIE.....        |                                                                                     | 124 |

## LISTE DES TABLEAUX

|             | Page                                                                                  |    |

|-------------|---------------------------------------------------------------------------------------|----|

| Tableau 1.1 | Bandes de fréquences ciblées pour la conversion numérique à analogique.....           | 8  |

| Tableau 1.2 | Comparaison des convertisseurs disponibles sur le marché.....                         | 13 |

| Tableau 1.3 | Rapport signal à bruit des convertisseurs avec un gain de sur-échantillonnage.....    | 14 |

| Tableau 2.1 | Délai de propagation des lignes de transmission du montage, en picosecondes.....      | 27 |

| Tableau 2.2 | Taux d'erreur et de codes sautés à l'entrée de l'analyseur logique.....               | 37 |

| Tableau 3.1 | Identification des appareils utilisés dans le montage expérimental.....               | 45 |

| Tableau 3.2 | Alimentations de la carte d'évaluation.....                                           | 46 |

| Tableau 3.3 | Mesures du rapport signal à bruit pour différentes fréquences d'échantillonnage ..... | 53 |

| Tableau 3.4 | Mesure de la plage dynamique sans parasites.....                                      | 56 |

| Tableau 3.5 | Bruit de phase de l'horloge du montage expérimental.....                              | 59 |

| Tableau 3.6 | Bruit de phase du convertisseur analogique à numérique.....                           | 60 |

| Tableau 4.1 | Effet du bruit de quantification sur la réception d'un signal QPSK.....               | 68 |

| Tableau 4.2 | Effet du bruit de quantification sur la réception d'un signal 16QAM.....              | 69 |

## LISTE DES FIGURES

|             | Page                                                                                                     |    |

|-------------|----------------------------------------------------------------------------------------------------------|----|

| Figure 1.1  | Architecture d'une radio logicielle idéale. ....                                                         | 3  |

| Figure 1.2  | Échantillonnage par entrelacement temporel. ....                                                         | 6  |

| Figure 1.3  | Modèle comportemental. ....                                                                              | 15 |

| Figure 1.4  | Transition d'un bit à la sortie d'un CAN. ....                                                           | 17 |

| Figure 1.5  | Remplissage d'une table de conversion par réseau de neurones.....                                        | 18 |

| Figure 2.1  | Impédance de ligne pour des traces de 0.2 mm en fonction de l'épaisseur du diélectrique.....             | 26 |

| Figure 2.2  | Schéma des connexions électriques entre les sondes et les connecteurs....                                | 28 |

| Figure 2.3  | Schéma d'interconnexion du signal d'horloge avec l'analyseur logique....                                 | 29 |

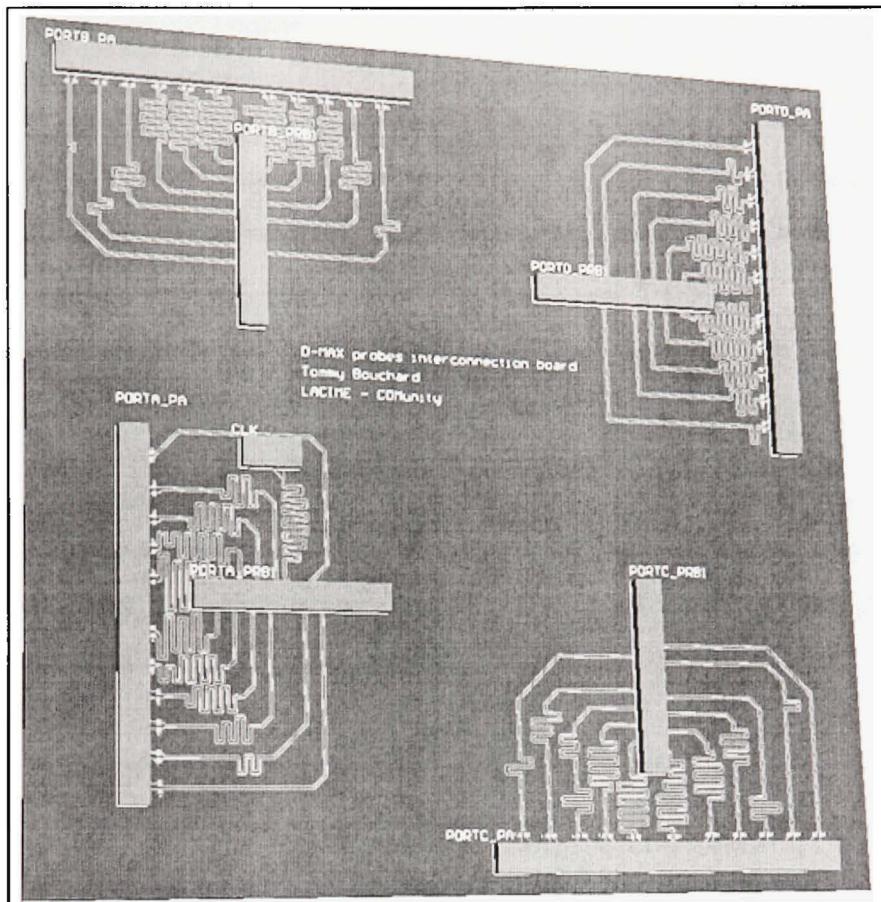

| Figure 2.4  | Circuit imprimé conçu avec <i>Altium Designer 6</i> . ....                                               | 30 |

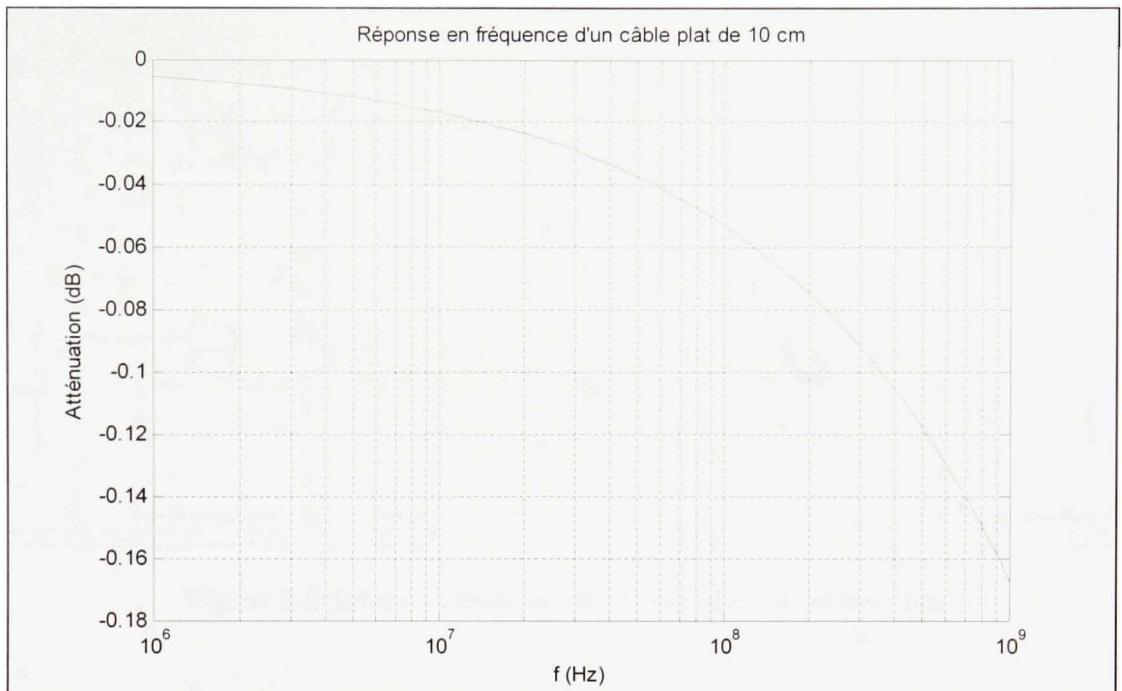

| Figure 2.5  | Réponse en fréquence d'un câble plat de 10 cm. ....                                                      | 32 |

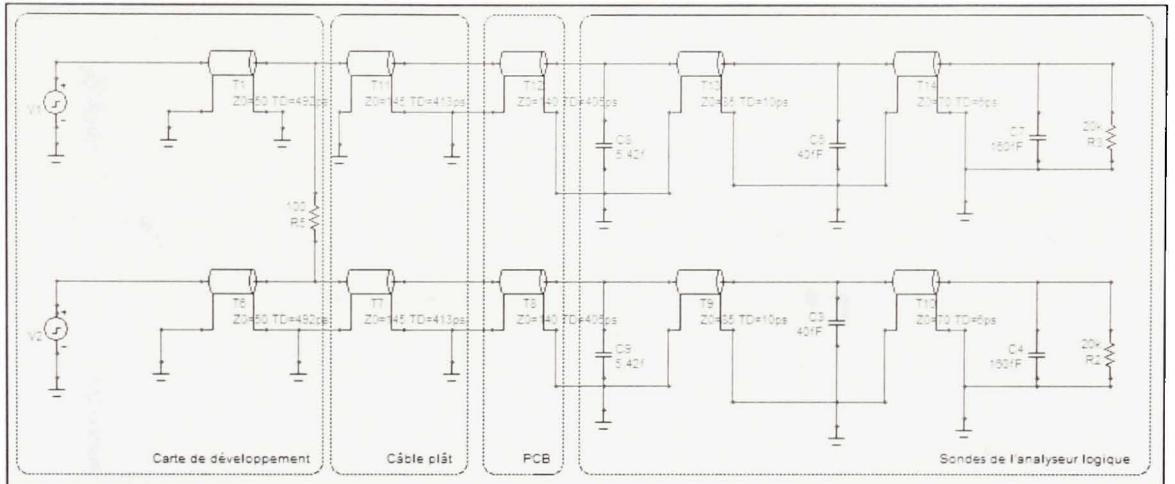

| Figure 2.6  | Schéma électrique de la simulation <i>Micro-Cap</i> . ....                                               | 33 |

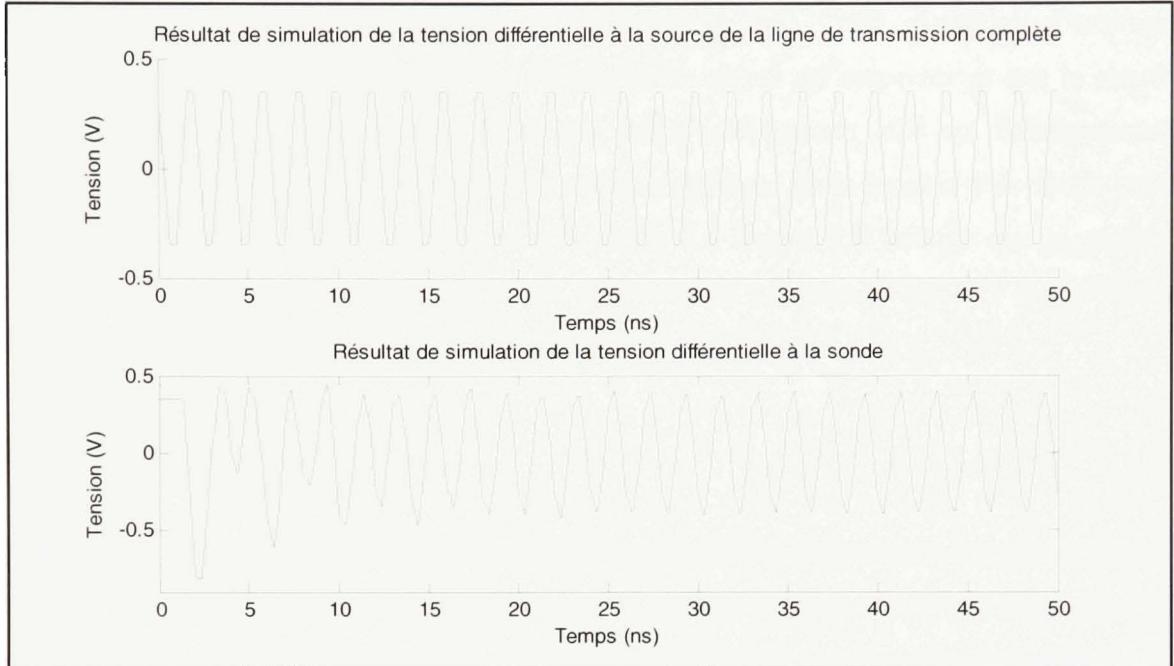

| Figure 2.7  | Simulations électrique de l'intégrité du signal. ....                                                    | 34 |

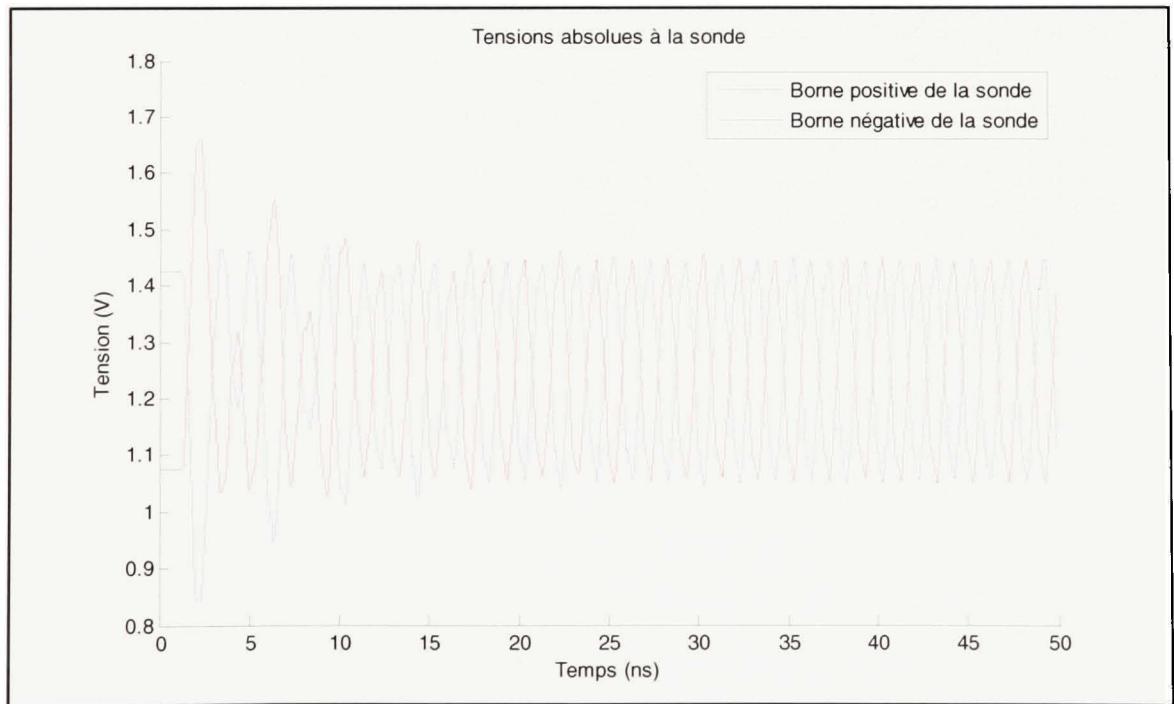

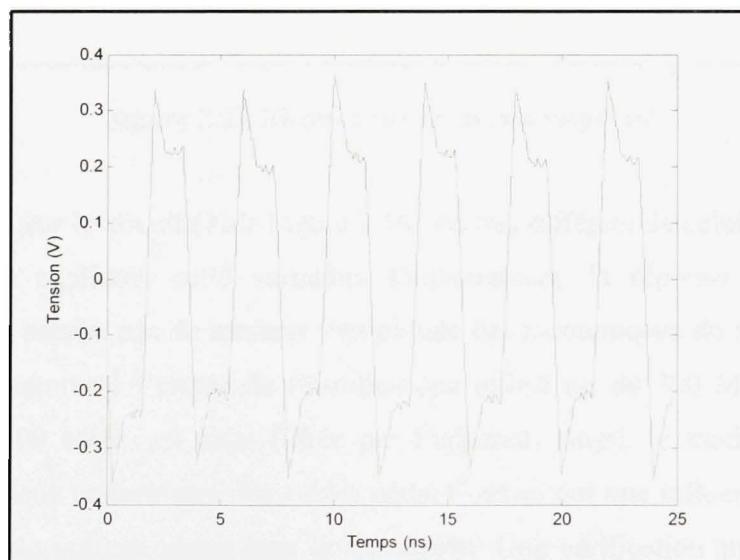

| Figure 2.8  | Simulation de la tension absolue à la sonde. ....                                                        | 34 |

| Figure 2.9  | Simulation de la tension différentielle au connecteur de la carte d'évaluation. ....                     | 35 |

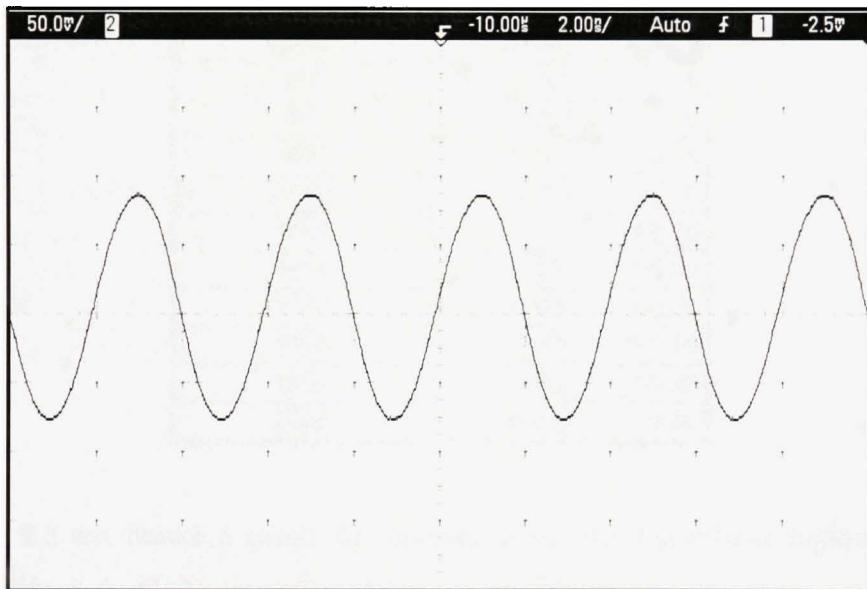

| Figure 2.10 | Mesure sur le circuit imprimé.....                                                                       | 36 |

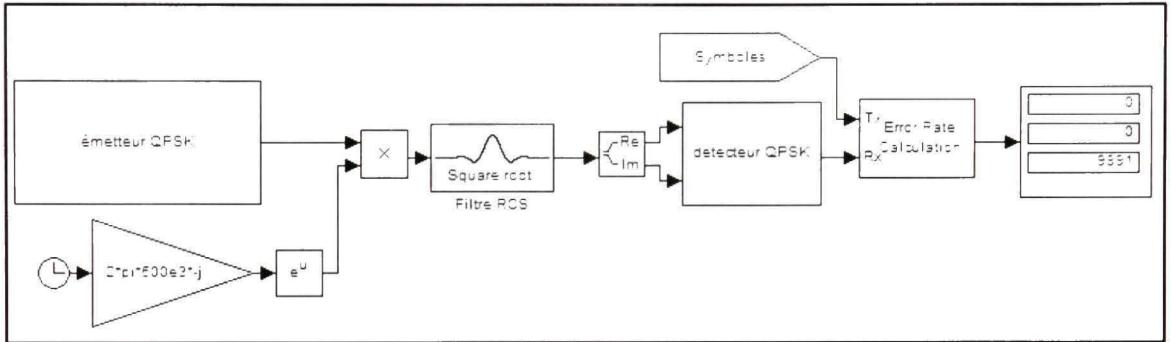

| Figure 2.11 | Schéma simplifié du récepteur QPSK. ....                                                                 | 40 |

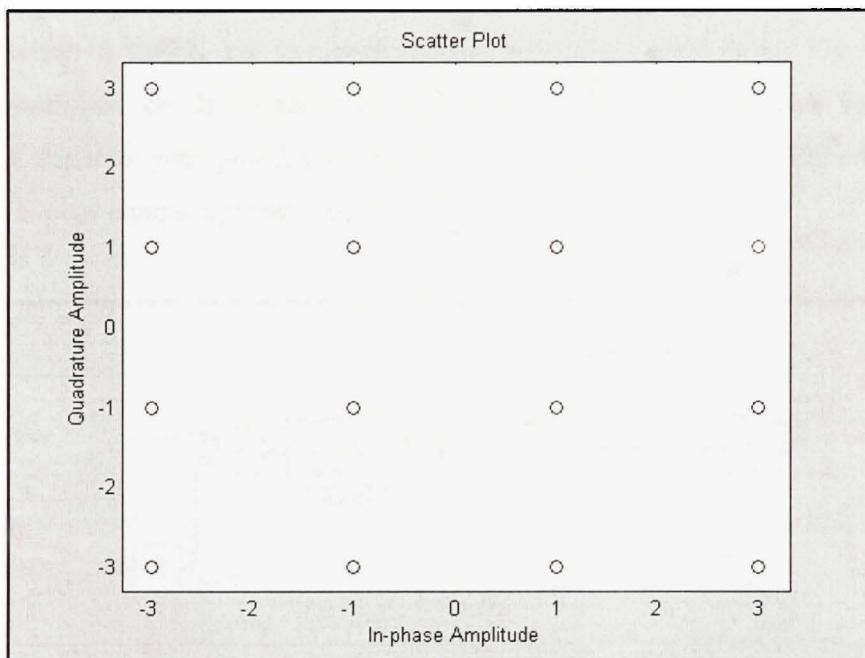

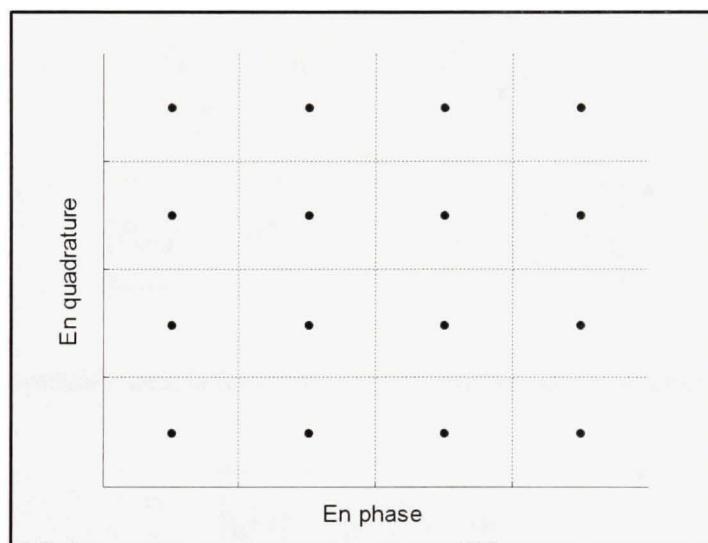

| Figure 2.12 | Constellation d'un signal 16QAM.....                                                                     | 41 |

| Figure 2.13 | Schéma simplifié du récepteur QAM. ....                                                                  | 42 |

| Figure 3.1  | Montage expérimental de l'évaluation du CAN.....                                                         | 45 |

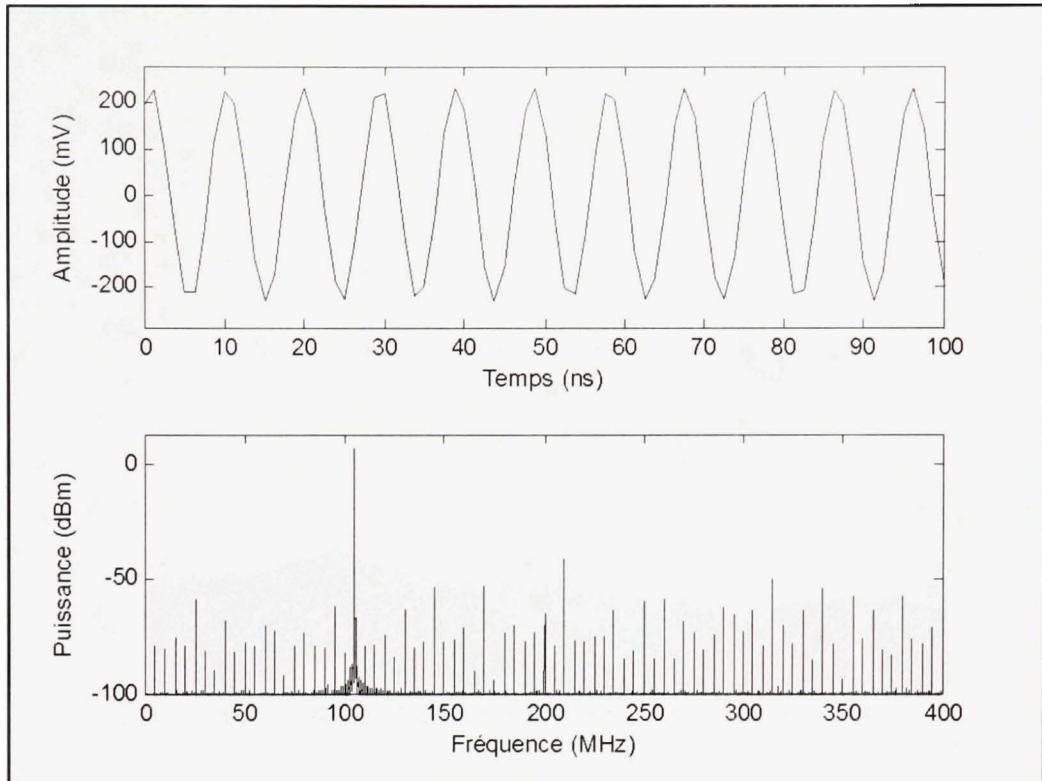

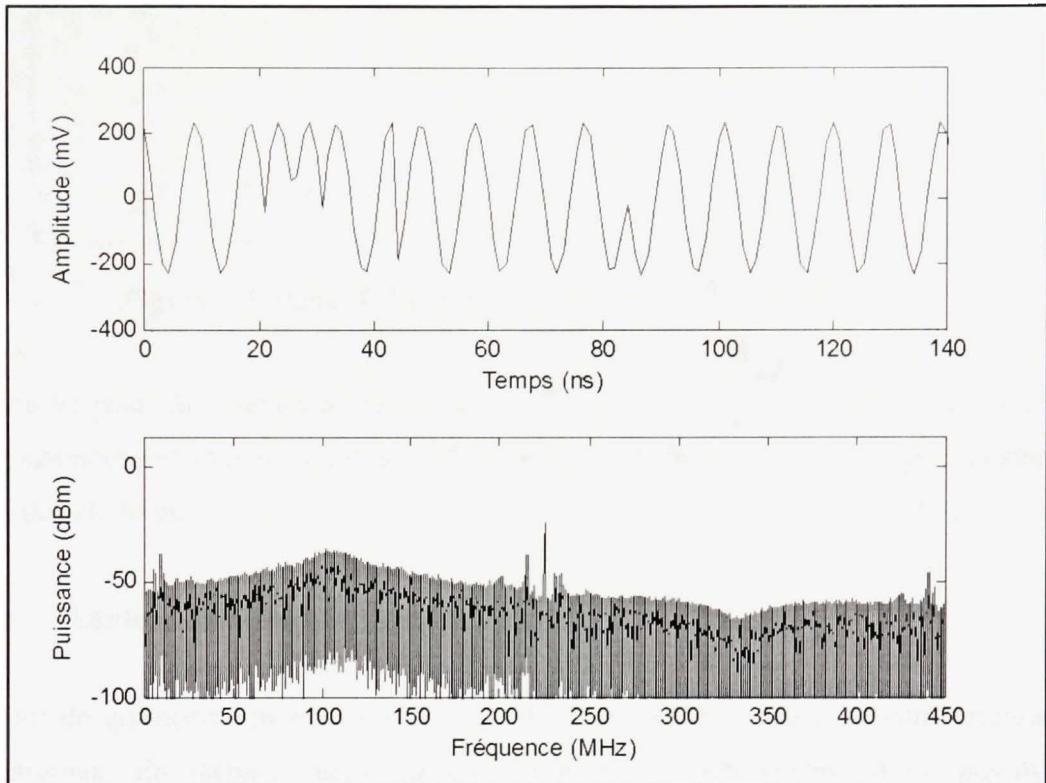

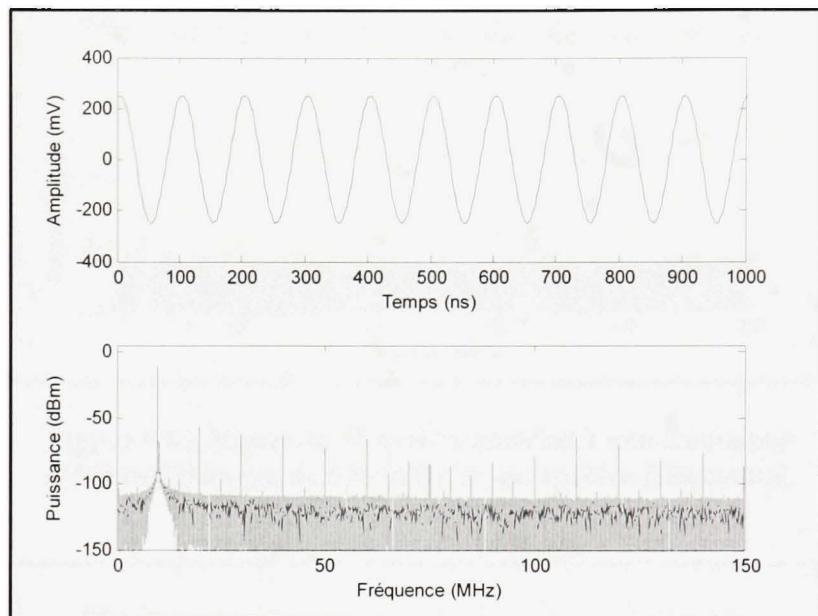

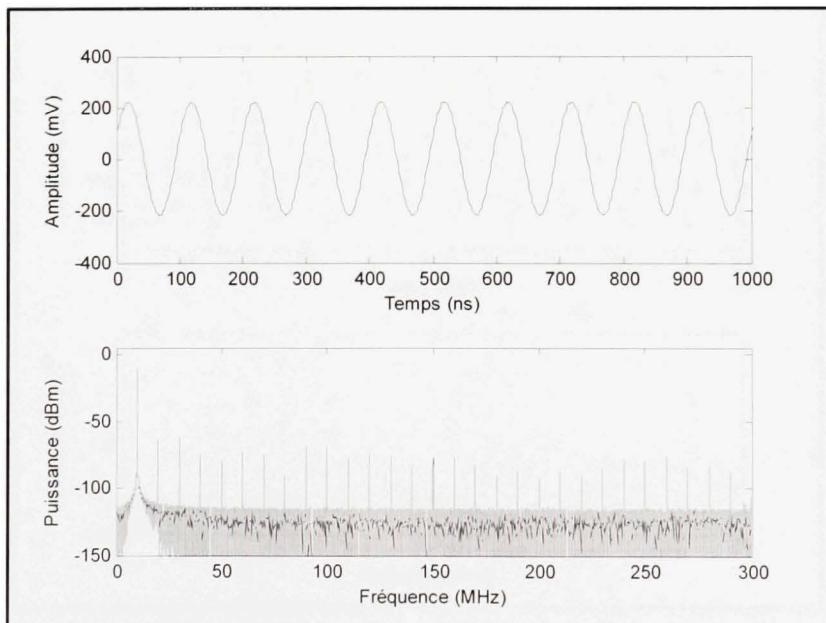

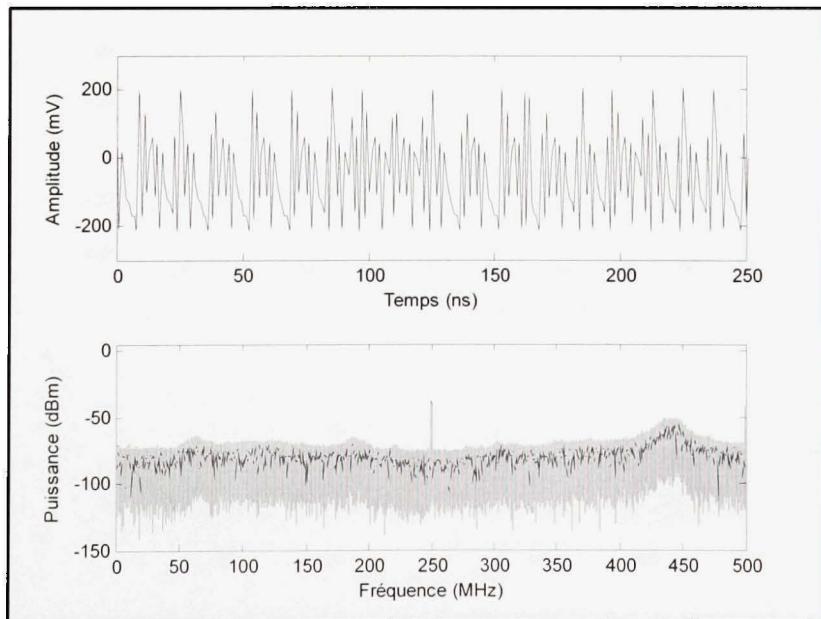

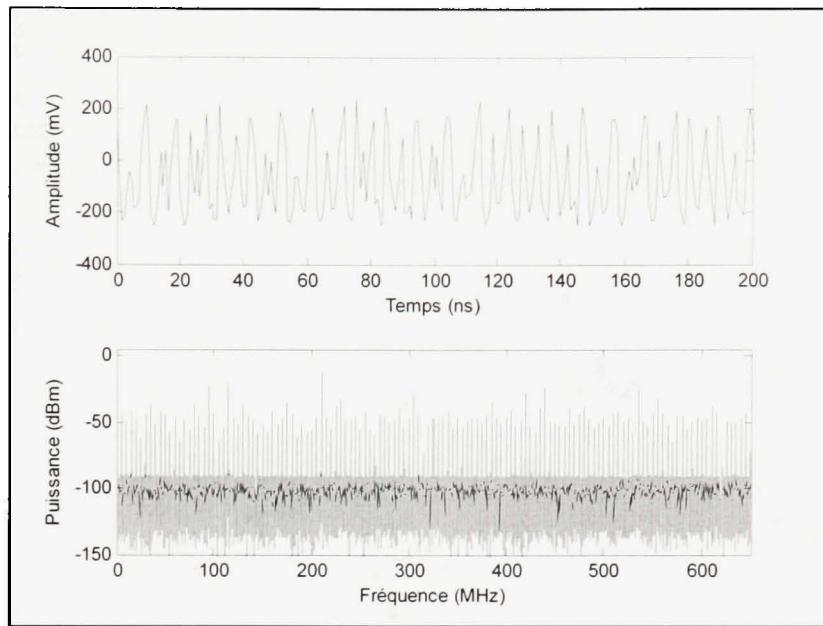

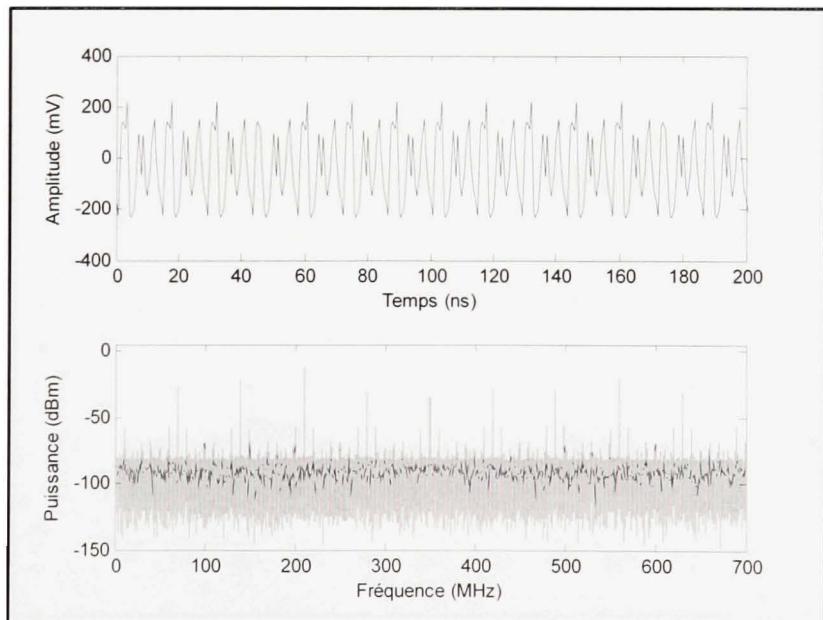

| Figure 3.2  | Signal de 105 MHz numérisé à une fréquence d'échantillonnage de 800 MHz et son spectre fréquentiel. .... | 48 |

|             |                                                                                                         |    |

|-------------|---------------------------------------------------------------------------------------------------------|----|

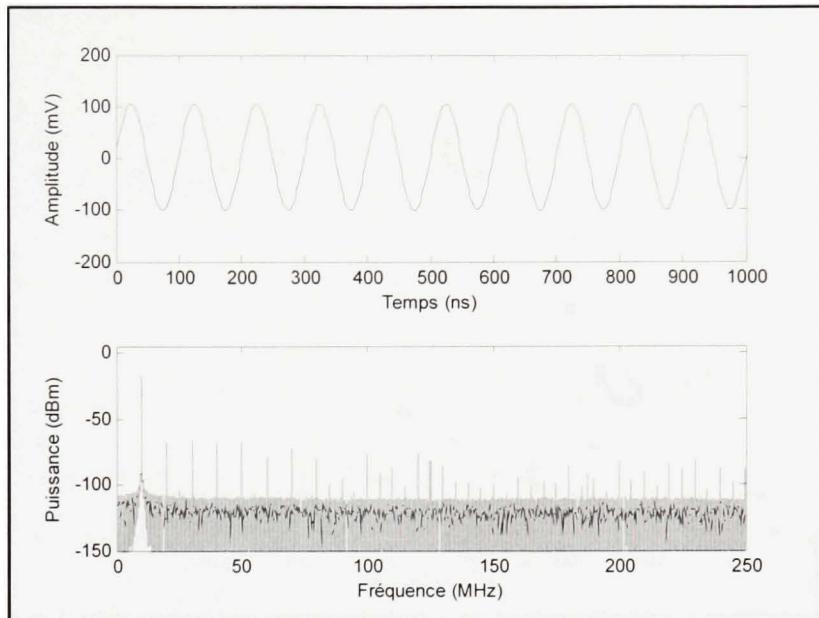

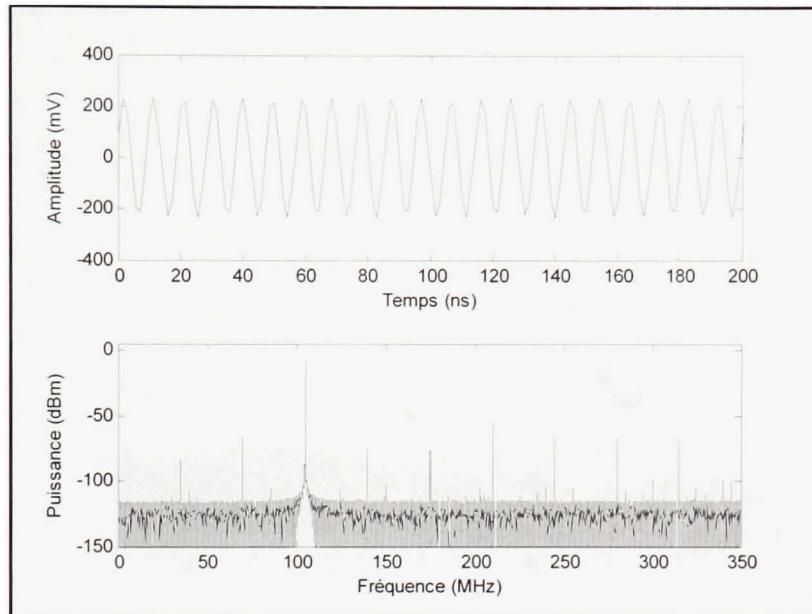

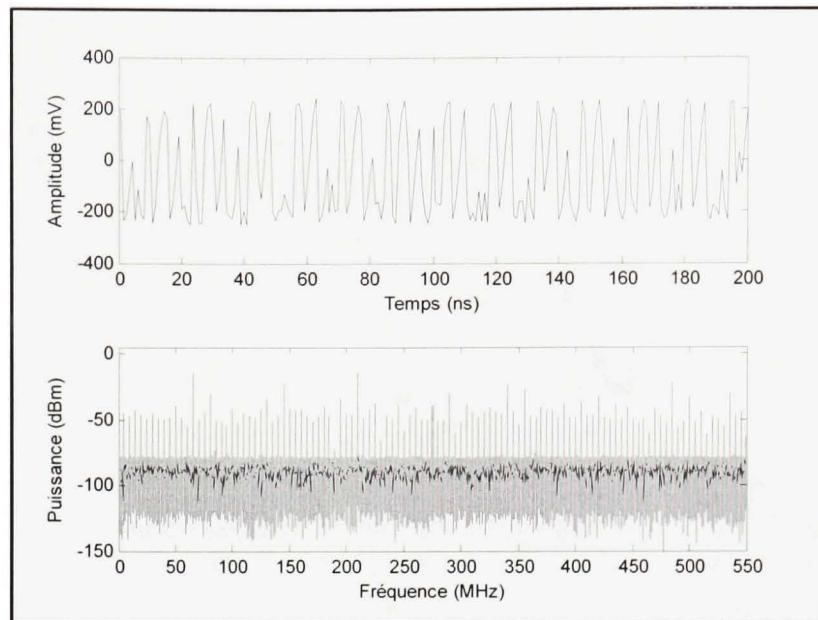

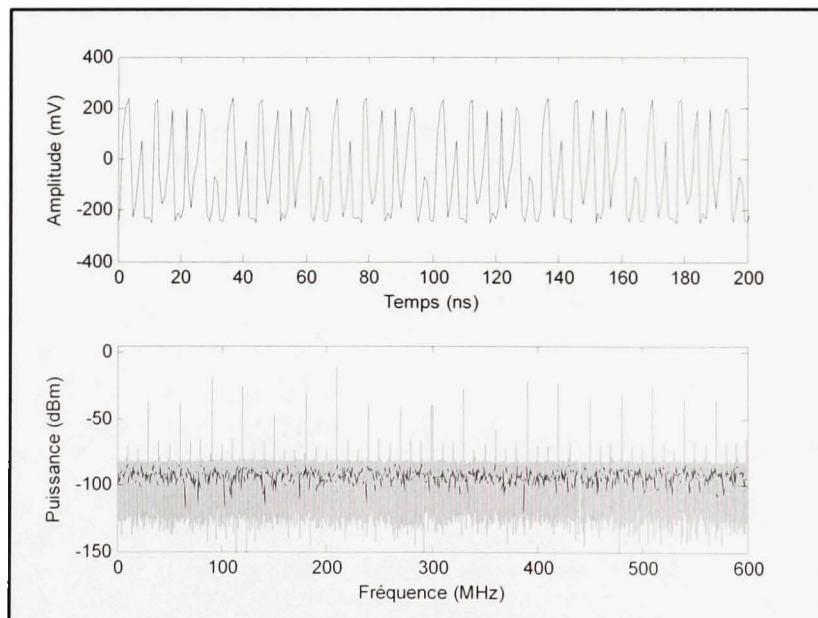

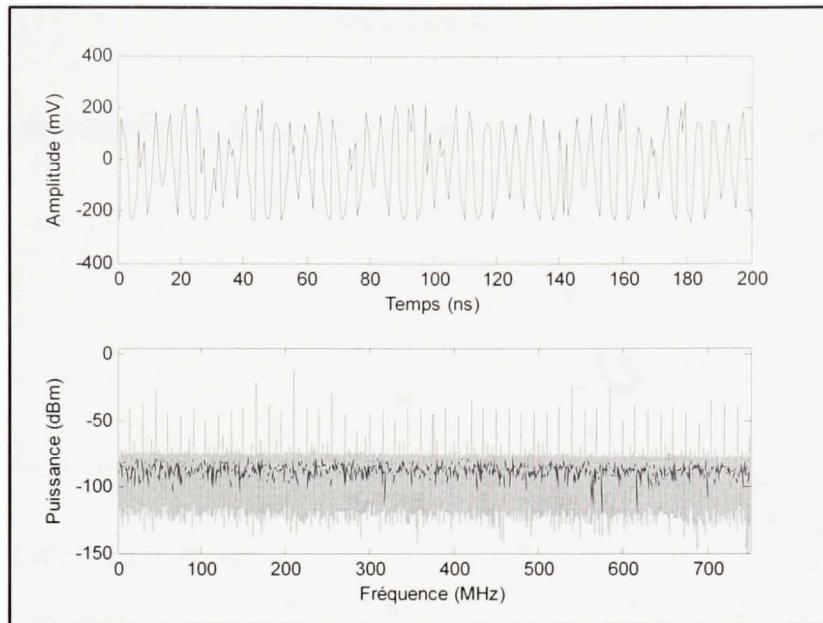

| Figure 3.3  | Signal de 105 MHz numérisé à une fréquence d'échantillonnage de 900 MHz et son spectre fréquentiel..... | 49 |

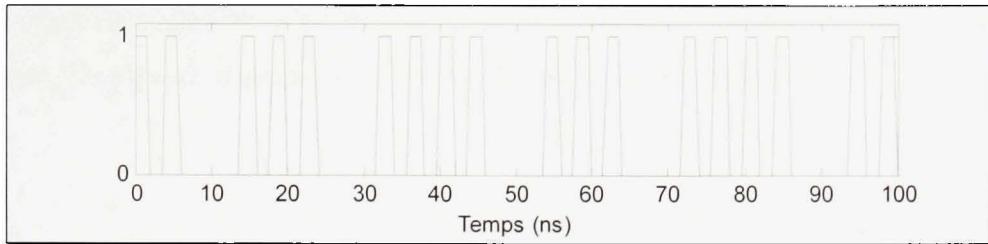

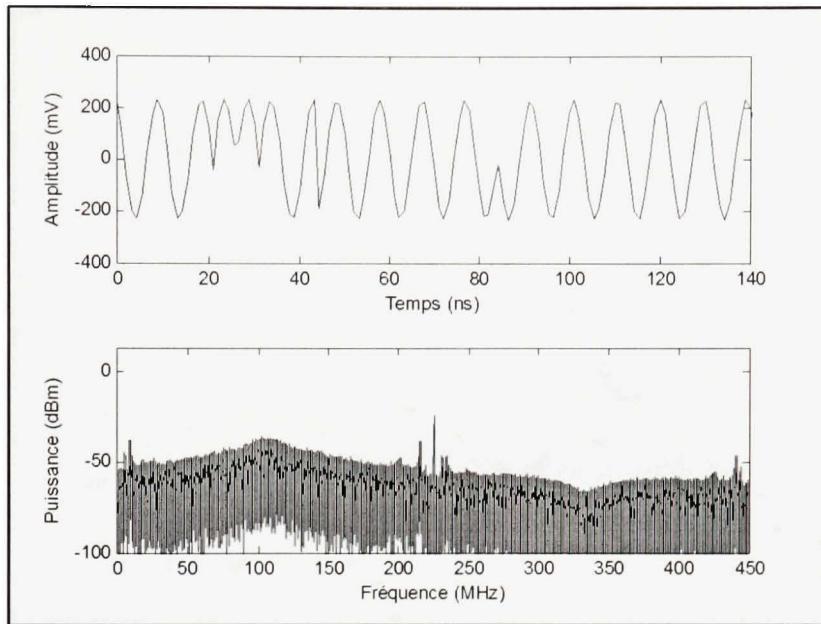

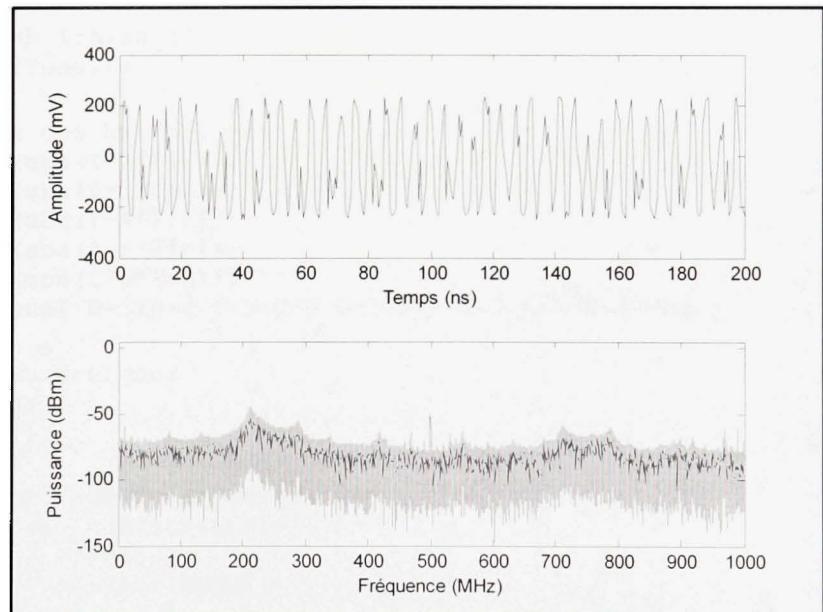

| Figure 3.4  | Signal DP lorsque le CAN est cadencé à 900 MHz. ....                                                    | 50 |

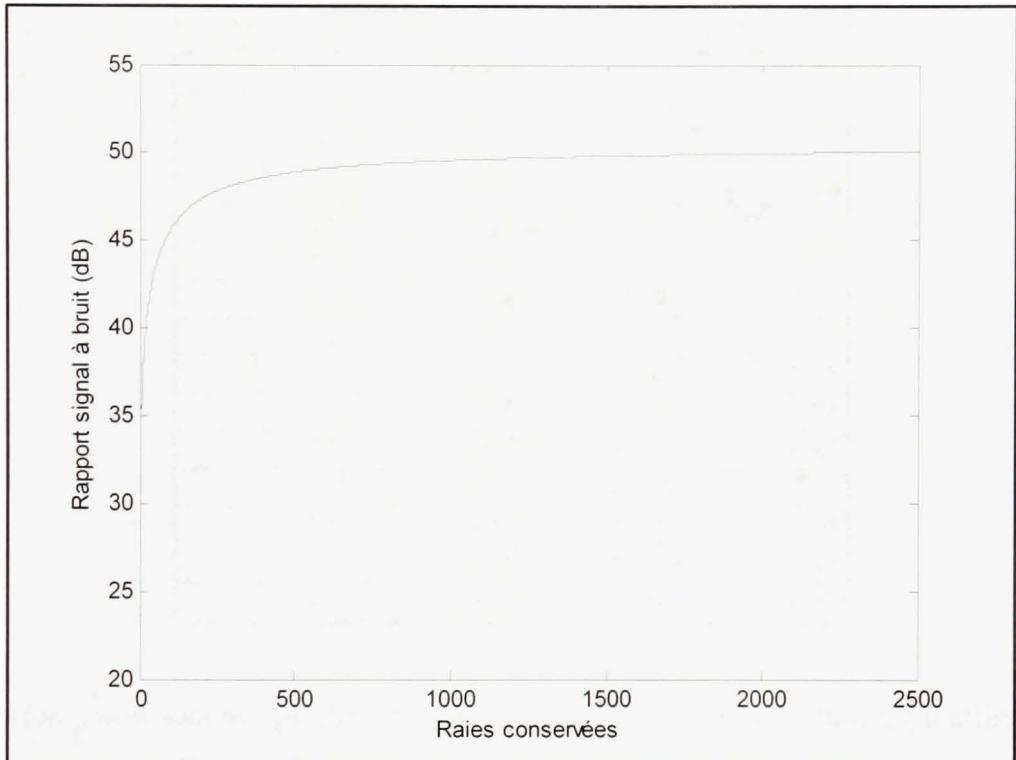

| Figure 3.5  | Rapport signal à bruit en fonction du nombre de raies conservées. ....                                  | 52 |

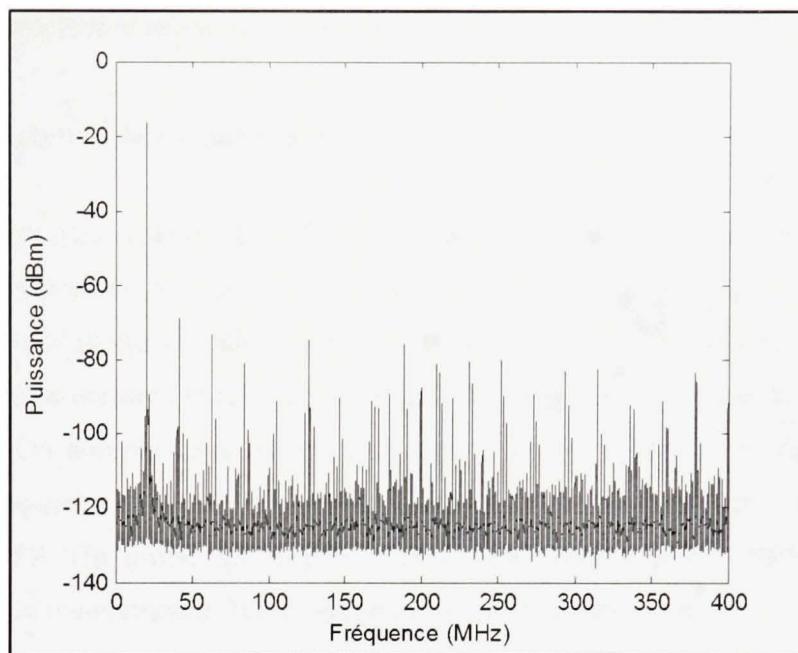

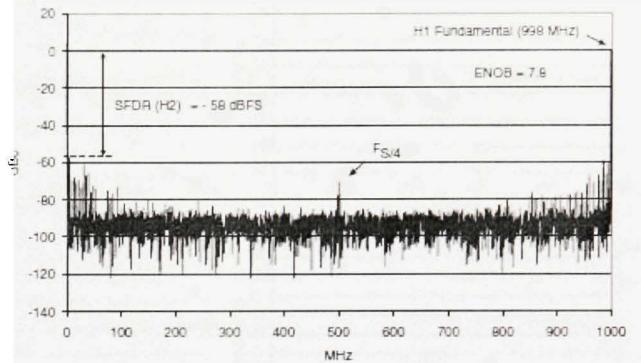

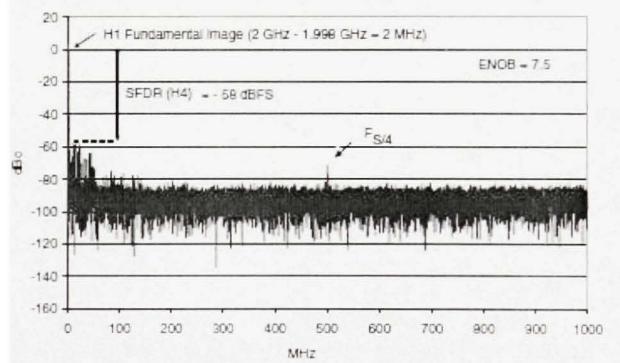

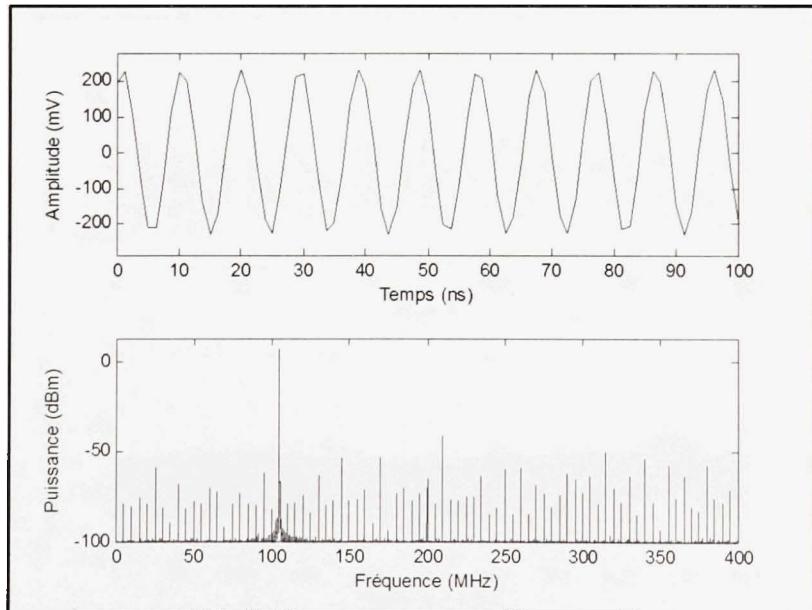

| Figure 3.6  | Spectre du signal de 21 MHz échantillonné à une fréquence de 800 MHz. ....                              | 54 |

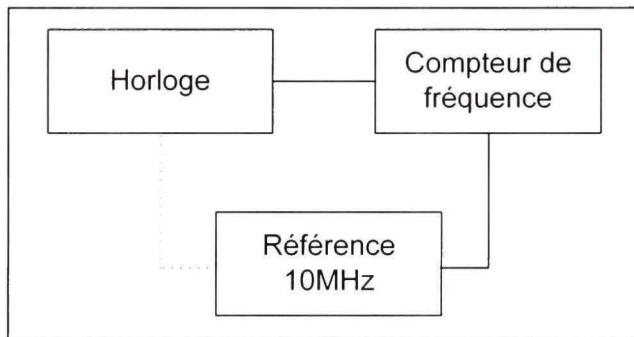

| Figure 3.7  | Montage expérimental du calcul du bruit de l'horloge.....                                               | 57 |

| Figure 4.1  | Régions de décision d'une constellation 16QAM. ....                                                     | 63 |

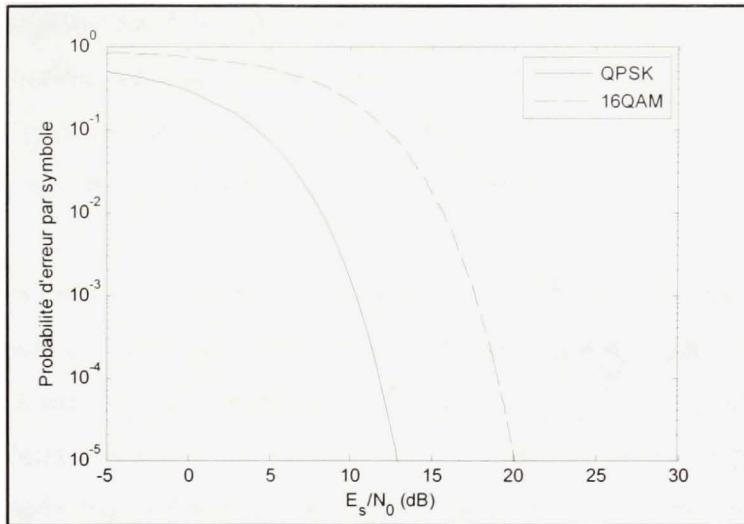

| Figure 4.2  | Probabilité d'erreur de signaux QPSK et 16QAM. ....                                                     | 65 |

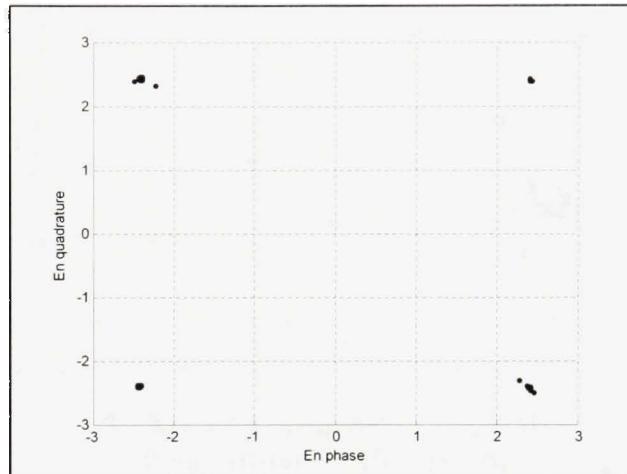

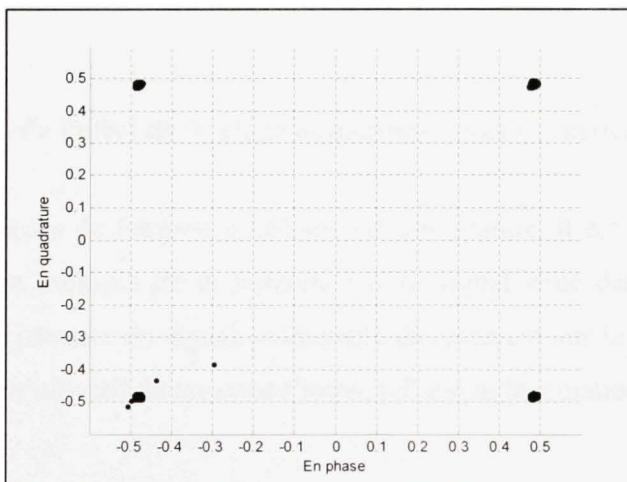

| Figure 4.3  | Constellation QPSK à un rythme de 10 ksym/s. ....                                                       | 70 |

| Figure 4.4  | Constellation QPSK à un rythme de 250 ksym/s. ....                                                      | 70 |

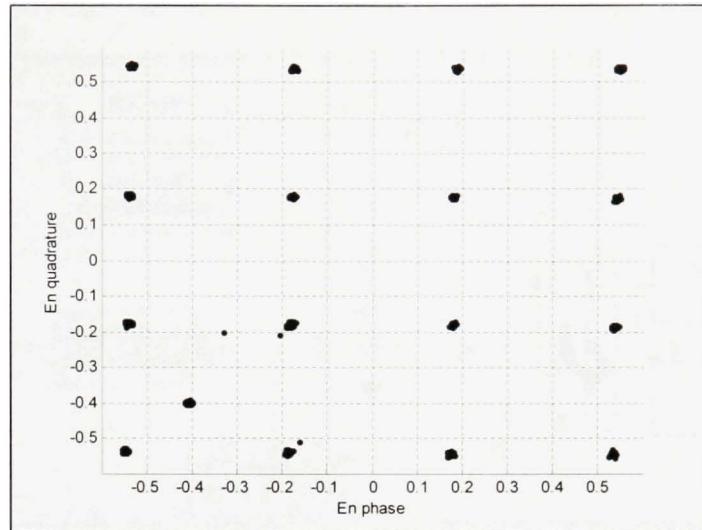

| Figure 4.5  | Constellation 16QAM à un rythme de 250 ksym/s. ....                                                     | 71 |

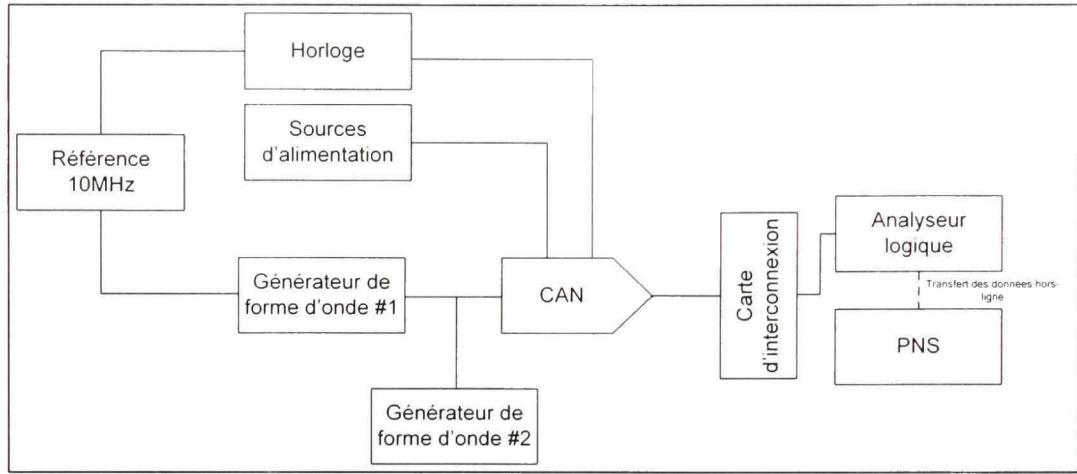

| Figure 4.6  | Montage expérimental pour déterminer l'influence de la SFDR sur la réception. ....                      | 72 |

| Figure 4.7  | Influence de la SFDR sur la réception d'un signal QPSK.....                                             | 73 |

| Figure 4.8  | Influence de la SFDR sur la réception d'un signal 16QAM.....                                            | 74 |

| Figure 4.9  | Constellation QPSK d'un signal à 88 MHz sans référence 10 MHz.....                                      | 75 |

| Figure 4.10 | Constellation 16QAM d'un signal à 291 MHz sans référence 10 MHz....                                     | 76 |

| Figure 4.11 | Constellation 16QAM d'un signal à 488 MHz sans référence 10 MHz....                                     | 76 |

| Figure 4.12 | Réception d'un signal QPSK en présence d'un site connexe.....                                           | 78 |

| Figure 4.14 | Nombre de bits effectifs minimal en fonction de la puissance relative du signal d'intérêt.....          | 79 |

## LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES

|       |                                                            |

|-------|------------------------------------------------------------|

| AVE   | Amplitude du vecteur d'erreur                              |

| BNC   | Baïonnette Neill-Concelmen                                 |

| BW    | <i>Bandwidth</i>                                           |

| CAN   | Convertisseur analogique à numérique                       |

| CC    | Courant continu                                            |

| CNA   | Convertisseur numérique à analogique                       |

| DP    | Données prêtées                                            |

| FR-4  | <i>Flame retardant 4</i>                                   |

| GSPS  | <i>Gigasamples per second</i>                              |

| NBE   | Nombre de bits effectifs                                   |

| PNS   | Processeur numérique du signal                             |

| QAM   | <i>Quadrature amplitude modulation</i>                     |

| QPSK  | <i>Quadrature phase shift keying</i>                       |

| RCS   | Racine de cosinus surélevé                                 |

| RF    | Radiofréquence                                             |

| SINAD | <i>Signal to noise and distortion</i>                      |

| SFDR  | <i>Spurious free dynamic range</i>                         |

| SMA   | Sous-miniature version A                                   |

| S/N   | Rapport signal à bruit                                     |

| SPICE | <i>Simulation program with integrated circuit emphasis</i> |

## LISTE DES SYMBOLES ET UNITÉS DE MESURE

### SYMBOLES

|               |                                                |

|---------------|------------------------------------------------|

| d             | Épaisseur du diélectrique                      |

| $\epsilon_r$  | Constante de permittivité relative du matériau |

| f             | Fréquence                                      |

| $f_a$         | Fréquence du signal analogique                 |

| $f_{knee}$    | Fréquence genoux                               |

| $f_{max}$     | Fréquence maximale                             |

| $f_s$         | Fréquence d'échantillonnage                    |

| $t_{10-90\%}$ | Temps de montée de 10% à 90%                   |

| $T_r$         | Temps de montée                                |

| v             | Vitesse                                        |

| W             | Largeur                                        |

| $Z_0$         | Impédance caractéristique                      |

### UNITÉS GÉOMÉTRIQUES

|    |           |

|----|-----------|

| m  | Mètre     |

| mm | Milimètre |

| pi | Pied      |

| po | Pouce     |

### UNITÉS ÉLECTRIQUES

|       |                                                                                       |

|-------|---------------------------------------------------------------------------------------|

| dB    | Décibel                                                                               |

| dBc   | Rapport de puissance exprimé en décibels par rapport à la porteuse.                   |

| dBFS  | Rapport de puissance exprimé en décibels par rapport à la puissance pleine amplitude. |

| dBm   | Rapport de puissance exprimé en décibels par rapport à 1 milliwatt.                   |

| fF    | Femtofarad                                                                            |

| Mbits | Mégabits                                                                              |

| mV    | Milivolts                                                                             |

| V     | Volts                                                                                 |

### UNITÉS DE TEMPS

|         |              |

|---------|--------------|

| GHz     | Gigahertz    |

| Hz      | Hertz        |

| MHz     | Mégahertz    |

| s       | Seconde      |

| fs      | Femtoseconde |

| ps      | Picoseconde  |

| $\mu s$ | Microseconde |

## INTRODUCTION

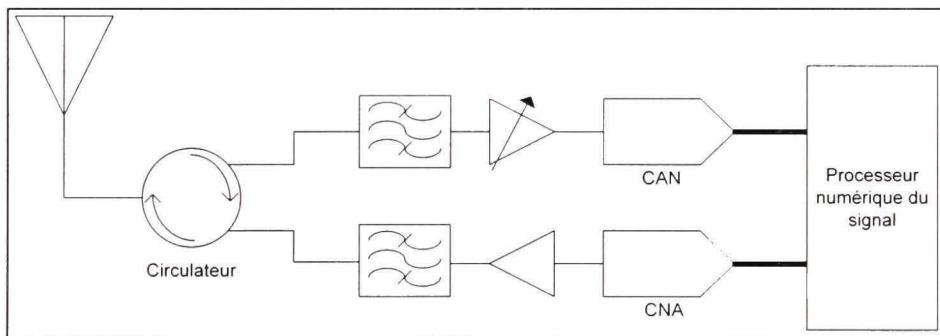

L'ère actuelle des télécommunications est marquée par l'utilisation de radios reprogrammables et reconfigurables : les radios logicielles. Ces appareils de communication sont caractérisés par une architecture flexible. En l'occurrence, les sections analogiques traditionnelles sont remplacées par un processeur numérique du signal (PNS), précédé d'un convertisseur analogique à numérique (CAN) et d'un convertisseur numérique à analogique (CNA). L'utilisation de ces seuls composants forment une radio-logicielle idéale. Bien que le matériel disponible et les techniques de conception aient beaucoup évolué depuis l'apparition des radios, l'architecture idéale reste peu répandue. La flexibilité de la radio-logicielle s'en trouve alors amputée.

L'objectif du présent travail est d'évaluer dans quelle mesure et de quelle façon les CAN disponibles sur le marché conviennent à une architecture de récepteur logiciel. Entre autres parce que les CNA disponibles sont plus performants que les CAN, l'étude de l'émetteur de la radio logicielle est omise du présent travail. De plus, les processeurs numériques du signal sont hors du cadre du travail. En effet, ils ne déterminent pas les performances de conversion.

Avant d'évaluer comment un CAN influence la réception d'un signal, des choix préliminaires s'imposent. Le premier des quatre chapitres de ce travail y est consacré. Les techniques de conversion plus récentes et traditionnelles sont passées en revue et le choix de la technique retenue est analysée. Ensuite, les principaux convertisseurs analogiques à numérique aptes à répondre aux besoins de la technique choisie sont comparés. Un survol des modèles théoriques de CAN conclut le chapitre.

Le deuxième chapitre est consacré à la conception du récepteur numérique. Il décrit d'abord la création du circuit imprimé, puis s'attarde sur la vérification de l'intégrité du signal. Enfin, la partie logicielle du récepteur est définie.

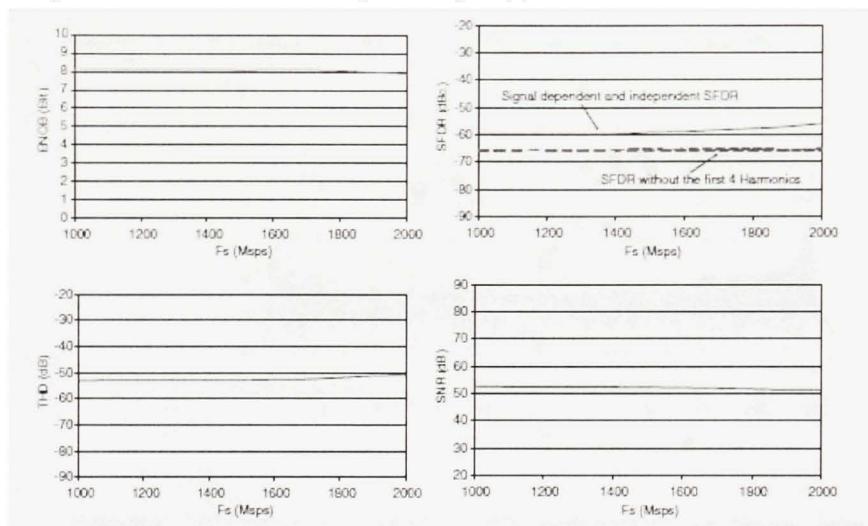

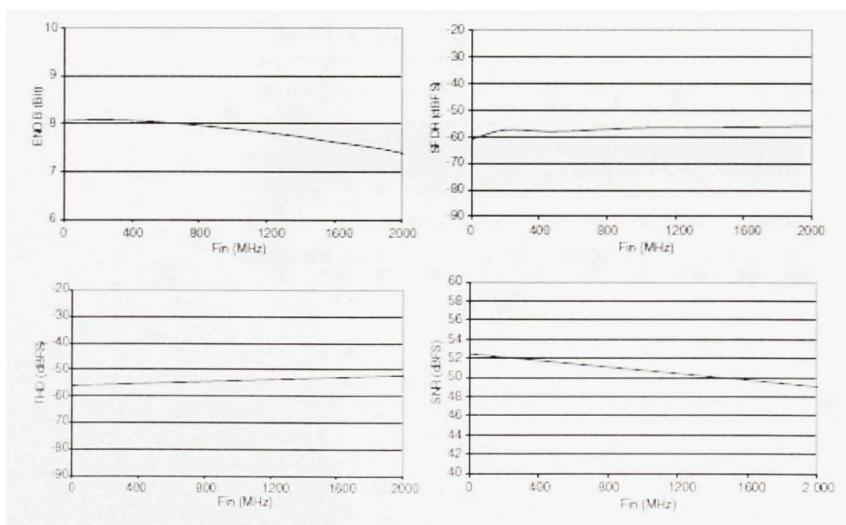

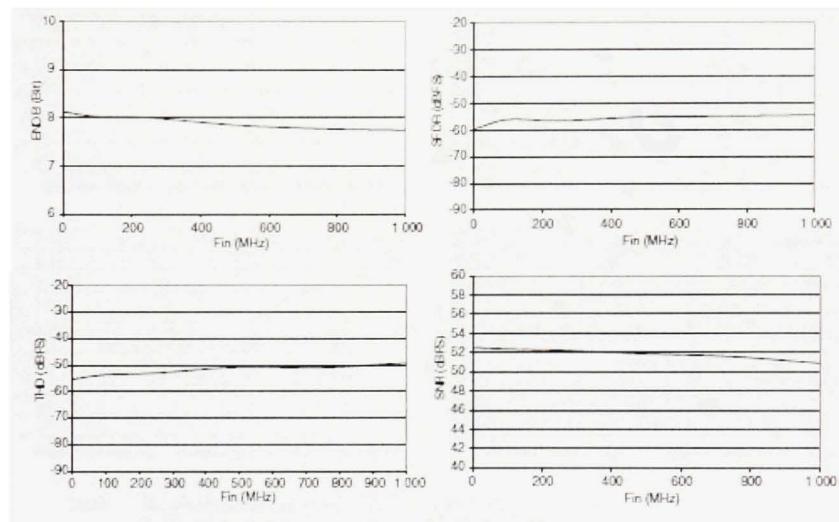

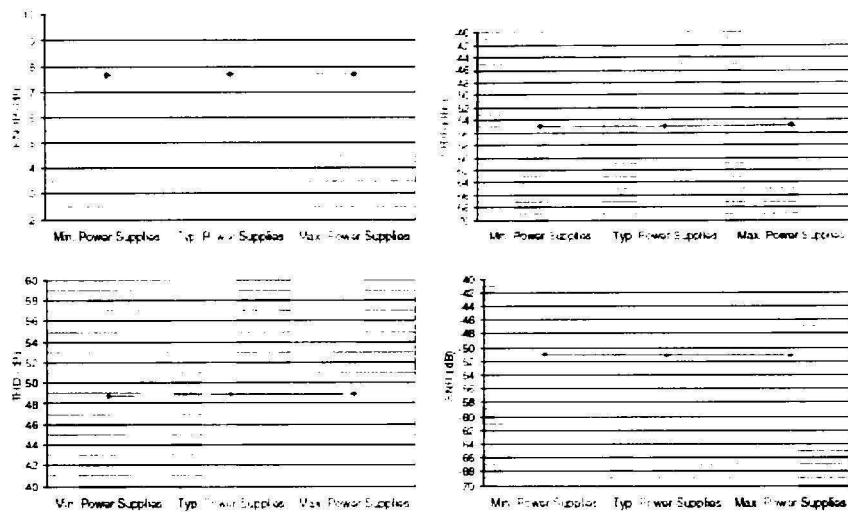

Le chapitre suivant présente les caractéristiques mesurées en laboratoire du CAN sélectionné. Quatre spécifications sont ainsi comparées aux données fournies par le manufacturier : la vitesse maximale de fonctionnement, le bruit de quantification à vitesse maximale, le *spurious free dynamic range* (SFDR) et le bruit de phase.

Enfin, le dernier chapitre est consacré au récepteur numérique proprement dit. L'effet des spécifications, mesurées au chapitre précédent, sur la démodulation est évalué pour deux modes d'échantillonnage distincts : l'échantillonnage direct et le sous-échantillonnage. Une discussion de l'influence du convertisseur sur la configuration idéale de la radio logicielle termine le travail.

Ce travail permet de démontrer que les détériorations occasionnées par la conversion du signal analogique en signal numérique n'empêchent pas l'utilisation d'un CAN comme récepteur direct des radiofréquences. La puissance du parasite le plus élevé et le bruit de phase de l'horloge sont les deux facteurs les plus limitatifs. La contribution principale de ce travail est la réalisation d'une radio-logicielle capable de démoduler un signal situé dans la bande comprise entre 0 et 800 MHz, sans utiliser de mélangeur et de filtres analogiques.

# CHAPITRE 1

## TECHNOLOGIES DE CONVERSION DE HAUT DÉBIT

### 1.1 Revue des techniques et des méthodes de conversion d'un signal analogique à un signal numérique

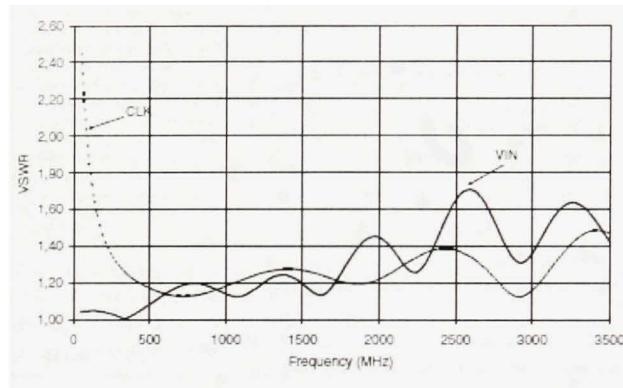

Plusieurs modèles de CAN sont disponibles sur le marché. À chaque modèle conviennent certaines techniques relatives à leur utilisation. Cependant, tous ne répondent pas aux besoins typiques d'un récepteur à étage radiofréquences (RF) numérique (*Voir Figure 1.1*). Soit une plage dynamique élevée, une SFDR de plus de 50 dBFS et une gigue de phase très petite. Avant même d'analyser ces besoins spécifiques, une revue de la littérature, traitant des techniques et méthodes de conversion d'un signal analogique à numérique, s'impose.

Figure 1.1 Architecture d'une radio logicielle idéale.

#### 1.1.1 Méthodes peu répandues de conversion d'un signal analogique à numérique

Cette section traite des méthodes utilisant des conversions de type théorique ou encore très peu répandues. La première méthode abordée est la conversion optique d'un signal électrique. Plusieurs auteurs proposent des convertisseurs analogiques à numérique optiques allant à des vitesses de beaucoup supérieures aux convertisseurs traditionnels. Selon (Clark, 2001), les CAN optiques permettent des vitesses beaucoup plus grandes avec une immunité quasi-complète aux interférences électromagnétiques. Cependant, de tels convertisseurs ne

sont pas commercialement disponibles. Ils nécessitent donc une fabrication à la pièce. (Jiang et al., 2005) en propose un, éprouvé expérimentalement, pouvant atteindre 80 milliard d'échantillons par seconde (GSPS, *Giga samples per second*). Le CAN qu'il propose module un signal provenant d'un laser verrouillé sur un mode à partir d'un signal en radiofréquence (RF), en utilisant un modulateur Mach-Zehnder. Bien que la largeur de bande présumée à l'entrée du CAN soit de 40 GHz, Jiang ne présente que des résultats utilisant un signal d'entrée inférieur à 11 GHz. De plus, le rapport signal à bruit de moins de 15 dB est bien inférieur à ceux des convertisseurs traditionnels.

Une autre méthode existante, combinant photonique et électronique, est l'étirement temporel. Typiquement, on utilise un circuit optique pour « ralentir » un signal RF entrant. Par « ralentir » on entend convertir le signal à une fréquence inférieure. On peut ensuite reconvertisir le signal optique résultant en signal électromagnétique et utiliser un CAN standard. On utilise ensuite un processeur numérique pour traiter le signal. Les avantages et inconvénients de cette méthode varient en fonction du circuit optique utilisé. Parmi ceux suggérés dans la littérature, celui de (Han, Boyraz et Jalali, 2005) permet d'atteindre une vitesse d'échantillonnage de 480 GSPS. Malheureusement, le CAN résultant n'a qu'une résolution de 5,17 bits effectifs (NBE).

La dernière méthode non-conventionnelle proposée consiste à utiliser un CAN supraconducteur. L'utilisation d'un tel dispositif permet des vitesses de conversion atteignant la dizaine de gigahertz (GHz). Par exemple, le circuit proposé par (Furuta et al., 2007) a été opéré à une vitesse de 10 GHz pour un rapport signal à bruit de 71 dB. Celui proposé par (Yoshida et al., 2007), conçu pour fonctionner à la vitesse théorique de 20 GHz, a été vérifié à 16 GHz avec un rapport signal à bruit de 69 dB. Les matériaux supraconducteurs utilisés dans ces convertisseurs permettent des temps de transition des semi-conducteurs plus courts, ainsi que la réduction du bruit thermique. Néanmoins, la bande passante du signal à l'entrée admissible de ces dispositifs est très limitée (10 MHz), rendant la bande passante instantanée comparable à des pièces disponibles commercialement. De plus, ces circuits doivent être

refroidis à une température proche du zéro absolu, rendant difficile, voir impossible, l'utilisation d'un tel convertisseur hors-laboratoire.

### 1.1.2 Méthodes traditionnelles de conversion d'un signal analogique à numérique

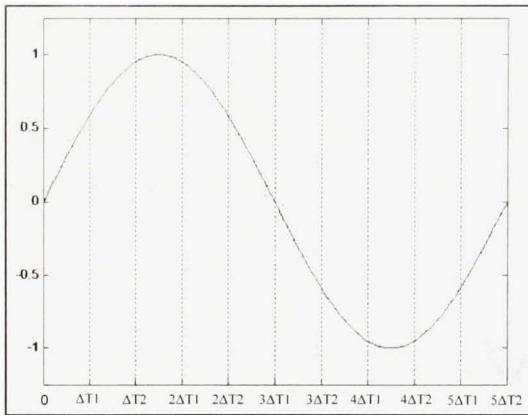

Les méthodes traditionnelles de conversion du signal utilisent des CAN commercialement disponibles. Ces méthodes sont aussi utilisées dans des systèmes connus. Par exemple, les oscilloscopes numériques utilisent l'entrelacement temporel pour faire l'acquisition de signaux à grande vitesse. L'entrelacement temporel consiste à utiliser plusieurs CAN pour numériser un seul signal. Les convertisseurs sont déclenchés à des intervalles différents espacés de  $\Delta T$  et quantifient une valeur différente du signal (*Voir Figure 1.2*). Les signaux numériques résultants sont ensuite recombinés à l'aide d'un PNS. Ainsi, on obtient un taux d'échantillonnage effectif proportionnel au nombre de CAN utilisés. Toutefois, l'incertitude sur le moment exact de quantification du signal analogique est accentuée par la présence de plusieurs CAN et par la précision relative du circuit qui déclenche les convertisseurs. Aussi, cette configuration est particulièrement sensible aux différences entre les non-linéarités des CAN utilisées (Kurosawa et al., 2001). Des méthodes de conception d'un tel circuit existent, comme démontré par les articles de (Jridi et al., 2006) et (El-Sankary, Assi et Sawan, 2003), qui proposent des méthodes de modélisation et d'analyse d'un canal entrelacé à plusieurs CAN. On doit aussi noter qu'il existe des puces électroniques contenant plusieurs CAN fonctionnant en entrelacement temporel. Ces puces sont vendues en tant que convertisseur unique et le manufacturier fourni les spécifications pour le système entier.

**Figure 1.2 Échantillonnage par entrelacement temporel.**

Les méthodes directes, utilisées les plus fréquemment, sont celles utilisant un seul convertisseur, numérisant un seul signal. Ces méthodes sont basées sur le critère de Nyquist (*Voir Équation 1.1*). Ce critère stipule qu'un signal analogique doit être échantillonné à une fréquence  $f_s$ , égale ou supérieure à deux fois la fréquence maximale de ce signal, pour un signal s'étalant de 0 Hz à  $f_{\max}$  Hz.

$$f_s \geq 2f_{\max} \quad (1.1)$$

Dans la configuration directe, on peut numériser un signal se trouvant dans la bande 1 de Nyquist, c'est-à-dire entre 0 et  $f_s/2$  Hz. On peut aussi échantillonner un signal se trouvant dans une bande de Nyquist supérieure, à condition que la bande passante à l'entrée du convertisseur le permette. Cette technique est appelée sous-échantillonnage. Le critère de Nyquist doit tout de même être respecté; la fréquence d'échantillonnage doit être égale ou supérieure à deux fois la largeur de bande du signal analogique.

La méthode de sur-échantillonnage s'applique en complément à toute autre méthode mentionnée précédemment. Le sur-échantillonnage permet des gains sur le rapport signal à bruit introduit par le CAN en numérisant le signal à une fréquence supérieure au rythme de Nyquist. Ce gain est possible en filtrant le signal numérique à l'aide d'un PSN. Comme le

bruit de quantification est distribué de façon uniforme entre 0 et  $f_s/2$  Hz, on peut l'étaler sur une plus grande plage de fréquence et en éliminer une partie par filtrage. Le gain potentiel associé peut être calculé en utilisant l'équation (1.2), tirée de (Kester, 2004). Le gain est calculé en décibels et le terme  $BW$  représente la bande passante du signal analogique.

$$\boxed{Gain_{dB} = 10 \log_{10} \frac{f_s}{2 \cdot BW}} \quad (1.2)$$

Le rapport signal à bruit de quantification et distorsion (S/N) peut aussi être calculé aisément en décibels (*Voir Équation (1.3)*), (Kester, 2004).

$$\boxed{S / N_{dB} = 6,02 \times NBE + 1,76} \quad (1.3)$$

Notons qu'en pratique, il est plus facile de mesurer le SINAD que le nombre de bits effectifs. Il est donc plus commun d'utiliser l'équation 1.3 pour connaître ce nombre que le rapport signal à bruit.

## 1.2 Choix de la technique retenue

Avant de sélectionner un convertisseur à utiliser, on doit d'abord décider laquelle des configurations mentionnées précédemment sera utilisée. Les méthodes décrites ont toutes des avantages et inconvénients. Des explications de ceux-ci précèdent le choix définitif de la méthode à utiliser.

Pour faire un choix éclairé, il est nécessaire de connaître les besoins spécifiques à la réalisation d'un étage RF numérique. Dans le présent travail, les bandes de fréquences ciblées, selon les standards militaires, sont énumérées dans le Tableau 1.1. On ne numérise ces bandes qu'une à la fois. Ainsi, la bande passante nécessaire maximale est de 850 MHz. Pour respecter le critère de Nyquist, on doit donc convertir le signal à un rythme minimum de 1,7 GSPS. De plus, le signal analogique RF est compris entre 225 MHz et 5000 MHz.

Tableau 1.1 Bandes de fréquences ciblées pour la conversion numérique à analogique.

| <b>Bandes</b> | <b>Fréquence inférieure</b> | <b>Fréquence supérieure</b> | <b>Largeur de bande</b> |

|---------------|-----------------------------|-----------------------------|-------------------------|

| <b>Nom</b>    | MHz                         | MHz                         | MHz                     |

| Bandes 1      | 225                         | 400                         | 175                     |

| Bandes 3      | 1350                        | 1850                        | 500                     |

| Bandes 3+     | 1850                        | 2700                        | 850                     |

| Bandes 4      | 4400                        | 5000                        | 600                     |

### 1.2.1 Avantages et inconvénients des méthodes exotiques et traditionnelles de conversion d'un signal analogique à numérique

Les convertisseurs optiques ont l'avantage d'être très rapides. Ainsi, le faible rapport signal à bruit rapporté dans la littérature peut être compensé par sur-échantillonnage. Cependant, l'absence de modèles commerciaux rend très difficile leur utilisation. Bien que plusieurs auteurs proposent des modèles « prêt à construire », une expertise humaine et technique est nécessaire pour réussir une telle fabrication. De plus, il est important de garder à l'esprit que le convertisseur utilisé doit être relié à un processeur numérique du signal. Ainsi, les grandes vitesses d'opération de ces convertisseurs deviennent difficiles à conjuguer avec un PNS standard.

La technique d'étirement temporelle semble plus intéressante parce que le signal est numérisé à l'aide d'un convertisseur conventionnel. De plus, le matériel optique nécessaire est vendu par des commerces spécialisés. Il est virtuellement possible d'échantillonner n'importe quel signal. La limite se situe au niveau de la précision du laser utilisé. Bien qu'attrayante, cette méthode comporte un désavantage majeur; il est impossible de traiter des données de façon continue, puisque l'étirement temporel sous-entend un délai inhérent. En effet, plus le signal à numériser est élevé en fréquence, plus il doit être ralenti pour être

numérisé par un CAN standard. La période étant inversement proportionnelle à la fréquence, le temps de traitement est alors augmenté conséquemment.

Les CAN supraconducteurs sont plus rapides que les convertisseurs traditionnels et offrent d'excellents rapports signal à bruit. Tout comme les convertisseurs optiques, ils ne sont pas disponibles autrement que par fabrication personnelle, demandant ainsi autant d'expertise.

La méthode d'entrelacement temporel permet d'augmenter la fréquence d'échantillonnage en augmentant le nombre de convertisseurs utilisés. Un circuit d'amorçage des CAN doit être conçu pour déclencher chaque convertisseur au bon moment. Une incertitude sur la période d'échantillonnage existe pour tous les CAN, ajoutant ainsi de la distorsion au signal original. En utilisant plusieurs convertisseurs, on accumule ces incertitudes. Le circuit d'amorçage ajoute aussi un bruit de phase supplémentaire au montage.

La conversion directe du signal analogique en signal numérique est la technique la plus simple. Elle est néanmoins limitée par le CAN utilisé. Les fréquences d'échantillonnage de ceux-ci dépassant rarement 200 MHz, la conversion directe du signal ne permet alors pas de numériser un signal d'une largeur de bande excédant 100 MHz. Cependant, il existe des CAN spécialisés fonctionnant à plus de 2 GSPS. Ces convertisseurs sont onéreux et souvent disponibles uniquement auprès de leurs fabricants.

Bien sûr, le sur- et sous-échantillonnage est compatible avec toutes les méthodes mentionnées.

### **1.2.2 Sélection préalable de la technique de conversion**

Comme les convertisseurs optiques et à supraconducteurs ne sont pas disponibles commercialement, ces méthodes sont à éviter.

L'étirement temporel s'applique à des communications par salves, en autant que ces salves soient d'une période connue. Les communications des radios logicielles ne font pas des transmissions par salves exclusivement. Ainsi, l'étirement temporel est inapproprié dans le cadre du présent travail. Les méthodes traditionnelles s'imposent donc.

Par entrelacement temporel, on peut utiliser plusieurs CAN pour arriver à numériser une grande largeur de bande. Pour limiter le budget alloué à l'achat des convertisseurs, il est préférable d'en choisir un modèle fonctionnant à moins de 150 MSPS; le prix grimpant rapidement après cette barrière. Aussi, puisque la distorsion occasionnée par l'utilisation de plusieurs convertisseurs est proportionnelle au nombre de CAN utilisés, ce nombre doit être le moins élevé possible. Pour numériser un signal d'une largeur de bande de 1 GHz, plus de dix convertisseurs sont requis, ce qui entraîne une très grande distorsion du signal.

Ainsi, la méthode retenue pour réaliser un étage RF numérique est la conversion directe. Les performances de la conversion directe dépendent directement du convertisseur utilisé. Le choix de ce dernier est donc une étape importante de la conception du récepteur direct des radiofréquences.

### **1.3 Revue des convertisseurs analogique-numérique disponibles sur le marché**

Afin de sélectionner un CAN adéquat, on doit d'abord revoir quelles spécifications influencent le plus la réception d'un signal analogique à large bande. Cette section dresse la liste des caractéristiques à rechercher chez un convertisseur, puis passe en revue des CAN disponibles sur le marché qui offrent des performances adéquates. Enfin, un de ces convertisseurs est sélectionné.

### 1.3.1 Caractéristiques souhaitables pour un CAN utilisé dans un étage de conversion directe des radiofréquences

#### Fréquence d'échantillonnage ( $f_s$ )

Tel que décrit à la section 1.1.2, la fréquence d'échantillonnage doit être au minimum deux fois supérieure à la fréquence maximale du signal analogique à échantillonner. Ici, la bande de fréquence la plus grande s'étend sur 850 MHz. Pour être en mesure de numériser cette partie du spectre au complet, la fréquence d'échantillonnage doit être d'un minimum de 1,7 GSPS. Puisqu'il s'agit d'une borne minimum, il est préférable d'utiliser une fréquence d'échantillonnage supérieure. Le nombre de convertisseurs permettant d'atteindre ce taux est très limité. Il est aussi possible d'utiliser une banque de filtres pour diviser la largeur de bande à échantillonner. Ainsi, on relâche les contraintes sur la fréquence d'échantillonnage, mais on diminue la bande passante instantanée disponible.

#### Nombre de bits

La conversion analogique à numérique implique une quantification du signal original. Le CAN assigne alors une valeur numérique au signal visé. Le nombre de bits disponibles définit le nombre de valeurs possibles du signal numérique. Puisque le signal analogique, contrairement au signal numérique, comprend une infinité de valeurs, il y a perte d'information. Cette perte d'information est appelée *bruit de quantification*. Plus il y a de bits, moins il y a de bruit de quantification. On doit noter que le CAN induit aussi d'autres formes de bruits. On calcule souvent le nombre de bits effectifs (NBE), inférieur au nombre de bits total, pour caractériser la l'ensemble du bruit infligé au signal.

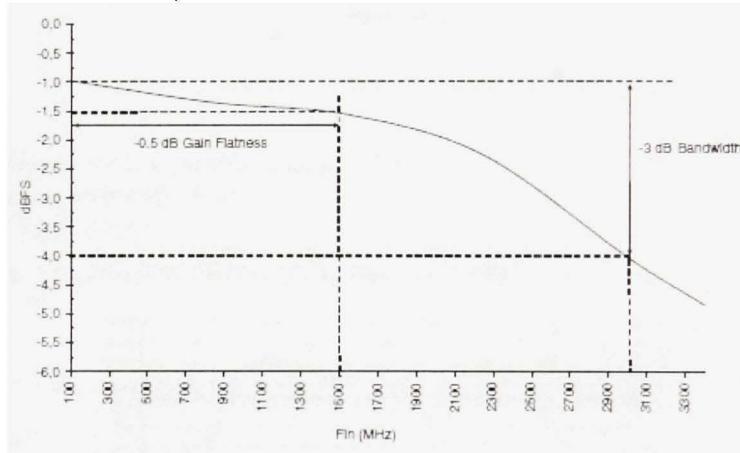

#### Largeur de bande

Puisque les bandes de fréquences à numériser sont principalement situées à plus de 1 GHz, et qu'aucun CAN n'échantillonne assez vite pour numériser cette portion directement, il est indispensable d'utiliser la technique de sous-échantillonnage. La bande passante à l'entrée du convertisseur est donc à surveiller.

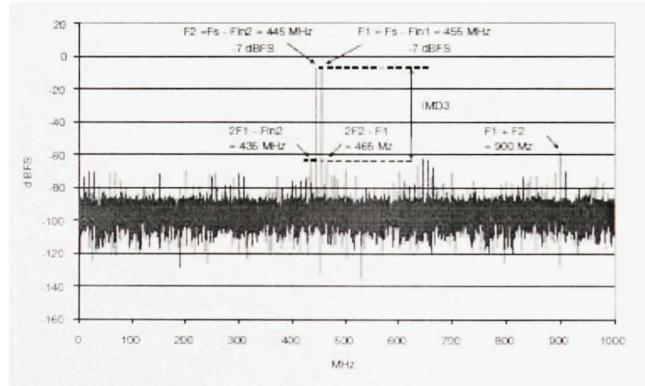

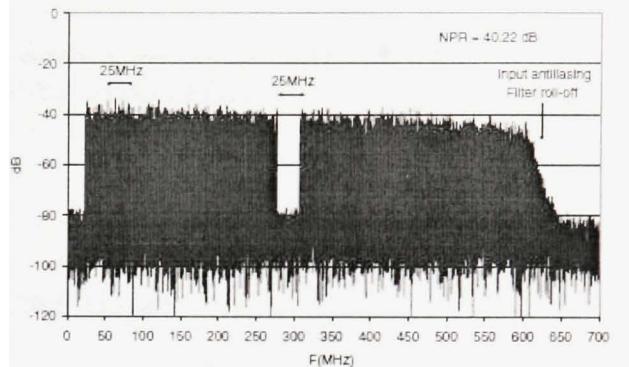

## Plage dynamique sans parasites (SFDR)

Les non-linéarités du convertisseur occasionnent des signaux parasites. Ces signaux parasites apparaissent comme des pics sur le spectre fréquentiel du signal numérique. On calcule la SFDR en faisant la différence des puissances en dBm, entre le signal d'intérêt et le parasite le plus puissant. La position des parasites varie en fonction du CAN, mais aussi en fonction du signal analogique à l'entrée. Bien sûr, les harmoniques du signal analogique, ainsi que l'intermodulation de ce dernier et de ses harmoniques avec l'horloge sont des parasites fréquemment obtenus. Cependant, ils ne sont pas systématiquement les parasites de plus forte puissance. Il est donc impossible de prédire et d'éliminer les parasites. Ainsi, la SFDR est une indication très pertinente sur le niveau des signaux non-désirés pouvant interférer avec les fréquences d'intérêt. Cette plage doit être la plus grande possible, sinon les informations à récupérer seront erronées.

## Sensibilité

La SFDR n'est pas suffisante à elle seule pour déterminer si les parasites occasionneront des pertes d'information. On doit comparer la puissance des parasites à la puissance du signal reçu. Dans un système où le canal est sélectionné avant le CAN, le signal d'intérêt est toujours le plus puissant. De plus, le gain du signal analogique est contrôlé de façon à optimiser la plage dynamique du convertisseur. Dans le cadre d'un récepteur direct, le signal le plus puissant n'est pas nécessairement celui ciblé. La sensibilité est définie comme l'amplitude minimale, en volts, que le convertisseur peut détecter. Cette valeur correspond aussi au pas de quantification et est liée au nombre de bits. On peut calculer la sensibilité à partir de l'équation (1.4).

$$q = \frac{V_{c-c}}{2^n} \quad (1.4)$$

Où  $q$  représente la sensibilité,  $V_{c-c}$  est la tension crête-à-crête maximale à l'entrée du CAN et  $n$  est le nombre de bits du convertisseur. On cherche à minimiser cette valeur en maximisant le nombre de bits.

## Rapport signal à bruit (S/N)

Le rapport signal à bruit donne une idée globale des performances du convertisseur. Les manufacturiers spécifient le rapport signal à bruit sous forme de courbes ou de tableaux. La valeur retenue pour comparaison est celle la plus proche possible de la fréquence de Nyquist, à une fréquence d'échantillonnage maximale. Il est possible, à partir du rapport signal à bruit en dB, de calculer le NBE (*Voir Équation (1.5)*).

$$NBE = \frac{S/N - 1,76}{6,02} \quad (1.5)$$

### 1.3.2 Comparaison et choix d'un convertisseur

Cette section présente les convertisseurs disponibles sur le marché ayant le potentiel d'être utilisés dans la réception directe des radiofréquences.

Tableau 1.2 Comparaison des convertisseurs disponibles sur le marché.

| <b>Fabricant</b> | <b>Modèle</b>  | <b>f<sub>s</sub></b> | <b>Nombre de bits</b> | <b>Largeur de bande</b> | <b>PDSP</b> | <b>Sensibilité</b> | <b>S/N</b> |

|------------------|----------------|----------------------|-----------------------|-------------------------|-------------|--------------------|------------|

|                  |                | (MSPS)               |                       | (GHz)                   | (dB)        | (mV)               | (dB)       |

| National         | ADC083000      | 3000                 | 8                     | 3                       | 52          | 2,3                | 41,1       |

| Maxim            | MAX109         | 2200                 | 8                     | 2,8                     | 50,3        | 2                  | 42,1       |

| e2v              | AT84AS004      | 2000                 | 10                    | 3                       | 55          | 0,4                | 51         |

| National         | ADC081500      | 1500                 | 8                     | 1,7                     | 53          | 2,5                | 43,9       |

| National         | ADC081000      | 1000                 | 8                     | 1,7                     | 58,5        | 2,3                | 47         |

| TI               | ADS5463        | 500                  | 12                    | 2,3                     | 75          | 0,5                | 64,6       |

| Intersil         | KAD5510P-50Q72 | 500                  | 10                    | 1,3                     | 68          | 1,4                | 58,5       |

| Analog device    | AD12401        | 400                  | 12                    | 0,175                   | 68          | 0,4                | 58         |

| Linear           | LTC2242-12     | 250                  | 12                    | 1200                    | 75          | 0,5                | 65,3       |

| NXP              | ADC0808S       | 250                  | 8                     | 0,56                    | 49          | 7,8                | 45         |

Le Tableau 1.2 compare les plus rapides d'entre eux, selon les caractéristiques mentionnées à la section précédente. À première vue, on constate que seulement trois modèles de

convertisseurs ont un taux d'échantillonnage de 2 GSPS ou plus. Le modèle ADC083000 de *National* est en fait un convertisseur à entrelacement temporel; la puce est constituée de deux convertisseurs ADC081500. Aussi, aucun CAN n'a plus de 12 bits disponibles. La plage dynamique sans parasites est semblable pour tous les modèles à très haute fréquence d'échantillonnage. On remarque des performances plus intéressantes à ce niveau pour des convertisseurs plus lents, c'est-à-dire de moins de 1 GSPS.

Pour faire la conversion directe d'un signal RF de 850 MHz de largeur de bande, on doit éliminer tous les convertisseurs de moins de 1700 GSPS, laissant seulement trois convertisseurs potentiels. Ces trois convertisseurs ont tous une plage dynamique, une largeur de bande à l'entrée et une fréquence d'échantillonnage semblable ou suffisante. On doit noter que les trois procèdent au démultiplexage des données numériques sur 4 ports. La sensibilité et le rapport signal à bruit étant reliés directement au nombre de bits, celui-ci devient un facteur comparatif très important.

Bien que les CAN de *National* et de *Maxim* soient plus rapides, le convertisseur de la compagnie *e2v* offre deux bits de plus. Avant d'affirmer que ce dernier est le meilleur choix dans le contexte d'utilisation souhaité, on doit s'assurer qu'il n'est pas surclassé par un autre convertisseur lorsqu'en présence d'un gain de sur-échantillonnage (*Voir Tableau 1.3*).

Tableau 1.3 Rapport signal à bruit des convertisseurs avec un gain de sur-échantillonnage.

| Fabricant | Modèle    | $f_s$  | Bande passante du signal | Nombre de bits | S/N avec sur-échantillonnage |

|-----------|-----------|--------|--------------------------|----------------|------------------------------|

|           |           | (MSPS) | (MHz)                    | (bits)         | (dB)                         |

| National  | ADC083000 | 3000   | 10                       | 8              | 62,9                         |

| Maxim     | MAX109    | 2200   | 10                       | 8              | 62,5                         |

| e2v       | AT84AS004 | 2000   | 10                       | 10             | 71,0                         |

On remarque ainsi que les deux bits supplémentaires du convertisseur ont une plus grande influence que le gain de sur-échantillonnage potentiel. On sélectionne donc l'AT84AS004 d'e<sup>2</sup>v comme étant le mieux adapté à la conversion directe des radio-fréquences.

## 1.4 Modèles de simulation de convertisseurs analogique à numérique

Il est avantageux d'être en mesure de simuler préalablement le système, sans avoir besoin d'un banc d'essai à chaque expérimentation. Cependant, pour être en mesure d'y arriver, un modèle complet et fiable est requis. Cette section présente trois modèles utilisés pour faire la simulation d'ADC tirés, entre autres, de (Arpaia, Daponte et Rapuano, 2004). Cet article, contenant plus de quatre-vingt-dix références, recense la plupart des modèles existants. Trois de ces derniers sont résumés et expliqués dans cette section : un modèle comportemental, le modèle par table de conversion, puis le modèle électrique.

### 1.4.1 Modèle comportemental

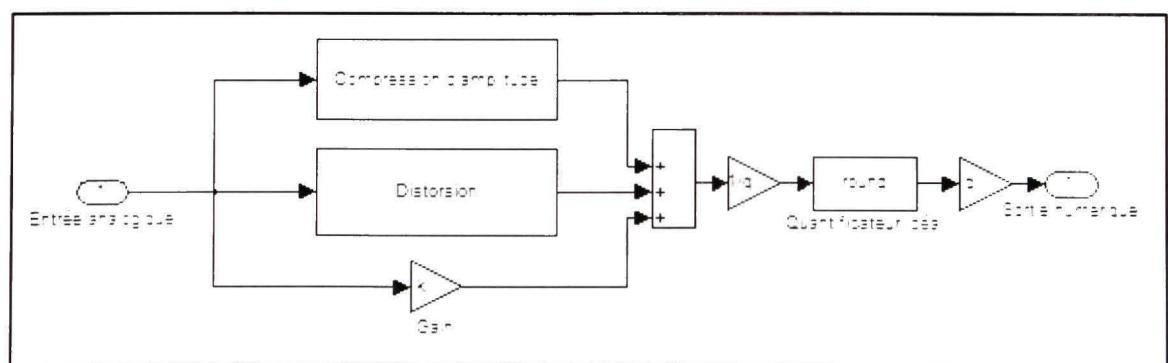

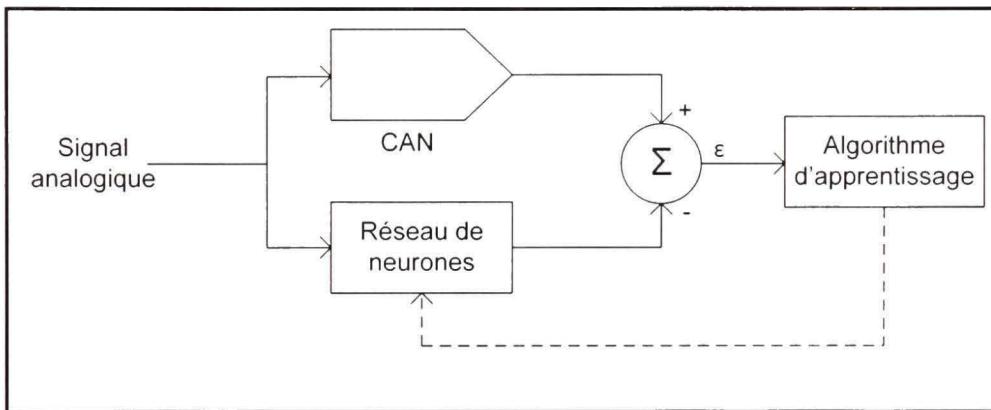

Les modèles comportementaux décrivent les comportements d'un ADC en particulier. Dépendamment des situations dans lesquelles les convertisseurs sont utilisés, plusieurs modèles comportementaux sont disponibles. Celui présenté ici (*Voir Figure 1.3*) est tiré de (Baccigalupi et D'Apuzzo, 1996).

**Figure 1.3 Modèle comportemental.**

Trois comportements sont modélisés : la compression d'amplitude, la distorsion et le gain du CAN. Les trois effets sont additionnés et un quantificateur idéal assigne une valeur numérique au résultat. Le gain est utilisé pour adapter la distorsion harmonique totale du modèle à celui du convertisseur. La compression d'amplitude représente la saturation des composantes électroniques. On peut décrire cette compression par l'équation suivante.

$$\boxed{\text{Sortie} = a * \tanh(\text{Entrée} / b)} \quad (1.6)$$

Les paramètres  $a$  et  $b$  varient en fonction du convertisseur et doivent être ajustés. Puisque la compression d'amplitude provient de la saturation d'éléments du convertisseur, elle suscite l'apparition d'harmoniques impaires dans le spectre fréquentiel (Baccigalupi et D'Apuzzo, 1996).

La distorsion représente les imperfections du convertisseur provoquant les harmoniques paires du spectre fréquentiel. On la calcule à l'aide de l'équation (1.7). Les paramètres  $c$  et  $d$  sont aussi à ajuster.

$$\boxed{\text{Sortie} = d * [1 - \cosh(\text{Entrée} / c)]} \quad (1.7)$$

L'avantage de cette méthode réside dans la facilité de son utilisation. L'ajustement des paramètres est fait par tâtonnement et l'implémentation du modèle est très rapide. Cependant, les paramètres ne sont valides que pour la forme d'onde utilisée pour les calculer. C'est-à-dire que si les paramètres sont obtenus par l'observation du spectre d'un sinus de 10 MHz numérisé, les paramètres ne sont valides que pour décrire la conversion de sinus de 10 MHz. Ainsi, on ne peut utiliser des paramètres obtenus à partir de la numérisation d'un sinus pour décrire la conversion d'une onde carrée par le CAN.

#### 1.4.2 Modèle par table de conversion

Le modèle par table de conversion est un type particulier de modèle comportemental. Il consiste à remplir une table qui associe la valeur numérique à la sortie du CAN à la valeur analogique correspondante. La taille de la table varie en fonction du nombre de bits du convertisseur. Pour un convertisseur 10 bits, la table comporte un minimum de  $2^{10}=1024$  éléments. Sans information complémentaire, ce modèle n'est pas plus précis qu'un bloc de quantification idéale. On tabule donc les valeurs du signal analogique auxquelles le signal numérique commute. On tient ainsi compte des non-linéarités du CAN.

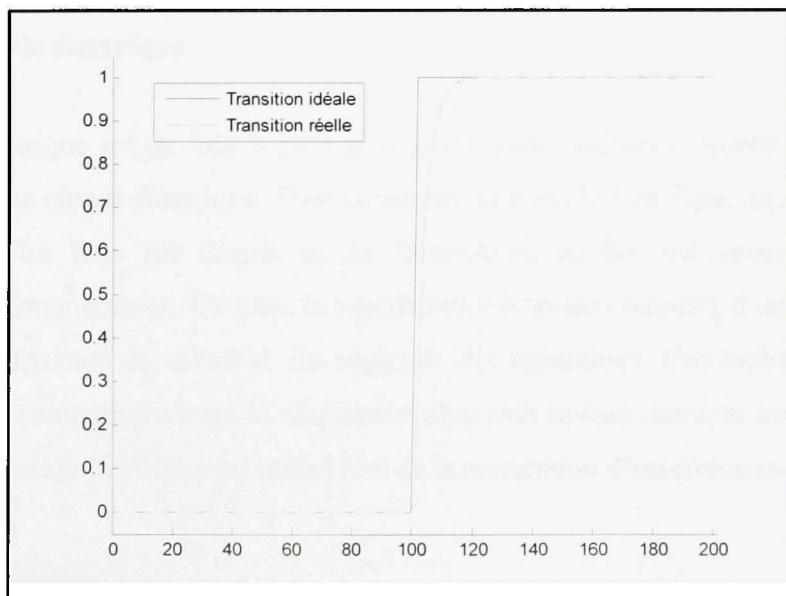

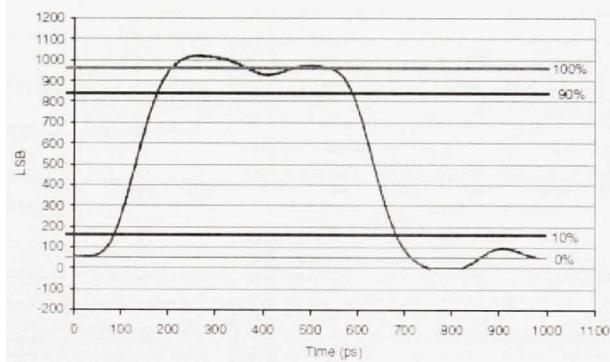

Bien que plus précise, cette méthode ne représente pas le convertisseur de façon optimale. La transition entre un « 1 » et un « 0 » logique à la sortie du CAN n'est pas idéale. Comme l'illustre la Figure 1.4, la transition prend un certain temps. Les manufacturiers donnent les spécifications relatives au temps que prend la sortie pour transiter. Cependant, cette seule valeur ne suffit pas à modéliser cet effet.

Figure 1.4 Transition d'un bit à la sortie d'un CAN.

Ces imperfections peuvent aussi dépendre du signal présent ou précédent à l'entrée. Il peut ainsi devenir difficile de remplir une table de conversion fidèle au comportement du CAN. (Bernieri, Daponte et Grimaldi, 1996) propose de remplir cette table par modélisation neurale. Sa technique consiste à utiliser un réseau de neurones associé à un algorithme d'apprentissage pour remplir la table (*Voir Figure 1.5*).

**Figure 1.5 Remplissage d'une table de conversion par réseau de neurones.**

#### 1.4.3 Modèle électrique

Le modèle électrique est de loin le plus précis des trois modèles présentés ici. Il décrit le CAN en tant que circuit électrique. Pour construire le modèle électrique d'un convertisseur, on doit connaître tous les détails de sa fabrication, ce qui est impossible pour les convertisseurs commerciaux. De plus, la simulation électrique complète d'un CAN demande beaucoup de puissance de calcul et des logiciels très spécialisés. Ces logiciels ne sont pas nécessairement compatibles avec la simulation plus haut niveau associée avec le traitement de signal. Le modèle électrique est utilisé lors de la conception d'un convertisseur.

### 1.5 Conclusion

Ce chapitre a présenté plusieurs méthodes de conversion d'un signal analogique à numérique. On y a vu que les méthodes théoriques, bien qu'elles permettent des rythmes de conversion

plus élevés, ne peuvent être utilisées dans le présent travail. Les méthodes traditionnelles, sont donc utilisées.

Après avoir expliqué le choix des méthodes traditionnelles, une revue des convertisseurs disponibles sur le marché permet d'en sélectionner un modèle de la compagnie *e2v* qui répond aux besoins. Finalement, on résume les techniques les plus courantes pour simuler les CAN. Comme les techniques de simulations précises nécessitent beaucoup de calculs que les techniques plus conviviales ne sont pas précises, on conclut que l'utilisation d'un banc d'essai est la meilleure façon de simuler le comportement d'un CAN.

## CHAPITRE 2

### CONCEPTION DU RÉCEPTEUR NUMÉRIQUE

#### 2.1 Introduction

Le premier chapitre élaborait la sélection d'une architecture de conversion et d'un convertisseur. À partir de ces informations, il est maintenant nécessaire de faire la conception du récepteur numérique utilisé pour évaluer l'impact du CAN sur la démodulation du signal.

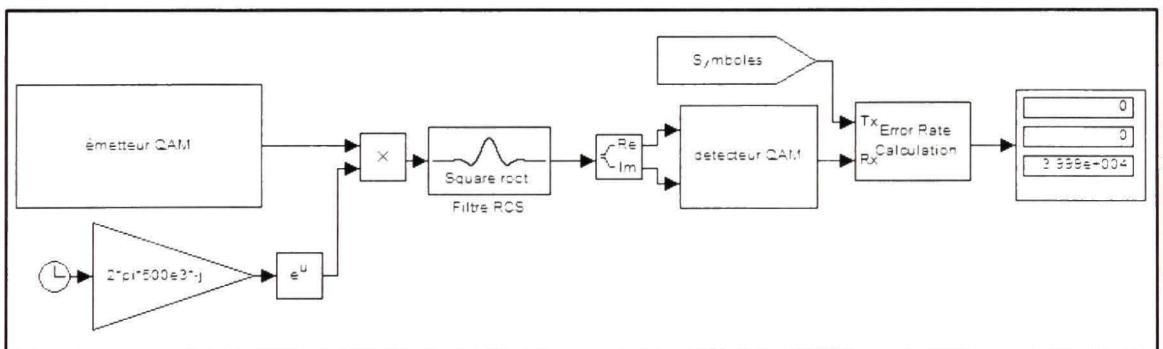

La première étape de la réalisation d'un récepteur direct des radiofréquences est la conception d'un circuit imprimé pour interconnecter le CAN et le PNS (*Voir CHAPITRE 3*). Ce circuit doit s'interfacer d'une part avec la carte de développement *e2v* et d'autre part avec les sondes d'un analyseur logique *Tektronix*. Le traitement du signal est fait hors-ligne, un ordinateur personnel sert de PNS. Des spécifications précises sur la fabrication de la carte de développement du CAN sont fournies par le manufacturier. Ainsi, la carte d'interconnexion sera conçue en s'inspirant de ces spécifications.

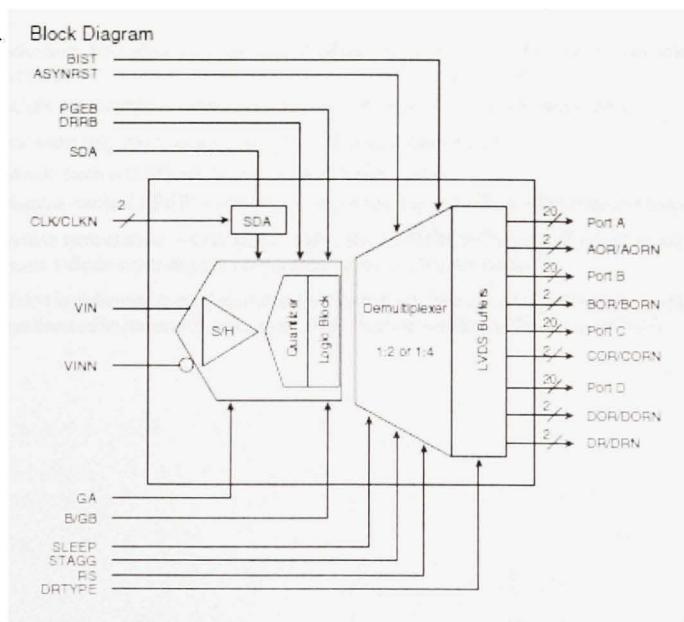

La carte d'évaluation comprend un convertisseur numérique à analogique AT84AS004 monté sur un circuit imprimé. On privilégie l'approche par carte d'évaluation, puisque le temps de conception est considérablement réduit. Le circuit imprimé permet de relier les sorties numériques et les entrées analogiques. Il est alimenté par 5 sources de tension différentes. Des cavaliers permettent de régler les paramètres du CAN, notamment le rapport de démultiplexage des sorties numériques (1:2 ou 1:4), la fréquence du signal « données prêtes » (DP) et le mode d'autotest. Les spécifications du convertisseur sont présentées en annexe (*Voir ANNEXE I*).

Le manuel d'utilisateur des sondes P6980, de la compagnie *Tektronix*, définit les critères à respecter pour relier la sonde à un circuit imprimé. De plus, le manuel fournit un modèle électrique haute et un autre basse fréquence. Ces modèles seront utilisés dans une simulation vérifiant l'intégrité du signal.

Dans cette section, on présente d'abord les critères de conception du circuit imprimé. Ensuite, l'intégrité du signal par simulation est vérifiée et comparée à des mesures prises sur le circuit final. Enfin, la partie logicielle du récepteur est exposée.

## 2.2 Conception du circuit imprimé

La conception du circuit imprimé commence par la détermination de paramètres à respecter. Certains de ces paramètres sont dictés par le fabricant du circuit, d'autres par des contraintes de design. Dans la première catégorie de paramètres, on retrouve l'épaisseur minimale des traces, la taille minimale des vias et le type de substrat diélectrique à utiliser. Les contraintes de design fixent les valeurs maximales de ces mêmes éléments. Celles-ci sont dictées par la taille même des éléments, l'impédance des traces à respecter et l'espace disponible pour les placer.

Dépendamment de la fréquence d'opération, une trace de circuit imprimé peut être considérée soit comme un élément de circuit électrique, soit comme une ligne de transmission. Il est alors de rigueur de débuter l'analyse en vérifiant de quel type il s'agit. De plus, l'impédance des câbles plats, utilisés pour relier le circuit imprimé à la carte d'évaluation, sera étudiée. Par la suite, l'essentiel théorique pour calculer l'impédance d'une ligne de transmission microbande est exposé, suivi du calcul pour le cas présent.

Le circuit imprimé aura comme fonction de raccorder la carte de développement du CAN aux sondes de l'analyseur logique *Tektronix TLA7012*. Ces dernières se branchent directement sur un circuit imprimé en utilisant un design précis fourni par le manufacturier. Les facteurs de tailles maximales des traces sont dictés par la taille des sondes. En effet, pour permettre un dégagement adéquat entre les traces et les points de raccordement, une largeur maximale de 0,2 mm doit être utilisée. Ainsi, l'épaisseur du diélectrique est calculée en conséquence pour adapter les impédances. Aussi, les vias doivent être localisés directement dans les points de connexion des sondes. Ainsi, le diamètre maximal de ceux-ci ne peut dépasser 0,5 mm.

### 2.2.1 Détails théoriques

Avant de débuter le calcul de l'impédance des traces du circuit imprimé, il est préférable de vérifier si ce calcul est nécessaire. Pour ce faire, on doit connaître le contenu fréquentiel du signal supporté par ces traces.

Ce contenu n'est pas seulement relié à la fréquence d'opération du signal numérique, mais aussi au temps de montée/descente des transitions. Ainsi, même si des données sont transférées à un rythme de 500 Mbits/seconde, la fréquence du signal doit être calculée indépendamment.

On sait que la puissance d'une onde carrée s'étend sur une très large bande passante. Cependant, la majeure partie de cette puissance se situe dans les premières harmoniques. Sur un tracé logarithmique, la puissance du signal suit une pente droite descendante dans cette zone.

(Johnson et Graham, 1993) proposent le calcul d'une fréquence  $F_{knee}$  à partir du temps de montée du signal. Cette fréquence correspond au point de la courbe de densité spectrale de puissance où l'amplitude du signal est 6.8 dB sous la pente droite. On peut calculer  $F_{knee}$  à partir de l'équation (2.1) où  $T_r$  est le temps de montée de du signal (10% à 90%).

$$F_{knee} = \frac{0.5}{T_r} \quad (2.1)$$

Le manufacturier du convertisseur analogique à numérique affirme que le temps de montée du signal aux sorties numériques est de 650 ps. Ce temps est mesuré entre 20% et 80% de l'amplitude totale du signal. En supposant que le type d'impulsion est gaussien, et en utilisant les relations décrites en annexe B de (Johnson et Graham, 1993), on calcule un temps de montée entre  $T_{10\%-90\%}$  de  $T_r=988$  ps. Donc, une fréquence  $F_{knee}=506$  MHz.

Selon (Pozar, 1997), « la principale différence entre la théorie des circuits électrique et la théorie des lignes de transmission est la taille électrique. L'analyse de circuits prend pour acquis que les dimensions physiques d'un réseau sont plus petites que la longueur d'onde électrique, tandis que les lignes de transmission peuvent être avoir une taille d'une fraction considérable de longueur d'onde, ou de plusieurs longueur d'onde. »

Donc, pour déterminer s'il est nécessaire de traiter les traces du circuit imprimé comme des lignes de transmission, il faut déterminer la longueur d'onde du signal et la comparer à la longueur totale des traces.

On sait que la longueur d'onde peut être exprimée en utilisant l'équation (2.2), où  $v$  est la vitesse de propagation de l'onde dans son milieu et  $f$  est sa fréquence. Dans le vide, la vitesse de propagation égale la vitesse de la lumière, soit environ  $3 \cdot 10^8$  m/s. Dans un autre milieu, elle ralentit selon les caractéristiques de perméabilité et de permittivité du matériel. Pour simplifier le calcul de la longueur d'onde, on utilise la vitesse de la lumière. Ainsi, on obtient une borne supérieure pour  $\lambda$ . Donc, pour un signal de 506 MHz, la longueur d'onde est d'environ 600mm.

$$\boxed{\lambda = \frac{v}{f}} \quad (2.2)$$

Les traces sur la carte de développement *e2v* ont une longueur de 80 mm. En posant une longueur maximale des traces sur la carte d'interconnexion de 65 mm, ainsi qu'une longueur maximale des câbles plat de 100 mm, on obtient une longueur totale de 245 mm. Soit 2/5 de la longueur d'onde du signal. Comme il s'agit d'une fraction importante de la longueur d'onde, les calculs vérifiant l'intégrité du signal utiliseront les formules de lignes de transmission.

### 2.2.2 Calcul de l'impédance des câbles

La carte de développement d'*e2v* laisse peu de place à la diversité dans le choix d'interconnexion de celle-ci. Le seul connecteur pouvant se raccorder à cette dernière est un connecteur de câble plat 50 conducteurs. Les caractéristiques électriques de ce type de câble peuvent facilement être trouvées sur les feuilles de spécification des manufacturiers. Il n'est donc pas nécessaire de faire des calculs pour le câble.

Typiquement, l'impédance d'un câble plat varie en fonction de la disposition des signaux dans le câble. Pour la carte de développement du CAN, les signaux sont alignés dans la configuration G-S-G. C'est-à-dire que chaque signal est entouré de deux mises à la terre. Cette configuration est appelée « non-balancée » (*unbalanced*) et offre une impédance moindre que dans une configuration « balancée ». Pour cette dernière configuration, le signal effectue le trajet « allée » dans un conducteur et le trajet « retour » dans le conducteur adjacent. L'impédance varie, selon le manufacturier, de  $80\Omega$  à  $150\Omega$ . Le câble utilisé a, pour sa part, une impédance de  $145\ \Omega$ .

### 2.2.3 Calcul de l'impédance des lignes microbandes

La ligne microbande est un type particulier de ligne de transmission. Il s'agit de lignes de cuivre déposées à la surface d'un matériau diélectrique. Le trajet de retour du signal passe par la surface opposée à la trace, qui est constituée d'un plan de cuivre.

Pour calculer l'impédance de lignes semblables, il faut résoudre des équations différentielles complexes. Cependant, comme les microbandes sont connues et utilisées depuis longtemps, plusieurs solutions sont disponibles pour calculer rapidement les caractéristiques d'une trace microbande. Plusieurs auteurs proposent des équations légèrement différentes les unes des autres. Par contre, les résultats obtenus sont toujours très semblables. (Pozar, 1997) fournit des équations élégantes pour calculer l'impédance  $Z_0$  d'une ligne de transmission microbande (*Voir Équations (2.3) et (2.4)*).

$$Z_0 = \begin{cases} \frac{60}{\sqrt{\epsilon_e}} \ln \left( \frac{8d}{W} + \frac{W}{4d} \right) & \text{pour } W/d \leq 1 \\ \frac{120\pi}{\sqrt{\epsilon_e} [W/d + 1.393 + 0.667 \ln(W/d + 1.444)]} & \text{pour } W/d \geq 1 \end{cases} \quad (2.3)$$

$$\epsilon_e = \frac{\epsilon_r + 1}{2} + \frac{\epsilon_r - 1}{2} \cdot \left[ \frac{1}{\sqrt{1 + 12d/W}} \right] \quad (2.4)$$

Dans ces équations,  $d$  représente l'épaisseur du diélectrique entre la trace et le plan de mise à la terre,  $W$  représente la largeur de la trace et  $\epsilon_r$ , la constante diélectrique spécifique au matériau utilisé. On calcule séparément la constante diélectrique équivalente  $\epsilon_e$  pour alléger l'équation.

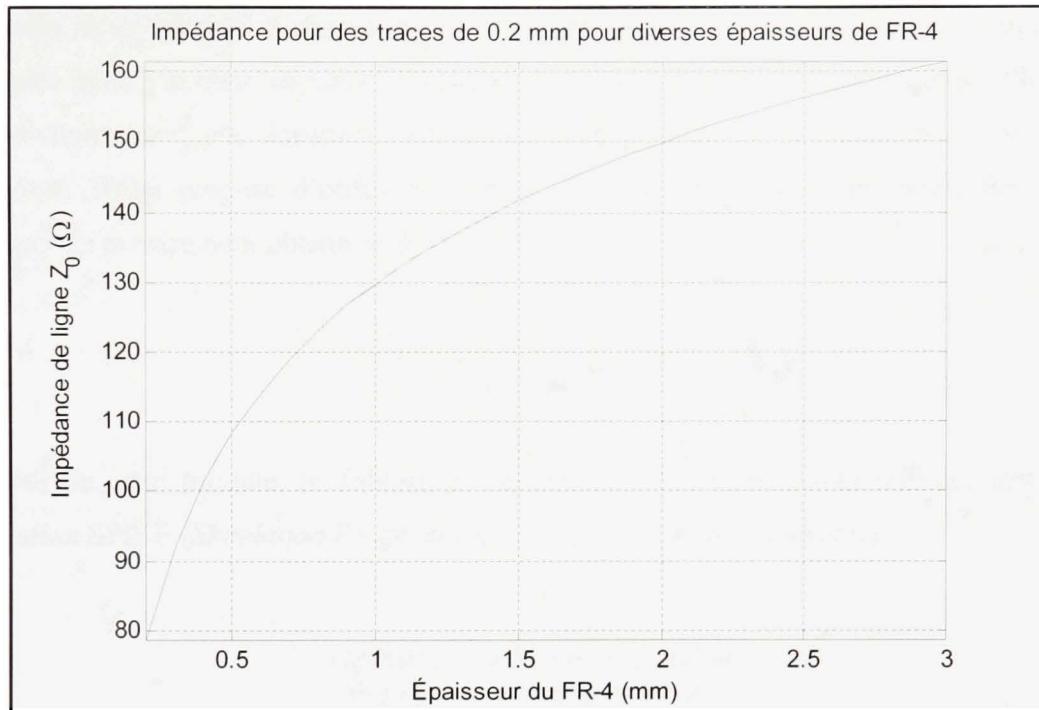

La largeur des traces utilisées dans le design doit permettre de router chaque signal au bon endroit. Dans cette optique, une largeur de trace de 0,2 mm est raisonnable. Le matériau isolant utilisé pour le circuit imprimé est le FR-4. Selon des mesures prises au laboratoire, la constante  $\epsilon_r$  du manufacturier retenu est de 3,48. La seule variable disponible pour choisir l'impédance des traces est donc l'épaisseur du diélectrique. Étant donné que les traces sont très minces, le rapport  $W/d$  sera impérativement supérieur à 1.

En utilisant *Matlab* pour tracer la courbe  $Z_0$  en fonction de l'épaisseur du diélectrique  $d$ , on peut visualiser graphiquement l'effet du diélectrique sur l'impédance (*Voir Figure 2.1*).

**Figure 2.1 Impédance de ligne pour des traces de 0.2 mm en fonction de l'épaisseur du diélectrique.**

L'atteinte d'une impédance de  $50\Omega$  est très difficile puisque l'épaisseur requise du substrat diélectrique est de l'ordre du circuit intégré. Cependant, comme les câbles plats qui relient les deux cartes ont une impédance plus élevée, il est souhaitable d'adapter l'impédance à ce câble plutôt qu'aux traces. Selon le graphique, une épaisseur de 1,5 mm permet d'atteindre une impédance semblable à celle des câbles plats, soit  $145\Omega$ .

L'impédance des traces de la carte de développement du convertisseur, selon le manufacturier, est  $50\Omega$ . Il fournit aussi les spécifications précises sur les paramètres du substrat et des traces. La constante diélectrique du matériel utilisé est de 3,4 et l'épaisseur est de  $200\mu\text{m}$ . La largeur des traces est de  $370\mu\text{m}$ . En utilisant ces valeurs et la formule de Pozar, on calcule plutôt une impédance de  $60\Omega$ . On utilise donc la valeur calculée dans les simulations.

Le calcul de ce paramètre permet de s'assurer, par simulation, que l'intégrité du signal est respectée. Pour y arriver, un autre paramètre est nécessaire; le délai de propagation. Plusieurs auteurs fournissent une équation pour le calcul de ce délai de propagation. Entre autres, (Thierauf, 2004) propose d'utiliser l'équation (2.5). On doit, bien sûr, multiplier par la longueur de la trace pour obtenir le délai absolu.

$$t_d = 84.72\sqrt{\varepsilon_r} \text{ (ps/po)} \quad (2.5)$$

À partir de cette formule, le Tableau 2.1 est dressé. Ces valeurs sont utilisées lors de la simulation SPICE (*Simulation Program with Integrated Circuit Emphasis*).

Tableau 2.1 Délai de propagation des lignes de transmission du montage, en picosecondes.

| Élément                              | Délai de propagation<br>$t_d$ (ps) |

|--------------------------------------|------------------------------------|

| Carte Atmel                          | 492                                |

| Carte d'interconnexion               | 405                                |

| Câble plat (selon les spécification) | 413                                |

#### 2.2.4 Crédit du circuit imprimé

À partir des paramètres calculés précédemment, on doit créer le circuit imprimé proprement dit. Le logiciel *Altium Designer 6* est utilisé pour faire le design complet. Le circuit sera fabriqué sur un diélectrique de type FR-4 d'une épaisseur de 1,5mm. La carte a une dimension de 150mm sur 150mm et comprend quatre interconnexions entre une sonde et un connecteur 50 conducteurs. Les interconnexions sont constituées de deux traces différentielles. Ces traces ont une longueur de 65mm avec une tolérance de  $\pm 0,25$ mm et une largeur de 0,2mm. La distance entre les conducteurs d'une paire différentielle est de

0,454mm. Les trous d'interconnexion ont un diamètre de 0,4mm. Le rapport complet de toutes les statistiques de la carte est disponible en annexe (*Voir ANNEXE II*).

L'empreinte des plots utilisée pour l'interconnexion des sondes avec le circuit imprimé est celle proposée par le manufacturier. Par contre, les trous d'interconnexion ne sont pas situés dans les pads, mais légèrement à l'extérieur de l'empreinte. Ainsi, la taille minimale des trous d'interconnexion respecte les normes minimales du fabricant du circuit imprimé.

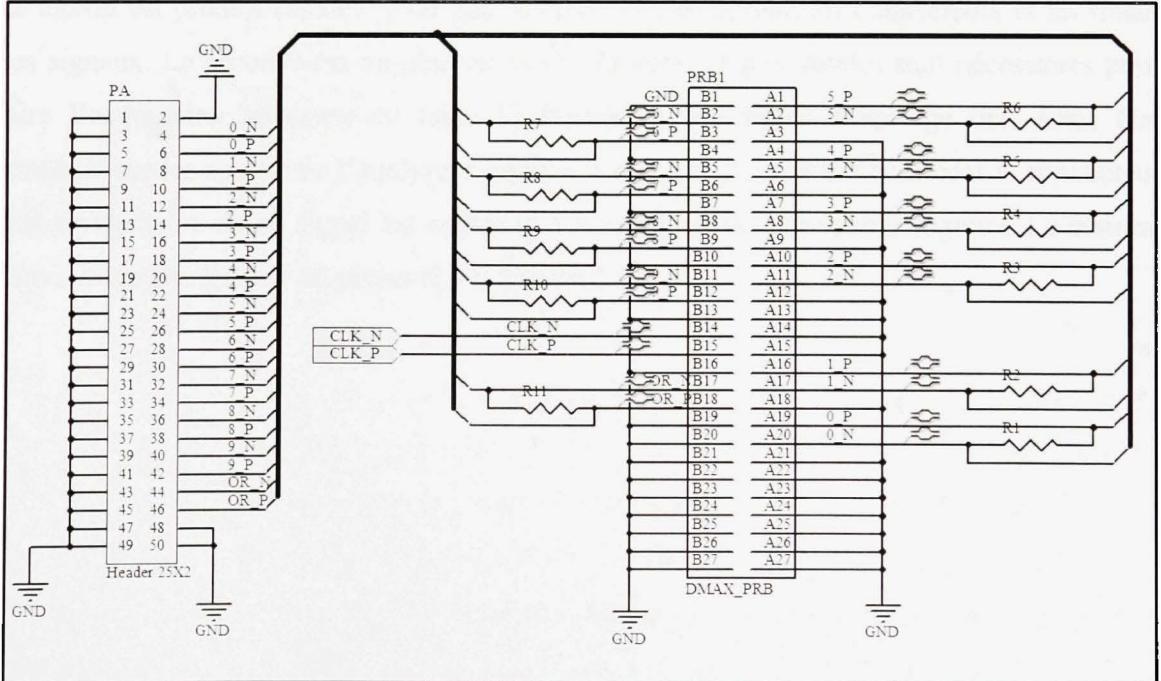

La Figure 2.2 illustre de quelle façon les sondes et les connecteurs sont interconnectés. On place des résistances entre les conducteurs positifs et négatifs des lignes différentielles par mesure préventive. C'est-à-dire que ces composantes ne seront pas ajoutées sur le circuit final, à moins qu'un problème d'intégrité de signal n'empêche le transfert adéquat de l'information entre les deux cartes.

Figure 2.2 Schéma des connexions électriques entre les sondes et les connecteurs.

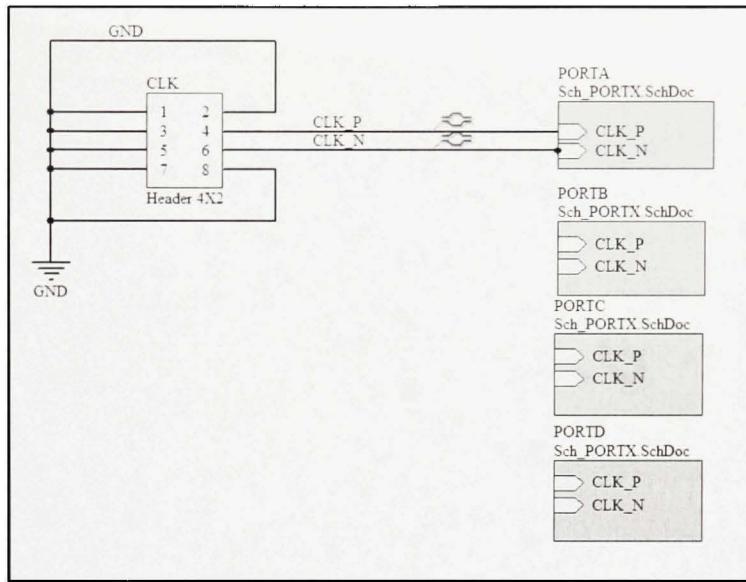

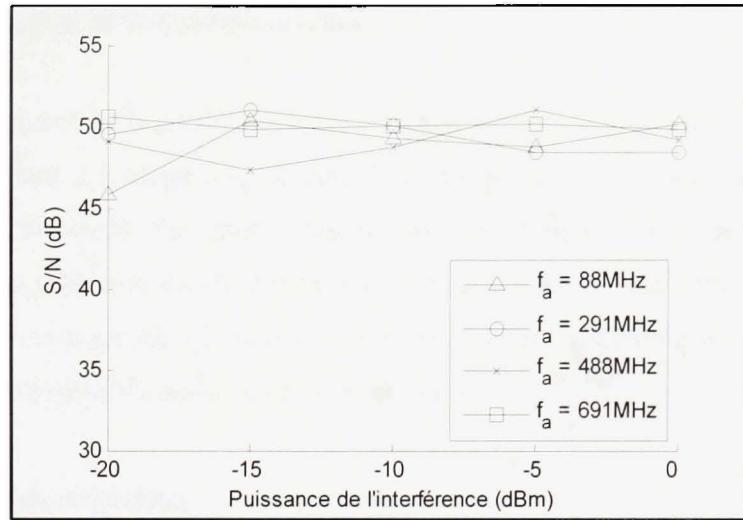

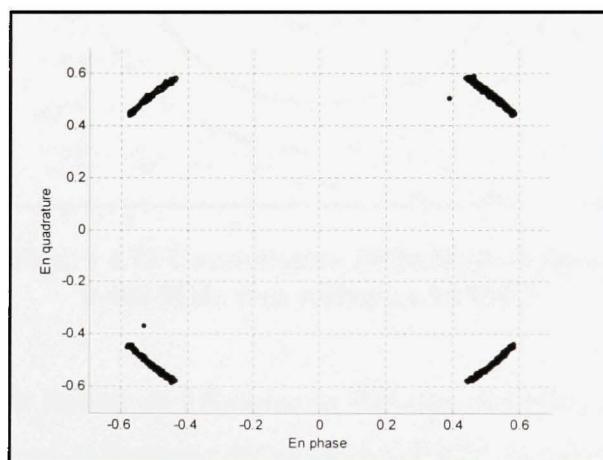

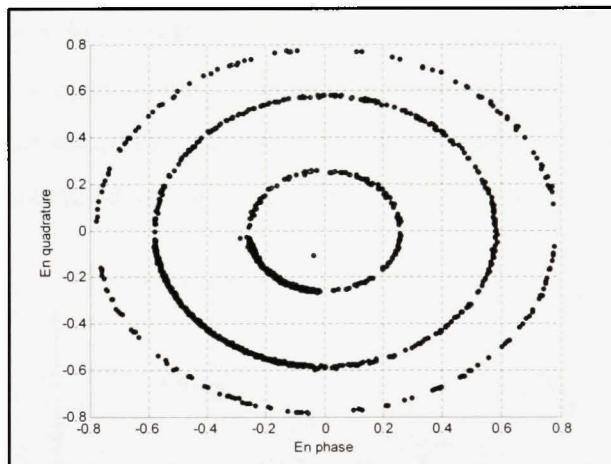

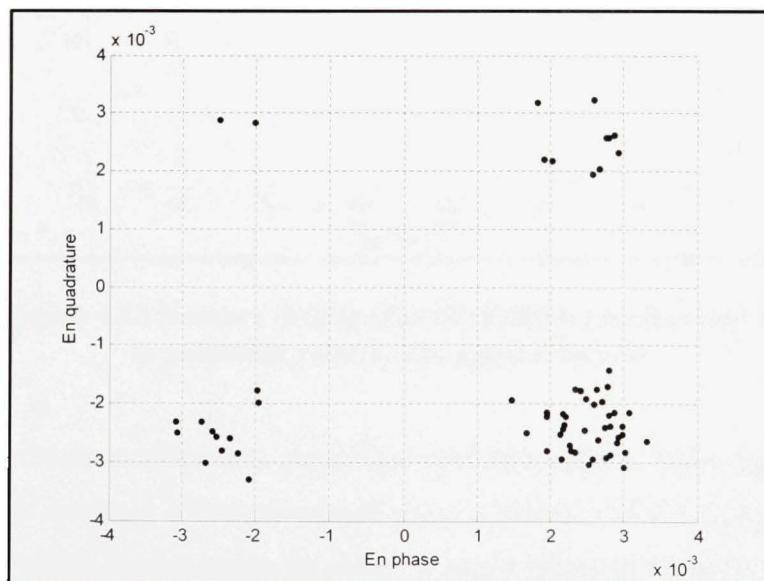

**Figure 2.3 Schéma d'interconnexion du signal d'horloge avec l'analyseur logique.**