# ÉCOLE DE TECHNOLOGIE SUPÉRIEURE UNIVERSITÉ DU QUÉBEC

## MEMORANDUM PRESENTED TO L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR A MASTER'S DEGREE IN ELECTRICAL ENGINEERING M. Eng.

## BY Éric THIBODEAU

PROFILING AND OPTIMIZING K-MEANS ALGORITHMS IN A BEOWULF CLUSTER ENVIRONMENT

MONTREAL, DECEMBER 21 2009

## PRESENTATION OF THE JURY

# THIS MEMORANDUM HAS BEEN EVALUATED

#### BY THE FOLLOWING BOARD OF EXAMINERS

M. Tony Wong, Memorandum Supervisor Département de génie de la production automatisée à l'École de technologie supérieure

M. Roberet Sabourin, Memorandum Co-supervisor Département de génie de la production automatisée à l'École de technologie supérieure

M. Guy Gauthier, President of the Board of Examiners Département de génie de la production automatisée à l'École de technologie supérieure

M. Eric Granger Département de génie de la production automatisée à l'École de technologie supérieure

THIS MEMORANDUM WAS PRESENTED AND DEFENDED BEFORE A BOARD OF

EXAMINERS AND PUBLIC

ON NOVEMBER 24 2009

AT ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

# PROFILAGE ET OPTIMISATION DE L'ALGORITHME DU K-MEANS DANS UN ENVIRONMENT DE GRAPE DE CALCUL DE TYPE BEOWULF

## Éric Thibodeau

### RÉSUMÉ

L'algorithme d'agglomération statistique K-means sert à classer des bases de données non libellées en K groupes. Faisant partie de la fonction d'évaluation d'un Algorithme Écolutionnaire (AE), l'optimisation de ce dernier est devenu un point d'intérêt. Malgré les multiples approches proposées pour son optimisation et sa parallélisation, très peu de recherche s'est attardée aux questions entourant la performance et l'efficacité parallèle des implantations. Dans la plupart des cas, les descriptions entourant l'environnement d'exécution demeurent opaques et la présentation précise de profiles d'exécution est souvent absente.

Nous pallions à ces lacunes en présentant une description détaillée de deux environnements, le grappes de calcul Beowulf et les machines parallèles de type Symmertric Multi-Processors (SMP). Une combinaison de modèles théoriques et empirique sert ensuite d'étalon dans la mesure de performance du K-means dans ces environnements. Étant la nécessité d'une expertise pluridisciplinaire, une utilisation détaillée de la suite d'outils Tuning and Analysis Utilities (TAU) est présentée pour simplifier la tâche du profilage de code parallèle. Couplée aux compteurs haute précisions fournies par l'interface Performance Application Programming Interface (PAPI), nous présentons une approche «grey box »ayant permis de muter une implémentation parallèle maître-esclave du K-means vers une version hautement efficace utilisant le paradigme d'îlots de calculs. Les optimisations sont guidées grâce à l'utilisation des modèles théoriques et empiriques que nous avons obtenus.

Notre travail révèle que l'optimisation de programmes parallèles relève de bien plus qu'un équilibre entre calcul et communications. Nous révélons les impacts négatifs de l'utilisation de bibliothèques de fonctions mathématiques ainsi que de certaines versions des bibliothèques de communications. Un profile d'exécution de haute précisions a permis d'établir que la représentation et le pré-traitement des données peuvent s'avérer être plus coûteux que le calcul et les communications combinés.

# PROFILING AND OPTIMIZING K-MEANS ALGORITHMS IN A BEOWULF CLUSTER ENVIRONMENT

Éric Thibodeau

#### **ABSTRACT**

The K-means algorithm is a well known statistical agglomeration algorithm used to sort a database of unlabeled items into K groups. As part of the fitness function of an Evolutionary Algorithm (EA), the optimization of the K-means algorithm has become a point of great interest. Although many approaches have been proposed for its parallelization and optimization, very few address the question of scalability and efficiency. In most cases, the description of the execution environment remains opaque and precise profiles of the program are mostly absent. Performance and efficiency issues are quickly relegated to communication issues.

We address these deficiencies by presenting a detailed description of two parallel environments, the Beowulf style clusters and the Symmetric Multi-Processors (SMP) parallel machines. A mixture of theoretical and empirical models were used to characterize these environments and set baseline expectations pertaining to the K-means algorithm. Due to the necessity of a multidisciplinary expertise, a detailed use of Tuning and Analysis Utilities (TAU) is provided to ease the parallel performance profiling task. Coupled with the high precision counter interface provided by Performance Application Programming Interface (PAPI), we present a *grey box* method by which a parallel master-slave implementation of the K-means is evolved into a highly efficient island version of itself. Communications and computational optimization were guided by prior theoretical and empirical models of the parallel execution environment.

Our work has revealed that there is much more to parallel processing than the simple balance between computation and communications. We have brought forth the negative impact of using mathematical libraries for specific problems and identified performance issues specific to some versions of the same series of Message Passing Inerface (MPI) libraries. High precision profiling has shown that data representation and processing can be a more significant source of scalability bottleneck than computation and communications put together.

# TABLE OF CONTENT

|       |          | ı                                                            | Page |

|-------|----------|--------------------------------------------------------------|------|

| INTRO | DUCTIO   | ON                                                           | 1    |

| СНАРТ | TER 1 I  | HARDWARE CHARACTERIZATION                                    | 4    |

| 1.1   |          | Computer Architecture                                        |      |

| 1.1   | 1.1.1    | The Control Unit and Arithmetic Logic Unit                   |      |

| 1.2   |          | g in on The Main Memory                                      |      |

| 1.2   | 1.2.1    | Accessing The Main Memory                                    |      |

|       | 1.2.2    | Cache Size and Contention                                    |      |

|       | 1.2.3    | Processor Performance                                        |      |

| 1.3   |          | inications                                                   |      |

| 1.5   | 1.3.1    | Bandwidth                                                    |      |

|       | 1.3.2    | Latency                                                      |      |

|       | 1.3.3    | The HyperTransport Interconnect                              |      |

|       | 1.3.4    | Benchmarking Network Communications                          |      |

|       | 1.3.5    | Theoretical and Empirical Model                              |      |

| 1.4   | Input/C  | output and Storage                                           |      |

|       | 1.4.1    | Local Versus Remote Storage                                  |      |

| 1.5   | Discuss  | sions                                                        |      |

| СНАРТ | TER 2    | THE PROFILING TOOLS                                          | 32   |

| 2.1   | Black,   | Grey and White Box                                           | 33   |

| 2.2   | Sequen   | tial Profiling: Use Of gprof                                 | 34   |

| 2.3   | -        | h Of Measuring Time                                          |      |

|       | 2.3.1    | PAPI: Time To Scratch Below The Surface                      | 36   |

| 2.4   | Tuning   | and Analysis Utilities (TAU)                                 | 39   |

|       | 2.4.1    | Configuring TAU                                              | 40   |

| 2.5   | Profilin | g the Source Code                                            | 41   |

|       | 2.5.1    | Automatic Code Insertions                                    | 42   |

|       | 2.5.2    | Semi-Automatic Code Insertions                               | 42   |

| 2.6   | Executi  | ng the Profiled Code                                         |      |

|       | 2.6.1    | Selecting The Profile Depth                                  | 44   |

|       | 2.6.2    | Selecting The Desired PAPI Events                            | 44   |

|       | 2.6.3    | Controlling The Data Flow                                    | 45   |

|       | 2.6.4    | Storing The Data                                             | 45   |

| 2.7   | Parapro  | of and PerfExplorer: The Profiling Graphical User Interfaces |      |

|       | 2.7.1    | The Paraprof Profile Viewer                                  |      |

|       | 2.7.2    | The PerfExplorer Performance Analyzer                        | 51   |

|       | 2.7.3    | Application Speedup                                          | 52   |

|       | 2.7.4    | Application Parallel Efficiency                                     | . 55 |

|-------|----------|---------------------------------------------------------------------|------|

|       | 2.7.5    | Runtime Breakdown                                                   |      |

|       | 2.7.6    | Views                                                               | . 57 |

| 2.8   | Discuss  | ions                                                                |      |

|       |          |                                                                     |      |

| СНАРТ |          | CASE STUDY: PARALLEL K-MEANS ALGORITHM ANALYSIS                     |      |

| 3.1   |          | quential k-means Algorithm                                          |      |

|       | 3.1.1    | Empirical Evaluation of the Algorithm                               |      |

| 3.2   |          | allel K-Means Algorithm                                             |      |

|       | 3.2.1    | First, Divide: The Segmentation Strategies                          |      |

|       |          | 3.2.1.1 Strided Segmentation                                        |      |

|       |          | 3.2.1.2 Blocked Segmentation                                        |      |

|       |          | 3.2.1.3 Hardware Considerations: Load Balancing                     |      |

|       |          | 3.2.1.4 Hardware Considerations: Physical Limitations               |      |

|       | 3.2.2    | Then Tell Everyone: Communications                                  |      |

| 3.3   | And Co   | nquer: Master-Slave Model                                           |      |

|       | 3.3.1    | Master-Slave Communications                                         | 70   |

|       | 3.3.2    | Master-Slave Empirical Modelization                                 | 73   |

| 3.4   | Or, Inva | de: Synchronous Island Model                                        |      |

|       | 3.4.1    | Optimizing the code                                                 | 82   |

|       | 3.4.2    | Island Communications                                               | 83   |

|       |          | 3.4.2.1 Overlapping Communications and Computation                  | 83   |

|       |          | 3.4.2.2 Less Talk, More Work                                        | 85   |

| 3.5   | Optimiz  | zation of Input/Output (I/O) Routines                               | 87   |

| 3.6   | Compu    | tational Optimizations: Coding for High Performance Computing (HPC) | 88   |

|       | 3.6.1    | Compiler Directives                                                 | 89   |

|       | 3.6.2    | Mathematical Libraries Versus Code                                  | . 89 |

|       | 3.6.3    | Using Single Instruction Multiple Data                              | . 90 |

|       | 3.6.4    | Loop Optimizations                                                  | . 91 |

|       | 3.6.5    | Basic Linear Algebra Subroutines (BLAS) Libraries                   | . 96 |

|       | 3.6.6    | Comparing All Approaches                                            | . 99 |

| 3.7   | Looking  | g at the Global Picture                                             | 101  |

| 3.8   |          | ions                                                                |      |

|       |          |                                                                     |      |

| CONCI | LUSION   |                                                                     | 106  |

| APPEN | DIX I    | THE GNU C Compiler (GCC)                                            | 111  |

| APPEN | DIX II   | COLLECTION OF COMMANDS                                              | 116  |

| APPEN | DIX III  | MACHINE DESCRIPTIONS                                                | 117  |

| APPEN | DIX IV   | SOURCE CODE                                                         | 125  |

| BIBLIOGRAPHY | 14 |

|--------------|----|

|--------------|----|

# LIST OF TABLES

|           | Page                                                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 | Black, Grey and White Box definitions                                                                                        |

| Table 2.2 | Black, Grey and White Box capabilities for the presented tools                                                               |

| Table 3.1 | Per bottleneck optimization recommendations. Prior profiling to identify the applicability of these approaches is primordial |

# LIST OF FIGURES

|        |     | F                                                                                                                                                                                                                                                                                                                                                           | Page |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure | 1.1 | Multi-processor memory access strategies for both Advanced Micro Devices (AMD) and Intel processors. AMD possesses Non Uniform Memory Access (NUMA) characteristics while Intel's implementation is essentially Uniform Memory Access (UMA)                                                                                                                 | 9    |

| Figure | 1.2 | These schematizations of the AMD Opteron Dual Core processors (800 series) and the Intel Core 2 Duo processors illustrates how the two core variants access Dynamic RAM (DRAM). In both cases, the Memory Management Unit (MMU) possesses dual channel connectivity to DRAM for link bandwidth aggregation.                                                 | . 10 |

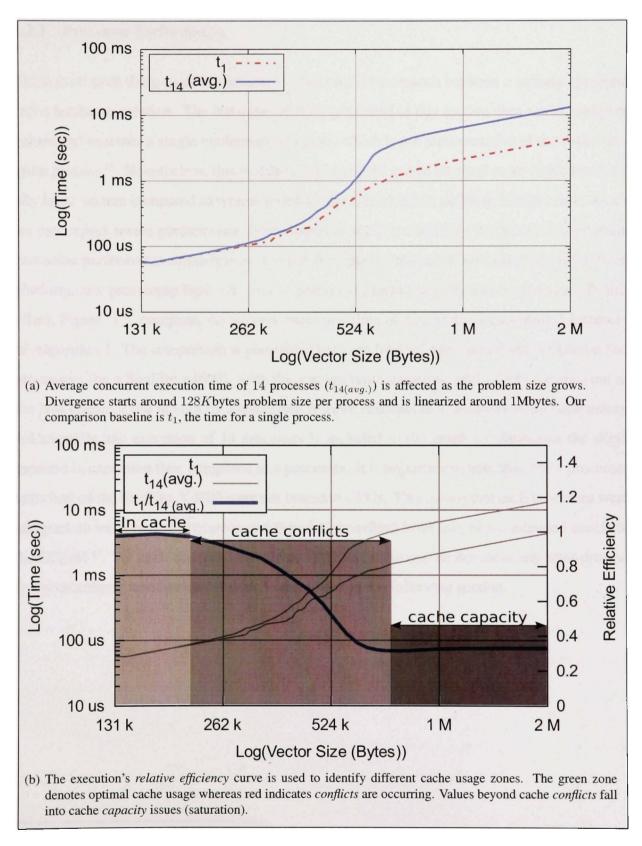

| Figure | 1.3 | Cache memory behavior on an Intel $Q6600$ (4 cores). Execution time characteristics are illustrated in (a). Cache usage zones are identified in (b).                                                                                                                                                                                                        | . 14 |

| Figure | 1.4 | Cache memory behavior on AMD Opteron $800$ series based processors using $14$ cores of a SUN SunFire $x4600$ . Execution time characteristics are illustrated in (a). Execution zones are identified in (b).                                                                                                                                                | . 15 |

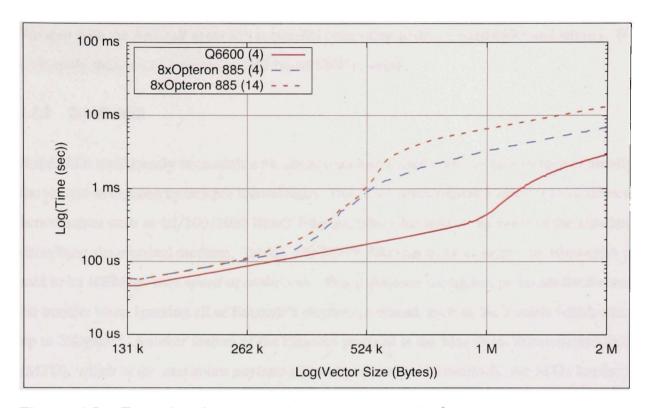

| Figure | 1.5 | Execution time comparison between Intel's $Q6600$ and AMD's Opteron 885 processors. The concurrent process count is in parenthesis. The raw computing power of the $Q6600$ outperforms the Opteron 885 for four processes. The case of 14 concurrent processes is presented to demonstrate the proportionally small impact of their simultaneous execution. | . 17 |

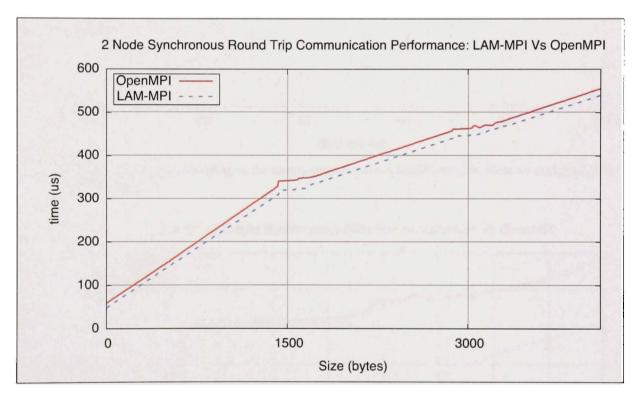

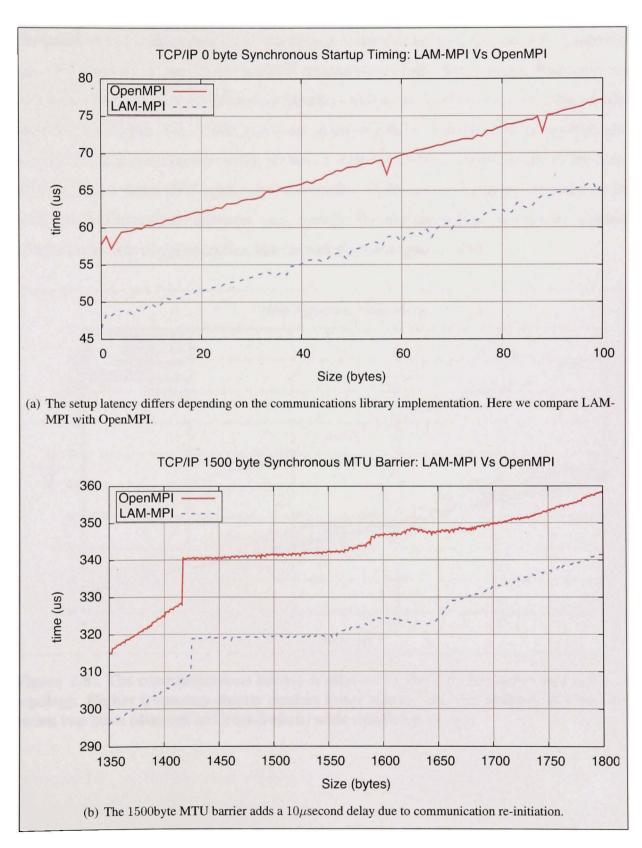

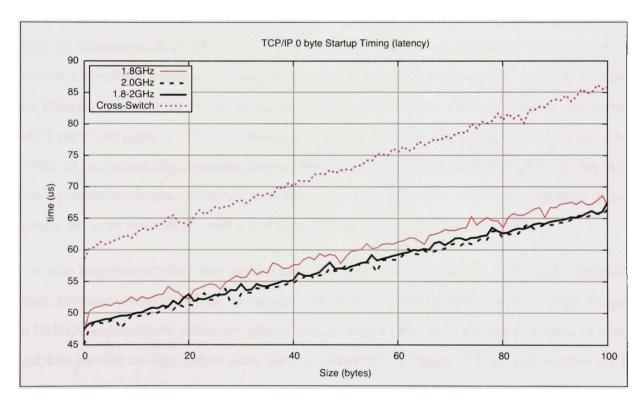

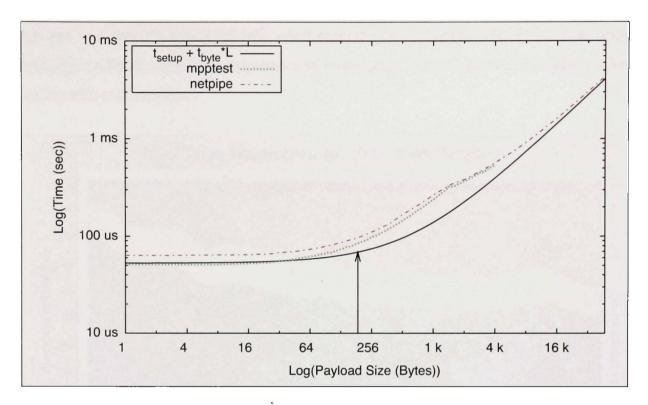

| Figure | 1.6 | LAM-MPI outperforms OpenMPI for any TCP/IP communications. The non-linearity are noted around the Maximum Transmission Unit (MTU) barriers of 1500bytes                                                                                                                                                                                                     | 20   |

| Figure | 1.7 | The round trip communication times using MPI libraries surrounding the start up times in (a) and the MTU in (b). Since these are round trip figures, all values have to be halved when considering asymmetric communication patterns.                                                                                                                       | 21   |

| Figure | 1.8 | The communications latency is affected by the Central Processing Unit (CPU) frequency and network topology. Higher frequency                                                                                                                                                                                                                                |      |

|             | clearly renders lower latency and the addition of a hop between two hosts (denoted as Cross-Switch) adds significant delays                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

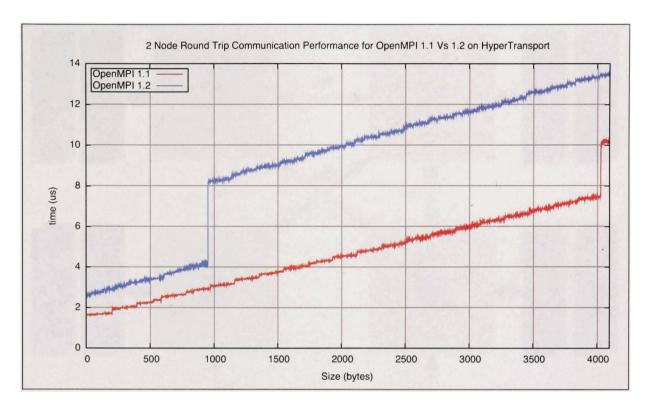

| Figure 1.9  | Comparing OpenMPI versions 1.1 and 1.2 on HyperTransport by varying the message size passed to the mpptest microbenchmark. The 1.1 implementations had performance issues characterized by a sudden jump in communication times around packet sizes of 1000bytes                                                                                                                                                                                                                                                           |

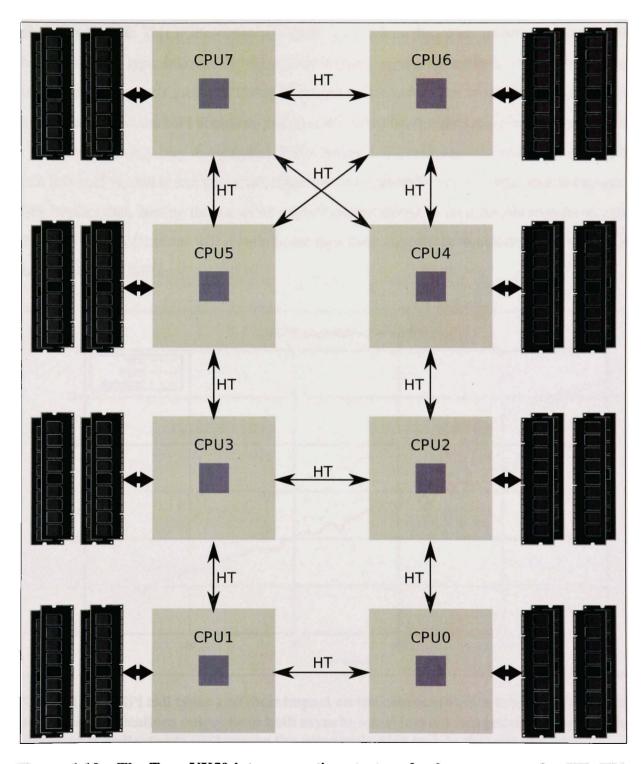

| Figure 1.10 | The Tyan VX50 interconnection strategy for 8 processors using HyperTransport (HT). This twisted ladder topology provides for an average 1.5 hop between processors and their farthest memory pages 25                                                                                                                                                                                                                                                                                                                      |

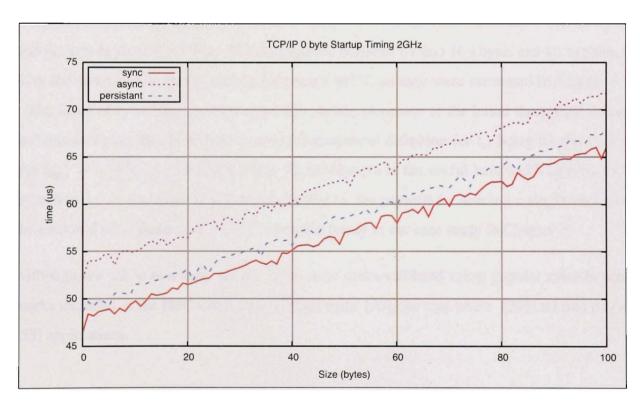

| Figure 1.11 | MPI call types and their impact on the communication times. Synchronous (sync) communications outperform both asynchronous (async) and persistant ones as the processor is dedicated to performing the communication task in that specific case                                                                                                                                                                                                                                                                            |

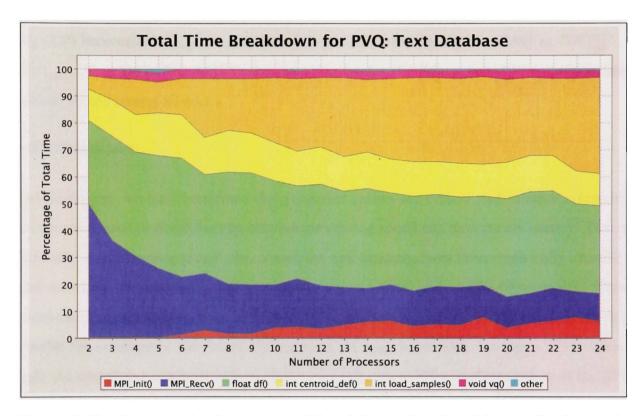

| Figure 1.12 | Comparing the general theoretical communications model with empirical values for a $100BaseT$ Ethernet network. Results from netpipe are slightly higher than mpptest, indicating there might be additional overhead to his test suite. The theoretical value bases its $t_s$ on results from mpptest, thus biasing it to be closer to that tool's results. An arrow is inserted at 188bytes as a point of reference for a vector of 47 floats, a unit which comes in handy in our case study.                             |

| Figure 1.13 | An example of proportional breakdown of each task's contribution to the execution time for the Parallel Vector Quantization (PVQ) implemented using a textual database (described in Chapter 3) and traversing its entirety at initiation. The loading of the data is performed by the load_samples() function and represents a significant portion of the total execution time.                                                                                                                                           |

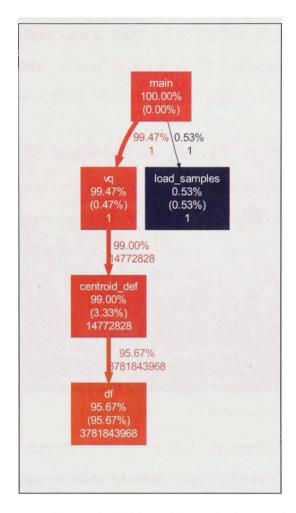

| Figure 2.1  | Output listing from <code>gprof</code> <code>-brief</code> <code>-p</code> <code>vq</code> . The columns describe the following metric for each function (each line): % time is the proportion of total execution time, cumulative seconds is the <code>inclusive</code> execution time, self seconds is the <code>exclusive</code> time, calls is the total count. Self and total s/call are for the <code>inclusive</code> and <code>exclusive</code> time per call. Finally, the last column holds the function name 35 |

| Figure 2.2  | The annotated source code as per the use of gprof -A vq. Only the two most called functions form the source code are presented                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.3  | The program call graph. This call graph draws the execution path of this simple program. Each box represents a function and the arrows indicate the call sequence. The percentages indicate the <i>inclusive</i> , or cumulative, time as one walks down the graph.  Exclusive times are indicated in parenthesis                                                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.4  | A sample use of gprof2dot to generate a dot file to be interpreted by Graphviz. The information is generated by gprof, then piped into gprof2dot.py, which itself pipes into the dot interpreter to generate the call-graph.pdf file                                                                                                                                                                                                                                                      |

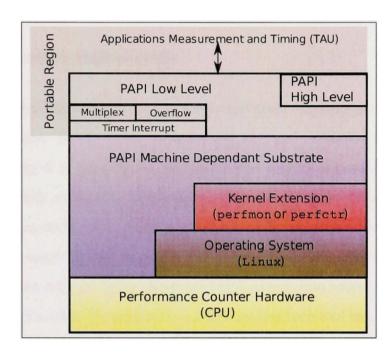

| Figure 2.5  | The PAPI implementation scheme. Adapted from [10] to include the software components, in parenthesis, relevant to each layer used in our implementation                                                                                                                                                                                                                                                                                                                                   |

| Figure 2.6  | Automated general configuration of TAU using the installtau script $40$                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 2.7  | Manual configuration of specific features (lines 4 and 5) using TAU's ./configure script                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 2.8  | Example of TAU profiling options that were compiled at installation time. Following the Makefile.tau- filename prefix are the options selected at compilation time                                                                                                                                                                                                                                                                                                                        |

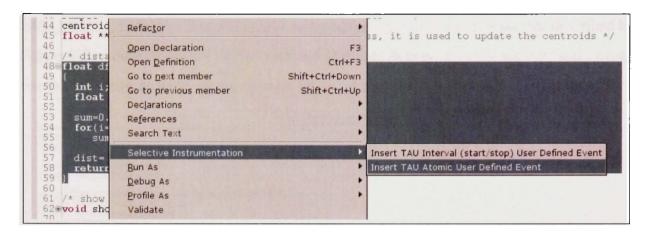

| Figure 2.9  | Selective profiling using Eclipse and TAU's selective instrumentation interface. The df() function is selected and specific type of profile pattern is applied to it. The modules then automatically generates a tau.selective file to be passed to the wrapper script.                                                                                                                                                                                                                   |

| Figure 2.10 | A sample script that sets up the environment for multiple runs of profiling 44                                                                                                                                                                                                                                                                                                                                                                                                            |

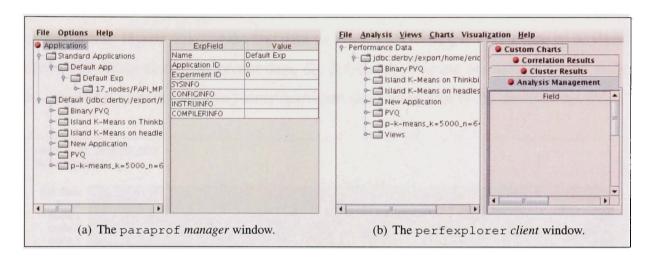

| Figure 2.11 | Both Graphical User Interfaces (GUIs) possess a main window from which the data set(s) to be analyzed is selected. The selection is performed in the left pane where trials are presented in the form of a tree structure. The latter depends on how the data was imported using Performance Data Management Framework (PerfDMF). We see in (a) that paraprof has an additional branch, which is used for the current folder's data and that (b) possesses an additional leaf named view. |

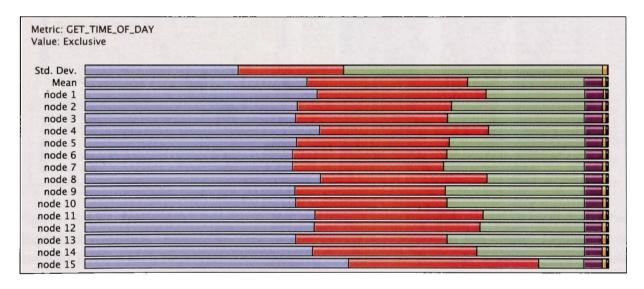

| Figure 2.12 | A normalized profile view of all processes including the global mean and the standard deviation (Std. Dev.) of each functions. In this case the metric is the time proportion as per GET. TIME, OF DAY, Each color represents a specific function                                                                                                                                                                                                                                         |

|             | and its length is proportional to the total execution time on that specific node                                                                                                                                                                                                                                                                                                                                                                                                                         | 7 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

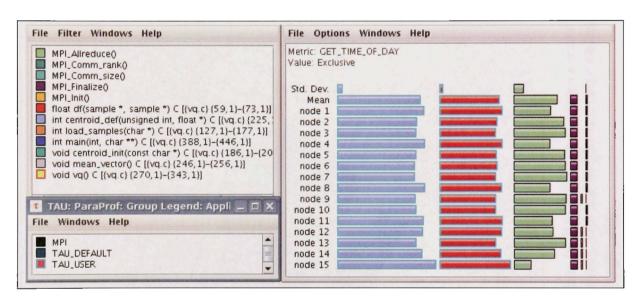

| Figure 2.13 | Individual functions and group of functions can be selected to focus the displayed statistics. Here, the TAU_USER group is selected in the <i>Group Legend</i> pane (bottom left), which highlights the relevant functions in the main window (right). Note that we have de-selected the stacked bar presentation for the main window to present an alternative to the normalized stacked bars from Figure 2.12                                                                                          | 3 |

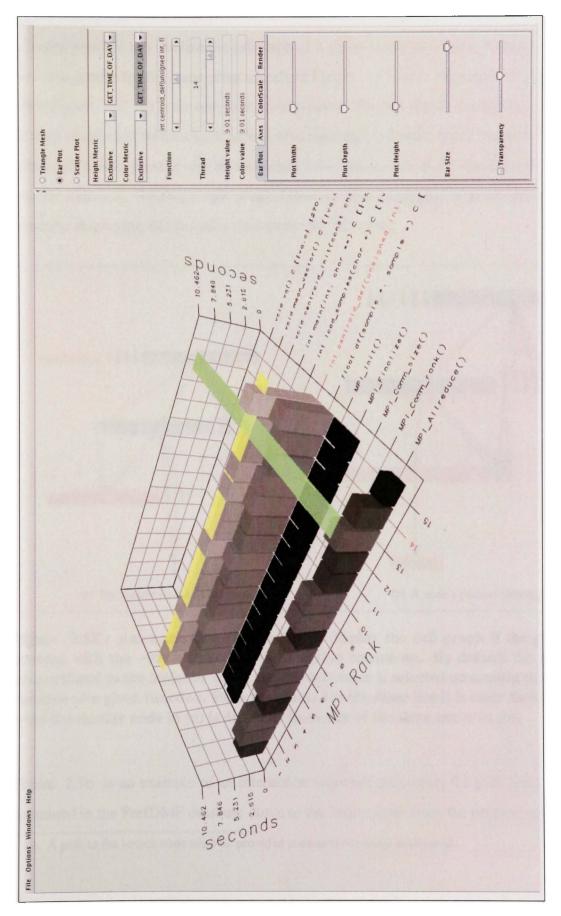

| Figure 2.14 | An alternate representation of the data in 3 Dimensional (3D). This view provides a more intuitive view of the data through a landscape representation or a series of bars (as shown). The bar height and color intensity can relate to any of the collected PAPI metric or one of the derived metrics created by the user.                                                                                                                                                                              | ) |

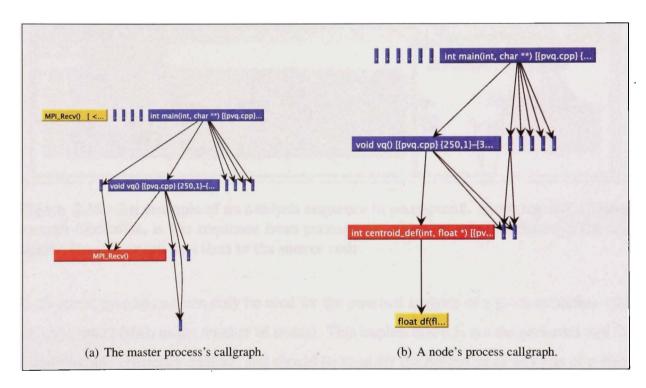

| Figure 2.15 | paraprof has the ability to display the call graph if the program was profiled with the -PROFILECALLPATH option turned on. By default the box width is proportional to the <i>inclusive</i> times and the box color is selected according to the <i>exclusive</i> runtime of a given function. Both programs are the same but it is clear that the call path from the master node in (a) is different from one of the slave nodes in (b).                                                                | 0 |

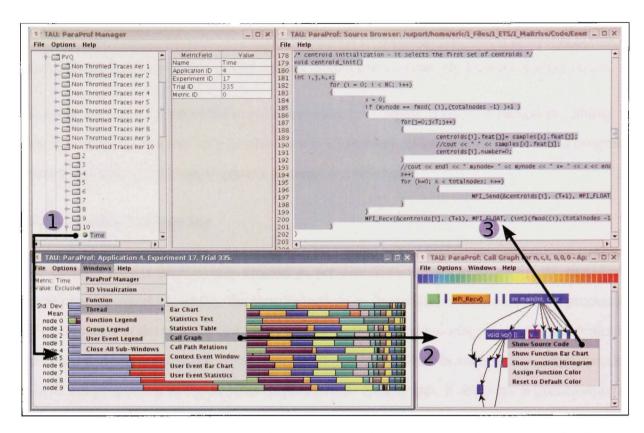

| Figure 2.16 | An example of an analysis sequence in paraprof. From top left, circling counter-clockwise, is the sequence from paraprof manager window, through the bar charts, the call graph and then to the source code.                                                                                                                                                                                                                                                                                             | 1 |

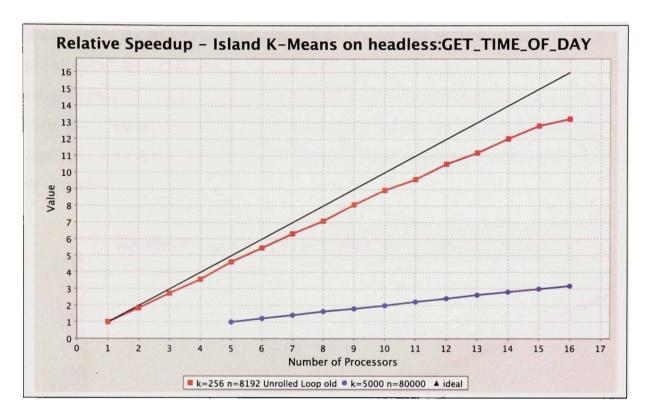

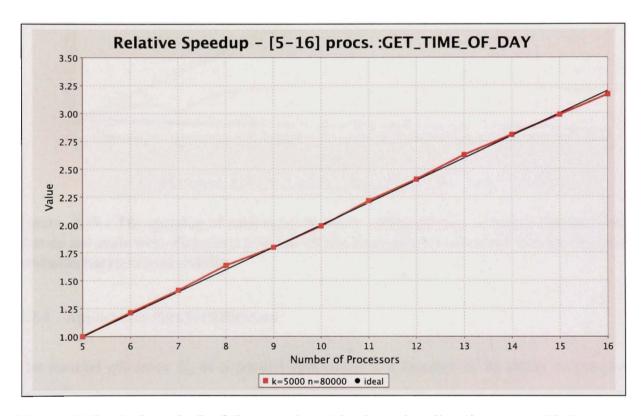

| Figure 2.17 | The top line shows the <i>ideal</i> speedup, based on the experimental data right below it, which starts with $t_{base} = t_1$ (1 processor) up to the timing for $p=16$ processors. The bottom line seems to have poor speedup as it is far from the <i>ideal</i> line (also drawn). For this curve, the baseline time $t_{base}$ is based on the execution with $p=5$ processes. This induces a distortion in the speedup representation as the two series have a different reference for $t_{base}$ . | 3 |

| Figure 2.18 | A closer look of the experiment having a baseline time $t_{base}$ with 5 processors demonstrates that it actually exerts <i>ideal</i> speedup according to perfexplorer's guideline.                                                                                                                                                                                                                                                                                                                     | 4 |

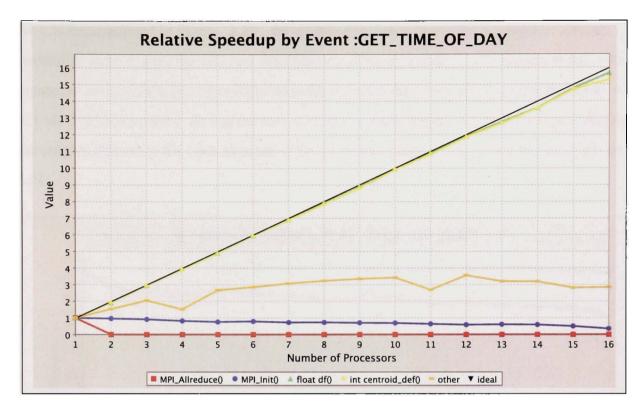

| Figure 2.19 | The speedup of each event is drawn independently to isolate the functions that do not scale well. Functions that fall off the ideal <i>speedup</i> reference line are the most probable barriers to scalability                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

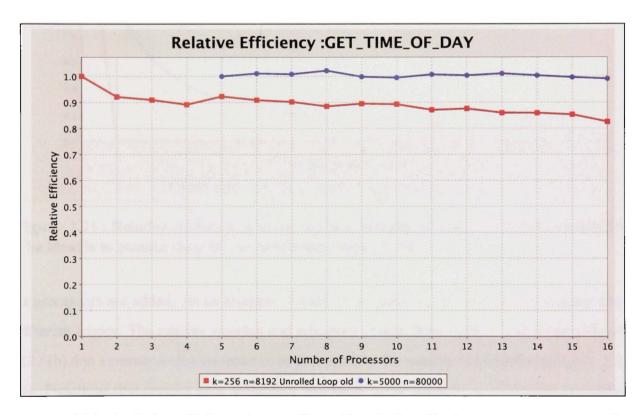

| Figure 2.20 | Relative efficiency is not affected by the baseline's processor count $p$ . The most efficient implementation (top line), averaging at 1, was originally presented as having comparatively poor speedup in Figure 2.17                                                                                                                                                                                                                                                                                                                                                                                                     |

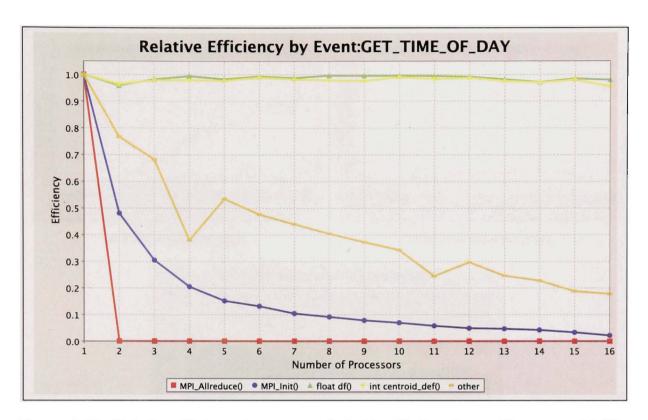

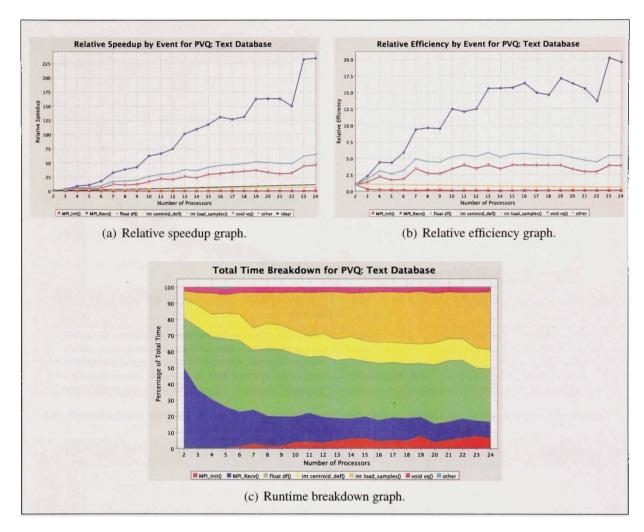

| Figure 2.21 | Relative efficiency by event can help identify functions with poor scalability. The ideal is to remain close to 1 as processor count grows 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.22 | Comparing three representation of the same profile run using relative efficiency in (b), relative speedup in (a) and a runtime breakdown graph in (c). The intuitive display from the runtime breakdown eases the identification of functions becoming problematic as processors are added. Simply put, a widening cone such as the second predominant layer from the top, is indicative of a growing bottleneck. A tightening cone, on the other hand, means that the function looses proportional importance in the overall execution time. Parallel or constant area are signs of linear (ideal) speedup of a function. |

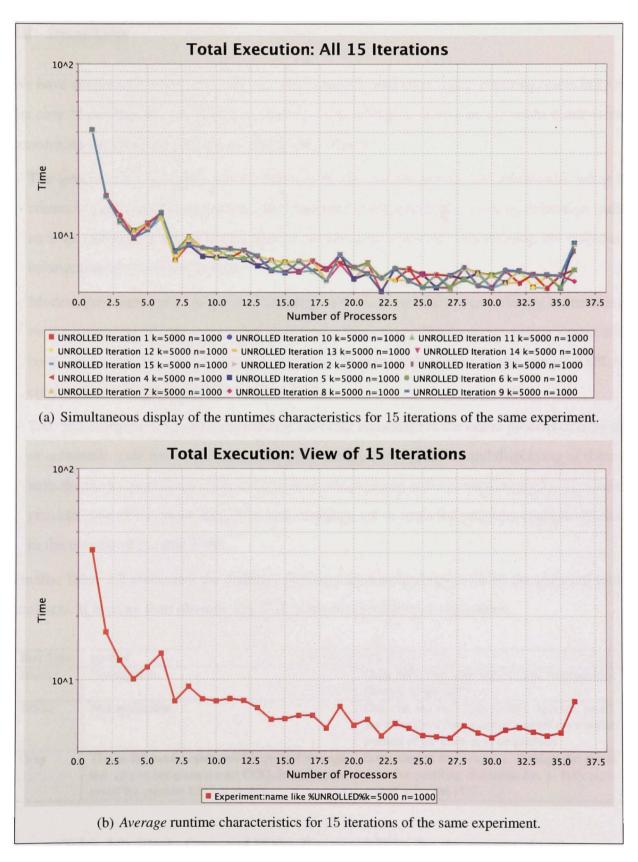

| Figure 2.23 | The use of perfexplorer views help consolidating experimental data for a better analytical perspective.  All 15 experiments are presented in (a) whereas an averaged view is presented in (b).                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3.1  | Profiling and execution of the sequential k-means algorithm using TAU. The program is then started by specifying the reference database and the number of samples to load from the database. Here we load 1% of the entire database. The [snip] tags indicate output truncation.                                                                                                                                                                                                                                                                                                                                           |

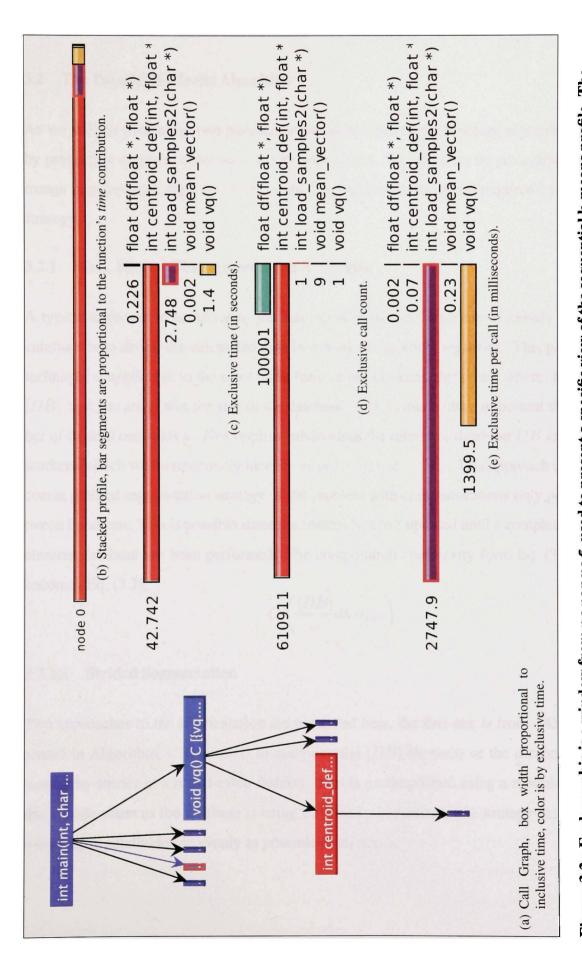

| Figure 3.2  | Each graphic is a window from paraprof, used to present a specific view of the sequential k-means profile. The call graph in (a) clearly shows that the execution time is mostly attributable to centroid_def(). The stacked bargraph in (b), and its deconstructed version in (c), also indicates this proportional importance. The call counts from (d) help identify potential partitioning areas as well as its grain. (e) is useful for identifying highly cohesive functions (many short calls), thus potential communication bottlenecks                                                                            |

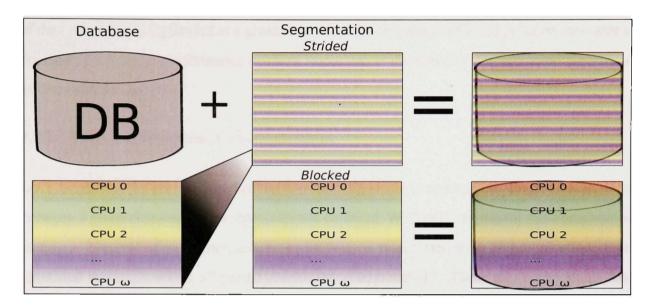

| Figure | 3.3  | Database segmentation strategies: TOP-Strided segmentation (fine grained) is used by the master-slave algorithm where each element of the database is assigned to one $\omega$ worker node in a round-robin fashion. BOTTOM- Block segmentation approach (coarse grained), assigns equal consecutive chunks of the database to each worker as per $ DB /\omega$ with the remainder assigned to the last worker 68 |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

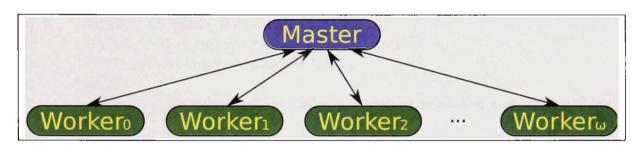

| Figure | 3.4  | A typical master-slave topology. All communications originate and terminate on the master. The nodes do not communicate between each other                                                                                                                                                                                                                                                                        |

| Figure | 3.5  | The workers send their partial results to the master                                                                                                                                                                                                                                                                                                                                                              |

| Figure | 3.6  | The master updates the workers with the new values                                                                                                                                                                                                                                                                                                                                                                |

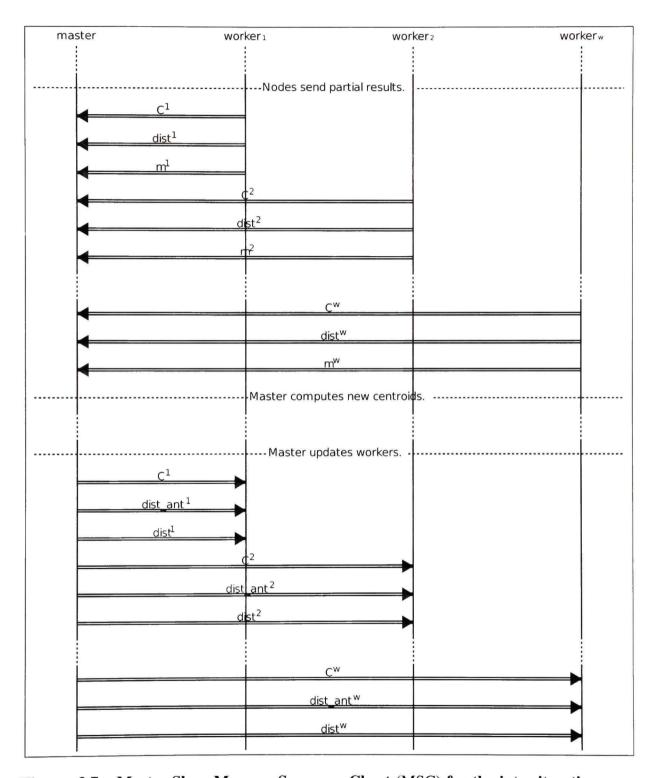

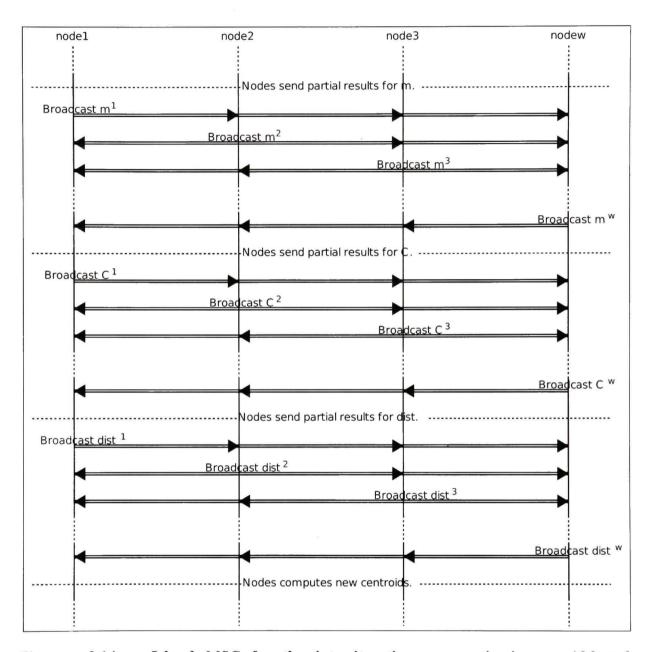

| Figure | 3.7  | Master-Slave Message Sequence Chart (MSC) for the interiteration communications. All communications are point to point and must be performed by all nodes                                                                                                                                                                                                                                                         |

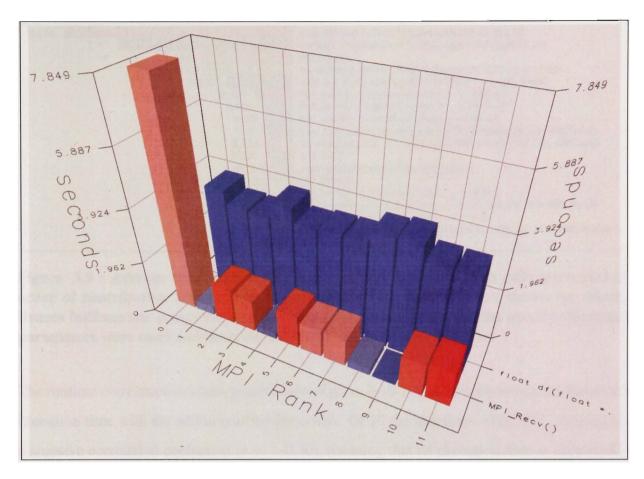

| Figure | 3.8  | The 3D view of the master-slave communications MPI_Recv() and computation cycles df() for all nodes. The master node (node 0) spends most of its time waiting for the results from the $\omega$ orker nodes. Columns are colored according to time per call for the function 76                                                                                                                                   |

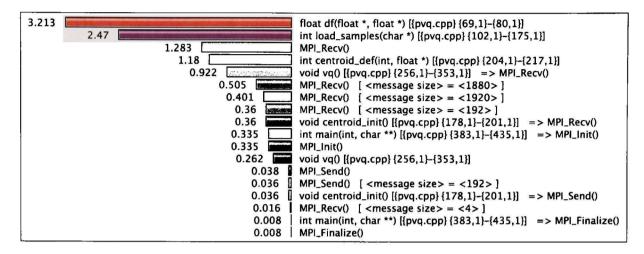

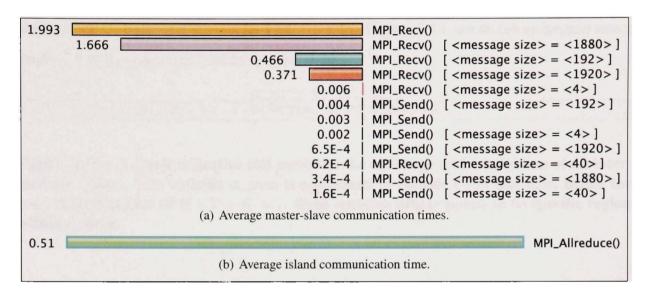

| Figure | 3.9  | Average time spent by all nodes in each function. Each calls are sorted by order of contribution importance. Calls under 0.008 seconds aren't shown for clarity. Braces indicate the source file and line numbers, bracket information specify which call parameters were used and function call paths are indicated using '=>'                                                                                   |

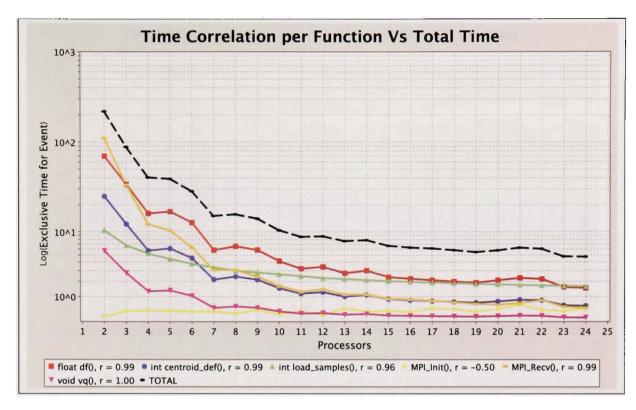

| Figure | 3.10 | Correlation analysis for $\omega=[2,24]$ . Each function's time contribution is drawn as the worker count grows. The correlation coefficient $r$ , indicates the correlation between the addition of nodes and the execution time of the function                                                                                                                                                                 |

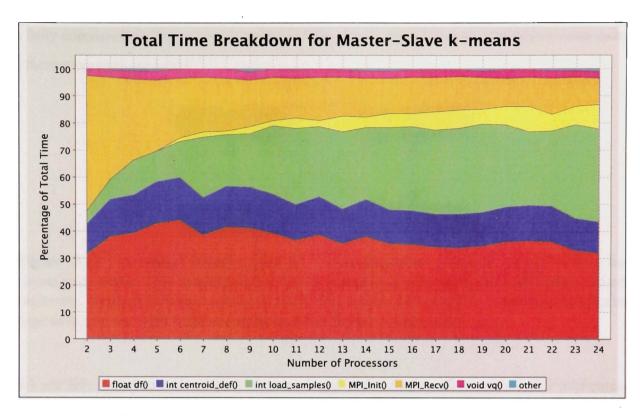

| Figure | 3.11 | Runtime breakdown for $\omega=[2,24]$ . Each function's proportional importance for the total execution time is depicted by its surface coverage as nodes are added to the computation. A perfectly scalable function would be represented by a constant surface area whereas a growing surface is indicative of poor scaling                                                                                     |

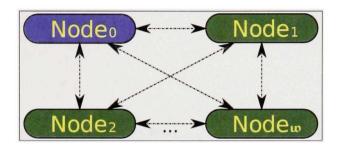

| Figure | 3.12 | A typical island topology. Communications originate and terminate between each node. This model implies a fully connected network where all nodes can see eachother (typical                                                                                                                                                                                                                                      |

|             | varies depending on the MPI implementation of the global communicators. 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.13 | The three collective calls used to communicate and perform an element by element summation of all three intermediate variables                                                                                                                                                                                                                                                                                                                                                                                                                                   |

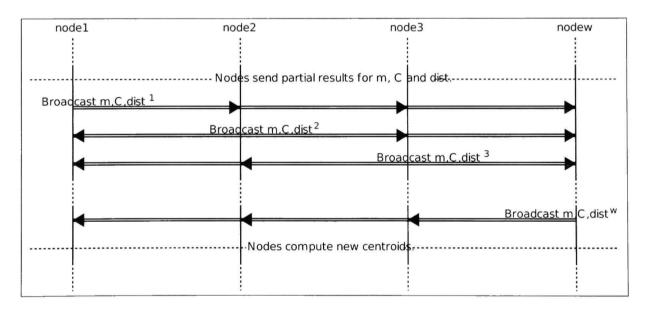

| Figure 3.14 | Island MSC for the inter-iteration communications. Although drawn as sequential, collective communications can overlap within the same call to MPI_Allreduce but must complete within the same call (equivalent to a communication barrier). These barriers are depicted by the horizontal dotted lines. They must also be performed by all nodes                                                                                                                                                                                                                |

| Figure 3.15 | Average communication times for both approaches. Master-slave communications are presented in (a) while the only communication for the island model is in (b)                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3.16 | A single collective call performs the exchange and summation of all intermediate values. The variable c_sum is supersized to include $C$ , $m$ and $dist$ , hence the communication size of $K*T+K+1$ . Each variable simply points to its specific region within c_sum 86                                                                                                                                                                                                                                                                                       |

| Figure 3.17 | Simplified Island MSC for the inter-iteration communications.  A single collective call from each node communicates all intermediate values and performs their sum at the same time                                                                                                                                                                                                                                                                                                                                                                              |

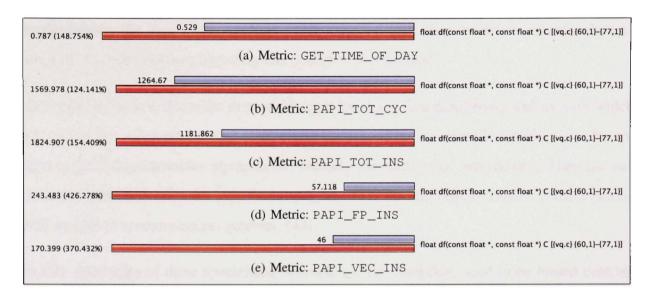

| Figure 3.18 | Comparing hand coded squared function $(a \times a)$ to the use of pow() on Intel $Q6600$ . The metric used in all cases is the exclusive mean per-call values of the fucntion. In all figures ((a) to (e)), the top bar (in blue) uses the explicit definition while the red bar below uses the library call to pow (a, 2). All the presented metrics point to the expanded version as being more efficient by consuming less total time (a), cycles (b), issuing less instructions (c) (total) and even less floating point (d) and vector instructions (e) 90 |

| Figure 3.19 | On the left, the original loop. On the right, the fourfold unrolled version of this same loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3.20 | Pre-assembly output from GCC for an Athlon $XP$ processor for df(). On the left, the code is compiled with explicit use of Single Instruction Multiple Data (SIMD) directives such as -mfpmath= sse -msse -m3dnow. On the right, the addition of -ffast-math has triggered unrolling of loop as well as additional use of the SIMD capabilities, generating more efficiently <i>vectorized</i> code                                                                                                                                                              |

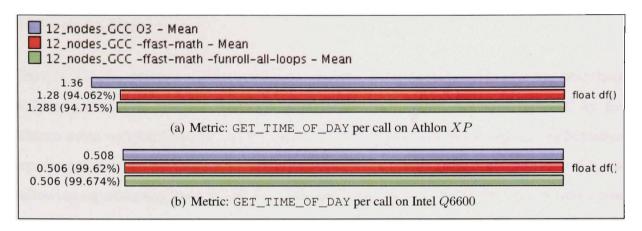

| 95  | Execution time comparison between using $-03$ (top bars in blue), adding $-ffast-math$ (middle bars in red), and also addinf $-funroll-all-loops$ (bottom bars in green). The (a) is for the execution time on Athlon $XP$ processors where we can see that $df()$ does not seem to benefit from $-funroll-all-loops$ but does perform better with about $6\%$ in time gain with only $-ffast-math$ . (b) is on Intel $Q6600$ where very little differences are noted between the three approaches. | Figure 3.21 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 96  | The df() function using BLAS. On the left, the original loop. On the right, the BLAS version of this same loop. The operations on the right are aligned with the ones they (mostly) replace on the left.                                                                                                                                                                                                                                                                                            | Figure 3.22 |

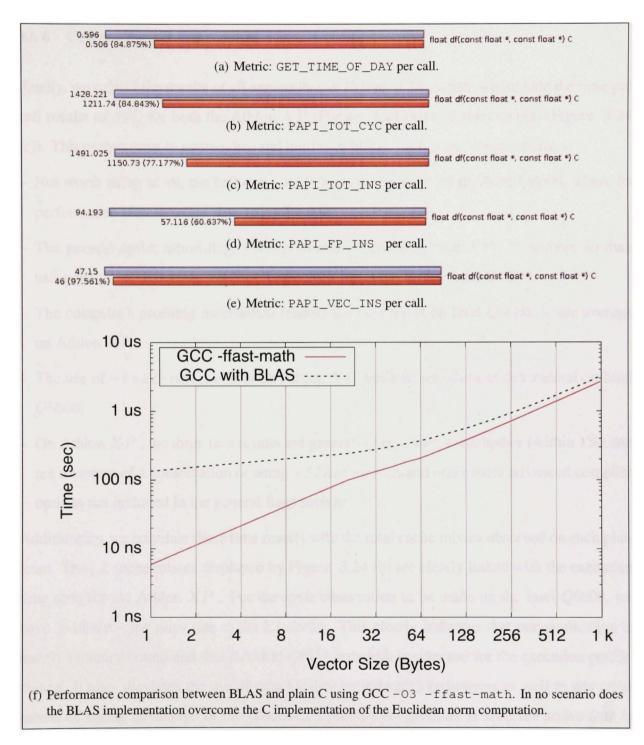

| 98  | The Level 1 BLAS libraraies (top blue bars and line) perform poorly in all cases compared to the code optimized with -ffast-math. This is reflected in all aspects of the computation whether it being time (a), CPU cycles (b), instructions (c) or even floating point operations ((d) and (e)). Further investigation by varying the vector size has proven this to always be the case as demonstrated in (f)                                                                                    | Figure 3.23 |

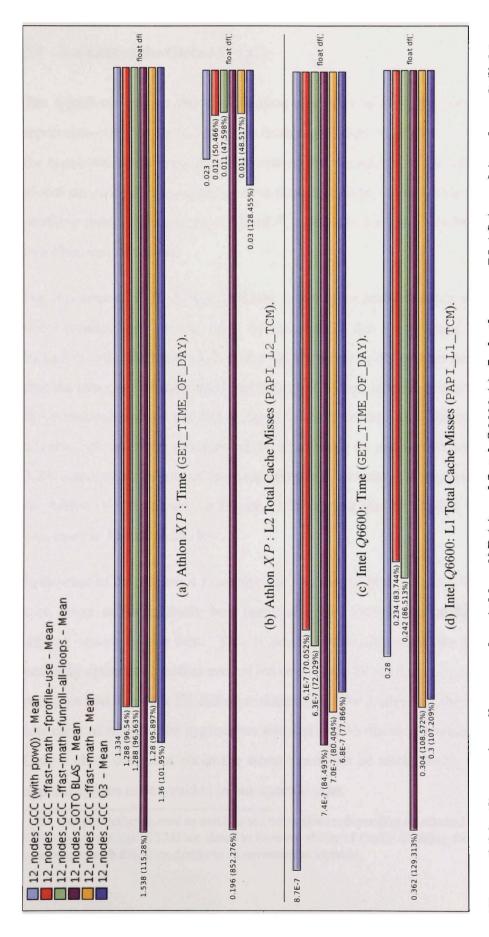

| 100 | Comparing all approaches Athlon $XP$ (a) and Intel $Q6600$ (c). In both cases, BLAS (purple) and pow() (light blue) are the worst performing. A direct correlation is made between performance and Level 2 (L2) cache misses (b) for the Athlon $XP$ . In the case of the Intel $Q6600$ , the same clear cut correlation, requires that we go down to the Level 1 (L1) cache (d).                                                                                                                   | Figure 3.24 |

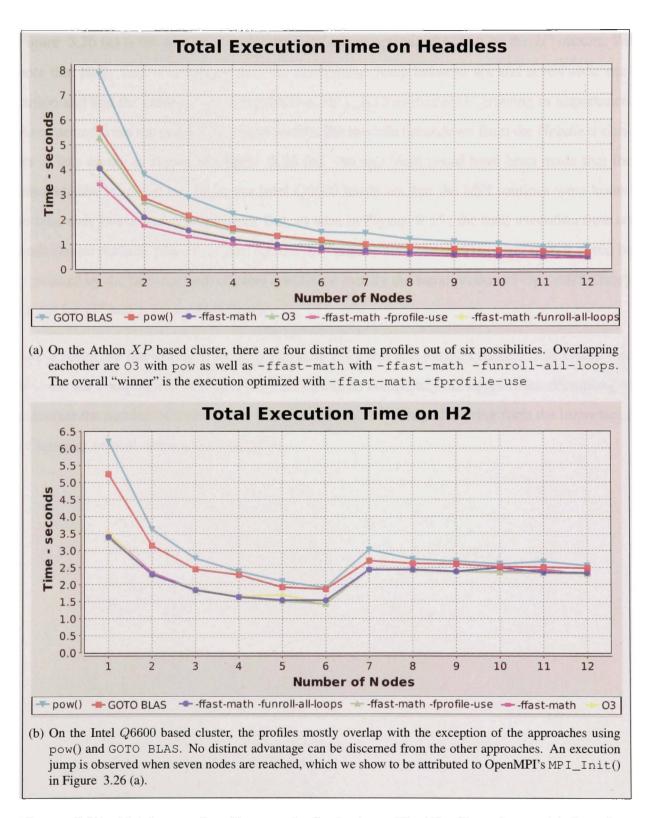

| 102 | Total execution times on both clusters. The Headless cluster (a), based on Athlon $XP$ hardware, lends a distinct advantage to the use of -ffast-math. On the $H^2$ cluster (b), based on Intel $Q6600$ hardware, most options overlap leading to no clear "winner", barring the use of GOTO BLAS and pow                                                                                                                                                                                           | Figure 3.25 |

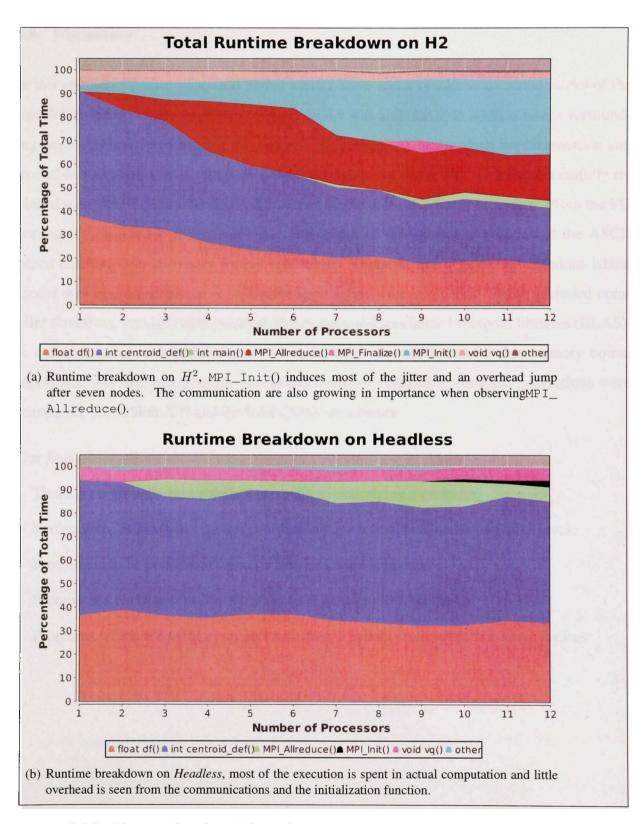

| 104 | The runrime breakdown for the best optimized options on both clusters. In (a) most of the execution time on the $H^2$ cluster is spent in MPI libraries. We see this is not the case in (b) for the headless cluster where most of the time is spent in computation                                                                                                                                                                                                                                 | Figure 3.26 |

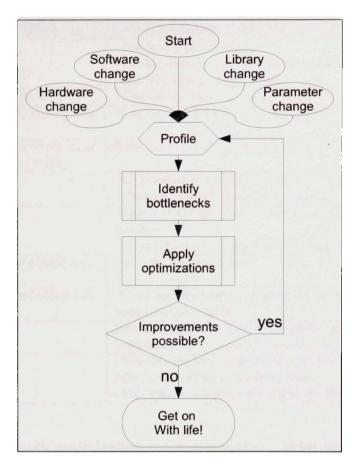

|     | A deceptively simple diagram depicting the iterative optimization process of a program. The multiple entry points recall that a change in any one of the elements from Figure 1 are susceptible to provoking a new optimization pass. The ultimate                                                                                                                                                                                                                                                  | Figure 3.27 |

| convergence   | being that   | there is no | more p  | ossible  | improvement     | S   |

|---------------|--------------|-------------|---------|----------|-----------------|-----|

| given a stabi | lized enviro | onment, and | one can | then ger | t on with life. | 108 |

## LIST OF SYMBOLS

$BW_{I/O}^{node}$  Node Input/Output Bandwidth

$BW_{I/O}^{server}$  Server I/O Bandwidth

$BW_{useful}$  Useful Band Width

c Number of cores in a given processor

C Table of k centroids

$c_x$  One of the k centroids from C

DB Data Base of vector elements

|DB| Data Base cardinality

$DB_{\omega j}$  Element j from  $\omega$ 's Local Data Base

d Vector dimension

dist Distance

$E_{comp}$  Execution's comparative efficiency

$E_p$  Parallell Efficiency

$E_p^{rel}$  Relative Parallell Execution Efficiency

$HDD_{I/O}^{node}$  Hard Disk Drive Input/Output Bandwidth

$HDR_{Ethernet}$  Ethernet Header Size

$HDR_{TCP/IP}$  TCP/IP Header Size

k Number of centroids used for the k-means algorythm

L Message Lenght (Payload)

$L_{max}$  Maximum length

$L_{short}$  Shortest Pacquet Size

x<sup>t</sup> A vector element from DB, the Data Base

$m_k$  Element counter for centroid k

$m_{\omega}^{k}$  Element counter for centroid k on node  $\omega$

MTU<sub>size</sub> Maximum Transmission Unit size

n Number of hosts

$N_{iter}$  Number of iterations

$\omega$  Number of worker nodes

p Number of processes

$p_{base}$  Number of processes for base line excution

$S_p$  Speedup using p processes

$t_1$  Time for single execution thread

$t_{avg}$  Average time

$t_{base}$  Base Line Execution Time

$t_{bute}$  Time to send a single byte

$t_{comm}$  Total Communication Time

$t_{comp||}$  Computation part of  $t_{||}$

$t_{con.avg}$  Average time of running concurrent threads

$t_{exec}$  Execution Time

$t_{f||\cdot||}$  Time to compute a single Euclidean norm

$t_{lat}$  Latency Time

$t_{load}$  Loading Time

$t_{navg}$  Average time for end execution threads

$t_{\parallel}$  Parallel Execution Time

$t_{seq}$  Sequential Execution Time

$t_{single}$  Time for a single thread

$t_s$  Setup Time

$t_{start}$  Start time

$t_{stop}$  Stop time

#### **ACRONYMS**

3D 3 Dimensional

ALU Arithmetic Logic Unit

AMD Advanced Micro Devices

API Application Programming Interface

bps bits per second

Bps bytes per second

BLAS Basic Linear Algebra Subroutines

CFD Compitational Fluid Dynamics

CMP Chip MultiProcessors

CPU Central Processing Unit

CPI Clock Per Instruction

CUDA Compute Unified Device Architecture

DMA Direct Memory Access

DRAM Dynamic RAM

EA Evolutionary Algorithm

CFD Computational Fluid Dynamics

FLOPS FLoating point OPertaions per Second

GA Genetic Algorithm

GCC GNU C Compiler

GigE Gigabit Ethernet

GPU Graphics Processing Unit

GPGPU General Purpose Graphics Processing Unit

GUI Graphical User Interface

GNU GNU is Not Unix

HPC High Performance Computing

HPCC HPC Challenge

HDD Hard Disk Drive

HMM Hidden Markov Model

HT HyperTransport

IEEE Institute of Electrical and Electronics Engineers

ILP Instruction-Level Parallelism

I/O Input/Output

Inf Infinity

IP Internet Protocol

ISO International Standards Organization

L1 Level 1

L2 Level 2

L3 Level 3

LLVM Low Level Virtual Machine

MIMD Multiple Instruction Multiple Data

MMU Memory Management Unit

MPI Message Passing Inerface

MSC Message Sequence Chart

MTU Maximum Transmission Unit

NaN Not a Number

NIC Network Interfafce Card

NFS Networked File System

UMA Uniform Memory Access

NUMA Non Uniform Memory Access

NFS Network File System

OpenCL Open Computing Language

OS Operating System

PAPI Performance Application Programming Interface

PerfDMF Performance Data Management Framework

PDT Program Database Toolkit

PtP Point to Point

PXE Pre eXecution Environment

PDT Program Database Toolkit

PVQ Parallel Vector Quantization

OPI Quick Path Interconnect

RAM Random Access Memory

RAID Redundant Array of Inexpensive Disks

SATA Serial Advanced Technology Attachment

SIMD Single Instruction Multiple Data

SPMD Single Program Multiple Data

SMP Symmetric Multi-Processors

SRI System Request Interface

SSE Streaming SIMD Extension

TAU Tuning and Analysis Utilities

TCP Transmission Control Protocol

ZCAV Zoned Constant Angular Velocity

#### INTRODUCTION

It is a well known fact that parallel processing is a multidisciplinary field of research where the computing infrastructure encompasses most of the electrical, software and telecommunication fields of engineering. And this is only for its implementation, to which we must add the disciplines proper to the environment being used, themselves covering a wide range of interests from Computational Fluid Dynamics (CFD) modeling (think weather forecasting) to biochemical engineering passing through genetics research. The intertwining complexity is amplified when one considers the Beowulf approach of High Performance Computing (HPC) where a wide range of configurations and heterogeneity of the hardware tends to transform traditional computational models into a complex mish mash of exceptions. If we also consider the widely varying computation characteristics of the code to be executed in such environments, ranging from embarrassingly parallel to highly cohesive (computation versus communications bound), the answer to Which clustering solution is the best? can simply not exist without intricate knowledge of the program and the underlying environment upon which the execution is to be performed.

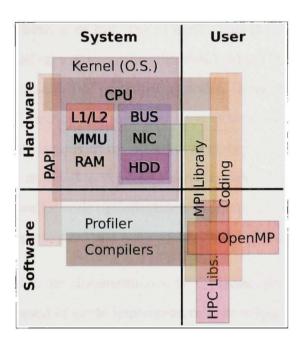

To illustrate these intricacies, Figure 1 presents an overlapping view of the typical hardware and software components involved in the HPC parallel processing context. In this figure, we have also separated the domains of interaction whether it be hardware versus software or user versus system. The quadrants generated by this subdivision can each be interpreted as a field of specialization which can be further subdivided by the components from which they are composed.

Taking all these facts into account, one cannot claim the existence of a universal solution, hardware or software, which can be applied to all cases. Profiling of any computational task and/or of the underlying hardware is therefore a requirement for the attainment of performance maximization given a specific environment.

Even with such precise knowledge of the software, estimating its performance on different hardware can prove to be a daunting task which will tend to lead to false conclusions implying that the exercise of profiling is a task to be re-iterated each time new hardware is encountered.

Figure 1: An illustration view of the multiple elements and disciplines involved in parallel processing. Each quadrant represents a field of research with each underlying component being a specialization. The crossing of quadrants signify its multidisciplinarity and the overlapping emphasizes integration complexity.

#### **Problem Statement**

Research in the area of machine learning algorithms (including Evolutionary Algorithms (EAs)) is known to be computationally intensive and has been a growing user of parallel processing approaches to enhance its capabilities.

As an accepted fact, most of the processing payload resides in the fitness evaluation functions where a proposed solution is weighed. In the realm of EAs, the acceleration of this computation step can either lead to a faster or a better solution for a given problem. Fitness evaluators are problem-specific and cannot be generalized, which is why we concentrate on such a given

fitness evaluator, the K-Means statistical classifier, as was implemented in [44], Section 3, Foreground-Background Feature Extraction (FBFE) Module.

Given the nature of the K-Means algorithm, the most classic means of determining execution performance, the total run time, is of little use in itself. This is due to the fact that this iterative process terminates based on a convergence threshold, which is in turn affected by random initialization values and the number of participating nodes. In the case of a parallel implementation, it requires that other metrics than total execution time be used to gauge its performance such as scalability and efficiency. With the added complexity of a parallel execution environment, specialized tools are required to provide a concise view of the program's behavior and evolution. As algorithmic and/or code optimization techniques are applied, one must ascertain that the latter lead to an improvement and not a scalability bottleneck.

All these constraints, added to the aforementioned HPC parallel processing paradigms, require that a unified approach be used to guide implementers as to where efforts should be deployed to enhance performance. It is common that, in university research, the implementers (graduate students) have a short time to learn all aspects of their project, programming environment and the code base they will most probably be using and modifying. These three aspects tend to mutate, implying that the performance analysis infrastructure used has to be adaptive, flexible, and most importantly, relatively simple of use.

To demonstrate how this can be accomplished, we start by describing technically and empirically the hardware characteristics in Chapter 1. We then present the techniques and tools by which we probe the software being executed on this hardware in Chapter 2. A case study is then presented in Chapter 3, where we fuse the tools from Chapter 2 and the architectural knowledge from Chapter 1 which brings us to recommendations and future outlooks in the conclusion.

#### CHAPTER 1

#### HARDWARE CHARACTERIZATION

Although it may seem trivial or paradoxical to possess knowledge about a program to be executed in a given HPC environment <sup>1</sup>, it is a key component to guide the proper profiling of any hardware platform. Ignoring the application domain can result in misguided concerns about a component that ends up being trivial for the targeted application. For example, concentrating on network fabric performance when, in fact, an application is memory or computationally bound, rather than communications bound, can turn out to be a waste of effort and resources. This fact is actually alleviated by the classic Beowulf rhetorical question:

What hardware should I use to build a cluster?

to which the non answer usually follows as:

It depends.

HPC coding requires intimate knowledge of the target hardware architecture as the implemented strategies depend on their characteristics. Starting from a superficial perspective, if the available hardware is in the form of an Symmetric Multi-Processors (SMP) machine, one would probably concentrate on applying approaches where communication costs can be neglected and where memory might be plentyfull. At the other end of the spectrum, the infrastructure might be composed of a mass of heterogeneous computers with varying specifications, interconnected using relatively slow links but possessing ample local storage. Digging deeper, one might find out that the second model proves to be more effective since each node would happen to have faster, less contentious memory access and demonstrate the ability to tap advantageous aggregated Input/Output (I/O) bandwidth thanks to local storage.

Obtaining knowledge of the target hardware architecture is a non trivial balance between theoretical models and supporting empirical data. The collection of such data is usually accomplished via micro-benchmarks and cluster gaging utilities [35]. Unfortunately, these remain

<sup>1.</sup> Which comes first, the software or the hardware, and is the profile on hardware X still applicable to hardware Y?

either too problem specific or too general to be of true value. For this reason, we will concentrate on characterizing the available hardware assuming some *a priori* knowledge of a problem to be optimized (in occurrence, the K-means algorithm detailed in Chapter 3), which exhibit vectorial computation features coupled with considerable data traversal and, in its parallel implementation, adds communications at each iteration <sup>2</sup>.

We now present some of the basic concepts pertaining to computer architecture and communications fabrics. These elements will be useful when attempting to describe some of the characteristics and results of software profiling as presented in Chapter 2 and 3.

### 1.1 Basic Computer Architecture

Today's common computers are still loosely based on the what is commonly known as the *Von Neumann architecture* [23, 50] which means that they are essentially comprised of (at least) one of each of the following elements:

- 1) A control unit (for decoding the instructions and managing data flow);

- 2) An Arithmetic Logic Unit (ALU);

- 3) Main memory (such as Random Access Memory (RAM) more often referred to as Dynamic RAM (DRAM));

- 4) An Input/Output unit managed by the control unit.

#### 1.1.1 The Control Unit and Arithmetic Logic Unit

The control unit and ALU are probably what characterizes a Central Processing Unit (CPU) core the most from the point of view of a compiler. It is in these components that mnemonics <sup>3</sup> are defined to mock up the instruction set and internal structure of a CPU. For the average user, these differences usually don't mean much but can have a significant impact in scientific computing.

<sup>2.</sup> The problems studied are embarrassingly parallel data mining applications which are typically memory bound.

<sup>3.</sup> Menmonics are the short textual words representing operations a CPU can execute (op-codes). They are the building blocs of the assembly language from which binary code (programs) are created.

For example, Advanced Micro Devices (AMD) has implemented a class of mnemonics which they have named 3DNow\* <sup>4</sup>. On their side, Intel has added their own class of mnemonics known as the Streaming SIMD Extension (SSE), which they have named SSE\* and SSSE\* <sup>5</sup>. In all cases, they are an implementation of Instruction-Level Parallelism (ILP), where performance enhancement is accomplished by applying a single instruction to multiple data elements loaded into independent registers of a given CPU core. This approach to low level parallelism is by definition known as Single Instruction Multiple Data (SIMD). The intent is that CPU cores would exhibit enhanced performance when dealing with vector intensive applications typical of multimedia and scientific computing. Nonetheless, proper use of these directives remains a daunting task for the compilers [15], which can benefit from some hints by the programmer, as we will see in Section 3.6.3.

One must not confuse the SIMD extensions with the advent of Chip MultiProcessors (CMP), which are part of yet another class of parallel architecture known as Multiple Instruction Multiple Data (MIMD). In this case, each processing stream (or program) is executing independently, implying a complete decoupling of instruction and data flow. The use of MIMD programming happens at the application level and does not exclude SIMD, the latter being implemented in each computing core. The only implication is that the program execution streams are independent in the case of MIMD and require explicit synchronization mechanisms. An automated implementation of such MIMD approach on CMP and SMP machines is the use of the OpenMP 6 compiler directives.

## 1.2 Caching in on The Main Memory

It is a well known fact that the DRAM performance curve is substantially inferior to the processor's speed evolution over the past decades [23], p.289. To compensate for this bottleneck, processors are built with on-chip caches <sup>7</sup> which help in speeding up memory access by

<sup>4.</sup> We use the \* as a globing character to include all subsequent classes.

<sup>5.</sup> AMD now also supports the SSE\* and SSSE\* class of mnemonics. Note that the extra S means "Supplemental".

<sup>6.</sup> OpenMP is a specification which compilers are free to implement. For details, please visit http://openmp.org/.

<sup>7.</sup> Instruction and data caches can either be separate or common, depending on the hardware implementation.

prefetching data and instructions. The size and speed of these caches is dictated by its proximity to the processor core(s), which in turn is guided by transistor count limitations for a given physical space, heat dissipation and, of course, production costs [23]. This leads to the hierarchical memory layout of most computers where the processor's access to memory is a growing succession of caches, known as levels, who's efficiency is characterized by the ratio of *hits* and *misses* to each of these levels. These cache *levels* are organized starting from the Level 1 (L1) cache, characterized by its high speed but relatively small size <sup>8</sup>. Then follows the Level 2 (L2) cache, slower than the L1 cache but many times larger, it currently ranges from a few hundred kilobytes to a few megabytes. Now becoming more common, the Level 3 (L3) cache is larger than L2 (two to four times), and is mostly used for CMPs as a shared memory space between multiple processors [52, 6]. The last and slowest link down the memory hierarchy being the DRAM memory modules <sup>9</sup> with their ample capacity of a few gigabytes but with comparatively slow access time and bandwidth.

## 1.2.1 Accessing The Main Memory

The L1/L2, Memory Management Unit (MMU) and RAM blocks of Figure 1 are a gross representation of the actual processor to memory architecture now present in modern computers. The model becomes more complex as caches, processors and cores are added to a system. One constant remains, the Memory Management Unit (MMU), which plays a critical role in computer performance as it manages the data flow between the main memory and the processor and is reputed as the bottleneck of any modern system. The two major computer processor manufacturers, AMD and Intel, have diverged in this respect during the past years when comparing AMD's Athlon/Opteron and Intel's Pentium/Core 2 processors. AMD has opted for a Non Uniform Memory Access (NUMA) approach where each physical processor integrates its own MMU and possesses a local memory bank. Although the *local* memory of each processor is globally accessible, accessing it comes at a *varying* (Non Uniform) cost depending on the

<sup>8.</sup> Current processors generally posses an L1 cache close or below 128 K bytes

<sup>9.</sup> Note that we could push the memory hierarchy down into *virtual memory*, residing on Hard Disk Drive (HDD), but we won't address this case as it is an aberration to HPC and must be treated as an element that must not be used in such a context given HDDs are many orders of magnitude slower than RAM.

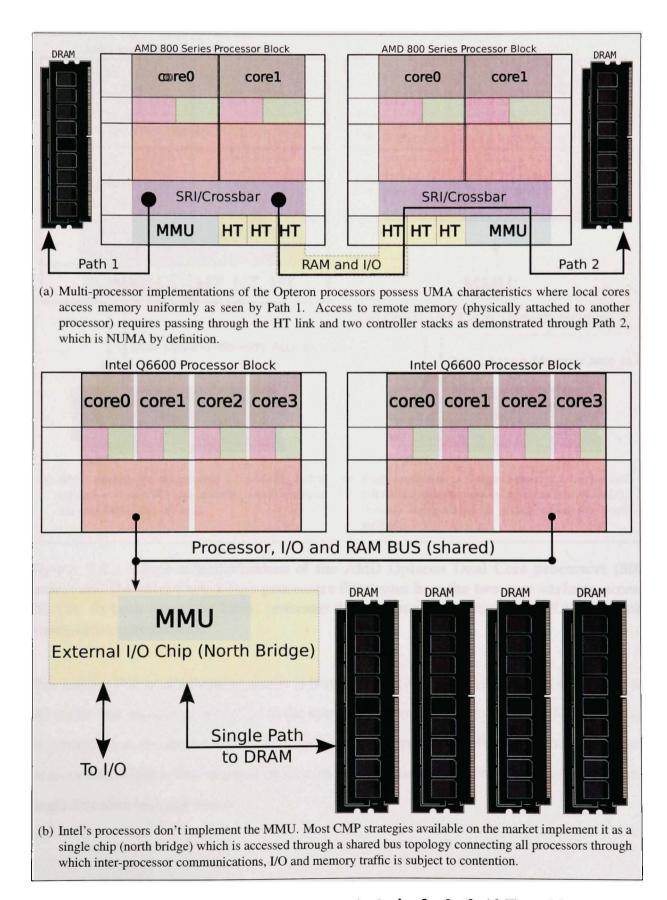

path required for Memory Access (hence NUMA). We illustrate this in Figure 1.1 (a) where a processor accessing its local memory has a direct path (depicted by Path 1) and accessing another processor's memory bank requires a more elaborate, thus longer, path (Path 2). Intel has typically kept the MMU as an external device, which implies a uniform access to the memory banks <sup>10</sup> as illustrated by Figure 1.1 (b).

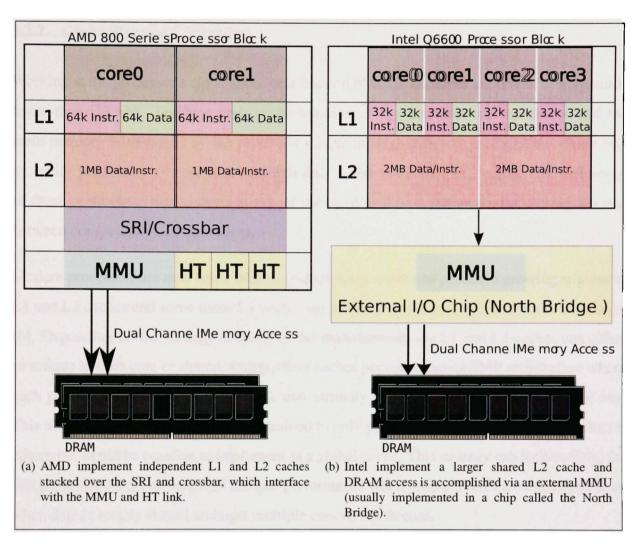

Figure 1.2 (a) is a schematization of a typical AMD Opteron series of processor. It possesses an on chip MMU where the System Request Interface (SRI) interconnects multiple cores through the Crossbar (internal processor communications fabric). The Crossbar then selects between the MMU for local memory requests, or the HT link if the requested memory address is on a *remote* processor. This implies that access to local memory (going through the MMU) is *uniformly* shared by all cores of a single processor unit. Intel's approach implemented in the Core 2 series processors is depicted by Figure 1.2 (b) where we can see that L2 cache is shared and that the MMU resides on an external chip (usually called the North Bridge).

In the case of AMD's implementation, access to memory physically connected to another processor requires the use of the HT link [32, 28] and is typically NUMA in nature. In Figure 1.1 (a), Path 1 illustrates the local core's direct path to memory going through the SRI/Crossbar and MMU. Access to remote memory is illustrated by Path 2 where a request has to traverse the HT link as well as both processor's SRI/Crossbar logic, which adds latency and transfer delays. As processors are added to the system, more of these *hops* can occur, depending on the interconnection strategy used [28]. For Intel type CMP systems, the MMU is an external device and is dependant upon the motherboard implementer to select the interconnection strategy. Generally, these consist in using a single fast bus for I/O, inter-processors and memory (through a single MMU), as illustrated by Figure 1.1 (b).

The direct implications of the differing memory subsystems is that, apart from external hard-ware required to link Intel's processors, they must share the memory bandwidth evenly across processors and devices whereas AMD's processors each have their own local memory banks.

<sup>10.</sup> Although this will no longer be true with their Core i7 series, where they have opted to integrate the MMU into the processor die.

Figure 1.1: Multi-processor memory access strategies for both AMD and Intel processors. AMD possesses NUMA characteristics while Intel's implementation is essentially UMA.

Figure 1.2: These schematizations of the AMD Opteron Dual Core processors (800 series) and the Intel Core 2 Duo processors illustrates how the two core variants access DRAM. In both cases, the MMU possesses dual channel connectivity to DRAM for link bandwidth aggregation.

This implies that Intel's memory access is bound to memory bandwidth and bus contention as I/O traffic and processors are added to the system. In theory, AMD's on-chip MMU leverages its processors as the ideal candidates for embarrassingly parallel applications where aggregate memory bandwidth across multiple processors (not just multiple cores) is more important than single-threaded memory access.

## 1.2.2 Cache Size and Contention

Working at the processor's clock speed or a fraction of it, these caches are orders of magnitude faster than DRAM. Fetching and synchronization of the data between the caches and the main memory is managed by the processor's logic through different mechanisms which rely on easily predictable or repetitive (strided) data access patterns [31], p.300. The efficiency of these *prefetching* mechanisms is one of the most critical components for closing the gap between computation and data access.

Modern processors are now being built to contain many cores and possess a growing amount of L1 and L2 caches and some times L3 caches are added as the inter-core communications layer [6]. Depending on the strategy adopted by the manufacturer, the L1 and L2 caches can either be unique to each core or shared. Independent caches per core mimics SMP architecture where each processor is essentially monolithic and virtually interconnected with a high speed *bus*. This also implies that each core is constrained to only possessing a fraction of the cache that it otherwise would be possible to implement as a global cache. This strategy can be beneficial for independent data flows but could hamper performance when problem sizes are considerable or when data is locally shared amongst multiple concurrent threads.

As a reciprocal to this approach, Intel has implemented a large shared inter-core L2 cache strategy for it's Core 2 processors. This approach has the advantage of a large cache for single threads but shared cache for concurrent threads. Figure 1.2 compares both of these strategies where AMD's Dual Core Opteron 800 class of processors assign independent L2 caches and Intel's Core 2 Quad processor is composed of four cores with L2 caches organized in core pairs.

To demonstrate the different cache issues with concurrent and independent processes running on a CMP, was programmed Algorithm 1 in  $\mathbb{C}$ . This Euclidean *computation kernel* is derived from our case study presented in Chapter 3. For our demonstration, we vary the vector dimension d between 128K bytes and 2M bytes per process in order to saturate the L2 caches when as many processes as cores are started (four processes for a quad-core CMP). Note that we kept

the problem size boundaries identical across experiments (not a function of the processor's cache size) to ease the comparison. We then compute the concurrent execution's *comparative* efficiency  $E_{comp}$ , which we define to be:

$$E_{comp} = \frac{t_{single}}{t_{con.avg}} \tag{1.1}$$

with  $t_{single}$  being the time for a single thread of execution on a given processor and  $t_{con.avg}$  the average time of running concurrent threads <sup>11</sup> on that same system. This result is useful in identifying the interaction zones for concurrent execution of independent programs on a CMP.

```

1: Set d to maximum vector dimension (||X||)

2: Set REPS to maximum repetitions

3: Initialization of vectors X and Y for Euclidean computation.

4: for all i = 1 to d do

5:

Set t_{start} = gettimeofday()

6:

repeat

Compute Euclidean norm such as dist = \sum_{i=1}^{i} (\|\mathbf{x_j} - \mathbf{y_j}\|)

7:

until Computation has been executed REPS times

8:

Set t_{stop} = gettimeofday()

Compute average time as t_{avg} = (t_{stop} - t_{start})/REPS

10:

11: end for

```

Algorithm 1: Memory contention test algorithm.

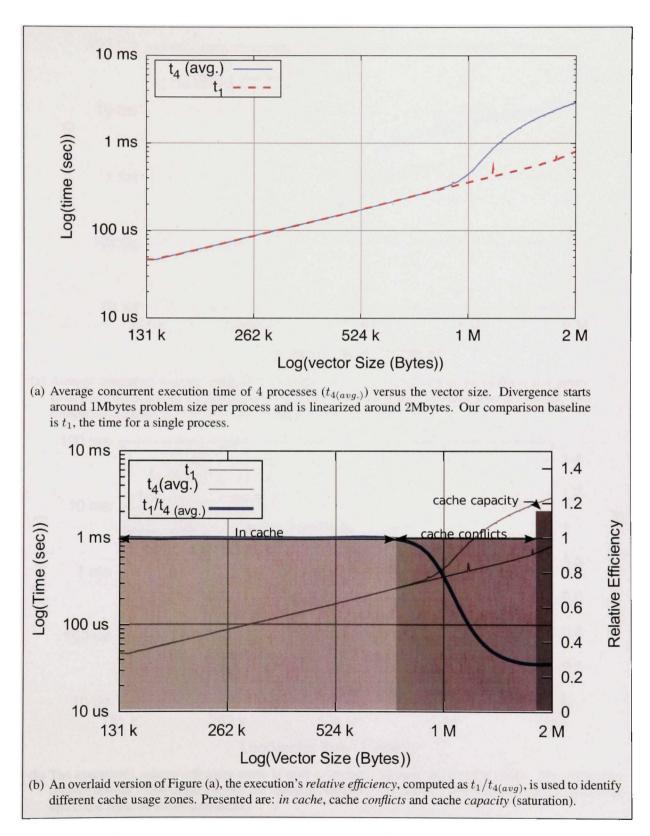

Our results for the Intel Q6600 processor are presented in Figure 1.3. Execution times are presented in Figure 1.3 (a) where we observe performance degradation due to execution concurrency. The cause for the degradation is attributable to the zones identified in Figure 1.3 (b) which correspond to cache usage zones. Performance degradation begins when the vectors X and Y both reach sizes of about 760kbytes per process are reached. With four concurrent processes, this brings the total to about 6Mbytes. This induces cache *conflicts* as the total cache capacity is 4Mbytes for all threads. The processor is forced to move parts of working data out of cache for one or all of the executing processes. Cache *capacity* issues are then reached at

<sup>11.</sup> The number of threads is equal to the number of available cores on the system.

2Mbyte vectors, which is concurrent with the processor's 4Mbyte cache as both vectors for a single thread fill up the cache, leaving no space for the three other threads. At this point, each thread is executed at about 30% efficiency (close to four times slower). These results clearly demonstrate the importance of cache size for the execution time of large *memory bound* kernels as well as concurrency issues that may arise within multi-core processors.