ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

UNIVERSITÉ DU QUÉBEC

THÈSE PRÉSENTÉE À

L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

COMME EXIGENCE PARTIELLE

À L'OBTENTION DU

DOCTORAT EN GÉNIE

Ph.D.

PAR

Christelle HOBEIKA

MÉTHODOLOGIE DE VÉRIFICATION AUTOMATIQUE BASÉE SUR

L'UTILISATION DES TESTS STRUCTURELS DE TRANSITION AVEC INSERTION

DE REGISTRES À BALAYAGE

MONTRÉAL, LE 4 OCTOBRE 2011

© Tous droits réservés, Christelle Hobeika, 2011

©Tous droits réservés

Cette licence signifie qu'il est interdit de reproduire, d'enregistrer ou de diffuser en tout ou en partie, le présent document. Le lecteur qui désire imprimer ou conserver sur un autre media une partie importante de ce document, doit obligatoirement en demander l'autorisation à l'auteur.

**PRÉSENTATION DU JURY**

CETTE THÈSE A ÉTÉ ÉVALUÉE

PAR UN JURY COMPOSÉ DE :

M. Claude Thibeault, directeur de thèse

Département de génie électrique à l'École de technologie supérieure

M. Jean-François Boland, codirecteur

Département de génie électrique à l'École de technologie supérieure

M. Stéphane Coulombe, président du jury

Département de génie logiciel et des TI à l'École de technologie supérieure

M. Marcel Gabrea, membre du jury

Département de génie électrique à l'École de technologie supérieure

M. Bruno De Kelper, membre du jury

Département de génie électrique à l'École de technologie supérieure

M. Othmane Ait Mohamed, membre du jury

Département de génie électrique à l'université concordia

ELLE A FAIT L'OBJET D'UNE SOUTENANCE DEVANT JURY ET PUBLIC

LE 29 SEPTEMBRE 2011

À L'ÉCOLE DE TECHNOLOGIE SUPÉRIEURE

## **REMERCIEMENTS**

Tout d'abord, mes plus sincères remerciements et reconnaissances s'adressent principalement à mon directeur de thèse, le Professeur Claude Thibeault pour son orientation, ses conseils et aussi son soutien moral et financier tout le long de ces années de thèse. Le Professeur Thibeault m'a accompagné tout au long de ma thèse et, par sa présence constante et ses conseils avisés, a grandement contribué à mon développement professionnel, en tant que chercheur, et personnel. J'ai pu accomplir mon doctorat avec succès grâce à ses connaissances, sa sagesse et ses excellentes aptitudes de professeur, chercheur et ami. Je le remercie profondément pour tout ce qu'il a fait pour moi tout au long de ces 5 ans.

J'aimerai remercier aussi mon co-directeur le professeur Jean-François Boland pour son soutien et ses conseils. Je remercie également les membres du jury pour leur collaboration durant l'examen de ce travail, leurs conseils et leur participation à la soutenance. Mes sincères remerciements à tout le personnel du département de génie électrique.

Je remercie aussi tous les collègues et amis, particulièrement ceux du LACIME, du département de génie électrique et de l'association étudiante ainsi que toutes les personnes côtoyées à l'ÉTS. De plus, des remerciements spéciaux pour tous mes amis au Canada et au Liban pour leur présence, leur encouragement, surtout leur amitié pendant toutes ces années. Un remerciement spécial à Mathieu, qui a été le premier à m'accueillir au laboratoire, et qui a partagé avec moi chaque moment de réussite et d'échec depuis le début de ma thèse. Merci pour ton amitié et ton grand amour.

Finalement, à mes parents François et Sonia et mon frère Georges qui m'ont donné l'amour, l'éducation et tout ce qui fait de moi la personne que je suis aujourd'hui. Malgré les longues années de distance, leur soutien, leur affection et surtout leur amour n'a fait qu'augmenter et m'a accompagné tout au long de cette thèse. Je vous aime énormément et je vous remercie pour tout ce que vous avez fait pour moi, cette thèse est la vôtre aussi.

À toute ma famille au Liban, un grand merci.

# **MÉTHODOLOGIE DE VÉRIFICATION AUTOMATIQUE BASÉE SUR L'UTILISATION DES TESTS STRUCTURELS DE TRANSITION AVEC INSERTION DE REGISTRES À BALAYAGE**

Christelle HOBEIKA

## **RÉSUMÉ**

Au cours des dernières décennies, l'évolution de la technologie n'a cessé d'introduire de nouveaux défis dans la vérification des circuits intégrés (IC). L'industrie estime que la vérification fonctionnelle prend environ 50% à 70% de l'effort total d'un projet. Et, malgré les budgets et les efforts investis dans la vérification, les résultats obtenus ne sont pas satisfaisants. La vérification basée sur la simulation, également appelée vérification dynamique, est la technique la plus utilisée dans la vérification fonctionnelle. Par contre, ce type de vérification a clairement échoué à suivre le rythme de croissance de la complexité. Par conséquent, des solutions innovantes sont requises, avec la concurrence sur les produits et les services ainsi que l'implacable loi du temps de mise sur le marché.

Plusieurs techniques ont été développées pour surmonter les défis de la vérification dynamique, allant de techniques entièrement manuelles à des techniques plus avancées. Les techniques manuelles et semi-manuelles ne peuvent être utilisées pour les designs complexes, et les approches les plus avancées qui sont couramment utilisés dans l'industrie ont besoin de compétences particulières et beaucoup d'efforts afin d'atteindre une bonne productivité de vérification.

Au niveau du test par contre, l'utilisation d'approches basées sur des modèles de pannes et sur les concepts de conception en vue du test (DFT), a conduit au développement d'outils automatiques de génération de test (ATPG) efficaces. L'infrastructure de test qui en résulte a grandement aidé la communauté du test à résoudre plusieurs problèmes.

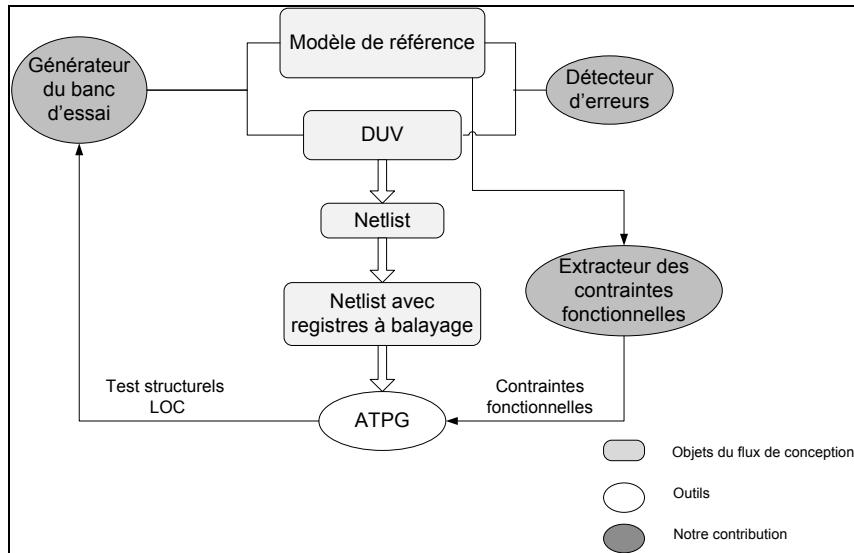

Dans cette thèse, nous nous intéressons principalement à la productivité du processus de vérification, plus particulièrement la vérification de circuits séquentiels. Nous proposons une nouvelle méthodologie qui explore la combinaison du test et de la vérification, plus précisément l'utilisation des tests structurels de transition dans le processus de vérification RT basée sur la simulation. Cette méthodologie a pour but de réduire le temps et les efforts requis pour vérifier un circuit et d'améliorer la couverture résultante, induisant des améliorations significatives de la qualité de la vérification et de sa productivité. La base de la méthodologie proposée est l'intuition (qui est devenu une observation), selon laquelle ce qui est difficile à tester (« Hard Fault ») est probablement difficile à vérifier (« Dark Corner »). L'objectif est de tirer profit des outils de test efficaces tels que les outils ATPG, et les techniques DFT tels que l'insertion des registres à balayage afin de simuler efficacement la fonctionnalité du design avec un minimum de temps et d'efforts. Sur la base de tous ces concepts, nous avons développé un environnement de vérification RTL automatisé composé de trois outils de base: 1) un extracteur de contraintes qui identifie les contraintes

fonctionnelles de conception, 2) un outil générateur de banc d'essai, et 3) un détecteur d'erreurs basé sur une observabilité élevée.

Les résultats expérimentaux montrent l'efficacité de la méthode de vérification proposée. Les couvertures de code et d'erreurs obtenues suite à la simulation avec l'environnement proposé sont égales à, et la plupart des fois plus élevé que, celles obtenues avec d'autres approches connues de vérification. En plus des améliorations de couverture, il y a une réduction remarquable de l'effort et du temps nécessaire pour vérifier les designs.

**Mots clés :** Vérification fonctionnelle, test, simulation, contraintes fonctionnelles, automatisation, RTL.

# MÉTHODOLOGIE DE VÉRIFICATION AUTOMATIQUE BASÉE SUR L'UTILISATION DES TESTS STRUCTURELS DE TRANSITION AVEC INSERTION DE REGISTRES À BALAYAGE

Christelle HOBEIKA

## ABSTRACT

Over the last few decades, technology scaling has continuously brought new challenges to the research community, from integrated circuit (IC) design to IC testing. Industry estimates that functional verification takes approximately 50% to 70% of the total effort on a project. And even with verification budgets dominating design budgets, there are increasingly more bug escapes through fabrication and consequently expensive re-spins. Verification methodologies are grouped into two main categories: 1) Simulation-based methods and 2) formal methods. Although both methodologies are now widely established for design verification, simulation-based verification remains the most commonly used technique. Yet, simulation has clearly failed to keep pace with complexity and faces lots of challenges. Therefore, with the continuous competition growth in products and services along with the harsh law of time to market, innovative solutions are required. Hence, a transition to new methodologies and tools is deemed crucial.

Several techniques have been developed to overcome simulation-based verification challenges, ranging from fully manual to advanced testbenches. The manual and semi-manual techniques cannot be scaled on complex designs, and the more advanced approaches that are commonly used in the industry, need special skills and human interaction to achieve good verification productivity.

From a test perspective, the use of structural approaches based on fault models and on design for testability (DFT) concepts (namely scan-based), has led to the development of efficient automatic test pattern generation (ATPG) tools. The resulting test infrastructure has greatly helped the test community to address previous encountered issues and to face the incoming ones.

In this thesis, we are primarily concerned with the productivity of the verification process, more specifically the verification of sequential circuits. We propose a new methodology that explores a new test/verification combination, namely the use of structural test patterns in the RT simulation-based verification process. This methodology is aimed to reduce time and effort required to verify a circuit and to improve the resulting coverage, inducing significant improvements in verification quality and productivity. The cornerstone of the proposed methodology is the intuition (that became an observation) according to which a node that is difficult to test (Hard Fault) is likely difficult to verify (Dark Corner). The goal is to take advantage of the efficient test tools as ATPG, and the advanced test techniques as scan-based DFT to simulate and exercise efficiently the model functionality with minimum time and effort. Based on all these concepts, we introduced an automated RTL verification environment

composed of three basic tools: 1) A constraint extractor that identifies design's functional constraints, 2) a test bench generator tool, and 3) an error tracker based on a high observability.

Experimental results showed the effectiveness of the proposed verification methodology. It could fast provide fault and code coverage that are equal to and even higher than one obtained with other well known simulation-based verification approaches. In addition to the coverage improvements, there is a remarkable reduction in effort and time needed to verify the designs. Unlike the other methodologies, the proposed approach requires little effort, in order to accomplish the simulation.

**Keywords:** Functional verification, test, simulation, functional constraints, automation, RTL.

## TABLE DES MATIÈRES

|                                                                                             | Page |

|---------------------------------------------------------------------------------------------|------|

| INTRODUCTION .....                                                                          | 23   |

| <br>                                                                                        |      |

| CHAPITRE 1 TEST ET VÉRIFICATION .....                                                       | 33   |

| 1.1 Introduction.....                                                                       | 33   |

| 1.2 Notions de base de la vérification .....                                                | 33   |

| 1.2.1 Méthodologie de vérification.....                                                     | 34   |

| 1.2.2 Vérification dynamique .....                                                          | 35   |

| 1.2.3 Vérification statique.....                                                            | 38   |

| 1.3 Notions de base du test .....                                                           | 41   |

| 1.3.1 Modèles de panne .....                                                                | 42   |

| 1.3.2 Génération automatique de vecteurs de test.....                                       | 44   |

| 1.3.3 Conception en vue du test.....                                                        | 44   |

| 1.3.4 Tests de transition avec insertion des registres à balayage .....                     | 46   |

| 1.4 Conclusion .....                                                                        | 48   |

| <br>                                                                                        |      |

| CHAPITRE 2 REVUE DE LITTÉRATURE .....                                                       | 49   |

| 2.1 Vérification dynamique .....                                                            | 49   |

| 2.1.1 Vérification aléatoire basée sur les contraintes.....                                 | 49   |

| 2.1.2 Vérification basée sur les assertions .....                                           | 52   |

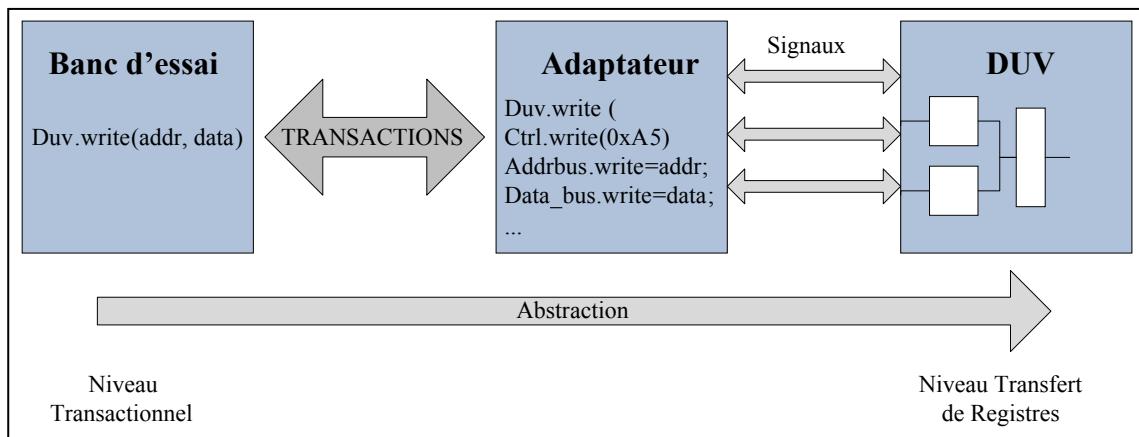

| 2.1.3 Vérification transactionnelle.....                                                    | 53   |

| 2.2 Combinaison du test et de la vérification.....                                          | 54   |

| 2.3 Les modèles d'erreurs RTL .....                                                         | 56   |

| 2.4 États illégaux d'un design.....                                                         | 58   |

| 2.5 Conclusion .....                                                                        | 59   |

| <br>                                                                                        |      |

| CHAPITRE 3 UTILISATION DES TESTS STRUCTURELS DANS LA SIMULATION.....                        | 61   |

| 3.1 Introduction.....                                                                       | 61   |

| 3.2 Pannes cachées versus coins sombres.....                                                | 62   |

| 3.2.1 Pannes cachées.....                                                                   | 62   |

| 3.2.2 Coins sombres.....                                                                    | 63   |

| 3.2.3 Corrélation entre les coins sombres et les pannes cachées .....                       | 64   |

| 3.3 Le choix des tests structurels .....                                                    | 66   |

| 3.4 Utilisation des vecteurs de test structurels dans la vérification RTL.....              | 68   |

| 3.4.1 Génération des vecteurs de test structurels .....                                     | 69   |

| 3.4.2 Application des tests de transition LOC avec registres à balayage au modèle RTL ..... | 70   |

| 3.5 Premiers résultats expérimentaux .....                                                  | 75   |

| 3.5.1 Corrélation entre les coins sombres et les pannes cachées .....                       | 75   |

| 3.5.1.1 Expériences.....                                                                    | 75   |

| 3.5.1.2 Conceptions.....                                                                    | 78   |

|                                                                                                                                 |                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|

| 3.6                                                                                                                             | Conclusion .....                                                                    | 83  |

| <br>                                                                                                                            |                                                                                     |     |

| <b>CHAPITRE 4 ÉTUDE THÉORIQUE DE LA DÉTECTION DES ERREURS DU DESIGN AU NIVEAU RTL À L'AIDE DES TESTS DE TRANSITION LOC.....</b> |                                                                                     | 85  |

| 4.1                                                                                                                             | Introduction.....                                                                   | 85  |

| 4.2                                                                                                                             | Hypothèses .....                                                                    | 86  |

| 4.3                                                                                                                             | Détection des erreurs RTL à l'aide des vecteurs structurels LOC et limitations..... | 86  |

| 4.3.1                                                                                                                           | Le modèle BOE.....                                                                  | 87  |

| 4.3.2                                                                                                                           | Le modèle BSE .....                                                                 | 89  |

| 4.3.3                                                                                                                           | Le modèle BDE.....                                                                  | 90  |

| 4.3.4                                                                                                                           | Le modèle MSE .....                                                                 | 91  |

| 4.3.5                                                                                                                           | Le modèle BCE.....                                                                  | 92  |

| 4.3.6                                                                                                                           | Le modèle MCE .....                                                                 | 93  |

| 4.3.7                                                                                                                           | Le modèle LCE .....                                                                 | 95  |

| 4.3.8                                                                                                                           | Le modèle ESE .....                                                                 | 97  |

| 4.3.9                                                                                                                           | Les erreurs FSM.....                                                                | 97  |

| 4.3.9.1                                                                                                                         | Le modèle SCE .....                                                                 | 98  |

| 4.3.9.2                                                                                                                         | Le modèle NSE.....                                                                  | 100 |

| 4.4                                                                                                                             | Test de transition versus <i>stuck-at</i> .....                                     | 102 |

| 4.5                                                                                                                             | Les états illégaux.....                                                             | 105 |

| 4.5.1                                                                                                                           | Effet des états illégaux .....                                                      | 105 |

| 4.5.2                                                                                                                           | Exemple : compteur .....                                                            | 106 |

| 4.5.3                                                                                                                           | Les fausses erreurs .....                                                           | 109 |

| 4.6                                                                                                                             | Conclusion .....                                                                    | 110 |

| <br>                                                                                                                            |                                                                                     |     |

| <b>CHAPITRE 5 EXTRACTION AUTOMATIQUE DES CONTRAINTES FONCTIONNELLES À PARTIR D'UN MODÈLE RTL .....</b>                          |                                                                                     | 111 |

| 5.1                                                                                                                             | Introduction.....                                                                   | 111 |

| 5.2                                                                                                                             | Grammaire d'analyse d'expression VHDL .....                                         | 112 |

| 5.2.1                                                                                                                           | VHDL .....                                                                          | 113 |

| 5.2.2                                                                                                                           | Grammaire d'analyse d'expression.....                                               | 113 |

| 5.2.3                                                                                                                           | La PEG VHDL.....                                                                    | 115 |

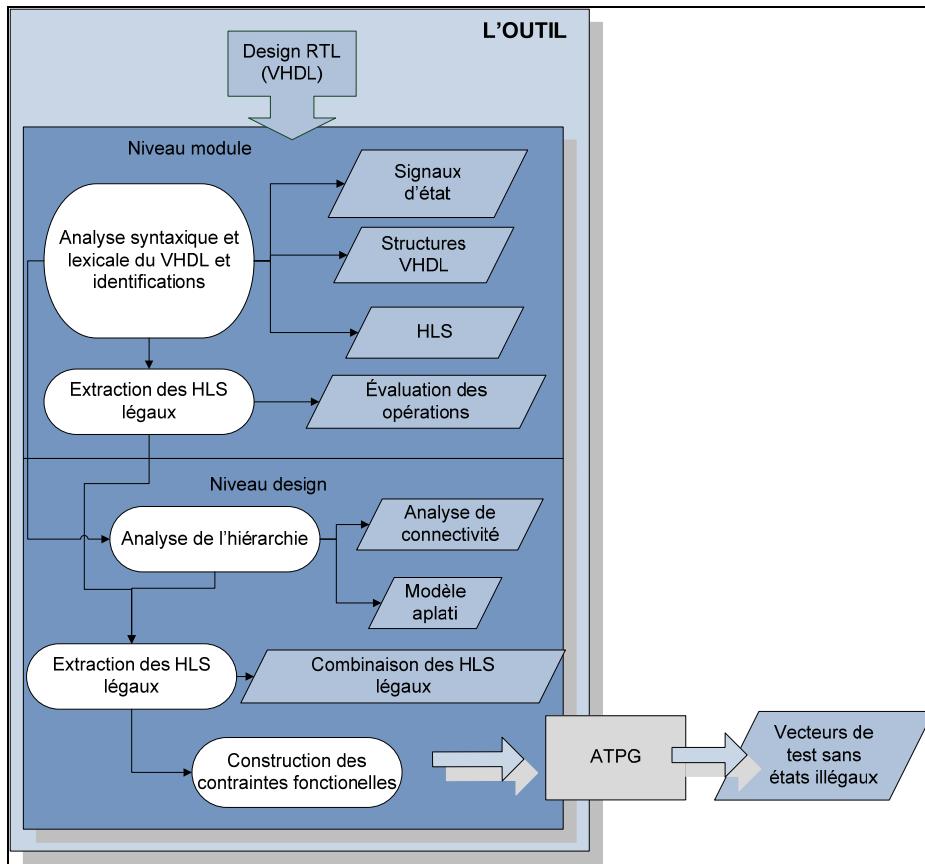

| 5.3                                                                                                                             | Approche proposée .....                                                             | 117 |

| 5.4                                                                                                                             | Implémentation détaillée.....                                                       | 119 |

| 5.4.1                                                                                                                           | Analyse du VHDL et identification des différentes structures .....                  | 120 |

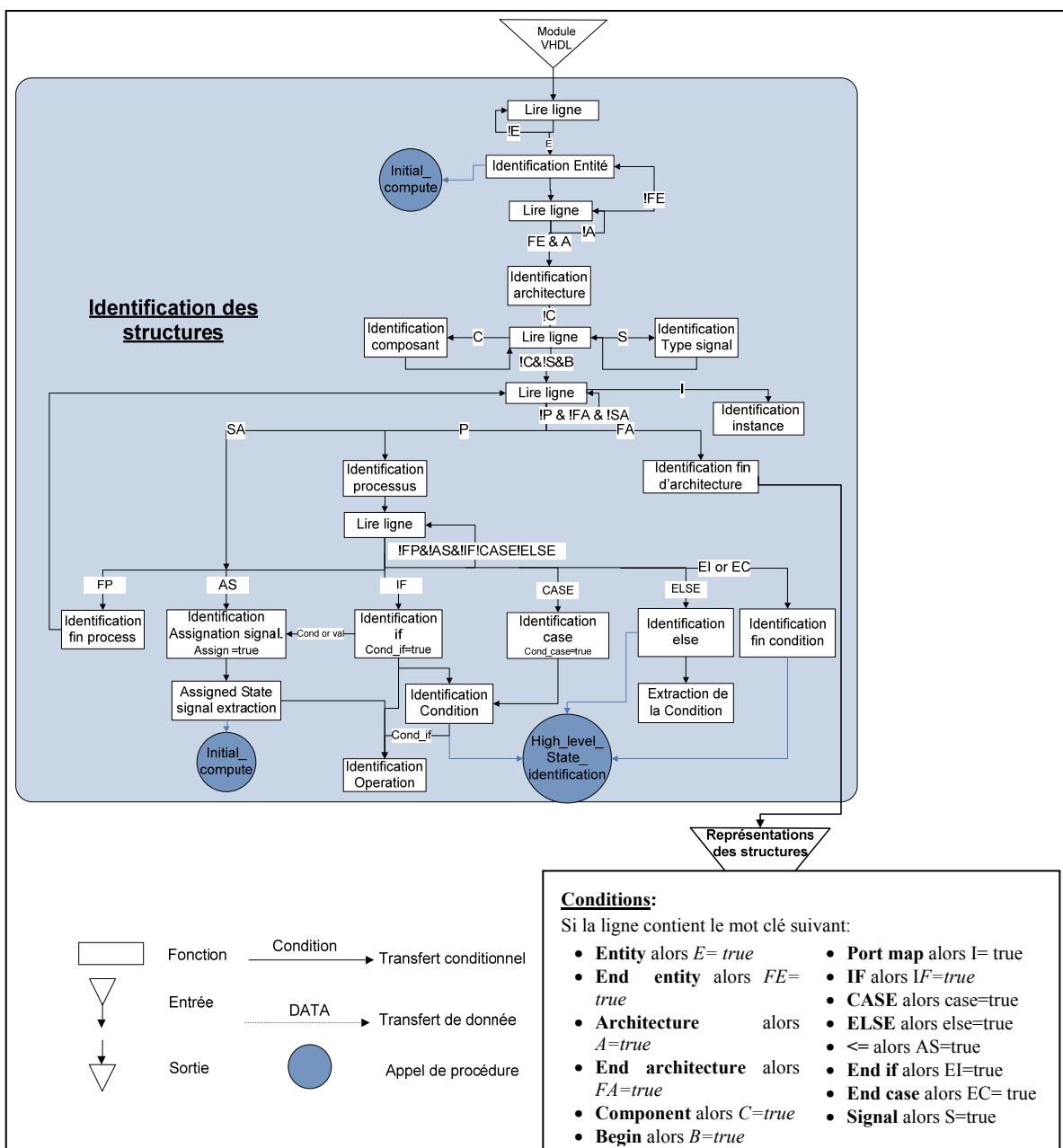

| 5.4.1.1                                                                                                                         | Identification des structures VHDL .....                                            | 122 |

| 5.4.1.2                                                                                                                         | Identification des valeurs initiales des différents signaux<br>d'états.....         | 125 |

| 5.4.1.3                                                                                                                         | Identification des HLS .....                                                        | 125 |

| 5.4.2                                                                                                                           | Extraction des HLS des module.....                                                  | 127 |

| 5.4.2.1                                                                                                                         | Évaluation des opérations .....                                                     | 127 |

| 5.4.2.2                                                                                                                         | Implémentation détaillée.....                                                       | 131 |

|                                                                       |                                                                |            |

|-----------------------------------------------------------------------|----------------------------------------------------------------|------------|

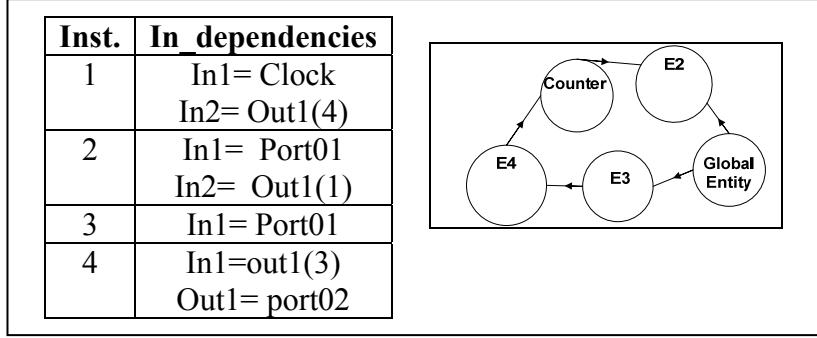

| 5.4.3                                                                 | Analyse hiérarchique du design .....                           | 134        |

| 5.4.3.1                                                               | Analyse de connectivité des modules .....                      | 134        |

| 5.4.3.2                                                               | Modèle aplati .....                                            | 137        |

| 5.4.4                                                                 | Extraction des HLS du design.....                              | 138        |

| 5.4.5                                                                 | Extraction des contraintes fonctionnelles .....                | 139        |

| 5.5                                                                   | Résultats expérimentaux .....                                  | 140        |

| 5.5.1                                                                 | La vérification .....                                          | 141        |

| 5.5.2                                                                 | Le test .....                                                  | 142        |

| 5.6                                                                   | Conclusion .....                                               | 143        |

| <b>CHAPITRE 6 ENVIRONNEMENT DE VÉRIFICATION COMPLET PROPOSÉ .....</b> |                                                                | <b>145</b> |

| 6.1                                                                   | Introduction.....                                              | 145        |

| 6.2                                                                   | Environnement de vérification proposé .....                    | 145        |

| 6.2.1                                                                 | Le générateur automatique du banc d'essai .....                | 146        |

| 6.2.2                                                                 | Le détecteur d'erreurs .....                                   | 148        |

| 6.3                                                                   | Résultats expérimentaux .....                                  | 148        |

| 6.4                                                                   | Conclusion .....                                               | 151        |

| <b>CONCLUSION .....</b>                                               |                                                                | <b>153</b> |

| <b>RECOMMANDATIONS .....</b>                                          |                                                                | <b>157</b> |

| ANNEXE I                                                              | LES MODÈLES D'UN SYSTÈME .....                                 | 159        |

| ANNEXE II                                                             | CODE PERL DU GÉNÉRATEUR DU BANC D'ESSAI .....                  | 161        |

| ANNEXE III                                                            | CODE PERL DU DÉTECTEUR D'ERREURS.....                          | 185        |

| ANNEXE IV                                                             | CODE PERL DE L'EXTRACTEUR DES CONTRAINTES FONCTIONNELLES ..... | 187        |

| <b>LISTE DE RÉFÉRENCES BIBLIOGRAPHIQUES.....</b>                      |                                                                | <b>223</b> |

## LISTE DES TABLEAUX

|              | Page                                                                                                                                                                                       |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 3.1  | L'ensemble des transitions du design 1, avec Tm= Transition montante et Td= transition descendante .....                                                                                   | 79  |

| Tableau 3.2  | L'ensemble des transitions possibles du design 2, avec Tm= Transition montante et Td= transition descendante .....                                                                         | 80  |

| Tableau 3.3  | Comparaison des couvertures des différentes techniques de vérification.....                                                                                                                | 82  |

| Tableau 4.1  | Les différents tests de transition possibles du nœud $X_i$ , basés sur les comportements de $X_i$ et $X_j$ .....                                                                           | 88  |

| Tableau 4.2  | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test de transition LOC du nœud $X_i$ , dans le cas d'une erreur de type BOE.....                     | 88  |

| Tableau 4.3  | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test de transition LOC du nœud $A_i$ , dans le cas d'une erreur de type BSE.....                     | 90  |

| Tableau 4.4  | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test de transition LOC du nœud $X_i$ , dans le cas d'une erreur de type BCE.....                     | 93  |

| Tableau 4.5  | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test de transition LOC du nœud $A_i$ , dans le cas de la suppression d'un module dans le design..... | 95  |

| Tableau 4.6  | Exemple d'erreur de type LCE.....                                                                                                                                                          | 96  |

| Tableau 4.7  | Les différents tests possibles s@1 (s@0) du noeud $X_i$ , basés sur les comportements de $X_i$ et $X_j$ .....                                                                              | 103 |

| Tableau 4.8  | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test s@1 du nœud $X_i$ , dans le cas d'une erreur de type BOE.....                                   | 103 |

| Tableau 4.9  | Le test de transition test 3.....                                                                                                                                                          | 103 |

| Tableau 4.10 | Comportement des modèles de référence et du DUV lors de l'application des vecteurs de test de transition test 3, dans le cas d'une erreur de type BOE.....                                 | 104 |

|              |                                                                                                                              |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau 4.11 | Différence entre les probabilités de détection d'erreurs des tests de transition et celle des tests « <i>stuck-at</i> »..... | 104 |

| Tableau 5.1  | Opérateurs de construction d'expression d'analyse.....                                                                       | 114 |

| Tableau 5.2  | L'ensemble des règles d'analyse VHDL .....                                                                                   | 116 |

| Tableau 5.3  | Identification des différentes structures VHDL.....                                                                          | 122 |

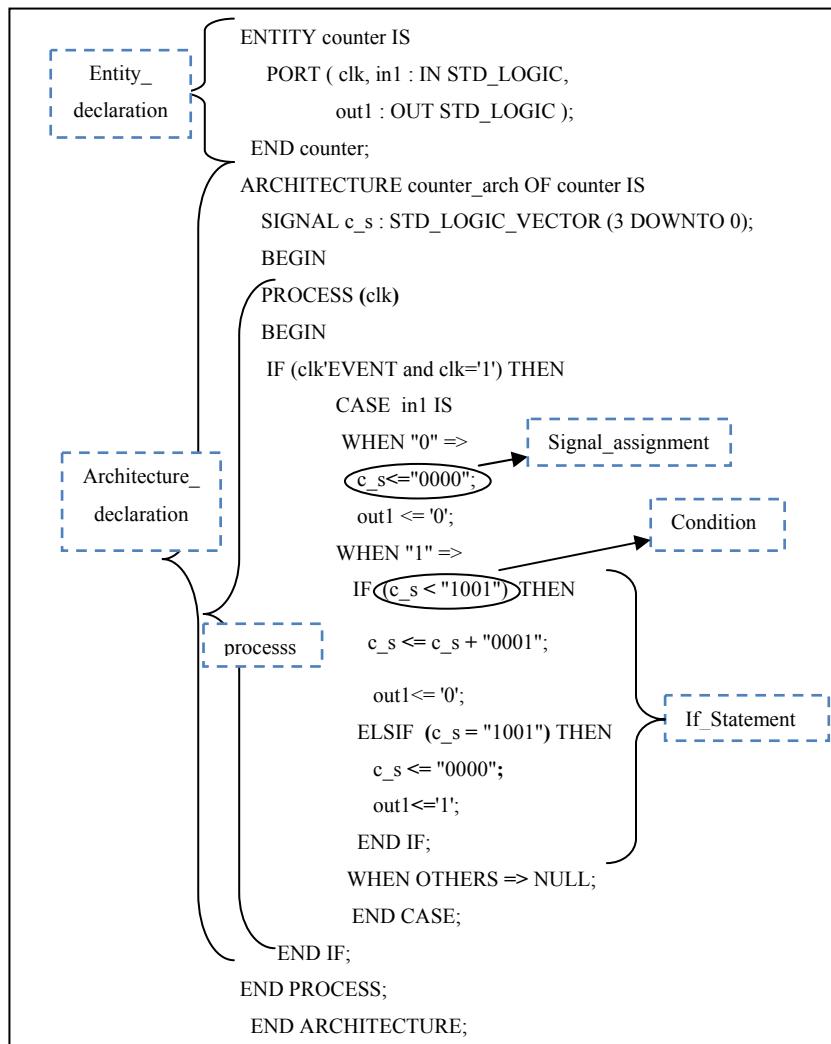

| Tableau 5.4  | Valeurs initiales des signaux d'état basées sur l'exemple de la Figure 5.1 .....                                             | 125 |

| Tableau 5.5  | HLS correspondants à l'exemple de la Figure 5.1.....                                                                         | 127 |

| Tableau 5.6  | Contraintes des signaux d'états.....                                                                                         | 130 |

| Tableau 5.7  | Affectation des signaux d'états.....                                                                                         | 130 |

| Tableau 5.8  | HLS.....                                                                                                                     | 132 |

| Tableau 5.9  | Procédures, paramètres et code.....                                                                                          | 132 |

| Tableau 5.10 | Contraintes des signaux d'états.....                                                                                         | 133 |

| Tableau 5.11 | Affectation des signaux d'états.....                                                                                         | 134 |

| Tableau 5.12 | HLS.....                                                                                                                     | 134 |

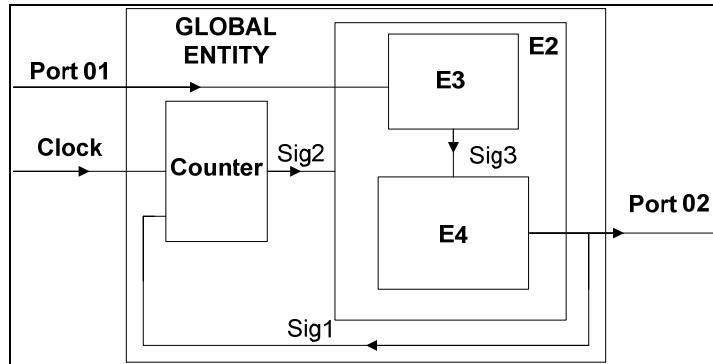

| Tableau 5.13 | Les représentations des entités du design de la Figure 5.6 .....                                                             | 135 |

| Tableau 5.14 | Les composants de l'entité Globale du design de la Figure 5.6.....                                                           | 135 |

| Tableau 5.15 | Les instances de l'entité globale du design de la Figure 5.6.....                                                            | 136 |

| Tableau 5.16 | Les composants de E2 du design de la Figure 5.6 .....                                                                        | 136 |

| Tableau 5.17 | Les instances de E2 du design de la Figure 5.6 .....                                                                         | 136 |

| Tableau 5.18 | Structure des données représentant les connexions du design de la Figure 5.6 .....                                           | 137 |

| Tableau 5.19 | Caractéristiques des circuits ITC'99 utilisés.....                                                                           | 141 |

| Tableau 5.20 | Nombre de fausses erreurs détectées sans contraintes .....                                                                   | 142 |

| Tableau 5.21 | ATPG avec contraintes versus sans contraintes.....                                                                           | 143 |

| Tableau 6.1  | Caractéristiques des circuits expérimentaux.....                                                                             | 149 |

|             |                                                            |     |

|-------------|------------------------------------------------------------|-----|

| Tableau 6.2 | Comparaison des couvertures d'états et de transitions..... | 150 |

| Tableau 6.3 | Comparaison des couvertures d'erreurs.....                 | 150 |

## LISTE DES FIGURES

|            | Page                                                                                                   |

|------------|--------------------------------------------------------------------------------------------------------|

| Figure 0.1 | Écart de productivité.....                                                                             |

| Figure 0.2 | Classification des pannes basée sur leur détectabilité.....                                            |

| Figure 1.1 | Flux de conception et de vérification.....                                                             |

| Figure 1.2 | La vérification dynamique.....                                                                         |

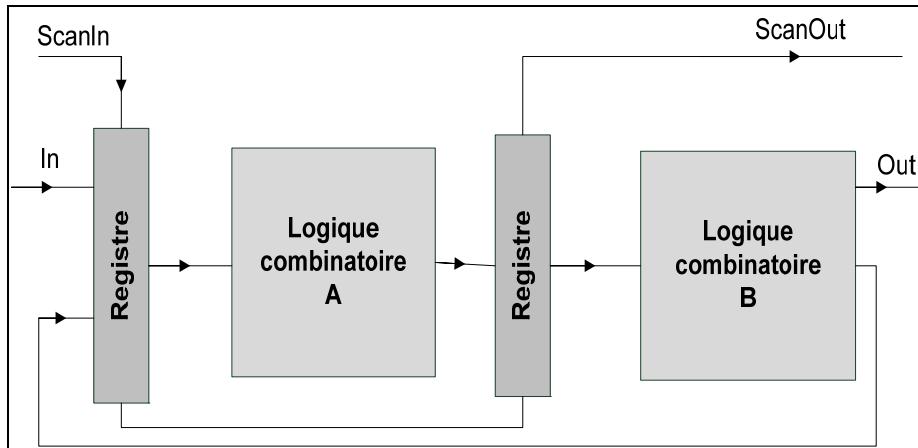

| Figure 1.3 | Test à balayage en série.....                                                                          |

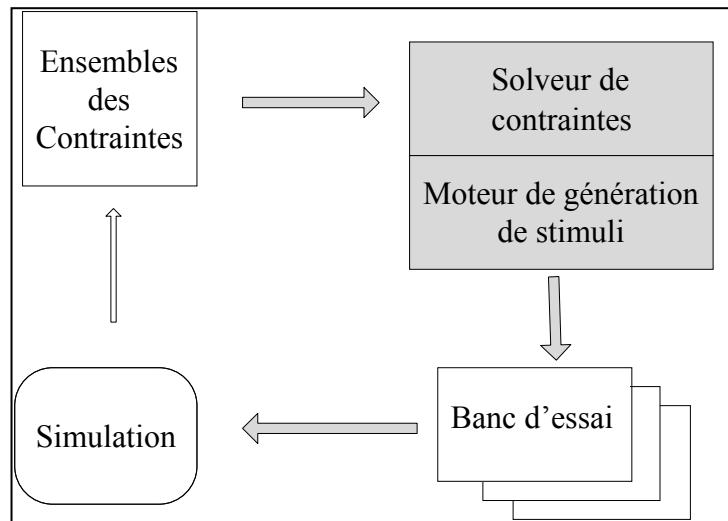

| Figure 2.1 | Environnement de vérification aléatoire basé sur les contraintes.....                                  |

| Figure 2.2 | Vérification transactionnelle.....                                                                     |

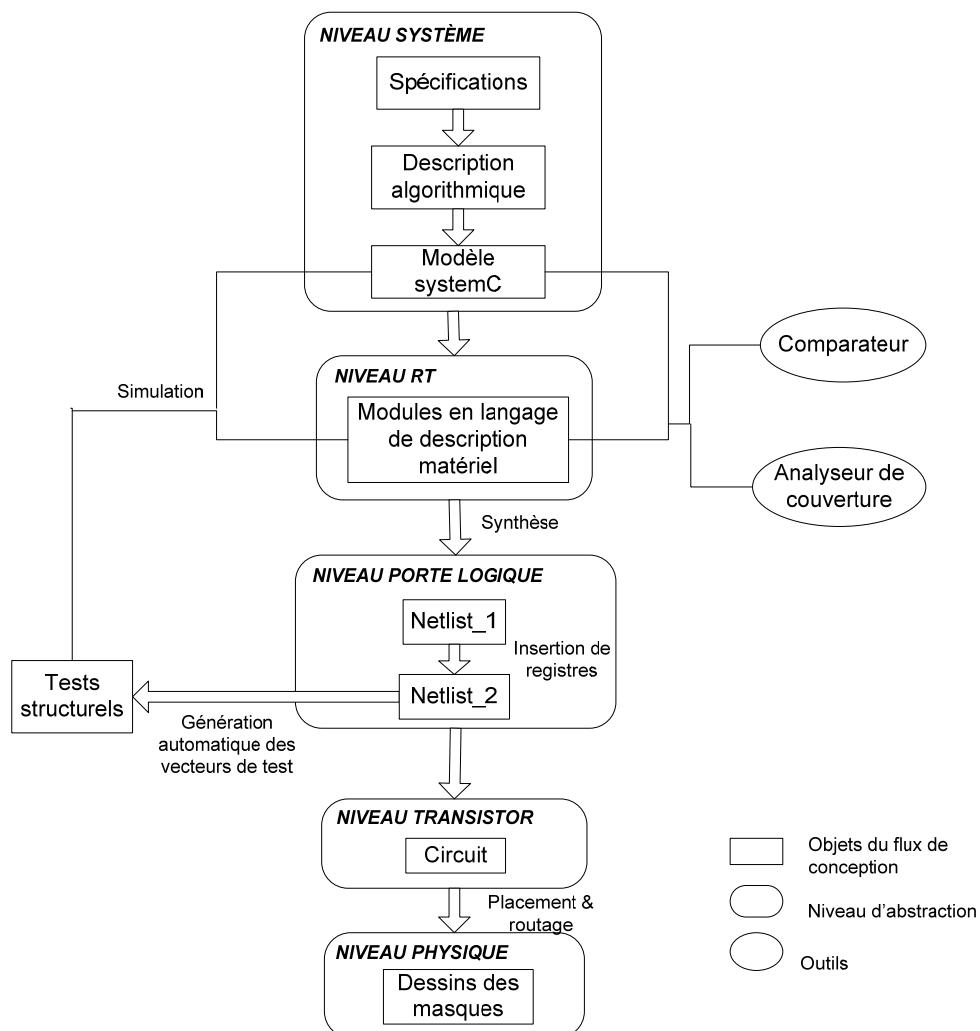

| Figure 3.1 | Flux de conception standard implémentant l'utilisation des tests structurels dans la vérification..... |

| Figure 3.2 | Test de transition STF (STR) sur un nœud $X_i$ .....                                                   |

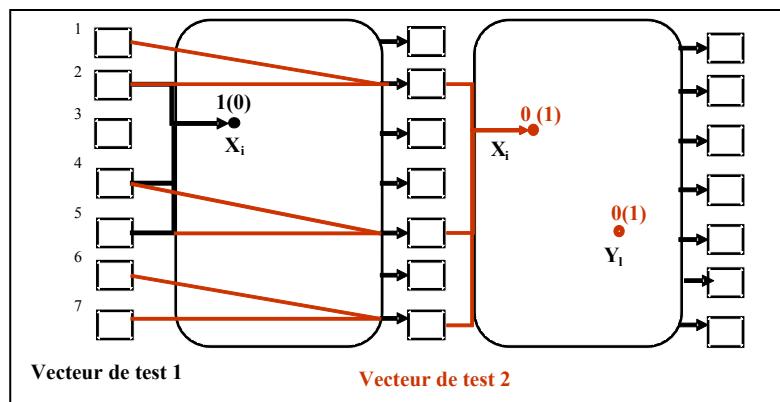

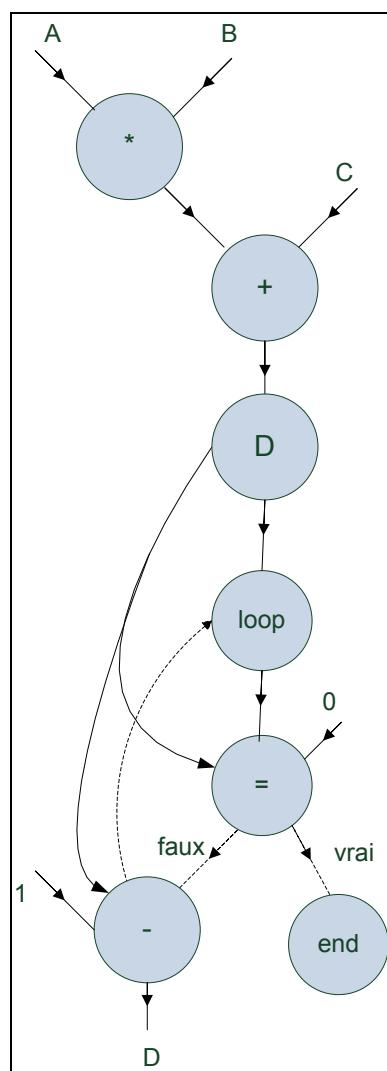

| Figure 3.3 | Exemple d'un modèle de test LOC avec registres à balayage.....                                         |

| Figure 3.4 | Vecteur de simulation RTL formé à partir du modèle de test LOC de la Figure 3.3.....                   |

| Figure 3.5 | Description RTL de l'entité du circuit 1.....                                                          |

| Figure 3.6 | Le diagramme TRIO correspondant au circuit 1.....                                                      |

| Figure 3.7 | Description RTL de l'entité du circuit 2.....                                                          |

| Figure 3.8 | Superposition des résultats des deux niveaux RT et porte logique pour le circuit 1.....                |

| Figure 3.9 | Superposition des résultats des deux niveaux RT et porte logique pour le circuit 2.....                |

| Figure 4.1 | Exemple d'erreur de type BOE.....                                                                      |

| Figure 4.2 | Exemple d'erreur de type BSE.....                                                                      |

| Figure 4.3 | Exemple d'erreur de type BDE.....                                                                      |

| Figure 4.4 | Exemple d'erreur de type MSE.....                                                                      |

|             |                                                                                                                                                                                         |     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.5  | Exemple d'erreur de type BCE.....                                                                                                                                                       | 92  |

| Figure 4.6  | Exemple d'erreur de type MCE .....                                                                                                                                                      | 94  |

| Figure 4.7  | Exemple d'erreur de type ESE.....                                                                                                                                                       | 97  |

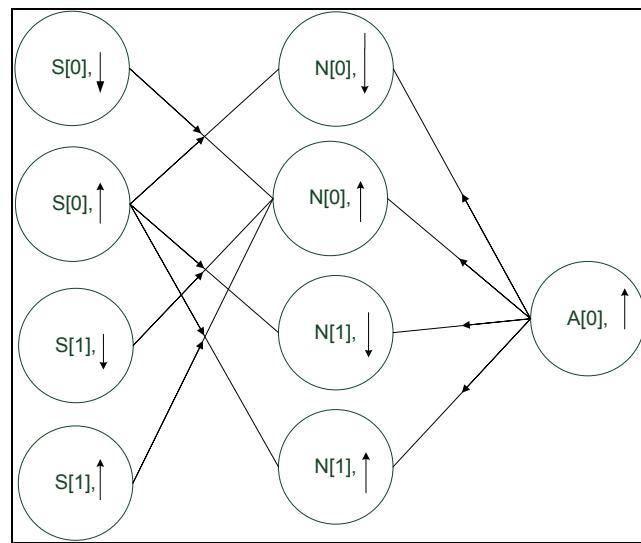

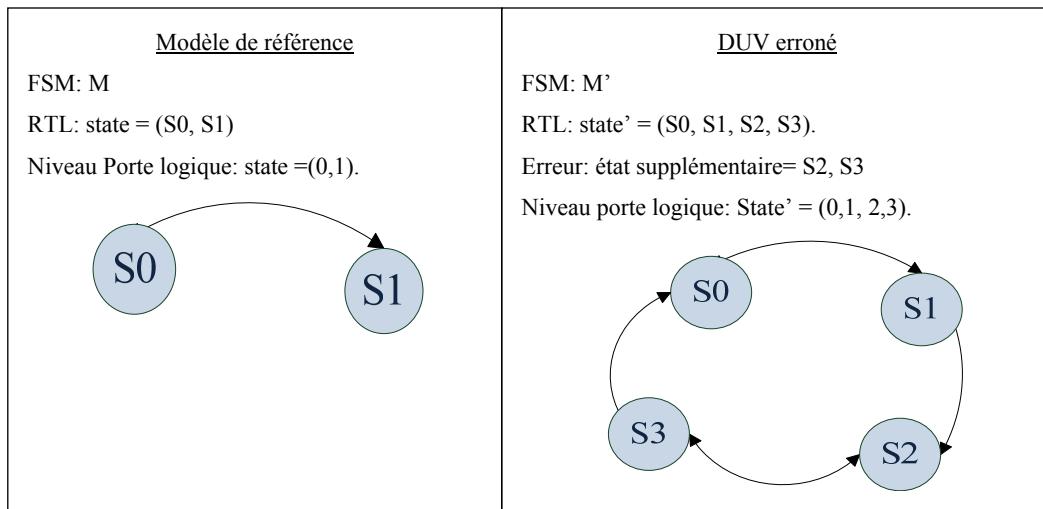

| Figure 4.8  | Exemple d'erreur de type NSE, états supplémentaires.....                                                                                                                                | 99  |

| Figure 4.9  | Exemple d'erreur de type NSE, états manquants.....                                                                                                                                      | 99  |

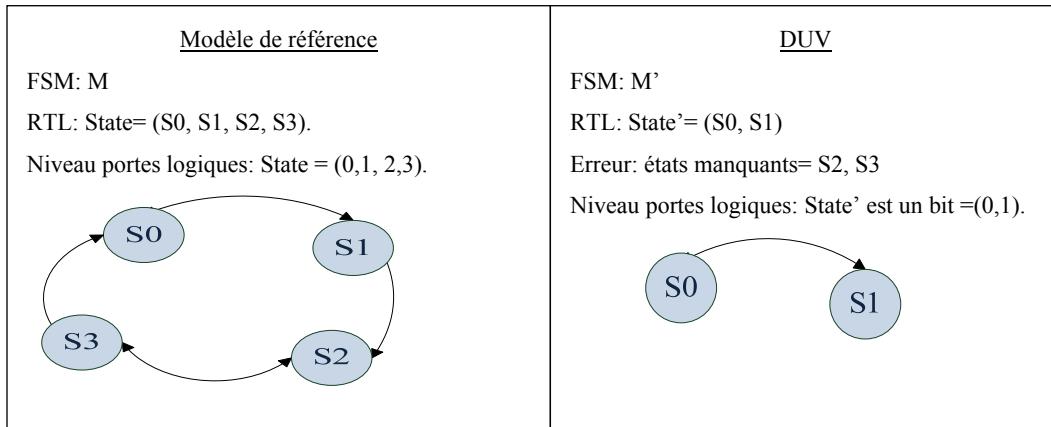

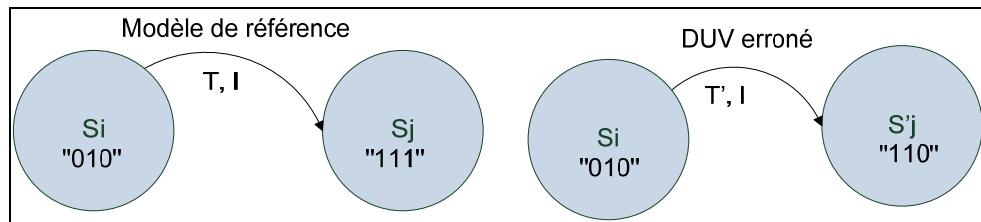

| Figure 4.10 | Exemple d'erreur de type NSE.....                                                                                                                                                       | 101 |

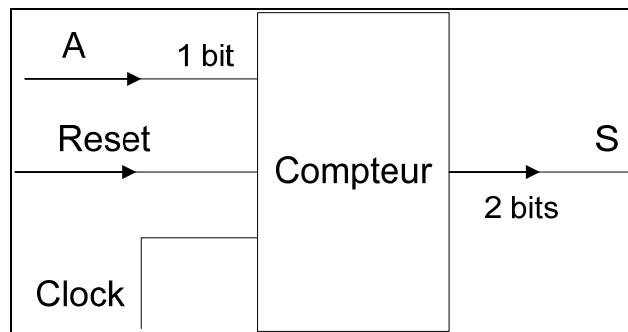

| Figure 4.11 | Exemple de deux codes VHDL différents d'un compteur.....                                                                                                                                | 107 |

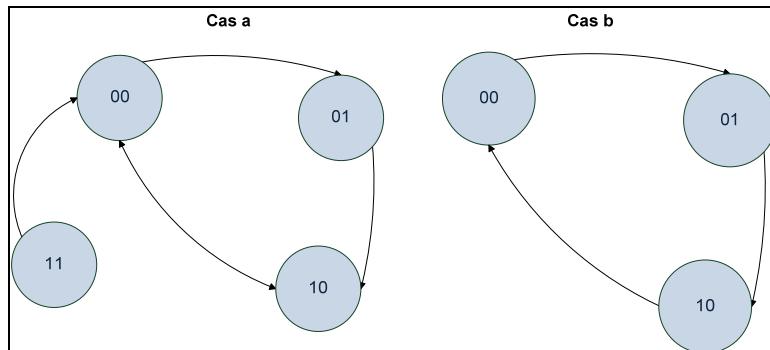

| Figure 4.12 | Les machines à états correspondants aux 2 styles de code cas a et<br>cas b du compteur 2 bits présenté dans l'exemple ci-dessus. <a href="#">107Thèse_corrigé_apresoutenance_v3.doc</a> |     |

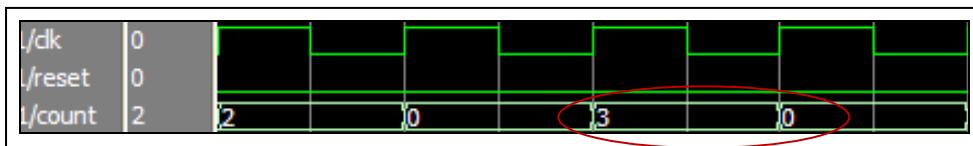

| Figure 4.13 | Vecteurs de test ATPG correspondant à l'exemple de la Figure 4.11....                                                                                                                   | 108 |

| Figure 4.14 | Résultat de la simulation du compteur (cas a) avec les vecteurs de<br>test de transition. <a href="#">108Thèse_corrigé_apresoutenance_v3.doc - _Toc305486240</a>                        |     |

| Figure 4.15 | Résultat de la simulation du compteur (cas b) avec les vecteurs de<br>test de transition.....                                                                                           | 109 |

| Figure 5.1  | Exemple de code VHDL.....                                                                                                                                                               | 115 |

| Figure 5.2  | Extraction des contraintes fonctionnelles d'un design VHDL.....                                                                                                                         | 118 |

| Figure 5.3  | Identification des structures VHDL d'un module.....                                                                                                                                     | 121 |

| Figure 5.4  | Les représentations de a) entité b) composant c) signal_type<br>d) instance e) affectation de signal f) structure if g) structure case g)<br>condition i) opération.....                | 124 |

| Figure 5.5  | Détails de l'implémentation de la procédure<br><i>high_level_state_identification</i> .....                                                                                             | 126 |

| Figure 5.6  | Exemple d'un design hiérarchique.....                                                                                                                                                   | 135 |

| Figure 5.7  | Pseudo-code de la création d'un modèle aplati.....                                                                                                                                      | 137 |

| Figure 5.8  | Modèle aplati du design de la Figure 5.6.....                                                                                                                                           | 138 |

| Figure 5.9  | Pseudo-code de l'extraction des contraintes fonctionnelles du design. ...                                                                                                               | 139 |

| Figure 6.1  | L'environnement de vérification proposé. ....                                                                                                                                           | 146 |

**LISTE DES ABRÉVIATIONS, SIGLES ET ACRONYMES**

|      |                                   |

|------|-----------------------------------|

| ATPG | Automatic test pattern generation |

| BCD  | Binary coded decimal              |

| BDD  | Binary decision diagram           |

| BIST | Built in self test                |

| BOE  | Bus order error                   |

| BDE  | Bus driver error                  |

| BCE  | Bus count error                   |

| CC   | Contrôlabilité combinatoire       |

| CS   | Contrôlabilité séquentielle       |

| DUV  | Design under verification         |

| DFT  | Design for testability            |

| ESE  | Expression structure error        |

| FSM  | Finite state machine              |

| HLS  | High level state                  |

| HDL  | Hardware description langage      |

| LOC  | Launch on capture                 |

| LCE  | Label count error                 |

| MSE  | Module substitution error         |

| MCE  | Module count error                |

| NSE  | Next state error                  |

| OC   | Observabilité combinatoire        |

|       |                                               |

|-------|-----------------------------------------------|

| OS    | Observabilité séquentielle                    |

| OSCI  | Open systemC intiative                        |

| OVL   | Open verification library                     |

| PSL   | Property specification language               |

| PEG   | Parsing expression grammar                    |

| RT    | Register transfer                             |

| RTL   | Register transfer level                       |

| ST-FU | Structurally testable functionally untestable |

| STR   | Slow to rise                                  |

| STF   | Slow to fall                                  |

| SCE   | State count error                             |

| SVA   | SystemVerilog assertions                      |

| TVM   | Transaction verification model                |

| TRIO  | Input output transition                       |

| QVL   | Questa verification library                   |

## INTRODUCTION

Le processus d'intégration des puces électroniques est divisé en 4 phases majeures : la conception, la vérification, la fabrication et le test. La conception permet de passer du "système" au "silicium", via plusieurs niveaux d'abstraction, allant du modèle dit de haut niveau correspondant à une description fonctionnelle du circuit, au modèle dit de bas niveau correspondant à l'élaboration des plans des masques (« *layout* ») définissant la topologie du circuit. Pour chaque étape de conception, diverses opérations doivent être effectuées pour s'assurer que le travail est bien fait et conforme aux spécifications. On retrouve dans la littérature deux termes représentant ces opérations : validation et vérification. Même s'il existe plusieurs définitions différentes pour ces termes, les plus courantes sont les suivantes (Sommerville, 2000): la validation est la série d'opérations par laquelle on s'assure qu'on conçoit le bon produit (i.e. correspondant aux spécifications fonctionnelles) alors que la vérification est la série d'opérations par laquelle on s'assure que le produit est intégré correctement. Dans le cadre de cette thèse, nous considérons que la validation est la série d'opérations effectuées à haut niveau d'abstraction pour confirmer le choix des algorithmes de traitement, via par exemple des simulations faites à l'aide d'un outil tel que Matlab. Nous considérons également que la vérification est la série d'opérations effectuées pour : 1) s'assurer de l'équivalence entre deux niveaux d'abstraction différents au niveau de la fonctionnalité, et 2) s'assurer du respect des spécifications dites non fonctionnelles, telles la fréquence maximale d'opération, la puissance dissipée, le respect des règles du dessin des masques, etc. Dans le cadre de cette thèse, nous nous intéressons au premier type de vérification, que nous appellerons vérification fonctionnelle.

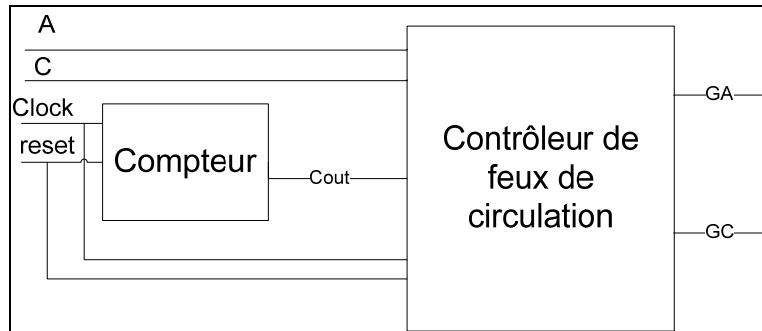

C'est après la fabrication du circuit que le test survient. Il permet de détecter les défauts et les pannes issus des procédés de fabrication afin d'assurer une bonne qualité des produits avant leur mise en marché. Depuis plusieurs décennies, la croissance de la complexité des systèmes numériques est en évolution constante. Au niveau du test, l'utilisation d'approches basées sur des modèles de pannes et sur les concepts de conception en vue du test (DFT, *Design For Testability*) a conduit au développement d'outils de

génération automatique de vecteurs de tests (ATPG, *Automatic Test Pattern Generation*) efficaces (Rabaey, 1996). L'infrastructure de test résultante a permis de palier aux principaux problèmes dus à la croissance de complexité. Dans le cadre de cette thèse, nous proposons de tirer avantage de la maturité de l'infrastructure de test afin d'améliorer la vérification.

En revanche, au niveau de la vérification, la complexité ne cesse de s'accentuer et s'accroît exponentiellement avec le temps. Ceci est du en grande partie à l'absence de procédés automatiques et efficaces permettant de faire face à la croissance de la complexité et de la taille des designs (Dempster, 2001). Cette problématique, qui constitue la problématique principale à laquelle s'attaque cette thèse, est décrite plus en détails dans ce qui suit. Notons également que l'utilisation proposée de l'infrastructure de test pour améliorer la vérification nous oblige à nous intéresser à une problématique secondaire, l'élimination des états illégaux des vecteurs de test. Cette problématique sera également définie plus loin.

### **Problématique principale**

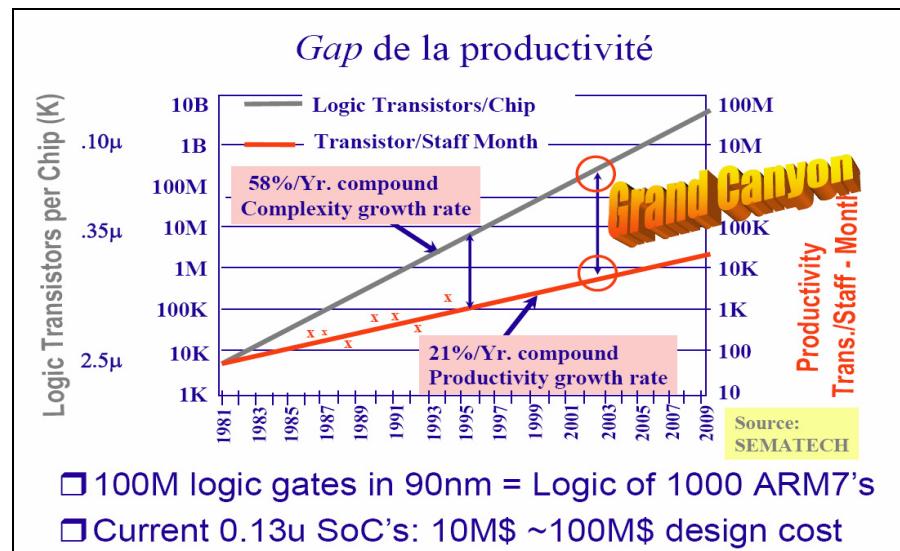

Le développement continu de la technologie induit une augmentation de la complexité et du niveau d'intégration d'un design. En 1965, Gordon Moore a prédit que le nombre de transistors pouvant être intégrés sur une puce augmenterait de manière exponentielle avec le temps. La tendance prédictive s'est matérialisée et est devenue la fameuse « loi de Moore ». Nous sommes par exemple passés de  $10^5$  transistors par chip en 1982 à  $10^9$  en 2009, ce qui a conduit à des systèmes de plus en plus complexes. L'augmentation de la complexité des dispositifs, que ce soit en termes du nombre de transistors ou encore en termes d'intégration de nouveaux types de modules (analogique, RF, MEMS, ...) conduit, outre les problèmes de conception, à de nombreux défis à relever dans le domaine de la vérification. La croissance de la complexité du design induit une augmentation de la complexité de presque toutes les étapes de la vérification allant de l'analyse du modèle jusqu'à l'analyse des résultats de la vérification, conduisant à une augmentation du temps alloué à la vérification et une diminution de la qualité de cette dernière. Dans le cas de la vérification fonctionnelle, comme la stratégie la plus utilisée demeure la simulation, l'explosion du temps se situe à ce niveau.

Le temps et les efforts investis ne se limitent pas à la définition des bancs d'essai et à la simulation en tant que tel, mais aussi à la compréhension et à l'analyse du modèle à simuler ainsi que de son contexte d'utilisation afin de bien vérifier sa fonctionnalité. En général, dans un projet de conception de circuit numérique, la conception et la vérification sont prises en charge par des équipes différentes. La Figure 0.1 montre l'écart grandissant qui se creuse entre la croissance de la complexité d'un circuit d'une part et la croissance de la productivité d'intégration d'une autre part. Cet écart est dû en grande partie à la vérification fonctionnelle, étant donné qu'elle occupe la majeure partie du temps d'un projet (Molina, 2007).

Figure 0.1 Écart de productivité.

Tirée de (Sematech, 1999)

Malgré les diverses méthodologies présentes dans la littérature et qui seront détaillées dans le chapitre 2 de cette thèse, la vérification présente encore plusieurs défis à relever, et ce à différents niveaux :

- le temps alloué à la vérification est très long : en plus du temps de la simulation, s'ajoute le temps d'analyse du modèle, de conception des bancs d'essai et de débogage. La phase de vérification occupe 50% à 70% du temps total d'un projet de conception (Molina,

2007), créant un délai majeur avant la mise sur le marché du produit. Et donc, la réduction du temps alloué à la vérification est devenue primordial pour les entreprises;

- les efforts alloués à la vérification sont colossaux : dépendamment de la méthodologie utilisée, les ingénieurs de vérification déploient beaucoup d'efforts à différentes étapes de la vérification :

- la lecture, l'analyse et la compréhension du modèle implémenté par les concepteurs;

- la génération d'un ensemble de bancs d'essai (i.e. vecteurs de simulation) efficaces permettant de couvrir le plus d'erreurs possibles en un temps limité;

- la détection des erreurs et le débogage;

- la prédition et l'analyse de la couverture.

- l'espace d'états des modèles séquentiels est énorme. La taille de l'espace d'états est le défi premier de la vérification. Pour vérifier la fonctionnalité d'un design, l'ingénieur de vérification doit s'assurer que chaque état courant possible et chaque combinaison d'entrée possible permettent une transition du système vers l'état suivant désirable. Un grand espace d'états requiert de longues et complexes séquences de stimuli induisant une simulation longue et complexe;

- la qualité de vérification et de la couverture atteinte est insatisfaisante. Selon une enquête menée par Collett International Research Inc en 2002 (Inc., 2002), 60% de la production défectueuse contient des défauts fonctionnels ou logiques; ce pourcentage a atteint 70% selon une étude menée par FarWest Research en 2007 (FarWest Research, 2007). Parmi ces designs défectueux, plusieurs d'entre eux avaient des erreurs de conception pouvant être détectées lors de la vérification : respectivement 70 et 78% en 2002 et 2007. Il est presque impossible de vérifier complètement un design, et une bonne couverture nécessite beaucoup de temps et d'efforts. Il est très difficile de produire un ensemble de vecteurs de simulation assez diversifié pour couvrir le plus de types et de nombre d'erreurs possibles et assez limité pour permettre une simulation de durée acceptable.

En conclusion, la phase de vérification est une phase complexe et exigeante qui affecte la productivité du design des circuits intégrés et consomme énormément de temps et d'efforts

sans toutefois atteindre des résultats satisfaisants. Bon nombre de problèmes associés aux méthodes de vérification fonctionnelles d'aujourd'hui sont causées par l'absence d'une automatisation efficace pour lutter contre la croissance rapide de la taille et la complexité des designs.

### Problématique secondaire

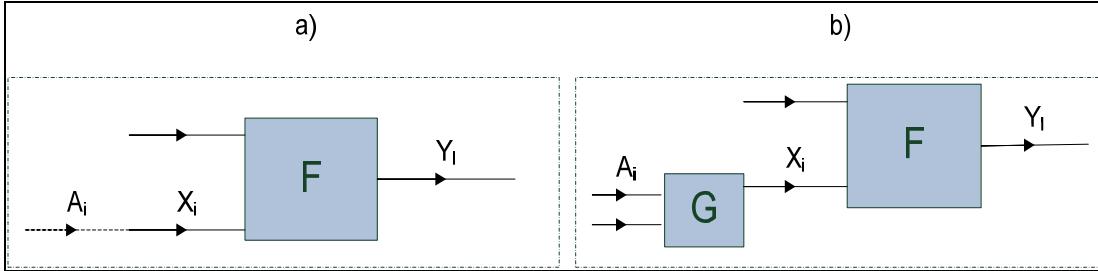

La méthodologie de vérification proposée dans cette thèse cherche à tirer profit de l'infrastructure avancée du test afin d'améliorer la vérification et surmonter les problèmes décrits précédemment. L'utilisation du test au niveau de la vérification impose une problématique secondaire, celle-ci étant l'existence des états illégaux dans les vecteurs de test.

Une machine à états modélisant le comportement d'un circuit séquentiel est une représentation de l'ensemble d'états valides de ce dernier ainsi que l'ensemble des valeurs d'entrées et de leurs combinaisons possibles permettant de transiter d'un état à l'autre. Dans la plupart des cas, une grande partie des espaces d'états des circuits séquentiels n'est pas utilisée. Ces états ne peuvent jamais se produire en mode fonctionnel : il s'agit des états illégaux. Prenons l'exemple d'un compteur 4 bits décimal codé binaire (BCD, « *Binary Coded Decimal* ») : sa sortie s'incrémente de 0 à 9, les états contenant les valeurs 10 à 16 correspondent à des états invalides appelés états illégaux. Bien que ces valeurs fassent partie de l'espace d'états de la sortie, ils ne se produisent jamais en mode fonctionnel.

La technique de DFT basée sur l'insertion des registres à balayage, présentée plus en détails dans cette thèse, permet l'application d'une valeur quelconque sur les nœuds internes d'un circuit. Ceci présente plusieurs avantages au niveau de l'observabilité et de la contrôlabilité d'un circuit, mais peut causer des problèmes au niveau du test et de la vérification lorsque les valeurs appliquées correspondent à des états illégaux et ne peuvent avoir lieu en mode fonctionnel.

Le problème au niveau de la vérification a été soulevé durant le développement de la méthodologie proposée dans cette thèse. La présence d'états illégaux peut dans certaines conditions causer des comportements différents du design en vérification (DUV, « *Design Under Verification* »), et du modèle de référence, causant ainsi la détection de fausses erreurs. Le problème au niveau de la vérification sera présenté en détails dans le chapitre 4 alors que le chapitre 5 présentera la méthodologie proposée pour y remédier.

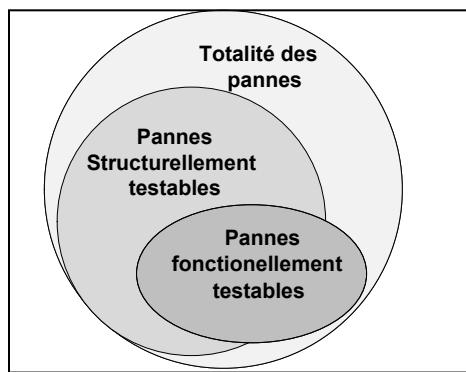

De plus, la présence des états illégaux dans l'ensemble des vecteurs de test crée des problèmes au niveau du test. En effet, ces vecteurs de test causent la détection de pannes fonctionnellement non testables (ST-FU, « *Structurally Testable Functionally Untestable* »), d'où le phénomène de surtest (« *overtesting* »). La raison pour laquelle une panne structurellement testable est fonctionnellement non testable est l'existence de contraintes au niveau des fonctions et des opérations du design, appelées contraintes fonctionnelles. Des résultats expérimentaux ont montré l'existence des pannes ST-FU (Krstic, 2003; Rearick, 2001). La Figure 0.2 montre la classification des pannes dans un design (Lin, 2006). Le surtest résulte en une perte du rendement qui peut être significative. Toutes les méthodes de test basées sur les registres à balayage font face au surtestage. Les pannes ST-FU sont détectées si l'état de départ est un état illégal. Pour minimiser le surtestage, en plus de l'identification des pannes fonctionnellement non testables, il faut également identifier les états illégaux. En général, l'identification des pannes ST-FU présente une complexité qui augmente exponentiellement avec la taille du circuit (Lin, 2005).

Figure 0.2 Classification des pannes basée sur leur détectabilité.

Adaptée de (Lin, 2006)

En plus du surtest, l’existence des états illégaux accentue la complexité de la génération de tests. En effet, la génération de vecteurs de test consiste essentiellement en 2 étapes : activation de la panne et propagation de cette dernière vers une sortie observable. Les deux étapes requièrent une analyse et une justification des valeurs à travers le circuit. En présence des états illégaux, l’espace de recherche devient plus grand et le générateur de test pourrait tenter de justifier des états qui sont injustifiables. Ceci dégrade l’efficacité de la génération de test. Plusieurs contributions sont faites dans le domaine mais la problématique est toujours là pour les circuits séquentiels complexes (Konijnenburg, 1999). L’identification des états illégaux aide à contraindre l’espace de recherche du STPG aux états légaux et justifiables afin d’éviter les recherches inutiles, sauver du temps CPU et augmenter l’efficacité du test (Konijnenburg, 1999).

En conclusion, l’existence potentielle des états illégaux dans les vecteurs de test générés en conjonction avec la technique DFT d’insertion de registres à balayage crée des problèmes au niveau de la vérification et du test.

### **Objectifs de la recherche**

Dans notre travail de recherche, nous visons à améliorer la qualité et la productivité de la vérification fonctionnelle des circuits séquentiels complexes, plus précisément au niveau

d'abstraction appelé transfert de registres (« Register Transfert, RT »), qui constitue le niveau dominant pour l'entrée du design (via l'utilisation de langages de description matérielle tel le langage de description matériel des circuits intégrés à grande vitesse (VHDL, *Very high speed integrated circuit Hardware Description Langage*) et qui se situe entre le niveau système et celui des portes logiques. Nous ciblons plus particulièrement les circuits séquentiels complexes dominés par le contrôle tels que les machines à états (FSM, *Finite State Machine*), sachant que la plupart de ces circuits peuvent être modélisés sous forme de machines à états finis (Goren, 2002). L'objectif principal des travaux de recherche est de développer un environnement de vérification permettant de surmonter les principaux défis de la vérification fonctionnelle et visant essentiellement à :

- éliminer la phase de lecture et de compréhension du modèle précédent la vérification;

- automatiser la conception des bancs d'essai basés sur des stimuli efficaces et puissants;

- augmenter la contrôlabilité du DUV lors de la simulation;

- réduire le temps de la simulation des circuits séquentiels;

- augmenter l'observabilité pour une meilleure détection d'erreurs;

- améliorer la couverture de la vérification, et permettre la couverture des nombreux états d'un design sans faire appel aux longues séquences de stimuli;

- réduire le temps et l'effort investis dans la vérification en automatisant le processus au complet.

Une nouvelle méthodologie de vérification est proposée. Cette méthodologie explore une combinaison entre le test et la vérification. L'idée est de tirer profit du développement et de l'évolution des techniques et outils de test (DFT, ATPG) pour améliorer la vérification. Cet objectif global se divise en plusieurs objectifs spécifiques :

- définir la relation entre ce qui est difficile à tester et ce qui est difficile à vérifier;

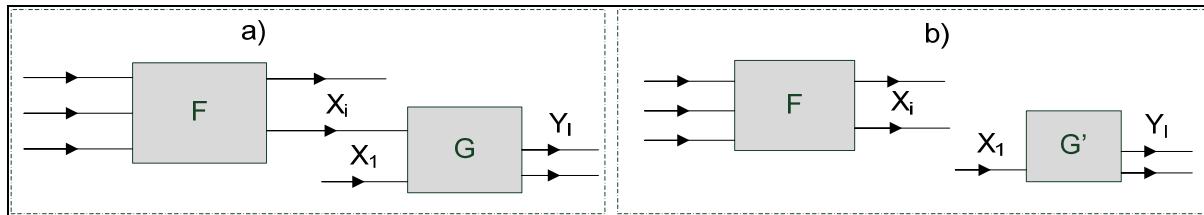

- développer une stratégie pour le passage du niveau porte logique structurel au niveau RT structurel ou comportemental;

- choisir un modèle de panne adéquat pour une simulation efficace de la fonctionnalité;

- éliminer les états illégaux des vecteurs de test structurels;

- émuler les techniques de conception en vue du test au niveau de la simulation RT;

- automatiser la conception des bancs d'essai au niveau RT (RTL, « Register Transfer Level») en exploitant les vecteurs de test structurels.

On suppose que les circuits sont au niveau RT (VHDL) et que leur modèle de référence (SystemC) est disponible (Séméria, 2002; Wagner I., 2007). Tous les outils présentés dans la thèse peuvent être adaptés pour couvrir d'autres langages de description matérielle (ex. Verilog).

### **Contributions de la thèse**

Les contributions majeures de cette thèse sont les suivantes :

- dans (Hobeika, 2008), nous avons montré que ce qui est difficile à tester est difficile à vérifier mais ce qui est difficile à vérifier n'est pas nécessairement difficile à tester. Cette corrélation a permis d'orienter notre recherche vers l'utilisation des vecteurs de test dans la vérification afin d'améliorer la qualité de la vérification fonctionnelle. Une justification du choix du type de vecteurs de test structurel (vecteurs de transition LOC *Launch On Capture*) ainsi qu'une description détaillée de la stratégie de passage du niveau logique au niveau RT sont aussi présentées;

- deux articles ont été publiés (Hobeika 2009; 2010) et un troisième de journal (Hobeika, 2011) (sujet du chapitre 5), présentant l'environnement de vérification automatique basé sur l'utilisation des tests structurels. De plus, nous avons reçu le prix de la meilleure affiche étudiante lors de l'IEEE VLSI Test Symposium qui a eu lieu en 2009 en Californie, toujours sur le même sujet. L'environnement de vérification proposé est composé de trois outils de base:

- un extracteur automatique identifiant les contraintes fonctionnelles de conception. Dans (Hobeika, 2010), nous avons développé une nouvelle approche pour l'extraction des contraintes fonctionnelles au niveau RT. La publication en cours de rédaction présente l'outil avec les algorithmes et les implémentations détaillées. Dans nos travaux, nous avons montré l'efficacité des contraintes extraites :

- au niveau de la vérification : Avec l'application des contraintes fonctionnelles aucune fausse erreur n'a été détectée;

- au niveau du test : Les contraintes fonctionnelles extraites ont permis une diminution du surtest.

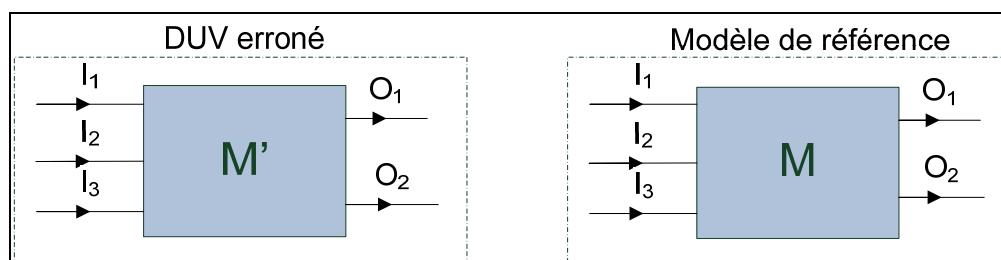

- un générateur automatique de bancs d'essai. Sur la base de la corrélation présentée dans (Hobeika, 2008), nous avons proposé dans (Hobeika, 2009) un générateur automatique de bancs d'essai permettant d'appliquer les vecteurs de test structurel lors de la simulation du DUV. L'outil permet d'adapter les vecteurs de test structurel au niveau RT, et d'émuler la technique DFT d'insertion de registres à balayage durant la vérification ;

- un détecteur automatique d'erreurs basé sur une observabilité élevée. Cet outil est présenté également dans (Hobeika, 2009). Il prend en entrée les réponses de la simulation du DUV et celles du modèle de référence, et produit en sortie une liste des erreurs détectées.

## **Organisation de la thèse**

La thèse est structurée comme suit. Le chapitre 1 présente les notions de bases des domaines du test et de vérification. Une revue de littérature englobant ces deux domaines est présentée dans le chapitre 2. D'un côté, nous présentons les algorithmes et techniques de tests avancées qui seront utilisés dans nos travaux, et d'un autre côté nous décrivons les différentes techniques et méthodologies les plus utilisées de nos jours dans le domaine de la vérification. Afin de justifier l'orientation de nos recherches, le chapitre 3 établit la relation existante entre la difficulté à tester et la difficulté à vérifier et présente la stratégie requise pour passer du niveau porte logique structurel au niveau RT comportemental ou structurel. Ensuite, une étude théorique montrant la capacité des tests structurels de transition LOC à détecter les erreurs RTL est présentée dans le chapitre 4. Le chapitre 5 décrit en détails la méthodologie proposée pour l'extraction des contraintes fonctionnelles d'un design afin d'éviter la production des états illégaux. Et finalement le chapitre 6 présente l'environnement de vérification complet incluant les 3 outils automatiques ainsi qu'une comparaison des résultats obtenus avec les techniques de vérification existantes afin d'évaluer la méthodologie proposée. La thèse se termine par les conclusions et recommandations.

## **CHAPITRE 1**

### **TEST ET VÉRIFICATION**

#### **1.1 Introduction**

Les travaux de recherche effectués dans le cadre de cette thèse englobent les domaines de la vérification fonctionnelle et du test. Une présentation de ces deux domaines, de leurs concepts et limitations s'avère essentielle pour introduire, par la suite, la méthodologie de recherche.

Ce chapitre est divisé en deux grandes parties. La première introduit le domaine de la vérification en présentant ses deux faces, statique et dynamique, et montrant les caractéristiques de chacune ainsi que les différents types de méthodologies impliquées. La deuxième partie présente le domaine du test, plus précisément les tests manufacturiers ainsi que les techniques développées pour améliorer leur qualité.

#### **1.2 Notions de base de la vérification**

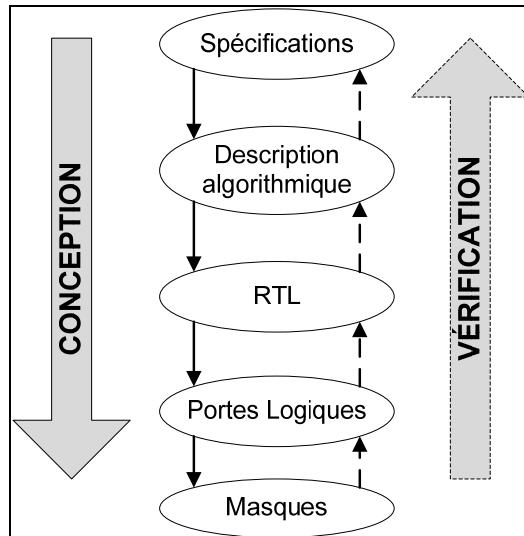

Le processus de conception consiste à transformer un ensemble de spécifications d'un design en une implémentation détaillée. Cette implémentation est raffinée en augmentant le niveau de détails lors du passage d'un niveau d'abstraction à l'autre. Les principaux niveaux d'abstraction des implémentations sont : les spécifications fonctionnelles, la description algorithmique, le RTL, les portes logiques (« *netlist* »), les transistors et les masques. La vérification est le processus inverse de la conception. Elle permet de s'assurer qu'une représentation du design à un niveau d'abstraction donné répond bien au niveau d'abstraction supérieur ou ultimement aux spécifications. On parle de vérification fonctionnelle lors qu'on s'intéresse plus particulièrement aux aspects de fonctionnalité d'un design (par opposition aux éléments dits non-fonctionnels telles la puissance dissipée, la fréquence maximale de l'horloge, etc.). À chaque étape de la conception, i.e pour chaque passage d'un niveau

d'abstraction à l'autre, correspond une étape de vérification. La vérification accompagne donc chaque raffinement durant la conception du design, chaque changement dans l'algorithme, chaque ajout de détail. Les deux processus de conception et de vérification sont décrits dans la Figure 1.1 (Lam, 2005).

Dans ce qui suit, nous présentons en quoi consiste une méthodologie de vérification et nous décrivons ses deux faces, statique et dynamique.

Figure 1.1 Flux de conception et de vérification.

Adaptée de (Lam, 2005)

### 1.2.1 Méthodologie de vérification

Une méthodologie de vérification débute par un plan de vérification mettant en relief l'ensemble des fonctionnalités à vérifier dans le but de satisfaire les spécifications d'un système.

Pour surveiller l'avancement du plan de vérification, un historique des éléments vérifiés ainsi que les éléments qui restent à vérifier est conservé. La réalité et l'expérience démontrent que la vérification complète d'un ensemble de spécifications est très difficilement réalisable, voir même impossible. C'est pourquoi il existe une mesure de la qualité de la vérification, appelée couverture, qui consiste en un estimé du pourcentage de spécifications vérifiées. En général, la qualité d'une méthodologie de vérification dépend de la couverture atteinte et du temps requis pour atteindre cette couverture. Une bonne méthodologie de vérification cherche donc généralement à réduire le temps et maximiser la couverture de la vérification.

Les méthodologies de vérification peuvent être regroupées en deux catégories (Lam, 2005):

- **la vérification dynamique** basée sur la simulation;

- **la vérification statique** basée essentiellement sur des techniques et des modèles mathématiques pour vérifier le design.

### 1.2.2 Vérification dynamique

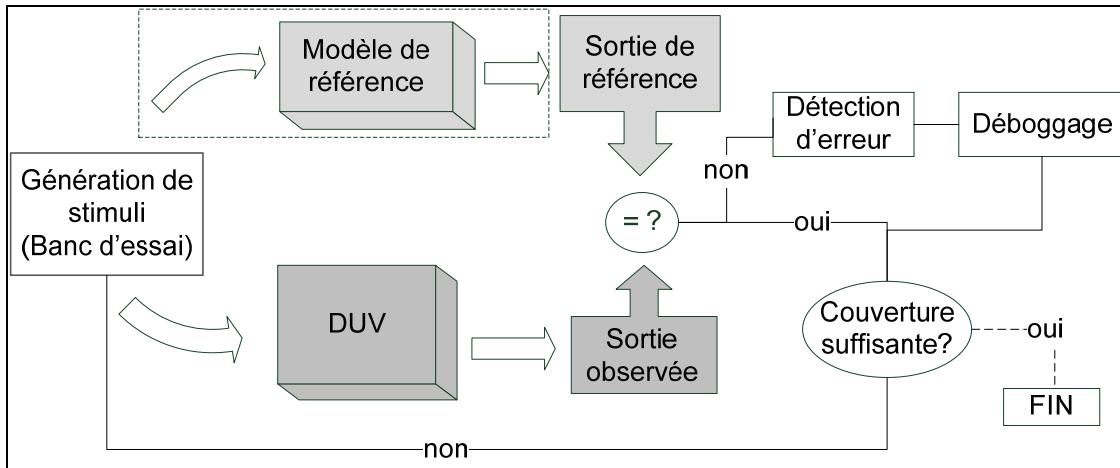

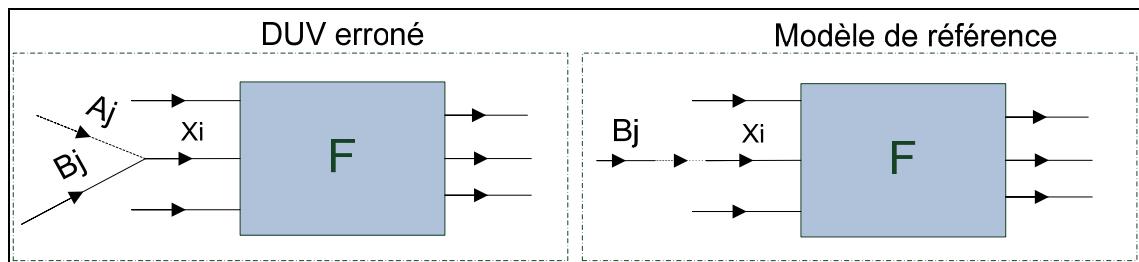

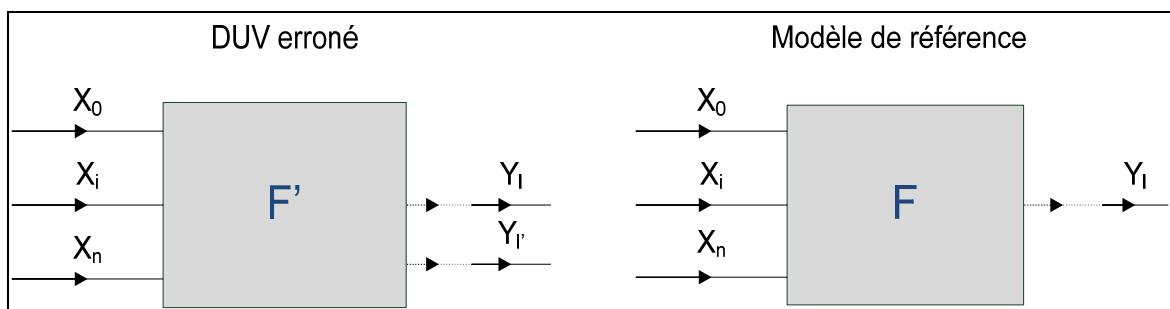

La vérification dynamique est l'approche la plus utilisée en vérification (Lam, 2005). Elle est basée sur la simulation du design. En effet, le DUV est soumis à un flux de vecteurs de vérification appelés stimuli, qui sont émis par un banc d'essai ou *testbench*, alors que la sortie du design est comparée à une sortie de référence afin de détecter les erreurs. Dans le cas où la sortie observée ne correspond pas à la sortie de référence, une erreur est détectée et le débogage est déclenché. La simulation prend fin lorsque la couverture atteinte est jugée suffisante. En utilisant une métrique de couverture, on peut voir les parties du design non simulées et créer des stimuli pour les couvrir. La Figure 1.2 décrit le processus de la vérification dynamique, le composant à l'intérieur du carré en pointillés étant optionnel. En effet, les sorties de référence peuvent être générées avant ou durant la simulation. Afin de les générer durant la simulation, le modèle de référence est simulé en parallèle avec le DUV.

Figure 1.2 La vérification dynamique.

Tirée de (Lam, 2005)

### Génération des stimuli

Les stimuli peuvent être générés préalablement à la simulation et lus à partir d'une base de données, ou encore être générés au cours de la simulation. La qualité de la simulation dépend de la couverture atteinte lors de leur application. Les techniques de génération de ces vecteurs de vérification diffèrent selon le type de ces derniers. On distingue :

- les vecteurs de vérification aléatoires: ces vecteurs de vérification sont générés à partir d'un algorithme de génération de valeurs aléatoires. Cet aspect aléatoire permet de couvrir les coins du design et les scénarios auxquels les concepteurs n'auraient peut-être pas pensé. Ces vecteurs permettent typiquement de détecter des erreurs dans ces espaces, ce qui élargit la couverture de la vérification. L'effort requis par cette méthode est minime dans la mesure où la génération aléatoire de vecteurs peut se faire automatiquement. La vérification basée sur ce type de stimuli est appelée vérification aléatoire (« *random verification* »);

- les vecteurs de vérification directs : ces vecteurs de vérification sont très spécifiques et visent des espaces déterminés du design, où les concepteurs sont conscients de la présence de certaines erreurs potentielles. Le concepteur établit une liste de scénarios spécifiques, où chaque scénario cible une erreur ou une partie de l'espace de design. Ceci demande un effort substantiel, le concepteur devant implémenter chacun des scénarios manuellement.

La vérification basée sur ce type de vecteurs est appelée vérification dirigée (« *directed verification* »);

- les vecteurs de vérification aléatoires basés sur les contraintes : ces vecteurs de vérification sont générés aléatoirement mais en respectant des contraintes spécifiques modélisant la fonctionnalité du DUV. Ce type de vérification conserve l'aspect aléatoire pour couvrir les détails manquants d'un scénario donné et sont plus productifs car ils sont dirigés par des contraintes représentant le design. Chaque slave de vérification décrit plusieurs scénarios. La vérification basée sur ce type de vecteurs est appelée vérification basée sur les contraintes (« *Constrained-based verification* »).

La génération de vecteurs de vérification reste une des étapes les plus exigeantes de la vérification, le but étant de produire avec un minimum d'effort un ensemble efficace de vecteurs permettant une bonne couverture et une simulation rapide.

### **Avantages et limitations de la vérification dynamique**

La vérification dynamique est la plus utilisée grâce à ses nombreux points forts (Lam, 2005) :

- l'aspect « *input driven* ». La vérification dynamique est basée sur des vecteurs d'entrée. Dans un premier temps, on génère ces vecteurs et dans un second temps on génère les sorties de référence correspondantes. Ceci est un avantage par rapport à la vérification formelle, dans laquelle le processus est inversé : le concepteur pense aux sorties désirables et laisse le vérificateur le prouver, d'où sa qualification de « *output driven* ». Il est beaucoup plus facile de penser « *input driven* » que « *output driven* »;

- l'aspect pseudo-aléatoire. En effet, les bugs ou les erreurs ont lieu souvent dans des régions que le concepteur ignore, et ce genre de vérification permet d'explorer ces régions en question. Les simulations pseudo-aléatoires peuvent utiliser des vecteurs au voisinage des vecteurs directs. En effet, si les vecteurs de vérification directs sont des points dans l'espace, les vecteurs aléatoires couvrent les régions entourant ces points. Donc pour décentrer la vérification et explorer toutes les régions possibles du design, les vecteurs pseudo-aléatoires sont utilisés en conjonction avec les vecteurs directs. Cette

approche permet une amélioration considérable de la couverture et du temps de simulation;

- la possibilité de vérification au niveau système. L'un des grands défis de la vérification est d'être exploitée au niveau système, ceci à cause de la complexité croissante des designs. La simulation ou la vérification dynamique permet de vérifier le design au niveau système sans se soucier de la taille et de la complexité de ce dernier.

La vérification dynamique présente aussi plusieurs limitations. Les défis auxquels elle fait face sont de plus en plus nombreux avec la croissance de la complexité des circuits (Lam, 2005):

- le temps de conception des bancs d'essai est énorme;

- la qualité des bancs d'essai est souvent médiocre;

- la couverture atteinte est habituellement insuffisante lorsque le temps alloué pour la vérification est limité;

- l'ingénieur n'est jamais sûr si le design est bien vérifié ou non;

- il y a souvent échec dans la détection des erreurs difficiles à vérifier, appelées « *corner case errors* » ou aussi les coins sombres.

Plusieurs méthodologies ont été développées pour améliorer la qualité de la vérification dynamique et surpasser ses limitations. Certains travaux seront présentés dans le chapitre 2 de revue de littérature.

### 1.2.3 Vérification statique

La vérification statique (Lam, 2005) diffère de celle basée sur la simulation par le seul fait qu'elle ne requiert pas de stimuli. Elle est basée essentiellement sur des techniques et des modèles mathématiques pour vérifier le design. Elle peut être classifiée en 2 grandes catégories : la vérification de propriété (« *property checking* ») (Baumgartner, 2002) et la vérification d'équivalence (« *equivalence checking* ») (Huang, 1998).

## **La vérification de propriété**

Un certain nombre de propriétés doivent être satisfaites lors du développement d'un design. Une approche classique de vérification, la vérification de propriété, consiste à : 1) construire un modèle complet  $S$  du comportement du système étudié (par exemple un graphe de flux de données, les différents modèles sont présentés en détails dans l'annexe I), 2) formaliser la propriété de correction attendue par une formule  $\Phi$ , et 3) utiliser un algorithme de vérification de modèle (« *Model-Checking* ») (Saidi, 2000) pour vérifier que  $S$  satisfait ou non  $\Phi$ . Une propriété est une description dupliquée du design et permet la vérification du design à travers la redondance. L'idée est d'explorer l'espace dans le but de trouver un point qui contredit la propriété. Si ce point existe alors la propriété échoue et ce point servira de contre-exemple, sinon la propriété est satisfaite.

La limitation majeure rencontrée dans ce genre de vérification est le temps mis pour déterminer les bonnes contraintes et pour débugger le système en cas d'échec de propriétés. Une alternative à l'exploration de l'espace existe et permet ainsi la vérification de propriétés. Il s'agit d'une approche basée sur les preuves de théorèmes. Dans une telle approche, la propriété est modélisée sous forme d'une proposition mathématique et le design sous forme d'entités mathématiques (i.e. un ensemble d'axiomes). L'objectif est de déterminer si les propositions (propriétés) peuvent être déduites des axiomes (système). Si c'est le cas, la propriété est vérifiée sinon elle échoue. Cette approche fait également face à plusieurs limitations, l'usager devant être familier avec les opérations internes des outils ainsi qu'avec les processus mathématiques formels de démonstration.

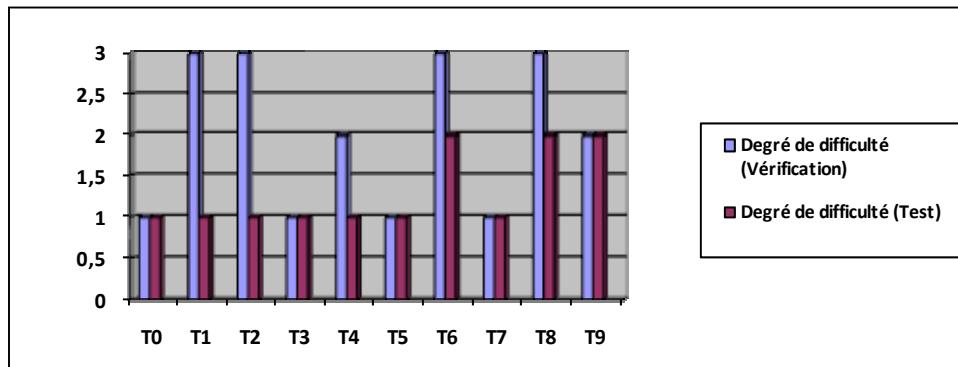

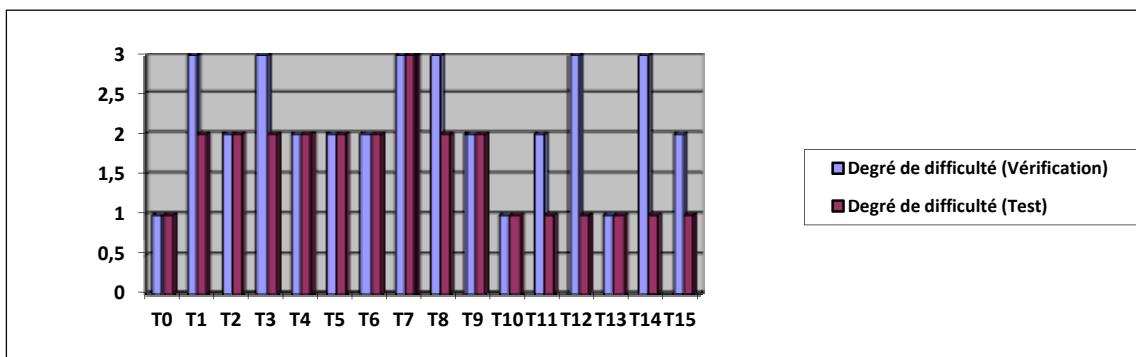

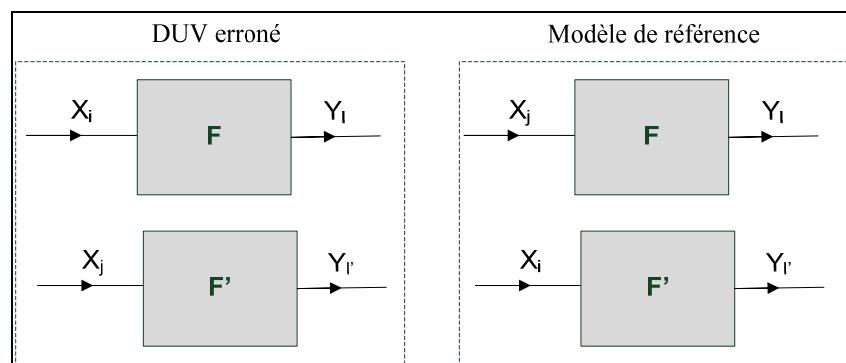

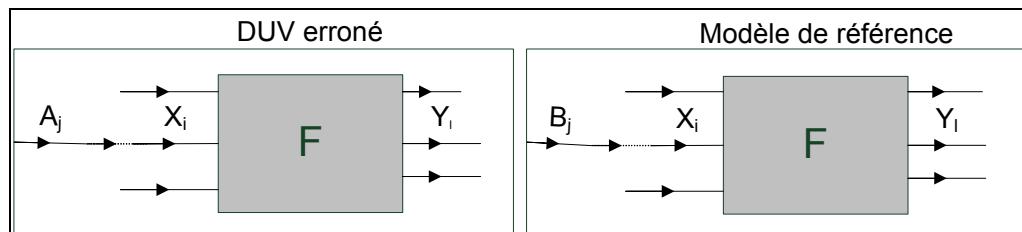

## **La vérification d'équivalence**